# ENERGY EFFICIENT AND ERROR RESILIENT NEUROMORPHIC COMPUTING IN VLSI

### A Dissertation

by

### YONGTAE KIM

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Peng Li             |

|---------------------|---------------------|

| Committee Members,  | Gwan Choi           |

|                     | Jose Silva-Martinez |

|                     | Rabi Mahapatra      |

| Head of Department, | Chanan Singh        |

December 2013

Major Subject: Electrical Engineering

Copyright 2013 Yongtae Kim

#### ABSTRACT

Realization of the conventional Von Neumann architecture faces increasing challenges due to growing process variations, device reliability and power consumption. As an appealing architectural solution, brain-inspired neuromorphic computing has drawn a great deal of research interest due to its potential improved scalability and power efficiency, and better suitability in processing complex tasks. Moreover, inherit error resilience in neuromorphic computing allows remarkable power and energy savings by exploiting approximate computing. This dissertation focuses on a scalable and energy efficient neurocomputing architecture which leverages emerging memristor nanodevices and a novel approximate arithmetic for cognitive computing.

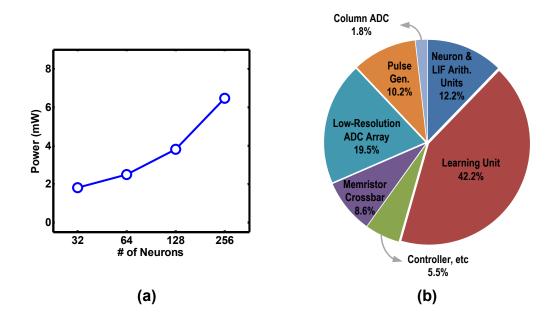

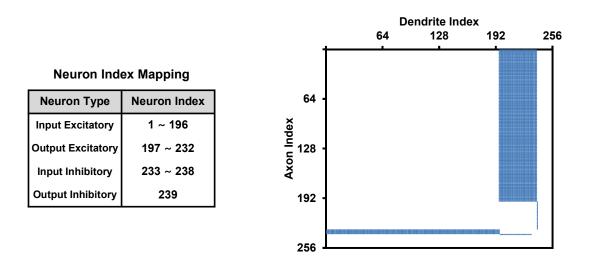

First, a brain-inspired digital neuromorphic processor (DNP) architecture with memristive synaptic crossbar is presented for large scale spiking neural networks. We leverage memristor nanodevices to build an  $N \times N$  crossbar array to store not only multibit synaptic weight values but also the network configuration data with significantly reduced area cost. Additionally, the crossbar array is accessible both column- and row-wise to significantly expedite the synaptic weight update process for on-chip learning. The proposed digital pulse width modulator (PWM) readily creates a binary pulse with various durations to read and write the multilevel memristors with low cost. Our design integrates N digital leaky integrate-and-fire (LIF) silicon neurons to mimic their biological counterparts and the respective on-chip learning circuits for implementing spike timing dependent plasticity (STDP) learning rules. The proposed column based analog-to-digital conversion (ADC) scheme accumulates the pre-synaptic weights of a neuron efficiently and reduces silicon area by using only one shared arithmetic unit for processing LIF operations of all N neurons. With 256 silicon neurons, the learning circuits and 64K synapses, the power dissipation and area of our design are evaluated as  $6.45 \ mW$  and  $1.86 \ mm^2$ , respectively, in a 90 nmCMOS technology.

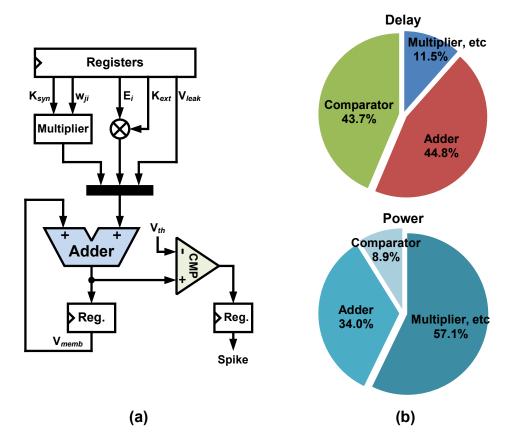

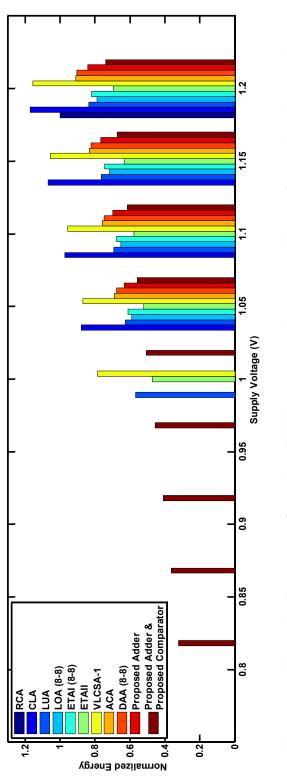

Furthermore, arithmetic computations contribute significantly to the overall processing time and power of the proposed architecture. In particular, addition and comparison operations represent 88.5% and 42.9% of processing time and power for digital LIF computation, respectively. Hence, by exploiting the built-in resilience of the presented neuromorphic architecture, we propose novel approximate adder and comparator designs to significantly reduce energy consumption with a very low error rate. The significantly improved error rate and critical path delay stem from a novel carry prediction technique that leverages the information from less significant input bits in a parallel manner. An error magnitude reduction scheme is proposed to further reduce amount of error once detected with low cost in the proposed adder design. Implemented in a commercial 90 nm CMOS process, it is shown that the proposed adder is up to  $2.4 \times$  faster and 43% more energy efficient over traditional adders while having an error rate of only 0.18%. Additionally, the proposed comparator achieves an error rate of less than 0.1% and an energy reduction of up to  $4.9 \times$  compared to the conventional ones. The proposed arithmetic has been adopted in a VLSI-based neuromorphic character recognition chip using unsupervised learning. The approximation errors of the proposed arithmetic units have been shown to have negligible impacts on the training process. Moreover, the energy saving of up to 66.5% over traditional arithmetic units is achieved for the neuromorphic chip with scaled supply levels.

# DEDICATION

To my wife

#### ACKNOWLEDGEMENTS

First and foremost, I am very grateful to have had the opportunity to work with a great research advisor Dr. Peng Li and would like to thank him with my deep respect for his valuable advice and consistent support during my doctoral studies at Texas A&M University. Dr. Li has actively encouraged me to move forward with new innovative research ideas and willingly shared his profound knowledge, deep insight and creative inspiration so I could learn the way of research from him. Also, I would like to thank my committee members Dr. Gwan Choi, Dr. Jose Silva-Martinez and Dr. Rabi Mahapatra for their constructive discussions and suggestions on my research, making this dissertation possible.

My appreciation goes to all the members in our research group for their knowledge, discussion and friendship. Particular thanks go to Yong Zhang and Qian Wang for the simulation and layout supports. Many friends in the department and the alumni of Korea University have made my stay of four years in College Station a pleasurable and unforgettable experience. I also want to acknowledge all my other friends who have consistently helped me at A&M for their considerable assistances.

From deep down in my heart, I would like to thank my parents and other family members for their devotion, support and encouragement. In particular, I would like to give special thanks to my wife for her unconditional love, trust, patience and sacrifice, leading me to successfully complete my Ph.D. studies.

Finally, the funding support from the Semiconductor Research Corporation is acknowledged.

### NOMENCLATURE

- ADC Analog-to-Digital Conversion/Converter

- ANN Artificial Neural Network

- CMOS Complementary Metal Oxide Semiconductor

- CLA/CLC Carry Lookahead Adder/Comparator

- DNP Digital Neuromorphic Processor

- EDAP Energy-Delay-Area Product

- EDC Error Detection and Correction

- EDEP Energy-Delay-Error Product

- EDP Energy-Delay Product

- FSM Finite State Machine

- LIF Leaky Integrate-and-Fire

- LSB Least Significant Bit

- LUT Look Up Table

- MSB Most Significant Bit

- PWM Pulse Width Modulation/Modulator

- RCA/RCC Ripple Carry Adder/Comparator

- SNN Spiking Neural Network

- STDP Spike Timing Dependent Plasticity

- VCO Voltage Controlled Oscillator

- VLSI Very Large Scale Integration

- WTA Winner-Take-All

# TABLE OF CONTENTS

|     |                                                       | F                                                                                                                                                                                                                                                                  | Page                                                         |

|-----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| AF  | BSTRA                                                 | CT                                                                                                                                                                                                                                                                 | ii                                                           |

| DE  | EDICA                                                 | TION                                                                                                                                                                                                                                                               | iv                                                           |

| AC  | CKNOV                                                 | WLEDGEMENTS                                                                                                                                                                                                                                                        | v                                                            |

| NC  | OMENO                                                 | CLATURE                                                                                                                                                                                                                                                            | vi                                                           |

| ТА  | BLE (                                                 | OF CONTENTS                                                                                                                                                                                                                                                        | vii                                                          |

| LIS | ST OF                                                 | FIGURES                                                                                                                                                                                                                                                            | x                                                            |

| LIS | ST OF                                                 | TABLES                                                                                                                                                                                                                                                             | xiii                                                         |

| 1.  | INTR                                                  | ODUCTION                                                                                                                                                                                                                                                           | 1                                                            |

|     | 1.2 A                                                 | Digital Neuromorphic Processor for Cognitive ComputingApproximate Arithmetic for Energy Efficient NeurocomputingOutline of the Dissertation                                                                                                                        | $2 \\ 3 \\ 5$                                                |

| 2.  | BACK                                                  | KGROUND AND RELATED WORKS                                                                                                                                                                                                                                          | 7                                                            |

|     | 22<br>22<br>22<br>22<br>2.2<br>2.2<br>2.3<br>4<br>2.3 | Brain-Inspired Neuromorphic Computing2.1.1Biological Motivation2.1.2Artificial Neural Networks2.1.3Spiking Neural Networks2.1.4Silicon Neuron Circuits2.1.5Neuromorphic VLSI SystemsApproximate ComputingEmerging Memory TechnologiesObjective of the Dissertation | $7 \\ 8 \\ 11 \\ 18 \\ 22 \\ 26 \\ 30 \\ 32 \\ 36 \\ 36 \\ $ |

| 3.  |                                                       | ONFIGURABLE DIGITAL NEUROMORPHIC PROCESSOR WITHRISTIVE CROSSBAR ARRAY                                                                                                                                                                                              | 39                                                           |

|     | 3<br>3.2 M<br>3                                       | Digital Neuromorphic Processor Architecture                                                                                                                                                                                                                        | 39<br>39<br>42<br>45<br>45<br>48                             |

|    |             | 3.2.3 Memristive Crossbar Array and Cells                                                                                                           | 9 |

|----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    |             | 3.2.4 Digital Pulse Width Modulation for Memristive Synaptic Cell 50                                                                                | 0 |

|    | 3.3         | Building Block Implementations                                                                                                                      |   |

|    |             | 3.3.1 Memristor Readout $\ldots \ldots 52$                             |   |

|    |             | 3.3.2 Neuron and LIF Arithmetic Units                                                                                                               |   |

|    |             | 3.3.3 Learning Unit                                                                                                                                 | 8 |

|    | 3.4         | Implementation of the Neuromorphic Processor and Simulation Re-                                                                                     |   |

|    |             | sults                                                                                                                                               |   |

|    |             | 3.4.1 Column ADC Performance                                                                                                                        |   |

|    |             | 3.4.2 Overall Processor Performance                                                                                                                 | 4 |

|    |             | 3.4.3 Application of the Neuromorphic Processor for Character Recog-                                                                                | _ |

|    | ٥. <b>٢</b> | nition System                                                                                                                                       |   |

|    | 3.5         | Summary 69                                                                                                                                          | 9 |

| 4. | ENE         | CRGY EFFICIENT APPROXIMATE ARITHMETIC    7                                                                                                          | 1 |

|    | 4.1         | Proposed Approximate Adder                                                                                                                          | 1 |

|    |             | 4.1.1 Approximate Adder Architecture                                                                                                                | 1 |

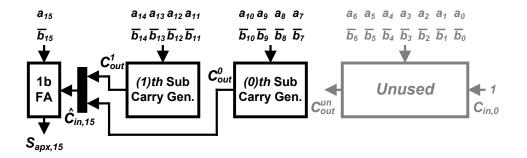

|    |             | 4.1.2 Error Rate Analysis                                                                                                                           | 4 |

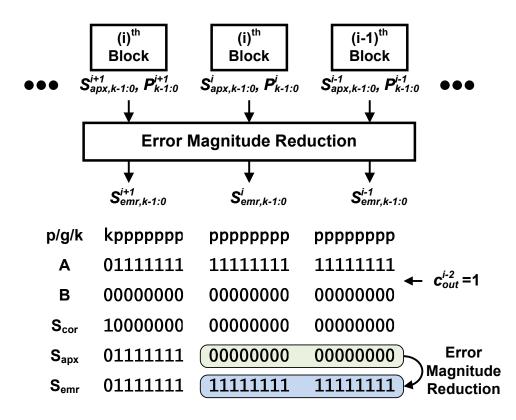

|    |             | 4.1.3 Error Magnitude Reduction Scheme                                                                                                              | 7 |

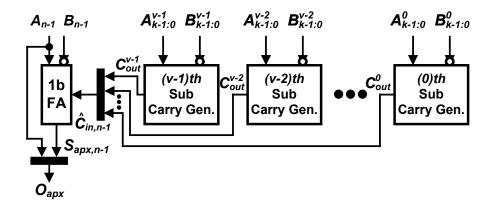

|    | 4.2         | Proposed Approximate Comparator                                                                                                                     |   |

|    |             | 4.2.1 Approximate Comparator Architecture                                                                                                           |   |

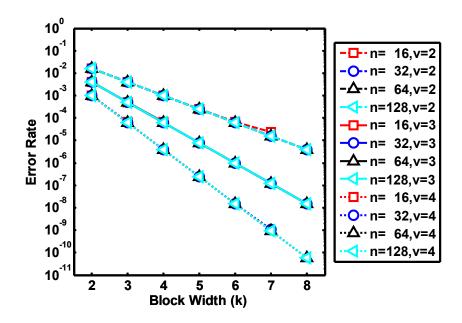

|    |             | 4.2.2 Error Rate Analysis                                                                                                                           |   |

|    | 4.3         | Simulation Results                                                                                                                                  |   |

|    |             | 4.3.1 Error Rate of the Proposed Approximate Adder                                                                                                  |   |

|    |             | 4.3.2 Performance of the Proposed Approximate Adder                                                                                                 |   |

|    |             | 4.3.3 Comparison with Seven Other Approximate Adders 88                                                                                             |   |

|    |             | 4.3.4 Comparison on Error-Free Operations                                                                                                           |   |

|    |             | <ul> <li>4.3.5 Error Rate of the Proposed Approximate Comparator 92</li> <li>4.3.6 Performance of the Proposed Approximate Comparator 92</li> </ul> |   |

|    | 4.4         | Summary                                                                                                                                             |   |

|    |             |                                                                                                                                                     | J |

| 5. |             | LICATION OF APPROXIMATE ARITHMETIC TO NEUROMOR-                                                                                                     |   |

|    | PHI(        | $C COMPUTING \dots \dots$                     | ő |

|    | 5.1         | Evaluation Environment                                                                                                                              |   |

|    | 5.2         | Impacts of Approximation Errors on Neuromorphic Applications 99                                                                                     | 9 |

|    |             | 5.2.1 Approximate Adder Error Effects                                                                                                               |   |

|    |             | 5.2.2 Approximate Comparator Error Effects                                                                                                          | 4 |

|    | 5.3         | Energy Efficiency of LIF Neurons with Approximate Adders and Com-                                                                                   |   |

|    | <b>.</b> .  | parators with Supply Voltage Scaling 108                                                                                                            | Ó |

|    | 5.4         | Energy Efficiency during the Training Process with Supply Voltage                                                                                   | _ |

|    |             | Scaling $\ldots \ldots \ldots$      |   |

|    | 5.5         | Summary 110                                                                                                                                         | J |

| 6. | CON         | VCLUSION AND FUTURE WORK                                                                                                                            | 1 |

| 6.1   | Conclus | sion   |  |   |   |  |   |   |   |   |   |   |  |   |   |   |   |   |   |   |   |   |   |   | 111 |

|-------|---------|--------|--|---|---|--|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|-----|

| 6.2   | Future  | Work . |  | • | • |  | • | • | • | • | • | • |  | • | • | • | • | • | • | • | • | • | • | • | 113 |

| REFER | ENCES   |        |  |   |   |  |   |   |   |   |   |   |  |   |   |   |   |   |   |   |   |   |   |   | 117 |

# LIST OF FIGURES

# FIGURE

# Page

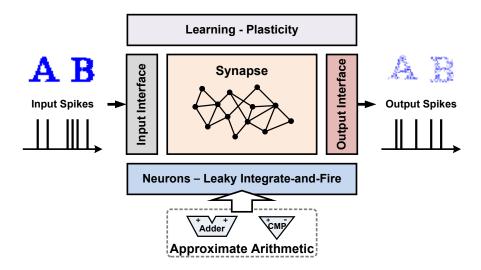

| 1.1  | Application of approximate arithmetic in neuromorphic computing.                                                                                                     | 4  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Biological neuron anatomy [57]                                                                                                                                       | 9  |

| 2.2  | Artificial neuron.                                                                                                                                                   | 12 |

| 2.3  | Activation functions: (a) step, (b) piecewise linear, and (c) sigmoid with different parameter $a$ .                                                                 | 14 |

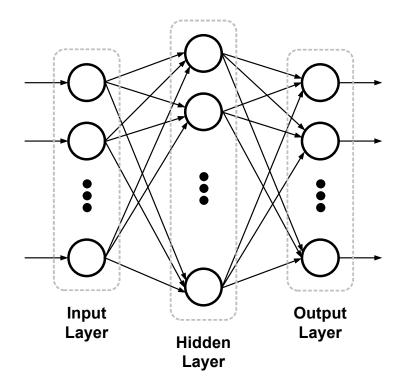

| 2.4  | Feedforward artificial neural network architecture                                                                                                                   | 16 |

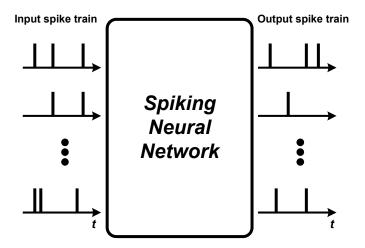

| 2.5  | Spiking neural network                                                                                                                                               | 18 |

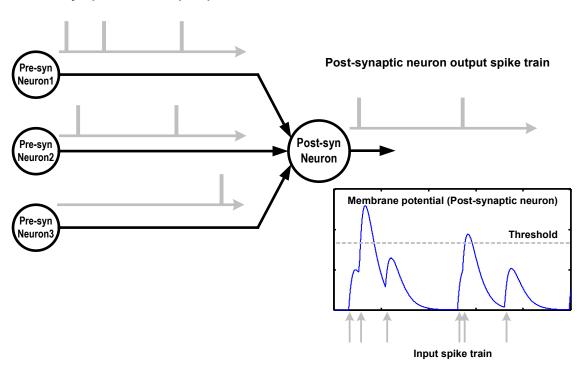

| 2.6  | Spiking neuron behavior                                                                                                                                              | 20 |

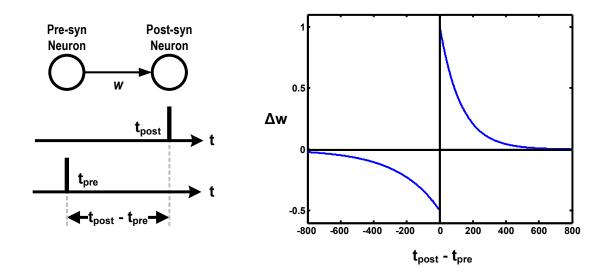

| 2.7  | Spike timing dependent plasticity                                                                                                                                    | 21 |

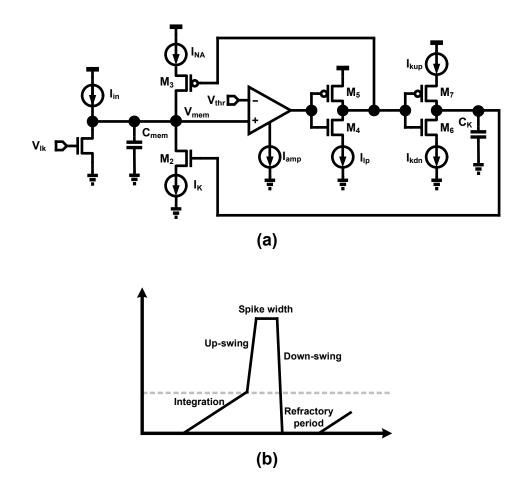

| 2.8  | Analog silicon neuron: (a) schematic and (b) timing diagram [29]                                                                                                     | 23 |

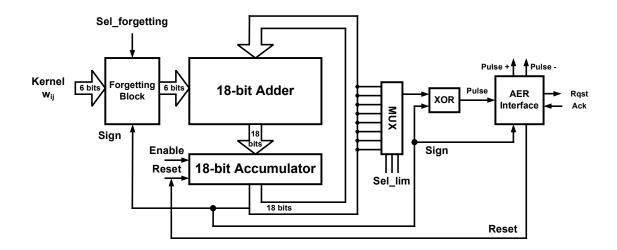

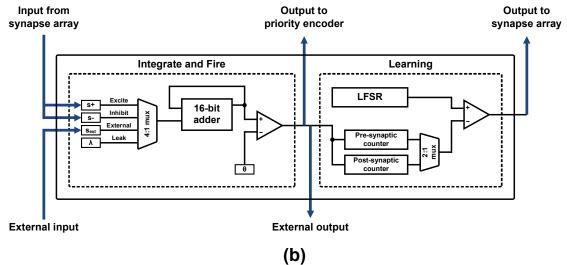

| 2.9  | Digital silicon neuron [6]                                                                                                                                           | 25 |

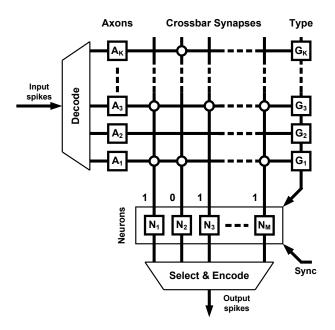

| 2.10 | Block diagram of digital neurosynaptic core [46]                                                                                                                     | 27 |

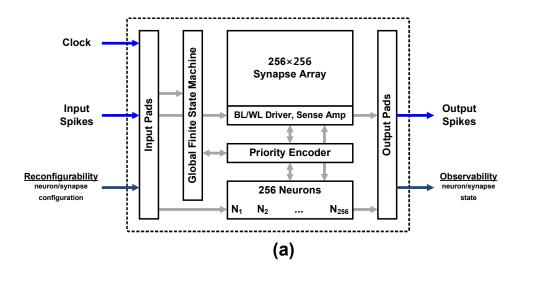

| 2.11 | Block diagram of (a) neuromorphic chip and (b) silicon neuron [58]. $% \left[ \left( {{{\bf{x}}_{{\rm{s}}}} \right) \right) = \left( {{{\bf{x}}_{{\rm{s}}}} \right)$ | 29 |

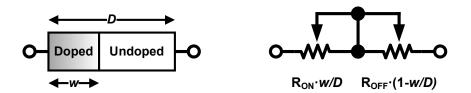

| 2.12 | Memristive device structure (left) and variable resistance model (right)<br>[63]                                                                                     | 34 |

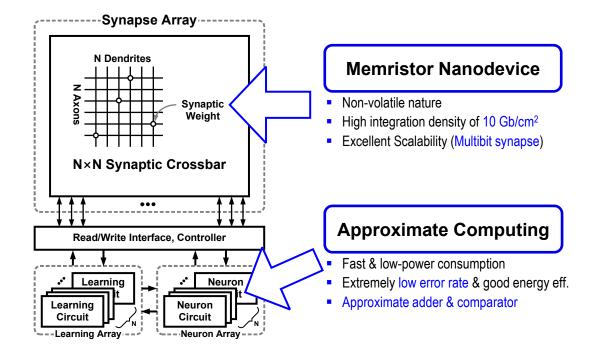

| 2.13 | Energy efficient and error resilient neuromorphic computing in VLSI.                                                                                                 | 36 |

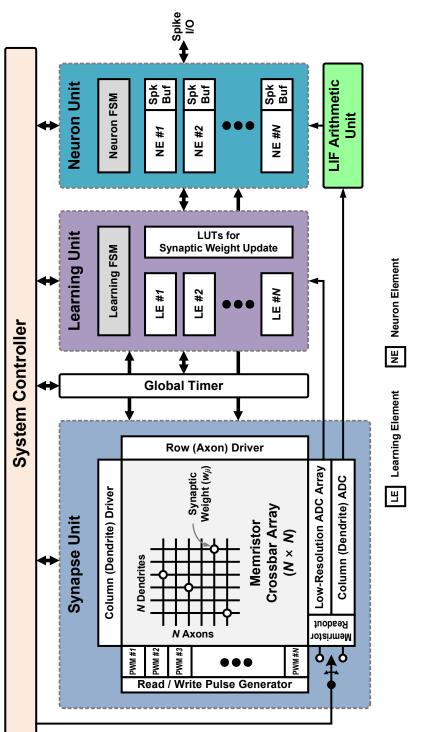

| 3.1  | Block diagram of the proposed digital neuromorphic processor archi-<br>tecture.                                                                                      | 40 |

| 3.2  | Flow diagram of the proposed neuromorphic processor                                                                                                                  | 42 |

| 3.3  | Memristor sensing schemes by (a) load resistor and (b) summing am-<br>plifier                                                                                        | 46 |

| 3.4  | Memristor level partitions by equal conductance                                                                                                                      | 48 |

| 3.5  | Proposed synaptic crossbar array and CMOS/memristor hybrid synap-<br>tic cell                                                  | 50 |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

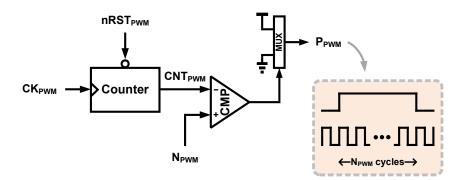

| 3.6  | Digital pulse width modulator                                                                                                  | 51 |

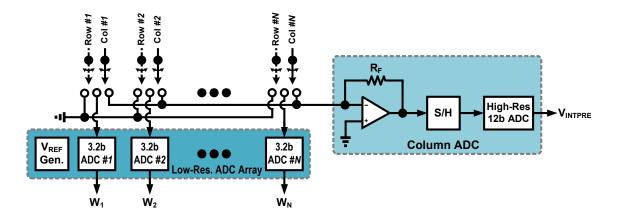

| 3.7  | Proposed memristor readout block consisting of column ADC and low-resolution ADC array.                                        | 52 |

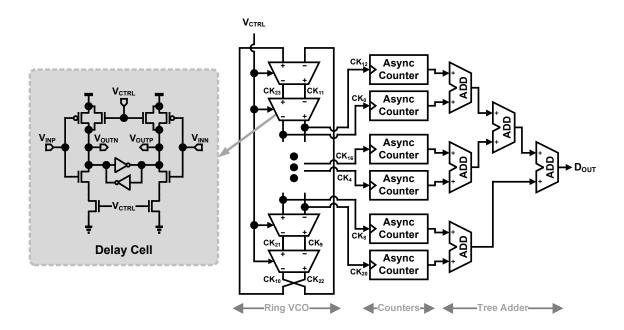

| 3.8  | Block diagram of VCO based ADC and proposed delay cell. $\ldots$ .                                                             | 55 |

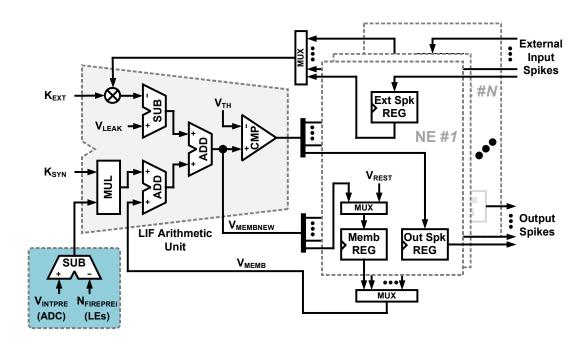

| 3.9  | Neuron elements with the LIF arithmetic unit                                                                                   | 56 |

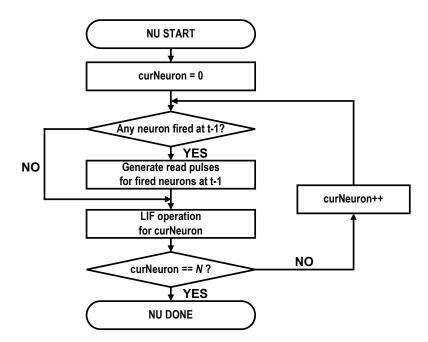

| 3.10 | Flowchart of the processing of the neuron unit                                                                                 | 57 |

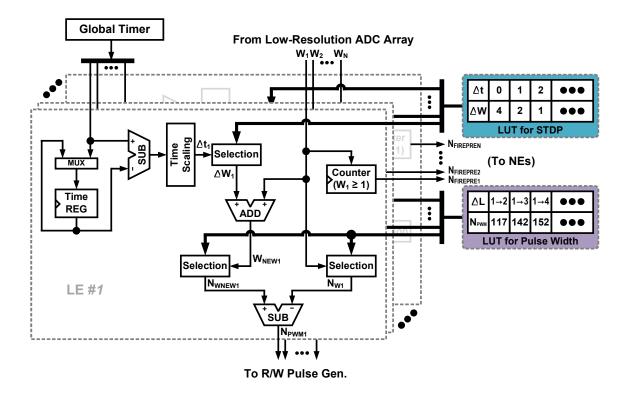

| 3.11 | Learning elements with global timer and shared LUTs                                                                            | 59 |

| 3.12 | Flowchart of the processing of the learning unit                                                                               | 60 |

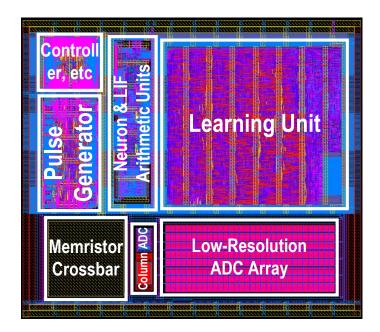

| 3.13 | Layout of the neuromorphic processor with 256 neurons and 65,536 synapses                                                      | 62 |

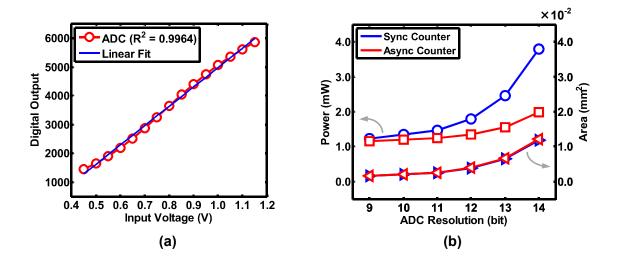

| 3.14 | Column ADC performance: (a) input-to-output characteristics and (b) power and area as functions of counter type and resolution | 63 |

| 3.15 | Neuromorphic processor performance: (a) power and (b) area break-<br>down                                                      | 64 |

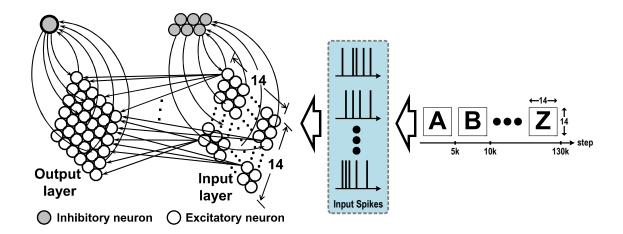

| 3.16 | Network for character recognition and training for alphabets                                                                   | 66 |

| 3.17 | Neuron index mapping and synaptic connections of the crossbar array.                                                           | 67 |

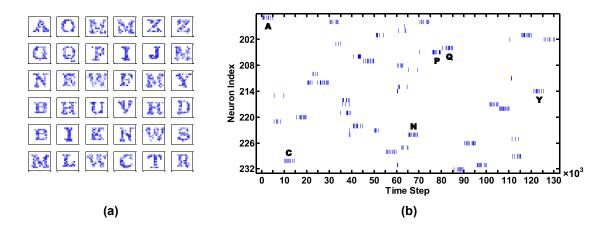

| 3.18 | Learning results for network: (a) receptive fields after training and (b) spike rasters for output neurons                     | 68 |

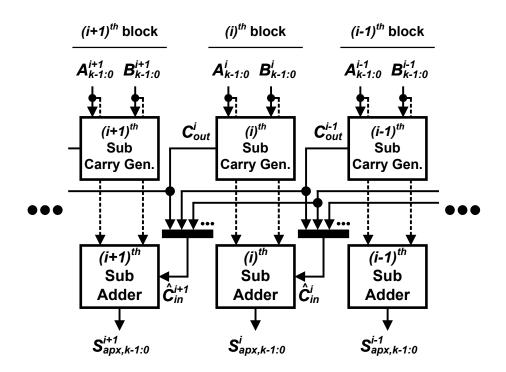

| 4.1  | Block diagram of the proposed approximate adder.                                                                               | 72 |

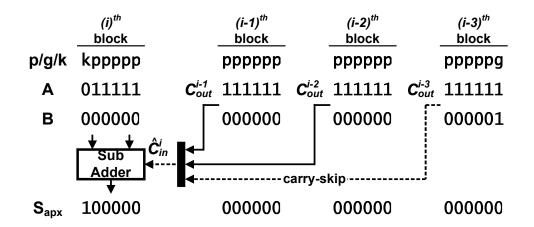

| 4.2  | Proposed carry prediction using parallel carry-skip ( $k=6, v=3$ )                                                             | 73 |

| 4.3  | Block diagram of the error magnitude reduction and an example of its operation $(k=8, v=2)$ .                                  | 78 |

| 4.4  | Block diagram of the proposed approximate comparator.                                                                          | 79 |

| 4.5  | Example of the comparator configuration $(n=16, k=4, v=2)$                                                                     | 81 |

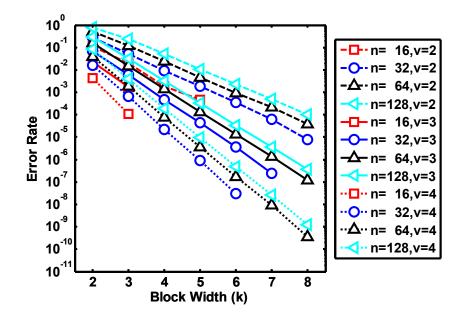

| 4.6  | Error rates of the proposed adder under different $n, k$ and $v. \ldots$                                                       | 84 |

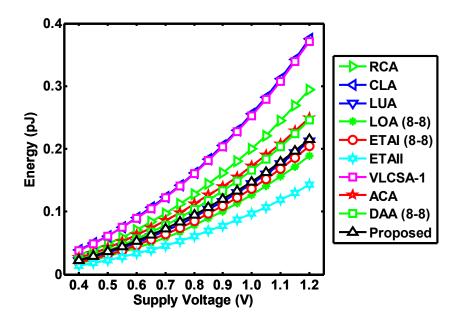

| 4.7  | Energy comparison under supply scaling                                                                                         | 89 |

| 4.8 | Error rates of the proposed comparator with various $n, k$ and $v. \ldots$                                                                                    | 91  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Digital LIF neuron: (a) block diagram and (b) delay and power break-<br>downs                                                                                 | 97  |

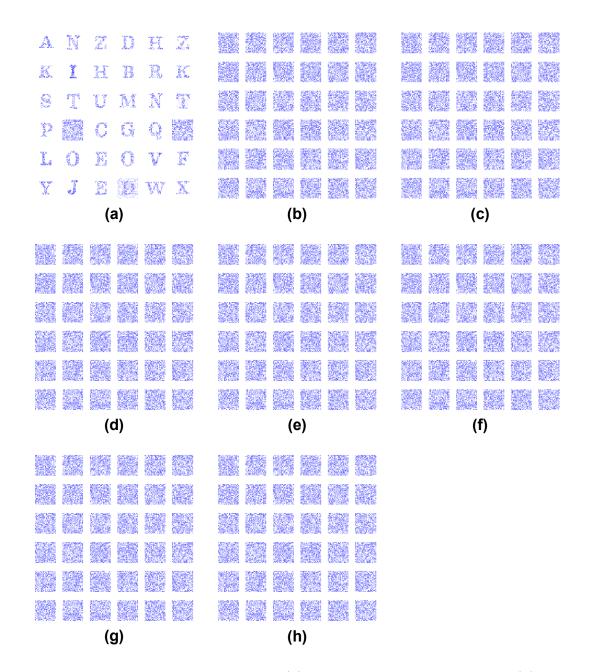

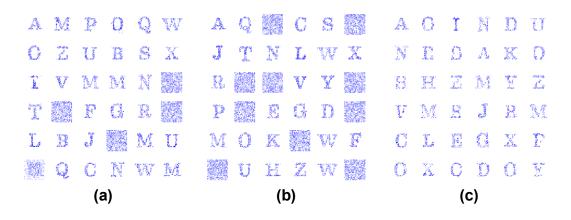

| 5.2 | (a) Input character patterns and (b) receptive fields with 16-bit accurate adders.                                                                            | 99  |

| 5.3 | Receptive fields with 16-bit (a) proposed approximate adder, (b) LUA, (c) LOA (8-8), (d) ETAI (8-8), (e) ETAII, (f) VLCSA-1, (g) ACA and (h) DAA (8-8).       | 101 |

| 5.4 | Receptive fields with 16-bit (a) LOA (13-3), (b) ETAI (15-1) and (c) DAA (11-5). $\ldots$                                                                     | 103 |

| 5.5 | Receptive fields with 16-bit (a) accurate adder with proposed com-<br>parator and (b) proposed adder with proposed comparator                                 | 104 |

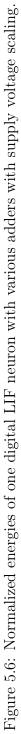

| 5.6 | Normalized energies of one digital LIF neuron with various adders<br>with supply voltage scaling.                                                             | 106 |

| 5.7 | Normalized energy consumptions by all the digital LIF neurons of the network while training with various adders and comparators under supply voltage scaling. | 109 |

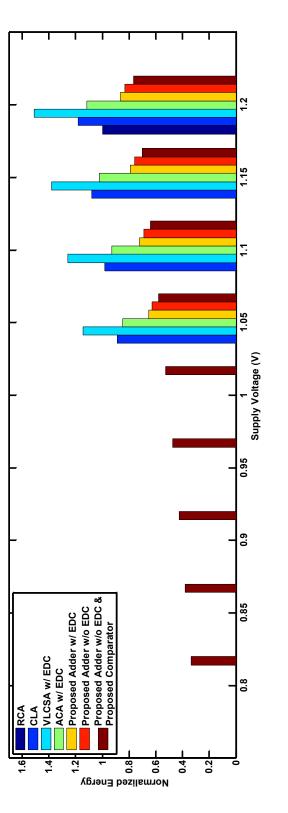

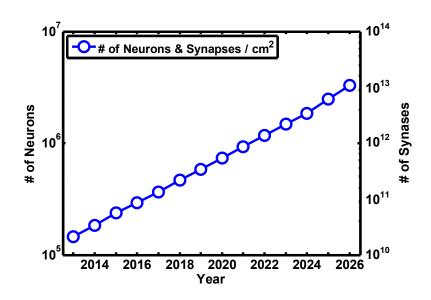

| 6.1 | Neuron and synapse integration densities as a function of technology.                                                                                         | 113 |

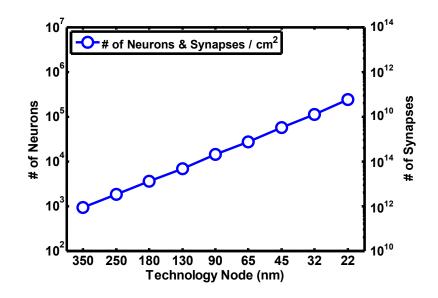

| 6.2 | Trends of gate length and power supply [70]                                                                                                                   | 115 |

| 6.3 | Scaling trend of neuron and synapse integration                                                                                                               | 115 |

### LIST OF TABLES

Page

### TABLE

#### Normalized write times to change one level of memristor conductance 3.1 $(R_{ON}=10K\Omega, R_{OFF}=500K\Omega, V_{WRITE}=1.2V)$ .... 483.2Neuromorphic processor implementation summary. 63 4.1Proposed adder with different n, k and $v, \ldots, \ldots, \ldots, \ldots$ 854.2Comparison with other 16-bit adders. 86 Approximate adders with error detection and correction. . . . . . 91 4.34.4924.5945.1Error rates and average error magnitudes of various adders during

#### 1. INTRODUCTION

The human brain mediates and produces our thoughts, actions, memory, feelings and other complex tasks. All these, however, are accomplished with great energy and space efficiency by the brain. In contrast, to achieve the same, the man-made conventional Von Neumann machines may require tremendous power, energy and space resources for computation, communication and memory if it is all possible [46]. To date, implementing the Von Neumann architecture faces grand challenges due to growing process variations, device reliability and power consumption. As an appealing architectural solution, brain-inspired neuromorphic computing has emerged as a promising solution to overcome these underlying constraints. It may be wellsuited for processing complex tasks, such as character or image recognition, classification and language learning and enjoy greater power efficiency and scalability [48, 58, 46, 59, 4, 43].

Furthermore, brain-inspired architectures may offer inherit error resilience and fault tolerance, which is very appealing for large-scale integration in scaled VLSI technologies. This inherit error resilience in neuromorphic computing allows remarkable power and energy savings by adopting approximate computing, which has drawn a significant research amount of interest in order to remedy the increasing energy efficiency challenges [21, 60, 8]. The key observation of approximate computing is that many applications, such as digital signal processing (DSP) and neuromorphic systems, have inherent error resilience, and hence 100% precision in computation is not required. This provides opportunities for energy saving by relaxing computation accuracy while achieving an acceptable processing quality. Particularly, the core of many DSP and neuromorphic applications lies in processing specific kernel functions, which occupy a significant portion of silicon area and computation time [49, 26]. For instance, MPEG motion estimation heavily performs the L1-norm arithmetic for sum of absolute difference (SAD) calculation [66] and spiking neural networks use the leaky integrate-and-fire (LIF) operation to mimic neuron behavior [58]. Obviously, adders are the primary component for building these arithmetic kernel functions. In addition, comparators are indispensable to determine firing activities in the LIF operation of neuromorphic applications.

To this end, this dissertation proposes two hardware design techniques for scalable and energy efficient neurocomputing applications: 1) reconfigurable digital neuromorphic processor (DNP) with memristive synaptic crossbar and 2) energy efficient approximate arithmetic for neuromorphic VLSI systems.

#### 1.1 Digital Neuromorphic Processor for Cognitive Computing

The first contribution of this dissertation includes a reconfigurable neuromorphic processor with memristive synaptic crossbar for cognitive computing. We propose a reconfigurable digital neuromorphic architecture comprising a memristive crossbar, an array of digital LIF spiking neurons and on-line learning circuits that support spike timing dependent plasticity (STDP) learning mechanisms. We leverage the memristor nanodevice to implement on-chip synaptic weight storage with low-cost since the memristor provides non-volatility, excellent scalability and high density of  $10 \ Gb/cm^2$  or more [23, 72]. To implement a multilevel memristor synaptic memory, we systematically analyze the memristor device in terms of programming time and level partitioning. We also investigate memristor readout schemes to more efficiently perform digital LIF operations with the crossbar structure and present a low-cost digital pulse width modulation (PWM) scheme for writing the memristor. While the previous analog-to-digital converter (ADC) design in [36] has a bottleneck of overall power dissipation, we address this limitation by optimizing the VCO based column ADC through the introduction of an asynchronous counter to measure the VCO frequency in digital form. In the proposed DNP, the  $N \times N$  memristive synaptic array, which stores both multibit synapse values and network configuration data, can be accessed both column- and row-wise to speed up the synaptic weight update process. The proposed column ADC effectively accumulates pre-synaptic weights and allows a single adder and comparator to be shared among all N neurons to perform LIF operations without degrading throughput. This leads to a considerable silicon area reduction and its digital implementation style is scalable for large scale integration.

When implemented in a commercial 90 nm CMOS technology, a 256 neuron design with a 256×256 synaptic array based on the proposed neuromorphic architecture has an estimated area of 1.86  $mm^2$  and power consumption of 6.45 mW under the regular supply voltage of 1.2 V, respectively. The proposed neuromorphic architecture is rather flexible and can be configured to various network topologies to support to a range of cognitive learning applications. To demonstrate its potential application, we configure our DNP to realize a two-layer spiking network with over two hundreds silicon neurons for character recognition with unsupervised learning.

1.2 Approximate Arithmetic for Energy Efficient Neurocomputing

Our second contribution is to apply an approximate computing scheme to the neuromorphic hardware design for considerable energy saving (see Figure 1.1). To achieve this, we propose a novel approximate adder with a parallel carry-skip scheme. While reducing the worst-case carry propagation delay, this carry-skip scheme allows for highly accurate carry prediction, making it possible to either speed up addition operations or reduce energy dissipation by lowering the supply voltage. The signif-

Figure 1.1: Application of approximate arithmetic in neuromorphic computing.

icantly improved error rate and critical path delay stem from the employed carry prediction technique that leverages the information from less significant input bits in a parallel manner. An error magnitude reduction scheme is proposed to further reduce amount of error once detected with low cost. Our adder design is rather flexible in the sense that a low-overhead error correction logic can be readily included to achieve error-free operations at the cost of one additional clock cycle. Additionally, we extend our approximate arithmetic scheme to comparator design and present a complete error rate analysis for the proposed arithmetic units. We extensively compare our approximates designs with a large number of existing accurate and approximate adders and comparators and show the large improvements in area, power, energy, timing and error rate brought by our design technique. To evaluate the performance of our approximate arithmetic units for neurocomputing applications, we present an efficient evaluation methodology to analyze large VLSI-based spiking neural networks with over a thousand silicon neurons for character recognition. We extensively study the error tolerance of the network, the overall energy consumption of digital LIF neurons during the learning process and its dependency on the underlying arithmetic units.

Implemented in a commercial 90 nm CMOS process, it is shown that the proposed adder is up to 2.4× faster and 43% more energy efficient over traditional adders while having an error rate of only 0.18%. In addition, the proposed comparator achieves an error rate of less than 0.1% and an energy reduction of up to 4.9× compared to the conventional ones. To evaluate the performance of the proposed arithmetics under neuromorphic applications, we develop a behavioral evaluation approach for a VLSI-based neuromorphic character recognition chip using unsupervised learning. The approximation errors of the proposed adder and comparator have been shown to have negligible impact on the training process while other approximate adders lead to unacceptable level of performance degradation. Furthermore, the proposed adder and comparator enable the overall energy reductions of up to 66.5% over traditional arithmetic units for the digital neuron circuits during the training process with the scaled supply.

#### 1.3 Outline of the Dissertation

The remainder of this dissertation is organized as the follows. Section 2 describes the background of brain-inspired neuromorphic and approximate computing, and the related works in the literature. The memristor nanodevice leveraged for synaptic array is also introduced in Section 2. The reconfigurable digital neuromorphic processor with memristive synaptic crossbar and its application for the character recognition system with unsupervised learning are presented in Section 3. After proposing energy efficient approximate arithmetic units in Section 4, the impacts of the approximation errors on the neurocomputing application and the energy efficiency analysis of the proposed approximate units for the neuromorphic hardware design are presented in Section 5. Finally, we conclude this dissertation and discuss the future works in Section 6.

#### 2. BACKGROUND AND RELATED WORKS

This section describes an overview of neuromorphic and approximate computing paradigms. It begins with the biological motivation of neuromorphic computing, then gives reviews of artificial and spiking neural networks and their learning algorithms. It also deals with the existing designs of silicon neurons and neuromorphic VLSI systems to mimic the biological brain on silicon, and discusses their key design issues and limitations. Next, it introduces a notion of approximate computing and several design approaches of the approximate adder, which is the primary component in approximate computing, are briefly reviewed and their advantages and disadvantages are presented as well. The overview of the memristor nanodevice, which is employed in our digital neuromorphic processor as on-chip storage to maintain a huge number of synaptic weight values, is given. Finally, it clarifies the objective of this dissertation.

### 2.1 Brain-Inspired Neuromorphic Computing

Today's Von Neumann computers are able to not only deal with very complicated numerical and algorithmic computations and procedural control tasks, such as sorting, but also store huge amount of data. Thus, they have been widely used for solving these complicated problems steadily which may be hard to be handled by humans. On the other hand, traditional machines may be limited by many other kinds of tasks that human beings can process without difficulties, such as character or image recognition, text reading and language learning. Importantly, the humans adapt to new situations and accumulate information and knowledge by an amazing ability of the brain, learning. In other words, when faced with a new situation, they make a proper decision and perform an appropriate behavior based on the acquired knowledge through the learning or training processes. Incredibly, the human brain processes these tasks much more energy efficiently than the conventional computers. In general, biological neurons are  $10^6 \times$  slower than silicon logic gates [20]. Silicon chips operate with a clock period in the range of the nanoseconds ( $10^{-9}$  sec.) while neural events happen in the millisecond ( $10^{-3}$  sec.) range. The slower operating speed of the biological neurons may have contributed to the brain's results in exceptionally good energy efficiency. Specifically, the brain consumes approximately  $10^{-16}J$  per operation per second, whereas the traditional computer requires an energy level of about  $10^{-6}J$  per operation per second [20].

Historically, from the past years, neuroscientists have devoted intense efforts towards investigating the human brain. As part of these efforts, a landmark work in modeling the dynamics of a biological neuron was conducted by Hodgkin and Huxley [24]. After that, a variety of computational neuron models, such as FitzHugh-Nagumo [17, 52], Hindmarsh-Rose [22], and Morris-Lecar [51], have been proposed. Also, scientists have studied the interactions among neurons through synapses. The brain and neuron modeling are greatly facilitated by the rapid advance of digital computers. However, simulating a large number of these computational neurons is still challenging to date because it requires tremendous computing power and simulation time. Meanwhile, neuromorphic engineers have been trying to reproduce the neuron behaviors by morphing their anatomy and physiology into silicon chips for simulating the human or mammal's brains in real-time [48, 58, 46, 59, 4, 43]. The hardware implementation provides very fast simulation of neural networks with less power consumption.

#### 2.1.1 Biological Motivation

Artificial or spiking neural networks are the core of brain-inspired neuromorphic computing systems. Their development has been motivated in the part by the insights obtained from biological nervous systems (e.g. the human brain) which are an extremely intricate interconnection of neurons. As an example, the adult human brain is estimated to contain a densely interconnected network of approximately  $10^{11}$ neurons and more than  $10^{14}$  synapses [13]. Neurons are the primary elements of a nervous system and are specialized types of biological cells that are electrically excitable. Neurons process and transmit information in the form of cellular signals which are either electrical or chemical for long and short distances, respectively. A considerable number of neurons connect to each other to form a neural network via synapses, which are specialized connections among the neurons.

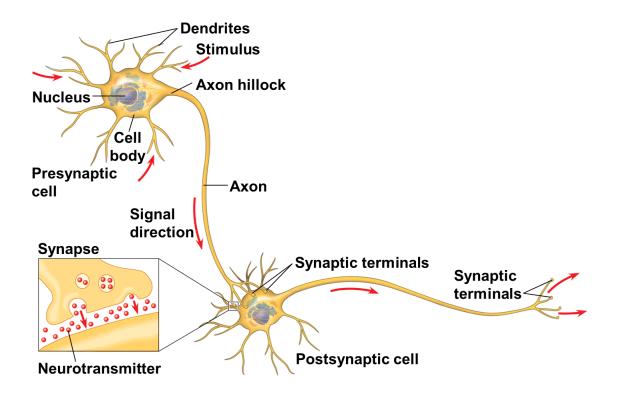

Figure 2.1: Biological neuron anatomy [57].

mainly consists of three functionally distinct parts, which are the cell body (often called the soma), axon and dendrites. The cell body is the heart of the neuron and includes the nucleus where most protein synthesis occurs. The dendrites of the neuron are highly branched extensions and receive nerve signals from other neurons. A neuron may have numerous dendrites and their overall shape is referred to as a dendritic tree. On the other hand, the neuron has only one axon that is typically thinner and much longer than the dendrites and transmits the signals to other cells via synapses. In short, the dendrites and axon act as the signal receiver and transmitter, respectively. Information of the nervous system is encoded in the form of an electrical impulse which is called the action potential or spike and the pulse is transmitted from a pre-synaptic neuron to a post-synaptic one. The action potentials are created by the axon hillock that is a specialized part of the cell body and connects to the axon. A neuron processes information by integrating the incoming nerve signals that come from its pre-synaptic neurons and the action potential is generated when the membrane potential of the neuron reaches a certain threshold. Briefly, the neuron transmits the information using the action potentials or spikes.

A synapse is basically a junction between two neurons, which are referred to as the pre-synaptic and post-synaptic neurons, respectively. In fact, neurons do not physically touch each other and are separated by a small space called the synaptic cleft. When an action potential arrives at the axon terminal, the pre-synaptic neuron releases chemical neurotransmitter molecules into the synaptic cleft and they diffuse across the synaptic junction, leading to interneuron communication at the synapse. These chemical molecules bind to the receptor which is placed on the opposite side of the cleft (*i.e.* post-synaptic neuron) and cause the membrane potential of the postsynaptic neuron to change. The type of the receptor and neurotransmitter employed at the synapse determines whether the post-synaptic neuron would be either excited or inhibited when a pre-synaptic spike is generated. The resulting effects of excitation and inhibition are to potentiate and depress the post-synaptic neuron's membrane potential. In addition, the strength of a synapse is defined by the amplitude change of the membrane potential as a result of a pre-synaptic action potential. Learning and memory are resulted from the changes in synaptic strength through the mechanism of synaptic plasticity that leads to either decrease or increase in the strength. In this way, the synapses store information.

### 2.1.2 Artificial Neural Networks

Artificial neural network (ANN) is a computational model inspired by the biological nervous systems, in particular the brain, and is widely adopted in applications of intelligent information processing, such as machine learning and pattern recognition [20, 30]. An ANN is simply an intricated web of connected artificial neurons (called the processing elements) that processes information in a way to mimic biological neural networks. The signals of the network are passed among the artificial neurons over the connection links called synapses. Each synapse has an associated weight or strength of its own, which typically multiplies the signal transmitted. The weight is a adaptive numerical parameter that can be manipulated by a learning algorithm. Additionally, each neuron accumulates the input signals that are weighted by the respective synapses of the neuron, and applies an activation function that may be either linear or non-linear to its net input (*i.e.* sum of the weighted input signals) to determine its output signal. Furthermore, ANNs are similar to their biological counterparts in the sense that they perform functions dispersively, collectively and in parallel by the processing elements.

Artificial neurons are the basic functional units to build an ANN and are a great simplification of biological neurons. The first computation model of artificial neurons was created by McCulloch and Pitts in [44]. The McCulloch-Pitts model is based on a simplified binary neuron whose state is either active or not-active, and implements a threshold function in discrete time. The state is determined by accumulating weighted incoming signals of activated pre-synaptic neurons at each neural computation step. Namely, it is set to active if the sum of the weighted signals exceeds a given threshold, otherwise it is not. Subsequent neuron models extend the McCulloch-Pitts model by introducing real-valued inputs and outputs and various threshold (activation) functions [20]. Figure 2.2 depicts a typical computation

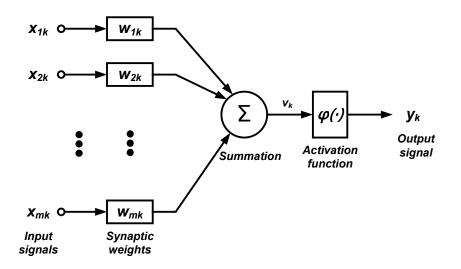

Figure 2.2: Artificial neuron.

model of the artificial neuron. The model consists of three basic elements: 1) a set of synapses which are represented by synaptic weights; 2) an adder for summing the input signals that are multiplied by the respective synaptic weights; and 3) an activation function to bound the amplitude of the output signal. The behavior of the neuron k is mathematically described by the following equations:

$$v_k = \sum_{j=0}^m w_{jk} x_j \tag{2.1}$$

$$y_k = \varphi(v_k) \tag{2.2}$$

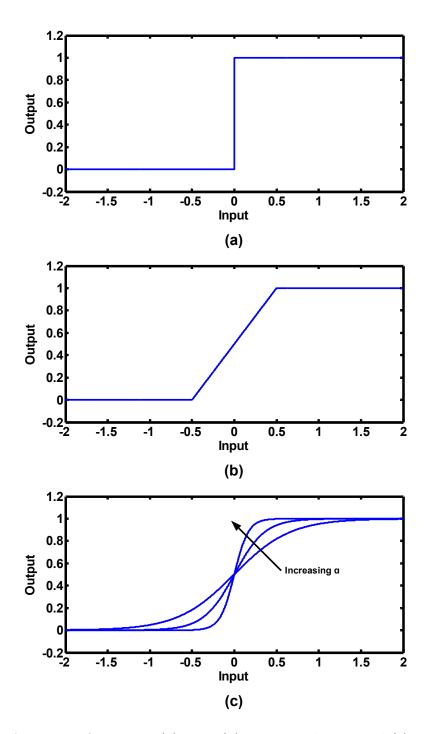

where m is the number of pre-synaptic neurons,  $x_j$  is the input signal coming from the neuron j,  $w_{jk}$  is the synaptic weight between the neuron j and k,  $v_k$  is the linear summation due to the input signals,  $\varphi(\cdot)$  is the activation function and  $y_k$  is the output signal of the neuron k. The activation function denoted by  $\varphi(\cdot)$  is play a role of defining the neuron output in terms of the summation input v. There are many possible activation functions but we introduce three basic types of functions: 1) step; 2) piecewise linear; and 3) sigmoid. They are plotted in Figure 2.3, respectively.

First, the step function makes a binary decision and produces only two values. The step function in Figure 2.3(a) can be described by

$$\varphi(v) = \begin{cases} 1 & \text{if } v \ge 0 \\ 0 & \text{if } v < 0 \end{cases}$$

(2.3)

where the threshold value is zero. The output value is "0" if the input v is greater than or equals to a given threshold, otherwise this function generates a value of "1" as the output.

Second, the piecewise linear function is composed of a number of linear segments over an equal number of intervals. The piecewise linear function described in Figure

Figure 2.3: Activation functions: (a) step, (b) piecewise linear, and (c) sigmoid with different parameter a.

2.3(b) is expressed by

$$\varphi(v) = \begin{cases} 1 & if \quad v \ge +\frac{1}{2} \\ v & if +\frac{1}{2} > v > -\frac{1}{2} \\ 0 & if \quad v \le -\frac{1}{2} \end{cases}$$

(2.4)

where the amplification factor for the linear region is unity. It has two saturation output levels corresponding an upper and lower bounds (e.g. 0 and 1 in (2.4)) and provides a linear response between them.

Third, the sigmoid function is a smooth version of the piecewise linear function in (2.4), and produces an S shaped graph. Moreover, it is most commonly adopted in the construction of ANNs and is mathematically defined by

$$\varphi(v) = \frac{1}{1 + e^{-av}} \tag{2.5}$$

where a is the slope parameter. Adjusting the parameter a allows the sigmoid function to generate different slopes as shown in Figure 2.3(c).

The artificial neurons are combined to form a neural network in many different ways. Most of the ANN architectures exhibit the layered structure. Figure 2.4 illustrated a typical feedforward ANN architecture. It has three layers of input, hidden and output neurons where a set of artificial neurons constitutes a layer. Typically, a standard *L*-layer ANN consists of an input layer, L - 2 hidden layers and an output layer and they are connected successively. It is worth to note that the hidden layer can be omitted in practice. The network can be connected either fully or partially. The communication proceeds layer by layer from the input to the output layers through the hidden ones. The neuron states of the output layer indicate the

Figure 2.4: Feedforward artificial neural network architecture.

computation result of the network. The neurons in the input layer receives external input signals in the form of activation pattern and projects them onto the next layer (e.g. hidden layer in Figure 2.4). The hidden layer plays a role of meditating between the external input and the network output. The addition of more hidden layers allows the network to perform high-order computations, which is particularly valuable when the size of the input layer is large [20]. The neurons in the output layer produce an overall response of the network under the external inputs. In contrast to the feedforward architecture, the recurrent network includes at least one feedback loop, which affects the learning capability of the network and its performance. This network behave like a sequential logic and thus the previous experience may have an impact on the activation of the neurons. The recurrent network is a dynamic system while the feedforward is a static one. When a new input pattern is given, the neuron outputs are computed, then the inputs to each neuron are modified due to the feedback loops, which makes the network enter a new state. Hence, this network topology can be used as associative memory.

Learning makes us to either increase knowledge or enhance understanding, and is archived by studying, experiencing or receiving instructions. For ANNs, learning refers to a process to adjust synaptic weights so that the network is able to perform a specific task efficiently. Many learning algorithms have been presented to appropriately adjust the synaptic weight values of the neural network but they are classified into two main learning paradigms: 1) supervised and 2) unsupervised [30].

Supervised learning is a synaptic weight change process that incorporates the global information. In short, this training process is performed with a teacher that has knowledge or correct answers. The underlying principle of this learning algorithm is the error correction rule that leverages the error signal (*i.e.* difference between the actual output and the correct output) to adjust the synaptic weight values to reduce the error gradually. In supervised learning, every training input is given to the network with each desired output (*i.e.* correct answer). The synaptic weights of the network are modified to produce the outputs as close as possible to the known correct answers. Therefore, the neural network tries to emulate the teacher gradually through the learning process. The backpropagation and perceptron learning algorithms are well known supervised learning methods.

In contrast, unsupervised learning does not have a teacher and utilizes only local information during the learning process. Briefly, it does not require a correct answer associated with each training input for the learning. This learning leverages the properties or correlations of the training inputs, and tries to organize patterns into categories from these correlations. The basic principle of unsupervised learning is that output units (*i.e.* neurons) compete among themselves for activation. Therefore, it allows only one output neuron to be activated at any given time. This phenomenon is referred to as winner-take-all (WTA), which is a common feature of unsupervised learning. Generally, the input patterns form a vector and the network maps the vectors into the synaptic weights. An example of the unsupervised learning algorithms is competitive learning [30].

### 2.1.3 Spiking Neural Networks

While the conventional ANNs described in Section 2.1.2 are a powerful computational tool to solve complex problems, they still suffer from fundamental limitations in emulating a real biological neural system due to the lack of temporal information of spikes. ANNs have become more powerful and biologically realistic. Spiking neural networks (SNNs), referred to as the third generation of ANNs, have been developed by considering the communication among neurons with precise timing information of the spikes. They more realistically resemble the biological brain than the conventional ANNs [18].

Figure 2.5: Spiking neural network.

SNNs exploit both the presence and timing of individual spikes as the means of communication among the spiking neurons while the conventional ANNs process neural information with real-valued numbers. As in Figure 2.5, an SNN receives the input spike train from the external environment, processes it, and produces the output of the network in the form of another spike train. In an SNN, it is assumed that the amplitude of spikes does not encode any information. Instead, information is encoded in the timing of the spikes that forms a spike train. Therefore, input vectors for an SNN have to be preprocessed to extract the input features that may contain real-valued timing information [18]. Similarly, the output spike train has to be decoded to interpret the result of the network. There are various coding schemes for inputs and outputs for SNNs to interpret a spike train as real-valued numbers, by using either the frequency of the spikes or the timing between the spikes.

Spiking neurons are similar to the conventional artificial ones, but spiking neurons utilize spikes as input and output while the traditional ones have real-valued counterparts. When the spikes from the pre-synaptic neurons arrive at a post-synaptic neuron, the membrane potential of the post-synaptic neuron changes. The membrane potential represents the internal state of the spiking neuron that is induced in the model to respond to pre-synaptic spikes. The membrane potential is affected by the synaptic characteristics such as strength of the synaptic connections. The postsynaptic neuron fires when its potential reaches a specific threshold. The behavior of spiking neurons is illustrated in Figure 2.6. The post-synaptic neuron connects with three pre-synaptic neurons that transmit their output spikes as inputs to the post-synaptic neuron. The pre-synaptic neurons produce the spike trains that consist of a sequence of three, two and one spikes, respectively, and these spikes occur at the different timings. Hence, the post-synaptic neuron receives six input spikes in total. The membrane potential of the post-synaptic neuron increases whenever

Pre-synaptic neuron output spike train

Figure 2.6: Spiking neuron behavior.

each spike receives as shown in Figure 2.6. It is important to note that the potential can either increase or decrease according to the type of neurons. In other words, inhibitory pre-synaptic neurons depress the membrane potential of the post-synaptic neuron whereas excitatory ones potentiate. All the pre-synaptic neurons in Figure 2.6 are assumed to be excitatory. The post-synaptic neuron temporally integrates the incoming spike trains to compute the internal state of the neuron (*i.e.* membrane potential) over time. The post-synaptic neuron generates a spike when the potential exceeds the threshold (*e.g.* two output spikes in Figure 2.6). The output spike train of the post-synaptic neuron can be either transmitted to other spiking neurons in the SNN or read off the external environment. Similar neuron behavior can be modeled with many different ways by exploiting the existing spiking neuron models, such as

Hodgkin-Huxley and Leaky Integrate-and-Fire models [54].

Similar to the traditional ANNs, SNNs also learn through synaptic plasticity which refers to an adaptation process that updates the strength of the synaptic connections among the neurons over time, in response to their increased or decreased activities. Neuroscientific research revealed that the change in the synaptic strength depends on the timings of pre- and post-synaptic spikes [42, 33]. This dependency was experimentally characterized in detail by Bi and Poo [3] and named spike timing dependent plasticity (STDP) [62]. STDP is most commonly utilized in modeling of circuit-level plasticity and learning [16]. Furthermore, the STDP rules have been recognized in a wide variety of tasks including associative memory and pattern recognition. STDP is basically a temporally asymmetric form induced by temporal

Figure 2.7: Spike timing dependent plasticity.

correlations between the spike firing events between pre- and post-synaptic neurons. Namely, the strength change of synaptic connection is a function of the spike time difference between pre- and post-synaptic firing events and the difference determines the synaptic weight change as illustrated in Figure 2.7. As one example, to achieve the STDP-based learning, the time difference  $\Delta t = t_{post} - t_{pre}$  of the firing times between the pre- and post-synaptic neurons needs to be calculated. Then, the synaptic weight update is done by adding the weight change  $\Delta w$  obtained from the STDP curve into the synaptic connection strength w between the pre- and post-synaptic neurons. In this case, the STDP learning is mathematically described by the following equations

$$\Delta w = W(t_{post} - t_{pre}) \tag{2.6}$$

$$w = w + \Delta w \tag{2.7}$$

where  $t_{pre}$  and  $t_{post}$  are the firing times of the pre- and post-synaptic neurons, respectively,  $W(\cdot)$  is the STDP learning function and w is the synaptic weight between the neurons. Since the STDP function  $W(\cdot)$  affects the learning performance of the SNN, it should be carefully designed according to the targeted applications.

The rest of this dissertation focuses only on SNNs, which are our primary targeted computational model.

#### 2.1.4 Silicon Neuron Circuits

Silicon neurons are the fundamental building blocks in neuromorphic hardware design [1]. They emulate the electrophysiological behavior of real neurons on a silicon chip rather than on a general purpose computer as software. Many design approaches to implement silicon neurons with analog and digital circuits have been presented [29]. Moreover, several different devices, ranging from conventional CMOS devices to recently developed nano-electro devices such as memristors, are exploited to realize silicon neurons. Considering the presented neuron models so far, the LIF neuron model is widely adopted to implement silicon neurons due to its simplicity in hardware implementation. In contrast, more detailed ordinary differential equation (ODE)-based models such as the Hodgekin-Huxley model can reproduce the behavior of biological neurons more closely, they are less hardware friendly and appropriate for large scale integration.

Figure 2.8: Analog silicon neuron: (a) schematic and (b) timing diagram [29].

Traditionally, silicon neurons have been implemented with analog circuits, which

utilize the I-V characteristics of the transistors to mimic the biological neurons [48, 65, 69, 11]. Figure 2.8 depicts an analog LIF silicon neuron [29]. The capacitor  $C_{mem}$ is used to keep the membrane potential and the leakage current of the membrane is controlled by the gate voltage  $V_{lk}$  of  $M_1$  as in Figure 2.8(a). The switches  $M_2$  and  $M_3$ play the role of charging and discharging the membrane capacitor  $C_{mem}$ , respectively. The circuit utilizes an analog comparator to compare the threshold  $V_{thr}$  with the membrane potential  $V_{mem}$ . The emulated membrane voltage over time is illustrated in Figure 2.8(b). If there is no input  $I_{in}$  applied, the membrane voltage  $V_{mem}$  is drawn to its resting potential, which is 0 V in this configuration, by the leakage current. If an excitatory input by a positive  $I_{in}$  is injected to the neuron circuit, then the membrane capacitor  $C_{mem}$  is charged while the inhibitory input by a negative  $I_{in}$ discharges  $C_{mem}$ . When the excitatory current is larger than the leakage current, the membrane potential  $V_{mem}$  increases. The potential  $V_{mem}$  is compared with the threshold voltage  $V_{thr}$  by the comparator which produces a spike when  $V_{mem}$  exceeds  $V_{thr}$ . The spike turns the switch  $M_2$  on and, as a result,  $V_{mem}$  is reset to the resting potential by  $I_k$ . The analog circuit based silicon neurons may have a simple structure with a few transistors and consume low power. Unfortunately, they are intrinsically sensitive to process, voltage and temperature (PVT) variations and thus it is essential to design carefully to make the circuits robust. Analog circuits are difficult to scale with technology, reconfigure, and interface with software systems. Importantly, the use of area-consuming capacitors to maintain a considerable number of synaptic weights and membrane potentials hinders large-scale integration of spiking neurons [28, 59].

A digital implementation of silicon neurons is illustrated in Figure 2.9 [6]. The neuron circuit mainly consists of a digital adder, a digital comparing circuit and some control blocks. The accumulator (*i.e.* register) stores an integrated digital

Figure 2.9: Digital silicon neuron [6].

value represented by a 2's complement signed number and its output correspond to a membrane potential. When the event input occurs, *Enable* signal is activated and the accumulator is updated with the corresponding kernel weight  $w_{ij}$  (*i.e.* synaptic weight value) through the adder. If the accumulator output reaches a programmed threshold, the neuron generates an event pulse (*i.e.* spike). The threshold value is determined by a 3-bit parameter *Sel\_lim* that selects one of the 18 accumulator output bits via the multiplexer. While a lower bit selected leads to a small threshold value, a higher one results in a large threshold. For instance, selecting the (5)*th* and (8)*th* bits sets the threshold value to 32 (2<sup>5</sup>) and 256 (2<sup>8</sup>), respectively. The selected bit is compared with the MSB of the accumulator continuously and the comparator (*i.e.* XOR gate) creates a spike when the MSB and the selected bit is different from each other. Lower thresholds make the neuron fire more frequently, and thus allow fast processing. The forgetting block mimics the leaking behavior of neurons. The periodic forgetting pulse *Sel\_forgetting* is applied to the forgetting block. If *Sel\_forgetting* signal is asserted, the block outputs a fixed leaky value (*e.g.* -1) so the accumulator output decreases, causing the membrane potential to decrease periodically. The digital neuron circuits are advantageous in terms of robustness against PVT variations, better reconfigurability and ease of implementation. However, it may consume large dynamic power due to digital switching activities.

# 2.1.5 Neuromorphic VLSI Systems

At the system level, while the conventional computers have become very powerful but they still require a huge amount of capacity, power and computation time to mimic the tasks that humans behave, VLSI-based neuromorphic systems can provide effective ways to emulating the functions of a biological brain in silicon while significantly saving computational power and time. Neuromorphic chips are usually composed of synapse circuits and silicon neurons that store synaptic weight values and emulate neuron dynamics, respectively. In addition, they can also include dedicated on-chip learning circuits according to the application. Recently, two digital reconfigurable neuromorphic chips integrating a large number of spiking neurons and their building blocks have been demonstrated in [58, 46, 27, 2]. These two designs support up to 256 programmable digital silicon neurons and  $1024 \times 256$  binary synapses by means of an SRAM crossbar array.

Figure 2.10 shows the block diagram of the digital neurosynaptic core in [46]. It consists of 256 digital LIF neurons with an output encoder, 1024 individually addressable axons, which can be either excitatory or inhibitory, with an input decoder and  $1024 \times 256$  programmable binary synapses implemented with an SRAM crossbar array. This design does not include an on-chip learning mechanism and necessitates loading of synaptic weights into the crossbar after the off-chip learning. It performs neural information processing in an event driven manner to save active power dissipation greatly. Specifically, it adopts an asynchronous design technique where all

Figure 2.10: Block diagram of digital neurosynaptic core [46].

communication among the blocks requires a request-acknowledge handshake without a global clock signal. The detailed operation in each time step t is divided into two phases. In the first phase, a set of input spike-events A are sent to the neurosynaptic core at a time, and these events are sequentially decoded to the appropriate axon block. The corresponding axon activates the SRAM's row, and reads out all of its connections and type G. If there are synaptic connections W, which are represented as "1", the inputs are sent to the corresponding neurons circuits. Then, they update the membrane potentials V appropriately. After a sequence of neuron updates, the axon block deactivates the SRAM and waits for the new inputs. In the second phase, a synchronization event that occurs in every millisecond period is sent to all the digital neurons. Each neuron checks whether its membrane potential reaches certain threshold. If so, it produces a spike and resets the potential to zero. These spikes of the neurons are encoded and sequentially sent off the chip through the encoder. After that, the leak parameter is applied to the neurons. Throughout the two phases of neural processing, the neurosynaptic core implements the neuron dynamics described by the following mathematical expression.

$$V_i(t+1) = V_i(t) + L_i + \sum_{j=1}^{K} \left[ A_j(t) \times W_{ji} \times S_i^{G_j} \right]$$

(2.8)

where L is the leaky parameter, K is the number of axons, A is the activity bit, W is the synaptic value and G is the axon type.

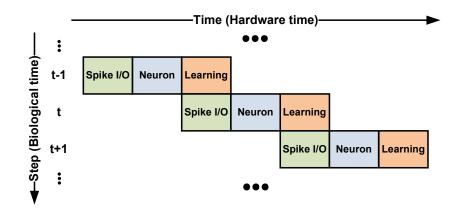

The digital neuromorphic chip incorporating on-chip learning capability in [58] is illustrated in Figure 2.11. This chip integrates 256 digital spiking neurons with  $256 \times 256$  binary synapses to implement a fully recurrent network. It operates in a synchronous manner with a global hardware clock signal and each biological step consumes many hardware clock cycles. In each time step, the digital spiking neurons calculate their membrane potential according to the implemented dynamics and produce spikes when the potentials reach the given firing threshold. The spikes created by the firing neurons lead to synaptic integrations in all target neurons (*i.e.* (i.e.post-synaptic neurons) and synapse weight updates according to certain learning rule. While the input spikes to the system represent external stimuli such as input patterns, the generated spikes (*i.e.* output spikes) indicate the output activities (e.q.recognition of a given pattern). The  $N \times N$  crossbar architecture is suitable to represent a neural network of N neurons and all  $N^2$  possible synaptic connections among them. Correspondingly, the on-chip storage used to keep the binary synapse values is implemented by a  $256 \times 256$  array of transposable SRAM cells. While the conventional memory array is accessible only in row-direction, the proposed transposable SRAM array is accessible in both row- and column-fashions for pre-synaptic and post-synaptic weight updates, respectively, leading to a significant speedup of the

Figure 2.11: Block diagram of (a) neuromorphic chip and (b) silicon neuron [58].

update process. Moreover, an entire row and column of the crossbar can be accessed simultaneously. Note that each row and column corresponds to a neuron's axon and dendrite, respectively, in the SRAM array. Based on the adopted single-bit memory cells, the binary weight of the synapses are probabilistically set to "1" or "0" according to the implemented learning rule. Each neuron in the Figure 2.11 implements both locally reconfigurable LIF functions and learning rules, and the following LIF neuron dynamics is conducted in each time step

$$V[t] = V[t-1] + s_{+}n_{+}[t] - s_{-}n_{-}[t] - \lambda$$

(2.9)

where V is the membrane potential,  $n_+$  and  $n_-$  are the numbers of excitatory and inhibitory inputs received through "on" synapses, respectively,  $s_+$  and  $s_-$  are the input strength parameters and  $\lambda$  is the leak parameter. The membrane potential and parameters are expressed with 8-bit digital values. Additionally, if the membrane potential V exceeds a given threshold  $\theta$  that is reconfigurable variable, a spike is generated and V is reset to the resting potential. On-chip learning is implemented in each neuron cell, which thus shares the learning circuit across axonal rows and dendritic columns of the synapses. The pre- and post-synaptic counters work with a linear feedback shift register (LFSR) to perform probabilistic synapse weight update.

The two neuromorphic designs both employ an SRAM array to store synaptic weight values, incurring a significant portion of the entire chip area. Furthermore, the learning performance may be degraded due to the adopted binary synapses that are updated by a probabilistic scheme [58]. The lack of an on-chip learning mechanism may limit the design of applications [46].

# 2.2 Approximate Computing

Aggressive CMOS technology scaling allows modern VLSI systems to integrate many high-performance functional modules, such as multi-media and communication processors. Meanwhile, today's circuit designers are facing grand challenges in managing overall chip power and energy consumptions. To remedy the increasing energy efficiency challenges, a new design paradigm of approximate computing has emerged as one promising solution and has drawn a significant research interest [7, 67, 21, 60, 8, 9]. Approximate computing can provide great computational and energy efficiencies by relaxing processing precision while maintaining an acceptable overall processing quality for many applications that involve signal processing of multimedia data (e.q. audio, video and image), machine learning and speech recognition. Fortunately, these classes of computation do not require perfect accuracy and approximate results with controlled accuracy may be sufficient. For example, while approximation errors in image processing may change the numerical values of the overall output, the users may not be very sensitive to certain amount of error and may still recognize the image. Similarly, there is certain level of error resilience in tasks performed by the human brain. The human brain is often able to fill the missing information and filter out the noisy or redundant information from the received inputs by its natural error compensation mechanisms. In short, the human brain has a certain degree of built-in error or fault resilience. Thus, it makes good sense to system design to reduce the cost in hardware realizations such as power, energy and area with approximate computing from a ranging from the algorithm to circuit levels [21, 60, 8, 9].

Certainly, addition is the fundamental operation in many processing applications and the adder is therefore an essential component to achieve approximate computing. Furthermore, other arithmetic units, such as comparator and multiplier, can be implemented based on the adder. Since approximate adder design is one primary contribution of this dissertation, we briefly review the existing approximate adder design techniques. Lu proposes an approximate adder [39] that leverages a limited number of previous (less significant) input bits for carry speculation to increase the overall speed by cutting down the long carry propagation chain. The critical drawback of this approach is the use of a considerable number of carry generators, which gives rise to large area and high power dissipation. The so-called ETAI [76] and LOA

[40] approximate adders are split into an accurate part for higher order bits and an inaccurate part, which utilizes a modified XOR (ETAI) and OR function (LOA) to approximately compute the remaining lower output bits. Therefore, the approximate errors are concentrated on the lower bits. A few transistors are eliminated from the traditional mirror adder to reduce power and area at the expense of accuracy degradation in [19]. These two approaches are limited by high error rates. The ETAIII [75] improves the error rate of ETAI by introducing a dynamic dividing strategy of the accurate and inaccurate parts by input patterns but still yields a high error rate. The segment based approximate adders are presented in [74] and [14] which are named ETAII and VLCSA-1, respectively. The carry for each k-bit segment is predicted from the lower k-bit inputs to reduce the delay of carry propagation. Similarly, the ACA [32] adopts a number of 2k-bit sub-adders and leverages only k most significant bit (MSB) outputs of the sub-adders to achieve approximate additions. Unfortunately, these adders have high error rates for the carry generations, particularly for 2's complement signed additions of small numbers. In addition, the use of carry selection in VLCSA-1 and middle sub-adders in ACA result in power consumption and area overhead. The lack of an error magnitude reduction in ETAII degrades the quality of addition. In [47], the approximation errors for less significant bits are reduced by conditional bounding logic with dithering, which causes area and power overheads.

#### 2.3 Emerging Memory Technologies

To date, various new memory technologies have emerged to replace the traditional memories such as SRAM and DRAM. Among these new memory technologies researched so far, spin-torque-transfer random access memory (STT-RAM), phasechange memory (PCRAM) and memristor based resistive random-access memory

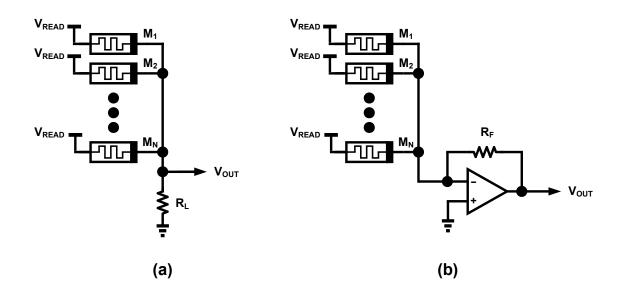

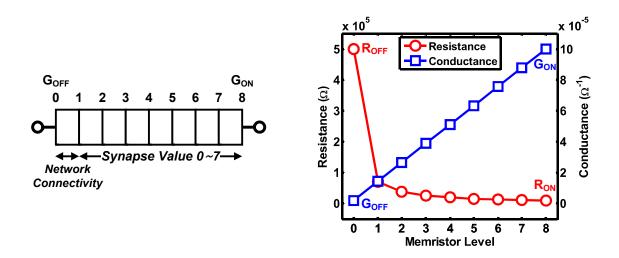

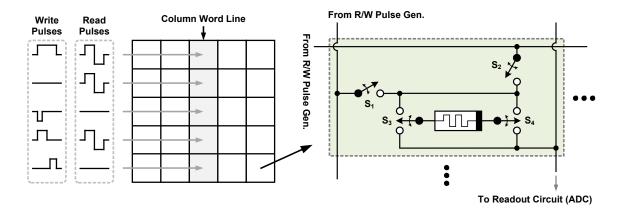

(ReRAM) are considered the most promising candidates for the future. STT-RAMs exploit a magnetic tunnel junction to store information and the difference in magnetic directions is used to represent a bit of information [12]. PCRAMs leverage chalcogenide materials for memory storage which can be switched between a crystalline phase (SET state) and an amorphous phase (RESET state) by heat [12]. ReRAMs are typically implemented with a memristor, as known as memory resistor, whose existence was theoretically predicted by Chua in 1971 as the fourth fundamental passive circuit element [10]. More recently,  $TiO_2$  thin-film based memristors have been demonstrated at the nanoscale [63]. The memristive nanodevice has gained increasing research interest and becomes a promising solution for low-cost on-chip storage thanks to its non-volatile nature, excellent scalability and high density of  $10\ Gb/cm^2$  or more [23, 72]. A number of multibit hybrid CMOS/memristor memory architectures targeting high integration density and low power dissipation have been proposed to substitute the conventional SRAM and flash memories that are confronted with the fundamental technology scaling limits [45, 41]. In addition, several recent studies have suggested leveraging memristive nanodevices for building synaptic arrays [31, 61, 55, 25].