**University Of Pisa**

**Department of information Engineering**

Master Thesis In Embedded Computing System

PORTING OF FREERTOS ON A PYTHON VIRTUAL MACHINE FOR EMBEDDED AND IOT DEVICES

Supervisor Co-Supervisor : Prof. Carlo Valatti Ext-Supervisor : Dr. Daniele Mazzei

: Prof. Enzo Mingozzi

Academic year: 2014-2015

Student: Nisar Ahmad

To my Family in Pakistan, To you, Afsheen

# Abstract

The fourth industrial revolution, The Industry 4.0, puts emphasis on the need of "Smart" and "Connected" objects through the use of services provided by Internet of Things, cyber-physical systems and cloud computing to optimize the cost, development time and remote connectivity. Development of highly scalable and flexible IoT applications is the need of time. These solutions require connectivity, less development time, time-to-market and at the same time offers a high performance and great reliability. Zerynth, a small company, provides its full stack for IoT solutions. Zerynth Virtual Machine is the core component among other components in stack which allow the programmers to code in python or hybrid C/Python coding with multithreaded Real Time OS with negligible memory footprint. The Python layer, Application Layer, is totally agnostic of underlying RTOS and hardware abstraction layer. This layered software architecture of Zerynth VM makes it totally compatible with new Industry 4.0 standard. The Hardware abstraction layer, VHAL, abstracts the hardware features of supported MCU and its peripherals while RTOS laver, VOSAL, uses the features of underlying Real Time OS. Zervnth VM can be ported with different Real Time OS and various hardware platforms depending upon the application's cost, features and other relevant parameters. Configuring Kinetis MCU (MK64FN1M0VDC12) with existing VM became the first objective of this thesis. This configuration covers from scratch the clock, boot loading and peripheral support. Since previous version of Zerynth VM had a support of only Chibi2 OS which has certain dependency on the hardware layer underneath so this became another objective to separate the Chibi2 OS from VHAL layer for total independence. Finally, Porting of FreeRTOS on Zerynth VM with Hexiwear MCU as target board could a make a room for another RTOS hence enhancing the features and support of currently available VM. This thesis report describes all porting steps, procedures and testing methodologies starting from configuring a new hardware platform Hexiwear to FreeRTOS porting on Zerynth VM.

# Contents

| 1. | INTRODUCTION                                                                                                                                                        | 6    |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1  | .1 Embedded Software Architecture                                                                                                                                   | 6    |

| 1  | .2 Types of Software Architectures                                                                                                                                  | 6    |

|    | 1.2.1 Static Architecture                                                                                                                                           | 6    |

|    | 1.2.2 Dynamic Architecture                                                                                                                                          | 6    |

| 1  |                                                                                                                                                                     | 6    |

|    | 1.3.1 Need for Real Time System                                                                                                                                     | 7    |

|    | 1.3.2 Tasks and Task State Model                                                                                                                                    | 7    |

|    | 1.3.3 Context Switching                                                                                                                                             | 8    |

|    | 1.3.4 Multitasking                                                                                                                                                  | 8    |

|    | 1.3.5 Preemptive and Non-Preemptive Scheduling                                                                                                                      | 8    |

| 1  | L.4 LAYERED SOFTWARE ARCHITECTURE                                                                                                                                   | 9    |

|    | 1.4.1 Microcontroller Abstraction layer                                                                                                                             | .10  |

|    | 1.4.2 Hardware Abstraction Layer                                                                                                                                    | . 11 |

|    | 1.4.3 RTOS Layer                                                                                                                                                    | . 11 |

|    | 1.4.4 Application Software Layer                                                                                                                                    | .11  |

| 1  | 1.5 ZERYNTH SOFTWARE ARCHITECTURE                                                                                                                                   | 11   |

| 1  |                                                                                                                                                                     | 11   |

|    | 1.6.1 Zerynth Virtual Machine                                                                                                                                       | . 12 |

|    | 1.6.2 Zerynth Studio                                                                                                                                                | . 13 |

|    | 1.6.3 Zerynth Connector                                                                                                                                             | . 14 |

|    | 1.6.4 Zerynth API                                                                                                                                                   | . 14 |

|    | 1.6.5 Zerynth App                                                                                                                                                   | . 14 |

|    | 1.6.6 Zerynth Toolchain                                                                                                                                             | . 14 |

| 1  | .7 ZERYNTH AND PYTHON                                                                                                                                               | 14   |

| 2. | THESIS OBJECTIVES                                                                                                                                                   | 16   |

|    |                                                                                                                                                                     |      |

| 2  | 2.1 ZERYNTH VIRTUAL MACHINE CURRENT CONFIGURATION                                                                                                                   |      |

|    | 2.1.1 Zerynth VM Platfrom Support                                                                                                                                   |      |

|    | 2.1.2 Zerynth VM VHAL layer                                                                                                                                         |      |

|    | 2.1.3 Zerynth VM VOSAL Layer                                                                                                                                        |      |

|    | 2.1.4 Zerynth VM Application Layer                                                                                                                                  |      |

| 2  | 2.2 DECOUPLING CHIBI OS FROM VHAL LAYER                                                                                                                             |      |

| -  | PORTING OF FREERTOS TO KINETIS MK64FN1M0VDC12                                                                                                                       |      |

| 2  | 2.4 Main Approach                                                                                                                                                   | 19   |

| 3. | DECOUPLING CHIBIOS FROM VHAL                                                                                                                                        | 21   |

|    |                                                                                                                                                                     |      |

| -  | B.1 MK64FN1M0VDC12 (HEXIWEAR) AS PORTING PLATFORM                                                                                                                   |      |

|    | 3.1.1 Industrie 4.0                                                                                                                                                 |      |

|    | 3.1.2 Over the Air Firmware Update                                                                                                                                  |      |

|    | 3.1.3 Haptic Feedback Support                                                                                                                                       |      |

|    | 3.1.4 Features and Sensors Support                                                                                                                                  |      |

|    | 3.1.5 DAPLink Firmware Update Support                                                                                                                               |      |

| 3  | 8.2 Setup for Development Environment in Windows 7                                                                                                                  |      |

|    | 3.2.1 Make for Windows                                                                                                                                              |      |

|    | 3.2.2 STM32 Toolchain for ARM GCC                                                                                                                                   |      |

|    | 3.2.3 Cygwin64 Tools                                                                                                                                                |      |

|    | 3.2.4 GITLAB support                                                                                                                                                |      |

|    | 3.2.4 Debug settings                                                                                                                                                |      |

|    | 3.2.5 OpenOCD Flash Programing                                                                                                                                      | 24   |

|    |                                                                                                                                                                     |      |

|    | 8.3 CONFIGURATION OF MINIMUM VIABLE ZERYNTH VIRTUAL MACHINE                                                                                                         |      |

|    | B.3       CONFIGURATION OF MINIMUM VIABLE ZERYNTH VIRTUAL MACHINE         B.4       BOOTUP CONFIGURATION FOR MK64FN1M0VDC12         3.4.1       Clock Configuration | 25   |

| 3.4.2          | Linker Script Configuration                               | 26 |

|----------------|-----------------------------------------------------------|----|

| 3.4.3          | Vector Table Configuration                                | 26 |

| 3.4.4          | MakeFile and Board Specific Configurations                | 27 |

| 3.5 Impli      | EMENTATION OF VHAL DRIVERS                                | 28 |

| 3.5.1          | VHAL GPIO Drivers for K64 MCU                             | 28 |

| 3.5.2          | VHAL Flash Drivers                                        | 29 |

| 3.5.3          | VHAL Serial Drivers                                       | 30 |

| 4. PORTIN      | NG FREERTOS ON ZERYNTH VIRTUAL MACHINE                    | 32 |

| 4.1 FREE       | RTOS BASICS                                               |    |

| 4.1.1          | Why choose FreeRTOS?                                      |    |

| 4.1.2          | FreeRTOS Directory Structure and Data Types               |    |

| 4.2 T          | asks and Co-Routines                                      |    |

| 4.2.1          | Tasks                                                     |    |

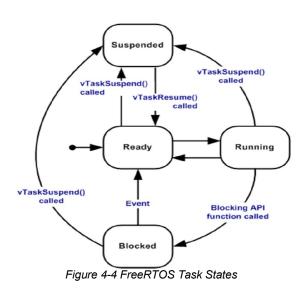

| 4.2.2          | Task States                                               |    |

| 4.2.3          | Tasks Priorities                                          |    |

| 4.2.4          | Co-Routines                                               |    |

|                | ueues, Mutexes and Semaphores                             |    |

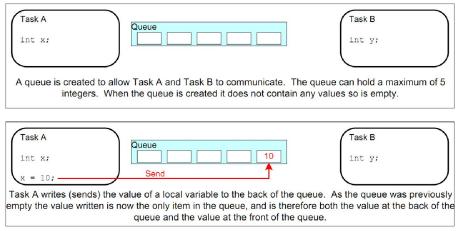

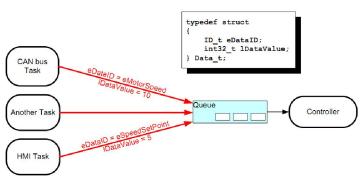

| 4.3.1          | Queves                                                    |    |

| 4.3.2          | Mutexes                                                   |    |

| 4.3.3          | Semaphores                                                | -  |

|                | Detware Timers                                            |    |

| 4.4.1          | Software Timer Callback Functions                         |    |

| 4.4.2          | Timer Period                                              |    |

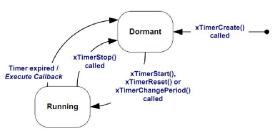

| 4.4.3          | Software Timer States                                     |    |

| -              | ENERAL PORTING STEPS                                      |    |

| 4.5.1          | Porting of FreeRTOS Suggested Steps                       |    |

| 4.5.2          | FreeRTOS Configuration                                    |    |

| 4.5.3          | Memory Management                                         |    |

| 4.6 P          | DRTING OF FREERTOS TO MK64FN1M0VDC12 (HEXIWEAR)           |    |

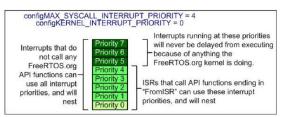

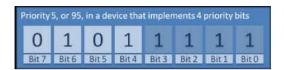

| 4.6.1          | Cortex-M4 FreeRTOS port specific configuration            |    |

| 4.6.2          | FreeRTOSConfig.h and Port.c Configuration                 |    |

| 4.6.3          | Static Memory Allocation by Garbage Collector             |    |

| 4.6.4          | Uplinker support                                          |    |

| -              | G AND RESULTS                                             |    |

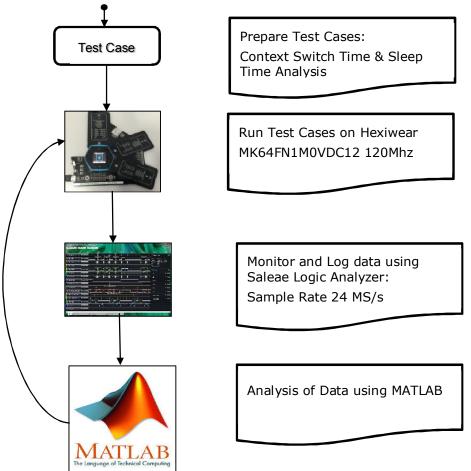

| 5.1 T          | esting Methodology                                        | ۸۵ |

| 5.1.1          | Test Criteria Specification                               |    |

| 5.1.2          | Test Case for Context Switch Time on Hexiwear with C      |    |

| 5.1.2          | Test Case for Context Switch Time on Hexiwear with Python |    |

| 5.1.2<br>5.1.4 | Test Case for Interrupt Latency Testing Using C           |    |

| 5.1.4<br>5.1.5 | Test Case for Sleep Time Analysis                         |    |

|                | rest case for sleep time Analysis                         |    |

| 5.2.1          | Performance Results of Context Switch Time with Both RTOS | -  |

| 5.2.2          | Interrupt Latency Time results                            |    |

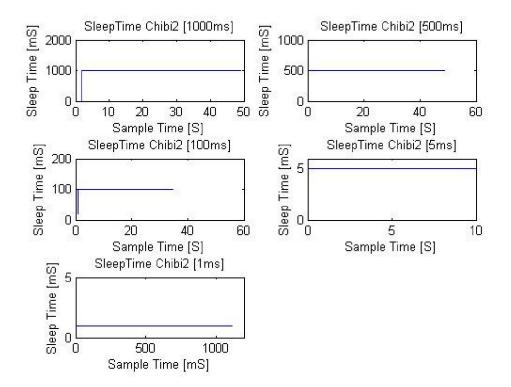

| 5.2.2          | Performance Results with Sleep Time results               |    |

|                | Α                                                         |    |

|                |                                                           |    |

| 6. BIBLIO      | GRAPHY                                                    | 63 |

# Chapter

# 1. Introduction

# 1.1 Embedded Software Architecture

Code reusability has been much increased over the past few years. This has led engineers and scientists to develop new methodologies for software architectures. It's apparent that reusing code across software projects decreases project development time. Nonetheless, software engineers often resist developing reusable code because they're burdened by time-to-delivery commitments.

In an effort to reduce the development time of designing reusable software, adopting an architectural template that can be applied from project to project would be beneficial. The template would define hardware-independent reusable modules and an interface layer that is hardware dependent--changing when the hardware in the system changes. By applying the architecture template consistently across several program platforms, the goal would be to decrease the development time from one project to another while improving the maintainability of the software product.

# 1.2 Types of Software Architectures

The software architecture of a program or computing system is the structure or structures of the system, which comprise software elements, the externally visible properties of those elements, and the relationships among them.

Software architecture involves the high level structure of software system abstraction, by using decomposition and composition, with architectural style and quality attributes. A software architecture design must conform to the major functionality and performance requirements of the system, as well as satisfy the non-functional requirements such as reliability, scalability, portability, and availability.

There in major two types for software architectures:

#### 1.2.1 Static Architecture

This type of architecture describes which part of the software consists of. What are the externally visible features the software has? How the parts of software are connected to each other? This architecture is hierarchical with several levels. It covers the encapsulation reusability and quality of software.

#### 1.2.2 Dynamic Architecture

This architecture covers the real time constraints and runtime efficiency. The structures of executable and allocation of run time to Tasks and processors. It also takes care of dynamic properties of tasks, priority and data dependencies.

# 1.3 Real Time Systems

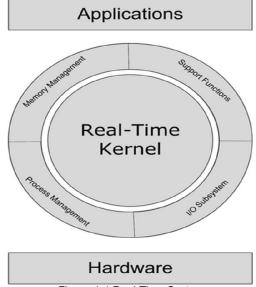

A real-time system has to guarantee the externally generated stimuli within specified amount of time. System performance not only depends on the correct results but also the timeliness behavior of certain events are also has same significance. The Figure1-1 shows that Real time system mainly consists of Real Time kernel which has to manage the processes, multitasking, inter process communication, memory & resource management and interface between hardware and Application software. There are two types of Real-Time systems

• Soft-Real Time

In Soft real time systems if a process misses its deadline or completion within specified amount of time then it does not have any hazardous effects on all of the system performance except some delayed results will be obtained and in certain scenarios these effects are acceptable e.g. a video frame has some deadline of 30ms which means that video must have to be received within this amount of time and if video frame is not received within this specified time, the only effect will the degradation of video quality and video can be jerky. So this doesn't have any hazardous effect on overall system performance and the environment.

Hard –Real Time Systems

In Hard-Real Time Systems if a process misses its deadline then system may undergo some changes which are catastrophic for overall system and its environment. For example, in aviation if engine thrust is not available within specified time or Navigation systems does not respond in time , then whole system may end up to very disastrous condition.

Figure 1-1 Real Time System

#### 1.3.1 Need for Real Time System

Real-time operating systems (RTOSs) are often used to develop applications for systems with complex time and resource constraints. This situation often typifies laboratory automation where one or more computers must synchronize the activities among one or more instruments involving time, process, or precedent constraints. Time constraints might include actions such as "mix for at least x seconds" or "heat at 100 °C for 1 min". Process constraints condition activities, for example, "pick x and place at y" or "rotate 30°". In addition, precedent constraints such as "before", "during", "after", and their complements add further complexity to process control. Fortunately, RTOSs provide the necessary features to handle the demanding time, process, and precedent constraints often associated with such systems.

#### 1.3.2 Tasks and Task State Model

Tasks are the basic functionalities that a real time system provides. Sometimes also knows as processes. Rea-time kernel is responsible to execute a task block or put in ready state. These states are determined based on different features, most importantly the priority of a task. The states of running tasks are shown in the following Figure 1-2 known as Task state Model. The tasks can be periodic, non-periodic or sporadic. Each task has its own memory stack, program counter and memory space to hold variables data.

wait running terminate waiting preempt start suspended release ready activate

Figure 1-2 Task State Model

#### 1.3.3 Context Switching

This is also a prime feature of Real-Time system. A running task can be suspended if a high priority task is ready to run. So real time kernel will put the current task into blocked queue by saving its current memory state and restore it when there are no higher priorities tasks are available to run. So a single CPU can be shared among many threads or Tasks. This phenomenon of saving and restoring the state of task or in other words putting a task into blocked state from running state or vice versa, is known as context switching.

#### 1.3.4 Multitasking

The scheduler has a responsibility to select a particular task, based on algorithm, and put into the ready queue where the task has to wait until the current high priority task finishes its execution. In this fashion, real-time kernel can manage a number of tasks in pseudo parallel way so called Multitasking.

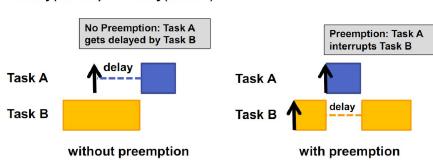

#### 1.3.5 Preemptive and Non-Preemptive Scheduling

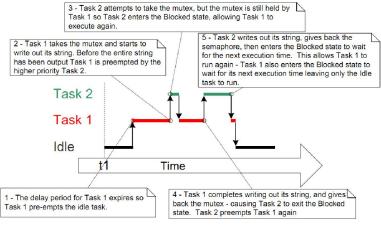

Preemptive as its name goes: interruption. Higher priority task can interrupt the running low priority task and context switch will happen in favor of higher priority task. If a scheduler allows this kind of feature then it is called *Preemptive Scheduler* otherwise in *Non-Preemptive Scheduling*, the low priority task keep on running even if higher priority task is ready to run and context switch will only happen when the current thread will finish its execution. As shown in the following Figure 1-3 below;

Figure 1-3 Preemptive and Non-Preemptive Scheduling

#### Task Synchronization and Resource Access

Priority(Task A) > Priority(Task B)

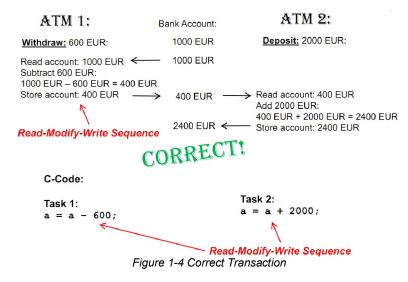

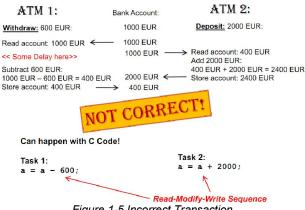

The tasks running in an RTOS may need to access the shared data, memory or files. Access to these resources can be given in a predefined way otherwise data corruption or false results can be obtained. Every RTOS provides some primitives to have this kind of synchronization. To illustrate this concept, let's take an example of a Bank account which is being accessed by two

[8]

persons simultaneously. One person want to withdraw some amount and other person wants to deposit some amount to the account. If these transactions are not done in a synchronized way then false updating of account may occur. Following Figure 1-4 shows the correct transaction of money and account updating with true results. But if user 1 on ATM 1 has certain

Delay after reading the account money and meanwhile user 2 on ATM 2 tries to read account for deposit it will read false money and final results will be incorrect. This situation is depicted in the following Figure 1-5.

Figure 1-5 Incorrect Transaction

So RTOS provides this kind of security to access shared resource with certain locking mechanism. This mechanism is ensures that resource access is certain and avoids any kind of failure such as Dead Lock and Priority Inversion. A Critical Section is defined as a piece of code which cannot be interrupted when it's locked by one task. Other task may have access to that piece of code (shared data) only when it is unlocked by current task. These primitives include Semaphores, Mutex and Mailboxes.

#### 1.4 Lavered Software Architecture

The focus on software reusability and portability has enabled the engineers to define a new design architecture which is flexible, scalable, maintainable and easily testable. This architecture allows software partitioning into different layers based on principle of partitioning, which conforms to the following three rules:

Abstraction

Abstraction is a view to look a particular side without going much into details of its implementation. This refers to look at problem with hiding all irrelevant details. At every step of software development phase it goes to different levels of abstraction. For example, at highest level just an application requirement are addressed and at lowest levels the source code is implemented on hardware to obtain the desired functionality. Abstraction inherently use *Information Hiding* concept which is very useful during testing and maintaining the software. Salient features of Information hiding are listed below;

- Low coupling

- Functional independence among components leads to fewer failures

- Higher quality Software is attained

- ٠

- Modularity

Software is written such that bigger *functionality* split into smaller modules which can be tested and maintained individually. Each module has a specific data and function to perform dedicated functionality. Criteria for modularization is

- Interfaces, among modules should be minimal and well defined

- Implementation, details for each module is hidden from other modules in a software

- Reusability

Reusability of software helps a lot to reduce the development activity. For software to be reusable interfaces should be well defined and among different layers there should be least dependence and coupling. Modules can be written and tested independently and integrated with main software.

The layered software architecture has made it possible for developers to achieve functionality with different software components by just integrating them successfully with main software thus enabling same architecture portable to various platforms. This architecture consists of the following layers:

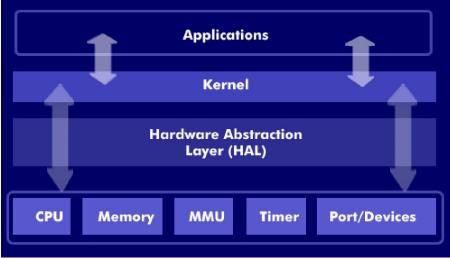

Figure 1-6 Layered software Architecture

#### **1.4.1 Microcontroller Abstraction layer**

MCAL is a software module used to access the physical hardware directly. The Hardware consists of MCU and some external devices. This layer implements the drivers for on-chip MCU peripherals and external devices. The Figure 1-6 shows that the lowest abstraction layer is MCAL. The peripherals consist of:

- Timers

- GPIO

- PWM

- Communication peripherals (SPI,I2C,USART,etc)

- ADC and DAC

- Memory

#### **1.4.2 Hardware Abstraction Layer**

Hardware abstraction layer is a division of code or providing an interface between physical hardware and software. It provides a direct access for OS to the hardware which is device independent.

Hardware abstraction layer is incorporated into numerous OSs to abstain from altering the OS which has an access to device independent hardware platform.

The HAL has the following benefits:

- It allows the applications to access the hardware with higher level of abstraction

- RTOS is able to access the hardware regardless of hardware architecture

- A generic approach for which makes the Software and Hardware independent of device architecture

- It is easy to port the main software to different MCU platforms.

#### 1.4.3 RTOS Layer

An operating system abstraction layer (OSAL) or Real Time kernel provides an application programming interface (API) to an abstract operating system making it easier and quicker to develop code for multiple software or hardware platforms. It abstracts many hardware functions and provides them to applications in the form of services. Scheduling, files synchronization, and networking are the most common services provided by the OS.

OS abstraction layers deal with presenting an abstraction of the common system functionality that is offered by any Operating system by the means of providing meaningful and easy to use Wrapper functions that in turn encapsulate the system functions offered by the OS to which the code needs porting. A well designed OSAL provides implementations of an API for several real-time operating systems (such as vxWorks, FreeRTOS, Chibi, RTLinux etc.). Implementations may also be provided for non-real-time operating systems, allowing the abstracted software to be developed and tested in a developer friendly desktop environment.

In addition to the OS APIs, the OS Abstraction Layer project may also provide a hardware abstraction layer, designed to provide a portable interface to hardware devices such as memory, I/O ports, and non-volatile memory. To facilitate the use of these APIs, OSALs generally include a directory structure and set of makefiles that facilitate building a project for a particular OS and hardware platform.

Implementing projects using OSALs allows for development of portable embedded system software that is independent of a particular real-time operating system. It also allows for embedded system software to be developed and tested on desktop workstations, providing a shorter development and debug time.

#### 1.4.4 Application Software Layer

This layer has the highest level of abstraction and it is located on the top of software hierarchy. It implements the system level functionality that stratifies the project goals. From the top view, all modules in this layer implement the system functionality. From a system perspective, each application is a separate OS process. Typically, applications run in the less-privileged processor mode and use the API system schedule provided by the OS to interact with the OS

## 1.5 Zerynth Software Architecture

Zerynth was born in 2015 to cater for the emerging needs in the area of *"Internet of Things"*. Zerynth provides the support to tailor existing objects to *"Smart Objects"*. With multi-compatible cross platforms, cloud & mobile integration and high-level python script to embedded development, Zerynth enables the users to completely encompass the growing demands in the field of IoT and Machine-to-Machine (M2M) solutions.

The modular approach adopted in the development procedure will not only reduce the time-tomarket of products and over all incurring expenses but also amplifies the potential for smart objects using python scripting.

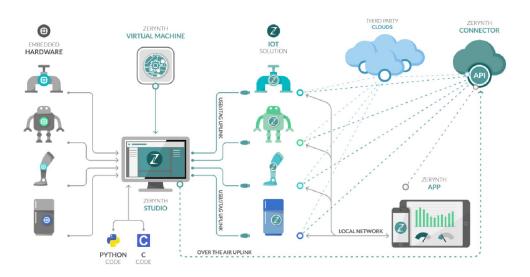

#### 1.6 Zerynth Stack

For complete IoT solution, *Zerynth* provides a full stack from firmware of multi-platforms of embedded devices to cloud integration and data visualization. The stack is flexible and modular giving a user complete freedom in selection of hardware platforms, Real Time systems and third

party cloud modules. The architecture described in the following Figure2-1 is the core of Zerynth stack.

Figure 1-7 Zerynth Stack

Zerynth uses two terminologies for its supported devices:

Internet Connected Devices

The device based on any MCU which has internet connection and implementing various communication protocols like MQTT, Coap etc., are called internet connected devices. These devices are generally equipped with sensors and actuators and can be programmed using high-level python script with Zerynth supported python libraries. They are used as gateways for non-internet connected devices.

Non-internet Connected devices

These devices do not have internet connections but they use some other data connection protocols: ZigBee, Lora or Z-wave.

A brief description to every component in Zerynth stack is as follows:

#### 1.6.1 Zerynth Virtual Machine

Zerynth VM comprises a set of Software and Hardware layers providing a quick design prototyping for any IoT solution. It contains a *Real Time Operating System* and Hardware platform to be accessed from higher layer based on python. Zerynth features multi-threaded environment. Software and hardware abstraction makes it easy for wide variety of applications. Zerynth VM is hardware agnostic, this feature enables the Zerynth VM hardware platform independent. Adding a python level application layer gives a comfort to the programmer to focus on functional requirements of project rather going deeper into details and debugging of lower level embedded development. It provides the support for network protocols like UDP and TCP and hence one can make the use of *http or https*. VM has separate cloud connector library written in python which act as unique communication interface for Zerynth enabled devices to connect any particular cloud. Hardware and RTOS independence makes Zerynth VM very flexible to any kind of IoT application with faster development time. Following Figure 2-2 shows block level view of Zerynth VM

The Zerynth VM can run Python scripts that are platform independent allowing a high reusability of code. Zerynth supports all the most used high-level features of Python like modules, classes, multithreading, callbacks, timers and exceptions, plus some hardware-related features like interrupts, PWM, digital I/O, etc.

Figure 1-8 Zerynth Virtual Machine

The inner workings of the Zerynth VM are complex but can be reduced to a few components:

\* \*\*Bytecode Interpreter\*\*: the Zerynth Compiler turns Python scripts to a set of bytecode objects, each one containing not only a sequence of instructions, but also enough information for memory management and error checking. Each bytecode instruction, called \*opcode\*, is exactly one byte in length with optional arguments going from 0 to 4 bytes. The bytecode interpreter simply scans the bytecode an opcode at time, executes the opcode in the current thread and continues to the next opcode until a stop is encountered. Zerynth bytecode closely resembles Python but introduces some embedded specific opcodes.

\* \*\*Global Interpreter Lock\*\*: the GIL is an object shared by all Python threads; it coordinates the sequence of opcode execution between threads so that each opcode can be considered "atomic". This means that while thread-one is executing opcode "x", thread-one has the right to do so until the execution of "x" reaches the end. No other thread can stop it without compromising the interpreter integrity. When a Python thread goes to sleep, or its time quantum ends, the GIL is released so that another thread can take control of the bytecode interpreter.

\* \*\*Garbage Collector\*\*: objects in Python have lifecycle. They are created and used by the programmer and must be removed when they are not needed anymore. While in low level languages the responsibility of freeing unused memory rests on the programmer, in Python it's the garbage collector (GC) duty. When necessary, a complete scan of the created object is performed in order to search the ones that can be removed safely. The VM GC algorithm is a mark-and-sweep-stop-the-world variant.

\* \*\*Interrupt Thread\*\*: it is a very high priority thread that is woken up when an interrupt configured to run a Python function is fired. Python bytecode is executed outside of the ISR routine, but inside the Interrupt Thread. This way the Python function can allocate memory as a normal function. However, since the interrupt thread has the highest priority it is important to spend the least time possible inside it.

\* \*\*VOSAL\*\*: it is the Zerynth VM operative system abstraction layer. It contains functions provided by the underlying RTOS to create threads, semaphores and other multithreading related objects. The VOSAL is linked into the VM, but many of its functions can be called from hybrid C/Python code.

\* \*\*VHAL\*\*: it is the Zerynth VM hardware abstraction layer. It contains functions to control the microcontroller peripherals: serial ports, SPI, I2C, ADC, PWM and so on. Each family of microcontroller has its own VHAL implementation so that the programmer calling C from Python can have a uniform hardware API across different microcontrollers.

#### 1.6.2 Zerynth Studio

Zerynth Studio is an IDE to manage Zerynth projects and virtualization of hardware platforms. This IDE is supported for Windows, Linux and Mac. User can develop the python projects in this IDE by selecting all supported boards and Operating Systems. Zerynth studio also has *"Package Manger"* for easy installation and management of libraries. All user applications developed in Zerynth studio can be uplinked to supported boards by JTAG or USB connections. It also gives a possibility to program "Over the air" using Zerynth Connector.

#### **1.6.3 Zerynth Connector**

Zerynth connector provides a frontend of a cloud for all connected devices to exchange data between a device or group of devices and cloud. Zerynth device manager supports bidirectional data transfer of TCP packets among multiple devices that are connected to the network. All of connected devices to local network can also be seen and also the devices which are connected remotely to cloud using Wi-Fi or mobile connection can also be explored.

#### 1.6.4 Zerynth API

Zerynth API allows the end user to avail services provided by Zerynth connector. This API has a responsibility to ensure that only authorized requests are made to connected devices. Zerynth API can be used to access the other cloud services and makes the API independent of SAS (Software as Service) API or any other API. Zerynth API makes it possible to store the collected data for different devices on local database or selected cloud.

### 1.6.5 Zerynth App

Zerynth App provides an interface for all the connected Zerynth-enabled devices. This can be a smartphone or tablet App which can be downloaded and installed like all other mobile Apps. When App is running it automatically discovers all the objects that are connected to local network. When a particular device is selected this App becomes an interface for that and associates the current user to interact with Zerynth API. Zerynth App interface is written in HTML and that can be edited in IDE and can easily be integrated python script. So there is no separate need to write code for android or iOS.

#### 1.6.6 Zerynth Toolchain

The Zerynth Toolchain (ZTC) is a command line tool that allows managing all the aspects of the typical Zerynth workflow.

Such workflow extends across different areas of the Zerynth programming experience:

- Managing projects

- o Discovering, managing and virtualizing devices with virtual machines

- Compiling projects into executable byte code

- Uplinking byte code to virtualized devices

- Adding packages (e.g. libraries, drivers, device classes...) to the current installation

- o Turn projects into libraries and publish them to the community repository

The workflow is made possible by the Zerynth backend that provides a set of REST API called by the ZTC. Therefore, most ZTC commands require an authentication token to act on the Zerynth backend on behalf of the user. Such token can be obtained by specific commands.

# 1.7 Zerynth and Python

The Zerynth VM has been developed with the goal of making Python usable in the IoT world. To do so some features of Python have been discarded because they were too resource intensive, while non-Python features have been introduced because they were more functional in the embedded setting. Here is a non-comprehensive list:

\* Python Object size has been reduced as much as possible:

\* Integers are signed and 31 bits wide, so that they can be represented with 4 bytes without additional overhead.

\* Garbage collector overhead has been brought down to 8 bytes per object (and there is still space for optimization)

\* Names are not saved as strings in the bytecode; they are converted to 16 bits integers to occupy much less space. This apparently minor change leads to a series of important consequences. First of all, Zerynth becomes a less "dynamic" language with respect to Python, since introspection is not allowed. However on the pro side, Zerynth scripts can be statically analyzed to remove unused bytecode greatly reducing memory usage. Another important consequence is that \*setattr\* and \*getattr\* cannot be used with non-constant arguments.

\* Sequences and dictionaries can have at most 65536 elements.

\* Exceptions have been transformed from full-fledged classes to a name organized in an inheritance tree. So an exception can't have methods, but it is faster to raise and to handle and it just takes 4 bytes of memory.

\* Compilation has been moved outside the language; by removing the compile () and eval () builtins the VM shrink greatly in size.

\* Not so often used Python features have been removed. Closures, generators and decorators will be added in future updates in a modular way.

\* True multithreading with priorities has been introduced. CPython implementations use greenthreads to emulate multithreaded environments without relying on any native OS capabilities, and they are managed in user space instead of kernel space, enabling them to work in environments that do not have native thread support. In Zerynth each thread is a RTOS thread with its own memory and priority. Because of the GIL, only one Zerynth thread can execute bytecode in a time quantum, but it is possible to have more than one non-Python thread running in parallel. For example, a complex driver can be structured as a VOSAL thread written in C to control hardware, with any number of Zerynth threads running bytecode.

\* New data structures have been introduced like shorts and short array to hold sequences of 16 bits integers. Big ints and fixed point math are in development.

# Chapter 2

# 2. Thesis Objectives

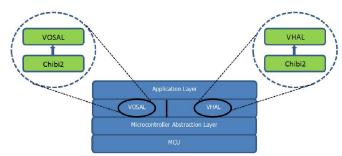

# 2.1 Zerynth Virtual Machine Current Configuration

This chapter describes the current configuration of Zerynth Virtual machine, uncompliance with standard software archeitecture, proposed solution and development methodolgy to proceed. The Current configuration of Zerynth VM shown in Figure 2-1 consists of the three layers: the second and third layer are are shown at the same level which represents that *Virtual Software Abstraction Layer(VOSAL)* and *Virtual Hardware Abstraction Layer (VHAL)* has certain dependencies over each other. These dependecies will have to be removed and making the VOSAL and VHAL totally agnostic from Hardware and Real time Operation System.

Figure 2-1 Zerynth VM Architecture

#### 2.1.1 Zerynth VM Platfrom Support

Zerynth VM is hardware agnostic and it can support multiple hardware platforms. Currently supported devices are the following

- Arduino DUE

- Arduino/Genuino Zero

- Flip & Click Sam3X

- Particle Photon

- Quail Board

The *Microcontroller Abstraction Layer (MCAL)* is responsible to implement MCU specific drivers for each peripheral. This layer also contains Board support packages for selected hardware platform and has different implementation of each peripheral depending upon the MCU specific libraries provided by vendor.

#### 2.1.2 Zerynth VM VHAL layer

The VHAL has generic implementation for all of supported MCUs. This layer is independent of underlying MCAL. It provides an interface between the higher software layer and the lower hardware layer. This layer provides following two features

Pin Mapping

The VHAL introduces a distinction between **physical pins** and **virtual pins**. Physical pins are the actual pins available on the board and are defined in the file *port.c* for every supported board. A physical pin usually maps to a microcontroller register and offset, needed to drive the pin.

A virtual pin is just a name which refers to a particular configuration of a physical pin.

Therefore different virtual pins can map to the same physical pin. For example, imagine a board where the first physical pin (P0) can be used as a general purpose input output (GPIO) or as the clock line (SCL) of the first instance of the I2C bus. Such physical pin is always controlled by same microcontroller register, but in the first case it is configured as a GPIO and the

corresponding virtual pin name will be D0, while in the second case it is configured as I2C clock and the virtual pin name will be SCL0.

The internal representation of virtual pins is a 16 bit integer where the high byte represents the name of the peripheral (the "class" of the pin), while the low byte is the row number in the table of physical pins for that peripheral.

All these levels of indirection are hidden by the VHAL using macros to access the relevant information about pins. All VHAL functions requiring pin names expect virtual pin names.

The following table summarizes the virtual pin information:

| ing table summarizes | the virtual piri informati | 011.      |       |

|----------------------|----------------------------|-----------|-------|

| Pin                  | Pin Offset                 | Pin Value | Pin   |

| Class                |                            |           | Name  |

| DIGITAL              | 0                          | 0x0000    | D0    |

| DIGITAL              | 1                          | 0x0001    | D1    |

|                      |                            |           |       |

| ANALOG               | 0                          | 0x0100    | A0    |

| ANALOG               | 1                          | 0x0101    | A1    |

|                      |                            |           |       |

| SPI                  | 0                          | 0x0200    | MOSI0 |

| SPI                  | 1                          | 0x0201    | MISO0 |

| SPI                  | 2                          | 0x0202    | SCLK0 |

|                      |                            |           |       |

| SER                  | 0                          | 0x700     | RX0   |

| SER                  | 1                          | 0x701     | TX0   |

|                      |                            |           |       |

| LED                  | 0                          | 0x900     | LED0  |

| LED                  | 1                          | 0x901     | LED1  |

|                      |                            |           |       |

Table 2-1 Virtual Pin Information

Where *Pin Name* is a C Macro corresponding to *Pin Value*. For each string in *Pin Class* there exists a C macro with PINCLASS\_prepended, corresponding to the high byte of *Pin Value* (i.e. PINCLASS\_DIGITAL is 0x00, PINCLASS\_ANALOG is 0x01, etc...).

• Peripherals Mapping

Each microcontroller peripheral is mapped to a peripheral index in the board porting files. For each peripheral there exists a table mapping multiple peripheral instances of the same type to different indexes. The following example will clarify the mapping. Imagine a microcontroller with four different USART peripherals named USART1 to USART4. In the board porting each USART is mapped to a peripheral index by creating such table:

| nack by oreating | Such tubic.       |       |

|------------------|-------------------|-------|

| Index            | Value             |       |

| 0                | 3                 |       |

| 1                | 1                 |       |

| 2                | 4                 |       |

| 3                | 2                 |       |

|                  | Table 2-2 VHAL Pe | eripi |

Table 2-2 VHAL Peripheral Mapping

When a VHAL function is called, expecting a peripheral index for a serial peripheral, the table is used to map the passed index (e.g. 0) to the corresponding mcu peripheral (e.g. USART3). Each board porting defines this kind of tables for each supported peripheral.

#### 2.1.3 Zerynth VM VOSAL Layer

The Zerynth VM uses a common API to create and manage threads and synchronization objects. Such API is called VOSAL and abstracts the details of the underlying RTOS, so that it can be changed as needed for performance or licensing reasons.

Currently supported RTOS is chibi2.

VOSAL layer provides generic implementation for the following primitives of underlying RTOS:

- Threads

- Semaphores

- Mutexes

- Mailboxes

• System Timers

#### 2.1.4 Zerynth VM Application Layer

Application layer is written in python. User can write application code using Zerynth studio accessing supported python libraries. C functions called from Python can create and handle Python entities like lists, tuples, and dictionaries and so on. In the current version of Zerynth only a few selected Python data structures can be accessed from C.

Following is a brief introduction to supported functionalities:

PObject

The VM treats every Python object as a pointer to a *PObject* structure. There exist two types of PObects: tagged and untagged. Tagged PObjects contains all the object information encoded in the 4 bytes of the pointer. Untagged objects are pointers to actual C structures. As a consequence, tagged PObjects are not allocated on the heap but reside on the stack of a frame of execution.

To better understand tagged PObjects imagine the case of integers: representing integers by allocating a PObject structure in memory is both a waste of ram and of computational power. Therefore small signed integers up to 31 bits are represented as tagged pointers. This "trick" is possible because a PObject pointer is 4 bytes (32 bits) and due to architecture constraints a valid PObject pointer is at least aligned to 2 or 4. In practical terms it means that the least significant bit of a valid PObject pointer is always 0: by "tagging" the PObject pointer, namely changing its lsb to 1, the VM is able to distinguish between concrete PObjects residing on the heap (untagged, lsb=0) and tagged PObjects (lsb=1). The representation of the number 42 as a tagged PObject follows:

MSB LSB

Sign bit

Bit 0 TAG = 1

Instead, an untagged PObject is a valid pointer to a C structure organized like this:

GCH: B0 B1 B2 B3 B4 B5 B6 B7

DATA: .....

Where GCH is an 8 byte header holding both garbage collection info and type/size info; DATA is whatever fields are needed to implement the PObject.

• Dictionaries and Sets

Some data structures in Python have functionalities similar to hash tables. In particular dictionaries are mappings from keys to values; set and frozen set are collections of items optimized to test the presence of a given item inside the set. Internally, the hash code of an item is calculated and used to find the item inside the structure in a fast way.

## 2.2 Decoupling Chibi OS from VHAL layer

It has been shown in the last sections that for Zerynth VM the VHAL and VOSAL layers, *shown at the same level*, are independent by design but by implementation there are certain dependencies. VOSAL layers abstract the features of underlying Chibi2 RTOS. So that layer by design and by implementation is correct. Since chibi2 RTOS provides itself some peripheral drivers, so VHAL is not totally independent from RTOS. Figure 2-2 clearly depicts the problem.

This task been assigned to remove this limitation and make the VM totally agnostic of hardware and Real Time Operating System.

Figure 2-2 VOSAL and VHAL Dependencies

# 2.3 Porting of FreeRTOS to Kinetis MK64FN1M0VDC12

Hexiwear (based on Kinetic K64 MCU) and other on-chip sensors was the first board of its kind was chosen to extend the board support for Zerynth VM and to remove the first limitation of VHAL layer dependency on Real Time system for chibi2 OS.

It was also important to make Zerynth VM capable to support an RTOS other than chibi2 to enhance the scope of VM for various applications. Porting of FreeRTOS on Kinetis K64 MCU was second objective to be achieved. The description of each step that is taken to implement these two objectives will be described in detail in subsequent chapters, however, in the next section there is an explanation to the main approach and sequence of steps.

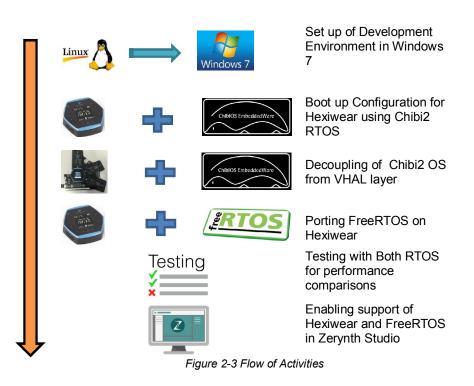

# 2.4 Main Approach

Porting of FreeRTOS on Hexiwear with Zerynth VM leads me to divide this thesis objectives in the following two parts:

Objective 1: Decoupling of ChibiOS from VHAL layer

Objective 2: Porting of FreeRTOS on Kinetis K64 MCU (Hexiwear)

Objective 1: Decoupling of ChibiOS from VHAL layer

For accomplishment of objective 1 it is required to break down the approach into some sequence of steps. Following Figure 2-3 summarizes the flow of activities. The flow of activities for this objective are listed below:

- i. Setup Development environment in Windows 7 by configuring all essential tools from Linux to windows

- ii. Bootup Configuration of Hexiwear with existing RTOS i.e. chibi2. The bootup configuration includes all necessary changes to be made in Makefiles for VHAL layer, Clock configuration and Linker script configuration. The details of each setting will be covered in the chapter 3.

- iii. Writing Code for minimum peripherals of K64 Platform required for *Minimum Viable Zerynth VM*. The peripherals include Serial, GPIO and Flash drivers.

- Objective 2: Porting of FreeRTOS on Kinetis K64 MCU (Hexiwear)

- i. Downloading and understanding the kernel FreeRTOS 9.

- ii. Configuring Systick and kernel priority

- iii. Replacing the Chibi2 with FreeRTOS v9 by modifying the VOSAL layer

- Testing

In this step, when Zerynth VM has a support for both Operating Systems and with basic hardware peripherals needed, a devised test criteria for LED blinking time with each RTOS. Which makes sure that each RTOS working fine in VM accessing properly the underlying the hardware layer. Also to determine performance comparison in terms of time taken on RTOS primitives to synchronize the activities.

• Enabling Support Zerynth Studio

Finally enabling the support for Zerynth studio with FreeRTOS and Hexiwear. A user can write a code in python and choose hardware platform and RTOS.

Here is the flow of activities to fulfill above to objectives:

First three steps explains how to complete the Objective 1 and fourth step will be carried out to port FreeRTOS on K64 MCU. In the last step, enabling Zerynth support for Hexiwear and FreeRTOS.

# Chapter 3

# 3. Decoupling ChibiOS from VHAL

# 3.1 MK64FN1M0VDC12 (Hexiwear) as Porting Platform

For porting purpose we have chosen the Hexiwear board based on Kinetis K64 MCU (Cortex M-4 core). Hexiwear provides complete IoT solution ranging from personal wearable watches to smart large scale industrial solution. The sleek and smart low power design equipped with sensors makes it an effective choice for IoT smart object. Following Figure 3-1 shows that Hexiwear can be used as wearable watch and its supported can be extended by mounting it on *Docking Station*.

Figure 3-1 Hexiwear

With three micro bus sockets, Micro-SD card, I2S interface extends the functionality of Hexiwear for large scale IoT applications. Following are few facts that describe the choice of Hexiwear for this Porting.

## 3.1.1 Industrie 4.0

Industry 4.0 is the current trend of automation and data exchange in manufacturing technologies. It includes cyber-physical systems, the Internet of things and cloud computing.

Industry 4.0 creates what has been called a "smart factory". Within the modular structured smart factories, cyber-physical systems monitor physical processes, create a virtual copy of the physical world and make decentralized decisions. Over the Internet of Things, cyber-physical systems communicate and cooperate with each other and with humans in real time, and via the Internet of Services, both internal and cross-organizational services are offered and used by participants of the value chain.

Figure 3-2 Industrie 4.0

Hexiwear is designed to make smart IoT solution which meets the need of Industrie 4.0.

#### 3.1.2 Over the Air Firmware Update

Hexiwear support Over the Air Programming feature which is useful in IoT field when firmware update is required via internet. It supports two Microcontroller K64 (Main CPU) and KW40 (for BLE) interface.

#### 3.1.3 Haptic Feedback Support

It has six capacitive touch buttons which can be used for haptics.

#### 3.1.4 Features and Sensors Support

Featuring more than traditional MCU development platforms, the Hexiwear platform is ideal for connected applications, thanks to its power-efficient Kinetis K64F MCU featuring:

- ARM® Cortex®-M4 core;

- max frequency up to 120MHz;

- 1024KB Flash, 256KB RAM;

- many peripherals (16-bit ADCs, DAC, Timers);

- Interfaces (USB Device Crystal-less, UART, SPI, I2C, I2S, and SD-card).

Integration is also a key feature of Hexiwear, with a Bluetooth Low Energy (BLE) SoC (Kinetis KW40z) and 8 Sensors onboard:

- 6-axis Accelerometer and Magnetometer combo (FXOS8700CQ);

- 3-axis Gyroscope (FXAS21002CQ);

- Pressure sensor accurate up to Altitude sensing (MPL3115A2);

- Temperature and humidity combo (HTU21D);

- Ambient light sensor (TSL2561);

- Optical Heart rate sensor (Maxim MAX30101).

#### 3.1.5 DAPLink Firmware Update Support

The Hexiwear docking station also integrates the openSDA adapter (with DAPLink firmware to support both MCUs), which enables virtual Serial, Flash-programming and several industry standard Debug interfaces, a JTAG debug connector for external probes.

## 3.2 Setup for Development Environment in Windows 7

It was important for developers to have both Linux and windows development environments. Sometimes it's more flexible to work in windows utilizing more graphical support for debugging and during other development activities so it was decided to work in windows. Zerynth VM compilation was totally done in Linux using ARM GCC compiler. It was an important task to have support of compilation equally in windows. So the following steps have been taken to configure Windows 7 for compiling code:

#### 3.2.1 Make for Windows

Make is a tool to generate executable, bin files or non-source files from source files. It gets all the information of files from a file called MakeFile which has information of all non-source or output files from given source files.

GNU provides a support to have make files for windows. From the following link downloaded the make utility for windows.

http://gnuwin32.sourceforge.net/packages/make.htm

To use make command independent of any path in command window we have to add the path of make.exe and other related files in system environment variables.

Add make path in System environment variables for Windows 7 like

- From the desktop, right click the **Computer** icon.

- Choose **Properties** from the context menu.

- Click the Advanced system settings link. ٠

- Click Environment Variables. In the section System Variables, find the PATH environment variable (Shown highlighted in Figure 3-3) and select it.

- Click on Path and edit the path. Every path is separated by semicolons (;)

- Go to end of all paths and insert a new path of make files, in this case it was the following path:

C:\Program Files (x86)\GnuWin32\bin;

| Divice Manager<br>Remote strings<br>System protection<br>Advanced system settings<br>Advanced system settings<br>Advanced system settings<br>Advanced system settings<br>Advanced system settings<br>Advanced system settings<br>Vacation on sain Advanced System Protection Protection<br>Vacation on sain Advanced System Protection Protection<br>Vacation on sain Advanced System System Vacation<br>Vacation on S                                                                                                                                                                                                                                                                                                                         |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| System protection Copyright & 200 Microsoft Corporation. All rights reserved. Service Pact.1 Service Pact.1 System Properties Vauar effects, processor schedung, memory usage, and visual memory Vauar effects, processor schedung, memory usage, and visual memory User Profes User Profes Settop and Recordy. Se                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| System protection Advanced system setsings Corputar Name Next 1 Corputar Name Next 1 Corputar Name Next 1 Corputar Name Next Next Next 1 Corputar Name Next Next Next Next Next Next Next Nex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| Advanced system settings Service Pack 1 System Properties System Properties System Properties Volume Indexts, processor scheduling, memory usage, and visual intervolution in the logged on at an Administrator to make mod of these changes. User Profes User Profes Settings Setting Seting Seting Setting Setting Setting Seting Setting Setting Se                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| System Properties         32           Computer Name, Hardness, Advanced<br>You must be logged on as an Administrator to make most of these changes.<br>Veau efficies, processor scheduling, memory usage, and vetual memory<br>Searings         Fear vanishes for Hear Administrator to make most of these changes.<br>Veau efficies, processor scheduling, memory usage, and vetual memory<br>Searings         Fear vanishes for Hear Administrator to make most of these changes.<br>Veau efficies, processor scheduling, memory usage, and vetual memory<br>Searings         Fear vanishes for Hear Administrator to make most of these changes.<br>Veau efficies, processor scheduling, memory usage, and vetual memory<br>System variables         Fear vanishes for Hear Administrator to make most of these changes.<br>Veau efficiency method by usages.           Searings         Searings         Searings         Fear Value to the value scheduling.           System variables         Veau efficience         Searings         Fear Value to the value scheduling.           System variables         Searings         Searings         Fear Value to the value scheduling.           System variables         Searings         Searings         Fear Value to the value scheduling.           System variables         Searings         Searings         Fear Value to the value scheduling.           System variables         Searings         Searings         Fear Value to the value scheduling.           System variables         Searings         Searings         Fear Value to the value scheduling.           Searing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| Computer Name         Advanced         System Protection         Remote           You mut be togoth on at an Administrator to make mod of these changes.         Velocity         Velocity           Velocity         Somma         Velocity         Velocity           Value Findles         Somma         Velocity         Velocity           User Findles         Somma         Velocity         Somma           User Findles         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, related to your logon         Somma         Velocity         Somma           System delugs, relation delugs, relation delugs, relation delugs, relation delugs         Somma         Velocity         Somma           Somma         Somma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ×        |

| You must be logged on as an Administrator to make most of these changes.       User Values for Hear Ahmad         Performance       Value of fields, processor scheduling, memory usage, and valuel memory         User Profiles       Setting         Desitop settings include (is your logon       Setting         Status and Recovery       Setting         System status, system failure, and debugging information       Optimized (is status)         Environment ValueBau.       Setting         Environment ValueBau.       Determine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

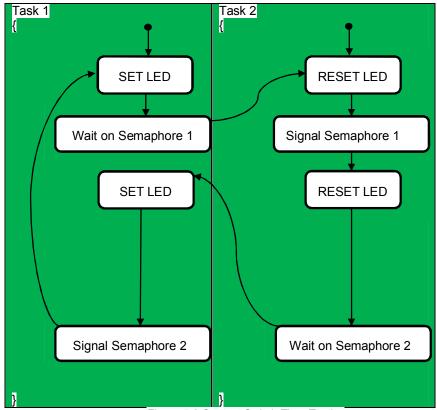

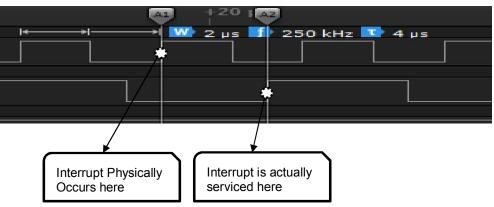

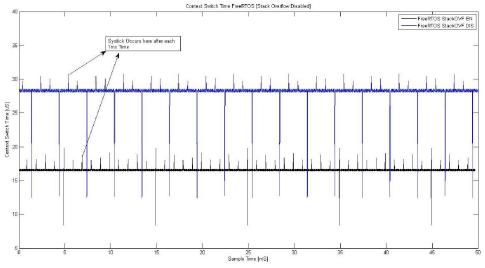

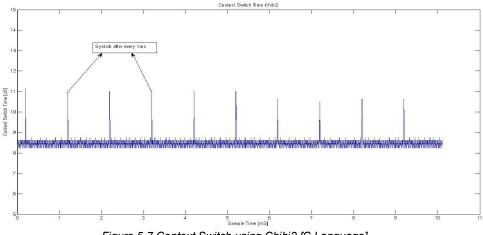

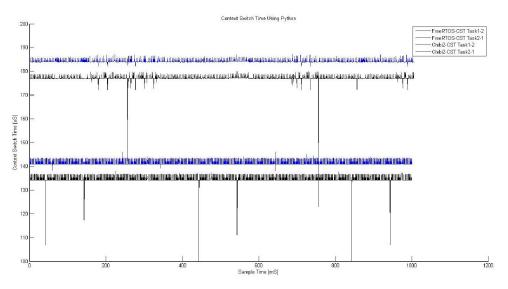

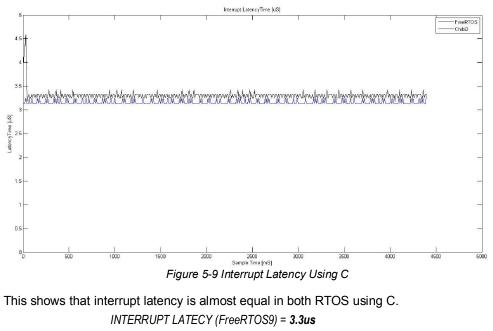

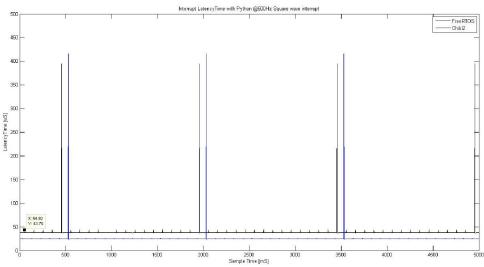

| Performance<br>Value fields, processor scheduling, menory usage, and visual menory<br>Setting<br>User holles<br>Desitop settings related to your logon<br>Setting<br>Setting<br>Setting<br>Setting<br>Setting<br>Environment Valuebles<br>Environment Valuebles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |