### Università di Pisa

#### DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di laurea magistrale

### Design of a CMOS chopper instrumentation amplifier with rail-to-rail input and output ranges

Candidato: Giovanni Gabrielli Relatore: Prof. Paolo Bruschi

Correlatore: Ing. Massimo Piotto

#### Abstract

This thesis deals with the design of a current feedback instrumentation amplifier, optimized for the readout of thermal sensors. This topology stands out for its excellent CMRR and the predisposition to feature low frequency error reduction techniques. Versatility is a main target for this work: 1 kHz bandwidth and Rail-To-Rail input common mode range allow the interfacing of a wide variety of sensors.

Chopper modulation is used to reduce offset and flicker noise, achieving a  $19 \,\mathrm{nV}/\sqrt{\mathrm{Hz}}$  RTI noise density and a flicker corner frequency of 6 mHz. A low total output noise power is achieved as well, reaching an ENOB of 12 bits with less than  $350 \,\mu\mathrm{A}$  current consumption.

The peculiar issue for this architecture, that is gain error, is solved by means of Port Swapping technique, together with an input Common Mode Equalization, that reduce untrimmed gain error to 0.5%. Chopped offset and Port Swapping ripple are completely filtered away by a third order Butterworth State Variable low pass filter, implemented with Gm-C integrators.

# Contents

| Li            | st of | Figures                                                                             | iv        |

|---------------|-------|-------------------------------------------------------------------------------------|-----------|

| $\mathbf{Li}$ | st of | Tables                                                                              | iv        |

| In            | trod  | action                                                                              | iv        |

| 1             | Sen   | sors and instrumentation amplifiers                                                 | 1         |

|               | 1.1   | Diffusion of sensors                                                                | 1         |

|               | 1.2   | Classification of sensors                                                           | 6         |

|               | 1.3   | In-Amps for sensor interfacing                                                      | 13        |

| <b>2</b>      | Inst  | rumentation amplifiers: state of the art                                            | <b>23</b> |

|               | 2.1   | In-Amp architectures                                                                | 23        |

|               |       | 2.1.1 Three Op-Amp $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 23        |

|               |       | 2.1.2 Switched Capacitor Topology                                                   | 24        |

|               |       | 2.1.3 Capacitively-Coupled Topology                                                 | 25        |

|               |       | 2.1.4 Current-Mode Topology                                                         | 26        |

|               |       | 2.1.5 Current Feedback Topology                                                     | 27        |

|               | 2.2   | Dynamic techniques for low frequency errors reduction                               | 28        |

|               |       | 2.2.1 Offset voltage $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 28        |

|               |       | 2.2.2 Flicker noise or $1/f$ noise                                                  | 29        |

|               |       | 2.2.3 Correlated Double Sampling                                                    | 31        |

|               |       | 2.2.4 Auto-Zeroing $\ldots$                                                         | 32        |

|               |       | 2.2.5 Chopper Stabilization                                                         | 34        |

|               | 2.3   | CFIA implementations and error reduction                                            | 38        |

|               |       | 2.3.1 Chopped offset reduction                                                      | 38        |

|               |       | 2.3.2 Gain Error Reduction                                                          | 41        |

| 3             | Hig   | n level desgin                                                                      | 46        |

|               | 3.1   | Reference design                                                                    | 46        |

|               | 3.2   | Proposed solution                                                                   | 52        |

|          |      | 3.2.1   | $Goals \dots \dots$        |

|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------|

|          |      | 3.2.2   | Third order LPF design                                                                                                           |

|          |      | 3.2.3   | Final high level design 60                                                                                                       |

| <b>4</b> | Trai | nsistor | level design 70                                                                                                                  |

|          | 4.1  | Overal  | l schematic $\ldots \ldots 70$ |

|          | 4.2  | Proces  | s and device models                                                                                                              |

|          |      | 4.2.1   | Process components                                                                                                               |

|          |      | 4.2.2   | Device models                                                                                                                    |

|          | 4.3  | Pream   | plifier                                                                                                                          |

|          |      | 4.3.1   | Topology and input range                                                                                                         |

|          |      | 4.3.2   | Thermal noise                                                                                                                    |

|          |      | 4.3.3   | Flicker noise                                                                                                                    |

|          |      | 4.3.4   | Input and output ranges                                                                                                          |

|          |      | 4.3.5   | Final design and dimensions                                                                                                      |

|          | 4.4  | OTA1    |                                                                                                                                  |

|          |      | 4.4.1   | Topology                                                                                                                         |

|          |      | 4.4.2   | Input range                                                                                                                      |

|          |      | 4.4.3   | Output range                                                                                                                     |

|          |      | 4.4.4   | Noise                                                                                                                            |

|          |      | 4.4.5   | Final dimensions                                                                                                                 |

|          | 4.5  | INT1    | CMFB                                                                                                                             |

|          |      | 4.5.1   | Operating principle                                                                                                              |

|          |      | 4.5.2   | Topology                                                                                                                         |

|          |      | 4.5.3   | Final dimensions                                                                                                                 |

|          |      | 4.5.4   | Loop stabilization                                                                                                               |

|          | 4.6  | INT2    |                                                                                                                                  |

|          |      | 4.6.1   | Topology                                                                                                                         |

|          |      | 4.6.2   | Input ranges                                                                                                                     |

|          |      | 4.6.3   | Final dimensions                                                                                                                 |

|          | 4.7  | INT3    |                                                                                                                                  |

|          |      | 4.7.1   | Topology                                                                                                                         |

|          |      | 4.7.2   | Input ranges                                                                                                                     |

|          |      | 4.7.3   | Output ranges                                                                                                                    |

|          |      | 4.7.4   | Noise                                                                                                                            |

|          |      | 4.7.5   | Common mode loop stabilization                                                                                                   |

|          |      | 4.7.6   | Final considerations and dimensions                                                                                              |

|          | 4.8  | CMDA    | Α                                                                                                                                |

|          |      | 4.8.1   | Topology                                                                                                                         |

|          |      | 4.8.2   | Noise                                                                                                                            |

|          |      | 4.8.3   | Input differential and CM ranges 112                                                                                             |

|          |      |         |                                                                                                                                  |

|          |       | 4.8.4   | Output ranges                                                                                            | • | 114 |

|----------|-------|---------|----------------------------------------------------------------------------------------------------------|---|-----|

|          |       | 4.8.5   | Cascode summing stage and Monticelli cells                                                               |   | 114 |

|          |       | 4.8.6   | Final dimensions                                                                                         |   | 115 |

|          | 4.9   | Switch  | nes and clock generator                                                                                  |   | 115 |

|          |       | 4.9.1   | Deviator                                                                                                 |   | 115 |

|          |       | 4.9.2   | Non overlapping clock generator                                                                          |   | 116 |

|          |       | 4.9.3   | Final dimensions                                                                                         | • | 116 |

| <b>5</b> | Sim   | ulatio  | ns and results                                                                                           |   | 118 |

|          | 5.1   | Freque  | ency domain                                                                                              |   | 118 |

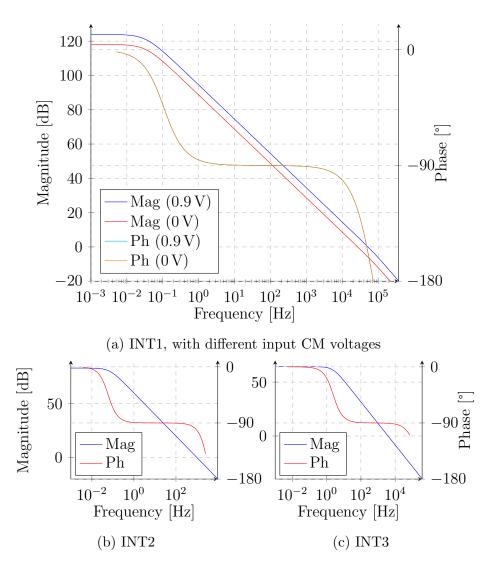

|          |       | 5.1.1   | Intergrators' open loop transfer functions                                                               |   | 118 |

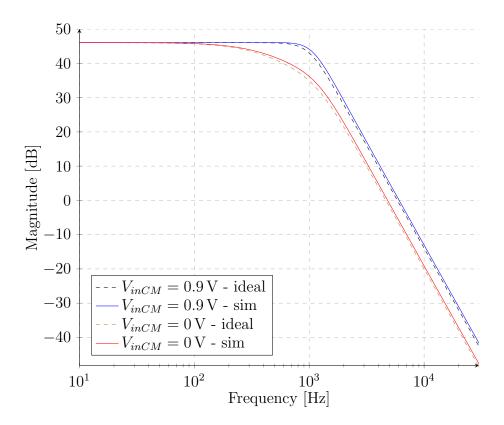

|          |       | 5.1.2   | Signal Transfer Function                                                                                 |   | 119 |

|          | 5.2   | Time    | domain                                                                                                   |   | 121 |

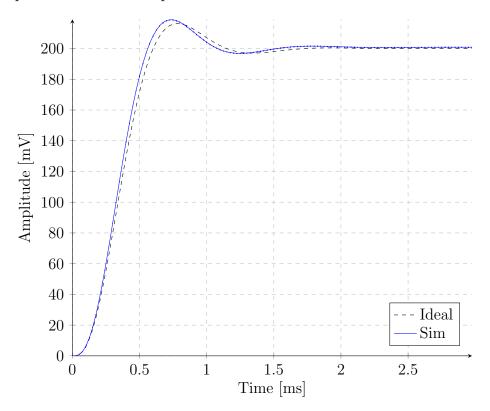

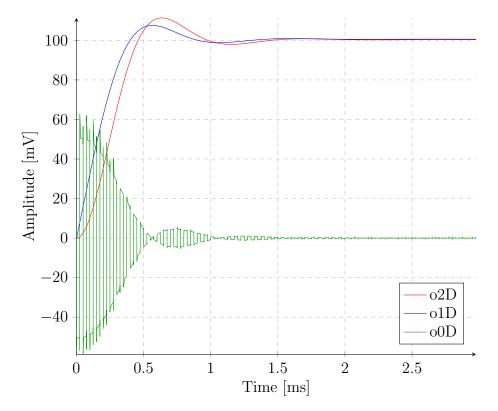

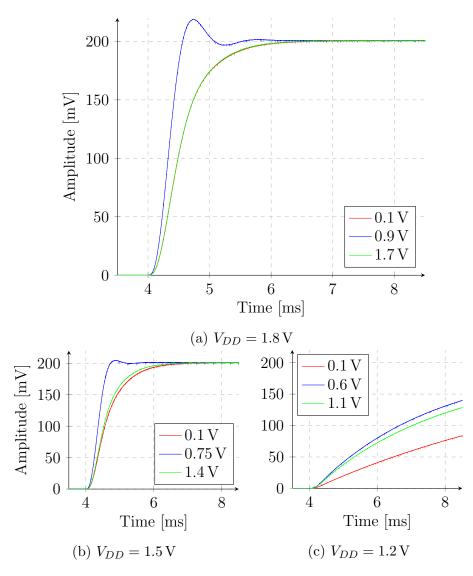

|          |       | 5.2.1   | Step response                                                                                            |   | 121 |

|          |       | 5.2.2   | Step response vs input CM and supply voltage                                                             |   | 123 |

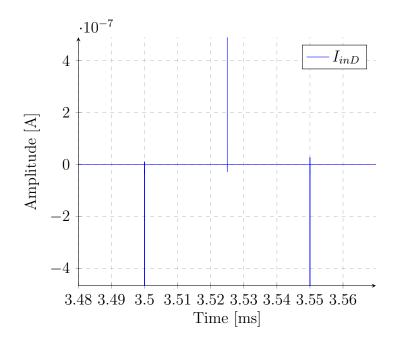

|          |       | 5.2.3   | Input impedance                                                                                          |   | 124 |

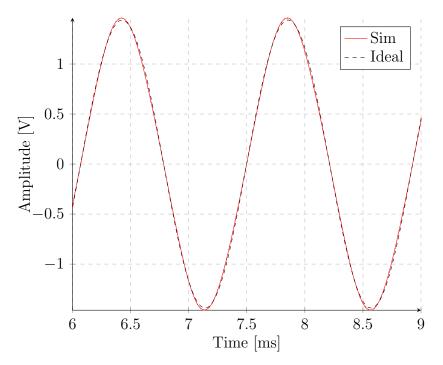

|          |       | 5.2.4   | High frequency distortion                                                                                |   | 127 |

|          |       | 5.2.5   | CM-differential intermodulation                                                                          |   | 128 |

|          | 5.3   | Differe | ential ranges                                                                                            |   | 129 |

|          | 5.4   | Noise   |                                                                                                          |   | 130 |

|          |       | 5.4.1   | Noise density, power and dynamic range                                                                   |   | 130 |

|          |       | 5.4.2   | Noise Equivalent Factor (NEF)                                                                            | • | 133 |

|          | 5.5   | CMFI    | $B \text{ loop stability } \ldots \ldots$ | • | 134 |

|          |       | 5.5.1   | CMFB open loop frequency response                                                                        | • | 134 |

|          |       | 5.5.2   | CMFB step response                                                                                       | • | 135 |

|          | 5.6   | Monte   |                                                                                                          | • | 136 |

|          |       | 5.6.1   | Offset                                                                                                   | • | 137 |

|          |       | 5.6.2   | Gain error                                                                                               |   | 138 |

|          | 5.7   | Electr  | ical parameters summary                                                                                  | • | 140 |

| Co       | onclu | isions  | and future developments                                                                                  |   | 142 |

| A        | Acr   | onyms   | 3                                                                                                        |   | 143 |

| Re       | efere | nces    |                                                                                                          |   | 145 |

# List of Figures

| 1.1  | A lambda sensor                                                 | 3   |

|------|-----------------------------------------------------------------|-----|

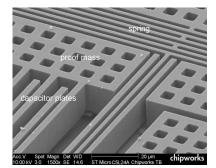

| 1.2  | A particular of a MEMS accelerometer                            | 5   |

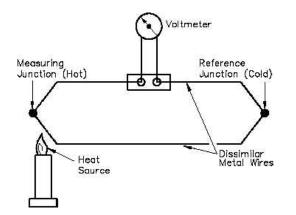

| 1.3  | Electric schematic of a thermocouple                            | 7   |

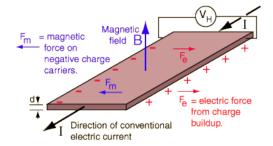

| 1.4  | Hall effect in magnetic sensors.                                | 9   |

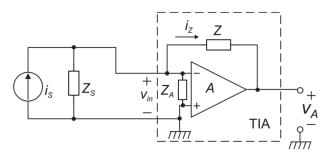

| 1.5  | TIA for interfacing sensors.                                    | 10  |

| 1.6  | Capacitive structure of inertial sensors                        | 11  |

| 1.7  | Capacitive interface for inertial sensors                       | 11  |

| 1.8  | Wheatstone bridge configuration to interface resistive sensors. | 12  |

| 1.9  | Noise bands determine the detection limit                       | 14  |

| 1.10 | Input and output signals in a fully differential amplifier      | 16  |

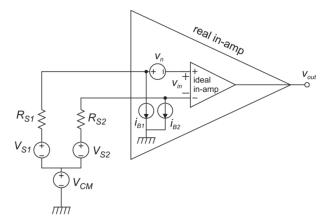

| 1.11 | Real inamp interfacing a real voltage generator                 | 20  |

| 0.1  |                                                                 | 0.4 |

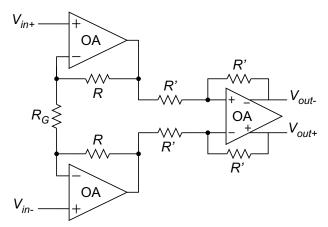

| 2.1  | Three Op-Amp topology                                           | 24  |

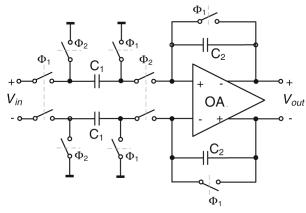

| 2.2  | SC topology.                                                    | 25  |

| 2.3  | Capacitively-Coupled topology.                                  | 26  |

| 2.4  | Current-Mode topology.                                          | 26  |

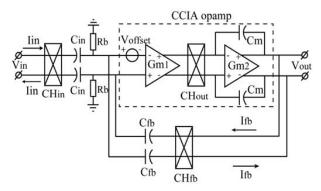

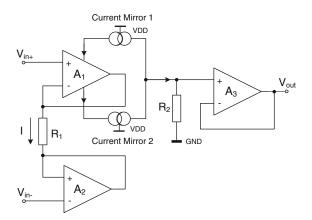

| 2.5  | Current Feedback topology.                                      | 27  |

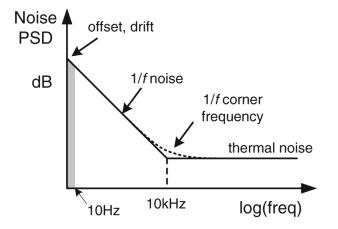

| 2.6  | Typical RTI noise PSD.                                          | 30  |

| 2.7  | CDS in a SC amplifier                                           | 31  |

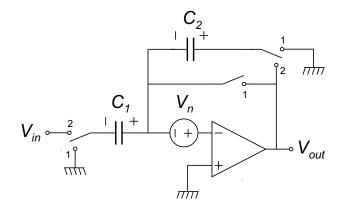

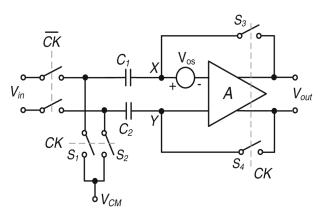

| 2.8  | Auto-Zeroing with input offset storage                          | 33  |

| 2.9  | Noise in Auto-Zeroing                                           | 34  |

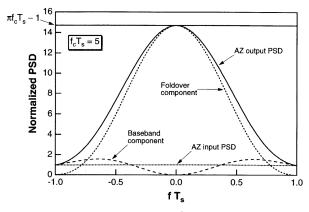

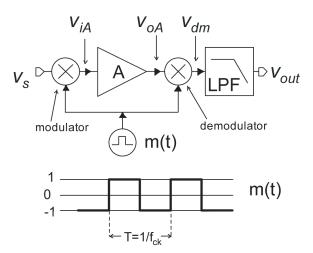

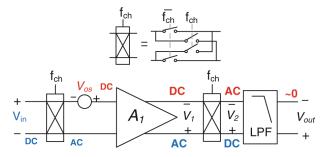

| 2.10 | CHS block schematic.                                            | 35  |

|      | Chopper modulator implemented with switches                     | 36  |

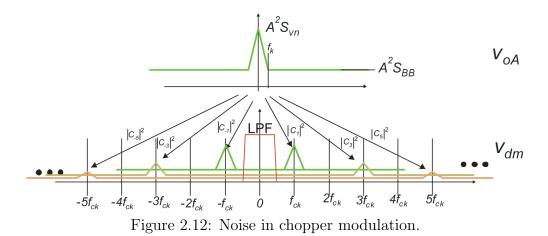

|      | Noise in chopper modulation.                                    | 37  |

| 2.13 | Miller integrators as LPF for a CFIA                            | 39  |

| 2.14 | State Variable Filter block diagram                             | 39  |

| 2.15 | State Variable Filter as LPF for a CFIA                         | 40  |

| 2.16 | Ripple Reduction Loop in a CFIA.                                | 40  |

|      | Dynamyc Element Matching in a CFIA                              | 42  |

| 2.18 | Gain Error Reduction Loop in a CFIA                             | 43  |

| 2.19 | Common Mode Equalization in a CFIA                              | 45  |

| 3.1  | High level schematic of the reference design                                    | 46  |

|------|---------------------------------------------------------------------------------|-----|

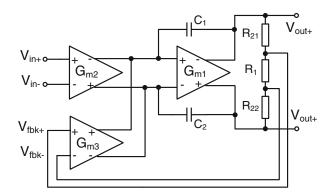

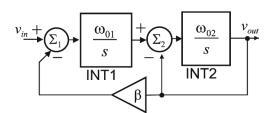

| 3.2  | Second order State Variable LPF block diagram                                   | 48  |

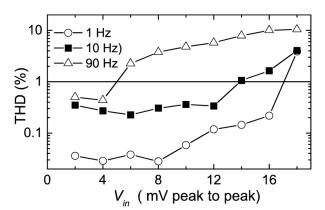

| 3.3  | THD vs input amplitude for different frequencies                                | 50  |

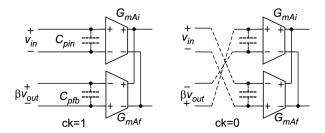

| 3.4  | Input connections in the two clock phases                                       | 51  |

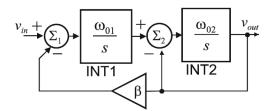

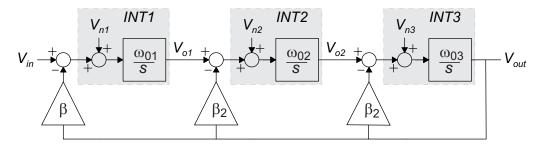

| 3.5  | Block diagram of a 3rd order State Variable LPF                                 | 54  |

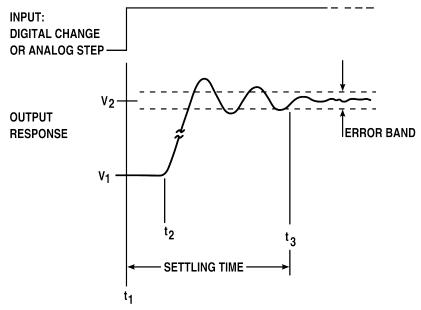

| 3.6  | Graphic representation of settling time                                         | 58  |

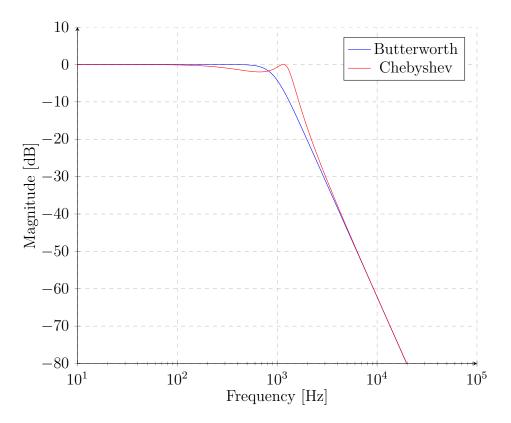

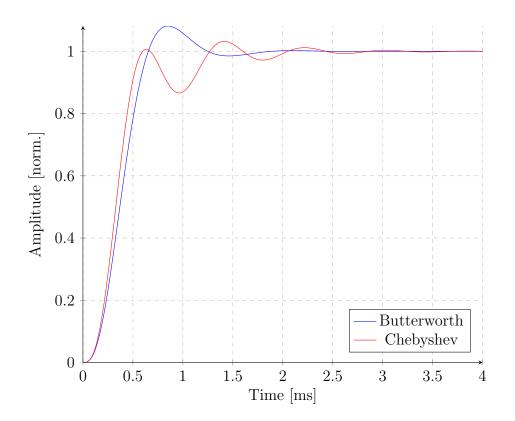

| 3.7  | Magnitude frequency response comparison                                         | 59  |

| 3.8  | Step response comparison                                                        | 60  |

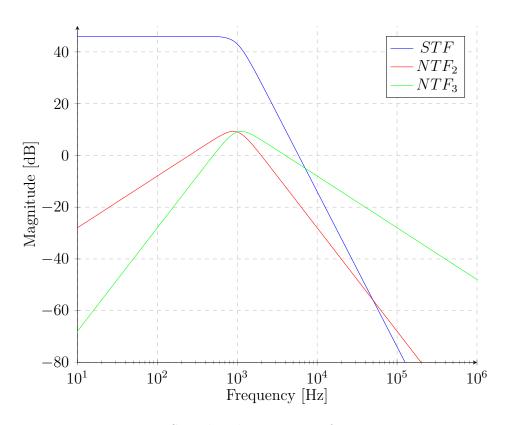

| 3.9  | Signal and Noise Transfer Functions                                             | 62  |

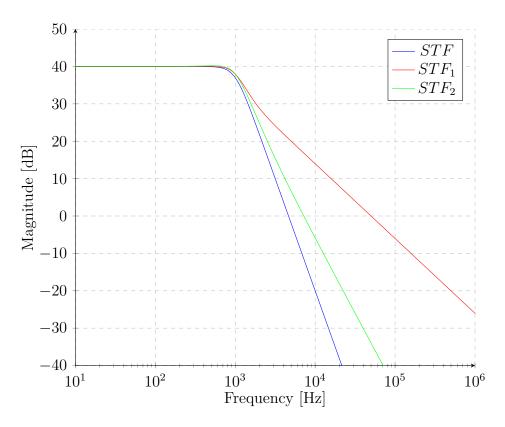

| 3.10 | Partial Signal Transfer Functions                                               | 67  |

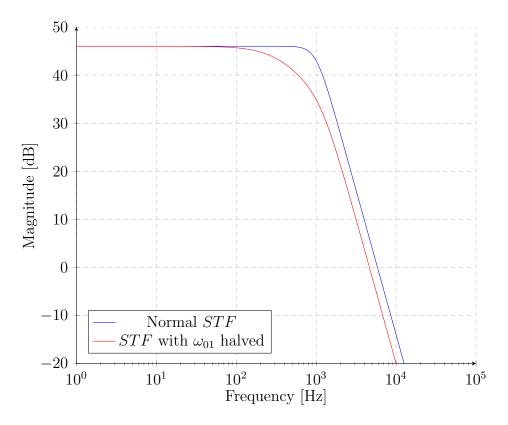

| 3.11 | STF comparison with different $\omega_{01}$                                     | 68  |

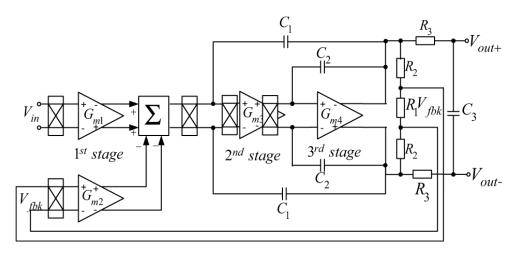

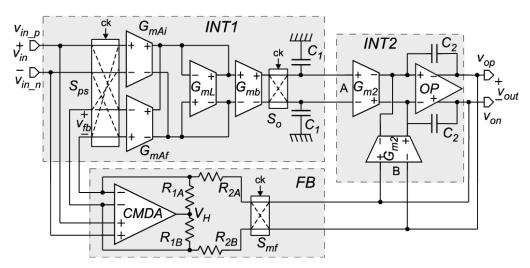

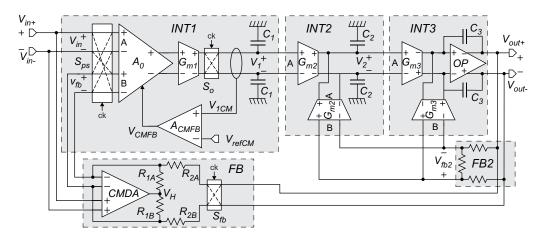

| 4.1  | Block schematic of the proposed InAmp                                           | 70  |

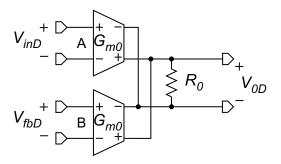

| 4.2  | Block schematic of the preamplifier                                             | 71  |

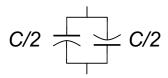

| 4.3  | Antisymmetric design of capacitors                                              | 74  |

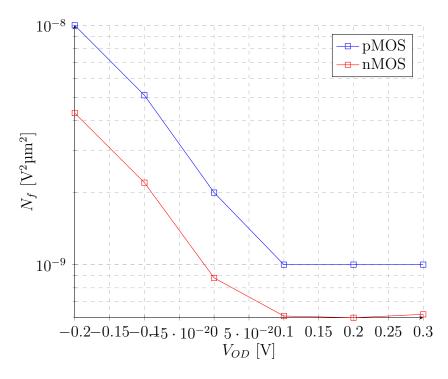

| 4.4  | $N_f$ values vs. $V_{OD}$ for p and n MOSFETs                                   | 78  |

| 4.5  | Classical folded cascode topology.                                              | 80  |

| 4.6  | Schematic of the preamplifier                                                   | 81  |

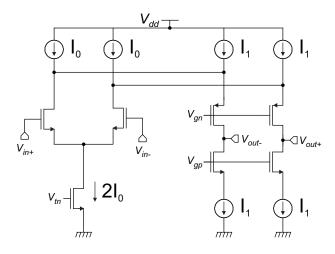

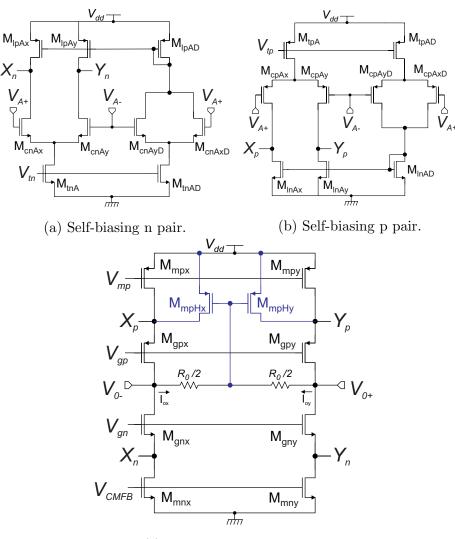

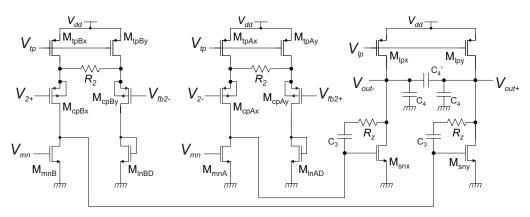

| 4.7  | Schematic of OTA1.                                                              | 88  |

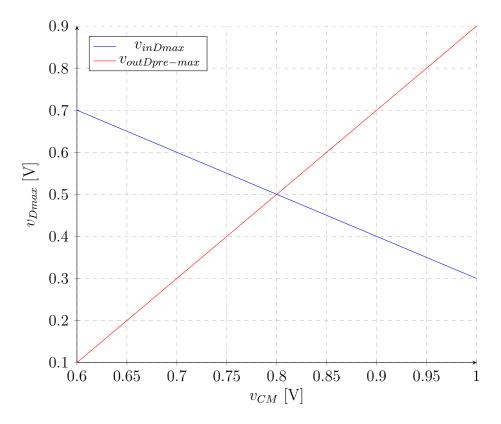

| 4.8  | Ranges intersection                                                             | 91  |

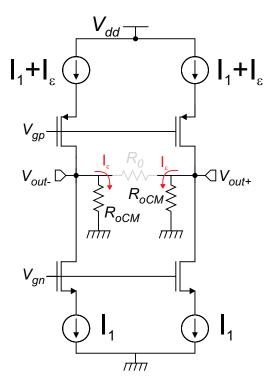

| 4.9  | Output CM offset in a cascode structure                                         | 94  |

| 4.10 | Classical CMFB block diagram.                                                   | 94  |

| 4.11 | Proposed implementation of CMFB                                                 | 95  |

| 4.12 | Block diagram of CMFB                                                           | 97  |

| 4.13 | Schematic of the Simple Buffer                                                  | 98  |

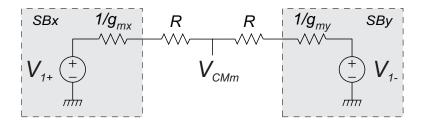

|      | The venin equivalent of the circuit                                             | 98  |

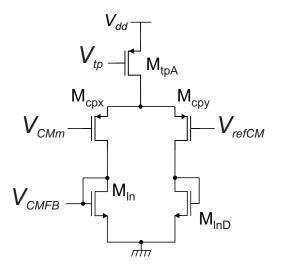

| 4.15 | Schematic of CMFB.                                                              | 99  |

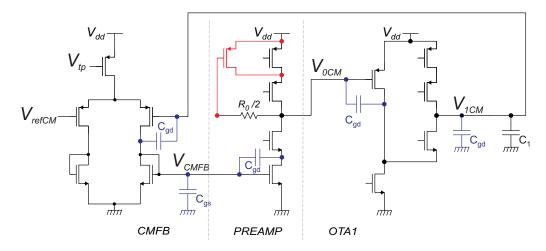

| 4.16 | Schematic of the CMFB loop, with the main devices involved                      |     |

|      | and the most relevant parasitic capacitances                                    | 102 |

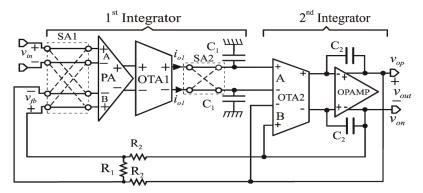

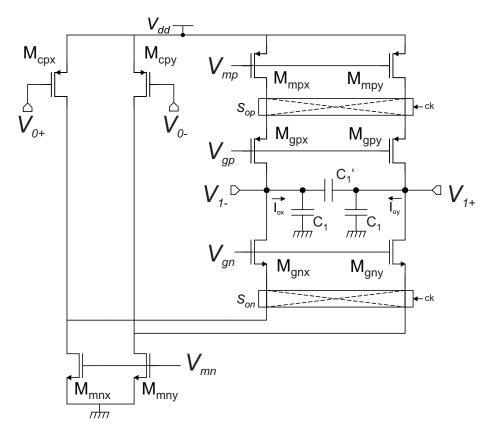

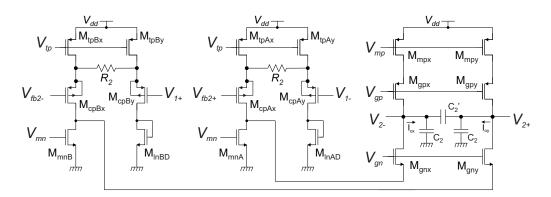

|      | Schematic of INT2                                                               | 104 |

|      | Schematic of INT3                                                               | 106 |

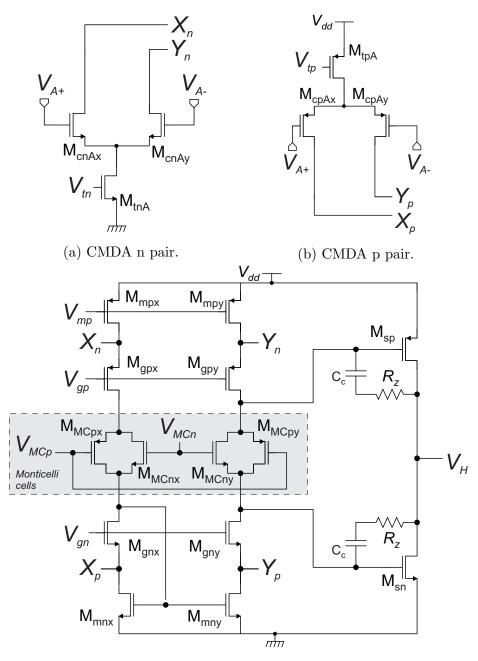

| 4.19 | Schematic of the CMDA. Only the differential pairs relative                     |     |

|      | to port are shown, for simplicity. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 113 |

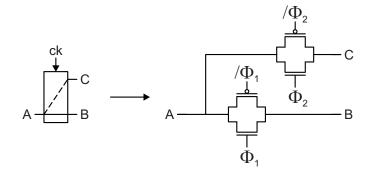

| 4.20 | Electrical implementation of a switch                                           | 116 |

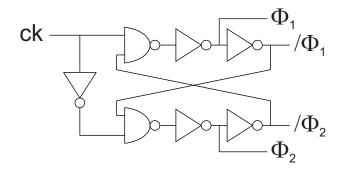

| 4.21 | Gate diagram of the Non Overlapping Clock Generator                             | 117 |

| 5.1  | Open loop frequency response of the three integrators                           | 119 |

| 5.2  | Frequency response                                                              | 120 |

| 5.3  | Step response                                                                   | 121 |

| 5.4  | Inner stages' signals for a step response                                       | 122 |

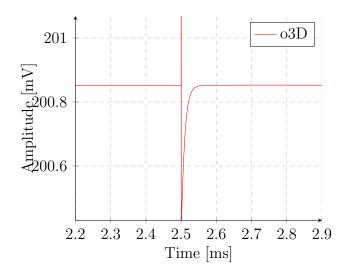

| 5.5  | Voltage spikes in the differential output.                                      | 123 |

| 5.6  | Step responses with different supply voltages and $V_{inCM}$ (val-               |

|------|----------------------------------------------------------------------------------|

|      | ues in the legends). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $124$ |

| 5.7  | Input differential current with 1 mV input                                       |

| 5.8  | Comparison between output and an ideal sine waveform 127                         |

| 5.9  | Inner stages signals                                                             |

| 5.10 | Intermodulation between common mode and differential paths.129                   |

| 5.11 | Voltage spikes in the differential output                                        |

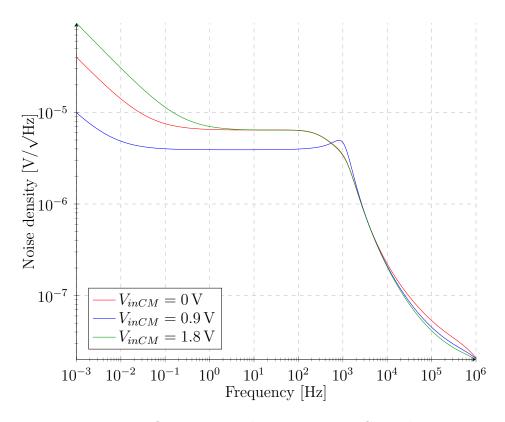

| 5.12 | Output noise density vs corners                                                  |

| 5.13 | Output noise density vs input CM voltage                                         |

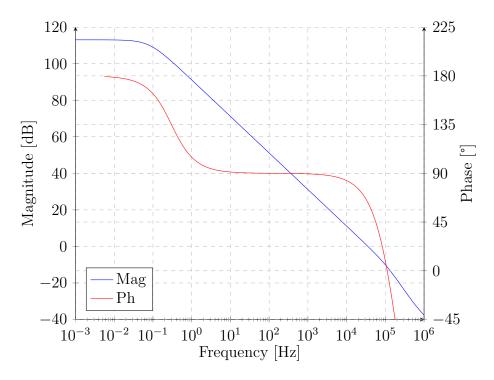

| 5.14 | CMFB loop frequency response                                                     |

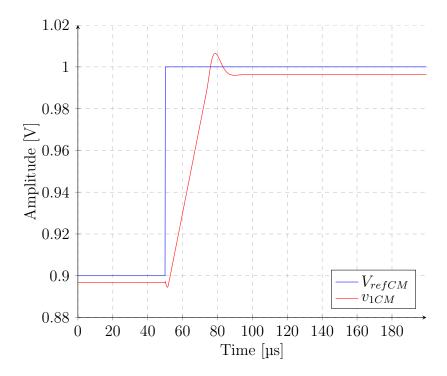

| 5.15 | Step response of the CMFB loop                                                   |

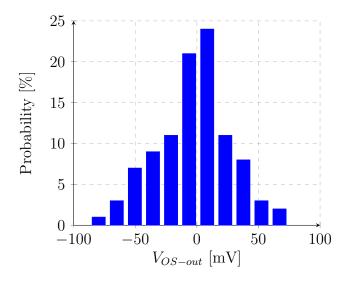

| 5.16 | Distribution of output offset (chopper disabled) 137                             |

| 5.17 | Distribution of output offset (chopper enabled)                                  |

| 5.18 | Distribution of gain values (chopper and port swapping dis-                      |

|      | abled)                                                                           |

| 5.19 | Distribution of gain values (chopper and port swapping en-                       |

|      | abled)                                                                           |

# List of Tables

| 3.1 | Normalized transfer function coefficients comparison. |   |   |   | 57  |

|-----|-------------------------------------------------------|---|---|---|-----|

| 3.2 | Unity-gain pulsations comparison                      |   |   |   | 57  |

| 3.3 | Settling time comparison.                             | • | • | • | 60  |

| 4.1 | Preamplifier devices dimensions                       |   |   |   | 87  |

| 4.2 | OTA1 devices dimensions                               |   |   |   | 93  |

| 4.3 | CMFB devices dimensions                               |   |   |   | 100 |

| 4.4 | INT2 devices dimensions                               |   |   |   | 106 |

| 4.5 | INT3 devices dimensions                               |   |   |   | 110 |

| 4.6 | CMDA devices dimensions                               | • | • | • | 115 |

| 5.1 | The three integrators' main parameters                |   |   |   | 118 |

| 5.2 | Offset $\sigma$ with and without chopper modulation   |   |   |   | 138 |

| 5.3 | Gain $\sigma$ with and without chopper modulation     |   |   |   | 139 |

| 5.4 | Simulated electrical parameters summary               |   |   |   | 141 |

## Introduction

Nowadays, while digital electronics is striving to reach higher and higher computational power and speed, analog electronics has found a renewed, fundamental role in the field of sensors readout. Sensors are used for in a wide variety of applications, from safety to environmental awareness, and can measure quantities such as temperature, pressure, radiation intensity, acceleration and angular velocity, strain and many others. The most important boost to the development of sensors was the introduction of MEMS in measurement systems: indeed, these extremely compact, low power, precise and low cost devices allow the integration of sensors in almost every context of everyday life, and smartphones are only one of the several examples of this trend.

In precision applications, it is compulsory to design a readout interface, called Analog Front End, that allows an accurate conversion of the measured quantity to a digital code. One of the most diffused architecture for an AFE is the instrumentation amplifier (InAmp), that is basically a differential amplifier with precise gain and high input impedance, thus able to interface a great variety of sensors. Among the several topologies, current feedback instrumentation amplifiers are often used, due to their high CMRR, effeciency and flexibility to be easily adapted to met different specification. The most relevant issue is gain error, caused by mismatch between the input stages, that can be critical when the circuit is implemented in a CMOS technology.

This technology is widely used thanks to its reduced cost, but CMOS analog circuits are affected, as known, by high offset, caused again by matching errors, and flicker noise. These problems are usually mitigated with the introduction of dynamic techniques such as Auto-Zero, Correlated Double Sampling and Chopper Modulation.

The purpose of this thesis is to propose an original solution for an instrumentation amplifier, with advanced strategies to reduce errors. Chopper modulation is used to reject offset and flicker noise, while the consequent products of demodulation (chopped offset) are strongly attenuated by a state variable third order Butterworth low pass filter. Port swapping is used to reduce the effects of the mismatch between the input stages, and thus to increase the gain accuracy, while it has a benefical side effect in increasing the input impedance, that with a simple chopper modulation would be too low for many application. On one hand, compactness and low power consumptions were goals as well; on the other hand, flexibility was the main keywork for this work. Indeed, while this amplifier is optimized to interface thermal sensors, it can work with a great variety of sensors thanks to its Rail-To-Rail common mode input range, that makes it suitable also for other application, such as current sensing.

Chapter 1 will present an overview of the most diffused sensors, to give an idea of the importance of analog design even in the digital era of these days and age. Then, sensors will be classified according to their output quantity, and the instrumentation amplifier will be presented, together with a brief description of all its characteristics, as the best achitecture to interface these sensors.

Chapter 2 will present the state of the art in the design of instrumentation amplifiers, highlighting pros and cons of the different topologies. From the most relevant references available in the literature, examples will be given for each one of them.

Chapter 3, instead, will focus on the reference design for this work, underlining the unsolved issues that were the starting point for this work. Then, the new solution is proposed, and the high level design is described: at this point, ideal stages will be considered, that however will allow the first expectations on the final performances of the proposed architecture.

A detailed transistor level description of each single block will be given in chapter 4, with an accurate mathematical analysis of the relevant equations that led to the sizing of the single devices. Noise, ranges, current consumption, compactness and feedback stability will be the main costraints to lead the transistor level design.

Finally, in chapter 5 we will present the most relevant simulations performed on the complete system, in order to evaluate the results of the accurate design and to present the most significant electrical specifications of the proposed solutions.

## Chapter 1

# Sensors and instrumentation amplifiers

### 1.1 Diffusion of sensors

The impressive development of electronics of the last few decades has deeply changed our lifestyle in several ways. On one hand, digital electronics has reached incredible levels of computational power and the telecommunication field has given us the chance to share information with the whole world in a stunningly simple and user-friendly way. On the other hand, the opportunity to acquire information about the physical world that surronds us was given by the development and the spread of sensors. Hundreds kinds of sensors are widely used in different context of our lives, and are more and more deeply embedded in our environment, so that common people usually don't even notice their presence nor appreciate their importance. But indeed they are often irreplaceable in many applications, whether they are just a means of monitoring physical quantities or they belong to a control loop together with a computational core and actuators.

**Safety related applications** There are many examples of critical contexts in which safety goals are achieved through a wide use of sensors. Let us think, for instance, of really complex architectures such as airplanes. The huge amount of flight and environmental variables, such as external air temperature and relative velocity, pressure and altitude, would make impossible for pilots alone to safely fly a plane, steadily facing all odds. Thus, these variables are constantly monitored by sensors literally spread all over the airplane, so letting pilots always make the better decision. In addition, redundant measurements (by means of multiple sensors of each kind) make the monitoring so accurate that is possible to let an automatic control system grab the reins of the flight. The importance of these sensors is testified by rare examples in which they did not work properly. One of the most famous is without any doubt the accident of flight Air France 447, in which on June, 1 2009 the 228 passengers of an Airbus A330-200 lost their lives: the final report showed that the accident was most probably caused by an incoherent air speed data measured by the Pitot tubes, that were obstucted by ice crystals. This situation led to a sudden disabling of the automatic pilot and the switching to *alternate law* flight program, an emergency program in which many other safety systems are disabled. The reaction of the pilots to the consequent stall was too slow, leading to the crash.  $^1$

Sensors of various types are of course embedded also in less complex systems, like trains or cars, in which they can achieve safety-related goals or simply can assist the user in common situations. One of the most popular cars' safety system is, for example, the Anti-locking Brake System (ABS): this feature prevents the wheels from blocking due to a too strong braking, thus avoiding unexpected skidding and keeping the braking distance The system continuously monitors each wheel's rotational speed short. through dedicated sensors, in order to release the brake and let the wheel regain static friction with the ground in case one of them turns significantly slower than the others. Another useful safety system in cars is the so called Electronic Stability Control (ESC). During normal driving, ESC works in background and continuously monitors steering and vehicle direction. It compares the driver's intended direction (determined through the measured steering wheel angle) to the vehicle's actual direction (determined through measured lateral acceleration, vehicle rotation (yaw), and individual road wheel speeds). ESC intervenes only when it detects a probable loss of steering control: this may happen, for example, when skidding during emergency evasive swerves, understeer or oversteer during poorly judged turns on slippery roads, or hydroplaning. In this case, ESC controls independently each wheel's brake in order to create torque about the vehicle's vertical axis, opposing the skid and bringing the vehicle back in line with the driver's commanded direction. Other safety related sensors can be the pressure sensors embedded in the newest cars' types, or the ones that detects if the driver is sitting and driving without the seat belt fasten. In addition, a relatively old safety system is the airbag: this balloon must inflate within a few milliseconds after a crash, that is detected by a fast accelerometer.

Another important and well-known sensor in modern cars is the so called

<sup>&</sup>lt;sup>1</sup>www.airfrance447.com

*lambda sensor* (figure 1.1). This sensor measures the quantity of uncombusted oxigen in the exaust stream, from which a CPU can calculate the air-fuel ratio in the engine and optimize the combustion process through a control loop.

Figure 1.1: A lambda sensor.

Another one is the speedometer, that is usually implemented as a set of magnets mounted on the output shaft or (in transaxles) differential crownwheel, or a toothed metal disk positioned between a magnet and a magnetic field sensor. Thus, the sensor produces a pulse wave at a frequency proportional to the average speed of the car. The speedometer, that usually is used just as an indicator for the driver, can

be part of a control loop, like many other senors, to form a cruise control: this feature, present in almost every new car, allows the driver to set a speed and then controls the fuel stream in order to mantain that speed within a certain range. This is just one of the many applications created to make the driving more comfortable: let us think, for instance, to assisted parking systems, in which proximity sensors inform the driver about the distance between the car and obstacles (other cars), or the automatic air conditioner, that controls the room temperature of the car with a closed loop that needs temperature sensors.

These are just a few examples of the most popular sensors: an average car can embed between 60 and 100 sensors, while this numbers are projected to reach as many as 200 sensors per car within few years.

Security related sensors are obviously present also in other contexts, like in factories where workers deal with dangerous machines (presses, saws or grindstones), or for monitoring the temperature of ovens in concrete production, or in the chemical industry where the concentration of toxic or dangerous gases must be constantly kept under control. Also the houses often feature safety systems such as anti-theft or antifire devices that use dedicated sensors.

**Sensors and environmental awareness** Safety is not the only reason for such a wide diffusion of sensors. In fact, one of the newest and most influencing trends is the aim to monitor and thus to protect the environment against pollution, especially in big cities. This field, known as *environmental awareness*, has grown strong in the latest years and aims to create a network of sensors, especially within the biggest urban areas, to monitor all the parameters that can affect the citizens' quality of life, such as air pollution but also traffic condition and availability of the major public services. This high level and complete monitoring, made possible also by the strong development of portable and low-cost digital devices with great communication capability, plays a key role in the creation of the idea of *Smart Cities*. One of the many definitions of this concept is given by Gerhard P. Hancke et al. (The Role of Advanced Sensing in Smart Cities, ): "A smart city is a city which functions in a sustainable and intelligent way, by integrating all its infrastructures and services into a cohesive whole and using intelligent devices for monitoring and control, to ensure sustainability and efficiency." One of the most advanced and effective example of the idea of Smart City is represented by the project called *SmartSantander*. In the spanish city of Santander, researchers from several universities have built a wide network of sensor nodes in order to constantly monitor the major environmental parameters and share them with all the citizen. The project exploits the rising idea of the Internet of Things, that is a network of thousands of intelligent sensing nodes communicating through an internet based protocol. The collected data can be of help to the common citizen to get information about traffic, available parking spots, and many other public services. On the other hand, data can be monitored by experts in order to control the air pollution level, the wind speed or the light intensity. From the sensors' point of view, the major innovation is the wide use of sensor nodes, that are tiny embedded systems with strong connection between sensors and computational/communication core: only the city of Santander counts as many as 12000 sensor nodes, monitoring parameters such as temperature, CO, noise, light, car presence in parking spots, etc. This is a great boost for the development of small and low power sensors of different kinds, the improvement of sensor fusion technologies and, with the advancing of process technologies, the diffusion of mixed signal architectures within miniaturized Systems on a Chip.

**MEMS sensors** In fact, the major boost to the wide diffusion of sensors was due to the development of small, low power, integrated sensors called MEMS (Micro Electro-Mechanical Systems). With this technologies it is possible to miniaturized even complex mechanical structures such as multi axes accelerometers and gyroscopes, advanced chemical and optical sensors, temperature and pressure sensors, as well as compasses, microphones, microfluidic devices and many others, all within a Silicon die (thus on a millimetric surface). The possibility to build such mechanical structures on the Silicon surface with a common CMOS process has significantly lowered these products' price, while usually really small dimensions bring low power consumption: these reasons make MEMS sensors particularly suitable for battery powered, portable devices like, most of all, smartphones.

In such devices, sensors are used to create a strong interaction with the user, even on a physical level: let us think, for example, of a multi axes accelerometer that informs the device about its orientation referred to the ground, thus, turning the screen in panorama mode when the phone's long edge is turned parallel to the ground (to better enjoy videos, for instance). Of course, the major benefits from the integration of accelerometers and gyros are earned

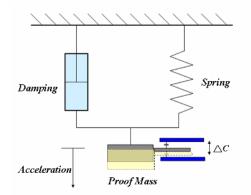

Figure 1.2: A particular of a MEMS accelerometer.

by videogames, nowadays fully diffused in smartphones. This technology for videogames, actually, was first implemented by Nintendo when it launched on the market its Wii products: this console, first in its category, used interactive remotes to control the game directly with the user's movement. The accelerometer is nothing more than a mass-spring-damper system, with submillimetric characteristic dimensions, that translates an acceleration into a displacement: the body of the sensor is tied to the device, thus when an acceleration is imposed to it, inertial forces are induced on the suspended proof mass that shifts from its quiescent position proportionally (for small variations) to the acceleration. The displacement then can be measured by a system of capacitive plates, giving a voltage difference proportional to it as output. After an analog to digital conversion, the data can be processed by a CPU and used, for instance, to control the game parameters.

Obviously, movement sensors are not used only in videogames. For instance, gyroscopes have found an important application in another field of consumer electronics, like professional cameras. Almost all new lenses for reflex cameras, as a matter of fact, feature a Vibration Reduction (VR) system, that tends to avoid the motion blur: often, when light conditions are not critical but not excellent either, the exposure time is long enough to let the optical sensor be influenced by the natural vibrations of the photographer's hand, thus creating an unpleasant micro-blur effect. It has been proved that these movements consists primarily in rotations along a horizontal axis (pitching, that is a vertical movement) and a vertical axis (yawing, that is a horizontal movement). A system of two gyros detects each one of these effects: a dedicated CPU then samples the data around a thousand times per second and controls actuators, that compensate the shift by moving the lens.<sup>2</sup>

Though, the most recent and advanced expample of miniaturization and integration between sensors and human life is probably the field of the *wearable* devices. This new concept exploits to a maximum level the concepts of miniaturization and energy efficiency in order to create and develop intelligent devices, thought to be constantly in touch with the human body, as an actual extension of it with a brand new set of possibility always at hand. One of the most important event in this field was the conference held in Santa Clara, California (US) on November 12-13, 2014, called "Wearable Sensors and Electronics"<sup>3</sup>, where reseachers and CEOs from all over the world gathered together to discuss the development of wearable devices, boosting the interest in areas such as energy harvesting, printable electronics and, of course, all kinds of integrated, low power MEMS sensors. The research in this field is being currently led in several institutions, one for all the Center for Wearable Sensors of the UCSD Jacobs School of Engineering <sup>4</sup>, Here they are working on the development of different kinds of sensors that should monitor several body parameters, through chemical, physical and electrophysiological techniques, sometimes even with polymer-based substrates that can be implanted inside the tissues for long term analysis. The aim of this project is, of course, healtcare and preventive medicine, through constant analysis of heart rate, hydration levels, blood sugar and more, or simply the user's comfort, like in smart clothes for personalized cooling and heathing.

### **1.2** Classification of sensors

As seen in the previous paragraph, electronic systems can deal with an enormous variety of sensors: what they have in common is the need to produce a value of the measured quantity to be elaborated by a processing unit, typically a digital CPU. Thus, a analog-to-digital converter (ADC) is needed to turn the analog output of the sensors into a properly coded binary number, so that the CPU can handle the data. On one hand, ADCs typically can convert an input voltage  $V_{in}$  into a coded binary number  $C_{out}$ , accordingly to an equation such as

$$C_{out} = \left\lfloor \frac{V_{in}}{V_{REF}} \cdot 2^n \right\rfloor \tag{1.1}$$

<sup>&</sup>lt;sup>2</sup>http://www.nikon.com/about/technology/rd/core/software/vr\_e/

<sup>&</sup>lt;sup>3</sup>www.wearablesensors2014.com

<sup>&</sup>lt;sup>4</sup>http://www.jacobsschool.ucsd.edu/wearablesensors

where  $V_{REF}$  is a reference voltage (often  $V_{DD}$ ) and n is the number of bits. On the other hand, a sensor is by definition a transducer, that is a device that translate a physical quantity (acceleration, temperature, pressure, etc.) into an electrical one, but not necessarily a voltage; and even if it is a voltage, this is often not suitable for a direct conversion. Here comes the need for an analog block, called Analog Front End (AFE), whose goal is to transorm the sensor's output quantity into a suitable voltage for the ADC. Thus, from the point of view of an analog designer, one of the most relevant classifications of sensors is according to their output quantity.

**Voltage** The category of sensors that produce a voltage as output quantity is surely the most populated. It gathers different subcategories, the most important of which are listed below.

• Thermoelectric sensors can transform a temperature difference into a voltage thanks to the Seebeck effect. The most diffused example is the thermocouple, that is basically a set of two different metals joined together in two different points (junctions).

Figure 1.3: Electric schematic of a thermocouple.

If one of the metals is cut, and the two junctions (A and B) are at different temperatures ( $T_A$  and  $T_B$ ), a voltage difference  $V_{out}$  is generated between the two ends of the cut metal. Usually one junction, called *measuring junction* (hot), is actually used to measure an absolute temperature  $T_x$ , and the other, called *reference junction* (cold), is kept at a reference temperature  $T_{REF}$ , like room temperature (that can be known or opportunely compensated) or at 0°C in a melting ice mixture. The output voltage is then a function of the temperature difference and can be approximated by a piecewise linear function. For most application, the function can be considered linear:

$$V_{out} \approx k(T_x - T_{REF}) \tag{1.2}$$

where the constant k depends strongly on the materials involved. One of the reason of the huge diffusion of thermocouples is that they can be easily integrated in a silicon chip: usually the two conductive materials are n and p polysilicon wires, with a silicide metalization on the junction to avoid a rectifying behaviour.

Furthermore, temperature measurements can be used for many other indirect measurements: it can be, in fact, the basic element of fluximeters, bolometers (IR light level detectors) or hot plates (sensors of eso/endothermic chemical reactions).

• Electrochemical sensors measure ion concentration in a liquid or a gas. Similarly to galvanic cells, they produce an output voltage proportional to the logarithm of a ion concentration:

$$V_{out} = k \cdot \log[C] \tag{1.3}$$

They can be used, for instance, to measure pH in solution, or gas concentrations like the *lambda sensor* (see above) to monitor the  $O_2$  level in the exaust stream.

- **Piezoelectric sensors** are crystals that, if compressed by an external force, produce on their faces an electric charge proportional to it (actually they are sensible only to force variations), thus a voltage difference can be measured. These are characterized by an extremely high sensitivity, that makes them perfect for integrated microphones (and, used as actuators, small speakers) or tactile sensors.

- Another widely used category of sensors with voltage as output quantity is that of **magnetic Hall sensors**. These are basically metal lines biased with a constant current I: if a magnetic field **B** is present, the current carriers travelling through the conductor undergo the Lorentz force, that pushes them in a direction orthogonal to both the magnetic field and their velocity. In the steady state condition, an electric field is generated in order to compensate the charge displacement, and the consequent voltage difference can be measured. Since the Lorentz force is  $\mathbf{F} = q\mathbf{v} \times \mathbf{B}$  and is equal to the electrostatic force, then  $E = vB_{\perp}$ . We have then V = Ew,  $I = j \cdot wh$  and j = qnv. Finally an expression for the measured voltage is:

$$V_H = \frac{1}{hnq} IB_\perp = k_H IB_\perp \tag{1.4}$$

being  $k_H$  a constant depending only on the sensor's electrical and geometrical parameters.

Figure 1.4: Hall effect in magnetic sensors.

A single Hall plate, like the one in figure 1.4, is obviously sensible to only one of the three components of the magnetic field **B**: in order to measure the direction of the field, three different plates are needed, and the three independent measurements must be opportunely elaborated by a CPU. This, for example, is how an integrated compass is achieved.

Even though these sensors produce a voltage as output quantity, in most cases it is not ready to be directly converted by an ADC (the reasons for this will be discussed later). Thus, a typical interface for this kind of sensors is the **instrumentation amplifier** (In-Amp): this device is mainly a differential amplifier with extremely precise gain, in order to adapt the input signal to the ADC input ranges (to increase resolution) without loss of accuracy in the measurement. All the characteristics of this kind of amplifier will be deeply discussed in the next paragraphs.

**Current** Among the sensors that produce a current as output quantity, one of the most relevant examples is the *photodiode*. These are basically *pn* junctions that, if hit by energetic particles like photons, produce electronhole pairs, that is an inverse bias current proportional to the number of photons that hit it (thus to the light intensity). To transform this current into a voltage, a first solution could be to simply bias a test resistor with that current and measure the voltage drop across the resistor. Actually, the sensor is nothing like an ideal current generator (its output impedance is often too low), so this way the loading effect would not be negligible. Instead,

a Trans-Inpedance Amplifier (TIA) is more often used, that guarantees a low loading effect at least al low frequencies.

Figure 1.5: TIA for interfacing sensors.

Other sensors have not a current output, but more precisely a charge output, that is the output quantity proportional to the signal to be measured is an electric charge. Though, the only relevant example is the Charge Coupled Device (CCD), a light sensor used years ago for image aquisition (mainly digital cameras), now almost completely replaced by CMOS sensors, that are basically photodiodes.

**Capacitance** Sensors belonging to this category have a capacitive structure, whose value of capacitance can vary mainly for two reasons. In one case, a physical quantity can modify the value of the relative dielectric constant  $\epsilon_r$  of the material between the conductive plates: in this case chemical substances can react with the dielectric material, obtaining thus a measure of its concentration. Far more frequent is the case in which the capacitance is changed because the geometry of the structure varies, that is the plates shift one on another (reducing the effective area of the capacitor) or simply they get closer or more distant. This, for example, is the case of inertial sensors, such as accelerometers and gyroscopes: as said in chapter 1, these consist in a proof mass that, thanks to inertial forces, shift from the quiescent position. Then, they usually feature one conductive plate per side while two others plates are tied to the substrate, as seen in figure 1.6.

So, being  $C_0 = \epsilon A/d$  the quiescent value of the two capacitances, when the mass shifts towards one side by a distance x the two capacitances change their value as follows:

$$C_1 = \epsilon \frac{A}{d+x} = \frac{C_0}{1 + \frac{x}{d}} \tag{1.5}$$

$$C_{2} = \epsilon \frac{A}{d-x} = \frac{C_{0}}{1 - \frac{x}{d}}$$

(1.6)

Figure 1.6: Capacitive structure of inertial sensors.

One simple way to extract a voltage from this structure is to supply a reference  $\pm V$  across the series of the two capacitances (see figure 1.7). The voltage present in the central node will then be:

Figure 1.7: Capacitive interface for inertial sensors.

$$V_{out} = V \frac{C_2 - C_1}{C_2 + C_1} = V \frac{1 + \frac{x}{d} - 1 + \frac{x}{d}}{1 + \frac{x}{d} + 1 - \frac{x}{d}} = V \frac{x}{d}$$

(1.7)

Alternatively, the measure can be made with means of a TIA and a sinusoidal generator, or with charge amplifiers (not discussed here).

**Resistance** A good variety of sensors have an output quantity that is a resistance: this is the case, for instance, of temperature sensors like thermistors or RTDs (Resistance Temperature Detectors). The latter are frequently Platinum resistors (PT100), that features a particularly linear and accurate T-R transcharacteristic:

$$R(T) = R_0 \left[ 1 + \alpha (T - T_0) \right]$$

(1.8)

where  $R_0$  is the resistance shown at  $T_0$  (for PT100 these values are 100 $\Omega$  at 0°C). The coefficient  $\alpha$ , also called Temperature Coefficient of Resistance (TCR) is crucial for the accuracy of the sensor: PT100 is often used because it has a particularly constant and precise value of TCR (0.00385/K over a wide range of temperatures).

Another important sensor belonging to this category is the piezoresistor, a resistor that changes its value of resistance when strained: it is used widely as a *strain gauge* to measure the strain ( $\epsilon = \Delta l/l$ ) of mechanical structures. Its resistance, at least for small variations, can be written as

$$R(\epsilon) = R_0(1 + G\epsilon) \tag{1.9}$$

where G is called gauge factor and depends strongly on the material. For example, for non-piezoresistive material this effect is only caused by geometric reasons: when a metal resistor is stretched, it gets longer and narrower, so its resistance gets higher, and vice versa. For piezoresistive materials, the effect is enhanced because the value of resistivity (independent on geometry) can change strongly with the strain.

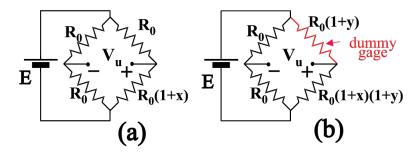

In order to interface these kinds of sensors, an accurate bias current could be sufficient to produce a voltage, but in general it is preferred to use a configuration called *Wheatstone bridge* (figure 1.8). Since both RTDs and strain gauges have the same kind of mathematical expression for R, let's consider the latter, with the variable  $x = G\epsilon$ .

Figure 1.8: Wheatstone bridge configuration to interface resistive sensors.

The output differential voltage is then:

$$V_{out} = E\left(\frac{R_0}{R_0(2+x)} - \frac{R_0}{2R_0}\right) = -E\frac{x}{2(2+x)} \approx -\frac{E}{4}x$$

(1.10)

for small variations. The main advantage of using this configuration is that, if the  $R_0$  resistors are dummy sensors (that is not used to measure anything, but shares the same environmental conditions) identical to the active one, all other dependancies and drifts are compensated. See again figure 1.8: on the right, the temperature dependance is expressed through the factor (1 + y). It is evident that this way the output voltage is completely independent from thermal drifts. Furthermore, if strain gauges could be placed in antisymmetrical position on the object to be monitored, and properly connected in the Wheatstone bridge, the sensitivity could be increased by a factor of 2 (or as much as 4 if 4 gauges are used).

Thanks to the Wheatstone bridge, again the best solution to deal with this output voltage is an instrumentation amplifier, that will now be discussed in detail.

### **1.3** In-Amps for sensor interfacing

We have said that, even for sensors that already present a voltage as output quantity (or resistive sensors in a Wheatstone bridge configuration), it's impossible to interface them directly to an ADC: in fact, many reasons concurr to this conclusion, the most relevant of which is related to the concept of Dynamic Range (DR).

Dynamic Range can be defined as the ratio between the greatest measurable value (Full Scale voltage) and the smallest detectable value (Detection Limit voltage):

$$DR = \frac{\Delta V_{FS}}{V_{DL}} \tag{1.11}$$

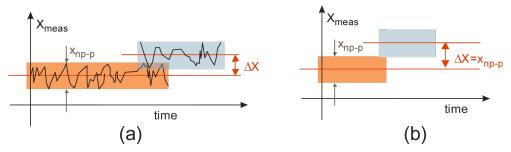

Now, the term  $\Delta V_{FS}$  is quite straightforward to understand: it is simply the sensor's output voltage swing correspondent to the difference between the highest and the lowest possible values of the measured quantity, and it depends only on the sensor's characteristics. As said above, it's quite common to have full scale voltages as high as a few mV: for example, a K type thermocouple (the most common type) has a sensitivity of  $41\mu V/^{\circ}C$ , that is a voltage of only 4.1mV for a  $100^{\circ}C$  full scale. The term  $V_{DL}$ , on the other hand, is strongly dependent on the noise voltage that is summed to the signal. This noise, in a first approximation, can be considered gaussian white noise because originated by random thermal agitation of the carriers (thermal noise). Although it can spread among a non limited interval of values, we can indentify bands in which the noise voltage will statistically reside: that is, given a certain RMS value  $v_n$ , equal to the standard deviation  $\sigma_n$  of the gaussian distribution, it is known that the noise will assume values in the range  $\pm 2\sigma$ , for example, in 95.4% of a given time interval. Then, we can consider a band wide  $4\sigma_n$ , that sets the measurement's detection limit: actually we have assimilated our noise to a periodic wave with a crest factor of 2, that is a  $v_{n-pp} = 4v_n$ . This value  $v_{n-pp}$  is then the width of the noise band of the signal: it is evident than that two different values of the signal can be distinguished reliably only if their noise bands don't overlap.

Figure 1.9: Noise bands determine the detection limit.

The relevance of Dynamic Range is that it is directly related to the Effective Number Of Bits (ENOB) that the following ADC will have. DR is in fact the number of different values of the input voltage that an ADC is able to distinguish: so an expression for the ENOB can be

$$ENOB = \lfloor \log_2(DR) \rfloor \tag{1.12}$$

Now, a crucial point is that DR cannot be raised during the signal elaboration: this is because each stage of the elaboration chain will surely present a Referred-To-Input (RTI) noise that will sum to the noise already present and will degrade the Dynamic Range. Our goal is to keep this degradation negligible, and the use of an In-Amp will be the best solution.

Let's suppose to place an ADC directly at the output of the sensor: the DR will then be (the notation  $v_{n-pp}$  will be omitted)

$$DR = \frac{\Delta V_{FS-s}}{v_{n-s} + v_{n-ADC}} \tag{1.13}$$

Since ADCs' RTI noise is usually extremely high and greater than the sensor's noise, such degradation of the dynamic range would compromise the measurement.

The use of a In-Amp as a *low noise preamplifier* solves this problem. In fact, the total RTI noise will now be

$$v_{nRTI} = v_{n-pre} + \frac{v_{n-ADC}}{A} \approx v_{n-pre}$$

(1.14)

if the preamplifier gain A is high enough. Then, if the preamplifier RTI noise  $v_{n-pre}$  is smaller enough than the sensor's noise, the degradation of the DR will be negligible:

$$DR = \frac{\Delta V_{FS-s}}{v_{n-s} + v_{n-pre}} \approx \frac{\Delta V_{FS-s}}{v_{n-s}}$$

(1.15)

Of course, the preamplifier gain cannot be made too high for range related matters: indeed, a condition to assert is that the preamplified full scale signal will fall in the ADC's input voltage ranges, otherwise the measurement would saturate before reaching the full scale values. This condition is expressed by the relation

$$A \cdot \Delta V_{FS-s} \le V_{REF-ADC} \tag{1.16}$$

In order to exploit the full DR of the ADC (given by its ENOB), it is necessary that the output range of the amplifier matches as closely as possible with the ADC input range.

While one of the main reasons to use a In-Amp has been made clear, it is necessary to analyze in detail all its characteristics, the reasons that make them relevant and non idealities to be considered in order to keep errors low.

Gain First of all, gain must be precisely known, constant and uniform through all the input signal bandwidth. This condition is compulsory, given the need to guarantee the precision of the measurement. Since gain is a dimensionless quantity, usually the best way to make it precise is to design an architecture in which gain is function of only ratios of homogeneic quantities, like resistances or capacitances. This is done to prevent the gain to depend too much on process errors and temperature: while global errors are usually huge, they usually affect the components' parameters with similar relative errors, if proper precautions are taken during the layout design. So, matching errors, that is parameters variations between two components of the same kind, in the same chip, are extremely lower than global errors: furthermore, in most processes matching is best for passive components, and this justifies the use of resistors or capacitors to set the gain of In-Amps. Of course, if matching errors affect the gain precision more than what allowed by specifications, other countermeasures are needed: the most frequent one in such cases is laser trimming, that is a post-production process in which dimensions of components are individually modified by burning sections of them with a high power laser beam, in order to reach the precision needed. Of course, since this process must be made for each chip individually, it implies a recurring cost that cannot be cut down with large scale production: laser trimmed chips are then far more expensive and are reserved for extremely high precision applications.

**Differential input** The use of differential approach has several advantages, often irreplaceable, that are making it more and more preferrable to a single-ended one in almost all fields of electronics. So, In-Amps have differential inputs not only to better interface all kinds of sensors, some of which have intrinsic differential output (like resistive sensors in a Wheatstone bridge configuration), but to take full advantages from the differential approach. In fact, while not requested by the definition of In-Amps, most of them in integrated applications are *fully differential*, meaning that they have both differential input and output.

A differential signal is the difference between two signals, both referred to ground. If these signals are  $v_p$  and  $v_n$ , we can define for the signal a differential mode and a common mode, as follows:

$$v_d = v_p - v_n \tag{1.17}$$

$$v_{cm} = \frac{v_p + v_n}{2} \tag{1.18}$$

In case of a fully differential amplifier (see fig 1.10), we can define the differential mode and common mode for both input and output ports.

Figure 1.10: Input and output signals in a fully differential amplifier.

In such configuration, we can also define four different gains as ratios between different small signals:

$$A_{dd} = \frac{v_{d-out}}{v_{d-in}} \qquad \qquad A_{cd} = \frac{v_{d-out}}{v_{cm-in}} \qquad (1.19)$$

$$A_{dc} = \frac{v_{cm-out}}{v_{d-in}} \qquad \qquad A_{cc} = \frac{v_{cm-out}}{v_{cm-in}} \qquad (1.20)$$

Of course, the most relevant gain is  $A_{dd}$ , since it deals with the meaningful signals and it has to be extremely precise. The strongest power of a differential approach is, beyond any doubt, disturbance rejection: if schematic and layout design is adequate, most interferences can be influencing only the common mode and thus be completely rejected by the differential mode, that is the meaningful signal. One of the most frequent interference that affect electronic circuits is caused by capacitive/inductive coupling of 50 Hz mains voltage: in biomedical applications - and it is just one of many examples - measurement instruments are tied through probes to the human body, that offers a huge parasitic capacitance with the building's electric net, thus cathcing a 50 Hz (60 Hz in America) large sine wave that is sensed by the measurement instruments. But if two differential probes are used, this disturbance would affect both of them almost in the same way, resulting in a common mode interference and leaving the differential mode unaltered.

Another problem, this time more frequent in PCBs, is non equipotential ground: when a cascade of components (or ICs) is given supply from one side, the supply current flowing through the parasitic resistance of ground wire causes a voltage drop between the ground pins of the different ICs, that thus work at different ground potentials. While this would be dangerous for a single ended signal, it is just a common mode disturbance for fully differential architectures.

Inside Silicon dies (but not only), in addition, a frequent issue is the so called *crosstalk*, that is capacitive coupling between metal lines close one to another: if a large voltage signal is in one line, it will pass into the other through the parasitic capacitance between them, resulting in a huge disturbance, especially if the second line is a high impedance node. With an accurate layout, a differential architecture can solve this problem trying to balance the parasitic capacitance between the first line and the other two: ideally, if they match (for example if the disturbing line is at the same distance from the other two), the disturbance will be the same in both lines and again will not affect the differential mode. All these advantages are achieved, of course, only if the common mode disturbance do not affect the output differential voltage: this is true if the following condition on the Common Mode Rejection Ratio (CMRR) applies.

$$CMRR = \left|\frac{A_{dd}}{A_{cd}}\right| \gg 1 \tag{1.21}$$

Furthermore, a full differential approach brings other relevant advantages that must be cited. First of all, it doubles the output swing: it is straitforward to understand that, if each signal could swing from  $V_{min}$  to  $V_{max}$ , the total output swing would be

$$\Delta V_d = V_{d-max} - V_{d-min} = (V_{max} - V_{min}) - (V_{min} - V_{max}) = 2(V_{max} - V_{min})$$

(1.22)

This, keeping equal the noise, brings an increment by a factor 2 to the Dynamic Range, so the ENOB is increased by one.

Last but not least, a subtle improvement is related to distortion. Let for example be  $v_{out-p} = f(v_{in-d})$  the transfer function between differential input and the positive output. The negative output will be characterized by an antisymmetric transfer function, that is  $v_{out-n} = f(-v_{in-d})$ . For a linear amplifier, it should be as linear as possible, but it will surely have second, third etc. order components, responsible for the degradation of the Total Harmonic Distortion (THD). If the output signal is differential, it will then be

$$v_{out-d} = f(v_{in-d}) - f(-v_{in-d})$$

(1.23)

that is evidently an odd function, so it has no even order terms: since most of the THD is usually given by second order harmonics, this consists in a good improvement for linearity.

**High CMRR** We have said that, in order to exploit the benefits of a differential approach, it is necessary for an In-Amp to have a CMRR as high as possible. Usually, it is so high that it is expressed in dB, and it's quite common to find In-Amps with CMRR as high as 120 dB. It is a measure of how much the output depends on the differential input more than on common mode input. Having a high CMRR is not important only to reject disturbances: indeed some application require a high CMRR even if no disturbance affected the circuit. This is the case of applications in which the input common mode voltage changes during the measuring process: one example could be the *current sensing* use to monitor discharge of lithium The easiest way to monitor the charge level of a battery is, batteries. knowing the initial charge, to keep track of the charge erogated by measuring the current and integrating it with respect to time: this method is known as *Coulomb counting*. It is achieved by using a shunt resistor in series to the battery, making it possible to measure the voltage drop on it and so the current. Now, usually the shunt resistor is placed next to the hot pole rather than the cold one, to avoid the effect of non equipotential ground already mentioned. Since the output voltage of a battery gets lower as the battery discharges, the In-Amp will work with different common mode voltages and the measure should not be affected.

It must be noticed that, if a circuit is designed with perfect symmetry, there's no reason for a common mode input voltage to affect the differential output: in this case as well, are matching errors that cause a degradation of CMRR, and they can be kept low, as well as with a proper layout, with post-production solutions like laser trimming.

**Input CM range** Although some application set *a priori* the input CM that the In-Amp will be dealing with, it is often a good quality to have a wide input CM range, in order to keep flexibility. A general purpose In-Amp, for instance, should have a Rail-To- Rail (R2R) input CM range, so that it can work in the widest variety of applications. Current sensing, for example, requires the In-Amp to work with input CM voltages near the positive rail ( $V_{DD}$ ); a Wheatstone bridge will give a CM around  $V_{DD}/2$ , while a microphone will usually give a 0V common mode.

Talking about flexibility - and not only about input CM range -, it must be noticed that even for non general purpose devices it could be a great quality. While flexible project can be sold in bigger quantities, with a decrease in the unitary price, they match with the concept of design reusability: in the context of a microelectronic firm, given the lenght and the cost of a complex analog design, a flexible device can be a solution for more than one project, thus decreasing the average cost and time-to-market of new products that can reuse old designs.

**High input impedance** As mentioned in the previous paragraphs, some sensors could have a really high output impedance, that makes them far from ideal voltage generators. So, an extremely precise gain is meaningless if the amplifier causes a huge loading effect on the sensor's output voltage: in order to avoid this, both differential input impedance and common mode input impedance (called isolation impedances) must be as high as possible.

**High PSRR** The Power Supply Rejection Ratio is a way to measure how much a variation on the supply voltage affects the output. It is defined as the ratio between a variation on the supply voltage  $\Delta V_{DD}$  and the input voltade that would cause the same effect on the output, that is  $\Delta V_{d-out}/A_{dd}$ :

$$PSRR = \frac{\Delta V_{DD}}{\Delta V_{d-out}} A_{dd} \tag{1.24}$$

Obviously, this parameter must be as high as possible, in order to keep the output signal independent from supply disturbances or drifts: it is usual to express it in dB given the high values that it can reach. The importance of this parameter is more evident in Mixed Signal circuits, where the presence of a clock signal causes spikes on the supply voltage. This is because, at every clock cycle, the digital part of the chip may require a huge amount of current from the supply rail, to charge all the gates. In these moments, the supply voltage can have a negative spike, due to the finite output resistance of the supply voltage generator, resulting in a disturbance that can be as high as hundreds of mV, in worst cases.

Low noise, offset and offset drift, bias currents The importance of having a low RTI noise has already been mentioned in this paragraph: it is crucial to mantain a good Dynamic Range on the signal. Togheter with noise, also offset and bias current can affect the measurement. See figure 1.11: an ideal In-Amp has been separeted from its non ideality generators.

$V_{IO}$  is the offset voltage, that is the voltage that must be imposed to the input in order to have a zero output.  $I_{B1}$  and  $I_{B2}$  are the bias currents for each input. The difference  $I_{IO} = I_{B1} - I_{B2}$  is called offset current.

In this configuration, the actual input voltage is:

$$V_{in} = (V_{S1} - V_{S2}) - V_n - R_S I_{IO}$$

(1.25)

if we suppose a balanced source (that is  $R_{S1} = R_{S2} = R_S$ ).

Figure 1.11: Real inamp interfacing a real voltage generator.

Bias currents are significant in JFET or BJT input amplifiers, while in MOSFET input devices they are often negligible (they are mainly leakage currents through the gate oxide); if input terminals are connected to the bonding pads, then there will be relevant bias currents caused by the protection diodes, but we they will be ignored for this purpose.

Noise voltage, as said, has a component given by thermal noise, a gaussian white noise, that is usually kept low by increasing the static current consumption. There is another component, however, that is the so called Flicker noise, that has a peculiar Power Spectral Density proportional to 1/f (so it is dominant at low frequencies). This noise, caused by imperfections at the gate oxide-substrate border, is extremely high in MOSFET devices and can be reduced only making active areas large. This is one of the main reasons because analog circuits often occupy great amounts of area on Silicon dies. Then, offset voltage, again, is mainly caused by mismatch between internal components of the circuit. At first thought, since offset affects the measurement with a systematic offset, a calibration would be sufficient: however, offset strongly depends on temperature. So, even if the amplifier is calibrated, its drift caused by temperature will often counter the effect of calibration.

There are several architectural solution to reduce offset (and drift as well) and Flicker noise, without which such amplifiers would either be unusable for most applications or have impractical prices. The most diffused are Correlated Double Sampling (CDS, that works only for discrete time applications), Auto-Zero (AZ) and chopper modulation. The latter, briefly, ideally modulates (*chops*) the input signal with a square wave before the amplifier, that works on a high frequency signal to which offset and noise are summed. Then, the demodulator brings the signal back to baseband, while offset and low frequency noise are shifted to high frequencies, far from the signal bandwidth, where they can be filtered away. Chopper modulation will be discussed in detail in the following sections.

Low power consumption and NEF If on one hand a low noise design is needed for precision applications, on the other hand these systems are often destinated to mobile application, supplied by small batteries: this means that a particular attention must be paid to current consumption. As discussed in the following chapters, the quiescient current of an amplifier is directly linked to its thermal noise: in particular, if we can neglect flicker noise (rejected by dynamic techniques like chopper modulation), quiescent current is inversely proportional to the total noise of the amplifier.

The different topologies can have different noise efficiency, that is the ability certain values of noise with low currents. A figure of merit of an amplifier, then, can be defined as Noise Efficiency Factor (NEF), introduced in 1987 by Steyaert and Sansen [1]. Basically, this parameter is the ratio between the total input RMS (Root Main Square) noise of the amplifier and the equivalent input noise of a bipolar transistor with same bandwidth B and with a collector current equal to the quiescent supply current  $I_{DD}$  of the amplifier. Here is the original definition and expression, as proposed in

[1]:

$$NEF = \frac{v_{n,amp}}{v_{n,bjt}} = \frac{v_{n,amp}}{\sqrt{B\frac{\pi}{2}\frac{4kTV_T}{I_{DD}}}}$$

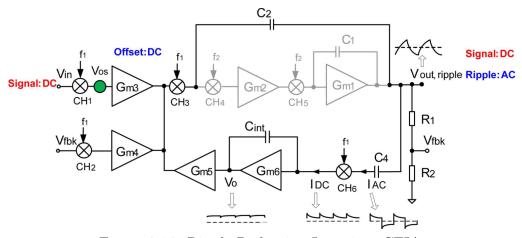

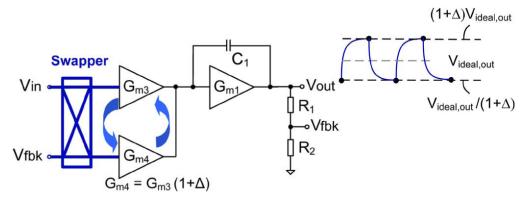

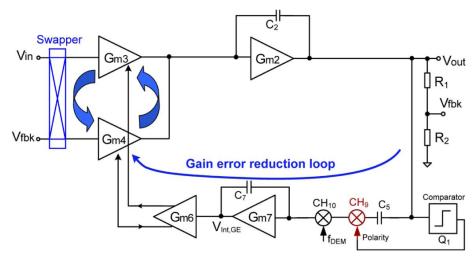

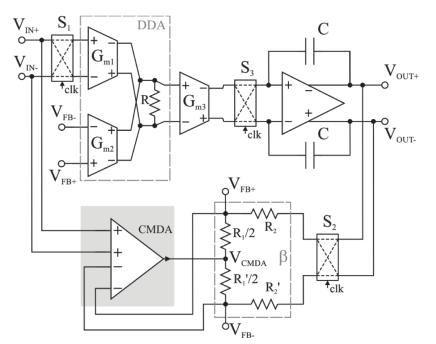

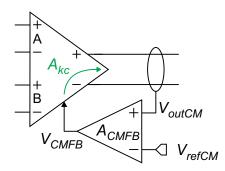

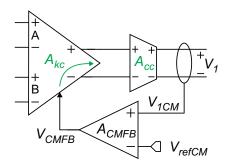

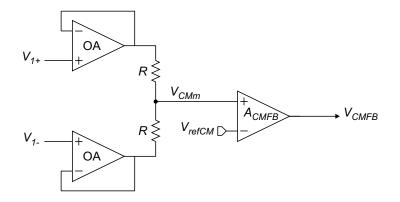

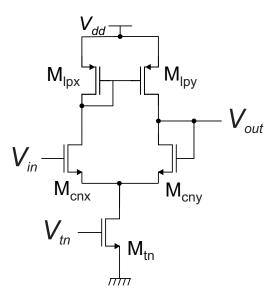

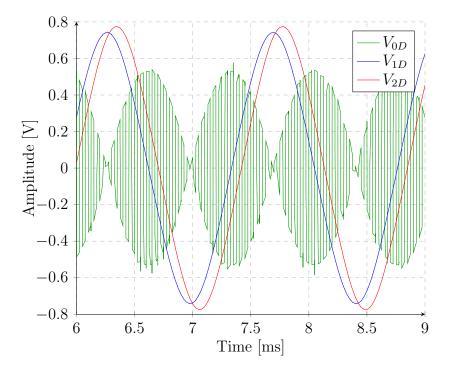

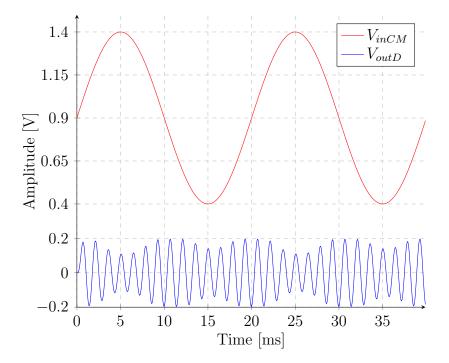

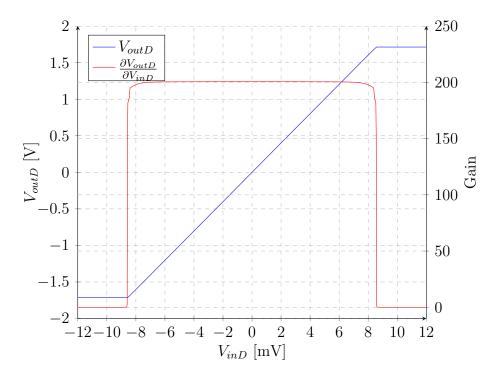

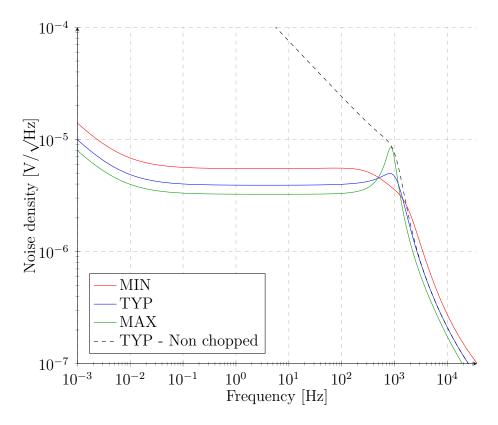

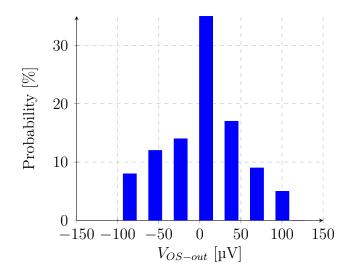

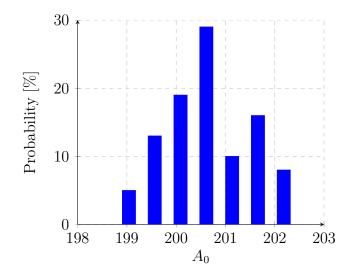

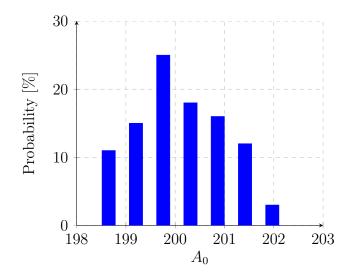

(1.26)