UNIVERSITY OF PISA

Department of Computer Science

Ph.D. Thesis

## FSCL

Homogeneous programming, scheduling and execution on heterogeneous platforms

CANDIDATE

Gabriele Cocco

SUPERVISOR

Dott. Antonio Cisternino

December 2014

### Acknowledgements

I wish to thank my parents, who have always believed in me, accepting and understanding every single choice I made along the road of life.

I thank my supervisor Antonio Cisternino, for his suggestions, his efforts and his valuable support throughout the years of my Ph.D. research.

Finally, I thank Davide Morelli and Andrea Canciani, who collaborated with me to build and validate the scheduling strategy, a critical part of the whole research.

## Contents

| Ι                                                                                           | Foundation of the Ph.D. Thesis                                                                                                                                                                                                                                                                                             | 13                                                             |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1                                                                                           | Introduction                                                                                                                                                                                                                                                                                                               | 15                                                             |

| <b>2</b>                                                                                    | Programming, scheduling and execution on heterogen                                                                                                                                                                                                                                                                         | eous plat-                                                     |

|                                                                                             | forms                                                                                                                                                                                                                                                                                                                      | 19                                                             |

|                                                                                             | 2.1 OpenCL                                                                                                                                                                                                                                                                                                                 | 19                                                             |

|                                                                                             | 2.1.1 OpenCL execution and memory model                                                                                                                                                                                                                                                                                    |                                                                |

|                                                                                             | 2.1.2 A summary on OpenCL programming                                                                                                                                                                                                                                                                                      |                                                                |

|                                                                                             | 2.2 High-level programming languages and libraries                                                                                                                                                                                                                                                                         |                                                                |

|                                                                                             | 2.3 Scheduling frameworks for heterogeneous platforms                                                                                                                                                                                                                                                                      | 34                                                             |

| 3                                                                                           | Conclusions                                                                                                                                                                                                                                                                                                                | 39                                                             |

|                                                                                             | 3.1 Thesis proposal                                                                                                                                                                                                                                                                                                        | 41                                                             |

| II                                                                                          |                                                                                                                                                                                                                                                                                                                            |                                                                |

| _                                                                                           | ning and execution                                                                                                                                                                                                                                                                                                         | rogram-<br>43<br>45                                            |

| m<br>4                                                                                      | ning and execution<br>Overview of the research                                                                                                                                                                                                                                                                             | 43<br>45                                                       |

| m                                                                                           | ning and execution<br>Overview of the research<br>F#: a flexible multi-paradigm language                                                                                                                                                                                                                                   | 43<br>45<br>49                                                 |

| m<br>4                                                                                      | ning and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1       Language constructs                                                                                                                                                                                   | 43<br>45<br>49<br>51                                           |

| m<br>4                                                                                      | ning and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1       Language constructs         5.1.1       Variables and functions                                                                                                                                       | 43<br>45<br>49<br>51<br>51                                     |

| m<br>4                                                                                      | <ul> <li>ning and execution</li> <li>Overview of the research</li> <li>F#: a flexible multi-paradigm language</li> <li>5.1 Language constructs</li></ul>                                                                                                                                                                   | 43<br>45<br>49<br>51<br>51<br>51                               |

| m<br>4                                                                                      | ning and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1       Language constructs         5.1.1       Variables and functions                                                                                                                                       | 43<br>45<br>49<br>51<br>51<br>56<br>58                         |

| 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ming and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1 Language constructs         5.1.1 Variables and functions         5.1.2 Data-types         5.1.3 Quotations         5.2 Conclusions                                                                         | 43<br>45<br>49<br>51<br>51<br>56<br>58<br>59                   |

| m<br>4                                                                                      | ning and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1 Language constructs         5.1.1 Variables and functions         5.1.2 Data-types         5.1.3 Quotations         5.2 Conclusions         FSCL kernel language                                            | 43<br>45<br>49<br>51<br>51<br>56<br>58<br>59<br>61             |

| 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ning and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1 Language constructs         5.1.1 Variables and functions         5.1.2 Data-types         5.1.3 Quotations         5.2 Conclusions         FSCL kernel language         6.1 Introduction and main approach | 43<br>45<br>49<br>51<br>51<br>56<br>58<br>59<br>61<br>61       |

| 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ning and execution         Overview of the research         F#: a flexible multi-paradigm language         5.1 Language constructs         5.1.1 Variables and functions         5.1.2 Data-types         5.1.3 Quotations         5.2 Conclusions         FSCL kernel language         6.1 Introduction and main approach | 43<br>45<br>49<br>51<br>51<br>56<br>58<br>59<br>61<br>61<br>63 |

|    |                                                                                                                    | 6.2.3                                                                                                                               | Abstraction and flexibility in FSCL composition 73                                                                                                                                                                                                                                                                                                                                 |

|----|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                    | 6.2.4                                                                                                                               | Notes on the execution model and on data constraints $\ 75$                                                                                                                                                                                                                                                                                                                        |

|    |                                                                                                                    | 6.2.5                                                                                                                               | Dynamic metadata                                                                                                                                                                                                                                                                                                                                                                   |

|    | 6.3                                                                                                                | Conclu                                                                                                                              | sions                                                                                                                                                                                                                                                                                                                                                                              |

| 7  | FSC                                                                                                                | CL Con                                                                                                                              | piler 83                                                                                                                                                                                                                                                                                                                                                                           |

|    | 7.1                                                                                                                | FSCL                                                                                                                                | Compiler structure                                                                                                                                                                                                                                                                                                                                                                 |

|    | 7.2                                                                                                                | Abstra                                                                                                                              | ct compilation process and components                                                                                                                                                                                                                                                                                                                                              |

|    |                                                                                                                    | 7.2.1                                                                                                                               | Steps and processors                                                                                                                                                                                                                                                                                                                                                               |

|    |                                                                                                                    | 7.2.2                                                                                                                               | Type-handlers                                                                                                                                                                                                                                                                                                                                                                      |

|    | 7.3                                                                                                                | Coordi                                                                                                                              | nation of steps, processors and type-handlers                                                                                                                                                                                                                                                                                                                                      |

|    | 7.4                                                                                                                | Native                                                                                                                              | compilation process and components                                                                                                                                                                                                                                                                                                                                                 |

|    |                                                                                                                    | 7.4.1                                                                                                                               | Expressions parsing, Kernel Flow Graph and Computing                                                                                                                                                                                                                                                                                                                               |

|    |                                                                                                                    |                                                                                                                                     | Expression Module                                                                                                                                                                                                                                                                                                                                                                  |

|    |                                                                                                                    | 7.4.2                                                                                                                               | Kernel compilation, kernel equivalence and Kernel Module 92                                                                                                                                                                                                                                                                                                                        |

|    |                                                                                                                    | 7.4.3                                                                                                                               | Native compiler components                                                                                                                                                                                                                                                                                                                                                         |

|    | 7.5                                                                                                                | -                                                                                                                                   | ler configuration and extensibility                                                                                                                                                                                                                                                                                                                                                |

|    | 7.6                                                                                                                | Conclu                                                                                                                              | sions $\ldots \ldots 105$                                                                                                                                                                                                                                                 |

|    |                                                                                                                    |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                    |

| 8  | FSC                                                                                                                | CL Run                                                                                                                              | time 107                                                                                                                                                                                                                                                                                                                                                                           |

| 8  | <b>FSC</b><br>8.1                                                                                                  |                                                                                                                                     | time         107           Runtime structure                                                                                                                                                                                                                                                                                                                                       |

| 8  |                                                                                                                    | FSCL I                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                    |

| 8  | 8.1                                                                                                                | FSCL I                                                                                                                              | Runtime structure                                                                                                                                                                                                                                                                                                                                                                  |

| 8  | 8.1                                                                                                                | FSCL Compu                                                                                                                          | Runtime structure                                                                                                                                                                                                                                                                                                                                                                  |

| 8  | 8.1                                                                                                                | FSCL 2<br>Compu<br>8.2.1<br>8.2.2                                                                                                   | Runtime structure                                                                                                                                                                                                                                                                                                                                                                  |

| 8  | 8.1<br>8.2                                                                                                         | FSCL Compu<br>8.2.1<br>8.2.2<br>Schedu                                                                                              | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115                                                                                                                                                                                                                                               |

| 8  | <ul><li>8.1</li><li>8.2</li><li>8.3</li></ul>                                                                      | FSCL Compu-<br>8.2.1<br>8.2.2<br>Schedu<br>Multith                                                                                  | Runtime structure107ating expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123                                                                                                                                                                                                    |

| 89 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li></ul>                                              | FSCL Compu<br>8.2.1<br>8.2.2<br>Schedu<br>Multith<br>Conclu                                                                         | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124                                                                                                                                                                                   |

|    | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li></ul>                                              | FSCL Compu<br>8.2.1<br>8.2.2<br>Schedu<br>Multitl<br>Conclu                                                                         | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124sions126                                                                                                                                                                           |

|    | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Run</li> </ul>                           | FSCL Compute<br>8.2.1<br>8.2.2<br>Schedu<br>Multith<br>Conclu                                                                       | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124sions126cheduling engine127                                                                                                                                                        |

|    | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Run</li> <li>9.1</li> </ul>              | FSCL Compute<br>8.2.1<br>8.2.2<br>Schedu<br>Multith<br>Conclu                                                                       | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123aread execution124sions126cheduling engine127l approach and strategy128                                                                                                                              |

|    | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Run</li> <li>9.1</li> </ul>              | FSCL<br>Compu<br>8.2.1<br>8.2.2<br>Schedu<br>Multitl<br>Conclu<br>ntime se<br>Genera<br>Code a                                      | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124sions126cheduling engine127l approach and strategy128nalysis and feature extraction130                                                                                             |

|    | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Run</li> <li>9.1</li> </ul>              | FSCL Compute<br>8.2.1<br>8.2.2<br>Schedu<br>Multith<br>Conclu<br>ntime se<br>Genera<br>Code a<br>9.2.1<br>9.2.2                     | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124sions126cheduling engine127l approach and strategy128nalysis and feature extraction130Feature finalizer building132                                                                |

|    | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Run</li> <li>9.1</li> <li>9.2</li> </ul> | FSCL Compute<br>8.2.1<br>8.2.2<br>Schedu<br>Multith<br>Conclu<br>ntime se<br>Genera<br>Code a<br>9.2.1<br>9.2.2                     | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124sions126cheduling engine127I approach and strategy128nalysis and feature extraction130Feature finalizer building132Cache miss estimation141                                        |

|    | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>Run</li> <li>9.1</li> <li>9.2</li> </ul> | FSCL Compute<br>8.2.1<br>8.2.2<br>Schedu<br>Multith<br>Conclu<br>ntime se<br>Genera<br>Code a<br>9.2.1<br>9.2.2<br>Predict<br>9.3.1 | Runtime structure107ting expression execution, caching and data management111Device and kernel resource caching114Data management115ling and execution control via metadata123nread execution124sions126cheduling engine127I approach and strategy128nalysis and feature extraction130Feature finalizer building132Cache miss estimation141tion model, profiling and regression153 |

### III Validation

| 10 Validation of the programming model                                                                     | 165 |

|------------------------------------------------------------------------------------------------------------|-----|

| 10.1 Black-Scholes                                                                                         | 165 |

| 10.2 K-Means                                                                                               | 168 |

| 10.3 Tiled matrix multiplication                                                                           | 171 |

| 10.4 Average image complexity                                                                              | 174 |

| 10.5 Conclusions $\ldots$ | 176 |

| 11 Validation of the prediction model for device-selection                                                 | 179 |

| 11.1 System setup, training samples and features                                                           | 180 |

| 11.1.1 Training set                                                                                        |     |

| 11.1.2 Features                                                                                            |     |

| 11.2 Fitting residuals, completion time prediction and best-device                                         |     |

| prediction accuracy                                                                                        | 183 |

| 11.2.1 Fitting residuals                                                                                   |     |

| 11.2.2 Completion time prediction                                                                          |     |

| 11.2.3 Impact of the feature set on the completion time predic-                                            |     |

| tion accuracy                                                                                              | 188 |

| 11.2.4 Best-device prediction                                                                              |     |

| 11.2.5 Interpretation of the regression coefficients                                                       | 190 |

| 11.2.6 Conclusions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$        |     |

| 12 Validation of compilation, scheduling and execution efficiency                                          | 195 |

| 12.1 Impact of optimisations on performances                                                               |     |

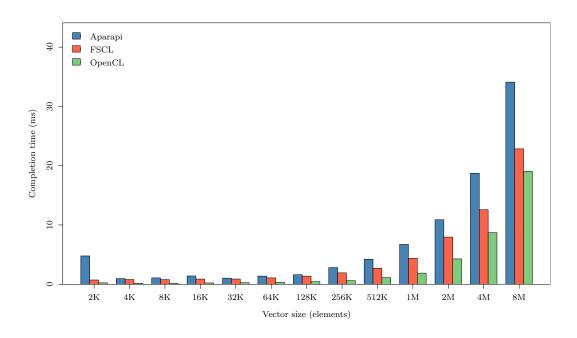

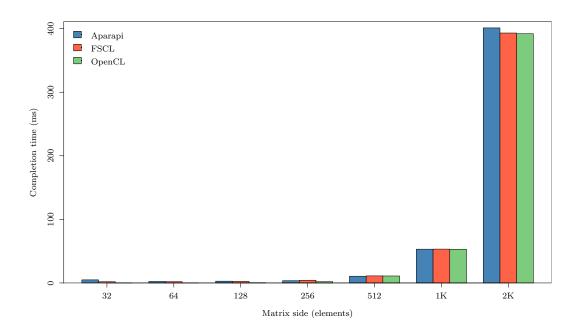

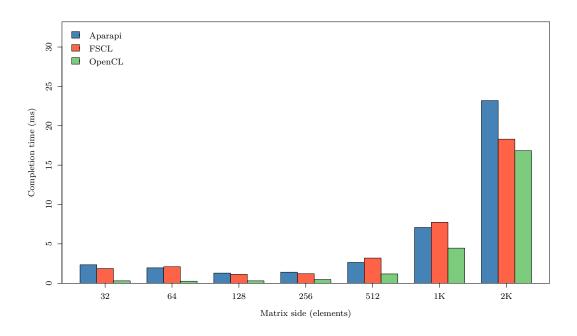

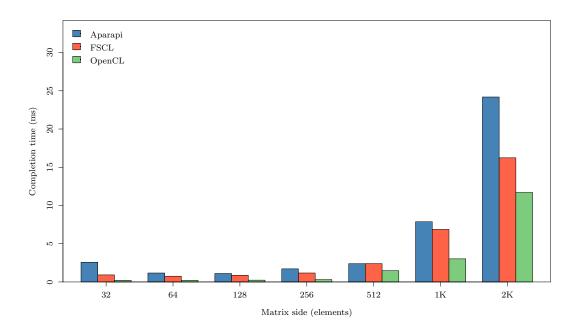

| 12.2 FSCL versus Aparapi and OpenCL                                                                        |     |

| 12.3 Impact of feature evaluation and device selection on average                                          |     |

| completion time                                                                                            | 200 |

| 12.3.1 Single versus hybrid execution for multi-kernel programs                                            |     |

| 12.4 Conclusions                                                                                           |     |

|                                                                                                            |     |

| IV Conclusions                                                                                             | 211 |

| 13 Research, challenges and results                                                                        | 213 |

| 14 Limitations, refinements and future works                                                               | 217 |

| 14.1 Research refinements                                                                                  |     |

| 14.2 Concurrent researches                                                                                 |     |

| Appendices                                                                                                 | 225 |

| F F C C C C C C C C C C C C C C C C C C                                                                    |     |

| Α | Defi                            | inition          | s of the elements of the kernel language                       | 227        |

|---|---------------------------------|------------------|----------------------------------------------------------------|------------|

| В | <b>Def</b><br>B.1<br>B.2<br>B.3 | Equiva<br>Equiva | s of equivalence of kernels and metadata<br>alence of metadata | . 230      |

| С | Sou                             | rce co           | de of samples used in language validation                      | <b>233</b> |

|   | C.1                             | Black-           | Scholes                                                        | . 233      |

|   |                                 | C.1.1            | FSCL                                                           | . 233      |

|   |                                 | C.1.2            | Aparapi                                                        | . 234      |

|   |                                 | C.1.3            | Dandelion                                                      | . 235      |

|   | C.2                             | K-Mea            | ans                                                            | . 236      |

|   |                                 | C.2.1            | FSCL                                                           | . 236      |

|   |                                 | C.2.2            | Aparapi                                                        | . 237      |

|   |                                 | C.2.3            | Dandelion                                                      | . 239      |

|   | C.3                             | Tiled :          | matrix multiplication                                          | . 240      |

|   |                                 | C.3.1            | FSCL                                                           | . 240      |

|   |                                 | C.3.2            | Aparapi                                                        | . 241      |

|   |                                 | C.3.3            | Dandelion                                                      | . 242      |

|   | C.4                             | Averag           | ge image complexity                                            | . 242      |

|   |                                 | C.4.1            | FSCL                                                           | . 242      |

|   |                                 | C.4.2            | Aparapi                                                        | . 243      |

|   |                                 | C.4.3            | Dandelion                                                      | . 245      |

## List of Figures

| 2.1  | Abstract view of host and devices in OpenCL                                               |

|------|-------------------------------------------------------------------------------------------|

| 2.2  | OpenCL index space showing work-items and their relative global,<br>local, work-group IDs |

| 2.3  | OpenCL conceptual organization of memory regions                                          |

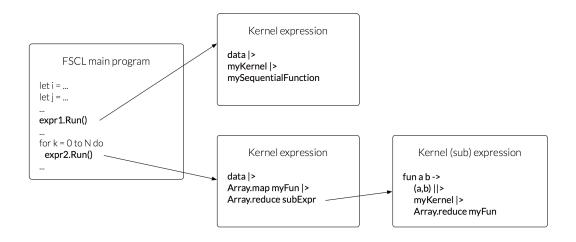

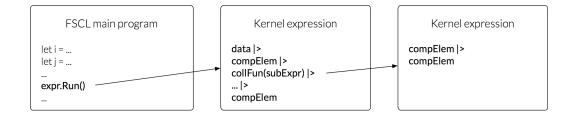

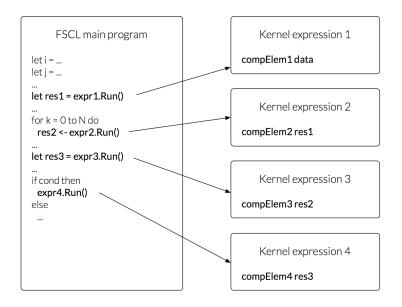

| 6.1  | Generic structure of an FSCL application                                                  |

| 6.2  | FSCL application employing pure functional composition 74                                 |

| 6.3  | FSCL application employing pure imperative composition 74                                 |

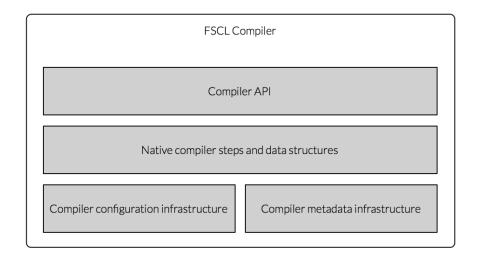

| 7.1  | Structure of the FSCL compiler                                                            |

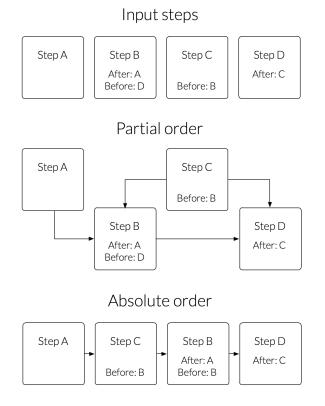

| 7.2  | Example of partial and absolute ordering of steps 86                                      |

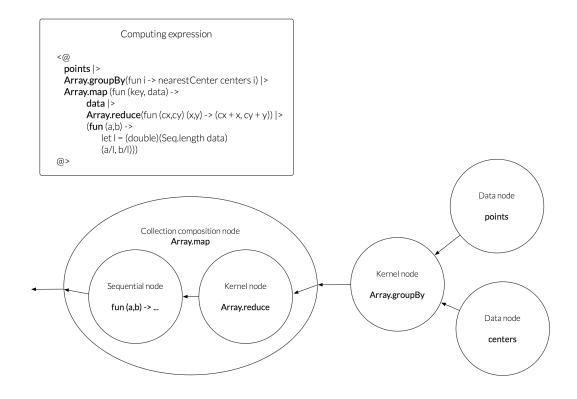

| 7.3  | Example of the KFG of a computing expression 91                                           |

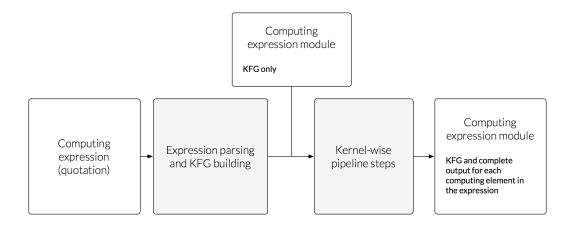

| 7.4  | Computing Expression Module instantiation and filling 92                                  |

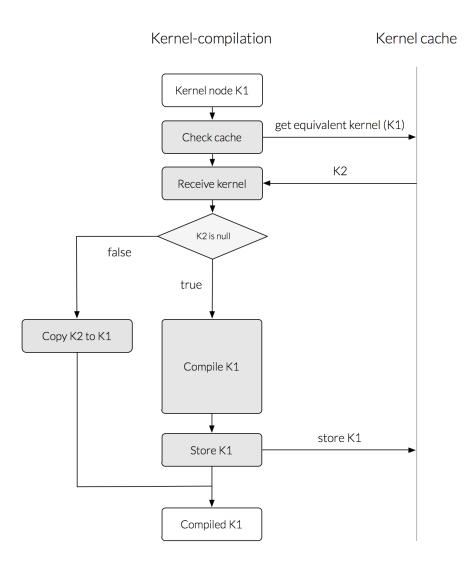

| 7.5  | Kernel compilation and caching                                                            |

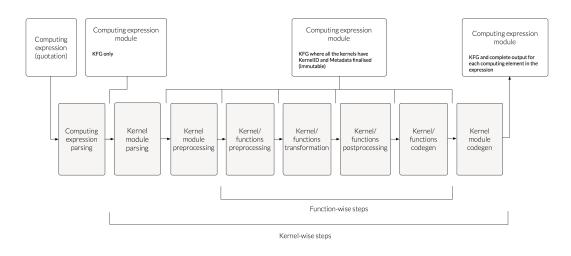

| 7.6  | Steps of the native compiler pipeline in the order or execution . 102                     |

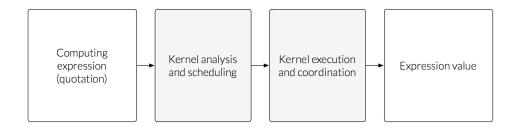

| 8.1  | Steps of the native runtime pipeline in the order or execution 108                        |

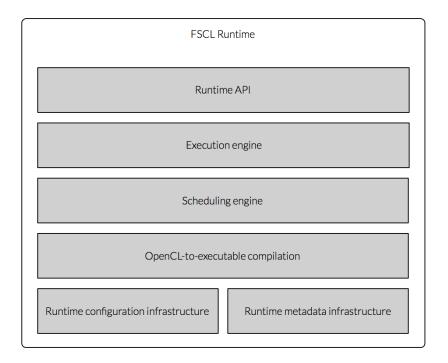

| 8.2  | Structure of the FSCL runtime                                                             |

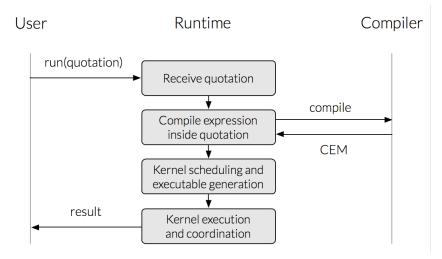

| 8.3  | Interactions between programmer, runtime and compiler 110                                 |

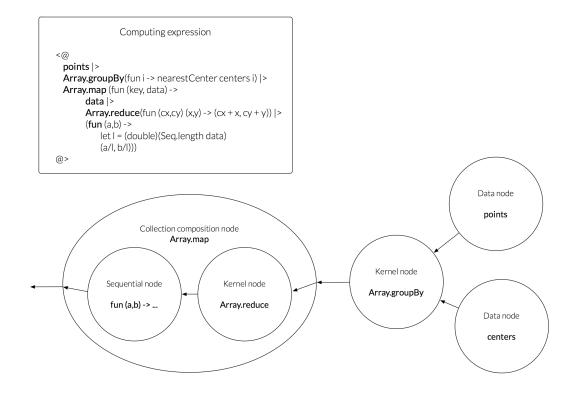

| 8.4  | Kernel Flow Graph for the K-Means computing expression $\ . \ . \ . \ 113$                |

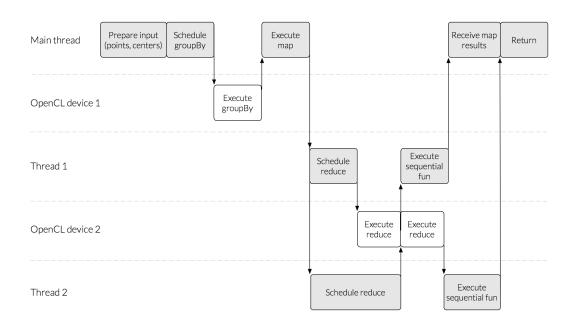

| 8.5  | Timeline and interactions with OpenCL devices in executing                                |

|      | K-Means                                                                                   |

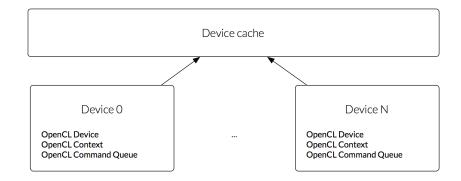

| 8.6  | Device information stored by the runtime                                                  |

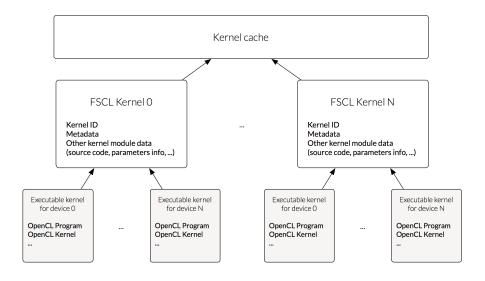

| 8.7  | Kernel information stored by the runtime                                                  |

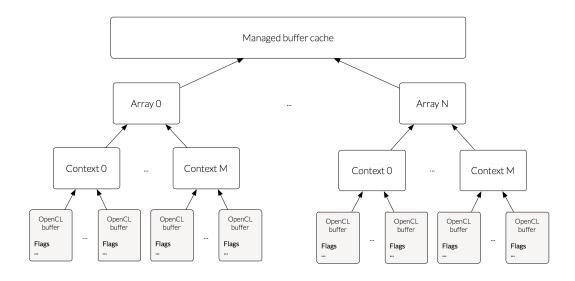

| 8.8  | Structure of the managed buffers cache                                                    |

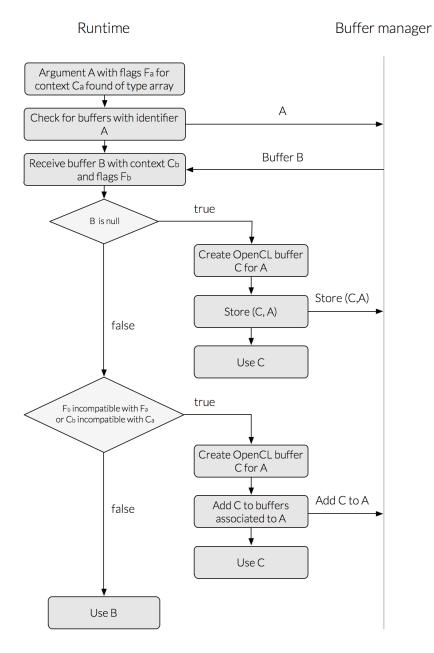

| 8.9  | Process of creation of a managed buffer                                                   |

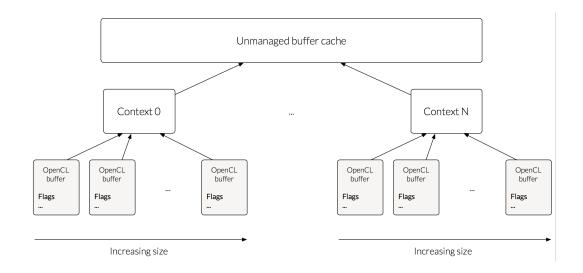

| 8.10 | Structure of the unmanaged buffers cache                                                  |

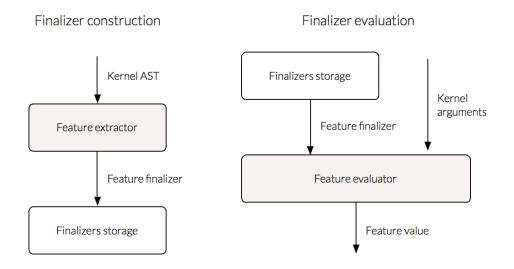

| 9.1  | Finalizer construction and evaluation                                                     |

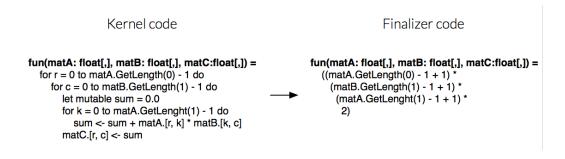

| 9.2  | Kernel to finalizer mapping for a feature that counts memory                              |

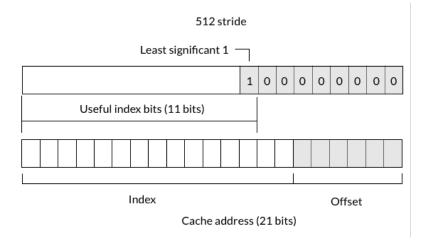

| 9.3   | Impact of memory access stride on the index part of a cache                   |

|-------|-------------------------------------------------------------------------------|

|       | address                                                                       |

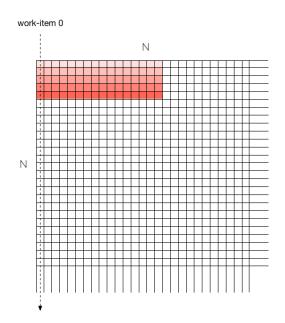

| 9.4   | Data loaded into cache when scanning the first column of a matrix 152         |

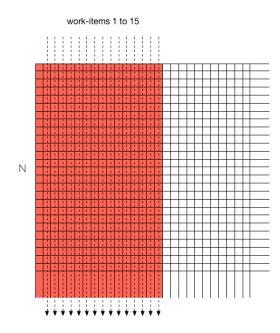

| 9.5   | Cache lines reused when scanning the columns 1-15 of a matrix 153             |

| 9.6   | Cache eviction when scanning the first column of a matrix $\ . \ . \ . \ 154$ |

| 11 1  | Fitting residuals                                                             |

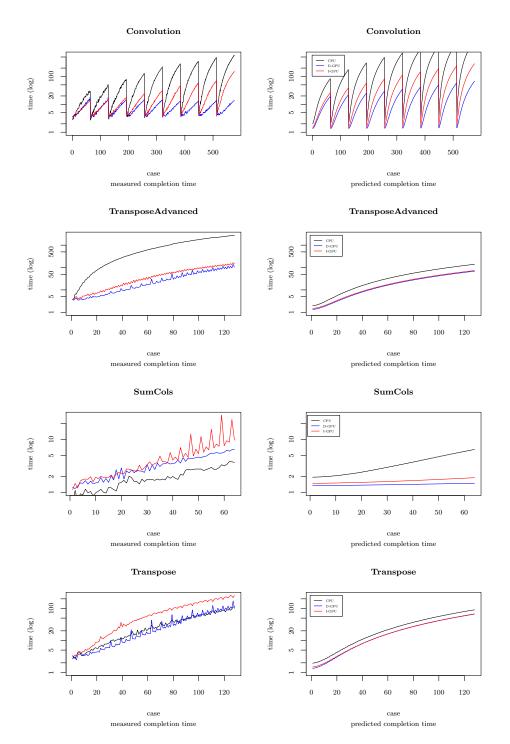

|       | Measured and predicted completion time                                        |

|       | Measured and predicted completion time                                        |

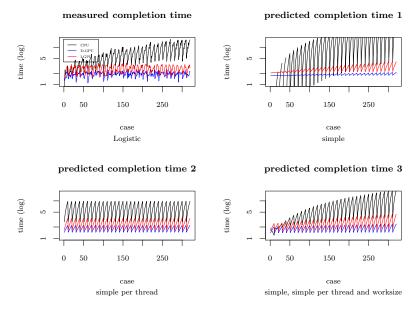

|       | Impact of features on prediction error for Logistic map 189                   |

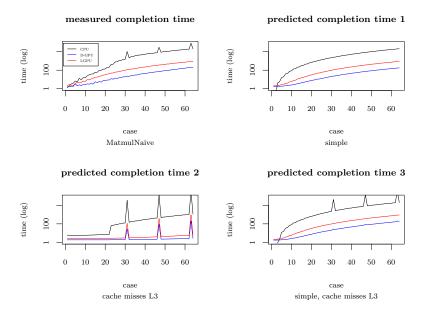

|       | Impact of features on prediction error for Matrix multiplication 189          |

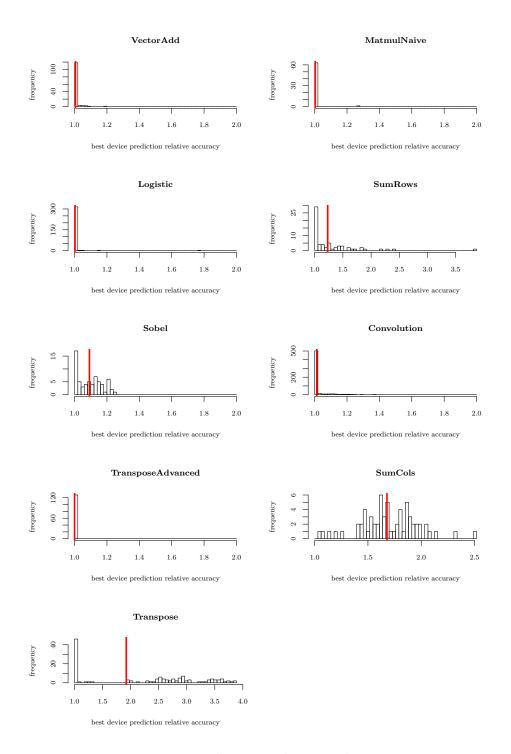

|       | Best device prediction relative accuracy                                      |

| 11.0  | Dest device prediction relative accuracy                                      |

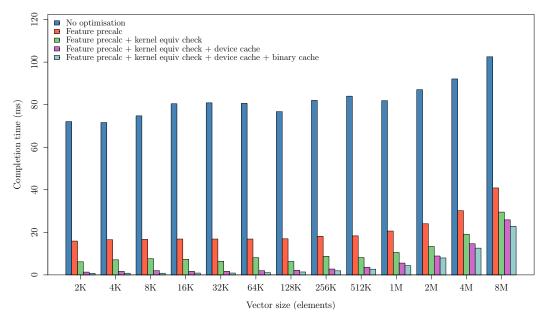

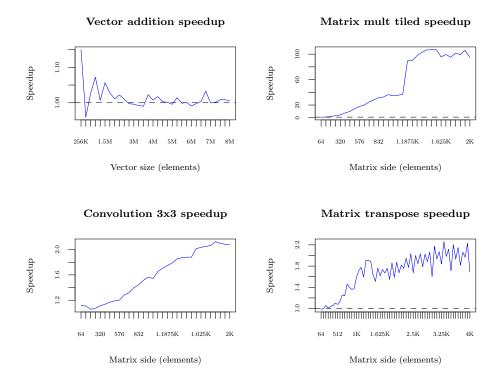

| 12.1  | Impact of successive optimisations on Vector addition 198                     |

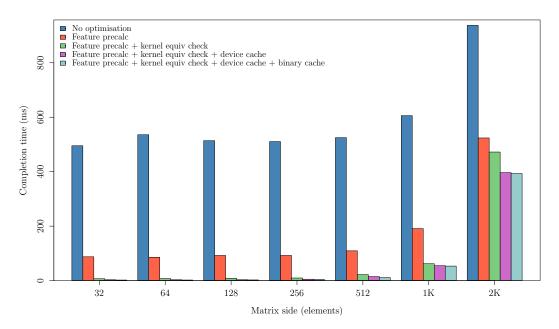

| 12.2  | Impact of successive optimisations on Matrix multiplication tiled 198         |

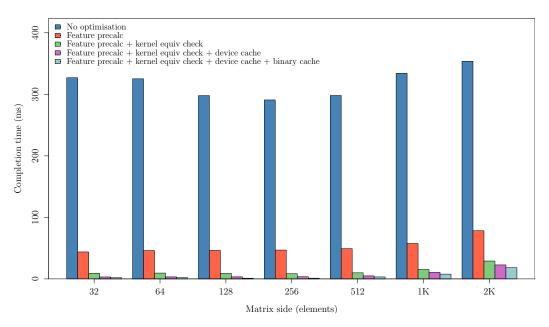

| 12.3  | Impact of successive optimisations on Convolution                             |

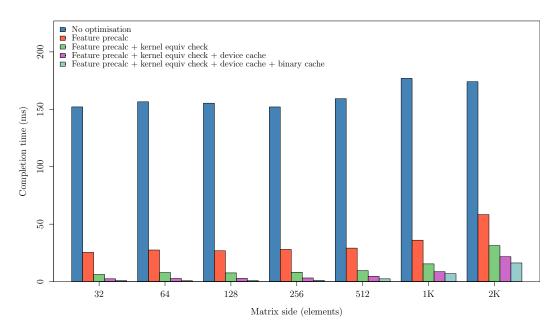

| 12.4  | Impact of successive optimisations on Matrix transpose 199                    |

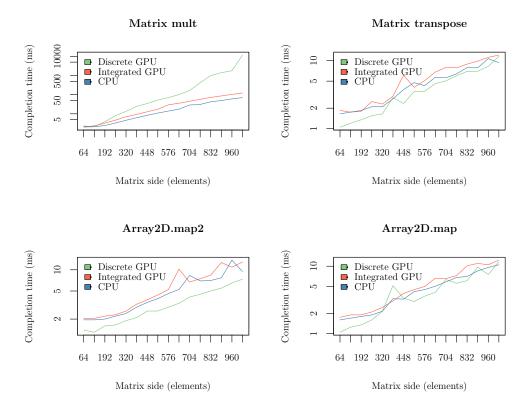

| 12.5  | Aparapi vs FSCL vs OpenCL for Vector addition                                 |

| 12.6  | Aparapi vs FSCL vs OpenCL for Matrix multiplication tiled 201                 |

| 12.7  | Aparapi vs FSCL vs OpenCL for Convolution                                     |

| 12.8  | Aparapi vs FSCL vs OpenCL for Matrix transpose                                |

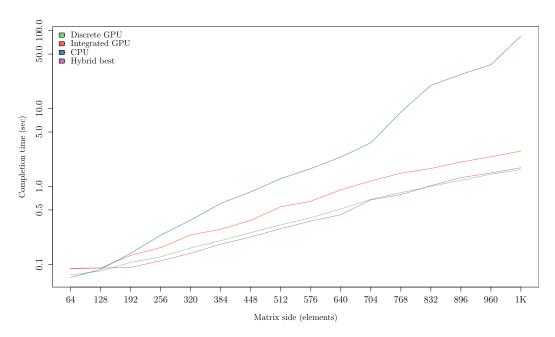

|       | Speedup of best-device over random device selection                           |

| 12.10 | Completion times for each kernel in the Newton's method 207                   |

| 12.11 | Completion times of single device execution and hybrid execu-                 |

|       | tion, logarithmic scale                                                       |

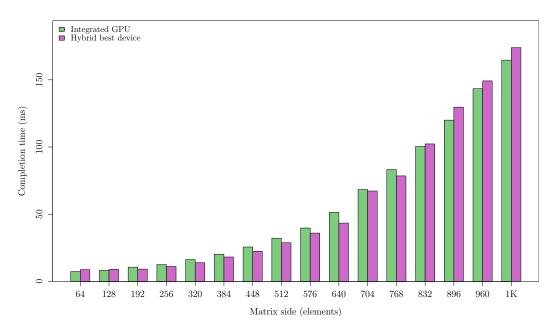

| 12.12 | 2Completion times of discrete-GPU-only versus hybrid execution 209            |

### Abstract

The last few years has seen activity towards programming models, languages and frameworks to address the increasingly wide range and broad availability of heterogeneous computing resources through raised programming abstraction and portability across different platforms.

The effort spent in simplifying parallel programming across heterogeneous platforms is often outweighed by the need for low-level control over computation setup and execution and by performance opportunities that are missed due to the overhead introduced by the additional abstraction. Moreover, despite the ability to port parallel code across devices, each device is generally characterised by a restricted set of computations that it can execute outperforming the other devices in the system. The problem is therefore to schedule computations on increasingly popular multi-device heterogeneous platforms, helping to choose the best device among the available ones each time a computation has to execute.

Our Ph.D. research investigates the possibilities to address the problem of programming and execution abstraction on heterogeneous platforms while helping to dynamically and transparently exploit the computing power of such platforms in a device-aware fashion. The Thesis in structured in four parts. In the first part we present today's situation in heterogeneous systems, we identify the major issues induced by spreading heterogeneity and we discuss the implications. We analyse the most recent and relevant works in high-level programming, scheduling and execution on heterogeneous platforms, which represent the starting point of our Ph.D. research. The part is concluded with the formalization of the Thesis proposal.

In the second part we present the research conducted. We define the context of our work and we discuss the approaches adopted to reach the goals that our proposal entails. The presentation is organized following the timeline and the structure of our research and the inter-dependencies between the goals.

In the third part we validate the results obtained against the state of the art in heterogeneous programming and execution. We evaluate the benefits of our work and we identify the principal limitations.

In the fourth part we summarise the work conducted and the relevant outcomes. We briefly propose again the statement of the Thesis and we match it against the results obtained. Finally, we present the implications of our work, the possible refinements and the potential future research.

# Part I Foundation of the Ph.D. Thesis

# Chapter 1 Introduction

In the last few years computing has become increasingly heterogeneous, offering a broad portfolio of different parallel devices, ranging from CPUs, through GPUs to APUs<sup>1</sup> and coprocessors. Most of the recent CPUs available on the market contain two parallel processing resources, which are a multicore CPU and a GPU. Given this on-die heterogeneity and the set of recent technologies for multi-GPU (e.g. SLI) nowadays desktop and laptop computers possibly expose one or more multicore CPUs and multiple GPUs. Intel recently released a coprocessor for cluster nodes and desktop systems, called "Xeon Phi", which is characterized by hybrid architecture and execution model.

Researches on manifacturing and optimizing hardware for heterogeneous platforms has been very active, as demonstrated by the effort spent by the majority of the silicon industries in this new kind of processing resources [3, 45,55].

Not only has the variety of devices increased, but it has spread towards systems traditionally characterised by single computing resources, such as netbooks and mobile phones, which nowadays are equipped with multicore CPUs and GPUs. Heterogeneity on mobile devices is a hot trend in the mobile market [47].

Given the spread of heterogeneous solutions across different systems, from mobile phones to desktop PCs, and the constantly dropping price of hardware components, heterogeneous configurations are increasingly popular and affordable for a broad range of users. This means that computing power is not only becoming highly heterogeneous but it is also becoming available to users that are unaware of the underlying parallel computing power and of how to exploit it. With the term "users", we refer to either developers with no parallel

<sup>&</sup>lt;sup>1</sup>APU is the term used by some processors brands to refer to a CPU and a GPU integrated onto the same die

programming skills or software that is not designed to dynamically leverage multiple heterogeneous devices.

The major problem that comes from the unawareness of platform heterogeneity is the underutilization of computing power. We consider underutilization of heterogeneous computing power a consequence of two principal aspects: the difficulty of programming across different, parallel devices and the complexity in understanding, exploiting and adapting to a highly dynamic set of resources.

To enhance portability, software tends to target the CPU, which is a computing resource available in the majority of systems. Similarly, generic programmers tend to be more productive in developing software that run sequentially on CPUs, because of the lack of parallel programming skills or because of the effort required to guarantee the software be able to fallback and adapt to different machine configurations. This is particularly true when the set of target platforms is extremely varied in terms of configurations, ranging from CPU-only systems up to machines equipped with multiple, different GPUs and coprocessors. When effort in exploiting multiple devices is spent, software tends to adopt a device-unaware usage policy, where the available resources are treated as an homogeneous set of computing nodes. Provided with an homogeneous programming layer, such a policy is easier to apply than one which takes into account the specific characteristics of each device in the set.

On mobile devices, the unawareness of the available resources and the lack of a strategy to get the most out of each of them can increase the power/battery consumption. In the last few years, research has demonstrated that CPUs and GPUs are described by two very different power consumption profiles. Whereas GPUs are described by an overall higher consumption, they tend to be more energy-saving in terms of performance per-watt [2, 12, 41].

In cloud computing, an inproper use of the available resources can lead to massive overspending. While load-balancing across the resources represents a good improvement [8,36], extending the traditional notion of cloud computing to provide a cloud-based access model that is heterogeneity-aware can play a key role to boost performance and energy efficience [17].

It is important to consider that the spread of heterogeneous platforms is not only widening the set of programmers that work on such platforms, but it also affects the type of computations possibly run on them. While research and industrial parallel computing centers are likely to accelerate specific, complex and long-lasting algorithms, programmers of today's heterogeneous platforms often develop and execute lightweight and more generic computations. Therefore, approaches that leverage the high completion times of the running computations to cover the scheduling overhead may turn out to be too expensive when applied to more generic and lightweight programs. Similarly, approaches based on task-subdivision of computations may be unfit to handle the generality of algorithms that run on today's heterogeneous platforms.

To address the issues related to spreading heterogeneity and the dynamicity of platform configurations, research should focus on two different but interrelated aspects.

The first aspect is the complexity of programming across different parallel devices, especially considered the broad audience of programmers working on heterogeneous systems. To widen the range of programmers able to exploit the set of parallel resources populating heterogeneous platforms, an homogeneous and abstract programming layer should be provided. Whereas abstraction and expressiveness can make it easier for generic programmers to develop across devices, flexibility must be also taken into account to guarantee the largest range of algorithms to fit the programming model.

The second aspect is the difficulty to detect and characterize the set of devices that populate heterogeneous platforms in order to use them in a deviceaware fashion. To get the most out of such platforms, the runtime support of an homogeneous programming layer must be able to transparently and dynamically analyse both the code to execute and the resources available in the running system. Coupling this information plays a key role in improving resource utilization and dynamic adaptation to different system configurations.

Given the wide variety of computations, possibly lightweight, that can be scheduled on today's heterogeneous systems, a pressing challenge of code analysis and scheduling is to be efficient, in order to guarantee that the overhead doesn't outweigh the time saved by running computations on the devices with the highest performance.

Finally, to enhance portability across systems and programmers, an abstract programming, scheduling and execution layer must be ready-to-go, which means to be able to transparently discover all the information needed about the running platform for self-configuration and deployment.

The two aformentioned challenges stress the need for research on raising abstraction over parallel programming and execution on heterogeneous platforms, hiding the complexity of the underlying system to the programmers while providing dynamic device- and computation-aware scheduling and execution to leverage the whole set of available computing resources.

Research towards high-level programming and execution on heterogeneous platforms should be particularly inspired by a technical report from the University of Berkeley [7], which states:

The struggle is delivering performance while raising the level of

abstraction. Going too low may achieve performance, but at the cost of exacerbating the software productivity problem, which is already a major hurdle for the information technology industry. Going too high can reduce productivity as well, for the programmer is then forced to waste time trying to overcome the abstraction to achieve performance.

Depite the years passed since this report was published, balancing abstraction and performance in parallel programming and execution is still an open problem. Actually, this challenge is renovated and underlined by the today's widespread heterogeneity of parallel computing power. Whereas performance is still a pressing challenge, the need of higher programming and execution abstraction is stressed by the increasing variety of available hardware resources and by the generality of the programs running on them.

### Chapter 2

## Programming, scheduling and execution on heterogeneous platforms

Recently effort has been spent to address the increasing heterogeneity of the computing platforms. In this chapter we present the state of the art of this research from both the perspective of programming abstraction and the one of scheduling and execution support.

The chapter is organized in four sections. In the first section we present and discuss OpenCL, which is the today's standard-de-facto for parallel programming across different resources. In the second section we show and discuss the most recent and relevant efforts to increase the abstraction over parallel programming on heterogeneous systems. In the third section we present the relevant works that try to address the problem of efficient scheduling and execution on multi-device platforms. Finally, in the fourth section we summarize the state of the art, we discuss the major flaws and the open challenges, and we formulate our Ph.D. Thesis proposal.

#### 2.1 OpenCL

Originally developed as a private API by Apple and published in 2009, OpenCL is an open specification for writing and executing programs for heterogenous platforms.

In the last couple of years, thanks to the huge contribution from the programming community and to the many companies that decided to support it on their own devices, OpenCL has become one of most popular solutions for heterogeneous programming.

#### 2.1.1 OpenCL execution and memory model

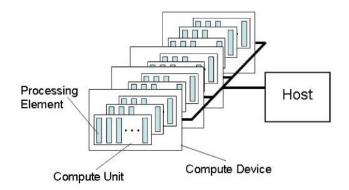

From the OpenCL point of view a system is made of one or more *devices* grouped into *platforms*. Each platform generally corresponds to a specific manifacturer (e.g. AMD, Intel) with its own OpenCL-to-executable compiler and runtime support (called *client driver*). Whereas multiple devices can populate a system, the OpenCL specification stands that there is one only *host*, running on the CPU, whose task is to coordinate the execution of computations on the devices (figure 2.1).

The OpenCL specification describes a device abstracted from the particular hardware configuration. An OpenCL device is made of one or more *compute units* (CUs) which are further divided into one or more *processing elements* (PEs). On a GPU, compute units map to independent cores that execute in parallel multiple instructions on multiple data, while processing elements map to the arithmetic and logic units in each core. On a CPU, both compute units and processing elements generally correspond to CPU cores.

An OpenCL application runs on the host according to the native model of the host platform. The OpenCL application submits commands to run computations on the processing elements of a device. The processing elements within a compute unit execute a single stream of instructions as SIMD units (Single Instruction Multiple Data) or as SPMD (Single Program Multiple Data) units.

Figure 2.1: Abstract view of host and devices in OpenCL

The distinction between host and devices is not only conceptual but affects the typical code structure of OpenCL programs. A program is in fact made of two distinct parts: the *kernel code* and the *host code*. The kernel code implements the parallel computation (kernel) to run on the device, while the host code handles resource allocation, computation setup, scheduling and synchronisation with the execution of the kernel on the device.

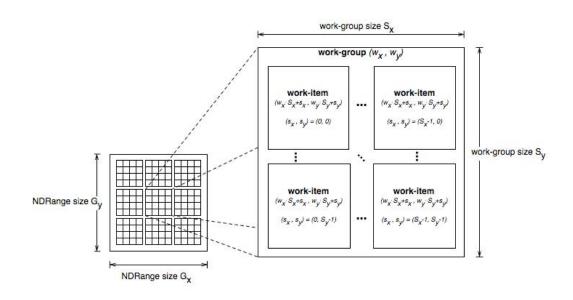

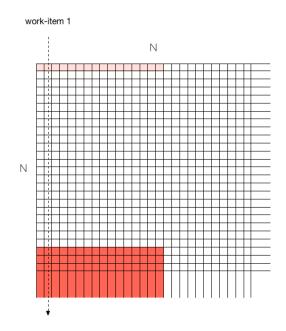

OpenCL defines an index space for parallel kernel execution. An instance of the kernel executes for each point in this index space. This kernel instance is called *work-item* and is identified by its point in the index space, which provides a *global ID* for the work-item. Each work-item executes the same code but the specific execution path through the code and the data used can vary per work-item.

Work-items are organized into work-groups. The work-groups represent a coarse-grained decomposition of the index space. Work-groups are assigned a unique *work-group ID* with the same dimensionality as the index space used for the work-items. Work-items are assigned a unique *local ID* within a work-group so that a single work-item can be uniquely identified by its global ID or by a combination of its local ID and work-group ID. The set of work-items in a given work-group execute concurrently on the processing elements of a single compute unit (figure 2.2).

Figure 2.2: OpenCL index space showing work-items and their relative global, local, work-group IDs

#### **OpenCL** context resources

The host defines a context for the execution of the kernels, which includes the following resources:

- **Devices** A collection of OpenCL devices to be used by the host for the execution of kernels;

- Kernels The set of parallel computations to run

- **Program Objects** The program source and executable that implement the kernels;

- Memory Objects A set of memory objects visible to the host and to the devices.

Program objects contain compiled kernels and other information essential for the execution on the device. To create a program object, the host uses specific OpenCL functions, submitting the sources of the kernels forming the program and obtaining an opaque pointer to the executable code. OpenCL kernels are therefore compiled into executables at (host) runtime.

Memory objects contain data that can be accessed and possibly modified by the instances of a kernel. These objects can be of two types: *buffer objects*, and *image objects*. A buffer object stores a one-dimensional collection of elements whereas an image object is used to store a two or three-dimensional texture, frame-buffer or image.

Elements of a buffer object can be scalar data (e.g. int, float), vector data (e.g. float4, int8), or user-defined structures. An image object instead represents a buffer that can be used as a texture or a frame-buffer, whose elements are selected from a list of predefined image formats.

The context and all its resources are created and manipulated by the host using the OpenCL API.

The host also creates a data structure called a *command-queue* to coordinate the execution of kernels on the devices. The host submits commands into the command-queue which are then scheduled onto the devices within the context. These commands include:

**Kernel execution commands** Execute a kernel on the processing elements of a device;

Memory commands Transfer data to, from, or between memory objects, or map/unmap memory objects to/from the host address space;

Synchronization commands Constrain the order of execution of commands.

Commands scheduled on the queue execute asynchronously between the host and the device and can run relative to each other in an *in-order* or *outof-order* mode. Programmers can choose a specific relative ordering when creating the command-queue. Kernel execution and memory commands submitted to a queue generate event objects, which are used to control the execution between commands and to synchronize the host with the device.

#### **OpenCL** memory model

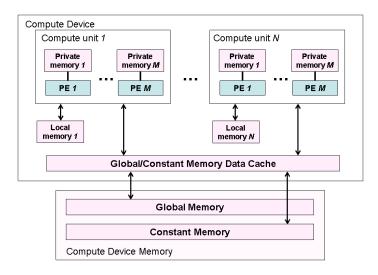

Work-items executing a kernel have access to four distinct memory regions, as illustrated in figure 2.3.

- **Global memory** This memory region allows access from all work-items in all work-groups. Work-items can read from or write to any element of memory objects placed in global memory;

- **Constant Memory** A region of global memory that remains constant during the execution of a kernel. The host allocates and initializes memory objects placed into constant memory. Work-items have read-only access rights to the elements of these objects;

- Local Memory A memory region local to a work-group. This memory region can be used to share data among the work-items in a work-group;

- **Private Memory** A region of memory private to a work-item. Data placed in one work-item private memory is not visible to the other work-items.

The application running on the host uses the OpenCL API to create memory objects in global/constant memory and to enqueue memory commands that operate on these objects.

Since the host is defined outside of OpenCL, the memory hierarchies of the host and the device are generally separated and independent from each other. Interactions between host and device memory occur by either explicitly copying data or by mapping/unmapping regions of a memory object. To copy data explicitly, the host enqueues commands to transfer data between the memory object and host memory. The mapping/unmapping functions instead allow the host to map a region from the memory object into its address space. Once a region from the memory object has been mapped, the host can read or write to this region. The changes to the content of the mapped region possibly performed by the host are visible to the device after the region is unmapped.

When a memory object is created, some *memory-flags* can be specified to determine the placement in the memory and the access to the object. For example, *AllocHostPtr* flag specifies that the application wants the OpenCL implementation to allocate memory from host accessible memory, while *Use-HostPtr* flag indicates that the application wants to use memory referenced by a user-provided pointer as the storage bits for the memory object.

Figure 2.3: OpenCL conceptual organization of memory regions

#### Synchronization between commands and processing elements

There are two domains of synchronization in OpenCL:

- Work-items in a single work-group

- Commands enqueued to command-queues in a single context

Synchronization between work-items in a single work-group is achieved using a work-group *barrier* in the kernel code. All the work-items in a workgroup must execute the barrier before any are allowed to continue. OpenCL doesn't provide any mechanism of synchronisation between work-groups.

The synchronization points between commands in command-queues are:

- **Command-queue barrier** A command-queue barrier ensures that all previously queued commands have finished execution and any resulting updates to memory objects are visible to subsequently enqueued commands before they begin execution. This barrier can only be used to synchronize commands in a single command-queue;

- Waiting on an event All the OpenCL API functions that enqueue commands return an event that identifies the command and the memory objects involved. A subsequent command waiting on that event is guaranteed that updates to those memory objects are visible before the command begins execution.

#### 2.1.2 A summary on OpenCL programming

OpenCL represents the today's standard for programming across heterogeneous devices, thanks to which parallel algorithms can be developed once to be then executed on a wide variety of different devices. Despite the portability and the homogeneity of coding, OpenCL shows various drawbacks and limitations.

With regards to programming, OpenCL coding is low-level and requires non-trivial parallel programming skills to guarantee the correctness of kernel execution. In addition, host-side and device-side models are quite different from each other, from both the language object-model and the concurrency paradigm points of view.

OpenCL kernels are written in a subset of C99 with some restrictions and extensions. For example, parameters of kernels that are pointers must come along with a *global*, *constant* or *local* qualifier. Pointers-to-pointers are not supported, which means that vector elements can be only of primitive or struct types. Kernel functions must return *void* and the library functions defined in the C99 standard headers are not supported<sup>1</sup>. On the other hand, host-side is programmed according to the native model of the host platform. Whereas C (without restrictions) is the specification language of the OpenCL API, various wrappers have been built over the latest years to support the execution of kernels from within different languages, like C# and Python.

Some data-types, like vector types (e.g. *float4*, *int8*, *half16*) and imagespecific types (e.g. *image2d\_t*) are available only on the kernel-side. On the host-side, programmers must use different data-types, such as regular pointers to primitive types (e.g. *float\**, *int\**, *half\**) in place of pointers to vector types (*float4\**, *int8\**, *half16\**) and the opaque *cl\_mem* to hold image data.

The concurrency model is also different between the host and the device. On the device, individual processing elements within a group synchronize with each other in a shared-memory fashion. On the other hand, synchronisation between the host and the device and between individual commands submitted by the host is based on events and explicit messages (commands), which resembles the message-passing paradigm.

From the productivity point of view, host-side coding is mostly boilerplate. The steps to code in the host are in fact the same, independently from the kernel executed. These steps include loading kernel sources, compiling them, instantiating a device, creating buffers, setting up kernel arguments, schedul-

<sup>&</sup>lt;sup>1</sup>This refers to OpenCL Specification 1.2. The new OpenCL specification 2.0 removes some of these restrictions

ing the kernel and waiting for its completion. Nevertheless, host-side coding requires time and effort to guarantee the correctness of execution, especially in allocating/initializing buffers and setting up kernel arguments. Whenever a programming mistake is introduced in the host-side (e.g. because of incorrect buffer size with consequent out-of-bounds accesses), kernel execution may fail or interrupt obscurely. Programmers are therefore asked to spend time and energy in coding *how* a computation has to be executed instead of strictly focusing on *what* the computation has to do (i.e. the kernel).

Despite the recent availability of debugging and profiling tools, debugging OpenCL computations is still difficult and error-prone. OpenCL compilers/client drivers are characterized by quite basic, and sometime obscure, error reporting, which is definitely not as advanced as in compilers like GCC and Clang-LLVM. Recently, real-time debugging of kernels executing on a device became possible, but programmers must use specific, third-party tools. Productivity in spotting and fixing coding mistakes as well as in detecting runtime issues is therefore very limited.

From the perspective of execution, OpenCL doesn't provide any help to optimise code for specific types of devices nor to understand which of the available devices should be selected to execute a particular kernel with high performance.

Even though kernels can run across different types of devices, to obtain the highest performance device-specific optimisations must be applied. For example, vector data-types can speed up computations on CPUs, while on most GPUs<sup>2</sup> they can be counterproductive. The memory access pattern is another aspect that can be deeply affected by optimisations for different types of devices. GPUs tend to perform better under interleaved accesses (i.e. successive work-items access successive elements of a buffer) while performance on CPUs in higher when a single work-item accesses a contiguous stride of memory, improving cache-usage and exploiting prefetching. To run efficient code across devices, OpenCL programmers must therefore be aware of the specific characteristics of the available devices and code different kernels, each optimised for a specific device.

$<sup>^2\</sup>mathrm{Especially}$  GPUs with an instruction set not based on Very Long Instruction Word(s) (VLIW)

### 2.2 High-level programming languages and libraries

From the early ages of general purpose programming on GPU (GPGPU), various researches have been focusing on the definition of an abstraction layer to simplify parallel programming on heterogeneous platforms.

Nowadays, CUDA and OpenCL are the two major solutions for programming on GPUs. Even though OpenCL obtained a wider popularity thanks to its industry standard specification and to the broad support, OpenCL and CUDA are very similar to each other, from both the abstract execution model, the memory model, and the programming-style points of view. For this reason, most of the relevant research of the last few years has leveraged OpenCL or CUDA as the "ground layer" over which to build a more abstract and easy way to express and execute parallel computations.

The first attempts to make parallel programming easier and more confortable are represented by language bindings for CUDA and OpenCL APIs [1,15,46,75]. Despite the ability that these solutions provide to program CUDA and OpenCL host-side using languages different from C/C++ (e.g. Java, C#), they do not introduce any significant abstraction over the low-level APIs.

Given the popularity of the LLVM compiler, and especially of its intermediate representation (IR), some recent efforts have been spent on extending the LLVM backend to map the IR to the specific intermediate or target representation of GPU executables [21,44]. LLVM has been employed to transparently extend the set of target device types of CUDA programs, traditionally GPUs only, to CPUs and to all the architectures supported by LLVM. While leveraging LLVM IR can enhance architecture-specific optimisations, deliver crossdevice execution transparency and, more generally, hide the heterogeneity of the platform to the frontend/users [73], from the programming abstraction perspective there have been no significant improvements. On top of these solutions, the developers continue to use the OpenCL/CUDA C/C++ API but relying on LLVM to produce the intermediate representation between code and brand-specific instruction sets. Nonetheless, being an open-source compiler, LLVM (and LLVM frontends like CLANG) may be succesfully employed to define more abstract programming models for heterogeneous platforms.

C++ AMP [30] is an open specification for implementing data-parallelism which represents a more interesting research from the point of view of programming abstraction. C++ AMP exposes reshaped programming constructs/patterns (e.g. *parallel\_for\_each*), lambdas and custom data-types (e.g. *array\_view*) to express data-parallelism on collections. C++ AMP supports both GPU execution<sup>3</sup> and CPU vector (SSE) processing. Lambda expressions represent a powerful and productive construct to express parallel code, especially in case of recurrent, succinct computations.

While leveraging on language constructs that C++ programmers are comfortable with, such as arrays and lambdas, the API also introduces additional language features for composition/dispatching that require a certain effort to be understood and used correctly. Native data-types (e.g. *array*) come along with brand new types (e.g. *array\_view*) that are specifically used in place of native types to drive a certain execution/memory behaviour (e.g. data-transfer on-request). The definition of custom types in order to drive the runtime behaviour, such as enabling a particular optimization, can be confusing and difficult to assimilate. We consider *pragma* directives, gcc-like attributes and .NET custom attributes examples of programming features that are more independent from the content of the computation and, for this reason, more suitable to express meta-information.

SkePU [22] is one of the most popular libraries for data-parallelism based on skeletons. Skeleton programming is an approach that shows several advantages from both the coding and the execution support points of view. Skeletons are intuitively mapped to specific, well-known processing behaviours, are parametric (i.e. customizable) and easy to compose with each other. This makes skeleton programming easy to learn and to apply productively. The abstraction provided by skeletons makes them also the perfect candidates for transparent target-specific optimisations. Finally, given the intrinsic restrictions on the code used to parametrize skeletons, such as on the input and output type, the correctness of skeleton-based parallel programs is easy to validate. The principal drawback of SkePU and, more generally, of skeleton programming, is the restricted flexibility. If a skeleton library doesn't provide any opaque "container" to define computations that go beyond the provided skeletons, the set of algorithms that can be effectively expressed using the model exposed by the library is very narrow.

Muesli [14] is another popular skeleton-based library. Muesli supports and seemlessly integrates both data and stream paralellism. In particular, a Muesli program is a stream-based computation, where each "node" of the stream can express data-parallelism. Muesli also introduces the concept of *sequential computations* inside parallel programs, especially to distribute and collect stream data. Despite the effort to enhance flexibility by joining stream parallelism, data-parallelism and sequential functions, Muesli designs new functions and data-types (e.g. distributed arrays and matrices) instead of leveraging native

$<sup>^3\</sup>mathrm{On}$  November 12, 2013 the HSA Foundation [3] announced a C++ AMP compiler that outputs to OpenCL

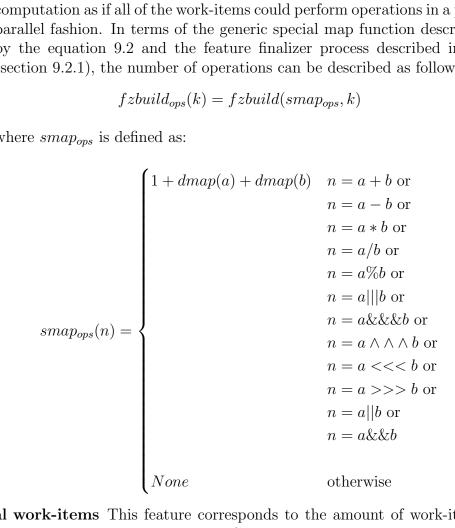

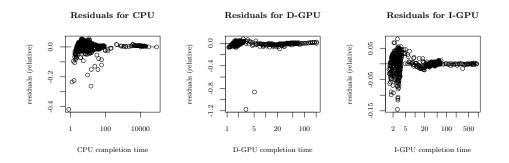

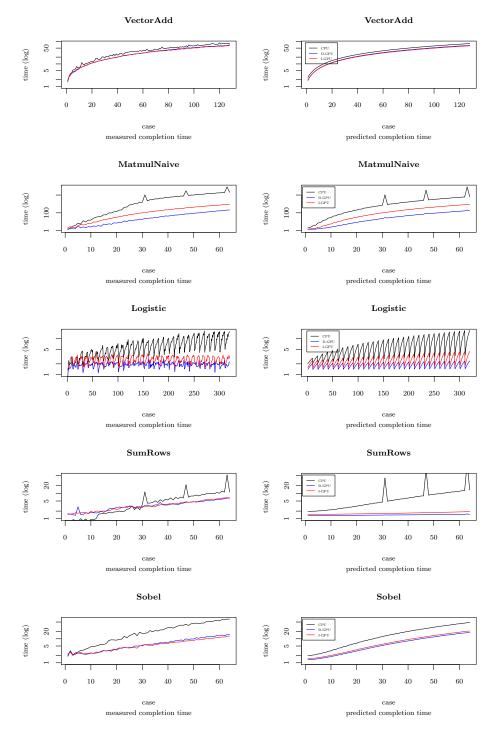

and possibly expressive language constructs.