## UNIVERSITY OF PISA COMPUTER SCIENCE DEPARTMENT

# The Prosper runtime monitor: design and formal verification

Candidate: Hind Chfouka hind.chf@gmail.com Supervisors Andrea Corradini Roberto Guanciale *Examiner* Fabrizio Baiardi

Academic year 2013-2014

To my sister Ymane

### Abstract

Runtime monitoring is a technique that can be used to guarantee a certain security property over a system resource. In computer systems, a common approach is to deploy a runtime monitor as a security module of the Operating System's kernel. This approach suffers from some vulnerabilities that can compromise the integrity of the security module. In a virtualized environment, an alternative approach is to exploit the isolation property to protect the security module. In this thesis, a runtime monitor supported by the Prosper hypervisor is presented. This is a fully verified Virtual Machine Monitor for embedded system targeting an ARM CPU architecture. The runtime monitor presented is able to guarantee a security property thanks to the monitoring of the hypercalls that are provided to the guest Operating System by the hypervisor. Through a formal methodology, the thesis discusses the enforceable security properties for the proposed monitor and identifies a security property that permits the protection of the Operating System from code injection attacks. The enforcement of this property is possible thanks to a validation mechanism of the hypercalls that is formally identified in this work. The thesis presents the proof of correctness of the validation mechanism that is fully verified with the support of the HOL4 proof assistant.

## Acknowledgements

I would like to thank my supervisors Andrea Corradini and Roberto Guanciale for the academic support; I express my gratitude to Andrea Corradini for all the feedbacks related to the thesis, for introducing me to the topic of the formal verification and for being my academic tutor during the last two years of my master studies. I am thankful to Roberto Guanciale for the valuable guidances during my studies and research at the Royal Institute Of Technology, thank you for the time spent to discuss the thesis and all my doubts. I would like to thank my examiner Fabrizio Baiardi for the important feedback about the thesis. My thanks goes also to Hamed Nemati and Oliver Schwarz for the technical help provided to me during the project work.

My sincere thanks also goes to Mads Dam and Christian Gehrmann for accepting my Erasmus Placement proposal and letting me take part of the Prosper project.

Besides the academic acknowledgements, I would like to thank Giulia and Roberto, Andrea Azzarà, Christiane Baum for their friendship during the months spent in Stockholm. Also, I would like to thank Aida and Bengt Nilsson for supporting and orienting me in the Swedish society.

I am grateful to my uncle Ahmed thanks to whom my passion for the mathematics started since an early age. My sincere thanks also goes to Maura Casella, thank you for your presence and support throughout my years of studies.

Thanks to my friends and colleges Ilaria Ceppa, Lorenzo Vannucci, Alessandro Bianchi, Laura Guidi, Annalisa Cipolli, Chiara Marcheschi and Marco Ponza for the time spent together. Your friendship coloured my days at the Polo Fibonacci for the last six years :-).

A special thanks goes to my parents. I am grateful for your unconditional love, support and patient. Thank you Ymane for being my sister, my strength and my inspiration in life. There are no words to express how I feel blessed for being part of our splendid family.

A big thanks goes to Emilio, thank you for your love and support and for being there for me.

Last but not least, I would like to thank my friend Giusi, thank you for being my best friend in life.

# Contents

| 1        | Intr | oduction                                        | <b>5</b>   |

|----------|------|-------------------------------------------------|------------|

|          | 1.1  | Structure of the thesis                         | 7          |

| <b>2</b> | Bac  | kground                                         | 8          |

|          | 2.1  | Virtualization                                  | 8          |

|          |      | 2.1.1 Overview on virtualization                | 9          |

|          |      | 2.1.2 Types of virtualization                   | 2          |

|          |      | 2.1.3 Advantanges of virtualization             | 15         |

|          | 2.2  | The Prosper Hypervisor                          | 17         |

|          |      | 2.2.1 ARM architecture                          | 8          |

|          |      | 2.2.2 Formal Model of the ARM architecture      | 24         |

|          |      | 2.2.3 Hypervisor: design and isolation property | 27         |

|          | 2.3  | Automated Theorem Proving 3                     | 32         |

|          |      | 2.3.1 The HOL4 thorem prover                    | 33         |

| 3        | Rui  | time monitoring for Prosper 3                   | 37         |

|          | 3.1  | Motivations and Goals                           | 37         |

|          | 3.2  | The Prosper runtime monitor                     | 10         |

|          |      | 3.2.1 Design choices                            | 42         |

|          |      | 3.2.2 Security properties                       | 16         |

|          |      | 3.2.3 Security policy and validation mechanism  | 50         |

|          | 3.3  | Formal proof of correctness                     | 61         |

|          |      | 3.3.1 Top Level Specification                   | 62         |

|          |      | 3.3.2 Goals formalization and proof             | 53         |

| 4        | Cor  | rectness of Prosper monitor with HOL4 7         | <b>'</b> 4 |

|          | 4.1  | General structure of the proof verification     | 74         |

|               | 4.2          | Example of proof with the HOL4 | 76 |  |  |

|---------------|--------------|--------------------------------|----|--|--|

| 5 Conclusions |              |                                | 79 |  |  |

|               | 5.1          | Related works                  | 80 |  |  |

|               | 5.2          | Future works                   | 81 |  |  |

| Bi            | Bibliography |                                |    |  |  |

# Chapter 1

# Introduction

Runtime monitoring [28] [15] [19] is a computing system analysis technique based on the observation of a running system and the consequent reaction in case of violation of certain security properties. A common application domain of this analysis technique are Operating Systems. An OS has the task of managing and protecting the system resources (memory, I/O devices, files, etc) from malicious accesses, based on a security policy. An approach [33] for realizing the system resources protection is to deploy a kernel security module that monitors and controls all the accesses of the system's subjects (processes, applications, users, etc) to the resources. The security module intercepts all the access operations on the basis of a security policy, and validates them using a suitable validation mechanism.

The approach of protecting the system resources with a kernel module suffers from some vulnerabilities [9] that are a motivation for this thesis. The runtime security module that protects the system resources is a security-critical component of the system. Therefore, a malicious manipulation of the module itself can compromise the system resources protection, and have undesirable consequences for the whole system security. This kind of attacks are possible in practice since commodity OS (Linux for instance) are not tamper-resistant [9], which means they are vulnerable to malicious manipulations as shown by many case studies in the literature on OS security.

A kernel security module should be part of the trusted computing base. Therefore, it is desirable to be able to *formally verify* its correctness. Unfortunately, the task of the formal verification of a software component becomes infeasible when it comes to an Operating System's module. In fact, it is well known that the complexity and size of Operating Systems are an obstacle to their formal verification.

In this thesis, we present an alternative approach for the runtime monitoring of a commodity OS that takes advantage of the *virtualization* [26] [31] technology. The approach relies on the *isolation property*, that is one of the main benefits of the virtualization, to provide a tamper-resistant runtime monitor. The runtime monitor proposed is based on the Prosper hypervisor [3] [11] [12] [20]. This is a fully verified Virtual Machine Monitor for embedded systems targeting the ARM architecture [27] [29] and developed in the Prosper project<sup>1</sup>.

We present the general design choices for a runtime monitor supported by the Prosper hypervisor. The goal of this monitor is to control the system running as guest of the hypervisor, and to enforce a correct system state with respect to a security property. The design choices exploit the infrastructure provided by the hypervisor and allow the *complete mediation* of the runtime monitor in the operations that are *sensitive* for the security property.

In this work, we present a general analysis that identifies what kind of security properties can be enforced by the Prosper monitor. This analysis takes into account the infrastructure provided by the Prosper hypervisor. Furthermore, since the Prosper monitor belongs to the general class of *Execution Monitors (EM)* [28], the thesis takes into account that the enforceable properties by an EM must satisfy a necessary condition, that is formalized in [28], in order to be ensured.

A significant part of the thesis studies a particular application of the Prosper monitor. This application has the goal of protecting the Linux kernel running as guest of the hypervisor from *code injection attacks*. To this purpose, we identify two security properties that need to be enforced. Through a formal methodology, we define an appropriate validation mechanism for the Prosper monitor that is able to guarantee the security properties. Therefore, we provide a complete proof of correctness for the validation mechanism. This proof is fully verified with the assistance of the HOL4 theorem prover [17].

An important part of the work described in this thesis has been realized at the Theoretical Computer Science group of the Royal Institute of Technology (KTH), where part of the Prosper project is developed.

<sup>&</sup>lt;sup>1</sup>The Prosper project is a collaboration between the Security Lab of the Swedish Institute of Computer Science, and the Theoretical Computer Science group at the Royal Institute of Technology (KTH)

## **1.1** Structure of the thesis

This thesis is structured as follows:

- Chapter 2 introduces all the background needed to understand the following chapters. Section 2.1 presents the virtualization describing the main concepts behind this technology, the main types of virtualization and its advantages. Section 2.2 presents the Prosper hypervisor and the formally verified isolation properties. Section 2.3 presents Automated Theorem Proving as a formal method for software and hardware verification, introducing the HOL4 theorem prover that is used to verify the proof of correctness of the validation mechanism.

- Chapter 3 presents the Prosper monitor designed and formally verified in this thesis. Section 3.1 discusses the main motivations of the approach proposed for the Prosper monitor, and describes the goals of the thesis work. Section 3.2 presents the Prosper monitor discussing the principle design choices, the enforceable security properties, and the application to the code injection attacks. Section 3.2.3 discusses the validation mechanism for this application, and Section 3.3 presents the proof of correctness of the validation mechanism.

- Chapter 4 presents the verification of the formal proof with the HOL4. Section 4.1 presents briefly the general structure of this verification. In order to give an idea to the reader about a machine assisted verification with the HOL4, in Section 4.2 we provide an example of proof for a lemma.

- Chapter 5 concludes the work presented in this thesis, mentioning some related works in Section 5.1 and discussing the possible future developments in Section 5.2

## Chapter 2

# Background

## 2.1 Virtualization

One of the most efficient approaches for managing complexity in computer systems is their division into *levels of abstraction* [31] [26]. Each level is responsible of managing a set of the system resources at a different level of details, providing a well defined *interface* to the other levels. The levels of abstraction or layers are organized in a hierarchy: lower layers are implemented in hardware and higher layers in software. The use of an interface allows the task of a computer system design to be divided into independent sub-tasks, so that the hardware design and the software design can proceed independently. This is only possible if the design of each part respects the specification of the same instruction set, that is a well defined interface. An Operating System as well provides an abstraction to the applications running on top of it. This is possible thanks to an interface defined as a set of system calls that are used by the applications developers without the need of hardware details knowledge.

The interface based approach has many advantages to manage computer system complexity, but it can be restrictive: a component that is designed for a specific interface will not work with other interfaces. There are different processors with different instruction sets, and there are different operating systems. For example, a user application distributed as binary program is committed to a specific instruction set and operating system. Therefore, diversity in computer system architecture reduces the portability of a computer software component. Another restriction is related to system resources consideration. A traditional computer systems design relies on the implicit assumption that there is a single operating system responsible of managing the system resources. This assumption reduces the system flexibility in case more operating systems would like to share a single set of resources.

Virtualization is the technology that overcomes the restrictions of flexibility and portability. When a computer system component is virtualized, its interface and all resources visible through the interface are mapped into the interface and the resources of the real system. Thus, with the virtualization a second (virtual) version of the real component is created so that it appears to be different. Virtualization can be applied to a computer system component, such as disks, I/O devices, memory, etc, but also to the entire hardware machine. In this thesis, we are interested in the last type of virtualization, that is in Virtual Machines.

## 2.1.1 Overview on virtualization

Virtualization [26] [31] [7] introduces an additional layer that creates a virtual version of the real computer system or subsystem. The virtual version is different from the real and physical subsystem, but thanks to the additional layer it is possible to emulate the real subsystem behavior. Let's consider the example of a hard disk. In some applications, it may be desirable to partition a single large disk into a number of small virtual disks. Having multiple virtual disks is more flexible than having a single physical disk, for example during resource allocation to user applications. The virtual disks are mapped to a real disk by implementing each of the virtual disks as a single large file on the real disk. It is therefore necessary to introduce an additional layer that provides a mapping between virtual disk contents and real disk contents using the file abstraction as an intermediate step. Furthermore, each read or write operation from the virtual disk operation, thanks to the mapping created.

More formally, virtualization involves the construction of an homomorphism f that maps a real *host* system to a virtual *guest* system [26]. This homomorphism maps the real state to the guest state, and for each possible sequence of operations that modify the state of the host from  $S_i$  to  $S_j$ , there is a corresponding sequence of operations that perform an equivalent modification to the guest state from  $S'_i$  to  $S'_j$ .

It's worth to stress that virtualization is different from abstraction. Virtualization does not necessarily hide details, and the level of detail in a virtual system is often the same as the underlying real system.

The virtualization of interest in this thesis is the hardware virtualization.

### Hardware virtualization

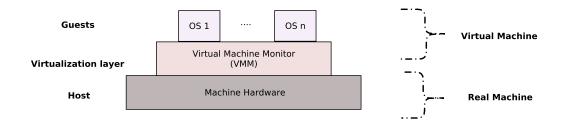

With hardware virtualization the intent is to create a *Virtual Machine*, that is an efficient and isolated duplicate of the real machine. This virtualization is implemented by adding a layer of software called *Virtual Machine Monitor (VMM)* to the real machine, as illustrated in figure 2.1. The VMM creates a simulated machine environment (the virtual machine) for the software running on top of the real machine. In general a VMM allows the execution of complete operating systems reaching a high versatility of the computer hardware.

Figure 2.1: Hardware Virtualization

In hardware virtualization, the real machine plays the role of a host, the virtual machine plays the role of the guest, whereas the VMM realizes the homomorphism mentioned above.

The article [26] of Popek and Goldberg is often referred to as the original source for the VMM criteria. Here the conditions for a computer architecture to support virtualization are defined. They also state the conditions a virtual machine monitor must satisfy. These conditions are referred to as *VMM properties*, and they are:

• Equivalence: The guest software should exhibit a behaviour that is *essentially identical* to the one demonstrated when running directly on the real

machine. This property is also referred to as *fidelity*.

- **Resource Control**: The VMM must have complete control of the system resources. This property is referred to as *Safety*.

- Efficiency: A significant number of machine instructions must be executed without the VMM intermediation or, in other words, by the real machine itself. This is referred to as *Performance*.

In order to satisfy the fidelity property, the environment provided by the VMM must be equivalent to the real machine. This is possible if and only if: for any possible starting state  $S_1$  of the real machine such that  $f(S_1) = S_2$ , where f is the homomorphism mentioned above, if the real machine reaches a consistent state  $S'_1$ , then the virtual machine reaches a state  $S'_2$  such that  $S'_2 = f(S'_1)$ . To fulfil the safety property, the VMM must be invoked for each attempt of affecting the system resources configuration by any arbitrary guest software. Finally, the third property depends on the ability of the VMM to provide a virtual environment in an efficient and optimized way.

Based on [26], the problem to be addressed in the creation of a VMM, when operating within the characteristics of the Instruction Set Architecture (ISA) of the targeted host machine, is the satisfaction of the above properties. Assuming that there are two possible execution modes in a computer system, user and privileged mode, the ISA includes two groups of instructions:

- *Privileged instructions:* these are instructions that trap if the processor is in user mode and do not trap if it is in a privileged mode. An instruction traps when a fault is raised causing a synchronous interrupt that must be handled by the appropriate handler.

- Sensitive instructions: these are instructions that change the configuration of the system resources.

The main result in [26] states that the construction of VMM that satisfies the three properties is possible only if each sensitive instruction is privileged. This criterion is now known as *classically virtualizable*. Assuming that a computer system is classically virtualizable, the VMM is supposed to work with each group of instructions maintaining the conditions of equivalence, resource control and

efficiency. To satisfy the first two properties, a VMM manage the guest software and the underlying real machine through *emulation*, *isolation*, *allocation*:

- 1. Emulation: emulation is important for all guest operating systems. The VMM must present a complete real environment, or virtual machine, for each software guest including operating system and user applications. Ideally, the OS and application are completely unaware they are sharing system resources with other applications. Emulation is the key to satisfy the equivalence property. However, in some cases reaching this complete unawareness is not possible. To overcome this problem a special virtualization has been introduced that is called *para-virtualization*. This is explained more in detail in section 2.1.2.

- 2. Isolation: isolation is important for a secure and reliable environment. Each virtual machine should be sufficiently separated and independent from the operations and activities of other virtual machines. Faults that occur in a single virtual machine should not impact others. This property provides high levels of security and availability in a virtualized system.

- 3. Allocation: the VMM must allocate the hardware resources to the virtual machines that it manages. Through allocation, the VMM satisfies the resource control property.

In a classically virtualizable system, a VMM must reside at a higher privilege level than the guest operating system. This is a necessary assumption to fulfil the complete resources control requirement. On the other hand, modern operating systems are designed to run in the highest privilege level. This is a challenging problem to be addressed when designing a hardware virtualization. In fact, without any intervention, a guest operating system is not able to perform privileged instructions to manage the system resources. This problem is solved differently based on the type of virtualization adopted.

## 2.1.2 Types of virtualization

In the literature on virtualization [32] [31], we can find different macro classes of virtualization. *Server virtualization* is basically another notation for the hardware

virtualization discussed in section 2.1.1, otherwise called *system virtualization*. Another class of virtualization is the *Storage virtualization* that deals with the virtualization of storage devices (hard disks, memory storage, etc..). Network virtualization instead applies the general concept of virtualization to a computer network architecture.

With restriction to the hardware architecture, there are different paradigms of virtualization that are deeply discussed in [13] and [14]. Here a summary is presented:

## Full virtualization

As discussed in Section 2.1.1, one requirement for a classically virtualizable system is that the Virtual Machine Monitor must execute in privileged level, while the guest OS executes in a non-privileged level. In this way, the guest OS is not able to perform the privileged operations needed for the resources management, but it must rely on the VMM mediation. In other words, the execution of privileged instructions are delegated to the VMM. In the full virtualization, each time the guest OS tries to execute a privileged instruction this generates a trap to the privileged mode. Since the VMM executes in a privileged mode, one possibility is to have a trap handler that emulates the privileged instruction requested by the guest OS. In this way, privileged instructions are handled by the VMM before their real execution by the real machine, while non-privileged instructions performed by the guest OS do not trigger the trap-and-emulate mechanism.

Advantages: the advantage with this type of virtualization is that the guest OS can run without any modification. This is possible since the virtual interface provided to the guest is identical to the real machine interface. Consequently, binary code of the operating system and user applications can run without any modification.

**Disdvantages** the trap-and-emulate mechanism introduces a significant overhead for each privileged execution performed in the system. Moreover, full virtualization can be applied only under the classically virtualizable assumption, since if there is a sensitive operation that is not privileged, the trap-and-emulate mechanism is not sufficient to guarantee a complete resource control by the VMM.

## **Binary translation**

This virtualization paradigm is presented as a solution in case the group of sensitive operations is not a subset of the group of privileged operations. In this case, the Popek and Goldberg requirement for a classically virtualizable system is not satisfied, and full virtualization cannot be applied. With binary translation, the idea is to perform a scan of the guest code (dynamically) identifying all sensitive operations, that do not trap, before they are executed. The identified operations are replaced an explicit invocation of the VMM. This approach increases the code size of the guest software introducing more vulnerabilities from a security point of view. In fact, it is desirable to have the amount of code running in privileged mode as small as possible: this reduces the area of possible attacks that affect the security of a computer system.

Advantages: The main advantage of binary translation is making possible the virtualization in case the Popek and Goldberg requirement is not satisfied.

**Disadvantages:** The scanning and replacement technique introduces an overhead that is larger than the overhead introduced in the full virtualization.

### Para-virtualization

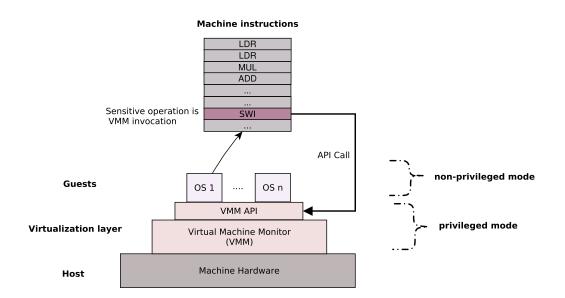

Para-virtualization eliminates much of the trap-and-emulate overhead introduced with the VMM implementing the virtualization. But to achieve this improvement the guest operating system must be modified. In para-virtualization, all privileged instructions in OS kernel must be modified to perform the appropriate invocation to the VMM. The guest OS communicates directly with the VMM through an interface provided by the VMM as illustred in figure 2.2. This direct communication eliminates the overhead introduced by the emulation mechanism of the full virtualization paradigm. The calls provided by the VMM interface are invoked by the sensitive operations that manage the system resources (calls for memory configuration and management, for interrupt handling, etc).

Advantages: The VMM interface offers an abstraction that is better than the trap-and-emulate mechanism. In addition, a VMM call performs operations

Figure 2.2: Paravirtualization

more efficiently than the emulation of a sensitive instruction. This introduces a significant improvement of efficiency.

**Disadvantages:** The inconvenient with para-virtualization is that a guest OS must be adapted to use the VMM's interface. This porting can require a lot of work. Besides, a closed-source operating systems cannot be ported to use the VMM interface without a knowledge of its design.

## 2.1.3 Advantanges of virtualization

Thanks to hardware virtualization it's possible to enable entire virtual machines to be logically separated by the VMM from the hardware they run on. This flexibility creates interesting possibilities for a system design and allows software designers to be independent from the machine architecture characteristics. Virtualization technology enhances other positive features highly required in a computer system, some of them are discussed in the following paragraphs.

## Isolation

An important benefit of virtualization is isolation. The VMM is able to manage all guests enforcing the isolation property. Each guest is allocated into a partition that is protected from the other partitions. A software guest can run on a dedicated virtual machine, without being aware of the presence of other guests. The isolation property enhances the system reliability. In fact, thanks to the isolation, a fault caused by a guest do not affect other partitions hosting other guests of the same machine.

It is worth mentioning that nowadays, instead of pure isolation, virtualization is used in architectures where guests want to communicate. It is then important for a VMM to provide a communication infrastructure to support inter-guest cooperation. This must be done preventing interferences between guests.

#### Minimized trusted computing base

The trusted computing base (TCB) of a system is the set of all hardware and software components that are critical to its security, in the sense that bugs or vulnerabilities occurring inside the TCB might compromise the security properties of the entire system. A given piece of hardware or software is part of the TCB if and only if it is designed to be part of the mechanism that provides security to the system. In operating systems, TCB consists of those functionalities that run under a privileged mode and manage the system resources. Therefore, having a large TCB increases the attack surface of the whole system.

With hardware virtualization, the problem of attacking the TCB is addressed minimizing the TCB itself. In fact, VMM code is the only one running in privileged mode, while the guest code executes with a non-privileged mode. Consequently, the TCB of a virtualized system is only the VMM code. With a minimal TCB, the attack surface of the system is minimal. Besides, since it is security-critical for the whole system, having a minimal code for the TCB open more chances to a formal verification if compared with an OS kernel.

## Security

Virtualization enhances the security of a system. This is thanks to the isolation and the minimized trusting computing base that characterize a virtualized system. In fact, with the isolation property an untrusted guest can execute on the same machine without compromising the other trusted parts of the system. Whereas a minimal TCB reduces the surface attack and allows a formal verification and analysis.

More in general, a VMM satisfying the VMM properties stated by Popek and Goldberg has a complete control over the system resources. This property enables possibilities for additional security services that a VMM can provide to their guests. These services can exploit the isolation property bringing benefit for a guest OS without its modification. The improved security offered by the hardware virtualization is one of the basic motivations leading this thesis work as it will be clear from Chapter 3.

## 2.2 The Prosper Hypervisor

Today the use of embedded systems in every day life is increasing dramatically. For example, a mobile phone is one of the most common embedded systems used for digital communication. More in general, embedded systems are being used more and more for several purposes and in different domains: entertainment, media and finance, control systems in industry and health. Consequently, given their employment in many areas, security in embedded systems is becoming a relevant research topic [22].

Security issues in embedded systems include different aspects related to reliability (low failure probability, robustness during execution, etc), but also related to protection from malicious software attacks. The second aspect is particularly critical considering that open source software is often used for embedded system. The use of open source software brings several benefits and open possibilities for improvements by a large community. However, source code and documentation availability might introduce some vulnerabilities in embedded system security, giving more chances for malicious attacks. One of the main focus of the Prosper project [3] is on addressing software attacks in embedded systems.

Virtualization can be a valid approach to enhance the security level in the realm

of embedded systems. A Virtual Machine Monitor runs at the most privileged execution level of the system providing isolation and security services to a software guest (see Section 2.1.1). Thanks to this benefits, trusted and untrusted applications can coexist sharing the same hardware without interferences, and relying on the security services provided by the VMM. In addition, with a tamper-resistant, minimal and formally verifiable trusted computing base (TCB), the embedded system security is enhanced. TCB can also provide the infrastructure for a security service such as monitoring or access control.

The Prosper project [3] has the goal of building a framework for fully verified and secure Virtual Machine Monitors for embedded systems, also denoted as *hypervisors*. The main result [11] [20] [10] [12] achieved so far is the design and the implementation of a fully verified tiny hypervisor targeting ARMv7 architecture [27] [29]. The Prosper hypervisor exploits the MMU (Memory Management Unit) security separation to embedded systems security. Thanks to the separation property, the Prosper hypervisor supports parallel execution of multiple para-virtualized guests running in user mode.

## 2.2.1 ARM architecture

A good overview about ARM architecture can be found in [27]. The article describes in a synthetic and readable way the architecture and suits perfectly with the knowledge requested for this thesis work.

Advanced RISC Machine (ARM) is a family of instruction set architectures (ISA) for computer processors based on a reduced instruction set computer (RISC) architecture developed by the British company ARM holdings. An instruction set, or instruction set architecture (ISA), is the part of the computer architecture related to programming, including the native data types, instructions, registers, addressing modes, memory architecture, interrupt and exception handling, and external I/O. An instruction set architecture provides a specification of the machine, and the native commands implemented by a particular processor.

The ARM ISA is a reduced instruction set, that is a particular CPU design strategy based on a small and simple set of instructions. The idea behind a RISC ISA is that simple instructions are highly-optimized, therefore a high level of performance can be achieved. On the other hand with a RISC ISA more responsibility is put on the compiler. *Complex instruction set computer (CISC)* is the alternative design strategy for CPUs. A CISC ISA consists of a set of complex instructions that rely more on functionalities provided at hardware level.

Today, ARM is the commonest ISA for embedded systems architecture, and this is mainly thanks to a combination of features that makes it particularly suitable for this kind of systems. First, ARM cores are very simple compared to most other general-purpose processors, which means that they can be manufactured using a comparatively small number of transistors. Second, both the ARM ISA and the pipeline design are aimed to minimize energy consumption, that is a critical requirement in mobile embedded systems. Third, the ARM architecture is modular: the only mandatory component of an ARM processor is the integer pipeline; all other components, including caches, MMU, floating point and other co-processors are optional, which gives a lot of flexibility in building system ARM-based CPUs.

The ARM ISA is a load-store architecture, that is, instructions that process data operate directly on registers and are separated from instructions that access memory. All ARM instructions are 32-bit long and most of them have a threeoperand encoding. There is also an ARM extension that introduces a subset of 16-bits instructions called *Thumb instructions*. This extension is introduced to achieve a higher code density for embedded applications, and considers a compressed version of the most commonly used 32-bit instructions. The ARM architecture specifies 16 general-purpose registers and provides support for coprocessors allowing the architecture to be extensible in case of specific applications.

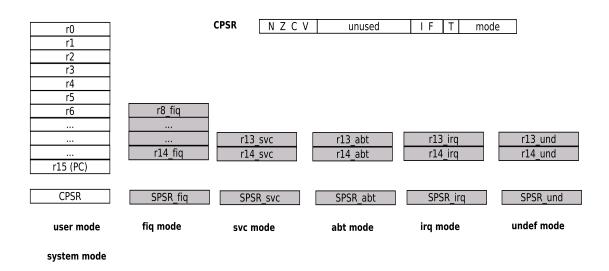

#### Registers

The ARM ISA provides 16 general-purpose registers in the user mode. Register 15 is the program counter, but can be manipulated as a general-purpose register. The general-purpose register number 14 is used as a link register by the branch-and-link instruction, that is provided by the ARM architecture to support conditional execution of arbitrary instructions. Register 13 is typically used as stack pointer, although this is not mandated by the architecture.

The current program status register (CPSR) contains four boolean condition flags (Negative, Zero, Carry, and oVerflow) and four fields containing the execution mode of the processor. The T field is used to switch between ARM and Thumb instruction sets. The I and F flags enable normal and fast interrupts respectively. Finally, the mode field selects one of seven execution modes that include a single non-privileged mode: **user mode** used for programs and applications running on the operating system, and six **privileged modes**:

- *Fast interrupt processing mode*: is enabled if the processor receives an interrupt request from a fast interrupt source.

- Normal interrupt processing request: is enabled when the processor receives an interrupt signal from any other interrupt source.

- Software interrupt mode: is enabled when the processor encounters a software interrupt instruction. Software interrupts are the standard way to invoke operating system services on ARM.

- Undefined instruction mode: is entered if the processor tries to execute an instruction that is not supported by the main integer core or some coprocessors.

- System mode: is used when privileged operating system tasks are running.

## Figure 2.3: ARM registers

Except of the boolean conditions field, CPSR is accessed only in a privileged mode. In addition to the 16 registers accessible in user mode, there are several

registers accessible in privileged modes only. For example, each SPSR (Saved Program Status Register) is used to store a copy of the value of the CPSR register when an exception is raised. Privileged modes that are activated in response to exceptions have their own R13 and R14 registers, which allows to avoid saving the corresponding user registers on every exception. For the quick handling of a fast interrupt request (FIQ), ARM provides 5 additional registers available only in the fast interrupt processing mode.

### Exceptions

The ARM architecture defines the following types of exceptions (listed in the order of decreasing priority):

- *Reset*: starts the processor from a known state and makes all other pending exceptions irrelevant.

- *Data abort*: is raised by the memory management unit when a load or store instruction violates memory access permissions.

- *Fast interrupt*: is raised whenever the processor receives an interrupt signal from the designated fast interrupt source

- *Normal interrupt*: is raised whenever the processor receives an interrupt signal from any non-fast interrupt source.

- *Prefetch abort*: is raised by the memory management unit when access permissions are violated during an instruction prefetch.

- *Software interrupt*: is raised by a special instruction, typically for an operating system functionality request.

- Undefined instruction: is generated when trying to decode an instruction that is not supported by the main integer core nor by one of the coprocessors.

All exceptions, except from the reset exception, are handled in a similar way: the processor switches to the corresponding execution mode presented in the previous section, saves the address of the instruction following the exception entry instruction in R14 of the new mode, saves the old value of CPSR to SPSR of the new mode, disables IRQ (in case of a fast interrupt, FIQ is also disabled), and starts execution from the relevant exception vector.

## Coprocessors

A coprocessor is a computer processor used to supplement the functions of the primary processor (the CPU). The ARM architecture supports a mechanism for extending the instruction set with additional coprocessors. For example, the ARM floating point unit is implemented as a coprocessor. Of more interest for this thesis is the system control coprocessor that is for the *Memory Management Unit* (*MMU*) and *translation lookaside buffer (TLB)*.

Memory Management Unit The Memory Management Unit (MMU) is a computer hardware unit which has the role of controlling all memory references. An MMU is the unit that effectively performs the virtual memory management, handling at the same time memory protection and cache control. General-purpose ARM-based systems are equipped with the MMU that provides a virtual memory model similar to conventional desktop and server processors. Through coprocessor  $15^{-1}$  of the ARM architecture, the MMU can be enabled. In case the MMU is disabled, when the CPU accesses memory, the virtual memory address is mapped to the same physical address (no translation is performed). If the MMU is enabled, the virtual address is translated to a physical address and the memory access is checked according to *access permissions*. This is done based on the mechanism of *page tables* that is discussed in the next paragraphs.

In order to improve virtual addresses translation, the MMU uses a cache called *Translation lookaside buffer (TLB)*. TLB contains the recently accessed mappings to speed-up the translations phase.

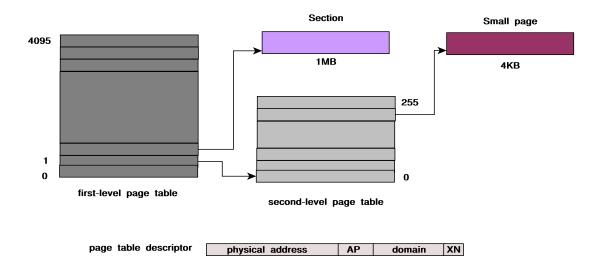

**Page tables** The MMU ARM architecture supports a two-level hierarchy for its page table structure, with page sizes of 1MB, 64KB, 4KB, and 1KB. For The Prosper hypervisor, we consider a page size of 1MB that are also called sections. A first-level page table (also called *master* page table) contains 4096 entries allowing up to 4GB of virtual memory. Each entry (also called page table descriptor), can be either unmapped, or it contains a pointer to a second-level table

<sup>&</sup>lt;sup>1</sup>The coprocessor 15 of an ARM chip is used to configure and control the ARM core modules including the caches and the MMU.

or a base address for a section of 1MB (in this case we have a section entry). A second-level page table has 256 entries each mapping 4KB of contiguous virtual memory. Figure 2.4 shows an overview of the first and second level page table.

Figure 2.4: 2-level page tables

Each page table descriptor is composed by three fields: the first one contains the physical address of the region where the virtual address is mapped, the second and third fields contain access permission bits and the domain of the mapped region respectively, that are needed for the memory protection mechanism.

When a mapping is needed, the TLB is searched first, if the mapping is not found the MMU performs the translation through a page table walk. That is the current master page table is used for the translation of the virtual address. If the mapping searched is section-mapped, the physical address is returned and the translation is finished. If the mapping is page-mapped (through a second-level page table), an additional level of translation is required. This translation is based on the second-level page table that is pointed by the master table descriptor. In both cases, the retrieved mapping is inserted into the TLB, possibly after the invalidation of an old entry if the cache is full. Memory protection mechanisms There are basically two mechanisms used by the MMU for memory protection. The first one is based on access permissions. Each page table descriptor contains access permission bits stating whether the mapped physical region can be accessed in readable and/or writable mode. A particular bit called *execute never (XN)* states if the mapped region can be executable. In this thesis we consider that the XN field is an access permission as well. A memory access is allowed only if it satisfies the access permissions retrieved during the translation phase, otherwise an exception is raised. The second protection mechanism consists of a *domain based memory access*. Every virtual memory page or section belongs to one protection domains. The current domain is contained in the *domain access register* of coprocessor 15. A running process can be either a manager of the domain, which means that it can access all pages belonging to this domain bypassing access permissions, a client of the domain, which means that it can access pages belonging to the domain at all.

## 2.2.2 Formal Model of the ARM architecture

In this section we present the formalization of the ARMv7 architecture (described in Section 2.2.1). This formal model is used in this thesis report as a building block to describe the behaviour of a system running on top of the Prosper hypervisor. In particular, this formalization will be used to describe a top level specification of the system behaviour running on top of hypervisor and monitored by the Prosper monitor. The formalization is also used to describe the formal verification performed in this work.

### Execution modes

The execution modes of an ARM CPU are formalized by the set mode:

$mode \stackrel{\text{def}}{=} \{usr, svc, abort, undef, irq, fiq, sys\}$

The non-privileged mode usr is used by the application processes, while all other modes are privileged and they are used to execute kernel activities. We define privileged and non-privileged modes as sub-sets of mode:

$$usrmode \stackrel{\text{def}}{=\!\!=} \{usr\}$$

$$privmode \stackrel{\text{def}}{=\!\!=} mode \setminus \{usr\}.$$

## Registers

The 16 ARM registers are formalized as a function *regs* that takes a register index, an execution mode and returns the register value if it is accessible in the input mode, otherwise it returns an undefined value. We formalize indexes and register values as sets:

$$idx \stackrel{\text{def}}{=} word8$$

$$regval \stackrel{\text{def}}{=} word32 \cup \{\bot\}$$

We denote with word8 and word32 an 8-bits and 32-bits values respectively. We denote with  $\perp$  the undefined value. Therefore, the function *regs* can be formalized as follows:

$regs: idx \times mode \longrightarrow regval$

The Program status register is formalized as a function that takes a privileged mode and returns as output the register content:

$$psrs: privmode \longrightarrow word32.$$

### Coprocessors

In this work, the only coprocessor of interest is the system control coprocessor 15 that controls the Memory Management Unit (MMU). We are interested in three registers of 32-bits of the coprocessor 15: the c1 represents if the MMU is enabled or not, the c2 gives the base physical address of the current master page table, and the register c3 identifies the current status of the domains. These registers are coregisters and we represent them as a tuple *coregs*:

$$coregs = \langle c1, c2, c3 \rangle$$

### Machine states

We consider a physical memory of 4GB that is addressed by a physical address of 32-bits. We denote a physical address with  $phy_addr$  and a value of memory with *memval*. These are basically *word32* and *word4* values. The physical memory is represented by a function *mem*:

$mem: phy\_addr \longrightarrow memval$

Finally, an ARM machine state  $\sigma$  is formalized as a tuple:

$\sigma = \langle m, regs, psrs, coregs, mem \rangle \in \Sigma$

Where:  $\Sigma$  is the set of all machine states,  $m \in mode$ , regs, psrs, coregs and mem are as described above.

### ARM machine behavior

An ARM machine behaviour is modeled by a transition system. The state transition relation is  $\rightarrow_l \subseteq \Sigma \times \Sigma$ , where  $l \in mode$ , and a transition is performed by the execution of an ARM instruction. A non-privileged transition  $\sigma \rightarrow_l \sigma'$ with  $l \in usrmode$  starts and ends in non-privileged states. Namely, if  $\sigma = \langle m, regs, psrs, coregs, mem \rangle$  and  $\sigma' = \langle m', regs', psrs', coregs', mem' \rangle$ , then  $m, m' \in usrmode$ . A privileged transition  $\sigma \rightarrow_l \sigma'$  with  $l \in privmode$  involves at least one state in privileged mode. The raising of an exception is modelled by a transition that starts in user mode and enables a privileged level  $l \in privmode$ .

### Memory Management Unit behavior

The main functionality provided by the MMU is to mediate all memory accesses, therefore it is invoked whenever an instruction that requires a memory access is performed. The MMU translates a virtual addresse to a physical address and mediates all memory accesses based on the protection mechanisms discussed in Section 2.2.1.

Given an ARM machine state and a virtual address of 32-bits, the MMU returns the physical address and the retrieved access permissions. These access permissions are represented as a 3-bits value and state whether the computed physical address can be accessed in readable, writable or executable mode. Both physical address and access permissions are computed using the master page table pointed by the coprocessor register c2, and the domain status and the current mode identified by the coprocessor register c3. The MMU behavior is formalized by the function mmu:

$$mmu: \Sigma \times virt\_addr \longrightarrow phy\_addr \times access\_mode.$$

Where  $virt_add$  is a word32 value, and  $access_mode$  is a word3 value. For instance, given a virtual address va and a machine state  $\sigma$ , we can apply mmu as follows:

$$mmu(\sigma, va) = \langle pa, (ex, w, r) \rangle$$

The application of the mmu function returns a pair  $\langle pa, (ex, w, r) \rangle$ , where pa is the physical address, (ex, w, r) are instead the access permissions: ex is 1 if and only if the address pa can be executed, w is 1 if and only if the address pa can be written and r is 1 if and only if the address pa can be read.

## 2.2.3 Hypervisor: design and isolation property

The Prosper hypervisor supports the ARMv7 architecture and is able to host a set of trusted guests along with an untrusted Linux guest [10]. The Linux guest may require a dynamic allocation of the memory, whereas all other guests have a static memory configuration. The trusted guests can provide for example some support services to the Linux kernel.

The Prosper hypervisor allows the execution and management of resources by all guests *without interferences* [12] [10]. This is guaranteed by ensuring the isolation property.

The hypervisor provides a virtualization mechanism of the memory subsystem allowing each guest to manage dynamically its own memory hierarchy and to enforce its own memory protection mechanisms.

The Linux kernel hosted by the hypervisor is a paravirtualized OS. Consequently the Linux kernel is aware of the hypervisor mediation. The hypervisor provides to Linux an API for a secure access to the hardware resources. This mediation allows the Prosper hypervisor to reach the requirement of *resources control* discussed in Section 2.1.

One of the most important system resource is the system memory. Therefore, the Prosper hypervisor has a complete control on the memory configuration. As introduced in Section 2.2.1, the main functionality of the MMU is managing the virtual memory mapping that is configured through a set of page tables residing in physical memory. Since page tables state how physical memory can be accessed by guests, they are a security critical part of the system and must be not directly manipulated by untrusted guests such as the Linux kernel. However, the Linux kernel needs to access dynamically page tables to set the memory layout. Therefore, page tables accesses are mediated by the hypervisor, thus providing an appropriate secure access that is called *MMU virtualization*.

## Virtualization mechanism

The virtualization mechanism implemented by the Prosper Hypervisor is based on *direct paging*. This is a common approach for the memory subsystem virtualization adopted for example in the Xen hypervisor [4] [8]. In this approach the page tables are located inside the guest memory simplifying the OS adaptation required by the paravirtualization. In order to guarantee the isolation, the hypervisor makes the page tables read-only to the OS providing an API to manipulate them safely.

Direct paging allows a guest to manipulate directly a page table as long as it is in passive state, that is not used by the MMU (also called active state). Once a page table is activated, all OS accesses are performed invoking the hypervisor through an appropriate API. This invocation is also called *hypercall*.

As presented in Section 2.2.1, the ARM MMU supports a two-level hierarchy for its page table structure. First-level page tables contain 4096 entries each of 32 bits, while second-level page tables contain 256 entries. Therefore, a page table of first-level is of 16KB, and the one of second-level is of 1KB. Physical memory is of 4GB and it is logically fragmented into blocks of 4KB, consequently a first-level page table occupies 4 blocks, while a single physical block can contain up to 4 second-level page tables.

Since page tables are kept in the guest space, this simplifies the OS adaptation. However, this implies that the hypervisor must protect the page tables from accesses in writable mode. In particular, the hypervisor must prevent all modifications of memory configuration that can be performed without the hypervisor mediation. To allow the hypervisor to protect the page tables, the virtualization mechanism types the physical blocks. Each physical block can have one of the following types:

- *data:* the block does not contain sensitive data and can be written by a guest.

- L1: the block contains a part of a first-level page table.

- L2: the block contains 4 second-level page tables.

Typing each physical block allows the hypervisor to write-protect active page tables enforcing *page type constraints*. These constraints require that a guest might write only physical blocks of type data. In order to fulfil this constraint, the virtualization mechanism maintains *reference counters* that track:

- For each block typed L2 the number of L1 page tables entries that point to one of the 4 L2 page tables residing in the physical block.

- For each block of type data, the number of entries (L1 or L2) that point to the physical block and are writable in user mode.

A guest can change the type of a physical block (for example by allocating or freeing a page table) only if the corresponding reference counter is zero. The hypervisor enforces this policy in addition to the general isolation policies (e.g. a guest may only modify a page within its assigned physical memory region) whenever the MMU configuration is updated. Since all MMU updates are performed through a dedicated API, the hypervisor performs the necessary checks to enforce security policies each time a hypercall is executed. The API offered by the hypervisor includes handlers for the manipulation of the MMU configuration, namely for:

- Page tables creation.

- Page tables freeing.

- Mapping of a page table entry.

- Unmapping of a page table entry.

- Setting a master page table as the current page table.

## **Top Level Specification**

The behaviour of the hypervisor is defined as a transition system. This specification, called the Top Level Specification (TLS), models the behaviour of a system in which an arbitrary guest is running on top of an ARMv7 CPU with MMU support, in alternation with executions of abstract handler events. Handler events are performed in correspondence to ARMv7 privileged instructions, in response to a hypercall. These events imply invocations of the hypervisor handlers as atomic transformations  $H_a$  operating on an abstract machine state. Abstract states are concrete ARMv7 states extended by auxiliary data structures such as page types or reference counters that reflect the internal state of the hypervisor. Auxiliary data structures are called *abstract hypervisor state*.

Formally, the TLS state is represented as a tuple  $\langle \sigma, \eta \rangle$ , consisting of an ARM state  $\sigma \in \Sigma$  and an abstract hypervisor state  $\eta = \langle pgtype, pgrefs \rangle$ . More precisely, *pgtype* is a function for memory block typing and *pgrefs* is a function tracking reference counters of memory blocks.

$$pgtype : [0, 2^{20}) \longrightarrow \{D, L1, L2\}$$

For each possible physical block of 4KB, pgtype returns the block type that can be data (D), first-level page table (L1), or second-level page table (L2).

$$pgrefs: [0, 2^{20}) \longrightarrow \mathbb{N}$$

For each possible physical block of 4KB, pgrefs returns the number of references to it in the memory.

The TLS interleaves standard non-privileged transitions with abstract handler invocations. The TLS transition relation  $\langle \sigma, \eta \rangle \rightarrow_{i \in \{0,1\}} \langle \sigma', \eta' \rangle$  is defined as the following:

$$\frac{\sigma \xrightarrow{op}_{l} \sigma' \quad l \in usrmode}{\langle \sigma, \eta \rangle \xrightarrow{op}_{0} \langle \sigma', \eta \rangle} usr \qquad \frac{\sigma \xrightarrow{op}_{l} \sigma' \quad l \in privmode}{\langle \sigma, \eta \rangle \xrightarrow{op}_{1} H_{a}(\langle \sigma', \eta \rangle)} priv$$

The first inference rule usr states that an instruction op executed in nonprivileged mode that does not raise exceptions behave equivalently to the standard ARMv7 semantics and does not affect the abstract hypervisor state. The second inference rule *priv* states that whenever an exception is raised, the hypervisor is invoked through a hypercall, and the reached state is resulting from the execution of the handler  $H_a$ .

## **Isolation Property**

Guaranteeing spatial isolation means confining each guest to manage only the partition of memory assigned to its uses. All partitions assigned to guests are statically defined. In general, no security property can be ensured if the starting state of the TLS is inconsistent with the security property itself. Therefore, a system invariant is defined  $I\langle\sigma,\eta\rangle$  to constrain the set of consistent initial states of TLS. In addition, a set  $Q_I$  of all the TLS states satisfying the system invariant is introduced.

The system invariant  $I\langle \sigma, \eta \rangle$ , consists of two predicates: RC and TC. RCensures soundness of the reference counters tracked by pgrefs, and TC guarantees that the state  $\sigma$  is well typed according to pgtype. The reference counter is sound  $(RC(\langle \sigma, \eta \rangle))$ , if for every physical block b, the reference counter pgrefs(b) is equal to  $\sum_{i \in \{0...2^{20}\}} count(\sigma, \eta, b, i)$ , where count is a function that counts the number of references to the block b, according to the reference counter policy. A system state is sound  $(TC(\langle \sigma, \eta \rangle))$ , if the MMU is enabled, the current master L1 page table is inside a physical block of type L1 and each physical block b of type different from data  $(pgtybe(b) \neq D)$ , contains a sound page table  $(sound(\sigma, \eta, b))$ . The predicate sound ensures, among other things that: (1) the page table grants writable access in user mode to blocks outside the guest partition and (3) each page table entry using a second-level page table points to a physical block typed L2 (See [12] for more details).

The security properties that are ensured by the Prosper hypervisor are stated by three theorems.

**Theorem 1.** Let  $\langle \sigma, \eta \rangle \in Q_I$  and  $i \in \{0, 1\}$ . If  $\langle \sigma, \eta \rangle \rightarrow_i \langle \sigma', \eta' \rangle$  then  $\langle \sigma', \eta' \rangle \in Q_I$ .

Theorem 1 states that, starting from a consistent state, an arbitrary TLS transition ends in a consistent state.

The hypervisor guarantees also data separation properties. In order to introduce theorems regarding these properties, some concepts related to *state observations* are needed. The observation of a guest in a state  $(\langle \sigma, \eta \rangle)$  is represented by the structure  $O_g(\langle \sigma, \eta \rangle) = \langle uregs, cpsr, mem_g, coregs \rangle$  of user registers *uregsg*, control register *cpsr*, guest memory *mem\_g* and coprocessor registers *coregs*. The register *cpsr* and the coprocessor registers are visible to the guest since they directly affect the guest behaviour, and do not contain any information the guest should not be allowed to see, even if all writes to the coprocessor registers must be mediated by the hypervisor. The remaining part of the state (i.e. the content of the memory locations that are not part of the guest memory or the special registers) and, again, the coprocessor registers constitute the secure observations  $O_s(\langle \sigma, \eta \rangle)$  of the state, which guest transitions are not supposed to affect.

Data separation properties are expressed through the following two theorems:

**Theorem 2.** Let  $\langle \sigma, \eta \rangle \in Q_I$ , If  $\langle \sigma, \eta \rangle \to_0 \langle \sigma', \eta' \rangle$ , then  $O_s(\langle \sigma, \eta \rangle) = O_s(\langle \sigma', \eta' \rangle)$

Theorem 2 states the *non-exfiltration* property. This guarantees that a transition executed by the guest does not modify the secure resources.

**Theorem 3.** Let  $\langle \sigma_1, \eta_1 \rangle$ ,  $\langle \sigma_2, \eta_2 \rangle \in Q_I$  and assume that  $O_g(\langle \sigma_1, \eta_1 \rangle) = O_g(\langle \sigma_2, \eta_2 \rangle)$ . If  $\langle \sigma_1, \eta_1 \rangle \to_0 \langle \sigma'_1, \eta'_1 \rangle$  and  $\langle \sigma_2, \eta_2 \rangle \to_0 \langle \sigma'_2, \eta'_2 \rangle$ , then  $O_g(\langle \sigma'_1, \eta'_1 \rangle) = O_g(\langle \sigma'_2, \eta'_2 \rangle)$

Theorem 3 states the *non-infiltration* property that is a non-interference property. Namely, a transition executed by the guest depends only on its observations.

All theorems 1, 2 and 3 are satisfied by the Prosper hypervisor. This is formally proved in HOL4 theorem prover, based on the hypervisor TLS definition in the HOL4, and on the HOL4 model of the ARM architecture that is developed at Cambridge [16].

## 2.3 Automated Theorem Proving

The goal of Automated Theorem Proving (ATP) is to prove automatically that a given statement expressed as a theorem follows logically from a set of hypothesis expressed as axioms and inference rules. The ATP deals with the development of computer programs that automatizes the process of proving that the theorem is a logical consequence of the hypothesis.

ATP can be applied to several domains, for example in mathematics it helps in proving a conjecture given a set of assumptions. In computer science ATP is used in artificial intelligence as a tool for the automated reasoning. ATP is also a formal method for the software and hardware verification. In the area of formal verification, ATP deals with the development of formal models that specify mathematically a given system, and the proof of correctness of these models with respect to a specified requirement or property. The mathematical model is expressed as *formulae* of a logic, and the property to verify is the theorem to be proved as a logical consequence of these formulae.

There are many theorem provers that support the process of proving automatically a theorem. A theorem prover provides a logical system with a set of axioms, theorems and inference rules that supports a user in writing a theorem's proof. The logic provided by a theorem prover can be for example a simple propositional logic, a temporal logic, a first-order logic or a higher-order logic.

A fundamental part of this work consists of the formal verification of a security module that is run as a guest of the Prosper hypervisor. The formal verification is assisted by the HOL4 theorem prover [17] that supports a higher-order logic.

## 2.3.1 The HOL4 thorem prover

The HOL4 is an ML-based environment supporting both specification and formal proofs in *higher order logic* [17]. The interactive environment of HOL4 allows to build new theories or to simply write personalized procedure of verification, using an ensemble of automated reasoning tools that are freely available. In the following paragraphs we introduce a few concepts related to the HOL4 logic, and we briefly discuss how a proof can be supported by the HOL4 theorem prover, the reader if interested can see [17] for more details.

#### The HOL4 Logic

The HOL4 system supports a higher order logic, that is a version of predicate calculus extended by two additional aspects:

- Logical variables can also range over functions and predicate.

- The logic is typed

The HOL4 Logic is essentially Church's Simple Type Theory [30]. It is based on simple types ty, that are used to build typed-lambda calculus terms tm. The HOL4 logic has a set-theoretic semantics. Types denote sets and terms denote members of these sets.

There are four kinds of types in the HOL logic that can be described by the following grammar:

$$ty := \alpha \mid c \mid (ty_1, \dots, ty_n) op_n \mid ty_1 \to ty_2$$

Where  $\alpha$  denotes type variable, c denotes an atomic type (for example the standard atomic type *bool*). A compound type is denoted with  $(ty_1, ..., ty_n)op_n$  where  $(ty_1, ..., ty_n)$  are the argument types and  $op_n$  is a type operator of arity n (for example *prod* is a type operator of arity two which denotes the cartesian product operation). The function type  $ty_1 \rightarrow ty_2$  denotes the set of all functions from the domain set of type  $ty_1$  to the codomain set of type  $ty_2$ .

A term of the HOL4 logic is an expression that denotes an element of the set denoted by the type associated to the term. There are four types of terms in the HOL4 logic that can be described by the following grammar:

$$tm := x \mid c \mid tm1 \ tm2 \mid \lambda x.tm$$

Where x denotes a variable term, c denotes a constant term,  $\lambda x.tm$  denotes a  $\lambda$ -abstraction term, and  $tm1 \ tm2$  denotes the function application term.

The interface to the HOL4 logic is the functional programming language ML. Terms of the HOL4 logic are represented in ML by an *abstract data type* called **term**, and they are introduced between double back-quote marks. The ML parser for HOL4's terms include an inference type checker that is able to assign a type to each well-formed term. A term is well-formed if it can be derived according to the logic syntax.

The logic of HOL4 is implemented by a small kernel, that includes the initial signature, the primitive rules of inference, the axioms and the primitive definition principles of the logic. These principles allow the extension of the logic in a consistency-preserving way.

# Proving with HOL4

A formal proof can be seen as a sequence of steps, each one consists of the application of an axiom or an inference rule. The last element of the proof is the theorem. In HOL4 theorems are represented as values of an abstract type *thm*. The only way to create a theorem is by providing a proof. This follows from the application of ML functions that represent inference rules to axioms or to previously computed theorems.

There are two methodologies that are supported by HOL4 for performing an interactive proof: the forward methodology and the goal oriented methodology.

The forward methodology Based on the forward methodology, the proof starts from the appropriate axioms, and through the application of the right inference rules, the theorem to be proved is reached as result at the end of the proof. A forward proof requires the selection of the axioms and the inference rules to be used before starting the interactive proof. Also the order of the application of axioms and rules must be decided. The knowledge requirement of all the proof steps in advance makes the forward methodology not easy to conduct in many cases.

The goal oriented methodology In the goal oriented methodology, a proof is called backward proof and it is the the reverse of the forward proof. This methodology is based on the concept of *tactic*, proposed by Robin Milner in 1970. A tactic is a function that splits a *goal* into *subgoals*, recording at the same time the reason that makes the goal solved once all subgoals are proved. A goal oriented proof starts with the main theorem to be proved, and proceeds by specifying a tactic that splits the main goal into subgoals. The intuition is that a subgoal can be easier to solve compared with the main goal, for example by matching an axiom, or with an automated reasoner provided by the HOL4 system.

A goal in HOL4 is a pair  $([t_1, ..., t_n], t)$  where the first component contains a term list representing the assumptions, whereas the second component contains the term goal. The achievement of solving the goal results in a theorem. A tactic is an ML function that applied to a goal generates subgoals and a *validation* that is a justification function of why solving the subgoals is a solution of the goal represented by t. The validation is basically an ML function representing the inference rule that allows to derive the main goal from the subgoals.

The HOL4 theorem prover provides many automatic reasoners and proof assistants that support the user during an interactive proof. These are organized as tactics or as procedures. The user can also write personalized procedures and tactic for its own proofs.

# The HOL4 theories

A HOL4 theory is a collection of valid HOL4 term definition, axioms and theorems. A theory can be loaded during an interactive session and used in a proof. Several mathematical concepts and models are defined and provided to users as theories. The Prosper hypervisor model is provided as a theory hypervisor\_modelTheory.

# Chapter 3

# Runtime monitoring for Prosper

This chapter presents the main contribution of the thesis, namely the definition of a validation mechanism for a security property guaranteeing protection against code injection attacks, and the proof of correctness of the validation mechanism based on assumptions on the underlying architecture, that exploits the Prosper hypervisor and the isolation property that it guarantees in a virtualization context.

The next section describes more in details the motivations already sketched in the Introduction, and provides an outline of the rest of the chapter.

# **3.1** Motivations and Goals

Runtime monitoring is a computing system analysis technique based on the observation of a running system and the consequent reaction in case of violation of certain security properties. The main goal of a runtime monitor is to ensure a security property preventing incorrect system states. Runtime monitoring is employed whenever a static analysis of the system behaviour against a security property is infeasible.

One of the most common applications of runtime monitoring, that is also in the focus of this thesis, is on Operating Systems. An OS is responsible for managing the computer system resources (files, memory, devices, etc). This management includes the allocation of a resource to the different user applications and its pro-

tection from unauthorized accesses through an appropriate access control policy.

A common approach is to realize the access control policy with a runtime monitor that controls all the accesses to the resource. This is achieved deploying the runtime monitor as a kernel security module. The kernel is usually explicitly developed to support this security module. In fact, whenever a critical operation is going to be performed by the kernel, the security module is explicitly informed. The Linux Security Module (LSM) [33] is an example of a runtime monitor for the Linux kernel that supports and provides access control security policies. The basic abstraction of the LSM interface is to mediate all the accesses to the internal kernel objects. The LSM is invoked each time the Linux kernel would have access to a system resource.

# Vulnerabilities in LSM approach

The standard approach of deploying a runtime monitor to protect a system resource as a kernel component has some vulnerabilities. This is mainly due to the kernel's complexity. In fact, the complexity of the kernels makes them susceptible to attacks [25] [9] that can bypass the security policy of the monitor. The design of the LSM allows the security module to mediate the accesses to a kernel object by placing *hooks* at every point of the kernel code where a user system call is about to result in an access to a kernel object. The hook is basically a call to a function provided by the module that implements the protection mechanisms. A malicious program, for example a rootkit that enables privileged access, can disable the mediation of the LSM or even modify the function invoked by a hook.

# Provably secure runtime monitor

In general, having a formal proof of correctness of a security critical component enhances the security level of the whole computing system. An OS runtime monitor that protects a system resource from malicious access is certainly a security critical part of the system. Therefore, it is desirable to provide a tamper-resistant and trustworthy runtime monitor. The trustworthiness can be significantly improved if a formal verification of the monitor's security policy against the desired security property can be performed. The tamper-resistance is possible only if the runtime monitor is itself protected from malicious manipulations. The approach of including a runtime monitor as a kernel security module introduces difficulties in achieving both the trustworthiness and the tamper-resistance of a security module. In fact, it's well known that the OS size and complexity make a formal proof of a kernel module correctness very hard. Also, the OS vulnerability against malicious intrusions prevents from providing a complete tamper-resistant kernel module.

# Exploiting virtualization

One of the advantages of the virtualization technology discussed in Section 2.1.3 is the *isolation*. This property allows several software guests to execute in separated and protected partitions without interferences. This property can be strongly related to the tamper-resistance requirement of a runtime security module. For example, a security module running as a guest of a Virtual Machine Monitor can benefit from the isolation property provided by the VMM. Moreover, a direct interaction between the VMM and the security module can allow the runtime monitoring of the guests without affecting the security module integrity.

An additional advantage of the virtualization consists of a minimal trusted computing base (TCB) of the virtualized system. This property is related to the trustworthiness requirement of a runtime security module (that is part of the TCB). In fact a minimal trusted computing base is more suitable for a formal verification.

# Goals

Given the motivations discussed above, a valuable idea for the Prosper project [3] is to introduce a security module that monitors the system guest of the hypervisor and that takes advantage from the virtualization benefits ensured by the hypervisor. In the following, we will refer to this security module as the Prosper (runtime) monitor or simply as the monitor.

The first goal consists of giving the general design choices for the Prosper runtime monitor in order to meet the motivations stated above (the design choices are discussed in Section 3.2.1). These choices take into account the infrastructure provided by the Propser hypervisor (the hypervisor is presented in Section 2.2.3). In particular, a desirable feature of the Prosper runtime monitor is to take advantage from the isolation property and the virtualization mechanism provided by the hypervisor. The second goal consists in analysing, in general, what kind of security properties can be provided by the Prosper runtime monitor. The third goal is the identification of an application for the Prosper runtime monitor. This is done through the identification of a security property, and an appropriate policy, to be enforced in order to protect the Linux kernel guest from code injection attacks (the second and the third goals are treated by Sections 3.2.2 and 3.2.3). The fourth goal consists in providing a formal proof of correctness for the Prosper runtime monitor. In particular, we would like to formally prove that the policy identified is able to ensure the desired security property. The formal proof is presented in Section 3.3 and it has been verified with the support of the HOL4 proof assistant as reported in Chapter 4.

# 3.2 The Prosper runtime monitor

The Prosper hypervisor [3] [11] [20] [12] [14] is a Virtual Machine Monitor and it satisfies the three properties of a VMM discussed in 2.1.1. In particular, the hypervisor has the complete control of the system resources. Therefore, a monitor that needs to enforce a security property over a system resource can be designed as a hypervisor module. This approach has the advantage of simplifying both the detection of the security critical operations and the monitor mediation on these operations. However, having an additional module of the hypervisor has the inconvenience of increasing the complexity and size of the hypervisor. This violates the requirement of keeping a minimal VMM and a minimized trusted computing base (TCB). Therefore, the approach of deploying the runtime monitor as a hypervisor module suffers from some vulnerabilities that are detected in the LSM approach.

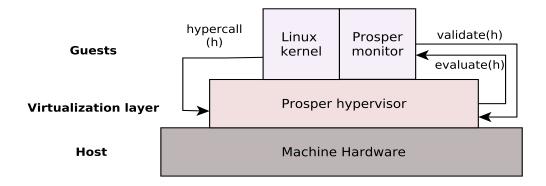

One possible alternative approach is to deploy the runtime monitor module as a guest of the Prosper hypervisor. Using a dedicated module on top of the hypervisor permits to decouple the enforcement of the security properties from the other hypervisor functionalities. This choice has mainly two benefits: first, it is possible to maintain a minimal trusted computing base. Second, having the security policy wrapped inside a guest enhances both the tamper-resistance and the trustworthiness of the monitor. In fact, if the monitor runs as a guest, it can take advantage from the isolation properties provided by the hypervisor. This choice

Figure 3.1: System setting