Energy-Efficient Digital Circuit Design using Threshold Logic Gates

by

Niranjan Kulkarni

## A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved November 2015 by the Graduate Supervisory Committee:

Sarma Vrudhula, Chair Charles Colbourn Jae-Sun Seo Shimeng Yu

ARIZONA STATE UNIVERSITY

December 2015

#### ABSTRACT

Improving energy efficiency has always been the prime objective of the custom and automated digital circuit design techniques. As a result, a multitude of methods to reduce power without sacrificing performance have been proposed. However, as the field of design automation has matured over the last few decades, there have been no new automated design techniques, that can provide considerable improvements in circuit power, leakage and area. Although emerging nano-devices are expected to replace the existing MOSFET devices, they are far from being as mature as semiconductor devices and their full potential and promises are many years away from being practical.

The research described in this dissertation consists of four main parts. First is a new circuit architecture of a differential threshold logic flipflop called PNAND. The PNAND gate is an edge-triggered multi-input sequential cell whose next state function is a threshold function of its inputs. Second a new approach, called hybridization, that replaces flipflops and parts of their logic cones with PNAND cells is described. The resulting *hybrid* circuit, which consists of conventional logic cells and PNANDs, is shown to have significantly less power consumption, smaller area, less standby power and less power variation.

Third, a new architecture of a field programmable array, called field programmable threshold logic array (FPTLA), in which the standard lookup table (LUT) is replaced by a PNAND is described. The FPTLA is shown to have as much as 50% lower energydelay product compared to conventional FPGA using well known FPGA modeling tool called VPR.

Fourth, a novel clock skewing technique that makes use of the *completion detection* feature of the differential mode flipflops is described. This clock skewing method improves the area and power of the ASIC circuits by increasing slack on timing paths.

An additional advantage of this method is the *elimination* of hold time violation on given short paths.

Several circuit design methodologies such as retiming and asynchronous circuit design can use the proposed threshold logic gate effectively. Therefore, the use of threshold logic flipflops in conventional design methodologies opens new avenues of research towards more energy-efficient circuits.

# DEDICATION

To my parents

who always encouraged and supported me throughout this endeavor

To my wife, Neha

without whose continued support this dissertation would not have been possible

#### ACKNOWLEDGMENTS

I would like to thank my adviser, Prof. Sarma Vrudhula, for having faith in my abilities, and for all his guidance through the years. Despite several frustrating times, he helped me keep moving with moral and intellectual support and for that I am deeply indebted to him. My sincere thanks to my committee members as well, for taking the time to review my work, attending my presentations, and offering many helpful suggestions.

I am fortunate to have collaborated with Tejaswi Gowda, who first got me interested in the field of threshold logic. I am thankful to many other colleagues who became my friends, who were there for me when I needed them and for making the otherwise grim workplace a whole lot more fun and cheerful. My special thanks to Jinghua Yang and Joseph Davis, without their collaboration, this work would not have been complete.

My family has always been a constant source of encouragement and support through these long years. I am grateful for their trust in me, and for everything they have done for me.

I gratefully acknowledge the support I received from the following agencies: The Stardust Foundation through a Science Foundation Arizona grant SRG 0211-01; The National Science Foundation for grants 1230401, 0702831 and PFI-BIC 1237856. I would also like to thank the School of Computing, Informatics and Decision Systems Engineering for granting me with necessary resources in a timely manner.

| TABLE OF | CONTENTS |

|----------|----------|

|----------|----------|

|      |      | Pa                                                        |

|------|------|-----------------------------------------------------------|

| LIST | OF 7 | TABLES                                                    |

| LIST | OF I | FIGURES                                                   |

| CHA  | PTEF | {                                                         |

| 1    | INT  | RODUCTION                                                 |

| 2    | BAG  | CKGROUND 1                                                |

|      | 2.1  | Necessity for Low Power                                   |

|      | 2.2  | Dynamic Power Reduction Methods                           |

|      | 2.3  | Static Power Reduction Methods                            |

|      | 2.4  | Threshold Logic: A New Approach                           |

|      | 2.5  | Threshold Logic Gates                                     |

|      | 2.6  | Synthesis and Mapping using Threshold Logic               |

|      | 2.7  | Threshold Logic in Field Programmable Environment         |

| 3    | THI  | RESHOLD LOGIC FLIPFLOP                                    |

|      | 3.1  | Architecture                                              |

|      | 3.2  | Asynchronous Preset, Clear and Scan implementations       |

|      | 3.3  | Threshold Functions Realized by a PNAND                   |

|      | 3.4  | PNAND Delay Characteristics 3                             |

|      | 3.5  | Robustness 3                                              |

|      |      | 3.5.1 Comparison with TLL                                 |

|      | 3.6  | PNAND-1 (KVFF) Design                                     |

|      |      | 3.6.1 Scan & Asynchronous Preset and Clear Architecture 4 |

| 4    | TEC  | CHNOLOGY MAPPING WITH THRESHOLD GATES                     |

|      | 4.1  | PNAND vs Conventional Circuits                            |

|      | 4.2  | BDD Based Decomposition using Cut Enumeration 5           |

|   |     | 4.2.1  | Enumeration of Cuts                      | 55 |

|---|-----|--------|------------------------------------------|----|

|   |     | 4.2.2  | Threshold Decomposition                  | 57 |

|   |     | 4.2.3  | Necessary Conditions                     | 60 |

|   |     | 4.2.4  | Threshold Decomposition Heuristic        | 61 |

|   | 4.3 | ILP B  | ased Decomposition                       | 64 |

|   |     | 4.3.1  | 0-1 ILP formulation                      | 65 |

|   |     | 4.3.2  | Speeding up the 0-1 ILP                  | 68 |

|   |     | 4.3.3  | Unate Function Enumeration               | 69 |

|   |     | 4.3.4  | Hybridization Procedure                  | 70 |

|   | 4.4 | Exper  | imental Results                          | 72 |

|   |     | 4.4.1  | Methodology                              | 72 |

|   |     | 4.4.2  | Circuits                                 | 74 |

|   |     | 4.4.3  | Results                                  | 74 |

|   |     | 4.4.4  | Advantages due to KVFF                   | 77 |

| 5 | FIE | LD PRO | OGRAMMABLE THRESHOLD GATE ARRAY          | 83 |

|   | 5.1 | Overv  | iew                                      | 83 |

|   | 5.2 | PNAN   | ID as a Majority Gate                    | 85 |

|   | 5.3 | FPTL   | A Architecture                           | 88 |

|   | 5.4 | Synthe | esis of Nanopipelined Threshold Networks | 90 |

|   |     | 5.4.1  | Area Minimization Algorithm              | 91 |

|   |     | 5.4.2  | Buffer Insertion                         | 93 |

|   | 5.5 | Robus  | tness and Temperature Monotonicity       | 95 |

|   |     | 5.5.1  | Temperature Monotonicity                 | 96 |

|   | 5.6 | Exper  | imental Results                          | 97 |

|   |     | 5.6.1  | Parameters for VPR                                   | 98  |

|---|-----|--------|------------------------------------------------------|-----|

|   |     | 5.6.2  | Circuit Comparison Results                           | 99  |

|   |     | 5.6.3  | Leakage Power and Glitching1                         | 01  |

|   |     | 5.6.4  | Circuit Yield1                                       | .03 |

| 6 | NEV | V CLO  | CK SKEWING STRATEGY 1                                | .09 |

|   | 6.1 | Introd | uction1                                              | .09 |

|   |     | 6.1.1  | Overview of Clock Skewing1                           | 09  |

|   |     | 6.1.2  | KVFF with Completion Detection1                      | 13  |

|   |     | 6.1.3  | Clock Skewing using KVFF with Completion Detection 1 | 14  |

|   | 6.2 | Optim  | al Clock Assignment1                                 | 16  |

|   |     | 6.2.1  | Notations1                                           | 16  |

|   |     | 6.2.2  | ILP Formulation1                                     | 17  |

|   | 6.3 | Exper  | imental Results1                                     | 22  |

|   |     | 6.3.1  | Duty Cycle Considerations1                           | 24  |

|   |     | 6.3.2  | Elimination of Hold Violations1                      | 25  |

|   |     | 6.3.3  | Power-on Initialization1                             | 25  |

| 7 | FUI | TURE V | WORK                                                 | 29  |

|   | 7.1 | Retim  | ing1                                                 | 29  |

|   |     | 7.1.1  | Retiming for Minimum Clock Period1                   | 29  |

|   |     | 7.1.2  | Retiming for Minimum Area1                           | 31  |

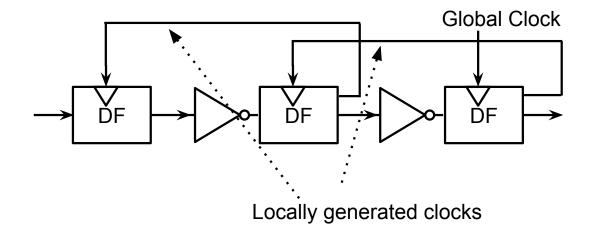

|   | 7.2 | Novel  | Clock Distribution                                   | 32  |

|   | 7.3 | Async  | hronous Circuit Design1                              | 33  |

|   |     | 7.3.1  | Dual Rail Circuits1                                  | 33  |

|      |      | 7.3.2  | Comparison with CMOS based Asynchronous Implementa-      |       |

|------|------|--------|----------------------------------------------------------|-------|

|      |      |        | tions                                                    | . 136 |

|      |      | 7.3.3  | Relaxing Delay Insensitivity                             | . 140 |

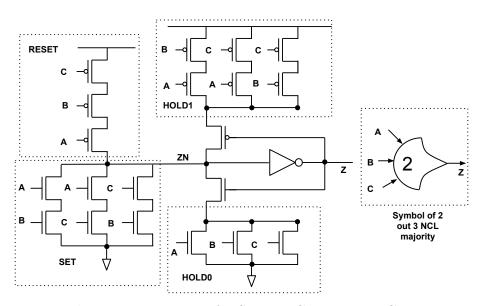

|      |      | 7.3.4  | Comparison with Null Convention Logic                    | . 140 |

|      |      | 7.3.5  | Implementing DI Primitive using PNANDs                   | . 145 |

|      |      | 7.3.6  | Implementing DI Primitive using NCL Majorities           | . 147 |

|      | 7.4  | Novel  | Scanning Mechanism                                       | . 149 |

|      |      | 7.4.1  | Flipflop Architecture                                    | . 150 |

|      |      | 7.4.2  | Proposed Scan Architecture                               | . 152 |

|      |      | 7.4.3  | Scan Chain Operation                                     | . 152 |

|      |      | 7.4.4  | Advantages of the Proposed Scan Mechanism                | . 155 |

|      |      | 7.4.5  | Flipflop Implementation                                  | . 156 |

| REFE | EREN | CES    |                                                          | . 158 |

| APPE | ENDE | X      |                                                          |       |

| А    | CUI  | Γ ENUI | MERATION                                                 | . 167 |

|      | A.1  | Introd | uction                                                   | . 168 |

|      | A.2  | Relate | ed Work                                                  | . 171 |

|      | A.3  | Strong | g line cuts                                              | . 172 |

|      |      | A.3.1  | Relationship between Unidirectional Node Cuts and Strong |       |

|      |      |        | Line Cuts                                                | . 173 |

|      | A.4  | Cut er | numeration                                               | . 175 |

|      |      | A.4.1  | MIS Pruning                                              | . 175 |

|      |      | A.4.2  | Enumerating MISs                                         | . 178 |

|      |      | A.4.3  | Results                                                  | . 178 |

# LIST OF TABLES

| Table | Page                                                                                    |

|-------|-----------------------------------------------------------------------------------------|

| 3.1   | Functions Realized by PNAND-K, for $K = 3, 5, 7, 9 \dots 36$                            |

| 3.2   | A Bad Signal Assignment for $f(a, b, c) = a \lor bc$ Denoted by $a + 2b + 2c > bc$      |

|       | $3 - 3a \rightarrow (a', b', c', c' a, a, a, 1, 1) \dots 39$                            |

| 3.3   | A Good Signal Assignment for $f(a, b, c) = a \lor bc$ Denoted by $3a + b + c > bc$      |

|       | $3 - a - b - c \rightarrow (a', a', a', b', c' a, b, c, 1, 1)$                          |

| 3.4   | Delays of PNAND-K w/wo Scan, Relative to D-FF in $65 \text{nm}$ LP process.             |

|       | Layout Extracted Netlist Simulated at $PVT = SS/1.1V/105^{\circ}C/$ , Input             |

|       | and Clock slews = $70$ ps, Output Load = $20$ fF 40                                     |

| 3.5   | Delay Distribution of Layout Extracted D-FF and PNAND Cells Sub-                        |

|       | ject to Global Variations and Local Mismatch in 100,000 Monte-Carlo                     |

|       | Trials                                                                                  |

| 3.6   | 65nm Technology Comparison of Clock-to-Q delay Across Process Vari-                     |

|       | ations. The Simulation Corner is Statistical at $0.8\mathrm{V}$ and $-40\mathrm{C}$ for |

|       | 100,000 Monte-Carlo Trials. All Delays in Picoseconds 49                                |

| 3.7   | 65nm Technology Design Comparison. The Simulation Corner is Slow/slow,                  |

|       | 1.1V VDD and $105^{\circ}C$ . The Load Cap is $20fF$ . Signal Transition Times          |

|       | are $70ps$ . Identical Drive Strengths were used for the Flipflops                      |

| 3.8   | 65nm Technology Comparison of Flipflop Characteristics. The Load                        |

|       | Cap is $20 f F$ . All Input Signal Slews are $5 ps$ . Identical Drive Strengths         |

|       | used for all the Flipflops 50                                                           |

| 4.1   | Comparison of PNAND with Conventional Standard Cell Implemen-                           |

|       | tation of Circuit Shown in Figure 4.2 (at SS, $105^{\circ}$ C, $1.1$ V) 54              |

| 4.2   | Area and Wire-length Reduction                                                          |

| 4.3 | Dynamic and Leakage Power Reduction @ TT, 25°C, 1.2V and 30%                 |

|-----|------------------------------------------------------------------------------|

|     | Switching Activity                                                           |

| 4.4 | Variation in the Dynamic Power                                               |

| 4.5 | Dynamic and Leakage power reduction @ TT, 25°C, 1.2V and $30\%$              |

|     | Switching Activity due to KVFF                                               |

| 5.1 | Threshold Functions Implementable by $4/7$ Majority                          |

| 5.2 | CLB and DTGB Properties Measured using Detailed SPICE Models                 |

|     | (supply = 1.2V)                                                              |

| 5.3 | FPGA and FPTLA Circuit Results at Fixed 1.2V Supply with LUT-4 . $106$       |

| 5.4 | FPGA and FPTLA Circuit Results at Fixed 1.2V Supply with LUT-6 . $107$       |

| 5.5 | Redundancy $m$ to be Added for Each Circuit                                  |

| 6.1 | Advantages of Local Clocking for the Circuit from Fig. 6.4 @ TT,1.2V,25C115  |

| 6.2 | Improvements due to Local Clocking Compared to the Conventional              |

|     | Globally Clocked CMOS Versions of 28-bit FIR Filter and 32-bit MIPS 123      |

| 6.3 | Dynamic Power (mW) Improvements due to Local Clocking, Post-                 |

|     | layout @ TT, 1.2V, 25C 124                                                   |

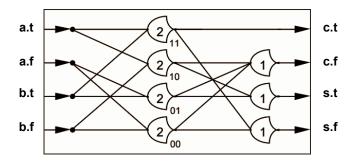

| 7.1 | Logic Values of Signal $x$ Represented using Dual Signals $x.f$ and $x.t133$ |

| 7.2 | Number of Transistors Required to Implement Dual-rail DI Implemen-           |

|     | tations                                                                      |

| 7.3 | Number of Transistors Required to Implement Dual-rail Function as a          |

|     | Single Gate                                                                  |

| 7.4 | Logic Values of Output Q151                                                  |

| A.1 | Running Times for Enumeration                                                |

# LIST OF FIGURES

| Figure | P                                                                                | age |

|--------|----------------------------------------------------------------------------------|-----|

| 1.1    | Power Reduction Techniques                                                       | 2   |

| 3.1    | PNAND Cell Design                                                                | 25  |

| 3.2    | Importance of Feedback Transistors in the Input Networks of PNAND .              | 28  |

| 3.3    | PNAND Cell Design with Asynchronous Set and Reset                                | 29  |

| 3.4    | PNAND Cell Design with Scan                                                      | 30  |

| 3.5    | Operation of a Scan Chain Consisting of Four PNAND-9 Cells                       | 31  |

| 3.6    | KVFF Architecture                                                                | 44  |

| 3.7    | KVFF Architecture with Asynchronous Preset and Clear                             | 46  |

| 3.8    | Differential Mode Strong Arm Flipflop Architecture                               | 49  |

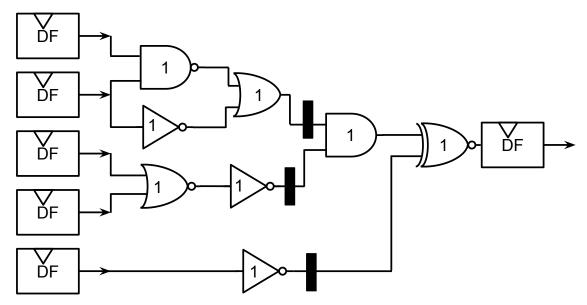

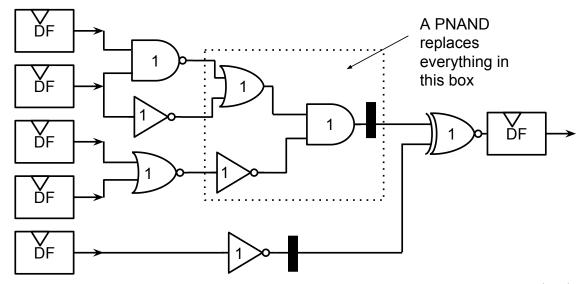

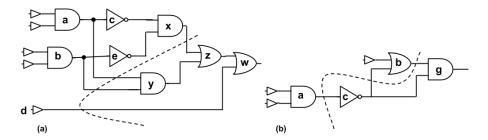

| 4.1    | Subcircuits Replaceable by a Single PNAND Cell                                   | 52  |

| 4.2    | Comparison of PNAND with Functionally Equivalent Network of Stan-                |     |

|        | dard Cells                                                                       | 53  |

| 4.3    | Comparison of Leakage of PNAND with Functionally Equivalent Net-                 |     |

|        | work of Standard Cells                                                           | 54  |

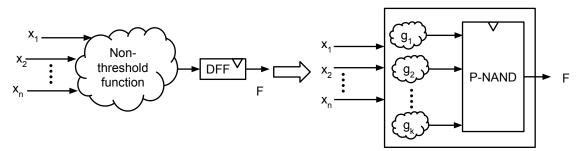

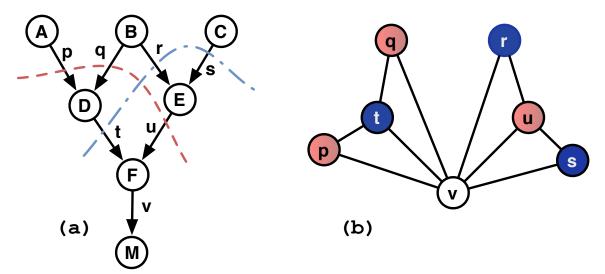

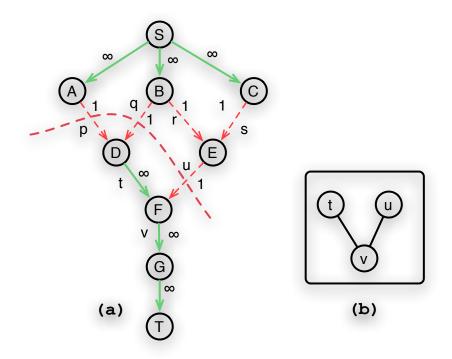

| 4.4    | Decomposition of a Nonthreshold Function w.r.t a Threshold Function .            | 55  |

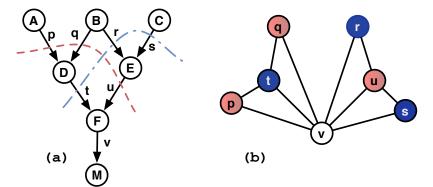

| 4.5    | a) DAG with Strong Cuts Annotated. b) Corresponding Maximal In-                  |     |

|        | dependent Sets in LDG                                                            | 56  |

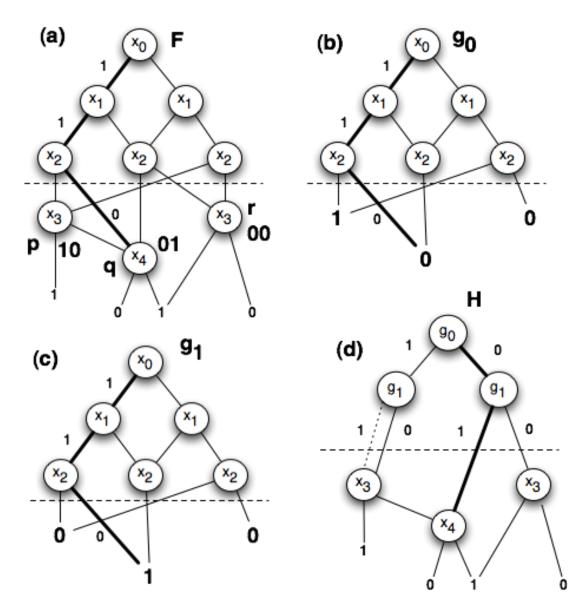

| 4.6    | (a) Function F to be Decomposed. (b),<br>(c) g-functions (d) H-function $\ldots$ | 79  |

| 4.7    | An Example of Threshold Decomposition (a) Non-threshold Input Func-              |     |

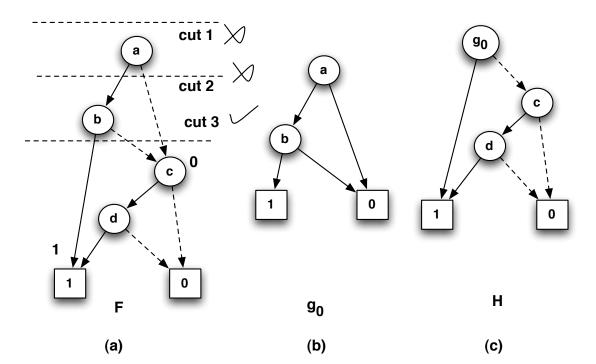

|        | tion F and Cut (b) Computation of $g_0$ (c) H-function                           | 80  |

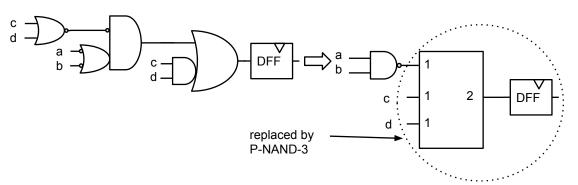

| 4.8    | A Motivational Example where a Non-threshold Function is Decom-                  |     |

|        | posed into a PNAND-3 Driven by a Single NAND Gate                                | 80  |

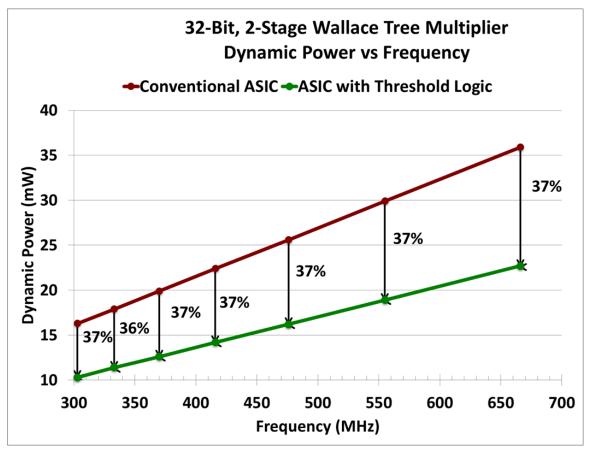

| 4.9    | Advantages of Hybrid Circuits are Maintained Irrespective of the Op-             |     |

|        | erating Frequency                                                                | 81  |

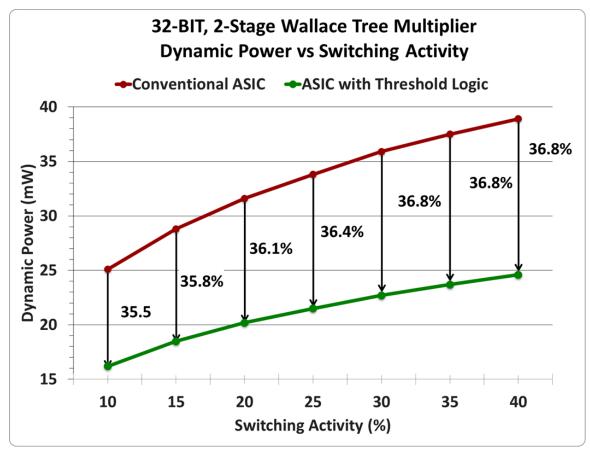

# Figure

| 4.10 | Hybrid Circuits are More Energy-efficient at Higher Switching Activity 82 |

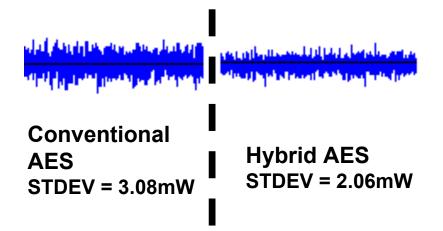

|------|---------------------------------------------------------------------------|

| 4.11 | Variations in Dynamic Power of AES Circuit                                |

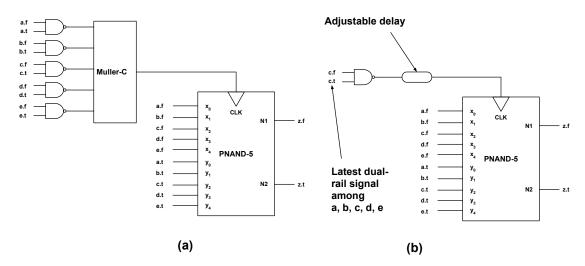

| 5.1  | Realizing a 3 out of 5 Majority using PNAND-5 86                          |

| 5.2  | A PNAND Gate Array                                                        |

| 5.3  | (a) Legal Function Substitution (b) Illegal Function Substitution Lead-   |

|      | ing to a Non-threshold Function                                           |

| 5.4  | Monotonicity of Temperature                                               |

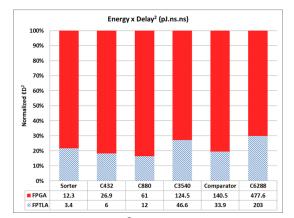

| 5.5  | Comparison of $ED^2$ between FPGA and FPTLA Circuits                      |

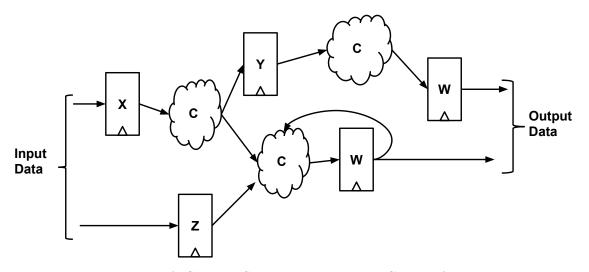

| 6.1  | A General Synchronous Digital Circuit Architecture                        |

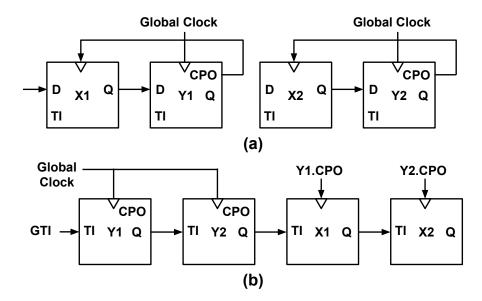

| 6.2  | (a) Clock Skewing Used to Increase Speed of the Circuit (b) Clock         |

|      | Skewing Used to Reduce Number of Flipflops111                             |

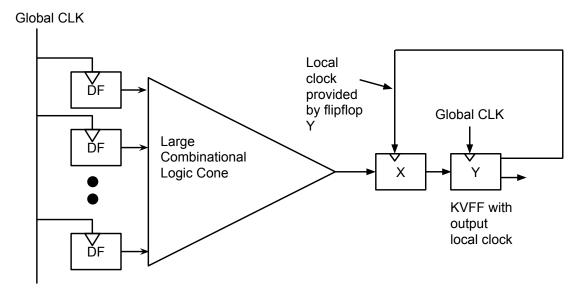

| 6.3  | The KVFF Architecture With Output Local Clock                             |

| 6.4  | A Motivational Example that Exhibits Maximum Advantages due to            |

|      | Local Clocking                                                            |

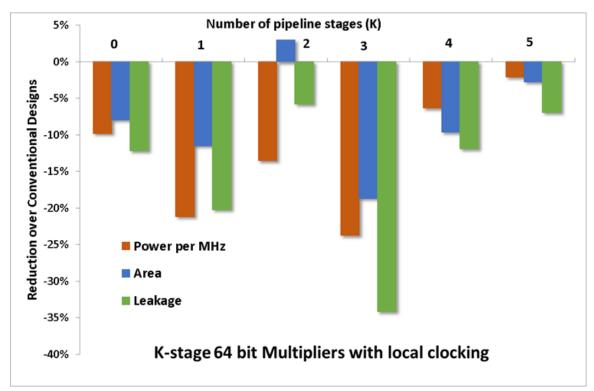

| 6.5  | Improvements due to Local Clocking and KVFF Flipflops in Conven-          |

|      | tional CMOS Circuits                                                      |

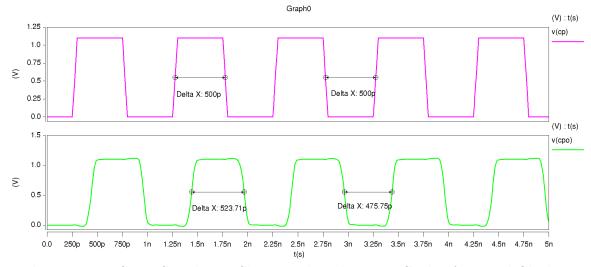

| 6.6  | Spice Simulation Showing that the Duty Cycle of a Local Clock is Near     |

|      | 50%                                                                       |

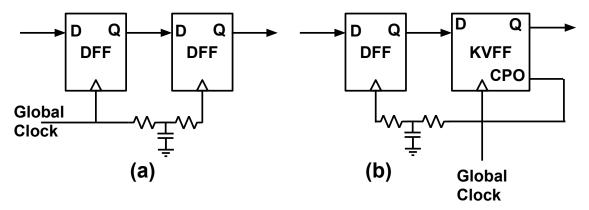

| 6.7  | (a) Regular Flipflops Exhibit Hold Time Violation as RC Delay In-         |

|      | creases (b) No Amount of RC Delay Induces A Hold Time Violation           |

|      | When Local Clocking is Used                                               |

| 6.8  | (a) Two Independent Pairs of Flipflops $(X1,Y1)$ and $(X2,Y2)$ in a Cir-  |

|      | cuit with Possible Initialization Issue (b) Their Positions in a Single   |

|      | Scan Chain to Eliminate Metastability                                     |

xii

Page

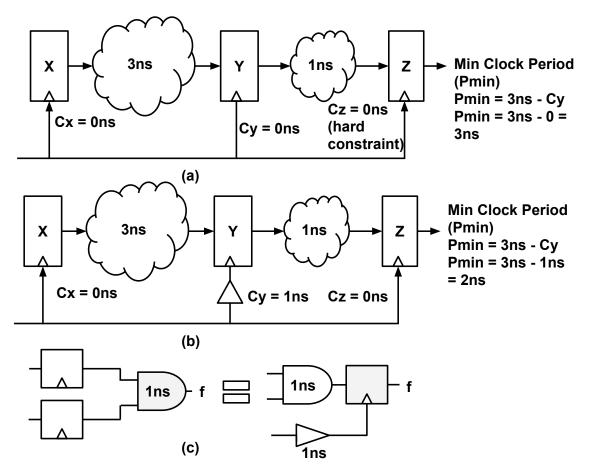

| 7.1  | Retiming for Minimum Delay using Conventional Flipflops Leads to        |

|------|-------------------------------------------------------------------------|

|      | 2ns Clock Period                                                        |

| 7.2  | Retiming for Minimum Delay using PNANDs Leads to Smaller (1ns)          |

|      | Clock Period                                                            |

| 7.3  | A Novel Clocking Distribution using Local Clocks                        |

| 7.4  | PNAND Circuit Abstraction                                               |

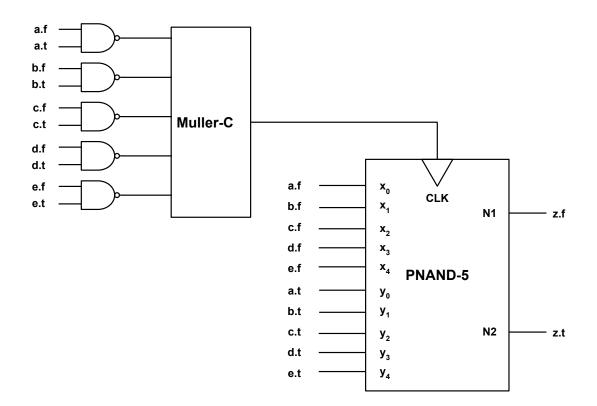

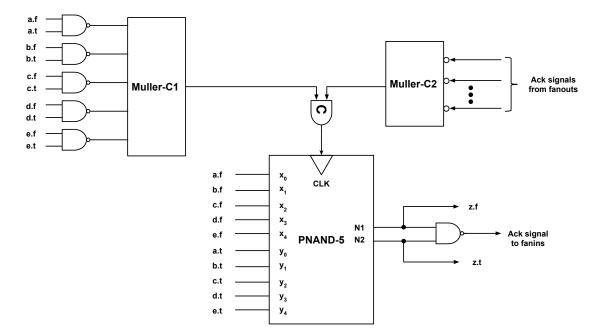

| 7.5  | Implementing Dual-Rail 3 out of 5 Majority Function using PNAND-5.135   |

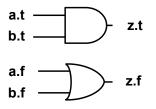

| 7.6  | A Dual Rail AND Gate using CMOS Gates                                   |

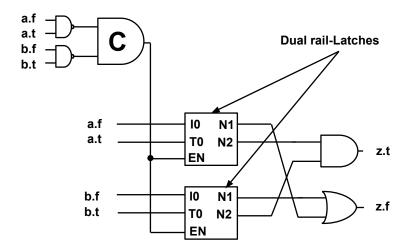

| 7.7  | A Dual Rail AND gate using CMOS Gates and Latches                       |

| 7.8  | A DIM Synthesis of Two Input AND Gate                                   |

| 7.9  | A Dynamic Dual Rail AND Gate                                            |

| 7.10 | (a) Delay-insensitive PNAND Gate (b) Delay-sensitive Gate Triggered     |

|      | Only by the Latest Arriving Signal                                      |

| 7.11 | 2 out of 3 Static NCL Majority Gate                                     |

| 7.12 | Dual Rail Delay Insensitive NCL Half Adder                              |

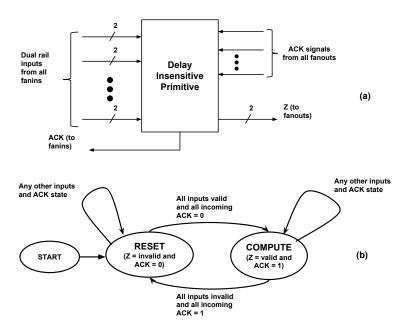

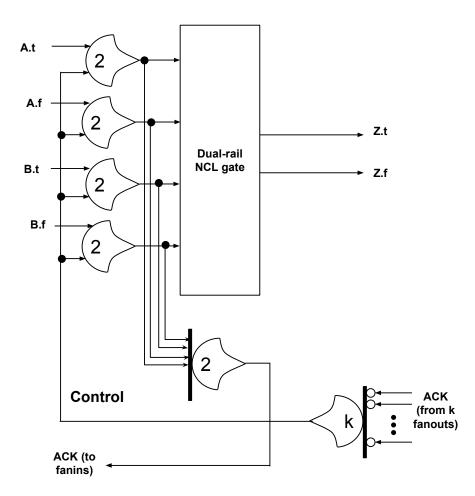

| 7.13 | (a) Generalized Primitive Used to Construct DI Netlist (b) State Tran-  |

|      | sitions for the Primitive                                               |

| 7.14 | Implementation of Generalized DI Primitive using PNAND146               |

| 7.15 | Implementation of Generalized DI Primitive using NCL Majority Gates 148 |

| 7.16 | Flipflop Architecture Required for the Proposed Scan Mechanism150       |

| 7.17 | Implementation of Function $F_{CD}$ from Fig. 7.16                      |

| 7.18 | Proposed Connections to Create Scan-Chain using Flipflop from Fig.      |

|      | 7.16                                                                    |

| 7.19 | A Possible Implementation of the Flipflop Shown in Fig. 7.16            |

# Figure

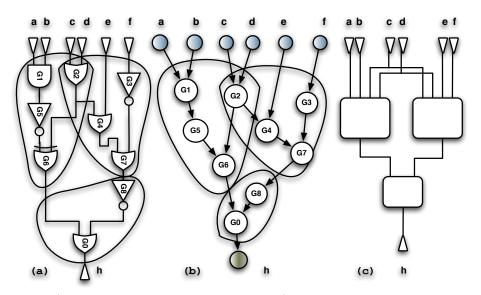

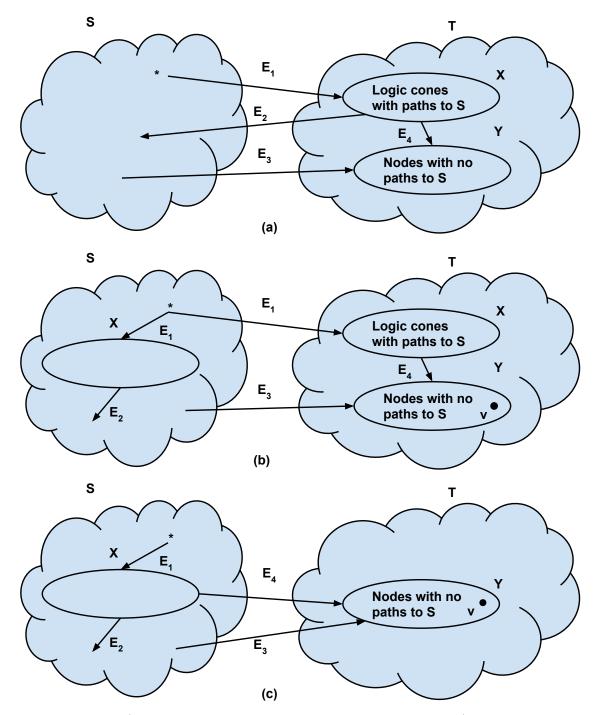

| A.1 | a) A Covered Boolean Network. b) Its Graph Representation. c) The         |

|-----|---------------------------------------------------------------------------|

|     | Network Mapped on the Library Gates                                       |

| A.2 | (a) Unidirectional Node Cut Denoted as $\{a, b, x, d\}$ (b) Bidirectional |

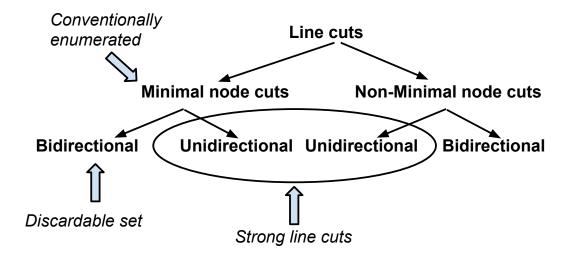

|     | Node Cut Denoted by $\{a, b\}$                                            |

| A.3 | Classification of Cuts and Their Relationships171                         |

| A.4 | a) a DAG with Strong Cuts Annotated. b) The Corresponding Maxi-           |

|     | mal Independent Sets in LDG                                               |

| A.5 | a) Classification of Edges in a Bidirectional Cut b) Replication after    |

|     | TM, (c) Classification of Edges in Corresponding Unidirectional Cut 180   |

| A.6 | a) Formation of $s - t$ Boolean Network for Determination of a Cut        |

|     | Containing Line p. b) LDG from Fig. A.4 Pruned for $k \leq 2$             |

#### Chapter 1

#### INTRODUCTION

Minimizing the area and dynamic power of digital CMOS circuits have always been two central objectives of the automated circuit design. This focus on dynamic power stems from several problems arising from an increased power consumption. First and foremost are thermal constraints. The increased temperature of circuits has several debilitating effects such as reduced speed, increased leakage (wasted power), accelerated aging etc. Reducing power consumption not only alleviates these problems but also reduces packaging and cooling costs (Lin and Banerjee, 2008).

The second requirement for low power comes from limited energy capacity of batteries used to power mobile devices, (Chalmers and Sloman, 1999). As more and more transistors are packed on today's chips, the power requirement starts growing beyond the capabilities of the batteries necessitating energy-efficient designs. Improvements in battery technology to increase their capacity have not kept pace with the increase in transistor count and transistor density made possible by technology scaling. Energy efficient design is therefore critical for mobile platforms.

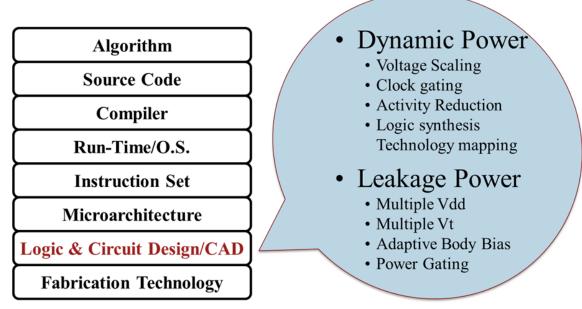

Efforts to reduce power consumption of digital CMOS circuits have been in progress for nearly three decades (Chandrakasan and Brodersen, 1998; Panda *et al.*, 2010). As a result, a number of well understood and proven techniques for reducing dynamic and leakage power have been incorporated into modern design practices and tools. Fig. 1.1 gives an idea about all the levels of hierarchy at which power reduction techniques have been explored.

Figure 1.1: Power Reduction Techniques

#### Power reduction techniques

A number of power reduction techniques have been applied at different levels of the circuit design hierarchy namely at the system level (algorithm, source code and OS compiler etc) (Piguet, 2005) (Lorch, 2001), at the architecture level (instruction set, micro-architecture) (Qadri *et al.*, 2009) (Zandrahimi and Al-Ars, 2014) (Moyer, 2001) and at the circuit level (circuit design, gate design and transistor design) (Devadas and Malik, 1995) (Chandrakasan and Brodersen, 2012). At each level, the techniques range from being completely general (applicable to all designs) to being applicable to specific types of circuits(such as only controllers or arithmetic designs). The dynamic power of the static (charge driven) digital switching circuit is given by

$$P_{dyn} = C.V^2.\alpha F \tag{1.1}$$

where C denotes the capacitance that is being charged or discharged during switching, V is the supply voltage,  $\alpha$  denotes the switching activity, and F denotes the frequency at which the circuit is operated. Each power reduction technique at any level targets a combination of these parameters to reduce the power. At the circuit and CAD level, efficient synthesis and technology mapping methods have been shown to reduce circuit area and switching activity (Brzozowski and Kos, 1999) (Keutzer, 1988) (Tiwari *et al.*, 1993). Additional methods such as logic restructuring (Brzozowski and Kos, 1999), gate sizing under timing slacks (Coudert, 1997), technology mapping (Tiwari *et al.*, 1993), re-timing (Monteiro *et al.*, 1996), clock gating (Chandrakasan and Brodersen, 2012) etc. have been applied and a large body of work have been published on these methods. We briefly summarize the techniques that are most relevant to this work. The techniques explored in this dissertation for improving digital circuits fall in to two categories.

- 1. Power and area reduction through gate sizing, and

- 2. Power reduction through the use of alternate types of timing elements.

#### Power and area reduction through gate sizing under timing slack

The use of smaller and slower cells can achieve reduction in area as well as dynamic power. For example, a 4-input AND gate is smaller and slower than a tree of 2-input AND gates. In the presence of positive timing slacks, it is possible to employ slower cells. A well-known method to reduce total power without sacrificing performance is to exploit slacks available on non-critical paths. The problem of choosing a particular gate size, formally known as the "gate sizing problem" (Coudert, 1997) consists of choosing, for each node of a mapped network, a gate implementation in the library, such that some cost function (e.g. dynamic power, leakage power or area or some combination of these) is optimized under given timing constraints. Techniques described in (Chen and Sarrafzadeh, 1996) (Coudert, 1997) reduce the available timing slack from a positive value to zero by using smaller and slower cells. The smaller cells typically require less area and have lower dynamic and leakage power. The average power improvement due to gate resizing in presence of timing slacks has been shown to be 38% (Chen and Sarrafzadeh, 1996). Similar techniques to reduce gate sizes are routinely employed in most commercial synthesis and mapping tools. Therefore, any additional timing slack introduced on the critical path without any change in clock period can reduce the total power considerably. This idea forms the basis of the power reduction ideas presented in this work. The techniques presented here maximize the timing slack on critical paths (for ASIC circuits) in order to reduce area and power.

#### Role of single and multi-input flip-flops in providing timing slack

In any timing path within a sequential circuit, the clock-to-Q delay and setup time of flipflops play an important role in determining the clock period. The is especially true in high speed pipelined datapath circuits. The clock period is determined by the total delay of the flipflop which is the sum of setup time and the clock-to-Q delay. Reducing the total delay results in extra slack, which can be used to reduce the size of the logic gates feeding the flipflop.

In order to reduce effective delay (also called pipeline overhead) of the flip-flops, attempts have been made to incorporate logic inside the flipflop. Dynamic and semidynamic flip-flops described in (Klass, 1998) (Partovi *et al.*, 1996) embed an NMOS logic block in the master latch. These flipflops have a dynamic master latch that presets and evaluates a logic function and a static back end that simply stores the value computed by the master latch for the remainder of the clock cycle. However these flip-flops pose few problems. First, their setup time grows substantially with the increased complexity of the embedded logic. Ideally the complexity of functions should not substantially affect the setup time. Second, for each logic function, a new flipflop has to be designed, optimized and characterized from scratch which can quickly become prohibitively expensive.

#### Threshold Logic Flipflops

#### Advantages of differential mode threshold gates

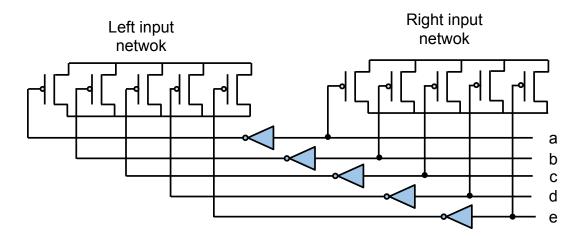

The static differential threshold gates (DTGs) overcome the obstacles posed by dynamic flip-flops that embed NMOS logic. The main feature of a DTG flip-flop is computing and amplifying the conductivity difference between two networks of parallel transistors referred to as the left input network (LIN) and the right input network (RIN). If the LIN has lower impedance then the output is logic 1, otherwise it is 0. Since the impedance of either network is an integral multiple of the number of ON transistors, the Boolean function of such DTG can be described by the predicate  $\sum x_i > \sum y_i$  where  $x_i$  are variables controlling the number of ON transistors in the LIN and  $y_i$  are Boolean variables controlling the number of ON transistors in the RIN. This predicate can be algebraically rearranged to yield the predicate  $\sum (x_i - y_i) > 0$ . This type of pseudo-boolean predicate corresponds to the class of linear threshold functions. Given a linear threshold function (which is a Boolean function), it is possible to connect the variables (and constants) to the input networks such that predicate of the DTG reduces to that of the given threshold function.

The DTGs (Strandberg and Yuan, 2000a)(Padure *et al.*, 2001b)(Leshner *et al.*, 2010) have been shown to be superior to the conventional multi-input and single input flip-flops because of following advantages: (1) They have a much lower and constant total delay whose value is almost independent of the complexity of the function being implemented (2) They impose no additional requirements from clock circuitry while exhibiting the same or lower clock load, (3) an they permit synthesis

time programmability i.e. the DTGs can be wired to implement a range of threshold functions which effectively reduces the number of cells in the library. In essence, the DTGs overcome most of the problems of flipflops embedding logic, however the type of logic they can implement is restricted to threshold logic functions as opposed to general Boolean functions.

One aspect of digital CMOS circuits that hasn't changed is how logic functions are computed. A CMOS ASIC circuit using static logic is a multi-level network of AND/OR logic gates or more complex cells such as AOI/OAI cells, in which each node computes a Boolean function of its inputs by establishing a conducting path from the supply rails to its output. However, *threshold* functions, which are a proper subset of unate Boolean functions, can be computed by fundamentally different mechanisms, and this presents the possibility of further improvements in power consumption, performance and area, which have not been thoroughly explored.

Let  $X = (x_1, x_2, \dots, x_n), x_i \in \{0, 1\}, \boldsymbol{w} = (w_1, w_2, \dots, w_n), w_i \in R$ , and  $T \in R$ . A unate Boolean function f(X) is called a threshold function if there exist weights  $\boldsymbol{w}$ and a fixed threshold T such that

$$f(X) = \begin{cases} 1 & \text{if } \boldsymbol{w}' X \ge T \\ 0 & \text{otherwise.} \end{cases}$$

(1.2)

$$= sgn^{+}(\boldsymbol{w}' X - T)^{1}$$

(1.3)

Without loss of generality, the weights  $\boldsymbol{w}$  and threshold T can be assumed to be positive integers. The following are two examples of threshold functions.

$$f(a, b, c) = ab \lor bc \lor ac$$

=  $[w_a = 1, w_b = 1, w_c = 1; T = 2]$  (1.4)

$$= [1, 1, 1; 2] \tag{1.5}$$

1sgn<sup>+</sup>(x) = 1 if  $x \ge 0$ , and  $sgn^+(x) = 0$  otherwise (see (Siu *et al.*, 1995)).

$$g(a, b, c, d, e) = a(b \lor c \lor d \lor e) \lor b(cd \lor de \lor ce) \lor cde$$

$$= [w_a = 2, w_b = 1, w_c = 1, w_d = 1, w_e = 1; T = 3]$$

(1.6)

$$= [2, 1, 1, 1, 1; 3].$$

(1.7)

A threshold function can be implemented in the same way as any logic function, e.g. network of logic primitives or a pull-up and pull-down network of pFETs and nFETs, etc. Such implementations are not considered here, as they offer nothing new, and in fact, can be quite inefficient for implementing threshold functions in terms of speed, power and area. The implementations of a threshold logic gate considered in this work compute the predicate in (1.2) by performing a comparison of some electrical quantity such as charge, voltage or current. This is what distinguishes such implementations of a threshold gate with any of the conventional implementations of CMOS logic functions.

The reason for examining threshold gates as logic primitives stems from the fact that they are computationally more *powerful* than the standard AND/OR logic primitives. Many common logic functions such as the n-bit parity, n-bit multiplication, division, powering, sorting, etc,. can be computed by polynomial size threshold networks of a fixed number of levels, while the same would require exponential size AND/OR networks (Siu *et al.*, 1995). A detailed treatment of the complexity of threshold networks and constructive methods for various types of arithmetic functions, including size-depth and weight-depth trade-offs is presented in (Siu *et al.*, 1995). An updated survey of the same appears in (Beiu, 2003), and an extensive survey of circuit architectures of threshold gates is given in (Beiu *et al.*, 2003). These surveys point to a large body of results which suggest that threshold gates and networks can potentially lead to significant reductions in circuit size and delay. However, the use of threshold logic gates in conventional ASIC design has not been thoroughly explored due to the lack of efficient and reliable gate implementations and the necessary infrastructure required for automated synthesis and physical design.

In this dissertation, new methodologies for digital circuit design with threshold logic gates are described. The applications of threshold logic gates to improve energyefficiency of two well known digital circuit design methodologies viz. - Application Specific Integrated Circuits (ASIC), Field Programmable Gate Arrays (FPGA) is described. We present the design of new circuit primitives and new logic synthesis algorithms.

The outline of the dissertation is as follows.

- 1. Chapter 2 describes the earlier work on the design and usage of differential mode threshold logic gates in circuit design.

- 2. Chapter 3 describes a new, robust architecture for a threshold gate that employs differential logic, referred to as a PNAND cell. As with other implementations in the same category, a PNAND cell is clocked, and its behavior can be abstracted to be that of a multi-input edge-triggered flip-flop (ETFF). Whereas a conventional D-type ETFF (D-FF) computes the identify function f(x) = x on a clock edge, a PNAND cell computes a threshold function  $f(x_1, x_2, \dots, x_n)$ , also on a clock edge. Furthermore, like the D-FF, a PNAND cell can be made scannable and have other features like asynchronous preset and clear.

Unlike conventional logic gates or cells, the function of a PNAND cell is not determined by the cell itself. Instead, its function is determined by the signals that drive its inputs. The signal assignment affects the delay, power and *robustness* of the cell to process variations. Therefore, a specific signal assignment that results in a least fanin PNAND cell to implement a given threshold function is defined. Conversely, for a PNAND cell with k inputs (PNAND-k), and with the specific signal assignment, the set of threshold functions that can be realized only by such a cell, and no other cell with a smaller k is determined. This leads to a small number of PNAND cells which collectively realize a substantial number of complex threshold functions, many of which would otherwise require a multi-level AND/OR network if implemented in a conventional design.

The robustness of the PNAND cell against parametric variations in 65nm technology is demonstrated (Section 3.5) through Monte Carlo simulations performed with vendor supplied variation data obtained from fabrication, and which include both global variations and local mismatch. The cells have been designed to achieve zero out 100,000 Monte-Carlo simulation trials.

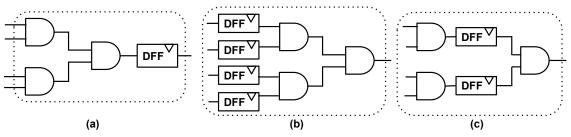

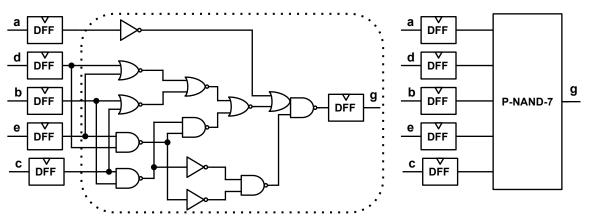

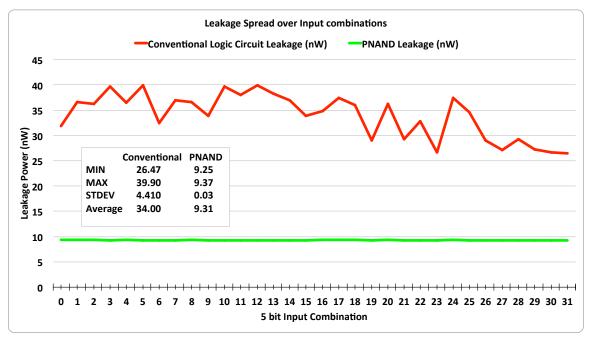

3. Chapter 4 describes two novel methods for technology mapping with PNAND cells starting from a generic AND/OR netlists. Since a PNAND cell may be viewed as a complex function embedded in a flip-flop, the technology mapping algorithm explores cones of logic that end at D-FFs for threshold functions, and replaces such subcircuits with the appropriate PNAND cell. The resulting circuit will have a mixture of conventional logic gates and threshold logic cells, and will be referred to as a *hybrid* design. A useful characteristic of threshold functions that is exploited during technology mapping is the ease of determining the NPN (input Negation, input Permutation, output Negation) equivalence of two threshold functions. This is not the case with AND/OR logic. This characteristic makes it simple to check if a a threshold function found in a logic cone is NPN equivalent to any of the functions implemented by the small set of PNAND cells in the library, thereby significantly increasing the set of possible matches during technology mapping.

The results of technology mapping with threshold gates for a number of complex

designs are presented and compared with conventional logic implementations. The PNAND cells were implemented as standard cells using a commercial 65nm technology. The netlists resulting from technology mapping with threshold cells were synthesized, and placed and routed using commercial tools. The same was done for the conventional design. The resulting final layouts were extracted and simulated for comparison with the conventional design.

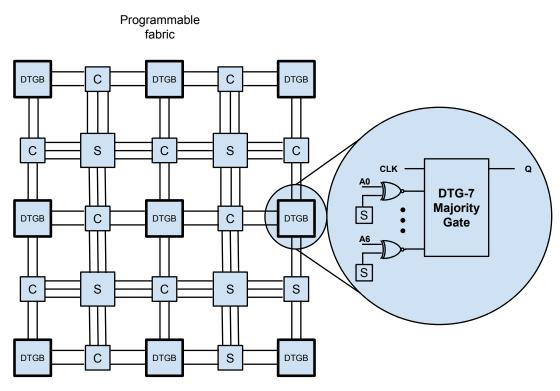

4. Using the proposed PNAND as a basic cell, chapter 5 describes a novel design of a field programmable threshold logic array (FPTLA), and a method to synthesize a network of TLGs that can be mapped on to the array.

The FPTLA can be programmed to realize any one of a number of threshold functions by assigning the appropriate signals to the inputs. This reduces the number of SRAMs required by the logic blocks by about 60%.

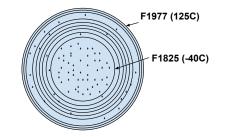

It is well known that differential mode threshold logic gates can be more sensitive to mismatch due to process variations. However, mismatch in a PNAND need not make the logic block unusable. Rather, mismatch causes the *set of* threshold functions realizable by the PNAND to be altered. This leads to two different scenarios in how the array can be utilized.

(a) A conservative approach is to simply ignore the cells whose functionality is altered by process variations. To ensure feasibility of the mapping, if a TLG network to be mapped has N TLGs, then an array of PNANDs larger than N would be required. We show that for a given probability of a cell's functionality being altered, the number of extra cells required to achieve a very high circuit yield is small.

(b) A key characteristic of PNAND cells is that mismatch can only result in another set of *threshold* functions. That is, mismatch will not change a threshold function into a non-threshold function – a characteristic that is demonstrated here. Hence, instead of simply ignoring the altered cells, the synthesis procedure can take in account the new set of all functions available on the array, and generate a TLG network accordingly. Note that the synthesis procedure that accounts for this additional flexibility is beyond the scope of this work.

We present experimental results by comparing FPTLA and conventional FPGA implementations of several nanopipelined combinational benchmarks. Nanopipelined circuits are path balanced in which each gate computes a function on a clock edge. The throughput and speed of such circuits is very high due to such deep level of pipelining. The power and delays of these circuits are obtained using the well established VPR tool that accurately models the *routing resources and logic blocks*.

5. Chapter 6 proposes a novel clocking method called as *local clocking* to further improve power reduction of ASIC circuits. The most important thing about local clocking is that it provides *incremental* improvements to existing circuits. Therefore whether a circuit is already hybrid or not, local clocking can still be applied. Local clocking works by deriving local clock signals from differential mode threshold gates. Most differential mode gate circuits operate using a sense-amplifier which has a differential amplified outputs (at logic 1 and logic 0 or vice versa). This state indicates the completion of computation which can be used to generate another output signal which has same pattern (albeit delay shifted) as the input clock. This skewed (delayed) output clock can be used to locally trigger other flipflops to realize additional advantages such as reduction in area and power under timing slack and elimination of hold time violations on certain short paths. A 0-1 integer programming formulation is provided for local clocking problem that decides which flipflops provide trigger to which other flipflops while satisfying timing constraints. Finally experimental results are provided on 64-bit multipliers with K pipeline stages (K=1 to 6) with locally clocked CMOS only and hybrid circuits. The local clocking provides additional 3% to 8% improvement in post-layout dynamic power.

#### Chapter 2

#### BACKGROUND

#### 2.1 Necessity for Low Power

Traditional ASIC (Application Specific Integrated Circuit) design involves constructing networks of CMOS (Complimentary Metal Oxide Semiconductor) logic gates to implement a given functionality. CMOS logic gates such as NAND, NOR, OR etc. consist of pullup and pull down networks and they function by establishing a conducting path between one of the supply rails and the output depending on the input combination. This paradigm has worked exceedingly well, in terms of dynamic power, size and robustness of the circuit. However there is even greater need for low power circuits due problems such as overheating and limited battery sizes of portable devices.

One of the most common way to address power problem is to scale the process geometry. As the size of transistors shrink, so does the area and power of circuits. However it's been observed that as process geometries shrink, the power density (power consumption per unit area) grows. The absolute power may drop but the power consumption per unit area (due to shrinkage in area) increases. The cooling solutions can withdraw a fixed amount of heat per unit area. Therefore shrinking process geometry does not diminish the need for low power circuits but rather makes it more severe.

The total power of CMOS circuit consists of three components.

$$P_{total} = P_{dyn} + P_{static} + P_{ss}.$$

(2.1)

The total power is sum of the dynamic power, the static power and the short circuit

power (when both pullup and pull-down networks are ON). Dynamic power which is the largest contributor to the total power is computed as

$$P_{dyn} = C.V^2.\alpha.F. \tag{2.2}$$

Equation 2.2 shows that a quick way to reduce power is to scale down the supply voltage (V), or the frequency (F) of operation. Indeed, techniques such as DVS (Dynamic Voltage Scaling) and DVFS (Dynamic Voltage-Frequency Scaling) are utilized routinely to minimize the power of circuits depending on the workload and task deadline requirements. However reducing voltage or frequency also reduces the speed of the circuit. Most ASIC chips must operate at certain minimum speed while some have more stringent high speed requirements. Therefore reducing voltage or frequency is beneficial only when speed is not a concern. For a given voltage and frequency, the power consumed by the circuit is a characteristic property of the circuit. Therefore the main concern of circuit designers is to improve *energy delay product* rather than power. Energy delay product (EDP) is computed as

$$EDP = E_{tot}/F,\tag{2.3}$$

where  $E_{tot}$  is total energy expenditure and F is the frequency of operation of the circuit. The unit of this metric is Joules × seconds per cycle which is equivalent to the amount of energy spent multiplied by the amount of time taken for one operation. A circuit with the lowest expenditure of energy and time combined for one unit of operation is the most desired. EDP is directly related to the *energy efficiency*. A circuit with lower EDP is said to be more energy-efficient (Gonzalez and Horowitz, 1996). We can improve the EDP by speeding up the circuit without increasing the power, or lowering the power without decreasing the speed. The ASIC and FPGA circuit designs proposed in this thesis explore both of these ideas.

#### 2.2 Dynamic Power Reduction Methods

The power reduction methods tried so far span several decades of research. The survey in (Devadas and Malik, 1995) gives an overview of most of the power reduction techniques. A brief summary of these ideas is presented here to give the reader an idea of how various approaches achieve power reduction.

#### Reducing Switching Activity

The *clock gating* technique enables the clock only when the circuit has a data input to process. The enable circuit typically produces a signal that is used in clock distribution networks to enable/disable propagation of the clock. The clock gating technique reduces activity factor ( $\alpha$ ) in the Equation 2.2. Another way to reduce the switching activity is restructure the logic. (Brzozowski and Kos, 1999) shows that a different synthesis of the same function can lead to lower switching activity.

Another important contributor to the dynamic power is glitching. It can contribute between 10% - 40% to the dynamic power. A glitch is a spurious transition of a signal caused by unbalanced path delays in combinational circuits. Techniques to minimize glitching by path balancing are presented in (Vijayakumar and Kundu, 2014) and (Lemonds and Shetti, 1994). Glitches are propagated by combinational gates from inputs to their outputs. However sequential elements such as flipflops do not propagate glitches. A retiming solution that introduces flipflops on most active wires to reduce power is described in (Monteiro *et al.*, 1996).

#### Reducing Capacitance

Almost all the remaining techniques focus on reducing the capacitance of the circuit. The capacitance is directly proportional to the transistor (or logic gate) sizes,

as well as their number. At the transistor level, transistor resizing technique in (Tan and Allen, 1994) minimizes the transistor sizes in a logic gate while meeting the delay constraints. The combinational networks can be reduced in size by techniques such as don't care based optimization (Shen *et al.*, 1992). Another approach for technology independent optimization is by improved factorization of logical expressions based on modified kernel extraction methods (Roy and Prasad, 1992).

Technology mapping step involves generating technology dependent realization of logic networks using a given set of library primitives. Techniques to minimize power by technology mapping are presented in (Keutzer, 1988) (Tiwari *et al.*, 1993).

The power reduction methods in sequential circuits involve modifying state encoding, retiming etc. The state encoding optimization technique which tries to reduce the state transition graph and the number of states is presented in (Tsui *et al.*, 1994).

#### 2.3 Static Power Reduction Methods

The static or leakage power of the circuit  $P_{static}$  is a function of supply voltage, temperature and the static currents through all the transistors in the circuit. The contribution of static power compared to the dynamic power increases with miniaturization. Therefore a number of techniques have been tried to reduce the static power as well.

Most of the fabrication processes allow for multiple threshold voltage  $(V_T)$  transistors, typically at three levels: low, standard and high. A transistor with high  $V_T$  has much less static current. However at the same time, high  $V_T$  transistors are also slower. Therefore a common technique is to use standard cells with high  $V_T$  on non-critical paths. This method is presented in (Roy *et al.*, 2003).

Connecting transistors in series results in a substantial reduction in leakage. Therefore placing a sleep transistor between the supply rail and one of the pullup/pulldown networks reduces the leakage substantially (Kumar *et al.*, 2013). The same stacking technique is extended to *power gating* wherein an entire block of logic is supplied power through a large PMOS transistor which is turned off when the circuit is not operated.

Controlling the supply voltage is another common technique to reduce static current. The supply voltage of memory modules is scaled down to a minimum possible value that ensures data retention. If a logic block is not required to operate faster a given certain speed its voltage can be reduced to a value that meets the speed requirements.

### 2.4 Threshold Logic: A New Approach

Static CMOS logic has been the dominant design methodology for digital circuits for the past several decades. Circuits consists of networks of AND, OR and NOT gates. As described above, techniques for reducing power consumption of CMOS circuits have been thoroughly investigated, and there hasn't been, nor likely to be, any new developments in reducing power consumption of static CMOS logic.

AND, OR and NOT functions are special cases of threshold functions, a natural question to investigate is whether networks of more general threshold functions can lead to faster, more compact, and lower power circuits. This is the main direction of this research.

A large of body theoretical work on threshold networks has demonstrated the numerous advantages in terms of size (i.e. number of gates), and speed (i.e. number of levels). We now briefly describe some of the many advantages of threshold networks over the conventional logic networks.

The symmetric functions are a subclass of Boolean functions whose output is only a function of number of 1's in the input vector. For example, parity or majority functions can simply count the number of 1's in the inputs to be able to produce the output value. Symmetric functions of n inputs can be realized using  $O(\sqrt{n})$  threshold gates with depth of 3 (constant depth). Whereas symmetric functions such as parity would require O(n) AND-OR-NOT gates with depth of  $O(\log n)$ .

Arithmetic circuits are the most commonly used blocks in today's ASIC circuits. Many n-bit functions such as multiplication and exponentiation require exponentially many AND-OR-NOT gates. In contrast, a threshold networks of these functions require at most a polynomial in n number of threshold gates and very small depth (logic levels). For example, Addition and Comparison can be computed with depth-2 and polynomial number of threshold gates. Multiplication can be computed with polynomial sized circuit with depth of 4. Along with multiplication, powering, division and sorting can also be computed with depth of 4 or less. It should be noted that the integer weights of the threshold gates used in above networks are also polynomially bounded.

The above results and others suggest that, at least in theory, threshold networks can potentially be far more compact and faster than conventional logic networks. Whether these advantages can be realized in practice depends on the physical characteristics of threshold gates. In this dissertation, we demonstrate that a combination of threshold gates and conventional logic can indeed result in smaller and lower power circuits, than conventional logic networks, without sacrificing performance.

## 2.5 Threshold Logic Gates

If the predicate (1.2) in the definition of a threshold function is to be realized by a single circuit, it must be able to selectively add some physical quantity that represents the weights and compare that with a fixed quantity (threshold) having the same type as the weights. Typically the physical quantity that is added is one of the charge, current, magnetic or electric fields. Depending on which physical quantity is utilized, there exists a range of threshold circuits that have been designed till date. The comprehensive survey in (Beiu *et al.*, 2003) shows nearly 50 different implementations based on different principles. Here we provide a short synopsis of some those implementations.

Threshold logic implementations can be broadly classified into two types: (1) static or combinational or (2) sequential (clocked). The static implementations essentially treat a threshold function as any other logic function, and therefore, a single pair of complementary pull-up and pull-down networks can be used to implement the given threshold function. However such implementations are prohibitively large and slow for all but small functions. Examples of such implementation are (J., 1964; Z. and W., 1967; Hidalgo-Lopez *et al.*, 1995). Another early design (J, 1973) uses multiple inverters driving a common node. The widths of these inverters are adjusted based on weights of the threshold functions which forms a non-linear voltage divider at the output node.

Among the sequential implementations, one of the earliest implementations is based on switched capacitors (CTL) (Özdemir *et al.*, 1996). Their main drawback was large delay, area, DC power and the need for precise capacitance values. Although the variant balanced CTL (B-CTL) (López-García *et al.*, 2004) eliminated the need for precise capacitance values by comparing relative voltages, it still retained the other drawbacks. Neuron MOS TLG (Shibata and Ohmi, 1991), which performs similar summation of voltage using capacitors eliminates the usage of a reference threshold voltage. Several modified versions of Neuron MOS TLGs (Kotani *et al.*, 1995, 1998) were proposed as improvements of the basic version. Later versions of the same used a sense-amplifier to sense the differential voltage after summation (Huang and Wang, 2000; Celinski *et al.*, 2001), which improved the sensitivity and power dissipation. The self-timed threshold logic (STTL) uses capacitor sharing to minimize capacitor areas and can include negative weights without inverting inputs. However all these implementations still utilized precise capacitance devices which are hard to fabricate and also require large area.

Threshold logic gate architectures based on comparing conductances include (1) Single input Current Sensing Differential Logic (SCSDL) (Strandberg and Yuan, 2000b), (2) Differential Current Switch Threshold Logic (DCSTL) (Padure *et al.*, 2001b), (3) Current Mode Threshold Logic (CMTL) (Bobba and Hajj, 2000) and some of its variants known as discharged CMTL (DCMTL) and equalized CMTL (ECMTL), and Threshold Logic Latch (TLL) (Leshner *et al.*, 2010; Leshner, 2010). A high fanin current mode threshold logic gate similar to CMTL is presented in (Dara *et al.*, 2012), along with a analysis of its delay based on device models without accounting for process variations. Technology independent analysis of the robustness of threshold gates is presented in (Dechu *et al.*, 2006), in which any type of variation is modeled as perturbations in the weights and threshold.

Researchers have recognized that several of the post-CMOS nano technologies <sup>1</sup> which make it possible to efficiently and naturally implement threshold functions. (Gupta and Jha, 2005) describes nano-pipelined implementations of threshold gates using RTDs and (Lageweg *et al.*, 2001) describes a novel design of an *n*-input linear threshold gate, requiring one tunnel junction and n+2 capacitors. Using an improved design of a SET based threshold logic gate, a full adder design is described in (Lageweg *et al.*, 2002). (Sulieman and Beiu, 2004) describes the optimal threshold gate based design of a 16-bit parallel-prefix adder using single electron transistors (SET). SETs

<sup>&</sup>lt;sup>1</sup>Resonant tunneling diodes (RTD)(Prost *et al.*, 2000), carbon nanotube FETs (CNFET) (Appenzeller *et al.*, 2005) and carbon nanowires; single electron transistors (SET) (Lageweg *et al.*, 2001), quantum cellular automata (QCA) (Blair and Lent, 2003; Jian *et al.*, 1998), non-charge based devices such as spin transfer torque magnetic tunnel junctions (STT-MTJ), etc.

have been shown to realize latches, flip-flops and majority gates (Lageweg *et al.*, 2001). A threshold gate has been built with an RTD and an HFET (Chen *et al.*, 1995). A primitive gate in a QCA is a majority gate which is a threshold function (Zhang *et al.*, 2005).

#### 2.6 Synthesis and Mapping using Threshold Logic

Most, if not all of the prior work on synthesis of threshold networks is technology independent, and the earliest work dates back to the 1960s. A comprehensive treatment of the subject through 1970s appears in (Muroga, 1971). Some of the methods summarized in (Muroga, 1971) are: (1) Minterm expansion, which uses exponentially many majority gates; (2) Akers' method based on self dualization and positivization; (3) Minnick's synthesis based on iterative solution of linear programming problems along with artificial variables; (4) Hughes method which is similar to Minnick's method but doesn't use artificial variables; (5) Winder's method based on geometric interpretation of monotonic properties of threshold gates and finally an optimum network synthesis for threshold networks based on integer linear programming. These techniques are generally not suitable for present day industrial designs.

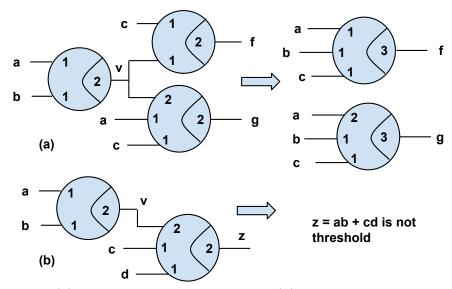

Reference (Siu *et al.*, 1995) presents a thorough treatment of the fundamental complexity results of threshold networks up to 1995, and (Beiu, 2003) covers many additional results through 1999. Most of these results point to the fact that threshold logic networks require fewer number and levels of gates compared to conventional AND-OR-NOT networks. A more recent threshold synthesis procedure is due to Zhang et al. (Zhang *et al.*, 2005) which shows an average of 52% reduction in gate count compared to Boolean networks for MCNC benchmarks. An improved method based on iterative decomposition of BDD of a general Boolean function is presented in (Gowda *et al.*, 2011).

It should be noted that most of the prior work on threshold synthesis assumes either an abstract threshold gate or nano-device based gates which are hard to fabricate with required precision. But the MOSFET based differential mode threshold gates (DTGs) that can compete with static CMOS style gates are essentially sequential by nature. It is possible to develop a balanced or nano-pipelined network consisting only of DTGs. Such networks, although faster than any conventional static CMOS gate networks, pose several additional challenges such as increased complexity of clock distribution, increased power and area etc. in ASIC domain <sup>2</sup>. Inspired from the work in (Leshner *et al.*, 2010), the present work in ASIC domain (Chapters 3 and 4) further extend the idea of hybrid networks that consist of an optimal mix of PNANDs and conventional CMOS standard cells.

#### 2.7 Threshold Logic in Field Programmable Environment

Compared to standard cell based circuits, the attempts to utilize threshold logic in a field programmable environment have been very scarce, and only a few implementations exist. (Rajendran *et al.*, 2010) describe a novel memristor based threshold logic gate array. The computing block in this architecture consists of a threshold gate where memristance of the device act as weights. The computing block consists of current mirrors which are used to add currents through the memristive devices which is then compared with a reference current. Although they show substantial improvements in power (about 75%) compared to MOSFET based 4-input LUT FPGA, the absolute delay of the threshold gates are quite high (12 times that of LUT). Another implementation that uses a nano-device is presented in (Nukala *et al.*, 2012). The computing block in this gate array is a threshold gate consisting of STT-MTJ (spin

<sup>&</sup>lt;sup>2</sup>However in field programmable circuit domain, the clock is already distributed and therefore a nano-pipelined implementation can take advantage of it. In fact, chapter 5 explores this idea.

transfer torque magnetic tunnel junction). This device switches its resistive state if a current larger than certain magnitude (switching current) is passed through it. A parallel network of pFETs is employed to tune the current passing through STT-MTJ. If enough inputs are 1, then the current through the STT-MTJ is greater than switching magnitude and it switches to the state of low resistance. Therefore the STT-MTJ acts as a natural threshold logic gate.

### Chapter 3

### THRESHOLD LOGIC FLIPFLOP

This chapter explains the architecture, operation and cell level analysis of the proposed threshold gate PNAND.

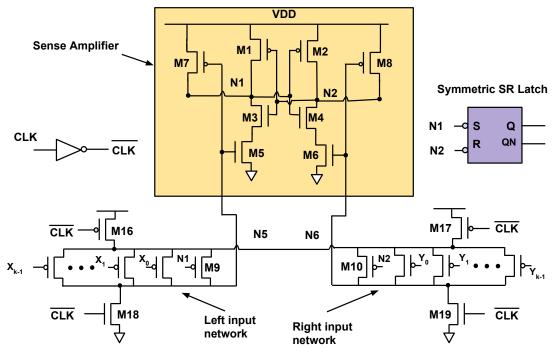

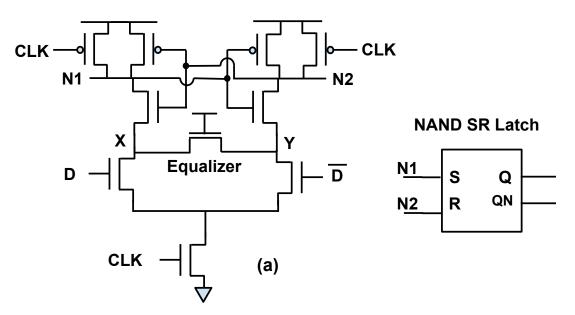

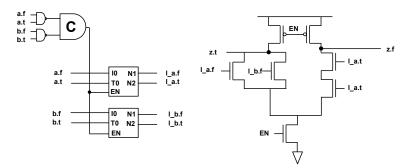

### 3.1 Architecture

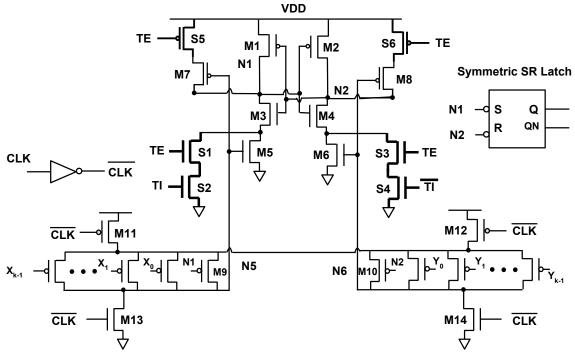

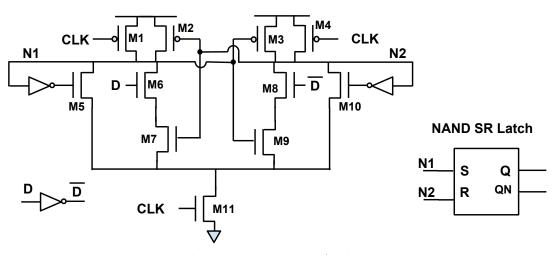

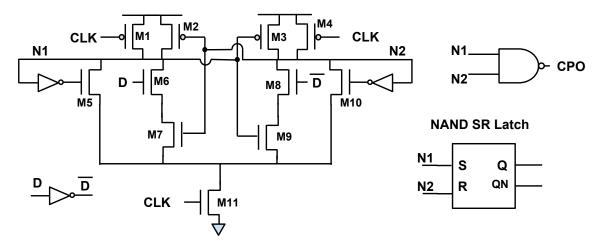

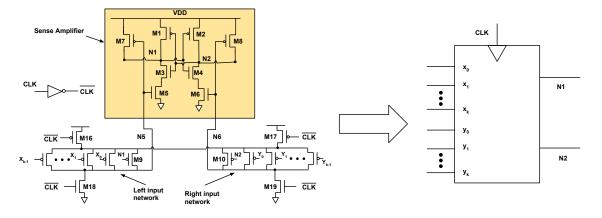

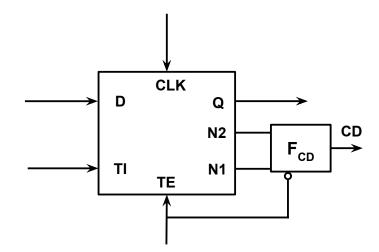

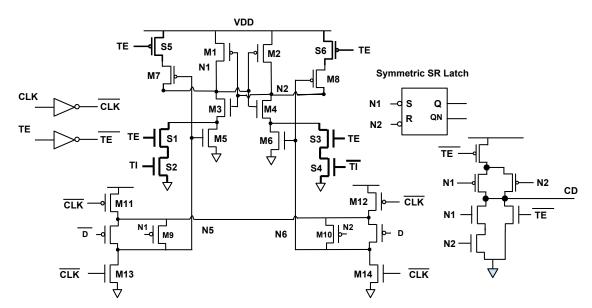

Figure 3.1 shows the schematic of the threshold gate with k inputs, henceforth referred to as PNAND-k. It consists of three main components: (1) two groups of parallel pFET transistors referred to as the left input network (LIN), and right input network (RIN), (2) a sense amplifier (SA), which consists of a pair of cross coupled NAND gates, and a (3) set-reset (SR) latch. The cell is operated in two phases: reset (CLK = 0) and evaluation (CLK  $0 \rightarrow 1$ ). For the moment, ignore the transistors M9 and M10.

Reset phase: With CLK = 0, the two discharge devices M18 and M19 pull nodes N5 and N6 low, which turn off M5 and M6, disconnecting all paths from N1 and N2 to ground. In addition, M7 and M8 are active, which results in N1 and N2 being pulled high. The nFETs M3 and M4 are ON. With N1 and N2 being high, the state of the SR latch does not change.

Evaluation Phase: This corresponds to when CLK  $0 \rightarrow 1$ . A input that results in  $\ell$  active devices in the LIN and r active devices in the RIN is denoted by  $\ell/r$ . The signal assignment procedure (to be explained shortly) will ensure that  $\ell \neq r$ . Assume that  $\ell > r$ . As a result, the conductance of the LIN is higher than that of the RIN.

As the discharge devices M18 and M19 are turned off, both N5 and N6 will rise to 1. Due to the higher conductivity of the LIN, node N5 will start to rise first,

Figure 3.1: PNAND Cell Design

which turns on M5. With M3 = 1, N1 will start to discharge through M3 and M5. The delay in the start time for charging N6 due to the lower conductance of the RIN allows for N1 to turn on M2 and turn off M4. Thus, even if N2 starts to discharge, its further discharge is impeded as M2 turns on, resulting in N2 getting pulled back to 1. As a result, the output node N1 is 1 and N2 is 0. As the circuit and its operation are symmetric, if  $\ell < r$ , then the evaluation will result in N1 = 0 and N2 = 1.

The active low SR-latch stores the signals N1 and N2. During reset, when (N1, N2) = 1, the SR-latch retains its state. After evaluation, if (N1, N2) = (0, 1), the output Q = 0, and if (N1, N2) = (1, 0), Q = 1, providing a dual-rail output for the threshold function being computed. Therefore, once evaluated after rising edge of the CLK, the output Q of the cell is stable for the remaining duration of the clock cycle. Hence, it operates like an edge-triggered flip-flop, that computes a threshold

function.

Since it is the "difference in conductivity" between the LIN and RIN that is sensed and amplified, the greater the difference, the faster and more "reliably" the cell operates. In the layout of the PNAND cell, several steps were taken to ensure robustness to process variations and signal integrity. A symmetric SR-latch (Nikolic *et al.*, 2000) was used to ensure near identical load on node N1 and N2 and near equal rise and fall delays. The source nodes of M16 and M17 are shorted so that the transistors in the LIN and RIN have nearly identical  $V_D$ ,  $V_G$  and  $V_S$  before clock rises. The sizes of the pull-down devices in the differential amplifier were optimized, as were the sizes of the input transistors in the LIN and RIN to maximize the conductivity difference for the input combination that results in the worst-case *contention* between the LIN and RIN, while keeping the RC delay of the input networks as low as possible. In addition, to further improve the robustness of the cell, an internal feedback is created with transistors M9 and M10 in the LIN and RIN, driven by N1 and N2, respectively.

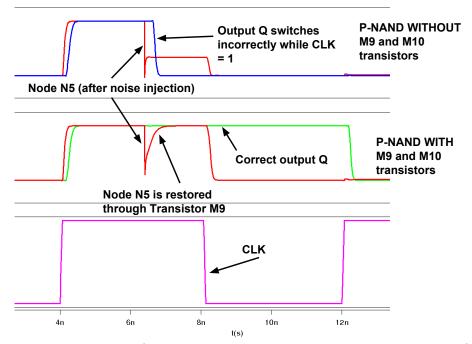

These additional transistors M9 and M10 in the input networks serve as keepers to avoid the situation where N5 and N6 might be in a high impedance states (HiZ1, HiZ0). Assume for the moment that M9 and M10 are not present, and consider the situation in which there are k active devices in the LIN and none in the RIN. After reset, N5 and N6 are both 0. When the clock rises to 1, N5 will rise to 1, and N6will be HiZ0, and the circuit will correctly evaluate with N1 = 0, N2 = 1. Note that M4 is inactive and M3 is active. Now suppose that while CLK = 1 the inputs change, and all transistors in the LIN become inactive and some k transistors in the RIN become active. N5 is now HiZ1, and N1 will remain at 0, keeping M4 inactive. However, N6 rises to 1, turning on M6, but as long as M4 remains inactive, and M2active, no change will take place. N5, being HiZ1, is susceptible to being discharged. If that happens, N1 rises, activating M4, and discharging N2, which results in the output being complemented.

Transistors M9 and M10 ensure that N5 and N6 do not become HiZ0 or HiZ1. In the above situation, once N1 = 0 during evaluation, the presence of M9 driven by N1 ensures that N5 = 1. Hence, after evaluation and while CLK = 1, any change in the input state will not affect the side that determined the output, i.e. was discharged first, and hence the output will not be disturbed.

Figure 3.2 shows waveforms from the SPICE simulation of a PNAND-9 netlist extracted from layout, with and without M9 and M10 transistors. For the specific signal assignment used in the technology mapping, the maximum number of active devices in the LIN or RIN among all the functions realized by a PNAND-9 is 5. Therefore the simulation shown in Figure 3.2 starts with applying a 5/4 input, which results in N1 = 0, N2 = 1 and Q = 1. While CLK is held at 1, the input is switched to 0/5, so that N5 = HiZ1. Next, N5 is discharged to ground through a capacitor, which turns off M5 and turns on M7, pulling N1 to 1. This turns on M2 and turns off M4, and N2 discharges to ground. The result is that while CLK = 1, if the input switched leaving N5 or N6 in a HiZ1 state, it is possible to switch the output due to coupling noise. The same experiment, when repeated with the presence of the keeper transistors M9 and M10, does not result in the output being disturbed.

#### 3.2 Asynchronous Preset, Clear and Scan implementations

The PNAND cell is a multi-input flip-flop, therefore it is necessary for it to have typical features of a D-flip-flop such as asynchronous preset and clear as well as scan. Evidently the PNAND cell operates quite differently compared to a master-slave Dflip-flop. In master-slave DFF, the asynchronous preset and clear inputs must change the state of both master and slave to make it independent of the state of the clock.

Figure 3.2: Importance of Feedback Transistors in the Input Networks of PNAND

However in PNAND, the SR latch always follows the nodes N1 and N2 irrespective of the clock. Hence the preset, clear and scan mechanisms need to change the state of the sense amplifier.

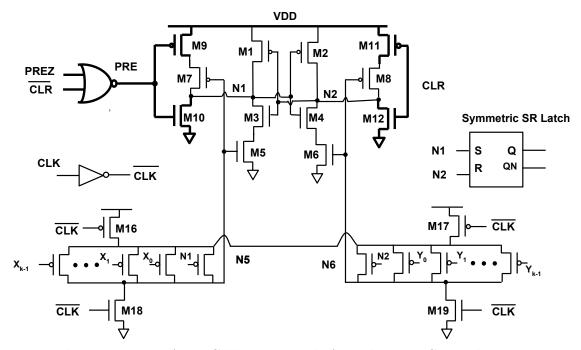

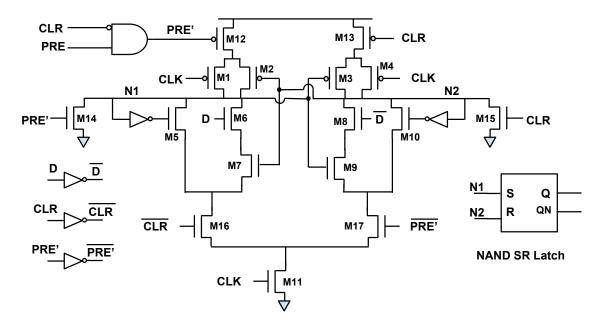

Fig. 3.3 shows the implementation of asynchronous preset PREZ (active low) and asynchronous clear CLR (active high). The additional transistors required in the basic PNAND to implement preset and clear are shown with thicker lines. When CLK is 0, N1 and N2 are both 1. When PREZ is asserted (set to 0) and CLR = 0, the signal PRE rises to 1. Therefore transistor M9 is off cutting supply to node N1. N1 discharges through the NMOS transistor M10 causing cell output Q to rise. When CLR is asserted (CLR = 1), node N2 discharges through transistor M12 causing latch output Q to fall. When both CLR and PREZ are asserted, then CLR alone operates and PREZ is filtered out indicating this is CLR dominated circuit. The NOR gate can actually be moved outside the cell and shared across all cells which allows the cell to have a single active high preset (PRE) signal. When CLK = 1, the state of N1 and N2 can be opposite. In this case, the NMOS transistors M10 and M12 must be sized to overcome PMOSes M1 and M2.

Figure 3.3: PNAND Cell Design with Asynchronous Set and Reset

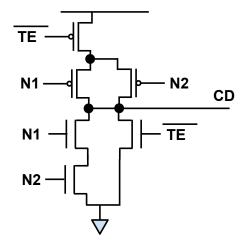

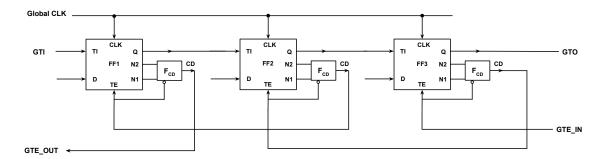

If PNAND cells are to replace flipflops, scan capability is essential. The simplest way to make a D-FF scannable is to use a 2:1 mux that selects between the input D and the test input (TI), depending on whether or not the test mode is enabled (TE). This is not practical for a multi-input flip-flop like the PNAND cell. Although there exist several ways to implement scan for a PNAND cell, the one shown in Figure 3.4 has negligible impact on the cell's performance and robustness during normal operation. All other variations were significantly worse in this regard.

The additional transistors for scan are labeled as S1 through S6. In the normal mode, the signals TE (test enable) and TI (test input) are both 0, which disables the scan related transistors (S1 through S4), and reduces the circuit function to the one

Figure 3.4: PNAND Cell Design with Scan

shown in Figure 3.1.

We can see that in the scan mode, the TE signal itself acts as a clock for a PNAND. In fact regular clock CLK must be held 0 for the scanning mechanism to work. Therefore, if a circuit has a mix of D-FFs and PNAND cells, the PNAND cells must be part of a separate scan chain. A common TE signal is used for both the scan chains. However the way this TE signal is operated is different from the conventional scanning mechanism. First the signal TE is held high and data is scanned into regular flipflops (conventional way). Once this is finished, the CLK is held 0 and following procedure is performed to stored data bits in PNANDs. Signal GTI (global test input) is the entry point for the scan data input to the PNAND chain.

- 1. Set CLK = 0 and TE = 0.

- 2. Set GTI = i'th bit of the input (i = 0 initially).

- 3. Set TE = 1. Each PNAND registers its TI input.

- 4. Set TE = 0.

- 5. Increment i and repeat until the end of stream.

Note that as long as CLK = 0, the toggling of TE signal alone does not alter the data already stored in the conventional D-Flipflop scan chain. Therefore at the end of this procedure both PNANDs and flipflops store the required set of bits and regular clocking can proceed. The pullup transistors S5 and S6 are included to eliminate a DC path during testing. In absence of these transistors, when TE is asserted  $(0 \rightarrow 1)$ , while CLK = 0, M7 is active, and there is a DC path  $VDD \rightarrow M7 \rightarrow M3 \rightarrow S1 \rightarrow S2 \rightarrow GND$ .

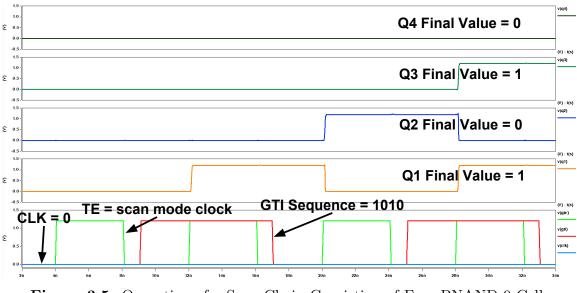

Fig. 3.5 shows the waveforms obtained via SPICE simulation of a scan chain of four PNAND-9 cells. The CLK is set to 0. The nodes Q1, Q2, Q3 and Q4 are output nodes of 4 cells that are initialized to 0. The scan pattern being registered is (Q1, Q2, Q3, Q4) = 1010.

Figure 3.5: Operation of a Scan Chain Consisting of Four PNAND-9 Cells

#### 3.3 Threshold Functions Realized by a PNAND

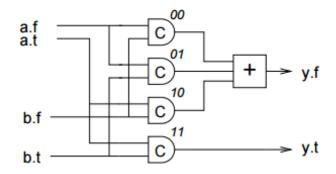

This section explains how PNAND cells can be used to compute a restricted set <sup>1</sup> of threshold functions. This is done by connecting the appropriate signals to the inputs in the LIN and RIN. If  $x_i$  and  $y_i$  are the signals that drive the gates of the transistors in the LIN and RIN, respectively, then the function of the PNAND cell can be expressed as

$$PNAND(x_{1}, x_{2}, \cdots, x_{n}, y_{1}, y_{2}, \cdots y_{k}) = \begin{cases} 1 & \text{if } \sum_{i=1}^{k} x_{i} > \sum_{i=1}^{k} y_{i}, \\ 0 & \text{if } \sum_{i=1}^{k} x_{i} < \sum_{i=1}^{k} y_{i}, \\ X & \text{if } \sum_{i=1}^{k} x_{i} = \sum_{i=1}^{k} y_{i}. \end{cases}$$

(3.1)

X in Equation 3.1 denotes an *indeterminate* state. This condition must be eliminated. Let  $f(X) = [\boldsymbol{w}, T]$ , be a threshold function, and  $\delta = \max_{X \ni f(X)=0} | \boldsymbol{w}'X - T |$ . That is  $\delta$  is the magnitude of the largest weighted minterm in the off-set of f. In (Siu *et al.*, 1995) it shown that that  $(\boldsymbol{w}'X - T + \delta/2) \neq 0$  and  $\operatorname{sgn}^+(\boldsymbol{w}'X - T) = \operatorname{sgn}^+(\boldsymbol{w}'X - T + \delta/2)$ . This means that if the threshold T is replaced by  $T + \delta/2$ , then the inequality  $\boldsymbol{w}'X \geq T$  in (1.2) becomes a strict inequality  $\boldsymbol{w}'X > T + \delta/2$ , without changing the threshold function. If the weights  $\boldsymbol{w}$  and threshold T are integers with minimum possible values, then  $\delta = 1$ . Then

$$\boldsymbol{w}'X \ge T \equiv \boldsymbol{w}'X \ge T - 0.5 \equiv 2\boldsymbol{w}'X \ge 2T - 1.$$

(3.2)

Therefore, the indeterminate state can be eliminated by doubling the weights and replacing the threshold T with 2T - 1.

<sup>&</sup>lt;sup>1</sup>It should be noted even though a given PNAND-k implements a limited set of functions, for any arbitrary threshold function H, there exists a k such that PNAND-k can implement H.

Let  $W = \sum_{i=1}^{k} w_i$ . The inequality in (3.2) can be realized as is by a PNAND in which the LIN has 2W transistors, whose gates are driven by the inputs, and the RIN has 2T - 1 active transistors, and 2(W - T) + 1 inactive transistors <sup>2</sup>. Hence a PNAND-2W will be required if the inequality (3.2) is used. As an example, consider the threshold function  $f(a, b, c) = a \lor bc \equiv 2a + b + c \ge 2 \equiv 4a + 2b + 2c > 3$ . If f is to be implemented with this inequality then a PNAND-8 will be necessary, with the following signal assignment.