Low-Overhead Built-In Self-Test for Advanced RF Transceiver Architectures

by

Jae Woong Jeong

# A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved November 2015 by the Graduate Supervisory Committee:

Sule Ozev, Chair Yu Cao Jennifer Kitchen Umit Ogras

ARIZONA STATE UNIVERSITY

December 2015

#### ABSTRACT

Due to high level of integration in RF System on Chip (SOC), the test access points are limited to the baseband and RF inputs/outputs of the system. This limited access poses a big challenge particularly for advanced RF architectures where calibration of internal parameters is necessary and ensure proper operation. Therefore low-overhead built-in Self-Test (BIST) solution for advanced RF transceiver is proposed. In this dissertation. Firstly, comprehensive BIST solution for RF polar transceivers using on-chip resources is presented. In the receiver, phase and gain mismatches degrade sensitivity and error vector magnitude (EVM). In the transmitter, delay skew between the envelope and phase signals and the finite envelope bandwidth can create intermodulation distortion (IMD) that leads to violation of spectral mask requirements. Characterization and calibration of these parameters with analytical model would reduce the test time and cost considerably. Hence, a technique to measure and calibrate impairments of the polar transceiver in the loop-back mode is proposed.

Secondly, robust amplitude measurement technique for RF BIST application and BIST circuits for loop-back connection are discussed. Test techniques using analytical model are explained and BIST circuits are introduced.

Next, a self-compensating built-in self-test solution for RF Phased Array Mismatch is proposed. In the proposed method, a sinusoidal test signal with *unknown* amplitude is applied to the inputs of two adjacent phased array elements and measure the baseband output signal after down-conversion. Mathematical modeling of the circuit impairments and phased array behavior indicates that by using two distinct input amplitudes, both of which can remain *unknown*, it is possible to measure the important parameters of the phased array, such as gain and phase mismatch. In addition, proposed BIST system is designed and fabricated using IBM 180nm process and a prototype four-element phased-array PCB is also designed and fabricated for verifying the proposed method.

Finally, process independent gain measurement via BIST/DUT co-design is explained. Design methodology how to reduce performance impact significantly is discussed.

Simulation and hardware measurements results for the proposed techniques show that the proposed technique can characterize the targeted impairments accurately. To My Parents and Family

#### ACKNOWLEDGMENTS

Firstly, I would like to express my deep gratitude to my advisor and committee chair, Professor Sule Ozev, without whom this dissertation would not have been possible. I am extremely grateful for her advising, encouragement, and support.

Besides my advisor, I would like to give special appreciation to Professor Jennifer Kitchen for guiding me during tapeout and serving as committee member. And I also would like to thank Professor Yu Cao and Professor Umit Ogras for serving as my committee members.

I would like to show my great appreciation to Friedrich Taenzler at Texas Instruments and LeRoy Winemberg at Freescale Semiconductor for offering me summer internship and for their valuable comments and support.

I want to thank all the members in RF Design & Test Group at ASU.

I would like to express my gratitude to my parents, my parents-in-law and brothers in South Korea for their continuous encouragement and support.

I sincerely would like to express my deepest gratitude to my wife, Mi Seon Huh who have always loved, sacrificed, and supported me. I also thank to my son and daughter-Myeonghun Jeong and Sieun Grace Jeong.

Finally, I would like to thank God for guiding me all the way.

# TABLE OF CONTENTS

| Page                                                     |

|----------------------------------------------------------|

| LIST OF TABLES ix                                        |

| LIST OF FIGURES                                          |

| CHAPTER                                                  |

| 1 INTRODUCTION1                                          |

| 1.1 Outline of Dissertation1                             |

| 2 A COMPREHENSIVE BIST SOLUTION FOR RF POLAR TRANSCEIVER |

| USING ON-CHIP RESOURCES10                                |

| 2.1 Polar Transceiver Overview10                         |

| 2.1.1 Overview of the Polar Transceiver                  |

| 2.1.2 RF Impairments in the Polar Transceiver            |

| 2.2 Test Methodology13                                   |

| 2.2.1 Receiver Gain and Phase Mismatch Measurements      |

| 2.2.2 Two-Tone Test in the Loop-Back Mode                |

| 2.2.3 AM/AM and AM/PM Distortion Measuremnt              |

| 2.2.4 Delay Skew Measurement in the Loop-Back Mode21     |

| 2.2.5 Envelope BW Limitation in the Loop-Back Mode       |

| 2.2.6 BIST Algorithm                                     |

| 2.3 On-Chip Implementation of the Loop-Back Path         |

| 2.3.1 Loop-Back Path Implementation                      |

| 2.4 Experimental Results                                 |

|        | 2.4.1  | Simulation Results                             |

|--------|--------|------------------------------------------------|

|        | 2.4.2  | Hardware Measurements                          |

|        | 2.4.3  | Accuracy of BW Measurement                     |

|        | 2.4.4  | Accuracy with On-chip Loop-Back Delay          |

|        | 2.4.5  | Test Time                                      |

| 2.3    | Conc   | elusion40                                      |

| 3 ROB  | UST AN | MPLITUDE MEASUREMENT FOR RF BIST APPLICATION42 |

| 3.1    | Prop   | osed Methodology42                             |

|        | 3.1.1  | Calibration Phase43                            |

|        | 3.1.2  | Measurement Phase                              |

| 3.2    | BIST   | Circuit Implementation46                       |

| 3.3    | Expe   | erimental Results                              |

|        | 3.3.1  | Simulation Results                             |

|        | 3.3.2  | Hardware Measurment Results                    |

|        | 3.3.3  | Test Time and Hardware Overhead54              |

| 3.4    | Conc   | clusion56                                      |

| 4 BIST | CIRCU  | JITS FOR LOOPBACK CONNECTION                   |

| 4.1    | Prop   | osed BIST Architecture                         |

|        | 4.1.1  | BIST Circuit for Loop-Back Connection          |

|        | 4.1.2  | BIST Circuit for Transmitter Gain              |

| 4.2    | Expe   | primental Results                              |

|        | 4.2.1  | BIST Hardware Demonstration                    |

# CHAPTER 43 5 ACCURATE ON-CHIP RF PHASED ARRAY CHARACTERIZATION WITH 5.1 5.2 Phase I: BIST Self-Loop......69 5.2.1 522 5.2.3 Phase III : Phase Mismatch Calculation ......71 5.3 5.3.1 Design of BIST input.....77 5.3.2

Page

| 5.4 | Expe  | erimental Results               | .78 |

|-----|-------|---------------------------------|-----|

|     | 5.4.1 | Simulation Results              | .78 |

|     | 5.4.2 | BIST System Design              | .81 |

|     | 5.4.3 | RF Phased Array PCB Design      | .82 |

|     | 5.4.4 | Hardware Measurement Test Setup | .83 |

|     | 5.4.5 | Test Time and Hardware Overhead | .91 |

## 5.5

# 6 PROCESS INDEPENDENT GAIN MEASUREMENT WITH LOW

| OVERHEAD | VIA BIST/DUT | CO-DESIGN | 94 |

|----------|--------------|-----------|----|

|          |              |           |    |

| 6.1 | BIST Circuit And Methodology | .94 | 4 |

|-----|------------------------------|-----|---|

|-----|------------------------------|-----|---|

| 6.2 BIS        | T/DUT Co-Design                 |     |

|----------------|---------------------------------|-----|

| 6.2.1          | Design Methodology              | 98  |

| 6.2.2          | Circuit Implementation          |     |

| 6.3 Exp        | erimental Results               | 101 |

| 6.3.1          | Simulation Results              | 102 |

| 6.3.2          | Hardware Measurement Results    | 104 |

| 6.3.3          | Test Time and Hardware Overhead | 107 |

| 6.3.4          | Comparison with Prior Work      | 109 |

| 6.4 Con        | clusion                         | 109 |

| 7 SUMMARY      | AND CONCLUSION                  | 111 |

| REFERENCES     |                                 | 115 |

| APPENDIX       |                                 |     |

| A. AM/AM AND A | M/PM DISTORTION MEASUREMENT     | 120 |

| B. DELAY SKEW  | AND BW LIMITATION MEASUREMENT   |     |

Page

# LIST OF TABLES

| Table | Pa                                                             | ige |

|-------|----------------------------------------------------------------|-----|

| 2.1.  | Monte-Carlo Simulation Results for Loop-Back Path              | .29 |

| 2.2.  | Simulation Results for Polar Transciever Parameters            | .31 |

| 2.3.  | Measurement Results for Receiver Parameters                    | .35 |

| 2.4.  | Measurement Results for Delay Skew                             | .36 |

| 2.5.  | Measurement Results for Envelop BW                             | .38 |

| 2.6.  | Accuracy with On-Chip Loop-Back Delay                          | .39 |

| 3.1.  | BIST Parameter Computation from Simulation                     | .50 |

| 3.2.  | Output Measurement with BIST from Simulation                   | .50 |

| 3.3.  | Monte-Carlo Simulation Results for Output Measurement          | .51 |

| 3.4.  | BIST Output Measurement and Computed Parameters                | .53 |

| 3.5.  | Parameter Computation from Hardware Measurements               | .54 |

| 3.6.  | Area Overhead for RF BIST with IBM 7RF 180nm Process           | .55 |

| 4.1.  | BIST Circuit Measurement Results                               | .60 |

| 4.2.  | Area Overhead Estimate for Loop-Back BIST with 180nm process   | .62 |

| 5.1.  | BIST Parameter Computation for Phased Array from Simulation    | .79 |

| 5.2.  | Gain Computation from Simulation Results                       | .80 |

| 5.3.  | Monte-Carlo simulation Results for Gain measurement            | .80 |

| 5.4.  | Monte-Carlo simulation Results for Phase Mismatch Computation  | .81 |

| 5.5.  | DC Output during Phase I and Phase II                          | .86 |

| 5.6.  | DC output during Phase III and Computation of Phase Difference | .86 |

| 5.7.  | Phase Difference Estimation for Different Arrays               | .90 |

| Table | Pa                                                              | age |

|-------|-----------------------------------------------------------------|-----|

| 5.8.  | Resolution Analysis with Different Number of Bits               | .91 |

| 5.9.  | Area Overhead Estimate with IBM 7RF process                     | .93 |

| 6.1.  | LNA Specifications1                                             | 02  |

| 6.2.  | LNA Simulation Results1                                         | .03 |

| 6.3.  | Performance Comparison: Standalone LNA vs. LNA with BIST1       | 07  |

| 6.4.  | Accuracy Comparison: Proposed Technique vs. Traditional Method1 | 07  |

| 6.5.  | Area Overhead Estimate with IBM 180 nm Process1                 | 08  |

| 6.6.  | Summary of Prior Work (Detector Only)1                          | .09 |

|       |                                                                 |     |

| LIST | OF | FIG | URES |

|------|----|-----|------|

|      |    |     |      |

| Figure                                                            | Page |

|-------------------------------------------------------------------|------|

| 2.1. Polar Transceiver Architecture                               | 11   |

| 2.2. Polar Transceiver with the Impairments in the Loop-Back Mode | 13   |

| 2.3. PA Supply Input Versus Receiver Output                       | 23   |

| 2.4. Flow Chart for BIST Algorithm                                | 27   |

| 2.5. Graph for Estimation of M                                    | 27   |

| 2.6. Circuit Topology for Loop-Back Path                          | 29   |

| 2.7. Monte-Carlo Simulation Results                               | 31   |

| 2.8. Implemented Polar Transceiver                                | 32   |

| 2.9. Measurement Setup for Clock Synchronization                  |      |

| 2.10. Experimental Setup for Polar Transceiver Characterization   | 34   |

| 2.11. FFT Results of the Output of the Receiver                   | 35   |

| 2.12. Measurement Results for Verification                        |      |

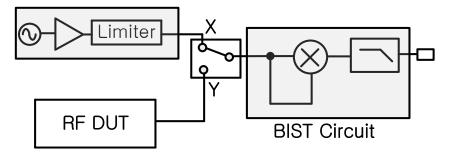

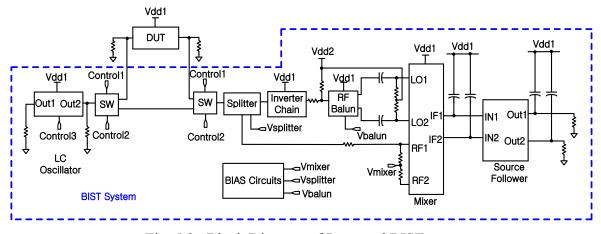

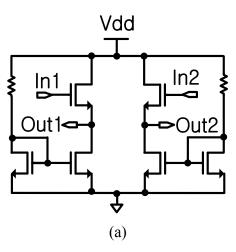

| 3.1. BIST System for an Amplitude Measurement                     | 43   |

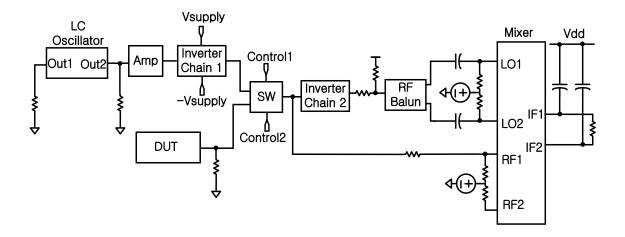

| 3.2. Test Bench for Entire BIST System                            | 47   |

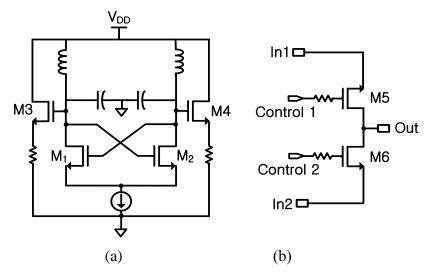

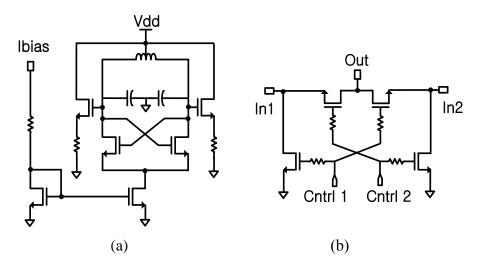

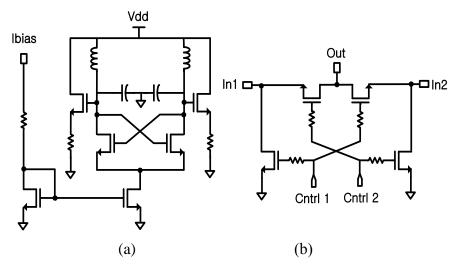

| 3.3. Circuit Topology of (a) LC Oscillator (b) RF Switch          | 47   |

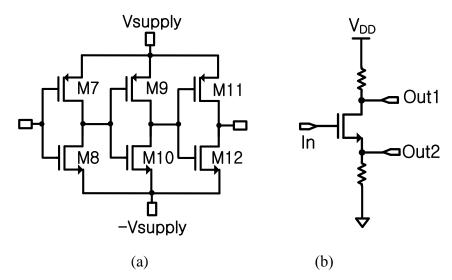

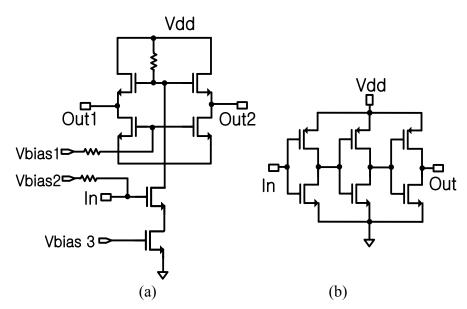

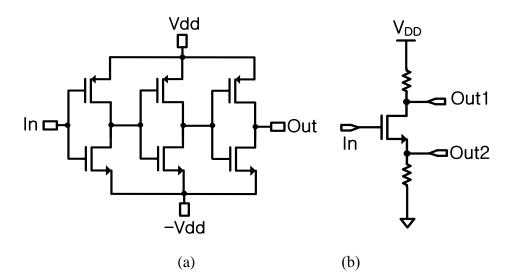

| 3.4. Circuit Topology of (a) Inverter Chain (b)Active balun       | 48   |

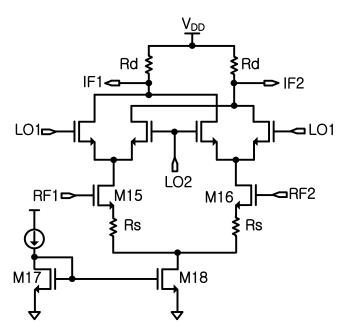

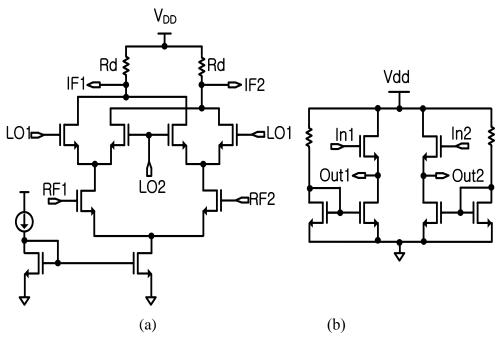

| 3.5. Circuit Topology of Gilbert Cell Mixer                       | 49   |

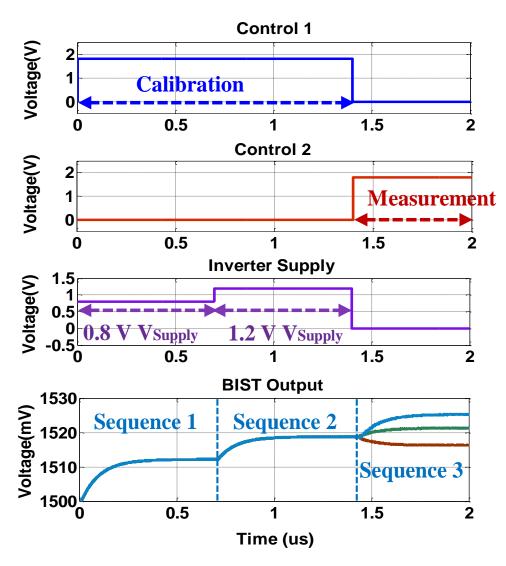

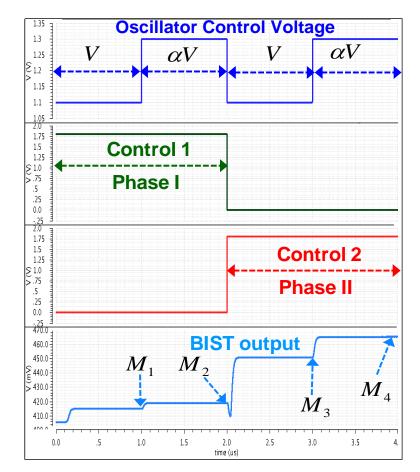

| 3.6. Transient Analysis in Cadence Simulation                     | 51   |

| 3.7. Implemented BIST Circuit for Hardware Experiments            |      |

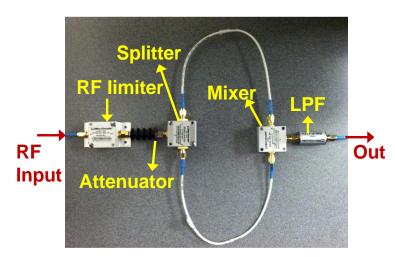

| 3.8. Measurement Setup Experiments                                | 53   |

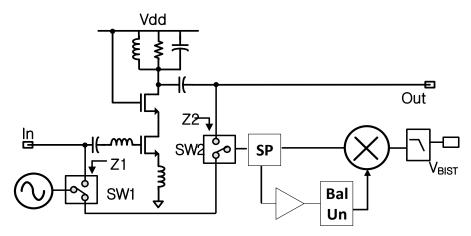

| 4.1. Proposed BIST Circuit in the Loop-Back Mode                  | 58   |

| Figure                                                                  | Page |

|-------------------------------------------------------------------------|------|

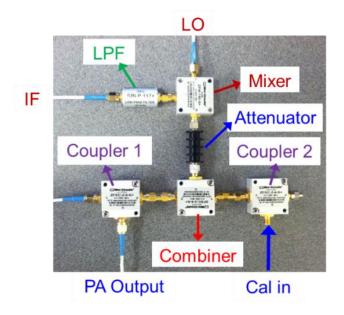

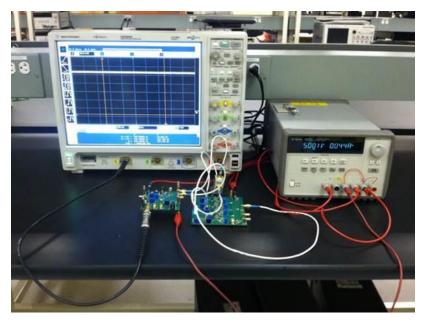

| 4.2. Hardware Demonstration for the Proposed BIST Circuit               | 59   |

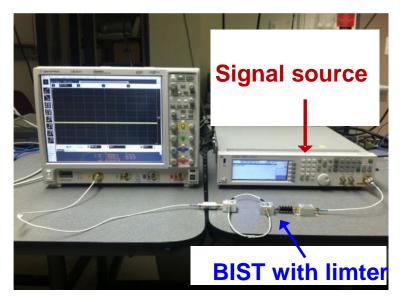

| 4.3. Experimental Setup for the Proposed BIST Circuit                   | 60   |

| 5.1. Block Diagram of Phased Array Receiver                             | 64   |

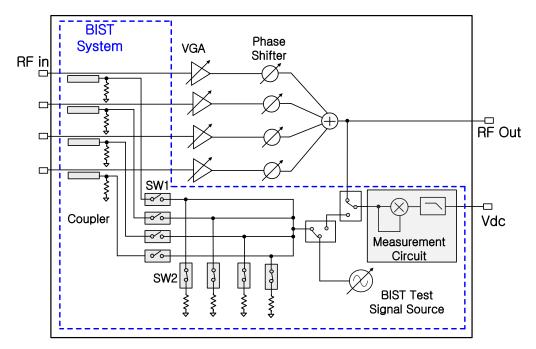

| 5.2. Block Diagram of Proposed BIST for Phased Array                    | 67   |

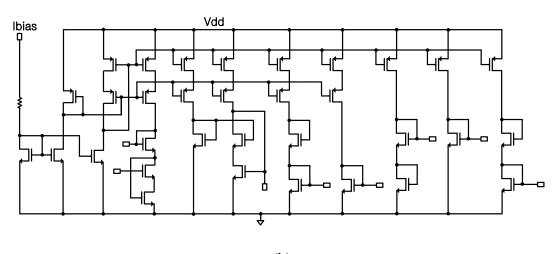

| 5.3. Block Diagram of Proposed BIST System                              | 73   |

| 5.4. Circuit Topology of (a) LC Oscillator (b) RF Switch                | 73   |

| 5.5. Circuit Topology of (a) Active Splitter (b) Inverter Chain         | 74   |

| 5.6. Circuit Topology of (a) Active Balun (b) Glibert Cell Mixer        | 75   |

| 5.7. Circuit Topology of (a) Source Follower (b) Biasing Circuits       | 76   |

| 5.8. Circuit Topology of (a) BIST Input Circuits (b) SPST RF switch     | 78   |

| 5.9. Transient Analysis in Cadence Simulation                           | 79   |

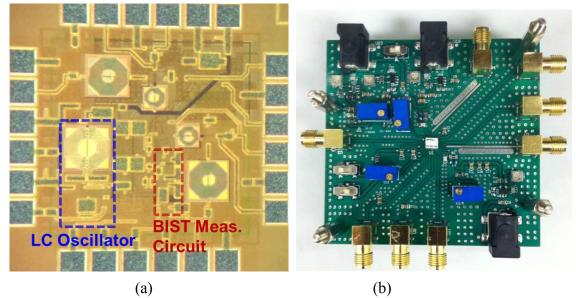

| 5.10. BIST System (a) Chip Microphotograph (b) Evaluation PCB           | 82   |

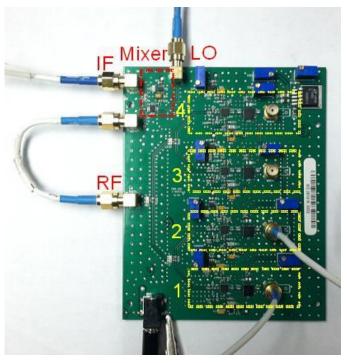

| 5.11. RF Phased array PCB                                               | 83   |

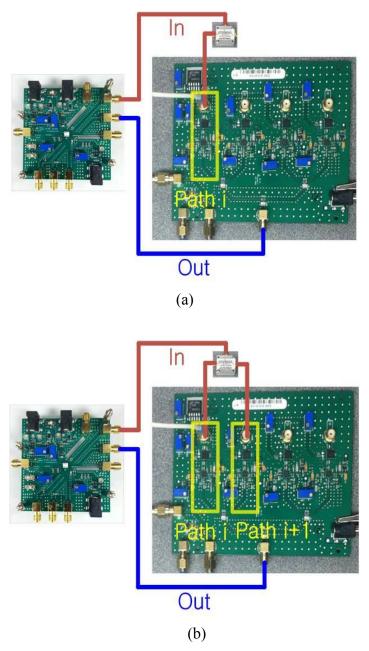

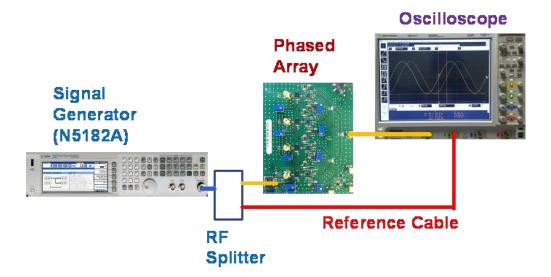

| 5.12. Test Set-up:(a) Gain Measurement (c) Phase Difference Measurement | 85   |

| 5.13. Test Set-up for the Proposed Phased Array BIST Technique          | 87   |

| 5.14 Test Set-up for the Traditional Phase Mismatch Measurement         | 88   |

| 5.13. Test Set-up for the Proposed Phased Array BIST Technique   | .87 |

|------------------------------------------------------------------|-----|

| 5.14. Test Set-up for the Traditional Phase Mismatch Measurement | .88 |

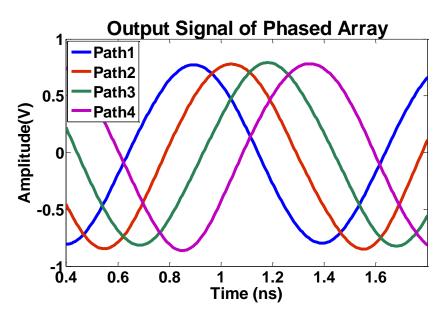

| 5.15. Output Signal of Each Path during Verification             | .88 |

| 6.1. BIST System with an LNA as the DUT                          | .95 |

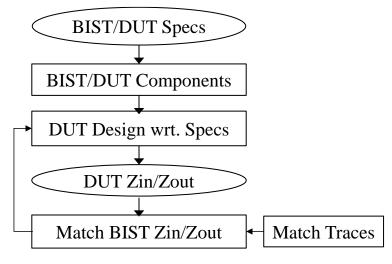

| 6.2. BIST/DUT Co-Design Flow                                     | .98 |

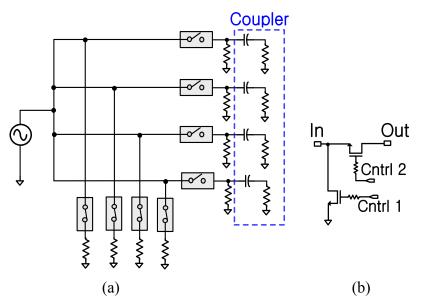

| 6.3. Circuit Topology of (a) LC oscillator (b) RF switc          | 100 |

| 6.4. Circuit Topology of (a) Inverter (b) Active Balun1          | 101 |

|                                                                  |     |

# Figure

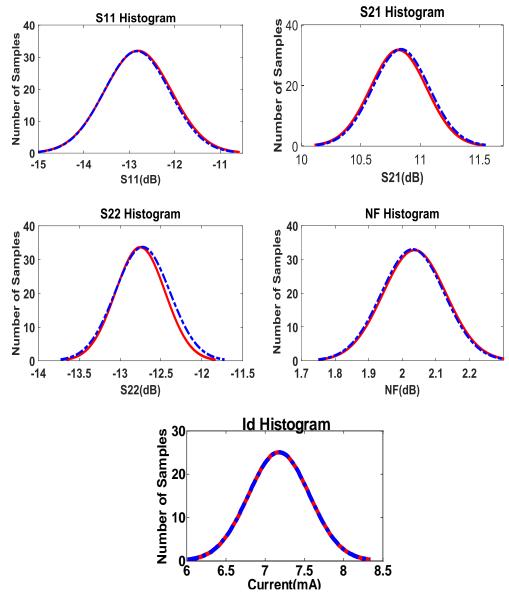

| 6.6. Monte-Carlo Simulation Results (Dashed Line: Stand-alone LNA, Solid line: | LNA |

|--------------------------------------------------------------------------------|-----|

| with BIST)                                                                     | 104 |

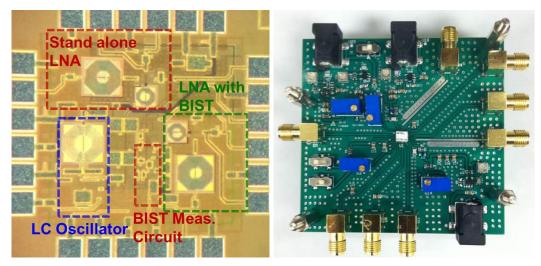

| 6.7. BIST/DUT IC (a) Fabricated Chip with Standalone LNA and LNA with BIST     | (b) |

| Evaluation PCB for Both LNAs                                                   | 105 |

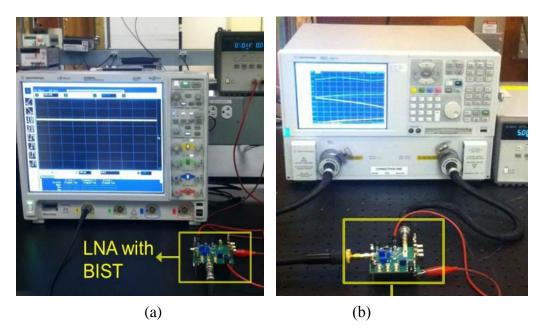

| 6.8. Measurement Setup (a) with BIST Output, which is DC, (b) for S-parameter  |     |

| Measurement to Compare the Two LNAs                                            | 106 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Outline of Dissertation

Continuous demand for RF system-on-chip (SoC) devices has fueled the integration of various RF components, such as power amplifier (PA), low-noise amplifier (LNA), and mixer, together with the baseband, analog, and digital subsystems into a single chip. However, this level of integration, while essential to meet increasing performance/power requirements, brings about challenges in terms of test and calibration of RF devices. Production test process for RF SoCs requires high caliber digital testers equipped with RF enabled instrumentation, increasing the total cost.

Several techniques in the literature aim to reduce the dependence on external RF instrumentation for low cost testing [1-17]. In [1-3], simple test signals such as multi-tone sinusoidal signals, are used to generate output data, where the performance of RF transceiver is predicted using the output data as well as machine learning methods. Another well-known test technique is loop-back based testing. In [4-9], the loop-back configuration is used to characterize both the transmitter and the receiver. In [4, 5], the authors derive the analytical model for the entire loop-back path and use numerical techniques in order to solve transmitter and receiver parameters simultaneously. In [6], authors use similar mathematical models with specialized signals in order to achieve an analytical solution. In [7], transceiver parameters are predicted using statistical learning, and in [8] embedded sensors are used together with statistical learning to improve prediction accuracy. In [9], most transceiver parameters are decoupled to characterize the entire system. While system-level testing and loop-back reduces the go/no-go testing burden significantly, some

parameters, such as linear gain, cannot be decoupled in the loop-back mode no matter what input signal is used due to linear dependencies. This hampers system-level calibration techniques [18] that rely on absolute complex coefficients of the system rather than ratiometric performance parameters, such as third or fifth order input intercept. Moreover, for RF circuit-level calibration, more fine-grained characterization may be necessary [19, 20]. Hence, robust RF BIST (Built-in Self-Test) methods are needed to measure parameters of individual blocks that can be independently calibrated. It has been shown through extensive hardware experiments that when RF blocks can be characterized in terms of performance, one-shot methods can be used to accurately calibrate devices without the need for iterations at the system level [21].

In this dissertation, RF BIST methods for advanced RF transceiver such as RF polar transceiver and RF phased array are proposed. In addition, robust amplitude and gain measurement for RF BIST application are proposed and discussed.

In chapter 2, a comprehensive BIST solution for RF polar transceiver is proposed. Among the RF transceivers, the polar transceiver architecture is a promising solution for future wireless communication systems in terms of power efficiency. In the polar transmitter, the In-phase/Quadrature (I/Q) signal is converted to polar form and divided into an amplitude component and a phase component. The amplitude component is used as an envelope to modulate the supply voltage of the PA while the phase component modulates the high frequency carrier directly, which leads to a constant amplitude signal at the input of the PA. Since the PA's supply voltage is modulated based on the amplitude of the PA output, it saves power, thus achieving significantly high efficiency [22]. The receiver in the polar transceiver is typically a traditional IQ receiver which consists of identical in-phase and quadrature paths.

Although polar transceivers provide high efficiency, their performance suffers from unavoidable inherent impairments, namely, gain and phase mismatches in the receiver, differential delay skew between the envelope and phase signals, and limited envelope bandwidth in the transmitter. Additionally, nonlinear behavior of the PA between supply voltage and PA output is still a problem. Hence, accurate measurement and calibration of the above impairments are essential to ensure operational compliance. At the high level, testing of the polar transceiver is same as testing of Cartesian transceiver. A modulated signal is applied to the input of the transmitter and spectral density at several offset frequencies, EVM, and output power are characterized using vector signal analyzers [23]-[24]. For the receiver, an RF modulated signal is applied to the input of the RF receiver and then sensitivity and selectivity can be determined by measuring Signal-to-Noise-Ratio (SNR) or Bit Error Rate (BER). However, such performance-based characterization does not lend to easy calibration since the required parameters are not directly measured. Instead, the system performances are optimized by trial and error, using a search process. For example, regarding the delay skew in the transmitter, the baseband signal is delayed stepby-step fashion until best performance is found [25]. Unfortunately, such an iterative search process for calibration significantly increases test cost since it can take several seconds [25]. This is particularly true for delay skew since the range of possible skew values can be large and this parameter needs to be tuned with acceptable accuracy. As an example, for the GSM-EDGE specification, the tolerable delay skew is 50 ns [23] while the search range

for delay skew is [0-500 ns], requiring at least 7 binary steps to find the optimum skew calibration point [23].

In order to calculate specific internal parameters of polar transceivers, the entire is modeled and analytical formulations along with a system parameter suppression/enhancement algorithm is used [26], [27]. In addition, target parameters in the receiver as well as the transmitter are determined using the loop-back configuration. Since the loop-back signals differ from the RF signal, specialized test signals are determined to de-embed each parameter of interest. This de-embedding is based on analytical derivations that can be computed within several milliseconds using the baseband digital signal processor (DSP). Removal of external RF equipment enables significant test cost reduction. Experimental results confirm that the gain and phase mismatches in the receiver, delay skew and the AM bandwidth in the transmitter can be determined with low-cost implementation.

In Chapter 3, a technique for robust amplitude measurement is proposed. RF amplitude measurement has been the focus of significant prior work. Generally an RF-to-DC or RF-IF conversion is used for the measurement and a single sinusoidal RF generator is used to generate the input signal. Most research in this domain has focused on the measurement side via the use of peak or power detectors [10-15]. Two kinds of RF detectors are widely used to measure RF circuit performance. The RF root mean square (RMS) detector relies on the quadratic relationship between the RF input and RF output of the device under test (DUT) [10-13]. The output of the detector is a DC voltage proportional to the amplitude of the detector's input signal. Hence, two identical detectors should be placed at the input and output of the DUT in order to accurately measure the DUT gain. Another popular detector

is an RF envelope detector [14, 15] that relies on a simple rectifier and low-pass filter. If the input is a simple sinusoidal waveform, the detector will yield the amplitude of the signal. Unfortunately, detectors are subject to the same process variations as the DUT, with their gain and DC offsets differing quite widely over process corners.

Gain measurement can be made relative to the input/output amplitudes. Hence, it does not necessarily require the knowledge of absolute signal amplitudes. However, such detectors cannot be used for the measurement of the absolute amplitude of the signal. Existing RF power/amplitude measurement techniques require an initial characterization phase involving RF instrumentation. However, the behavior of these circuits also drifts with in-field wearout, use, and environmental conditions. Hence, a robust, self-calibrating BIST circuit is necessary to enable RF power/amplitude measurements not only during initial production phase, but also in the field as the circuit is subjected to different conditions.

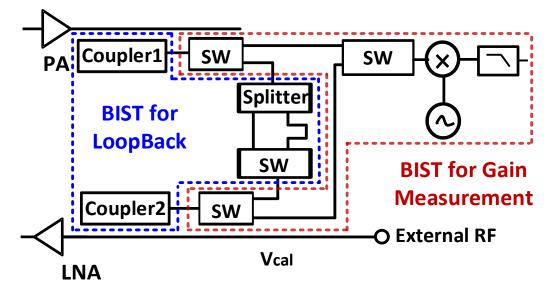

In Chapter 4, BIST system for loopback connection is proposed. The RF transceiver contains two paths with complimentary operation, namely a transmitter and a receiver, which can be placed in a loop-back configuration. Naturally, loop-back based testing of RF transceivers has attracted a lot of attention [5]–[8]. Hence BIST hardware support components are designed and analyzed in terms of area overhead, performance impact, and accuracy.

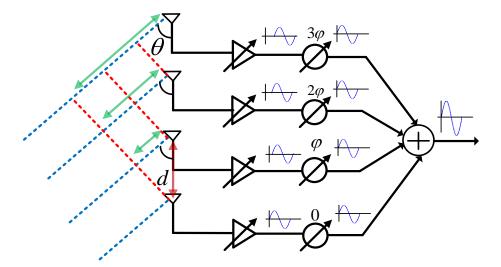

In Chapter 5, BIST for RF phased array is introduced and discussed. It is progressively more difficult to improve spectral efficiency using pure time and frequency domain methods. Recently, utilization of the spatial dimension to improve spectral efficiency has attracted much attention. The spatial dimension can be used by directing the RF beam according to the signal frequency. An RF phased array is a special case of a system that uses the spatial dimension. Contrary to a fixed directional antenna system, the phased array enables controlling the beam direction electronically. Phased arrays provide high signal-to-noise ratio (SNR) and directivity [28], [29] and have been used in communication systems for space and military applications [30], car radars, and high-speed point-to-point systems [31], [32].

Since the primary function of the phased array is to shift the phase of the incoming signal, this parameter is of utmost importance. Unfortunately, due to increasing process variations during fabrication, it is increasingly more difficult to match the phases of the elements perfectly. Even a few degrees of error can be detrimental to the phased array operation. Hence, it is absolutely imperative that the phase mismatch of the elements is calibrated, which requires a measurement/calibration approach that involves high frequency signals. Traditionally, measurement of phase and gain mismatch requires the use of an RF network analyzer. Using this equipment, the amplitude and phase of S-parameters are measured and the mismatches are calculated. While a network analyzer is a common piece of test bench equipment, it is an expensive enhancement to the automatic test equipment (ATE). Furthermore, if an RF mixer is integrated on the phased array path in an effort to bring down the measurement signal frequency, the frequency of the RF input signal is different than the frequency of the baseband signal. In such a down-conversion system, it is not easy to define an absolute phase shift between the input and the output signal, and the phase mismatch between phased array elements still needs to be measured and calibrated. High performance synchronized instrumentation, which can simultaneously generate and analyze signals, is required to measure the phase shift of signals with different frequencies. An instrument that includes this capability increases the cost of the ATE.

Built-in self-test (BIST) is an alternative to lower the test cost by shifting some of the burden to the chip. BIST also brings about the added benefit of in-field calibration, as the use and environmental conditions shift the parameters of the phased array. The additional circuits for test purposes should not affect the performance of the existing RF circuits. This can be enabled by the use of RF couplers rather than RF switches to enable the BIST operation. More importantly, since the BIST circuit is integrated with the circuit under test (CUT), its parameters are also unknown. The test technique should not rely on the knowledge of these parameters. In addition, the test results using the BIST technique should still provide high accuracy compared with the traditional technique using expensive RF equipment.

Various methods to test the phased arrays exist in literature. In [33], [34], the performance of the phased array is tested using an artificial wave front. The wave is generated by feeding the RF inputs to each receiver path via power splitters as well as adjustable phase shifters. The external phase shifters are adjusted until maximum power is reached. At this point, the phase mismatch in the external phase shifters matches the phase mismatch of the phased array. Hence, the phased array phase mismatch is measured in a trial-and-error search manner. This technique is not desirable for high volume production due to the high cost and long test time. In [35], RF signals with a fixed phase are applied to the inputs of two elements, and the output baseband signal is captured for different settings of the phase generators. In this method, the baseband waveforms are measured in time domain using an oscilloscope. However, the phase difference is manually measured

in the time domain, which is not appropriate for a BIST operation. In [36], [37], the BIST method for a phased array RFIC is proposed. The BIST test signal is coupled to all the antenna ports using a 20 dB coupler and a pair of full receivers is integrated on-chip to measure the amplitude and phase of the injected signal, thus determining the channel vector response. In this technique, the output signal is a DC value, since the frequency of the RF test signal is same as the frequency of the receiver local oscillator (LO). However, the circuits in the phased array may include a DC offset, which is unknown, and hence degrade the accuracy of the measurement. This technique also requires large area overhead because two full receivers and an external RF source need to be embedded on the. Moreover, since signals are not combined until the end of the full receiver paths, any mismatch in the receiver paths degrades the accuracy of the accuracy of the measurement.

In [38], the authors propose a test solution for multi-input, multi-output RF systems (MIMO), which have similar parameters to the phased arrays. However, since the intended application is production test, all test signals are assumed to have known amplitude/phase relations and the capture and analysis are done via external equipment. Hence, a new BIST method and the associated circuitry are proposed in order to measure the phase mismatch of the phased array using signals with unknown amplitudes.

In Chapter 6, a technique on process independent gain measurement is proposed via BIST/DUT co-design. RF detectors are subject to the same process variations as the DUT, with their gain and DC offsets differing quite widely over process corners. Gain measurement can be made relative to the input/output amplitudes. Hence, the knowledge of absolute signal amplitudes is not required. However, we cannot assume that the parameters of the detector circuit are known. Even for two identical detectors [10], [11],

[19], within-die mismatch for active devices generates unpredictable DC offsets, which introduces errors in measurements.

Another major issue with RF BIST is the impact on DUT performance due to the additional BIST circuit. Even when BIST can generate accurate results with low area overhead, it is frowned upon by designers due to the parasitics introduced by the BIST circuit that alters the DUT performance. This is particularly troublesome when contact-based BIST is used (e.g. driving the input and sensing the output directly). In [39], the authors show that the performance degradation due to BIST for an LNA is about 1dB for gain, and can be up to 8dB for S11. In this chapter, a BIST solution that is robust with respect to process variations is proposed to determine the gain of an RF DUT.

#### CHAPTER 2

# A COMPREHENSIVE BIST SOLUTION FOR POLAR TRANSCEIVERS USING ON-CHIP RESOURCES

Most communications systems use variable amplitude signals, which necessitate the use of linear PAs with low efficiency. The discrepancy between the output signal level and the supply voltage, which is dissipated as heat, causes the loss in efficiency. This leads to poor battery life and increases heat around the PA, causing reliability concerns. As a solution to this problem, the RF polar transceiver architecture has been proposed.

# 2.1 Polar Transceiver Overview

## 2.1.1 Overview of the Polar Transceiver

In polar transmitters, the baseband DSP converts the baseband I(t) and Q(t) data to polar form, as in Eqn. (2.1) and modulates the carrier with this information, as in Eqn. (2.2). From a modulated signal perspective, this polar-modulated RF signal is mathematically equivalent to the Cartesian modulated RF signal, shown in Eqn. (2.3). Hence, the polarmodulated signal can be received and down converted using a traditional Cartesian receiver.

$$A(t) = \sqrt{I(t)^{2} + Q(t)^{2}} \qquad \varphi(t) = \tan^{-1} \left( \frac{Q(t)}{I(t)} \right)$$

(2.1)

$$V_{RF}(t) = A(t) \cdot \cos(\omega_c t + \varphi(t))$$

(2.2)

$$V_{RF}(t) = I(t) \cdot \cos(\omega_c t) + Q(t) \cdot \sin(\omega_c t)$$

(2.3)

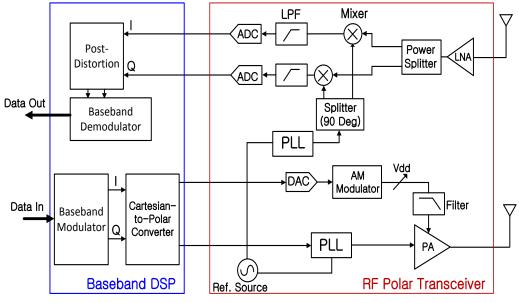

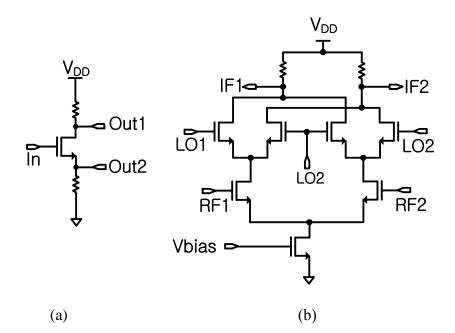

Fig. 2.1. Polar Transceiver Architecture.

Fig. 2.1 shows a typical RF polar transceiver architecture which consists of polar transmitter and IQ receiver. In the transmitter of Fig.2.1, the IQ signal information is converted into a constant amplitude high frequency carrier which is modulated with the phase of the baseband signal, and a low frequency envelope signal which is equal to the magnitude of the original complex IQ signal. The envelope signal is used to modulate the supply of the PA, while the phase modulation is conducted within a phase-locked loop (PLL). The envelope and phase components of the signal are divided into two completely different paths and they must arrive at the PA where they are mixed at exactly the same time. The receiver is implemented using the LNA, mixers, low pass filters, and PLL. Because the receiver includes I and Q paths, in-phase and quadrature component of the RF input signal are recovered at the receiver output.

#### 2.1.2 RF Impairments in the Polar Transceiver

Ideally, the transmitter has to send RF modulated signal which satisfies spectral mask and EVM requirements with high efficiency while the receiver needs to recover in-phase and quadrature components from the RF input signal. Impairments due to the non-linear nature of the underlying devices as well as process variations cause distortion in the transmitted and received signals.

In the transmitter, delay skew between the envelope path and the phase path is detrimental to the operation of the transceiver [40]. As an example, a 100 ns delay skew alone can cause the EVM-EDGE polar transmitter to fail its spectrum mask specifications [23]. In addition to delay skew, a low pass filter (LPF) is located in the envelope path in order to prevent leakage from the supply modulator [25] and it has limited bandwidth (BW). This BW limitation of the envelope signal causes distortion of the RF signal at PA output because the envelope signal may have a high BW compared to filter bandwidth. Nonlinearity of PA with respect to the supply voltage also results in additional distortion. Among these three sources, the delay skew is the most significant contributor to distortion and must be compensated for the transmitter to function. [23], [25]. Envelope bandwidth may also be calibrated by tuning filter components [41], hence suppressing its contribution to the signal distortion. PA non-linearity needs to be characterized and may be compensated using advanced techniques of pre-distortion [42] or post production tuning [43].

In the receiver, process variations cause gain mismatch as well as phase mismatch, which degrade the quality of the received signal [5], [44]. These two impairments can be compensated using post-distortion [43]. More importantly, receiver impairments need to be characterized and calibrated prior to transmitter characterization in the loop-back mode.

There is currently no published work to characterize and de-embed both the transmitter and receiver impairments in the loop-back mode.

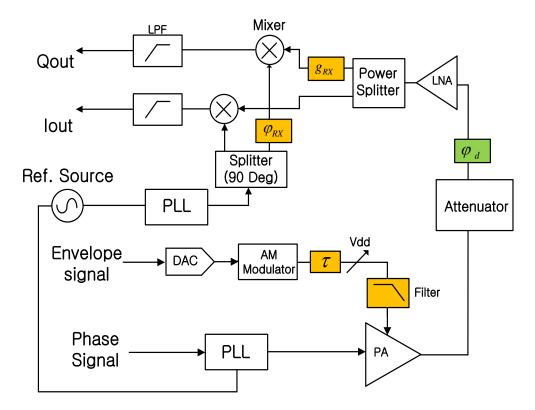

Fig. 2.2. Polar Transceiver with the Impairments in the Loop-Back Mode.

## 2.2 Test Methodology

In order to develop a technique to measure the target parameters of the transmitter and the receiver, first the transceiver in the loop-back mode needs to be configured. As shown in Fig. 2.2, the output of the PA is connected to the input of the low noise amplifier (LNA) through an attenuator. The RF input of the receiver is down converted to the baseband trough the mixer. The down converted signal is digitized through the ADC and the signal is converted to frequency domain using Fast Fourier Transform (FFT). After taking the FFT, spectral analysis is performed in order to determine the internal parameters. In this chapter,

a BIST solution for the characterization of the entire path is proposed in a step-by step fashion.

## 2.2.1 Receiver Gain and Phase Mismatch Measurements

Gain and phase mismatches between I and Q channels degrade the performance of the receiver. In order to use digital compensation techniques, gain imbalance needs to be measured within 1% error and phase imbalance needs to be measured within 1° error [45].

The proposed technique uses the baseband output signal of the receiver in the loopback mode. Even though the polar transceiver uses a variable envelope signal, the baseband parameters can be set such that a single-tone signal will appear at the PA output, transforming the polar transmitter into a single-tone signal generator. Hence, transmitter impairments in terms of delay skew, envelope BW limitation, or PA nonlinearity will not distort this single tone signal and it can be used for receiver characterization. This signal can be obtained by applying a DC signal for the I(t) and Q(t) input of the polar transmitter, making A(t) and  $\varphi(t)$  in Eqn. (2.1) constant terms. In the loop-back mode, the receiver outputs are also DC signals, given by Eqn. (2.4) and (2.5).

$$I_{out} = \frac{1}{2} \times A_{in} G_{RX} G(v_{dd1}) \cdot \cos(\varphi(v_{dd1}) + \phi + \varphi_d) + DC_I$$

$$(2.4)$$

$$Q_{out} = \frac{1}{2} \times A_{in} G_{RX} (1 + g_{RX}) G(v_{dd1}) \cdot \sin(\varphi(v_{dd1}) + \phi + \varphi_d + \varphi_{RX}) + DC_Q$$

(2.5)

Where  $A_{in}$  is the input of the polar transmitter, GRX is the gain of the receiver,  $\varphi(vdd1)$  is the phase of the PA,  $\phi$  is additional delay from RF path and LO path,  $g_{RX}$  is gain mismatch,  $\varphi_{RX}$  is phase mismatch between I and Q channel,  $\varphi d$  is the delay in the loop-back path, and  $DC_I$  and  $DC_Q$  are additional DC offsets.

As expressed in Eqns. (2.4) and (2.5), the direct-conversion receivers suffer from the additional DC offsets (DCI and DCQ) because a fraction of the LO signal leaks to the RF port of the mixer due to finite isolation between LO port and RF port. This finite amount of the LO leakage is mixed with the LO signal again, which is called "LO self-mixing". The LO self-mixing generates a DC component which is unknown and combine it with the DC value that is generated by phase and gain mismatches.

From Eqn. (2.4) and Eqn. (2.5), the contribution of the input signal is dependent on amplitude of the input signal. However the DC offset remains constant because LO leakage is not dependent on the amplitude of input signal. In addition, all other DC offsets in the path are a function of process variation, but not a function of the input signal. Hence if two test signals with different amplitudes are used, it is possible to obtain two linearly independent equations to solve for the DC offset term as well as the term related to the input signal. There are multiple ways to generate two different amplitudes at the receiver input. The baseband input amplitude at the transmitter could be changed. However, this would change the supply voltage and also change the phase shift through the PA which would cause uncertainty. Therefore, this simple way of amplitude control is not desirable. An alternate way of generating two different amplitudes is through the loop-back path with a variable attenuator. Of course, in this case, the attenuator through the loop-back path must be treated as an unknown. Hence any knowledge on the input amplitudes,  $A_1$  and  $A_2$  for parameter calculation cannot be assumed. With these two inputs, if the differences of output DC measurements are taken, the DC offset term will disappear as in Eqn. (2.6) and Eqn. (2.7).

$$I_{out,2} - I_{out,1} = \frac{1}{2} (A_2 - A_1) \cdot G_{RX} G(v_{dd1}) \cdot \cos(\varphi(v_{dd1}) + \phi + \varphi_d)$$

(2.6)

$$Q_{out,2} - Q_{out,1} = \frac{1}{2} (A_2 - A_1) \times G_{RX} (1 + g_{RX}) G(v_{dd1}) \\ \times \sin(\varphi(v_{dd1}) + \phi + \varphi_d + \varphi_{RX})$$

(2.7)

However, this equation still contains a number of unknowns such as  $A_1$ ,  $A_2$ ,  $\varphi(v_{dd1})$ ,  $\phi$ ,  $\varphi d$ , in addition to the impairment parameters,  $g_{RX}$ , and  $\varphi_{RX}$ . In order to decouple the target parameters from the additional unknowns, more information needs to be generated. Note that measurement  $M_1$  and  $M_2$  have non-linear dependency on  $\phi_{tot} = \varphi(v_{dd1}) + \phi + \varphi_d$  as well as  $\varphi_{RX}$ . In order to generate more information, the parameter  $\phi_{tot}$  needs to be adjusted in a predictable manner. Luckily, this can be done using the loop-back path, which is not part of normal operation mode. The loop-back path can be switched between two traces with different lengths without affecting the performance of the transmitter, with a predictable phase difference of  $\Delta \varphi_d$ . This phase difference depends on the difference in trace length, and can be realized within 0.1% error. Thus Eqns. (2.6) and (2.7) are the difference in I and Q (with two input levels) outputs with one loop-back delay, and Eqns. (2.8) and (2.9) are the difference in I and Q outputs with the same two input levels but different loop-back delay.

$$I_{out,4} - I_{out,3} = \frac{1}{2} (A_2 - A_1) \cdot G_{RX} G(v_{dd1}) \cdot \cos(\varphi(v_{dd1}) + \phi + \varphi_d + \Delta \varphi_d)$$

(2.8)

$$Q_{out,4} - Q_{out,3} = \frac{1}{2} (A_2 - A_1) \times G_{RX} (1 + g_{RX}) G(v_{dd1}) \\ \times \sin(\varphi(v_{dd1}) + \phi + \varphi_d + \Delta \varphi_d + \varphi_{RX})$$

(2.9)

With the two input amplitudes set at  $A_1$  and  $A_2$ , and the two loop-back delays with a phase difference of  $\Delta \varphi_d$ , two additional measurements can be obtained if Eqn. (2.8) is

divided by Eqn. (2.6) and Eqn. (2.9) is divided by Eqn. (2.7). The resulting expressions will also be independent of the input signal amplitude which is a quantity that cannot be predicted with high accuracy since it depends on the power amplifier gain and synthesizer output voltage. The results are given by Eqn. (2.10) and Eqn. (2.11) as follows.

$$\varphi(v_{dd1}) + \phi + \varphi_d$$

$$= \tan^{-1} \left( \frac{-(I_{out4} - I_{out3}) / (I_{out2} - I_{out1}) + \cos(\Delta \varphi_d)}{\sin(\Delta \varphi_d)} \right)$$

(2.10)

$$\varphi(v_{dd1}) + \phi + \varphi_d + \varphi_{RX}$$

=  $\cot^{-1}\left(\frac{(Q_{out4} - Q_{out3})/(Q_{out2} - Q_{out1}) - \cos(\Delta \varphi_d)}{\sin(\Delta \varphi_d)}\right)$  (2.11)

The phase mismatch is determined by subtracting (2.10) from (2.11) and given by (2.12) as follows.

$$\varphi_{RX} = \cot^{-1} \left( \frac{(Q_{out4} - Q_{out3}) / (Q_{out2} - Q_{out1}) - \cos(\Delta\phi)}{\sin(\Delta\phi)} \right) - \tan^{-1} \left( \frac{-(I_{out4} - I_{out3}) / (I_{out2} - I_{out1}) + \cos(\Delta\phi)}{\sin(\Delta\phi)} \right)$$

(2.12)

The gain mismatch is computed next by dividing Eqn. (2.7) by Eqn. (2.6) and given by Eqn. (2.13) as follows.

$$g_{RX} = \frac{Q_{out,2} - Q_{out,1}}{I_{out,2} - I_{out,1}} \times \frac{\cos(\varphi(v_{dd1}) + \phi + \varphi_d)}{\sin(\varphi(v_{dd1}) + \phi + \varphi_d + \varphi_{RX})} - 1$$

(2.13)

Note that these computations do not require knowledge of the input amplitude or the loop-back attenuation level. As a result, process variations affecting these parameters will not affect the accuracy of the proposed technique.

## 2.2.2 Two-Tone Test in the Loop-Back Mode

In order to determine performance of the transmitter, the effect of the delay skew and limited envelop BW should be analyzed. In prior work, it has been shown that these two parameters cause intermodulation distortion (IMD) [27]. Thus, the simple way to analyze these effects is to use a two-tone signal as the input, as in Eqn. (2.14) and analyze the output of the receiver in the loop-back mode. The resulting PA output is represented as in Eqn. (2.15) in polar form where the amplitude signal and the phase signal are given in Eqn. (2.16). Once the transceiver is configured in the loop-back mode, this signal is down converted to baseband at the output of the receiver. It is noted that both amplitude and phase components are still maintained after down conversion in frequency domain as in Eqn. (2.17).

$$V_{RF}(t) = \frac{1}{2} \left( \cos(\omega_c t - \omega_m t) + \cos(\omega_c t + \omega_m t) \right) = \cos(\omega_m t) \cdot \cos(\omega_c t)$$

(2.14)

$$V_{RF}(t) = \cos(\omega_m t) \cdot \cos(\omega_c t) = a_y(t) \cdot \cos(\omega_c t + \varphi_y(t))$$

(2.15)

$$a_{y}(t) = \left|\cos(\omega_{m}t)\right| \quad \varphi_{y}(t) = \frac{\pi}{2} (1 - c(t))$$

(2.16)

$$V_{RX}(t) = \frac{1}{2} G_{RX} a_y(t) \cdot c(t)$$

(2.17)

A challenge in modeling this system in the loop-back mode is to maintain phase coherence. As Fig. 2.2 shows, while the two PLLs in the transceiver are synchronized by the same reference source, their phase relation will be random every time a measurement is taken. Therefore it is necessary to include a random phase offset in the receiver LO signal that changes at every step. This additional variable prevents us from using any phase-related information.

In order to analyze the impact of delay skew and BW limitation of the transmitter in the loop-back mode, a time delay,  $\tau$ , is injected into the envelope signal and express the envelope signal using a Fourier series. The resulting signal at the output of the receiver can be expressed by Eqn. (2.18).

$$V_{RX \text{ with Delay Skew}}(t) = \frac{1}{2} G_{RX} a_y(t+\tau) \cdot c(t)$$

=  $\frac{1}{2} \cdot \left( a_0 + \sum_{m=2,4,\cdots,M} a_m \cos(m\omega_m(t+\tau)) \right) \cdot \left( \sum_{n=1,3,5,\cdots} c_n \cos(n\omega_m t) \right)$

=  $\frac{G_{RX}}{2} \left( a_0 + a_2 \cos(2\omega_m(t+\tau)) + \cdots + a_M \cos(M\omega_m(t+\tau)) \right)$

$\times \left( c_1 \cos(\omega_m t) + c_3 \cos(3\omega_m t) + \cdots \right)$  (2.18)

Where  $G_{RX}$  is gain of the receiver, am is Fourier coefficient of envelope signal,  $c_m$  is Fourier coefficient of phase signal, and M is number of harmonics included in envelop signal.

Since the envelope signal,  $|\cos(\omega_m t)|$  has sharp discontinuities, the bandwidth of this signal is theoretically infinite. However, the constructed signal has finite frequency components due to the limited bandwidth of reconstruction filter and the supply modulator, which causes IMD. The delay skew between the envelope and the phase signal as well as the PA nonlinearity further increase the IMD levels. The effects of all of these contributors are intertwined and combined in a nonlinear fashion. Thus, they need to be isolated properly in the loop-back mode in order to measure the parameters respectively.

#### 2.2.3 AM/AM and AM/PM Distortion Measurement

The relevant AM/AM and AM/PM distortion for polar transceivers is due to the nonlinear relation between the control voltage and PA output. This nonlinearity causes the violation of spectral mask as well as EVM requirements of the transmitter. Therefore these distortions need to be characterized accurately.

The AM/AM distortion and AM/PM distortion of the PA in the polar transmitter generally are characterized from S-parameter measurements using a vector network analyzer (VNA). The gain and phase of the PA are measured by sweeping supply voltage and measuring amplitude and phase of S21. However, as seen in Fig. 2.2, the PA is integrated in the polar transmitter and the PA input typically is connected to the baseband DSP through the PLL. For measurement using VNA, input and output of the device under test (DUT) should be connected to ports of the VNA. Therefore nonlinearity measurement of the polar transmitter using VNA is not feasible once the PA is integrated into the single chip. In addition, measurement using a high caliber RF instrument such as VNA, is not appropriate for BIST solution.

In order to characterize the PA in the polar transmitter using the proposed BIST solution, the loop-back configuration is desirable, which is already proposed in the previous work. [27] However, in [27], it is assumed that the receiver is ideal, which means that there are no gain and phase mismatches in the receiver. In order to compensate for the gain and phase mismatches of the receiver, the overall signal model must contain this information. With the receiver impairments, the phase and amplitude of the baseband signal at the output of the receiver are given by Eqn. (2.19) and Eqn. (2.20).

Phase =

$$\varphi(v_{dd,n}) + \phi + \varphi_d$$

=  $\tan^{-1} \left( \frac{-\frac{(Q_{out,n,2} - Q_{out,n,1})}{((I_{out,n,2} - I_{out,n,1})(1 + g_{RX}))} + \cos(\varphi_{RX})}{\sin(\varphi_{RX})} \right)$  (2.19)

Amplitude

$$= A_{in}G'_{RX}G(v_{dd,n}) = \frac{2 \times (I_{out,n,2} - I_{out,n,1})}{\cos(\varphi(v_{dd,n}) + \phi + \varphi_d)}$$

$$(2.20)$$

$$(G'_{RX} = G_{RX}\cos(\varphi_{RF} - \varphi_{LO}))$$

Note that with the two-tone test, the effect of random phase mismatch between the transmitter and receiver PLL is eliminated from the equations. The effect of this phase offset is a part of the term  $G'_{RX}$ , which will be treated as an unknown for each separate step. By using comparative analysis, it can be eliminated from calculation. According to Eqn. (2.19), the phase can be calculated from the measured DC values at the receiver output as well as the phase mismatch that is obtained in Eqn. (2.12). Once we calculate the phase, the amplitude of the baseband output can be calculated from Eqn. (2.20). Therefore AM/AM distortion and AM/PM distortion can be characterized in the loop-back mode using the derived equations although the receiver includes phase and gain mismatch.

## 2.2.4 Delay Skew Measurement in the Loop-Back Mode

For delay skew measurements the three contributors to IMD, namely limited envelope BW, nonlinearity of the receiver, and nonlinearity of the PA, need to be isolated. First the effect of the limited BW should be considered. As indicated in Eqn (2.16), the envelope signal has a square wave component, which makes its BW theoretically infinite. However, signal power diminishes as one moves away from the fundamental tone. If a sufficient number of harmonics are included in the final signal, the distortion caused by the BW limitation can be minimized. In order to enable this, M in Eqn. (2.18) needs to be sufficiently large. At around M >10, the distortion contribution of the BW limitation can be ignored. While the BW of the envelope path is not known yet, it is ensured that M is large by using a low-bandwidth envelope signal.

The second contributor which needs to be isolated is nonlinearity of the receiver. The receiver needs to operate in linear region to eliminate its contributors to the IMD levels. The amplitude of the input signal at the receiver should be sufficiently small to ensure linear operation. Luckily, if the input of the LNA is limited to 3-6 dB below the 1 dB compression point, the IMD generated by the receiver will be negligible. Therefore an attenuator between transmitter output and receiver input is used to ensure that the receiver operates in the linear region.

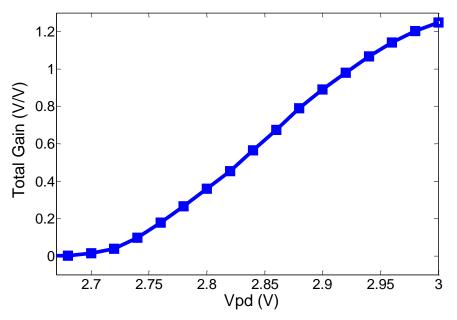

In addition to the receiver, the PA of the transmitter needs to operate at a voltage where the relation between PA gain and PA supply voltage is mostly linear. Note that this is not possible in the normal mode of operation since the supply voltage is determined by the input stimulus. However, during testing, the test input signals can be set. Hence the PA supply voltage can be maintained at the desired level, which corresponds to around the mid-point of the operation, as shown in Fig. 2.3. When the test signal is set with the abovementioned constraints, the major contributor to IMD at the output of receiver will be the delay skew.

Fig. 2.3. PA Supply Input Versus Receiver Output.

However, determining the primary input signal that satisfies all these constraints is not trivial. The two-tone signal response of the transceiver is given by Eqn. (18). This signal however spans a supply voltage level between zero and maximum. This signal will result in PA to generate IMD and corrupt the information for the delay skew measurements. In order to solve this problem, a DC offset needs to be added to the envelope signal and derive the system response with this new input signal. With the DC offset, the output of the receiver can be expressed as in Eqn. (2.21), where the output amplitude and the DC offset are expressed as in Eqn. (2.22).

$$V_{RX,out}(t) = \left(A_{RX,out} \times \left|\cos(\omega_m(t+\tau))\right| + \Delta V_{RX,out}\right) c(\omega_m t)$$

$$A_{RX,out} = G'_{RX} \times \left(G(v_{dd2}) - G(v_{dd1})\right) \times A_{in}$$

$$\Delta V_{RX,out} = G'_{RX} \times G(v_{dd1}) \times A_{in}, \quad G'_{RX} = G_{RX} \cos(\varphi_{RF} - \varphi_{LO})$$

(2.22)

In this response, the highest power intermodulation product is the third order intermodulation distortion (IMD3), which can be calculated using Eqn. (2.23).

$$\frac{|IMD_3|}{A_{RX,out}} = \frac{1}{2} \sqrt{a_3^2 + \left(b_3 + \frac{\Delta V_{RX,out} \times c_3}{A_{RX,out}}\right)^2}$$

(2.23)

Where  $a_3$  and  $b_3$  are Fourier coefficients, as expressed in (2.24).

$$a_{3} = -\frac{2}{\pi} \left[ \frac{1 - \cos(4\tau)}{4} + \frac{\cos(2\tau) - 1}{2} \right]$$

$$b_{3} = -\frac{2}{\pi} \left[ \frac{\sin(2\tau)}{2} - \frac{\sin(4\tau)}{4} \right], \quad c_{3} = \frac{-4}{3\pi}$$

(2.24)

It is noted that since  $A_{RX,out}$  is also measured, the effect of the unknown gain is eliminated from the IMD3 expression. By using these specified signals, there are no additional unknowns in (2.23) and (2.24). Hence the delay skew can be calculated from the measurement of IMD3.

### 2.2.5 Envelope BW limitation in the loop-back mode

Once this delay skew is determined, it can be compensated digitally, by leading or lagging the envelope signal, thus minimizing its contribution to IMD. And once the distortion components for delay skew are eliminated, other factors can be measured. To measure the envelope BW, it needs to be emphasized, rather than suppress it. The input signal of Eqn. (2.18) is modified by increasing the bandwidth of the envelope signal. This will spread the harmonics further into the spectrum and reduce the number of harmonics included in the envelope BW. The harmonic contribution of the envelope BW will increase accordingly. The amplitude of the IMD3 with the DC offset voltage at the output of the receiver can be expressed as in Eqn. (2.25) and Eqn. (2.26) according to the number of harmonics (M).

$$\left| IMD_{3} \right|_{M=2} = \frac{1}{2} \times \left| A_{RX,out} \left[ 2a_{0}c_{3} + a_{2}(c_{1} + c_{5}) \right] + \Delta V_{RX,out} \times c_{3} \right|$$

(2.25)

$$|IMD_{3}|_{M=4} = \frac{1}{2} \times |A_{RX,out} [2a_{0}c_{3} + a_{2}(c_{1} + c_{5}) + a_{4}(c_{3} + c_{7})] + \Delta V_{RX,out} \times c_{3}|$$

(2.26)

The direct relation between M and the amplitude of IMD3 at the baseband output of the receiver enables us to generate a lookup table. Thus, once the IMD3 level is measured, the amplitude of IMD3 is compared with the calculated values in the lookup table. From the IMD3 measurement, the number of frequency components that are included in the passband of the filter can be determined. In order to calculate the BW more accurately, this measurement may need to be repeated several times with different baseband signal frequencies and interpolate the results.

# 2.2.6 BIST Algorithm

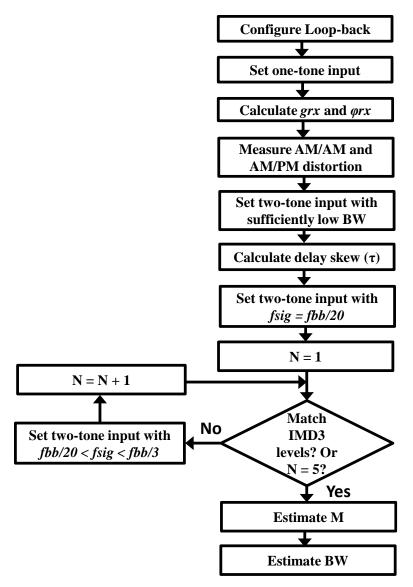

The BIST algorithm is based mostly on analytical derivation and carefully crafted test signals. Here, the computational overhead of the algorithm is quite low. Fig. 2.4 shows the flow of the BIST algorithm.

First the system in the loop-back mode is configured by applying the appropriate control signals. Next, the input is set to the single tone signal where the baseband signal frequency is set to the mid-point of the band. Gain and phase imbalance of the receiver are calculated using Eqn. (2.12) and Eqn. (2.13).

Second, AM/AM and AM/PM distortion is characterized in the loop-back mode by sweeping the supply voltage of the PA, measuring the receiver output, and using Eqns. (2.19) and (2.20). Third, the envelope signal amplitude and DC levels is set to the midpoint of the PA operating range and generate the signal at the baseband processor. The

frequency of the baseband signal is set to  $f_{bb}/20$  to ensure that at least 10 harmonics are present in the envelope signal after filtering. The envelope/phase skew is calculated as in Eqn. (2.23) and Eqn. (2.24).

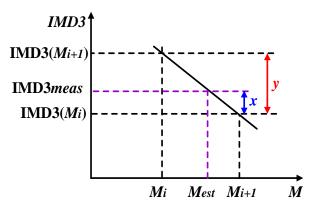

Finally, using the calculated skew value, the baseband signal is calibrated and the same measurement is repeated in a binary search fashion between  $f_{bb}/3$  and  $f_{bb}/20$  until the measured IMD3 levels match with the pre-determined values based on M, as in Eqn. (2.25) and Eqn. (2.26). If a match cannot be found, after 5 iterations, the bandwidth is interpolated between two closest measurements. As shown in Fig 2.5, estimated M (Mest) is given by (2.27)

$$M_{est} = -\frac{IMD_{meas} - IMD(M_i)}{IMD(M_{i+1}) - MD(M_i)} \cdot (M_{i+1} - M_i) + M_{i+1}$$

(2.27)

Fig. 2.4. Flow Chart for BIST Algorithm.

Fig. 2.5. Graph for Estimation of M.

### 2.3 On-Chip Implementation of the Loop-Back Path

The proposed BIST technique requires minimal hardware support to enable measurements. The hardware components include mainly the loop-back path, which is not part of the design. Note that in all of the derivations, the loop-back path parameters, such as gain, delay, and phase have been treated as unknowns and have been eliminated from the equations using comparative analysis with one exception, namely the phase difference between two loop-back path traces. In this section, the circuit implementation details of the loop-back components are presented and the error is analyzed by this assumption using extracted layout simulations. In the next section, this error is included in the calculations and present accuracy results with the effect of this error.

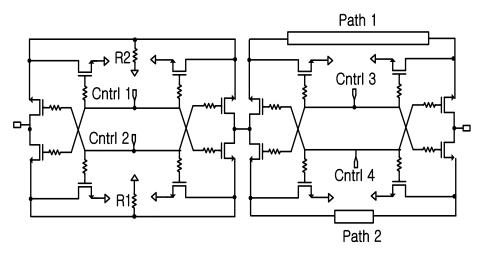

### 2.3.1 Loop-Back Path Implementation

As explained III-A, in order to characterize the receiver using the proposed technique, two test signals with different amplitude and another two test signals with different delays are required. Two test signals with different amplitude can be generated by using variable attenuator in the loop-back path. Note that in the derivation, the amplitudes and the relation between them do not need to be known. Hence the effect of process variations is eliminated. The two test signals with different delays can be generated in the loop-back path by switching between two traces with different length. In order to verify a functionality of the proposed concept, loop-back path is designed using 0.18 $\mu$ m IBM 7RF process. Fig. 2. 6 shows the circuit topology for the loop-back path. The proposed loop-back path consists of four single pole double throw (SPDT) switches, two resistors ( $R_1$  and  $R_2$ ), and two metal lines with different length. The switches are used to select one of two different metal lines as well as one of two different attenuation values.

Fig. 2.6. Circuit Topology for Loop-Back Path.

Post-layout Monte-Carlo simulations on the loop-back circuit have been conducted with 50 samples including die-to-die and within-die variations. Table 2.1 shows the delay difference for the nominal circuit as well as the worst-case deviation from the nominal for the 50 Monte-Carlo samples. This data shows that even though process variations severely affect transistor parameters, by designing symmetric switch circuits, and relying on trace differences (which are subject to much lower process variations), the delay difference can be predicted very accurately. Note that the delay difference is the only parameter that is assumed to be known in terms of its absolute value in the entire process. In the next section, the effect of the error that is made in this estimation on the accuracy of the gain and phase mismatch calculations is analyzed. Transmitter parameters do not rely on the estimated delay difference.

Table 2.1. Monte-Carlo Simulation Results for Loop-Back Path

| Nominal | Worst-case | Error |

|---------|------------|-------|

| 20.32°  | 20.02 °    | 0.3°  |

### 2.4 Experimental Results

## 2.4.1 Simulation Results

In order to evaluate the BIST solution for a wide variety of gain and phase mismatches/delay skew/BW scenarios, MATLAB model of the transceiver was implemented in the loop-back mode. RF components of the polar transceiver such as the PA, LNA, attenuator, and mixer are included in the model. Noise and DC offsets which results from LO leakage are also added. In the simulation set-up, all aforementioned impairment parameters are introduced at the same time.

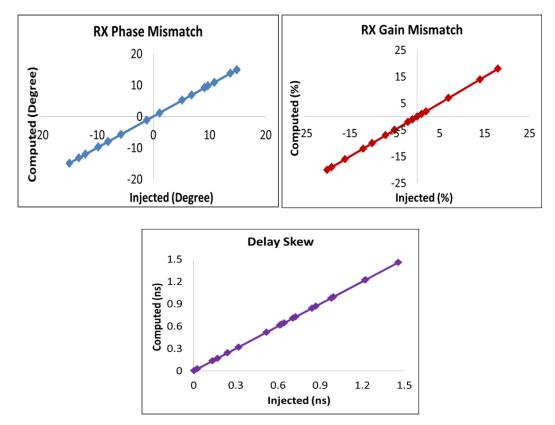

Monte Carlo simulations using the MATLAB model were conducted to inject various impairment parameters, and the proposed technique in the loop-back mode is used to extract the parameters. Fig. 2.7 shows Monte-Carlo simulation results for each parameter and Table II shows the bounds of the injected parameters and RMS error of the extracted parameters in Monte-Carlo simulation. These results indicate that the proposed technique accurately determines the desired parameters.

Fig. 2.7. Monte-Carlo Simulation Results.

| Parameter      | <b>RMS Error</b> | Injection Limit |

|----------------|------------------|-----------------|

| Gain Mismatch  | 0.023 %          | [-20%, 20%]     |

| Phase Mismatch | 0.015°           | [-15°, 15°]     |

| Delay Skew     | 0.00053 ns       | [0ns, 2ns]      |

| М              | 0                | [1, 5]          |

Table 2.2. Simulation Results for Polar Transceiver Parameters

# 2.4.2 Hardware Measurements

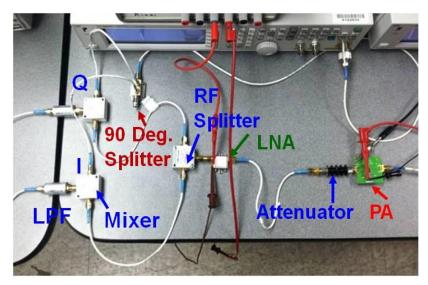

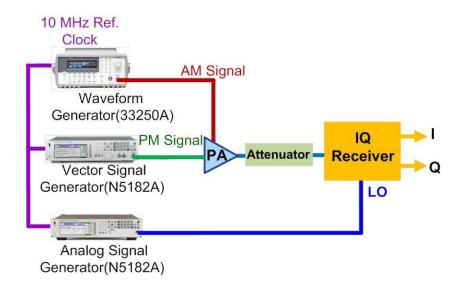

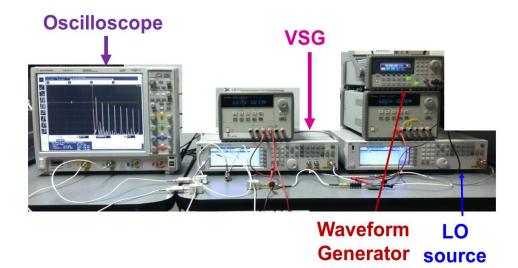

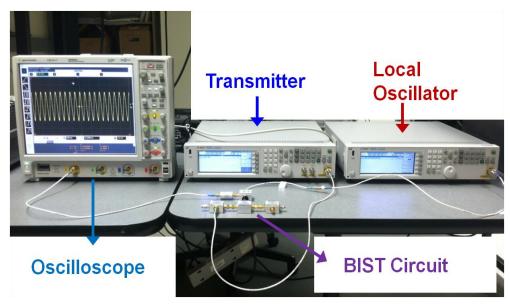

The polar transceiver was emulated using bench equipment and discrete components. As shown in Fig.2.8, the polar transmitter was implemented using the PA module (Hittite Microwave HMC450QS16G), an arbitrary waveform generator (Agilent Technologies 33250A), and a vector signal generator (Agilent Technologies N5182A). The receiver was formed using discrete components, which consists of LNA (Mini-Circuits ZX60-2522+), RF splitters (Mini-Circuits ZFSC-2-4-S+), 900 RF splitters (Mini-Circuits ZX10Q-2-13-S+), mixers (Mini-Circuits ZFM-15-S+), low pass filters (Mini-Circuits SBLP-117+). The LO signal was generated using analog signal generator (Agilent Technologies N5182A) and the baseband digital signal processing (DSP) unit was built using MATLAB.

Fig. 2.8. Implemented Polar Transceiver.

The arbitrary waveform generator is used to generate the envelope signal while the vector signal generator is used to generate the phase modulated (PM) signal. Both the envelope and the PM signals should have same clock frequency and be phase locked together in order to extract the delay skew. Additionally, the transmitter and receiver should use same reference clock for coherence. Hence, all equipment should share reference clock to implement complete RF polar transceiver. Fig. 2.9 shows measurement setup with clock synchronization. Synchronization between the envelope and phase generator is ensured by locking the clock of these two pieces of equipment. This clock synchronization enables

that the delay skew remains constant between the envelope path and the phase path. However, phase coherence is not ensured as it will be the case for an IC implementation. In addition, the reference clock source in the receiver also should be same as one in the polar transmitter. Therefore, as seen in Fig.2.9. instruments use same clock source by connecting external 10 MHz output of the vector signal generator to 10 MHz input of the arbitrary waveform generator and 10 MHz input of the vector signal generator to 10 MHz output of the analog signal generator. Fig. 2.10 shows the experimental setup for the polar transceiver characterization, which matches all of the limitation of the IC-based implementation. The overall system works with a carrier frequency of 1 GHz and a baseband frequency of 1 MHz. These values were based on the specifications of the commercial RF components. The technique can be applied to other carrier frequencies.

Fig. 2.9. Measurement Setup for Clock Synchronization.

Fig. 2.10. Experimental Setup for Polar Transceiver Characterization.

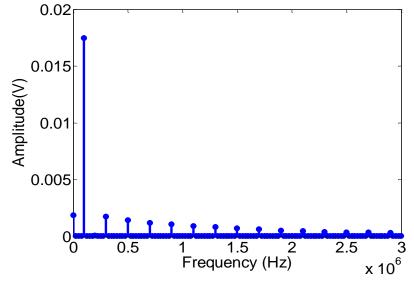

Measurements for the receiver impairments have been conducted for two different cases. Different phase mismatches were implemented using cables with different lengths. For comparison purpose, impairments of the receiver were measured manually in time domain using the oscilloscope. Table 2.3 shows actual impairments measured from traditional method as well as extracted values from the proposed method. As the results show, analytically computed results from the proposed method are highly accurate compared with values from the traditional manual method. For transmitter characterization, all measurements use the IMD3 information which is obtained by taking the FFT of the baseband signal as shown in Fig. 2.11.

| Case | Parameter | Traditional | Proposed | Error |

|------|-----------|-------------|----------|-------|

| 1    | Gain MM   | -5.4 %      | -5.8 %   | 0.5 % |

|      | Phase MM  | -33.9°      | -33.5°   | 0.4°  |

| 2    | Gain MM   | -3.6 %      | -3.9 %   | 0.3 % |

|      | Phase MM  | -3.0°       | -3.3°    | 0.4°  |

Table 2.3. Measurement Results for Receiver Parameters.

Fig. 2.11. FFT Results of the Output of the Receiver.

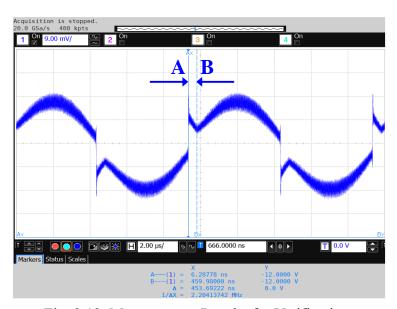

In order to verify the accuracy of the proposed delay skew measurement technique, the baseband output response in the time domain is used. The delay skew can be measured manually in time domain in order to compare the proposed technique with traditional method. Fig. 2.12 shows the measured waveform at the receiver output using the oscilloscope. In the waveform, the delay skew can be measured manually because it is expressed as time difference between A and B in Fig. 2.12. Table 2.4 summarizes the comparison of the results. As these results indicate, the proposed technique is able to

measure the delay skews accurately within sub-ns error. Note that compared to [5], the proposed technique provides better accuracy thanks to baseband signal analysis, which can be more accurate than RF signal analysis. As noted earlier, for effective digital calibration, receiver gain mismatch needs to be measured within 1%, phase mismatch needs to be measured within 1% phase mismatch needs to be measured within 50 ns [2]. The proposed test method provides excellent accuracy for these target parameters.

| Case | Traditional | Proposed | Error  |

|------|-------------|----------|--------|

| 1    | 294.2 ns    | 294.4 ns | 0.2 ns |

| 2    | 453.7 ns    | 453.8 ns | 0.1 ns |

| 3    | 956.4 ns    | 955.6 ns | 0.8 ns |

Table 2.4. Measurement Results for Delay Skew

Fig. 2.12. Measurement Results for Verification.

#### 2.4.3 Accuracy of BW measurement

Once the delay skew in the loop-back mode is calculated and compensated, the finite bandwidth in the envelope signal is determined by applying the relatively high bandwidth two-tone signal to the input of the transmitter. Since the other effects such as delay skew and nonlinearity of the transceiver are already minimized, the IMD3 at the output of the receiver is mainly due to the finite envelope BW and the offset voltage. The measured amplitude of IMD3 is compared with the calculated values in the lookup table.

In order to evaluate the BW measurement technique, the envelope path with two different BWs is generated and the algorithm to determine the closest M value for the baseband signal is used. Table V shows the actual BW of the envelope signal, measured IMD3 value, the M value for the closest IMD3 table entry, and estimated BW of the envelope path. Using the algorithm, the BW can be confirmed accurately in less than 5 iterations.

Note that envelope BW measurement requires compensation of delay skew. A potential pitfall in this compensation is frequency-dependent group delay of the envelope filter. The delay skew is measured with one frequency  $\omega_m$ . This delay is used to calibrate for the effect of skew and calibrated signal is used to measure envelope BW. The envelope BW measurement can have a different frequency than  $\omega_m$  and in this case there may be a slight variation for the delay through the filter, causing additional IMD that would be attributed to the filter. This variation for a simple RC filter (10 MHz bandwidth) has been analyzed, and the deviation of the delay through the filter has been calculated for the two extreme frequencies ( $f_m = 100$  KHz and  $f_m = 3$  MHz) used in delay and BW measurements. It was found that there is a 0.14 ns delay difference through the filter between 100 KHz and 3

MHz baseband input. Then this error was used in the calibration for delay difference and IMD3 component was calculated due to incorrect delay calibration. After that, this error (refer to Table V) was included in the BW calculation and found that it may be cause about 3 % error in the IMD3 calculations. In the experiments, this error does not cause misprediction. It can be safely said that the effect  $(22\mu V)$  is negligible for BW estimation.

|                  | Case    | e 1     | Cas      | se 2     |

|------------------|---------|---------|----------|----------|

| fm               | 100 KHz | 3 MHz   | 100 KHz  | 3 MHz    |

| Envelope<br>BW   | 4 MHz   | 4 MHz   | 8 MHz    | 8 MHz    |

| Measured<br>IMD3 | 1.71 mV | 1.77 mV | 0.596 mV | 0.618 mV |

| Closed<br>IMD3   | 1.61 mV | 1.61 mV | 0.557 mV | 0.557 mV |

| Actual M         | 2       | 2       | 4        | 4        |

| Estimated<br>M   | 2       | 2       | 4        | 4        |

| Estimated<br>BW  | 4 MHz   | 4 MHz   | 8 MHz    | 8 MHz    |

Table 2.5. Experimental Results for Envelope BW

# 2.4.4 Accuracy with On-chip loop-back Delay

In order to investigate how on-chip loop-back delay affects the accuracy of the proposed technique, the error in delay difference  $(\Delta \varphi_d)$  of the worst case from Monte-Carlo

simulation in Table I was taken and it was substituted into Eqn. (12) and Eqn. (13) for gain and phase mismatch computation. The computed values from the worst case are compared with actual values and shown in Table 2.6. As these results show, even with the worst-case delay difference estimation, the gain imbalance can still be determined within 1% error, and the phase imbalance can be determined within 1° error. These error numbers are well within target values for polar transceiver calibration.

| Parameter | Traditional | Proposed | Worst Case |

|-----------|-------------|----------|------------|

| Gain MM   | -5.4 %      | -5.8 %   | -6.0 %     |

| Phase MM  | -33.9°      | -33.5°   | 33.28°     |

Table 2.6. Accuracy with On-Chip Loop-Back Delay

### 2.4.5 Test Time

The proposed technique requires four steps. (a) measurements of gain and phase mismatches between I and Q channel at the receiver (b) voltage sweep at the PA supply input to determine the linear range (c) measurement of delay skew, and (d) measurement of the envelope BW. In order to increase the resolution of the BW measurement, step (d) needs to be repeated multiple times with varying baseband input frequencies. Step (a) and step (b) need several DC measurements and step (c) and step (d) require 1024-point FFT at the output of the receiver. The signal capture time for each step is around 128µs. FFT requires around 1 ms of computation time. Additional computation time for Eqn. (1) through Eqn. (26) is negligible because all of target parameters can be directly obtained based on analytically derived equations. Note that the proposed technique uses same test set-up for all measurement steps. Hence there is no signal source or output switching

overhead. Assuming step (b) takes 15 DC measurements and step (d) is repeated 5 times, the overall test time is less than 50 ms. This overall test time is comparable to one instrument and relay settling time which is generally around 50 ms-100 ms.

## 2.5 Conclusion

In this chapter, a new BIST solution to measure the internal parameters is proposed for RF polar transceivers, namely gain and phase mismatches, delay skew between the envelope and phase signals, and the finite envelope BW. In order to solve for these parameters using baseband signal analysis, the transceiver in the loop-back mode is configured, the baseband output response of the receiver is observed, and the parameters are extracted using analytically derived equations. Special test signals are developed in the loop-back mode, which enable isolation of the effect of one parameter at a time. First, gain and phase mismatches in the receiver are determined from the measured DC values at the output of the receiver in the loop-back mode. Regarding the transmitter, the delay skew is calculated from the measured IMD3 at the output of the receiver by applying low BW twotone signal. After compensating for the effect of delay skew, the envelope BW is measured by increasing the BW of two-tone input signal. From the second measurement of IMD3 in the loop-back mode, the finite envelope bandwidth can be estimated by comparing the measured IMD3 with a lookup table that consists of the calculated IMD3 values according to the number of harmonics included in the passband of the reconstruction filter. The loopback path circuit is designed and its functionality and performance are verified. Based on simulation and hardware measurements, the proposed method determines the critical parameters accurately while eliminating the expensive RF equipment. In addition, the proposed method enables implementation of BIST and internal calibration for the RF polar transceiver because with complexity, high accuracy, and short test time.

#### CHAPTER 3

#### ROBUST AMPLITUDE MEAASUREMENT FOR RF BIST APPLICATION

In this chapter, a new robust BIST solution is proposed to determine amplitude of an RF DUT. The variation issue is solved via (a) analytical modeling of the imperfections in the BIST circuit, and (b) a multi-step measurement procedure with carefully designed input signals. The necessary BIST components have been designed at the transistor level and simulated them over process variations. Experimental results show that the measurement can be attained with high accuracy over process corners. The BIST measurement system have been also constructed using off-the-shelf components, which are inherently subject to process variations, and demonstrated the measurement concept via hardware.

# 3.1 Proposed Methodology

The configuration of the proposed BIST system is shown in Fig. 3.1. A simple LC oscillator is used to generate the RF test signal and the test signal is amplified and applied to an RF limiter. The limiter generates a square wave with known amplitude. While the RF circuits are band limited, and are expected work with sinusoidal waveforms, it is difficult to generate sinusoidal signals with known amplitudes over process variations. The response of the limiter, on the other hand, is deterministic in terms of the amplitude of the fundamental tone. Its response in terms of the higher order tones is not an issue as will be shown mathematically in this section. Hence, by using the square wave signal, an implicit sine wave can be generated with known amplitude. This square wave test signal is applied to the input of the BIST circuit (measurement system). A self-mixing technique is used for the BIST measurement.

Fig. 3.1. BIST system for an Amplitude Measurement.

The BIST measurement circuitry consists of a mixer and low pass filter (LPF). The test signal (either from the BIST source or from the DUT output) is applied to the input of the BIST measurement system. This signal is divided into two paths before the input of the mixer. Because the RF and LO signals have the same frequency, the IF output of the mixer generates a DC component as well as high frequency component. The LPF removes the unnecessary high frequency component. The measured DC value at the output is determined by four variables: (a) BIST measurement system gain, (b) DUT output amplitude (target variable), (c) path losses, and (d) DC offsets generated in the path. In order to extract the DUT output amplitude, analytical modeling is used for the BIST system response and four consecutive measurements are conducted.

### 3.1.1 Calibration Phase