Dynamic Analysis of Embedded Software

by

Young Wn Song

# A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved August 2015 by the Graduate Supervisory Committee:

Yann-Hang Lee, Chair Aviral Shrivastava Georgios Fainekos Joohyung Lee

ARIZONA STATE UNIVERSITY

December 2015

#### ABSTRACT

Most embedded applications are constructed with multiple threads to handle concurrent events. For optimization and debugging of the programs, dynamic program analysis is widely used to collect execution information while the program is running. Unfortunately, the non-deterministic behavior of multithreaded embedded software makes the dynamic analysis difficult. In addition, instrumentation overhead for gathering execution information may change the execution of a program, and lead to distorted analysis results, i.e., probe effect. This thesis presents a framework that tackles the non-determinism and probe effect incurred in dynamic analysis of embedded software. The thesis largely consists of three parts. First of all, we discusses a deterministic replay framework to provide reproducible execution. Once a program execution is recorded, software instrumentation can be safely applied during replay without probe effect. Second, a discussion of probe effect is presented and a simulation-based analysis is proposed to detect execution changes of a program caused by instrumentation overhead. The simulation-based analysis examines if the recording instrumentation changes the original program execution. Lastly, the thesis discusses data race detection algorithms that help to remove data races for correctness of the replay and the simulation-based analysis. The focus is to make the detection efficient for C/C++ programs, and to increase scalability of the detection on multi-core machines.

# DEDICATION

To my parents for their love and support. To my wife, Jeyeon, for enduring this long journey with me. To my sweet girls, Angela and Minji.

## ACKNOWLEDGMENTS

First of all, I would like to thank my advisor, Dr. Yann-Hang Lee for his encouragement and support, and for guiding me with his knowledge and experience. It took almost 6 years (that's such a long time!) to complete my Ph.D study. This dissertation would not be possible without his trust and great patience.

Secondly, I would like to thank my committee members, Dr. Aviral Shrivastava, Dr. Georgios Fainekos, and Dr. Joohyung Lee for suggestions and insightful comments. I sincerely appreciate their time and guidance to broaden the scope of this dissertation.

This work was supported in part by the NSF I/UCRC Center for Embedded Systems, and from NSF grant #0856090.

|      |      |        | Р                                          | age  |

|------|------|--------|--------------------------------------------|------|

| LIST | OF 7 | TABLES | 5                                          | viii |

| LIST | OF F | FIGURE | ES                                         | x    |

| CHA  | PTEF | ł      |                                            |      |

| 1    | INT  | RODU   | CTION                                      | 1    |

|      | 1.1  | Motiva | ation                                      | 1    |

|      | 1.2  | Contri | butions                                    | 3    |

|      |      | 1.2.1  | Reproducible Execution                     | 3    |

|      |      | 1.2.2  | Probe Effect Analysis                      | 4    |

|      |      | 1.2.3  | Data Race Detection                        | 4    |

|      | 1.3  | Overv  | iew                                        | 4    |

| 2    | BAG  | CKGRO  | UND                                        | 6    |

|      | 2.1  | Happe  | ens-before Relation                        | 6    |

|      | 2.2  | Logica | l Clock                                    | 7    |

|      | 2.3  | Vector | Clock                                      | 8    |

| 3    | REC  | CORD A | AND REPLAY                                 | 11   |

|      | 3.1  | Introd | uction                                     | 11   |

|      | 3.2  | Dynar  | nic Analysis with Execution Replay         | 14   |

|      | 3.3  | Record | d and Replay                               | 16   |

|      |      | 3.3.1  | Record and Replay Operations               | 17   |

|      |      | 3.3.2  | Handling Data Races                        | 19   |

|      |      | 3.3.3  | Debugging Support                          | 21   |

|      | 3.4  | Execu  | tion Time Estimation                       | 22   |

|      |      | 3.4.1  | Execution Time Estimation at Program Level | 23   |

|      |      | 3.4.2  | Overhead Measurements                      | 24   |

# TABLE OF CONTENTS

|   |     | 3.4.3  | Execution Time Estimation at Thread Level | 26 |

|---|-----|--------|-------------------------------------------|----|

|   | 3.5 | Evalua | ation                                     | 27 |

|   |     | 3.5.1  | Overheads of Record and Replay Operations | 28 |

|   |     | 3.5.2  | Execution Time Estimation                 | 29 |

|   |     | 3.5.3  | Accuracy of Analysis in Replay Execution  | 30 |

|   | 3.6 | Relate | d Work                                    | 33 |

|   | 3.7 | Chapt  | er Conclusions                            | 35 |

| 4 | PRC | )BE EF | FECT ANALYSIS                             | 36 |

|   | 4.1 | Introd | uction                                    | 36 |

|   | 4.2 | Multi- | threaded Program Execution                | 39 |

|   | 4.3 | Model  | of Multi-threaded Program Execution       | 41 |

|   | 4.4 | Simula | ated Program Execution                    | 44 |

|   | 4.5 | Analys | sis of Simulation Results                 | 47 |

|   | 4.6 | Impler | nentation                                 | 49 |

|   |     | 4.6.1  | Execution Environment                     | 49 |

|   |     | 4.6.2  | Execution Trace and Measurements          | 49 |

|   |     | 4.6.3  | Simulation Analysis Algorithm             | 50 |

|   | 4.7 | Evalua | ation                                     | 52 |

|   | 4.8 | Relate | d Work                                    | 58 |

|   | 4.9 | Chapt  | er Conclusions                            | 61 |

| 5 | DAT | TA RAC | CE DETECTION FOR C/C++ PROGRAMS           | 62 |

|   | 5.1 | Introd | uction                                    | 62 |

|   | 5.2 | Discus | sion of Data Race Detection               | 66 |

|   |     | 5.2.1  | What is a (Data) Race?                    | 66 |

# Page

|   |     | 5.2.2  | Static Race Detection                  | 70  |

|---|-----|--------|----------------------------------------|-----|

|   |     | 5.2.3  | Using Model Checking Techniques        | 73  |

|   | 5.3 | Vector | Clock Based Race Detectors             | 77  |

|   |     | 5.3.1  | DJIT+                                  | 77  |

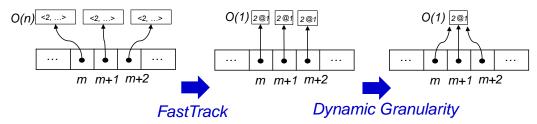

|   |     | 5.3.2  | FastTrack                              | 80  |

|   | 5.4 | Dynan  | nic Granularity Algorithm              | 81  |

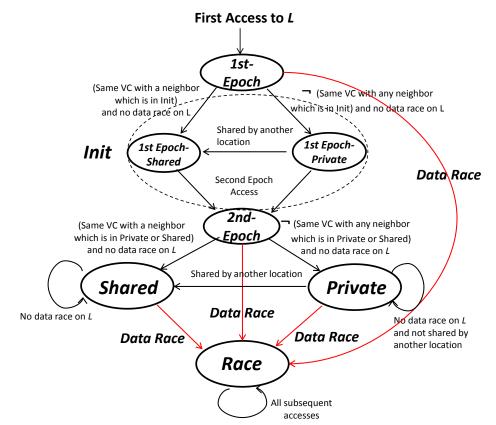

|   |     | 5.4.1  | Vector Clock State Machine             | 82  |

|   |     | 5.4.2  | Dynamic Granularity                    | 85  |

|   | 5.5 | Impler | nentation                              | 85  |

|   |     | 5.5.1  | Instrumentation                        | 86  |

|   |     | 5.5.2  | Data Structures                        | 87  |

|   | 5.6 | Evalua | ation                                  | 88  |

|   |     | 5.6.1  | Performance and Detection Precision    | 89  |

|   |     | 5.6.2  | Analysis of State Machine              | 94  |

|   |     | 5.6.3  | Case Studies                           | 95  |

|   | 5.7 | Relate | d Work                                 | 97  |

|   |     | 5.7.1  | Hybrid Race Detectors                  | 97  |

|   |     | 5.7.2  | Sampling/HW-assisted Approaches        | 98  |

|   |     | 5.7.3  | Data Race Detection for C/C++ Programs | 99  |

|   |     | 5.7.4  | Classifying/Surviving Data Races       | 99  |

|   |     | 5.7.5  | Automatically Fixing Data Races        | 100 |

|   | 5.8 | Chapt  | er Conclusions                         | 101 |

| 6 | DAT | TA RAC | CE DETECTION ON MULTI-CORE SYSTEMS     | 102 |

|   | 6.1 | Introd | uction                                 | 102 |

|      | 6.2  | Overhead and Scalability of FastTrack105   |  |  |

|------|------|--------------------------------------------|--|--|

|      | 6.3  | Parallel FastTrack Detector                |  |  |

|      | 6.4  | Implementation                             |  |  |

|      |      | 6.4.1 Instrumentation and Optimization110  |  |  |

|      |      | 6.4.2 Parallel FastTrack                   |  |  |

|      | 6.5  | Evaluation                                 |  |  |

|      |      | 6.5.1 Analysis of Race Detection Execution |  |  |

|      |      | 6.5.2 Performance and Scalability117       |  |  |

|      | 6.6  | Related Work                               |  |  |

|      | 6.7  | Chapter Conclusions                        |  |  |

| 7    | CON  | NCLUSIONS                                  |  |  |

|      | 7.1  | Summary                                    |  |  |

|      | 7.2  | Future Work                                |  |  |

| REFE | EREN | CES                                        |  |  |

# LIST OF TABLES

| Table | Page                                                                     |

|-------|--------------------------------------------------------------------------|

| 1.1   | QT Application with Mouse Inputs                                         |

| 1.2   | POSIX Message Queue Application 2                                        |

| 3.1   | Record and Replay Overheads                                              |

| 3.2   | Revisit of the QT Application with Recording Operations                  |

| 3.3   | Revisit of the MQ Application with Recording Operations                  |

| 3.4   | Execution Time Estimation without Replay Operation 30                    |

| 3.5   | Data Race Detection with FastTrack                                       |

| 3.6   | Flat Profiling Comparison with Callgrind 32                              |

| 3.7   | Cache Simulation Results from PIN Cache                                  |

| 4.1   | CPU Time for the Dining Philosophers                                     |

| 4.2   | CPU Time for the Sleeping Barber                                         |

| 5.1   | Races Detected by a Static Detector, RELAY                               |

| 5.2   | Races Detected by a Static Detector, LOCKSMITH 71                        |

| 5.3   | Overall Experimental Results                                             |

| 5.4   | Memory Overhead of FastTrack Detection with Different Granularities . 91 |

| 5.5   | Maximum Number of Vector Clocks Present                                  |

| 5.6   | Measures of Same Epoch Accesses                                          |

| 5.7   | Comparisons of State Machines with Different Configurations              |

| 5.8   | Performance Comparisons with Valgrind DRD and Intel Inspector XE . $95$  |

| 6.1   | Number of Accesses Filtered and Checked in the FastTrack Detection 113   |

| 6.2   | Overheads of the FastTrack Detector                                      |

| 6.3   | Comparison of CPU Core Utilization                                       |

| 6.4   | Performance Comparison for the Parallel FastTrack Detection              |

# Table

| 6.5 | Speedups with Additional Cores          | 120 |

|-----|-----------------------------------------|-----|

| 6.6 | Maximal Memory Usages of the Detections | 121 |

# LIST OF FIGURES

| Figure | F                                                               | Page |

|--------|-----------------------------------------------------------------|------|

| 1.1    | Dissertation Overview                                           | 5    |

| 2.1    | An Example of the Happens-before Relation and Logical Clocks    | 7    |

| 2.2    | An Example of Vector Clocks                                     | 8    |

| 3.1    | Dynamic Analyses with Execution Replay                          | 15   |

| 3.2    | Examples of Replay Minima/Maxima                                | 21   |

| 3.3    | Debugging Support in Eclipse                                    | 22   |

| 3.4    | Displaying Events and Threads in Eclipse                        | 22   |

| 3.5    | Calculation of Blocking Time of Events by the Replay Scheduling | 25   |

| 3.6    | Decomposition of the Replay Overhead                            | 31   |

| 4.1    | An Example of Global/Local Clocks and Event Executions          | 43   |

| 4.2    | An Example of Partial Order Graph $G$                           | 44   |

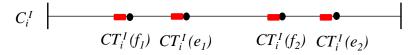

| 4.3    | Execution Time for the Simulation                               | 45   |

| 4.4    | Sub-routines for the Simulation Algorithm                       | 51   |

| 4.5    | Simulation Algorithm                                            | 52   |

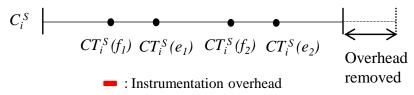

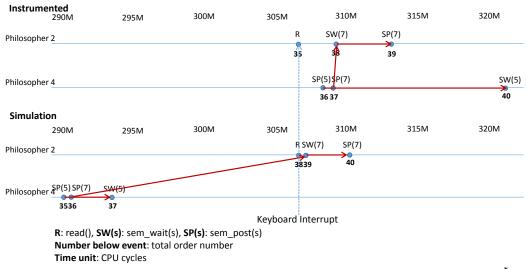

| 4.6    | An Example Execution with the Same Partial Order                | 55   |

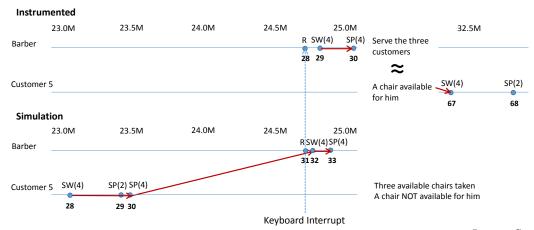

| 4.7    | An Example Execution with Different Partial Orders              | 55   |

| 4.8    | An Example Execution with Different Execution Paths             | 56   |

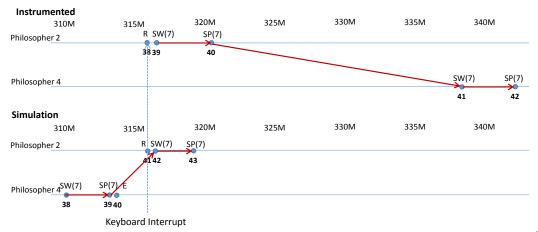

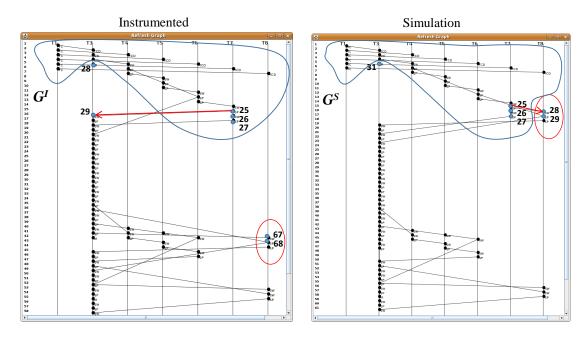

| 4.9    | Partial Order Graphs from Instrumented and Simulated Executions | 57   |

| 5.1    | An Example of Atomicity Violation without Data Races            | 67   |

| 5.2    | Classification of Data Races                                    | 68   |

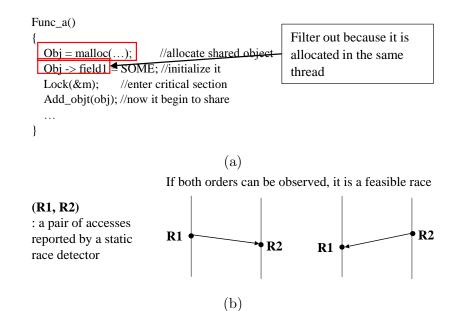

| 5.3    | Examples of Feasible/Apparent Races                             | 69   |

| 5.4    | A Benign Race Example                                           | 69   |

| 5.5    | Filtering out False Alarms from Static Race Detection           | 72   |

# Figure

| 5.6  | An Example for Predictive Analysis Technique               |

|------|------------------------------------------------------------|

| 5.7  | Example Executions of DJIT+ and FastTrack                  |

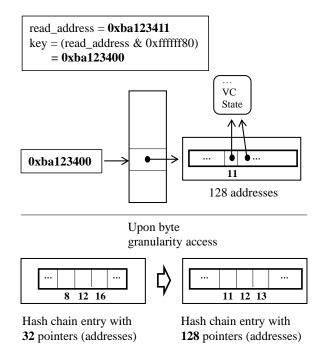

| 5.8  | Idea of Dynamic Granularity 82                             |

| 5.9  | Vector Clock State Machine for Each Read or Write Location |

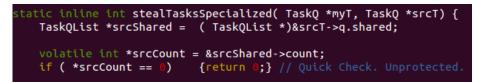

| 5.10 | Instrumentation Code for Memory Read 86                    |

| 5.11 | Indexing Data Structures                                   |

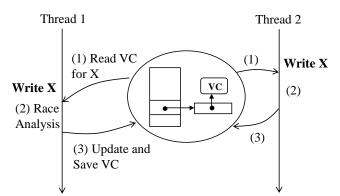

| 6.1  | A High Level View of the FastTrack Detection               |

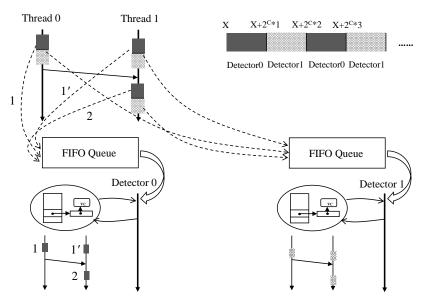

| 6.2  | An Overview of Parallel FastTrack                          |

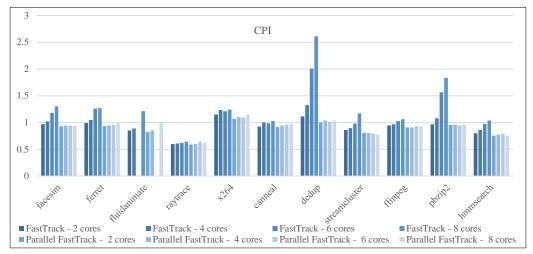

| 6.3  | CPI Measures of the Race Detection Programs                |

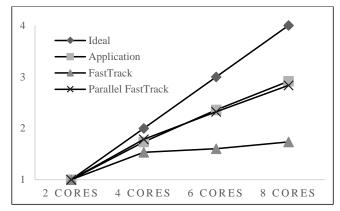

| 6.4  | Scaling Factors of Race Detectors                          |

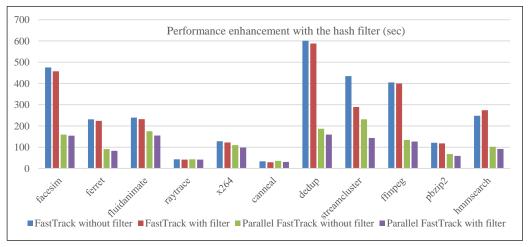

| 6.5  | Performance Comparison with/without the Hash Filter        |

Page

#### Chapter 1

# INTRODUCTION

#### 1.1 Motivation

Dynamic program analysis is widely used to collect execution information while programs are running. The approach is widely used to aid optimization and debugging of the programs. However, the non-deterministic behavior of embedded software and probe effect [22] make it a challenging task as embedded applications are often constructed with multiple threads and I/O operations.

In Tables 1.1 and 1.2, the probe effect is illustrated in the execution of two embedded programs. The two programs are based on the class projects of Embedded Systems Programming [4] in Arizona State University. The first program is a QT [91] application which draws lines following the inputs of mouse movement. The program consists of three threads. The first thread receives mouse movement packets and sends them to a POSIX message queue (MQ). The second thread receives the input packets from the MQ and draws lines on a display device. The last thread performs a line detection algorithm with the received mouse inputs. We collected mouse movement at a normal sampling rate of 300 inputs per second and then fed the inputs to the application with variant speeds. If the first thread was delayed and was not ready to receive an input, we counted it as a missed input. The program is instrumented using two dynamic analysis tools, i.e., the cache simulator using PIN [29] and our implementation of the FastTrack data race detector [19]. The workload of the program is very light as it only spends less than 10% of CPU time. However, the instrumented execution may miss up to 45% of the inputs. The impact of probe effect caused by the

| inputs/sec | Native execution | PIN<br>Cache | Race detector |

|------------|------------------|--------------|---------------|

| 150        | 0.0%             | 16.8%        | 0.3%          |

| 300        | 0.0%             | 36.1%        | 1.2%          |

| 450        | 0.0%             | 45.5%        | 1.9%          |

**Table 1.1:** QT Application with Mouse Inputs (% of inputs missed out of 4445 mouse movement inputs)

| Queue<br>Length | Native execution | PIN<br>Cache | Race detector |

|-----------------|------------------|--------------|---------------|

| 5               | 1.3/7.5          | 8.3/191.9    | 5.5/56.3      |

| 10              | 0.5/8            | 2.5/146.8    | 2.4/37.9      |

Table 1.2: POSIX Message Queue Application (# of Queue full/# of Queue empty)

instrumentation is obvious since analysis results may be misleading when the input data are missed.

The second program shown in Table 1.2 is a MQ (Message Queue) test program with six threads and two MQs. The two sender threads send items to the first MQ and the two router threads receive the items from the first MQ and send them to the second MQ with timestamps. Finally, two receiver threads receive the items from the second MQ. We used asynchronous functions for queue operations and, if a queue is empty or full, the thread sleeps a fixed time interval and retries. We count the numbers of occurrences that the queues become empty or full as a way of measuring different program behaviors. In this program, there is no external environment affecting the program execution, but the execution is determined by order of thread executions on the shared MQs. As the results show, instrumentation overhead from the tools has changed the relative ordering of thread operations on the shared MQs which, in turn, leads to different status of the message queues.

The other concern, followed by the data shown in Tables 1.1 and 1.2, is that it will be very hard to know if there exists any probe effect from the execution of instrumented program. If we take any amount of measurement to examine probe effect, the measurement itself would incur instrumentation overhead that can lead to execution divergence. Even if we know that there were some changes in program execution, we still would not be able to know how the changes affect the results of the analysis.

## 1.2 Contributions

The goals of this thesis are to provide (1) a reproducible execution environment such that software instrumentation can be applied without any changes of program execution, and (2) analysis frameworks for probe effect and data race detections which are essential for building the reproducible execution environment.

# 1.2.1 Reproducible Execution

To provide a reproducible execution environment, we consider a record and replay framework. First a program execution is recorded. Second, we apply software instrumentation on replayed execution. If the replay guarantees the same execution as the record, dynamic analyses with the instrumentation can be safely performed without worrying about execution changes of the program. In the record and replay framework, the key is to have minimal recording overhead. Since the recording operation itself is instrumenting the program, the recording overhead can change the program execution.

To provide minimal recording overhead, we model a program execution as a partial order of synchronization and I/O events, i.e., the happens-before relation [39]. In other words, two executions of a program are same if and only if the partial orders from the two executions are identical. In our record and replay, we record a partial order of synchronization and I/O events, and we guarantee the same execution as the recorded one by enforcing the same partial order during the replay.

#### 1.2.2 Probe Effect Analysis

It is perceivable that any recording operation should incur some instrumentation overhead since the execution of the recording itself would have caused perturbation to the original execution. We provide a simulation-based analysis for embedded software to detect any variations of event ordering caused by instrumentation overhead. The simulation-based analysis examines if the recording instrumentation changes the original program execution.

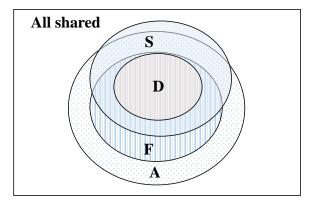

## 1.2.3 Data Race Detection

In our program execution model, we only consider synchronization and I/O events. However, the deterministic replay and the simulation-based analysis might not succeed in the presence of data races. For this end, this thesis describes the data race detection algorithms that help to remove data races. The algorithms are designed for efficient data race detection for C/C++ programs on multi-core machines. The race detector has low runtime and memory overheads by enabling large detection granularity, and we have further improved the performance and increased scalability on multi-core machines by decoupling data race detection from application execution.

# 1.3 Overview

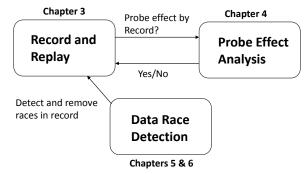

Figure 1.1 illustrates an overview of this thesis. In the following chapter, we present an overview of background on which this thesis is built.

Chapter 3 describes our deterministic replay. We present the construction of our replay followed by the effectiveness of dynamic analysis of embedded software using the replay.

Chapter 4 discusses the probe effect analysis for multithreaded embedded software.

**Figure 1.1:** Dissertation Overview. The program under test is executed with recording operations. A recorded execution is reproduced and analyzed in replayed executions. Probe effect that might be induced by the recording is checked before replay. Data races are detected and removed when the replay fails.

The simulation-based analysis can detect any changes of program execution based on our modeling of multithreaded program execution.

Chapter 5 describes a data race detection algorithm for C/C++ programs. Based on the FastTrack algorithm [19], we build an efficient data race detector for C/C++programs by utilizing large detection granularity during runtime.

Chapter 6 discusses how a data race detection can be parallelized by decoupling race detection from application execution. We show the effectiveness of our approach by parallelizing the FastTrack detector [19].

Chapter 7 concludes the thesis. We summarize our contributions and discuss our future work.

#### Chapter 2

## BACKGROUND

#### 2.1 Happens-before Relation

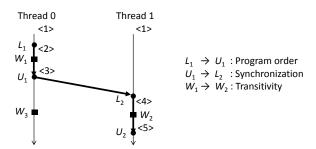

The happens-before relation [39] over the set of events in a program execution, denoted " $\rightarrow$ ", is the smallest relation satisfying,

- **Program order:** If a and b are in the same thread and a occurs before b, then  $a \rightarrow b$ .

- Synchronization <sup>1</sup>: If a is a release operation of synchronization object (e.g., unlock) and b is the subsequent acquiring operation on the same object (e.g., lock), then a→b.

- Transitivity: If  $a \rightarrow b$  and  $b \rightarrow c$ , then  $a \rightarrow c$ .

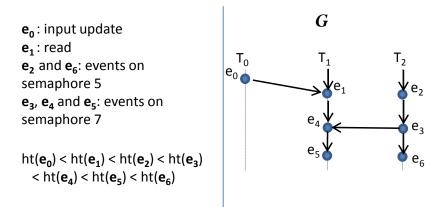

The happens-before relation implies a partial ordering of events. Two operations, a and b, are concurrent if they are not ordered by the happens-before relation, i.e.,  $a \not\rightarrow b$  and  $b \not\rightarrow a$ . An example of the happens-before relation in a program execution is shown in Figure 2.1.

An event, as a sequence of instructions that a program executes, defines a particular action (e.g., system call, memory read/write). We consider only a particular set of events for the underling system. In the deterministic replay (Chapter 3) and the probe effect analysis (Chapter 4), program execution is represented by a set of synchronization and I/O events. For the data race detection (Chapter 5 & 6), the

<sup>&</sup>lt;sup>1</sup>Communication primitives such as message send and receive can be similarly defined. In this thesis, we discuss thread interactions only in terms of synchronization for clarity.

**Figure 2.1:** An Example of the Happens-before Relation and Logical Clocks in a Program Execution. The events  $L_1$  and  $L_2$ , and  $U_1$  and  $U_2$  are lock and unlock operations for the same lock object, respectively. The events  $W_1$  to  $W_3$  are memory write operations. The numbers on the right of each thread are logical clocks updated for the event executions.

execution of a program consists of memory read and write events as well as synchronization and I/O events.

#### 2.2 Logical Clock

In this section, we discuss the logical clock [39] which is the building block for vector clock defined in Section 2.3. We define a clock  $C_i$  for each thread *i*, and  $C_i$ is a function which assigns a number  $C_i(a)$  to an event *a* in that thread. The clock  $C_i$  is logical rather than a physical clock since we do not assume any physical timing mechanism. For the correctness of the system, we need to ensure that if an event *a* happens-before another event *b*, then the logical clock values for events *a* and *b* should represent the relation as in a physical clock system. The condition can be stated as follows,

Clock Condition. For any events a and b:

if

$$a \rightarrow b$$

, then  $C(a) < C(b)$

To satisfy the *Clock Condition*, the logical clock  $C_i$  is updated with the following update rule:

- UR1. Each thread i increments  $C_i$  on every synchronization event.

- UR2. (1) If a is a release operation of a synchronization object s (e.g., unlock(s))

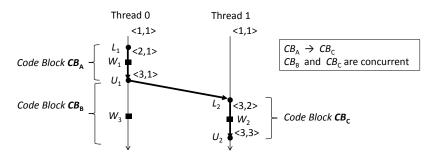

Figure 2.2: An Example of Vector Clocks in a Program Execution. For the same execution as in Figure 2.1, we illustrate vector clocks updates for each thread.

by thread *i*, then the logical clock of the synchronization object *s*,  $C_s$ , is set to the timestamp of *a*, i.e.,  $C_s = C_i(a)$  (2) On the subsequent acquiring operation on the same object *s* (e.g., lock(*s*)) by thread *j*, thread *j* sets  $C_j$  as the maximum of its present value and  $C_s$ .

In Figure 2.1, we show an example of happens-before relations with logical clock updates. In the example, since  $W_1$  happens-before  $W_2$ ,  $C(W_1) = 2 < C(W_2) = 4$ . Note that the converse of the *Clock Condition* does not hold. Hence, for a given program execution with logical clocks for events, we are not able to find out the partial ordering of events in the execution. In the following section, we show how we can decide if two events are ordered by the happens-before relation given a collection of logical clock information.

## 2.3 Vector Clock

A vector clock is [14] is an array of logical clocks for all threads. Each thread i has a vector clock  $T_i$  and the vector clock is indexed with a thread id. For instance, in Figure 2.2,  $T_1[0]$  gives the logical clock of thread 0 in thread 1's vector clock, and after event  $L_2$ ,  $T_1[0] = 3$ . The execution of a thread is logically divided into code blocks by synchronization operations.

The vector clock for each thread is updated similarly as in the logical clock update

in Section 2.2.

- VUR1. On a synchronization operation <sup>2</sup> in thread *i*, the vector clock entry for the thread is incremented, i.e.,  $T_i[i]$ ++.

- VUR2. Each synchronization object also maintains a vector clock to convey synchronization information from a releasing thread to the subsequent acquiring thread. At a release operation of object s by thread i, the vector clock for the object s is updated to the element-wise maximum of vector clocks of thread i and object s. Upon the subsequent acquire operation of the object s by thread j, the vector clock for thread j is updated as the element-wise maximum of vector clocks of thread j and object s.

With **VUR1** and **VUR2**, each element of a vector clock contains synchronization information for the corresponding thread. For instance,  $T_i[j]$  is the current logical clock for thread j that has been observed by thread i. If there has not been any synchronization from thread j to thread i either directly or transitively,  $T_i[j]$  will keep the initialization value.

With the vector clocks in a program execution, we can decide if two events are ordered by the happens-before relation. Consider two vector clocks  $V_a$  and  $V_b$  for events a and b, respectively. We define " $\square$ " as ordering vector clocks in a elementwise manner such that  $V_a \square V_b$  if for all thread indexes i, the element of  $V_a$  is smaller than the element of  $V_b$ , i.e.,  $\forall i : V_a[i] < V_b[i]$ . Then, the happens-before relation between a and b can be decided as follows:

$$a \rightarrow b$$

, if  $V_a \sqsubset V_b$

$<sup>^{2}</sup>$ In a vector clock based race detection (Chapter 5 & 6), a thread's vector clock is incremented only for release operations. For the consistent discussion with Section 2.2, we consider all synchronization operations.

As examples, consider the code blocks <sup>3</sup>  $CB_A$ ,  $CB_B$ , and  $CB_C$  in Figure 2.2. Let vector clocks of all events in  $CB_A$ ,  $CB_B$ , and  $CB_C$  be  $V_{CB_A}$ ,  $V_{CB_B}$ , and  $V_{CB_C}$ , respectively. Since  $V_{CB_A} = < 2, 1 > \Box V_{CB_C} = < 3, 2 >$ , and  $W_1 \in CB_A$  and  $W_2 \in CB_C$ ,  $W_1 \rightarrow W_2$ . Also consider  $W_3$  and  $W_2$ . Since  $V_{CB_B} = < 3, 1 > \Box V_{CB_C} = < 3, 2 >$ , and  $W_3 \in CB_B$  and  $W_2 \in CB_C$ ,  $W_3$  and  $W_2$  are concurrent.

$<sup>^{3}</sup>$ We discuss memory read/write events with being in code blocks for the sake of simplicity. The detailed descriptions are presented in Chapter 5.

### Chapter 3

# RECORD AND REPLAY

For program optimization and debugging, dynamic analysis tools, e.g., profiler, debugger, are widely used. To gather execution information, software instrumentation is often employed for its portability and convenience. Unfortunately, instrumentation overhead may change the execution of a program and lead to distorted analysis results, i.e., probe effect. Even without software instrumentation and with the same input data, consecutive runs may result in different executions. In embedded software which usually consists of multiple threads and external inputs, program executions are determined by the timing of external inputs and the order of thread executions. Hence, probe effect/non-deterministic program execution incurred in an analysis of embedded software will be more prominent than in desktop software. This chapter presents a reliable dynamic analysis method for embedded software using deterministic replay. The idea is to record thread executions and I/O operations with minimal record overhead and to apply dynamic analysis tools in replayed execution. In this chapter, we describe our record/replay framework [43, 83], based on Lamport's happens-before relation [39], and show that how dynamic analyses can be managed in the replay execution as if the program execution is deterministic regardless of any instrumentation.

# 3.1 Introduction

Dynamic program analysis is widely used to collect execution information while programs are running. The approach is widely applied to aid optimization and debugging of the programs. For the collection and analysis of program execution, software instrumentation is often employed for its portability and convenience. For instance, dynamic binary instrumentation tools such as Intel PIN [29] and Valgrind [61] are most commonly used since they do not require source code and recompilation of program. However, instrumentation overhead from the tools is very high no matter how trivial the analysis is.

The instrumentation overhead can perturb the execution of a program and lead to different execution paths, and consequently misrepresent analysis results. This is so called the probe effect [22]. One example is the delayed executions of input events caused by the instrumentation overhead. Consequently, arriving external inputs may be lost or the deadlines for real-time applications may be missed. The instrumentation overhead may also lead to different order of thread operations on a shared resource and produce different execution results.

In the cyclic debugging process, breakpoints are set in the program and the application is re-run. Thus, the cause of the failure can be observed. As long as each execution is deterministic and repeatable, the cause of the observed failure can be reproduced and identified. However, the program execution can be non-deterministic and non-reproducible as input events can be delayed or O/S internal states (e.g., run-queue state) can be changed due to the pauses of the execution.

In embedded systems, applications run with multiple threads interacting with each other as they share resources, and the execution of threads is often triggered by external inputs. Hence, embedded software will be sensitive to probe effect caused by instrumentation overhead as the timing of input events and the order of thread executions can be easily deformed. On the other hand, probe effect and non-deterministic program execution are less concerns in desktop applications which usually perform predefined work load (e.g., file input) with fixed loop counts. Even if there were execution changes due to the uses of analysis tools, analysis results would be amortized with repeated executions of the same code, e.g., consistent data races and call-path analysis results. In Tables 1.1 and 1.2, we have shown examples of probe effect caused by instrumentation overhead; the instrumentation overhead has changed the program executions such that the program missed input data and the interaction of threads has been deformed.

To make dynamic analysis tools as non-intrusive as possible, hardware-based dynamic analyses can be used. Intel Vtune Amplifier XE [28] exploits on-chip hardware for application profiling. ARM RealView Profiler [5] supports non-intrusive profiling using dedicated hardware or simulator. However, they are specific for performance profiling and do not support the analyses that require significant processing capabilities. Sampling based analyses [9, 21, 28, 50, 108] can also be used, but the analysis accuracy decreases when sampling rate is reduced to limit any measurement overhead.

For debugging multithreaded programs, one may claim that the existing debugging tools [2, 20, 75] can be used. Although the tools include the functions of setting up breakpoint, single stepping and monitoring at thread level, they do not ensure the reproduction of execution behavior that is required in cyclic debugging. Hence, the developers are responsible for feeding external signals synchronously, and he/she need to manually schedule threads to reproduce the bugs.

Researchers have proposed deterministic replays [7, 24, 41, 42, 52, 68, 76, 77, 97, 104] to reproduce program execution. That is, developers may record a failed run of a program and analyze the failed execution during replay. However, in those works the overhead during recording will be too high such that the recorded execution itself may change the program execution, and none of them have discussed the capabilities and functionalities that replay phase can provide to users.

In this chapter, we present a dynamic program analysis for embedded software using deterministic replay. The idea is to record thread executions and I/O events with a minimal recording overhead, and the program execution is analyzed with analysis tool/debugger during replayed executions. For this end we have developed a deterministic replay framework [43, 83]. The design goal is to minimize recording overhead to prevent probe effect during recording and to have minimal disturbance on analyzed program executions during replaying. The contributions of this chapter are:

- We present a dynamic analysis method that makes analyses of a program feasible and faithful, and expedites the debugging and optimization process for embedded programs.

- 2. We present a record/replay framework that can be incorporated with dynamic analysis tools.

- 3. We present an overhead analysis of replay which can be incorporated in thread profilers for accurate measurements of thread execution time.

The rest of chapter is organized as follows. In the following section, the dynamic analysis method with deterministic replay is described. Section 3.3 presents the design and implementation of the deterministic replay, and Section 3.4 describes the overhead analysis of replay. In Section 3.5, we present the performance evaluation of the record and replay, and the accuracy of dynamic analysis with the deterministic replay. A concise survey of related work is described in Section 3.6 and we conclude this chapter in Section 3.7.

# 3.2 Dynamic Analysis with Execution Replay

For dynamic analysis of a program, instrumentation overhead is not avoidable whatever optimization techniques are used. During a cyclic debugging, pausing a thread execution is inevitable to stepping through the thread. The overhead/pausing

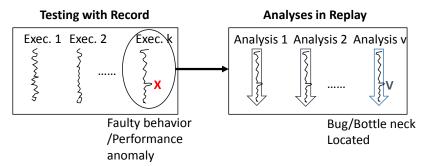

Figure 3.1: Dynamic Analyses with Execution Replay.

can result in different execution behavior. It is possible to repeat the same analysis again and again hoping that eventually we see the true program behavior without the overhead. This repeated running is not even feasible if the program execution depends on the timing of external inputs. Consider the idea of using a record/replay framework for dynamic analysis as shown in Figure 3.1. First, an execution of a program is recorded. If the overhead of recording is insignificant to avoid probe effect by the recording overhead itself, we can assume that the recorded execution is as same as the original program execution. Second, we apply dynamic analyses on the replayed execution which has the same thread executions and I/O events as the recorded one. Thus, the analyzed program will be executed as if there is no execution change by instrumentation. In addition, we can pause and resume any thread during debugging without worrying about execution changes.

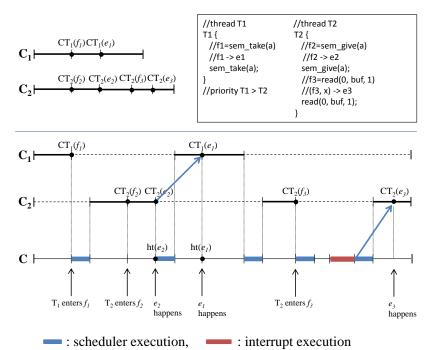

Moreover, analysis of program can be expedited with reproducible execution. When we find an unexpected execution during testing of a program, the first step will be to locate the cause of the problem. We may need to run various analysis tools to locate the cause. This will be very time consuming and multiple trials may be needed since it can be hard to reproduce the execution given the significant overhead of the analysis tools. Instead, we record the program execution during the test run. As the execution is reproducible in replayed execution, analysis runs can be performed in the same program execution. With a deterministic replay, execution times of a thread can be precisely calculated. In *thread profiling*, execution time of each function is measured for each thread. Since there can be probe effect caused by the measurements, researchers have proposed several execution time estimation algorithms [49, 103] that recover the real execution time without the measurement overheads. In the approaches, the real execution time can be recovered with the considerations of three factors: 1) thread local measurement overhead, 2) event reordering, and 3) execution time difference due to the event reordering. As an example of the factors 2) and 3), consider the take and give operations performed on a semaphore. Assume that in the real execution, the semaphore is given first and is taken afterward. Hence there is no blocking. In the instrumented execution, if the semaphore give operation had started late due to the delay of instrumentation overhead, then the thread taking the semaphore would have been blocked. The estimation algorithms [49, 103] can account for the blocking time and then reorder the events. However, if there is a change of program execution path, then there will be no way to recover the real execution.

To avoid the above-mentioned problem, thread profiling can be applied in a replayed execution. Note that the execution with the profiling is deterministic as the event reordering is handled by the replay scheduling. The overhead compensation for the reordering events is no longer needed. Therefore, as long as we can identify the overhead caused by the replay mechanism, the total overhead from the thread profiling tool on a replayed execution is simply the sum of the replay overhead and the thread local measurement overhead from the profiler.

#### 3.3 Record and Replay

In this section, we describe our record/replay framework. The framework is designed to have minimal record and replay overheads. To enable execution replay, we consider the happens-before relation [39] among events which are execution instances of synchronization or IO function calls. The record/replay operations are implemented in the wrapper functions for events. The happens-before relation over a set of events in a program's execution is logged during recorded execution and is used to guide the thread execution sequence in execution replay.

In the deterministic framework, a data race detector is included as an analysis tool and for managing execution replay in the presence of data races. It also provides an approach for recovering real execution time without measurement overhead of thread profilers (presented in Section 3.4).

# 3.3.1 Record and Replay Operations

During recording operation, happens-before relations for all events in a program execution are traced and saved into a log file, and the same happens-before relations are to be enforced during execution replay.

A general approach [76] to obtain the happens-before relation is to use Lamport clock [39]. In the approach, a Lamport clock is maintained for each thread and the clock is incremented and synchronized by the happens-before relation as explained in Section 2.2. A timestamp (Lamport clock value) is attached to each recorded event. During the subsequent replay operations, the corresponding event is delayed until all other events having smaller clock values are executed. For instance, consider the execution of event b and let C be a function that returns Lamport clock value for an event. For any other event a, C(a) < C(b) implies that  $a \rightarrow b$  and event a has already been executed, or events a and b are concurrent. Therefore, it is safe to execute event b without violation of the happens-before relation. This can enforce a stronger condition than necessary for replaying the partially ordered events as we are also considering events that are concurrent. In our approach, we use a global sequence number to order the events traced in recording operation. This sequence represents a total order of events and is used to index the set of events during execution replay.

To identify the happens-before ordering, the event log of an event consists of the two sequence numbers for the event itself and the event immediately before it, plus thread id, the function type and arguments for the event. For instance, for event b, let a be the event happened before b immediately. For the execution of event b, the sequence numbers of both events a and b are recorded in the event log of event b. For an input event, the received input is saved into the log file as well. All logging operations are performed in a dedicated logging thread to avoid possible jitters caused by file operations.

In a subsequent replay operation, an event table is constructed from the recorded log. The event table contains a list of events for each thread. Using the sequence numbers in the record log, events are indexed to represent the happens-before relations. Thus, based on the table, the next event for each thread that is eligible for execution can be identified and the same happens-before relations as the recorded ones are used to schedule thread execution.

In our initial version of replay [43], the replay scheduling is performed inside GDB. That is, the GDB thread module is modified to schedule thread executions according to the recorded partial order of events. The GDB command "set scheduler-locking on" is used to lock the Linux scheduler and a breakpoint is set at each event for checking happened-before relations. The GDB command "thread thread-num" is used for switching to a thread numbered "thread-num". This approach can be efficient in debugging of a program as the replay scheduling and the debugging capabilities are in the same software module. However, the uses of replay are limited only for debugging of a program. Hence, in our latest version [83] the replay scheduling is performed inside replay wrapper functions. Thus, the replay operation is implemented purely in application level, and the uses of replay is as general as possible.

In our latest version of replay, a replay wrapper function for each event (e.g., pthread\_mutex\_lock()) consists of three parts. Firstly, a thread looks up the event table for the events happened before its current event. If any of the events that should be happened before are not executed, the thread is suspended waiting for a conditional variable. In the second part, when a thread can proceed with its current event, the thread carries out the original function. If the function is for an input event, the thread reads input value from the log file instead of actual reading from an I/O device. Lastly, the event for this wrapper function is marked as executed and the thread wakes up (signal) other threads waiting for the execution of this event. Note that the total order of events based on the sequence numbering is used only for indexing events and the replay operation follows the same partial order as in the recorded execution.

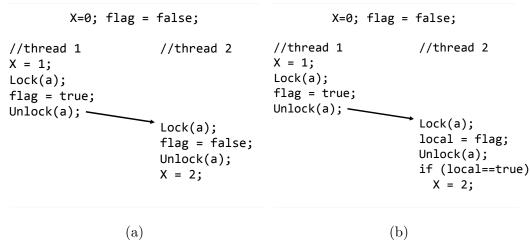

### 3.3.2 Handling Data Races

For efficient record and replay operations, only synchronization and I/O events are considered. However, one drawback is that a replay may not be correct in the presence of data races. A data race occurs when a shared variable is accessed by two different threads that are not ordered by any happens-before relation and at least one of the accesses is a write. Assume that, as an example, in the recorded execution there is a data race on a variable that is used to decide alternative execution paths. The presence of the data race implies that the order of accessing the variable is not recorded. Hence, if an alternate accessing order from the record one is chosen in replayed execution, the replayed program may take a different execution path, and the replay is not reproducing the same execution as the record anymore.

We use a similar approach as RecPlay [76] to handle the presence of data races

in replaying operations. RecPlay records an execution of a program as if there is no data race and any occurrences of data races are checked during replay operation using a data race detection tool. If data races are found, the races are removed and record and replay operations are repeated. The approach is correct since a replayed execution is correct up to the point where the first race occurs as shown in [10]. However, a data race detector incurs a substantial runtime overhead. Note that not every data race causes execution path changes. Hence, it may not be practical to fix every data race during replaying operations.

Instead of replaying a race-free program, our replay detects the occurrence of an unexpected event. The detection of an unexpected event is done in the replay wrapper by comparing the current events with the events in the record log. The detection of an unexpected event stops the replay with the location of the unexpected event. Then, the race can be detected with a data race detector and fixed. After fixing the race that results in different execution path, the replay can be safely used with various analysis tools including a data race detector for detecting races that cause errors other than a change of execution paths.

We have implemented a data race detector for C/C++ programs based on Fast-Track [19] and the detector is modified to be integrated with our deterministic replay. The FastTrack algorithm detects data races based on happens-before relations in a program execution. However, the replay scheduler invokes additional locking operations which appear as extra happens-before relations for the FastTrack detector. As a consequence, some data races may not be detected in the replayed execution. To correct the missed detections, we alter the FastTrack approach to discount the synchronization operation introduced by the replay scheduler.

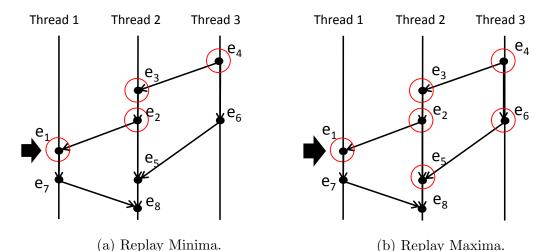

(a) Replay Minima. (b) Replay Maxima. **Figure 3.2:** Examples of Replay Minima/Maxima. (a): replay minima on event  $e_1$ . Only events  $e_2$ ,  $e_3$ , and  $e_4$  are executed since they are the minimum set of events to reach  $e_1$ . (b): replay maxima on event  $e_1$ . All events except  $e_7$  and  $e_8$  are executed since events  $e_7$  and  $e_8$  can be executed only after event  $e_1$  is executed.

# 3.3.3 Debugging Support

During a replay, the execution follows the same partial order graph of events as in the recorded execution. Hence, given the partial order graph, there can be many different orders of event executions. We provide two debugging modes for more controllable executions of threads:

- Replay Minima: For a selected event in a thread, the events of other threads will be executed only if they are happened before the selected event. That is, only the minimum amount of executions to reach the selected events are executed.

- 2. **Replay Maxima**: For a selected event in a thread, other thread can proceed until there is a happens-before dependency on the selected event. That is, the maximum amount of executions before the selected events are executed to see how far the impact of the selected event can stretch.

(a) Compiling for Record/Replay

(b) Menu of Replay Commands

Figure 3.3: Debugging Support in Eclipse.

Figure 3.4: Displaying Events and Threads in Eclipse. The executed events are colored in red. The line between two events represents the happens-before relation.

Examples of replay minima/maxima are shown in Figure 3.2. The two debugging modes are incorporated into GDB by adding two GDB commands, "set replay\_minima" and "set replay\_maxima". GDB communicates with the record/replay library through log files for the control of each event.

We provide a graphical environment in the form of Eclipse [88] plug-ins. The Eclipse plug-ins includes interfaces to automate compiling process for record/replay and to support the two debugging modes. The Eclipse environment also displays threads and events during a debugging session. Figures 3.3 and 3.4 shows the Eclipse supports for debugging.

#### 3.4 Execution Time Estimation

In this section, we present an approximation approach to estimate execution time that can account for the overheads of replay operation and thread profilers. First, we present the algorithm that can estimate the real execution time without replay at program level. Second, the algorithm is refined to estimate the real execution time at thread level without the overheads of profilers and replay operation. The replay overhead is approximated based on the assumptions that 1) threads run on multiple cores, 2) events are evenly distributed to each core, 3) the record overheads for all event types are same, and 4) the number of worker threads is greater than or equal to the number of cores.

# 3.4.1 Execution Time Estimation at Program Level

The estimated execution time of a program execution,  $C_{estimate}$ , can be calculated by subtracting the replay overhead  $O_{replay}$  from the replayed execution time  $C_{replay}$ , such that,

$$C_{estimate} = C_{replay} - O_{replay} \tag{3.1}$$

The replay overhead  $O_{replay}$  is the sum of 1) replay initialization time  $C_{init}$ , 2) extra execution time (CPU time),  $C_e$ , spent in replay wrapper functions, and 3) blocking time,  $B_u$ , by the replay scheduling that leads to extra delay of replay execution, such that,

$$O_{replay} = C_{init} + C_e + B_u \tag{3.2}$$

The replay initialization is processing the log file and preparing the event table before the replayed program runs. Hence it runs on a single core.

The extra execution time  $C_e$  is the sum of overheads for two different cases of event executions. The replay has two different program paths for an event execution depending on whether the event can proceed without blocking or not. For instance, consider two events a and b with  $a \rightarrow b$ . The execution of event b can be *delayed* until event a is executed, or can be executed with *no-delay* if event a has already been executed. The two possible ways of event executions contribute to various amount of overheads, thus we account them differently. Let  $n_{nd}$  and  $n_d$  be the numbers of events of *no-delay* and *delayed* executions, respectively. Let  $c_{nd}$  and  $c_d$  be the execution time for a *no-delay* and the execution time for a *delayed* event, respectively. Then,  $C_e$  is expressed as,

$$C_e = n_{nd} * c_{nd} + n_d * c_d \tag{3.3}$$

The replay overhead should also include extra blocking time (other than extra execution time) by the replay scheduling. Threads can be blocked by the replay scheduling in two ways: 1) the global locking used by the replay scheduling blocks threads, and (2) if a thread tries to execute an event and the partial ordering becomes different from the record as the result of the event execution, then the reply scheduler blocks the thread (delayed event). The blocking of threads leads to additional execution time only when the number of ready threads becomes less than the number of cores, i.e., when the cores are underutilized. Let  $n_g$  be the number of occurrences that threads are blocked by the global locking and let  $b_g$  be the average delay caused by each global locking. Also, let  $b_d$  be the total execution delay caused by the delayed events due to the replay scheduling at the end of a replay execution (i.e., the sum of blocking times of events). Then,  $B_u$  is expressed as,

$$B_u = n_g * b_g + b_d \tag{3.4}$$

Combining Equations 3.3 and 3.4 into Equation 3.2 gives,

$$O_{replay} = C_{init} + n_{nd} * c_{nd} + n_d * c_d + n_g * b_g + b_d$$

(3.5)

# 3.4.2 Overhead Measurements

The replay initialization time  $C_{init}$ , and the counter values,  $n_{nd}$ ,  $n_d$ , and  $n_g$ , can be measured during a replay execution. The blocking delay,  $b_d$ , is calculated using the algorithm in Figure 3.5 based on the utilization of the cores. On the other hand, the per event overheads,  $c_{nd}$ ,  $c_d$ , and  $b_g$ , are hard to measure online in the execution on

| n = number of runnable threads<br>M = number of cores                                                                        | //At start of event delay in thread $T$<br>$t_{s-T} = get_timestamp();$                                      |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| //At start of every delayed event<br>if $(n==M)$ //start measurement<br>$t_s = get_timestamp();$<br>else if $(n \le M)$      | //At end of event delay in $T$<br>$t_{e-T} = get\_timestamp();$<br>$b_T += (t_{e-T} - t_{s-T});$             |

| $tmp = get_timestamp();$<br>$b_d += (tmp- t_s)*((M-n)/M);$<br>$t_s = tmp;$<br>n;                                             | int blocking_overhead(thread <i>T</i> ) {     if <i>T</i> is not blocking from replay     return <i>br</i> ; |

| //At end of every delayed event<br>if $(n < M)$<br>tmp = get_timestamp();<br>$b_d += (tmp - t_s)*((M-n)/M);$<br>$t_s = tmp;$ | else<br>return \<br>(br + get_timestamp()-t <sub>s</sub> -r);<br>}                                           |

| <i>n</i> ++;                                                                                                                 |                                                                                                              |

**Figure 3.5:** Calculation of Blocking Time of Events by the Replay Scheduling. (Left): the time measurement in which the cores are underutilized due to the delayed events by the replay scheduling. (Right): the measurement of blocking overhead for a thread T.

multi-core systems. To avoid the online measurement, we assume they can be viewed as constants for a given system and can be estimated offline using measurement programs.

The measurement program for  $c_{nd}$  consists of multiple threads which invoke their own locks. Thus, threads are independent of each other and there is no overhead from delayed events. Hence,  $n_d * c_d = 0$  and  $b_d = 0$ . To avoid any idle CPU core caused by the global locking, extra threads running busy loops and with no synchronization and IO event are added. Hence, the blocking overhead from the global locking becomes zero ( $n_g * b_g = 0$ ) since all cores are utilized fully. The execution time without replay,  $C_{m1}$ , is measured and we can assume that  $C_{m1} = C_{estimate}$ . Then, with Equations 3.1 and 3.5,  $c_{nd}$  can be calculated using the following equation:

$$C_{m1} = C_{replay} - (C_{init} + n_{nd} * c_{nd})$$

(3.6)

A similar program is used for measuring  $c_d$ , where a lock is shared among all

threads. Hence,  $n_d * c_d \neq 0$ . Using the extra threads with busy loops, the program keeps  $n_g * b_g = 0$  and  $b_d = 0$ . Assuming that the execution time without replay,  $C_{m2}$ , is equal to  $C_{estimate}$ ,  $c_d$  can be calculated using the following equation:

$$C_{m2} = C_{replay} - (C_{init} + n_{nd} * c_{nd} + n_d * c_d)$$

(3.7)

The remaining constant  $b_g$  is calculated using a similar measurement program for measuring  $c_d$  but without the extra threads and with busy loops.

#### 3.4.3 Execution Time Estimation at Thread Level

In this subsection, we present how we can estimate per-thread replay overhead based on the estimation algorithm presented in the previous Subsections 3.4.1 and 3.4.2, and show how the overhead from a thread profiler can be calculated based on the perthread overhead estimation. In thread profiling, the execution times of threads' activities such as function executions can be measured and analyzed for each thread. As described in Section 3.2, the measurement overhead from the thread profiler consists of 1) thread local overhead and 2) execution time differences due to event ordering. When the profiler runs in a replayed execution, the latter overhead is contained in the replay overhead for delayed events  $(n_d * c_d + b_d)$ . Therefore, the total overhead from the profiling on a replay execution is simply the sum of the replay overhead and the thread local overhead of the profiler. To estimate the real execution time without the overheads, we need a per-thread measurement at a given time instant. For instance, if a function in thread T is invoked at  $t_s$  and finishes at  $t_e$ , then the execution time of the function is measured as  $t_e - t_s$ . Let  $C_{estimate-T}$  be a function that returns the estimated execution time of thread T up to a given time instance. Then, the real execution time of the function can be estimated as,  $C_{estimate-T}(t_e) - C_{estimate-T}(t_s)$ .

We can start the measurements after the initialization of a replay execution, thus

$C_{init} = 0$ . All counter values  $(n_{nd}, n_d, \text{ and } n_g \text{ in Equation 3.5})$  are maintained for each thread. Note that all per-event measurements  $(c_{nd}, c_d, \text{ and } b_g \text{ in Equation 3.5})$ are measured for concurrent executions on multiple cores. Hence, the per-event measurements for each thread are approximated considering the number of cores in the system. Let M be the number of cores in the system. Then, the per-event measurements for each thread, denoted as  $c'_{nd}$ ,  $c'_d$ , and  $b'_g$ , can be approximated as the product of M and  $c_{nd}$ ,  $c_d$ , and  $b_g$ , respectively. The blocking delay,  $b_d$ , is replaced with accumulated blocking time for each thread and it can be calculated as shown in Figure 3.5. Then, the replay overhead in thread T at a given instant t can be represented as,

$$O_{replay-T}(t) = n_{nd-T}(t) * c'_{nd} + n_{d-T}(t) * c'_{d} + n_{g-T}(t) * b'_{g} + b_{T}(t)$$

(3.8)

Let the thread local overhead from the profiler in thread T up to a given instant t be  $O_{profile-T}(t)$ . Then, the estimated execution time for thread T at time t can be expressed as,

$$C_{estimate-T}(t) = t - (O_{replay-T}(t) + O_{profile-T}(t))$$

(3.9)

#### 3.5 Evaluation

In this section, we show the effectiveness of the analysis approach in replay execution through several benchmark experiments. First, we show the overheads of the record and replay operations. Second, we present the evaluation results of the execution time estimation algorithm. Lastly, the accuracy of dynamic analyses using the record and replay is presented. All experiments were performed on an Intel Core Duo processor running Ubuntu 12.04 with kernel version 3.2.0.

The two programs shown in Section 1.1 are used to illustrate the effect of the minimized probe effect in record phase. All other experiments were performed with 11 benchmark programs for desktop computing to reveal the efficiency and accuracy of the dynamic analysis methods performed in the replay phase. Out of the 11 programs, 8 programs are from the PARSEC-2.1 benchmark suite [8] and 3 programs are from popular multithreaded applications: FFmpeg [89], a multimedia encoder/decoder; pbzip2 [30], a parallel version of bzip2; and hmmsearch [15], a sequence search tool in bioinformatics.

## 3.5.1 Overheads of Record and Replay Operations

Table 3.1 shows the overheads of the record and replay operations in our deterministic replay. "Number of events/sec" column shows the number of recorded events per second in the execution of each benchmark program. The column shows a general idea of how much the overheads will be in the record/replay executions as the record/replay operations are performed in the wrapper functions of the events. The overheads of record and replay operations are 1.46% and 2.78% on geometric mean, respectively. The results suggest that the record/replay will be suitable for dynamic program analysis of embedded software. The record operation would not have intrusion on the execution, and analysis results during replay will have insignificant amount of interferences (e.g., extra instructions counted from replay operation for instruction counting profiling) due to replay operation. One exceptional case is *fluidanimate* which incurs noticeable record/replay overheads due to a large number of events in the execution.

Tables 3.2 and 3.3 are the revisits of Tables 1.1 and 1.2 with the additional measures collected in record phase. For fair comparisons for the QT application, the QT libraries are not instrumented/analyzed for all analyses including our record operation, as there is no event to record in the QT libraries. The results in both tables suggest that the recording operation does not have intrusion on the executions (i.e.,

|       | Benchmark      | Base time | Record | Replay | Number of   | Record   | Replay   |

|-------|----------------|-----------|--------|--------|-------------|----------|----------|

|       | Program        | (sec)     | (sec)  | (sec)  | events/sec  | Overhead | Overhead |

|       | facesim        | 6.050     | 6.054  | 6.055  | 2,200.5     | 0.07%    | 0.08%    |

|       | ferret         | 5.027     | 5.073  | 5.161  | 2,066.2     | 0.92%    | 2.67%    |

| -     | fluidanimate   | 2.054     | 3.620  | 4.887  | 2,163,267.3 | 76.24%   | 137.93%  |

| SE    | raytrace       | 9.823     | 9.843  | 9.813  | 9.8         | 0.20%    | -0.10%   |

| PARSE | x264           | 2.196     | 2.288  | 2.323  | 17,487.2    | 4.19%    | 5.78%    |

| P     | canneal        | 6.643     | 6.674  | 6.677  | 1.5         | 0.47%    | 0.51%    |

|       | dedup          | 7.750     | 8.208  | 8.711  | 75,623.9    | 5.91%    | 12.40%   |

|       | streamcluster  | 3.781     | 4.071  | 4.092  | 38,417.1    | 7.67%    | 8.23%    |

|       | ffmpeg         | 3.053     | 3.052  | 3.157  | 3,560.4     | -0.03%   | 3.41%    |

|       | pbzip2         | 5.297     | 5.396  | 5.381  | 622.2       | 1.87%    | 1.59%    |

|       | hmmsearch      | 26.550    | 26.624 | 26.699 | 3,644.7     | 0.28%    | 0.56%    |

| C     | Beometric mean |           |        |        |             | 1.46%    | 2.78%    |

|       | Average        |           |        |        |             | 9.78%    | 17.31%   |

Table 3.1: Record and Replay Overheads

| inputs/sec | Native<br>execution | Record | PIN Cache | FastTrack |

|------------|---------------------|--------|-----------|-----------|

| 150        | 0.0%                | 0.0%   | 16.8%     | 0.3%      |

| 300        | 0.0%                | 0.0%   | 36.1%     | 1.2%      |

| 450        | 0.0%                | 0.0%   | 45.5%     | 1.9%      |

Table 3.2: Revisit of the QT Application (Table 1.1) with Recording Operations.

no probe effect).

## 3.5.2 Execution Time Estimation

Based on the overhead analyses in Section 3.4, the replay overhead for each benchmark can be measured and calculated with Equation 3.5 and the real execution time without the replay overhead can be estimated using Equation 3.1. Table 3.4 shows the estimated execution times and errors. Column 2 and 3 list the measured times

| Queue<br>Length | Native<br>execution | Record  | PIN Cache | FastTrack |

|-----------------|---------------------|---------|-----------|-----------|

| 5               | 1.3/7.5             | 1.3/8.1 | 8.3/191.9 | 5.5/56.3  |

| 10              | 0.5/8               | 0/7.1   | 2.5/146.8 | 2.4/37.9  |

Table 3.3: Revisit of the MQ Application (Table 1.2) with Recording Operations

| Benchmark<br>Program | Base time<br>(sec) | Replay<br>(sec) | Estimation<br>(sec) | Error |

|----------------------|--------------------|-----------------|---------------------|-------|

| facesim              | 6.050              | 6.055           | 6.041               | -0.2% |

| ferret               | 5.027              | 5.161           | 5.122               | 1.9%  |

| fluidanimate         | 2.054              | 4.887           | 2.144               | 4.4%  |

| raytrace             | 9.823              | 9.813           | 9.812               | -0.1% |

| x264                 | 2.196              | 2.323           | 2.247               | 2.3%  |

| canneal              | 6.643              | 6.677           | 6.677               | 0.5%  |

| dedup                | 7.750              | 8.711           | 7.838               | 1.1%  |

| streamcluster        | 3.781              | 4.092           | 3.859               | 2.1%  |

| ffmpeg               | 3.053              | 3.157           | 3.052               | 0.0%  |

| pbzip2               | 5.297              | 5.381           | 5.378               | 1.5%  |

| hmmsearch            | 26.550             | 26.699          | 26.595              | 0.2%  |

| Average              |                    |                 |                     | 1.24% |

Table 3.4: Execution Time Estimation without Replay Operation.

of the application execution without and with the replay, respectively. Column 4 show the estimated execution times with Equation 3.1. Column 5 lists the estimation error for each program, i.e., the difference between columns 2 and 4. On average, the estimation error is only 1.24%.

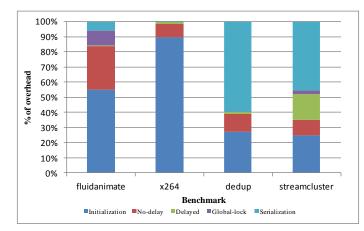

The replay overhead is classified into the 5 categories as shown in Equation 3.5. In Figure 3.6, the relative overhead in the 5 categories is illustrated for the four benchmarks that have more than 5% of replay overhead: *fluidanimate*, *x264*, *dedup*, and *streamcluster*. In the chart, the items are correspondent to the five categories of Equation 3.5 in the order. Two applications, *dedup* and *streamcluster*, show relatively more percentages of blocking overhead caused by delayed events (around 50%) than the other two applications. This is because there have been more per-event disturbances caused by the replay scheduling than the other two applications.

## 3.5.3 Accuracy of Analysis in Replay Execution

In this section, we present experimental results to show the accuracy of dynamic analysis with replay execution. Once we have a recorded execution which is as same as the original execution, the analysis result in replay execution will be as close

Figure 3.6: Decomposition of the replay overhead is shown only for benchmarks that have more than 5% replay overhead

| Benchmark     | Slowd          | Slowdown    |                                |  |  |

|---------------|----------------|-------------|--------------------------------|--|--|

| Program       | Without replay | With replay | Number of<br>races<br>detected |  |  |

| facesim       | 140            | 139         | 8907                           |  |  |

| ferret        | 86             | 82          | 2                              |  |  |

| fluidanimate  | 85             | 116         | 1                              |  |  |

| raytrace      | 27             | 27          | 13                             |  |  |

| x264          | 74             | 77          | 1300                           |  |  |

| canneal       | 12             | 12          | 0                              |  |  |

| dedup         | 151            | 148         | 0                              |  |  |

| streamcluster | 244            | 251         | 1053                           |  |  |

| ffmpeg        | 120            | 120         | 1                              |  |  |

| pbzip2        | 68             | 69          | 0                              |  |  |

| hmmsearch     | 83             | 86          | 1                              |  |  |

| Average       | 99             | 103         |                                |  |  |

Table 3.5: Data Race Detection with FastTrack.

as the analysis without any instrumentation. Since it will be very hard to know what the analysis results will be without any instrumentation  $^1$ , it will be difficult to compare results using real embedded software (i.e., non-deterministic program with I/O events). Instead of using embedded software, we use the 11 benchmark programs (which are for desktop computing) and assume that the programs show no (or negligible) probe effect from the instrumentation. Therefore, in the experiments we consider the execution without replay as the original execution.

$<sup>^1\</sup>mathrm{We}$  present the idea of revealing the original execution without any instrumentation in Chapter 4

| Benchmark     | Slowe                         | Slowdown |                                      |  |

|---------------|-------------------------------|----------|--------------------------------------|--|

| Program       | Without With<br>replay replay |          | # of differer<br>function<br>entries |  |

| facesim       | 37                            | 37       | 0                                    |  |

| ferret        | 50                            | 50       | 0                                    |  |

| fluidanimate  | 59                            | 127      | 7                                    |  |

| raytrace      | 59                            | 59       | 0                                    |  |

| x264          | 77                            | 79       | 0                                    |  |

| canneal       | 25                            | 24       | 0                                    |  |

| dedup         | 41                            | 43       | 0                                    |  |

| streamcluster | 58                            | 52       | 4                                    |  |

| ffmpeg        | 66                            | 66       | 0                                    |  |

| pbzip2        | 51                            | 50       | 1                                    |  |

| hmmsearch     | 28 2                          |          | 0                                    |  |

| Average       | 50                            | 56       |                                      |  |

Table 3.6: Flat Profiling Comparison with Callgrind.

| Benchmark     |         | down   | Cache mi    | ss rate - Witho | out replay | Cache n     | niss rate - Witl | h replay |

|---------------|---------|--------|-------------|-----------------|------------|-------------|------------------|----------|

| Program       | Without | With   | L1-         | L1-             | L2-        | L1-         | L1-              | L2-      |

| Tiogram       | replay  | replay | Instruction | Data            | Unified    | Instruction | Data             | Unified  |

| facesim       | 472     | 462    | 0.00%       | 5.92%           | 12.02%     | 0.00%       | 5.92%            | 12.07%   |

| ferret        | 336     | 341    | 0.02%       | 4.73%           | 16.89%     | 0.02%       | 4.74%            | 16.14%   |

| fluidanimate  | 398     | 731    | 0.00%       | 1.15%           | 17.13%     | 0.00%       | 1.58%            | 18.72%   |

| raytrace      | 395     | 387    | 0.00%       | 2.77%           | 2.23%      | 0.00%       | 2.77%            | 2.23%    |

| x264          | 411     | 424    | 1.34%       | 4.07%           | 8.10%      | 1.32%       | 4.07%            | 9.62%    |

| canneal       | 92      | 91     | 0.00%       | 4.06%           | 43.46%     | 0.00%       | 4.08%            | 43.12%   |

| dedup         | 286     | 301    | 0.00%       | 4.06%           | 7.25%      | 0.01%       | 3.93%            | 7.66%    |

| streamcluster | 395     | 454    | 0.00%       | 6.55%           | 49.14%     | 0.00%       | 6.42%            | 48.95%   |

| ffmpeg        | 478     | 478    | 0.01%       | 4.52%           | 11.56%     | 0.01%       | 4.61%            | 11.26%   |

| pbzip2        | 377     | 381    | 0.00%       | 4.03%           | 13.54%     | 0.00%       | 4.03%            | 14.40%   |

| hmmsearch     | 498     | 475    | 0.00%       | 0.78%           | 7.14%      | 0.00%       | 0.78%            | 7.10%    |

| Average       | 376     | 411    |             |                 |            |             |                  |          |

Table 3.7: Cache Simulation Results from PIN Cache.

Table 3.5 compares analysis results of the FastTrack race detector with and without replay operation. As shown in the table, the two approaches locate the same data races. For *facesim*, there was a data race that may result in different execution paths. Our replay has detected the unexpected event diverging from the recorded one, and stops the replay execution. Then, the race is detected with the FastTrack detector and fixed with correct synchronization. The data in the table shows the detection result after fixing the race for *facesim*.

Table 3.6 compares the flat profiling results from the Callgrind profiler [93]. The

flat profiler lists the functions in decreasing order that have fetched most instructions. For each benchmark program, we compare the top 10 function entries from normal program execution and replay execution, and the number of different function entries is shown in the last column of Table 3.6. There are three cases showing different function entries. For *streamcluster*, the function entries are different from the  $6^{th}$  entries due to the functions invoked for replay execution. However, from the  $3^{rd}$  function in the list, the functions have used less than 1% of total instructions. Similarly, the  $10^{th}$  function entries are different in *pbzip2* which fetches a negligible percentage of instructions. For *fluidanimate*, it shows 7 different function entries since the benchmark program has high replay overhead with the replay library functions included in the result. However, after removing the replay library functions, the same function entries are shown in the same order.

Table 3.7 shows the comparisons of PIN Cache simulator running in normal program execution and in replay execution. As can be seen from the comparisons, the differences are negligible. There are only two measures of cache miss rates with a more than 10% discrepancy between normal program execution and replay execution.

#### 3.6 Related Work

Instant Replay [41] is one of the earliest works that support deterministic replay on a multiprocessor. It records and replays a partial order of shared memory accesses. Microsoft's iDNA [7] also trace every shared access to enable deterministic replay. However, monitoring every shared memory access is too expensive (over 10x slowdown).

Due to the high overhead of instrumenting all shared memory accesses, researchers have proposed replay systems that reduce the scope of programs that can be replayed [42, 76, 77, 97]. RecPlay [76, 77], which is most similar to our system, logs only synchronization operations. As in our system, this approach only ensures a deterministic replay up until the first race in the program. However, the replay overhead is too high (around 2x) for uses with dynamic analyses.