Design and Development of Protection Schemes

for FREEDM Smart Grid Systems

by

Pavanchandra Mandava

A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved August 2014 by the Graduate Supervisory Committee:

George Karady, Chair Raja Ayyanar Keith Holbert

# ARIZONA STATE UNIVERSITY

December 2014

### ABSTRACT

This research work describes the design and validation of protection schemes developed to solve the problem of communication with an ability to detect and sectionalize the fault. Protection schemes have been designed according to the requirements of the Future Renewable Electric Energy Delivery and Management (FREEDM) system. Due to the presence of distributed generation (DG), power flow in the loop is bi-directional and conventional protection schemes may face the problem of unwanted tripping. Hence customized protection schemes have been developed specific to the FREEDM system. Former FREEDM students at ASU have developed ultrafast pilot differential protection using fast analog communication (Ethercat communication) and modified it in various ways to speed up the fault detecting capability of the algorithm. However, the National Science Foundation (NSF) criticized the use of Ethernet communication, as it is not compatible for long distances. FREEDM loop uses a fault current limiter (FCL) to limit the fault current and the substation solid state transformer (SST) reduces the system voltage to limit the fault current to 2 per unit. This allows the protection scheme to detect fault current in 2-3 cycles. However a much delayed fault detection is not encouraged as it will disrupt the power supply to healthy parts of the system for a longer duration. Time inverse directional overcurrent protection, pilot directional protection and PMU based protection are developed in this thesis work addressing the communication problem and at the same time with the ability to quickly detect the faults. Validation of the protection scheme is performed on the Real Time Digital Simulator (RTDS) at the Center for Advanced Power Systems (CAPS) using SEL relays and simulation models are developed in PSCAD.

#### ACKNOWLEDGMENTS

I would like to sincerely thank my advisor and chair Dr. George Karady for his advice and continued support throughout my work. His expertise and technical suggestions have been influential in performing this research work and have been a great inspiration throughout my entire masters. I would like to thank Dr. Raja Ayyanar and Dr. Keith Holbert for being a part of my thesis committee. I am also very grateful to NSF and FREEDM research center for supporting and financing my research work.

I would like to thank Dr. Mischa Steurer, Isaac Leonard, Mike Sloderbeck and Ravindra Harsha at Center for Advanced Power Systems (CAPS) for helping me to work on real time digital simulator to validate my research work. I would also like to thank SEL for their continuous support helping me to enrich my results and research work.

I would like to thank my parents Mr. Venkateswara Rao and Mrs. Vijayalaxmi for encouraging me in every step of my life. I would like to thank my family and friends for their love and support during hard moments. I take this opportunity to thank my roommates Gokul kumar, Goutam Tadimalla, Karthik palepu and Naren for their support during hard times. I am indebted to Divya Reddy for her love and support throughout my master's tenure.

# TABLE OF CONTENTS

|                      | Page |

|----------------------|------|

| LIST OF TABLES       | vi   |

| LIST OF FIGURES      | vii  |

| LIST OF NOMENCLATURE | xii  |

| CHAPTER              |      |

Page

| CHAF | TER                                                                   |

|------|-----------------------------------------------------------------------|

| 1    | INTRODUCTION TO THE FREEDM SYSTEM 1                                   |

|      | 1.1 Overview1                                                         |

|      | 1.2 FREEDM System2                                                    |

|      | 1.3 Objectives of the Reserach                                        |

|      | 1.4 Organization of the Thesis5                                       |

| 2    | LITERATURE REVIEW                                                     |

|      | 2.1 Overcurrent Protection7                                           |

|      | 2.2 Pilot Protection11                                                |

|      | 2.3 Detecting the Direction of Fault Current                          |

|      | 2.4 Application of Synchrophasors in Power System Monitoring, Control |

|      | and Protection24                                                      |

| 3    | TIME INVERSE DIRECTIONAL OVER CURRENT PROTECTION                      |

|      | 3.1 Protection Algorithm                                              |

|      | 3.2 Implementation of Protection Scheme over the FREEDM Loop33        |

|      | 3.3 Single Line to Ground Fault at location F1                        |

|      | 3.4 Single Line to Ground Fault at location F2                        |

|      | 3.5 Single Line to Ground Fault at location F337                      |

|      |                                                                       |

|   |          | 3.6 Selection of Time Dial Settings and Current Pick Values for Time | •   |

|---|----------|----------------------------------------------------------------------|-----|

|   |          | Inverse Over Curent Relays                                           | 38  |

|   |          | 3.7 Effect of Fault Current Limiter on the Protection Algorithm      | .44 |

|   |          | 3.8 Response Time of the Relays to Detect and Isolate the Fault      | .51 |

|   |          | 3.9 Variation of the Trip Signal for Fault Current Chopped at        |     |

|   |          | different Magnitudes                                                 | .60 |

|   |          | 3.10 Determining the Directionality of Fault Current                 | .60 |

|   |          | 3.11 Application of Directionality in PSCAD                          | .61 |

|   |          | 3.12 Practical Implementation                                        | .64 |

| 4 | PILOT DI | RCTIONAL PROTECTION                                                  | 65  |

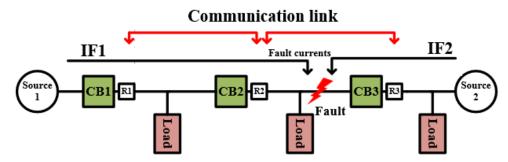

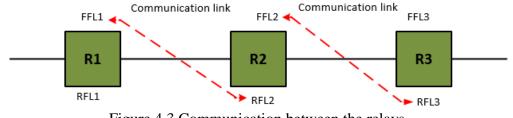

|   |          | 4.1 Communication Between the Relays                                 | .66 |

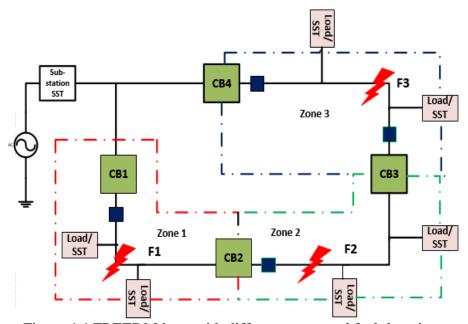

|   |          | 4.2 Application of Pilot Directional Scheme over the FREEDM Syste    | m   |

|   |          |                                                                      | .68 |

|   |          | 4.3 Simulation Results                                               | .70 |

|   |          | 4.4 Hardware Implementation                                          | .74 |

| 5 | VALIDA   | TION OF PILOT DIRECTIONAL SCHEME OVER THE FREEDM                     |     |

|   | S        | YSTEM ON REAL TIME DIGITAL SIMULATOR (RTDS)                          | 78  |

|   |          | 5.1 ABC to Ground Fault at Zero Degrees of Phase A Current           | .80 |

|   |          | 5.2 ABC-LLL Fault at Zero Degree of Phase A Current                  | .82 |

| 6 | PMU BA   | SED PROTECTION                                                       | 85  |

|   |          | 6.1 Single Line to Ground Fault on Phase A near F1 at 2 seconds      | .86 |

|   |          | 6.2 3 Phase to Ground Fault near F1 at 2 seconds                     | 90  |

| CHAPTER                                                 | Page       |

|---------------------------------------------------------|------------|

| 6.3 Hardware Implementation                             | 94         |

| 7 CONCLUSIONS AND FUTURE WORK                           | 97         |

| 7.1 Conclusions                                         | 97         |

| 7.2 Things to Take Care When Implementing Above Mention | oned       |

| Schemes                                                 | 102        |

| 7.3 Future Work                                         | 103        |

| REFERENCES                                              | 104        |

| A FREEDM SYSTEM USED IN PSCAD SIMULATION                | 109        |

| B SVP CONFIGURATOR PROGRAM                              | 111        |

| C GENERATOR AND SYSTEM DATA OF THE FREEDM LOOP MC       | DELED ON   |

| REAL TIME DIGITAL SIMULATOR USED IN VALIDA              | ATING THE  |

| PILOT DIRECTIONAL SCHEME                                | 113        |

| D DETERMINING VOLTAGE PHASE DIFFERENCE BETWEEN PMU      | J'S DURING |

| MAXIMUM POWER FLOW OF THE TRANSMISSION                  | LINE115    |

# LIST OF TABLES

| Table | Page                                                                                               |

|-------|----------------------------------------------------------------------------------------------------|

| 2.1   | Equations associated with US Time Inverse Overcurent Curves [6]                                    |

| 2.2   | Equations associated with IEC Time Inverse Overcurrent Curves [6]                                  |

| 2.3   | Quantities used in Cross Polarization for various type of Faults                                   |

| 3.1   | Operating Time of Relays corresponding to Circuit Breakers                                         |

| 3.2   | Fault Current Magnitudes for Faults at different locations                                         |

| 3.3   | Fault Current seen by Clockwise and Anti-Clockwise Relays 40                                       |

| 3.4   | Chopped value of Fault Current Magnitude at various locations                                      |

| 3.5   | Chopped value of Fault current seen by Clockwise and Anti-Clockwsie Relays                         |

|       |                                                                                                    |

| 3.6   | Trip Signal Time for Fault Currents Chopped at <sup>1</sup> / <sub>2</sub> of their Peak Values 60 |

| 3.7   | Trip Signal Time for Fault Currents Chopped at 1/4 <sup>th</sup> of their Peak Values 60           |

| 3.8   | Trip Signal Time for Fault Currents Chopped at 1/6 <sup>th</sup> of their Peak Values 60           |

| 4.1   | Trip Signal Logic for Pilot Directional Protection                                                 |

| 4.2   | Average Trip Signal Delay for Faults at different places                                           |

| 5.1   | Breaker 2 trip time for different fault Inception Angles                                           |

| 5.2   | Breaker 3 Trip Time for Different Fault Inception Angles                                           |

| 7.1   | Trip Signal Time for Fault Currents Chopped at <sup>1</sup> / <sub>2</sub> of their Peak Values    |

| 7.2   | Trip Signal Time for Fault Currents Chopped at 1/4 <sup>th</sup> of their Peak Values 98           |

| 7.3   | Trip Signal Time for Fault Currents Chopped at 1/6 <sup>th</sup> of their Peak Values 98           |

| 7.4   | Breaker 2 Trip Time for different Fault Inception Angles                                           |

| 7.5   | Breaker 3 Trip Time for different Fault Inception Angles 100                                       |

| Page                                                                  |

|-----------------------------------------------------------------------|

| FREEDM Concept Model                                                  |

| FREEDM Loop                                                           |

| Time Inverse Over Current Curve 8                                     |

| Operation of Differential Relay without Fault 10                      |

| Operaton of Differential Relay for an External Fault 10               |

| Operaton of Differential Relay for an Internal Fault 11               |

| Pilot Protection Scheme                                               |

| Pilot Differential Protection                                         |

| Creating Phase Differnce between Voltage and Current using Lead/Lag   |

| Compensator                                                           |

| Sequnce Networks for a Single Line to Ground Fault [24] 20            |

| Balanced Phase Voltages [24]                                          |

| Phase Voltages during SLG Fault on Phase A [24] 21                    |

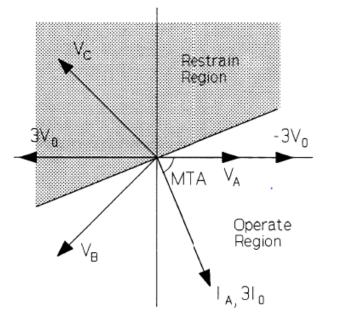

| Operating Region and Restraining Region of the Relay [24] 21          |

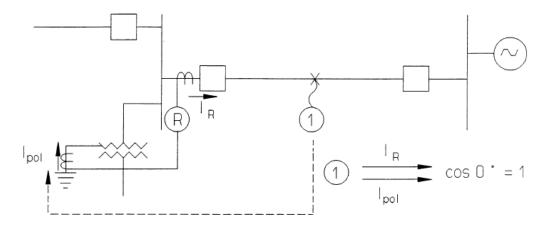

| Current Polarization for Forward Fault [24] 22                        |

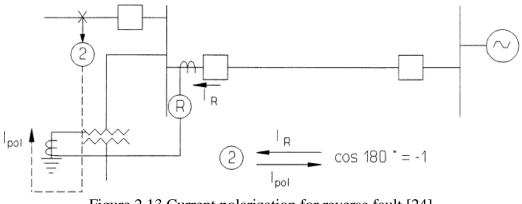

| Current Polarization for Reverse Fault [24]                           |

| Representation of Synchrophasor [30]                                  |

| Stable and Un-Stable Region to determine Out of Step Tripping [55] 29 |

| Loop System fed with Multiple Sources                                 |

| Location of Clockwise Relays on the Loop System                       |

| Location of Anti-Clockwise Relays on the Loop System                  |

|                                                                       |

# LIST OF FIGURES

| 3.4  | Fault Location F1 on the Loop Sstem                                    |  |  |

|------|------------------------------------------------------------------------|--|--|

| 3.5  | Arrangement of Anti-Clockwise Relays on the FREEDM Loop                |  |  |

| 3.6  | Arrangement of Clockwise Relays on the FREEDM Loop                     |  |  |

| 3.7  | Fault Current directions for Fault at F1                               |  |  |

| 3.8  | Fault Current directions for Fault at F2                               |  |  |

| 3.9  | Fault Current directions for Fault at F3                               |  |  |

| 3.10 | Fault Current without the Influence of Current Limiter                 |  |  |

| 3.11 | Implementation of Fault Current Limiter in PSCAD 45                    |  |  |

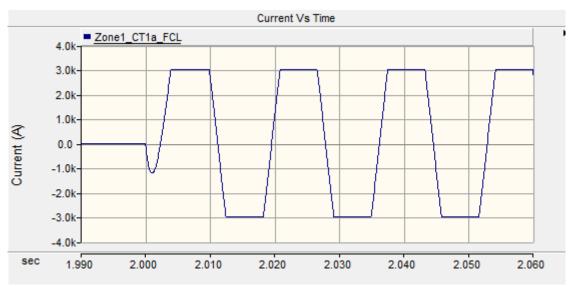

| 3.12 | Fault Current with the Influence of Current Limiter                    |  |  |

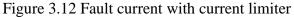

| 3.13 | FREEDM Loop with different Zones and Fault Locations                   |  |  |

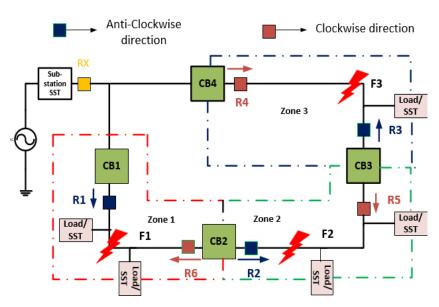

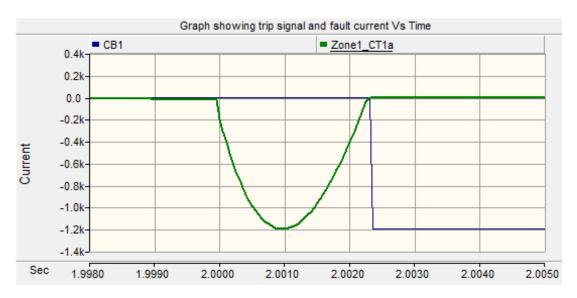

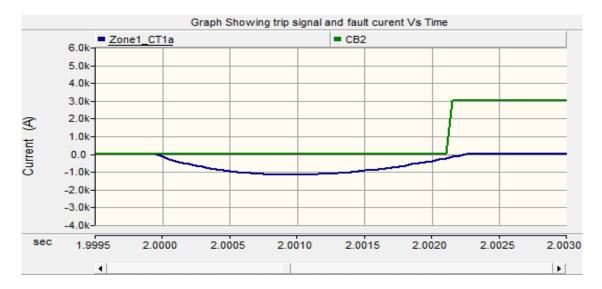

| 3.14 | Fault Current in Zone 1 and Trip Signal of CB1 52                      |  |  |

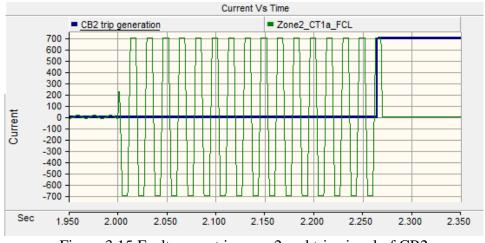

| 3.15 | Fault Current in Zone 2 and Trip Signal of CB2 52                      |  |  |

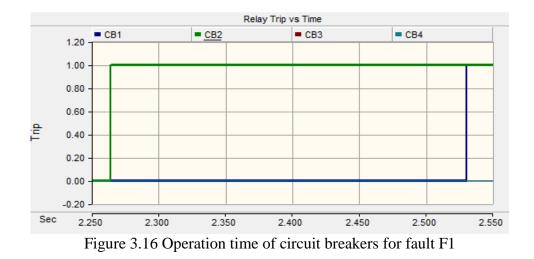

| 3.16 | Operation Time of Circuit Breakers for Fault F1 53                     |  |  |

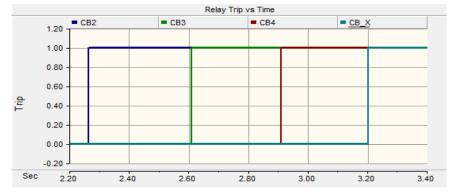

| 3.17 | Operation Time of Back-Up Circuit Breakers when CB2 Fails to Clear the |  |  |

|      | FaultF1                                                                |  |  |

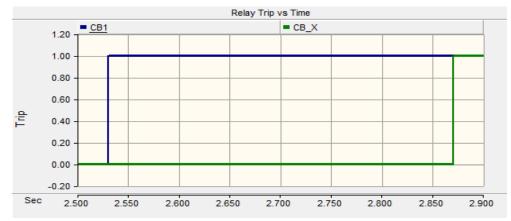

| 3.18 | Operation Time of Back-up Circuit Breakers when CB1 Fails to Clear the |  |  |

|      | Fault F1 54                                                            |  |  |

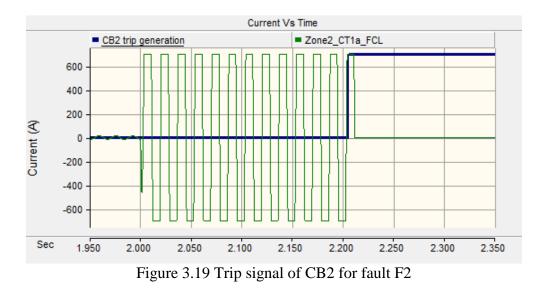

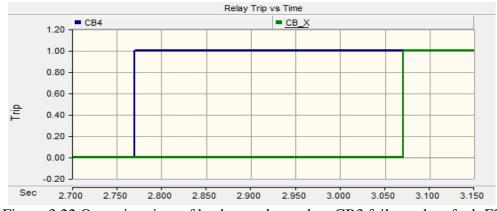

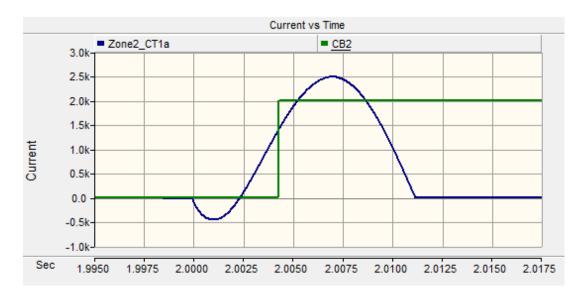

| 3.19 | Trip Signal of CB2 for Fault F2 55                                     |  |  |

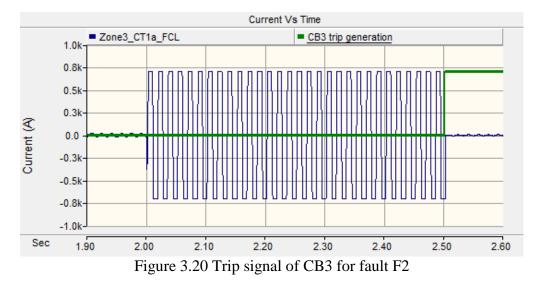

| 3.20 | Trip Signal of CB3 for Fault F2 55                                     |  |  |

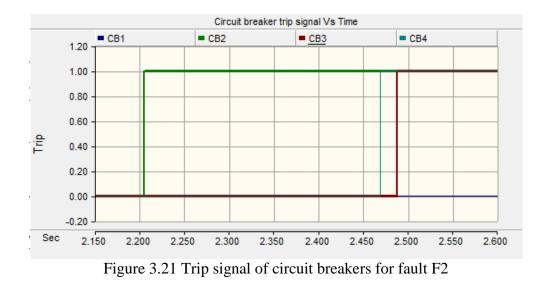

| 3.21 | Trip Signal of Circuit Breakers for Fault F2 56                        |  |  |

| 3.22 | Operation Time of Back-up Relays when CB3 Fails to Clear Fault F2 56   |  |  |

Page

| 3.23 | Operation Time of Back-up Relays when CB2 Fails to Clear Fault F2. 57       |  |  |

|------|-----------------------------------------------------------------------------|--|--|

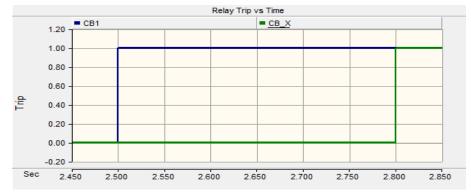

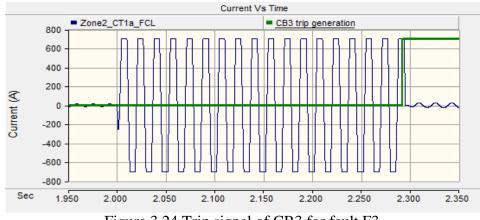

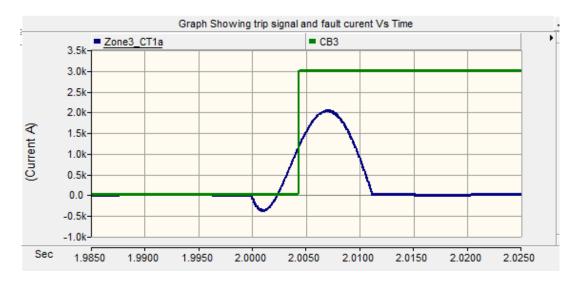

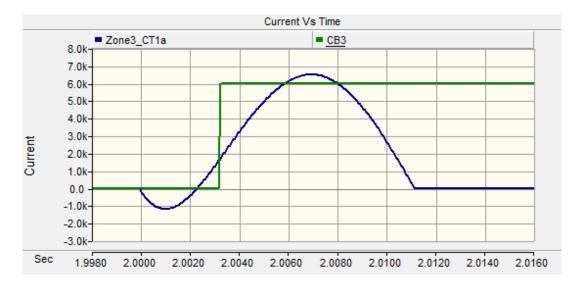

| 3.24 | Trip Signal of CB3 for Fault F3 57                                          |  |  |

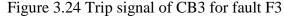

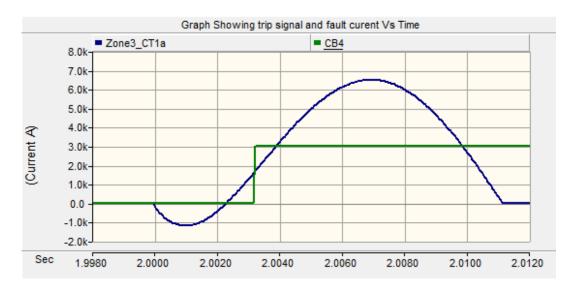

| 3.25 | Trip signal of CB4 for Fault F3 58                                          |  |  |

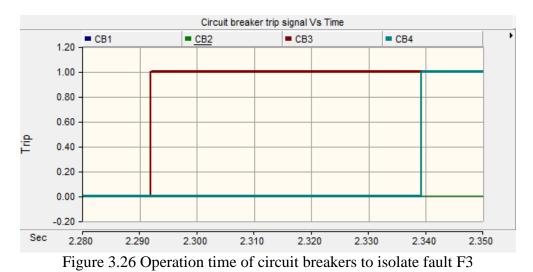

| 3.26 | Operation Time of Circuit Breakers to Isolate Fault F3 58                   |  |  |

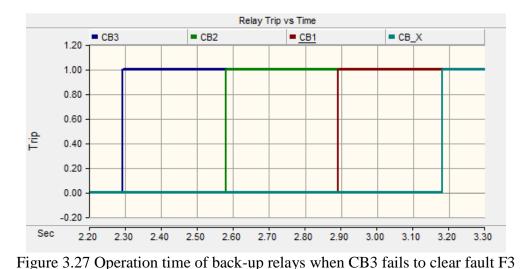

| 3.27 | Operation Time of Back-up Relays when CB3 Fails to Clear Fault F3. 59       |  |  |

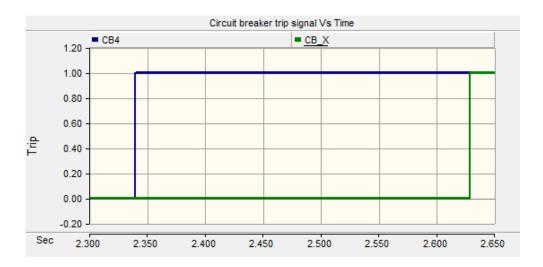

| 3.28 | Operation Time of Back-up Relays when CB4 Fails to Clear Fault F3. 59       |  |  |

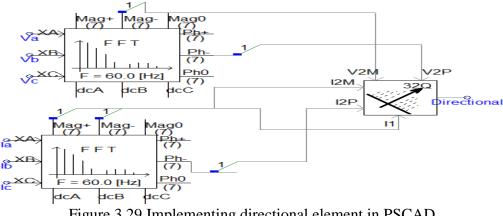

| 3.29 | Implementing Directional Element in PSCAD 62                                |  |  |

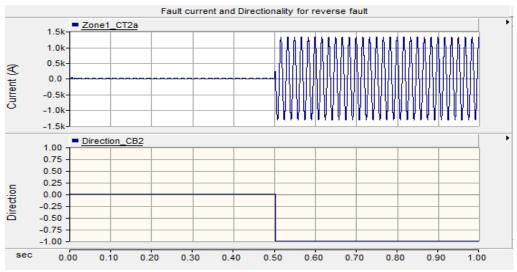

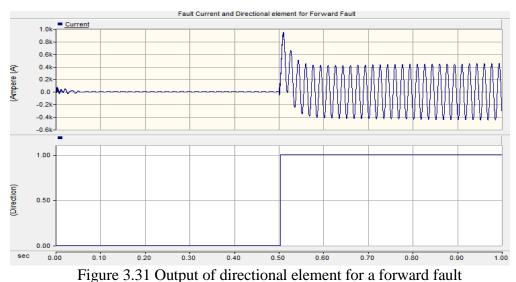

| 3.30 | Output of Directional Element for a Reverse Fault                           |  |  |

| 3.31 | Output of Directional Element for a Forward Fault                           |  |  |

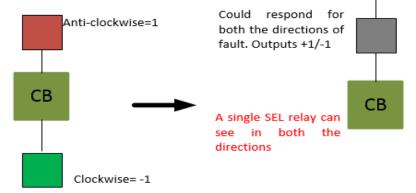

| 3.32 | Implementig Clockwise and Anti-Clockwise Relays using a Single Negative     |  |  |

|      | Sequence Directional Element F32 Q64                                        |  |  |

| 4.1  | Radial System with Sources fed from both ends65                             |  |  |

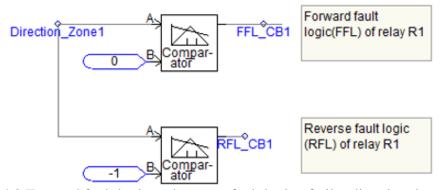

| 4.2  | Forward Fault Logic and Reverse Fault Logic of Pilot Directional Protection |  |  |

|      |                                                                             |  |  |

| 4.3  | Communication between the Relays 67                                         |  |  |

| 4.4  | FREEDM Loop with different Zones and Fault Locations                        |  |  |

| 4.5  | Trip Signal of CB1 for Fault at F1 70                                       |  |  |

| 4.6  | Trip Signal of CB2 for Fault at F1 71                                       |  |  |

| 4.7  | Trip Signal of CB2 for Fault at F2 71                                       |  |  |

| 4.8  | Trip Signal of CB3 for Fault at F2 72                                       |  |  |

| 4.9  | Trip Signal of CB3 for Fault at F3 73                                       |  |  |

| 4.10 | Trip Signal of CB4 for Fault at F3 73                                 |

|------|-----------------------------------------------------------------------|

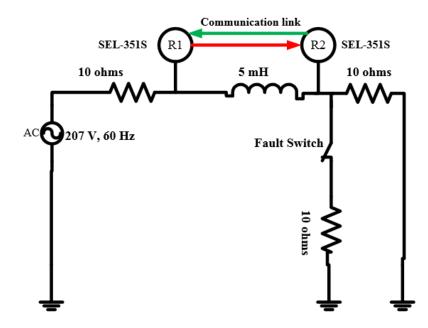

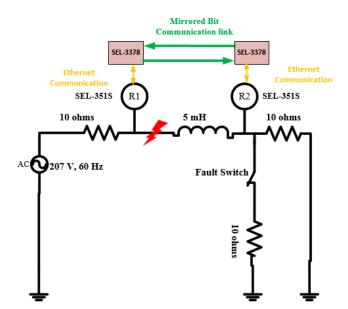

| 4.11 | Single Line Diagram of the Hardware Test Bed                          |

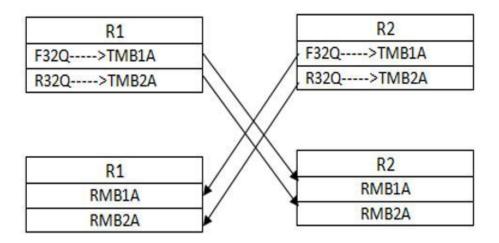

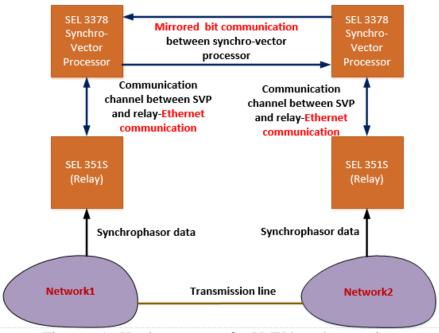

| 4.12 | Mirrored Bit Communication                                            |

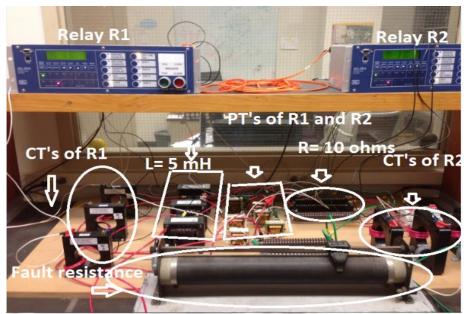

| 4.13 | Experimental Set up for Pilot Directional Protection                  |

| 4.14 | Trip Signal from AcSELerator Quickset Software of SEL 77              |

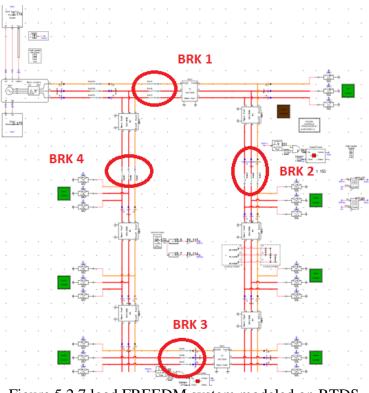

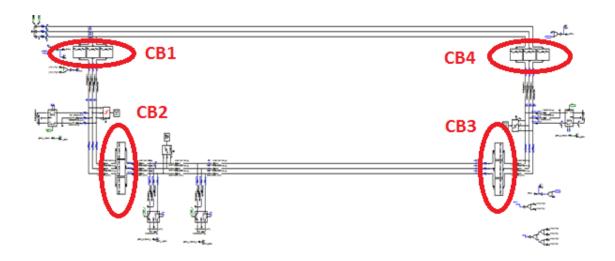

| 5.1  | 7 Load FREEDM Systesm developed by MS&T 78                            |

| 5.2  | 7 Load FREEDM System Modeled on RTDS 79                               |

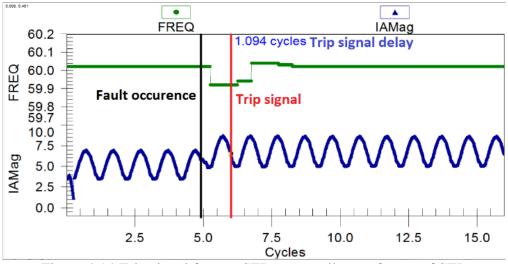

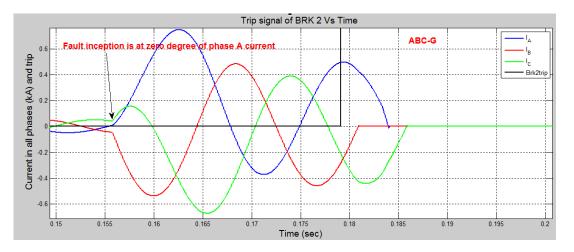

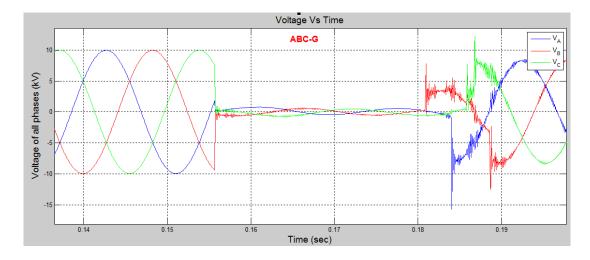

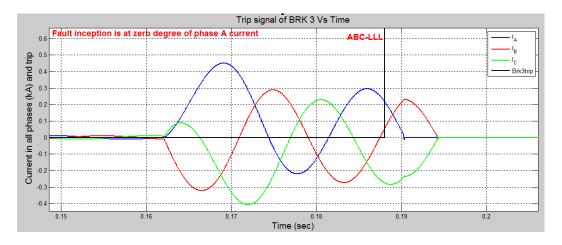

| 5.3  | Trip Signal of CB2 for a 3 Phase to Ground Fault 80                   |

| 5.4  | Voltage seen by Relay during 3 Phase Fault                            |

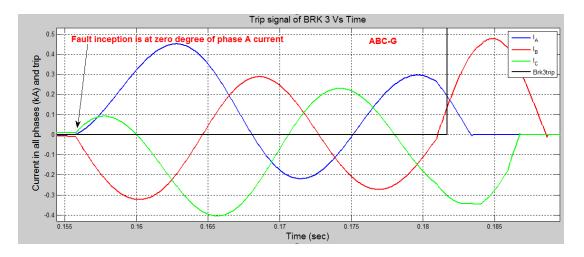

| 5.5  | Trip Signal of CB3 for a 3 Phase to Ground Fault                      |

| 5.6  | File Generated from AcSELerator Quickset for a 3 Phase Fault          |

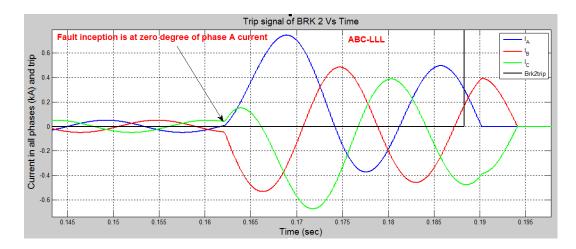

| 5.7  | Trip Signal of CB2 for a ABC-LLL Fault                                |

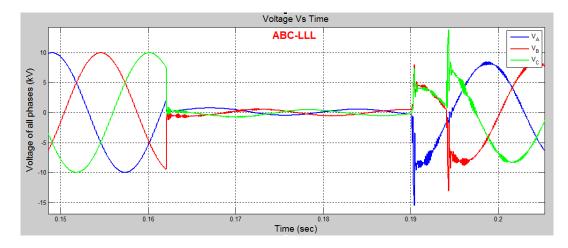

| 5.8  | Voltage seen by Relay for a ABC-LLL Fault                             |

| 5.9  | Trip Signal of CB3 for a ABC-LLL Fault                                |

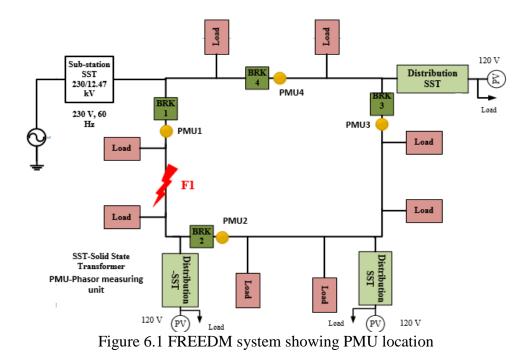

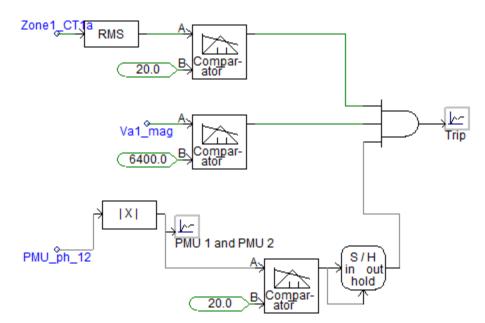

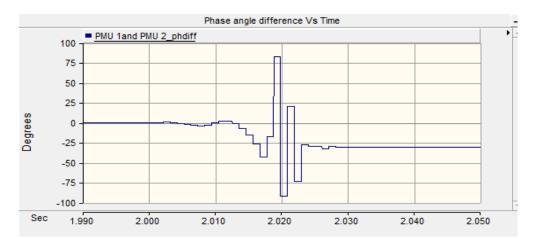

| 6.1  | FREEDM System showing PMU Location                                    |

| 6.2  | Logic to Detect an Event Using Synchrophasor Measurements             |

| 6.3  | Voltage Phase difference of Phase A between PMU 1 and PMU 2 for a SLG |

|      | Fault                                                                 |

| 6.4  | Absolute Value of Voltage Phase differene of Phase A between PMU 1 and |  |

|------|------------------------------------------------------------------------|--|

|      | PMU 2 for a SLG Fault                                                  |  |

| 6.5  | Voltage Phase difference of Phase A between PMU 2 and PMU 3 for a SLG  |  |

|      | Fault                                                                  |  |

| 6.6  | Voltage Phase difference of Phase A between PMU 3 and PMU 4 for a SLG  |  |

|      | Fault                                                                  |  |

| 6.7  | Voltage Phase difference of Phase A between PMU 4 and PMU 1 for a SLG  |  |

|      | Fault                                                                  |  |

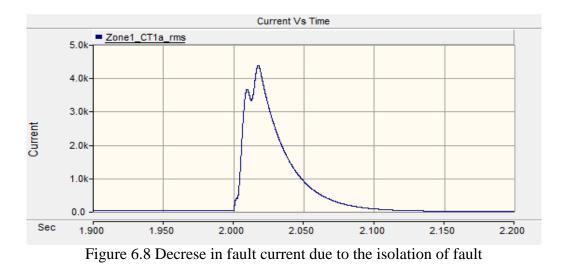

| 6.8  | Decrease in Fault Current due to the Isolation of Fault                |  |

|      |                                                                        |  |

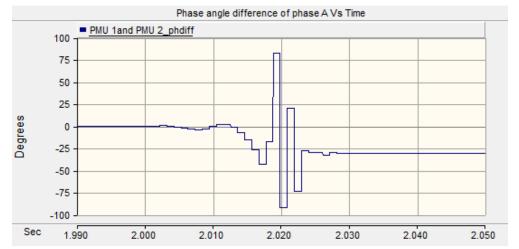

| 6.9  | Voltage phase difference of Phase A between PMU 1 and PMU 2 for ABC-   |  |

|      | GFault90                                                               |  |

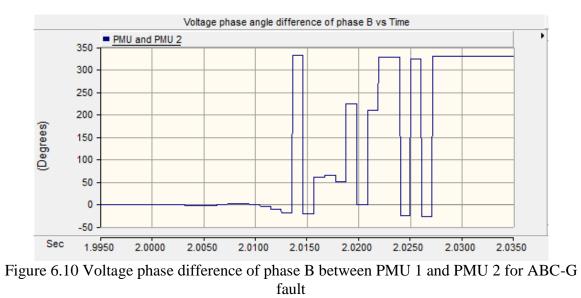

| 6.10 | Voltage Phase difference of Phase B between PMU 1 and PMU 2 for        |  |

|      | ABC-GFault                                                             |  |

|      |                                                                        |  |

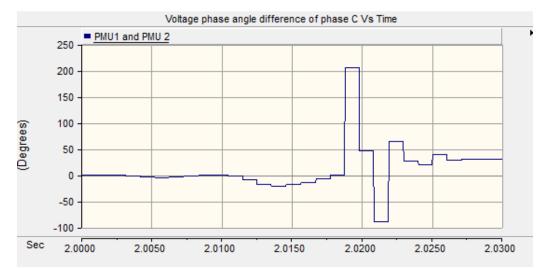

| 6.11 | Voltage Phase difference of Phase C between PMU 1 and PMU 2 for        |  |

|      | ABC-                                                                   |  |

|      | GFault                                                                 |  |

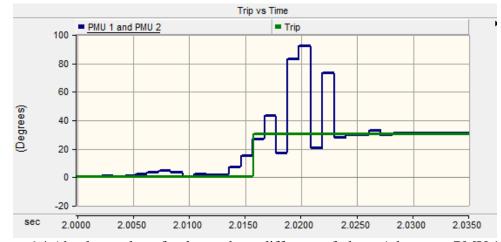

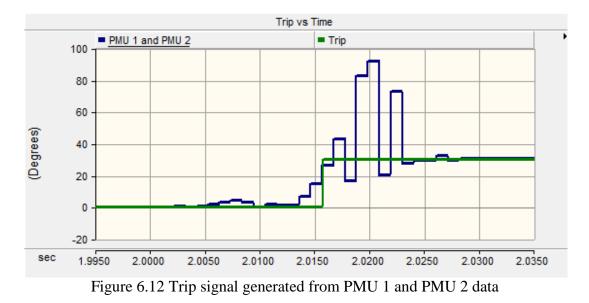

| 6.12 | Trip Signal Generated from PMU 1 and PMU 2 Data                        |  |

|      |                                                                        |  |

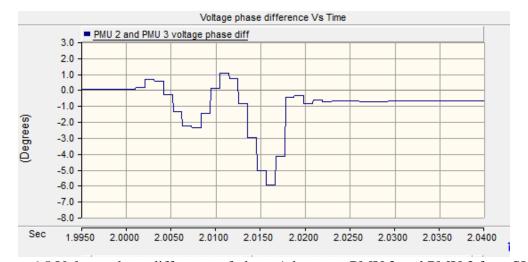

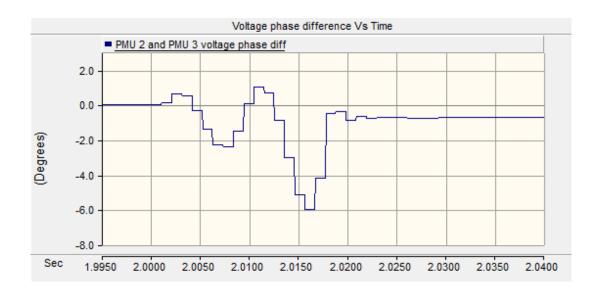

| 6.13 | Voltage Phase difference of Phase A between PMU 2 and PMU 3 for AF | 3C |

|------|--------------------------------------------------------------------|----|

|      | GFault                                                             | 2  |

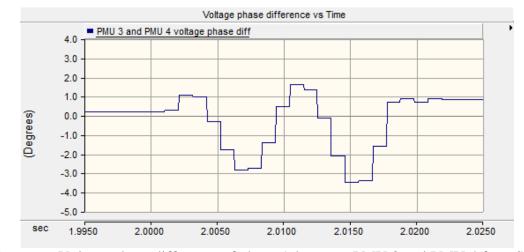

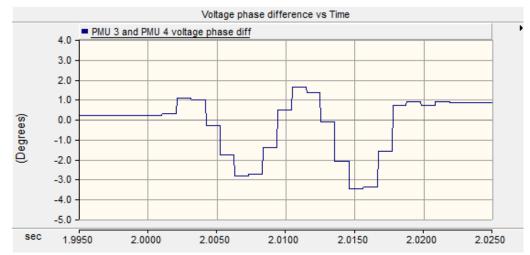

| 6.14 | Voltage Phase difference of Phase A between PMU 3 and PMU 4 for    |    |

|      | ABCG Fault                                                         | 3  |

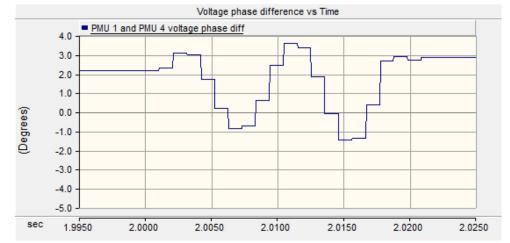

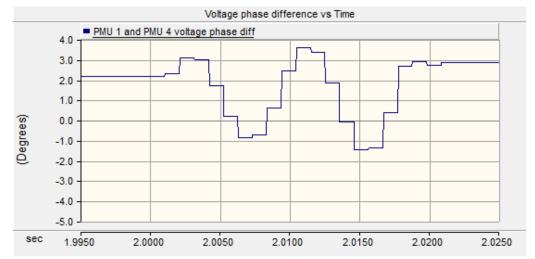

| 6.15 | Voltage Phase difference of Phase A between PMU 4 and PMU 1 for    |    |

|      | ABCGFault                                                          | 3  |

| 6.16 | Hardware Set up for PMU based                                      |    |

|      | Protection                                                         | 5  |

| 6.17 | Single Line Diagram of 3 Phase Test Bed used for Hardware          |    |

|      | Implementation96                                                   | )  |

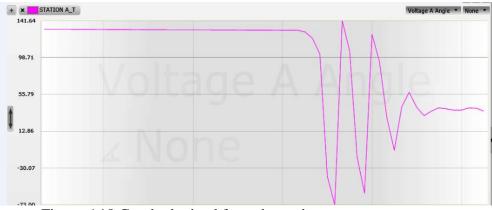

| 6.18 | Graph Obtained from Synchro Vector                                 |    |

|      | Processor                                                          | 5  |

# NOMENCLATURE

FREEDM Future Renewable Electric Energy delivery and Management

- SST Solid State Transformer

- AC Alternating Current

- *DC* Direct Current

- TDS Time Dial Settings

- FCL Fault Current Limiter

- RTDS Real Time Digital Simulator

- PMU Phasor Measuring Unit

- TIDOC Time Inverse Directional Overcurrent

- SCDR Symmetrical Component Distance relay

- FFL Forward Fault Logic

- RFL Reverse Fault Logic

- DG Distributed Generation

- PSAT Power System Analysis Tool

- CT Current Transformer

- PT Potential Transformer

- UPFC Unified Power Flow Controller

- SLG Single Line to Ground

- ABC-G Three Phase to ground

- ABC-LLL Three Phase Short Circuit

#### CHAPTER 1

# INTRODUCTION TO THE FREEDM SYSTEM

### 1.1 Overview

Burning out the fossil fuels for power generation and increased global warming caused by excessive  $CO_2$  emissions have become a greater concern for the US government [1]. In order to prevent the excessive exhaustion of natural resources by power companies without having a reduction in power generation, federal government passed a strict law to include the renewable sources in total power generation. In addition to the federal laws, ambitious renewable portfolio standards (RPS) and advancements in technology have led to an extensive increase in renewable integration in the US power industry. Renewable integration has become a dominant area of research both at the academic and industry level. Integrating wind, solar PV, bio-fuel and others to the existing power system at the distribution level would create a wide variety of technical difficulties. In spite of the advancement in power electronics, energy storage devices and communication there are still few problems like grid reliability, price of electricity and others that are to be taken care of while integrating renewable resources.

FREEDM (Future Renewable Electric Energy Delivery and Management) is an initiative by the National Science Foundation (NSF) to overcome the above mentioned problems. The solution to solve the energy crisis is not solely the renewable energy but the equipment involved in delivering the energy and maintaining the system operating conditions [1]. Due to the presence of local distributed generation, the power flow in the system is bi-directional and the conventional protection methods may face the problem of

false tripping. Due to the presence of power electronic converters and devices (power electronic based fault current limiters and solid state transformer) the behavior of fault current is different from a conventional distribution system [2], [3].

# 1.2 FREEDM system

FREEDM system was developed as a smart grid system with a motivation to include renewable sources into the existing power grid. FREEDM system is a culmination of high bandwidth digital communication, power electronics and digital communication [1]. It replaces conventional transformer of 60 Hz with solid state transformer (SST) incorporating bidirectional power flow. Solid state transformer is a package of cascaded rectifier, dual active bridge converter and inverter. It has an input of 7.2 kV AC and output of 120 V AC single phase, 208 V AC (3 phase) and 400 V DC. All the DC loads, distributed generation and energy storage devices are connected to the DC link and AC loads are connected to the AC output.

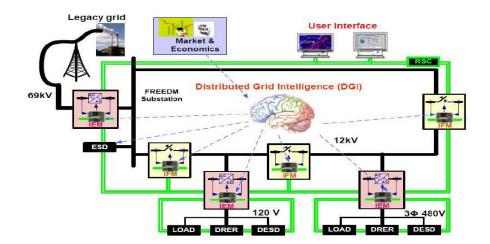

Figure 1.1 FREEDM concept model

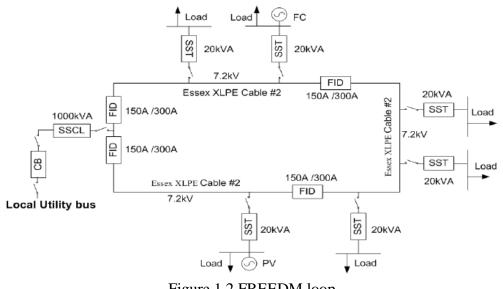

To demonstrate the advancement done in FREEDM project, a 1 MW green energy smart hub is under development. The proposed FREEDM loop allows consumers to plug and play energy sources or storage devices from anywhere on the loop [1]. To provide effective power flow, power distribution and fault detection; intelligent energy management (IEM) and intelligent fault detection (IFD) control schemes are incorporated in the FREEDM system. Following Figure 1.1 shows the schematic layout of the FREEDM system and Figure 1.2 shows the single line diagram of the FREEDM system. The FREEDM loop is connected to grid and in the case of grid failure, the loop can operate independently.

Figure 1.2 FREEDM loop

#### 1.3 Objectives of the research

The power flow in the FREEDM system is bi-directional due to the presence of distributed generation (DG) and the conventional protection methodologies must be modified accordingly to detect fault conditions and prevent false tripping. The solid state transformers (SST) have self-protection, which shuts them down during faults when the

voltage goes below a certain threshold voltage and it can be adjusted. In the case of a loop system during faults, the voltage of the entire loop plummets to zero or typically a low value. In such a scenario all the SST's connected to the loop will shut down due to its selfprotection. Hence, it is important to isolate the faulted part of the network from the rest of the system to prevent the shutdown for SST's. Pilot differential protection was developed as a solution to the above mentioned problem by former ASU FREEDM students. It was able to detect faults within quarter of a cycle but it suffered from the problem of communication [4]. Ethernet cable was used as the communication medium to transfer the sampled signals from the current transformers to the central processor. The central processor analyzes the sampled current signals, generates the trip depending up on the system conditions and sends the trip signal back to the breaker. The entire communication is carried out by the ethernet cable which is practically not feasible to implement for longer distances (7 mile to 10 mile) because of latency and economical factors. A solution to the above communication problem is suggested in this thesis as a part of FREEDM research work.

- A protection method is developed that could protect looped systems with multiple sources without using any sort of communication. Directional relays with time inverse over current characteristics are coordinated affectively to detect and sectionalize the fault location without affecting the healthy part of the system. This serves as a reliable back-up protection system when the communication system fails.

- A new pilot protection method is developed using the commercial SEL relays which uses the direction of fault currents to locate the fault. The communication is done using fiber-optic cables and the only data needed to be transferred between the relays is the

fault location which is transferred in the form of digital bits. Simulation, hardware implementation and real time digital system (RTDS) validation is explained in the thesis.

- A protection method is suggested monitoring the sychrophasor measurements, voltage of the system and current during faults.

- 1.4 Organization of the thesis

Chapter 2 presents the existing over current protection, differential pilot protection schemes and use of synchrophasor data in power system monitoring and control. Standard method of implementing pilot protection scheme is explained. Chapter 3 presents the development of time inverse directional over current and PSCAD simulation. Chapter 4 presents the development of pilot directional protection, PSCAD simulation, hardware implementation and validation of the protection scheme on RTDS system. Chapter 5 presents the validation of pilot directional scheme over the FREEDM system on real time digital simulator (RTDS). Chapter 6 presents the development of PMU based protection and hardware implementation. Chapter 7 presents conclusions, problems faced during hardware implementation and future work.

Appendix A presents the graphs showing trip signal of breakers, fault current magnitude and variation in system voltage for different faults at various fault angles. Appendix B presents the code used in Synchro Vector Processor (SVP) configurator used to communicate with the SVP SEL 3378. Appendix C presents the generator data and system data used in real Time Digital Simulator (RTDS) simulation. Appendix D presents

the power flow information used to determine the voltage phase angle difference during maximum power flow.

#### CHAPTER 2

# LITERATURE REVIEW

# 2.1 Over current protection

# Instantaneous Over current protection

Relay operates when current value goes beyond a preset threshold value. Instantaneous over current protection is most commonly used in distribution systems and equipment as a protection against short circuits and high fault currents.

# Definite time over current protection

Relays operate with a definite preset time delay when current value goes beyond a threshold value. It's operation is independent of magnitude of fault current above the threshold value.

# *Inverse time over current relays*

Relays operate when the current value goes beyond a pick up current value. The time of operation is inversely proportional to the magnitude of fault current. High fault currents operate the relay faster than lower value of fault currents. It has two settings:

- (i) Time dial settings (TD)

- (ii) Current pick up settings

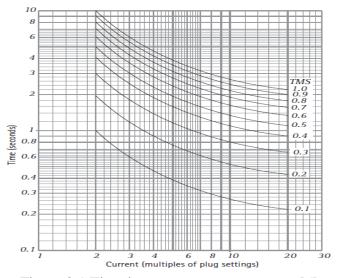

Figure 2.1 shows the time inverse over current characteristics with time dial settings and current pick up values.

Figure 2.1 Time inverse over current curve [5]

These relays are classified into different types based on their operating time and reset time. Table 2.1 and Table 2.2 describe the standard inverse time characteristic equations of the relays as per IEEE C37.112-1996 standards and IEC standards [5], [6].

| S.no | Curve Type              | Operating Time                                         | Reset Time                                    |

|------|-------------------------|--------------------------------------------------------|-----------------------------------------------|

| 1    | U1 (Moderately Inverse) | $t_p = TD. (0.0226)$                                   | $t_r = TD. \left(\frac{1.08}{1 - M^2}\right)$ |

|      |                         | $+\frac{0.0104}{M^{0.02}-1})$                          | 1 171                                         |

| 2    | U2 (Inverse)            | $t_p = TD. \left(0.180 + \frac{5.95}{M^2 - 1}\right)$  | $t_r = TD.(\frac{5.95}{1-M^2})$               |

| 3    | U3 (Very Inverse)       | $t_p = TD. \left(0.0963 + \frac{3.88}{M^2 - 1}\right)$ | $t_r = TD.(\frac{3.88}{1-M^2})$               |

| 4    | U4 (Extremely Inverse)  | $t_p = TD. \left(0.0352 + \frac{5.67}{M^2 - 1}\right)$ | $t_r = TD.(\frac{5.67}{1-M^2})$               |

| 5    | U5 (Short-Time Inverse) | $t_p = TD. (0.00262 + \frac{0.00342}{M^{0.02} - 1})$   | $t_r = TD.(\frac{0.323}{1-M^2})$              |

Table 2.1 Equations associated with US curves [6]

| S.no | Curve Type            | Operating Time                                     | Reset Time                                 |

|------|-----------------------|----------------------------------------------------|--------------------------------------------|

| 1    | C1 (Standard Inverse) | $t_p = TD.(\frac{0.14}{M^{0.02} - 1})$             | $t_r = TD.\left(\frac{13.5}{1-M^2}\right)$ |

| 2    | C2 (Very Inverse)     | $t_p = TD.(\frac{13.5}{M^2 - 1})$                  | $t_r = TD.\left(\frac{47.3}{1-M^2}\right)$ |

| 3    | C3(Extremely Inverse) | $t_p = TD.\left(\frac{80}{M^2 - 1}\right)$         | $t_r = TD.\left(\frac{80}{1-M^2}\right)$   |

| 4    | C4(Long time Inverse) | $t_p = TD.\left(\frac{120}{M-1}\right)$            | $t_r = TD.\left(\frac{120}{1-M}\right)$    |

| 5    | C5(Short-Time Invese) | $t_p = TD. \left(\frac{0.05}{M^{0.04} - 1}\right)$ | $t_r = TD.\left(\frac{4.85}{1-M^2}\right)$ |

Table 2.2 Equations associated with IEC curves

# Over current differential protection

Over current differential protection is based on the Kirchhoff's first law, "the sum of the current flowing into a node must be equal with the sum of the currents leaving the same node." Over current differential scheme is applied to various parts of power system equipment such as transformer, bus-bar, generators with small and moderate kVA, motors, transmission lines and other parts of the power system [7]. In the case of an external fault to a transmission line or a transformer, the sum of the current entering and leaving the element would be equal. However, in the case if an internal fault, current will be sinking into the element and summation of the current entering into the element will not be equal to the current leaving the element.

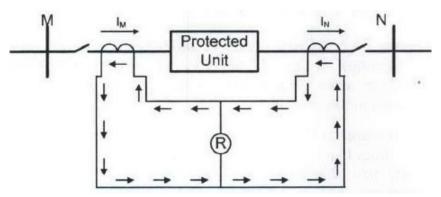

# *Operating principle of differential relay*

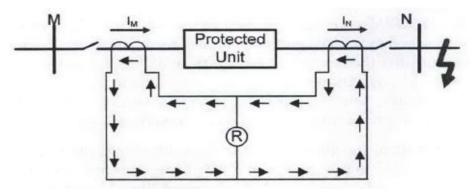

The current flowing through the operating coil is the difference of the input entering current and output leaving current. During the normal operation without any fault, both the entering current and leaving currents are equal. So the current in the operating coil is zero. Figure 2.2 shows the arrangement for differential protection of an element in the power system.

Figure 2.2 Operation of differential relay without fault [9]

During an external fault to the protected unit, the current in the operating coil is still zero as the current entering equals the current leaving the unit. Figure 2.3 shows the operation of a differential relay for an external fault.

Figure 2.3 Operation of differential relay for an external fault [9]

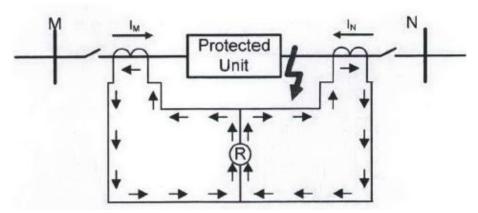

But for an internal fault current sinks into the protected unit and the current in the operating coil goes higher than the pickup value and results in a trip signal generation [8], [9]. Figure 2.4 shows the operating current activating the relay trip coil during an internal fault.

Figure 2.4 Operation of differential relay for an internal fault [9]

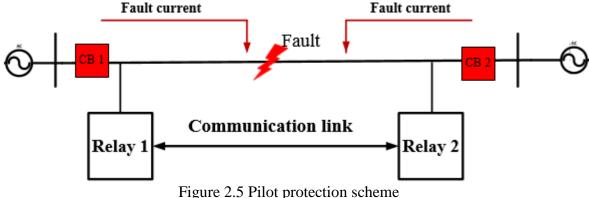

# 2.2 Pilot protection

The advancement of serial and wireless communication created a significant improvement in the usage of communication link in protection schemes. Pilot protection scheme employs communication to use the information from local relay and remote relay to effectively make decision for the trip signal generation. Fault clearing time is very important in long transmission lines operating at high voltage or extra high voltage. Any delays in the trip signal could cause severe stability problems to the network. High fault currents created in transmission lines could cause severe damage to the equipment. Hence it is vital to clear the fault as soon as possible and pilot protection helps to achieve the fast means of trip generation [10]. The communication in pilot protection schemes is usually analog or digital transmitting at power frequencies or higher frequencies. Following are few modes of existing communication [11].

- 1) Audio frequencies ranging from 20-20000 Hz,

- 2) Power carrier frequency in the range from 30 to 600 kHz,

- 3) Radio frequencies ranging from 10kHz to 100,000MHz,

- 4) Microwave frequency bands loosely applied to radio waves from 1000 MHz,

- 5) Visible light frequencies with nominal wavelength range of about  $0.3\mu m 30\mu m$ .

Pilot protection scheme is classified in following types depending on the quantities transferred and compared.

# *i.* Unit pilot protection schemes

In this protection scheme only the analog quantities such as amplitude or phase are compared over the communication link between the relays [11].

# *ii.* Non-unit pilot protection schemes

In this protection scheme the logical states related to fault information of the protection algorithm is transferred and compared over the communication channel between the relays or in a central processor to generate trip signal [11].

# Unit protection schemes

# *a)* Longitudinal differential Scheme or pilot differential scheme

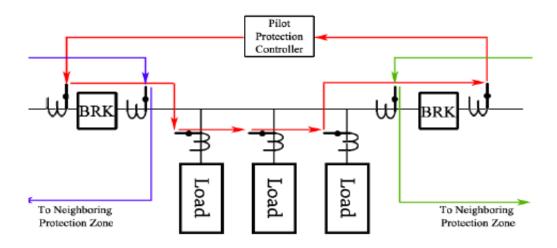

Pilot differential scheme is based on the principle of over current differential protection. The comparison of current signals and decision making takes place over the communication link. The relays gather the current magnitude and phase angle information and transfer it over the communicating link to the adjacent relays. The comparison of the signals and decision making for trip generation takes place in the relay or a centralized processor [9], [12]. Figure 2.5 shows basic pilot scheme.

#### *b*) Pilot differential protection in commercial relays

Commercial relays like SEL 587 (Current differential relay), SEL 387 (Current differential and over current relay), SEL 387L (Line current differential relay) and SEL 311L (Line current differential protection and automation system) could be used to implement line differential protection or a transformer differential protection. These commercial relays could be programmed according to the differential algorithm to generate trip signal [13].

#### c)Communication medium and available protocols

The transfer of analog data from one relay to the other is facilitated through various means of communication medium. SEL provides serial cable, ethernet, fiber-optic and radio-wave communication. All the relays have serial and ethernet ports on the devices to facilitate communication [5]. Fiber-optic communication is achieved using a serial to fiber interface. SEL 2814 and SEL 2812 is widely used serial to fiber optic interface to transmit the signals over fiber-optic cables. Two sets of fibers should be used to transmit and receive the signals. Selection of fiber optic transceivers must be done basing on how long the data must be transferred. Radio wave communication is achieved using the SEL-3031 module.

It could generate waves up to 915 MHz with point to point and point to multiple point operation modes [13]. All the communication ports could be accessed by various protocols. Following are the communication protocols present in the SEL relays:

1) DNP 3

2) Modbus

3) SEL fast messages

4) Mirrored bit communication

5) Plain ASCII

# Protection method

The analog current signals are transferred with the time stamp using a synchronized GPS clock. Instantaneous current values and current phase angles are transferred over the available communication cables using any of the above mentioned protocols [14], [15]. Figure 2.6 shows the schematic for pilot differential protection.

Figure 2.6 Pilot differential protection

Current signal at every load is sampled with a GPS time stamp and passed through the following algorithm [12] to determine the existence of fault in the system.

$$\frac{I_{Operation-I_0}}{I_{Restrain}} \leq S_0$$

$$I_{Operation} = |I_1 + I_2 + I_3 \dots \dots I_n|$$

$$I_{Restrain} = |I_1| + |I_2| + |I_3| \dots \dots |I_n|$$

$$I_0 \text{ is 10 \% of nomial operating current}$$

$$S_0 \text{ is the threshold slope usually set to 0.3 or 0.4}$$

$$(2.1)$$

If the ratio of operation current to restrain current is more than the threshold slope value then the algorithm designates this condition as fault in the system.

*d) Phase comparison scheme*

In this pilot protection scheme, the phase angles of the currents and voltage are transferred over the communication link to a central processor or relays to make the decision for trip generation based on the variation of the phase angle difference during faults. Care must be taken when implementing this protection method, as the change in network configuration would result a change of the phase angles [16].

#### *Non-unit pilot protection schemes*

#### a) Distance scheme

Communication in distance protection can eliminate the time delays that occur to detect the existence of faults in zone 2 or zone 3. Local relays could communicate to the remote relays in long transmission lines to guarantee the fault and it could speed up the operation. Permissive under reaching and permissive over reaching are the popular pilot schemes used.

# 2.3 Detecting the direction of fault current

Above explained pilot methods transfer analog signal data with a time stamp. The implementation of the above methods requires a huge data storage and data handling capacity by the communication system. One solution to the above problem is to use the direction of fault current to locate the fault. Following explains the different methods developed in the literature to determine the fault current direction.

The deviation in the voltage and current from normal steady state condition due to fault was used to determine the power direction. But there is a chance for the protection strategy to mis-trip if it fails to distinguish in between the switching transients and lightning with fault conditions [17]. A new method was developed using the superimposed sequence currents (vector ratio of positive sequence and negative sequence currents) to determine the faulty phase and fault current direction [18]. It requires a high speed phase selector in-order to determine the fault phase by comparing the sequence components. The evolution

of microprocessor relays simplified the work of protection engineers to find the sequence components. Scalar product of incremental in voltage and current is used to determine the fault current direction [19]. Following section describes different methods used to implement the directional relay.

# *i.* Conventional method

In electro-mechanical relays the direction of fault is determined depending on the direction of torque produced. The torque equation for the electro-mechanical relay is shown below.

$$T = V_{pol} I_{op} \cos(\angle -V_{pol} - \varDelta_{op})$$

(2.2)

# $I_{op}$ is the current of the faulted phase

Positive torque results from forward faults and negative torque from reverse faults. Jeff Roberts and Armando Guzmán demonstrated that equation 2 is computationally efficient to determine the fault direction in microprocessor based relays [20].

$$T = Re[-V_{pol}.I_{pol}] \tag{2.3}$$

There is no single approach that could work for all faults and all line configurations. Therefore microprocessor based relays use multiple algorithms in combination to determine fault location. Polarizing signals are a reference for comparing the operating quantities that are affected during fault. They help to determine the direction of fault to a relay (forward or reverse). Polarizing signals should be present at all the times irrespective of fault type and location.

# ii. Cross polarizing

During a single phase to ground fault the  $V_{PN}$  (phase to neutral voltage) goes to zero and the corresponding fault current lags the voltage by a large angle due to the high reactance of line. This prevents the relay from detecting the correct fault direction. To resolve the low voltage issue the voltage of unaffected phases is used. Phase to phase voltages (VBC and IA) are used to detect the direction of fault [21].

| Faulted phase | Operating Quantity | Polarizing Quantity |

|---------------|--------------------|---------------------|

| А             | Ia                 | Va-Vb               |

| В             | Ib                 | Vc-Va               |

| С             | Ic                 | Va-Vb               |

| AB            | Iab                | -j.Vc               |

| BC            | Ibc                | -j.Va               |

| СА            | Ica                | -j.Vb               |

Table 2.3 Cross polarizing table

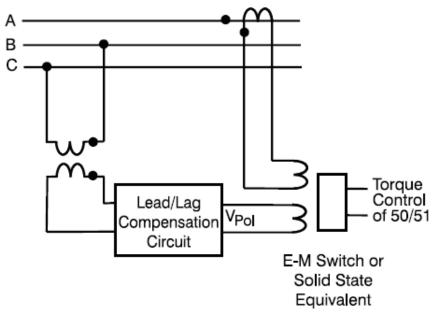

To overcome the backdrop due to high lagging current, the voltage of the relays in the algorithm is passed through a lead or lag compensator so that the relays could detect the fault. Figure 2.7 shows the compensation of phase-phase voltage [22]. Every relay manufacturer has its own voltage compensation algorithm to detect the fault.

Figure 2.7 creating phase angle difference between voltage and current [21]

The development of micro-processor relays enabled protection engineers to use sequence components for developing new methods to determine the direction of fault current. Zero-sequence voltage polarization, zero-sequence current polarization, negative sequence polarization are the popular methods developed from sequence components.

# *iii.* Zero sequence voltage polarization

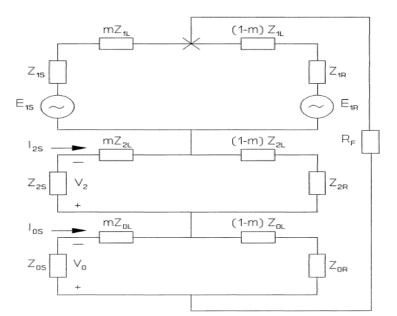

Zero sequence voltage polarization measures the angle between the zero sequence voltage and residual current to determine the direction of fault current. Residual current is obtained from summation of individual phase currents and is usually obtained from the current transformer installed in the neutral wire. The residual current and the zero sequence voltage are displaced by an angle of line impedance and source impedance [23], [24]. Figure 2.8 represents the sequence network of a system with sources  $E_S$  and  $E_R$  supplied from both the ends. The fault location on the line is at a distance  $m.Z_{Line}$  where m is the per unit length of the line.

Figure 2.8 Sequence networks for a single line to ground fault [24]

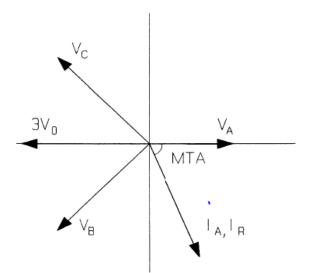

Because of the reactive nature of the transmision line and the fault impedance being reactive the torque developed is maximum when current lags the residual voltage by an angle called "Maximum Torque Angle (MTA)."

$$32VT = |V_0| \cdot |I_R| \cdot [\cos(\angle -V_0 - (\angle I_R + MTA))]$$

(2.4)

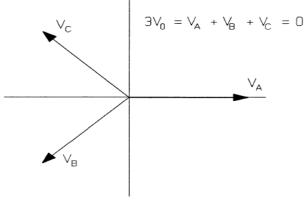

The torque value is positive for a forward fault and negative for a reverse fault. The directional elements also require minimum voltage and current for their operation to produce torque value. Figure 2.9 shows the balanced phase angles of a system.

Figure 2.9 Balanced phase voltages [24]

Assuming there is a phase to ground fault on phase A with a negligible resistance the voltage of phase A gets diminished. Figure 2.10 and figure 2.11 show the lagging current and the zero sequence voltage developed.

Figure 2.10 Phase voltage during SLG fault on phase A [24]

Figure 2.11 Operating region and restraining region if the relay [24]

#### *iv.* Zero Sequence Current Polarization

For few fault conditions the residual voltage developed is not sufficient to polarize the relay. To overcome such scenarios, the neural current of a transformer (near to the relay) with a grounded neutral can be used as a polarizing quantity [24]. For a forward fault, the residual current seen by the relay and the neutral current are in the same direction. For a reverse fault, the direction of the residual current is in opposite direction to that of the neutral current.

$$32IT = \left| I_{pol} \right| \cdot \left| I_R \right| \cdot \cos(\angle I_{Pol} - \angle I_R)$$

$$(2.5)$$

From the torque equation, the maximum torque is developed when the polarizing current and the residual current are in phase. One thing that has to be taken care of when using this technique is the direction of polarizing current has to be same for all faults. If the direction of the polarizing current is not the same then this technique cannot be used. Figure 2.12 shows the direction of fault current and polarizing current for a forward fault.

Figure 2.12 Current polarization for forward fault [24]

Figure 2.13 shows the direction of fault current direction and polarizing current for a reverse fault.

Figure 2.13 Current polarization for reverse fault [24]

#### v. Dual Polarization

Both the zero sequence voltage polarization and zero sequence current polarization are used when the residual voltage is not sufficient and when the auto-transformer is out of service. Any one of the above methods can be used to detect the direction of fault current when the appropriate polarizing quantity is present [24].

#### vi. Negative Sequence Polarization

Negative sequence voltage and current are used to determine the direction of fault current in this technique. Negative sequence directional elements are very helpful when the zero sequence polarizing current is not reliable [24].

$$32QT = |V_2| \cdot |I_2| \cdot \cos(\angle -V_2 - (\angle I_R + MTA))$$

(2.6)

The output of the torque is positive for a forward fault and negative for a reverse fault. This technique fails when the negative sequence voltage is insufficient for the relay to operate as it has some minimum sensitive levels. This drawback is overcome with the following approach developed by Edmund O. Schweitzer, III.

#### vii. Negative Sequence impedance technique

Relay calculates the apparent negative sequence impedance between the faults and relay location. It overcomes the problem of weak polarizing quantity caused by low voltage source (weak in-feed) behind the relay. For faults at remote location, the magnitude of negative sequence voltage seen by the relay might be very less. To overcome this problem a compensating quantity is added that boosts the negative sequence voltage. The compensating quantity is added to V2 for forward faults and subtracted for reverse faults.

$$Z_{2} = \frac{Re[V_{2}.(I_{2}.1\angle\theta)^{*}]}{Re[(I_{2}.1\angle\theta).(I_{2}.1\angle\theta)^{*}]} = \frac{Re[V_{2}.(I_{2}.1\angle\theta)^{*}]}{I_{2}^{2}}$$

(2.7)

The calculated  $Z_2$  is compared to the forward and reverse impedance thresholds to determine the fault location. If the calculated impedance is less than the forward threshold impedance then he fault is forward, if  $Z_2$  is greater than reverse threshold impedance then the fault is reverse. If the calculated impedance  $Z_2$  lies within forward threshold impedance and reverse threshold impedance then there is no fault [25]. This approach is not affected by the zero-sequence mutual coupling between the parallel lines [26], [27], [28].

#### 2.4 Application of synchrophasors in power system monitoring, protection and control

Power system is a vast electrical network spread through the geographical locations. Electricity is transferred from the generation site to hundreds of miles over various locations. It is highly essential to monitor the states of power system to effectively monitor the operation and control of power delivery. Voltage magnitude, voltage phase angle, current magnitude, current phase angle and frequency are the important states that should be monitored. If these values are known active and reactive power in the system can be calculated using the line impedance.

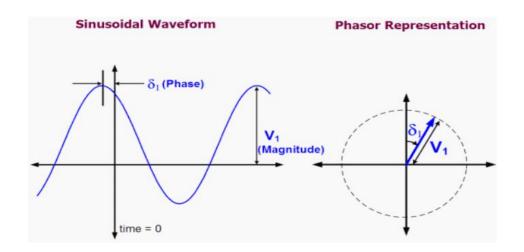

Due to the vast separation between different electrical nodes it was difficult to estimate these states. However, with the development of synchrophasor measurements the above challenge could be handled effectively with good communication technology. The device capable of measuring synchrophasors is called phasor measuring unit (PMU). A phasor is a complex number that represents magnitude and phase angle of a waveform at specified frequency at a specific point in time [29]. Figure 2.14 shows the phasor representation of a sinusoidal waveform.

Figure 2.14 Representation of synchrophasor [30]

GPS synchronized time stamp is used as a reference for the measurement of phasors. The widely accepted standards for measuring and communicating the time stamped signals are defined in IEEE C37.118 standards.

#### IEEE C37.118 standards

These standards specify the frequency and rate of change of frequency under all operating conditions. It specifies only about the measurements but not about the hardware, software and the method for computing these phasors.

The standard mentions about two classes of performance: M and P. In the M class, phasors are passed through an anti-aliasing filter and are used in the applications where the fast transfer of signals is not needed. In the P-class, the signals are not passed through any sort of filter and are typically intended to use for protection application. The standard also talks about the accuracy of the measurements in terms of Total Vector Error (TVE). The maximum allowable phase angle error is 0.57 degrees [31], [32], [33].

#### History of PMU development and its wide area applications

The blackout of 1965 in North-East United States resulted in wide areas of research to improve the secured operation of power system. The idea of static state estimator was introduced to have a wide area monitoring of the system. Due to the technological limitations at that point of time, an approximate state estimation is evaluated known as quasi-steady state using the wide area inputs [34].

Computer relaying was first introduced as a research field in 1960's to detect the fault location. This research led to the development of symmetrical component distance relay (SCDR) for protecting high voltage transmission lines [35], [36]. PMU was developed from the idea of SCDR. It was first developed in 1988 by Dr. Arun G. Phadke and Dr. James S. Thorp at Virginia Tech and the phasor calculation is based on the paper presented by Charles Proteus Steinmetz about using the mathematical description of complex numbers in electrical engineering [37]. Since then, PMU's have become a wide area of research for their application in monitoring, protection and control.

Paper [38] presents a method to use current differential algorithm along with wide area measurements to secure the operation of distance relays during power swing blocking. A new algorithm is presented in paper [39] to determine the fault location without installing PMU at every bus location. It uses the phase angle data to find out the area in which the fault has occurred. Particle swarm optimization is then used to find out the exact location of the faulted section in the network. A wide area back-up protection algorithm is suggested in [40] that could detect the faulted branch basing on the steady state fault components. Subsets of bus called as protection correlation regions (PCR) are formed, basing on the placement of PMU's at bus locations and network topology. During fault conditions, the steady state components of the network are co-related to the PCR's to determine the exact faulted branch.

An algorithm to detect fault location in a combined overhead and under-ground transmission line system has been proposed in [41] using the positive sequence voltage and synchrophasor at both the ends of a line section. This method helps to block the operation of re-closer when the fault is determined in under-ground section. The advantage of synchrophasor measurements over the SCADA monitoring to determine the control decisions is discussed in paper [42]. Syncrophasor data could help in visualizing power system conditions and dynamics, efficient operation of manual and automatic control systems and protective relays could take high speed control actions which have an impact on the system stability. A predictive out of step condition is presented in [43] based on the real time dynamic states monitoring for the system's transient swings using the dynamic state estimation. Dynamic state estimation is performed using the synchrophasor measurements at the generator terminals and at the end of line. A new protection method for transmission lines without series compensation is proposed using the synchronized phasor measurements in [44], [45]. In paper [46], a novel method to detect the fault location

in presence of thyristor controlled series compensated transmission line (TCSC) is proposed using the synchronized phasor measurements at the line ends. A new method for fault detection and fault location in presence of UPFC using the GPS based phasor measurement is suggested using the sequence components [47]. It could accurately detect the fault location and existence of fault in the presence of UPFC unlike distance relays which suffer from the problem of over reach or under each [48].

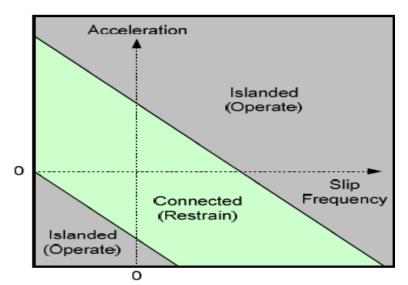

A smart Remedial Action Scheme (RAS) is proposed in [49] using the PMU data. It helps to identify the lines that could cause the system to suffer from stability issues due to heavy loading and during sustained faults. It could generate the trip signals to protect the lines by monitoring the live load flow. Phase angle data from the PMU is used to trip off the distribution relays at the local generation (DG's) using the telecommunication signals. This method lets the distribution generation to ride through the system faults [50]. Real time transmission line data measurement is done using the PMU data to use in the protective relays. The settings of distance relays could be updated adaptively to the change in the operating conditions of the system [51]. Existing zone 3 elements of distance relay that act as a back-up suffer from the problem of unintentional tripping. Back up relays use the local measurements to detect the fault occurrence and they are not accurate in distinguishing the faults from heavy loaded conditions or stressful conditions. A novel method is proposed in [52] to supervise and secure the operation of back up relays using the synchronized state estimation form the PMU data. The proposed method assumes the system is fully observable from the installed PMU's. Paper [53] talks about the use of PMU data to identify stable and unstable regions to determine out of step tripping. The variation of phase angle with respect to time (slip frequency) and change of slip frequency with time is found. These are mapped on a slip frequency and acceleration graph to identify the regions of stability and instability. Paper [54] talks about the use of slip frequency and rate of change of frequency (slip acceleration) to determine the islanding condition for distributed generation. Following shows the graph of slip acceleration versus slip frequency to determine the islanding condition. Figure 2.15 shows the restrain region and operating region for islanding mode basing on the slip frequency and acceleration.

Figure 2.15 Stable and un-stable region to determine out of step tripping [55]

The ability to use the time stamped synchrophasor measurements to detect the voltage instability and respond, high speed distributed generation islanding complying with IEEE 1547 standards and grid interconnection oscillations are shown in paper [55], [56]. Conventional methods for voltage drop calculation and fault detection in series compensated transmission lines use the model of series compensated (either the switched capacitor or FACTS device) in the algorithm. The algorithm suffers from the back-drop that it could not exactly estimate the mode of operation of the compensation device and gives erroneous results in the fault detection and location. A new method to

detect the fault location is proposed without using the model of series compensation device and using the synchrophasor values at the line terminals is proposed in [57]. The proposed algorithm initially estimates the fault location and corrects the value in the next step depending on the type of fault.

#### CHAPTER 3

#### TIME INVERSE DIRECTIONAL OVER CURRENT PROTECTION

This section describes the implementation of time inverse over current protection with directional capability for loop systems. This method is applied over FREEDM loop to demonstrate it's working and capability to detect faults.

# 3.1 Protection algorithm

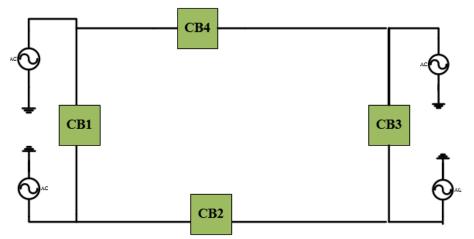

For a fault on any section of the loop, fault current is driven from both the ends. Fault current magnitude is almost same in all the sections of the loop. Due to this, it is very difficult to co-ordinate over current relays in a loop system. In order to detect and sectionalize the fault a directional element must be added to the relays which could detect fault current only in one direction [58]. Figure 3.1 shows a loop system with a breaker in each section and is fed with multiple sources.

Figure 3.1 Loop system fed with multiple sources

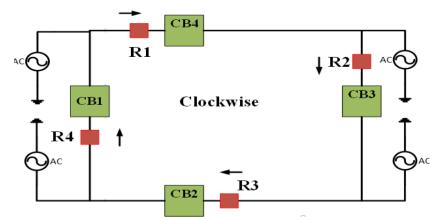

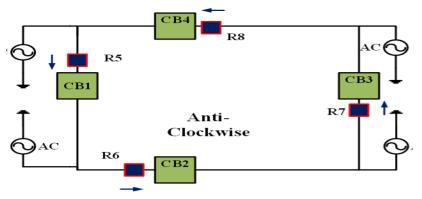

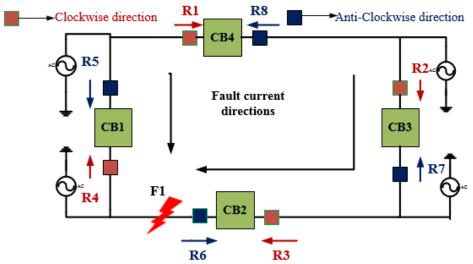

In order to identify the fault location, two set of relays are selected which act in clockwise and anti-clockwise direction during faults. R1, R2, R3, R4 are selected to operate

in clockwise direction and R5, R6, R7, R8 in anti-clockwise direction. Figure 3.2 and Figure 3.3 show the location of clockwise and anti-clockwise relays respectively.

Figure 3.2 Location of clockwise relays on the loop system

Figure 3.3 Location of anti-clockwise relays on the loop system

The location of a fault is sensed by the closest clockwise and anti-clockwise relays located near the circuit breakers. In addition to the directional capability, relays are fed with the time inverse over current characteristic. When a fault occurs, relays act according to time inverse over current characteristics and the relays closest to the fault act first. For a relay to respond, both the directional and time inverse over current element must be set at high. The operation of relays during a fault is explained below in the Figure 3.4.

Figure 3.4 Fault location F1 on the loop system

For a fault at F1, fault current passes through the relays R5 and R4 in anti-clockwise direction and through relays R1, R8, R2, R7, R3 and R6 in clockwise direction. Since R5 is configured to act in anti-clockwise direction, it responds to the fault current and R4 does not detect the fault. Similarly R1, R2 and R3 detect the fault current and respond while the relays R8, R7 and R6 stay idle. Since all the relays are configured to act according to time inverse over current characteristics with a coordination time interval (CTI) of 0.3 s, only the relay closest to fault location acts first. Therefore the relays R3 and R5 operate to isolate the fault. If R3 fails to operate, R2 backs up R3 after 0.3 s and if R2 also fails, R1 backs up R2 after 0.3 s.

## 3.2 Implementation of protection scheme over the FREEDM loop

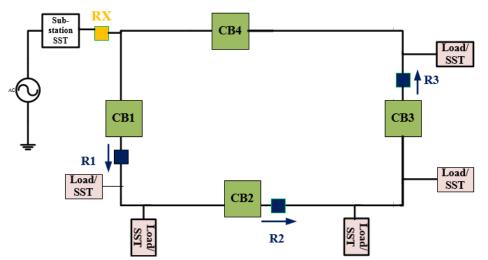

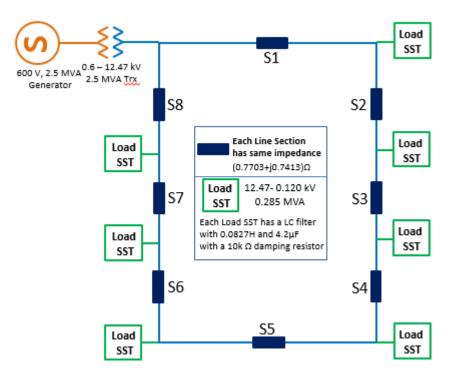

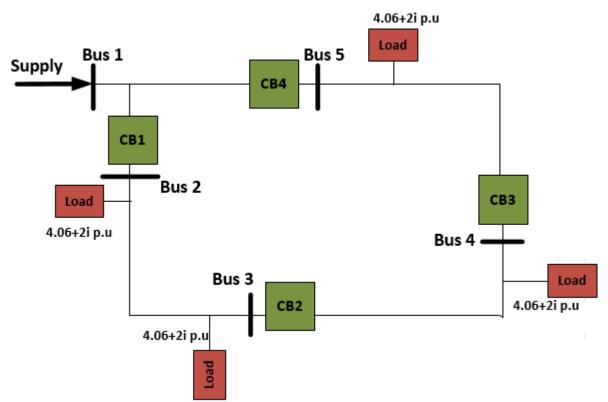

Future Renewable Electric Energy Delivery and Management (FREEDM) loop is a 12.47 kV, 2 MVA distribution system with local generation, energy storage devices capable of supplying both alternating current (AC) and direct current (DC) supply through solid state transformer (SST) [60]. The system used in the simulation has 4 breakers located in each section of the loop with solid state transformers and local loads [4]. Above mentioned algorithm is applied on the FREEDM loop and Figure 3.5 shows the model used in simulation.

Figure 3.5 Arrangement of anti-clockwise relays on the FREEDM loop

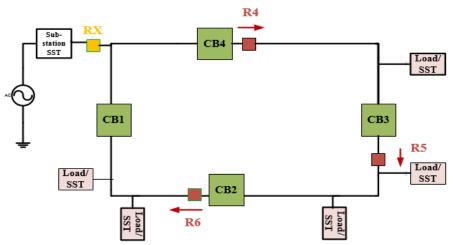

In Figure 3.5, relays R1, R2 and R3 are anti-clockwise and RX is the sub-station relay used to isolate the loop for faults near the sub-station. Co-ordination is done in such a way that R2 backs up R1 and R3 backs up R2. If R3 fails, RX operates. Figure 3.6 shows the arrangement of clockwise relays and their coordination.

Figure 3.6 Arrangement of clockwise relays on the FREEDM loop

Coordination is done such that R6 backs up R5, R5 backs up R4 and if R4 fails to operate RX operates. Following section shows the operating relays and their corresponding

operating times for faults at various locations on the test bed at 0.2 s. For simulation, the forward threshold impedance is taken to be 0.5 ohm and reverse threshold impedance is taken to be 0.6 ohm. The area in between the CB1 and CB2 is considered as zone 1, CB2 and CB3 is considered as zone 2 and, CB3 and CB4 is considered as zone 3.

#### 3.3 Single line to ground fault at location F1

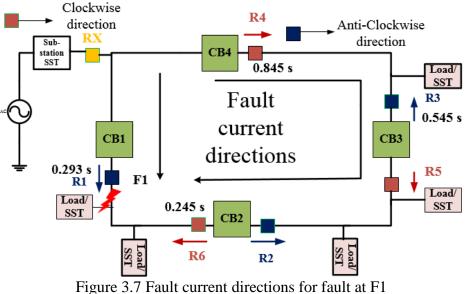

Figure 3.7 shows the location of a single line to ground (SLG) fault F1 on phase A at 0.2 seconds and the direction of fault currents in the loop. Calculations for current transformer (CT) selection, current pick up values and time dial settings of the relay are shown in the next section.

For a fault F1 at 0.2 s, relays R1 and R6 act to isolate the fault. Relay R1 acts as the fault current passes through it in anti-clockwise direction and R6 acts as fault current passes through it in clockwise direction. Relays R4 and R5 also act as the fault current passes through it in clockwise direction. But only the relays close to the fault acts first due to the time inverse characteristics. R5 acts if R6 fails to operate with a co-ordination time interval of 0.3 s. If R5 fails, R4 backs-up after 0.3 s.

Relays R1 and R6 are the primary relays. R1 operates at 0.293 s and R6 operates at 0.245 s. If R6 fails to operate, R5 backs up R6 with a CTI of 0.3 s at 0.545 s and if R5 fails, R4 backs up R5 at 0.845 s. If all the relays fail to operate relay RX disconnects the supply from the rest of the system. Time shown in the Figure 3.7 is the instance at which the relay operates for fault at 0.2 s, not the time of operation. Time of operation of R1 is 0.293-0.2=0.093 s which is approximately 5.8 cycles.

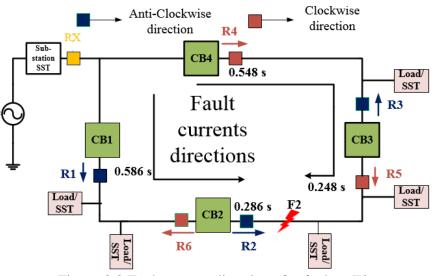

3.4 Single line to ground fault at location F2

Figure 3.8 shows the location of a single line to ground (SLG) fault F2 on phase A at 0.2 seconds and the direction of fault currents in the loop.

Figure 3.8 Fault current directions for fault at F2

For a fault at F2, relays R2 and R5 are the primary relays. Relay R2 acts at 0.286 s and R5 acts at 0.248 s. If R5 fails, R4 backs up R5 with a CTI of 0.3 s at 0.548 s. If R2

fails, R1 backs up R2 with CTI of 0.3 s at 0.586 s. If all the relays fail to act, then RX disconnects the supply from the system.

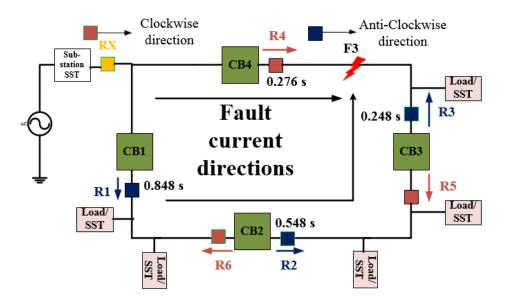

## 3.5 Single line to ground fault at location at F3

Figure 3.9 shows the location of a single line to ground (SLG) fault F3 on phase A at 0.2 seconds and the direction of fault currents in the loop.

Figure 3.9 Fault current directions for fault at F3

For a fault at F3, relays R4 and R3 are the primary relays. R3 acts at 0.248 s and R4 acts at 0.276 s. If R3 fails to operate, R2 acts at 0.548 s and if R2 fails, R1 acts at 0.848 s. If R4 fails to operate, RX disconnects the supply from the system. Table 3.1 shows the operation time of the relays for faults F1, F2 and F3 at 0.2 seconds.

Table 3.1 Operating times of relays corresponding to circuit breakers

| Fault | CB1     | CB2     | CB3     | CB4     |

|-------|---------|---------|---------|---------|

| F1    | 0.093 s | 0.045 s | XXX     | XXX     |

| F2    | XXX     | 0.086 s | 0.048 s | XXX     |

| F3    | XXX     | XXX     | 0.048 s | 0.076 s |

3.6 Selection of time dial settings and current pick values for time inverse over current relays

Extremely time inverse over current characteristic is considered to coordinate the relays. Table 3.2 shows the fault current magnitude seen by relays for ABC-G fault and SLG fault on phase A at different sections of the loop.

|       | Curre          | urrent seen Current seen by |                |        | Current        | seen by | Current seen by |       |  |

|-------|----------------|-----------------------------|----------------|--------|----------------|---------|-----------------|-------|--|

|       | by relay R1 at |                             | relays         | R2, R6 | relays         | R3, R5  | relay R4 at     |       |  |

|       | CB1 in         | n zone 1                    | at CB2 in zone |        | at CB3 in zone |         | CB4 in zone 3   |       |  |

|       | (k             | xA)                         | 2 (kA)         |        | 2 (kA)         |         | (kA)            |       |  |

| Fault | LLL-           | SLG                         | LLL- SLG       |        | LLL-           | SLG     | LLL-            | SLG   |  |

|       | G              |                             | G              |        | G              |         | G               |       |  |

| F1    | 7.73           | 5.5                         | 0.994          | 0.615  | 0.988          | 0.609   | 0.982           | 0.600 |  |

| F2    | 4.476          | 2.47                        | 4.476          | 2.68   | 2.342          | 1.2     | 2.344           | 1.2   |  |

| F3    | 2.47           | 2.172                       | 2.172          | 1.84   | 2.168          | 1.842   | 2.219           | 1.888 |  |

Table 3.2 Fault current magnitudes for faults at different sections are listed below

Selection of relay current pick up values

## a) Relay pick up settings for R1

The maximum fault current seen by relays R1 is 7.73 kA for a 3 phase fault to ground fault at F1 and the minimum fault current seen is 2.172 kA for a single line to ground fault at F3.

CT ratio of 600:5 is assumed.

"Relay pick up current is taken to be approximately half of the minimum fault current and greater than 200% of the full load current."

$$2 * IFL \le I \le 0.5 * Ifmin \tag{3.1}$$

*IFL*= *Full load current seen by relay*

*Ifmin= minimum fault current seen by relay I= relay pick up current*

$$2 * \frac{5 * 20}{600} \le I \le \frac{0.5 * 2172 * 5}{600}$$

$$0.333 \le I \le 9.05$$

$$I = 3 \text{ A is selected}$$

# b) Relay pick up settings for R2 and R6

The maximum fault current seen by R2 and R6 is 4.476 kA for a three phase to ground fault at F2 and the minimum fault current seen is 615 A for a single line to ground fault at F1.

CT ratio of 200:5 is assumed.

$$\frac{5 * 2 * 20}{200} \le I \le \frac{0.5 * 5 * 615}{200}$$

$$1 \le I \le 7.68$$

$$I = 5$$

(3.2)

# c) Relay pick up settings for R3 and R5

The maximum fault current seen by relays R3 and R5 is 2.342 kA for a 3 phase fault to ground fault at F2 and the minimum fault current seen is 609 A for a single line to ground fault at F1.

CT ratio of 200:5 is assumed.

$$\frac{5*40*2}{200} \le I \le \frac{0.5*5*609}{200}$$

$$2 \le I \le 7.6125$$

$$I = 4$$

(3.3)

## d) *Relay pick up settings for R4*

The maximum fault current seen by relays R4 is 2.344 kA for a 3 phase fault to ground fault at F2 and the minimum fault current seen is 600 A for a single line to ground fault at F1.

CT ratio of 200:5 is assumed.

$$\frac{5 * 20 * 2}{200} \le I \le \frac{0.5 * 5 * 600}{200}$$

$$1 \le I \le 7.5$$

$$I = 7$$

(3.4)

The fault current magnitude near the relay RX would almost be equal to that of relay R4. Hence a CT ratio of 200:5 is selected with a current pick up of 7 A.

# Selection of time dial settings

In-order to determine time dial settings, maximum fault current seen by relays is taken for calculation to ensure quick operation of relays for all type of faults. Table 3.3 shows the maximum current seen by the relays during fault conditions.

| Relays in clockwise |                 |         |                 |         | Relays in anti-clockwise |         |                 |         |  |

|---------------------|-----------------|---------|-----------------|---------|--------------------------|---------|-----------------|---------|--|

|                     | Relay acting as |         | Relay acting as |         | Relay acting as          |         | Relay acting as |         |  |

|                     | primary         |         | back up         |         | primary                  |         | back up         |         |  |

| Fault               | Relay           | Current | Relay           | Current | Relay                    | Current | Relay           | Current |  |

|                     |                 | seen    |                 | seen    |                          | seen    |                 | seen    |  |

| F1                  | R6              | 994 A   | R5              | 998 A   | R1                       | 7.73 kA | RX              | 7.73    |  |

|                     |                 |         |                 |         |                          |         |                 | kA      |  |

| F2                  | R5              | 2.342   | R4              | 2344 A  | R2                       | 4.476   | R1              | 4.478   |  |

|                     |                 | kA      |                 |         |                          | kA      |                 | kA      |  |

| F3                  | R4              | 2219 A  | RX              | 2220 A  | R3                       | 2.168   | R2              | 2.170   |  |

|                     |                 |         |                 |         |                          | kA      |                 | kA      |  |

Table 3.3 Clockwise and anti- Clockwise relays

Time dial settings are determined from the co-ordination of relays. Coordination of relays is explained in the following section.

# Co-ordination of clockwise relays

## *i.* Fault F1

For a fault at F1, R6 acts as primary protection and R5 acts as a back-up. Extremely time inverse type over current relay is used. For the relay to act instantaneously time dial settings for R6 is chosen to be 0.5, the minimum value for extremely inverse curve.

$$TD6 = 0.5$$

$$tr6 = TD6 * (0.0352 + \frac{5.67}{M^2 - 1})$$

(3.5)

$$M = \frac{Ifault \ seen \ by \ R3}{I \ pick \ up} = \frac{Ifault \ * \left(\frac{1}{CT \ ratio}\right)}{relay \ Pick \ up \ current} \frac{982 \ * \ 5/_{200}}{5} = 4.97$$

$$tr6 = 0.5 \ * \left(0.0352 + \frac{5.67}{4.91^2 - 1}\right) = 0.13721 \ s$$

Assuming a co-ordination time interval of 0.3 s, relay 5 operates at tr5= 0.13721+0.3 = 0.4372 s. Current seen by R5 for fault at F1 is 988 A.

$$TD5 = \frac{tr5}{(0.0352 + \frac{5.67}{M^2 - 1})}$$

$$M = \frac{988 * 5}{200 * 4} = 6.175$$

$$TD5 = 2.326$$

(3.6)

# *ii.* Fault F2

For a fault at F2, R5 acts as primary relay and R4 acts as back up relay. Time to detect the fault current by relay R5 can be found by using the time dial setting of R5 calculated above step. Fault current seen by R5 is 2.342 kA.

$$M = \frac{2342 * 5}{200 * 4} = 14.637$$

$$tr5 = 2.326 * (0.0352 + \frac{5.67}{14.637^2 - 1})$$

$$tr5 = 0.1437 s$$

(3.7)

Relay R4 acts 0.3 s after the operation of R5. Time of operation of R4 is 0.1437+0.3=0.4437 s. Current seen by relay R4 for fault at F2 is 2.344 kA.

$$M = \frac{2344 * 5}{200 * 7} = 8.371$$

$$TD4 = \frac{tr4}{(0.0352 + \frac{5.67}{M^2 - 1})} = 3.78$$

(3.8)

Relay RX backs up R4 0.3 s after the operation of R4. tRX =0.4437+0.3= 0.7437 s. Current sensed by the relay RX is 2219 A.

$$M = \frac{2219 * 5}{200 * 7} = 7.925$$

$$TD_RX = \frac{tRX}{(0.0352 + \frac{5.67}{M^2 - 1})} = 5.85$$

(3.9)

## Co-ordination of anti-clockwise relays

## *i.* Fault F3

For a fault at F3, R3 acts as primary relay and R2 acts as back up relay. Fault current seen by R3 is 2.168 kA. For the relay to act instantaneously time dial settings for R3 is chosen to be 0.5, the minimum value for extremely inverse curve.

$$TD3 = 0.5$$

$$M = \frac{2168 * 5}{200 * 4} = 13.55$$

$$tr3 = TD3 * \left(0.0352 + \frac{5.67}{M^2 - 1}\right) = 0.0331 s$$

(3.10)

Relay R2 acts as back-up 0.3 seconds after the operation of R3. Time of operation of R2 is tr2=0.0331+0.3=0.3331 s.

Time dial setting of R2 can be found out using the tr2 calculated in the above equation. Fault current seen by R2 is 2170 A.

$$M = \frac{2170 * 5}{200 * 5} = 10.85$$

$$TD2 = \frac{tr2}{(0.0352 + \frac{5.67}{M^2 - 1})} = 3.9748$$

(3.11)

*ii.* Fault F2

For a fault at F2, R2 acts as primary relay and R1 acts as back up relay. Time to detect the fault current by relay R2 can be found by using the time dial setting of R2 calculated in the above step. Fault current seen by R2 is 4.476 kA.

$$M = \frac{4476 * 5}{200 * 5} = 22.38$$

$$tr2 = TD2 * \left(0.0352 + \frac{5.67}{M^2 - 1}\right) = 0.1849 s$$

(3.12)

Relay R1 acts as back up 0.3 seconds after the operation of R2. Time of operation of R1 is tr1=0.3+0.1849=0.4849 s. Time dial settings of relay R1 can be found by using tr1calculated in the above equation. Current seen by relay R1 is 4.478 kA.

$$M = \frac{4478 * 5}{600 * 3} = 12.43$$

$$TD1 = \frac{tr1}{(0.0352 + \frac{5.67}{M^2 - 1})} = 6.72$$

(3.13)

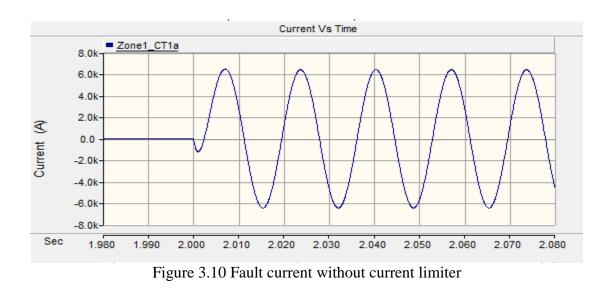

# 3.7 Effect of fault current limiter on the protection algorithm

Fault current limiters (FCL) reduce the magnitude of fault current by chopping off the peak value to a particular level. In-order to have this affect, fault current is passed through an inbuilt function in PSCAD called "Hard Limiter" and current could be chopped to any desired level. Fault current in zone1 is chopped to 3000 A. It gets chopped to this value only if fault current is above 3000 A. Similarly, currents in zone 2 and zone 3 are chopped to 700 A. Table 3.4 shows the chopped value of fault currents seen by relays.

| Fault | Current seen by  |      | Current seen by  |     | Current          | seen by | Current seen by     |     |

|-------|------------------|------|------------------|-----|------------------|---------|---------------------|-----|

|       | relays R1 at CB1 |      | relays R2, R6 at |     | relays R3, R5 at |         | relays R4 at CB4 in |     |