Total Dose Simulation for High Reliability Electronics

by

# Garrett Schlenvogt

## A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved April 2014 by the Graduate Supervisory Committee:

Hugh Barnaby, Chair Stephen Goodnick Dragica Vasileska Keith Holbert

## ARIZONA STATE UNIVERSITY

May 2014

## ABSTRACT

New technologies enable the exploration of space, high-fidelity defense systems, lighting fast intercontinental communication systems as well as medical technologies that extend and improve patient lives. The basis for these technologies is high reliability electronics devised to meet stringent design goals and to operate consistently for many years deployed in the field.

An on-going concern for engineers is the consequences of ionizing radiation exposure, specifically total dose effects. For many of the different applications, there is a likelihood of exposure to radiation, which can result in device degradation and potentially failure. While the total dose effects and the resulting degradation are a well-studied field and methodologies to help mitigate degradation have been developed, there is still a need for simulation techniques to help designers understand total dose effects within their design.

To that end, the work presented here details simulation techniques to analyze as well as predict the total dose response of a circuit. In this dissertation the total dose effects are broken into two sub-categories, intra-device and inter-device effects in CMOS technology. Intra-device effects degrade the performance of both n-channel and pchannel transistors, while inter-device effects result in loss of device isolation. In this work, multiple case studies are presented for which total dose degradation is of concern. Through the simulation techniques, the individual device and circuit responses are modeled post-irradiation. The use of these simulation techniques by circuit designers allow predictive simulation of total dose effects, allowing focused design changes to be implemented to increase radiation tolerance of high reliability electronics.

i

#### ACKNOWLEDGMENTS

First I would like to thank my graduate advisor, Dr. Hugh Barnaby. Throughout my time as a member of Hugh's research group, I have benefited from his experience and guidance, both personally and professionally. Hugh takes great care to understand his students' strengths and put them in a position to be successful. Conversely Hugh drives his students to examine their weaknesses, and helps them improve and become wellrounded engineers. I believe the skills and lessons Hugh has taught me will serve me well as I go forward, and for this I am deeply grateful. Also I'd like to thank all the members of Dr. Barnaby's research group throughout the years, who I've enjoyed working beside. I'd like to specifically thank Jeff Rollins, Ivan Esqueda and Tyler Stevenson for their direct contributions to work presented here.

Additionally I would like to thank the other members of my Ph.D. committee: Dr. Stephen Goodnick, Dr. Dragica Vasileska and Dr. Keith Holbert. During both my 9 years undergraduate and graduate coursework at ASU I had the pleasure to take courses with all of these professors, all of which make student success a top priority.

The work presented here would not be possible without the financial support of Medtronic, Inc. Moreover, I am very thankful to the contributions of Medtronic engineers Jeff Wilkinson, Larry Tyler and Scott Morrison. Through countless hours of meetings, working sessions, and lab hours they enabled both the success of this work as well as my personal success as a young engineer. For that I am very thankful.

Last but certainly not least I'd like to thank my friends and family, all of which contribute to my personal and professional growth and success. To my mother and father I thank you for always pushing me to be my best, affording me the opportunity to experience many great things growing up, and always there for me. Erica, you have been a great big sister, and I can truly say you are a best friend. Finally, to the love of my life Marisa, our journey has only just begun. While we may only be on our first stop along the way, I'm so very excited to see where life takes us next. To all I love you and thank you.

# TABLE OF CONTENTS

|                                                  | Page |

|--------------------------------------------------|------|

| LIST OF TABLES                                   | vi   |

| LIST OF FIGURES                                  | vii  |

| CHAPTER                                          |      |

| 1 INTRODUCTION                                   | 1    |

| High Reliability Electronics                     | 1    |

| Medical Devices                                  | 2    |

| Total Dose Hardening Approaches                  | 7    |

| Approach and Goals                               | 13   |

| 2 TOTAL DOSE EFFECTS                             | 17   |

| Brief History                                    | 17   |

| Effects of Total Dose Irradiation                | 18   |

| Device Response Considererations                 | 30   |

| 3 SIMULATION OF INTER-DEVICE EFFECTS             | 35   |

| Charge Pump Case Study – Background and Approach |      |

| Charge Pump Case Study – Results and Analyisis   | 42   |

| Analysis of Parasitic Field Oxide Transistors    | 55   |

| Conclusions                                      | 72   |

| 4 SIMULATION OF COMBINED INTRA-DEVICE EFFECTS    | 74   |

| Case Study – The Ring Oscillatior                | 75   |

| Experimental Setup                               | 77   |

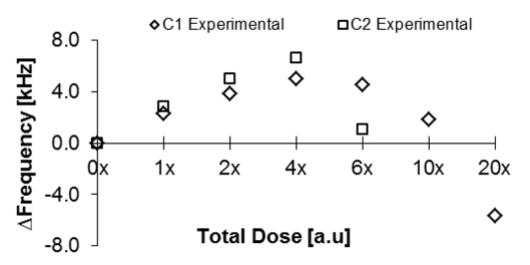

| Experimental Results – Ring Oscillator           | 79   |

| CHAPTER    |                                                     | Page |

|------------|-----------------------------------------------------|------|

|            | Experimental Results – Individual Test Transistors  | 80   |

|            | Analysis                                            |      |

|            | Simulation Details                                  | 85   |

|            | Simulation Results                                  |      |

|            | Discussion                                          | 95   |

| 5 PREDIC   | TIVE MODELING OF PARASITIC EDGE EFFECTS             |      |

|            | Approach                                            | 97   |

|            | TCAD Device Modeling                                |      |

|            | Analyitical Extraction of Parasitic NFET Parameters | 101  |

|            | Implementation into Simulation                      | 104  |

|            | Simulation Results                                  | 107  |

|            | Summary of Predictive Modeling                      | 109  |

| 6 CONCLU   | JSIONS                                              | 111  |

|            | Summary and Contributions                           |      |

|            | Recommendations for Future Work                     | 114  |

| REFERENCES |                                                     | 116  |

## LIST OF TABLES

| Table | Page                                                                                |

|-------|-------------------------------------------------------------------------------------|

| 2.1   | Minimum electron-hole pair creation energy, density and pair density generated      |

|       | per rad for a given material [18, 38]                                               |

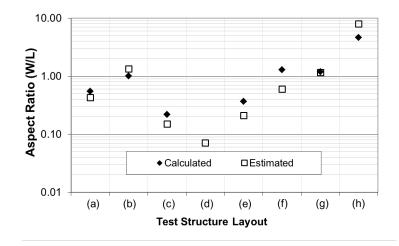

| 3.1   | Effective FOXFET Aspect Ratios                                                      |

| 4.1   | Summary of circuit and transistor irradiation bias conditions utilized. Best- and   |

|       | worst-case correspond to the least and most potential bias-dependent total-dose     |

|       | degradation, respectively                                                           |

| 5.1   | Incremental oxide thickness $(T_{OXi})$ and doping $(N_{Ai})$ for each of the seven |

|       | parasitic edged transistors. Values extracted from Fig. 5.4 results 105             |

| 5.2   | Incremental threshold voltage $(V_{Ti})$ for each of the seven parasitic edged      |

|       | transistors at each total dose stress step modeled in TCAD. Values extracted        |

|       | from Fig. 5.6 results                                                               |

# LIST OF FIGURES

| Figure | Page                                                                                         |

|--------|----------------------------------------------------------------------------------------------|

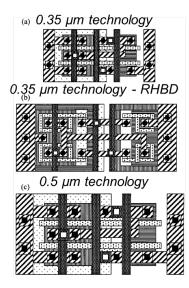

| 1.1    | Example of a 2 input NAND cell. Examples of an unhardened (a) and a                          |

|        | Radiation Hardening by Design (b) cell in a 0.35 $\mu$ m technology. For reference           |

|        | an unhardened (c) cell in 0.5 µm technology is shown [21] 12                                 |

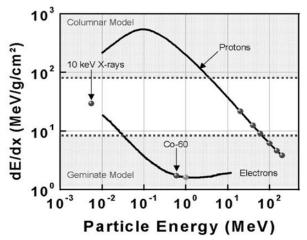

| 2.1    | LET in $SiO_2$ vs. particle energy for electrons, protons, and secondary electrons           |

|        | generated by 10 keV x-rays and 1.25 MeV $^{60}$ Co $\gamma$ -rays [36]19                     |

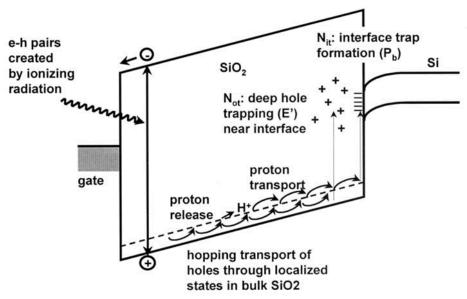

| 2.2    | Energy band diagram of MOS capacitor which illustrates the main processes for                |

|        | radiation induced charge generation [18][34]                                                 |

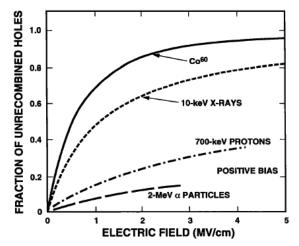

| 2.3    | Fraction of uncombined holes vs. electric field for various incident particles [18,          |

|        | 20, 39]                                                                                      |

| 2.4    | Band Diagram of SiO <sub>2</sub> illustrating possible oxygen vacancies [38]                 |

| 2.5    | Model of $P_{b0}$ and $P_{b1}$ interface trap centers on (111), (110) and (100) silicon [38, |

|        | 54]                                                                                          |

| 2.6    | Illustration of the shift in the drain current vs. gate voltage characteristics of n-        |

|        | and p-channel MOSFETs as a result of positive oxide-trapped charge [38] 30                   |

| 2.7    | Illustration of the shift in the drain current vs. gate voltage characteristics of n-        |

|        | and p-channel MOSFETs as a result of interface traps [38]                                    |

| 2.8    | Possible intra- and inter-device leakage current path resulting from oxide trapped           |

|        | charge buildup in LOCOS or STI isolation oxides [38]                                         |

| 2.9    | Cross section of a) LOCOS isolated and b) STI isolated transistor showing                    |

|        | trapped-charge location corresponding with intra-device edge leakage current                 |

|        | [18, 57]                                                                                     |

|        | vii                                                                                          |

| 2.10 Current-voltage characteristics of gate-oxide and a parasitic "edge" transistor           |

|------------------------------------------------------------------------------------------------|

| showing increase in current post-irradiation due to the parasitic edge transistor              |

| [18]                                                                                           |

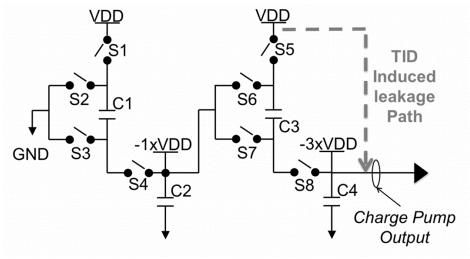

| 3.1 Simplified block diagram of integrated circuit implementation of Negative                  |

| Supply Pumps                                                                                   |

| 3.2 Dual charge pump configuration implemented to generate $-1 \times VDD$ and $-3 \times VDD$ |

| from the externally available VDD and GND voltages                                             |

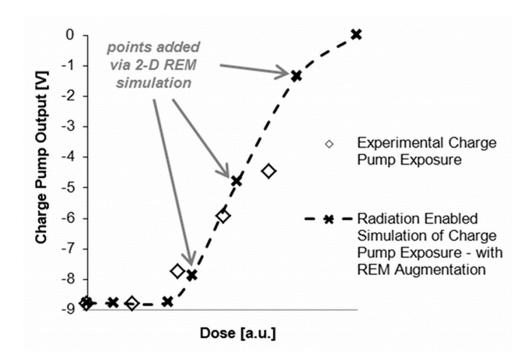

| 3.3 Experimental results showing voltage collapse of the -3×VDD charge pump                    |

| output versus applied total dose. Total dose increases from left to right                      |

| 3.4 Flowchart detailing steps to generate the -3×VDD collapse vs. dose via radiation           |

| enabled simulation41                                                                           |

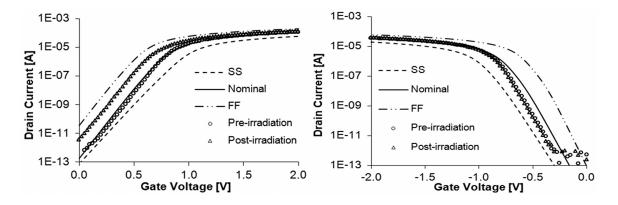

| 3.5 Current-voltage characteristics for the 50 $\mu$ m /3 $\mu$ m NFET (left) and PFET         |

| (right) transistors. Additionally, model corners (SS, FF and nominal) are                      |

| provided for comparison                                                                        |

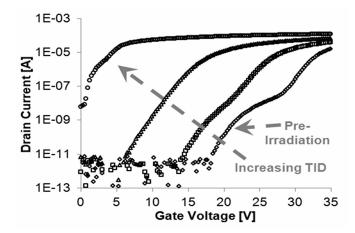

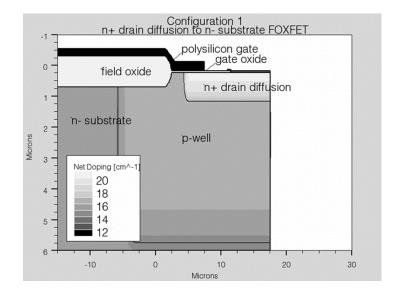

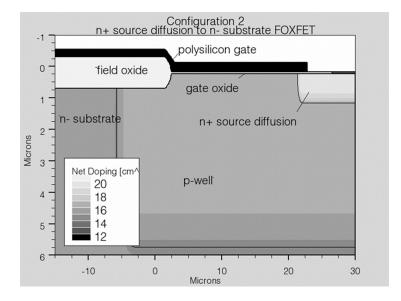

| 3.6 Typical radiation response for the specialized n-channel field oxide FETs                  |

| (FOXFETs) (W=50 μm, L=3 μm)                                                                    |

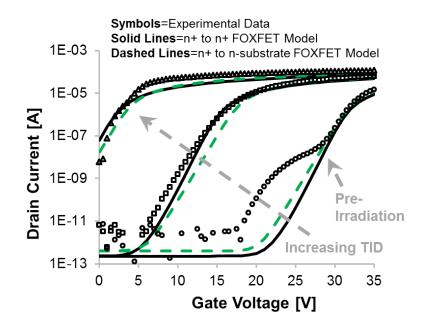

| 3.7 Comparison of Silvaco ATLAS simulation (solid lines) to experimental data                  |

| (symbols) for the n-channel FOXFET structure                                                   |

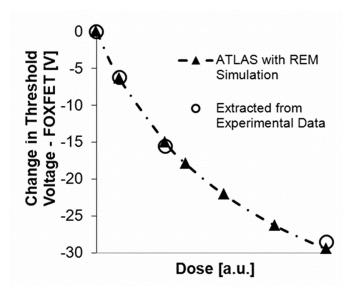

| 3.8 Change in threshold voltage of the FOXFET versus applied total dose showing                |

| good agreement experimental irradiation and ATLAS simulation data                              |

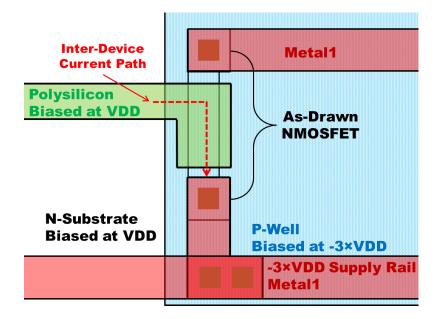

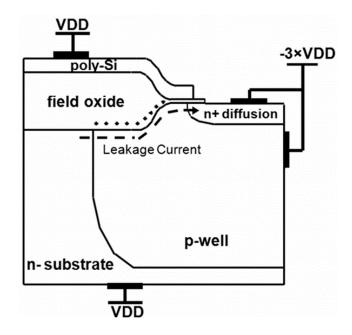

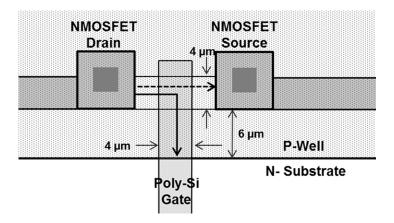

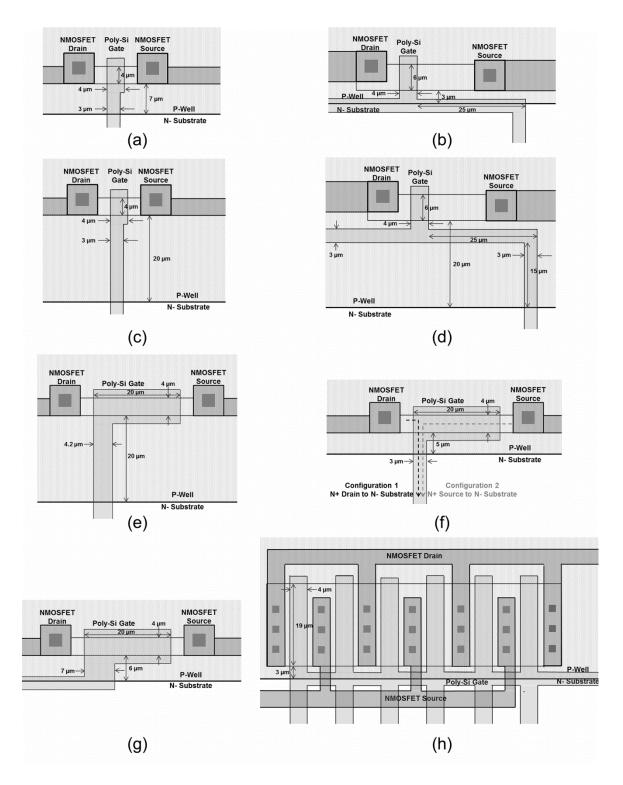

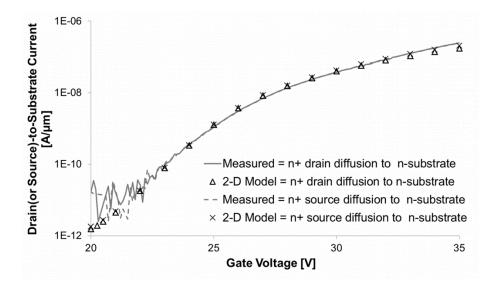

| 3.9 Layout example of the parasitic FET structure with inter-device current path               |

| from the n-substrate to the n+ diffusion                                                       |

| 3.10 Cross-section of the parasitic FOXFET structure occurring in the charge pump          |

|--------------------------------------------------------------------------------------------|

| layout. Also indicated is the typical bias configuration for each region                   |

| 3.11 Simplified charge pump schematic illustrating the radiation induced leakage           |

| path associated with the activation of parasitic FOXFET devices                            |

| 3.12 Radiation-enabled circuit simulation of the charge pump output voltage (-             |

| 3×VDD) compared against experimental test data                                             |

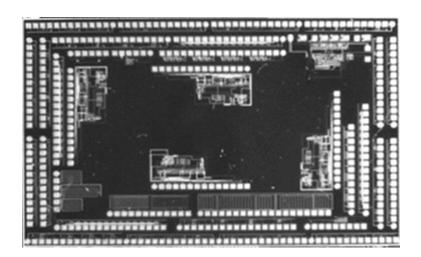

| 3.13 Integrated test coupon developed specifically for radiation effects investigations    |

| containing various sub-circuits and test structures, including an array of                 |

| FOXFETs                                                                                    |

| 3.14 Layout of 4 $\mu$ m/4 $\mu$ m NMOSFET. Arrows indicate designed MOSFET drain-         |

| to-source (dashed) and parasitic FOXFET drain-to-substrate (solid) current                 |

| paths                                                                                      |

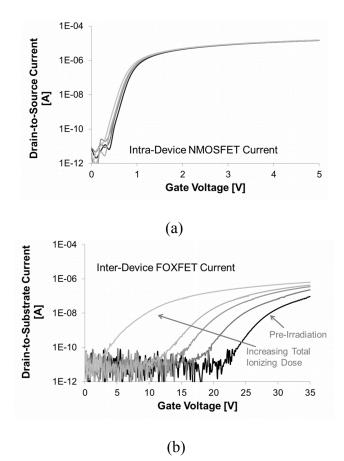

| 3.15 Pre-and post-irradiation current-voltage response of the Fig. 3.14 test structure.    |

| Drain-to-source current vs. gate voltage response (a) shows minimal change                 |

| post-irradiation. Drain-to-substrate current vs. gate voltage response (b) shows           |

| significant increase in inter-device current with increasing TID                           |

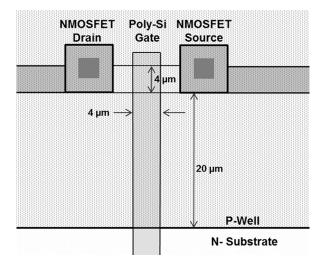

| 3.16 Layout of 4 $\mu$ m/4 $\mu$ m NMOSFET similar to Fig. 3.14 with the distance from as- |

| drawn transistor to n- substrate boundary increased                                        |

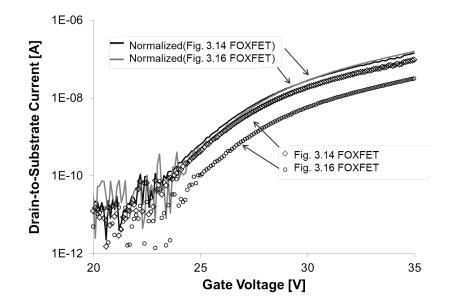

| 3.17 Current-voltage response of the FOXFETs found in Fig. 3.14 and Fig. 3.16              |

| (symbols). Normalization of the each of the FOXFET currents (solid lines)                  |

| illustrates good agreement                                                                 |

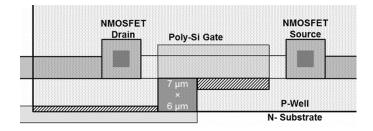

- 3.19 Test structure layout previously shown in Fig. 3.18(g) with added marking to denote our estimated effective aspect ratio of 7  $\mu$ m/6  $\mu$ m. The polysilicon regions shown with striped shading are discounted in the aspect ratio estimate. 65

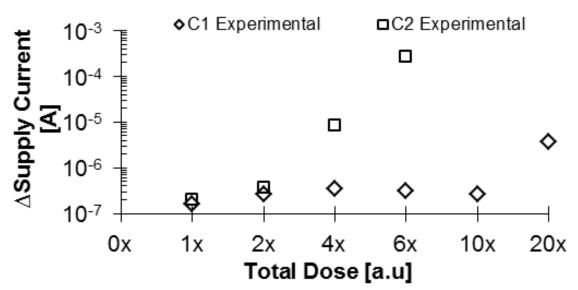

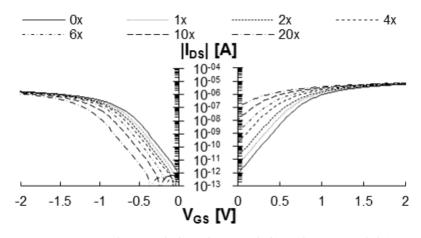

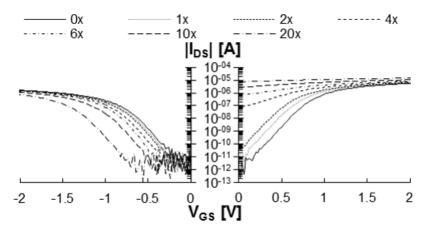

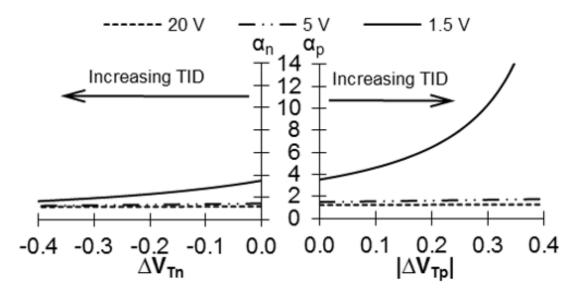

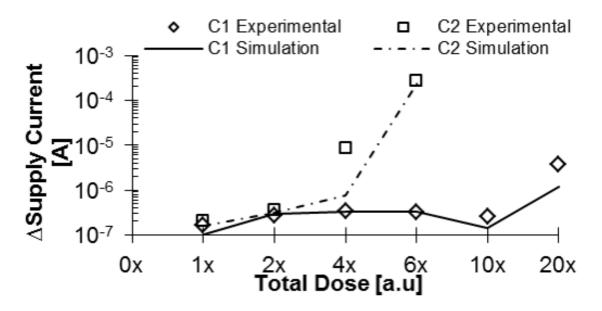

- 4.3 Experimentally observed RO supply current vs. total dose. Shown are results for irradiation bias configurations C1 and C2. Pre-irradiation average supply current is ~4 μA, at a supply voltage of 1.5 V.

80

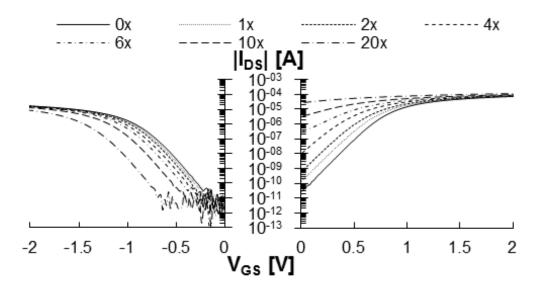

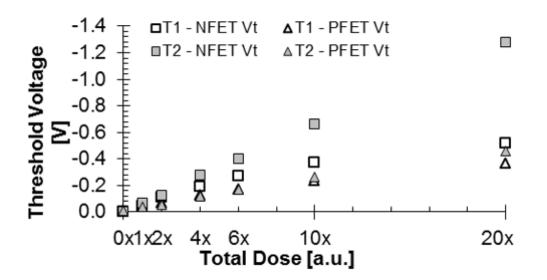

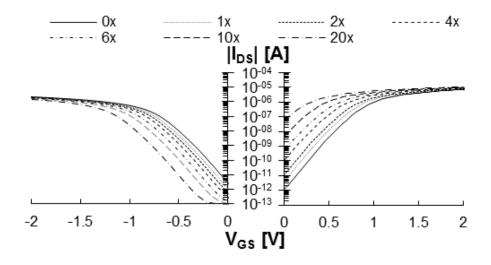

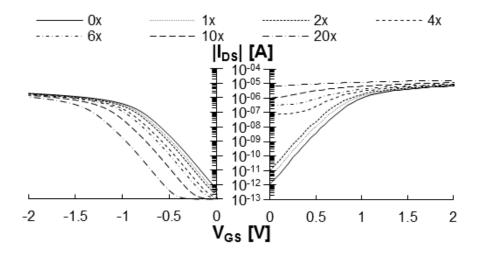

- 4.8 Extracted NFET and PFET threshold voltages versus increasing total dose. Results shown are extracted from a W/L=2.5  $\mu$ m /1.4  $\mu$ m PFET experimental data for both bias conditions (T1 and T2). Alternatively W/L=2.5  $\mu$ m /1.4  $\mu$ m

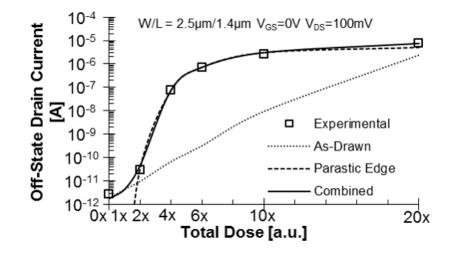

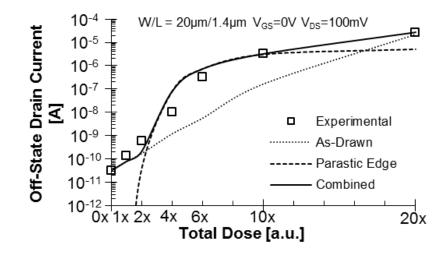

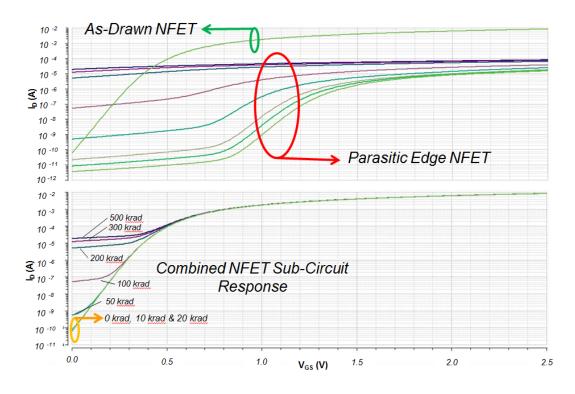

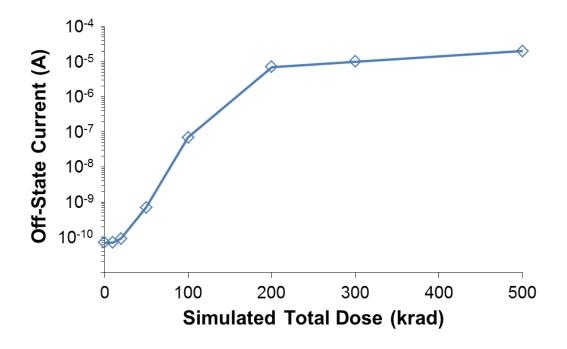

- 4.9 Off-state drain current (i.e.  $I_D @ V_{GS}=0$ ,  $V_{DS}=100mV$ ) vs. total dose for a W/L = 2.5  $\mu$ m / 1.4  $\mu$ m NFET. Squares indicate experimental data while lines indicate analytical calculations. 90

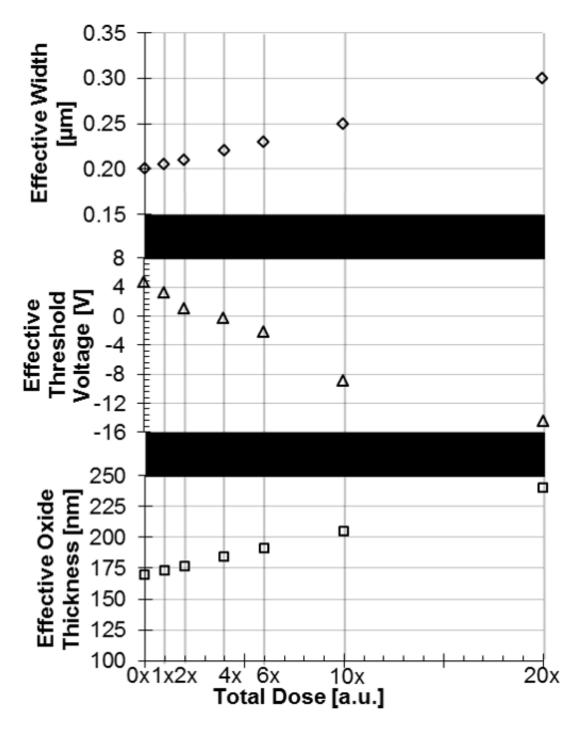

- 4.11 Effective width (top), threshold voltage (middle) and oxide thickness (bottom) found for the parasitic edge transistor resulting from the fitting methodology illustrated in Fig. 4.9 and Fig. 4.10.

- 4.15 Experimentally observed supply current vs. total dose. Shown are results representative of irradiation bias configurations C1 and C2 as defined in the text. Pre-irradiation average supply current is  $\sim 4\mu A$  at a supply voltage V<sub>DD</sub>=1.5V. 94

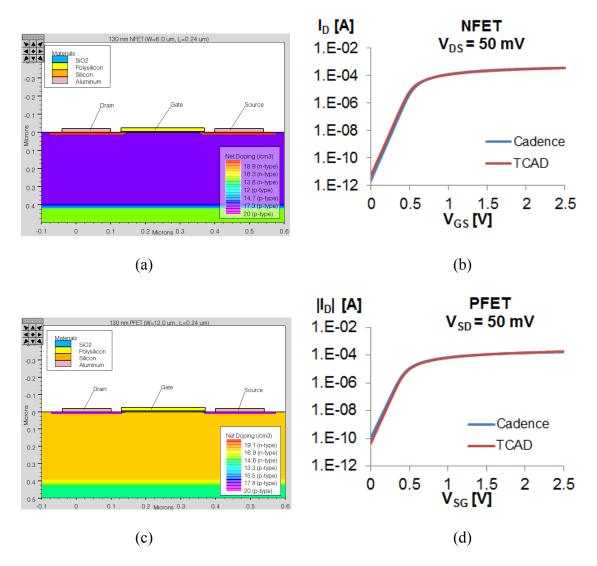

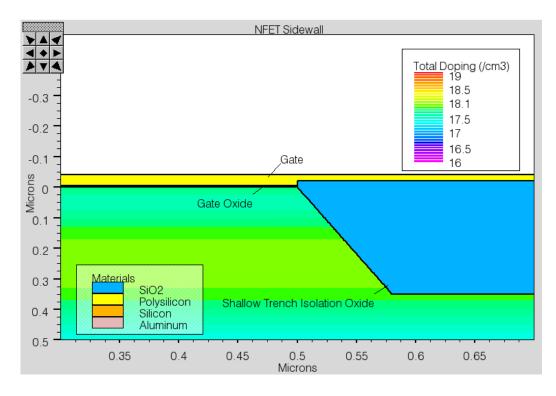

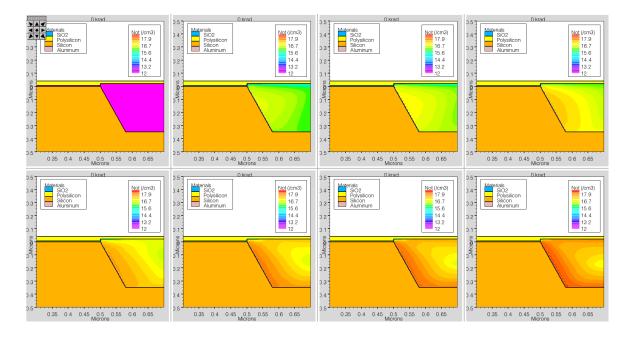

- 5.1 2-D TCAD structures of the 130 nm (a) NFET and (c) PFET. TCAD modeled current-voltage characteristics of both (b) NFET and (d) PFET compare well against Cadence AMS simulation with the foundry-supplied compact models.. 99

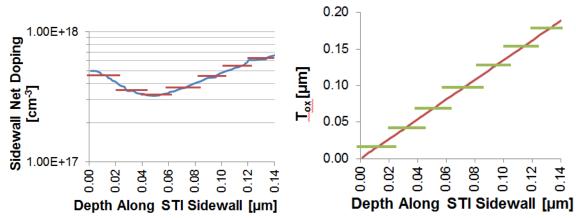

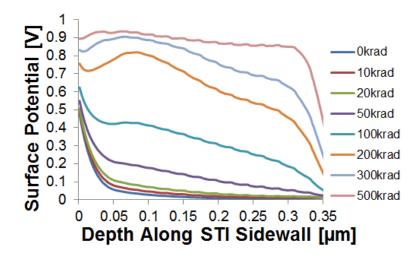

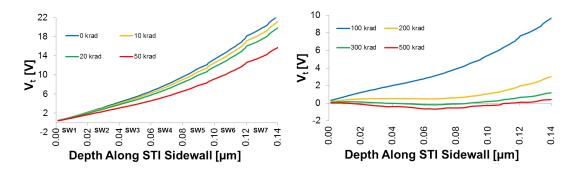

- 5.4 Extracted Sidewall Doping vs. sidewall depth (left) and calculated effective oxide thickness vs. sidewall depth (right). Overlaid horizontal lines indicate the average value over a 20 nm depth increment. 102

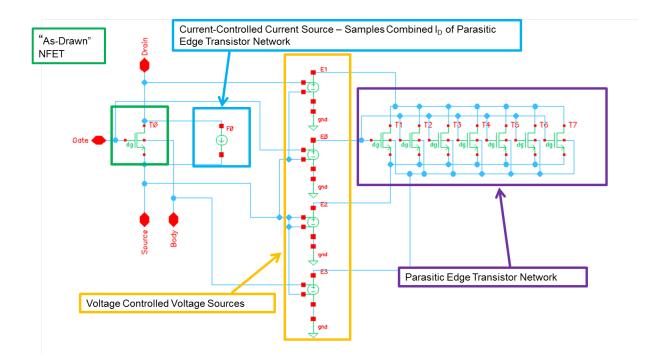

| 5.7 | NFET    | sub | circuit | used | as a | a drop-in | replacement | for | regular | NFET's | in | a given |

|-----|---------|-----|---------|------|------|-----------|-------------|-----|---------|--------|----|---------|

|     | design. |     |         |      |      |           |             |     |         |        |    | 107     |

### CHAPTER 1

## **INTRODUCTION**

### **High Reliability Electronics**

High reliability electronics are at the heart of some of the greatest technological advancements today. From deep space exploration, telecommunications, aerospace and defense as well as implantable medical devices, highly reliable electronics allow assurance that critical systems will operate as designed for the duration of their intended lifetime. Scientists, medical doctors and engineers will continue to employ electronics to advance society, exploring our universe, enabling lighting fast communications as well as extending and improving quality of life. As new technologies come to fruition, it is imperative that they are as reliable as possible.

It is important to understand the commonalities among high reliability electronics. First, high reliability electronics are mission-critical and cannot easily be replaced in the field. One can see the difficulty of replacing a failed integrated circuit on a satellite in space or a medical device implanted in a patient. High reliability electronics are also expected to operate within design specifications over multiple years. Another characteristic of high reliability electronics is that they are often manufactured at low volumes. Due to the nature of their applications, specifically space, defense and medical, high reliability electronics are not fabricated in the same volume as the majority of commercial electronics. Finally high reliability electronics can also have longer design cycles compared to commercial electronics, sometimes lasting tens of years.

While many applications can fall under the categorization of high reliability electronics, we focus here on medical devices. This emphasis is chosen since radiation effects within medical device electronics is a growing concern; and, moreover, the

majority of the work presented here was performed specifically for medical device applications. However, the techniques developed and presented are believed to be widely valid, appropriate for implementation as part of a design-for-reliability program in other applications and environments.

## **Medical Devices**

In the last 60 years, the world has seen development of implantable medical devices that serve to improve patient quality of life. This has led to the development of a multi-billion dollar industry. Through collaboration between medical professionals and engineers, implantable device technology has evolved into complex systems capable of such activities as patient monitoring, drug delivery, neurological stimulation and support of heart function through artificial pacing and defibrillation [1]. These devices currently serve to treat a wide array of diseases, and continued breakthroughs in the medical and engineering fields will expand their usage going forward [2-4].

All electronics designed for medical devices are constructed with a primary goal of increased battery life through ultra-low power consumption while maintaining a high standard of reliability. In fact, reliability and device lifetime are the primary product differentiation factors [4]. Today, the U.S. Food and Drug Administration (FDA) regulate medical devices to ensure quality and protect patients. Field failures of implanted devices are unacceptable, as a fault could require device replacement involving surgery or, in extreme cases, put the patient's life in danger. Great care is taken in the front-end design and qualification process to ensure a reliable product.

Since the medical device market is rather low volume in comparison to the commercial electronics industry, medical device companies have employed a "fast follower" approach by leveraging new integrated circuit (IC) processes only after they have been developed by higher volume industries such as consumer electronics. This approach allows for medical device companies to have a better understanding of product reliability and reduce development times.

IC designs are primarily fabricated in silicon based CMOS processes due to the low standby power consumption and high device reliability. The continued tracking of CMOS technology with Moore's Law has allowed designs to increase the complexity of systems without swelling power consumption or device size. Additionally the integration of multiple functional blocks into a single system-on-a-chip (SOC) serves to limit current draw in comparison to older designs, which relied on inter-chip communication in the system requiring more power. As device feature size shrinks at each successive technology node, overall maximum supply voltage shrinks as well. However, with decreased supply voltage, the device threshold voltage is also lowered. This is undesirable as reduction in threshold voltage leads to increased off-state leakage. So, selection of the CMOS process must balance the benefits of shrinking feature size with the requirements of ultra-low power consumption.

Another undesired aspect for the medical device industry related to shrinking geometries is the reduction in standard gate oxide thickness. Most if not all pacemaker designs require the use of large output voltage (5-20V) for pacing, for which the newest technology nodes' ultra-thin gate oxides cannot reliably support. To solve this issue many companies employ technologies that provide devices of different gate oxide thicknesses

within the standard process. This allows circuit designers the option to use transistors with thicker oxides for use in high voltage output sub-circuits while still having the opportunity to employ thin gate oxide transistors in lower voltage digital sub-circuits. The requirement of thicker oxides and high circuit voltages is deleterious when considering susceptibility to ionizing radiation, as will be shown and discussed in Chapter 2.

A typical pacemaker device uses a non-rechargeable battery as the system's sole power source. Battery supply voltage is usually targeted near 3 V with design considerations made to accommodate an end-of-life battery voltage reduced as low as 1.7 V. To maximize battery life, all systems operate at currents as low as 10 μA and a leakage for off-state transistors targeted to be less than 1 pA per micrometer of gate width. This is a difficult task as system designs often include a microcontroller IC, onchip read only memory (ROM) with static random access memory (SRAM), a mixedsignal IC for biological sensing and generating output signals, a protection IC to shield against interference, a large SRAM for storage of diagnostic data and possibly very-high voltage electronics for generation of defibrillation signals [5].

The main figure of merit for implantable medical devices, specifically pacemakers, is the device's expected lifetime and reliability. Many of the reliability concerns of implantable device designers are not exclusive to the medical device field. These include the deleterious device effects of gate-induced drain leakage (GIDL), stressinduced leakage current (SILC), negative-bias temperature instability (NBTI) as well as other material and packaging related reliability concerns [4-7]. However, many of these concerns are well monitored and are of utmost consideration during the front-end design

process. Additionally, all devices undergo stringent qualification and "burn-in" testing to check for defects before reaching doctors and surgeons for use in patients.

However one area of medical device reliability that has not been significantly explored by medical device engineers is the effect of radiation on implanted devices. Exposure of implanted devices to ionizing radiation is possible during diagnostic x-rays or through the use of radiation therapy for cancer treatment. Traditionally, the effects of ionizing radiation in semiconductor devices and integrated circuits were a concern for engineers designing for space and nuclear applications only. However, as implantable devices continue to grow in usage, there is a need to address radiation effects in these devices in more depth.

Currently, some pacemaker device manufacturers list relatively low thresholds (1-5 Gy) for acceptable device exposure levels, with some manufacturers stating that no level of exposure is acceptable [8]. Therapeutic dose for tumor treatment can range from 10 to 70 Gy, although it is assumed that the pacemaker device will see only a fraction of the total dose, thus should maintain full functionality [9]. It is considered "best practice" to avoid directly exposing the device to radiation during cancer therapy, with many recommendations going as far to say that patients with implantable medical devices need to have their pacemakers relocated, or that the plan of cancer therapy should be reevaluated to avoid radiation exposure [10-12]. Numerous clinical studies which test commercial pacemaker devices for their radiation tolerance report mixed results [8, 13-15].

Generally it is concluded that the use of radiation therapy for patients with implantable devices is safe, but only if extreme caution is taken. Additionally,

recommendations are made to a) consider other treatment options, b) surgically relocating the device, c) attempt to exclude the pacemaker from the radiotherapy portal and d) attempt to calculate dose to the pacemaker. It is also recommended that device manufacturers make radiation data for their devices more readily available.

The drawback of most clinical studies of radiation effects on implantable medical devices is that they all approach the problem from a medical perspective. The studies focus on a "pass/fail" methodology for device performance post-irradiation, only monitoring external electrical signals as would be seen by the heart. As such, they do not explore radiation effects on internal circuitry to analyze the true effect of ionizing radiation and consider if latent reliability issues exist, or if the expected device lifetime has been significantly reduced. If design specifications such as current draw are affected and exceed specification after exposure, battery life would be reduced and surgical replacement of the pacemaker could potentially be needed years earlier than originally predicted.

As the medical technology, surgical techniques and device designs advance the likelihood that implanted devices will see increased exposure levels during therapy could increase. This necessitates preemptive steps be taken to improve device radiation tolerance. The primary reason ionizing radiation effects warrant serious consideration in implantable electronics is the nature of device technologies and designs, specifically:

• Medical devices must utilize technologies with thicker dielectrics and lower doping levels. It is well known that these properties make high voltage MOS technologies more susceptible to ionizing radiation [16].

- Higher voltage requirements of pacemaker sub-blocks such as voltage multiplication circuitry and high voltage output generators result in larger electric fields throughout the circuit, particularly in the device oxides, which will enhance radiation-induced defect buildup [17, 18].

- Ionizing radiation is known to cause increases in off-state currents, reduce threshold voltage in n-channel devices and cause parasitic inter-device leakage [16], all of which are damaging to the low-power consumption design goals.

- Tolerance of field failures of implantable devices is unacceptable and the consequences are severe. Radiation induced failures, or even battery life degradation, could result in surgical replacement of devices and put patient health in jeopardy.

The mechanisms of ionizing radiation effects in CMOS integrated circuits are explored in detail in Chapter 2, while the remainder of this work describes methodologies to analyze ionizing radiation effects at the device and circuit levels, with the end result being circuit simulation techniques that capture radiation response characteristics. The capability for predictive radiation effects simulation allows designers to examine sensitive circuitry, and enables design changes to be made early in the product development process that would serve to increase radiation tolerance.

## **Total Dose Hardening Approaches**

Chapter 2 will provide details on total dose effects in CMOS technologies, and later chapters will illustrate the impact of total dose on devices and circuits. However, it

is important to briefly highlight the effects here before reviewing radiation-hardening approaches. Total dose effects in CMOS devices can be placed in two categories: intradevice and inter-device effects. Intra-device effects consist of total-dose induced degradation of both the gate oxide as well as the isolation oxide sidewalls. These mechanisms are classified intra-device as both affect the drain-to-source current-voltage characteristics within a field effect transistor (FET). Specifically, gate oxides are degraded by buildup of both positive oxide trapped charge as well as interface traps. Oxide trapped charge is also a significant issue in isolation oxide sidewalls of n-channel field effect transistors (NFETs), resulting in parasitic off-state drain-to-source current from conduction along the isolation oxide sidewall. Buildup of oxide-trapped charge is also the root cause of inter-device effects, as charge buildup along the base of isolation oxides results in the undesired loss electrical isolation.

To mitigate the total dose effects, many methods and approaches have been developed to increase radiation hardness. However this does not mean that a given hardening technique is always appropriate for all applications. Engineers must consider the dose level expected, the likelihood of exposure, as well as the place total dose reliability concerns in context with other design and reliability goals. This section outlines current methods that can be used to increase radiation hardness.

### Hardening by Process

Radiation hardened foundries, have been developed specifically to produce radiation-resilient circuits via specially tuned manufacturing processes. For applications in which a high total dose can be anticipated (i.e. deep space missions and defense

applications), utilization of radiation-hardened processes are common. However, these processes are not generally accessible for commercial purposes, and often restricted only to government and military design groups. Additionally, utilization of trusted foundries can be highly cost prohibitive due to the low-volume nature of their business.

Commercial processes, however, offer inherent radiation hardening through device scaling. The semiconductor industry's continued respect for Moore's law has led it to continually scale devices at each successive technology node. This scaling has reduced oxide thickness so much that positive charge trapping within ultra-thin gate oxides is now uncommon, as will be detailed in Chapter 2. This benefit is widely exploited for hardening purposes, as transferring designs into a scaled technology node not only improves general circuit performance but also improves total dose hardness [16, 19] [19]. Additionally, as device geometry has scaled, supply voltages in new technology nodes have also been scaled, as ultra-thin oxides cannot support voltages above their dielectric breakdown limit. Scaling of supply voltages is advantageous from a power perspective; so many applications gladly exploit all benefits related to porting circuit designs to smaller technology nodes.

However, hardening by process options are often impractical for manufacturers of integrated circuit applications in which total dose hardening is not the most critical reliability concern, for example implantable medical devices. Due to the low-volume nature of "rad-hard" foundries, they are often highly cost prohibitive for all except cases where extreme radiation tolerances are required. Since medical device radiation exposure levels are expected to be low, rad-hard processing is not a prudent option. As described previously, current commercial state-of-art technologies have been shown to be more

radiation tolerant than older processes. However, medical device designs still require high device reliability and ultra-low power consumption. Additionally, high voltage design requirements preclude the use of the most advanced technologies, as ultra-thin oxides cannot support these supply voltages. Due to these stringent requirements, medical device manufacturers adopt a "fast follower" approach to new technologies, and will not adopt a new process unless thoroughly vetted [4, 5, 7].

### Hardening by Design

Radiation hardening can also be accomplished in circuit design, utilizing layout and operation specifications to mitigate total dose radiation effects. Compared to radiation hardening by process, radiation hardening by design (RHBD) can be considerably less expensive and can be implemented on a per-design basis. Many of these strategies are realized through adherence to process design kit design rules, implemented throughout the entire design.

As mentioned previously, intra-device effects consist of degradation of either (or both) the gate oxide or the isolation oxide sidewall. Mitigation of gate oxide degradation is best handled via process hardening as described previously. However, designers can also limit the damage to gate oxides by limiting electric fields within the oxides during exposure, as the field dependency degradation is a well-known effect [18, 20]. This is accomplished by minimizing transistor-gate-to-body bias. However, one can see the limitation of this strategy, as modifying circuit operation (i.e. completely powering off the circuit) at the instance of exposure in the field is impractical or impossible. Completely powering off a potentially application-critical system is obviously

undesirable. In theory, a designer could design low-bias "safe mode" for critical subcircuits, to be triggered during exposure to limit damage. To this end, predictive simulation of total dose degradation like that presented in this dissertation would empower designers to anticipate damage and design in safe modes.

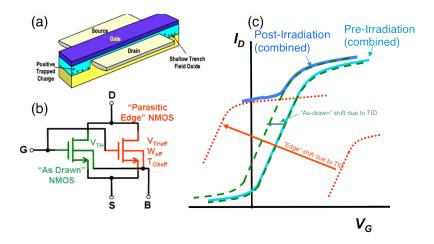

The other intra-device effect to be mitigated is parasitic off-state drain-to-source leakage due to oxide-trapped charge in NFET isolation oxide sidewalls. As this is a predominant total-dose effect, much work has been performed to mitigate this effect by way of specialized NFET device layout. The parasitic current post-irradiation is due to the proximity of the isolation oxide sidewall to the NFET channel. Buildup of oxide trapped charge in the sidewall results in parasitic current in parallel to the as-drawn NFET channel. So-called "enclosed gate" layouts have been demonstrated to be significantly more resilient to total dose effects, as isolation oxides are moved away from the NFET channel, mitigating the intra device parasitic current. However this strategy comes with area and performance penalties, as enclosed gate NFET layouts are significantly larger than a standard layout. The increase in layout area then, in turn, degrades transistor performance through increased gate capacitance; reducing device switching speed. However the effectiveness of enclosed gate layout designs for total dose hardening is undeniable.

Inter-device effects between n-type regions on-chip can also be effectively mitigated via layout modifications. The addition of "channel stops" to field regions surrounding a transistor will prevent leakage between devices. The channel stop is implemented via a highly doped p-type diffusion, which raises the local threshold voltage significantly. Even with significant oxide trapped charge buildup in the isolation oxide

base, the local threshold voltage in the region remains high, eliminating currents between inter-device n-type regions. Mitigation via channel stops also comes at a cost, as cell area is increased when this additional layout element surrounding the transistors is included [19, 21, 22].

In one published study, hardening by design is implemented on a two-input NAND cell, utilizing edgeless transistors and p+ guard rings to mitigate intra- and interdevice total dose effects, as seen in Fig. 1.1 [21]. In this study, it was shown that the implementation of RHBD strategies in a 0.35  $\mu$ m technology dramatically increased the cell size. It was found that the total cell area of the RHBD NAND cell has increased by 73%, and was comparable in size to a NAND from a 0.5  $\mu$ m technology. Additionally, it was found that the power dissipation (in  $\mu$ W/MHz) had increased 120% for the RHBD NAND compared to the unhardened 0.35  $\mu$ m NAND cell. While effective in mitigating TID effects, the penalties are evident.

Fig. 1.1 Example of a 2 input NAND cell. Examples of an unhardened (a) and a Radiation Hardening by Design (b) cell in a 0.35  $\mu$ m technology. For reference an unhardened (c) cell in 0.5  $\mu$ m technology is shown [21].

It is apparent widespread implementation of hardening by design techniques will impact the size and performance of any circuit. In cases for which a large total dose in the application is expected and unavoidable, hardening by design is an absolute necessity. However, in cases for which total dose levels may be lower and exposure is not guaranteed, such as in implanted medical devices, designers may choose not to sacrifice for radiation hardening. Because of these reasons, medical device manufacturers are advised to implement radiation hardening by design in a strategic and measured fashion. By making the most minimally invasive design and layout changes, while working within current circuit design goals and constraints, a targeted level of radiation tolerance can be achieved. In this work, modeling techniques are presented to both replicate and predict total dose response of circuits in simulation. Designers then can use these simulations early in the development cycle and implement measured RHBD design changes to improve total dose hardness while maintaining other design goals.

## **Approach and Goals**

The dissertation is divided into six chapters, focusing on total dose effects and their impact on circuits. The early chapters serve as introduction and motivation for the work, establishing the need for simulation of total dose effects as part of a design-forreliability approach. The remaining chapters focus on describing and validating simulation techniques to successfully capture the various effects of total dose degradation within the normal circuit simulation design flow. Case studies presented to provide realworld examples of both the degradation that can occur, as well as provide perspective to the simulation methodologies.

Chapter 2 discusses the effects of ionizing radiation, and its damaging effect on CMOS circuits. A brief history is presented, covering the establishment of the radiation effects field. Then the physics of total dose damage are described, explaining how ionizing radiation degrades silicon dioxide. The effect is then correlated to its effect on the electrical operation of CMOS devices and circuits. Understanding the basic physical mechanisms of total dose degradation establishes a basis for the simulation techniques presented in the following chapters.

Chapter 3 focuses on simulating the effects of inter-device effects related to totaldose irradiation. A case study, completed as part of my Master's Thesis, is reviewed, setting the stage for follow-up work completed to further analyze inter-device effects [23]. In a presented case study, an analysis of a dual charge pump circuit, radiationinduced charge buildup in the base of LOCOS isolation oxide results in inter-device current flow between NFETs and the n-type substrate. This loss of isolation leads to collapse of the charge pump output voltage, which serves as a primary supply rail for the rest of the circuit. Through a combination of experimental, modeling and simulation techniques the observed voltage collapse of the charge pump circuit is reproduced. Follow up work is then presented, in which specialized total-dose test structures were created to analyze the parasitic transistors in depth. This study serves as a guide for the modeling and simulation of inter-device total dose effects in other applications.

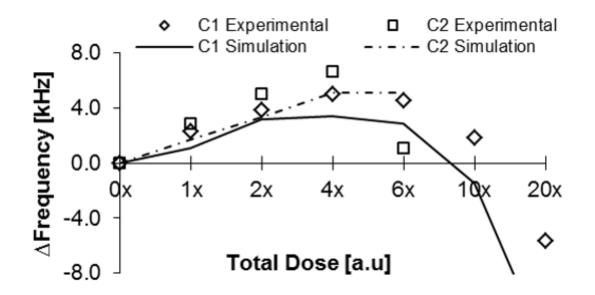

In Chapter 4 a ring oscillator case study is presented, showcasing another primary outcome of total dose degradation in CMOS technologies; intra-device effects such as threshold voltage shifts and increased off-state leakage. In the case study of interest the combined effect of both NFET and p-channel field effect transistor (PFET) threshold

voltage shifts, along with parasitic inter-device edge leakage in the NFET lead to changes in oscillation frequency and supply current draw in the ring oscillator. The novel analysis methodology presented successfully investigates the observed response, replicating it via simulation. Not only does this give greater insight into the operation of the ring oscillator, the techniques and findings are useful in the analysis of oscillators in other applications. Additionally the use of a ring oscillator as a health monitor circuit is proposed.

Chapter 5 is a special circumstance of design-for-reliability analysis, for which no irradiation characterization data is available. Instead, a combination of TCAD modeling, analytical extraction and compact modeling techniques allow for predictive modeling of potential post-irradiation inter-device edge leakage. Predictive datasets generated from the technique provide inexpensive and rapid access to potential reliability pitfalls in a given circuit design. This allows designers to make hardening changes on-the-fly improving radiation hardness early in the design cycle.

The final chapter recaps the dissertation, discusses my contributions, and suggests future work. With respect to my contributions, the primary goals are to:

- Detail total dose simulation techniques which are verified on real-world case studies, but widely applicable in other process technologies and designs.

- Advance the use of commercially available processes for high reliability applications. Total dose simulation techniques like those presented could be implemented in a design for reliability flow making commercial processes a cost effective yet trustworthy option for high-reliability designs.

- Illustrate the use of simulation techniques and TCAD modeling as a rapid yet effective substitute for experimental data, which can be expensive and time consuming to acquire.

- Empower those designers to increase total dose hardness of designs without being experts in the radiation effects field. Make simulation techniques easily accessible for application to new designs early in the design cycle.

#### **CHAPTER 2**

## TOTAL DOSE EFFECTS

#### **Brief History**

Research on the effects of ionizing radiation has been ongoing for more than 60 years, studying the consequences of exposing electronics to harsh environments, like space and nuclear systems. Work began after the failure of seven satellites in 1963. On July 9<sup>th</sup>, 1962 the Atomic Energy Commission and Defense Atomic Support Agency detonated a thermonuclear warhead above Johnson Island in the South Pacific Ocean. This experiment and similar nuclear tests by the Soviet Union were identified as causes of an increased amount of nuclear particles in the Earth's Van Allen belt [24-27].

It was later determined that the failure mechanism for the satellites could be attributed to the ionization of particles in the bipolar transistor packages, leading to trapped charge accumulating on the silicon die surface. This resulted in increased leakage currents, causing circuit failure [24]. At that time, it was believed that complementary metal-oxide-semiconductor (CMOS) transistors would be more radiation tolerant compared to bipolar transistors; as their transfer characteristics are not dependent on minority carrier lifetime [26]. However, testing of CMOS device radiation sensitivity at the Naval Research Laboratory (NRL) in 1964 revealed otherwise. It was reported that both n- and p-channel MOS devices exhibited sensitivity, which was linked to buildup of oxide-trapped charge and interface traps in device oxides [28, 29]. These results motivated the federal government to fund multiple research groups to investigate radiation effects and their impact on military space systems.

In the 1970s programs were established to develop radiation hardened CMOS integrated circuits. Sponsored by the Defense Nuclear Agency, these programs focused

on altering gate dielectrics through oxide growth techniques; annealing and doping modifications [28]. Additionally during this time, electronic spin resonance (ESR) on CMOS silicon dioxide films at NRL helped identify the primary damage mechanism, which was related to oxygen vacancy defects in silicon dioxide [28, 30]. Through the collaborative work of numerous research groups, the basic mechanisms of total dose degradation in silicon dioxide were identified.

Over time, the scaling of state-of-the-art digital technologies has reduced gate oxide thicknesses to less than a few nanometers. This has made degradation of gate oxides caused by ionizing radiation exposure in CMOS less of a concern. However for designs that require thicker gate oxides such as mixed-signal, power CMOS and Flash Memory, threshold voltage shifts in gate oxide MOS systems are still a major concern [31-33]. Moreover, even thicker isolation oxides are still significantly affected by ionizing radiation in modern CMOS devices, making inter-device leakage, so-called device "edge" leakage, a continued limitation to the radiation tolerance of commercial processes [16, 19, 34].

#### **Effects of Total Dose Irradiation**

Ionization is the process for which exposure to radiation in solid-state materials causes electrons to be liberated from atoms in a material. This occurs through the absorption of energy in the material from charged particles (i.e., electrons, protons, alpha particles, and heavy ions) and/or high-energy photons [35]. The quantity of energy converted into ionization can be determined by the linear energy transfer (LET) function, which gives the energy loss per unit length (dE/dx) of a particle in a given material. LET

is a function of the mass and energy of the particle as well as the target material density. The LET is expressed in units of MeV-cm<sup>2</sup>/g, or in simple terms, the energy loss per unit length normalized to the density of the material exposed [35, 36]. Fig. 2.1 illustrates the LET in SiO<sub>2</sub> versus particle energy for electrons, protons, and secondary electrons generated by 10 keV x-rays and 1.25 MeV <sup>60</sup>Co  $\gamma$ -rays [37].

The interaction between charged particles and a material generates electron-hole pairs (ehps) that lead to direct ionization. Alternatively, ionization due to photons is indirect. During indirect ionization ehps are created along the track of secondary electrons emitted during the photon interaction with the material. In both indirect and direct ionization, the density of ehps generated along the tracks of the charged particles is proportional to the energy transmitted to the material [38].

Fig. 2.1 LET in SiO<sub>2</sub> vs. particle energy for electrons, protons, and secondary electrons generated by 10 keV x-rays and 1.25 MeV <sup>60</sup>Co  $\gamma$ -rays [37].

Energetic secondary electron generation from photon exposure occurs through three different processes. The dominant process depends on the photon energy and the material exposed. For low-energy photons (~10-100keV) interacting with SiO<sub>2</sub>, the photoelectric effect dominates as a photon excites an electron to a high enough state to be emitted free

of the atom. For higher energy photons (0.1-10MeV) the Compton effect dominates. Similar to the photoelectric effect, a photon excites an electron to a higher, free state. However, with Compton scattering, a lower energy photon is also created, which is free to interact with other atoms. Pair production occurs only at very high photon energies (>3MeV). In this process the high-energy photon creates an electron-positron pair. The positron has the same properties as an electron, except that the charge is positive [18].

The total amount of energy deposited by a particle that causes the generation of ehps is quantified as total ionizing dose (TID). A typical unit of TID is the rad (radiation absorbed dose), which signifies the energy absorbed per unit mass of a material (1 rad = 100 ergs absorbed per gram of material) [36]. The SI unit for TID is a gray (1 Gy = 100 rad). Gray is the commonly used while discussing ionizing radiation in medicine; however the rad is the conventional unit used by the electronic radiation effects community.

In SiO<sub>2</sub>, immediately after the generation of electron-hole pairs, many of the electrons rapidly transport out of the dielectric leaving behind the slower holes. Depending on the electric field in the oxide during exposure, some electrons will recombine with holes. The fraction of the holes that do not recombine is known as the fractional hole yield. These remaining holes will transport along localized states in the oxide. During this transport process, some of the holes will be trapped, forming positive oxide-trapped charge, primarily near the SiO<sub>2</sub>-Si interface. Additionally, during the hole hopping and the charge trapping processes, hydrogen ions (protons) can be released. These ions can also drift or diffuses to the interface where they can cause the formation

interface traps in the silicon bandgap. These four processes are illustrated in Fig. 2.2 [18,

35].

Fig. 2.2 Energy band diagram of MOS capacitor which illustrates the main processes for radiation induced charge generation [18][35].

#### Charge Yield

The four processes of ionizing radiation induced charge generation are all the result of conversion of dose (energy absorbed per unit mass of the material) into the generation of ehps. The amount of free holes generated can be expressed analytically using the following formula [18, 39]:

$$N_h \left[\frac{\# ehp}{cm^2}\right] = f_y(E_{ox})g_o Dt_{ox}, \qquad (2.1)$$

which gives the total number of holes generated per unit area of the material,  $N_h$ , as a function of the charge (or hole) yield,  $f_y(E_{ox})$ , the pair density conversion factor,  $g_o$ , the dose, D, and the oxide thickness in centimeters,  $t_{ox}$ . This equation is can be easily

understood when related to the qualitative description the four processes illustrated in Fig. 2.2.

As described above, part of the energetic particle's kinetic energy is transferred to the material for ehp generation. The minimum energy required for creating an electronhole pair,  $E_p$ , depends on the bandgap of the material. The pair density conversion factor,  $g_0$ , which relates ehps generated to total dose can be calculated using following formula: [40]:

$$g_o\left[\frac{\#ehp}{cm^3 \cdot rad}\right] = 100\left[\frac{erg}{g}\right]\left[\frac{1}{rad}\right] \cdot \frac{1}{1.6 \times 10^{-12}}\left[\frac{eV}{erg}\right] \cdot \frac{1}{E_p}\left[\frac{\#ehp}{eV}\right] \cdot \rho\left[\frac{g}{cm^3}\right].$$

(2.2)

The relationship between ionization energy, material density, and generated carriers are listed in Table 2.1 for both Si, and SiO<sub>2</sub> [18, 39].

Table 2.1 Minimum electron-hole pair creation energy, density and pair density generated per rad for a given material [18, 39]

| Material        | Ep   | Density    | Pair density, $g_o$        |

|-----------------|------|------------|----------------------------|

|                 | (eV) | $(g/cm^3)$ | (ehp/cm <sup>3</sup> ·rad) |

| Silicon         | 3.6  | 2.328      | $4 \times 10^{13}$         |

| Silicon Dioxide | 17   | 2.2        | $8.1 \times 10^{12}$       |

Once the generation of ehps has occurred, a fraction of the ehps are almost

immediately annihilated through either columnar or geminate recombination [38]. The fraction of ehps that avoid initial recombination is the charge yield,  $f_y$ . If an electric field is present during this process, it separates electrons and holes and reduces recombination. It then follows that charge yield is dependent on the magnitude of the local electric field in the material. The charge yield can be approximated as

$$f_{\mathcal{Y}}\left(\vec{E}\right) \approx \left(\frac{\left|\vec{E}\right|}{\left|\vec{E}\right| + E_0}\right) \quad ,$$

(2.3)

where  $\vec{E}$  is the local field vector and  $E_0$  is the threshold field constant (=  $5.5 \times 10^5$  V/cm) [20, 40]. For two common radiation sources used for experimental testing, <sup>60</sup>Co gamma rays and 10 keV x-rays,  $f_y(\vec{E})$  can be expressed as [41],

$$f_{y}(\vec{E})_{Co-60} = \left(\frac{0.55}{|\vec{E}|} + 1\right)^{-0.7}$$

(2.4)

and

$$f_{y}(\vec{E})_{x-ray} = \left(\frac{1.35}{|\vec{E}|} + 1\right)^{-0.9},$$

(2.5)

respectively, where the local field vector  $(\vec{E})$  is expressed in units of MV/cm. The charge yield is plotted for various radiation sources in Fig. 2.3 [18, 20, 40].

Fig. 2.3 Fraction of uncombined holes vs. electric field for various incident particles [18, 20, 40].

It is of note that the fractional hole yield plotted in Fig. 2.3 actually increases with decreased energy of the incident or secondary particle. This can be explained by observing that a strongly ionizing particle forms dense columns of charge, in which the ehp recombination rate is high because of the decreased average spacing between pairs

[18]. It is also obvious in Fig. 2.3 that with increased electric field the probability of recombination decreases.

## Hole Transport

After ehp generation and initial recombination, the holes and electrons that do not recombine can transport through the silicon dioxide due to the local electric field. Since electrons have a higher mobility (e.g.,  $\mu_n = ~20 \text{ cm}^2/\text{Vs}$  at 300K) they are able to transport out of the oxide, on the order of picoseconds [35, 36, 42]. However holes have a lower mobility ( $\mu_p = ~1.6 \times 10^{-5} \text{ cm}^2/\text{Vs}$  at 300K), and consequently remain in the oxide for much longer periods. Holes still transport through the oxide, some toward the SiO<sub>2</sub>-Si interface. However, this process is a great deal slower than electron transport, and is temperature and electric field-dependent [40].

As holes transport through the oxide, they causes a distortion of the localized potential field in the lattice due to their charge, as described by the continuous-time-random-walk (CTRW) hopping transport formalism [43, 44]. This model suggests that holes move by hopping between localized shallow trap states in the oxide. As a hole transports through the oxide, it causes distortion of the local lattice in the SiO<sub>2</sub> layer. This distortion also serves to increase the effective mass of the hole and decrease its mobility. The combination of the charged hole and its strained field is known as a polaron; and it is said that hole transport occurs through the lattice via "polaron hopping" [40, 44].

Once the trap depth increases past a certain limit, there is a possibility the hole could become trapped, where they form the previously mentioned positive oxide-trapped charge ( $N_{ot}$ ). These trapping sites are thought to be primarily the result of neutral oxygen

vacancies in the SiO<sub>2</sub> (E' centers) [45, 46], although other works have proposed that hydrogen containing defects in the oxide may also trap holes [47, 48]. Reactions between holes and defects in the oxide can also lead to the creation of interface traps ( $N_{it}$ ) [49]. The nature of positive oxide-trapped charge and interface traps generated due to ionizing radiation will be discussed further in later sections.

### Positive Oxide Trapped Charge

Holes generated via ionizing radiation can transport toward the SiO<sub>2</sub>-Si interface in the presence of a positive gate bias. Due to lattice mismatch and the out-diffusion of oxygen, there are a large number of oxygen vacancies near the interface [50]. These vacancies can also be thought of as "excess" silicon near the interface that did not completely oxidize during fabrication. As the holes approach the interface, these vacancies trap some fraction of the holes. This fraction is a function of the capture cross section of these defect precursors. The capture cross section depends strongly on the fabrication process, as fraction of trapped holes can vary from  $\sim$ 3% for radiation hardened processes to as high as 50-100% for soft oxides [18].

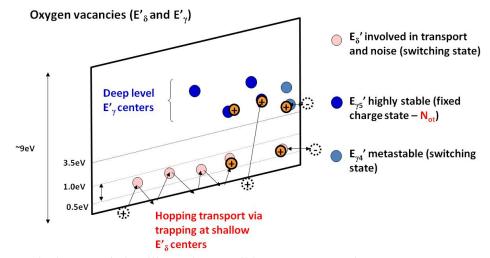

Two oxygen vacancy defect types play a role in the transportation toward the interface and subsequently trapping of the hole as positive oxide-trapped charge. These defects, or E' centers, are classified as either  $E'_{\delta}$  or  $E'_{\gamma}$  centers [16]. The  $E'_{\delta}$  center is a shallow trap that impacts hole transport, as most of the  $E'_{\delta}$  centers have energies located in the SiO<sub>2</sub> bandgap less than 1.0 eV from the oxide valence band. Alternatively, the  $E'_{\gamma}$  center is a deep trap, located at energy levels greater than 3 eV above the oxide valence band, and is responsible primarily for fixed positive charge buildup in the oxide [39]. Fig.

2.4 illustrates an energy band diagram of  $SiO_2$  showing of the main E' centers and their relative position in the oxide.

Fig. 2.4 Band Diagram of SiO<sub>2</sub> illustrating possible oxygen vacancies [39].

Following the trapping of charge in the oxide, neutralization of the charge can occur. The rate at which charge neutralization occurs has been shown to be time, temperature and electric field dependent. It is found experimentally that the voltage shift due to oxide-trap charge ( $\Delta V_{ot}$ ) exhibits logarithmic decrease in magnitude as a function of time during post-irradiation anneal. Additionally this logarithmic decrease is shown to be independent of the irradiation dose rate, however the magnitude of total recovery (total decrease in magnitude of  $\Delta V_{ot}$ ) is highly process dependent with some commercial processes exhibiting little charge neutralization [18, 51]. Elevated temperature anneals have shown that that for some technologies neutralization is a strongly thermally activated process, with time to 50% neutralization varying by approximately an order of magnitude between anneal temperatures of 25°C to 125°C [18, 51]. Finally charge neutralization shows a strong bias dependency, with experimental data indicating that it is

possible for charge neutralization under a large positive bias during anneal to be double that of neutralization seen in an unbiased anneal [18, 52].

It has also been illustrated in experiments that some of the charge neutralization seen is reversible by switching to a negative anneal bias. This indicates that the defect centers associated with the oxide-trapped charge are still present after anneal, and some of the appeared neutralization is actually just charge compensation [18]. There are two physical mechanisms that are used to describe the time, temperature and bias dependence of charge neutralization seen in experiment. Charge neutralization can occur from the tunneling of electrons from the silicon or the thermal emission of electrons residing in the oxide valance band to the oxide traps. The effects on transistor operation caused by positive-oxide trapped charge will be discussed further in this chapter.

### Interface Traps

Ionizing radiation also produces interface traps, which form in the silicon bandgap. Since the radiation induced traps are develop physically at the SiO<sub>2</sub>-Si interface, traps can either be charge positive, neutral or negative as the trap easily donates or accepts electrons from the silicon, subject to the trap location in the bandgap and the applied external bias. Interface traps that fall in the upper half of the silicon bandgap, i.e., above the intrinsic Fermi energy, are generally considered acceptor-like. For these defects, if the Fermi level is above the trap energy level, the defect accepts an electron from the silicon and is negatively charged. If the trap energy falls in the lower half of the bandgap, i.e., below the intrinsic Fermi energy, the defects are typically denoted as donor-like. For donor-like traps, if the Fermi level is below the trap level, an electron is donated to the silicon leaving behind a positive charge. If the intrinsic Fermi energy is equal to the Fermi level at the interface (a midgap voltage is applied to the gate), there is no net charge contributed by the interface trap [18].

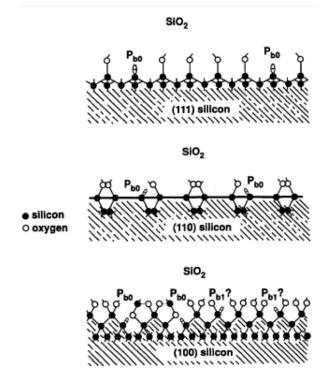

Interface states resulting from ionizing radiation exposure are identified as dangling bond defects called  $P_b$  centers [39, 53]. These  $P_b$  defects are classified by two center types,  $P_{b0}$  and  $P_{b1}$ .  $P_{b0}$  centers are common to the (111) silicon surface, with the dangling bond defect extending normal to the oxide. The  $P_{b1}$  center is closely related to the  $P_{b0}$ defect but common to (100) silicon [39]. A graphical representation of the two common defect centers is provided in Fig. 2.5.

The build-up of interface traps following irradiation is a relatively slow process, with trap generation occurring in seconds to thousands of seconds after exposure. It is believed trap formation occurs by way of a two-step process. The process begins in a similar fashion to that of the oxide-trapped charge formation, with the ehp generation due to ionization. Again, the fraction of holes that do not immediately recombine are capable of transport through the oxide. As previously discussed, the hole can be trapped or it may interact with oxide defect centers containing hydrogen (DH centers). These defect centers are found to be naturally occurring in the oxide or formed during fabrication processing. This results in the release of positively charged hydrogen atoms, also known as protons  $(H^+)$  [47, 54]. It is thought that the majority of the protons are released when a hole is captured or released from a hydrogen-passivated oxygen vacancy during the hole hopping process [54]

Fig. 2.5 Model of P<sub>b0</sub> and P<sub>b1</sub> interface trap centers on (111), (110) and (100) silicon [39, 55].

The released proton ( $H^+$ ) can transport toward the interface in a manner similar to the hole hopping process under the influence of a positive electric field. At the interface the protons can serve to break the Si-H bonds, form in H<sub>2</sub> and a dangling Si-bond. This reaction can be expressed as [39, 49],

$$SiH + H^+ \to D^+ + H_2.$$

(3.6)

The product of this reaction is an interface trap defect  $(D^+)$ . As discussed previously, the interface traps  $(N_{it})$  can interchange charge with the silicon due to the close proximity of the trap to the interface, leaving no barrier to charge exchange. The use of hydrogen is prevalent during CMOS processing thus the possibility of hydrogen-passivated silicon dangling bonds is highly likely.

# **Device Response Considerations**

## Effects on Gate Oxides

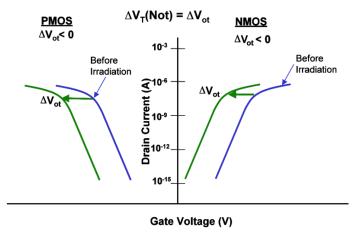

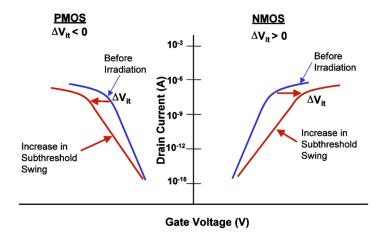

Both positive oxide-trapped charge and interface traps resulting from ionizing radiation can be seen manifested in the DC characteristics of both n- and p-channel MOSFETs as a reduction of the threshold voltage and increase in the subthreshold swing. This is illustrated by example in Fig. 2.6 and Fig. 2.7.

Fig. 2.6 Illustration of the shift in the drain current vs. gate voltage characteristics of n- and pchannel MOSFETs as a result of positive oxide-trapped charge [39].

Fig. 2.7 Illustration of the shift in the drain current vs. gate voltage characteristics of n- and p-channel MOSFETs as a result of interface traps [39].

As seen Fig. 2.6 the buildup of positive oxide trapped charge in the gate oxide reduces the threshold voltage for both n and p-channel MOSFETs. Additionally the shift in threshold voltage for n-channel MOSFETs results in an increase in off-state and drive currents, while in p-channel MOSFETs off-state and drive currents are reduced. As seen in Fig. 2.7 interface trap buildup serves to decrease the subthreshold slope, or as it is often described an increase the subthreshold swing, of a CMOS device. Additionally an increase in threshold voltage is seen for n-channel MOSFET while the threshold voltage of a p-channel MOSFET is reduced (becomes more negative) with the increased presence of interface traps. The bias dependency of the interface trap charge state (i.e. positive, negative or neutral) explains this decrease in subthreshold voltage swing. During the current-voltage characterization, the silicon surface at the Si-SiO<sub>2</sub> interface is swept from accumulation to inversion by the gate voltage. Increased interface trapping inhibits the gate's ability to invert the silicon surface.

It is seen in Eq. 2.1 that the magnitude of holes generated from ionizing radiation shows a linear dependence on oxide thickness  $(t_{ox})$ . The amount of holes generated directly determines the amount of oxide-trapped charge  $(\Delta N_{ot})$  and interface traps  $(\Delta N_{it})$ generated in the oxide as discussed previously. This indicates that the magnitude  $\Delta N_{ot}$ and  $\Delta N_{it}$  will both drop with decreased oxide thickness due to device scaling. Additionally, it is understood that the magnitude of the radiation induced voltage shift  $(\Delta V_{ot})$  due to oxide-trapped charge  $(\Delta N_{ot})$  can be calculated using the following formula [16]:

$$\Delta V_{ot} = -\frac{t_{ox}}{k_{ox}\epsilon_o} q \Delta N_{ot}.$$

(2.7)

Eq. 2.7 includes constants for elementary charge (q), dielectric constant for SiO<sub>2</sub>  $(k_{ox})$ and permittivity of free space  $(\epsilon_o)$ . The  $\Delta N_{ot}$  dependence on oxide thickness in Eq. 2.7 shows that negative threshold voltage shifts caused by fixed oxide trapped charge buildup is proportional to the square of oxide thickness, i.e.,

$$-\Delta V_t (\Delta N_{ot}) = -\Delta V_{ot} \propto t_{ox}^2 \tag{2.8}$$

This indicates that device scaling and the corresponding reduction of gate oxide thicknesses will serve to limit the effect of ionization damage on gate oxides in deep submicron CMOS technologies. Indeed device scaling has increased the radiation hardness in the most state of the art technologies making threshold voltage shifts due to gate oxide degradation a minimal concern, as verified through experiment [19].

### Effects on Isolation Oxides

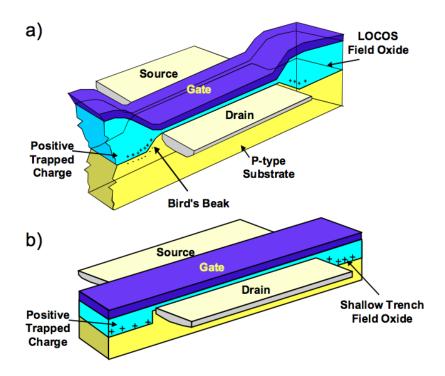

While the hardness of gate oxides to ionizing radiation has been greatly increased due to device scaling, isolation oxides still remain relatively soft. In both older (LOCOS) and later (STI) isolation technologies, the buildup of oxide-trapped charge and interface traps are on-going concerns due to very thick of oxides and relatively poor oxide quality compared to gate dielectrics. Of chief concern is oxide-trapped charge with isolation oxides, as it can result in significant parasitic leakage currents [16, 18, 30, 34, 35, 38, 56, 57].

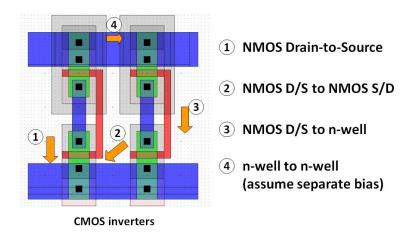

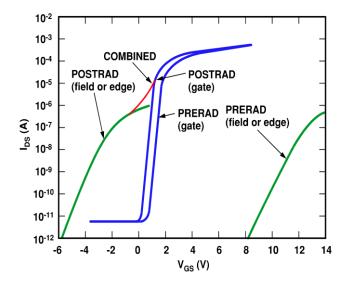

Possible leakage current paths are identified in Fig. 2.8. Intra-device drain-tosource (so called "edge") leakage in n-channel MOSFETs can result from the buildup of oxide-trapped charge near the active device edge, as seen in Fig. 2.9 This edge leakage can be thought of as a separate parasitic edge transistor acting in parallel with the gate oxide transistor. This is illustrated in current-voltage characteristics of Fig. 2.10.

Additionally the buildup of oxide-trapped charge in the base of the isolation oxide can result in inversion of silicon causing inter-device leakage current (paths 2 to 4 of Fig. 2.8). Oxide trapped-charge buildup is enhanced by the presence of a local electric field in the isolation oxide. High bias voltages on polysilicon and metal device interconnections on top of isolation oxides serve to generate this field. Parasitic current between active transistors can result in loss of device isolation, increased drain on voltage supplies, and the collapse of desired node voltages [16, 18, 25, 34, 57].

Fig. 2.8 Possible intra- and inter-device leakage current path resulting from oxide trapped charge buildup in LOCOS or STI isolation oxides [39].

Fig. 2.9 Cross section of a) LOCOS isolated and b) STI isolated transistor showing trappedcharge location corresponding with intra-device edge leakage current [18, 58].

Fig. 2.10 Current-voltage characteristics of gate-oxide and a parasitic "edge" transistor showing increase in current post-irradiation due to the parasitic edge transistor [18].

#### CHAPTER 3

# SIMULATION OF INTER-DEVICE EFFECTS

As explained in Chapter 2, inversion below field isolation oxides can result in significant inter-device leakage current. This current can, at minimum, hinder circuit operation and reduce battery life and at maximum, cause circuit failure. In order to design radiation-hardened circuits extreme care is taken to prevent inter-device leakage between active circuit elements. This includes adding highly doped "channel stop" implants as well as tightly controlled routing schemes of polysilicon and metal interconnect layers. Channel stop implants will inhibit creation of parasitic inter-device current paths by increasing inversion threshold voltage in these regions.

One alternative to channel stop placement is the use of careful routing of polysilicon or metal interconnects to avoid high electric fields in isolation oxides. Minimizing electric field is a worthwhile total dose hardening method for two reasons. First, reduced electric field decreases initial charge yield during irradiation, which then reduces defect buildup near the SiO<sub>2</sub>/Si interface. Second, applied bias (electric field) increases the likelihood of parasitic inversion of silicon beneath the oxide. However, both channel stop placement and routing schemes add complexity to the design, and hurt design efficiency by increasing cell layout size.

Instead of implementing these techniques uniformly across the entire design, it would be advantageous for designers to be empowered to choose these techniques only when necessary. To do this, designers must be able to predictively model and simulate a given circuit, including the effect of parasitic inter-device current flow, and weigh the resulting circuit performance against design metrics. Predictive simulation capability

allows targeted hardening decisions to be made, implementing such hardening by design changes only when necessary.

In this chapter a charge pump case study, first presented in my Masters' Thesis, is reviewed to illustrate simulation of inter-device effects [23]. Moreover, the charge pump case study establishes context for follow-up work, presented in the second half of this chapter, specifically investigating geometric effects of inter-device parasitic structures. Together both works effectively illustrate techniques to effectively simulate inter-device effects.

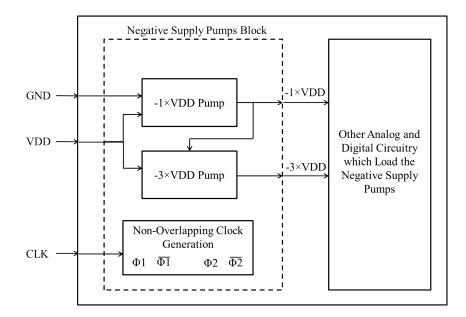

## Charge Pump Case Study – Background and Methodology

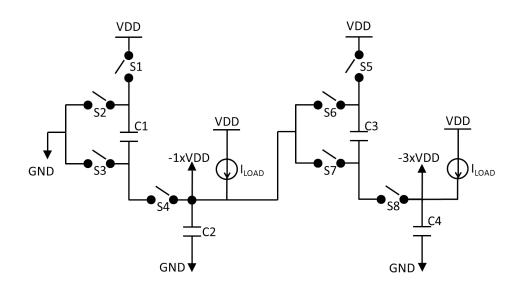

To develop and validate a design strategy for simulation of inter-device leakage, an integrated circuit, which is part of an implantable pacemaker design, is presented as a case study. The IC is used to provide electrical impulses, delivered by electrodes contacting the heart muscles, to regulate the beating of the heart. The IC has multiple functional digital and analog blocks used to provide multi-chamber pacing and recharge support for the pacemaker device. However the focus of this study is on a single block of the IC, the negative supply pumps. Fig. 3.1 illustrates the charge pump implementation in the overall integrated circuit scheme. The charge pump is used to generate two supply rails, -1×VDD and -3×VDD, from a single VDD supply. A simple schematic representation of the charge pump is shown in Fig. 3.2.

The choice to investigate the negative supply pumps, implemented as a charge pump topology, is particularly appropriate as a) charge pumps are widely used in implantable device and medical applications for voltage generation and b) high circuit

bias conditions serve to enhance ionizing radiation damage. High voltage switched capacitor charge pump topologies are becoming increasingly implemented in such applications as non-volatile memory and medical devices to generate a range of potentials from a single battery voltage [59-61]. In many cases, existing supply voltages in low power ICs are insufficient for some application specific operations, such as floating gate programming, as an LCD driver or simply to generate battery-multiplied supply rails on chip.

Fig. 3.1 Simplified block diagram of integrated circuit implementation of Negative Supply Pumps.

Charge pumps used in these types of applications are particularly susceptible to radiation-induced degradation because their higher voltage specifications typically require the utilization of devices manufactured with thicker dielectrics and lower doping levels. It is well known that these properties make high voltage CMOS technologies more susceptible to TID damage than advanced low power CMOS processes [16]. Moreover,

the higher voltage requirements result in larger electric fields, particularly in isolation (field) oxides, which will enhance radiation-induced defect buildup [17, 18]. The combined impact of lower doping and high electric fields leads to greater levels of field oxide leakage that, as will be shown, increases current draw at the charge pump output.

Fig. 3.2 Dual charge pump configuration implemented to generate -1×VDD and -3×VDD from the externally available VDD and GND voltages.

#### Experimental Irradiation Results

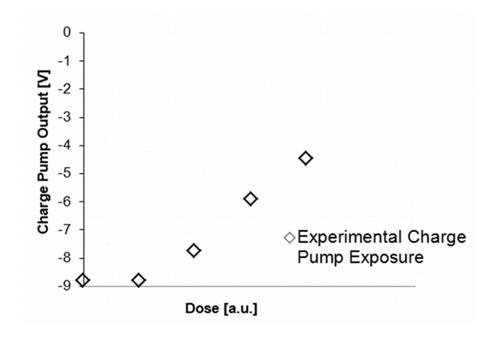

For the total dose failure analysis of the charge pump, the focus was on degradation in the high voltage -3×VDD output node. The radiation response of the -3×VDD with applied total dose is shown in Fig. 3.3. Pre-irradiation and after the first total dose stress step the output voltage remains constant at -9 V (-3×VDD). However at the second of total dose exposure stress step, the output has reduced by more than 1 V, and after third total dose stress step the output has reduced 50% from the operation specification. Such a reduction in the charge pump output is considered unacceptable for the integrated circuit design. These results serve as motivation for the failure analysis case study, and represent the dataset that is to be recreated via a radiation-enabled simulation.

Fig. 3.3 Experimental results showing voltage collapse of the -3×VDD charge pump output versus applied total dose. Total dose increases from left to right.

#### Charge Pump Analysis Approach

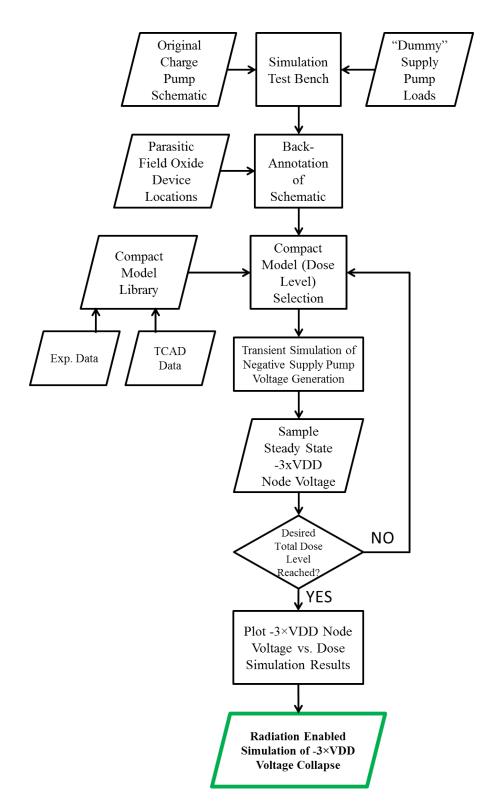

The goal of the charge pump analysis case study is to explain the degradation exhibited as a collapse of the -3×VDD charge pump output with increasing total dose exposure. To accomplish this, extensive experimental work, device modeling and circuit and layout analysis are needed. The analysis approach, to be detailed in following sections, is represented graphically in the flowchart of Fig. 3.4.

First the inputs to the radiation enabled simulation must be determined, specifically compact models representing the most sensitive elements of the charge pump, parasitic inter-device field-oxide FET (FOXFET) structures. Compact models are generated for the FOXFETs through modeling a combination of experimental and TCAD datasets. Then, the charge pump circuit and layout are analyzed, pinpointing numerous FOXFET-like structures within the charge pump layout. Back-annotation of FOXFETs into the circuit schematic combined with a FOXFET compact model set establishes the basis for a radiation enabled simulation test bench. Utilizing the charge pump test bench, the simulation dose level can be assigned by selecting the appropriate FOXFET compact model. Since the models were created after a specific dose exposure level, the model represents the device's operation at that exposure level. By selecting a particular exposure level (compact model set) for all devices in the schematic, we then simulate the circuit at that exposure level.

For the charge pump circuit we run a transient simulation of the pump operation as the -3×VDD node voltage builds up on the hold capacitor. We then note the final steady state voltage for the node at the chosen simulated exposure level. Next we select a compact model library set at the next exposure level, and repeat the simulation. Simulating the charge pump circuit with dose specific compact model sets models the effect of increasing total dose exposure.