Electrical and Thermal Transport in Alternative Device Technologies

by

Suleman Qazi

# A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved November 2013 by the Graduate Supervisory Committee:

Dragica Vasileska, Co-Chair Stephen Goodnick, Co-Chair Meng Tao

ARIZONA STATE UNIVERSITY

December 2013

#### ABSTRACT

The goal of this research work is to develop a particle-based device simulator for modeling strained silicon devices. Two separate modules had to be developed for that purpose: A generic bulk Monte Carlo simulation code which in the long-time limit solves the Boltzmann transport equation for electrons; and an extension to this code that solves for the bulk properties of strained silicon. One scattering table is needed for conventional silicon, whereas, because of the strain breaking the symmetry of the system, three scattering tables are needed for modeling strained silicon material. Simulation results for the average drift velocity and the average electron energy are in close agreement with published data.

A Monte Carlo device simulation tool has also been employed to integrate the effects of self-heating into device simulation for Silicon on Insulator devices. The effects of different types of materials for buried oxide layers have been studied. Sapphire, Aluminum Nitride (AIN), Silicon dioxide (SiO<sub>2</sub>) and Diamond have been used as target materials of interest in the analysis and the effects of varying insulator layer thickness have also been investigated. It was observed that although AIN exhibits the best isothermal behavior, diamond is the best choice when thermal effects are accounted for.

# DEDICATION

To my parents who have been a great inspiration for me

To my wife, Abeer, and our daughter, Arfa.

#### ACKNOWLEDGMENTS

I would like to acknowledge the immense support from my mentor and advisor, Professor Dragica Vasileska. Without her guidance and strong motivation, the work on this thesis would not have been possible. Her expertise in the area helped me gain the knowledge and skills needed to complete this thesis. I am also grateful to Dr. Stephen Goodnick for continued support and guidance during the time I was working on completing the thesis.

I would like to extend my appreciation to the School of Electrical, Computer and Energy Engineering at Arizona State University for providing me this opportunity to pursue my Masters' degree. I want to mention the great support from my colleagues, in particular Robin Daugherty and Pradyumna Muralidharan, at the Nano Electronics Research Group at ASU for their useful advice during our academic discussions that helped me debug errors in the code.

It goes without saying that I am totally indebted to my parents, my sisters and my wife for their continued support during the quest of my higher studies in the United States.

# TABLE OF CONTENTS

|     |               | Pa                                                  | ige  |

|-----|---------------|-----------------------------------------------------|------|

| LIS | ST OF TABLES. |                                                     | vi   |

| LIS | ST OF FIGURES | 5                                                   | .vii |

| СН  | APTER         |                                                     |      |

| 1   | INTRODUCTI    | ON                                                  | 1    |

|     | 1.1           | Need for High Field Study                           | 2    |

|     | 1.2.          | Operational Problems with MOSFETS                   | 3    |

|     |               | a. Subthreshold leakage                             | .3   |

|     |               | b. Interconnect capacitance                         | 4    |

|     |               | c. Heat production                                  | 4    |

|     |               | d. Gate oxide leakage                               | 4    |

|     |               | e. Process variations                               | 5    |

|     | 1.3           | Alternative Device Technologies                     | 5    |

|     |               | J                                                   |      |

| 2   | MODELING /    | APPROACH                                            | . 6  |

|     | 2.1           | Need for Monte Carlo Simulations                    | 7    |

|     | 2.2           | Scattering mechanisms                               | 9    |

|     |               | a. Acoustic Phonon Scattering (non-parabolic bands) | 9    |

|     |               | b. Non-polar optical phonon scattering              | 10   |

|     |               | c. Coulomb scattering                               | 12   |

|     | 2.3           | Bulk Monte Carlo method                             | 12   |

|     | 2.4           | Simulation Results                                  | 16   |

|     | 2.4           | Simulation Results                                  | 10   |

| 3   | STRAINED S    | ILICON DEVICE                                       | 21   |

|     | 3.1           | Difference between un-strained and strained Silicon | .22  |

|     | 3.2           | Modeling Approach                                   | 23   |

| CHAPTER |                                          | Page |

|---------|------------------------------------------|------|

|         | 3.3 Simulation Results                   | 24   |

| 4       | SOI DEVICES AND THE ROLE OF SELF HEATING | 30   |

|         | 4.1 Simulation Scheme                    | 32   |

|         | 4.2 Simulated Device                     | 35   |

|         | 4.3 Simulation Results                   | 36   |

| 5       | CONCLUSIONS AND FUTURE WORK              | 45   |

| REF     | FERENCES                                 |      |

# LIST OF TABLES

| Table |                                            | Page |

|-------|--------------------------------------------|------|

| 4.1.  | Properties of the BOX Materials Considered | 36   |

| 4.2.  | Design of experiments results              | 43   |

# LIST OF FIGURES

| Figure | e Page                                                                 |

|--------|------------------------------------------------------------------------|

| 1.     | Transistor count trend 2                                               |

| 2.     | Constant energy surface for silicon - f-type and g-type processes 11   |

| 3.     | Flowchart - Ensemble Monte Carlo Algorithm                             |

| 4.     | Flowchart for the Free flight-Scatter routine                          |

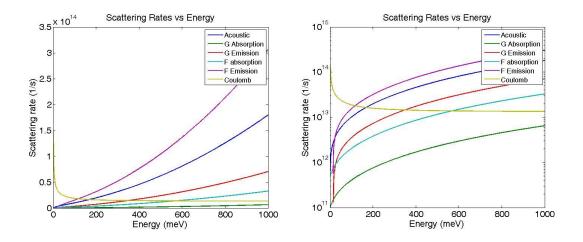

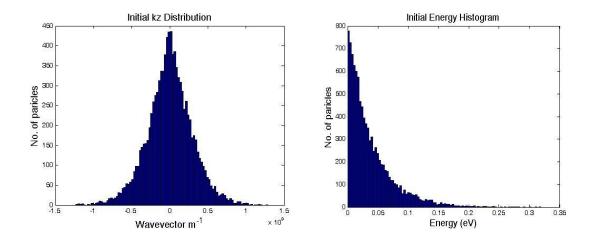

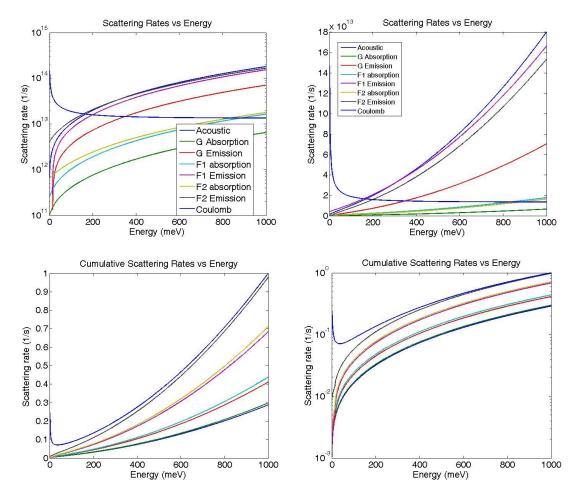

| 5.     | Scattering rates in normal and log scale16                             |

| 6.     | Cumulative Scattering rates in normal and log scale                    |

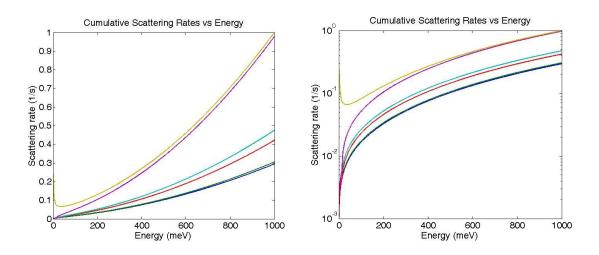

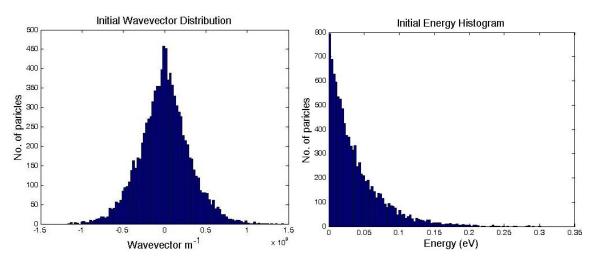

| 7.     | Initial Wavevector and Energy Distribution                             |

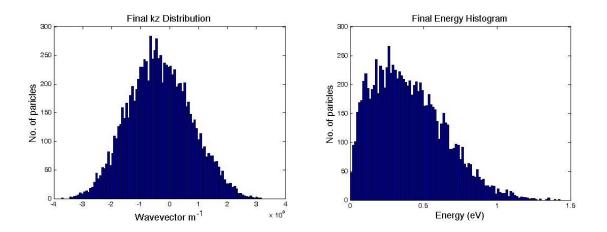

| 8.     | Final Wavevector and Energy Distribution 18                            |

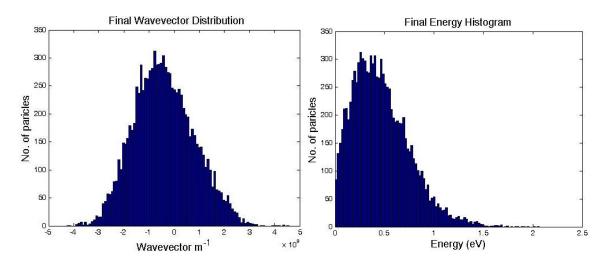

| 9.     | Time evolution of Drift Velocity 19                                    |

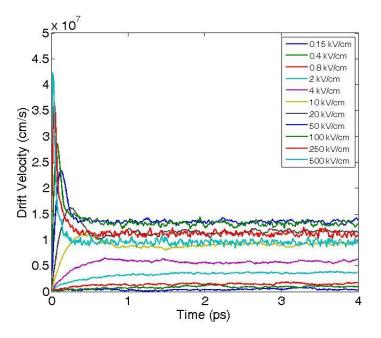

| 10.    | Time evolution of Energy 19                                            |

| 11.    | Velocity saturation with applied Electric Field 20                     |

| 12.    | Tensile Strain in Si layer    22                                       |

| 13.    | Scattering rates in normal and log scale 24                            |

| 14.    | Initial Wavevector and Energy Distribution 25                          |

| 15.    | Final Wavevector and Energy Distribution 25                            |

| 16.    | Time evolution of Drift Velocity                                       |

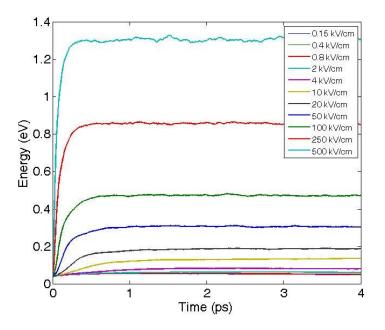

| 17.    | Time evolution of Energy 26                                            |

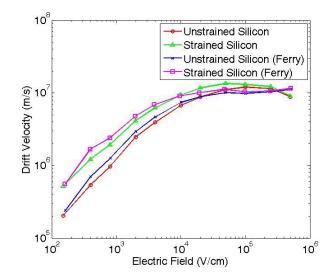

| 18.    | Velocity Field Characteristics for Strained and un-strained Silicon 27 |

| 19.    | Peak overshoot velocity for starined and unstarined Si 27              |

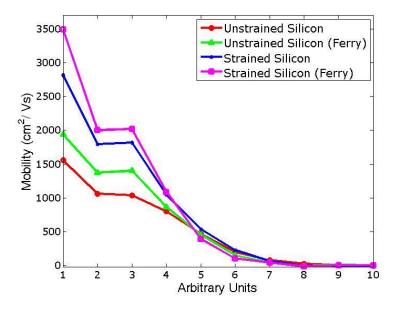

| 20.    | Mobility in strained and unstrained Silicon 28                         |

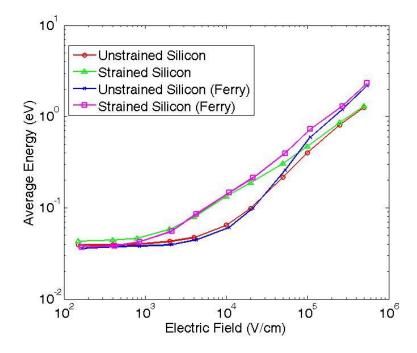

| 21.    | Energy Field Characteristics for strained and un-strained Silicon 29   |

| 22.    | Structure of a reference SOI NMOS device                               |

# Figure

| 23. | Depletion region of PD and FD SOI devices                        | 31  |

|-----|------------------------------------------------------------------|-----|

| 24. | Path between energy-carrying particles in a semiconductor device | .33 |

| 25. | Exchange of variables between EMC and Energy Balance kernels     | 35  |

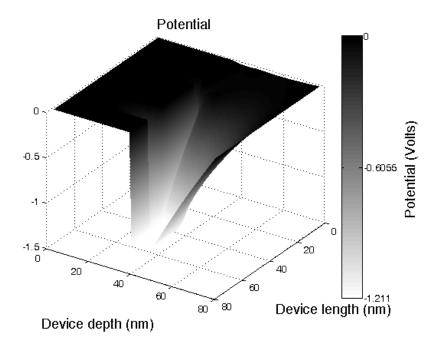

| 26. | Potential Profile in the device                                  | 37  |

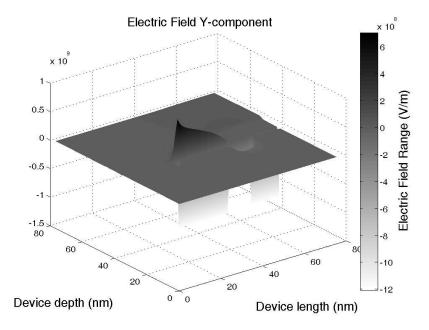

| 27. | Electric Field Y component profile in the device                 | 37  |

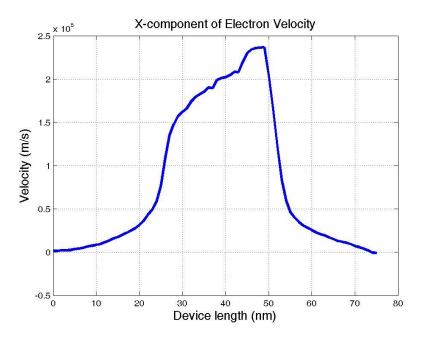

| 28. | Electron Velocity X Component in the device                      | 38  |

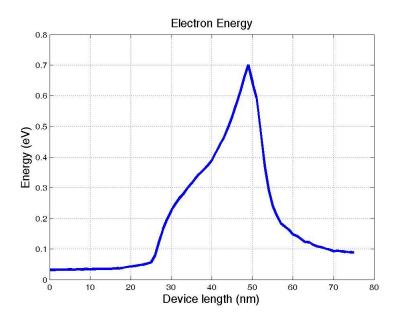

| 29. | Electron Energy variation in the device                          | 38  |

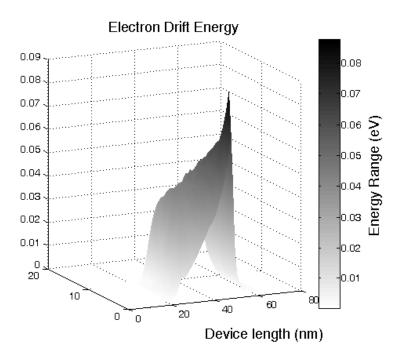

| 30. | Electron drift energy profile in the device                      | 40  |

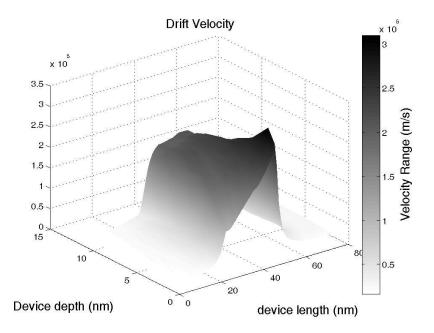

| 31. | Electron drift velocity profile in the device                    | 40  |

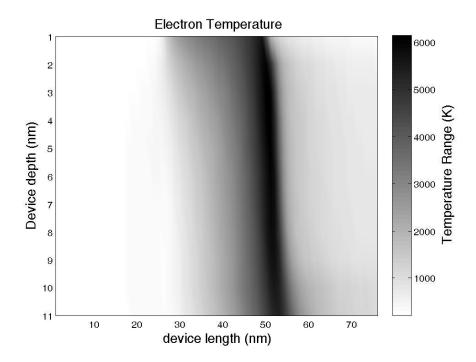

| 32. | Electron temperature profile in the device                       | 41  |

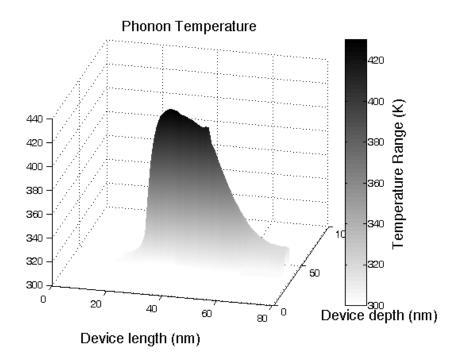

| 33. | Optical phonon temperature profile in the device                 | 42  |

| 34. | Lattice temperature profile in the device                        | 42  |

| 35. | Isothermal and Thermal simulations                               | 44  |

Page

#### CHAPTER 1

#### INTRODUCTION

Semiconductor materials have been researched for their electrical transport characteristics since nearly the start of the 20th century. The main interest in these materials arose due to their ability to change the conductivity merely by introducing dopants and also under the application of an electric field. Even with an immense interest in those materials, it was not until 1947 that the semiconductor materials became useful for devices when William Shockley, John Bardeen and Walter Brattain sandwiched two diodes together to create the world's first transistor at Bell Labs. Since then, the investigation in the field of semiconductor materials grew immensely which led to the development of a variety of devices exploiting the many individual and unique characteristics of these materials. The experimental success of the semiconductor industry was possible only due to the development of an understanding of the physical, electrical and chemical properties of the materials.

Without going into the details about the development of semiconductor industry starting in the 1950's to this day, the modern day electronics has been possible only due to the consistent reduction in the size of the devices. Since the applied voltage did not reduce at the same rate as the device dimensions, the field applied across the devices increased. Soon after the invention of the transistor in 1947, it was observed that very high electric field strengths could cause the Ohm's law to fail [1]. At the beginning of the semiconductor industry, power was not one of the main concerns but later on, having such high electric fields in commercially available transistors, called for the need of new physics to help explain how these devices worked. As a result, soon after the invention of transistors, the field of nonlinear transport saw a period of rapid development [2]. Many researchers devoted their time and efforts to improve the scientific knowledge in the area of high field transport. The physical and chemical properties of materials were investigated in details that lead to the understanding of their energy band structures. From the better understanding of band structures, the characteristic electrical properties of the materials were theorized and the resulting devices were found to match the results obtained from theory.

#### 1.1. Need for High Field Study

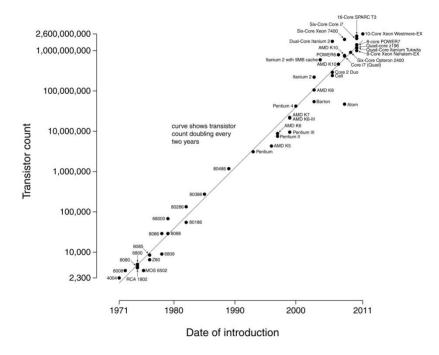

The study of charge transport in semiconductor materials is of fundamental importance not only from the point of view of the basic physics but also for its application to electrical devices [3]. With the increase in demand of electronic appliances, the need for more powerful and faster devices grew, ultimately resulting in a higher transistor density. Figure 1.1 shows the increase in the number of transistors in a device, following Moore's law [4]

Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1.1 Transistor count trend (courtesy Intel.com)

This increased transistor count per unit area of the chips came about through the use of device scaling. Bipolar Junction Transistors (BJTs) were traditionally used in the beginning of the semiconductor history due to their higher power handling capabilities, larger gain and transconductance and many other unique properties. However with modernization, Metal Oxide Semiconductor Field Effect Transistors became the go to choice for newer devices.

Typical MOSFET channel lengths originally started out as several micrometers. However, the modern integrated circuits incorporate MOSFETs with channel lengths that are about a few tens of nanometers. Until the late 1990s, this continuous size reduction brought great improvements to MOSFET device operation without any bad effects. Historically, the difficulties associated with decreasing the size of MOSFET were due to the limitations in the semiconductor device fabrication process. Smaller MOSFETs are desirable for three reasons.

- 1. Smaller MOSFETs allow more current density to pass.

- 2. Smaller MOSFETs have less power consumption.

- Smaller MOSFETs have reduced area, eventually reducing the overall cost for fabrication.

Hence, smaller Integrated Circuits (IC) allow more chips per wafer that reduce the price per chip.

#### **1.2.** Operational Problems with MOSFETS

The scaling of the size of the MOSFET has created a few operational problems that are discussed below.

## a. Subthreshold leakage

Due to the reduced MOSFET geometries, the voltage that is applied to the gate must also be reduced to maintain reliability. To maintain the same performance

as before, the corresponding threshold voltage of the MOSFET needs to be reduced too. That results in a weak-inversion layer, which keeps consuming the power as subthreshold leakage, even when the transistor is not conducting. Subthreshold leakage if not properly managed, can consume up to half of the total power consumed by the chip.

## b. Interconnect capacitance

With transistors becoming smaller and the chip densities getting higher, interconnect capacitance is becoming a large percentage of the total capacitance. That increased capacitance leads to increased delays and can at times also lower the performance of the device.

#### c. Heat production

The ever-increasing density of MOSFETs on an IC can create problems as a lot of heat is generated in a small area of the device that can impair circuit operation. Circuits cannot operate faster at higher temperatures, and have a reduction in their reliability and lifetime. Heat sinks and similar other cooling methods are needed to cool off these devices, in particular, microprocessors. The on-state resistance increases with temperature which aggravates the heat further and if this feedback loop is not controlled, extreme levels of heat can eventually result in total destruction of the device.

#### d. Gate oxide leakage

The gate oxide needs to be as thin as possible for the increased channel conductivity when the transistor is on. The same is needed to reduce the subthreshold leakage when the transistor is off. However, in the current device technologies, the gate oxides have a thickness of around 2 nm. This atomic level of thickness leads to the phenomenon of tunneling leakage between the gate and the channel, leading to an overall increased power consumption. Hi-k dielectric insulators

e.g. hafnium and zirconium oxides are currently being actively researched to reduce the gate leakage. Traditionally silicon dioxide has been used as the insulating material. Its barrier height is approximately 3 eV. However many of the alternative dielectrics have a significantly lower barrier height that negates the advantages of having a higher dielectric constant.

## e. Process variations

With the miniaturization of MOSFETS, the number of atoms per transistor is becoming fewer. Random process variations during device manufacture can affect heavily the transistor characteristics making them less than ideal. Such a variation can increase the difficulty in design processes.

## **1.3.** Alternative Device Technologies

As a result of all of the above mentioned problems with the conventional MOSFET designs, there came the need to find alternative device technologies. One of the technologies that has become the norm in the last couple of decades, or so, is the Silicon on Insulator (SOI) device and the Strained Silicon on  $Si_xGe_{1-x}$  substrate devices.

In the current work, we have examined the characteristics of strained Si and compared them with the unstrained Si and the results show that strained Si shows better mobility and higher peak velocity for given applied electric fields. Also we studied the impact of heat generation in the SOI technologies and compared different SOI materials and also looked at the effects of varying thickness of the buried oxide layer in the device.

5

#### CHAPTER 2

#### MODELING APPROACH

The aim of computational electronics is to develop simulation tools with enough sophistication to capture the essential physics of the devices while at the same time reducing the computational burden and thus decrease the time in which the results can be obtained. In an electronic device, transport equations govern the flow of charge while the fields drive the charges.

So, in order to completely specify the working operation of a device, it is needed to know the state of each carrier within the device which can be accomplished through the use of semi-classical transport model. Newtonian mechanics is one way of specifying the state of the carriers and according to the Langevin equation

$$\frac{d\mathbf{p}}{dt} = -e\mathbf{E} + R(\mathbf{r}, \mathbf{p}, t) \quad \text{and} \quad \mathbf{v}(t) = \frac{d\mathbf{r}}{dt}, \qquad (2.1)$$

where  $R(\mathbf{r}, \mathbf{p}, t)$  is a random force function that can arise due to scattering by imperfections in the system. Alternatively the probability of finding a carrier with a crystal momentum  $\mathbf{k}$  at time t and position  $\mathbf{r}$  is given by the distribution function f( $\mathbf{r}, \mathbf{k}, t$ ) which is obtained by solving the semi-classical Boltzmann Transport Equation (BTE) [3, 5, 6]. Some of the assumptions made in the modeling scheme are as below:

- Holes and electrons are independent particles.

- Particles may be scattered by impurities, phonons, etc. but they do not interact with each other.

- A set of Bloch functions describes the electronic structure of the system [7, 8].

• Also by definition, the number of electrons in a volume  $\Delta V$  centered relative to **r** with a distribution function *f* having wavevectors in the range of d<sup>3</sup>k relative to **k** is given by

$$2 \times \frac{\Delta V}{8\pi^3} f(\mathbf{r}, \mathbf{k}, t) d^3 k$$

(2.2)

Various moments of the distribution function give us the following

$$n(\mathbf{r},t) = \frac{1}{V} \sum_{k} f(\mathbf{r},\mathbf{k},t) , \qquad \text{particle density}$$

(2.3)

$$\mathbf{J}(\mathbf{r},t) = -\frac{e}{V} \sum_{k} \mathbf{v}(\mathbf{k}) f(\mathbf{r},\mathbf{k},t) \text{, current density}$$

(2.4)

$$W(\mathbf{r},t) = \frac{1}{V} \sum_{k} E(\mathbf{k}) f(\mathbf{r},\mathbf{k},t) , \text{ energy density}$$

(2.5)

When the device dimensions are scaled to 100 nm or below, velocity overshoot starts to dominate the overall device behavior. In such cases, the drift diffusion model, which is the basis for conventional transport in semiconductor devices, is no longer valid. Hydrodynamic models account for non-stationary effects and many of the commercially available software including Silvaco and Synopsys etc. deploy them already. However the hydrodynamic model breaks down as well for short dimensions.

## 2.1. Need for Monte Carlo Simulations

Velocity overshoot depends on the energy relaxation time. A standard way for calculating the energy relaxation times is to use bulk Monte Carlo simulations. However, the energy relaxation times of the device under consideration are material, geometry and doping dependent so that the determination of energy relaxation times in advance is not possible. Using the Monte Carlo method is the best choice in many cases as it may be shown that within semi-classical limits, the one-particle distribution function obtained from the random walk Monte Carlo technique satisfies the Boltzmann Transport Equation (BTE) for a homogeneous system in the long-time limit where BTE is an integral, differential, kinetic equation of motion for the probability distribution function for particles in the six-dimensional phase space of position and (crystal) momentum. In its most general form the BTE is given by:

$$\frac{\partial f(\mathbf{r},\mathbf{k},\mathbf{t})}{\partial t} + \frac{1}{h} \nabla_{\mathbf{k}} E(k) \cdot \nabla_{r} f(\mathbf{r},\mathbf{k},\mathbf{t}) + \frac{\mathbf{F}}{h} \cdot \nabla_{k} f(\mathbf{r},\mathbf{k},\mathbf{t}) = \frac{\partial f(\mathbf{r},\mathbf{k},\mathbf{t})}{\partial t} \bigg|_{coll}$$

(2.6)

where f(r, k, t) is the one-particle distribution function. The right-hand side is the rate of change of the distribution function due to randomizing collisions and is an integral over the in-scattering and the out-scattering terms in momentum space. The particle dynamics and scattering processes are treated quantum mechanically through the electronic band structure and the use of the time-dependent perturbation theory.

For non-degenerate semiconductors, the collision integral equals

$$\frac{\partial f(\mathbf{r}, \mathbf{k}, t)}{\partial t} \bigg|_{coll} = \sum_{\mathbf{k}'} \left[ f(\mathbf{r}, \mathbf{k}', t) S(\mathbf{k}', \mathbf{k}) - f(\mathbf{r}, \mathbf{k}, t) S(\mathbf{k}, \mathbf{k}') \right]$$

(2.7)

where the first term describes the scattering into a state **k** and the second one represents scattering out of a state **k**. The transition rates  $S(\mathbf{k}, \mathbf{k'})$  and  $S(\mathbf{k'}, \mathbf{k})$  for the scattering between states **k** and **k'**, are calculated using time-dependent perturbation theory, which in the long time limit is also called Fermi's Golden Rule and is given as

$$S(\mathbf{k},\mathbf{k}') = \frac{2\pi}{\hbar} \left| \left\langle \mathbf{k}' \right| H' \left| \mathbf{k} \right\rangle \right|^2 \delta \left( E_{k'} - E_k \mp \hbar \omega \right)$$

(2.8)

for scattering between some initial state **k** to some final state **k'**. Here  $|\mathbf{k}\rangle$  and  $|\mathbf{k'}\rangle$  are the initial and final states of the carriers (electron or hole) respectively,  $E_k$  and  $E_{k'}$  is the corresponding kinetic energy, and  $\hbar\omega$  is the phonon energy. The matrix element  $\langle \mathbf{k'} | H' | \mathbf{k} \rangle$  contains the momentum conservation, while  $\delta(E_{k'} - E_k \mp \hbar\omega)$  describes the conservation of energy during the scattering process, which is only valid in the long-time limit, and when the scattering events are infrequent. Note that the top sign is for absorption and the bottom sign is for the phonon emission process.

The total scattering rate out of the initial state  ${f k}$  is obtained by summing over all final states

$$W(k) = \frac{\Omega}{\left(2\pi\right)^3} \int_{0}^{2\pi} d\phi \int_{0}^{\pi} \sin\theta d\theta \int_{0}^{\infty} S(\mathbf{k}, \mathbf{k}') k'^2 dk'$$

(2.9)

where  $\Omega$  is the total volume of the crystal. The result given in (2.8) is used to calculate the scattering rates due to vibrations of the lattice that dominate carrier transport in Si at room temperature and high electric fields.

## 2.2. Scattering mechanisms

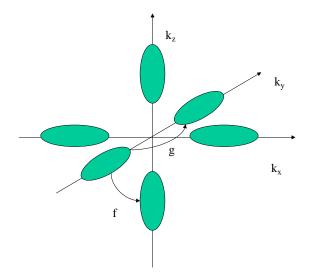

Some of the scattering mechanisms included in this work are acoustic and intervalley phonon scattering which include f and g type phonons.

### a. Acoustic Phonon Scattering (non-parabolic bands)

The total scattering rate out of state  $\mathbf{k}$  (in the elastic and equipartition approximation) equals to [9]

$$W(k) = \frac{2\pi \Xi_d^2 k_B T_L}{\hbar c_l} \cdot \frac{(2m_d^2)^{3/2} \sqrt{E_k (1 + \alpha E_k)}}{4\pi^2 \hbar^3} (1 + 2\alpha E_k)$$

(2.10)

where  $\boldsymbol{\alpha}$  is the non-parabolicity factor for silicon

$$\alpha = 0.5 \text{ eV}^{-1}$$

(2.11)

where  $m_l$  and  $m_t$  are the longitudinal and the transverse effective mass, respectively. For silicon,  $m_l = 0.916m_0$  and  $m_t = 0.196m_0$  where  $m_0$  is the rest mass of an electron. The density-of-states effective mass  $m_d^*$  is defined as

$$m_d^* = (m_l m_t^2)^{\frac{1}{3}}$$

(2.12)

In Eq. (2.10)  $T_L$  is the lattice temperature and  $c_L$  is the material elastic constant and  $\Xi_d$  is the deformation potential constant which for Si is 9.0 eV.

## b. Non-polar optical phonon scattering

This describes the intervalley transitions in Si, and is given by [9]

$$S(\mathbf{k},\mathbf{k'}) = \frac{\pi D_{ij}^2 Z_j}{\rho \omega_{ij} \Omega} \left[ n(\omega_{ij}) + \frac{1}{2} \mp \frac{1}{2} \right] \delta(E_{k'} - E_k \mp \hbar \omega_{ij} + \Delta E_{ji}), \qquad (2.13)$$

where  $D_{ij}$  is the intervalley deformation potential,  $Z_j$  is the total number of available final valleys for the carrier to scatter into,  $\hbar \omega_{ij}$  is the energy of the intervalley optical phonons involved in the scattering process,  $\Delta E_{ji}$  is the potential energy difference between the bottom of valley j and the bottom of valley i. Substituting equation (2.13) into (2.8) gives

$$W(k) = \frac{\pi D_{ij}^2 Z_j}{\rho \omega_{ij}} \Big[ n(\omega_{ij}) + \frac{1}{2} \mp \frac{1}{2} \Big] N(E_k \pm \hbar \omega_{ij} - \Delta E_{ji}) , \qquad (2.14)$$

The top sign in (2.14) corresponds to phonon absorption process and the bottom sign to the phonon emission process. The phonon occupancy factor is described with the Bose-Einstein distribution function given by

$$n(\omega_{ij}) = \frac{1}{e^{\hbar \omega_{ij} / k_B T} - 1}$$

(2.15)

For inter-valley scattering, if an electron residing in a valley on the negative y-axis is scattered into a valley on the same axis, there is only one choice for the final valley, i.e. the valley on the positive y-axis. If the phonon is scattered into a valley on a different axis, there are four choices for the final valleys; two valleys on the x-axis and two valleys on the z-axis. The former is called g-process and  $Z_j$  is one. The latter is called f-process and  $Z_j$  is four. Schematic description of these is given in figure 1.

Figure 2. Constant energy surface for silicon - "f-type" and "g-type" processes

## c. Coulomb scattering

For Coulomb scattering, the total scattering rate is given by [9]

$$W(k) = \frac{\sqrt{2}n_i Z^2 e^4}{\varepsilon_{sc}^2 \sqrt{m_a^* E_\beta}} \sqrt{E(1+\alpha E)} \frac{1+2\alpha E}{1+4(E(1+\alpha E)/E_\beta)}$$

(2.16)

where the parameter  $E_{\beta}$  is given as

$$E_{\beta} = \frac{\hbar^2 q_D^2}{2m_d^*}$$

(2.17)

where  $q_D = 1/L_D$  such that L<sub>D</sub> is the Debye length and

$$q = |k - k'| = k^{2} + k'^{2} - 2kk'\cos\theta = 2k^{2}(1 - \cos\theta)$$

(2.18)

## 2.3. Bulk Monte Carlo method

A single particle Monte Carlo method is suitable for analyzing the steady-state carrier transport under uniform electric field, whereas the Ensemble Monte Carlo (EMC) method is more widely used for non-stationary transport and transient behaviors that occur under non-uniform electric fields. The EMC algorithm consists of

- 1. Generating random free flight times for each particle

- 2. Choosing the type of scattering occurring at the end of the free flight

- 3. Changing the final energy and momentum of the particle after scattering

- 4. Repeating the procedure for the next free flight

Sampling the motion of particles at various times during the simulation allows for the statistical estimation of physically interesting quantities such as

- 1. A single particle distribution function

- 2. The average drift velocity in the presence of an applied electric field

- 3. The average energy of the particles, *etc*.

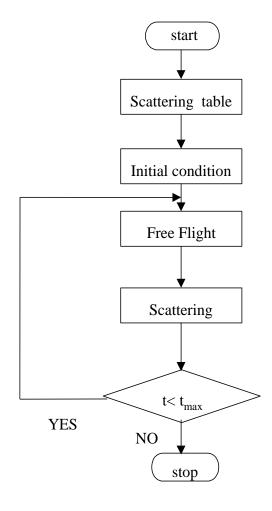

This random walk approach breaks down when quantum mechanical effects become pronounced, and one cannot unambiguously describe the instantaneous position and momentum of a particle. The flowchart shown in figure 3 explains the parts of Ensemble Monte Carlo simulation process.

Figure 3. Flowchart for description of Ensemble Monte Carlo Algorithm [9]

At the beginning of the simulation, the carriers are initialized with random energy, azimuthal angle and polar angles as

$$E = -\frac{3}{2}k_{B}T\ln(rand)$$

$$\varphi = 2\pi \cdot rand$$

$$(2.19)$$

$$\cos\theta = 1 - 2 \cdot rand$$

The x, y and z component of the momentum vector are defined as

$$k_{x} = k \sin \theta \cos \phi$$

$$k_{y} = k \sin \theta \sin \phi$$

$$k_{z} = k \cos \theta$$

(2.20)

The scattering rates for the various scattering mechanisms (acoustic and intervalley scattering in this case) are calculated for different carrier energies. These scattering rates are then tabulated as well as accumulated to form a cumulative scattering table. The energy step in the actual implementation is taken to be 1.0 meV. A number  $\Gamma_0$ , larger than or equal to the maximum accumulated scattering rate is used to normalize the scattering table so that the maximum cumulative scattering rate is unity. A self-scattering mechanism is introduced to achieve constant total scattering rate, which simplifies the free-flight calculation.

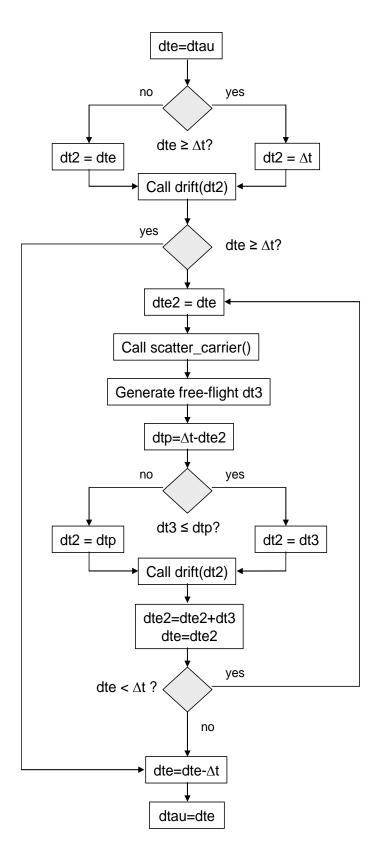

A random number is used for each electron to determine its free-flight time using

$$\tau = -\frac{1}{\Gamma_0} \ln(rand) \tag{2.21}$$

Figure 4. Flowchart for the Free flight-Scatter routine [9]

The free flight and scatter routine is explained in detail by the flow chart in figure 4. An electron is accelerated by the applied electric field during the free flight. If the carrier free-flight time is larger than the observation time, carriers are accelerated only up to the observation time and then stopped to allow for calculation of the ensemble averaged quantities. After the calculation of average drift velocity and average electron energy, the carriers are allowed to continue their next free-flight.

## 2.4 Simulation Results

In the actual implementation, 10000 electrons are traced for around 4 ps, with a time step  $\Delta t$  of 10fs. The average drift velocity and average kinetic energy are plotted against time to obtain the transient velocity and energy variation. The applied electric field for the current set of simulations varies between 0.15 KV/cm all the way up to 500 KV/cm. The total simulation time is usually taken to be long enough for steady-state conditions to be established. Some of the representative plots for different simulations are displayed here. The first set of plots below shows the Scattering rates, both in the linear scale as well as the log scale.

Figure 5. Scattering rates in linear (left) and log (right) scale

The second set below shows the cumulative scattering table/ rates, again, in normal and log scales.

Figure 6. Cumulative Scattering rates in linear (left) and log (right) scale

The next couple of plots show the initial wavevector distribution in the Zdirection and the Energy distribution of the carriers for an applied field value of 100 KV/cm. The X and Y valley distributions resemble closely to this distribution and hence are not included

Figure 7. Initial Wavevector and Energy Distribution.

One point to be noted here is that the z-direction (the direction of applied field) shows the displaced Maxwellian distribution as can be seen in the figure below.

Figure 8. Final Wavevector and Energy Distribution (for Field=100 KV/cm)

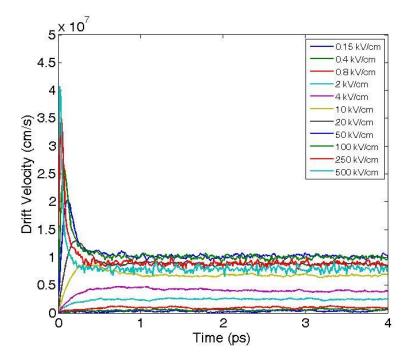

From the results shown in figure 9, it can be seen that that for electric fields lower than 50 KV/cm, the mean drift velocity along the electric field direction increases gradually towards its steady-state value. For electric field higher than 50 KV/cm, the mean drift velocity increases rapidly, overshoots, and then decreases down towards the steady-state value. An equivalent behavior is also observed in the Energy evolution over time in figure 10. The reason for this behavior is that the energy relaxation time in silicon is larger than the momentum relaxation time.

Figure 9. Time evolution of Drift Velocity

Figure 10. Time evolution of Energy

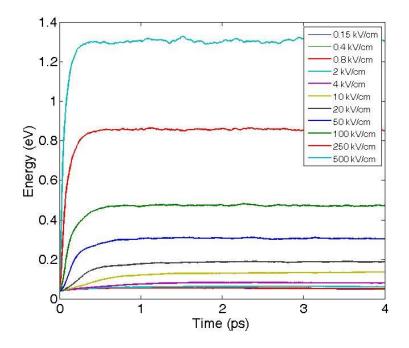

Figure 11 illustrates the steady-state velocity-field characteristics for Silicon. This plot is obtained in the following manner. First, the time evolution of the drift velocity is evaluated for a given value of the electric field. The steady-state drift velocity is then calculated by truncating the overshoot portion of velocity and averaging over the saturated value. The applied electric field is varied from 0.15 KV/cm to 500 KV/cm. The simulation results are compared with experimental data from Canali and the two show very close agreement [10]. It can be seen from the simulation results that the mean drift velocity increases with applied electric field and then starts to saturate for fields larger than 2 MV/m.

Figure 11. Velocity saturation with applied electric field

#### CHAPTER 3

#### STRAINED SILICON DEVICE

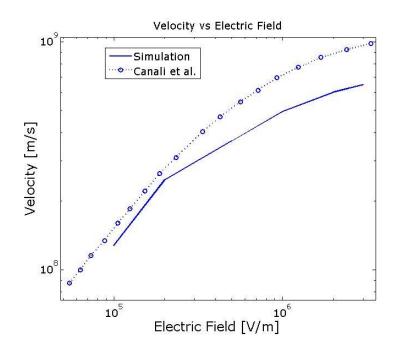

Strained silicon has been known to be a possibility for improvement in the quest for faster and smaller electronic devices [11]. Strain is described by the displacement of atoms from their regular positions in bulk silicon. Strain can be either compressive or tensile. Hooke's law defines strain as stress. There can be many ways for stress to be induced in Silicon. Some are side effects of different processing steps such as doping, etching, oxidation and most importantly thermal steps. The amount of stress produced inside a Silicon lattice is inversely proportional to the distance inside the structure from the source of the stress.

There are several ways in which stress can be artificially induced in Si. One of the most common methods is to grow silicon on a layer of pre-deposited Si<sub>1-x</sub>Ge<sub>x</sub> where x represents the molar ratio of Ge in the SiGe alloy. Si has a lattice constant of 5.43Å while lattice constant for Ge is 5.658Å. There is a lattice mismatch of only about 4.2% between them and hence can be combined together to form a SiGe alloy. The lattice constant of this SiGe alloy lies between that of Ge and Si. Now if a layer of Si is deposited on top of this SiGe alloy, the Si layer on top is put under strain. The amount of strain that the Si layer on top is put under is directly proportional to the amount of Ge in the SiGe layer below. In this case it is a tensile stress in 2 dimensions.

21

Figure 12. Tensile Strain in top Si layer when combined with SiGe layer on bottom

## 3.1 Difference between un-strained and strained Silicon

The band structure of strained silicon, as a result of the induced strain, has two key differences when compared with the bulk silicon band structure.

1. The four minima in the conduction band are raised in directions parallel to the plane of strain. This leads to an increase in the population of the two minima that are vertical to the plane of strain and the carrier movement. The overall effect is lowering of effective masses and higher mobility for the electrons [12].

2. The second major difference is the splitting of the light hole and heavy hole bands leading to an increase in the hole mobility. Higher mobility means faster carrier transport, therefore, an increase in the device current is possible.

With the advancement in device fabrication techniques, it is possible to adjust the strain by varying the concentration of Ge and Si in the Si<sub>1-x</sub>Ge<sub>x</sub> alloy to meet specific needs and performance of devices. In certain cases, device performance can be increased by up to 100% while in others power consumption can be drastically reduced [13]. The splitting energy between the lowered and raised valleys, is empirically represented by [12]

$$\Delta E = 0.67x \tag{3.1}$$

where x is the fraction of Ge in the Si<sub>1-x</sub>Ge<sub>x</sub> substrate. For an equal concentration of Si and Ge in the alloy (x=0.5), the valley splitting energy is above 0.3eV which, even at the normal room temperature, is more than ten times than the thermal energy (0.0268 eV). For the particular case of this thesis, the splitting energy was taken to be 0.2 eV. This wide splitting energy ensures that the intervalley scattering is reduced to a minimum and the carriers are confined, naturally, to the lower energy valley. As already mentioned, electrons confined in the lower valley show a smaller transverse mass in the transport direction parallel to the (100) direction. This is considered to be the main mechanism for the high mobility and the high transconductance in the devices.

## 3.2. Modeling Approach

For this thesis, we adopted an Ensemble Monte Carlo technique such that strain is included only in the band structure through the valley splitting energy  $\Delta E$ . It was assumed that the effective masses of electrons were unchanged and that the coupling constants for the scattering modes were also the same as those for regular Silicon [14].

The masses have the longitudinal and transverse orientations and they were implemented using the Herring-Vogt transformation in a three-valley model [3]: lowered valley pair 1 was considered to be in the (010) direction, raised valley pairs 2 and 3 were in the (100) and (001) directions while the electric field was applied in the (001) direction.

## 3.3. Simulation Results

Figure 13. Top Panel: Scattering rates in linear (left) and log (right) scale

Bottom Panel: Normalized Scattering rates in linear (left) and log (right) scale

All of the scattering mechanisms that were used for the un-strained Silicon were also used for the strained Silicon case as well. However, one major difference is that instead of having single scattering table, we have three scattering tables, one for each valley pair. As can be seen in figure 13, there are eight scattering mechanisms per valley pair, as in the case of f and g intervalley phonon scattering mechanisms,

there are possibly two different valley pairs for the carriers to scatter to.

Figure 14. Initial wavevector and energy distribution.

Figure 15. Final wavevector and energy distribution (for Field=100 KV/cm)

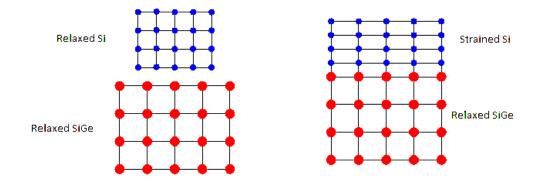

Figure 16. Time evolution of Drift Velocity

Figure 17. Time evolution of Energy

The results were obtained at T=300K with the applied fields ranging from 0.15KV/cm to 500KV/cm. Under the influence of the applied fields that are larger than 20 KV/cm, all of the curves approach one another and tend to have a similar

saturation velocity i.e.  $1.0 \times 10^7$  cm/, although strained Si shows a higher value all throughout the simulation regime.

Figure 18. Velocity-field characteristics for strained and un-strained Silicon

A comparison of peak overshoot velocities also proves the same results. At very low applied electric fields, velocity overshoot effect is not very effective and we do not see a difference in the peak overshoot velocities. As the applied field increases, we see that the peak overshoot velocity increases for the case of strained silicon.

Figure 19. Peak overshoot velocity for strained and unstrained Si for different fields

The mobility calculations were done with the change in the drift velocity for a given change in electric fields according to the relation

$$\mu = dv/dE \tag{3.1}$$

We see that as the fields are increased, there is sharp decrease in the mobility due to the fact that there is not much change in the average drift velocity as given in Figure 18. However one can clearly see that the mobility for the case of strained silicon is nearly two times better than that for the unstrained silicon case.

Figure 20. Mobility in strained and unstrained Silicon

The energy field characteristics were also determined and they were found to be in line with the results from [15].

Figure 21. Energy-field characteristics for strained and un-strained Silicon

It is concluded that the strain at the hetero-interface removes the degeneracy of the six-fold valleys in unstrained Si and, as a result, the electrons prefer to stay in the lower valley which is normal to the interface, thereby reducing inter-valley scattering. The transport in the strained device is characterized by the electrons having a smaller transverse mass. The overall result is improved transport characteristics (mobility) which is very desirable in current day electronics.

#### CHAPTER 4

# SOI DEVICES AND THE ROLE OF SELF HEATING

The conventional bulk silicon technology suffers from problems such as parasitic capacitances, poor subthreshold slope, presence of latch-up, and is prone to radiation effects. [16]. Operating these devices at higher speeds is not possible.

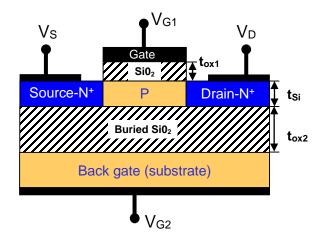

As a result of the continued device scaling to nanometers regime, there was a need to develop an alternative technology that could address these problems with the conventional CMOS technology while scaling down in dimensions. In that quest, Silicon-on-Insulator (SOI) technology proved itself to be a viable candidate [17]. SOI metal-oxide-silicon field-effect transistor (MOSFET) devices employ a thin buried insulating layer, usually made out of an insulating material to isolate the devices electrically from the bulk semiconductor. The preferred insulator at the advent of the SOI technology was silicon dioxide (SiO<sub>2</sub>). However, lately, some alternatives like Diamond, AIN and Sapphire have also been considered to be used as insulating materials [18]. Figure 22 below gives an overview of the structure for a SOI device [9].

Figure 22. Structure of a reference SOI NMOS device

There are many different variations possible in the structure of the device. The insulating layer increases the device performance by reducing overall junction capacitance since the junction is electrically isolated from the bulk. This junction capacitance reduction also reduces overall power consumption.

As can be seen in the figure, the buried dielectric layer insulates the MOSFET from the bulk not only electrically but, due to the poor heat conductance of the SiO<sub>2</sub>, thermally as well [19]. As a result the heat generated in SOI devices can cause a larger temperature rise than in bulk devices. This self-heating effect can be critical to device function as it can lead to a reduced carrier mobility. Correspondingly, decrease in speed and transconductance is an inherent issue for this technology. As part of this thesis we have studied the effect of different insulating materials on the output characteristics of the devices, both electrically and thermally. For an nchannel SOI device, there are three modes of operation:

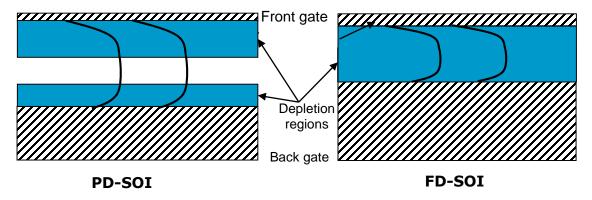

- Thick-film (Partially-depleted) PD-SOI devices: x<sub>dmax</sub> < t<sub>si</sub>

- Thin-film (fully-depleted) FD-SOI devices: x<sub>dmax</sub> > t<sub>Si</sub>

- medium film SOI devices: x<sub>dmax</sub> < t<sub>Si</sub> < 2x<sub>dmax</sub>

Figure 23 below gives a self-explanatory visual expression to the meaning of fully depleted and partially depleted devices.

Figure 23. Depletion region of PD (left) and FD (right) SOI devices [9]

### 4.1. Simulation Scheme

The current device simulator used in this work for the electrons involves solving the Boltzmann's Transport Equation coupled with Poisson Solver. For phonons [20], the acoustic and optical phonon energy balance equations are solved simultaneously while taking into account the coupling of the two subsystems. In other words, from the general system of Boltzmann transport equations for electrons and phonons, as depicted below in Eq. (4.1) and (4.2), we arrive at a simplified system that solves the electron Boltzmann transport equation (using the Monte Carlo method) and energy balance equations for the optical and the acoustic phonon bath (by taking moments of the phonon Boltzmann transport equation).

The general Boltzmann transport equations for electrons and phonons are of the form [9]:

$$\left(\frac{\partial}{\partial t} + v_e(k) \cdot \nabla_r + \frac{e}{h} E(r) \cdot \nabla_k\right) f = \sum_q \left\{ W_{e,q}^{k+q \to k} + W_{a,-q}^{k+q \to k} - W_{e,-q}^{k+q \to k} - W_{a,q}^{k+q \to k} \right\}$$

(4.1)

$$\left(\frac{\partial}{\partial t} + \nu_{p}(\mathbf{q}) \cdot \nabla_{r}\right) g = \sum_{k} \left\{ W_{e,q}^{k+q \to k} - W_{a,q}^{k+q \to k} \right\} + \left(\frac{\partial g}{\partial t}\right)_{p-p}$$

(4.2)

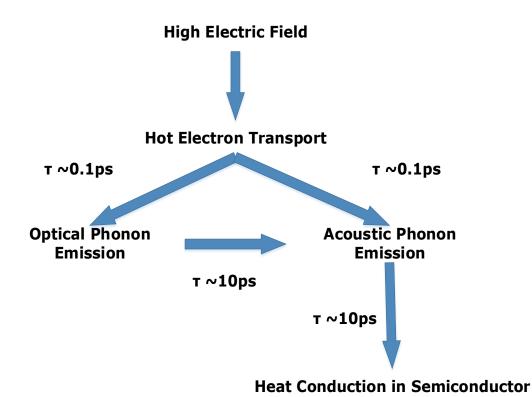

In the equation set above,  $f(\mathbf{r}, \mathbf{k}, \mathbf{t})$  and  $g(\mathbf{r}, \mathbf{k}, \mathbf{t})$  are the distribution functions for electrons and phonons, respectively.  $W_{e,q}^{k+q\to k}$  is the probability for an electron transition from k+q to k due to the emission of phonon q. Similarly  $W_{a,q}^{k+q\to k}$  refers to the absorption process. This is a complex set of equations as it involves different time scales as the velocity of electrons is two orders of magnitude greater than the velocity of phonons. As a result, heat transfer in the device is a much slower process than the electrical transport inside the device. The need for separate consideration of the acoustic and phonon system comes from the very nature of the heat transfer phenomenon inside the device as depicted in figure 24.

**Figure 24.** Path between energy-carrying particles in a semiconductor device along with the corresponding scattering time constants

It is clear from the figure above that the heat conduction depends on the transport of energy through electrons giving off their energy to both the acoustic and optical phonons combined. During the system evolution, the electrons gain energy from the electrical field E in the device. They give off their energy to optical phonons  $(T_{LO})$  which pass on their excess energy to the lattice  $(T_{LA})$ . The transfer of energy between electrons and phonons takes place on a timescale on the order of 0.1 ps.

The energy balance equations of the optical and acoustic phonon energy transfer are of the form [21]:

$$C_{LO} \frac{\partial T_{LO}}{\partial t} = \frac{3nk_B}{2} \left( \frac{T_e - T_{LO}}{\tau_{e-LO}} \right) + \frac{nm^* v_d^2}{2\tau_{e-LO}} - C_{LO} \left( \frac{T_{LO} - T_A}{\tau_{LO-A}} \right)$$

(4.3)

$$C_{A} \frac{\partial T_{A}}{\partial t} = \nabla (k_{A} \nabla T_{A}) + C_{LO} \left( \frac{T_{LO} - T_{A}}{\tau_{LO-A}} \right) + \frac{3nk_{B}}{2} \left( \frac{T_{e} - T_{L}}{\tau_{e-L}} \right)$$

(4.4)

The first two terms in (4.3) on the RHS represent the energy gained from the electrons whereas the last term represents the energy lost to the acoustic phonons. The first term in (4.4) on the RHS accounts for the heat diffusion.  $C_{LO}$  and  $C_A$  are the heat capacities of the optical and acoustic phonons and  $k_A$  is the thermal conductivity. The electron temperature, represented by  $T_e$  is obtained from the EMC simulation.

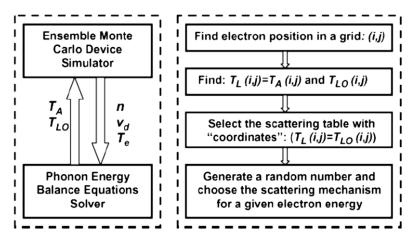

Figure 25 gives an overview of the transfer of variables between the two kernels [9]. It also illustrates a very important concept of the creation of temperature dependent scattering tables. An energy-dependent scattering table is created for each combination of optical and acoustic phonon temperatures. This involves additional steps in the MC phase since random selection of a scattering mechanism for a given electron energy depends on finding the corresponding scattering table.

34

**Figure 25.** Left: Exchange of variables between EMC and Energy Balance kernels. Right: Choice of the proper scattering tables

For the solution of this BTE-Poisson-Thermal self-consistent problem, Gummel method was implemented [22].

# 4.2. Simulated Device

The structure of the n-channel FD SOI MOSEFT device observed in this work had 25 nm channel length, source/drain doping of  $1 \times 10^{19}$  cm<sup>-3</sup> with a channel doping of  $1 \times 10^{18}$ . Silicon thin film width was 10nm, gate oxide width was 2nm. The insulating materials thicknesses were varied as 30nm, 60nm and 90nm. The applied biases were V<sub>GS</sub> = V<sub>DS</sub> = 1.2 V.

In our simulation experiments, different buried oxide (BOX) materials and different thicknesses of the BOX were being considered to get optimal choice of the BOX for superior device performance. The materials considered for the BOX were: SiO, Diamond, AIN and Saphire (Al2O3). Their relative dielectric constants and thermal conductivities of the target materials are summarized in the table 4.1.

| Material        | Relative Dielectric<br>Constant | Thermal Conductivity<br>(W/mK) |  |

|-----------------|---------------------------------|--------------------------------|--|

| Silicon Dioxide | 3.9                             | 1.38                           |  |

| AIN             | 9.14                            | 272                            |  |

| Diamond         | 5.68                            | 2000                           |  |

| Sapphire        | 11.5                            | 23.1                           |  |

**Table 4.1** Properties of the BOX Materials Considered

# 4.3. Simulation Results

To test the overall convergence of the coupled EMC and thermal codes, we observed the variations in the output drain current by changing the number of Gummel iterations for a given bias conditions. The solver was run for two different numbers of Gummel iterations: 1 and 10, to see the effect of convergence on the output characteristics. Some of the characteristic representative results of these simulations are given here for Diamond as an insulating material for 10 Gummel cycles.

The conduction band edge is shown in figure 26. One can clearly see the position of the source, gate and drain contacts of the simulated structure. The electric field profile in the y-direction (depth of the device) is shown in Figure 27. Another standard characteristic of Monte Carlo simulations are the average electron velocity along the channel (figure 28) and the average electron energy (figure 29). We see that the maximum average electron energy is below 0.7 eV which justifies the use of the non-parabolic band model. This point is clearly explained by Fischetti

and co-workers [23], who did a comparison of the full-band density of states and the non-parabolic approximation for the density of states.

Figure 26. Potential Profile in the device

Figure 27. Electric Field Y component profile in the device

Figure 28. Electron Velocity X Component in the device

Figure 29. Electron Energy variation in the device

The electron drift energy and the electron drift velocity are shown in figures 30 and 31, respectively. The values obtained for the drift energy suggest that heated Maxwellian is a good approximation for the distribution function and the concept of temperature is a viable choice, which, in turn, justifies the solution of the energy balance equations for the acoustic and longitudinal optical phonon bath.

It is important to point out that heat is the total energy of molecular motion in a substance while temperature is a measure of the average energy of molecular motion in a substance. Heat energy depends on the speed of the particles, the number of particles (the size or mass), and the type of particles in an object.

Temperature does not depend on the size or type of object. For example, the temperature of a small cup of water might be the same as the temperature of a large tub of water, but the tub of water has more heat because it has more water and thus more total thermal energy. It is heat that will increase or decrease the temperature.

If we add heat, the temperature will become higher. If we remove heat, the temperature will become lower. Higher temperatures mean that the molecules are moving, vibrating and rotating with more energy. If we take two objects which have the same temperature and bring them into contact, there will be no overall transfer of energy between them because the average energies of the particles in each object are the same. But if the temperature of one object is higher than that of the other object, there will be a transfer of energy from the hotter to the colder object until both objects reach the same temperature. Temperature is not energy, but a measure of it. Heat is energy.

39

Figure 30. Electron drift energy profile in the device

Figure 31. Electron drift velocity profile in the device

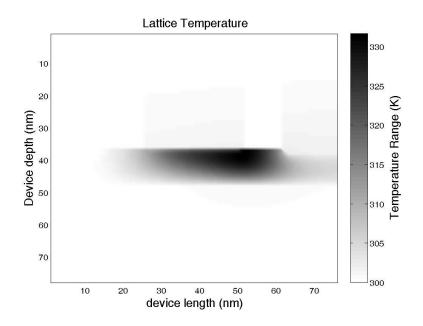

The electron temperature plot shown in figure 32 is in agreement with the average electron energy plot shown previously in figure 29. Clearly, we have the hottest electrons at the drain end of the channel that give energy to optical phonons. Therefore, where the electron temperature is the highest, the optical phonon temperature is the highest as well (see figure 33). In figure 34 we show the acoustic/lattice temperature. We see from the results shown that the lattice temperature is lower than the optical phonon temperature. Since the box is diamond, we see that peak lattice temperature is smaller than 330 K. This is not the case when SiO<sub>2</sub> is used as a box. Lattice temperatures in excess of 400K are reached when SiO<sub>2</sub> is used as a BOX material [24].

Figure 32. Electron temperature profile in the device

Figure 33. Optical phonon temperature profile in the device

Figure 34. Lattice temperature profile in the device

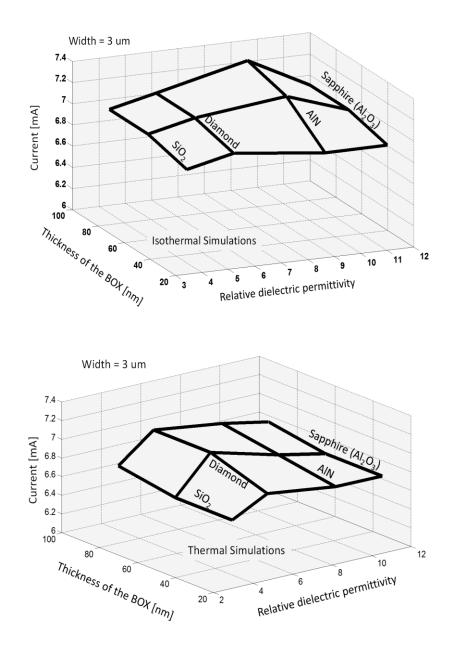

Next, we perform design of experiments for the materials from Table 4.1. We vary the BOX thickness and examine which material has the best performance. The values for the current, for a device with 3 um width are summarized in Table 4.2.

| Material | BOX Width (nm) | Gummel Cycles | Current (mA) |

|----------|----------------|---------------|--------------|

| AIN      | 30             | 1             | 6.9          |

|          | 30             | 10            | 6.7          |

|          | 60             | 1             | 7.2          |

|          | 60             | 10            | 6.8          |

|          | 90             | 1             | 7.3          |

|          | 90             | 10            | 6.9          |

| SiO2     | 30             | 1             | 6.9          |

|          | 30             | 10            | 6.6          |

|          | 60             | 1             | 7.0          |

|          | 60             | 10            | 6.6          |

|          | 90             | 1             | 7.0          |

|          | 90             | 10            | 6.7          |

| Sapphire | 30             | 1             | 6.9          |

|          | 30             | 10            | 6.7          |

|          | 60             | 1             | 7.0          |

|          | 60             | 10            | 6.7          |

|          | 90             | 1             | 7.0          |

|          | 90             | 10            | 6.8          |

| Diamond  | 30             | 1             | 7.0          |

|          | 30             | 10            | 6.8          |

|          | 60             | 1             | 7.1          |

|          | 60             | 10            | 7.0          |

|          | 90             | 1             | 7.1          |

|          | 90             | 10            | 7.0          |

Table 4.2 Design of experiments results

In figure 35 we graphically illustrate the results from Table 4.2. It is more evident from these results that when only the isothermal situation is considered, AIN is the material of choice for the BOX. However, when thermal effects are accounted for then diamond wins as a material of choice.

Figure 35. (Top panel) Isothermal simulations. (Bottom panel) Thermal simulations.

#### CHAPTER 5

### CONCLUSIONS AND FUTURE WORK

The ultimate goal of this work is to develop a simulator that will be able to simulate fully-depleted SOI devices and strained Si nMOSFETs. At this point the following parts of our final product have been developed:

- Bulk Monte Carlo for Si and strained-Si

- Simulation of different BOX materials using ASU's particle-based device simulator

- A particle-based device simulator is almost completed in a MATLAB environment

The results for the drift velocity for bulk silicon are in agreement with experimental data [9]. The results for strained Si are in agreement with the theoretical calculations from Ref. [15].

With regard to the particle-based simulations, the designs of experiment results clearly illustrate that aluminum nitride has preferable isothermal characteristics, but when thermal simulations are performed, diamond comes about as the best choice. Further work needs to be done in this area in terms of calculation of equivalent electrical and thermal circuit models to quantitatively explain the observed trends.

In summary, the work to be completed consists of extension of the bulk Si Monte Carlo device simulator so that the Monte Carlo kernel can model Silicon, strained-Si and SiGe random alloy. This will allow us to simulate strained Si devices.

# REFERENCES

[1]. Arora, Vijay K., "Failure of Ohm's Law: Its Implications on the Design of Nanoelectronic Devices and Circuits," Microelectronics, 2006 25th International Conference on, vol. 15, no. 22, pp.15, 22, 2006.

[2]. Schockley, W. 1951, Bell Syst. Tech. J. 30, 990.

[3]. C. Jacoboni and L. Reggiani, "The Monte Carlo method for the solution of charge transport in semiconductors with applications to covalent materials", Rev. Mod. Phys., Vol. 55, pp. 645–705, 1983.

[4]. Moore G.E, Electronics, Volume 38, Number 8, April 19, 1965.

[5]. P.J. Price, "Monte Carlo calculation of electron transport in solids," Semiconductors and Semimetals, Vol. 14, pp. 249-334, 1979.

[6]. C. Jacoboni and P. Lugli, "The Monte Carlo Method for Semiconductor Device Simulation", Springer-Verlag, Wien New York.

[7] C. Kittel, Introduction to Solid State Physics 6th edition, Wiley, New York, 1986.

[8] N. W. Aschroft and N. D. Mermin, Solid State Physics, Saunders College Publishing, 1976.

[9] D. Vasileska, S.M. Goodnick; G. Klimeck, 'Computational Electronics: Semiclassical and Quantum Device Modeling and Simulation', CRC Press, June 2, 2010.

[10] C. Canali, G. Ottaviani, and A. Alberigi-Quaranta, J. Phys. Chem. Solids, Vol. 32, 1707, 1971.

[11] Fischetti M V, Laux S E., "Band structure, deformation potentials and carrier mobility in strained Si, Ge and SiGe alloys", J. Appl. Phys., 80(4): 2234–2252, 1996

[12] G. Abstreiter, H. Brugger, T. Wolf, H. Jorke, and H. J. Herog, Phys. Rev. Lett., 54, 2441, 1985.

[13] C. Smith, Piezoresistance Effect in Germanium and Silicon, Phys. Rev., vol. 94, no. 1, pages 42-49, 1954.

[14] M. M. Rieger, Diploma Thesis (Prof. Vogl), Technical University Munich, 1991 (unpublished).

[15] H. Miyata, Toshishige Yamada, and D. K. Ferry, "Electron transport properties of a strained Si layer on a relaxed Si1–xGex substrate by Monte Carlo simulation", Appl. Phys. Lett. 62, 2661, 1993.

[16] R. Chau, B. Doyle, M. Doczy, S. Datta, S. Hareland, B. Jin, J. Kavalieros, and M. Metz, "Silicon nano-transistors and breaking the 10 nm physical gate length barrier," in Proc. Device Res. Conf., Jun. 2003, pp. 123–126.

[17] http://www-03.ibm.com/press/us/en/pressrelease/2521.wss

[18] Colinge, Jean-Pierre (1991). Silicon-on-Insulator Technology: Materials to VLSI. Berlin: Springer Verlag. ISBN 978-0-7923-9150-0.

[19] T. Numata and S. Takagi, "Device design for subthreshold slope and threshold voltage control in sub-100-nm fully depleted SOI MOSFETs," IEEE Trans. Electron Devices, vol. 51, no. 12, pp. 2161–2167, Dec. 2004.

[20] Raleva, K.; Vasileska, D.; Goodnick, S.M.; Nedjalkov, M., "Modeling Thermal Effects in Nanodevices," Electron Devices, IEEE Transactions on, vol.55, no.6, pp.1306, 1316, June 2008

[21] J. Lai and A. Majumder, "Concurrent thermal and electrical modeling of submicrometer silicon devices," J. Appl. Phys., vol. 79, no. 9, pp. 7353–7361, May 1996.

[22] H. K. Gummel, "A self-consistent iterative scheme for one-dimensional steady state transistor calculations," IEEE, Trans. Electron Devices, vol. ED-11, pp. 455-465, 1964.

[23] M. V. Fischetti and S. E. Laux, "Monte Carlo Analysis of Electron Transport in Small Semiconductor Devices Including Band-Structure and Space-Charge Effects", Phys. Rev. B 38, 9721-9745, 1988.

[24] Katerina Raleva, PhD Thesis, Faculty of Electrical Engineering and Information Technologies, University "Cyril and Methodius", Skopje, Republic of Macedonia