A Structured Design Methodology for High Performance VLSI Arrays

by

Satendra Maurya

## A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved April 2012 by the Graduate Supervisory Committee:

Lawrence Clark, Chair Keith Holbert Sarma Vrudhula David Allee

## ARIZONA STATE UNIVERSITY

May 2012

#### ABSTRACT

The geometric growth in the integrated circuit technology due to transistor scaling also with system-on-chip design strategy, the complexity of the integrated circuit has increased manifold. Short time to market with high reliability and performance is one of the most competitive challenges. Both custom and ASIC design methodologies have evolved over the time to cope with this but the high manual labor in custom and statistic design in ASIC are still causes of concern.

This work proposes a new circuit design strategy that focuses mostly on arrayed structures like TLB, RF, Cache, IPCAM etc. that reduces the manual effort to a great extent and also makes the design regular, repetitive still achieving high performance. The method proposes making the complete design custom schematic but using the standard cells. This requires adding some custom cells to the already exhaustive library to optimize the design for performance. Once schematic is finalized, the designer places these standard cells in a spreadsheet, placing closely the cells in the critical paths. A Perl script then generates Cadence Encounter compatible placement file. The design is then routed in Encounter. Since designer is the best judge of the circuit architecture, placement by the designer will allow achieve most optimal design.

Several designs like IPCAM, issue logic, TLB, RF and Cache designs were carried out and the performance were compared against the fully custom and ASIC flow. The TLB, RF and Cache were the part of the HEMES microprocessor.

i

## DEDICATION

Dedicated to my parents Shri Mahendra Kumar Maurya and Smt. Vinod Kumari

#### ACKNOWLEDGMENTS

First of all, I would like to thank my parents and family for the support they have given throughout my studies. They have stood by me through the ups and downs of my graduate life and I am really grateful for that.

I am deeply indebted to my advisor Dr. Lawrence Clark, for the guidance and support that he has given me throughout my masters. Rarely have I walked into Dr. Clark's office with a problem and walked out without a solution. He has been a tremendous source of counseling and inspiration for me. I truly believe that I have become a better engineer under his guidance and I thank him for that. I also thank Dr. David Allee, Dr. Keith Holbert and Dr. Sarma Vridulla for being on my committee.

I thank Dan Patterson, Nathan Hindman, Thomas Mozdzen, Jerin Xavier, Srivatsan Chelleppa, Sandeep Shambhulingaiah for their support in the research and for their technical and non-technical ideas without which the successful completion of the work would not have been possible. Also my friends Nishant Chandra, Ashutosh Singuraur and Vinay Chinti for their moral and immoral support both academia and non-academia.

Finally, I would like to thank the Almighty for His grace. It would not have been possible without His blessings.

### TABLE OF CONTENTS

| Pag                                                      | e |

|----------------------------------------------------------|---|

| LIST OF TABLES i                                         | X |

| LISTA OF FIGURES                                         | x |

| CHAPTER 1. INTRODUCTION                                  | 1 |

| 1.1 Design Challenges                                    | 2 |

| 1.2 Logic design methodologies                           | 5 |

| 1.2.1 Full-custom design                                 | 6 |

| 1.2.2 Application specific integrated circuit (ASIC)     | 7 |

| 1.3 Designing comparing ASIC and full-custom techniques1 | 2 |

| 1.3.1 Full adder case analysis1                          | 2 |

| 1.3.2 Viterbi Decoder1                                   | 3 |

| 1.3.3 Microprocessor Design1                             | 5 |

| 1.3.3.1 iCORE to bridge ASIC and custom performance1     | 7 |

| 1.4 Comparison of different design styles1               | 8 |

| 1.5 Contribution of this work                            | 0 |

| 1.6 Thesis Organization2                                 | 1 |

| CHAPTER 2. HIGH PERFORMANCE DESIGN TECHNIQUES2           | 3 |

| 2.1 Achieving high frequency design2                     | 3 |

|                                                          |   |

2.1.1 Micro-architecture and hardware implementation......24

# CHAPTER 3. PROPOSED STRUCTURED METHODOLOGY OF IC DESIGN37

Page

v

## Page

| 5.1.1 Router Functionality                  |

|---------------------------------------------|

| 5.1.2 Overall Architecture61                |

| 5.1.3 Match block                           |

| 5.1.3.1 Head Circuit65                      |

| 5.1.3.2 Masking67                           |

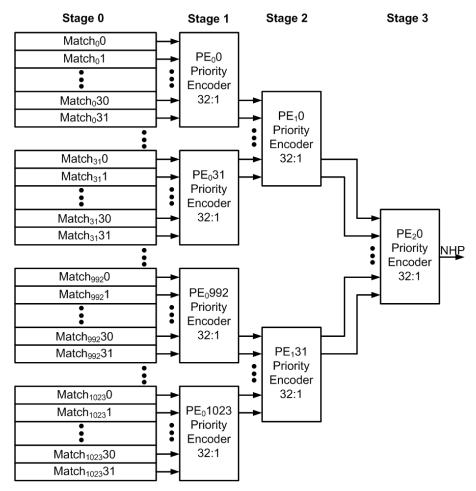

| 5.1.4 Priority Encoder                      |

| 5.1.5 Layout of design70                    |

| 5.1.6 Performance analysis71                |

| 5.2 Out of order Issue Logic72              |

| 5.2.1 Instruction Issue Logic72             |

| 5.2.2 Layout of the shifter1 structure73    |

| CHAPTER 6. FULLY STATIC ARRAY BLOCKS75      |

| 6.1 Translation look-aside buffer (TLB)75   |

| 6.1.1 Memory management unit (MMU)75        |

| 6.1.2 Design Specification76                |

| 6.1.3 Operation                             |

| 6.1.4 Radiation hardened TLB design80       |

| 6.1.4.1 TLB Radiation Hardening81           |

| 6.1.4.2 Results and Analysis82              |

| 6.1.5 TLB design using commercial library84 |

| 6.1.5.1 Dynamic TLB design85                |

| 6.1.5.1.1 Micro-architecture details        |

| 6.1.5.1.2 Multiple page size support                            |

|-----------------------------------------------------------------|

| 6.1.5.2 Structured static low power TLB design                  |

| 6.1.5.3 Performance analysis of the TLB design using commercial |

| <i>library</i> 89                                               |

| 6.1.5.3.1 Physical design and Area Comparison                   |

| 6.1.5.3.2 Delay92                                               |

| 6.1.5.3.3 Power Dissipation93                                   |

| 6.2 Register File (RF)94                                        |

| 6.2.1 Multiported RF94                                          |

| 6.2.2 Multiported RF design95                                   |

| 6.2.2.1 Microarchitecture details95                             |

| 6.2.3 Performance Analysis97                                    |

| 6.2.3.1 Physical design and Area Comparison                     |

| 6.2.3.2 Delay100                                                |

| 6.2.3.3 Energy Dissipation101                                   |

| CHAPTER 7. CACHE DESIGN: COMPLEX CIRCUIT COMPRISING OF          |

| BOTH STATIC AND DYNAMIC LOGIC102                                |

| 7.1 Introduction102                                             |

| 7.2 Cache architecture104                                       |

| 7.3 Design details106                                           |

| 7.3.1 Data Array106                                             |

| 7.3.1.1 Layout of data array109                                 |

## Page

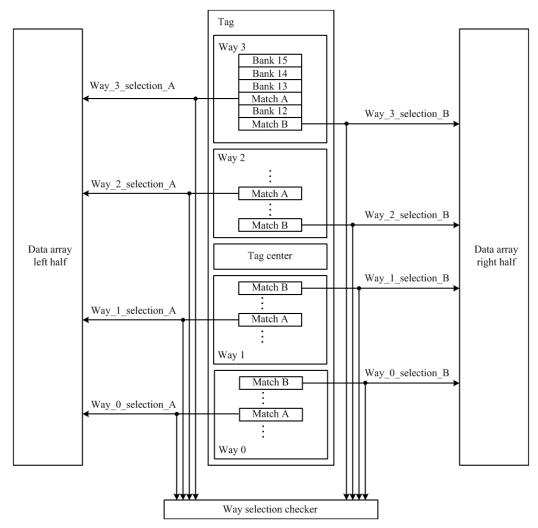

| 7.3.2 Tag array              |     |

|------------------------------|-----|

| 7.3.2.1 Layout of tag array  | 114 |

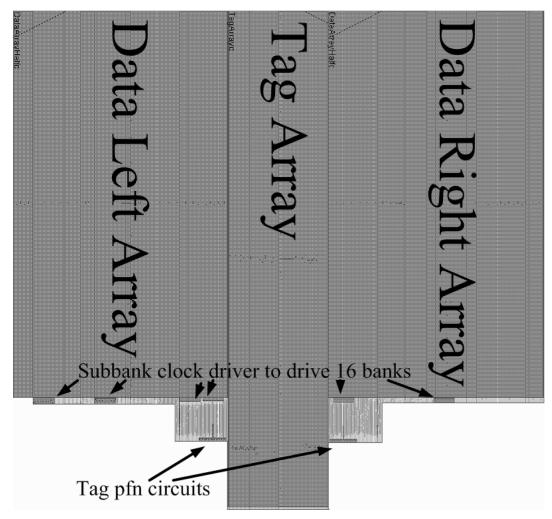

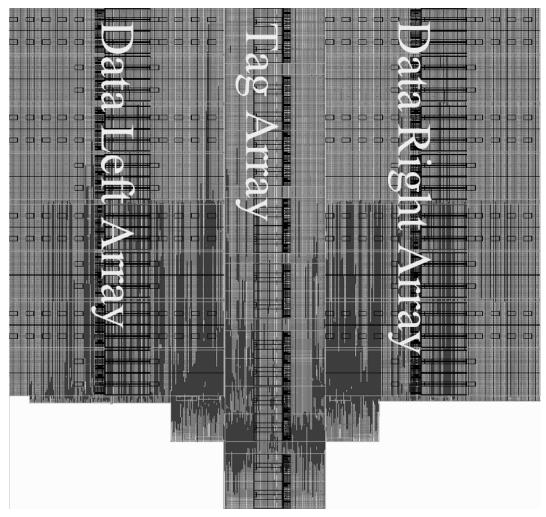

| 7.3.3 Overall cache layout   | 115 |

| 7.3.3.1 Performance analysis | 118 |

| CHAPTER 8. CONCLUSION        |     |

| REFERENCES                   |     |

## LIST OF TABLES

| Table Page                                                                |

|---------------------------------------------------------------------------|

| 1.1 Microprocessor Scorecard [Ogdin75] [Microprocessor12]3                |

| 1.2 Performance comparisons for custom and ASIC micro-architectures11     |

| 1.3 Performance comparisons for Adders13                                  |

| 1.4 Performance comparisons for Viterbi decoder15                         |

| 6.1 TLB Energy per operation (pJ)80                                       |

| 6.2 TLB delay comparisons                                                 |

| 6.3 Mask bits corresponding to Page size and Odd Page select signals      |

| 6.4 Performance analysis of the TLB designs                               |

| 6.5 Energy comparisons for various RF design                              |

| 6.6 Delay and Area comparisons for various RF design100                   |

| 7.1 Maximum power consumption estimation during a read and write cycle at |

| $V_{DD} = 1.2 \text{ V}$                                                  |

## LIST OF FIGURES

| Figure Page                                                                         |

|-------------------------------------------------------------------------------------|

| 1.1 Figure showing the CPU transistor count against the Moore's law2                |

| 1.2 Traditional Hardware Levels of Abstraction                                      |

| 1.3 Figure showing the different stages of ASIC design flow                         |

| 1.4 Comparison of 3-bit comparator/multiplexer circuit14                            |

| 1.5 Alpha performance versus time17                                                 |

| 1.6 RISC softcore roadmap                                                           |

| 2.1 Pipelined and un-pipelined logic implementation and the speedup from            |

| pipelining24                                                                        |

| 2.2 Routing patterns and resistance/capacitance associated with the net             |

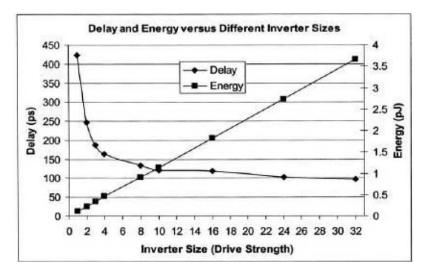

| 2.3 Delay and energy for increasing inverter sizes                                  |

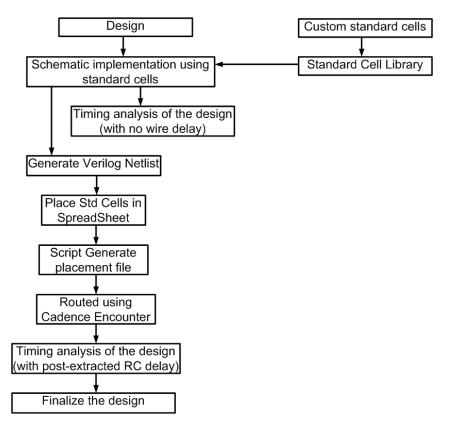

| 3.1: The proposed structured design flow                                            |

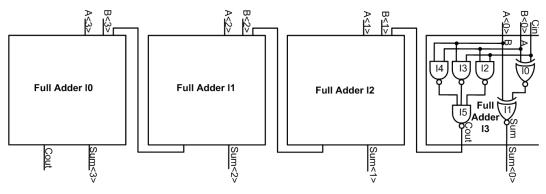

| 3.2: Schematic of the 4-bit adder                                                   |

| 3.3 Output of the verilog.infile                                                    |

| 3.4 Content of netlist_file41                                                       |

| 3.5 Content of hierarchy.txt                                                        |

| 3.6 Content of netlist.v42                                                          |

| 3.7 Spreadsheet for various layouts of the 4-bit adder block. Each full adder block |

| is shown with different shades to differentiate with other blocks45                 |

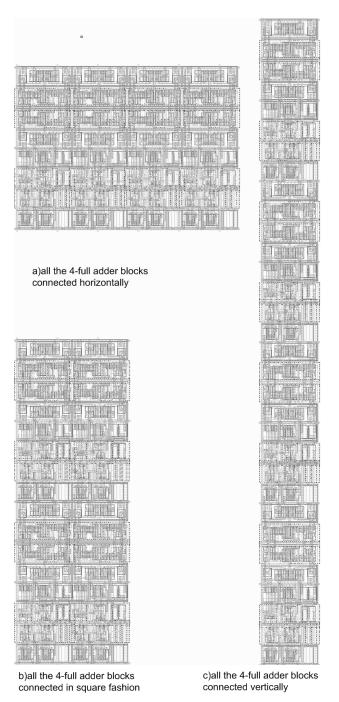

| 3.8 Different layouts of the 4-bit adder cells when the four full-adder blocks are  |

| placed differently47                                                                |

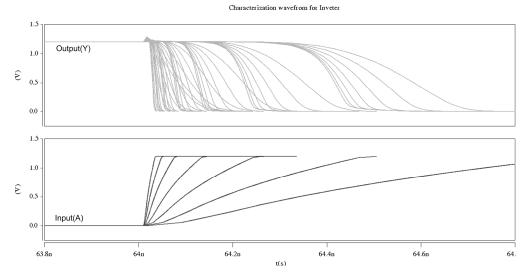

| 4.1: Input transition vs output load waveform for characterizing an inverter52      |

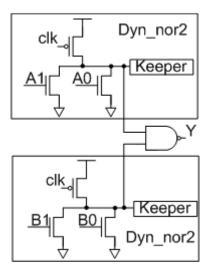

| 4.2: Dynamic 4-input OR gate                                                          |

|---------------------------------------------------------------------------------------|

| 4.3: 2-input dynamic NOR gate state-table55                                           |

| 4.4: 4-input dynamic NOR gate state-table55                                           |

| 4.5: Simplified 4-input dynamic NOR gate truth-table                                  |

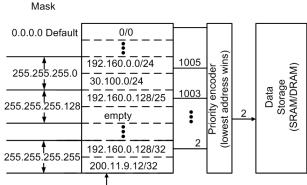

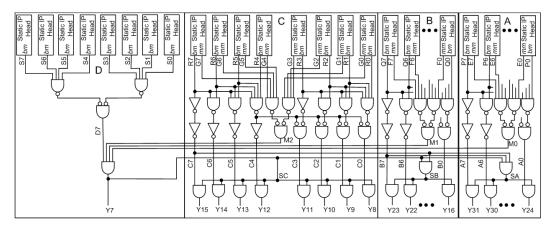

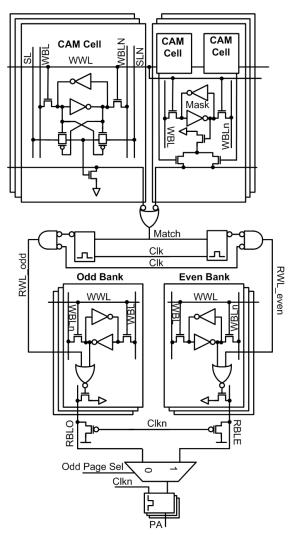

| 5.1 Basic IP router logical structure. The values after the slashes indicate the mask |

| values. Final hops are in external memory as shown60                                  |

| 5.2 Architectural details of proposed routing table circuit. The match block is       |

| composed of static IPCAM circuits, followed by the priority encoder.                  |

| The next hop address pointer NHP, corresponding to the location of the                |

| best match, is output61                                                               |

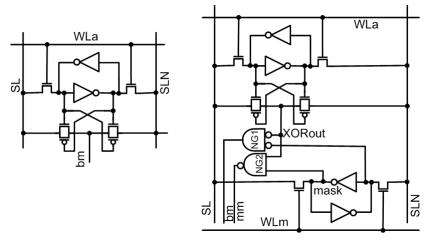

| 5.3 Proposed SIPCAM circuit for one entry. One row for implementing IPv4 is           |

| shown63                                                                               |

| 5.4 The CAM head circuitry driving each column of the Static IPCAM row66              |

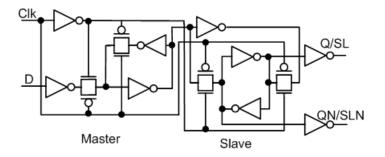

| 5.5 The flip-flop circuitry showing both master and slave circuit driving each        |

| search line of the Static IPCAM row67                                                 |

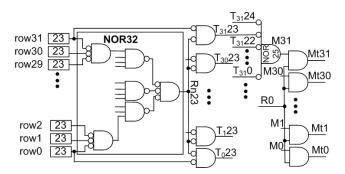

| 5.6 Priority encoder example                                                          |

| 5.7 Logic implementation of the proposed priority encoder                             |

| 5.8 Placement of standard cells for 32-entry SIPCAM array including both match        |

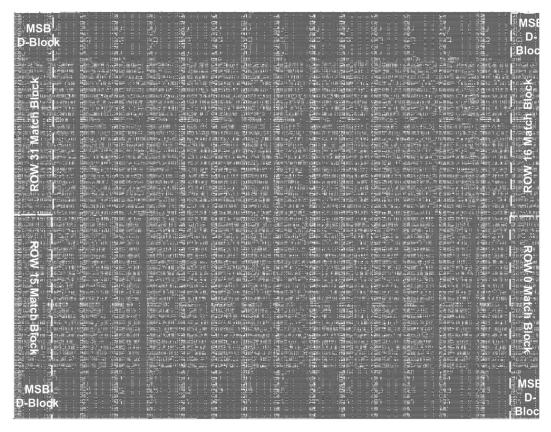

| block and PE70                                                                        |

| 5.9 Layout of 32-entry SIPCAM array including both match block and PE71               |

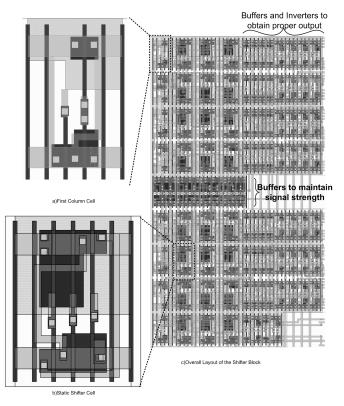

| 5.10 Layout of the shifter1 structure implemented on the 45 nm foundry process.  |

|----------------------------------------------------------------------------------|

| Details of the gates are shown to the left (a) and (b), while a full entry is    |

| shown to the right                                                               |

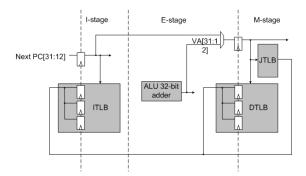

| 6.1 Microprocessor pipeline stages with integrated MMU unit                      |

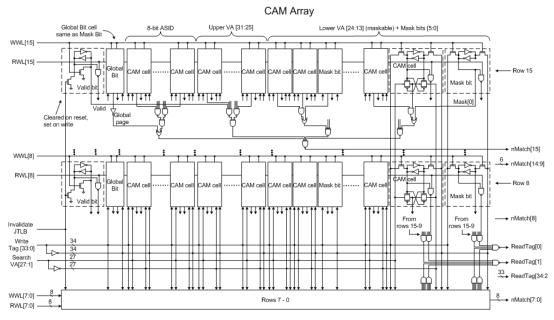

| 6.2 JTLB CAM array showing the timing/logic critical path gates77                |

| 6.3 Bottom half of the JTLB data array logic                                     |

| 6.4 RHBD buffer layout showing the annular NMOS and guard rings for PMOS.79      |

| 6.5 Standard cell placement details for CAM and Data part of TLB81               |

| 6.6 Single instance TLB layouts using both structured flow layout (engineer      |

| controlled placement in the arrays) and using standard DC/APR                    |

| approach. With engineered placement, less cells are used and the delay           |

| and area allow DMR TLB in the same footprint as a conventionally done            |

| soft-core                                                                        |

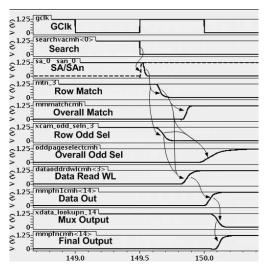

| 6.7 TLB simulation waveform showing assertion of match-line and data read        |

| word-line                                                                        |

| 6.8 The fully associative dynamic TLB reference circuits                         |

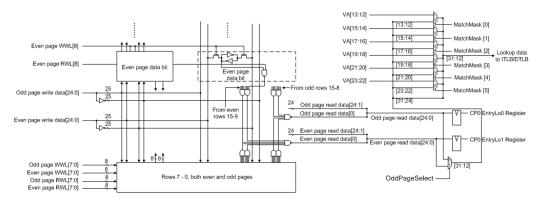

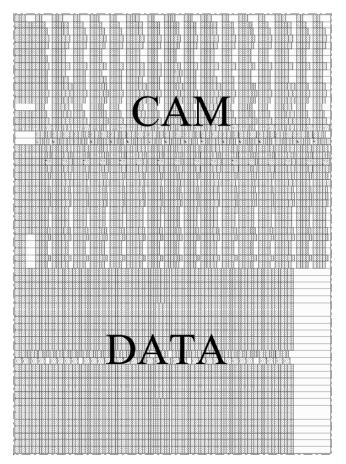

| 6.9 Standard cell placement for the 45-nm TLB showing both CAM and DATA90        |

| 6.10 Layout of the stuctured and the dynamic TLB design. a) shows the layout for |

| the proposed TLB design using the structured approach. b) shows the              |

| layout of the reference TLB design. c) and d) shows the synthesis layout         |

| using the design and rtl compiler respectively of the proposed TLB               |

| design91                                                                         |

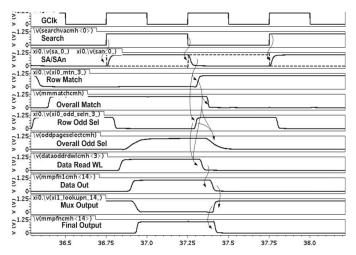

| 6.11 Simulated waveforms for the structured static design at 2GHz92                    |  |  |  |

|----------------------------------------------------------------------------------------|--|--|--|

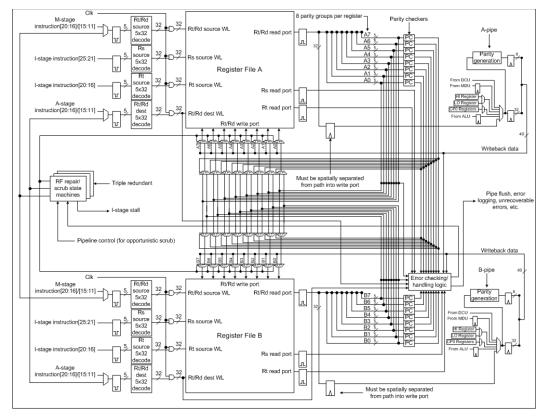

| 6.12 Schematic of the complete register file implementation. The dual instance of      |  |  |  |

| the core register file block and the error correction architecture is shown.96         |  |  |  |

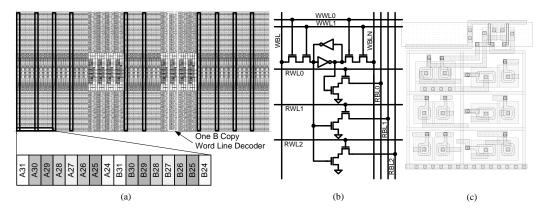

| 6.13 32 entry 40-bit DMR RF layout with parity group interleaving (color coded)        |  |  |  |

| and one parity group's bits outlined to show critical node separation (a);             |  |  |  |

| RF cell schematic showing the unconventional dual WWL connections                      |  |  |  |

| (b) and cell layout through metal 1 (c). The latter is non-rectangular with            |  |  |  |

| the adjacent cell storage node PMOS load transistors sharing the same                  |  |  |  |

| well. The A and B decoders are separated as well                                       |  |  |  |

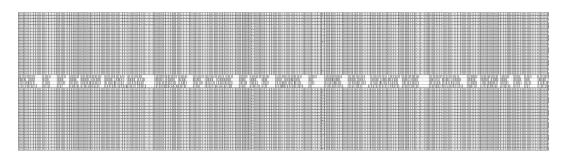

| 6.14 Standard cell placement for the dual modular register file                        |  |  |  |

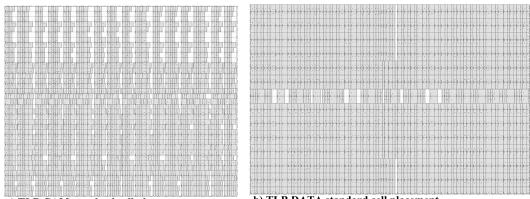

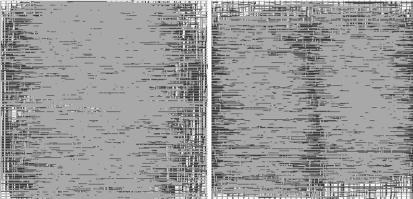

| 6.15 Layout of the dynamic and static RF design. a) Shows the layout for the           |  |  |  |

| proposed dynamic RF design b) shows the layout of the static RF using                  |  |  |  |

| the structured approach c) and d) shows the synthesis layout using the                 |  |  |  |

| design and rtl compiler respectively of the proposed RF design                         |  |  |  |

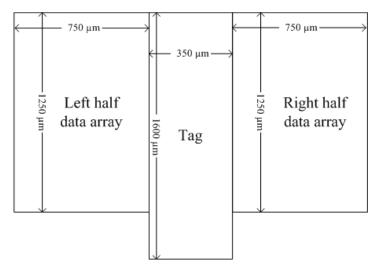

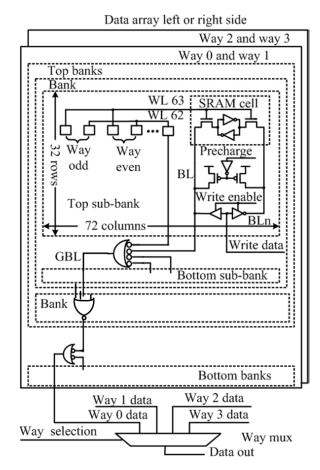

| 7.1 Floor plan of cache104                                                             |  |  |  |

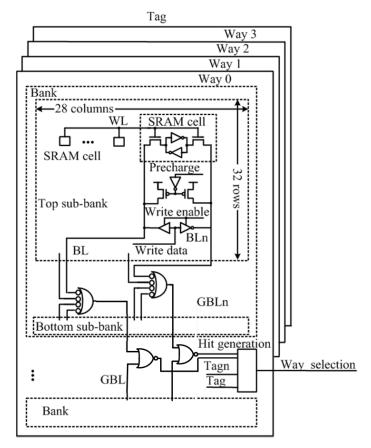

| 7.2 Basic diagram of data array (after [Yao09])108                                     |  |  |  |

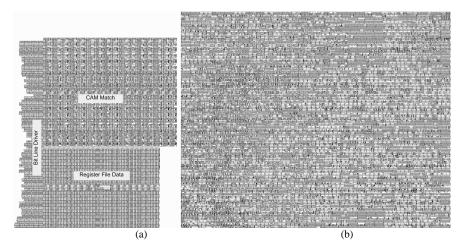

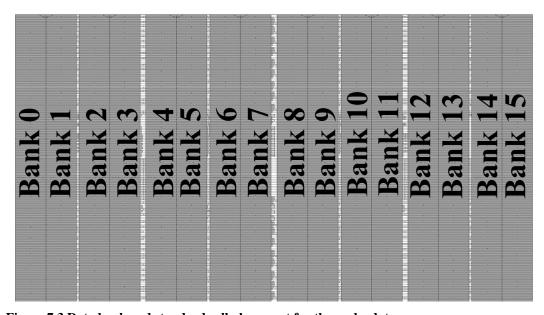

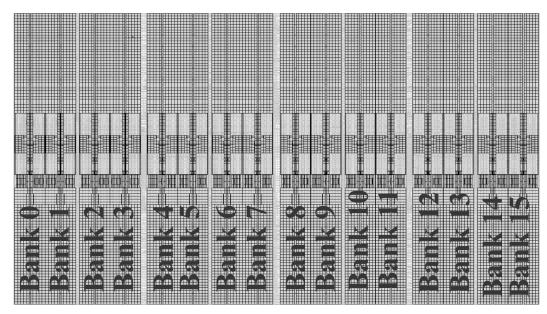

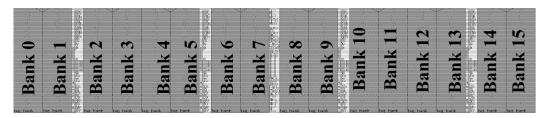

| 7.3 Data bank and standard cell placement for the cache data array110                  |  |  |  |

| 7.4 complete layout of cache data array showing the banks and the standard cells111    |  |  |  |

|                                                                                        |  |  |  |

| 7.5 Basic diagram of tag (after [Yao09])113                                            |  |  |  |

| 7.5 Basic diagram of tag (after [Yao09])1137.6 Basic diagram of tag (after [Yao09])115 |  |  |  |

|                                                                                        |  |  |  |

| Figure Pa                                                                       | ige |

|---------------------------------------------------------------------------------|-----|

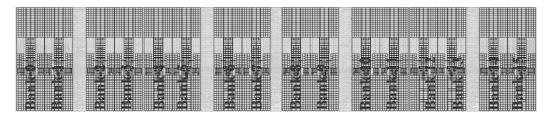

| 7.9 Tag and data array along with standard cell and periphery block placement f | for |

| the overall cache design1                                                       | 17  |

| 7.10 Complete layout of the overall cache design showing the tag and data array | У   |

| along with standard cell and periphery block1                                   | 18  |

#### CHAPTER 1. INTRODUCTION

Integrated circuits (IC) have demonstrated a compound annual growth of 53% over 50 years as measured by transistor count [Westel0]. Digital circuits progress with technology scaling roughly following the Moore's Law [Moore65] which has become a self-fulfilling prophecy for this enormous growth. It is driven primarily by scaling down the transistor size and to minor extent by building larger chips. In general, each generation shrinks the linear dimension by 0.7. The development of new CMOS technology nodes has been primarily motivated by the rapidly growing demand for high performance in digital circuits. Table 1.1 and Figure 1.1 show how the transistor count and integration density has dramatically increased in the microprocessors over the time [Moore03] [Ogdin75]. Smaller transistor feature sizes make it possible for digital circuits to run faster and consume less power. Moreover, it makes them cheaper to manufacture with each generation. Both speed and power efficiency has improved geometrically (by the approximated  $0.7 \times$  per generation) in the past two decades, resulting in a huge overall performance improvement.

The increasing density of IC's has led to the emergence of system-on-chip (SOC) design with a concomitant increase in design size and complexity. However, this has resulted in significant increases in the cost of IC design and corresponding increases in mask costs on the order of millions of dollars. High performance IC designs have stringent area, speed, and power requirements. In the past this has been dealt with by having large design teams, but must increasingly be automated as design team cannot be made larger.

#### 18-Core SPARC T3 Six-Core Core Six-Core Xeon 740 2,600,000,000 -Cora Xeon Westmera-E Dual-Core Itanium 20 POWER7 AMD K10 1,000,000,000 -Tukwik POWER6 Hanium 2 with SME Six-Core Opteron 2400 Cors 2 Duo Itenium 2 100,000,000 -AMD K8 Barion Pentium 4 6 AMD K7 AMD K6 curve shows transistor Transistor count 10,000,000 - Pentium I intum II count doubling every £́ь. two years @ AMD K5 Pentiun 80488 1,000,000 -80386 802864 100,000 -68000 **6** 80196

## Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1.1 Figure showing the CPU transistor count against the Moore's law

1980

8088 • \$25088

MOR 8502

**6**6809

6800

anna

1971

4004

#### 1.1 Design Challenges

10,000

2,300

With the improving design performance and reduced cost of the IC, increasing system complexity poses a major challenge. Modern SOC designs combine memories, processors, high speed I/O interfaces, and dedicated application-specific logic on a single chip. Partitioning the design to simplify the implementation process is necessary. However, the interdependence between the structures complicates partitioning. The practice of structured design relies on hierarchy, regularity, modularity and locality to manage complexity.

1990

Date of introduction

2000

2011

| Processor                | Transistor count | Area                | Year |

|--------------------------|------------------|---------------------|------|

| Intel 4004               | 2300             | 12 mm <sup>2</sup>  | 1971 |

| Intel 8008               | 3500             | 14 mm <sup>2</sup>  | 1972 |

| Zilog Z80                | 8500             | 18 mm <sup>2</sup>  | 1976 |

| Intel 8086               | 29000            | 33 mm <sup>2</sup>  | 1978 |

| Pentium                  | 3,100,000        |                     | 1993 |

| AMD K5                   | 4,300,000        |                     | 1996 |

| AMD K7                   | 22,000,000       |                     | 1999 |

| Pentium 4                | 42,000,000       |                     | 2000 |

| POWER6                   | 789,000,000      | 341 mm <sup>2</sup> | 2007 |

| Atom                     | 47,000,000       |                     | 2008 |

| AMD K10                  | 758,000,000      |                     | 2008 |

| Core i7 (Quad)           | 731,000,000      | 263 mm <sup>2</sup> | 2008 |

| Six-Core Opteron 2400    | 904,000,000      | 346 mm <sup>2</sup> | 2009 |

| 10-Core Xeon Westmere-EX | 2,600,000,000    | 512 mm <sup>2</sup> | 2011 |

Table 1.1 Microprocessor Scorecard [Ogdin75] [Microprocessor12]

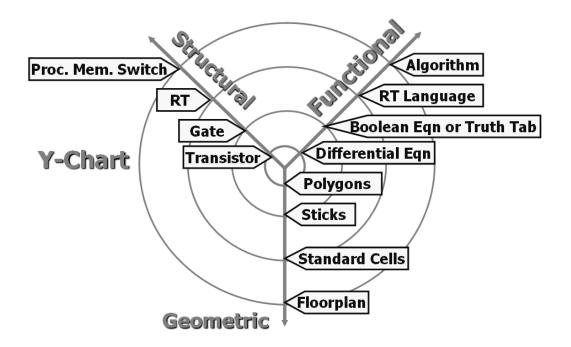

Digital VLSI design is often partitioned into five levels of abstraction: architecture, micro-architecture, logic, circuits, and physical design. Architecture describes the user visible function of the design. Partitioning the design into registers and other functional blocks is determined by the micro-architecture level. Logic describes how the functional units are constructed. Use of transistors to implement the logic comprises circuit design. Finally, layout and placement of these transistors are part of physical design level. These elements are relatively independent and all influence each of the design objectives. Figure 1.2 shows the various levels of abstraction in the modern VLSI design.

The viability of VLSI design depends on a number of conflicting factors, e.g., performance in terms of speed or power consumption, cost, and production volume. Performance excellence at low cost can only be achieved using volume production. With ultimate performance as the primary design goal, high performance custom design techniques are often desirable. However, the cost of a sufficiently large team for this approach is becoming untenable. Reducing the system size through integration, not performance, is the major objective in most consumer applications. Under these circumstances, the design cost can be reduced substantially by using advanced design-automation techniques. VLSI architectures should exploit the potential of the VLSI technology and also take into account the design constraints introduced by the technology. Some of the key design requirements are summarized below:

<u>Simplicity and regularity:</u> Cost effectiveness has always been a major concern in designing VLSI architectures. A structure, if decomposed into a few types of building blocks which are used repetitively with simple interfaces, results in great savings. In VLSI, there is an emphasis on keeping the overall architecture as regular and modular as possible, thus reducing the overall complexity. For example, memory and processing power will be relatively cheap as a result of high regularity and modularity.

**Design reuse:** It improves the design productivity and also saves time and effort. Effective reuse of existing designs requires proper representation, abstraction, and characterization in terms of its functionality, performance, reliability, and possible interactions with the environment, so that it can be seamlessly integrated with the rest of design for synthesis, simulation and verification. Such representation and abstraction should also support efficient update of the design when migrating from one technology generation to another, from one foundry to another, and from one design environment to another. Design reuse should also include the development of reusable design process,

**Figure 1.2 Traditional Hardware Levels of Abstraction**

methodology, and tools so that they can be retargeted for different technology generations and easily shared among different design projects.

<u>Scalability and optimization</u>: Complexity management requires improvement for global performance, power, area, and reliability optimization. Innovations in highly scalable optimization algorithms which can handle complex design constraints, multiple design objectives, and rapidly increasing design sizes will significantly improve the capability, efficiency, and quality of the design tools for future ICs.

#### 1.2 Logic design methodologies

Over the last three decades, several logic design methodologies have evolved to cope with technological advancements in semiconductor circuit design. Based on the design approach they can be broadly classified into full-custom and ASIC (application-specific integrated circuit) methodology.

#### 1.2.1 Full-custom design

Full-custom design relies extensively on manual effort for most design decisions. For example, transistor sizing, transistor layout, device placement and routing are all carried out manually with the aid of computer-aided design (CAD) tools. The circuit is partitioned into a collection of sub-circuits based on functionality creating several levels of hierarchy. Each functional block can be of any size.

This technique offers the greatest flexibility from a designer perspective, because circuits can be tailored to specifications with superior performance in terms of area, delay or power [Hurst99]. When designing a custom IC, the designer has a full range of choices in design style and benefits from the ability to optimize across domains. These include micro-architecture, logic design, floorplanning and physical placement, and most importantly choice of logic family. Circuits can be carefully optimized and use special circuit styles and arbitrary sizing of the transistors for high speed, lower power, and lower area. Custom designs may also show superior logic-level design of regular structures such as adders, multipliers, and other data-path elements. They achieve fewer levels of logic on the critical path with more compact, complex logic cells and by combining logic with the latches [Hwang93]. Due to lack of any constraints on the physical design perspective, the custom design achieves very compact layout design.

6

However, there is a high engineering cost overhead involved. The amount of effort required for full-custom design scales linearly with the number of unique circuits in the design [Chen06]. Furthermore, given shrinking time-to-market windows and market lifetime of IC products, it becomes increasingly difficult to depend on full-custom techniques for IC design. For example, a large IC design house like Intel requires large teams of designers working for the equivalent over a thousands of man-years to deliver high-performance full-custom products such as the Pentium 4 chip on schedule. This results in huge expenses that has an impact on the pricing of such chips and the products that use them (e.g., personal computers) [Hurst99]. This limits the custom design to be used when the final design must have high performance requirement and the design time is less of a factor.

#### 1.2.2 Application specific integrated circuit (ASIC)

In order to reduce engineering effort, some vendors resort to automated design techniques to deliver new products much faster and at lower cost [Costa84]. They rely exclusively on electronic design automation (EDA) tools to implement logic and circuits [Loos96]. These EDA tools use libraries of pre-designed logic cells, standard cells, blocks, and or cores, to implement circuits in much shorter time but with some overhead costs, and significant restrictions on the IC designer [Loos96].

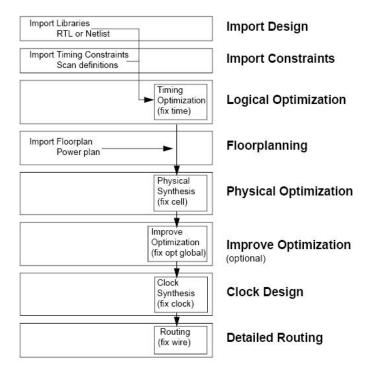

This flow is known as the application specific integrated circuit (ASIC) flow as illustrated in Figure 1.3. This approach of circuit design has become immensely popular and is used for the implementation of virtually all logic

elements in today's integrated circuits. This has been made possible because of the advent of sophisticated logic-synthesis tools and increased quality of automatic cell placement and routing tools. It is a structured methodology that theoretically limits the space of exploration, yet still achieves superior results in the fixed time constraints of the design [Vincentelli04].

In standard-cell-based designs, vendors develop cell libraries that implement generic logic gates such as NOR and NAND gates with different drive strengths and in accordance with a constrained physical layout, typically with fixed cell height [Yoshida04]. These libraries of logic gates are then mapped from register transfer level (RTL) descriptions of desired hardware behavior written in VHDL or Verilog [Zhang01], into gates using logic synthesis tools such as Synopsys Design Compiler and Cadence RTL Compiler [Stine05]. A more aggressive form of cell-based design allows designers to build custom cells and tools according to their own specifications and tailored for a particular circuit or group of circuits [Dally00] [Chinnery02] [Bhattacharya04] [Scott94].

Synthesis mapping is automated and can be constrained for area and performance [Dunlop85]. Placement involves reading a netlist of gates generated through logic synthesis and then arranging the corresponding standard cells in rows. This high degree of automation is made possible by placing strong restrictions on the layout options. Standard cells are arranged in rows so that power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) rails of adjacent cells are connected by abutment since all the standard cells are of same height [Xing02]. Routing tools connect nodes (with metal wires) to implement the desired logic function. A substantial

Figure 1.3 Figure showing the different stages of ASIC design flow

fraction of area still must be devoted to signal routing [Gyurcsik89] [Keyes82]. The minimization of interconnect overhead is the most important goal of the standard cell placement and routing tools. The routing area, for design rules with two metal layers, is about 50% of the chip area [Moraes98]. For design rules with three or more metal layers, it is possible to aggressively use the over-the-cell routing [Kim96] to reduce the routing area to 25% of the chip area. The approach "zero routing footprint" [Sherwani95] (no routing area) is possible because the cells are designed to be transparent to several routing tracks, increasing in this way the cell height. When more than three metal layers are available for routing, they must be used to connect different blocks, not inside them (transparency over blocks). There are cells without any transistors, called feed-through or filler cells. They can be added between cells to allow vertical connectivity when there are no

more routing resources over the cell, thus reducing long wires [Clein99]. More interconnect layers also reduce wiring area.

The speed of average ASIC design lags that of the fastest custom circuits in the same processing geometry by factors of as much as six to eight [Chinnery02]. The standard cell layout is inherently non-hierarchical. ASIC designs are limited by the algorithms in the synthesis. The performance achieved solely depends on the efficiency these algorithms to select right logic implementation, placement and finally routing the standard cells. The algorithms read the design data for each of the standard cells that consist of dimensions, timing, drive strength and power dissipation and try to meet the specification. The optimization scale is limited by the granularity of the standard cell library. Today's libraries contain from several hundred to more than a thousand cells comprising of range that vary in terms of drive strengths  $(2\times, 4\times$  etc.), logic styles (static, dynamic, sequential etc.), and logic type (NAND, NOR etc.). These cells have to be redesigned with every migration to a new technology, and technology sub-nodes must also be supported. A number of iterations of the synthesis flow shown in Figure 1.3 are needed until the specifications are matched [McFarland88]. Depending on the design and the target specification, several iterations need to be done that can take longer [Tiri04].

Cell based "soft-IP" microprocessors are not typical, because they bear more similarity to custom microprocessors, but they present a good mid-point in the comparison between custom design and a typical ASIC design. This methodology is mostly used to implement random or control logic part of the

| Custom                |                |          |                        |

|-----------------------|----------------|----------|------------------------|

| Name                  | Frequency(GHz) | Power(W) | Area(mm <sup>2</sup> ) |

| Pentium III(Tualatin) | 1.4            | 31.0     | 80.0                   |

| Pentium 4 (Northwood) | 2.2            | 55.0     | 146.0                  |

| ASIC                  |                |          |                        |

| Lexra LX4380          | 0.420          | 0.05     | 0.8                    |

| ARM1022E              | 0.325          | 0.23     | 7.9                    |

Table 1.2 Performance comparisons for custom and ASIC micro-architectures

micro-processor design. Table 1.2 exemplifies some of the microprocessor designs carried out at 0.13  $\mu$ m technology node using both custom and full synthesis approach. At the outset, it can be observed that custom microprocessor operate 3× to 4× faster than those fully synthesized in the same process [Chinnery02]. This gap seems staggering– the speed improvement due to one process generation (e.g. 0.18 $\mu$ m to 0.13 $\mu$ m) is 1.5× [Moores] then this gap is equivalent to that of two process generations.

However, in the future, with increasing design rule complexity and restrictions, imposed regularity, there will be very little room for improvement with manual design. Furthermore, due to increased complexity of the design rules, manual designs may gravitate towards local optimizations rather than global, and thus may even be suboptimal [Borkar09]. Custom design will be limited to memory arrays, register files and large arrays. This is where the current area of this research concentrates and proposes methods to optimize the design time without deteriorating the performance.

#### 1.3 Designing comparing ASIC and full-custom techniques

In order to completely understand the two design approaches and their feasibility for different types of designs, several works has been published that compare ASIC designs against those using full-custom techniques.

#### 1.3.1 Full adder case analysis

A case study carried for adder design by Henrik et al. quantifies the performance gap between the two techniques for two types of adder structures [Eriksson03]. The adders used in the comparison are one 64-bit ordinary ripplecarry adder (RCA) and one 64-bit Han-Carlson tree adder (HCA) [Han87]. These adder topologies were chosen since they represent two adder implementation extremes. The interconnect wire run in RCA is very small as the carry propagates only to the neighboring adder cell. However the small interconnect run comes at the cost of poor performance. The performance was improved by using dynamic circuit. The fully custom RCA design leads to much higher performance over the unstructured standard cell implementation both in terms of delay and area. The HCA, on the other hand has, as all tree adders do, complex interbitslice interconnections to achieve high performance [Knowles01]. The performance of the design carried out using the custom placement or using ASIC flow was close. Table 1.3 summarizes the two adders performance built using the two methodologies.

Thus the ASIC tool performs place and route as efficiently as custom designer would do for implementation with inter-bitslice interconnections, but that full-custom designs reach higher performance through the use of advanced circuit

| Adders | ASIC      |                        | Custom    |                        |

|--------|-----------|------------------------|-----------|------------------------|

|        | Delay(ns) | Area(mm <sup>2</sup> ) | Delay(ns) | Area(mm <sup>2</sup> ) |

| RCA    | 30.24     | 0.045                  | 23.54     | 0.015                  |

| HCA    | 3.92      | 0.110                  | 2.13      | 0.416                  |

Table 1.3 Performance comparisons for Adders

technique. This is due to the fact that the length of the critical wires in full-custom bitsliced layouts is proportional to width of adder, but in standard-cell based layouts the length is proportional to the square root of the width. For small tree adders full-custom layouts are preferable, but for wide adders standard-cell based layouts are better since the routing-dependent delay scales better with the adder width [Eriksson03].

#### 1.3.2 Viterbi Decoder

A similar analysis was carried out by Grey *et al.* for a Viterbi decoder that assumed trellis encoded modulation with an 8 PSK signal set, rate 2/3 and memory length 2 encoder [Gray91]. At each transmission interval, the decoder processes a measure for each of the eight possible transmit signals and decides upon the most likely transmitted symbol. This decoder architecture is highly parallel to optimize for speed. One symbol is decoded at every clock cycle. The Viterbi decoding algorithm leads to an implementation comprised of flip-flop storage elements and combinational logic elements to create fast adders, comparators, multiplexors and control circuits which are the main constituents of digital circuit designs.

The synthesized decoder is 16% smaller and 13% faster than the hand optimized design possibly because synthesis could optimize larger circuits better than custom optimization. Approximately 120 man-hours were used to enter the

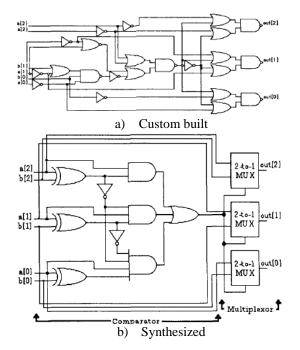

Figure 1.4 Comparison of 3-bit comparator/multiplexer circuit

schematic and simulate the decoder for the "hand" design. This does not include the time spent simulating the algorithm, finding the minimal logic and minimal gate level implementation. For comparison, the total time required to learn the ASIC synthesis tool, Verilog HDL, write and debug the Verilog code, test the netlist and compile the decoder took the same amount of time, approximately 120 man-hours. The performance comparison for the design using the two methodologies is shown in Table 1.4.

The performance degradation for custom design in terms of both area and delay could be attributed to simple design approach of using two input NAND/NOR/INV gates for the implementation. However the synthesis tool used complex XOR gates and multi-input gates and multiplexers to optimize the design. This difference is clearly inferred from the two schematics of the 3-bit

Table 1.4 Performance comparisons for Viterbi decoder

|        | Delay(ns) | No. of Std cells | Transistor Count | $Area(mils^2)$ |

|--------|-----------|------------------|------------------|----------------|

| Custom | 41.6      | 1359             | 16545            | 21877          |

| ASIC   | 36.3      | 1493             | 11946            | 18322          |

comparator shown in Figure 1.4 for design using the custom and synthesized. The 3-bit comparator compares two 3-bit inputs and outputs the smallest.

#### 1.3.3 Microprocessor Design

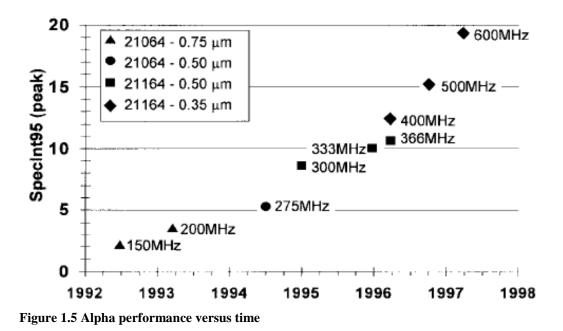

For microprocessors the custom design methodologies have proven to have much better performance than synthesized designs. One of the most acclaimed high performance fully custom microprocessors was the Dec Alpha 21064 introduced in 1992 [Gronowski98]. It was the culmination of three generations of Alpha microprocessors that achieved high performance through process advancements, architectural improvements, and very aggressive circuit design techniques. Figure 1.5 shows the integer benchmark performance of as a function of time. The Alpha chips showed that manual circuit design applied to a simpler, cleaner architecture allowed for much higher operating frequencies than those that were possible with the more automated design methodologies. These chips caused a renaissance of custom circuit design within the microprocessor design community at that time (as it is now) the microprocessor industry was dominated by automated design and layout tools [Bolotoff07].

As mentioned, the DEC Alpha microprocessor designs used full-custom circuit design methodologies. All circuits were designed at the transistor level, and were uniquely sized to meet speed and area goals. Custom layout design techniques optimized parasitic capacitances for all circuits. Automatic synthesis approaches for logic and circuit design were used for fewer than 10% of the circuits. The use of a full-custom design methodology gave the designer flexibility. The Alpha microprocessors were implemented with a wide range of circuit styles including conventional complementary CMOS logic, single and dual rail dynamic logic, cascode logic, pass transistor logic, and ratioed static logic [Benschneider95]. Dynamic circuits were one of the most commonly used circuit styles, and were present in both data path and random control structures. Another circuit style that was widely used in the microprocessors was dual-rail cascode voltage switch logic (CVSL) [Dobberpuhl92]. Although full custom circuit techniques allowed designers to build very high speed circuits, the verification and validation of the design at process corners presented a challenge that lead them to develop many in-house CAD tools. Also migrating from one technology node to other took much more time than required for move automated methodologies.

Soft-cores are microprocessors whose architecture and behavior are fully described using a synthesizable subset of a hardware description language (HDL). The use of soft-cores provides many advantages for the embedded system designer. First, soft-core processors are flexible and can be customized for a specific application with relative ease. Second, since soft-core processors are technology independent and can be synthesized for any given target technology, they are more immune to becoming obsolete when compared with circuit or logic level descriptions of a processor. Finally, since a soft-core processor's architecture and behavior are described at a higher abstraction level using an HDL, it becomes much easier to port the design. As against the soft-core fully

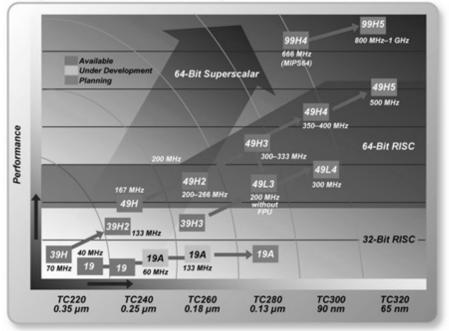

synthesized RISC microprocessors, which are standard in the current embedded market, we can see from the Figure 1.6, for the 0.35  $\mu$ m technology node the performance significantly lags the Alpha processor at the same technology node [Toshiba].

#### 1.3.3.1 iCORE to bridge ASIC and custom performance

The iCORE project by STMicroelectronics tried to prove that a proPerly configured ASIC design flow could give a soft CPU core custom performance [EEtimes02]. The goal was to create a very high performance version of the company's ST20-C2 embedded CPU architecture, but it also show that the design could be portable as a soft-core across existing and future technologies. This ruled out the extensive use of custom circuits, and led to the adoption of a methodology close to a traditional ASIC design flow, but one tuned to the aggressive performance goals demanded by the project.

Firstly, the performance gap between custom and synthesized embedded cores was closed by using deep, well-balanced pipelines, coupled with careful partitioning, and mechanisms that compensate for increased pipeline latencies. This enables the use of simple and well-structured logic functions in each pipeline stage that are amenable to synthesis. Secondly, the performance gains are consolidated by use of placement-driven synthesis, thirdly, by using more careful clock-tree design. Delays were also reduced by creating larger, single level cells for high-drive gates. Physical compiler was used for cell placement. Timing simulation indicated that a good balance of delays between the pipeline stages was achieved. Silicon testing showed functional performance of the design from 475 MHz at  $V_{DD}$ = 1.7 V to 612 MHz at  $V_{DD}$ = 2.2 V and 25 °C in 0.18µm CMOS process [Richardson03]. This performance is close comparison to the DEC Alpha 21164PC implementation which was implemented at 0.28µm technology node rather than the iCore which was on 0.18µm [David09], lag of one process technology node.

#### 1.4 Comparison of different design styles

Thus we have found that the performance of a design depends on choice of methodology adopted which intern depend on the intended functionality of the chip, time-to-market and total number of chips to be manufactured. For designs that are more random or control logic type, ASIC methodology is well suited whereas for structures that are regular and hierarchical, custom design has proven results. But still the time and effort of the custom design and the inconsistent and ergodic implementation of the ASIC methodology are the major cause of concern.

#### TX System RISC Core Roadmap

#### Figure 1.6 RISC softcore roadmap

A mid-way between the two where the implementation of the design is done similar to using the custom methodology in which the designer chooses the cells (both size and implementation kind) and also carry out the floorplanning of the placement of these cells along with the highly proven optimized routing using the ASIC methodology would result in high performance designs.

Thus high performance design can be obtained by judiciously employing number of custom design techniques including floorplanning, prerouting critical signals, tiling datapaths, and generating crafted cells [Dally00]. These techniques all structure the design by routing the critical wires first and then placing the devices. This 'key wires first' approach exploits the structure of the logic to reduce wire loads, provide early visibility into the timing and power dissipation of a design, and gives the designer control of the key wiring. Custom designs have proven performance for regular, repetitive and hierarchical designs like VLSI Arrays (TLB, RF, cache etc). These array structures require high performance implementation as they are time critical for the microprocessor. They are mostly implemented using the custom flow requiring large implementation team and man hours and also migrating from one technology node to other requires significant rework. However if these blocks are implemented by incorporating special standard cells, a method similar to the ASIC flow and the placement is directed by the designer instead of random placement of synthesis flow and finally routed using the ASIC efficient algorithms, the output design will be regular, easy to amend and migrate across technology nodes could be easy while maintaining high performance.

#### 1.5 Contribution of this work

In the proposed methodology, we put forward a structured IC design approach where the regularity of custom IC design, together with the fast layout and routing of the ASIC approach, using the EDA tools are exploited. The proposed design approach is targeted for VLSI arrayed structures however other designs can be implemented using this flow too. In the structured approach, the design is implemented using the standard cells with designer crafted schematics. The design is then verified across various corners using the timing tools to ensure design robustness. The standard cells are then automatically placed in the floorplan using programs developed as a part of this work. Since the designer is the best judge of how the cells should be placed to reduce the critical path delays, the placement is crafted so that the drive strengths, path delays and regularity of the design can be exploited. The fast and optimal routing of the synthesis tools are then exploited by routing the placed cells using the auto-routing tools. Fully routed design can be imported back as GDSII file.

The structured approach of building the digital circuits make the design more controllable for timing and area constraints. Since moving the standard cells in the spreadsheet is easy and comfortable. It is also repeatable and several iterations to meet the specifications can be run in few hours. Portability of the design across technology nodes is very easy. Replacing the standard cells in the spreadsheet with the equivalent driver cells of new technology makes the design ready for the next technology. Robustness is guaranteed as each step is checked using the ASIC tools like timing (Prime Time) and placement routing (Encounter). These tools can easily be run at various corners to ensure margin checks and other failure analysis.

#### 1.6 Thesis Organization

This chapter gives an introduction to custom and ASIC design methodologies. Chapter 2 highlights various ASIC and custom designs features and how to manipulate them to achieve high performance design. The proposed structured methodology of IC design which achieves performance benefits in terms of speed, area and power as of the custom design is comprehended in chapter 3. Chapter 4 discusses how to characterize the complex static and dynamic gates using the Synopsys NCX tool. Chapter 5 discusses various designs examples viz. Internet protocol content addressable memories (IPCAM) and issue logic design where proposed methodology is used to estimate the performance of the design. Chapter 6 focus on building static design like translation look-aside buffer (TLB) design and register file design; that exploits the structured approach in their implementation. A detail performance comparison in terms of area, delay and power is also presented. Chapter 7 explains yet another highly complicated cache design. Chapter 8 concludes.

### CHAPTER 2. HIGH PERFORMANCE DESIGN TECHNIQUES

Implementation of a SOC design depends on broad range of factors:

- i) Performance, power and cost constraints

- ii) Design complexity

- iii) Testability

- iv) Time to market and time to revenue

- v) Application range covered by the design

A number of these factors tend towards more flexible, programmable components that can be reused and that can be modified even after manufacturing i.e. reconfigurable components. Finding the balance between these extremes is the ultimate challenge for the modern designer. New implementation styles have emerged over the last decades, presenting the designer with wide variety of options. Various methodologies have been proposed in order to push the performance of ASIC designs closer to that of custom designs. Since the ASIC designs are tool based, the performance improvement techniques can be grouped into two major groups. Firstly, achieving high frequency design and secondly, ensuring low power implementation.

## 2.1 Achieving high frequency design

The speed of a digital circuit is determined by the delay of its longest critical timing path. The length of the critical timing path is a function of gate delays, wiring delays, set-up and hold-times, clock-to-Q (the delay from when a clock signal arrives at a latch to when the latch output stabilizes), and clock skew [Weste92]. As previously explained in Chapter 1, the speed of ASIC designs lags

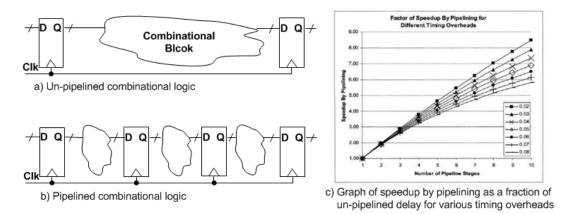

Figure 2.1 Pipelined and un-pipelined logic implementation and the speedup from pipelining

that of the custom design in the same technology node by factors of 1.5 to 2. To improve the speed of an integrated circuit requires reducing the delay of one or more of these elements. High frequency design requires the ability to apply costly (as measured by effort) local optimizations to the design critical paths.

#### 2.1.1 Micro-architecture and hardware implementation

Pipelining can be productive if multiple tasks can be initiated in parallel or if there is one signal flow direction. Splitting a large operation into smaller independent operations by placing storage elements between them allows the circuit to operate at higher frequency. Figure 2.1 shows the basic un-pipelined and pipelined combinatorial logic implementation. The graph shows the estimated speedup by pipelining, assuming that the combinational logic can be split equally and flip-flops are balanced which is overly optimistic.

The increase in the throughput is at the cost of latency and complexity. Simply increasing the clock speed by adding latches would only increase latency due to the additional latch setup and hold times. By placing additional latches or registers in long chains of logic, the number of gates in critical path in each stage can be reduced and hence higher operating frequency can be obtained. With flipflops the timing overhead is between 0.06 and 0.08 times, and this larger timing overhead substantially reduces the benefit of having more pipeline stages (refer to Figure 2.1) [Chinnery02]. Pipelining ASICs is also limited by the speed of registers in the pipeline, and greater automated clock tree generation produced skew than can be obtained in carefully designed custom clock trees.

Custom designs may show superior logic-level design of regular structures such as adders, multipliers, and other datapath elements. They achieve fewer levels of logic on the critical path with more compact, complex logic cells and by combining logic with the latches. A careful custom design can balance the logic in pipeline stages after placement, ensuring that the delays in each stage are close, whereas an ASIC may have unbalanced pipeline stages resulting in more levels of logic on the critical path.

Fast datapath designs, such as carry-lookahead and carry-select adders and other regular elements, do exist in pre-designed libraries, and are easily invoked in RTL logic synthesis of ASICs. Use of these predefined macro cells for an ASIC can significantly improve the resulting design, by reducing the number of logic levels for implementing complex logic functions and reducing the area taken up by logic [Chang98]. However these have to be compatible with the pipeline micro-architecture organization. All the operations in the macro block must complete within that particular pipeline stage.

Design of memory macro blocks like register file (RF), translation lookaside buffer (TLB), cache etc. are some of the most critical blocks to

incorporate in the pipeline stage. Since these blocks are very time critical, they are usually custom crafted in high performance processor; however all vendors have RAM compilers that generate memory blocks [Shinohara91]. Most of these blocks, being in the critical timing path of the pipeline stage, decide the maximum clock period. Consequently, dynamic logic is incorporated in the worst case delay paths to optimize the delay, which is achievable using custom circuits only.

## 2.1.2 Wire-delay Optimization

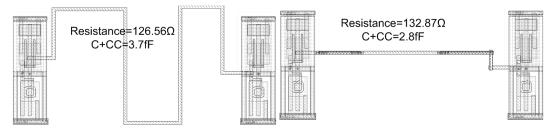

Wire-delays associated with "global" wires between physical modules can be a dominant portion of the total path delay [Xing02]. The delay associated with wires depends on the length of the wire, the width and aspect ratios of the wire, and on proper drive [Gyurcsik89]. Properly driving a wire requires not only sizing of drivers, but insertion of repeaters. However, the primary factor in wire delay is wire length. Wire length is obviously dependent on placement, which in turn depends on floor-planning. However, it is also influenced by the quality of routing. Most reported systems use classical routing algorithms such as maze, line-probe, river routing and the left edge algorithm [Lefebvre97]. Routers based on the above combination generally rely on some net classification scheme based on the location of terminals associated with each net [Ong89]. Routing on a single

Figure 2.3 Delay and energy for increasing inverter sizes

metal layer incurs less delay. Similarly for zigzag as against straight wires with several metal layers switching in between. This is because of vias that are required to shift between metal layers. These vias have higher resistance and capacitance. Use of several of these can incur higher path delay. Figure 2.2 shows an example for such layout. The total capacitance (including the coupling capacitance) is less for the straight routing with many metals but the resistance is higher that eventually increases the path delays.

Custom ICs are typically manually floor-planned. Tools with the capacity to identify similar structures that may be abutted or placed next to each other appropriately will reduce area, reducing wire lengths and increasing performance. A bit slice may be laid out automatically then tiled, rather than the circuitry being placed without considering that it may be abutted [Chang98]. Regular data paths can be best laid out by hand or by tiling slices for abutment.

## 2.1.3 Transistor sizing

Based on the timing constraints, each transistor in a custom design is sized to meet the drive requirements of the capacitive load it faces. Increasing the sizes lowers the delay until the intrinsic capacitances start dominating as shown in Figure 2.3. Wires may be widened to reduce the delays (proportional to the product of resistance and capacitance) by reducing the resistance. Additional buffers may be included to drive large capacitive loads that would otherwise be charged and discharged too slowly. However, ASIC methodology requires cell selection from a fixed library, where transistor sizes and drive strengths are constrained to the library, and routing wire widths are usually fixed. Fundamentally, the discrete transistor sizes of a library only approximate the continuous transistor sizing of a custom design. ASIC cells typically include design guard banding, such as fully buffered flip-flop inputs, which introduces overhead. Hence a rich library of sizes with varied drive strengths and buffer sizes, as well as dual polarities for functions (gates with and without negated output) [Scott94] can impact the performance of ASIC design drastically. A richer library also reduces circuit area [Keutzer87].

Initial logic synthesis chooses drive strengths using estimated wire lengths and the net load a gate has to drive, but this will differ from that in the final layout. After placement gates are resized accounting for the drive strengths required to send signals across the circuit, and buffers are inserted or removed as necessary. Smaller transistors are used to reduce power consumption. However on critical paths transistors are optimally sized to meet speed requirements. They can make a speed difference of 20% or more [Fishburn85]. Later arriving signals can be routed closer to the gate output and transistors moved to maximize the adjacent drains and sources for diffusion sharing [Hill85]. Iterative gate resizing and resynthesis can improve speeds by 20% [Gavrilov97].

## 2.1.4 Design using Dynamic Gates

Dynamic logic is significantly faster than static CMOS logic and requires less area, but requires very careful design to ensure there is no glitching of input signals, limited cross talk between neighboring signals, no charge sharing and latching at the end to hold the evaluated value during the precharge phase. Nonetheless, they can be used to speed up critical paths within the circuit.

Dynamic logic libraries are not available for ASIC design, because of the difficulties and care required by dynamic logic. Design with dynamic logic requires careful consideration of noise and power consumption. Dynamic logic is particularly susceptible to noise, as any glitches on input voltages may cause a discharge of the charge stored, which should only occur when the logic function evaluates to false. Additionally, dynamic logic has higher power consumption, requiring careful design of the power distribution, and of the clock distribution as well; the clock determines when precharging occurs, and inputs must not glitch during or after the precharge. These problems become more pronounced with deeper submicron technologies.

#### 2.1.5 Reducing uncertainty in the design process

A higher frequency of operation can be achieved by accurately determining which paths in the design are critical and then applying local optimization to those parts [Stephen01]. In order to differentiate the critical from the non-critical paths, design must have minimal uncertainties in the design process. This enables one to apply global optimizations to the non-critical portions of the design and limit the costs of local optimizations to the critical paths.

Design uncertainty is caused by inaccuracy in the design analysis tools or unpredictable variations in the design between iterations. The unforeseen nature of the routing causes significant variations from iteration to iteration which may lead to reordering of the paths. This reduces the confidence that the critical path in any iteration will continue to be the critical path in future iterations. As the frequency increases, the tolerance for design uncertainty drops dramatically as the uncertainty becomes a larger percentage of the total cycle time. The sources of design uncertainty grow as the frequency increases and second order electrical effects become first order effects [Bai02]. By using a better design practice, such as prerouting, the uncertainty of routing can be significantly reduced between iterations. This helps to stabilize the path ordering attributed to such variations [Kheterpal04].

#### 2.2 Achieving low power design

For a specific application, the energy efficiency of different implementations can differ by multiple orders of magnitude [Chang05]. Implementation that uses dynamic logic dissipates more power due to higher activity factor than those that uses static logic to implement the same logic. Also, circuits sized with higher fanout also dissipate lesser power due to lower m wiring capacitance. Every design has a unique power versus performance characteristic. Maximizing the energy efficiency of a design enables the minimization of power dissipation by creating the largest range of trade-offs between performance and power. Increasing the efficiency of a design and reducing the power necessary to deliver the required application performance are achieved by accomplishing one or more of the following three basic goals:

- Moving along the power versus performance curve towards a more efficient operating point.

- ii) Reducing power dissipation by operating at a lower performance and lower-dissipation point.

- iii) Moving to a different power-performance curve by changing either the architecture or the process node.

For a fixed process technology, architectural choices have the greatest impact on the system's energy and power efficiency as they potentially enable the design to operate on an improved power-performance curve [Dally00] [Chinnery02].

#### 2.2.1 Dynamic Energy Optimization

Dynamic power dissipation is due to charging and discharging load capacitance as gates switch, as well as and short-circuit current while both PMOS and NMOS stacks are partially ON. Digital circuit dynamic power consumption (assuming constant frequency clock and balanced number of 0-to- 1, 1-to-0 transitions) is

$$P_{dyn} = \alpha C V_{DD}^2 f \tag{2.1}$$

where  $\alpha$  is the activity factor, and *f* is the switching frequency.

Hence the dynamic energy can be reduced by reducing any of these parameters. However the exponential dependence on  $V_{DD}$  makes it the more appealing parameter to minimize. The design can have dynamic lowering of supply voltage or creation of distinct voltage islands to reduce the energy dissipation. Lowering the supply voltage or gating the supply to the blocks are some of the techniques adopted to achieve lower energy [Borkar01]. Explicitly disabling unnecessary portions of the chip through clock-gating and/or block enables or dynamic frequency scaling are the methods to lower the frequency and the activity factor of the design. Redundant transitions in the address or data bus can be reduced by bit encoding [Weng05]. Elimination of glitches by optimizing the delays in converging paths will reduce the activity factor and subsequently the energy dissipation. Load matching, where each gate is sized according to its load driving capability, and parasitic reduction reduces the capacitive loads.

Switching capacitance comes from the wires and transistors in a circuit. Wire capacitance is minimized through good floorplaning and placement. Device switching capacitance is reduced by choosing fewer stages of logic and smaller transistors. Near minimum sized gates can be used on non-critical paths. Although logical effort finds that the best stage effort is 4, using a larger stage effort increases delay only slightly and greatly reduces the transistor sizes. Therefore, gates that are larger or have a high activity factor and thus dominate the power can be downsized with only a small performance impact as is depicted in Figure 2.3.

## 2.2.2 Optimizing the Static power dissipation

In nanometer processes with low threshold voltages and thin gate oxides, leakage can account for as much as a third of total active power. The main sources of static power dissipation in the digital ICs are:

- i) Sub-threshold leakage through OFF transistors

- ii) Gate leakage through gate dielectric

- iii) Junction leakage from source/drain diffusions

In semiconductor devices, the leakage power is an increasingly important contributor to overall design power and at sub-micron level; leakage power can be the dominant component of power consumption in specific applications. Two main contributors are sub-threshold leakage current ( $I_{sub}$ ) and gate-oxide leakage current ( $I_{ox}$ ). The basic equations for digital circuit static power consumption [Chandrakasan01] are:

$$P_{static} = V_{DD} \times (I_{sub} + I_{ox})$$

(2.2)

$$I_{sub} = K_1 W e \left( -\frac{V_t}{n V_{\theta}} \right) \left( 1 - e \left( -\frac{V_{gs}}{V_{\theta}} \right) \right)$$

(2.3)

$$I_{ox} = K_2 W \left(\frac{V_{gs}}{t_{ox}}\right)^2 e\left(-\frac{\alpha t_{ox}}{V_{gs}}\right)$$

(2.4)

where  $K_1$ ,  $K_2$ ,  $\alpha$  and n are empirically determined and W is the transistor width,  $V_{DD}$  is the supply voltage,  $V_{gs}$  is the gate-to source voltage,  $V_t$  is the threshold voltage, and  $V_{\theta}$  is the thermal voltage (kT/q, 25mV at 25 °C).

Similar to dynamic energy optimization,  $V_{DD}$  reduction also assists in reducing the static power. Power gating is a prominent technique in which power supply is gated off to the sleeping blocks [Agarwal06]. However, it requires the state to be saved or reset upon power-up [Little92]. Substituting high threshold devices in non-critical logic paths or by employing transistor stacking to generate negative body-to-source voltages, negative  $V_{gs}$  and reduce the effect of draininduced barrier lowering (DIBL) on V<sub>t</sub> and introducing body-bias (either static or active) to increase the effective V<sub>t</sub> which eventually reduces the static power. The leakage through two or more series transistors is dramatically reduced on account of the stack effect.

## 2.3 Optimizing placement of standard cell

Analyzing the various methodologies in the previous sections, interconnect routing seems to be one of dominant criteria for both speed and power. Large wire load requires either large driving devices that increase power dissipation or more buffering that incurs higher delay. For high performance chips, it is important to route each net such that it meets the timing requirement.

It has been well known that the placement quality has a profound impact on the routing complexity and hence the layout compactness. The length of the interconnect route directly depends on the placement of the cells. Timing assurance placement and routing methods have been reported previously [Dunlop84] [Burstein85] [Ogawa86] [Teig86] [Hauge87] [Jackson89]. Priority weight assignment for controlling wire length in automatic layout was proposed in [Dunlop84]. When a signal delay is above a specified upper bound after layout design, a high priority weight is assigned to the corresponding net and the placement and routing are rerun using the updated weight. The greater the weight of a net connecting two cells together, the closer they tend to be placed. However, in practice, when many nets are given high weights, the wire lengths of nets with high weights are not always short in the resulting layout. Thus, it needs various weights to control wire lengths, resulting in long design time. The methods proposed in [Burstein85] [Ogawa86] [Teig86] [Hauge87] are variations of net weighting. In a recent study [Jackson89], a performance-driven placement approach using LP (linear programming) optimization was proposed [Terai90].

Min-cut placement is one of the most practical and widely used placement techniques. It performs two dimensional placements [Dun83] to reduce the wiring density by partitioning the cells into two groups. In order to partition the cells above and below a horizontal line, the algorithm first determines the set of nets that must exist above and below that line. It then partitions the cells into two groups of approximately equal size. Once the partition in Y has been accomplished, it repeats the process in X, then in Y again, etc. At each step, it calculates the set of necessary connections on each side of the partition and uses this to guide the min-cut [Hill88].

For a net whose pin-pairs are too far apart, the constraint will not be meet even if it is interconnected with the shortest routing path. Thus the constraint becomes more important in the placement process than in the routing process. For this reason, a placement algorithm that controls wire lengths of nets is essential for timing assurance post-layout. Since placement has been proven to be computationally difficult, most modem placement is done in consecutive steps. First a global placement is carried out that tries to roughly spread the cells on the chip as evenly as possible. Then legalization of these cells, to align them in rows without overlaps follows. Finally, a detailed placement that further optimizes the legal placement to improve the placement quality according to certain criteria is carried out [Yanwu10].

The primary disadvantage of using this approach is the amount of CPU time required. The common weaknesses of the aforementioned, and most other existing cell placement algorithms, is that they all ignore the circuit properties. So in order to cope with this issue, the proposed structured methodology relies completely on the knowledge of the circuit designer for the placement. The design is built semi-custom using the standard cells and the designer places each of these standard cells in a spreadsheet as per the logic and also comprehends the timing of the design. Since the designer is the best judge for circuit functionality and optimization for the structured flow, the design is highly regular and can be repeated with minimal efforts as compared to the stochastic floor-plan of the standard cells every time placement effort is made in the ASIC flow. All the algorithms in the ASIC flow seeds a random number to start an initial placement and then optimize the overall floor-plan based on the constraints. Details of the proposed flow are highlighted in the following chapters.

# CHAPTER 3. PROPOSED STRUCTURED METHODOLOGY OF IC DESIGN

Achieving custom performance using ASIC methodologies is a big challenge for the IC industry. However, the required time, reliability and resource requirements of custom design are again a challenge. The blend of the two techniques where the ease of circuit design using standard cells with appropriate sizing and optimal logic implementation, along with the ease of placement and routing of the standard cells, seems to be a captivating solution. They not only allow the designer achieve higher productivity, circuit speed, lower power and lower area, but also facilitates the portability of the design from one technology node to other in a short span of time. In the proposed IC design methodology, both the custom techniques and the ASIC design steps are jointly exploited to achieve the desired performance with low complexity, ease of repeatability and methods to verify the design both functional and timing so as to develop a robust design.

#### 3.1 Overall flow of the structured methodology

The custom design requires analyzing the complete design architecture and micro-architecture level to gain maximum optimization. The design is then implemented in the schematic editor using the standard cell libraries. The regularity of the array based design makes this approach productive. Custom standard cell required to meet the requirement are also added to the libraries. Analysis of the design across multiple corners is subsequently carried out for timing verification using timing tools like Synopsys Prime Time. At this point,

Figure 3.1: The proposed structured design flow

since the design is not routed, the wire delay is ignored. However, the timing tool checks for the proper drive strengths of standard cells by analyzing the transitions at every node in the critical path. Optimal use of the standard cells and proper signal transition rates helps not only to achieve optimal delay but also lower energy dissipation in the design.

Once design at the schematic level is finalized, the floor-planning of these standard cells is carried out. This is done by placing the cells in a spreadsheet, each cell of which corresponds to each instantiation of the standard cell in the design. Since global wires between physical modules are a dominant portion of the total path delay, proper placement of the standard cells and their drivers make the path delay within the design limit, thus achieving high speed. The spreadsheet

Figure 3.2: Schematic of the 4-bit adder

is then read by Perl scripts that convert it into a placement file readable by the Cadence Encounter routing tool for actual placement of the standard cells in its floor-plan. The floor-plan in the Cadence Encounter can be analyzed and the standard cells can be replaced to obtain better area. By simply swapping or shifting the placed cells in the spreadsheet and re-running the Perl scripts to obtain the new placements, the task is productive and allows designer flexibility of moving the cells across for area and delay optimization.

As soon as the Encounter floor-plan is settled, the routing of all the cells is carried out using the Encounter auto-route tool. This is the step where the ASIC design methodology is used. Since the algorithms for routing are resonably optimal and regular, they can give similar results as manual routing but at far less effort. The netlist and the timing information (that captures the estimated wire delays) from the routed block can then be extracted. The timing tool then reanalyzes the block but this time with estimated wire RC delays. Changes, if required, can be carried out in the spreadsheet for placement changes or in the schematic for better drive strengths in case the cell is driving long wire. Since // Verilog HDL and netlist files of

// "4-bit\_adder 4-bit schematic"

// Netlisted models

// netlist file - RHBDcellLibSF\_NDHv4, nand3x0018, schematic. ihnl/cds0/netlist // netlist file - RHBDcellLibSF\_NDHv4, nand2x010, schematic. ihnl/cds1/netlist // netlist file - RHBDcellLibSF\_NDHv4, xnor2x010, schematic. ihnl/cds2/netlist // netlist file - 4-bit\_adder, full\_adder, schematic. ihnl/cds3/netlist // netlist file - 4-bit\_adder, 4-bit, schematic. ihnl/cds4/netlist

// End HDL models

// globals file hdlFilesDir/cds\_globals.v

#### Figure 3.3 Output of the verilog.infile

these steps are fast and require less effort, the proposed methodology generates a design with better performance, regularity, repeatability, and ease of portability. The main labor required by the designer is only in making the micro-architecture of the design and circuit design as embodied by the schematic.

## 3.2 Generating the placement file from Perl scripts

Details of the Perl script usage and steps to obtain the final placement file are explained in the following sections. For better understanding the methodology, an example with 4-bit adder design is also presented.

# 3.2.1 Creating the flatten netlist file

Once the micro-architecture of the design using the designated standard cell library is completed, the schematic of the design is created in the Virtuoso Schematic editor. Verilog-XL is invoked by selecting tools  $\rightarrow$  simulations. In order to set the netlisting options, select the setup tab and Netlist in the Virtuoso Verilog Environment for Verilog-XL integration window. In the Verilog Netlisting Options window check *Generate Test Fixture Template*, and *Netlist Explicitly*. All other options must be unchecked. *Generate Test Fixture Template*

standard cell ihnl/cds0/netlist ihnl/cds1/netlist ihnl/cds2/netlist macro cell ihnl/cds3/netlist ihnl/cds4/netlist

#### Figure 3.4 Content of netlist\_file