# A Bang-Bang All-Digital PLL for Frequency Synthesis

by

Joshua Zazzera

A Thesis Presented in Partial Fulfillment of the Requirements for the Degree Master of Science

Approved January 2012 by the Graduate Supervisory Committee:

Bertan Bakkaloglu, Chair Hongjiang Song Sule Ozev

#### **ABSTRACT**

Phase locked loops are an integral part of any electronic system that requires a clock signal and find use in a broad range of applications such as clock and data recovery circuits for high speed serial I/O and frequency synthesizers for RF transceivers and ADCs. Traditionally, PLLs have been primarily analog in nature and since the development of the charge pump PLL, they have almost exclusively been analog. Recently, however, much research has been focused on ADPLLs because of their scalability, flexibility and higher noise immunity. This research investigates some of the latest all-digital PLL architectures and discusses the qualities and tradeoffs of each.

A highly flexible and scalable all-digital PLL based frequency synthesizer is implemented in 180 nm CMOS process. This implementation makes use of a binary phase detector, also commonly called a *bang-bang* phase detector, which has potential of use in high-speed, sub-micron processes due to the simplicity of the phase detector which can be implemented with a simple D flip flop. Due to the nonlinearity introduced by the phase detector, there are certain performance limitations. This architecture incorporates a separate frequency control loop which can alleviate some of these limitations, such as lock range and acquisition time.

## TABLE OF CONTENTS

|                                                                    | Page |

|--------------------------------------------------------------------|------|

| LIST OF TABLES                                                     | iv   |

| LIST OF FIGURES                                                    | v    |

| CHAPTER                                                            |      |

| 1 INTRODUCTION                                                     | 1    |

| 1.1: Motivation                                                    | 1    |

| 1.2: Thesis Organization                                           | 3    |

| 2 CHARGE PUMP PLL                                                  | 4    |

| 2.1: PLL Fundamentals                                              | 4    |

| 2.2: CPPLL Building Blocks                                         | 5    |

| 2.2.1: Phase Detector                                              | 6    |

| 2.2.2: Charge Pump and Loop Filter                                 | 13   |

| 2.2.3: VCO                                                         | 15   |

| 2.2.4: Frequency Divider                                           | 17   |

| 2.3: Jitter and Phase Noise                                        | 18   |

| 2.4: Analysis and Parameter Selection                              | 20   |

| 2.4.1: Small Signal Analysis for 2 <sup>nd</sup> Order Analog PLLs | 20   |

| 2.5: Analog PLL non-idealities                                     | 24   |

| 3 ALL-DIGITAL PLL                                                  | 26   |

| 3.1: All-Digital PLL Building Blocks                               | 26   |

| 3.1.1: Time to Digital Converter                                   | 27   |

| 3.1.2: Digital Loop Filter                                         | 35   |

| 3.1.3: Digitally Controlled Oscillator                             | 36   |

| 3.1.4: Frequency Divider                                           | 38   |

| 3.2: Limit Cycles and Quantization Noise in ADPLLs                 | 39   |

| CHAPTER                                                   | Page |

|-----------------------------------------------------------|------|

| 3.3: State of the Art                                     | 39   |

| 4 CIRCUIT DESIGN AND IMPLEMENTATION                       | 43   |

| 4.1: Application                                          | 43   |

| 4.2: Specifications                                       | 45   |

| 4.3: Design                                               | 46   |

| 4.3.1: Top Level                                          | 47   |

| 4.3.2: Frequency Divider                                  | 48   |

| 4.3.3: Phase Controller and Loop Filter                   | 49   |

| 4.3.4: Frequency Detector                                 | 52   |

| 4.3.5: Frequency Controller                               | 55   |

| 4.3.6: Digital to Analog Converter                        | 57   |

| 4.3.7: Current Controlled Oscillator                      | 61   |

| 4.4: Analysis and Parameter Selection for Bang-Bang ADPLL | 64   |

| 4.4.1: Non-Linear Analysis and Design                     | 65   |

| 4.4.2: Linearized Analysis and Design                     | 67   |

| 5 RESULTS                                                 | 74   |

| 6 CONCLUSION                                              | 92   |

| 6.1: Conclusion                                           | 92   |

| 6.2: Future Work                                          | 92   |

| 6.2.1: Layout and Verification                            | 92   |

| 6.2.2: Post Silicon Validation                            | 93   |

| 6.2.3: Design Features and Improvements                   | 95   |

| REFERENCES                                                | 99   |

## LIST OF TABLES

| Table                          | Page |  |

|--------------------------------|------|--|

| Table 1. ADPLL Specifications. | 46   |  |

| Table 2. Simulation Corners.   | 84   |  |

| Table 3. Performance Summary   | 91   |  |

## LIST OF FIGURES

| Figure Page                                                                       |

|-----------------------------------------------------------------------------------|

| Figure 1. Clock recovery application of PLLs. 2                                   |

| Figure 2. RF synthesizer application of PLLs                                      |

| Figure 3. Block diagram of PLL. 4                                                 |

| Figure 4. Block diagram of clock multiplying PLL5                                 |

| Figure 5. Charge pump PLL6                                                        |

| Figure 6. Gilbert cell                                                            |

| Figure 7. AND gate phase detector and transfer characteristic                     |

| Figure 8. OR gate phase detector and transfer characteristic                      |

| Figure 9. XOR gate phase detector and transfer characteristic                     |

| Figure 10. Standard logic phase detector timing diagrams                          |

| Figure 11. Data phase detector                                                    |

| Figure 12. Phase frequency detector and transfer characteristic                   |

| Figure 13. PFD timing diagram with input signals at same frequency and with phase |

| difference. 12                                                                    |

| Figure 14. PFD timing diagram for input signals with different frequencies        |

| Figure 15. PFD timing diagrams in phase lock                                      |

| Figure 16. Basic charge pump and loop filter                                      |

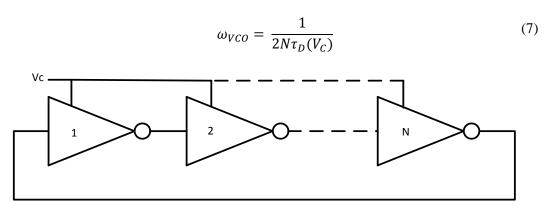

| Figure 17. Ring oscillator with controlled delay                                  |

| Figure 18. Fully differential ring oscillator                                     |

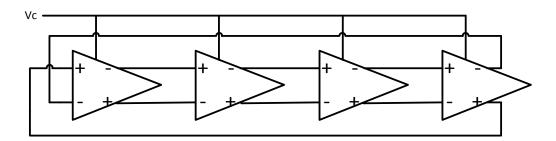

| Figure 19. Tunable LC tank based VCO                                              |

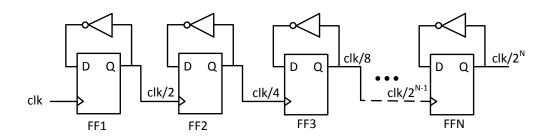

| Figure 20. Frequency divider                                                      |

| Figure 21. Programmable frequency divider                                         |

| Figure     | Р                                                     | age  |

|------------|-------------------------------------------------------|------|

| Figure 22. | Timing jitter                                         | . 19 |

| Figure 23. | Simplified schematic of a charge pump PLL.            | .20  |

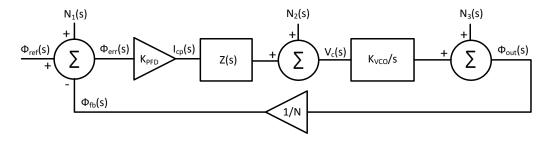

| Figure 24. | PLL small signal model.                               | .21  |

| Figure 25. | PLL small signal model with noise sources.            | .22  |

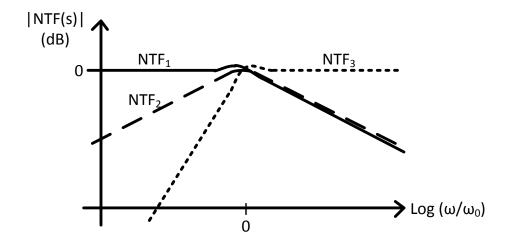

| Figure 26. | 2 <sup>nd</sup> order PLL noise transfer functions    | .23  |

| Figure 27. | Dead zone of PFD.                                     | . 24 |

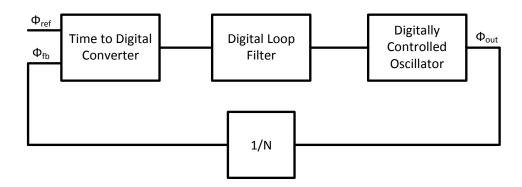

| Figure 28. | Block diagram of ADPLL.                               | .26  |

| Figure 29. | Simple time to digital converter.                     | .28  |

| Figure 30. | Vernier delay line based TDC.                         | . 29 |

| Figure 31. | TDC using DLL to control the delay.                   | .30  |

| Figure 32. | Generic transfer function of TDC                      | .30  |

| Figure 33. | Stochastic TDC                                        | .32  |

| Figure 34. | Stochastic TDC transfer characteristic.               | .32  |

| Figure 35. | Alexander phase detector                              | .33  |

| Figure 36. | Bang-bang phase detector and transfer characteristic. | .34  |

| Figure 37. | Digital PFD                                           | .35  |

| Figure 38. | Continuous and discrete time equivalent loop filters. | .36  |

| Figure 39. | Gated ring oscillator-based DCO.                      | .37  |

| Figure 40. | LC tank-based DCO.                                    | .38  |

| Figure 41. | DAC and VCO-based DCO                                 | .38  |

| Figure 42. | Serializer top level.                                 | . 44 |

| Figure 43. | 14 bit mux                                            | .45  |

| Figure 44. | ADPLL block diagram.                                  | .46  |

| Figure 45. | Top level of ADPLL.                                   | .47  |

| Figure     | Pa                                                                               | age  |

|------------|----------------------------------------------------------------------------------|------|

| Figure 46. | Frequency divider.                                                               | .48  |

| Figure 47. | Reset logic.                                                                     | .48  |

| Figure 48. | Small signal model of 2 <sup>nd</sup> order PLL loop filter.                     | .50  |

| Figure 49. | Z-domain equivalent of 2 <sup>nd</sup> order PLL loop filter                     | .50  |

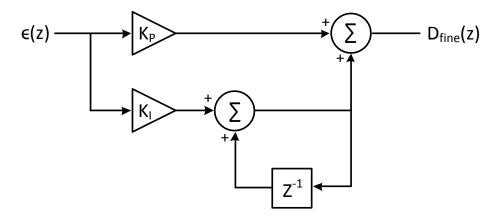

| Figure 50. | Implementation of digital 2nd order PLL loop filter.                             | .51  |

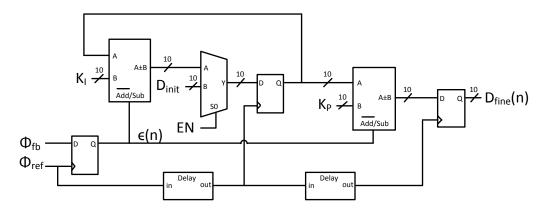

| Figure 51. | Adder/subtractor.                                                                | .52  |

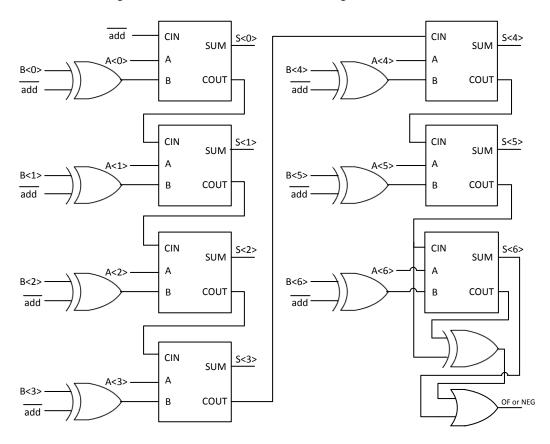

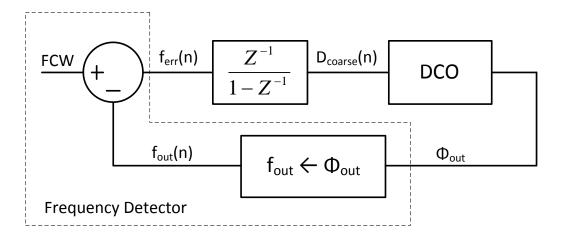

| Figure 52. | Frequency control loop.                                                          | .53  |

| Figure 53. | Frequency detector.                                                              | . 54 |

| Figure 54. | 6-bit counter                                                                    | . 54 |

| Figure 55. | Frequency control                                                                | .56  |

| Figure 56. | Lock detect logic.                                                               | .56  |

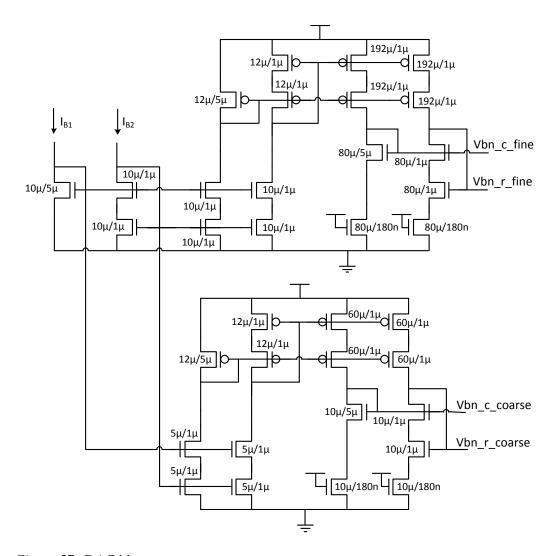

| Figure 57. | DAC bias.                                                                        | .58  |

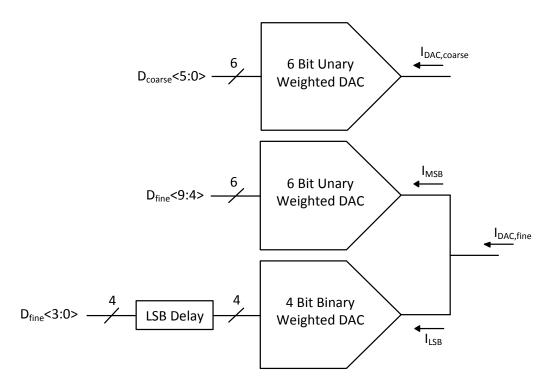

| Figure 58. | Segmented current DAC top level                                                  | . 59 |

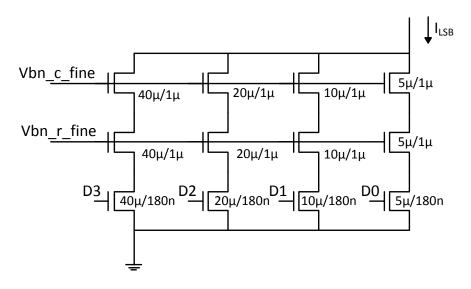

| Figure 59. | 4 bit binary weighted DAC                                                        | .59  |

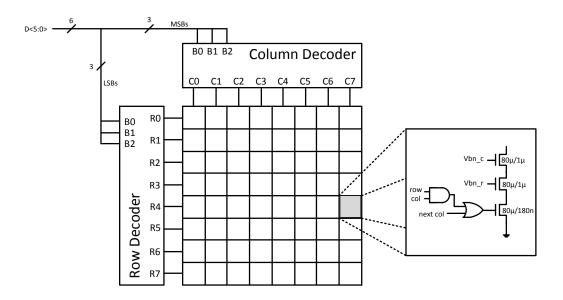

| Figure 60. | 6 bit unary weighted (thermometer coded) DAC [30]                                | . 60 |

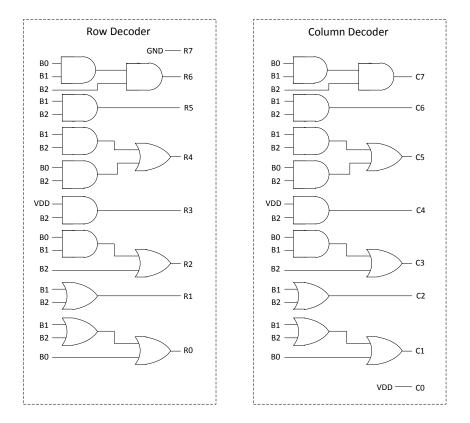

| Figure 61. | Row and column decoders                                                          | . 60 |

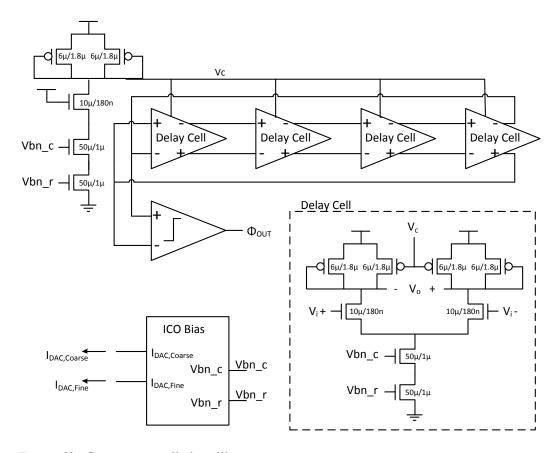

| Figure 62. | Current controlled oscillator.                                                   | . 62 |

| Figure 63. | ICO bias                                                                         | . 62 |

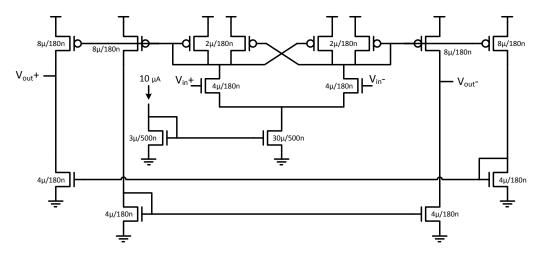

| Figure 64. | DCO comparator.                                                                  | . 63 |

| Figure 65. | Simplified block diagram of bang-bang ADPLL.                                     | . 64 |

| Figure 66. | Modeling BBPD using delta-sigma modulator approximation [40]                     | . 67 |

| Figure 67. | Non-linear small signal model of bang-bang ADPLL                                 | . 68 |

| Figure 68. | Linearized small signal model of bang-bang ADPLL                                 | . 68 |

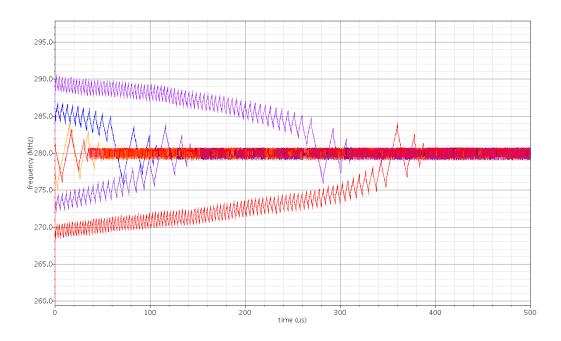

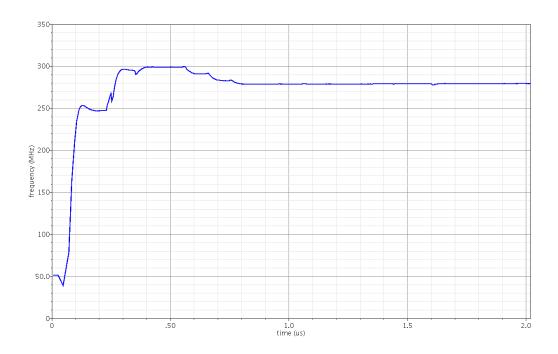

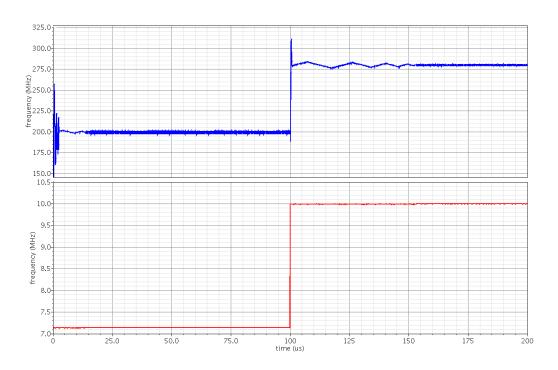

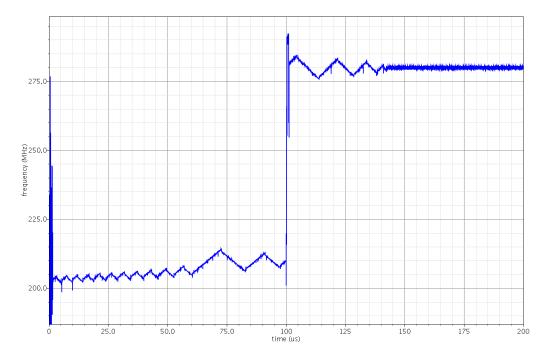

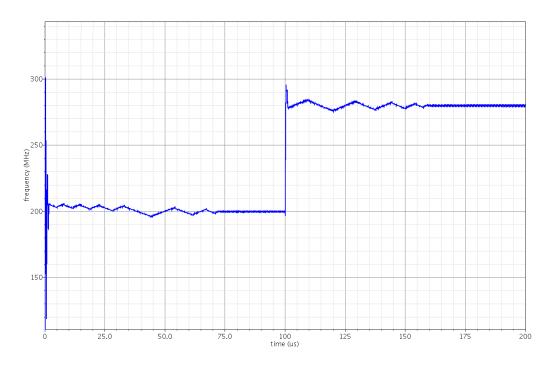

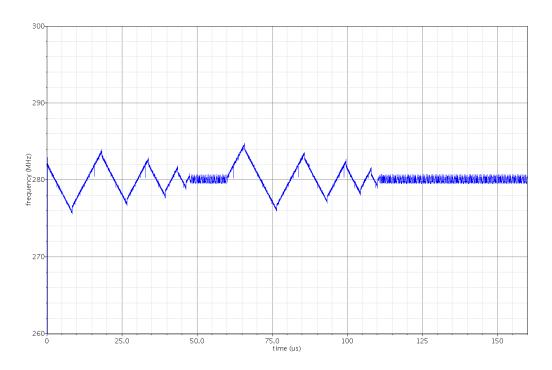

| Figure 69. | Lock time for various start frequencies (behavioral DCO, $K_p = 4$ , $K_i = 1$ ) | .74  |

| Figure     | Page                                                                                |

|------------|-------------------------------------------------------------------------------------|

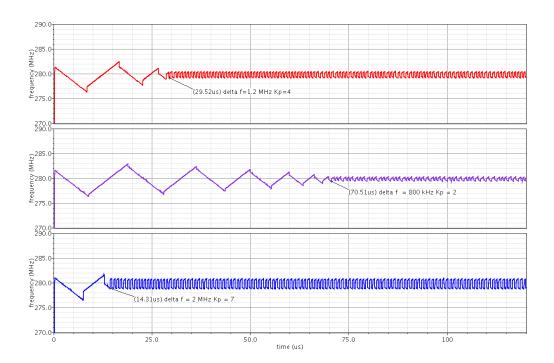

| Figure 70. | Lock time for various $K_p$ (behavioral DCO, $K_i=1$ )75                            |

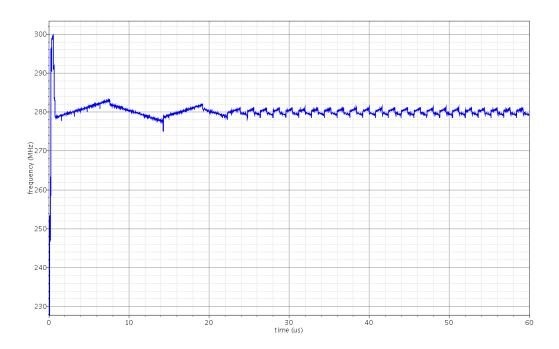

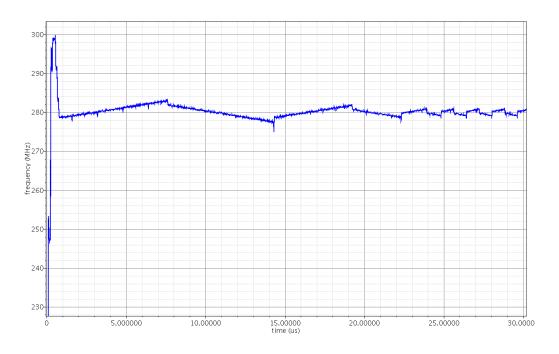

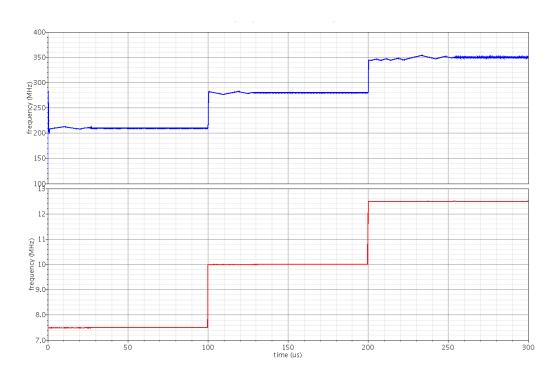

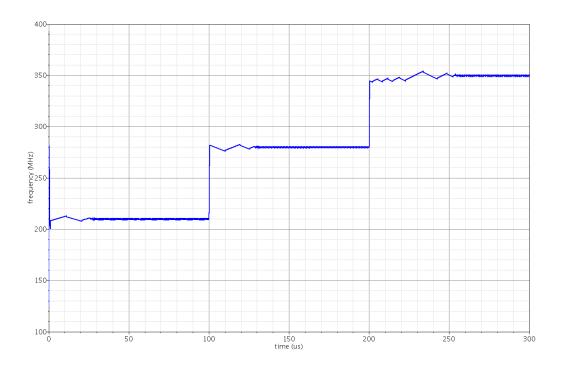

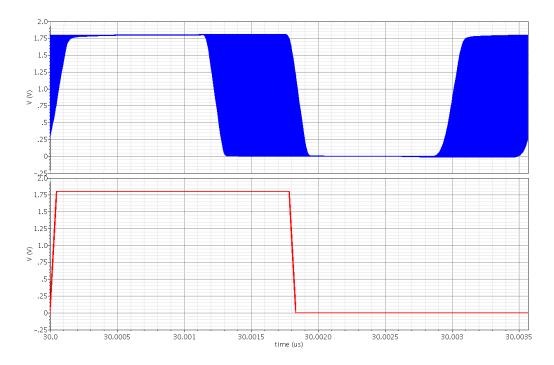

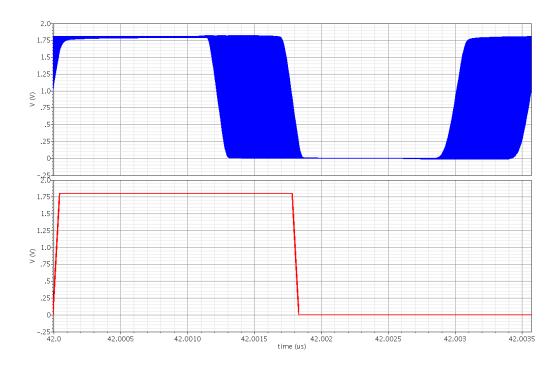

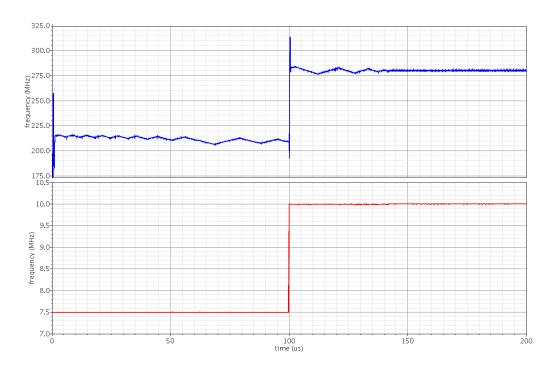

| Figure 71. | Transient with FLL and PLL (BSIM 3.3 DCO, $K_p=8$ , $K_i=1$ )76                     |

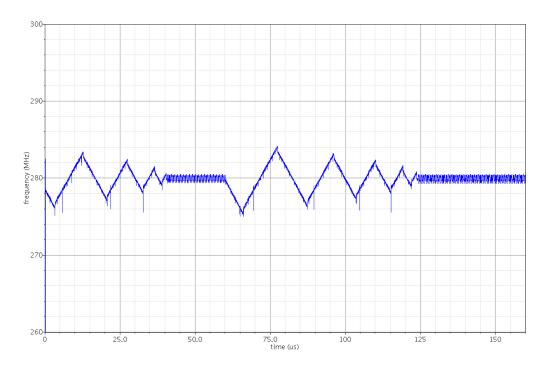

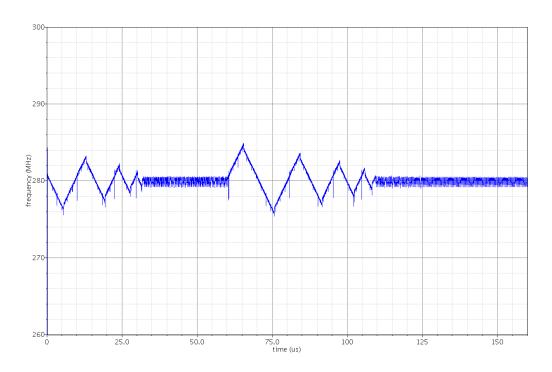

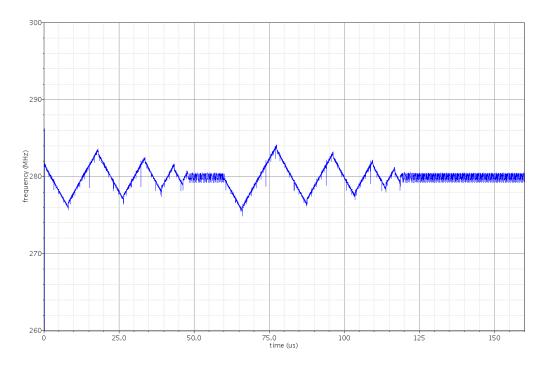

| Figure 72. | Transient with FLL and PLL zoomed (BSIM 3.3 DCO, $K_p=8$ , $K_i=1$ )77              |

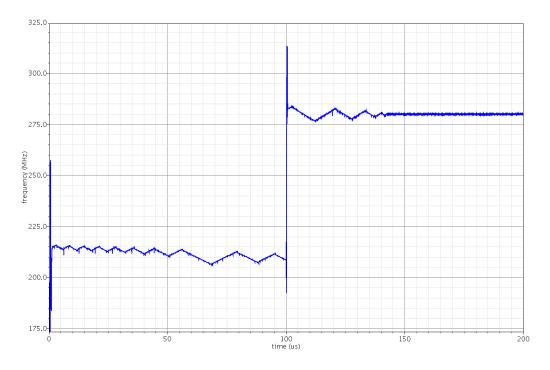

| Figure 73. | Transient with FLL and PLL zoomed further (BSIM 3.3 DCO, $K_p$ =8, $K_i$ =1).       |

|            | 77                                                                                  |

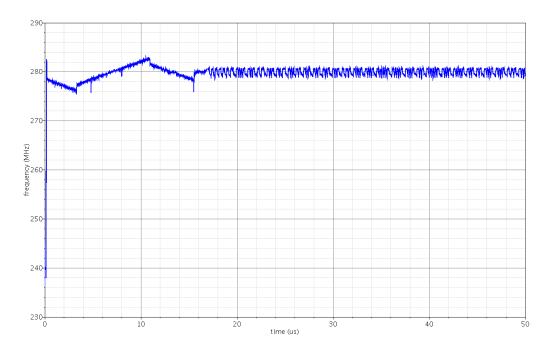

| Figure 74. | Step response (Behavioral DCO, K <sub>p</sub> =8, K <sub>i</sub> =1)                |

| Figure 75. | Step response without reference (Behavioral DCO, $K_p=8$ , $K_i=1$ )79              |

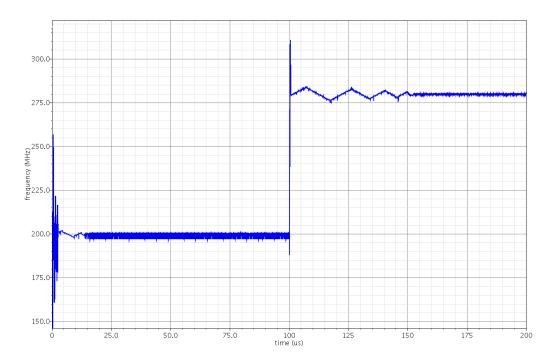

| Figure 76. | Transient without DLL (BSIM 3.3 DCO, K <sub>p</sub> =8, K <sub>i</sub> =1)80        |

| Figure 77. | Persistence plot without DLL (BSIM 3.3 DCO, K <sub>p</sub> =8, K <sub>i</sub> =1)80 |

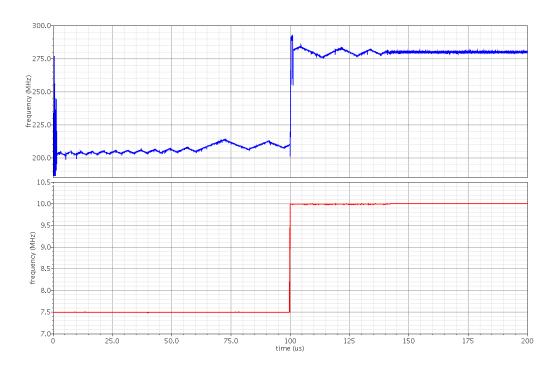

| Figure 78. | Transient without DLL (BSIM 3.3 DCO, K <sub>p</sub> =4, K <sub>i</sub> =1)81        |

| Figure 79. | Persistence plot without DLL (BSIM 3.3 DCO, Kp=4, Ki=1)82                           |

| Figure 80. | Transient without DLL with 20 mVpp, 1 MHz supply noise (BSIM 3.3 DCO,               |

| Kp=4, Ki=  | -1)83                                                                               |

| Figure 81. | Persistence plot without DLL with 20 mVpp, 1 MHz supply noise (BSIM 3.3             |

| DCO, Kp=   | -4, Ki=1)84                                                                         |

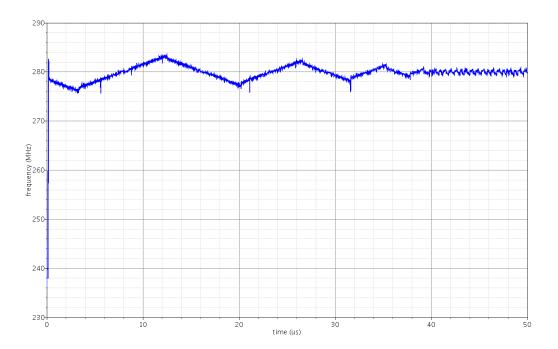

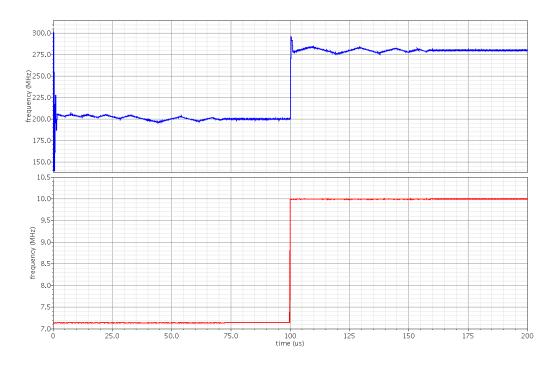

| Figure 82. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'nom')85                         |

| Figure 83. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'nom')85                         |

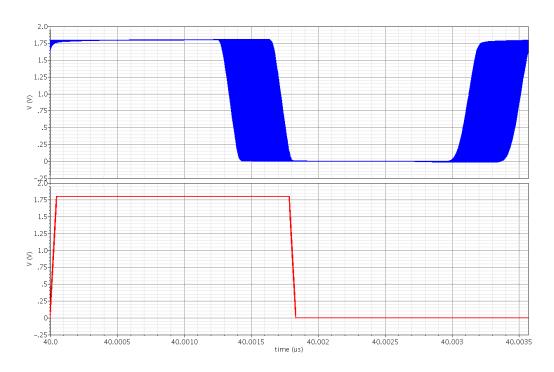

| Figure 84. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'fast')86                        |

| Figure 85. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'fast')86                        |

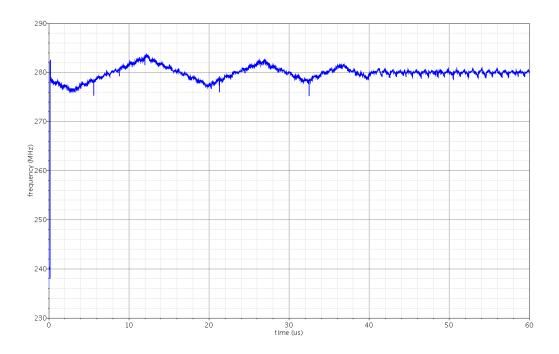

| Figure 86. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'slow')87                        |

| Figure 87. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'slow')87                        |

| Figure 88. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'room temp')88                   |

| Figure 89. | Frequency step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'room temp')88                   |

| Figure 90. | Phase step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'nom')89                             |

| Figure                                                                  | Page |

|-------------------------------------------------------------------------|------|

| Figure 91. Phase step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'fast')       | 90   |

| Figure 92. Phase step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'slow')       | 90   |

| Figure 93. Phase step response (BSIM 3.3 DCO, Kp=4, Ki=1, 'room temp'). | 91   |

| Figure 94. Evaluation board setup.                                      | 95   |

### Chapter 1: INTRODUCTION

#### 1.1: Motivation

Phase locked loops (PLLs) are critical components to any digital or mixed-signal system that requires an accurate clock signal. PLLs find applications in communications, wireless transceivers, data converters and other mixed signal systems. Two particular applications of PLLs are data recovery circuits and frequency synthesis. In clock and data recovery circuits used in high-speed I/O systems, the PLL can be used to recover the clock signal embedded in a serial data stream and capture the data using this recovered clock signal to sample the data optimally to minimize error in data transmission. In wireless transceivers which require a local oscillator signal which is some multiple of a stable crystal oscillator frequency, the PLL is used for frequency synthesis and facilitates mixing for baseband processing or high frequency transmission. Other uses of PLLs are clock generation and distribution, jitter filtering, and clock skew removal.

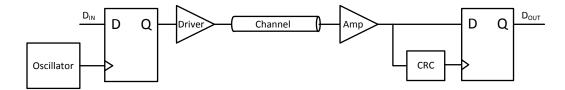

A simplified high speed I/O link is shown in Figure 1 which can be any serial link such as USB, PCI Express, SATA, etc. This basic configuration consists of a transmitter on one chip and a receiver on another chip separated by a long electrical, and possibly physical, distance. The transmitter and receiver are connected by the channel which can be a long cable which causes frequency dependent attenuation of the signal and other detrimental transmission line effects such as ringing. The transmitted data is synchronized with one clock and the clock is recovered from the data at the receiver end and used to capture the data. The circuit that extracts the clock from the received data is the clock recovery circuit, or CRC. The CRC and receiver flip flop make up the data recovery circuit, or DRC. The CRC is made up of a PLL which typically consists of a data phase detector, loop fil-

ter and VCO. The clock generated by the CRC sample the received data such that the bit error rate can be minimized.

Figure 1. Clock recovery application of PLLs.

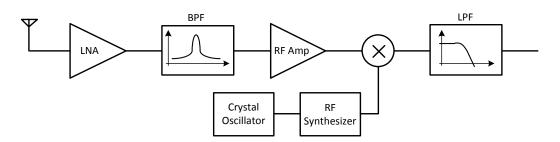

Another important application that utilizes PLLs is frequency synthesis in RF transceivers. A simplified RF receiver system is shown in Figure 2. The low level wireless signal is picked up by the antenna and amplified by the low noise amplifier, or LNA. This amplified signal is then band-pass filtered and amplified again. This amplified and spectrally pure signal is then mixed with a local oscillator, LO, and low-pass filtered which converts it to the baseband for processing. The LO is generated by another configuration of the PLL known as a frequency synthesizer which consists of a clock phase detector or phase-frequency detector, loop filter, VCO and frequency divider. The crystal oscillator generates a spectrally pure, low frequency clock signal which is essentially multiplied by the feedback action in the PLL.

Figure 2. RF synthesizer application of PLLs.

Since the development of PLLs using a phase frequency detector and charge pump, the charge pump based PLL has been the dominant choice in high performance clock recovery and frequency synthesis applications. Although the concept of digital phase locked

loops has been around since the 1970's [15], it is only within the last decade that all-digital PLLs have gained much attention from researchers. As process geometries continue to scale down and more systems are being integrated on a single chip, sensitive analog circuitry is being surrounded by more and more noisy digital circuitry. This is especially true in wireless communication SoCs. Since analog circuitry does not scale as well as digital, it has become necessary to limit analog circuitry wherever possible, including PLLs.

All-digital implementations of PLLs are necessary to reduce the sensitivity to process, voltage and temperature (PVT) variations as well as minimize circuit area, power and noise susceptibility. Loop filter capacitor leakage and design portability are other very important reasons for going digital. The goal of this thesis is to explore the current state of the art in ADPLLs and implement a high performance, low power, highly integrated ADPLL in a 180 nm CMOS process.

### 1.2: Thesis Organization

Chapter 2 introduces the basic concept of phase locking and discusses different implementations of analog phase locked loops with emphasis on the charge pump based PLL. The various building blocks and implementations as well as modeling of these blocks and the system are examined. Chapter 3 introduces the all-digital PLL and surveys different implementations and discusses the state of the art of these systems. Chapter 4 discusses an application of an all-digital PLL and covers its specification, design and circuit implementation. Chapter 5 examines the simulation results and Chapter 6 concludes the work.

#### Chapter 2: CHARGE PUMP PLL

#### 2.1: PLL Fundamentals

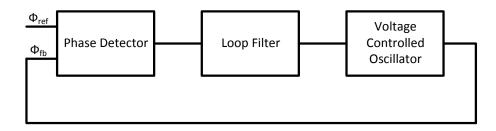

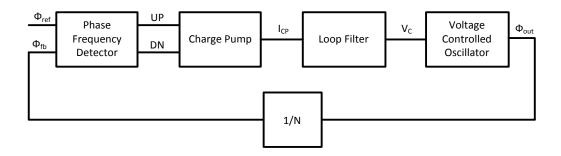

PLLs can be thought of as a phase buffer circuit. A typical PLL block diagram is shown in Figure 3. These blocks will be discussed in detail in the following sections. The PLL attempts to keep the phase difference between the reference clock,  $\Phi_{ref}$ , and the feedback clock,  $\Phi_{fb}$ , zero through negative feedback. This mechanism is very similar to the feedback mechanism in a voltage follower circuit, except in the phase domain. This type of circuit is particularly useful in clock distribution in microprocessors and SoCs and data recovery circuits in communications systems.

Figure 3. Block diagram of PLL.

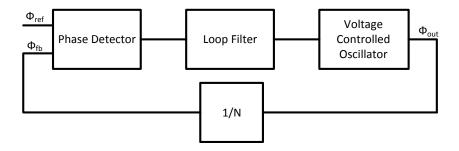

The PLL can also be used to generate a higher frequency which is a multiple of the reference frequency which is known as *frequency synthesis*. Frequency synthesis is commonly used in systems that require a stable clock frequency generated from a much lower frequency but more stable crystal oscillator. Figure 4 shows the basic diagram of the clock multiplying PLL. The added block is a frequency divider which can also be programmable as discussed later. The PLL attempts to keep the phase difference very small between  $\Phi_{ref}$  and  $\Phi_{fb}$ , and if a phase-frequency detector (to be discussed later) is used, the frequency of  $\Phi_{ref}$  and  $\Phi_{fb}$  will also be identical which means the frequency of signal  $\Phi_{out}$  must be N times higher than the frequency of  $\Phi_{fb}$  and  $\Phi_{ref}$ . This is analogous to the voltage amplification that occurs when an opamp is set up in a non-inverting feedback con-

figuration with a voltage divided output signal fed back to the negative input and the positive terminal connected to a reference voltage.

Figure 4. Block diagram of clock multiplying PLL.

### 2.2: CPPLL Building Blocks

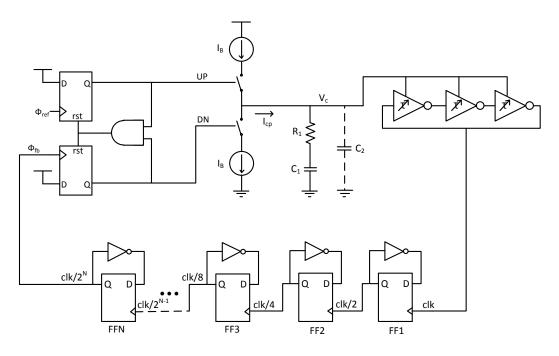

Most high performance frequency synthesizers are implemented using the charge pump based PLL as shown in Figure 5. The phase frequency detector detects the phase, and frequency, difference between the reference and divided clock signals and generates UP and DN signals. The charge pump outputs a square wave output current whose average value is proportional to the phase and frequency difference detected in the PFD. The loop filter removes the high frequency components from the square wave and converts the current signal to a voltage signal which is the input to the next stage, the voltage controlled oscillator. The VCO generates a signal whose frequency is proportional to the input voltage. This output signal frequency is divided by N by the frequency divider and the output of the frequency divider is fed to the input of the PFD to be compared to the reference clock signal.

Figure 5. Charge pump PLL.

#### 2.2.1: Phase Detector

The phase detector is a circuit that generates an output signal whose average value is linearly related to the difference in phase of the reference clock and the divided clock signals. This relationship can be described by the equation,

$$Y_{out,avg} = A(\Phi_{ref} - \Phi_{div}), \tag{1}$$

In this equation,  $Y_{out,avg}$  is the average value of the output signal in a given period and can be a voltage, current or charge depending on the particular implementation.

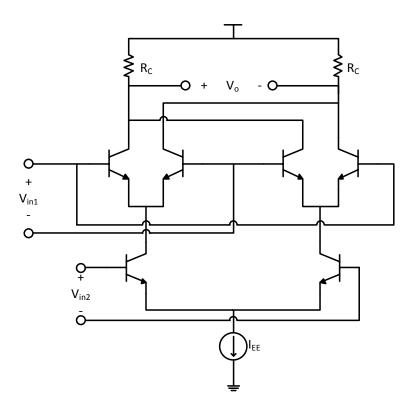

Phase detection can be accomplished in a number of ways. Early on, phase detection was accomplished through analog multiplication. In general, if  $V_{in1}$  and  $V_{in2}$  are sinusoidal signals at frequencies of  $\omega_1$  and  $\omega_2$ , with phases  $\Phi_1$  and  $\Phi_2$ , then the product signal will contain terms which are sums and differences of the total phase of each signal.

$$V_{in1} = \cos(\omega_1 t + \Phi_1) \tag{2}$$

$$V_{in2} = \cos(\omega_2 t + \Phi_2) \tag{3}$$

$$V_{out} = V_{in1}V_{in2} = \frac{1}{2}(\cos((\omega_1 - \omega_2)t + \Phi_1 - \Phi_2) + \cos((\omega_1 + \omega_2)t + \Phi_1 + \Phi_2))$$

(4)

If  $\omega_1 = \omega_2 = \omega_0$ , Equation 4 simplifies to

$$V_{out} = V_{in1}V_{in2} = \frac{1}{2}(\cos(\Phi_1 - \Phi_2) + \cos(2\omega_0 t + \Phi_1 + \Phi_2))$$

(5)

The average or DC term is proportional to  $\cos(\Phi_1 - \Phi_2)$ . While this method does in fact produce an output with a DC value dependent on the phase difference of the input signals, the dependence is not linear. Analog multiplication can be accomplished using the Gilbert cell, shown in Figure 6[14].

Figure 6. Gilbert cell.

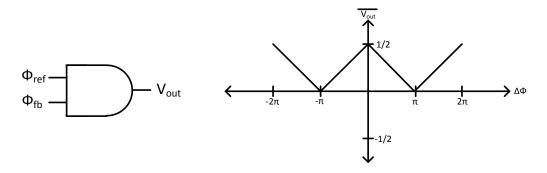

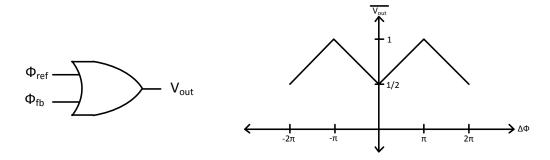

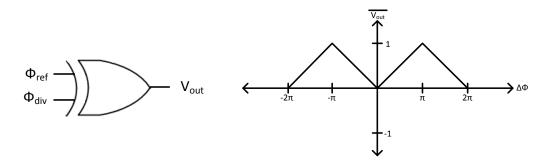

Linear phase detection can also be implemented with standard CMOS logic gates. AND, OR, XOR and latches can be used to generate output voltages whose average value is linearly dependent on the phase difference of the input signals. The output of CMOS logic phase detectors is actually a PWM signal which is digital in the voltage domain but analog in the time or phase domain, so these phase detectors are considered to be analog phase detection circuits.

Figure 7. AND gate phase detector and transfer characteristic.

Figure 8. OR gate phase detector and transfer characteristic.

Figure 9. XOR gate phase detector and transfer characteristic.

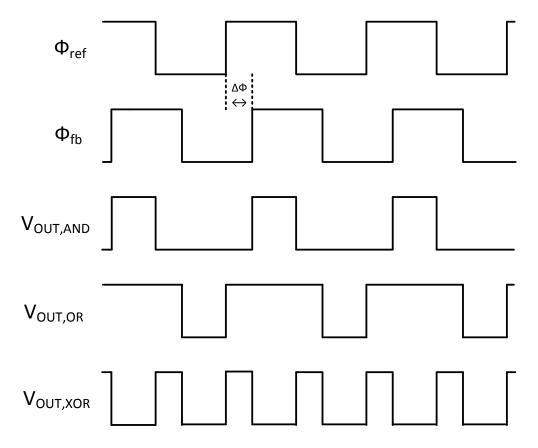

Figure 10. Standard logic phase detector timing diagrams.

The timing diagrams for some standard logic phase detectors are shown in Figure 10. The output of standard logic phase detectors are typically low pass filtered and then passed to the VCO, so the average (DC) value of the phase detector output is of interest. It can be seen in the figures above that the static logic phase detector circuits have voltage and phase offsets. The Gilbert cell (digital CMOS version) however has zero voltage offset and the *double XOR* structure has zero voltage and phase offset as discussed in [33]. These phase detectors do still suffer from limited linear range and duty cycle distortion effects.

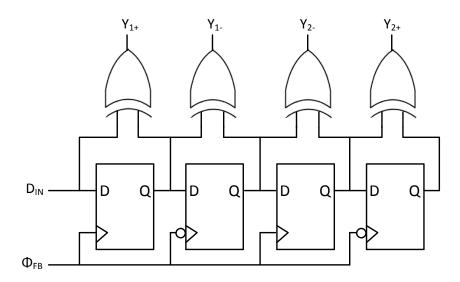

The phase detectors discussed so far are typically used for clock synthesis applications. In clock and data recovery applications, a data phase detector circuit is used to determine the phase difference between the incoming data and the recovered clock. In CDR cir-

cuits, the incoming data frequency has a maximum frequency of half the recovered clock.

One data phase detector implementation is shown in Figure 11. In this data phase detector, the average output voltage is calculated as

$$\overline{Y_{OUT}} \equiv \overline{Y_{1+} - Y_{1-} + Y_{2+} - Y_{2-}} \tag{6}$$

The linear range of this particular implementation is increased to  $2\pi$ , compared to only  $\pi$  of the previously discussed clock phase detector circuits. There is still a voltage and phase offset, as in the basic static logic clock phase detectors. There are a variety of different clock and data phase detector circuits each with their own merits as described in [33].

Figure 11. Data phase detector.

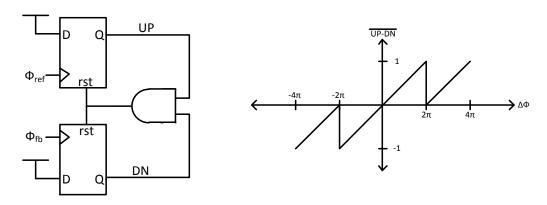

Due to the duty cycle distortion sensitivity, phase and voltage offsets and limited linear range of these standard logic phase detectors, they may necessitate additional circuitry. In applications like frequency synthesis and clock distribution, phase frequency detectors (PFDs) are widely used. The basic PFD is shown in Figure 12. There are many variations of this circuit, but all perform the same fundamental function. In this circuit, it is the average difference of the UP and DN signals that is of interest. One advantage of the

PFD is the ability to not only detect the phase difference but also the frequency difference of the reference and divided clock signals. Insensitivity to duty cycle distortion, increased linear range, and zero phase and voltage offset are other key advantages of this structure.

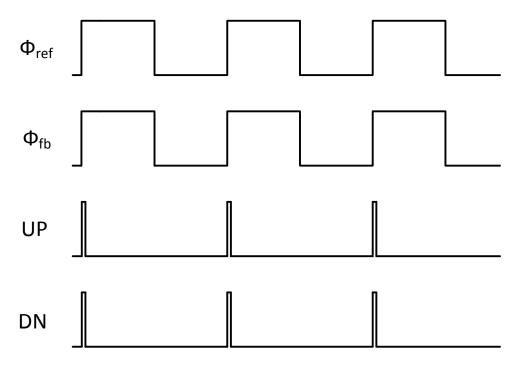

Figure 12. Phase frequency detector and transfer characteristic.

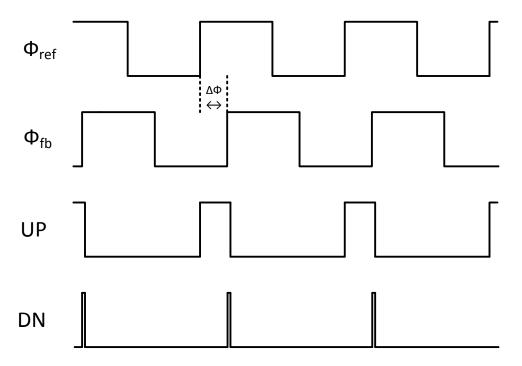

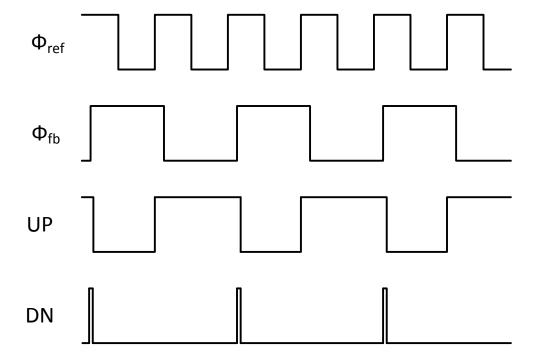

Shown in Figures 13, 14 and 15 are the timing diagrams for the PFD for different conditions of the inputs phase and frequency differences. It can be seen that the DC component of the difference of the UP and DN signals is in fact linearly related to the phase and frequency difference of the reference clock and the divided clock. One interesting quality of PFDs to note is the short pulses on both UP and DN signals when the phase difference is small and the frequency is locked, this can lead to a so-called *dead zone* as described later and may require additional circuitry.

Figure 13. PFD timing diagram with input signals at same frequency and with phase difference.

Figure 14. PFD timing diagram for input signals with different frequencies.

Figure 15. PFD timing diagrams in phase lock.

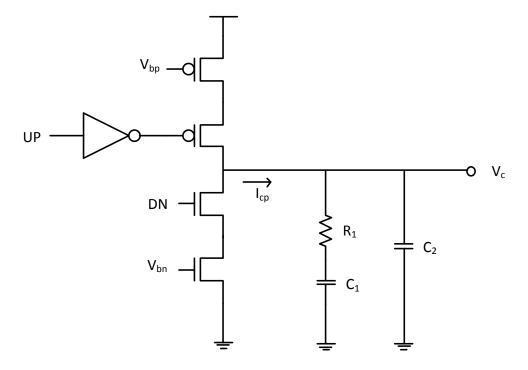

### 2.2.2: Charge Pump and Loop Filter

The PFD is typically used in conjunction with a charge pump and loop filter to generate the control voltage signal of the VCO. A basic charge pump implementation is shown in Figure 16 along with a passive loop filter. The charge pump converts the UP and DN signals to a summed current output, depicted as  $I_{cp}$ . The ease of current summation is one of the benefits of using the charge pump structure. The current source transistors at the rails are biased by  $V_{bp}$  and  $V_{bn}$  to provide identical currents such that the average output current is equal to the average difference of the duty ratio of UP and DN signals times the bias current. This figure shows a basic charge pump, but typically a fully differential version is used for improved noise rejection and can provide offset cancellation [33]. In an analog PLL, the phase detector, or phase frequency detector, and charge pump generate a current with average value proportional to phase difference, and frequency difference if using a PFD. This current is fed to the loop filter which is typically a combination

of a series resistor and capacitor in parallel to another capacitor.  $C_2$  is chosen to be much smaller than  $C_1$  and typically serves to provide additional filtering at high frequencies and minimize charge injection from the charge pump. The effect of  $C_2$  can be neglected if the associated pole is at high enough frequency (beyond the loop gain unity gain frequency) and thus does not affect the stability of the system.

The output of the loop filter is a voltage and the input is a current, so the transfer function is the equivalent impedance of the parallel connection of a capacitor and a capacitor in series with a resistor. This loop filter is essentially a PI controller with one pole at the origin for ideally infinite DC gain which is necessary for low steady state phase error. The zero due to the resistor and capacitor in series is selected to ensure the loop gain rolls off at -20 dB/decade before the unity gain frequency which ensures stability.

Figure 16. Basic charge pump and loop filter.

### 2.2.3: VCO

The VCO is an essential block of the PLL. VCOs are voltage to frequency converters. The output frequency of the VCO is ideally linearly dependent on the input control voltage,  $V_C$ . The two main flavors of voltage controlled oscillators are the delay line ring oscillator and the LC tank oscillator. Shown in Figure 17 is a basic ring oscillator where the delay cell is shown as an inverter with an input to output delay,  $\tau_D$ , is a function of the control voltage,  $V_C$ . The number of inversions must be odd so that the criterion for oscillation is met.

Figure 17. Ring oscillator with controlled delay.

Figure 18. Fully differential ring oscillator.

Typically the delay line based ring oscillator is implemented with fully differential delay elements for noise and supply immunity. A four stage fully differential ring oscillator is shown in Figure 18. This configuration is particularly useful in application requiring multiple clock phases. One very popular delay cell is discussed in [27]. This structure

utilizes symmetrical loads and replica biasing to provide a wide tuning range all CMOS implementation which is self-biased and supply noise insensitive.

The LC tank based oscillator is used where spectral purity and minimal jitter are essential such as in RF synthesizers. The LC tank VCO is shown in Figure 19. Frequency tuning is typically accomplished through tuning the capacitance of the tank. In an LC tank the oscillation frequency is determined from the inductance and capacitance of the resonant tank,

$$\omega_{VCO} = \frac{1}{\sqrt{LC_{tune}}} \tag{8}$$

In modern CMOS processes, variable capacitance is accomplished with reverse biased diode varactors or MOS capacitors. The capacitance is a junction capacitance in the case of varactor diodes or a gate to channel capacitance in the case of MOScaps and is non-linear in either case. Although LC tank based VCOs can be realized with only two stages and the resonant peaking allows for lower phase noise, the tuning range is limited.

Figure 19. Tunable LC tank based VCO.

### 2.2.4: Frequency Divider

A frequency divider can be built using cascaded flip flops as shown in Figure 20, which is basically an asynchronous binary counter. This circuit block is essential in PLLs used for frequency synthesis. The input signal is the high frequency output signal from the VCO and the output is a lower frequency which is fed to one input of the PD/PFD. If N is the divider ratio, the divider output frequency can be calculated:

$$\omega_{div} = \frac{\omega_{VCO}}{N} \tag{9}$$

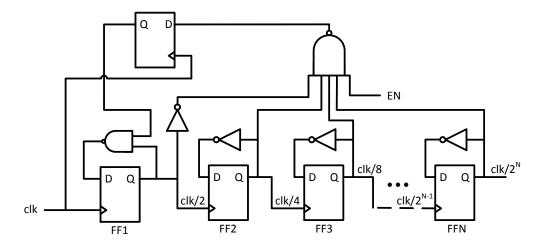

Figure 20. Frequency divider.

This topology can be modified to a programmable frequency divider using the cycle stretch method as shown in Figure 21 [33]. This circuit functions similar to the asynchronous binary counter based divider when the EN signal is low. When the EN signal is high, the first flip flop does not toggle on the clock cycle following the cycle stretch code, effectively dividing the input clock frequency by  $2^N+1$ . In general, the cycle stretch method can also be used to divide the input clock frequency 2N+M by cycle stretching at M different codes.

Figure 21. Programmable frequency divider.

Fractional N multipliers can be realized using a programmable frequency divider and using delta-sigma modulation of the EN signal to toggle back and forth between a divide ratio of  $2^N$  and  $2^N+1$ .

#### 2.3: Jitter and Phase Noise

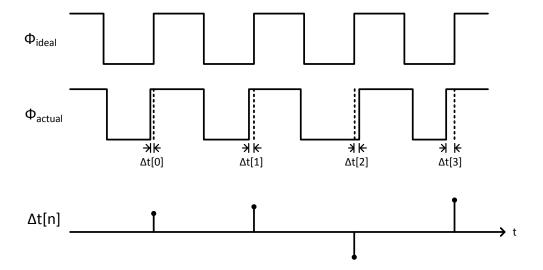

Timing jitter and phase noise are two different ways of looking at the same phenomena. Jitter is the deviation of clock edges or the clock period between an ideal "golden" clock and the actual clock signal. Jitter is basically a measure of how noisy a clock signal is in the time domain. There are different ways of representing jitter as discussed in [33]. Typical jitter representations of jitter are absolute jitter, period jitter, and cycle-to-cycle jitter. Absolute jitter is the time difference between the actual clock signal rising (falling) edges and the ideal clock signal rising (falling) edges. Absolute jitter is depicted in Figure 22 and is of importance for this application. Period jitter is the difference between the period of the actual clock signal and the ideal clock signal period. Cycle-to-cycle jitter is the difference in time of adjacent clock signal periods.

Figure 22. Timing jitter.

Phase noise is the frequency domain representation of timing jitter. Timing jitter manifests itself as spurs in the spectrum of clock signals and typically phase noise is quantified in units of dBc/Hz which is the noise power relative to the carrier contained in a 1 Hz bandwidth centered around some offset frequency.

### 2.4: Analysis and Parameter Selection

# 2.4.1: Small Signal Analysis for 2<sup>nd</sup> Order Analog PLLs

Figure 23. Simplified schematic of a charge pump PLL.

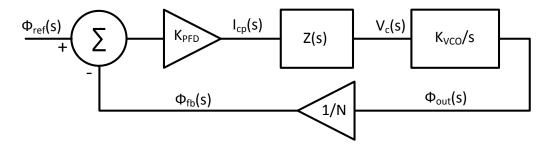

A typical charge pump based PLL is shown in Figure 23. When modeling the small signal behavior of PLLs in phase lock, it is convenient to work in the phase domain. The various blocks of the PLL can be modeled in the phase domain and the basic time domain signal processing operations can be recognized. In the phase domain, the PFD performs subtraction of the reference and feedback phases as well as gain, the VCO performs integration, the divider performs scaling, and the loop filter performs frequency dependent gain. The charge pump performs the voltage to current transformation. The small signal model of the charge pump based PLL is shown in Figure 24.

Figure 24. PLL small signal model.

Typically, the loop filter is designed so that the value of  $C_2$  is much smaller than  $C_1$ , as depicted by the dotted lines shown in Figure 23, and can be neglected if the associated pole is beyond the unity gain frequency loop gain response. The series resistor and capacitor,  $R_1$  and  $C_1$ , are selected so that the unity gain frequency of the closed loop signal transfer function is approximately 10 to 20 times smaller than the reference frequency. The zero from  $R_1$  and  $C_1$  is placed far enough before the unity gain frequency so as to give the loop adequate phase margin to ensure loop stability over PVT corners.

The loop gain is derived as follows:

$$A_{OL}(s) = K_{PFD} \left( \frac{\frac{1}{C_1} \left( \frac{s}{\omega_Z} + 1 \right)}{s} \right) \left( \frac{K_{VCO}}{s} \right) \left( \frac{1}{N} \right)$$

(10)

$$\omega_Z = \frac{1}{R_1 C_1} \tag{11}$$

Here, the transfer function of the loop filter is given in a form which allows for the determination of a unique value of the capacitor,  $C_1$ , based on the design constraints as well as the unity gain frequency and the phase margin design parameters.

The first step is to determine the unity gain frequency and the desired phase margin. Typically, the phase margin is chosen to be around 60 degrees as this gives a good tradeoff between speed and minimal overshoot in response to a phase step. The unity gain bandwidth is typically chosen to be much smaller than the input reference frequency.

The frequency of the zero is chosen based on the unity gain frequency and the phase margin as follows:

$$f_{\rm z} = \frac{f_{\rm UG}}{\tan(PM)} \tag{12}$$

Next the capacitor value,  $C_1$ , is chosen as follows:

$$C_{1} = \frac{K_{PFD}K_{VCO}\sqrt{\left(\frac{f_{UG}}{f_{z}}\right)^{2} + 1}}{4\pi^{2}Nf_{UG}^{2}}$$

(13)

Then the resistor value,  $R_1$ , is chosen:

$$R_1 = \frac{\tan(PM)}{2\pi f_{UG}C_1} \tag{14}$$

When noise sources are inserted and the closed loop transfer function is analyzed, the noise transfer function can be determined for each noise source.

Figure 25. PLL small signal model with noise sources.

The signal and noise transfer functions are derived and the results are shown below. The output phase as a function of the signal and each noise source is shown in Equation 18. The signal and noise transfer functions are given in Equations 19-22 and plotted in Figure 26.

$$Z(s) = R_1 + \frac{1}{c_1 s} \tag{15}$$

$$\omega_0 = \sqrt{\frac{K_{PFD}K_{VCO}}{NC_1}} \tag{16}$$

$$Q = \frac{\sqrt{\frac{NK_{PFD}K_{VCO}}{C_1}}}{R_1K_{PFD}K_{VCO}} \tag{17}$$

$$\Phi_{out}(s) = \frac{\left(\frac{s}{\omega_0}\right)^2 N_3(s) + \left(\frac{s}{\omega_0}\right) N_2(s) + \left(\frac{1}{Q}\left(\frac{s}{\omega_0}\right) + 1\right) \left(N\Phi_{ref}(s) + N_1(s)\right)}{\left(\frac{s}{\omega_0}\right)^2 + \left(\frac{s}{\omega_0}\right)\frac{1}{Q} + 1}$$

(18)

$$STF = \frac{\Phi_{out}(s)}{\Phi_{ref}(s)} \bigg|_{N_3 = N_2 = N_1 = 0} = \frac{N\left(\frac{1}{\varrho}\left(\frac{s}{\omega_0}\right) + 1\right)}{\left(\frac{s}{\omega_0}\right)^2 + \left(\frac{s}{\omega_0}\right)\frac{1}{\varrho} + 1}$$

(19)

$$NTF_{1} = \frac{\Phi_{out}(s)}{N_{1}(s)} \Big|_{N_{3} = N_{2} = \Phi_{ref} = 0} = \frac{\left(\frac{1}{Q}\left(\frac{s}{\omega_{0}}\right) + 1\right)}{\left(\frac{s}{\omega_{0}}\right)^{2} + \left(\frac{s}{\omega_{0}}\right)\frac{1}{Q} + 1}$$

(20)

$$NTF_{2} = \frac{\Phi_{out}(s)}{N_{2}(s)} \Big|_{N_{3} = N_{1} = \Phi_{ref} = 0} = \frac{\left(\frac{s}{\omega_{0}}\right)}{\left(\frac{s}{\omega_{0}}\right)^{2} + \left(\frac{s}{\omega_{0}}\right)^{\frac{1}{2}} + 1}$$

(21)

$$NTF_{3} = \frac{\Phi_{out}(s)}{N_{3}(s)} \Big|_{N_{2} = N_{1} = \Phi_{ref} = 0} = \frac{\left(\frac{s}{\omega_{0}}\right)^{2}}{\left(\frac{s}{\omega_{0}}\right)^{2} + \left(\frac{s}{\omega_{0}}\right)^{2} + 1}$$

(22)

Figure 26. 2<sup>nd</sup> order PLL noise transfer functions.

It can be seen that noise injected into the input experiences low pass filtering and this is similar to the signal transfer function, but without the scaling due to the frequency divider. Noise injected from the phase detector, charge pump and loop filter experiences bandpass filtering. It is particularly interesting to note that noise from the VCO experi-

ences high pass filtering, so any high frequency phase noise will pass directly to the output.

### 2.5: Analog PLL non-idealities

One of the issues in traditional charge-pump PLL that utilize phase frequency detectors is the *dead zone* phenomenon that occurs when the system is in phase lock. This situation arises when the phase error between the reference and feedback clocks becomes comparable to the transition time of the output of the flip flops. The gain of the PFD around this point drops due to the switches not turning on or turning on for an uncertain period of time. This decrease in PD gain around phase lock can result in jitter at the output since the output of the loop filter does not correct for phase differences in this dead zone region. The transfer characteristic around the dead zone is shown in Figure 27.

Figure 27. Dead zone of PFD.

The dead zone issue is more of a problem with older designs that used external charge pump due to the loading on the outputs of the flip flops. The dead zone issue can be mitigated if the delay from the output of the flip flops back to the reset is longer than the transition time, and the outputs of the flip flops can be simultaneously high.

The mismatch between the current sources in the charge pump will also have a negative effect on the performance of the charge pump. During phase lock, both UP and DN cur-

rent sources will be on briefly, as described above. This means that any mismatch between the current sources will periodically disturb the VCO control voltage and introduce sidebands in the output spectrum as well as a steady state phase error. Other issues related to the current sources are finite output impedance, charge sharing and charge injection as described in [29].

A large capacitor is required in the loop filter to set the bandwidth of the PLL. If these caps are implemented using MIM caps, they may take up larger area and increase the chip cost. Since the large cap is connected between the VCO control voltage node and ground, it makes the control node susceptible to noise injection from the ground node. In deep sub-micron CMOS PLL designs, MOScaps are utilized to reduce production costs. MOScaps are inherently non-linear so this can decrease the functional range of the VCO. Another drawback of using MOScaps, particularly at smaller geometries, is the increasing gate leakage current of the MOScaps, which causes spurs in the output spectrum and jitter on the output clock.

## 3.1: All-Digital PLL Building Blocks

The charge-pump PLL has long been the topology of choice for frequency synthesis and clock and data recovery circuits. As CMOS process technologies move further into the deep submicron realm, analog circuitry does not scale as well as digital circuitry. The analog loop filter is consuming more relative area and leakage current of the MOS capacitor is increasing. The noise sensitivity of the analog PLL is also deteriorating as scaling continues. Recently, increasing attention is being paid to all-digital PLL systems not only because of the previously mentioned reasons, but also because of the other benefits of digital systems such as PVT insensitivity, programmability, scaling and ease of design migration. Also, with higher levels of integration such as in SoC, the analog circuits are surrounded by more and more digital circuits, causing issues of higher supply and ground noise as well as cross talk. Another benefit of the ADPLL is that no charge pump is required, and the limitations of this block can be eliminated.

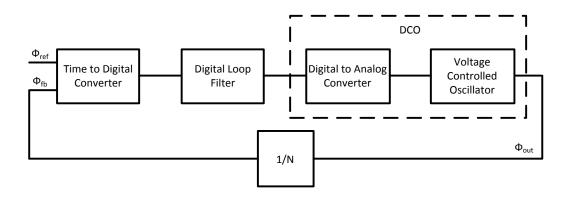

Figure 28. Block diagram of ADPLL.

## 3.1.1: Time to Digital Converter

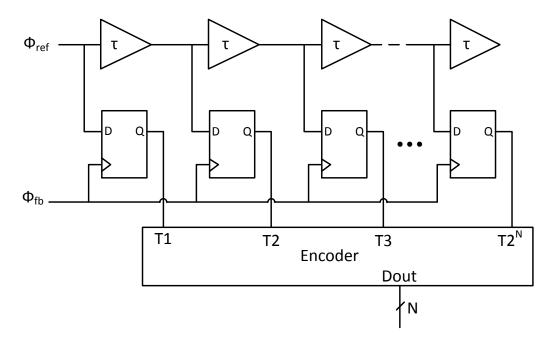

All PLLs require some means of measuring the phase error between the reference clock and the feedback clock. In charge pump PLLs, this can be accomplished with standard logic gates such as XORs, AND, ORs, latches and flip flops. In the charge pump PLLs, the output of the phase frequency detector is digital in the form of voltage, but continuous in time, so it is not a fully digital system. In ADPLLs the measured phase error is digital in time and voltage and this is where the time to digital converter comes in. The TDC is analogous to an analog to digital converter, but in the time domain. The simplest time to digital converter is shown in Figure 29. In this TDC, the phase error between the reference and feedback clock is digitized by using one clock signal rising edge to capture data from the taps of a delay line. The output of the TDC is a thermometer code and this sort of TDC is analogous to a flash ADC in the time domain. The delay elements can be simple CMOS buffers which can be two back to back inverters. In this case, the minimum resolution for the TDC is twice the intrinsic delay of the process being used. Mismatch is a concern as it will lead to DNL in the transfer characteristic of the TDC.

Figure 29. Simple time to digital converter.

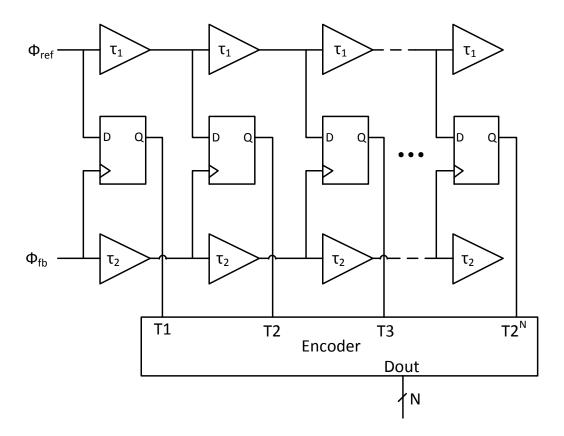

In order to overcome the limitation imposed by the process intrinsic delay, a Vernier delay line type TDC can be used as shown in Figure 30. The minimum resolution for this topology is now determined by the difference of the propagation delay of two buffers, instead of the buffer propagation delay. Even though the minimum resolution can be smaller than the intrinsic delay of the process, since the minimum delay is now a difference of two delay cells, there are two sources of mismatch and the DNL of the TDC will likely be very poor.

Figure 30. Vernier delay line based TDC.

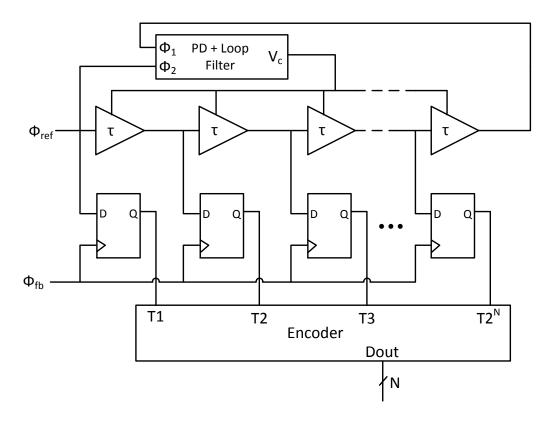

The two TDC topologies discussed so far will have a limited linear range if the total delay from the first buffer to the last is less than the unit interval. This means that the range of phase error is limited by the number of buffer stages and the delay of each stage. Mismatch and PVT variations will change the linear range as well as the gain of the TDC due to variations in each buffer propagation delay. A delay locked loop (DLL) can be used to ensure the total delay through the chain of buffers is exactly equal to the unit interval, thus giving maximum linear range and gain accuracy to the TDC. This is shown in Figure 31. While this method improves the performance of the delay line based TDC, it not only adds complexity, but also an analog block, the DLL, which is not favorable in ADPLLs.

Figure 31. TDC using DLL to control the delay.

Figure 32. Generic transfer function of TDC.

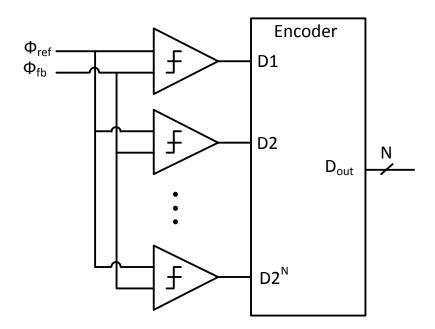

Another type of TDC utilizes the random nature of input threshold offset of latches and finite slope of the clock signals to determine the phase error. The stochastic TDC, shown in Figure 33, is composed of many latches whose input offset varies stochastically due to process variations. Since the input to each latch has a finite slope these different input offsets translate into thresholds in time which the reference and the feedback clock signals are connected to the inputs. If enough of these latches are used, the threshold offsets and thus time offsets will follow a normal or Gaussian distribution. The outputs of the latches are summed with the encoder and this output will essentially be the integration of a Gaussian random variable and the transfer function is approximately linear in the locked condition where the phase difference is small. The linearized gain of the STDC in locked condition is given in Equation 23 [19]:

$$K_{STDC} = \frac{N_{ARBS}SL}{\sqrt{2\pi}\sigma_{v}} \tag{23}$$

Here,  $N_{ARBS}$  is the number of latches or arbiters, SL is the slope of the clock signal, and  $\sigma_v$  is the standard deviation of the voltage threshold of the latches.

Figure 33. Stochastic TDC.

Figure 34. Stochastic TDC transfer characteristic.

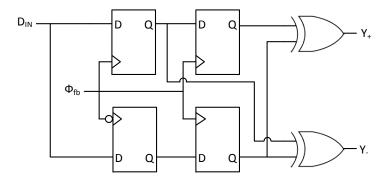

The digital phase detectors discussed so far are useful in frequency synthesis but not in clock and data recovery circuits because they rely on the input clock transitions every reference cycle. One popular digital phase detector suitable in CDR circuits is the Alexander phase detector. This configuration can be seen in Figure 35. This phase detector

oversamples the random input data by a factor of two and gives an indication of the phase difference. This architecture can determine if the data is leading or lagging the sampling clock and can also generate a *no change* signal when there is no data transition during the recovered clock period. For this reason, this topology is sometimes called a *ternary* phase detector.

Figure 35. Alexander phase detector.

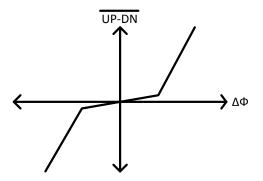

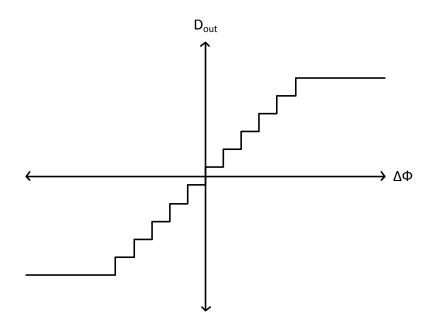

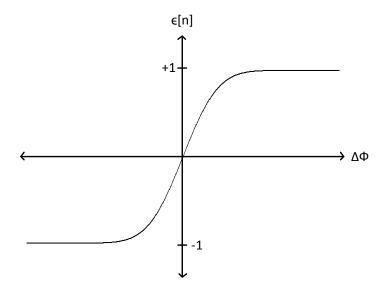

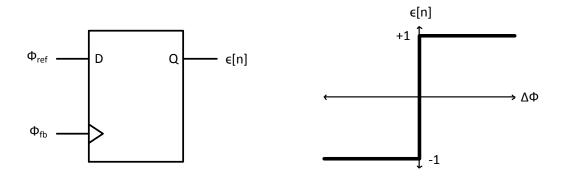

The *lead-lag* or *bang-bang* phase detector is basically a single bit TDC which outputs a digital '1' or '0' depending on whether the feedback signal is leading or lagging with respect to the reference signal. The single bit nature of the BBPD makes it very difficult to analyze the PLL by linearizing the transfer function of the BBPD because the gain is undefined. The simplest BBPD can be constructed using a D flip flop as shown in Figure 36. Benefits of such a structure are simplicity and high speed limited only by the speed of the fastest FF that can be designed in a given process. Another subtle advantage of using a DFF over an Alexander phase detector is that the multi-phase sampling nature of the latter leads to a dead zone in the linearized phase detector transfer function as discussed in [17].

Figure 36. Bang-bang phase detector and transfer characteristic.

As discussed in [9], [17], [22] and [38], the gain of the BPD can be linearized in the presence of input reference clock jitter assuming it has a Gaussian distribution and the linear range is approximately twice the standard deviation of the jitter. The offset of the FF translates to a static phase offset in the ADPLL, so it can be neglected in the small signal AC analysis. The transfer function is very similar to the stochastic TDC, since the gain is derived based on statistical analysis. This method of linearizing binary TDC will be covered in more detail in section 4.4.2.

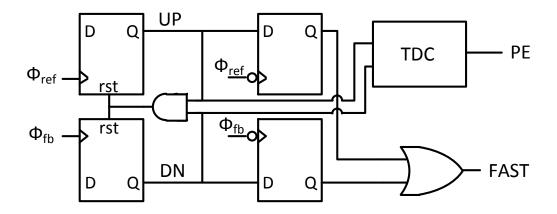

The charge pump PLL utilizes a phase frequency detector which simultaneously provides an indication of phase and frequency error. Some research has focused on digital PFDs. [46] implements the digital PFD shown in Figure 37. This implementation generates a single bit which indicates the polarity of the phase error shown here as PE, and another signal, FAST, which indicates a magnitude of phase error greater than  $\pi$ . A frequency decision circuit is used to increase or decrease frequency based on whether there are only UPs or DNs in a decision period. [21] implements a similar circuit using with a multibit TDC in Simulink to model the behavior of the digital PFD.

Figure 37. Digital PFD.

[44] uses another configuration where the UP and DN signals of the PFD are used in the proportional path and this is added to an integral path with consists of an accumulated output of a DFF which is sampled on the rising edge of the DN signal from the same PFD. [39] implements a digital bang-bang PFD which provides an indication of which clock signal is faster during frequency acquisition and once the frequencies of the two clock signals are close, the circuit indicates which signal is leading or lagging.

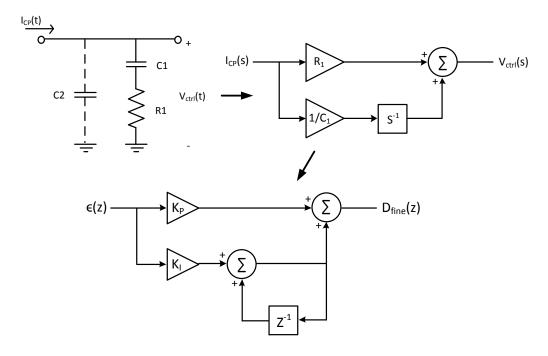

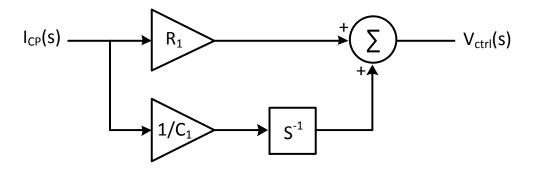

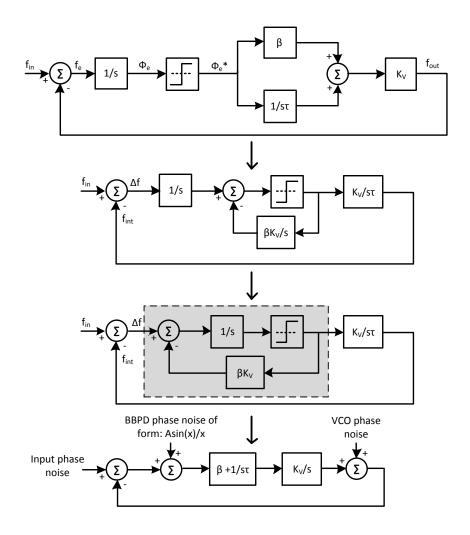

## 3.1.2: Digital Loop Filter

The digital output from the TDC must be averaged to provide the control word to the digitally controlled oscillator. For the typical analog PLL with  $2^{nd}$  order loop filter, the backward Euler s-to-z transformation can be performed to determine the digital implementation of this filter. Shown in Figure 38 is the typical s-domain of the analog loop filter that follows the charge pump of a CPPLL and the digital equivalent. The digital loop filter is a has proportional and integral branches each with gain of Kp and Ki respectively.

Figure 38. Continuous and discrete time equivalent loop filters.

# 3.1.3: Digitally Controlled Oscillator

The digitally controlled oscillator is the digital counterpart to the VCO in charge pump PLLs. The output frequency of a DCO is controlled by a digital word instead of an analog control voltage or current. In an analog PLL, noise on the control voltage line propagates to the output in the form of jitter. Digital control improves the noise immunity of this very critical component of the PLL.

There are several methods to implement digital control of the output frequency. Direct digital synthesis is one method of generating an output frequency which is proportional to the decimal value of a control word. The output frequency can be generated by using a look up table. Various waveforms such as triangle waves, sine waves or square waves can be generated at various frequencies based on the reference clock frequency and the tuning word. Direct digital synthesizers, however, require a reference clock of at least twice the synthesized frequency, which is of little use in clock multiplier applications.

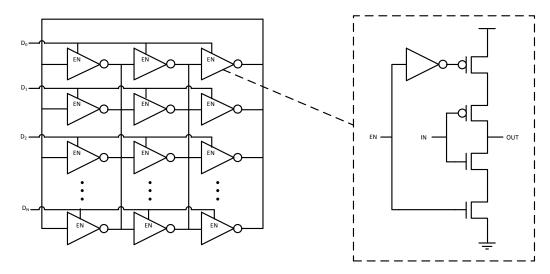

Gated ring oscillators can be used to generate a digitally controlled output frequency by turning on and off inverters in the ring so as to digitally control the drive strength, and hence the propagation delay, of each inverter in the chain. Figure 39 shows one implementation of a gated ring oscillator based DCO. In this GRO-based DCO, the inverters in the ring are gated inverters and connected in parallel. The control word can be binary or can be thermometer code depending on whether the inverters are binary or unary weighted.

Figure 39. Gated ring oscillator-based DCO.

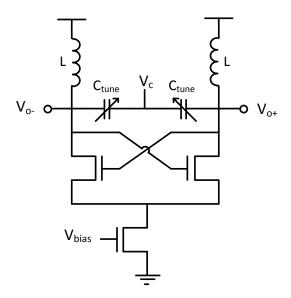

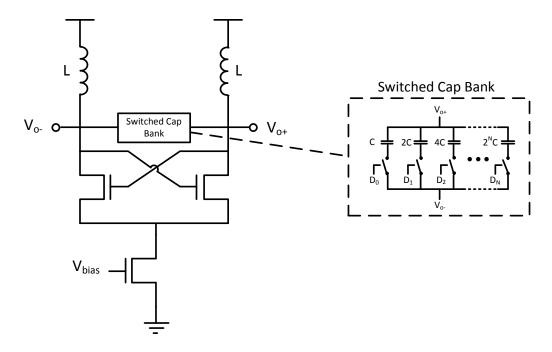

LC tank oscillators can also be controlled digitally by switching the capacitors of the tank to control the output frequency. One implementation of this is shown in Figure 40 where the digital tuning is accomplished through a bank of switched capacitors. The LC tank-based DCO can also be tuned digitally with varactors as described in [35].

Figure 40. LC tank-based DCO.

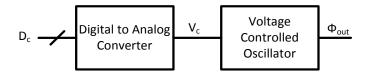

The DCO can also be implemented using any of the analog voltage or current controlled oscillators by using a voltage or current mode DAC as the interface between the digital and analog domains. Shown in Figure 41 is a voltage domain DCO formed from a voltage mode DAC and VCO.

Figure 41. DAC and VCO-based DCO.

## 3.1.4: Frequency Divider

The frequency dividers used in analog PLLs can be used in digital PLLs because they are digital and hence need no further discussion.

### 3.2: Limit Cycles and Quantization Noise in ADPLLs

Due to the finite nature of the signals in the ADPLL, there will inevitably be quantization noise sources due to the phase to digital conversion from the TDC and the digital to frequency conversion from the DCO. The quantization noise can be modeled in a similar fashion to data conversion systems where the TDC and DCO are analogous to an ADC and DAC, respectively. In ADPLLs with binary phase detectors, a limit cycle occurs due to the non-linearity introduced into the loop. These effects will be considered further in section 4.4.2.

### 3.3: State of the Art

An MDLL based digitally intensive clock multiplier is presented in [18]. This design makes use of a new correlated double sampling method to reduce path delay mismatch effects which lead to increased deterministic jitter. The DLL tuning voltage is generated differently than the traditional MDLL based synthesizer. The TDC is GRO based and the phase error is calculated by sampling the pulse width of the ring oscillator period and the ring oscillator period plus the additional error due to the replacement of every Nth edge of the ring oscillator output. This topology first processes the digital error signal and then converts it to an analog voltage with a DAC and performs additional analog processing using an RC filter. Total rms jitter was reported to be 930 fs at 1.6 GHz in 0.13 um CMOS process at an estimated 9.1 mW overall power consumption. The total peak to peak jitter was reported to be 11.1 ps with 760 fs estimated deterministic jitter. Phase noise was reported to be -58.3 dBc at 50 MHz offset.

In [39] an all static CMOS ADPLL is designed on 65 nm CMOS SOI process. The ADPLL utilizes a 3 stage, static inverter based ring oscillator DCO. The design also utilizes a BBPFD which is acceptable due to relaxed noise and bandwidth requirements.

The topology does not use an explicit DAC, but instead directly converts from digital to frequency using the GRO DCO. The design also utilizes a programmable PID controller and third order MASH sigma-delta for the LSB of the DCO. The sigma-delta modulation of the LSBs helps to noise shape the phase noise generated by the limit cycle caused by the BBPD. This work reports 32 mW power consumption and 6 ps rms jitter at 1.2 V supply and 4 GHz output frequency.

In [35], an ADPLL is fabricated on 90 nm CMOS process as part of a single-chip GSM/EDGE transceiver. This work utilizes an LC oscillator as the DCO which is programmable by using varactor banks. A very interesting feature in this paper is the operation of the ADPLL in a digitally synchronous fixed-point phase domain. This is unlike traditional charge pump PLLs whose phase detection mechanism is correlational and causes significant spurs. The output phase is first measured by accumulating clock edges which gives a coarse indication of the output phase. A TDC is used to generate a phase error signal with finer resolution. The digital derivative of the output phase and the phase error is taken to provide a frequency signal which is subtracted from a frequency command word. This frequency error is then accumulated to produce an equivalent phase error and processed by a digital 4-pole IIR filter. The output of the filter then controls the DCO. This topology reports phase noise of -122 dBc/Hz at 400 kHz offset. [23] describes the design of an ADPLL for wireless applications in the WiMAX 3.3-3.8 GHz bandwidth in 90 nm CMOS process. This design utilizes a DLL based TDC to decrease sensitivity to PVT variations and also uses a BBPD and digital loop filter. Spurs generated by skew between a counter and TDC are corrected by glitch detection logic. The DCO is composed of a LC tank based oscillator that is digitally tuned by a switched capacitor bank in the LC tank. The frequency and phase error are measured similar to

[35] and the frequency error signal is digitally integrated and fed to a digital PI filter. This work reports in band phase noise of -95 dBc/Hz.

[24] describes the design of an ADPLL in 180 nm CMOS technology which achieves 210 ps peak to peak jitter. This ADPLL is based on a two loop architecture for fine and coarse frequency tuning of a DCO (or RCO as it is referred to in the literature). Coarse tuning is performed using a digitally controlled symmetrical delay line and fine tuning is done with capacitor banks. An all-digital PFD is used as well to provide digital phase and frequency error detection. The ADPLL in this case is used for clock synchronization for a memory interface at 200 MHz and consumes 5.9 mW at supply of 2.5 V.

In [46], a 4 GHz ADPLL is fabricated on 90 nm CMOS technology for frequency synthesis which features programmable loop bandwidth from 100 kHz to 6 MHz. The DCO in this work is the LC-tank based oscillator with capacitor bank for frequency tuning. The work uses a digital PFD composed of a conventional tri-state PFD and BBPD. The control loop uses a digital PI controller as the loop filter. This work reports phase noise at 1 MHz offset as -106 dBc/Hz.

[20] describes the design of an ADPLL using a 6-bit stochastic TDC for phase control and BBPFD for frequency control. This design also uses delta-sigma dithering to improve bandwidth and minimize jitter. The DCO is composed of a current steering DAC, current to voltage converter and a differential ring oscillator VCO. This design was fabricated on 130 nm CMOS technology and reports 6.9 ps rms jitter and 56 ps peak to peak jitter with a tuning range of 0.7 to 1.7 GHz tuning range at 17 mW (at 1.2 GHz) from a 1.2 V supply.

In [3] a DLL based frequency multiplier is implemented in  $0.35~\mu m$  CMOS technology for use as a 900~MHz frequency synthesizer for a wireless application. In this design, the spectrally pure crystal oscillator clock signal is fed into a DLL to produce evenly spaced

clock edges and these clock edges are combined with digital logic to produce a low jitter output clock. This output frequency is a multiple of the reference frequency determined by the number of delay stages in the DLL. The DLL in this design still relies on traditional analog functions of phase detection, charge pump and loop filtering. This design achieves -123 dBc/Hz at 60 kHz offset and consumes 130 mW from a 3.3 V supply. A similar approach is used in [2] for a 108 MHz synthesized clock for an 8-bit video-rate DAC and reports 80 ps jitter and 0.9 mW from 3.3 V supply on 0.5 µm CMOS process. In [42], an ADPLL frequency synthesizer with dynamically reconfigurable digital loop filter coefficients is designed on 90 nm CMOS process. The digital loop filter coefficients are adjusted by a locking process monitor circuit which improves lock time without sacrificing jitter performance. The design is a dual loop design with frequency and phase lock loops. This design uses a DCO composed of an LC oscillator with digitally tunable varactor banks. The work reports 7.1 mW from 1 V power supply with 0.9 ps rms jitter at 10 GHz.

### Chapter 4: CIRCUIT DESIGN AND IMPLEMENTATION

# 4.1: Application

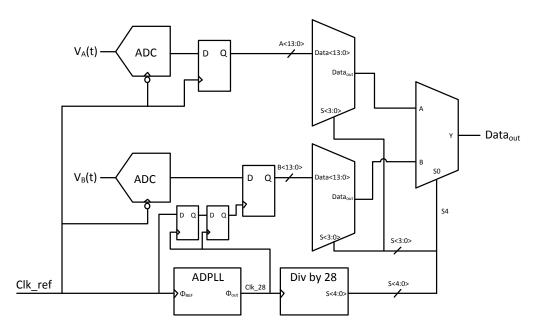

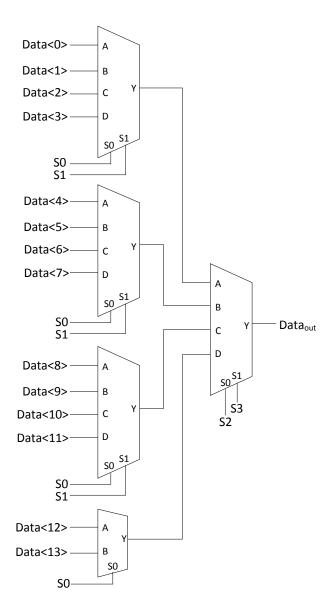

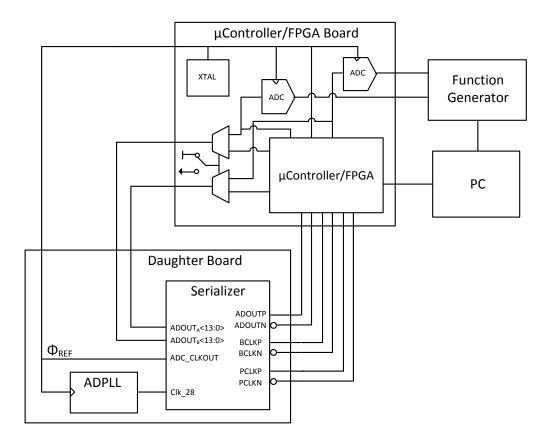

The DPLL is designed to be used in a read out integrated circuit (ROIC) which is connected to a focal plane array (FPA) in order to digitize and serialize the incoming image data, essentially serving as the analog front end (AFE) of the imaging system. The system needs to be operational at room temperature and optimized for operation at -195 °C. The digitized data is sent outside of the ROIC to an FPGA for further processing. The ADPLL will generate the 280 MHz clock signal used in the serializer circuit. The serializer in this application will interface two parallel 14 bit ADC outputs and combine them into a serial output at a frequency 28 times the sampling frequency. The ADC sampling frequency for this application is a stable 10 MHz generated from a crystal oscillator, which necessitates an output frequency of 280 MHz. This system is shown in Figure 42 and 43. Not shown is the circuitry used to synchronize the counter in the divider with the rising edge of the reference clock.

An all-digital PLL was chosen instead of the traditional analog PLL because of the programmability, lower power, higher noise immunity and portability of digital systems. Since the system will be operating at cryogenic temperatures around -195 °C, power consumption is a critical performance parameter because for every 1 mW consumed in a cryogenic dewar, 40 mW is used to remove the heat. The system must be immune to single event effects (SEEs) and latch up. The process chosen for integration is Jazz's CA18HD process.

The two loop PLL and FLL architecture was chosen as opposed to summing the frequency and phase errors together and passing them through a single loop filter or using a digital PFD. The primary motive for using two separate control loops is flexibility. Decou-

pling of phase and frequency control allows for low jitter without sacrificing frequency acquisition time. Another benefit of this architecture is the potential for a reduction in power consumption by putting the FLL in a standby mode while the PLL is active by using a separate lock detection circuit.

Figure 42. Serializer top level.

Figure 43. 14 bit mux.

# 4.2: Specifications

The specifications for this design were chosen based primarily on minimal power consumption and functionality within the serializer under all conditions. The table below lists the most critical specifications for this application.

Table 1. ADPLL Specifications.

| Specification  | Min | Тур     | Max    |

|----------------|-----|---------|--------|

| Power          |     | 2 mW    | 4 mW   |

| Temp. Range    |     | -195 °C | 25 °C  |

| Total Jitter   |     |         | 357 ps |

| Supply Voltage | 1.7 | 1.8     | 1.9    |

# 4.3: Design

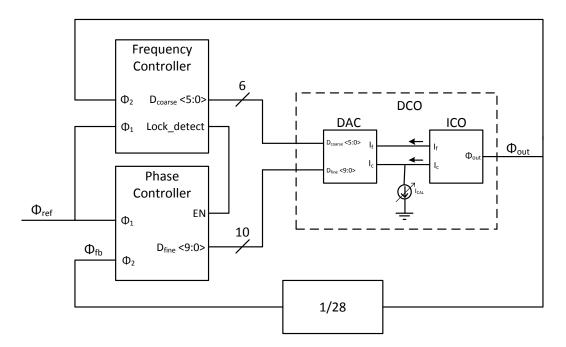

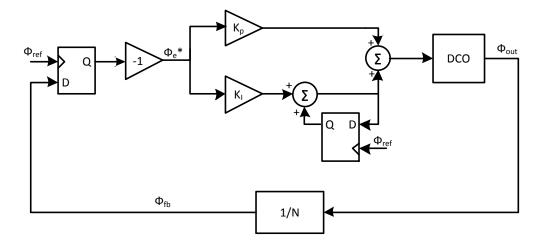

Figure 44. ADPLL block diagram.

## 4.3.1: Top Level

Figure 45. Top level of ADPLL.

Implementation of a digital phase locked loop requires the digital equivalents of the analog blocks used in the traditional analog PLL. Shown in Figure 45 is the top level of the DPLL with phase and frequency control loops, digitally controlled oscillator and frequency divider. The frequency divider is already fully digital and the same basic methods for frequency division can be used in the ADPLL as in the analog PLL. Standard cells are utilized wherever possible to allow for design portability and reconfigurability. The frequency divider, phase control and frequency control blocks are all fully digital and implemented with standard cells. The crucial mixed signal block is the digitally controlled oscillator and is implemented with a current mode DAC and a current controlled oscillator. The DAC serves as the interfacing element between the digital and analog domains. In most analog PLLs, the oscillation frequency is controlled by a voltage which is generated by the charge pump and loop filter. This method of frequency control signal generation can problematic in that high frequency ground noise can easily couple onto

this node and cause jitter on the output of the oscillator. Another disadvantage of voltage signal control of frequency is that the large filter capacitors that are typically implemented with MOS capacitors with large leakage currents. The following sections will discuss the individual blocks in detail.

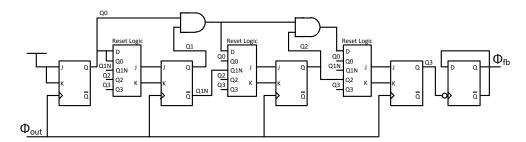

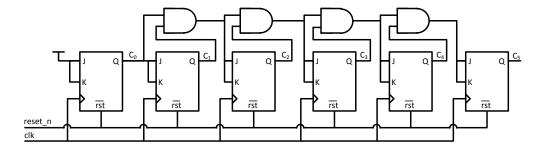

### 4.3.2: Frequency Divider

The frequency divider is similar to the frequency dividers previously discussed. The output of the oscillator is used in a binary up counter and reset to zero when it hits the decimal equivalent of 13, which is a total of 14 counts. The falling edge of the MSB of the count clocks a basic divide-by-two circuit for an output frequency of  $\frac{f_{in}}{28}$ . This output frequency is fed back to the BBPD for phase detection.

Figure 46. Frequency divider.

Figure 47. Reset logic.

### 4.3.3: Phase Controller and Loop Filter

As described in [40], with a first order loop (proportional branch only), the loop is in lock if the input frequency deviation from the nominal VCO frequency,  $\delta f$ , is less than the bang-bang frequency update, or equivalently:

$$|\delta f| < K_P K_{VCO} \tag{24}$$

Proportional, "bang-bang", loop sets the duty cycle of the phase detector to:

$$C = \left(\frac{1}{2} + \frac{\delta f}{2K_P K_{VCO}}\right) \tag{25}$$

An integral branch is typically added to increase the frequency locking range of the BBPLL, due to the very limited locking range of the first order loop. The proportional, "bang-bang", branch is the phase tracking loop, while the integral branch is the frequency tracking loop which centers the VCO at the average incoming data frequency and thus the duty cycle of the phase detector to around 50%. It is assumed that the proportional branch is dominant over the integral branch and the two branches can be viewed as non-interacting. One interesting point to note is that if power supply noise induced is limited to  $\pm K_P K_{VCO}$ , there is no jitter accumulation, unlike linear PLLs.

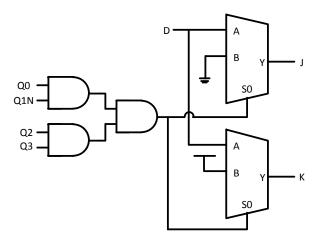

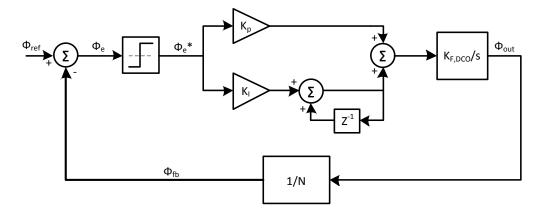

The phase controller is designed to be the digital counterpart of the analog 2<sup>nd</sup> order PLL. The s-domain representation of the loop filter can be seen in Figure 48. This continuous time analog filter can be converted to the discrete time digital version shown in Figure 49 through the use of the backward Euler s-to-z transformation.

Figure 48. Small signal model of 2<sup>nd</sup> order PLL loop filter.

Figure 49. Z-domain equivalent of 2<sup>nd</sup> order PLL loop filter.

The digital equivalent of this circuit can be realized using adders, registers and gain stages. Digital multiplication is much simpler if the gain is a power of two since it only involves the use of shift registers. In this application, because the output of the phase detector can only take on two values, +1 or -1, the value at the output of the proportional gain block will simply be  $+K_P$  or  $-K_P$ . The same is true for the integral path. Taking advantage of this fact, the digital loop filter can be implemented as shown in Figure 50. Many of the ADPLL designs in the literature use TDCs for phase detection. In order to minimize circuit complexity and increase potential for high speed use and design portability and process compatibility, a DFF was used as a *lead-lag*, also known as a *bang-bang*, phase detector. The output of the flip flop is logic high if the feedback clock leads

the reference clock, and vise-versa. The output of the BBPD controls the adder/subtractor circuits such that if the reference phase leads the feedback phase, the circuits add  $K_I$  and  $K_P$  to the control word,  $D_{fine}$ , and subtract  $K_I$  and  $K_P$  if the contrary is true.

One important design consideration in the phase control circuit is the synchronization. The addition and subtraction operations in the proportional and integral branches are synchronous to the reference clock. The registers that sample and hold the outputs of the adder/subtractor are delayed versions of the reference clock. This allows for minimal delay through the phase control loop which, as discussed in section 4.4, is essential for minimizing the jitter due to the limit cycle. The delay times are chosen such that the last register in the pipeline is updated only after the longest possible data transition due to both adder/subtractor circuits and the multiplexer. The multiplexer is used as an initialization block where D<sub>init</sub> is the value when EN signal is high. EN is high whenever the frequency control loop is active.

Figure 50. Implementation of digital 2nd order PLL loop filter.

Shown in Figure 51 is the ripple carry adder/subtractor circuit used throughout the design. The 6 bit version is shown here, the 7<sup>th</sup> bit is the sign bit, but the 10 bit version is essentially identical. This is basically a typical ripple carry adder when the subtract signature.

nal (shown here as 'add' with a bar over it) is low and the XOR gate is simply a buffer. When the subtract signal is high, the XOR gates invert all the bits from the second input and the carry-in bit of the first adder is high. Inverting all bits and adding one is the two's complement representation of the negative value of the second input, so subtraction is performed when subtract signal is high. There is also overflow logic which determines if an overflow occurs. In circuits where a negative value is not valid, the overflow condition includes a negative result, which is shown in this figure.

Figure 51. Adder/subtractor.

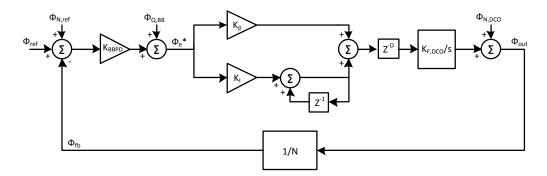

### 4.3.4: Frequency Detector

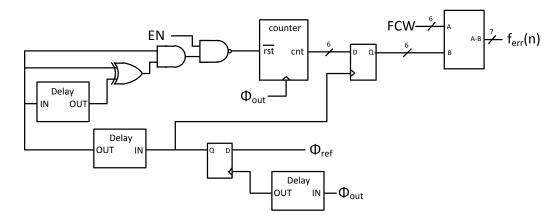

In most analog PLLs, a PFD is used which produces an output proportional to the phase difference as well as the frequency difference. The BBPD has a limited lock range because of the inability to detect difference in frequency. In order to remedy this, another control loop must be added which can provide a measure of frequency control. In order to detect the frequency of the output signal, this block counts the number of clock periods of the oscillator output clock within one reference clock and compares this value with a frequency control word (FCW) which is programmed to be equal to the output frequency multiple of the input reference clock frequency. A similar method is discussed in [35], where the reference clock as well as the output clock are used to clock two counters with different increments and comparing the outputs periodically, which is essentially converting from frequency to phase. This count is subtracted from the FCW to give a measure of the error in frequency. The frequency resolution is limited by the reference frequency, but this is not critical as the purpose of the frequency detector and control loop is to initialize and keep the system to within the lock range of the BBPD. A simplified block diagram showing the z-domain model of the frequency control loop is shown in Figure 52.

Figure 52. Frequency control loop.

The frequency detector performs the function of converting the output phase into the output frequency word,  $f_{out}$ . Since the phase to frequency converter counts the number of rising output clock edges between reference clock edges, the output of the frequency de-

tector can be thought of as an average output frequency relative to the reference frequency. The frequency detector generates a digital code proportional to the difference in output frequency from the target frequency

$$FCW * f_{ref} = 28 * 10 MHz = 280 MHz$$

(26)

There will also be quantization noise due to the finite resolution of the frequency detector which will be discussed further in section 4.4. The frequency detector implementation is shown in Figure 53. The combination of delay cell, XOR and AND gate generates a short positive pulse on the rising edge of the delayed and retimed reference clock which is then inverted so that a short negative pulse resets the counter on the rising edge of the reference clock. The lower delay cells and D flip flop retime the reference clock and ensure no setup or hold time violation at the counter sampler.

Figure 53. Frequency detector.

Figure 54. 6-bit counter.

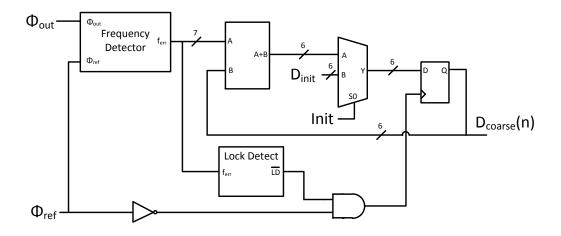

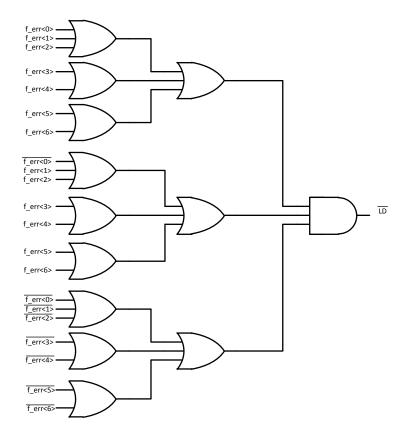

### 4.3.5: Frequency Controller

The frequency error is added to the current coarse DCO tuning word, which is essentially integration in the analog domain. The frequency detector and control loop serve as a secondary control loop which forces the frequency error of the output to be zero in addition to providing fast frequency acquisition during transients as well as startup conditions. In order to account for uncertainties due to the difference clock domains as well as to limit the activity of the frequency detector when the frequency is in range of phase lock, additional lock detect circuitry is added to disable the frequency control loop when the output frequency is between approximately  $\pm$  10 MHz of the target frequency. The frequency control and lock detect blocks are shown in Figure 55 and Figure 56.

The frequency lock loop controls 6 coarse tuning bits of the DCO. The frequency tuning resolution of the 6 coarse bits is approximately 4.7 MHz for a full scale of about 296 MHz. The resolution was chosen to be below the reference frequency as this is the minimum frequency the detector can resolve. The full scale value gives an adequate frequency range to account for process or supply voltage variations as well as flexibility to use different reference frequencies or frequency multiplication factors. The multiplexer initializes the accumulator loop to the center code of the DCO coarse tuning word for faster frequency acquisition upon startup. The INIT signal is used as the select signal for the multiplexer and is synchronous to the reference clock to provide maximum timing margin at the coarse tuning register.

Figure 55. Frequency control.

Figure 56. Lock detect logic.

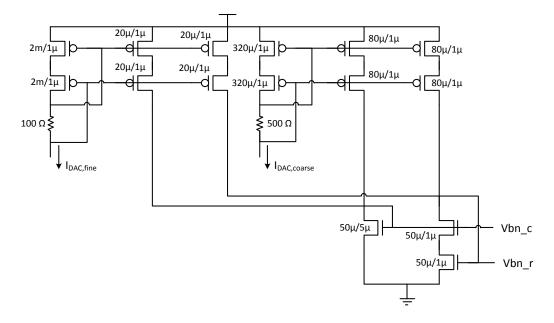

### 4.3.6: Digital to Analog Converter

The DCO is essentially a current mode DAC and a current controlled oscillator (ICO). Current mode was chosen due to simplicity, lower power and better monotonicity. Lower processing power is required to perform addition in the current domain when compared to voltage domain addition. Another advantage of current mode control is the decreased susceptibility to supply noise and SEEs. The DAC is actually comprised of a coarse 6 bit DAC controlled by the frequency controller in parallel with a 10 bit segmented DAC controlled by the phase controller.

The DAC is not the usual current steering structure which switches the current between the output and ground. Instead, the current sources are switched at the source terminal so current is not wasted due to the lower power requirement of the application. The switches are scaled up with the current sources so as to provide the same voltage drop and across the switches and ensure accurate current mirror matching. The fine DAC uses 4 binary weighted current sources for the least significant bits, and the thermometer coded array for the most significant bits. The reason for this type of segmentation was to minimize glitch amplitude due to mismatches in the binary weighted current sources at higher current levels. Delay blocks were added between the LSB control lines and the switches to compensate for the difference in delay due to the decode logic in the MSB array. The circuits that compose the DAC can be seen in Figures 57-61.

Figure 57. DAC bias.

Figure 58. Segmented current DAC top level.

Figure 59. 4 bit binary weighted DAC.

Figure 60. 6 bit unary weighted (thermometer coded) DAC [30].

Figure 61. Row and column decoders.

### 4.3.7: Current Controlled Oscillator