## Pázmany Péter Catholic University

DOCTORAL THESIS

## Parallelization of Numerical Methods on Parallel Processor Architectures

Author: Endre László Thesis Advisor: Dr. Péter SZOLGAY, D.Sc.

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

$in \ the$

Roska Tamás Doctoral School of Sciences and Technology Faculty of Information Technology and Bionics

February 12, 2016

DOI:10.15774/PPKE.ITK.2016.002

## Abstract

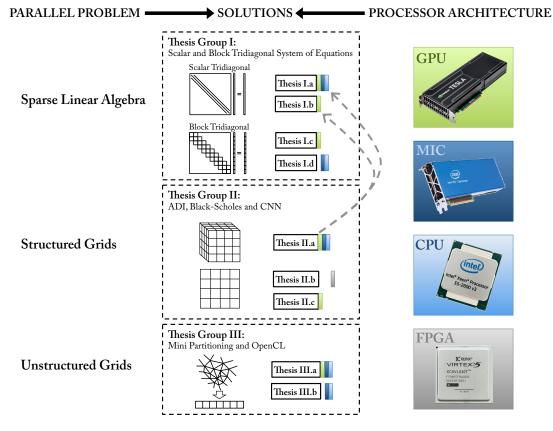

Common parallel processor microarchitectures offer a wide variety of solutions to implement numerical algorithms. The efficiency of different algorithms applied to the same problem vary with the underlying architecture which can be a multi-core CPU (Central Processing Unit), many-core GPU (Graphics Processing Unit), Intel's MIC (Many Integrated Core) or FPGA (Field Programmable Gate Array) architecture. Significant differences between these architectures exist in the ISA (Instruction Set Architecture) and the way the compute flow is executed. The way parallelism is expressed changes with the ISA, thread management and customization available on the device. These differences pose restrictions for the efficiency of the algorithm to be implemented. The aim of the doctoral work is to analyze the efficiency of the algorithms through the architectural differences and find efficient ways and new efficient algorithms to map problems to the selected parallel processor architectures. The problem selected for the study are numerical algorithms from three problem classes of the 13 Berkeley "dwarves" [1].

Engineering, scientific and financial applications often require the simultaneous solution of a large number of independent tridiagonal systems of equations with varying coefficients. The dissertation investigates the optimal choice of tridiagonal algorithm for CPU, Intel MIC and NVIDIA GPU with a focus on minimizing the amount of data transfer to and from the main memory using novel algorithms and register blocking mechanism, and maximizing the achieved bandwidth. It also considers block tridiagonal solutions which are sometimes required in CFD (Computational Fluid Dynamic) applications. A novel work-sharing and register blocking based Thomas solver is also presented.

Structured grid problems, like the ADI (Alternating Direction Implicit) method which boils down the solution of PDEs (Partial Differential Equation) into a number of solutions of tridiagonal system of equations is shown to improve performance by utilizing new, efficient tridiagonal solvers. Also, solving the one-factor Black-Scholes option pricing PDE with explicit and implicit time-marching algorithms on FPGA solution with the Xilinx Vivado HLS (High Level Synthesis) is presented. Performance of the FPGA solver is analyzed and efficiency is discussed. A GPU based implementation of a CNN (Cellular Neural Network) simulator using NVIDIA's Fermi architecture is presented.

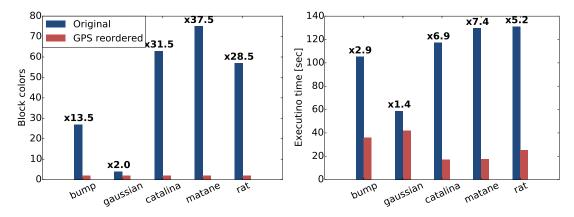

The OP2 project at the University of Oxford aims to help CFD domain scientists to decrease their effort to write efficient, parallel CFD code. In order to increase the efficiency of parallel incrementation on unstructured grids OP2 utilizes a mini-partitioning and a two level coloring scheme to identify parallelism during run-time. The use of the GPS (Gibbs-Poole-Stockmeyer) matrix bandwidth minimization algorithm is proposed to help create better mini-partitioning and block coloring by improving the locality of neighboring blocks (also known as mini-partitions) of the original mesh. Exploiting the capabilities of OpenCL for achieving better SIMD (Single Instruction Multiple Data) vectorization on CPU and MIC architectures throught the use of the SIMT (Single Instruction Multiple Thread) programming approach in OP2 is also discussed.

## Acknowledgements

I would like to thank my supervisor Prof. Dr. Péter Szolgay from the Pázmány Péter Catholic University for his guidance and valuable support.

I am also grateful to my colleagues István, Zoltán, Norbi, Bence, András, Balázs, Antal, Csaba, Vamsi, Dániel and many others whose discussion helped in the hard problems.

I spent almost two years at the University of Oxford, UK where I met dozens of great minds. First of all, I would like to thank for the supervision of Prof. Dr. Mike Giles who taught me a lot about parallel algorithms, architectures and numerical methods. I am also grateful to Rahim Lakhoo for the disucssions on technical matters, Eamonn Maguire for his inspiring and motivating thoughts.

All of these would not have been possible without the support of Hajni and my family throughout my PhD studies.

I would like to acknowledge the support of TÁMOP-4.2.1.B-11/2/KMR-2011-0002 and TÁMOP-4.2.2/B-10/1-2010-0014 and Campus Hungary. The research at the Oxford e-Research Centre has been partially supported by the ASEArch project on Algorithms and Software for Emerging Architectures, funded by the UK Engineering and Physical Sciences Research Council. Use of the facilities of the University of Oxford Advanced Research Computing (ARC) is also acknowledged.

# Contents

| Α  | bstra | lct          |                                                       | ii        |

|----|-------|--------------|-------------------------------------------------------|-----------|

| A  | ckno  | wledge       | ments                                                 | iii       |

| С  | onter | nts          |                                                       | iv        |

| Li | st of | Figur        | es                                                    | vii       |

| Li | st of | <b>Table</b> | 5                                                     | xi        |

| A  | bbre  | viation      | IS                                                    | xii       |

| N  | otati | ons an       | d Symbols                                             | xv        |

| 1  | Intr  | oducti       | ion                                                   | 1         |

|    | 1.1   | Classi       | fication of Parallelism                               | 3         |

|    | 1.2   | Select       | ed and Parallelized Numerical Problems                | 7         |

|    |       | 1.2.1        | Tridiagonal System of Equations                       | 7         |

|    |       | 1.2.2        | Alternating Directions Implicit Method                | 9         |

|    |       | 1.2.3        | Cellular Neural Network                               | 9         |

|    |       | 1.2.4        | Computational Fluid Dynamics                          | 9         |

|    | 1.3   | Parall       | el Processor Architectures                            | 10        |

|    |       | 1.3.1        | GPU: NVIDIA GPU architectures                         | 11        |

|    |       |              | 1.3.1.1 The NVIDIA CUDA architecture                  | 11        |

|    |       |              | 1.3.1.2 The Fermi hardware architecture               | 13        |

|    |       |              | 1.3.1.3 The Kepler hardware architecture              | 14        |

|    |       | 1.3.2        | CPU: The Intel Sandy Bridge architecture              |           |

|    |       | 1.3.3        | MIC: The Intel Knights Corner architecture            |           |

|    |       | 1.3.4        | FPGA: The Xilinx Virtex-7 architecture                | 16        |

| 2  | Alt   | ernatir      | ng Directions Implicit solver                         | 17        |

|    | 2.1   | Introd       | uction                                                | 17        |

|    | 2.2   | Solvin       | g the 3D linear diffusion PDE with ADI                | 18        |

| 3  | Sca   | lar Tri      | diagonal Solvers on Multi and Many Core Architectures | <b>22</b> |

|    | 3.1   | Introd       | uction                                                | 22        |

|    | 3.2   |              | gonal algorithms                                      | 23        |

|    |       | 3.2.1        | Thomas algorithm                                      | 23        |

| 3.3<br>3.4<br>3.5<br>3.6                  | <ul> <li>3.2.2 Cyclic Reduction</li></ul>                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $3.4 \\ 3.5$                              | <ul> <li>3.2.4 Hybrid Thomas-PCR Algorithm</li> <li>Data layout in memory</li> <li>Notable hardware characteristics for tridiagonal solvers</li> <li>CPU and MIC solution</li> <li>GPU solution</li> <li>3.6.1 Thomas algorithm with optimized memory access pattern</li> <li>3.6.1.1 Thomas algorithm with local transpose in shared memory</li> </ul> |

| $3.4 \\ 3.5$                              | Data layout in memoryNotable hardware characteristics for tridiagonal solversCPU and MIC solutionGPU solution3.6.1Thomas algorithm with optimized memory access pattern3.6.1.1Thomas algorithm with local transpose in shared memory                                                                                                                    |

| $3.4 \\ 3.5$                              | Notable hardware characteristics for tridiagonal solversCPU and MIC solutionGPU solution3.6.1Thomas algorithm with optimized memory access pattern3.6.1.1Thomas algorithm with local transpose in shared memory                                                                                                                                         |

| 3.5                                       | CPU and MIC solutionGPU solution3.6.1Thomas algorithm with optimized memory access pattern3.6.1.1Thomas algorithm with local transpose in shared memory                                                                                                                                                                                                 |

|                                           | GPU solution3.6.1Thomas algorithm with optimized memory access pattern3.6.1.1Thomas algorithm with local transpose in shared memory                                                                                                                                                                                                                     |

| 5.0                                       | <ul><li>3.6.1 Thomas algorithm with optimized memory access pattern</li><li>3.6.1.1 Thomas algorithm with local transpose in shared memory</li></ul>                                                                                                                                                                                                    |

|                                           | 3.6.1.1 Thomas algorithm with local transpose in shared memory                                                                                                                                                                                                                                                                                          |

|                                           | •                                                                                                                                                                                                                                                                                                                                                       |

|                                           |                                                                                                                                                                                                                                                                                                                                                         |

|                                           | shuffle                                                                                                                                                                                                                                                                                                                                                 |

|                                           | 3.6.2 Thomas algorithm in higher dimensions                                                                                                                                                                                                                                                                                                             |

|                                           | 3.6.3 Thomas-PCR hybrid algorithm                                                                                                                                                                                                                                                                                                                       |

| 3.7                                       | Performance comparison                                                                                                                                                                                                                                                                                                                                  |

|                                           | 3.7.1 Scaling in the $X$ dimension                                                                                                                                                                                                                                                                                                                      |

|                                           | 3.7.1.1 SIMD solvers                                                                                                                                                                                                                                                                                                                                    |

|                                           | 3.7.1.2 SIMT solvers                                                                                                                                                                                                                                                                                                                                    |

|                                           | 3.7.2 Scaling in higher dimensions                                                                                                                                                                                                                                                                                                                      |

|                                           | 3.7.2.1 SIMD solvers                                                                                                                                                                                                                                                                                                                                    |

|                                           | 3.7.2.2 SIMT solvers                                                                                                                                                                                                                                                                                                                                    |

| 3.8                                       | Conclusion                                                                                                                                                                                                                                                                                                                                              |

| $4.2 \\ 4.3 \\ 4.4$                       | Block-Thomas algorithm       Data layout for SIMT architecture         Cooperating threads for increased parallelism on SIMT architecture                                                                                                                                                                                                               |

| 4.5                                       | Optimization on SIMD architecture                                                                                                                                                                                                                                                                                                                       |

| 4.6                                       | Performance comparison and analysis                                                                                                                                                                                                                                                                                                                     |

| 4.7                                       | Conclusion                                                                                                                                                                                                                                                                                                                                              |

| Solv                                      | ving the Black-Scholes PDE with FPGA                                                                                                                                                                                                                                                                                                                    |

|                                           | Introduction                                                                                                                                                                                                                                                                                                                                            |

|                                           | Black-Scholes equation and its numerical solution                                                                                                                                                                                                                                                                                                       |

|                                           | Multi and manycore algorithms                                                                                                                                                                                                                                                                                                                           |

|                                           | 5.3.1 Stencil operations for explicit time-marching                                                                                                                                                                                                                                                                                                     |

|                                           | 5.3.2 Thomas algorithm for implicit time-marching                                                                                                                                                                                                                                                                                                       |

| 5.4                                       | FPGA implementation with Vivado HLS                                                                                                                                                                                                                                                                                                                     |

|                                           | 5.4.1 Stencil operations for explicit time-marching                                                                                                                                                                                                                                                                                                     |

|                                           | 5.4.2 Thomas algorithm for implicit time-marching                                                                                                                                                                                                                                                                                                       |

| 5.5                                       | Performance comparison                                                                                                                                                                                                                                                                                                                                  |

| 5.6                                       | Conclusion                                                                                                                                                                                                                                                                                                                                              |

| CP.                                       | U based CNN simulator with double buffering                                                                                                                                                                                                                                                                                                             |

|                                           |                                                                                                                                                                                                                                                                                                                                                         |

| n I                                       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                            |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Introduction                                                                                                                                                                                                                                                                                                                                            |

|                                           | 3.8<br>Bloc<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br><b>Solv</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                                                                                                                                                   |

|   | <b>C 1</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00  |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 6.4        | er e same erst my                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86  |

|   | 6.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 87  |

|   | 6.6        | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88  |

| 7 | Uns        | tructured Grid Computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89  |

|   | 7.1        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89  |

|   | 7.2        | The OP2 Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91  |

|   | 7.3        | Mini-partitioning and coloring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94  |

|   |            | 7.3.1 Mesh reordering in Volna OP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|   |            | 7.3.2 Benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|   | 7.4        | Vectorization with OpenCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|   | 7.5        | Performance analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|   | 1.0        | 7.5.1 Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

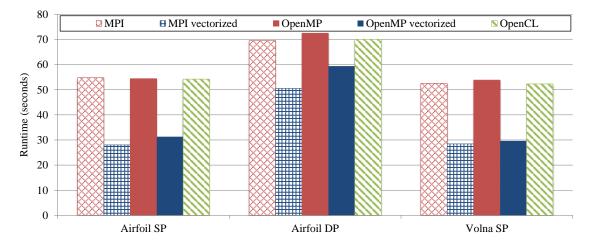

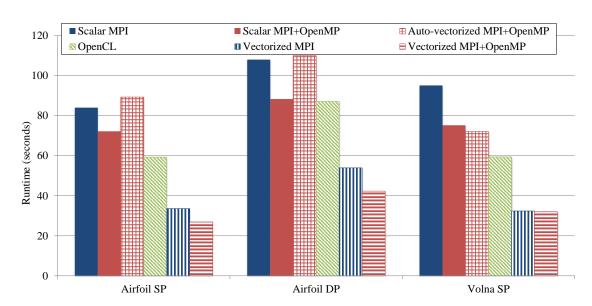

|   |            | 7.5.2 OpenCL performance on CPU and the Xeon Phi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|   | 7.6        | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|   | 7.0        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .07 |

| 8 | Con        | clusion 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 09  |

|   | 8.1        | New scientific results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .09 |

|   | 8.2        | Application of the results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16  |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| A | App        | pendix 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17  |

|   | A.1        | Hardware and Software for Scalar and Block Tridiagonal Solvers 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17  |

|   | A.2        | System size configuration for benchmarking block tridiagonal solvers 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19  |

|   | A.3        | Volna OP2 benchmark setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20  |

|   | A.4        | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|   |            | The second s | -   |

#### References

# List of Figures

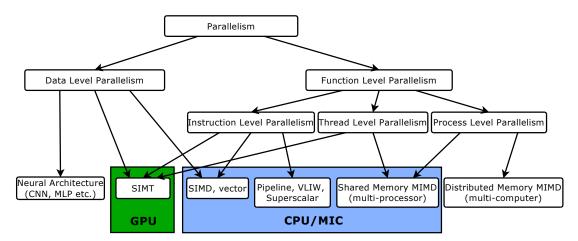

| 1.1 | Classification of parallelism along with parallel computer and processor<br>architectures that implement them.                                                                                                                             | 4   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

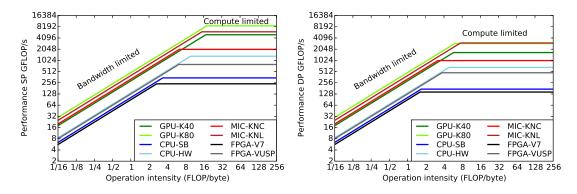

| 1.2 | Roofline model for comparing parallel processor architectures. Note: SP stands for Single Precision and DP stands for Double Precision                                                                                                     | 5   |

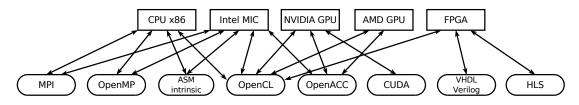

| 1.3 | Relations between processor architectures, languages and language exten-                                                                                                                                                                   | 5   |

| 1.0 | sions                                                                                                                                                                                                                                      | 6   |

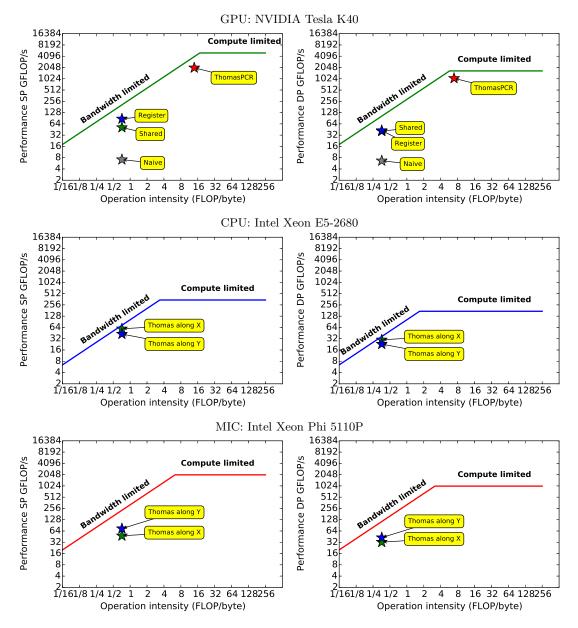

| 1.4 | Roofline model applied to the implemented scalar tridiagonal solvers on GPU, CPU and MIC processor architectures. The proximity of stars to the upper computational limits shows the optimality of the implementation on the architecture. | 8   |

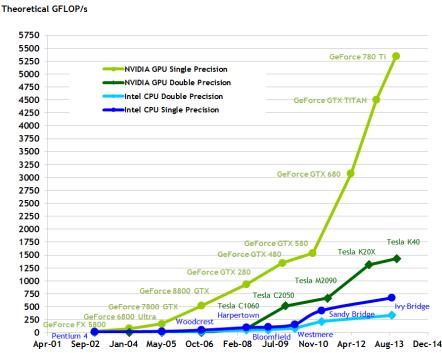

| 1.5 | The increase in computation power. A comparison of NVIDIA GPUs and<br>Intel CPUs. [20]                                                                                                                                                     | 11  |

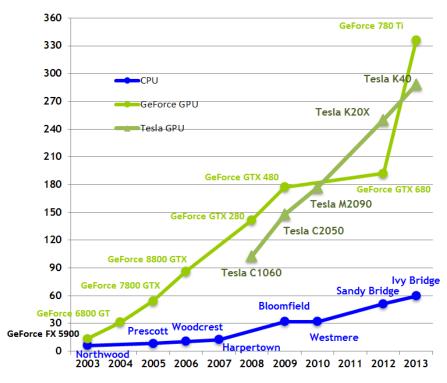

| 1.6 | The increase in memory bandwidth. A comparison of NVIDIA GPUs and<br>Intel CPUs. [20]                                                                                                                                                      | 12  |

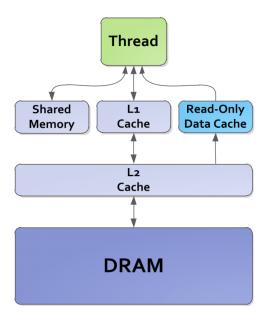

| 1.7 | Kepler and Fermi memory hierarchy according to [22]. The general purpose read-only data cache is known on Fermi architectures as texture                                                                                                   |     |

|     | cache, as historically it was only used to read textures from global memory.                                                                                                                                                               | 15  |

| 3.1 | Starting state of the equation system. 0 values outside the bar are part<br>of the equation system and they are needed for the algorithm and imple-                                                                                        |     |

|     | mentation.                                                                                                                                                                                                                                 | 31  |

| 3.2 | State of the equation system after the forward sweep of the modified<br>Thomas algorithm.                                                                                                                                                  | 31  |

| 3.3 | State of the equation system after the backward sweep of the modified<br>Thomas algorithm. Bold variables show the elements of the reduced sys-                                                                                            | 0.1 |

| 9.4 | tem which is to be solved with the PCR algorithm.                                                                                                                                                                                          | 31  |

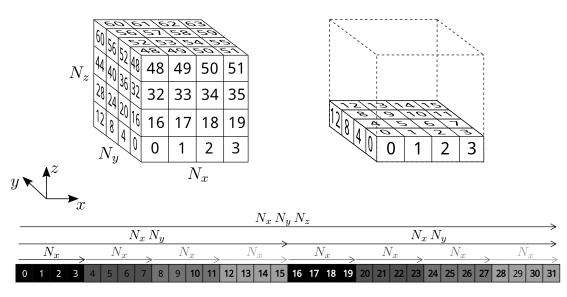

| 3.4 | Data layout of 3D cube data-structure.                                                                                                                                                                                                     | 32  |

| 3.5 | Vectorized Thomas solver on CPU and MIC architectures. Data is loaded<br>into $M$ wide vector registers in $M$ steps. On AVX $M = 4$ for double<br>precision and $M = 8$ for single precision. On IMCI $M = 8$ for double                  |     |

|     | precision and $M = 16$ for single precision. Data is then transposed within<br>registers as described in Figure 3.6 and after that $M$ number of iterations<br>of the Thomas algorithm is performed. When this is done the procedure       |     |

|     | repeats until the and of the systems is reached                                                                                                                                                                                            | 38  |

|     |                                                                                                                                                                                                                                            |     |

| 3.6  | Local data transposition of an $M \times M$ two dimensional array of $M$ consecutive values of $M$ systems, where $a_{ti}$ is the <i>i</i> th coefficient of tridiagonal system $t$ . Transposition can be performed with $M \times \log_2 M$ AVX or IMCI shuffle type instructions such as swizzle, permute and align or their masked counter part. On AVX $M = 4$ for double precision and $M = 8$ for single precision. On IMCI $M = 8$ for double precision and $M = 16$ for single precision.                                                                | 38 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

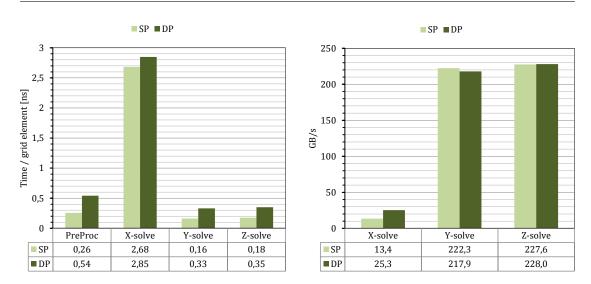

| 3.7  | ADI kernel execution times on K40m GPU, and corresponding bandwidth<br>figures for $X$ , $Y$ and $Z$ dimensional solves based on the Thomas algo-<br>rithm. Single precision $X$ dimensional solve is slower $\times 16.75$ than the $Y$<br>dimensional solve. Bandwidth is calculated from the amount of data that<br>supposed to loaded and stored and the elapsed time. High bandwidth in<br>the case of $Y$ and $Z$ dimensional solve is reached due to local memory                                                                                          |    |

|      | caching and read-only (texture) caching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

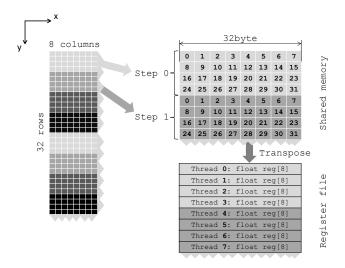

| 3.8  | Local transpose with shared memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

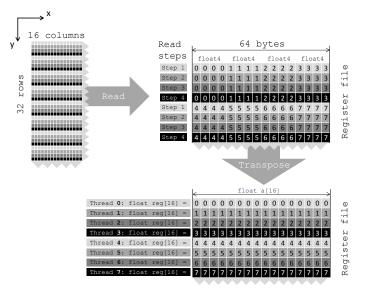

| 3.9  | Local transpose with registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45 |

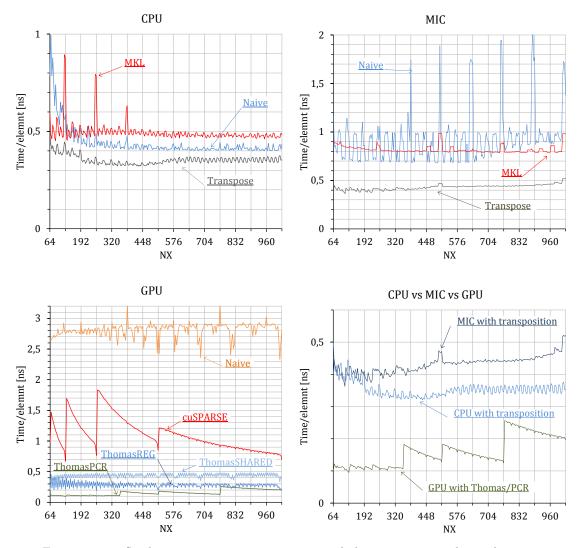

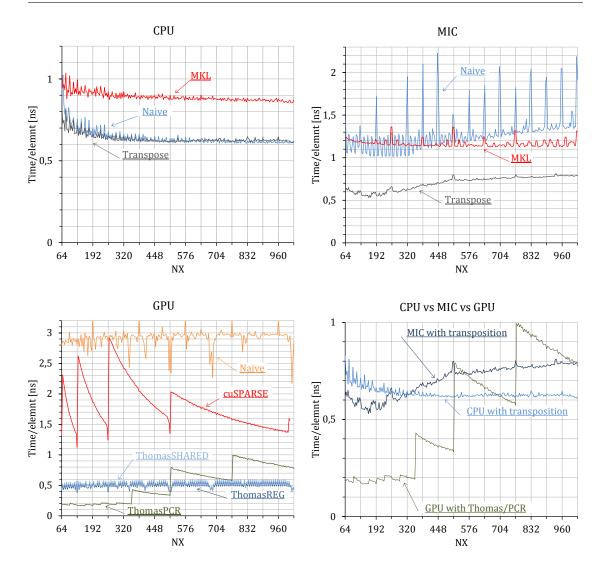

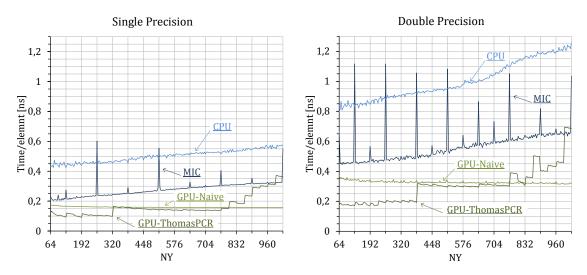

| 3.10 | Single precision execution time per grid element. $65536$ tridiagonal systems with varying $NX$ length along the X dimension are solved. CPU, MIC and GPU execution times along with the comparison of the best                                                                                                                                                                                                                                                                                                                                                   | 50 |

| 3.11 | solver on all three architectures are show                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 |

| 3.12 | solver on all three architectures are show                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51 |

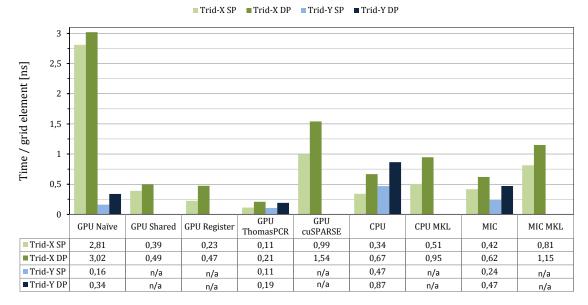

| 3.13 | CPU, MIC and GPU execution times along with the comparison of the best solver on all three architectures are show. $\dots \dots \dots \dots \dots$ Grid element execution times per grid element on a $240 \times 256 \times 256$ cube domain. X dimension is chosen to be 240 to alleviate the effect of caching                                                                                                                                                                                                                                                 | 55 |

|      | and algorithmic inefficiencies which occurs on sizes of power of 2 as it can be seen on Figures 3.10,3.11,3.12. Missing bars and n/a values are due to non-feasible or non-advantagous implementations in the Y dimension. $\therefore$                                                                                                                                                                                                                                                                                                                           | 57 |

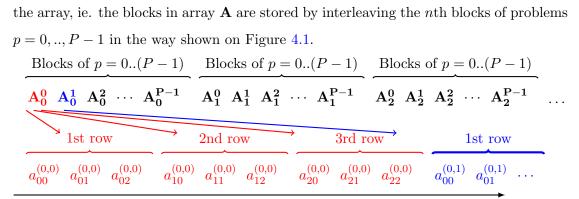

| 4.1  | Data layout within coefficient array <b>A</b> . This layout allows nearly coa-<br>lesced access pattern and high cache hit rate when coalescence criteria is<br>not met. Here $\mathbf{A}_{\mathbf{n}}^{\mathbf{p}}$ is the <i>n</i> th block (ie. <i>n</i> th block-row in the coefficient<br>matrix) of problem $p$ and $p \in [0, P-1]$ , $n \in [0, N-1]$ . Notation for the<br>scalar elements in the <i>n</i> th block of problem $p$ are shown on Eq. (4.3).<br>Bottom part of the figure shows the mapping of scalar values to the linear<br>main memory. | 61 |

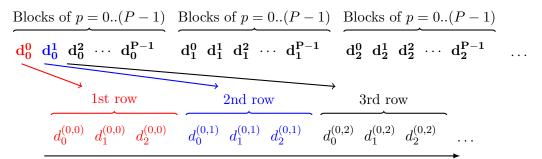

| 4.2  | Data layout of <b>d</b> as block vectors. This layout allows nearly coalesced<br>access pattern and high cache hit rate when coalescence criteria is not<br>met. Here $\mathbf{d_n^p}$ is the <i>n</i> th block (ie. <i>n</i> th block-row in the coefficient matrix)<br>of problem $p$ and $p \in [0, P-1]$ , $n \in [0, N-1]$ . Notation for the scalar<br>elements in the <i>n</i> th block of problem $p$ are shown on Eq. (4.4). Bottom<br>part of the figure shows the mapping of scalar values to the linear main                                          |    |

|      | memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61 |

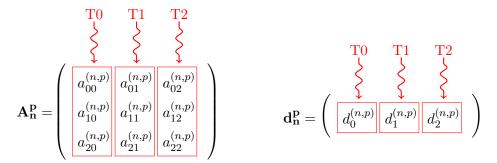

| 4.3                                       | Shared storage of blocks in registers. Arrows show load order. Thread $T0,T1$ and $T2$ stores the first, second and third columns of block $\mathbf{A_n^p}$ and first, second and third values of $\mathbf{d_n^p}$ .                                                                                                                                                                                                                                            | 63       |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.4                                       | Data layout within coefficient array <b>A</b> suited for better data locality on CPU and MIC. Here $\mathbf{A_n^p}$ is the <i>n</i> th block (ie. <i>n</i> th block-row in the coefficient matrix) of problem $p$ and $p \in [0, P-1]$ , $n \in [0, N-1]$ . Notation for                                                                                                                                                                                        | 65       |

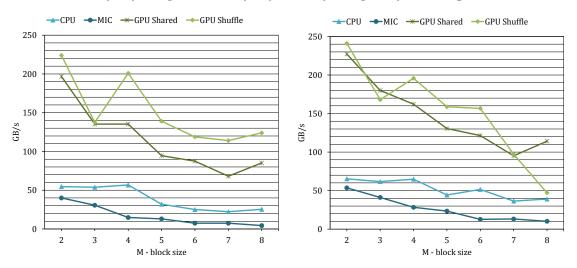

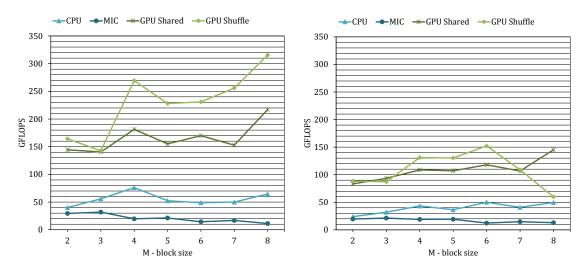

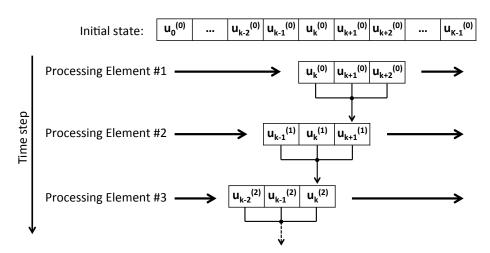

| 4.5                                       | Single (left) and double (right) precision effective bandwidth when solv-<br>ing block tridiagonal systems with varying $M$ block sizes. Bandwidth is<br>computed based on the amount of data to be transferred. Caching in L1<br>and registers can make this figure higher then the achievable bandwidth                                                                                                                                                       | 67       |

| 4.6                                       | Single (left) and double (right) precision effective computational through-<br>put when solving block tridiagonal systems with varying $M$ block sizes.<br>GFLOPS is computed based on the amount of floating point arithmetic<br>operations needed to accomplish the task. Addition, multiplication and<br>division is considered as floating point arithmetic operations, ie. FMA                                                                             |          |

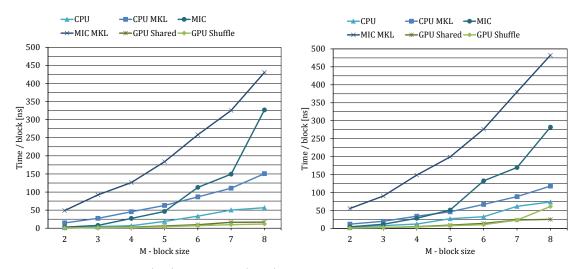

| 4.7                                       | (Fused Multiply and Add) is considered as two floating point instructions.<br>Single (left) and double (right) precision block-tridiagonal solver execu-<br>tion time per block matrix row for varying block sizes.                                                                                                                                                                                                                                             | 68<br>69 |

| 4.8                                       | Single (left) and double (right) precision block tridiagonal solver speedup over the CPU MKL banded solver.                                                                                                                                                                                                                                                                                                                                                     | 69       |

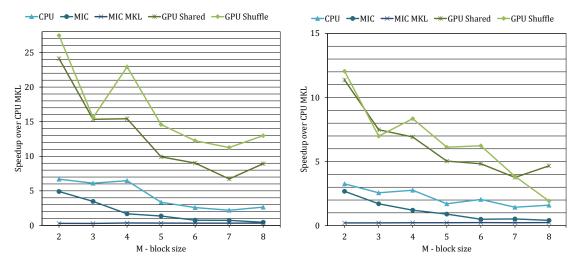

| 5.1                                       | Stacked FPGA processing elements to pipeline stencil operations in a systemic fashion. The initial system variables $u_0^{(0)},, u_{K-1}^{(0)}$ are swept by the first processing element. The result $u_{k+1}^{(1)}$ is fed into the second processing element.                                                                                                                                                                                                | 77       |

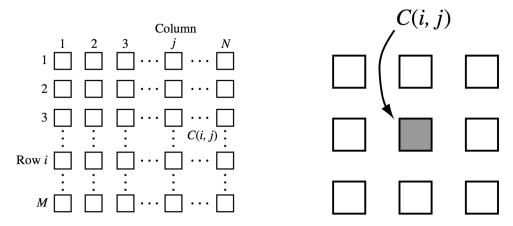

| 6.1                                       | Left: standard CNN (Cellular Neural Network) architecture. Right: CNN local connectivity to neighbor cells. Source: [64]                                                                                                                                                                                                                                                                                                                                        | 82       |

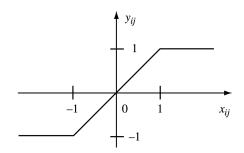

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | Piecewise linear output function defined in Eq. (6.2). Source: [64] Example of diffuson template. Original image on the left, diffused image on the right                                                                                                                                                                                                                                                                                                       | 83       |

| 6.4                                       | The use of texture and constant caching - code snippets from source code.                                                                                                                                                                                                                                                                                                                                                                                       |          |

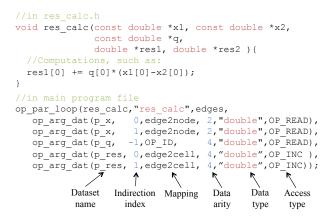

| 7.1                                       | Demonstrative example of the OP2 API in Airfoil: parallel execution of the res_calc kernel function by the op_par_loop for each elements in the edges set.                                                                                                                                                                                                                                                                                                      | 92       |

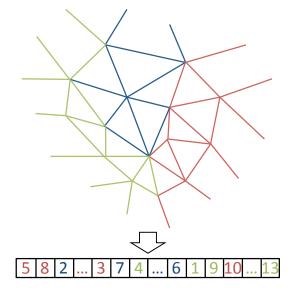

| 7.2                                       | Demonstrative example of block coloring: edges are partitioned into three<br>blocks colors. Indices of edges belonging to different colors are shuffled in                                                                                                                                                                                                                                                                                                      | 52       |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93       |

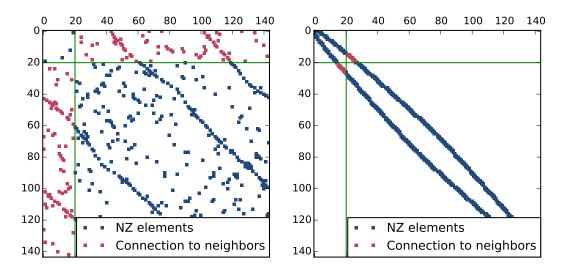

| 7.3                                       | Example of sparse symmetric matrix or adjacency matrix representing an<br>unstructured mesh (left) and the same matrix after matrix bandwidth<br>minimization reordering (right). Elements connecting the vertices of the<br>first block (elements 0-19) of the mesh with other blocks of the mesh (20-<br>39, 40-59, etc.) are denoted with red color. On the left matrix the first<br>block of the mesh is connected to other blocks. On the right matrix the |          |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95       |

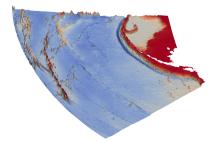

| 7.4                                       | Demonstrative examples of the Volna OP2 test cases.                                                                                                                                                                                                                                                                                                                                                                                                             | -95      |

| . 96  |

|-------|

| . 98  |

| 100   |

| . 101 |

|       |

|       |

| . 106 |

|       |

|       |

| . 107 |

|       |

|       |

|       |

| . 110 |

|       |

# List of Tables

| 2.1        | Number of parallel systems increases rapidly as dimension $d$ is increased.<br>$N$ is chosen to accommodate an $N^d$ single precision problem domain on<br>the available 12 GB of an NVIDIA Tesla K40 GPU                                                                                     | . 18  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.1        | FPGA Resource statistics for a single processor. The final number of implementable explicit solvers is bounded by the 3600 DSP slices, while the number of implicit solvers is bounded by the 2940 Block RAM Blocks on the Xilinx Virtex-7 XC7V690T processor.                                | . 78  |

| 5.2        | Performance - Single Precision                                                                                                                                                                                                                                                                |       |

| 5.3        | Performance - Double Precision                                                                                                                                                                                                                                                                |       |

| 6.1        | Comparison table                                                                                                                                                                                                                                                                              | . 87  |

| 7.1        | Details of the representative tsunami test cases. BW - Bandwidth                                                                                                                                                                                                                              | . 97  |

| 7.2        | Properties of Airfoil and Volna kernels; number of floating point opera-                                                                                                                                                                                                                      | 109   |

| 7.3        | tions and numbers transfers                                                                                                                                                                                                                                                                   |       |

| 7.3<br>7.4 | Useful bandwidth (BW - GB/s) and computational (Comp - GFLOP/s)                                                                                                                                                                                                                               | . 104 |

|            | throughput baseline implementations on Airfoil (double precision) and<br>Volna (single precision) on CPU 1 and the K40 GPU                                                                                                                                                                    | 105   |

| 7.5        | Timing and bandwidth breakdowns for the Airfoil benchmarks in dou-<br>ble(single) precision on the 2.8M cell mesh and Volna using the OpenCL<br>backend on a single socket of CPU and Xeon Phi. Also, kernels with                                                                            | . 100 |

|            | implicit OpenCL vectorization are marked in the right columns                                                                                                                                                                                                                                 | . 106 |

| A.1        | Details of Intel Xeon Sandy Bridge server processor, Intel Xeon Phi co-<br>processor and the NVIDIA Tesla GPU card. *Estimates are based on<br>[23], [44] and [94]. Both Intel architectures have 8-way, shared LLC with<br>ring-bus topology. HT - Hyper Thread, MM - Multi Media, RO - Read |       |

|            | Only                                                                                                                                                                                                                                                                                          | . 118 |

| A.2        | Parameter $N$ - Length of a system used for benchmarking a processor<br>architecture and solver. The length of the system is chosen such that the                                                                                                                                             |       |

|            | problem fits into the memory of the selected architecture                                                                                                                                                                                                                                     | . 119 |

| A.3        | Parameter $P$ - Number of systems used for benchmarking a processor<br>architecture and solver. The number of systems is chosen such that the                                                                                                                                                 |       |

|            | problem fits into the memory of the selected architecture.                                                                                                                                                                                                                                    | . 119 |

| A.4        | Details of Intel Xeon Haswell server processor used in the benchmarks of                                                                                                                                                                                                                      |       |

|            | Volna OP2. HT - Hyper Thread, MM - Multi Media                                                                                                                                                                                                                                                | . 120 |

| A.5        | Benchmark systems specifications                                                                                                                                                                                                                                                              | . 120 |

# Abbreviations

| ADI            | Alternating <b>D</b> irections <b>I</b> mplicit method                                                                                                                                                                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALU            | Arithmetic Logic Unit                                                                                                                                                                                                                                                     |

| AoS            | Array of Structures                                                                                                                                                                                                                                                       |

| ARM            | $\mathbf{A}$ dvanced $\mathbf{R}$ ISC $\mathbf{M}$ achine Holdings Plc.                                                                                                                                                                                                   |

| ASIC           | ${\bf A} {\rm pplication} \ {\bf S} {\rm pecific} \ {\bf Integrated} \ {\bf C} {\rm ircuit}$                                                                                                                                                                              |

| $\mathbf{ASM}$ | Asembly                                                                                                                                                                                                                                                                   |

| AVX            | $\mathbf{A}$ dvanced $\mathbf{V}$ ector $\mathbf{E}\mathbf{x}$ tensions                                                                                                                                                                                                   |

| BRAM           | Block RAM                                                                                                                                                                                                                                                                 |

| BS             | Black-Scholes                                                                                                                                                                                                                                                             |

| CFD            | Computational Fluid Dynamics                                                                                                                                                                                                                                              |

| CLB            | Configurable Logic Block                                                                                                                                                                                                                                                  |

| CMOS           | $\mathbf{C} \mathbf{o} \mathbf{m} \mathbf{p} \mathbf{e} \mathbf{m} \mathbf{i} \mathbf{o} \mathbf{N} \mathbf{i} \mathbf{d} \mathbf{e} \mathbf{-} \mathbf{S} \mathbf{e} \mathbf{m} \mathbf{i} \mathbf{c} \mathbf{o} \mathbf{d} \mathbf{u} \mathbf{c} \mathbf{o} \mathbf{r}$ |

| CNN            | Cellular Neural Network                                                                                                                                                                                                                                                   |

| CPU            | Central Processing Unit                                                                                                                                                                                                                                                   |

| CR             | $\mathbf{C}$ yclic $\mathbf{R}$ eduction                                                                                                                                                                                                                                  |

| CUDA           | Compute Unified Device Architecture                                                                                                                                                                                                                                       |

| DDR            | Double Data Rate                                                                                                                                                                                                                                                          |

| DP             | Double Precision                                                                                                                                                                                                                                                          |

| DSL            | $\mathbf{D}$ omain $\mathbf{S}$ pecific $\mathbf{L}$ anguage                                                                                                                                                                                                              |

| DSP            | $\mathbf{D}$ igital $\mathbf{S}$ ignal $\mathbf{P}$ rocessing                                                                                                                                                                                                             |

| FLOP           | Floating Point $OP$ eration                                                                                                                                                                                                                                               |