#### A Comprehensive Approach to MPSoC Security

Achieving Network-on-Chip security: a hierarchical, multi-agent approach

Doctoral Dissertation submitted to the

Faculty of Informatics of the Università della Svizzera Italiana

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

presented by Slobodan Lukovic

under the supervision of Prof. Mariagiovanna Sami

November 2012

#### Dissertation Committee

Prof. Laura PozziUniversity of LuganoProf. Evanthia PapadopoulouUniversity of Lugano

Prof. Miroslaw Malek Humboldt University, Berlin, Germany

**Dr. Guido Marco Bertoni** ST Microelectronics, Italy

Dissertation accepted on 13 November 2012

Research Advisor PhD Program Director

Prof. Mariagiovanna Sami Prof. Antonio Carzaniga

I certify that except where due acknowledgement has been given, the work presented in this thesis is that of the author alone; the work has not been submitted previously, in whole or in part, to qualify for any other academic award; and the content of the thesis is the result of work which has been carried out since the official commencement date of the approved research program.

Slobodan Lukovic Lugano, 13 November 2012

To my family

Scio me nihil scire.

Socrates

#### Abstract

Multiprocessor Systems-on-Chip (MPSoCs) are pervading our lives, acquiring ever increasing relevance in a large number of applications, including even safety-critical ones. MPSoCs, are becoming increasingly complex and heterogeneous; the Networks on Chip (NoC) paradigm has been introduced to support scalable on-chip communication, and (in some cases) even with reconfigurability support. The increased complexity as well as the networking approach in turn make security aspects more critical.

In this work we propose and implement a hierarchical multi-agent approach providing solutions to secure NoC based MPSoCs at different levels of design. We develop a flexible, scalable and modular structure that integrates protection of different elements in the MPSoC (e.g. memory, processors) from different attack scenarios. Rather than focusing on protection strategies specifically devised for an individual attack or a particular core, this work aims at providing a comprehensive, system-level protection strategy: this constitutes its main methodological contribution. We prove feasibility of the concepts via prototype realization in FPGA technology.

## Acknowledgements

This doctoral dissertation would not have come to a successful completion, without the help I received from many people that have helped me over my challenging but interesting Ph.D. adventure. Professor Mariagiovanna Sami, my supervisor, is the first person that I would like to thank, without whom I do not think I would have been where I am now. She has been a true friend and a supporter. I am truly indebted to her for insightful guidance over my candidature.

Next I would like to acknowledge the support and patience of my family members. You have supported me in the most difficult times and believed in me even when I did not believe in myself.

My work could not be efficient and successful without great help of my environment. I'd like to thank to all ALaRI staff for collaboration in different aspects of my research. In particular I'd like to mention my officemates and at the same time travel-mates and flat-mates in some cases, who have helped me grow in areas not exclusively related to my core research. I'd certainly never would be able to structure, organize and write my papers in such a good manner without great guidance of Leandro Fiorin and I would certainly never perform so well in diplomacy and other 'soft-skills' without lessons learnt from my great Sicilian friend Anotnio Taddeo. Finally, I'd like to thank Igor Kaitovic, the youngest member but great asset to our team, for many advices, hints and tips in various areas. Still, it is worth mentioning here Umberto Bondi, ALaRI program manager who has never restricted me from traveling to conferences regardless the location. I'd also like to thank members of secretary office for their patience and understanding in resolving sometimes very complicated administrative situations. I would like to thank my former students Paolo Pezzino, Nikolaos Christianos and Anurbay Srinavasta who have greatly contributed to some of my publications. Their efforts are embedded in my thesis as well as their friendship to my memory.

At the end, I'd like to thank my Ph.D. thesis committee as well as all those unknown reviewers of my papers who have pointed out many inconsistence and also sometimes sparked good ideas for my work. They have provided me with valuable feedback on my work, and helped in improving it.

# Contents

| Co  | onten   | ts                                                                                               | хi  |

|-----|---------|--------------------------------------------------------------------------------------------------|-----|

| Lis | st of l | Figures                                                                                          | xv  |

| Lis | st of 7 | Tables                                                                                           | xix |

| 1   | Intr    | oduction and Motivation                                                                          | 1   |

|     | 1.1     | Multi-Processor Systems-on-Chip                                                                  | 2   |

|     | 1.2     | Network-on-Chip based Multi-Processor Systems-on-Chip                                            | 4   |

|     | 1.3     | Security vulnerabilities and protection strategies for NoC based Multi-Processor Systems-on-Chip | 4   |

|     | 1.4     | Problem, objectives and contributions of the thesis                                              | 6   |

| 2   | Bacl    | kground and Related Work                                                                         | 11  |

|     | 2.1     | On-chip interconnecting strategies - Networks-on-Chips                                           | 12  |

|     | 2.2     | Security overview - basic terms and taxonomies                                                   | 17  |

|     |         | 2.2.1 Security taxonomies                                                                        | 18  |

|     | 2.3     | Security aspects and on-chip systems                                                             | 20  |

|     |         | 2.3.1 Protection against specific attacks                                                        | 23  |

|     |         | 2.3.2 Trusted Systems, Trusted Computing and Trusting Policy .                                   | 31  |

|     | 2.4     | Multiple-agent systems                                                                           | 32  |

|     | 2.5     | FPGA technologies and their utilization for design of Multi-Processor                            |     |

|     |         | Systems-on-Chip                                                                                  | 33  |

| 3   | Refi    | ned Problem Statement                                                                            | 35  |

|     | 3.1     | Security vulnerabilities of Multi-Processor Systems-on-Chip                                      | 35  |

|     | 3.2     | Main challenge addressed - Security from a system wide perspective                               | 36  |

xii Contents

| Ι   | Res  | earch                 | Approaches and Conceptual Solution                                                                      | 39        |

|-----|------|-----------------------|---------------------------------------------------------------------------------------------------------|-----------|

| 4   | Refe | rence .               | Architecture and Attack Models                                                                          | 41        |

|     | 4.1  | Refere                | ence architecture                                                                                       | 41        |

|     |      | 4.1.1                 |                                                                                                         | 42        |

|     |      | 4.1.2                 | NoC architecture                                                                                        | 43        |

|     | 4.2  | Attack                | models                                                                                                  | 49        |

|     |      | 4.2.1                 | Unauthorized memory access                                                                              | 49        |

|     |      |                       | Code Injection Attacks - Buffer Overflow                                                                | 50        |

|     |      |                       | Denial-of-Service attack                                                                                | 51        |

| 5   | The  | propos                | sed conceptual solution - a Hierarchical Agent-Based Secu                                               | <b>!-</b> |

|     | rity | Frame                 | work                                                                                                    | 53        |

|     | 5.1  | Securi                | ty Agents                                                                                               | 54        |

|     | 5.2  | Hierar                | chical Structure of Security Agents                                                                     | 55        |

|     | 5.3  | Comm                  | nunication among Security Agents                                                                        | 56        |

|     | 5.4  | Securi                | ty policy                                                                                               | 58        |

|     |      | 5.4.1                 | Disruptions, security alerts and positive feedback                                                      | 58        |

|     |      | 5.4.2                 | Trusting policy                                                                                         | 60        |

| II  | Im   | 5.4.3<br>p <b>lem</b> | Security domains, violation detection and countermeasures  entation and Validation of the Proposed Solu |           |

| tio | ns   | _                     | _                                                                                                       | 65        |

| 6   | Fron | n the G               | General Approach to Actual Architectural Design                                                         | 67        |

|     | 6.1  | SoC D                 | esign Flow and Fast Prototyping Strategies                                                              | 67        |

|     |      | 6.1.1                 | The Standard FPGA design flow                                                                           | 69        |

|     |      | 6.1.2                 | Network-on-Chip adjusted FPGA design flow                                                               | 71        |

|     | 6.2  | Netwo                 | ork-on-Chip as a medium to accommodate security related                                                 |           |

|     |      | enhan                 | cements                                                                                                 | 73        |

|     |      | 6.2.1                 | Enhancing Network Interfaces                                                                            | 74        |

|     | 6.3  | Attack                | specific protection                                                                                     | 74        |

|     |      | 6.3.1                 | Attack Specific Agent - Data Protection Unit                                                            | 75        |

|     |      | 6.3.2                 | Attack Specific Agent - Stack Protection Unit                                                           | 77        |

|     |      | 6.3.3                 | Attack Specific Agents - DoSPROT                                                                        | 83        |

|     | 6.4  | Local                 | Security Agent                                                                                          | 86        |

|     |      | 6.4.1                 | Local Security Manager                                                                                  | 87        |

|     |      | 6.4.2                 | Communication interface                                                                                 | 89        |

|     |      | 6.4.3                 | Specific Local Security Agent solutions                                                                 | 90        |

xiii Contents

|    | 6.5   | Central Security Agent                                            | 1  |

|----|-------|-------------------------------------------------------------------|----|

|    | 6.6   | Secure NoC                                                        | 5  |

| 7  | Test  | ing and Validation 9                                              | 7  |

|    | 7.1   | _                                                                 | 7  |

|    | 7.2   | Attack Specific Agent - Data Protection Unit - implementation and |    |

|    |       |                                                                   | 8  |

|    |       |                                                                   | 8  |

|    |       | 7.2.2 Reconfiguration of the DPU table 9                          | 9  |

|    |       | 7.2.3 Costs of implementation                                     | )2 |

|    | 7.3   | Attack Specific Agent - Stack Protection Unit                     | )3 |

|    |       | 7.3.1 Costs of implementations                                    | )5 |

|    | 7.4   | Attack Specific Agent - Vulnerable DoS - validation 10            | )6 |

|    | 7.5   | Attack Specific Agent - Flooding DoS - validation                 | )7 |

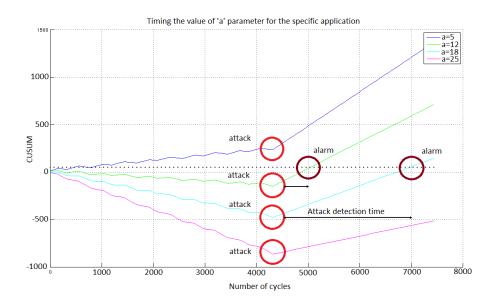

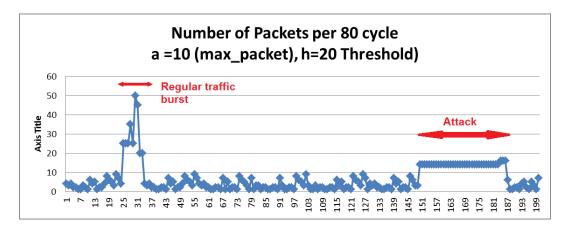

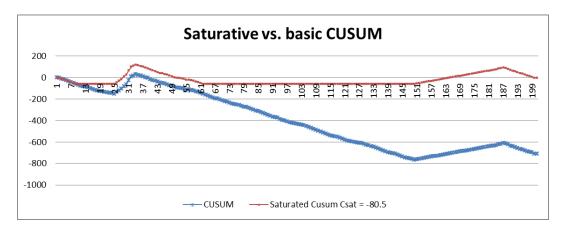

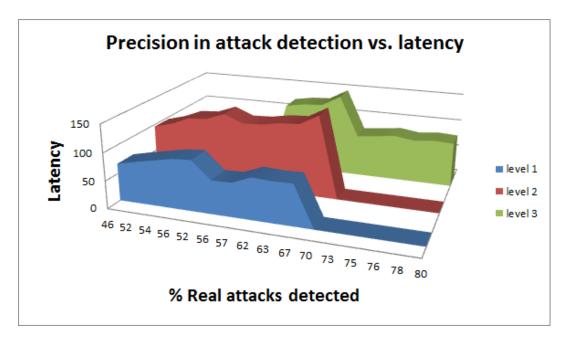

|    |       | 7.5.1 Simulation of FDoS detection by CUSUM algorithms and        |    |

|    |       | parameters tuning                                                 | )8 |

|    |       | 7.5.2 Costs of the implementation                                 | 13 |

|    | 7.6   | Validation of the overall security framework                      | 13 |

|    |       | 7.6.1 Overall security framework efficiency                       | 8  |

| 8  | Asse  | essment and Comparisons with Other Approaches 12                  | 3  |

|    | 8.1   | General considerations and comparisons with other approaches . 12 | 23 |

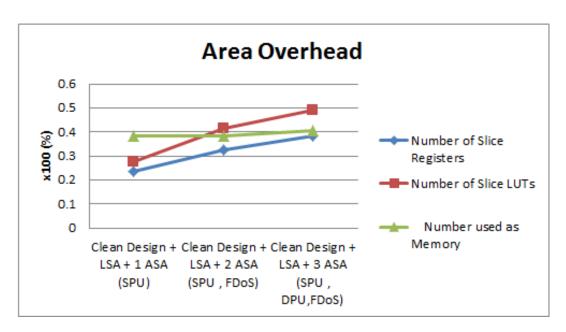

|    | 8.2   | Area overhead                                                     | 26 |

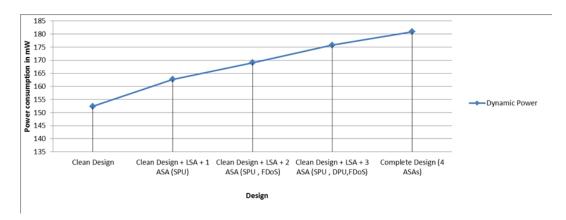

|    | 8.3   | Power consumption overhead                                        | 28 |

|    | 8.4   | Impact on performance                                             | 31 |

| 9  | Con   | clusions and Future Work 13                                       | 3  |

|    | 9.1   | Concluding evaluations and remarks                                | 34 |

|    |       | 9.1.1 Portability and scalability of the solution                 | 35 |

|    | 9.2   | Future work                                                       | 35 |

| Bi | bliog | raphy 13                                                          | 7  |

|    |       |                                                                   |    |

xiv Contents

# Figures

| 1.1 | Network-on-Chip based Multi-Processor Systems-on-Chip - general structure                                                               | 5       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1.2 | Architecture of the fully secured system (security related elements are denoted in red)                                                 | 6       |

|     |                                                                                                                                         |         |

| 2.1 | Computer and Network incident taxonomy by (Howard and Longstaff [1998])                                                                 | f<br>19 |

| 2.2 | Taxonomy of security attacks on embedded systems according to (Ravi et al. [2004]; <i>Hardware-software design methods for security</i> |         |

|     |                                                                                                                                         | 20      |

| 2.3 | A taxonomy of code injection attacks according to (Mitropoulos                                                                          |         |

|     | et al. [2011])                                                                                                                          | 25      |

| 2.4 | A taxonomy of code insertion attack countermeasures according                                                                           |         |

|     | to (Mitropoulos et al. [2011])                                                                                                          | 26      |

| 2.5 | A stack based buffer overflow attack by overwriting the return ad-                                                                      |         |

|     | dress register (a) Vulnerable code (b) Layout of the stack before                                                                       |         |

|     | an attack (c) Layout of the stack after an attack, from (Hardware-                                                                      |         |

|     | software design methods for security and reliability of MPSoCs [2009])                                                                  | 27      |

| 2.6 | Denial-of-Service attacks taxonomy, from (Ramanauskaite and Cenys                                                                       |         |

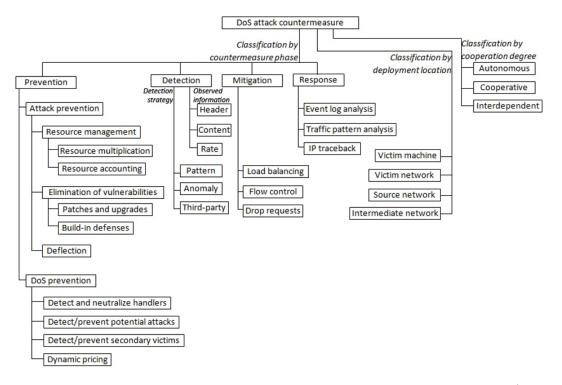

|     |                                                                                                                                         | 28      |

| 2.7 | Denial-of-Service countermeasure classification scheme, from (Ra-                                                                       |         |

|     | manauskaite and Cenys [2011])                                                                                                           | 30      |

| 4.1 | Overview of the multiprocessor system implemented to serve as                                                                           |         |

|     |                                                                                                                                         | 42      |

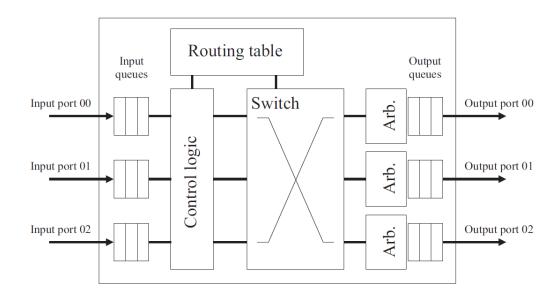

| 4.2 |                                                                                                                                         | 44      |

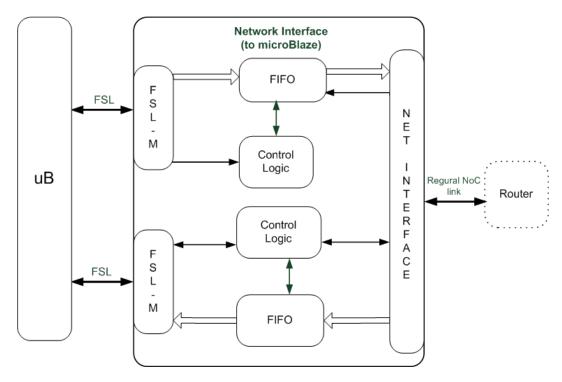

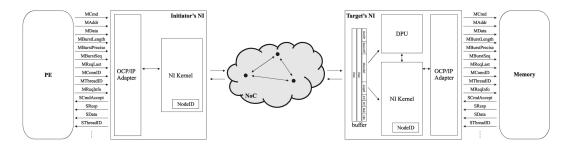

| 4.3 | Internal implementation of the Network Interface to the MicroBlaze                                                                      | 46      |

| 4.4 | Control and data words sent by the MicroBlaze to the Network                                                                            |         |

|     | ·                                                                                                                                       | 46      |

xvi Figures

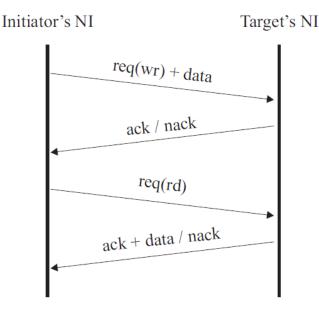

| 4.5  | Transaction based protocol implemented between Initiators and Targets                                                                | 47 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

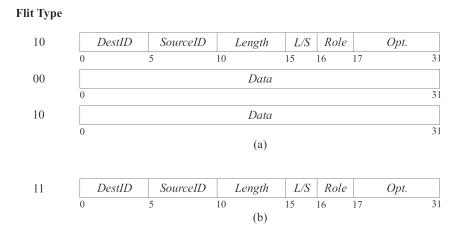

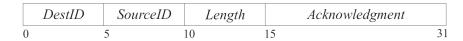

| 4.6  | Structure of the packet used within the NoC                                                                                          | 48 |

| 4.7  | Structure of the acknowledgment packets                                                                                              | 48 |

| 4.8  | Buffer overflow attack scenario                                                                                                      | 50 |

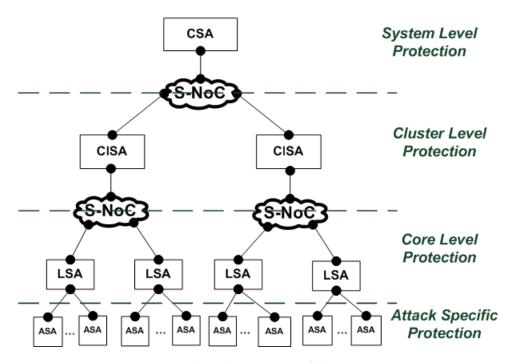

| 5.1  | Hierarchical structure of the security system                                                                                        | 57 |

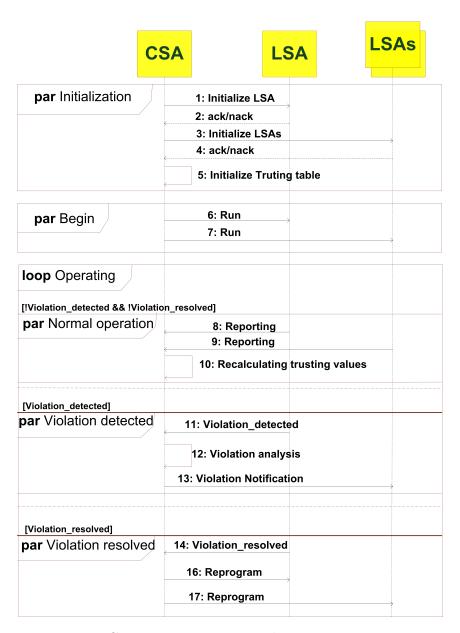

| 5.2  | Communication protocol among security agents                                                                                         | 59 |

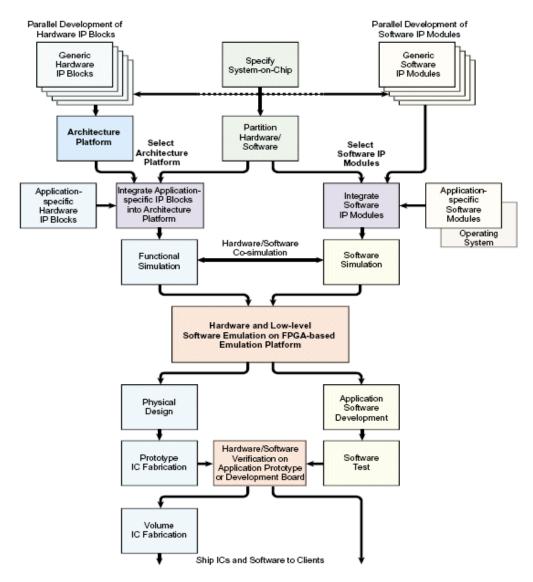

| 6.1  | Standrad SoC hardware-software design flow (taken from Bishop [n.d.])                                                                | 68 |

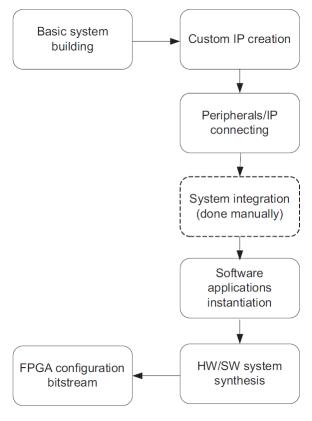

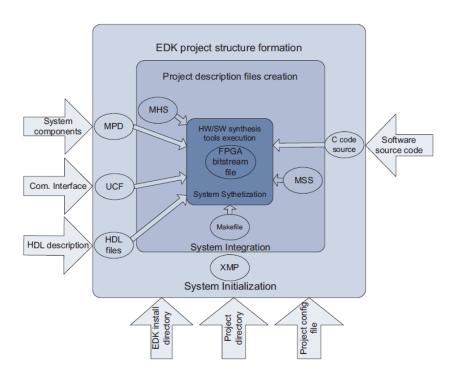

| 6.2  | The Xilinx EDK design flow                                                                                                           | 70 |

| 6.3  | The layered structure of design flow                                                                                                 | 72 |

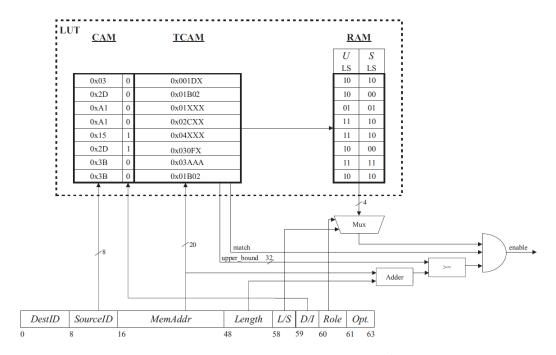

| 6.4  | Data Protection Unit - internal structure                                                                                            | 76 |

| 6.5  | Overview of the whole NoC-based architecture including the Data                                                                      |    |

|      | Protection Unit at target Network Interface                                                                                          | 77 |

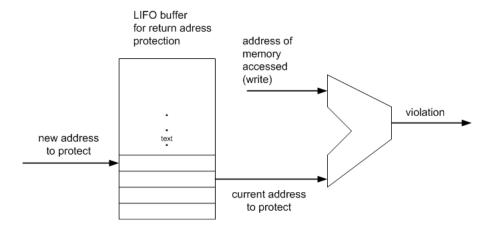

| 6.6  | Basic concept of Attack Specific Agent - Stack Protection Unit                                                                       | 78 |

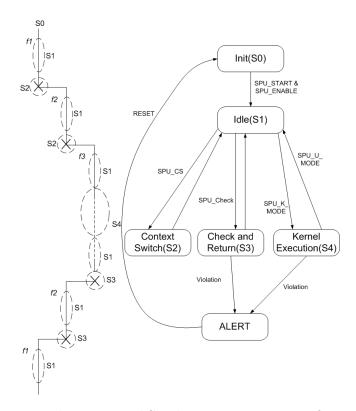

| 6.7  | Functions' nesting and Stack Protection Unit as finite state ma-                                                                     |    |

|      | chine that follows the scenario                                                                                                      | 79 |

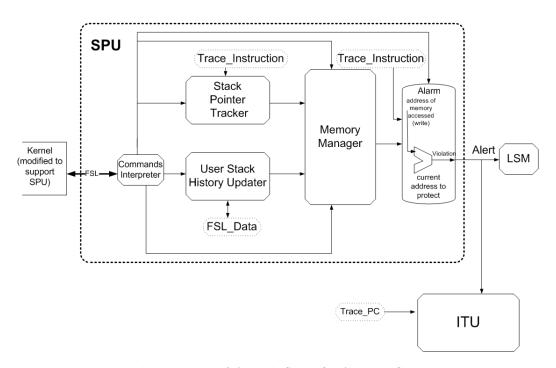

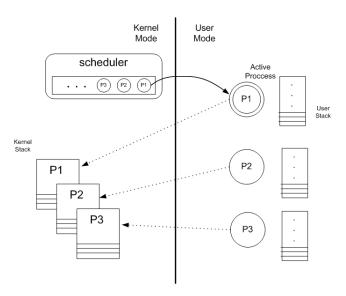

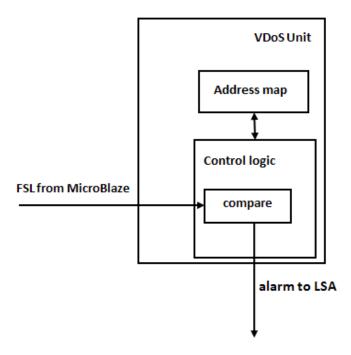

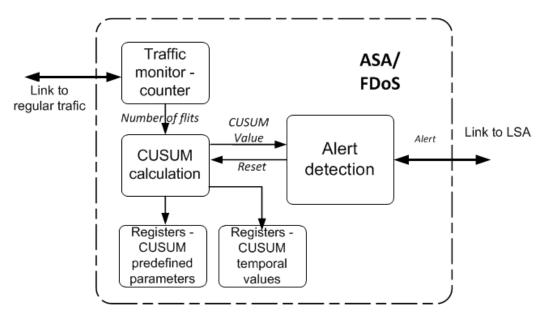

| 6.8  | Internal structure of Attack Specific Agent - Stack Protection Unit                                                                  | 80 |

| 6.9  | Processes and stacks considering Operating System modes                                                                              | 82 |

|      | Architecture of the <i>Vulnerable DoS</i> - Attack Specific Agent                                                                    | 84 |

|      | Architecture of the <i>Flooding DoS</i> - Attack Specific Agent                                                                      | 86 |

| 6.12 | General Local Security Agent architecture (details explained in                                                                      |    |

|      | Figure 6.4.1)                                                                                                                        | 87 |

|      | Instruction Tracing Unit structure                                                                                                   | 90 |

| 6.14 | Enhanced NI to microBlaze with Local Security Agent involving<br>Attack Specific Agent - Stack Protection Unit (security related el- |    |

|      | ements are denoted in red color)                                                                                                     | 92 |

| 6.15 | Enhanced NI to uBlaze with Local Security Agent involving ASA/V-                                                                     |    |

|      | DoS and ASA/FDoS (security related elements are denoted in red                                                                       |    |

|      | color)                                                                                                                               | 93 |

| 6.16 | NI to memory with Local Security Agent for involving Attack Specific Agent - Data Protection Unit (security related elements are     |    |

|      | denoted in red color)                                                                                                                | 94 |

| 6.17 | Structure of Central Security Agent                                                                                                  | 95 |

| 7.1  | Internal implementation of the Network Interface to BRAM em-                                                                         |    |

|      | bedding the ASA/DPU                                                                                                                  | 99 |

xvii Figures

| 7.2  | Activity diagram of the NI embedding the DPU: access to memory        |     |

|------|-----------------------------------------------------------------------|-----|

|      | and reconfiguration                                                   | 100 |

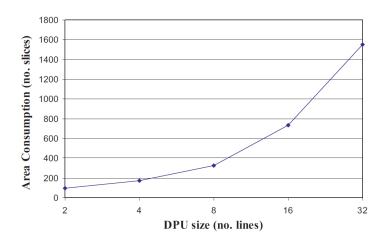

| 7.3  | Area of the DPU for different numbers of entry lines                  | 103 |

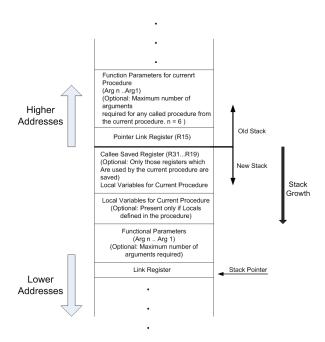

| 7.4  | MicroBlaze stack organization                                         | 104 |

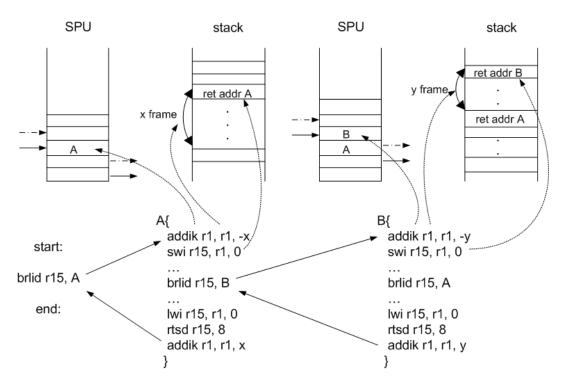

| 7.5  | MicroBlaze and SPU context switch scenario                            | 105 |

| 7.6  | Experimental MPSoC setup used for final system validation             | 108 |

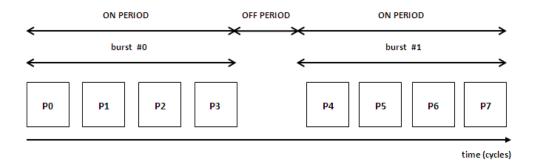

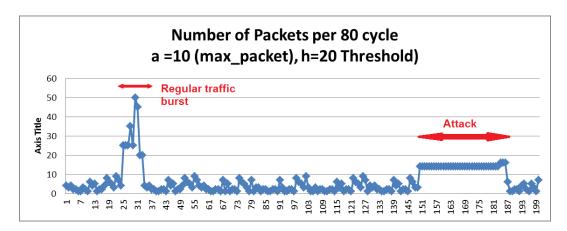

| 7.7  | On-Off Traffic Model of the test application                          | 110 |

| 7.8  | Impact of step parameter 'a' on attack detection latency              | 112 |

| 7.9  | Detection latency vs. false alerts trade-off - optimal value of a     |     |

|      | parameter may be 10 or 11 for the specific case                       | 113 |

| 7.10 | Input traffic sent to the NoC by the monitored core (the attack       |     |

|      | starts around slot 150)                                               | 115 |

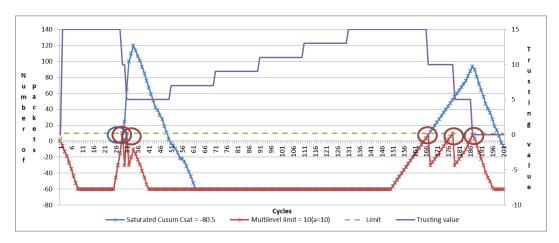

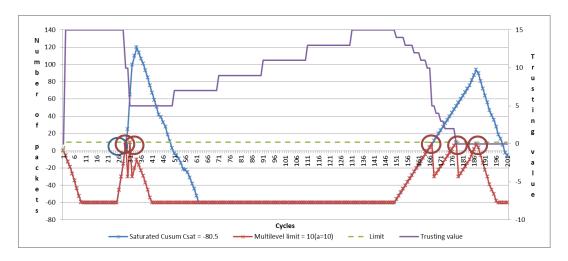

| 7.11 | Measured CUSUM values - for the basic and saturative algorithms       | 116 |

| 7.12 | Core trusting value changing for basic and enhanced CUSUM al-         |     |

|      | gorithm                                                               | 116 |

| 7.13 | Total trusting value (including CUSUM and DPU alerts and posi-        |     |

|      | tive feed-backing)                                                    | 117 |

| 7.14 | Input traffic pattern                                                 | 119 |

| 7.15 | Real alerts detection efficiency                                      | 119 |

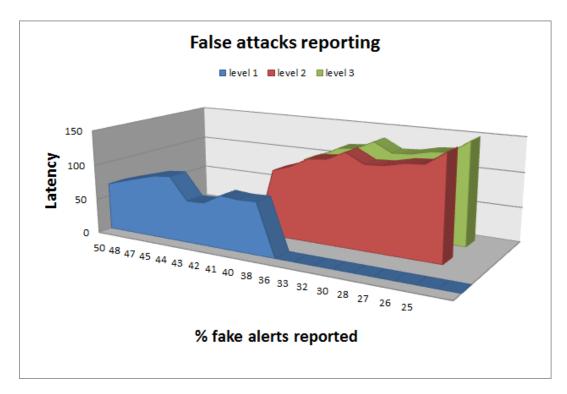

|      | False alerts detection - as a consequence of regular traffic bursts . | 120 |

| 0.1  | A1 1                                                                  |     |

| 8.1  | Absolute increase of area consumption with addition of core frame-    |     |

|      | work (i.e. LSA+CSA+SNoC) and extra ASAs with respect to orig-         | 100 |

| 0.0  | inal design                                                           | 128 |

| 8.2  | Absolute increase of power consumption with addition of an extra      | 100 |

|      | ASA with respect to original 'clean' design                           | 130 |

xviii Figures

# Tables

| 7.1 | FPGA resources consumption - System composed of two Microb-         |     |

|-----|---------------------------------------------------------------------|-----|

|     | lazes, shared BRAM and NoC (implemented on a Xilinx Virtex II       |     |

|     | board)                                                              | 101 |

| 7.2 | Area consumption (occupied slices) as relative ratio between com-   |     |

|     | ponents                                                             | 102 |

| 7.3 | Area consumption (in number of occupied slices) per component       |     |

|     | - implemented on Xilinx Virtex-II board                             | 106 |

| 7.4 | Resource Utilization in terms of area (implementation on Xilinx     |     |

|     | Virtex-V FPGA)                                                      | 114 |

| 8.1 | Resource utilization of the components of the system for the Xilinx |     |

| 0.1 | Virtex V FPGA on ML510 board                                        | 126 |

| 8.2 | Power consumption of the design with subsequent addition of an      |     |

|     | ASA measured for the Xilinx Virtex V FPGA                           | 130 |

xx Tables

## Chapter 1

#### Introduction and Motivation

In this Chapter we provide an introduction and motivation for the submitted work. First of all, basic concepts concerning Multiprocessor Systems-on-Chip (MPSoCs) and Networks-on-Chips - of fundamental importance for the present thesis - are presented. An overview of NoC-based MPSoCs is given afterwards, introducing at the same time the security challenges such systems face. The specific problem addressed and the desired goals are briefly exposed. Finally, the outline of the original contributions of the proposed solutions is given and their relevance is discussed.

The use of MultiProcessor Systems-on-Chips (MPSoCs) is constantly increasing, with reference to both number of fields where they are utilized in and diversity of applications involved. In particular these systems are widely used for signal processing, packet processing in computer networks, multimedia processing, in cell-phone processors (see, e.g. Wolf et al. [2008]). All these applications in turn involve networking and Internet enabled access. Such developments are posing many novel design challenges (as stated by Martin [2006]). One of the notable trends in MPSoC design is constituted by shifting towards communication centric design (as shown by D. [2000]; Ogras et al. [2005]; Henkel and Wolf [2004]; Grecu et al. [2004]).

With increased exposure of MPSoCs, we are experiencing an ever growing number of attack techniques: a fact that brings additional challenges for system designers.

Security risks caused by rapid penetration of MPSoCs in all segments of our lives on the one side and increasing concern about the evolution of malicious attack techniques on the other hand have created a global sensitivity to security in MPSoC design, as well as an interest in finding adequate protection solutions. Moreover, modern complex and sensitive embedded systems involve increasing

numbers of actors and technologies, a fact which requires modular integration of reliable and secure components. Therefore, there is a necessity to devise holistic approaches to security protection strategies. Such strategies would consider different aspects of system design and a variety of attack scenarios in order not only to protect from 'infection' but also to prevent the propagation of attacks through the system. Aligned with such approach we consider a comprehensive protection strategy which provides solid ground for system defense combining both distributed (i.e. the protection of individual cores) and centralized protection approaches (i.e. system level). The proposed security framework is built as a flexible, modular and scalable structure that incorporates different attack specific protection methods and integrates them in a system-wide hierarchical security system.

In the development of the solution we rely on Network-on-Chip communication architecture extending its components to host and support security enhancements.

#### 1.1 Multi-Processor Systems-on-Chip

The steady technological evolution has enabled the adoption of many advanced architectural concepts and the integration of increasing numbers of cores onto a single chip. Considering in particular processing architectures, the development of the System-on-Chip (SoC) concept supports evolution towards multiprocessor-based and reconfigurable design. In turn, this has led to the Multi-Processor Systems-on-Chips (MPSoCs) solutions which group multiple standard CPUs together with customized IPs, DSPs, input-output interfaces and other hardware subsystems in the same chip. In particular, when embedded systems are considered, an MPSoC is not simply a traditional multiprocessor shrunk to a single chip but rather an innovative solution that has been designed to fulfill the unique requirements of embedded applications (see e.g. Wolf et al. [2008]).

Such scenario in turn requires innovative system design techniques, new programming models and many other novel strategies to support rapid development of many-core platforms and of the applications using them (Wolf et al. [2008]; Martin [2006]). At the same time, the increasing complexity that will be required in next generation's SoCs pushes designers to research new on-chip communication solutions due to limitations (in particular low scalability) of existing bus-based interconnecting means (Benini and De Micheli [2002]; Dally and Brian [2001]).

In summary, researchers have identified as follows the most important issues

regarding efficient MPSoC design (Martin [2006]; Patel et al. [2010]):

- The number and configuration(s) of processors required for the application. How homogeneous should the architecture be, versus how heterogeneous?

- Interprocessor communication choosing the right communication solution, taking into account emerging network on chip approaches

- Concurrency, synchronization, control and programming model(s). In many instances, multiple models will be appropriate

- Memory hierarchy, types, amounts, and access methods, along with the capacity of estimating with acceptable accuracy the required latency

- Power reduction and low energy consumption

- Application partitioning, use of appropriate APIs and communications models, and associated design space exploration

- Design and platform scalability

- Security and reliability of architectures especially due to the increased role they play in modern society and to the growing attention payed by the criminal community to these systems Diguet et al. [2007]; Ahmad and Arslan [2005]; Wolf et al. [2008]; Zhou and Wu. T. snd Wu [2009]

In our work we focus on security aspects with special regard to Networkon-Chip architectures (refer to Section 2.1) as communication medium among MPSoC components. Our approach to protection of these systems relies mostly on three basic ideas:

- Extension of NoC components to support security related services

- Adoption of multi-agent system strategies when designing the protecting architecture

- Integration of different security aspects into one system level protection mechanism

These methods represent an original contribution of this work to MPSoC security. The validation of the proposed solutions is performed via design of demonstrators making use of FPGA technology.

# 1.2 Network-on-Chip based Multi-Processor Systems-on-Chip

As previously stated, increased chip density has created many new design challenges. Considering in particular on-chip communications, global wires, connecting many different functional units, are likely to have propagation delays exceeding the clock period, moreover, the arbitration process among growing numbers of units on the bus becomes very complex. The Network-on-Chips (NoCs) concept (Benini and De Micheli [2002]; Dally and Brian [2001]) represents a promising solution to these issues. NoC has been proven as a solid interconnection strategy that brings reliable, efficient, scalable and fast intercore communication, capable of to providing a satisfactory answer to a number of issues in MPSoC design, including scalability, arbitration problems, power management etc. Moreover, scalable and modular NoC design facilitates porting at system level a number of advanced concepts not exclusively related to communications such as system monitoring, security, fault tolerance etc.

We focus on MPSoCs architectures based on the Network-on-Chip (NoC) paradigm, identifying their peculiar challenges insofar as security is concerned and developing solutions as well as a complete approach to meet such challenges. NoC-based MPSoCs are basically composed of three kinds of cores:

- Processing cores (e.g. microprocessors, DSPs etc.)

- Data storage elements (i.e. shared memories)

- Communication elements (Routers and Network Interfaces)

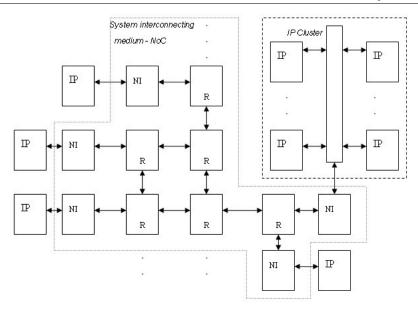

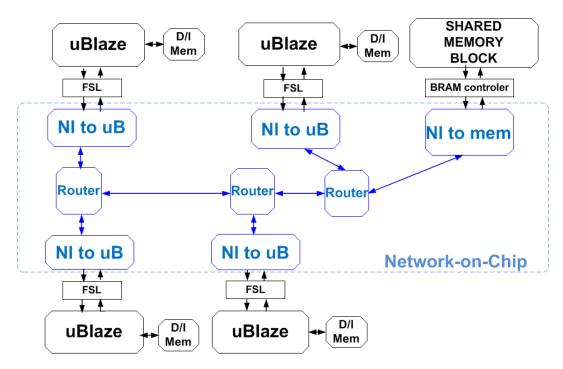

The work presented here takes such composition of the system as its reference architectural template. The basic system structure is presented in Figure 1.1.

#### 1.3 Security vulnerabilities and protection strategies for NoC based Multi-Processor Systems-on-Chip

Increasing complexity of MPSoCs and increased networking possibilities make systems more vulnerable to different kinds of attacks (Diguet et al. [2007]; Ahmad and Arslan [2005]; Wolf et al. [2008]; Zhou and Wu. T. snd Wu [2009]). This problem acquires particular relevance as MPSoCs find increasing application in critical systems (even mission-critical or safety-critical ones); this in turn

Figure 1.1. Network-on-Chip based Multi-Processor Systems-on-Chip - general structure

makes security aspects more important. On the other hand, we experience rapid growth of attack techniques and increasing flexibility of malicious software.

As a consequence, there is increased need of security-aware design solutions, in particular in the design of reconfigurable SoCs that by their nature are even more vulnerable (attacks can target not only the operation but even the very configuration of the device). However, even though research on NoC-related topics has been an emerging area of interest, security issues in this field have been often shadowed by other topics and have not been explored to the same extent, being only recently addressed by the research community (Diguet et al. [2007]; Fiorin et al. [2008]).

The presence on the chip of different kinds of data-processing cores as well as of various storage elements constitutes a common ground for a number of attacks. A variety of attack models have been detected so far as shown in Section 4.2 and accordingly a number of techniques have been devised to fight them as presented in Chapter 2. However, most of these protection strategies consider only specific types of attacks or specific architectures - a fact that represents a major obstacle for their wide adoption. Therefore, a need for comprehensive approach to security design emerges: the aim of this work is to develop such an approach.

#### 1.4 Problem, objectives and contributions of the thesis

Integrating and coordinating all security-related aspects in an MPSoC requires flexible (i.e. modular and scalable) solutions to be devised. Rather than targeting ad-hoc solutions for specific system architectures, an approach valid for the widest spectrum of NoC-based architectures is needed. Developing of an efficient system-level protection mechanism for MPSoCs is the main challenge we are tackling. For this reason we propose a security framework based on a hierarchical multi-agent structure, capable of being specialized for a large variety of architectures and of attacks.

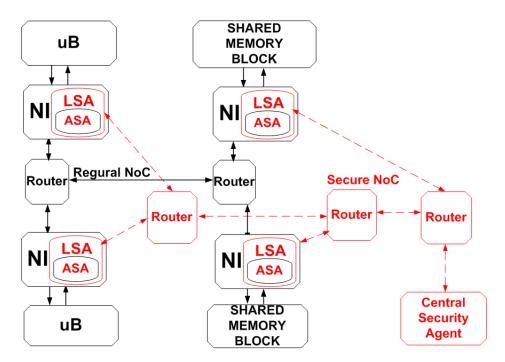

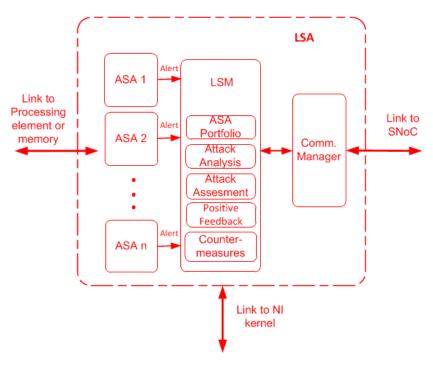

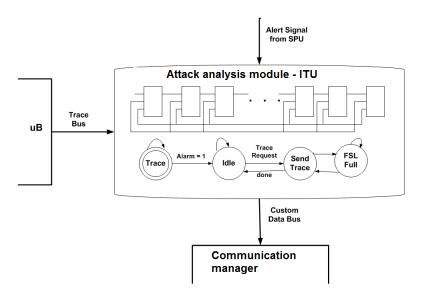

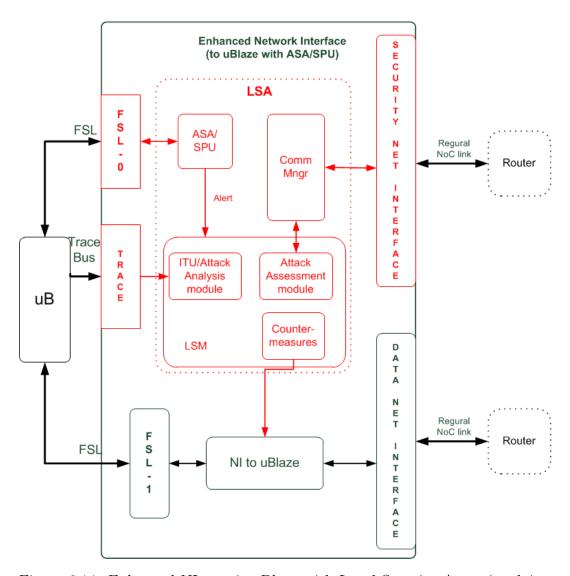

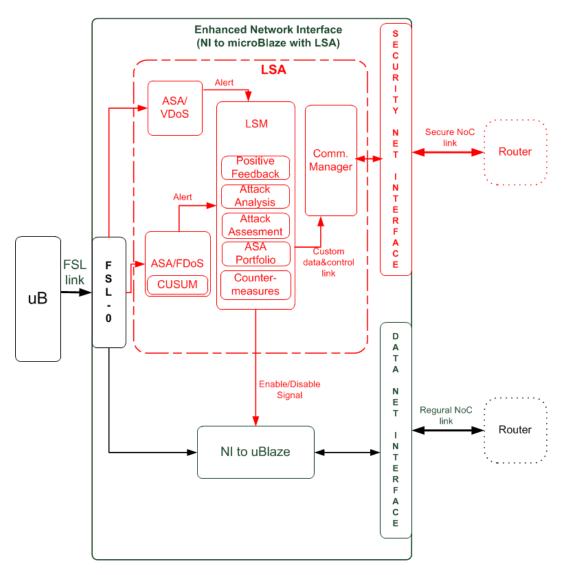

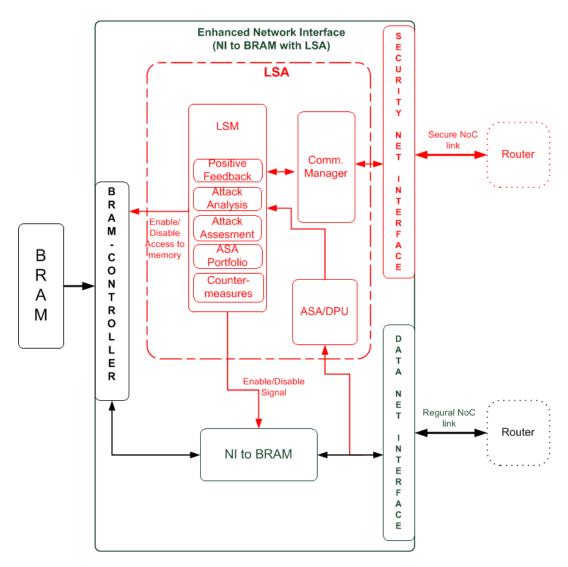

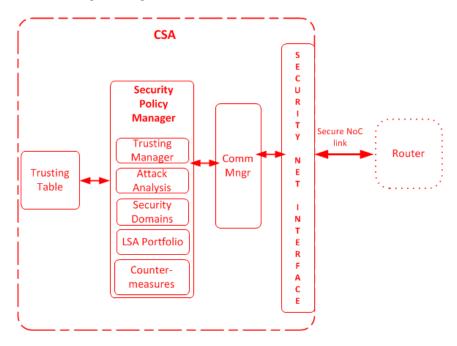

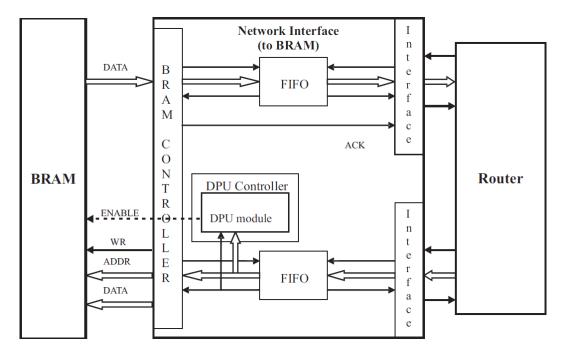

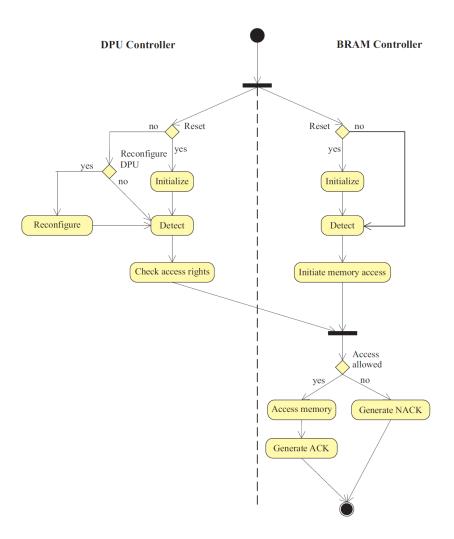

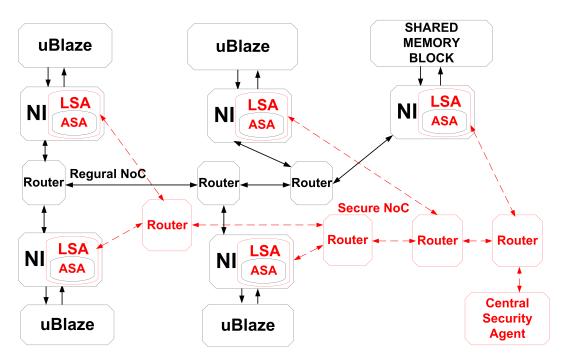

The proposed solution relies on the implementation of a multi-agent system, based on a hierarchy of agents: at the lowest level, there are - *Local Security Agents* (LSAs) employed locally on the individual cores and integrated in a hierarchical system by means of *Cluster Security Agents*, that are in turn coordinated by a *Central Security Agent* - CSA. The system architecture is shown in Figure 1.2. It can be noted from this figure that LSAs represent logical encapsulations of locally deployed protection mechanisms (that actually are Attack Specific Agents - ASAs). The solution is highly modular, so that ASAs can be individually devised and optimized without requiring an overall re-design.

Figure 1.2. Architecture of the fully secured system (security related elements are denoted in red)

Given the general framework proposed, in our work we then focus on protection from software-based attacks to processing and memory cores as these emerge to be the most common type of problems when security of embedded systems - and especially of networked ones (Internet-enabled) - is considered. In order to prove the viability of the solution one of the most common types of attacks 'code-injection'- a type of attack that actually exercises in an very extended way our proposed solution is emulated. It is actually a technique to redirect execution of a trusted application to the malicious code by taking over the instructions' control flow. This is usually done by exploiting buffer overflows and smashing parts of the stack in which the correct return address has been saved. Another major security threat that is considered in this work is related to the Denial-of-Service attack type. This attack is widely present in computer networks and it mostly exploits limitations of communication channels throughputs which are prone to congestion in case of massive data transmission (this is usually done by initiating different kinds of irregular traffic). To validate our approach with real-world experiments we address here such type of problems in an NoC-based MPSoC system implemented in FPGA. As a demonstrator for the attack scenarios and the proposed protection concepts we use a system based on MicroBlaze CPUs (available on the Xilinx FPGAs) running uClinux embedded operating system. Considering individual characteristics of each type of core, autonomous protection solutions able to secure single core from targeted attack should be designed. Accordingly, in the scope of this work and bearing in mind the system composition exposed in the Section 4.1.1 we propose appropriate protection techniques, developed and integrated in the wider security framework in form of *Attack Specific Agents*. More specifically:

- MemPROT is based on Data Protection Unit (DPU), a firewall-like structure

that filters unauthorized memory access requests. DPU is employed in the

Network Interface attached to a shared memory block (Fiorin, Palermo,

Lukovic and Silvano [2007]; Fiorin et al. [2008]). The solution which

represent one type of Attack Specific Agent (ASA) is explained in details

in Section 6.3.1

- *InjectPROT* is a set of combined SW/HW units replicating functions' return addresses and providing protection from buffer-overflow code-injection types of attacks. Stack Protection Unit (SPU), as a central part of Inject-PROT, is employed directly at each processing core (Lukovic et al. [2010]; Lukovic and Christianos [2010a]) and represents another ASA, explained in details in Section 6.3.2.

- *DoSPROT* is a Denial-of-Service detecting system that is embedded in the security framework based on traffic monitoring units (deployed in form of ASAs in each core) and detecting algorithms employed in the CSA. The solution has been implemented in a form of ASA, the detailed description is given in Section 6.3.3.

- A dedicated secure NoC (SNoC) (Lukovic and Christianos [2010b]) is implemented in parallel with the 'nominal' (regular) one, connecting security elements embedded in NIs with a central security manager. It is implemented as a simplified version of the regular NoC and it is probably more efficient than a virtual channel based structure, at least for systems with a limited number of cores as suggested by Yoon et al. [2010]

The general system representation containing these components is given in Figure 1.2, that shows also the place of all aforementioned components inside the architecture. Based on such core-level protection structure we further build, in bottom-up fashion, a system-level security architecture which in fact relies on coordination of all security related actions by CSA.

In order to prove the feasibility of the concept we have adapted and synchronized with each other a number of different Attack Specific Agents encapsulated in Local Security Agents (one per each core). Protections against code injection type of attacks, unauthorized memory access and Denial-of-Service are combined in the prototype being integrated in appropriate LSAs. Both, LSA for MicroBlaze processor and LSA for shared memory cores are designed and implemented. Moreover, all the security related elements of the system are interconnected by means of a dedicated secure NoC. Monitoring and coordination of all agents is done through defined policies implemented by CSA. The experimental evaluation of the model is provided in described in details in Chapter 7.

In summary, the main contribution of the work lays in the novel approach to system level security, based on multi-agent technology, which integrates in hierarchical fashion, a variety of protection strategies establishing in such a way as to provide a system wide, comprehensive security framework.

The rest of the document is organized as follows: Chapter 2, provides an overview of ongoing research on security protection techniques in MPSoCs and NoCs. In Chapter 3, fundamental problems and challenges tackled are exposed; while Chapter 4 describes reference architecture and attack models, Chapter 5 shows the proposed conceptual solution. Chapter 6 provides detailed information on the solution implementation, and Chapter 7 shows synthesis and testing

results. Chapter 8 discusses the costs introduces by the proposed solution and provides comparison with other relevant related solutions. Finally, Chapter 9 presents conclusions and future work of the present thesis.

## Chapter 2

## Background and Related Work

Over the last decades the number of transistors integrated on a chip has been steadily increasing more or less according to Moore's Law. Intel 4004 introduced in 1971 had 2300 transistors and was running at 106KHz, while the first Intel Pentium introduced in 1992 had 3.1 million transistors running at 66MHz. The transistor count for modern processors is in a order of few billion transistors and operating frequencies can reach up to 5GHz. Still, it might be worth noting that while transistor count has kept increasing following forecasts made in the '90s, since the early 2000's frequency increase has slowed down, due to excessive power consumption problems, heating and increased impact of wire-delay on the communication. The exponentially increasing number of transistors has since then been invested in ever larger on-chip caches, but even there we have reached the point of saturation (Duato [2008]; De Bosschere et al. [2007]). Such trends urged for a massive paradigm shift towards multi-core architectures. Improvements in performance are now achieved by putting multiple cores on a single chip, effectively integrating a complete multiprocessor on one chip. Since the total performance of a multi-core is improved without increasing the clock frequency, multi-cores offer a better performance/Watt ratio than a single core solution with similar performance (De Bosschere et al. [2007]).

The many-core paradigm poses new challenges for researchers, including such aspects as (according to De Bosschere et al. [2007]):

- new design complexity issue (as special-purpose computing nodes can have a significant impact on the memory hierarchy of the system)

- on-chip communication (that requires more scalability and flexibility)

- low power design strategies

- security in different aspects

- new programming paradigms (programming environments supporting heterogeneous multi-core systems enabling the user to manually express concurrency as

Today, heterogeneous processing units such as dedicated units as DSPs, different kinds of accelerators or application specific processors might be integrated in the same system. This introduces problems of application mapping and optimizations. Architectures like this require tools for fast and efficient prototyping and testing of the design. Moreover, design trends in MPSoCs design go in the direction of blurring the traditional distinction between SW and HW elements of a system Vahid [2003]; modern system design is actually HW/SW co-design, so that designer decides based on cost-performance analysis on how specific functionality can be realized.

In the scope of this work we focus our attention on Network-on-Chip interconnection solutions and on security issues relevant for MPSoC design.

#### 2.1 On-chip interconnecting strategies - Networks-on-Chips

As the number of cores per chip is growing, followed by increased cores heterogeneity, many challenges for the architecture designer derive from the interconnection solutions. Chip size will scale up slightly while gate delays decrease compared to wiring delays. A simple computation shows that delays on wires that span the chip could extend longer than the clock period ((Sylvester and Keutzer [2000]; Ho et al. [2001])) which is already the case, e.g., for Intel multicore chips (buses are pipelined, for that reason). Synchronization of future chips with a single clock source and negligible skew will be extremely difficult; energy and device reliability concerns will impose small logic swings and power supplies. Electrical noise due to crosstalk, electromagnetic interference, and radiation-induced charge injection will likely produce data errors. Thus, transmitting digital values on global wires will be inherently unreliable (Benini and De Micheli [2002]).

The Network-on-Chip (NoC) concept (Benini and De Micheli [2002]; Dally and Brian [2001]) has emerged as a promising solution for the communication needs initiated by aforementioned trends. NoCs scale well, eliminate the

need for arbitration when accessing the communication medium, provide well-defined interfaces for the cores to be attached and, due to their flexibility, provide fertile soil for deployment of many auxiliary services. Researchers have proposed enhancements of NoC architectures for supporting system monitoring (Ciordas et al. [2006]; Fiorin et al. [2009]) as well as security services (Diguet et al. [2007]; Fiorin et al. [2008]).

In general the trend of paradigm shift from bus-centric toward core-centric interconnection design has been well documented and advocated by the research community (D. [2000]; Grecu et al. [2004]). The main differences between the two can be summarized as follows:

- Bus-Centric Protocol Interface

- Cores are forced to interface to the particular bus facing all the limitation such bus may bring

- Interfaces to a different buses may cause incompatibilities

- Core-Centric Protocol Interface

- Facilitates unrestricted delivery of all core signals

- Enables unconstrained interface bridge to any interconnect

- Number of gates in interface is typically lower than for bus interface

One of the most widespread open core protocols is OCP (*Open Core Protocol* [2000]), that is aimed at defining a common standard for intellectual property (IP) core interfaces, or sockets, capable of facilitating 'plug and play' SoC design. Its foundation is strongly supported by leading industrial and academic institutions targeting at facilitating design of complex SoC so as to make it more efficient for wider audiences. Moreover, OCP defines a set of standard signals for test and debugging. A number of NoCs implement the OCP communication interface (Bjerregaard et al. [2005]; Dall'Osso et al. [2005]; Fiorin et al. [2008]).

Fundamental NoC advantages over traditional bus solutions are considered to be (according to Benini and De Micheli [2002]; Bjerregaard and Mahadevan [2006]):

• Only point-to-point wires are used in NoCs (as compared to buses where each attached unit adds parasitic capacitance)

- NoCs are layered structures that separate and encapsulate different issues at different levels (e.g. transaction and transport) leaving more space to deal with problems like timing and Quality of Service.

- Bus arbiter delays grow with the number of masters while in NoCs routing decisions are distributed

- While bus bandwidth is shared by all units attached, in the case of NoCs aggregated bandwidth scales with network size

Surely there are also NoC shortcomings, such as (according to Guerrier and Greiner [2000]):

- Internal network congestion may introduce latencies

- Network introduces significant area overhead

- Cores need wrappers to adapt to NoC

- The concept is novel and requires acquisition of new skills by the designer

In general Network-on-Chip architectures are characterized by (Benini and De Micheli [2002]; Benini and Bertozzi [2005]): Network topology; Switching and Routing strategies; Flow control mechanism.

*Network topology* (Pande et al. [2005]; Bartic et al. [2005]) denotes the physical interconnection structure of the network graph (e.g. mesh, torus, binary tree or irregular, see e.g. DeMicheli and Benini [2006]). It may be: direct (each node is connected to every switch) - or indirect - nodes are connected to specific subsets of switches.

Routing represents determination of an optimal source-destination path while switching describes a way the data is actually transferred through the switching elements (Hu and Marculescu [2004b]; Bjerregaard and Mahadevan [2006]; Palesi et al. [2006]). Several different aspect can be considered for these strategies (according to Bjerregaard and Mahadevan [2006] and DeMicheli and Benini [2006]):

• *Circuit vs packet switching*. In the first strategy, the link from source to destination is established and reserved until the transport of data is complete. Packet switched traffic, on the other hand, is performed on a per-hop basis, each packet contains routing information as well as data.

- Connection-oriented vs connectionless. Connection-oriented mechanisms involve a dedicated (logical) connection path established prior to data transport. The connection is then terminated upon completion of communication. In connectionless mechanisms, the communication occurs in a dynamic manner with no prior arrangement between the sender and the receiver. Thus circuit switched communication is always connection-oriented, whereas packet switched communication may be either connection-oriented or connectionless.

- Deterministic vs adaptive routing. In a deterministic (static) routing strategy, the traversal path is determined by its source and destination alone. Adaptive schemes involve dynamic arbitration mechanisms which results in more complex design.

- Central vs distributed control. In centralized control mechanisms, routing decisions are made globally. In distributed control, the routing decisions are made locally.

As for packet switching several forwarding strategies which show how the packets are passed from one to another router are present. Three main strategies are defined (Bjerregaard and Mahadevan [2006]):

- *Store-and-forward* is a packet switched protocol in which the node stores the complete packet and forwards it based on the information within its header. Thus the packet may stall if the router in the forwarding path does not have sufficient buffer space.

- Wormhole routing combines packet switching with the data streaming quality of circuit switching to minimize packet latency. The node looks at the header of the packet to determine its next hop and immediately forwards it. The subsequent flits are forwarded as they arrive. This causes the packet to move in 'worm' fashion through the network, hence the name.

- *Virtual cut-through* routing has a forwarding mechanism similar to that of wormhole routing. But before forwarding the first flit of the packet, the node waits for a guarantee that the next node in the path will accept the entire packet. Thus if the packet stalls, it aggregates in the current node without blocking any links.

There are variety of popular routing algorithms with different properties (e.g. table-based routing, source routing, node-table routing, 'hot potato' etc.).

Flow Control Mechanism is defined as the mechanism that determines the packet movement along the network path by Dally and Brian [2001]. Flow control addresses the issue of ensuring correct operation of the network. It also encompass issues on optimal utilization of network resources optimally Bjerregaard and Mahadevan [2006]. A concept of Virtual Channels VCs implements flow control in a particular way, in that it relies on the sharing of a physical channel by several logically separate channels with individual and independent buffer queues.

A number of NoC related topics have been raised in recent years and have attracted remarkable attention from both academic and industrial community. In essence, main research topics includes:

- Architecture and design flow (Kumar et al. [2002]; Benini and Bertozzi [2005]; Goossens, Dielissen and Radulescu [2005])

- Programming models (e.g. message passing vs. shared memory) Bjerregaard and Mahadevan [2006]; Benini and De Micheli [2006]; Goossens, Dielissen and Radulescu [2005]

- Low power design (Silvano et al. [2011]; Lee et al. [2006]; Shacham et al. [2007])

- Fault-tolerance (Pullini et al. [2005]; Tamhankar et al. [1297–1310]; Derin et al. [2011])

- Cache coherence (Petrot et al. [2006]; Bolotin et al. [2007]; Kurian et al. [2010]; Seiculescu, Volos, Khosro, Falsafi and De Micheli [2011])

- Buffer sizing and queue management (Marculescu et al. [2005]; Hu and Marculescu [2004a])

- QoS and Security (Guz et al. [2006]; Harmanci et al. [2005]; Faruque et al. [2006]; Rijpkema et al. [2003])

The most recent NoCs research trends go in the direction of design of photonic Network-on-Chips (Shacham et al. [2007]; Gu et al. [2009]; Kurian et al. [2010]) and also introducing 3D design (Pavlidis and Friedman [2007]; Kim et al. [2007]; Feero and Pande [2009]; Seiculescu, Murali, Benini and De Micheli [2011]). Nevertheless, the solutions we propose are independent of specific interconnect technology so that their validity will keep.

In the following we will provide an outlook on security with special regard on the most common attacks and on-chip protection solutions.

# 2.2 Security overview - basic terms and taxonomies

Security is, broadly speaking, considered to be a composite of the attributes of confidentiality, integrity, and availability, requiring the concurrent existence of 1) availability for authorized actions only, 2) confidentiality, and 3) data integrity (according to Avizienis et al. [2004]).

The increasing pervasiveness of computer science and spreading of computers through practically all segments of modern life were followed by steady increase of criminal activities directed to data theft of proprietary information, financial frauds, virus attacks, sabotage etc. The dimensions of computer crime have been investigated in time span of thirteen years involving hundreds of computer security practitioners and reported by Computer Security Institute (CSI) in (Richardson [2003]). The most expensive computer security incidents were those involving financial fraud with an average reported cost of close to \$500,000. The second-most expensive, on average, was dealing with 'bot' computers within the organization's network, reported to cost an average of nearly \$350,000 per respondent. The overall average annual loss reported was just under \$300,000. Virus incidents occurred most frequently, being reported at almost half (49 percent) of the respondents' organizations.

Remarkable research efforts, mostly done in general purpose computing and communications, have resulted in robust protection solutions involving sophisticated cryptographic algorithms, communication protocols, anti-virus programs etc. Security in MPSoCs, that is the focus of this work, represents a fairly specific case, and because of that it has been separately highlighted and detailed in Section 2.3. Prior to going into the details of security in this particular field we will expose basic definitions and later in Section 2.2.1 security taxonomies.

We briefly list here the definitions of key terms regarding security (according to Howard and Longstaff [1998]):

- vulnerability represents a weakness in a system allowing unauthorized action

- tool a means of exploiting a computer or network vulnerability

- *event* is an action directed at a target which is intended to result in change of state (status) of the target

- attack represents a series of steps taken by an attacker to achieve an unauthorized result

- *incident* denotes a group of attacks that can be distinguished from other attacks because of the distinctiveness of the attacker, attack, objectives, sites and timing

- *unauthorized result* an unauthorized consequence of an event (e.g. disclosure if information, corruption of information, denial of service, recourses theft and so forth)

These terms represent basic 'building blocks' of the security theory and taxonomies shown in Section 2.2.1.

# 2.2.1 Security taxonomies

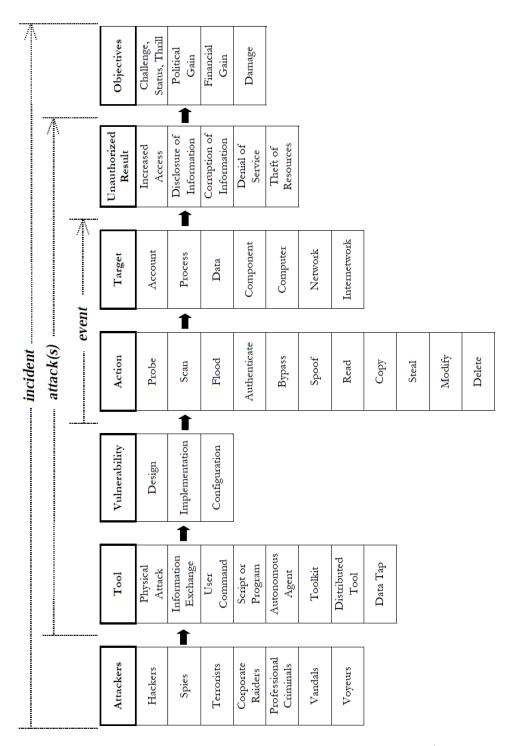

A **taxonomy** is a classification scheme (a structure) that partitions a body of knowledge and defines the relationship of the pieces (Howard and Longstaff [1998]). Security related taxonomies are commonly organized as attacks' and countermeasures' ones (Ramanauskaite and Cenys [2011]; Igure and Williams [2008]). Still, there are several ways to derive a taxonomy as for instance *action-based* security taxonomy presented in (Stallings [1995]). A more comprehensive *incident* taxonomy is developed by (Howard and Longstaff [1998]). It correlates all the actors, their interactions, actions and objectives as presented in Figure 2.1.

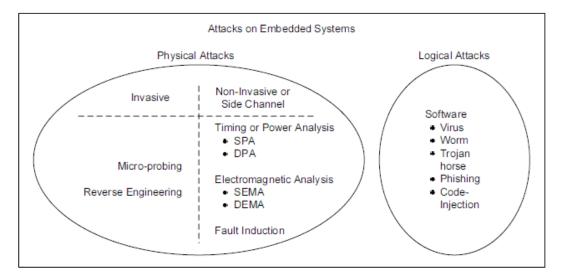

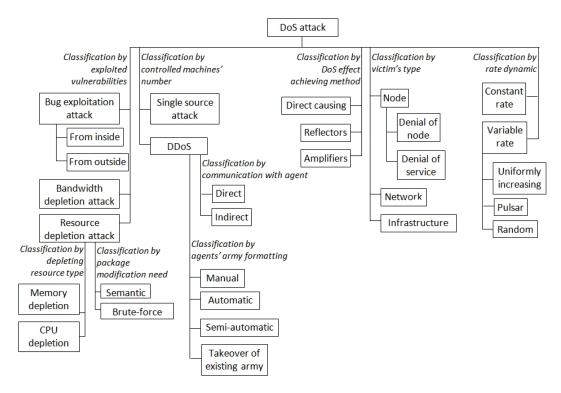

General overview of computer attack specification is given in (Paulauskas and Garsva [2006]). The taxonomy of the attacks on embedded systems is presented in (Ravi et al. [2004]). In general it groups all the attacks in two disjoint groups namely, physical and logical attacks (refer to Figure 2.2).

In this work we focus on software attacks and we do not consider any kind of physical or side-channel attacks. In the general case, software attacks address existing (i.e. installed) software applications in the targeted system. They mostly aim at redirecting regular application's control flow to inserted malicious code by means of 'code injection' or similar techniques. Usually these attacks are fought off by diverse software countermeasures. Unfortunately, this approach is restricted to known attack scenarios and it cannot protect from an unknown threat that avoids the existing protection.

In this work we consider, without diminishing the general validity, a case study targeted on the most usual software attacks such as unauthorized memory access, Code Injection and Denial of Service (as they are the most widespread according to Patel et al. [2010] and the most expensive as stated in Richardson [2003]).

Figure 2.1. Computer and Network incident taxonomy by (Howard and Longstaff [1998])

Figure 2.2. Taxonomy of security attacks on embedded systems according to (Ravi et al. [2004]; Hardware-software design methods for security and reliability of MPSoCs [2009])

# 2.3 Security aspects and on-chip systems

Protection against malicious attacks is considered at different levels and from various points of view. Although security has been so far often neglected by embedded system designers, it is in fact, a new dimension that designers should consider in the design process, along with other metrics such as area cost, performance, and power. The challenges unique to embedded systems require new approaches to security covering all aspects of embedded system design from architecture to implementation (Ravi et al. [2004]). Many solutions employed in general purpose computing and communication systems (e.g cryptography strategies, anti-virus programs etc.) introduce relevant communication and computation overhead, which in turn impacts on performance and power consumption in a measure that is not tolerable in systems with limited resources, such as MPSoCs. Hence, custom solutions for protecting such systems by enhancing existing architecture (communication structures) have been proposed by various researchers (Coburn et al. [2005]; Fiorin et al. [2008]; Porquet et al. [2011]). Commercial solutions are present as well. Trusted Platform Module (TPM) (see Trusted Platform Module (TPM) Specifications [2011]) introduces secure generation of cryptographic keys, in addition to a hardware pseudo-random number generator. It is implemented by some Dell BIOS settings. Several other designs appear, such as: Mobile Trusted Modules (MTM) (Ekberg and Kylanpaa [2007]) by Nokia; M-Shield (Srage and Azema [2008]) by Texas Instruments for security on mobile handsets, which are either hardware agnostic (e.g., MTM), or designs that augment the processing core for increased security (Ekberg and Asokan [2010]; Alves and Rudeli [2007]).

ARM has developed the TrustZone system (refer to Alves and Felton [2004]), described in details in Section 2.3.1 of the thesis. In (Schellekens et al. [2008]) authors present a protocol by which an external component containing non-volatile memory, some logic, additional write-once memory for shared keys, and an integrated HMAC primitive can be used to provide external authenticated non-volatile memory (EANVM) sufficient to support the required protection of secure state. A similar solution has been used for Intel Authenticated Memory developed to complement ARM TrustZone (Ekberg and Asokan [2010]); Sonics introduced its' own protection system (*SonicsMX SMART Interconnect Datasheet* [2008]) (also explained in details in Section 2.3.1 of the thesis). It is expected that Intel will experiment with on-chip anti-virus security solutions in light of recent acquisition of McAfee (refer to Greenberg [2011]).

Regarding the protection of MPSoCs against malicious attacks, recently proposed solutions can be mostly classified in two groups, namely:

- 1. Establishment of different *security domains* being defined as applications' execution environments used to confine their operation effects and resources utilization (usually related to the level of the trust or importance that is assigned to certain application). Access to system resources is then allowed/restricted accordingly to the 'trustiness' of the domain to which the application belongs. Considerable numbers of solution based on such approach have been implemented in general purpose computing, but their cost in terms of resources consumption may represent a serious obstacle for wider adoption in MPSoCs. So far, in this sense two different approaches have been adopted in the case of embedded systems:

- Implementation of *virtual security domains* (Inoue et al. [2005]; Hiroaki et al. [2008]). Dedicated execution environments are established for execution of untrusted applications in a way that separates them from the system itself (Gong and Ellison [2003]). This approach is usually very costly in terms of resources utilization and performance degradation.

- Implementation of specific structures separately dedicated to different application execution environments. One of such approaches consists in introduction of different *compartments* with dedicated identifiers and accordingly assigned privileges. For instance, the NoC-MPU

(Memory Protection Unit by Porquet et al. [2009]) aims at defining a set of access rights on various address regions for different compartments at platform level.

2. Monitoring of application execution and validation of behavior correctness (Patel and Parameswaran [2008]; Arora et al. [2005]; Patel et al. [2010]). The method relies on defining 'permissible behavior' by identifying suitable or expected program properties in run-time execution. The application code is instrumented by inserting special instructions so that control flow can be monitored in desired 'resolution'. An additional processing core is usually employed as system monitor and verification unit. The drawbacks of this strategy are in problems with code insertion which imposes additional design efforts and performance degradation. Moreover, 'permissible behavior' is usually fairly difficult to be precisely defined and verified.

Our work can be roughly classified in the second group, even thought it does not fully implements system monitoring and on the other hand it still implements some aspects of security domains approach. A portion of the proposed security framework (see for instance MemPROT described in Section 6.3.1) relies on a firewall-like protection mechanism, that filters access to the shared memory according to assigned rights following a philosophy not far from the security domains concept (actually different privileges establishment and verification of the access rights prevent access to resources in a similar fashion as security domains do). In that sense this particular solution can be classified in the first class of protection strategies listed above. Still, the proposed work differs from the aforementioned solutions in the general approach to system security. In other words, we target system-level protection rather then 'localized' IP custom solutions. In that sense the proposed solution is platform-oriented rather than processor oriented.

The architectural framework for security and reliability of MPSoCs proposed by (Patel et al. [2010]) represents in a way a solution similar to ours since it targets security at the level of MPSoC by employing a dedicated security processor and tests it against buffer overflow type of attack. Nevertheless, there are several considerable differences in methodology and implementation between their work and our envisioned solution. In (Patel et al. [2010]) the customized implementation for an Application Specific Instruction set Processor (ASIP) is presented; the solution there presented does not consider NoC architectures but relies on application code instrumentation which is not needed in our case. A

detailed comparison of the two solutions in terms of performance, power and area overhead is given in Section 7.3 and Chapter 8.

A proposal for establishment of a trustworthy system based on a set of dynamically reconfigured firewalls embedded in NoC is presented in (Sepulveda et al. [2011]). They propose a security architecture similar to (Fiorin, Palermo and Silvano [2007]) system with additional support for dynamical reconfiguration of security policies. The implementation allows the MPSoC protection by means of communication management. The security mechanism uses the information embodied in the packets that flow through the NoC to enforce the different security policies. This work has been recently enhanced (Sepulveda et al. [2012]) so that they introduce QoSS (quality of security service) exploiting the NoC components to detect and prevent a wide range of attacks. They present the implementation of a layered dynamic security NoC architecture that integrates dynamic security firewalls in order to detect attacks based on different security rules. They provide SystemC-TLM cycle-accurate model of the architecture and no hardware implementation has been provided. Comparison with this solution is discussed in Section 8.

# 2.3.1 Protection against specific attacks

Considering specific attacks and protection solutions for specific platforms, many efforts have been invested in research in general purpose computing and recently in embedded systems design. In this section we review the most relevant work concerning attacks of greatest relevance for us, namely on-chip memory protection, 'code injection' and Denial-of-Service attacks.

### On-chip memory protection

Data protection in MPSoCs is one of the relevant topics for our work (Fiorin et al. [2008]). An implementation of a protection unit for data stored in memory is described in (Coburn et al. [2005]). The proposed module enforces access control rules that specify how a component can access a device in a particular context. AMBA bus transactions are monitored and a lookup table (indexed by the concatenation of the master identifier signals and the system address bus) is employed to store and check access rights for the addressed memory location and to stop potential not-allowed initiators.

As mentioned above, similar problems have been addressed as well in industrial solutions. The on-chip memory protection unit developed by ARM, in systems adopting the ARM TrustZone technology (Alves and Felton [2004]),

provides the possibility of including a specific module - the AXI TrustZone memory adapter - to support secure-aware memory blocks. A single memory cell can be shared between secure and nonsecure storage areas. Transactions on the bus are monitored to detect the addressed memory region and security mode in order to cancel nonsecure accesses to secure regions and accesses outside the maximum address memory size. The module is configured by the TrustZone Protection Controller, which manages the secure mode of the various components of the TrustZone-based system and provides the software interface to set up the security status of the memory areas.

The SMART Interconnect solution by Sonics (refer to *SonicsMX SMART Interconnect Datasheet* [2008]), introduces on-chip programmable security 'firewall' which is employed to protect the system integrity and the media content passed among on-chip processing blocks, various I/Os, and the memory subsystem. The firewall is implemented through an optional access protection mechanism to designate protection regions within the address space of specified targets. The mechanism can be dynamic, with protection region sizes and locations that can be programmed at runtime. It can also be role dependent, with permissions defined as a function not only of which initiator is attempting to access but also which processing role the initiator is playing at that time. Protection regions subdivide a target's address space, where each target can have up to eight protection regions. Each protection region is assigned to one of the four levels of priority.

NoC-MPU described in (Porquet et al. [2011]) is a dedicated Memory Protection Unit allowing to support the secure and flexible co-hosting of multiple native software stacks running in multiple protection domains, on any shared memory MP-SoC using a NoC.

Our solutions goes a step farther than previous implementations of data protection techniques in the sense that, for the first time, it addresses the problem of the data protection on an NoC-based MPSoC. The details of the solution for this particular type of the attackis given in Section 6.3.1.

### Code insertion

A Code Injection attack exploits a vulnerability or an error in a program injecting or introducing malicious code into a program execution. The Code Injection attack could inject some malicious code or some code that points to a malicious code that may already be present in a system. Executing the malicious code aims to change the control flow of the main program and may have unpredictable consequences (Hardware-software design methods for security and

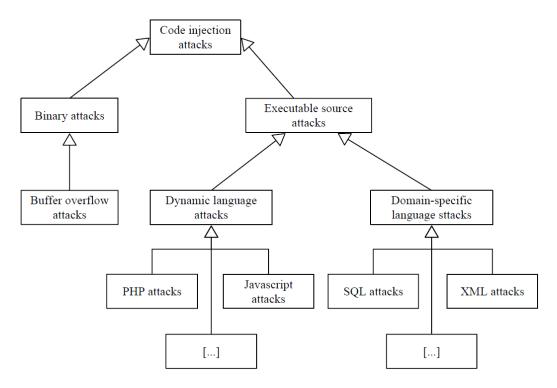

Figure 2.3. A taxonomy of code injection attacks according to (Mitropoulos et al. [2011])

### reliability of MPSoCs [2009]).

Weaknesses in system implementation inevitably remain and are often exploited by the attackers in the form of either physical, software or side-channel attacks. Software attacks that exploit vulnerabilities in software code or weaknesses in the system design are the most common type of attacks (Coburn et al. [2005]). Stack and heap based buffer overflows are the most common type of Code Injection attacks (Pincus and Baker [2004]).

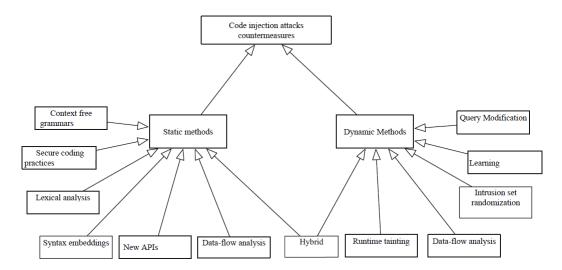

A variety of forms of *code injection attack* have been determined and a taxonomy of this kind of attack has been developed and presented by (Mitropoulos et al. [2011]) as shown in Figure 2.3. Appropriate countermeasures have been designed as well, these are presented in form of taxonomy (Mitropoulos et al. [2011]) in Figure 2.4.

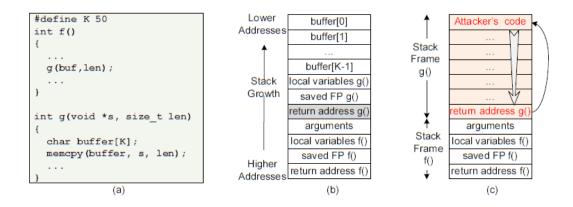

In the present work we consider the *buffer overflow* (also known as 'stack smashing') type of the attack, actually constituting a special form of *binary code injection* group of attacks: therefore, we analyze it here in particular detail.

Figure 2.4. A taxonomy of code insertion attack countermeasures according to (Mitropoulos et al. [2011])

Binary code injection - Buffer overflow Binary code injection involves the insertion of binary code in a target application to alter its execution flow and execute inserted compiled code (Mitropoulos et al. [2011]).

Buffer overflow represents one of the most widespread types of software attacks, and CERT reports that nearly 11% of discovered vulnerabilities pertain to this type of the code injection attacks (Pincus and Baker [2004]; Patel et al. [2010]). The attack scenario is rather simple: the attack is performed by writing an array to the stack without checking its upper bound (e.g. using C function strcopy(), one can overwrite the data of the valid stack frames). Even if the stack memory is not executable, and/or separated, overwriting the return address of the caller and saved registers is still possible. This means that the attacker can redirect the control flow by giving to the targeted return function the corrupted values. The simple scenario is presented in Figure 2.5

### **Protection strategies**

Several related works on the topic of *buffer-overflow* protection focus on proposing a variety of static methods for detecting *code injection*, to be applied at design or at compilation time (Dor et al. [2003]; Wagner and Dean [2001]). However, due to the increased portability and networking of MPSoC devices, very often these systems are exposed to threats that become manifest during run time execution of untrusted applications (usually downloaded from Internet).

Figure 2.5. A stack based buffer overflow attack by overwriting the return address register (a) Vulnerable code (b) Layout of the stack before an attack (c) Layout of the stack after an attack, from (Hardware-software design methods for security and reliability of MPSoCs [2009])

StackGuard by (Cowan et al. [1998]), a compiler-based solution, inserts a randomly generated value in the stack position next to the return address as well as in a general purpose register. These two values are compared, at the time the execution is returned to the caller function, in order to detect buffer overflow occurrence. While this solution is simple (in hardware terms) and elegant, some techniques to overcome this protection have been devised (e.g. by Bulba and Kil3r [2000]).