### Universidad Carlos III de Madrid Escuela Politécnica Superior Electronic Technology Department BACHELOR'S DEGREE IN TELECOMMUNICATION TECHNOLOGIES

Final Degree Project

### Implementation and Study of a True Random Number Generator

Author: Elena Martínez López Tutor: Honorio Martín González

Leganés, September 2015

This work is licensed under the Creative Commons License Attribution-NonCommercial-NoDerivs 3.0 Unported (CC BY-NC-ND 3.0. To see a copy of this license visit

http://creativecommons.org/licenses/by-nc-nd/3.0/deed.en or send a letter to Creative Commons, 444 Castro Street, Suite 900, Mountain View, California, 94041, EE.UU.

Any and all opinions here expressed belong to the author and do not necessarily reflect the opinions of the Universidad Carlos III de Madrid.

ii

**Title:** Implementation and Study of a True Random Number Generator **Autor:** Elena Martínez López **Tutor:** Honorio Martín González

### THE TRIBUNAL

President: Ignacio Soto Campos

Vocal: Pablo Acedo Gallardo

Secretary: Jose Luis González de Suso Molinero

Substitute: Pedro Martín Mateos

.....

VOCAL

SECRETARY

PRESIDENT

iv

# Acknowledgements

Thanks to my parents and friends who have supported and encouraged me to get to where I am today.

Special gratitude goes also to my tutor whose advice and assistance were key to complete this project.

vi

# Contents

| Abstract |                              | xv                              |     |

|----------|------------------------------|---------------------------------|-----|

| Abstract |                              | xvii                            |     |

| Su       | ımma                         | ary                             | xix |

| 1        | Intr                         | oduction                        | 1   |

|          | 1.1                          | Motivation                      | 1   |

|          | 1.2                          | Objectives                      | 2   |

|          | 1.3                          | Structure of this Document      | 3   |

| <b>2</b> | State of the Art             |                                 |     |

|          | 2.1                          | Security and Hardware           | 5   |

|          |                              | 2.1.1 Random Number Generators  | 6   |

|          | 2.2                          | Pseudo-random Number Generators | 7   |

|          | 2.3                          | True Random Number Generators   | 9   |

|          |                              | 2.3.1 Structure of a TRNG       | 10  |

|          | 2.4                          | FPGA Technology                 | 17  |

|          |                              | 2.4.1 FPGA Block Structure      | 19  |

|          |                              | 2.4.2 Xilinx Spartan- $3E$      | 20  |

|          | 2.5                          | Implementing TRNGs on FPGAs     | 22  |

| 3        | Characterization of the TRNG |                                 | 27  |

|          | 3.1                          | TRNG Under Study                | 27  |

|          | 3.2                          | Experimental Framework          | 28  |

|          |                              | 3.2.1 FPGA Implementation       | 29  |

#### CONTENTS

|              |                      | 3.2.2   | Treatment of the Data                                                    | . 30 |

|--------------|----------------------|---------|--------------------------------------------------------------------------|------|

|              |                      |         | $3.2.2.1  \text{Post Processing} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | . 32 |

|              | 3.3                  | Exper   | iments: Results and Analysis                                             | . 35 |

|              |                      | 3.3.1   | Frequencies                                                              | . 36 |

|              |                      | 3.3.2   | Intradevice Testing                                                      | . 46 |

|              |                      | 3.3.3   | Interdevice Testing                                                      | . 50 |

|              |                      | 3.3.4   | Restart Experiment                                                       | . 51 |

|              | 3.4                  | Final   | Analysis                                                                 | . 53 |

| 4            | Cor                  | nclusio | ns                                                                       | 55   |

|              | 4.1                  | Conclu  | usion                                                                    | . 55 |

|              | 4.2                  | Future  | e developments                                                           | . 57 |

| 5            | $\operatorname{Leg}$ | al Asp  | ects                                                                     | 61   |

| 6            | Pro                  | ject M  | Ianagement                                                               | 65   |

|              | 6.1                  | Plann   | ing                                                                      | . 65 |

|              |                      | 6.1.1   | Initial Planning                                                         | . 65 |

|              |                      | 6.1.2   | Final Planning                                                           | . 66 |

|              | 6.2                  | Budge   | et                                                                       | . 67 |

|              |                      | 6.2.1   | Initial Costs                                                            | . 67 |

|              |                      |         | 6.2.1.1 $$ Initial Estimated Material Costs $$ .                         | . 67 |

|              |                      |         | 6.2.1.2 $$ Initial Estimated Personnel Costs $.$                         | . 68 |

|              |                      | 6.2.2   | Final Costs                                                              | . 69 |

|              |                      |         | 6.2.2.1 Final Material Costs                                             | . 69 |

|              |                      |         | 6.2.2.2 Final Personnel Costs                                            | . 69 |

| A            | ppen                 | dices   |                                                                          | 70   |

| $\mathbf{A}$ | TR                   | NG Co   | ode                                                                      | 73   |

| в            | $\operatorname{Cre}$ | ating t | the Hard Macro                                                           | 83   |

| $\mathbf{C}$ | $\mathbf{Pyt}$       | hon So  | cripts                                                                   | 87   |

viii

| CONTENTS     | ix |

|--------------|----|

| D Glossary   | 97 |

| Bibliography | 99 |

CONTENTS

# List of Figures

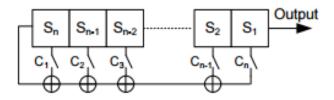

| 2.1  | LFSR scheme                                                                                                           | 9  |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

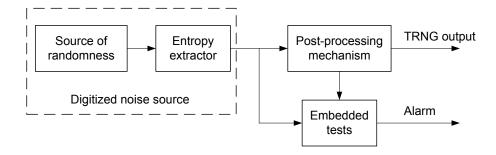

| 2.2  | TRNG scheme                                                                                                           | 10 |

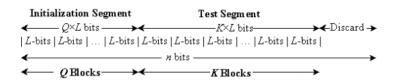

| 2.3  | Universal test sequence partitioning                                                                                  | 17 |

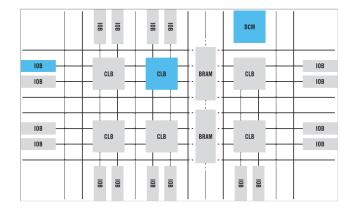

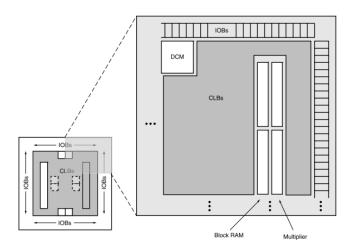

| 2.4  | FPGA Block Structure                                                                                                  | 19 |

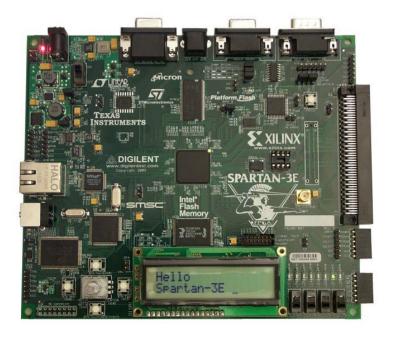

| 2.5  | Spartan-3E                                                                                                            | 20 |

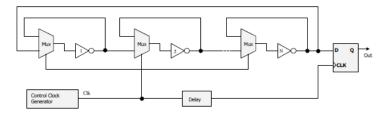

| 2.6  | Spartan-3E Family Architecture                                                                                        | 21 |

| 2.7  | Vasyltsov et al. TRNG                                                                                                 | 23 |

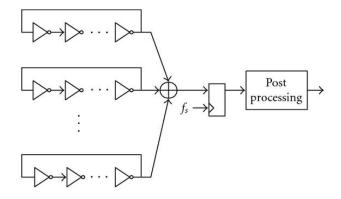

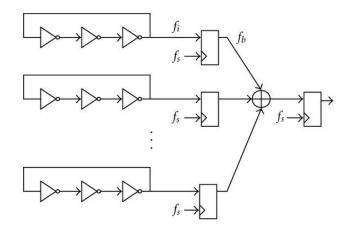

| 2.8  | Sunar et al. TRNG                                                                                                     | 24 |

| 2.9  | Wold et al. TRNG                                                                                                      | 25 |

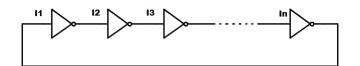

| 2.10 | Ring Oscillator basic stucture                                                                                        | 26 |

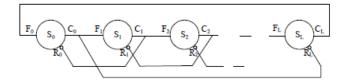

| 2.11 | Self-Timed Ring basic stucture                                                                                        | 26 |

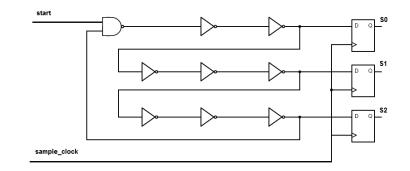

| 3.1  | TRNG design                                                                                                           | 28 |

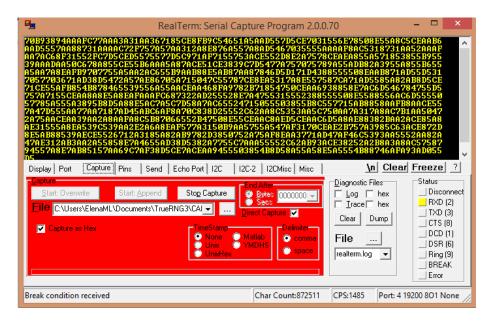

| 3.2  | Capturing software $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                     | 31 |

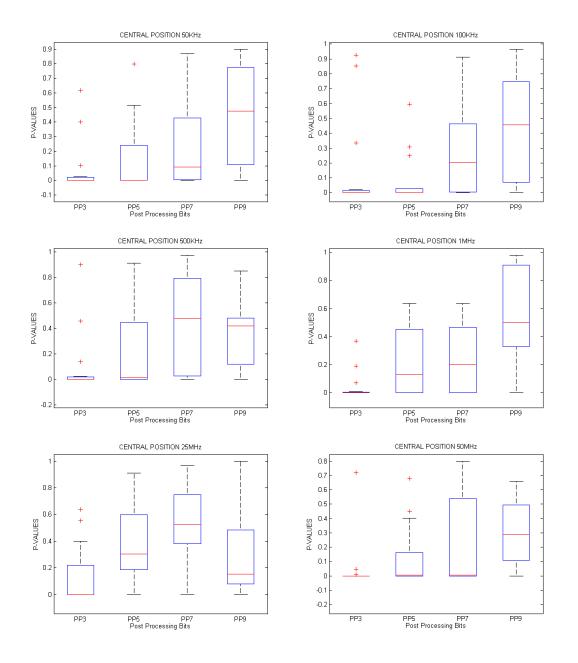

| 3.3  | Tested Frequencies in Central Position $\ldots \ldots \ldots$                                                         | 41 |

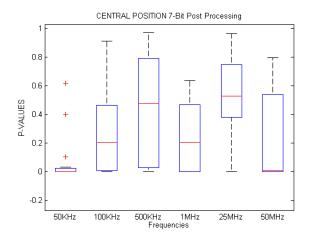

| 3.4  | Comparison of 7-bit XOR of central position                                                                           | 43 |

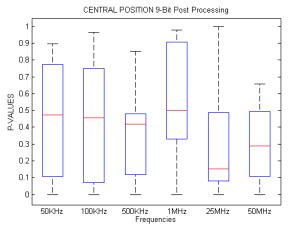

| 3.5  | Comparison of 9-bit XOR of central position                                                                           | 43 |

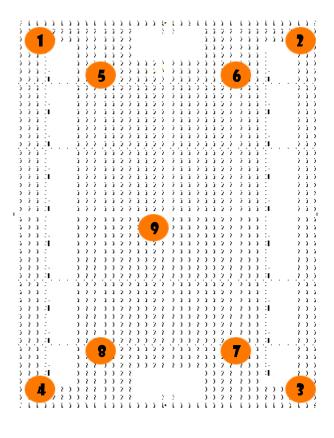

| 3.6  | Tested Positions of the FPGA                                                                                          | 46 |

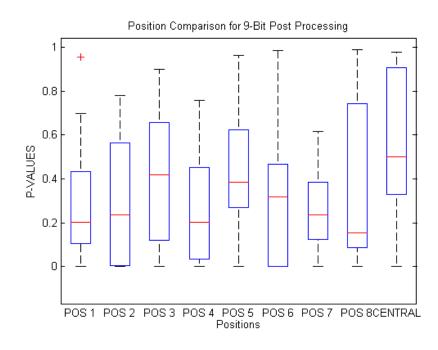

| 3.7  | Intradevice Test: 1MHz and Post-Procressing of 9-Bits $% \left( {{\left( {{{{\rm{B}}}} \right)}_{{\rm{B}}}}} \right)$ | 47 |

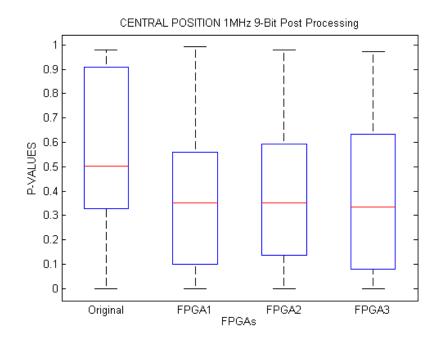

| 3.8  | Interdevice Test: 1MHz and Post-Procressing of 9-Bits                                                                 | 51 |

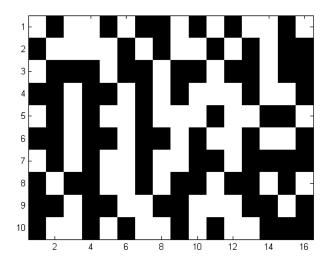

| 3.9  | Restart Experiment Results                                                                                            | 52 |

| 3.10 | Another Restart Experiment Results                                                                                    | 54 |

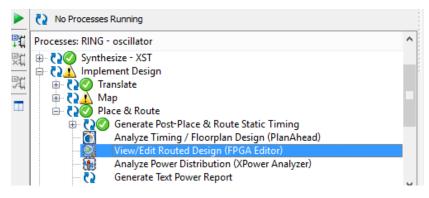

| 4.1  | Modified TRNG design with more inverters                                                                              | 57 |

| 4.2 | Modified TRNG design with more inverters and more sampling stages | 58 |

|-----|-------------------------------------------------------------------|----|

| 6.1 | Initial Gantt                                                     | 66 |

| 6.2 | Final Gantt                                                       | 68 |

| B.1 | FPGA Editor                                                       | 83 |

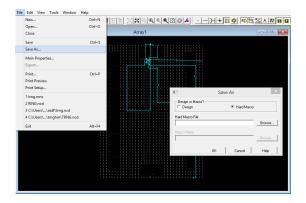

| B.2 | FPGA Editor Save as Hard Macro                                    | 84 |

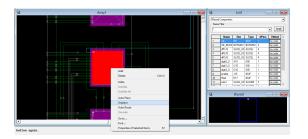

| B.3 | FPGA Editor Read Write mode                                       | 84 |

| B.4 | FPGA Editor Unplace component                                     | 85 |

| B.5 | FPGA Editor Add Hard Macro External Pin                           | 85 |

xii

# List of Tables

| 3.1  | XOR operation of 2 bits                                                    | 33 |

|------|----------------------------------------------------------------------------|----|

| 3.2  | XOR operation of 3 bits $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 33 |

| 3.3  | XOR operation of 5 bits $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

| 3.4  | Central Position 50KHz                                                     | 37 |

| 3.5  | Central Position 100KHz                                                    | 38 |

| 3.6  | Central Position 500KHz                                                    | 39 |

| 3.7  | Central Position 1MHz $\ldots$                                             | 39 |

| 3.8  | Central Position 25MHz                                                     | 40 |

| 3.9  | Central Position 50MHz                                                     | 40 |

| 3.10 | Central Position Post-Processing of 7-bits                                 | 44 |

| 3.11 | Central Position Post-Processing of 9-bits                                 | 45 |

| 3.12 | All positions Post-Processing of 9-bits                                    | 49 |

| 3.13 | Several FPGA, 1MHz, Post-processing of 9-bits $~$                          | 50 |

| 6.1  | Initial Planning                                                           | 66 |

| 6.2  | Final Planning                                                             | 67 |

| 6.3  | Initial Estimated Costs                                                    | 67 |

| 6.4  | Initial Estimated Personnel Costs                                          | 68 |

| 6.5  | Final Material Costs                                                       | 69 |

| 6.6  | Final Personnel Costs                                                      | 69 |

|      |                                                                            |    |

LIST OF TABLES

$\operatorname{xiv}$

### Abstract

Securing information has been a concern throughout history. Especially nowadays since many user applications such as smart cards or Internet connections deal with sensible data. To protect this information different cryptography protocols are used. These are algorithms that encapsulate the data by ciphering it. However, this is done by programming an application to run a digital mathematical function. This means that it is also possible to program malign applications to decode the cipher. In order to avoid this it is necessary to add unpredictability or randomness to the encoding process which can be done by employing a Random Number Generator.

A RNG can be implemented in both software and hardware; however, a truly unpredictable sequence is not achieved through a digital process governed by mathematical formulae. This results in most RNGs producing a form of pseudo-randomness. A True Random Number Generator must be implemented on a technology that allows it to harvest entropy from an unpredictable or even chaotic physical process. This is why TRNGs are designed and implemented for hardware. In fact, it is possible to gather entropy through integrated circuits like ASICs or FPGAs. The objective of this project is to design and implement a TRNG on FPGA technology because its pre-defined logic blocks that only require a small amount of resources make it an appealing solution.

First, an analysis of typical RNG designs is presented to understand the between a pseudo-RNG and a TRNG. Once this is stablished, the specific ways of designing TRNGs for integrated circuits are delved into. Moreover, the need for evaluation of the quality of randomness is also stated. This is ensured by a battery of tests that study the statistical properties of the output of a RNG.

Secondly, the TRNG design proposals by Böhl on which this project is based on are introduced and analyzed before creating the design and implementation. Afterwards, the four experiments performed are explained. It was decided to first test the behavior of the TRNG at different frequencies to decide which provided randomness with the best quality. Afterwards, the TRNG was placed in different areas of the FPGA at the optimal frequency to test the variability of the device. A third experiment consisted of comparing these results in more devices to further study the variability. The final experiment consisted on forcing a reset of the circuit to ensure that the TRNG was resilient against this type of attacks.

Last but not least, the results are summarized and several future developments are presented. After this the legal aspects and management of the project are explained.

**Keywords:** random number generator, true random number generator, FPGA, hardware security.

xvi

### Abstract

La protección de información ha sido una constante preocupación a lo largo de la historia. Especialmente hoy en día debido a las muchas aplicaciones que manejan datos confidenciales como tarjetas inteligentes o conexiones a Internet. Para proteger esta información diferentes protocolos criptográficos son usados. Estos son algoritmos que cifran los datos para encapsularlos. Sin embargo, esto se hace programando una aplicación que corre una formula matemática digital. Esto significa que también es posible programar aplicaciones maliciosas para decodificar el cifrado. Para poder evitar esto es necesario añadir aleatoriedad o un elemento impredecible al proceso de codificación. Esto puede hacerse empleando un Generador de Números Aleatorios cuyas siglas en inglés son RNG.

Es posible implementar un RNG tanto en software como en hardware; sin embargo, una secuencia realmente impredecible no se puede generar a través de un proceso digital basado en la computación de fórmulas matemáticas. Esto es lo que hace que la mayoría de RNGs produzcan una especie de pseudo-aleatoriedad. Un Generador de Números Realmente Aleatorios (True Random Number Generator o TRNG) debe ser implementado en una tecnología que le permita extraer entropía de un proceso físico impredecible o caótico. Es por esto que los TRNG se implementan en hardware. De hecho, es posible obtener entropía a través de circuitos integrados como ASICs o FPGAs. El objetivo de este proyecto es diseñar e implementar un TRNG en tecnología FPGA puesto que sus bloques lógicos predefinidos que solo necesitan unos recursos reducidos la convierten en una solución atractiva.

Se empieza por presentar un análisis de los diseños de RNG típicos para comprender la diferencia entre generadores pseudo aleatorios y TRNGs. Tras esto, se especifica la forma en la que los TRNGs se diseñan para circuitos integrados. Además, se expone la necesidad de evaluar la calidad de la aleatoriedad que se genera. Esta se comprueba a través de una batería de tests que estudian las propiedades estadísticas del output del TRNG.

A continuación, las propuestas de diseño de TRNGs de Böhl en las que este proyecto se basa son introducidas y analizadas seguidas del diseño e implementación propios. Tras lo cual se explican los cuatro experimentos realizados. Primero se decidió comprobar el comportamiento del TRNG a diferentes frecuencias con el fin de determinar a cuál de ellas se producía la aleatoriedad de mayor calidad. Segundo, el TRNG fue posicionado en diferentes áreas de la FPGA a la frecuencia óptima para evaluar la variabilidad de la placa. El tercer experimento explora aún más la variabilidad al realizar el experimento anterior en otras placas. El último experimento consistió en forzar un reset del circuito para comprobar la resistencia TRNG ante ataque de este tipo.

Finalmente, los resultados obtenidos se presentan resumidos junto con varias propuestas de mejoras futuras. Tras ello se muestran los aspectos legales del proyecto y su gestión.

**Keywords:** generador de numeros aleatorios, generador de numeros realmente aleatorios, FPGA, seguridad hardware.

xviii

### Summary

Throughout history many different forms of protecting sensible information have been designed but nowadays the most commonly used are cryptographic protocols. These protocols consist of algorithms that attempt to encapsulate the data by ciphering it. However, the algorithms are digital functions computed by a machine, therefore, the protocol is as reliable as the computer that generated it. If a software application was pre-programmed to encode a secure environment, another malign application can be programmed to decode it. An extra layer of security that an external application would find unpredictable is required. This can be achieved by employing a Random Number Generator.

There are several ways to create random numbers but the most desirable is to design a generator that produces an uniformly distributed sequence in which there is no discernible pattern. In other words, any element taken from it must be statistically independent from the rest. This can be implemented in both hardware and software but, again, the mathematical formulae on which digital processes are based on are not reliable to produce a truly unpredictable sequence. This is why many RNGs have a deterministic component that results in the generation of a sequence that can only be considered pseudo-random.

True randomness originates from the entropy of an aleatory or chaotic physical phenomenon such as noise or nuclear decay. A True RNG will harvest this entropy and handle it to generate a sequence of numbers. In order to do this a hardware device is required. Despite this seemingly complicated process, many small-sized devices can implement a TRNG such as integrated circuits like ASICs or FPGAs. For this project FPGA boards seemed an appealing solution because not only they are highly affordable but also because their resource consumption is reduced by the use of pre-defined logic blocks. In FPGA devices, there are several sources from which randomness can be extracted. First, through analog peripherals integrated circuits can gather entropy directly from a chaotic event, however most models do not include such technology. Second, there is metastability which refers to unpredictable voltage oscillations of flip-flops when their hold time and setup times are violated. However, FPGA technology is designed so that these effects can be reduced. Third, using SRAM memories to either simulate metastability or through its start-up state that generates non-deterministic noise. Fourth, Open Delay Chains that XOR many delay stages originated by Dlatches. Last but not least, jittery clock that deviate from the ideal behavior of a signal. This has proven to be the best method for FPGAs since it only requires simple components that can be found in any type of FPGA.

There are two ways to exploit jitter in RNGs: coherent sampling and jittery clock sampling. In coherent clock sampling several jittering clocks are necessary. A jittery clock takes samples from another one, since none of them are ideal the samples results in a random sequence. Meanwhile, jittery clock sampling takes samples from oscillators. An oscillator can either be a Ring Oscillator, a feedback loop of an odd number of oscillators, or a Self-Timed Ring, a loop of adjacent stages.

It is very likely that the quality of the randomness generated by any of these means may not be perfect. The output of any TRNG must be analyzed by any of the official batteries of statistical tests dedicated to estimate whether the randomness is truly unpredictable and uniformly distributed or not. If a RNG does not pass these tests it means that it has a deterministic component. A module can be added to the design of the TRNG to correct biases in the numbers generated: a post-processing mechanism. The two most common are: the XOR corrector which simply compresses the sequence by performing an XOR operation of n consecutive bits and the von Neumann corrector that takes pairs of bits and either returns the first bit if they are different and discards them otherwise. There are other mechanisms such as hash and resilient functions, linear feedback registers, encrypting the noise signal, etc.

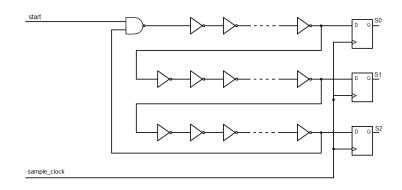

The TRNG implemented and studied in this project is based on Böhl's proposal for a fault attack robust generator. It consists of a Ring Oscillator of nine inverting components: an initial NAND gate and eight inverters. The random sequence is obtained by sampling at three points of the ring through D flip-flops. Each of these are placed after three inverting elements.

xx

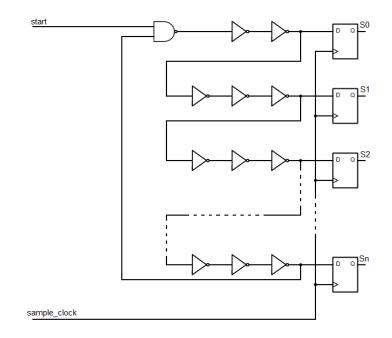

FPGAs, such as the Xilinx Spartan-3E board used, reduce the difficulties in designing circuits by routing the signals and elements in the hardware automatically. Nevertheless, this means that for each measurement that would be taken there is a chance that the hardware would be routed differently. Thus, it would be impossible to guess if the quality results obtained each time a measurement would be taken would depend on the variables controlled during the experiments or because a different routing was more or less effective. To avoid this ambiguous situation, it was decided to turn the TRNG into a Hard Macro. In other words, custom analog block surrounded by digital logic that fixes the components and routing it requires in every implementation.

It was found after a first attempt at evaluating this TRNG that a post-processing mechanism is required to correct its weaknesses. An XOR corrector has been chosen for this purpose. It was desirable to test the performance the post-processor at different lengths: 3-bit, 5-bit, 7-bit and 9-bit. Originally, this was going to be implemented on the hardware. However, it was soon realized that the time that would be wasted in doing so and capturing the data afterwards would not be advantageous. Instead, the corrector was implemented as a digital Python script which greatly reduced the time spent in post-processing. The script treats the random sequence captured by XORing as many bits as specified. As such, it only took a couple of minutes to post-process the sequence with the four XOR correctors.

At the beginning of the project, due to the time constraints, only two experiments had been scheduled but because of the Python optimization another two experiments could be performed. The four experiments are: an evaluation of the TRNG at different frequencies of oscillation, an intradevice test, an interdevice test and a forced restart of the oscillations. The four of them as explained in the following paragraphs.

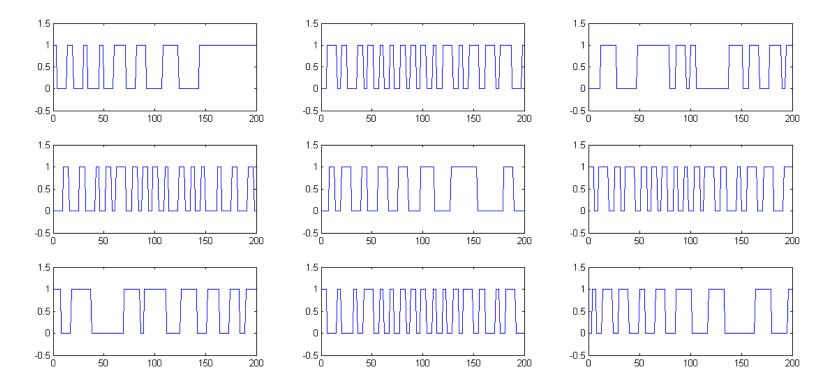

The experiment is the evaluation at different frequencies. In the reference proposal, it was declared that the frequency of oscillation at which the TRNG produces optimal results is 1MHz. It was decided to prove or disprove this by measuring the random sequence produced by the TRNG in a fixed position of the FPGA at several oscillation frequencies: 50KHz, 100KHz, 500KHz, 1MHz, 25MHz and 50MHz. The XOR correctors of 3 and 5 bits did not produce satisfactory results as they failed many statistical tests. Nevertheless, at 7 bits the post-processing started to correct the bias effectively, although the best results were obtained with a 9-bit XOR. It was found that at higher frequencies there is not enough time for

jitter accumulation which reduces the quality of randomness. Meanwhile, while at low frequencies the time for accumulation is greater, at some point the penalty in throughput becomes too high also affecting the performance of the TRNG negatively. It was therefore proven that at 1MHz the best quality was produced.

The second experiment consists of an intradevice test. This time, using the best frequency of oscillation (1MHz) and the best postprocessing (9-bits) the quality of the TRNG is evaluated in different locations of the FPGA board. The objective of this is to test the hardware variability. Nine positions were evaluated: the center of the board, the four outer corners and the four inner corners. The best results were obtained at the center. The reason for this is that, despite the Hard Macro, the connections in surrounding components can affect the jitter. At the center the board has more space to place other elements further away from the TRNG so they would not affect its performance.

The third experiment consists of an interdevice test to further test the hardware variability. This has been done by evaluating the performance of the TRNG in several devices under the established variables: the optimal position, frequency of oscillation and postprocessing. It is found that the four boards passed the same number of statistical test but an oddity occurred: the quality of results of the three the newly acquired FPGAs were significantly worse. It has been deduced that these measurements were taken during a heat wave which indicates that the TRNG is not resilient against environmental changes.

Lastly a restart experiment was performed. This consisted on bringing the oscillations to a halt by force and restarting them in order to evaluate whether or not the TRNG could still generate a robust random output. The initial NAND gate of the oscillator is fed by a reset signal. If this signal becomes zero for some reason while the TRNG is running the oscillations will stop. This reset is directly connected to a trigger of the FPGA board. All that is needed to restart the circuit is to pull down this trigger and immediately pull it up again. After many restarts were performed sequence generated was analyzed. No patterns were found that would indicate that the sequence produced after a restart could be guessed. Therefore it has been concluded that the TRNG is secure against this type of attack.

To sum up, it has been found that for this TRNG on a Spartan-3E board, 1MHz is the optimal frequency of oscillation but a postprocessing mechanism is required. An XOR corrector of 9-bits yields

xxii

the best quality. The TRNG can be implemented anywhere within the FPGA but the best results are obtained at a centered position. Moreover, the TRNG is resilient against restart attacks but not to environmental changes.

There have been previous attempts at implementing this proposal of a TRNG in several technologies. These found that it was robust with a 3-bit XOR corrector and also fault and attack resilient. From this it can be deduced that the quality and weaknesses of this implementation may be caused by the variability of the FPGA model chosen that could be influencing the Ring Oscillator negatively. It would be desirable to repeat these experiments under a controlled environment in other FPGA technology in the future to be able to assure that the Xilinx Spartan-3E is to blame.

Nevertheless, since the TRNG was proven to generate a good quality output given the appropriate conditions, several future developments could be implemented to improve the quality of the output of the TRNG.

Originally, in his proposal, Böhl suggested that the random output of the TRNG could be built in another way. Instead of directly outputting the three bits stored in the three DFFs consecutively, the three of them could be XORed. The actual random sequence would be the output of this last operation. The first modification to the design would have to be testing the quality of the design slightly modified in this way.

The next possible modification to the design would be to add more inverting elements to the ring oscillator. The randomness would have higher quality because the more stages the more jitter that would accumulate. This change to the design would probably change the optimal frequency of oscillation so the first experiment would need to be re-evaluated. There would be two possible ways of modifying the design according to this: first, add more inverters before each sampling stage since it could be assumed that the weaknesses could be appearing because three inverters before sampling are not enough; second, add more sampling stages preceded by three inverters although this would most likely drain more resources. In case any of these two possibilities were implemented, it would be recommended to evaluate the quality of the output first from just outputting the sampled bits and afterwards by XORing them before generating the sequence.

Another completely different approach would be to evaluate other post-processing mechanisms in hopes that there might be a better correction of bias such as a Linear Feedback Shift Register, the von Neumann algorithm or a hash or resilient function. However, it would also be interesting to test the quality of the current XOR corrector with the previous proposals either using a new technology or by changing the current design.

A last consideration would be to compare the results obtained by this TRNG with a different type of feedback loop. The Ring Oscillator of inverting elements would be replaced by a Self-Timed Ring since that kind of implementation has been proven to be more resistant to variabilities and generate jitter with higher quality.

In conclusion, the TRNG implemented did manage to produce a considerably reliable random sequence given the appropriate postprocess was appended. In spite of this, the TRNG is not without its faults and weaknesses which may have been caused by the hardware limitations. It is recommended to repeat these experiments in several FPGAs but it would also be possible that by slightly modifying the current design the deficiencies could be corrected.

#### xxiv

### Chapter 1

## Introduction

Sensible data and information has always been secured employing a wide variety of ways all through history. In fact, nowadays many applications use some form of security: smart cards, Internet routers, home computers and all sorts of mobile and wireless devices. All of these applications demand that the information is handled and stored in a secure way. Modern cryptography attempts to serve this purpose through codes that cipher the data and the transmission channel. However, cryptographic protocols are usually generated by software as a digital function which is not enough to store the data securely, to achieve it, hardware security is required.

Security in hardware usually consists on the use of circuits or other devices that add the conditions necessary for the application to run over a secure environment. In the case of embedded systems, random number generation is a very useful process for addressing this issue. There are several ways to create random numbers but the most desirable is to design a generator that produces a sequence that cannot be guessed because it is uniformly distributed and unpredictable, in other words, a generator that can achieve true randomness.

### 1.1 Motivation

The motivation of this project is to study how TRNGs can be designed and implemented on integrated circuits and particularly on Field Programmable Gate Arrays.

Random numbers are used in many different types of applications from gambling to data encryption and more. In cryptographic applications, it is very beneficial to have a generator that can produce a truly random sequence to cipher and/or secure data. As such, many Random Number Generators have been designed in software and hardware.

A sequence is considered truly random when it cannot be predicted. However, especially in software RNGs this is difficult to achieve because they create a sequence according a pre-programmed mathematical formula therefore only obtaining a form of pseudorandomness. True randomness is not accomplished through an algorithm but it is produced as a result of a physical process such as noise or nuclear decay. True random number generators are implemented on hardware devices that have the ability to harvest entropy from these processes.

Despite the apparent difficulty that gathering randomness presents, it is possible to do so through very small integrated circuitry like ASICs or FPGAs. ASICs are very advantageous since they can integrate tailored blocks including many sorts of analog elements. However, tuning all the parameters and components that the generator requires can make implementing a TRNG on ASICs quite expensive. In contrast, despite their constrained resources FPGAs are a very popular hardware on which to implement TRNGs due to their pre-defined logic blocks which greatly reduces their price.

#### 1.2 Objectives

The main objective of this project is to implement a TRNG on integrated circuitry and study its behavior. More specifically, this project tests the behavior of a TRNG based on Böhl's attractive proposal in [1] on a FPGA board.

According to [1], the a jittery clock such as the one included in FPGAs can be used at an oscillation of 1MHz to produce true randomness but it also states that a post-processing technique is required to enhance entropy. In [2], another paper based in [1], a simple post process is used: an XOR operation of 3 bits. This is tested on a couple of different hardware solutions. One of them is a FPGA which is a very interesting type of hardware it allows to place the TRNG almost anywhere within it. However, this feature is not tested in [2] as it only provides data based on frequency samples. Another important reason to try to emulate their approach of implementing the TRNG in FPGA technology is that, FPGAs also introduce the great advantage of reducing costs in materials.

#### 1.3. STRUCTURE OF THIS DOCUMENT

There are several things that it was desirable to demonstrate as they were not delved into by neither [1] or [2]. The experiments that were decided to be carried out are:

- 1. The reliability of the TRNG at several frequencies and prove or disprove that the optimal frequency of oscillation is 1MHz.

- 2. Expand on the use of the TRNG on FPGA technology and check if its placement in different areas of the same hardware affects its performance.

- 3. Test its output with and without post processing.

- 4. Post process of the output with a XOR operation of not just 3 bits but also several more bits to test how this affects randomness.

All of these experiments will be performed by passing the data captured through the Statistical Test Suite provided by the National Institute of Standards and Technology. This battery of tests has been especifically designed to examine the quality of a random sequence. [3].

#### **1.3** Structure of this Document

This document is structured as follows:

- Chapter 1 provides the basic introductory information to the project that will be discussed in later chapters.

- Chapter 2 expands the theory introduced in the previous chapter as well as providing information on the technology used.

- Chapter 3 is an in depth explanation of the solution created to implement and design the True Random Number Generator and how it has been tested.

- Chapter 4 presents the final conclusions that have been reached after the results of the tests have been analyzed and provides future possible developments.

- Chapter 5 exposes the legal conditions that the project is required to meet.

• Chapter 6 includes a initial economic management of the project as well as its estimated duration of the project along with the final real money and time spent.

### Chapter 2

### State of the Art

In this chapter we present an overview of the theory of random number generation as well as the hardware technology that is used in the project to this end.

#### 2.1 Security and Hardware

The creation of secure environments has always been an issue throughout all the history of humanity. The greatest advance in security occurred with the discovery of electricity which led to a new form of security: hardware security. Its first incarnation was introduced in 1853 with the creation of electro-magnetic alarms used to protect businesses and residences. By the end of the  $19^{th}$  century this groundbreaking technology had advanced to be able to electronically controlled vaults [4].

However, protecting physical property is not the only use for hardware security. Securing sensible information has been an issue dating back to ancient times. Cryptography fulfilled this necessity through the use of codes and ciphers generated in a manual process. In contrast, modern cryptography focuses not only on coding the data to be transmitted but also on creating a secure transmission channel. The first instances of these new methods of encryption appeared in military applications by the end of the  $19^{th}$  century but they became a major security measure during World War II with the creation of the German Enigma rotor machine. Breaking the code of this and other encryption machines also became a military priority which resulted in a constant flow of revolutionary hardware security techniques such as *computing*. It was only a matter of time that these technological advances were applied to civil applications leading to the first computing mainframes in the 1960s, supercomputers in the 1960s and finally personal microcomputers in the 1970s. [5] [6]

Nowadays, hardware security can be found practically every aspect of our daily lives as it is necessary in many consumer applications such as: ID-cards, Internet routers, sim cards, smart cards, game controllers, car electronics. All these applications require hardware security not only to handle information in a secure way but also to store it anywhere at any time with small costs in energy and resources. Modern cryptographic protocols are generally a series of mathematical digital functions that must be made resistant to algorithmic attacks. These protocols generally rely on private or session keys to secure data before exchanging it. An attacker would attempt to eavesdrop on the transmission and guess the key. It is necessary to make the channel resilient against malicious listeners but, in case that line of protection failed, the keys must also be very hard to decode. One way to ensure this is to employ a Random Number Generator: a device that can generate a key so complicated so that an attacker cannot guess it or even produce a sequence to envelop the channel and protect the data to be transmitted from eavesdroppers.

RNGs have been implemented in several types of technologies. Modern integrated circuits (IC), such as Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs), are very popular technology to implement RNGs precisely because they are highly affordable and they only require a small amount of resources.

#### 2.1.1 Random Number Generators

Generating random numbers has always been required in many situations. In ancient times, divination and card or dice games were the main areas where randomness was applied which entailed a very elaborated and difficult calculation process. However, due to the processing capacity of computational or physical devices nowadays random number generation has radically changed. New applications for it have also appeared such as new forms of massive national and international gambling games as well as many security measures such as producing secure data encryption keys.

These modern Random Number Generators (RNGs) in order to be considered secure and trustworthy are expected to produce a sequence of numbers in which there is no pattern: any element taken from it must be statistically independent from the rest. [7] There exist statistical tests for randomness to study how successfully a RNG produces an indiscernible pattern. However, many generators that pass them do not actually produce a truly random sequence. In computer applications this is due to the fact that, after all, since a computer simply follows the commands that have been given to it, its behavior is predictable. Hardware RNGs pose a better solution over software applications since they are based on a, usually, unpredictable physical phenomenon although that does not mean that they are without fail.

Therefore, there exist two kinds of RNGs [8]:

- Pseudo-random Number Generators based on a deterministic bit generation process.

- True Random Number Generators based on non-determinisctic random bit generation.

In the following sections of this document these RNGs are explained in greater detail.

### 2.2 Pseudo-random Number Generators

A Pseudo-random Number Generator or PRNG consists of a deterministic mathematical algorithm that produces output sequences of numbers that appear to be random. This is because all of them have the same probability of appearing and can satisfy statistical tests. However, this output, also known as a unbiased random output, is not truly random. The output is obtained through a pre-calculated list or mathematical formulae that contains all possible values the PRNG can take. In order to simulate randomness, this list is traversed at an unknown starting point known as 'seed' which is fed to the generator [9] [10]. This quality means they can generate long sequences of numbers quite fast which makes them very efficient but it is also what makes them deterministic, any time you feed the same seed to the PRNG it will return the same output sequence. It can also be deduced from this that PRNGs are generally periodic, while this at first may seem like a hindrance to randomness it should be taken into account that the period would be so long that it would not be noticed in most applications in which PRNGs are used. Moreover, there may be certain applications in which it might be useful to repeat a previous sequence easily such as in simulation and modelling [7].

There are many PRNGs being used but some of the most well-known are:

- Mersenne twister is the most widely used algorithm in PRNGs for software systems such as Python, PHP, MATLAB, Maple, Apache, etc. It was developed in 1997 and was designed to correct the many flaws in previous PRNGs by generating pseudorandom integers with speed and high-quality. Although there is a 64-bit word length implementation, the standard is to produce a sequence of a 32-bit integers based on the Mersenne prime that produces a period of  $2^{19937} - 1$ . In any case, for a w-word length, integers are generated in a range of  $[0, 2^w - 1]$ which is k-distributed to v-bit accuracy by the following equation:  $(trunc_v(X_i), trunc_v(X_{i+1}), ..., trunc_v(X_{i+k-1}))$  (0 < i < P) where P is the period of a kv-vector and  $trunc_v(x)$  denotes the first v bits of x, each of the  $2^{kv}$  combinations occur the same number of times during a period.[11]

- Blum-Blum Shub generates a bit sequence according to the formula:  $X_{n+1} = X_n^2 mod_M$  where M is the product of two very large secret and distinct prime numbers each congruent to 3 modulo 4.  $X_0$  is calculated through the seed which is in the random interval [1, n 1] and must meet the condition gcd(seed, n) = 1, thus  $X_0 = seed^2 mod_M$  [9]

- Linear Congruential Generator (LCG) is one of the oldest PRNGs. It is based on the recurrence relation:  $X_{n+1} = (aX_n + c)mod_m$  in which a, c, m and the seed  $X_0$  are constants that, if selected properly can make the PRNG a maximal period generator. LCGs have been proven to be quite efficient when m is selected to be a power of 2, generally  $2^{32}$  or  $2^{64}$ . However, since  $X_n$  and  $X_{n+1}$  are not independent, the sequence generated could be guessed by an attacker, therefore, LCGs are not a type of CSPRNG and cannot be used in cryptographic applications. [10]

- Linear Feedback Shift Register (LFSR) is a shift register which is fed an input bit that is actually a linear function of its previous state. As a PRNG this feedback function consists of a combination of XOR gates as can be seen in figure 2.1 which results in:  $(C(x) = 1 + c_1x^1 + c_2x^2 + ... + c_nx^n)$ . While LFSR are

8

Figure 2.1: LFSR scheme

a very popular PRNG, the fact that they are linear presents a serious weakness[10].

• Xorshift is an specification of the LFSR that introduces the advantange that the needed state bits are a multiple of the length of the word. The number of state bits can be as large as 4096, this ensures that the memory cache of a computer can process the PRNG without slowing down while also generating a quite robust output [12].

Other algorithms commonly used as PRNGs include: Wichmann-Hill, Inversive congruential generator, ISAAC, Lagged Fibonacci generator, Maximal periodic reciprocals, Multiply-with-carry, RC4 PRGA, etc.

#### 2.3 True Random Number Generators

Unlike PRNGs, True Random Number Generators (TRNGs), also known as Hardware Random Number Generators, provide randomness from a physical phenomenon rather than a pre-calculated list. There are many possible physical sources of randomness but all of them must allow the TRNG to generate unpredictable data, which in turn means that, as opposed to PRNGs, this kind of generators are nondeterministic because any sequence generated must not be possible to be reproduced at will and thus the random sequence must not be periodic. However, all of this also means that a TRNG will be more inefficient than a PRNG since it takes much more time to produce random numbers. [7]

TRNGs must be very reliable and robust as they are a very important element in cryptography since they are typically used in the generation of secure keys, nonces, padding or even shielding with random noise the data transmitted at a certain bandwidth in order to prevent modifications that can range from natural disruptive

Figure 2.2: TRNG scheme

environmental changes to intended malicious attacks to the channel. Embedded systems also require the security a TRNG provides, however, these hardware devices tend to be designed to implement deterministic functions which may lead to costly undesired results and an overconsumption of the available resources. In the specific case of FPGAs, since the resources are limited to the logic blocks it contains the flexibility to implement a TRNG is reduced. [10]

#### 2.3.1 Structure of a TRNG

The structure of any TRNG depends on the quality of the four basic components that can be seen in figure 2.2.

- Source of Randomness: also known as Entropy source, consists on a physical process that can be used to create unpredictable behaviour. These generally are: chaos, electronic noise, nuclear or quantum decay and free running oscillators [13]. However, most logic devices, such as FPGAs, do not contain analog blocks that can reproduce those physical phenomena. Instead, the phenomena used in those devices are:

- Metastability refers to performance of logic gates between two different logic levels. This occurs when the hold time of flip-flops and the setup are violated. The reaction of the internal gates of the flip-flop is unpredictable oscillating at a voltage that is neither the expected logical low or high. After a while the oscillations recede and it outputs a logical low or high randomly [14].

- Jitter is the short-term variation in signals between logic gates from their ideal position. This causes deviations and delays in the propagation of signals. The jitter is also seen as an instability of the clock period due to clock generators

that contain elements in a closed loop that produce a delay such as ring oscillators [15].

- Thermal Noise produced by the components inside the device, commonly resistors and capacitors. The noise is used as the frequency of a free running oscillator which to be extracted needs first to be converted to the time domain. However, FPGAs cannot implement resistors and capacitors therefore it is not possible to use this as a source of randomness in FPGAs [10].

- Entropy Extractor is a sampler that collects and digitalizes the maximum entropy of the source of randomness without tampering with the analog physical process. Moreover, a particular type of extractor will be used depending on the source employed. In the case of logic devices without analog blocks the extraction is done through synchronous or asynchronous flip-flops that sample the rising or falling edges of the desired signal. The synchronous case consists on taking samples at fixed time intervals of a random signal while asynchronous flipflops take samples at random time intervals of a regular signal

- Post-processing Mechanism is used to conceal the weaknesses or bias of the random signal that has been obtained. Imperfections in the signal can cause it to produce very weak random numbers that can even be considered non-random by the statistical tests. These weaknesses can be produced by a not high enough entropy source (metastability), a faulty extraction mechanism, environmental changes or tampering [15] [14]. Post-processing may not be applied if the TRNG does not suffer from this bias, otherwise it is required. By employing a post-processing mechanism that compresses the signal, entropy is increased and correlation and bias are reduced. The most common mechanisms are:

- XOR corrector: applies a simple linear exclusive-OR operation on blocks of n consecutive bits to the signal outputting one bit. If the bits of the original signal were independent this compression of the data can reduce the bias the signal had very effectively. However, if they were correlated the bias won't be corrected. Not only this postprocessing is very simple to implement in hardware but also keeps a constant throughput. [16]

- Von Neumann corrector: probably the most well-known post-processing mechanism not only because it produces an unbiased output but also because it's a simple non-linear function. It processes pairs of successive bits: it outputs the first one if they are different and discards the pair if they are equal. As a result, about a 75% of the bits are discarded. In spite of this, its output will be unbiased even if the original was stationary and biased. [17]

- Hash functions: an almost uniform and collision-resistant stream can be generated by a hash function it its fed a high entropy signal. However, these functions consume many resources so they are not easy to implement in hardware. [18]

- Linear Feedback Shift Registers: not only are they aesy to implement in hardware but also they are able to output a sequence with a quite long period and very stastiscally robust. [19]

- Good Linear Codes: also known as Resilient functions (a derivative of boolean functions [20]). If any attacker has discovered n bits of the random sequence they still cannot guess the full sequence adding robustness to the sequence. Moreover, these codes do not consume many resources and have a very good throughput. [21] [22] [23]

- Encryption of the digitalized noise signal: based on the cryptographic diffusion and confusion properties to dynamically modify the output of the generator. However, this mechanism is not easy to implement and is quite expensive. [15]

- Embedded tests are required before the TRNG can be implemented in secure cryptographic applications. The tests examine the quality of the random signal generated by evaluating that it is uniformly distributed. Some of these tests are also used for PRNGs.

- DIEHARD: one of the toughest test batteries, it has two versions: the original consisting of 15 tests [24] and a newer lightweight suite of 3 tests with updated versions of the three selected tests [25].

- **ENT:** calculates five statistical meassures of the input stream: entropy, chi-square, arithmetic mean, Montecarlo value for Pi and the serial correlation coefficient. It is used

not just for testing the quality of RNGs but also for testing algorithms or applications that mask information density such as compression algorithms [26].

- FIPS: developed by the National Institute of Science and Technology (NIST), the Federal Information Processing Standard is used by the government of the United States. It specifies 4 levels of security for a cryptographic application designed to secure unclassified but sensitive data.

[27]

- AIS31: exclusive to test TRNGs and developed by the Bundesamt für Sicherheit in der Informationstechnik (BSI) or the German Federal Office for Information Security. It consists of two levels of security: the first one, consisting of 6 tests (disjointness, autocorrelation and 4 FIPS tests), evaluates the final signal after post-processing while the second level that consists of three tests (distribution, comparative of multinomial distributions and entropy) evaluates the output signal of the source of randomness. The AIS31 also establishes that an alarm should be generated when the minimum entropy by bit is not achieved, this can be done through an on-line test. [28]

- On-line Test: According to [29] these tests should fulfill the next requirements:

- \* It must detect almost immediately breakdowns of the source of randomness.

- \* It must detect fatal statistical imperfections of the random sequence being tested.

- \* If the sequence has a slight deviation from ideal randomness it must not raise an alarm.

- \* It must barely consume any memory, run fast and be easy to implement.

- NIST Statistical Test Suite for Random Number Generators: a statistical package that includes 15 tests and developed by the National Institute of Science of Technology. It is generally used on PRNGs but is also suitable for TRNGs since it tests the quality of the distribution of large binary sequences as well as their unpredictability [3]. This is the battery of tests that will be used to test our TRNG. Take into account that out of the 15 tests only 13 will be required since the Random Excursions and the Random Excursions Variant tests are only suitable to test

PRNGs [30]. It should be noted that for all of these tests, only if the P-value obtained is > 0.01 the sequence tested is considered random. The P-value of each test is calculated from a test statistic individual for each test. For more information see the documentation provided by the NIST. [31]

- \* Frequency Test This test focuses on the frequency in which zeroes and ones appear in the sequence being tested. In order to pass the test, the proportion of zeros and ones must be approximately equal as is expected from a sequence that is truly random. Passing this test is crucial as all the others depend on this one. To compute the test statistic it is first required that the binary numbers are converted to  $\pm 1$ . The zero values of the input sequence are converted to -1 while the ones are considered as +1. Then, they are added to produce the function:  $S_n = X_1 + X_2 + ... + X_n$  in which  $X_i = 2\epsilon_i - 1$ , where  $\epsilon_i$  is either a -1 or a +1. If  $S_n$  results in a large positive value it means that in the sequence there were far more ones than zeros and viceversa if  $S_n$  results in a large negative number.

- \* Frequency Test within a Block In this test, the frequency of ones is calculated by the proportion in which they appear in non-overlapping blocks of M-bits. Any bits that cannot fill a full block are discarded. Since the previous test stablished that the number of zeros and ones in the sequence should be approximately equal, for the sequence to pass this test, it is expected that the number of ones in the block should approximately be  $\frac{M}{2}$ , otherwise the sequence is considered non-random. In case that M = 1 the test works just like the previous monobit test. It is recommended that the sequence to be tested should at least be of 100 bits.

- \* Cumulative Sums Test This test first computes the cumulative sum, also known as a random walk, of partial sequences of the input sequence ( $\epsilon$ ). To do so, it is necessary to form a normalized sequence by turning the bits of  $\epsilon$  into  $\pm 1$  according to  $X_i = 2\epsilon_i - 1$ . Afterwards, the test determines how large or small the random walk is compared to the one expected from a random sequence. If the statistic results in a small value it means that there is a similar amount of ones

and zeros and is therefore random. Otherwise, a large value indicates that there are either too many ones or zeroes at the beginning of the sequence or at the latter stages.

- \* Runs Test A run is the name given to an uninterrupted sequence of the same bits, therefore, a run of k bits also has length k and is preceded and followed by the opposite bit value. The goal of this test is to check how many runs are there in the input sequence whether their lengths are suitable for a random sequence as well as how fast the oscillation between bits takes place. This test requires a previous calculation of the Frequency test to work, if it failed this one is not performed and its P-value is set to 0. In order to be considered random there must be a lot of changes in the sequence.

- \* Tests for the Longest-Run-of-Ones in a Block Expanding upon the previous test, the sequence is divided in blocks of M bits from which the longest run of ones will be the focus. In order to be considered a random sequence, the length of the longest run of ones should be consistent with that of a random sequence. The same could be tested taking the runs of zeroes but it is not required as if the length of the longest run of ones does not meet the criteria it implies that the same is most likely to happen with the longest run of zeroes. The test has been prepared to work at 3 different sizes of M: 8, 128 and 10<sup>4</sup> for which the minimum length of the sequence is 128, 6272 and 750000 bits respectively.

### \* Binary Matrix Rank Test

The goal of this test is to determine whether or not there exists a linear dependence among substrings of the input sequence. These substrings are organized as sub-matrices of MxQ bits and from them the rank of disjoint is calculated. The test has been configured to set M = Q = 32. The bits that cannot fill an entire matrix are discarded.

### \* Discrete Fourier Transform Test

This test detects periodicity in the form of repetitive patterns in the input sequence. This is done by calculating the Discrete Fast Fourier Transform of the sequence and checking its peak heights. The number of peaks that exceed the threshold by 95% should considerably differ from 5%.

### \* Overlapping Template Matching Test

In this test, the focus is the number of times target strings occur. It will consider the sequence as random if the number of ones of a certain length does not deviate from the number it expects from a random sequence. As in the Longest-Run test, it is not necessary to test the number of zeros since an anomaly in the number of ones also means an anomaly in the zeros. This process is done through a window of m bits that used to search an m-bit pattern throughout the whole sequence to check how often that pattern appears. The window slides by one bit whether the pattern is found or not.

### \* Non-overlapping Template Matching Test

As in the previous test, this test focuses on the number of times target strings occur. However, unlike the Overlapping Template Test, this tes only considers random those sequences that do not contain many occurrences of the pre-defined aperiodic strings. As such something very important to mention is that in this one many P-values are computed because it depends on several variables and not just the test statistic. This test works similarly to the previous one with the exception that the window only slides one bit when the pattern has not been found, otherwise, the window slides m bits or, in other words, to the next position to where the pattern was found.

### \* Maurer's "Universal Statistical" Test

In this test randomness is related to the compression of the sequence. A sequence can be compressed as long as no information is lost. If a sequence can be compressed greatly it is not random because there were many matching patterns and thus they did not add any new information. To determine this, the input sequence has to be partitioned as seen in figure 2.3 so that  $K = \frac{n}{L} - Q$  If there are any remaining bits that cannot form a L-bit block they are discarded. This test is also based in a series of pre-computed values, it should be noted that if the test statistic differed considerably from these pre-computed expected values, the P-value will not fall in the desired range. In that case,

Figure 2.3: Universal test sequence partitioning

the sequence can be compressed and thus not random.

\* Approximate Entropy Test

The goal of this test is to check the frequency of every overlapping blocks of similar lengths in the sequence, one of m bits and the other of m+1 bits.

\* Serial Test

Since a random sequence should be uniform, any of the  $2^m$  m-bit overlapping string or pattern must appear the same number of times as any other m-bit pattern. As such, this test checks if the frequency of appearance of any possible overlapping pattern of m bits throughout the entire sequence is approximately the same. If m = 1 this test operates just like the Frequency test.

\* Linear Complexity Test

This test establishes the complexity of the sequence comparing it to a LFSR. The longest the LFSR is the more complex the sequence and the better the randomness. If the length is too short the test fails. The shortest possible LFSR is computed through the Berklekamp-Massey algorithm [32].

### 2.4 FPGA Technology

Field Programmable Gate Arrays (FPGAs) are semiconductor devices that contain generic logic cells in a two dimensional array along with programmable switches forming a matrix of Configurable Logic Blocks (CLBs) whose interconnections are also programmable (see section 2.4.1 for more details). Unlike Application Specific Integrated Circuits (ASICs) devices that are designed for a specific design, the programmable capacity of FPGAs means they can be reprogrammed to run several applications with very different circuit layouts without having to re-design the application nor changing the hardware [33]. The main manufacturers of this hardware are Xilinx and Altera which have controlled the market for years. While Altera was the first of the two in producing a truly reprogramable industrial logic device in 1984, it was Xilinx who a year later released a commercial FPGA known as the XC2064 (whose name refers to its 64 CLBs). These two companies were unchallenged in the market during a decade until the mid-1990s when other companies started to become serious competitors, among these are: Microsemi, SilliconBlue Technologies, Achronix, QuickLogic, Lattice Semiconductor, Tabula, etc

Nowadays, some areas in which FPGAs are commonly used in [34] are:

- Aerospace and Defence: avionics, missiles and munition, security, space, etc.

- ASIC Prototyping: it is possible to verify an embedded system.

- Audio: with Digital Signal Processing FPGAs provide a wide range of applications in this field.

- Automotive: driver assistance systems, vehicle networking and connectivity and in-vehicle infotainment.

- Broadcast: Encoders, decoders, displays, switches and routers, Real-Time Video Engines, etc.

- **Consumer Electronics:** portable electronics, digital cameras, printers, home networking, etc.

- Data Center: storage in Servers for Cloud Computing.

- Industrial: imaging, networking, motor control, etc.

- Medical: Ultrasound, CT scanning, X-ray, etc

- Video and Image Processing: video over IP, high resolution video, digital displays, etc.

- Wired and Wireless Communications: optical networks, network processing, radio, connectivity interfaces, compatible with standards such as HSDPA and WiMax

The FPGA behaviour is programmed or described through a design in a schematic or it is written in a hardware description language (HDL), the most well know among these languages are VHDL (VH-SIC hardware description language) and Verilog although there are

18

Figure 2.4: FPGA Block Structure

newer graphical programming languages like National Intrument's LabView. For this project, as we have chosen a Xilinx Spartan-3E Board their official design suite has been used and therefore, our design is written in VHDL as it is the recommended option for this application and our target device.

Generally, before synthesizing and running an application on the FPGA hardware, circuit designs are first tested by simulating them with software programs such as Modelsim however, this is not possible for testing True Random Number Generators because it is impossible for the software to emulate the source of entropy that the TRNG requires.

### 2.4.1 FPGA Block Structure

Every model has different components that make it unique however, as seen in figure 2.4, there are some that can always be found in the block structure of a FPGA board:

• Logic Blocks. Formed by a switching matrix, flip-flops and selection circuits like multiplexers or demultiplexers. This Configurable Logic Block can have a synchronous or asynchronous output thanks to these components and moreover, it is always accompanied by several I/O pads as well as flexible interconnection routes between them and other blocks of the board. To reduce design complexity the routing is an automatic task generally hidden from the designer of FPGA applications however this may cause a wrong use of the FPGA resources and take more routing tracks than the design might actually need.

Figure 2.5: Spartan-3E

- Memories. FPGA designs can have on-chip memory as most boards contain some sort of Embedded Block RAM (BRAM) memory that can also work in a dual-port operation with diferent clocks.

- Clocking. Many components will require a synchronous clock signal for them to work therefore a Digital Clock Manager (DCM) will always be present alongside with routing dedicated exclusively to clock and reset signals all throughout the board as well as clock frequency synthetization through analog PLLs or DLLs and sometimes even a Digital Signal Processor (DSP). A DCM can manipulate clock signals by eliminating their skew, adding a different phase shift, multiplying or diving the signal, etc.

### 2.4.2 Xilinx Spartan-3E

This project uses a board from the Xilinx Spartan-3E family devices which is an improvement over the previous successful Spartan-3 family. This is done by improving the configuration costs and system performance since the amount of I/O pads per logic cell is higher. Moreover, it comes with newer, cheaper and more advanced 90nanometer technologies which not only allow for more bandwidth

Figure 2.6: Spartan-3E Family Architecture

but also many functionalities that make them ideal for their use in consumer electronics such as home networking with broadband access and digital displays for television. [35]

There are five main programmable types of elements in this family of FPGAs, their distribution in a device are as shown in figure 2.6:

- **CLBs:** store data in latches and flip-flops as well as implement the logic of the circuit.

- I/O Blocks: manage the data transmitted and received bidirectionally in between I/O pins and the rest of the device.

- Block RAM: stores data in dual-port blocks of 18Kb. Each BRAM has their dedicated multiplier.

- Multiplier Blocks: can calculate the product of two binary numbers of 18 bits.

- **DCM Blocks:** to digitally self-calibrate clock signals. It is possible to multiply, divide, delay, phase-shift and distributing the signal.

The board that has been used in this project, the Xilinx Spartan-3E Starter Board (see figure 2.5), also has as some its main features [36]:

• 232 I/O pins

- A Xilinx 4Mbit PROM

- Parallel 16MB NOR Flash configuration

- 16Mbit SPI serial Flash configuration

- MicroBlaze<sup>TM</sup>32-bit embedded RISC processor

- $\bullet$  PicoBlaze  $^{\rm TM}8\text{-bit}$  embedded controller

- 64MB DDR SRAM interfaces.

## 2.5 Implementing TRNGs on FPGAs

As mentioned in section 2.4, when designing a solution for integrated circuits it is important to take into account that the resources they provide are limited. In spite of this, there are several ways to implement TRNG on FPGA technology. These can be presented according to the method employed to extract randomness or their source of entropy.

- 1. Metastability. As seen in section 2.3.1, it refers to the ability of a circuit to endure an unstable state during a prolonged time. FPGAs are designed to avoid situations that can produce metastability which makes it difficult to use this mechanism. However, a couple of solutions employing metastability have been implemented on FPGAs, the most well-known is the one designed by Vasyltsov et al. [37] As presented in figure 2.7, it is a ring oscillator (RO) formed by inverters whose output is connected to their input by a multiplexer that acts as a switch. The state of those switches determines if the circuit works in entropy accumulation mode (metastability) or in oscillating mode. When the inverters are disconnected from each other metastability occurs and the output voltage fluctuates. Therefore, when they are connected again the state of the ring oscillator depends on the entropy created in each inverter.

- 2. **Open Delay Chain.** Through a chain of delay elements an n-bit signal is obtained by using D-latches in the LUTs. Afterwards, it is XOR-ed to produce a random bit. There are two advantages to this method: first, it is possible to produce high rates of data at the maximum clock frequency and second, it is a simple structure without the need of PLLs or ROs.

Figure 2.7: Vasyltsov et al. TRNG

- 3. Chaos. Obtaining randomness from a chaotic event is only possible through an analog device. Most FPGAs lack such technology but certain models have several analog blocks or peripherals. However, these cannot produce the chaotic behavior required for a TRNG. Although it is possible to produce this behavior through an Analog to Digital converter which is only a matter of time until FPGAs are manufactured with one.

- 4. Use of SRAM Memories. There are two methods to make use of the SRAM in an FPGA to generate random numbers: first, through the start-up state of the SRAM that generates non-deterministic noise [38] and second, by the *write collisions* method which consist of trying to write opposite values at the same time which results in a process similar to metastability [39].

- 5. Jittery Clock Sampling. The deviation from ideal behavior of a signal or jitter has been proven to be the best method for FPGAs since the possible implementations are technology independent and require components that can be found in any type of FPGA. The jittery signals are composed of thermal noise and flicker noise. The former results in the non-deterministic behavior while the latter adds a deterministic behavior dependent of the technology on which the TRNG is implemented. The two techniques of using jitter are:

- Coherent Sampling. This method employs two or more clocks with output frequencies or phases that are related. One of the clock signal samples the others in the edges but since none of them are ideal the result will be a random sequence. There are two well-known implementations of this principle: Fischer and Drutarovsky's [40] and Kohlbrenner and Gaj's [41]. In the former, PLLs are used to generate the jittery clock signals, no post-processing is required

Figure 2.8: Sunar et al. TRNG

and the output bit rate, while considerably low, is constant. However, many FPGA families do not contain PLLs and therefore this TRNG cannot be implemented in them. Kohlbrenner and Gaj solve this problem by replacing the PLLs by ROs that can be implemented in all FPGAs. The frequencies of the oscillators must be very similar but not the same in order to obtain the desired random sequence which will have a very long period.

Jittery Clock Signals. This method uses a synchronous or asynchronous D flip-flop (DFF) to sample the high frequency signals generated by oscillators. A reference clock (generally obtained from a quartz oscillator) is used to obtain the sampling frequency. This technique was originally coined by Sunar et al. (see figure 2.8) [42] who samples several ROs at the same time. Their outputs are XOR-ed to obtain a high-frequency random signal which is sampled by the DFF. Afterwards a resilient function is used as post-processing that makes the output bit-rate constant. This implementation, however, has two disadvantages: not only the power consumed by this TRNG is substantial since many ROs are required to oscillate simultaneously and continuously but also the XOR and the DFF are not capable of handling all the transitions. A solution to this problem is proposed in [43] and can be seen in figure 2.9. It consists of putting a DFF after each RO. Moreover, it claims that by doing this the post-processing would become unnecessary and the number of ROs can be reduced. It has been argued however that the behavior it produces is not true randomness but pseudo-randomness. Another

Figure 2.9: Wold et al. TRNG

improvement to this was proposed in [44] where instead of ROs, Self-Timed Rings are used.

In this project, a jittery clock has been used as entropy source. It has just been stated above that this can be implemented by using ROs or STRs, therefore an explanation of both is in order.

- Ring Oscillators: consist of a chain of an odd number of elements connected in a feedback loop to form a ring. These elements are either inverters as seen in figure 2.10 or an initial inverter and delay elements. They are widely used in ASICs and FPGAs in jittery clock sampling due to their many useful features [45]:

- They are easy to design in integrated circuit technology.

- High frequency oscillations with dissipating low power are achieved at a low voltage.

- Their frequency of oscillation can be tuned with a wide range of possibilities.

- It is possible to obtain a multiphase output.

The frequency of oscillation depends on the number of delay elements and the propagation delay they produce. A selfsustained oscillator must have a  $2\pi$  phase shift. For a RO of nelements to achieve this, if each element adds a  $\frac{\pi}{n}$  phase shift and a propagation delay of  $\tau_d$  (its actual value depends on the parameters of the circuit), the RO completes a first revolution in a time of  $n\tau_d$  with a phase shift of  $\pi$ . Another revolution

Figure 2.10: Ring Oscillator basic stucture

Figure 2.11: Self-Timed Ring basic stucture

is required to reach the  $2\pi$  phase and thus the time period of the whole process becomes  $2n\tau_d$ . Therefore, the frequency of oscillation on an RO is  $f_o = \frac{1}{2n\tau_d}$ .

• Self-Timed Rings: are a handshake protocol that controls a sequence of events by distributing them through different adjacent stages (each consisting of a Muller C-element and an inverter) forming a micropipeline FIFO as can be seen in figure 2.11. The clocks of synchronous designs are replaced by these handshakes and therefore the oscillator is highly configurable allowing to choose phase and frequency between signals. The jitter does not depend on the length of the ring but on the one that each stage generates [46].