#### A Thesis Submitted for the Degree of PhD at the University of Warwick

Permanent WRAP URL: <a href="http://wrap.warwick.ac.uk/86733">http://wrap.warwick.ac.uk/86733</a>

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright. Please scroll down to view the document itself. Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: <a href="mailto:wrap@warwick.ac.uk">wrap@warwick.ac.uk</a>

# Finite Element Electrothermal Modelling and Characterization of Single and Parallel Connected Power Devices

### Ji Hu

A thesis Submitted to the University of Warwick

in partial fulfilment of the requirements for the degree of

## **Doctor of Philosophy**

School of Engineering

©September 2016

## **Table of Contents**

| List of Tables   |                                                    | V            |

|------------------|----------------------------------------------------|--------------|

| List of Figures. |                                                    | vi           |

| Acknowledgem     | ents                                               | xvi          |

| Declaration      |                                                    | xvii         |

| List of Publicat | ions                                               | xviii        |

| Abstract         |                                                    | XX           |

|                  |                                                    |              |

|                  |                                                    |              |

| -                | oduction                                           |              |

|                  | round                                              |              |

| 1.2 A Brie       | ef History of Power Electronics                    | 5            |

| 1.3 Resea        | rch Objectives and Contribution                    | 6            |

| 1.4 Outlin       | e of Thesis                                        | 9            |

| Chapter 2. Pow   | er device modelling                                | 11           |

| 2.1 Introd       | uction to Modelling of Power Semiconductor Devices | 11           |

| 2.1.1            | Compact Device Models                              | 12           |

| 2.1.2            | Numerical models                                   | 13           |

| 2.2 Comp         | act Models for Power Semiconductor devices         | 14           |

| 2.3 Transi       | ent Thermal Impedance Characteristics and Thermal  | Modelling of |

| Power            | · devices                                          |              |

| 2.3.1            | Thermal network in finite element modelling        | 35           |

| 2.4 Finite       | Element Modelling of Power Semiconductor Devices   |              |

| 2.4.1            | Continuity equation                                |              |

| 2.4.2            | The Transport Equations                            |              |

| 2.4.3            | Drift-diffusion Transport Model                    |              |

| 2.4.4            | Poission's Equation                                |              |

| 2.4.5            | Carrier Generation-recombination models            |              |

| 2.4.6            | Mobility models                                    | 44           |

|                  |                                                    |              |

| 2.4.7           | Impact ionization models                                           |           |

|-----------------|--------------------------------------------------------------------|-----------|

| 2.4.8           | Heat flow equations in semiconductors                              |           |

| 2.4.9           | Contact model                                                      |           |

| 2.5 Finite      | Element Modelling of Power Devices                                 |           |

| 2.5.1           | Clamped Inductive Switching Circuit                                |           |

| 2.5.2           | PiN Rectifier                                                      |           |

| 2.5.3           | SiC Schottky diodes                                                |           |

| 2.5.4           | Avalanche Ruggedness under Unclamped Inductive Switchi             | ng 58     |

| 2.5.5           | Unclamped Inductive Switching of CoolMOS Device                    |           |

| Chapter 3. Anal | ysis of Electrothermal Balance in SiC Schottky and PiN D           | iodes68   |

| 3.0 Introdu     | uction                                                             |           |

| 3.1 The ex      | perimental set-up                                                  | 73        |

| 3.2 Silicor     | n PiN diodes and SiC Schottky diodes under Clamped                 | Inductive |

| Switch          | ing Measurements                                                   | 76        |

| a. Silico       | on PiN diodes in CIS measurements                                  | 76        |

| b. SiC S        | Schottky diode in CIS measurement                                  |           |

| c. Com          | parisons of Thermal Transients in Silicon PiN and SiC Schottl      | ky Diodes |

| under R         | Repetitive Clamped Switching                                       |           |

| 3.3 Electro     | othermal Balance in Parallel Connected Diodes                      |           |

| a. Temp         | perature Imbalance                                                 |           |

| b. Dyna         | amic behaviour evaluation                                          |           |

| 3.4 Electro     | othermal evaluation of Silicon PiN and SiC Schottky Dio            | des under |

| Unclar          | nped Inductive Switching                                           |           |

| 3.5 UIS m       | easurements and Simulations for Parallel Connected Diodes          |           |

| a. UIS 1        | measurements on parallel Silicon PiN diodes                        |           |

| b. UIS          | measurements on parallel SiC Schottky diodes                       | 96        |

| c. Avala        | anche Ruggedness of the Parallel Pairs with different $\Delta T_J$ |           |

| d. Finite       | e Element Modelling                                                |           |

| 3.6 Conclu      | usion                                                              |           |

| Chapter 4. Mod  | elling and Experimental Characterization of Parallel Con           | nected    |

| Power Do        | evices under Clamped Inductive Switching                           |           |

| 4.0 Introdu     | action                                                             |           |

| 4.1 Experimental Set-up111                                                          |

|-------------------------------------------------------------------------------------|

| 4.2 The Impact of Switching Rate Mismatch                                           |

| 4.3 Finite Element Simulations of Switching Rate Mismatch between Parallel          |

| DUTs                                                                                |

| 4.4 Impact of Initial Junction Temperature Mismatch128                              |

| 4.5 Finite Element Simulations of Initial Junction Temperature Mismatch132          |

| 4.6 Impact of Temperature Variations on Parallel Connected NPT IGBTs 136            |

| 4.7 Impact of Switching Rate Variations on Parallel Connected NPT IGBTs141          |

| 4.8 Impact of Variations in Case-to-Ambient Thermal Resistances and                 |

| Capacitances (Different Heatsink Thermal Transients)                                |

| 4.9 Conclusions                                                                     |

| 4.10 Implications for Power Electronic Applications                                 |

| Chapter 5. Electrothermal ruggedness of parallel connected sic mosfet and coolmos   |

|                                                                                     |

|                                                                                     |

| 5.1 Introduction                                                                    |

| 5.2 Electrothermal Ruggedness of Power MOSFETs under Unclamped Inductive            |

| Switching                                                                           |

| 5.3 Experimental Test-Rig                                                           |

| 5.4 Compact Model Estimation for Junction Temperature of Power MOSFETs<br>under UIS |

| 5.5 Finite Element Simulation of UIS in Parallel Connected DUTs                     |

| 5.6 Unclamped Inductive Switching Measurements on Parallel Connected DUTs           |

| (Impact of Junction Temperature Variation).                                         |

| 5.7 Finite Element Simulation of UIS in Parallel Connected DUTs (Impact of          |

| Junction Temperature Variation)181                                                  |

| 5.8 Impact of Variation in Switching Rates between the Parallel DUTs on             |

| Avalanche Ruggedness                                                                |

| 5.9 Finite Element Simulations of the Impact of Different Switching Rates 194       |

| 5.10 Conclusions                                                                    |

| 5.11 Implications for Power Electronic Applications                                 |

| Chapter 6. Conclusions and future work                                              |

| 6.1 Conclusions                                                                     |

| 0.1 Conclusions                                                                     |

| Refer | rences                                                        | 211                  |

|-------|---------------------------------------------------------------|----------------------|

|       | 6.3 Future Work                                               |                      |

|       | Electronic Devices                                            |                      |

|       | 6.2 Implications of the Thesis Findings for The Industrial Ap | pplications of Power |

## **List of Tables**

| Table 2-1: Loss classification and corresponding equations                                  |

|---------------------------------------------------------------------------------------------|

| Table 2-2: The value of the thermal resistance and thermal capacitance in the matched       |

| foster network                                                                              |

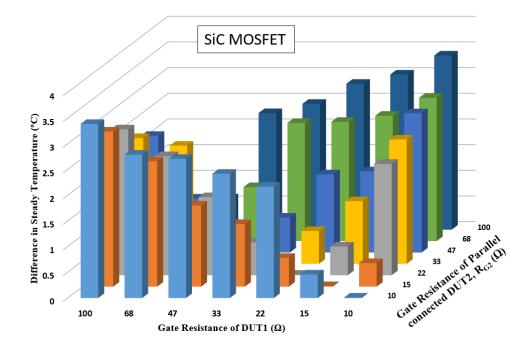

| Table 4-1: Temperature Rise look up table for parallel-connected SiC MOSFETs                |

| switched with different gate resistance                                                     |

| Table 4-2: Temperature Rise look up table for parallel-connected CoolMOS devices            |

| switched with different gate resistance                                                     |

| Table 4-3: Parameters of the simulated finite element model                                 |

| Table 5-1: The intrinsic carrier concentration as a function of temperature for silicon and |

| SiC163                                                                                      |

| Table g-1: Gate driver board truth table                                                    |

# **List of Figures**

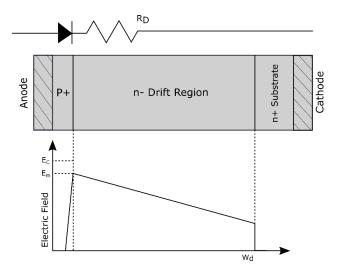

| Figure 2.1: The electric field distribution of the PiN diode14                                |

|-----------------------------------------------------------------------------------------------|

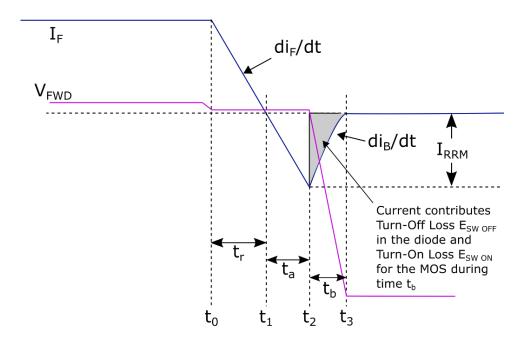

| Figure 2.2: The reverse recovery characterize waveform for the PiN diode                      |

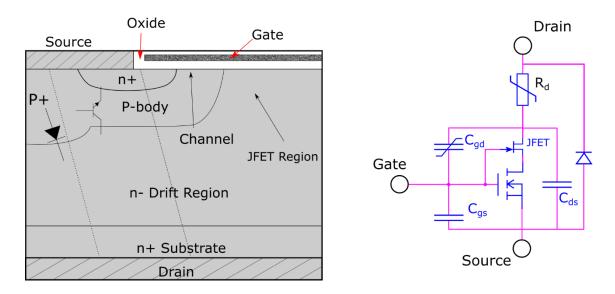

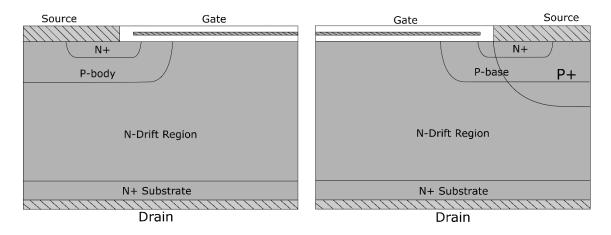

| Figure 2.3: Vertical Diffusion MOSFET structure                                               |

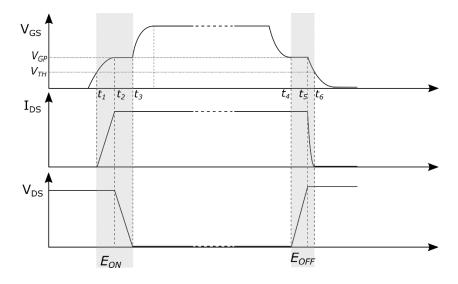

| Figure 2.4: Switching characteristic waveforms for the MOSFET with clamped inductive          |

| load24                                                                                        |

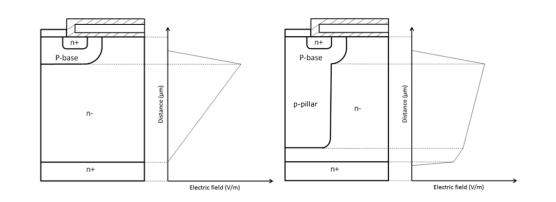

| Figure 2.5: A Comparison of electric field distribution for the MOSFET and CoolMOS            |

|                                                                                               |

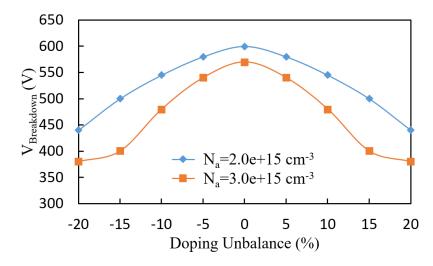

| Figure 2.6: The breakdown voltage as a function of doping balance for CoolMOS26               |

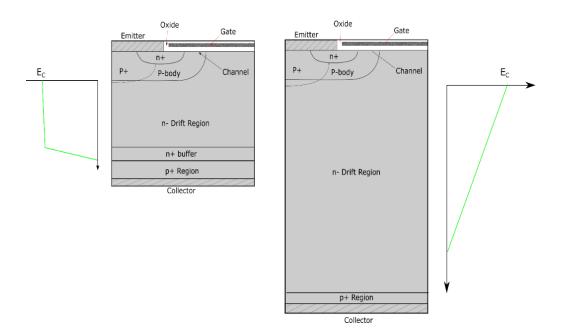

| Figure 2.7: PT and NPT IGBT structure27                                                       |

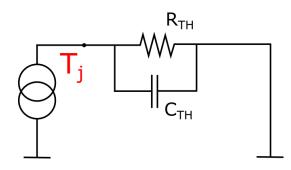

| Figure 2.8: The schematic of thermal equivalent elements                                      |

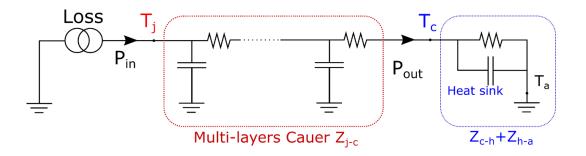

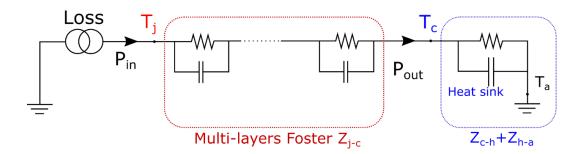

| Figure 2.9(a): The Cauer thermal network schematic                                            |

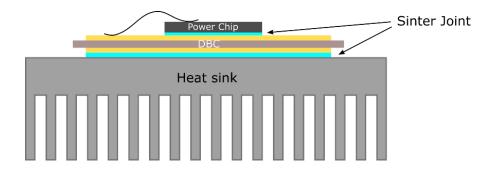

| Figure 2.10: The thermal model of device in FEM model                                         |

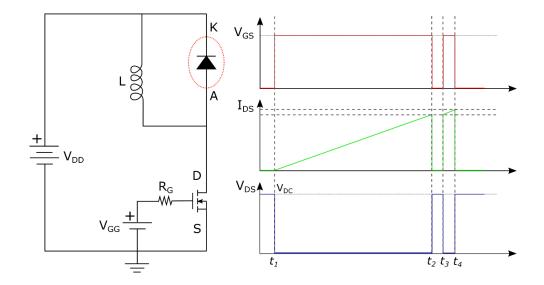

| Figure 2.11: The schematic of clamped inductive switching circuit and waveforms48             |

| Figure 2.12: (a) the 2-D structure plot for the PiN diode and (b) Electric field distribution |

| at breakdown voltage                                                                          |

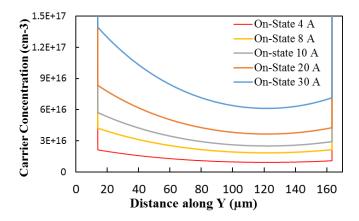

| Figure 2.13: The carrier distribution for different on-state current density                  |

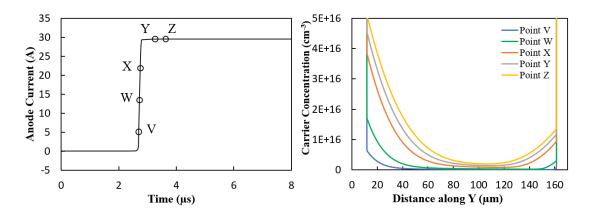

| Figure 2.14: (a) The turn-On current transient waveform for the PiN diode. (b) The carried    |

| distribution in the drift region corresponding to point V to Z in 2.14(a)51                   |

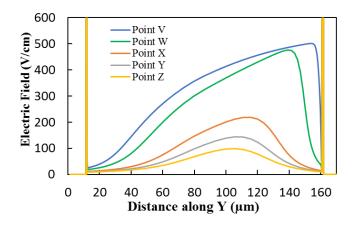

| Figure 2.15: The electric field distribution in the drift region corresponding to point V to  |

| Z in Figure 2.14(a)                                                                           |

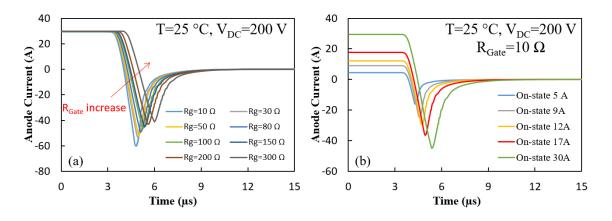

| Figure 2.16: Diode reverser recovery waveform as a function of (a) switching rate and (b)     |

| forward current rating                                                                        |

| Figure 2.17: Diode reverser recovery waveform as a function of temperature and supply         |

| voltage                                                                                       |

| Figure 2.18: (a) Simulated Reverse recovery waveform for the PiN diode. (b) The carrier       |

| distribution within the drift region for the PiN diode corresponding to point A, B, C, D      |

| and E                                                                                         |

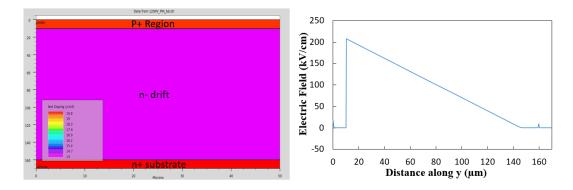

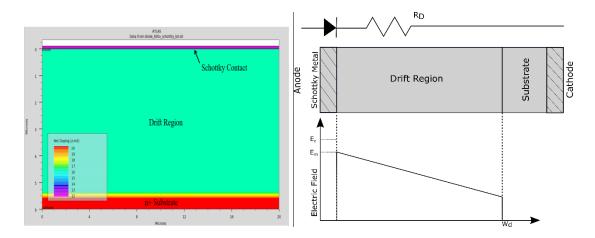

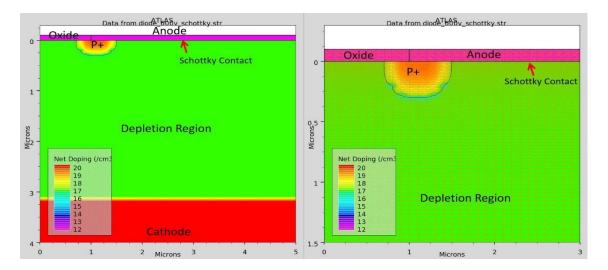

| Figure 2.19: (a) The SiC Schottky diode model rated at 600V. (b) The electric field           |

| distribution at its breakdown voltage55                                                       |

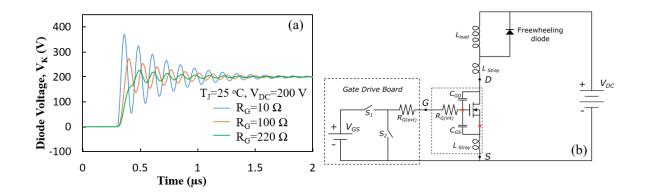

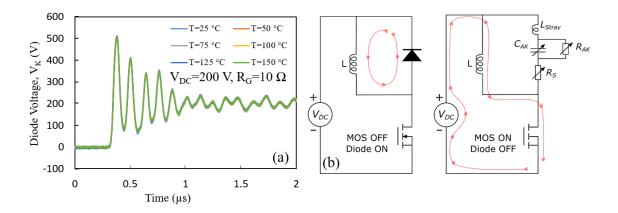

| Figure 2.20: The (a) simulated turn-Off voltage and (b) simulation circuit                    |

| Figure 2.21: The (a) measured turn-Off voltage for the SiC SBD and (b) equivalent circuit     |

|                                                                                               |

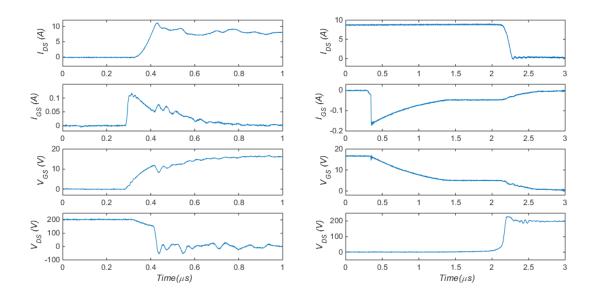

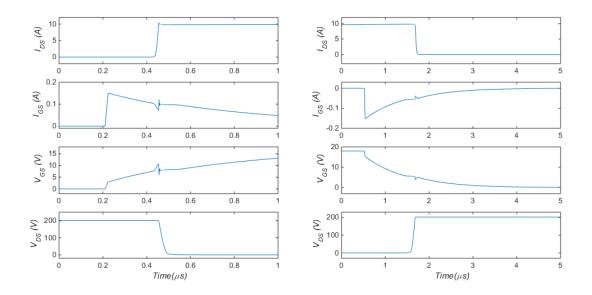

| Figure 2.22: The measured (a) turn-On and (b) turn-Off transient characteristics for the       |

|------------------------------------------------------------------------------------------------|

| SiC MOSFET                                                                                     |

| Figure 2.23: The simulated (a) turn-On and (b) turn-Off transient characteristics for the      |

| SiC MOSFET                                                                                     |

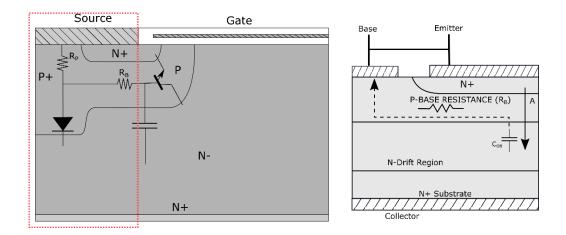

| Figure 2.24: Shorted base-emitter BJT within the VD-MOSFET structure                           |

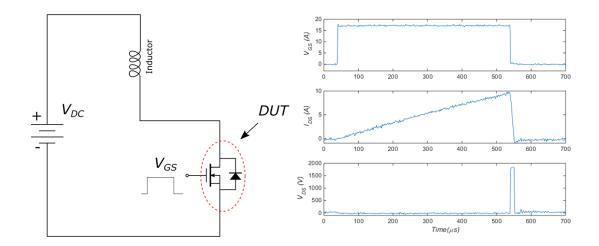

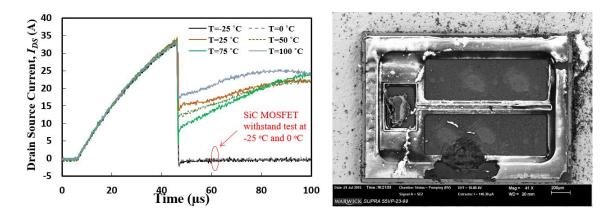

| Figure 2.25: UIS test rig and avalanche measurements on a SiC Power MOSFET60                   |

| Figure 2.26: (a) UIS Measurements for a SiC Power MOSFET at different temperatures.            |

| (b) Picture of the device after BJT latch-up61                                                 |

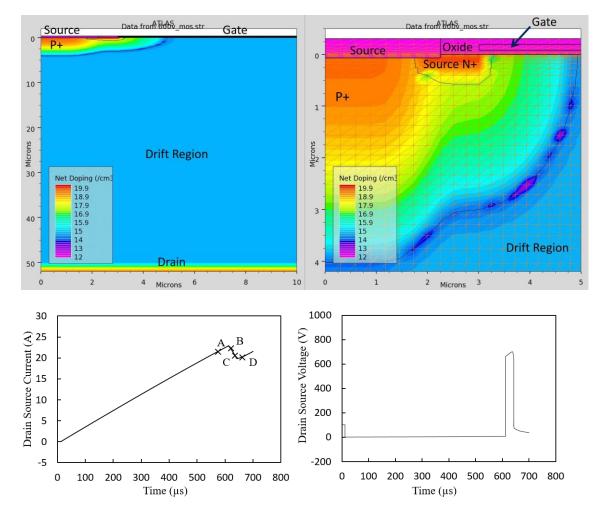

| Figure 2.27: (a) The layout of the simulated 600V silicon MOSFET, (b) the simulated            |

| avalanche current for the SiC MOSFET which failed in UIS and (c) Corresponding drain           |

| voltage characteristics                                                                        |

| Figure 2.28: Simulated (a) Avalanche Power and (b) Highest Lattice Temperature of the          |

| Power MOSFET under UIS63                                                                       |

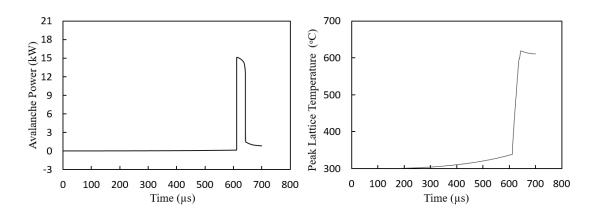

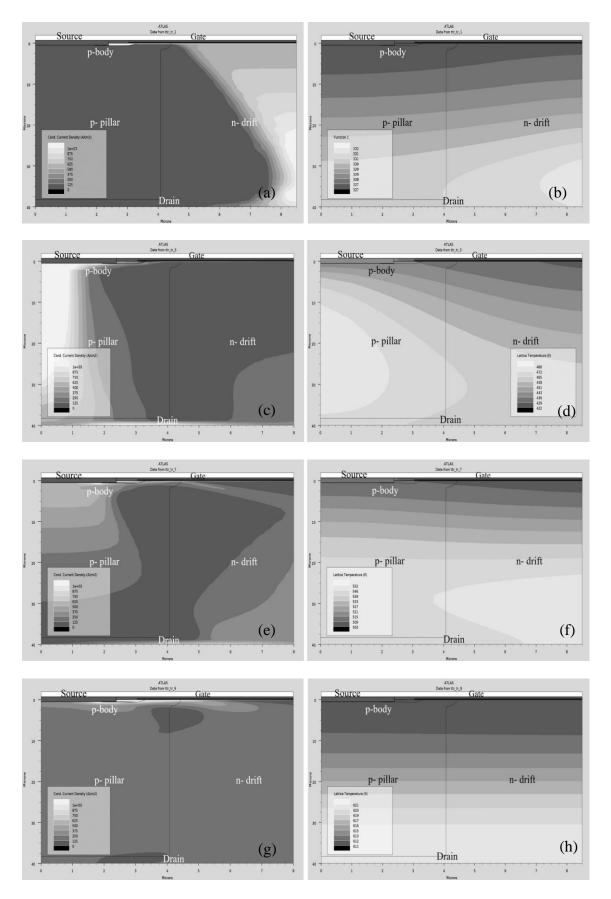

| Figure 2.29: The simulated 2-D current density contour plot for the 600V silicon               |

| MOSFET corresponding to point A, B, C and D in Figure 2.27(b)64                                |

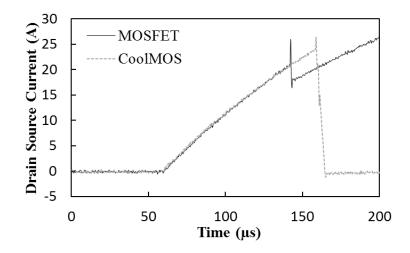

| Figure 2.30: The measured UIS waveform for the CoolMOS and conventional MOSFET                 |

| at room temperature                                                                            |

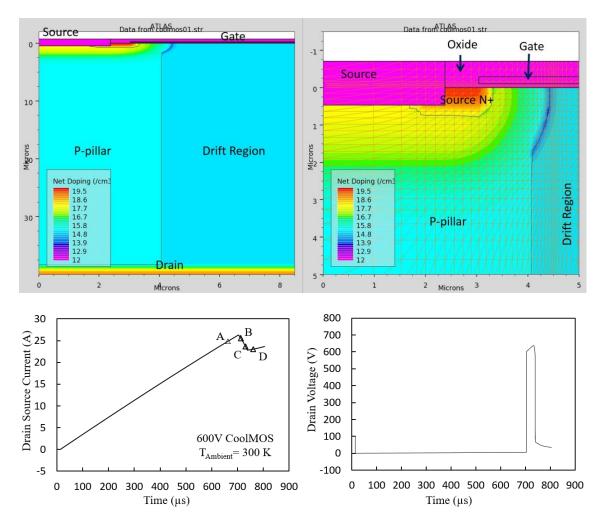

| Figure 2.31: (a) The layout of the simulated 600 V silicon CoolMOS device, (b) the             |

| simulated avalanche current and (c) voltage characteristics of the CoolMOS device66            |

| Figure 2.32: The simulated avalanche characteristic for the CoolMOS under in UIS               |

| corresponding to point A, B, C and D in Figure 2.31(b)67                                       |

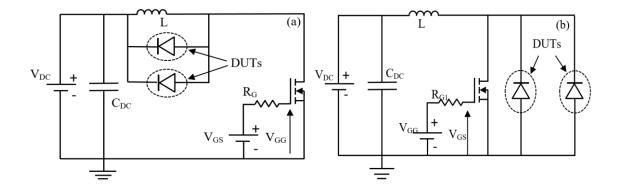

| Figure 3.1: (a) the clamped inductive switching schematic and (b) unclamped inductive          |

| switching schematic74                                                                          |

| Figure 3.2: The measured (a) turn-ON and (b) turn-OFF transient waveform of power PiN          |

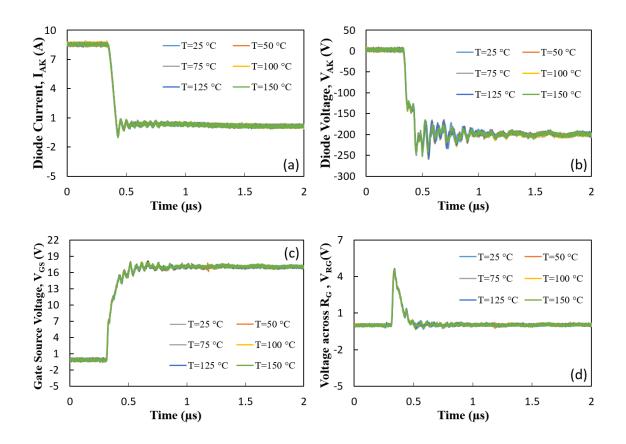

| diode in a clamped inductive switching measurement77                                           |

| Figure 3.3: The measured turn-OFF transient waveform of Silicon PiN diode showing the          |

| Transient Characteristics of the (a) $I_{AK}$ , (b) $V_{AK}$ , (c) $V_{GS}$ and (d) $I_{G}$ 78 |

| Figure 3.4: The measured (a) turn-ON and (b) turn-OFF transient waveforms of SiC               |

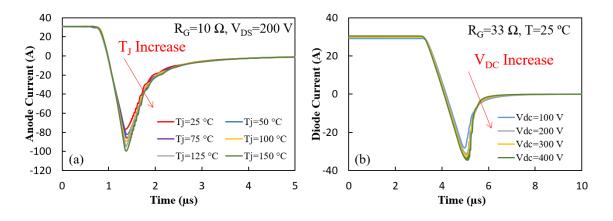

| Schottky diode in clamped inductive switching measurement80                                    |

| Figure 3.5: The measured turn-OFF transient waveform of the SiC Schottky diode                 |

| showing (a) $I_{AK}$ , (b) $V_{AK}$ , (c) $V_{GS}$ and (d) $I_G$                               |

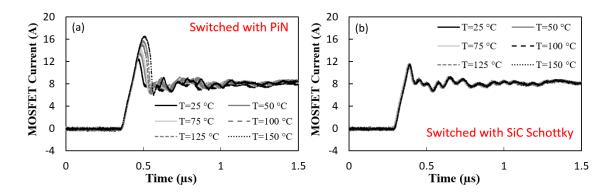

| Figure 3.6: The measured turn-on waveform of the driver MOSFET switched with (a)               |

| PiN diode operating at different temperatures. (b) Similar measurement for the MOSFET          |

| switched with SiC Schottky diode                                                               |

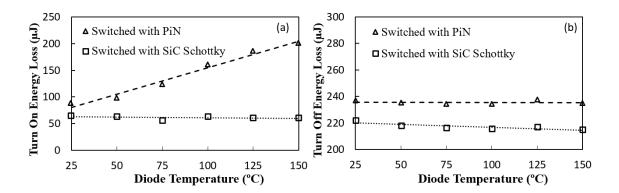

| Figure 3.7: The measured (a) turn-on and (b) turn-off switching energy of the MOSFET               |

|----------------------------------------------------------------------------------------------------|

| as a function of diode operation temperature                                                       |

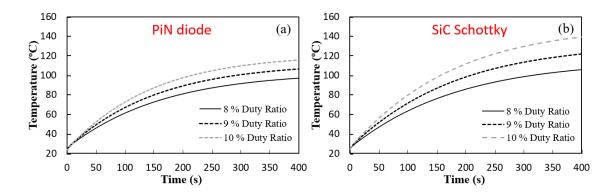

| Figure 3.8: The measured case temperature rise for the (a) PiN diode switched with                 |

| different duty ratios. (b) Similar measurement for the SiC Schottky diodes83                       |

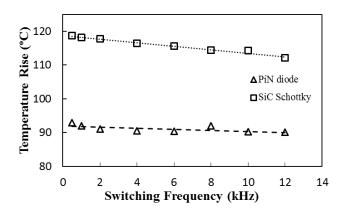

| Figure 3.9: The case temperature rise as a function of switching frequency for both the            |

| silicon PiN and SiC Schottky diodes                                                                |

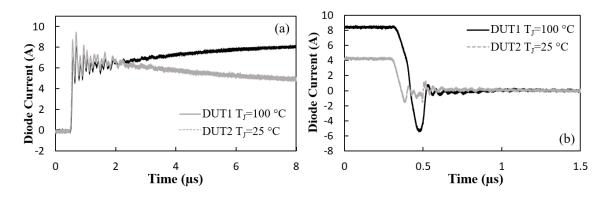

| Figure 3.10: The measured (a) turn-ON and (b) turn-OFF current waveforms of parallel               |

| connected PiN diodes with junction temperatures of 25 °C and 100 °C85                              |

| Figure 3.11: The measured (a) turn on and (b) turn off current waveform of the parallel            |

| connected SiC Schottky diodes with junction temperatures of 25 $^\circ C$ and 100 $^\circ C$       |

| respectively                                                                                       |

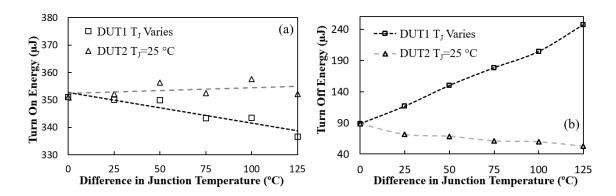

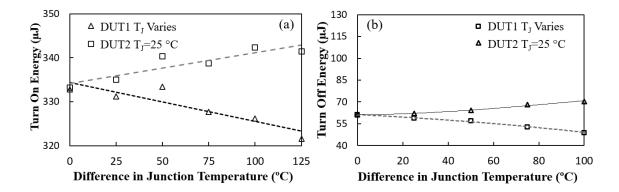

| Figure 3.12: The measured (a) turn-ON and (b) turn-OFF switching energies of the                   |

| parallel connected PiN diodes as a function of the difference in junction temperature87            |

| Figure 3.13: The measured (a) turn-ON and (b) turn-OFF switching energies of the                   |

| parallel-connected SiC Schottky diodes as a function of the difference in junction                 |

| temperature                                                                                        |

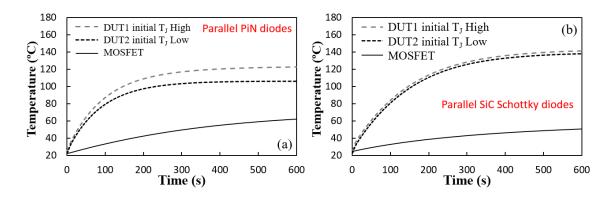

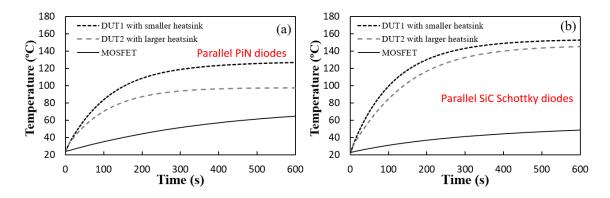

| Figure 3.14: The measured case temperature rise for the (a) parallel-connected PiN diodes          |

| switched with same heatsink but with 3 $^{\circ}$ C difference in initial temperature. (b) Similar |

| measurement for the parallel connected SiC Schottky diodes                                         |

| Figure 3.15: The measured case temperature rise for the (a) parallel-connected PiN diodes          |

| switched with different size heatsinks. (b) Similar measurement for the parallel connected         |

| SiC Schottky diodes                                                                                |

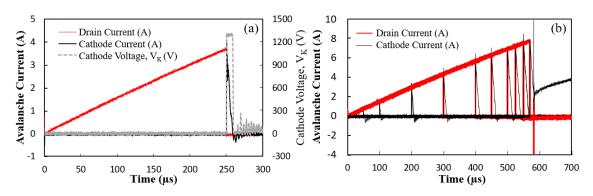

| Figure 3.16: (a) UIS characteristics of a 600 V SiC Schottky diode and (b) UIS test with           |

| different pulse width91                                                                            |

| Figure 3.17: UIS Current waveform of (a) PiN diode and (b) SiC Schottky diode failure              |

| under avalanche mode conduction                                                                    |

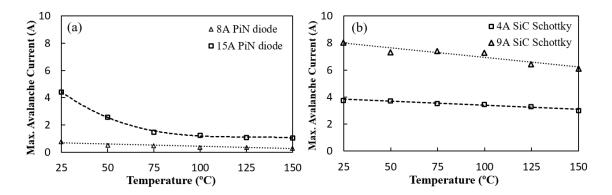

| Figure 3.18: The maximum avalanche current for different current rated (a) PiN diodes              |

| and (b) SiC Schottky diodes at different junction temperatures                                     |

| Figure 3.19: (a) The measured peak avalanche current and (b) calculated avalanche                  |

| energy for the 4A SiC Schottky diode as a function of junction temperature for different           |

| avalanche durations                                                                                |

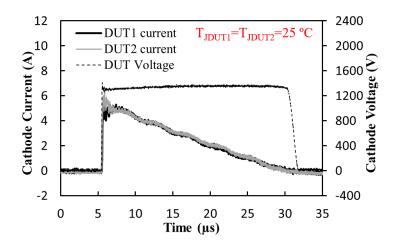

| Figure 3.20: Avalanche current characteristics for the parallel SiC Schottky diodes with           |

| equal junction temperatures between the DUTs (T <sub>J1</sub> =T <sub>J2</sub> =25 °C)94           |

|                                                                                                    |

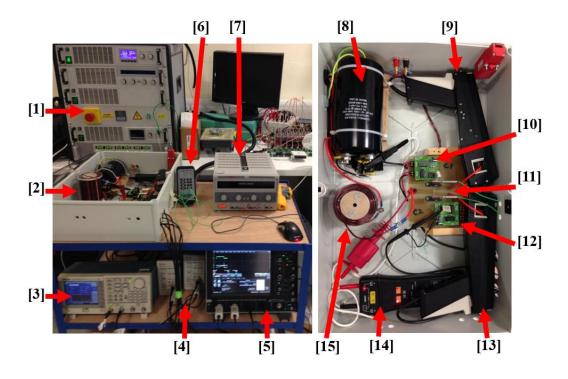

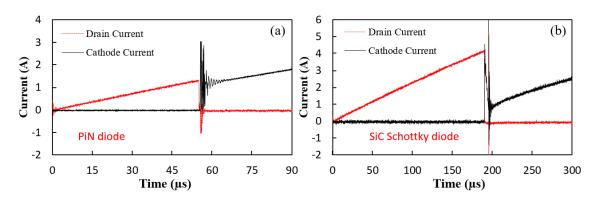

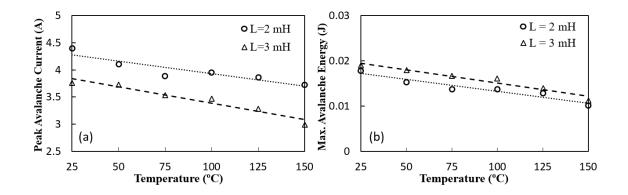

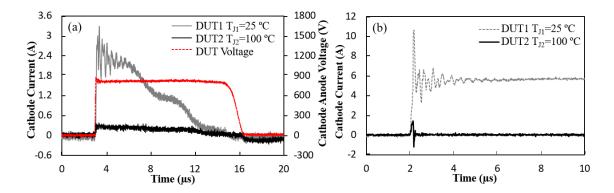

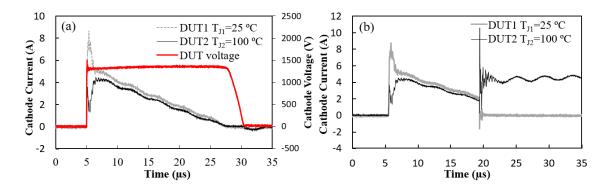

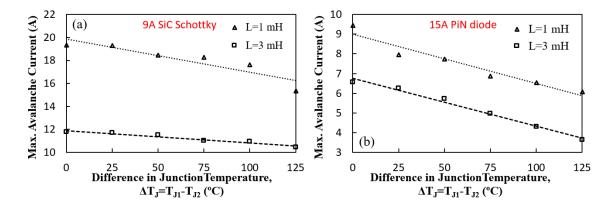

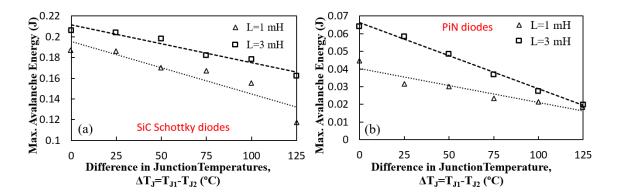

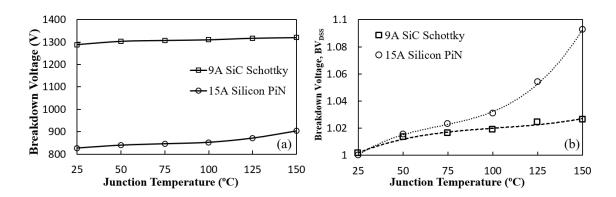

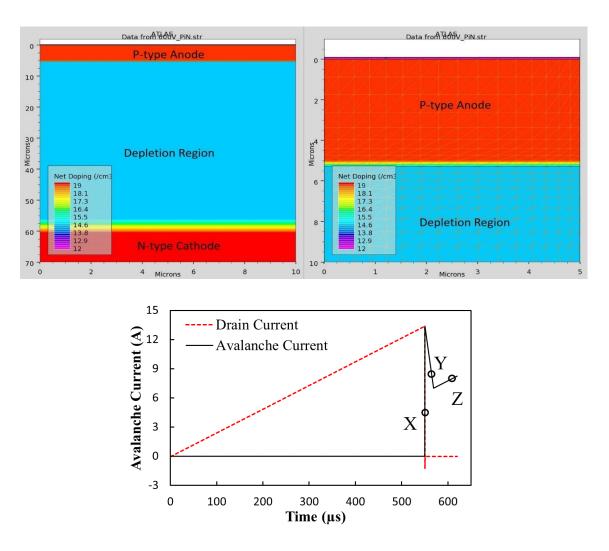

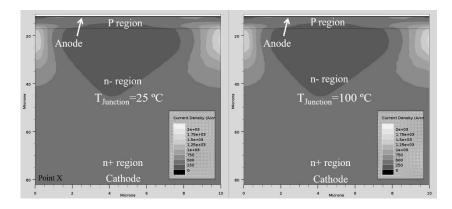

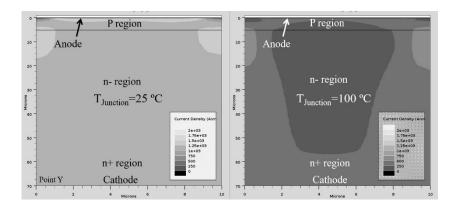

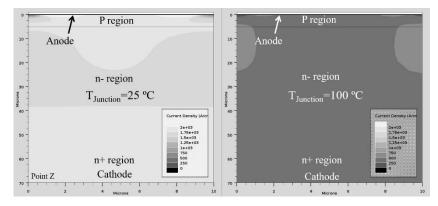

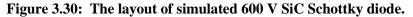

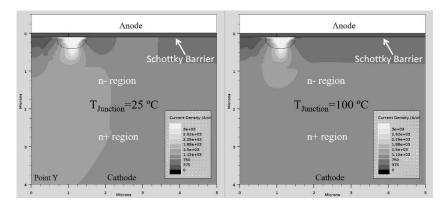

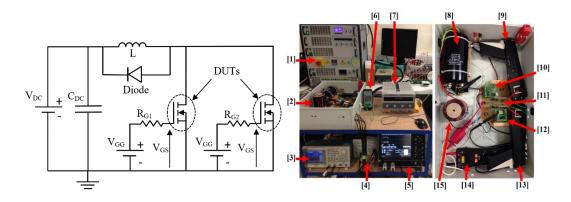

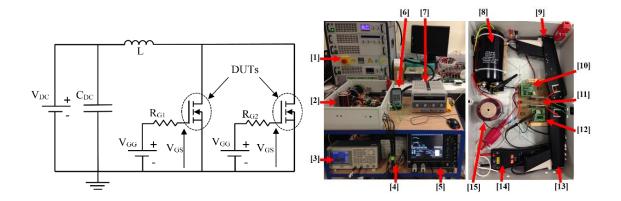

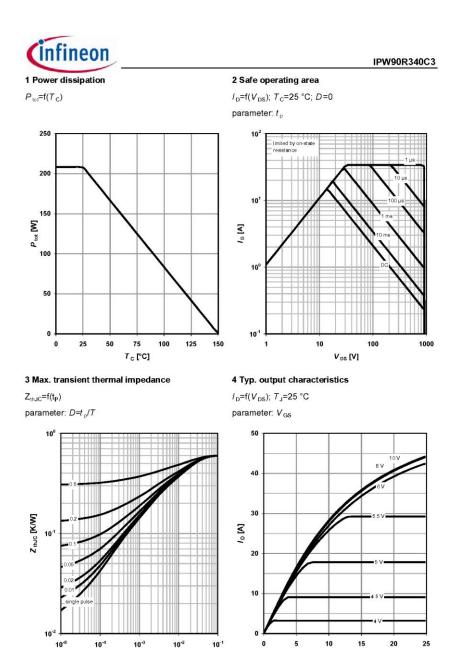

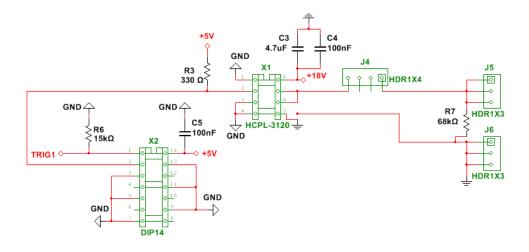

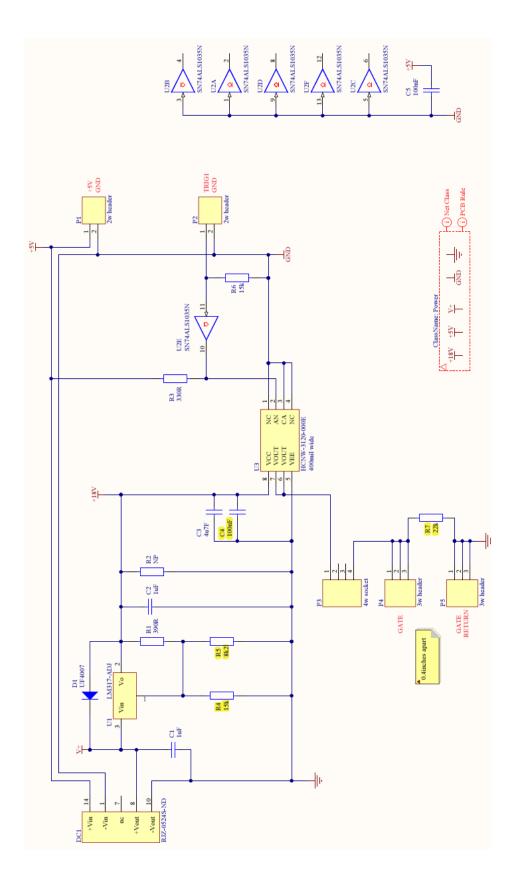

Figure 3.21: (a) Avalanche current waveforms for the parallel PiN diodes with different junction temperatures showing (a) no thermal runaway at 3 A peak current (b) thermal Figure 3.22: (a) Avalanche current waveforms for the parallel SiC Schottky diodes with different junction temperatures showing (a) no thermal runaway at 8 A peak current (b) Figure 3.23: The peak avalanche current as a function of temperature difference between the parallel connected (a) silicon PiN diodes and (b) SiC Schottky diodes for two inductor Figure 3.24: The measured avalanche energy dissipated in the (a) SiC parallel Schottky pairs and (b) Silicon PiN diode pairs as a function of temperature difference between the Figure 3.25: (a) The measured breakdown voltages of the silicon PiN and SiC Schottky diodes as functions of temperature (b) Normalised breakdown voltages. .....101 Figure 3.26: (a) The layout of the simulated 600 V silicon PiN diode, and (b) the simulated avalanche current for the parallel connected PiN diodes with different junction temperatures......102 Figure 3.27: 2-D current density plots for parallel connected PiN diodes with different Figure 3.28: 2-D current density plots for parallel connected PiN diodes with different junction temperature under UIS. This corresponds to point Y in Figure 3.26.....103 Figure 3.29: 2-D current density plots for parallel connected PiN diodes with different junction temperature under UIS. This corresponds to point Z in Figure 3.26 where the Figure 3.31: 2-D current density plots for parallel SiC Schottky diodes with different junction temperature under UIS. This corresponds to point Y in Figure 3.26.....105 Figure 3.32: 2-D current density plots for parallel SiC Schottky diodes with different junction temperature under UIS. This corresponds to point Z in Figure 3.26 where the Figure 4.1: (a) Circuit schematic for the experimental set-up. (b) shows the picture of the experimental set-up with [1] Power Supply. [2] Test Chamber. [3] Function Generator. [4] Current probe Amplifier. [5] Oscilloscope. [6] Thermometer. [7] DC power supply for heater. [8] DC capacitor. [9] and [13] Current Probes. [10] and [12] Gate Drives. [11]

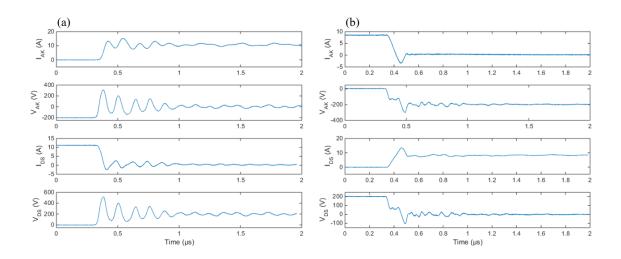

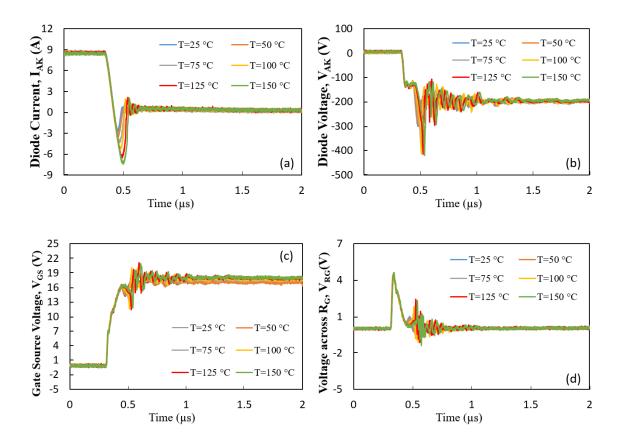

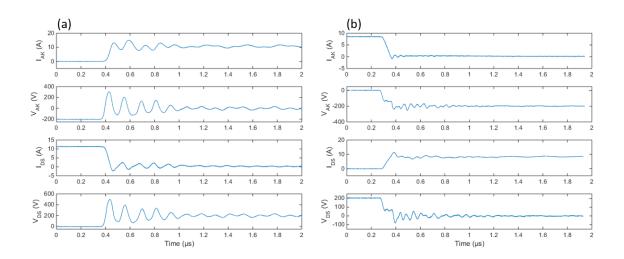

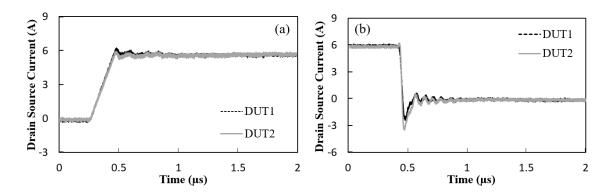

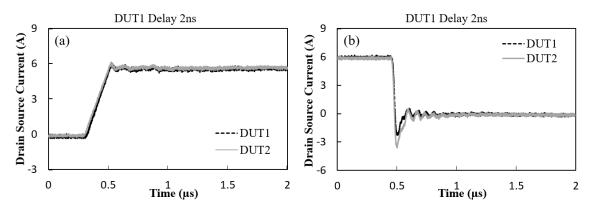

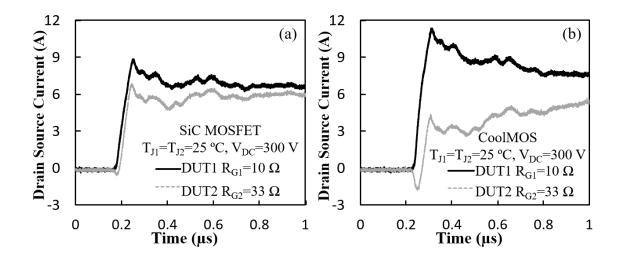

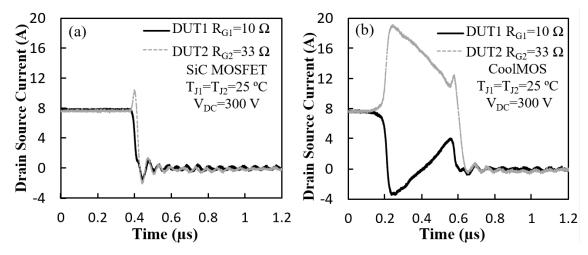

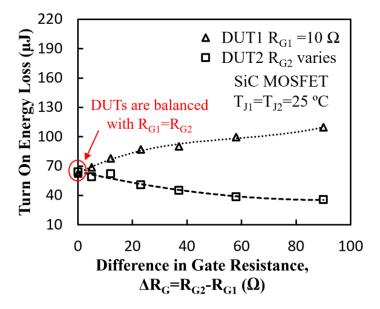

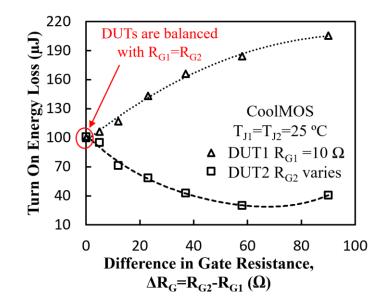

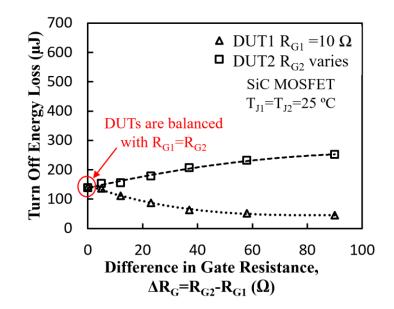

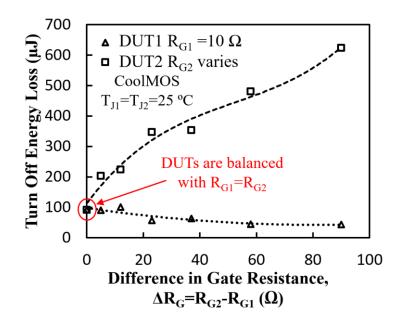

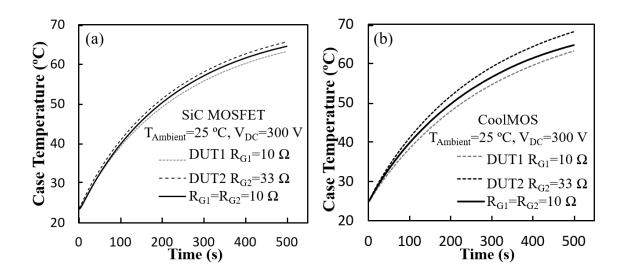

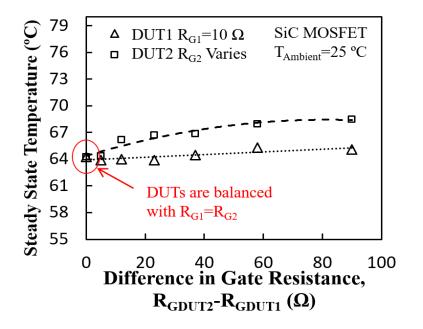

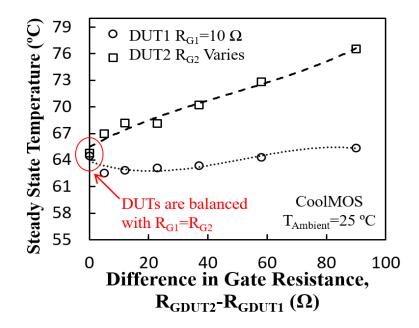

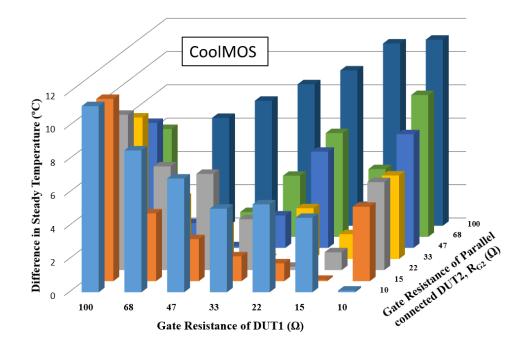

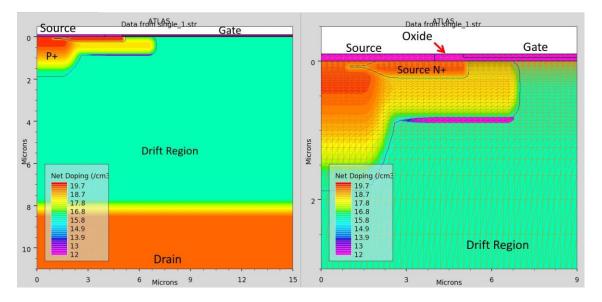

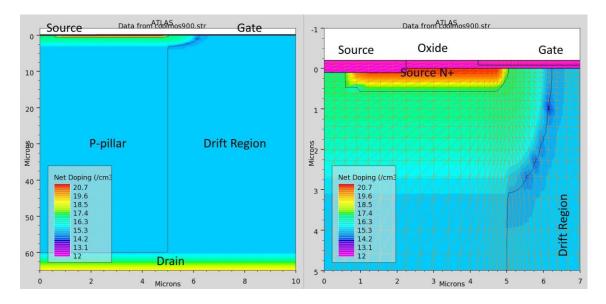

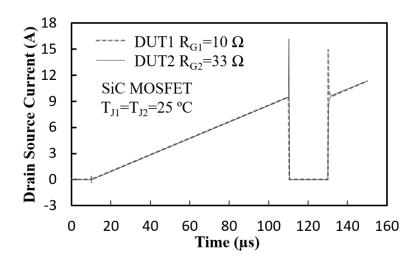

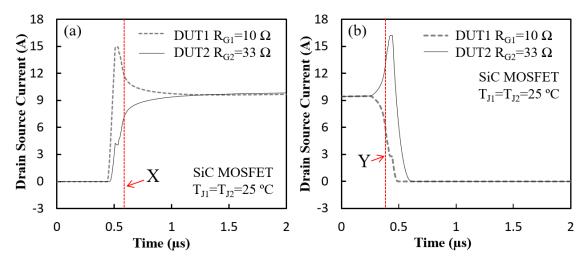

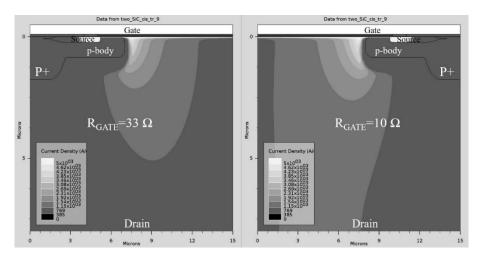

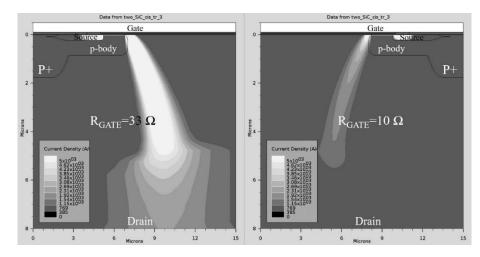

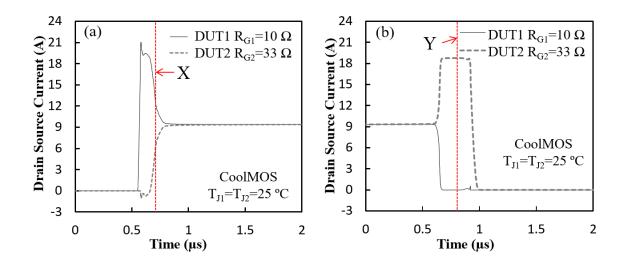

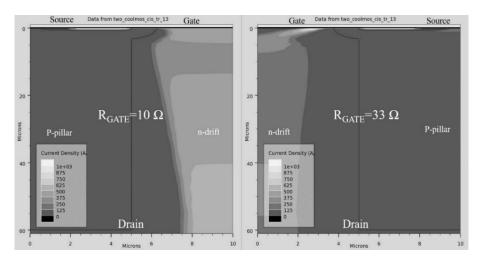

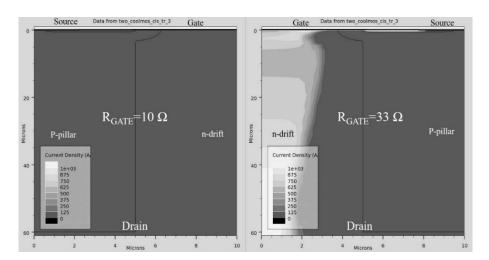

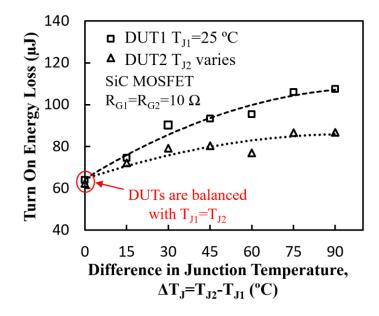

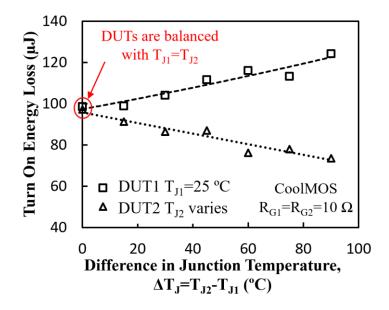

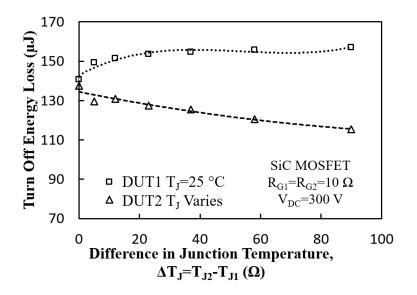

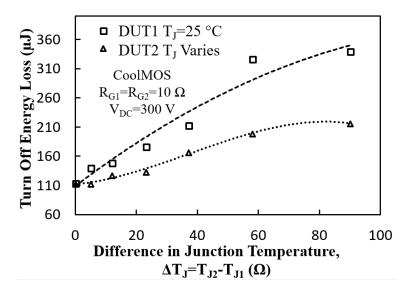

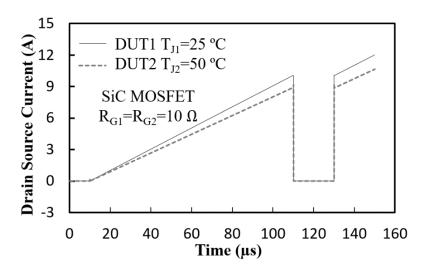

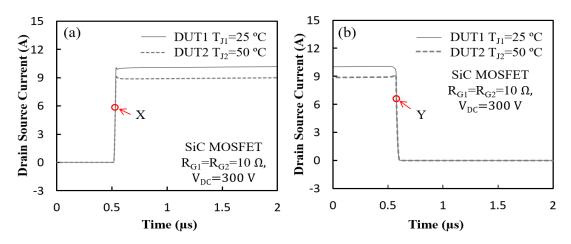

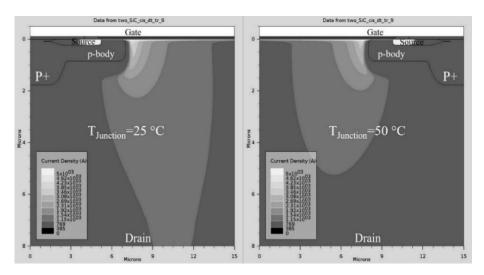

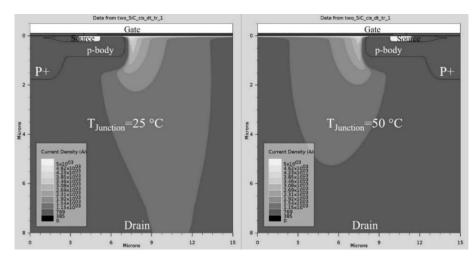

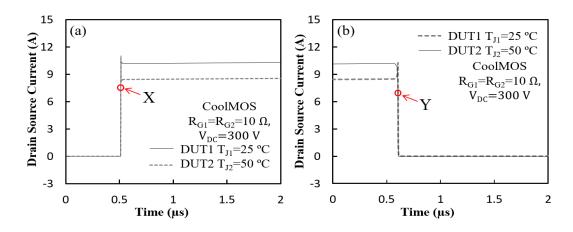

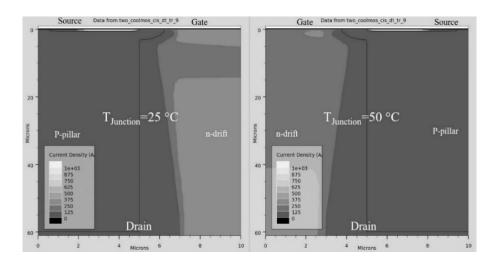

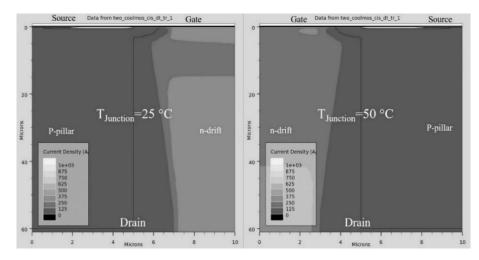

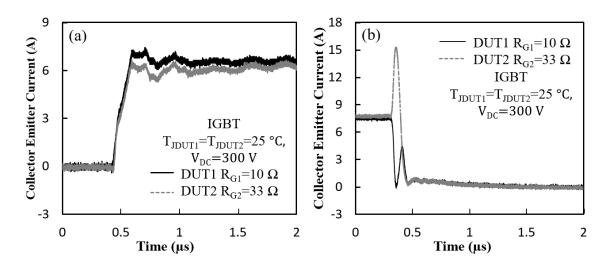

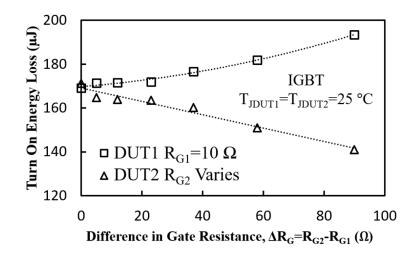

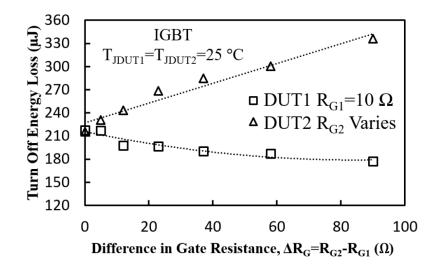

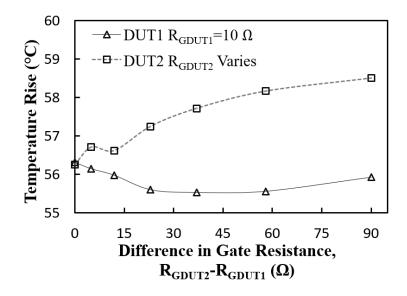

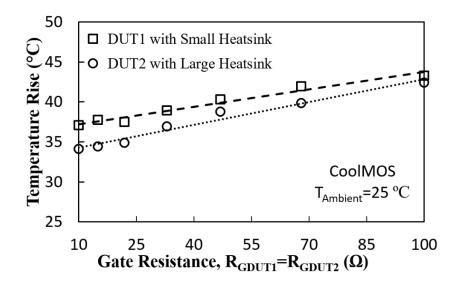

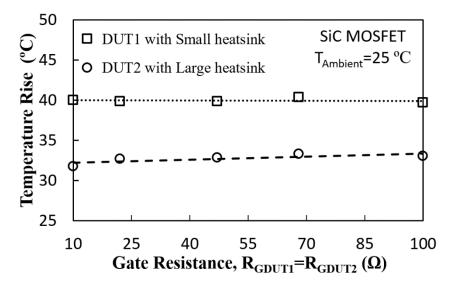

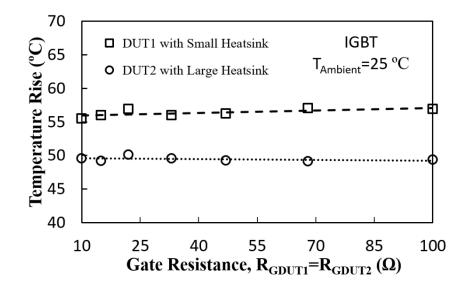

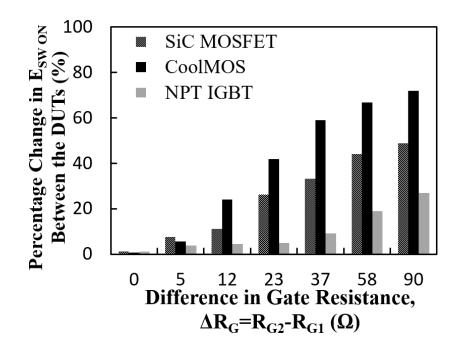

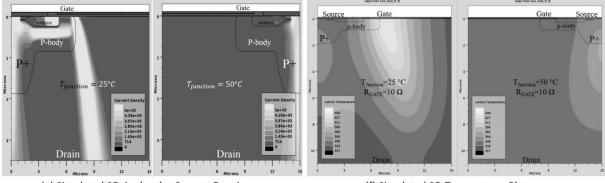

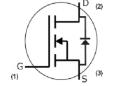

Figure 4.2: (a) Current switching transient characteristics for the parallel connected SiC power MOSFETs at turn-ON under balanced conditions (b) Similar measurements for Figure 4.3: (a) Current switching transient characteristics for the parallel connected SiC power MOSFETs at turn-ON driven with 2 ns delay between the gate drivers (b) Similar Figure 4.4: (a) Turn-ON current waveforms for parallel connected SiC MOSFETs with Figure 4.5: (a) Turn-OFF current waveforms for parallel connected SiC MOSFETs with different switching rates. (b) Similar characteristics for the CoolMOS device. ......116 Figure 4.6: The measured turn-ON switching energies of the parallel connected SiC Figure 4.7: The measured turn-ON switching energies of the parallel connected CoolMOS Figure 4.8: The measured turn-off switching energies of the parallel connected SiC Figure 4.9: The measured turn-off switching energies of the parallel connected CoolMOS Figure 4.10: (a) The measured case temperature rise for the parallel connected SiC MOSFETs switched with  $R_G$  of DUT1 and DUT2 as 10  $\Omega$  and 33  $\Omega$  respectively. (b) Figure 4.11: The measured case temperature rise for the parallel connected SiC Figure 4.12: The measured case temperature rise for the parallel-connected CoolMOS Figure 4.13: SiC MOSFET TCAD Model showing the doping profile and the meshes. 124 Figure 4.14: CoolMOS TCAD Model showing the doping profile and the meshes....124 Figure 4.15: The simulated current waveforms for the parallel connected SiC MOSFETs Figure 4.16: The simulated (a) turn-ON and (b) turn-OFF current waveforms for the Figure 4.17: The 2-D current density contour plot for the parallel connected SiC MOSFETs with different switching rate corresponding to point X in Figure 4.16(a). 126

| Figure 4.18: The 2-D current density contour plot for the parallel connected SiC         |

|------------------------------------------------------------------------------------------|

| MOSFETs with different switching rate corresponding to point Y in Figure 4.16(b)126      |

| Figure 4.19: (a) turn-ON and (b) turn-OFF current waveforms for the parallel-connected   |

| CoolMOS devices switched with different gate resistance                                  |

| Figure 4.20: The 2-D current density contour plot for the parallel connected CoolMOS     |

| devices with different switching rate corresponding to point X in Figure 4.19(a) 128     |

| Figure 4.21: The 2-D current density contour plot for the parallel connected CoolMOS     |

| devices with different switching rate corresponding to point Y in Figure 4.19(b) 128     |

| Figure 4.22: (a) The measured turn-ON current for the parallel connected SiC MOSFETs     |

| driven at 2 different junction temperatures. (b) Similar measurements for the CoolMOS    |

| device                                                                                   |

| Figure 4.23: Measured turn-ON switching energy for the parallel connected SiC            |

| MOSFETs with the DUTs set at different junction temperatures                             |

| Figure 4.24: Measured turn-on switching energy for the parallel-connected CoolMOS        |

| devices with the DUTs set at different junction temperatures                             |

| Figure 4.25: Measured turn-OFF switching energy for the parallel connected SiC           |

| MOSFETs with the DUTs set at different junction temperatures                             |

| Figure 4.26: Measured turn-Off switching energy for the parallel-connected CoolMOS       |

| devices with the DUTs set at different junction temperatures                             |

| Figure 4.27: The simulated current waveforms for the parallel connected SiC MOSFETs      |

| switched at different initial junction temperatures                                      |

| Figure 4.28: The simulated (a) turn-ON and (b) turn-OFF current waveforms for the        |

| parallel connected SiC MOSFETs switched with different initial junction temperatures.    |

|                                                                                          |

| Figure 4.29: The 2-D current density contour plot for the parallel connected SiC         |

| MOSFETs switched at different junction temperature corresponding to point X in Figure    |

| 4.26(a)                                                                                  |

| Figure 4.30: The 2-D current density contour plots for the parallel connected SiC        |

| MOSFETs switched at different junction temperature corresponding to point Y in Figure    |

| 4.26(b)                                                                                  |

| Figure 4.31: The simulated (a) turn-ON and turn-OFF currents for the parallel connected  |

| CoolMOS devices switched at different initial junction temperatures                      |

| Figure 4.32: 2-D current density contour plot for the parallel connected CoolMOS devices |

| switched at different junction temperatures corresponding to point X in Figure 4.31(a).  |

|                                                                                          |

| Figure 4.33: 2-D current density contour plots for the parallel connected CoolMOS              |

|------------------------------------------------------------------------------------------------|

| devices switched at different junction temperatures corresponding to point Y in Figure         |

| 4.31(b)                                                                                        |

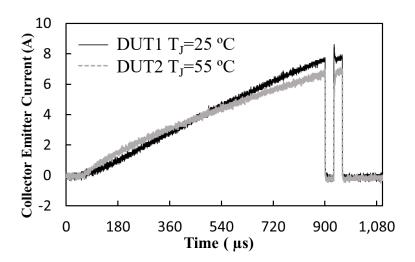

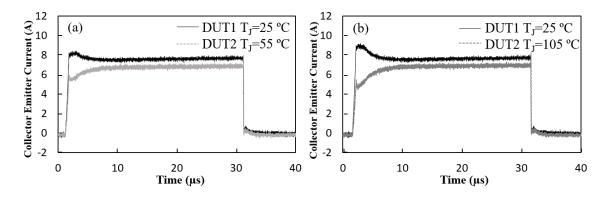

| Figure 4.34: The measured current waveform of parallel-connected IGBTs switched with           |

| different initial junction temperatures (25 °C and 55 °C)                                      |

| Figure 4.35: The measured current waveform of parallel connected IGBTs switched with           |

| different junction temperatures (a) Junction temperature of DUT1=25 °C and DUT2=55             |

| °C (b) Junction temperature of DUT1=25 °C and DUT2=105 °C138                                   |

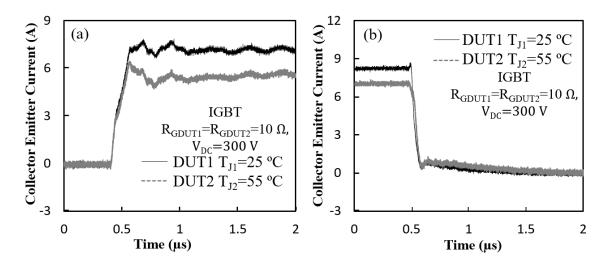

| Figure 4.36: The measured (a) turn on and (b) turn off waveform of parallel connected          |

| IGBTs switched at different initial junction temperature                                       |

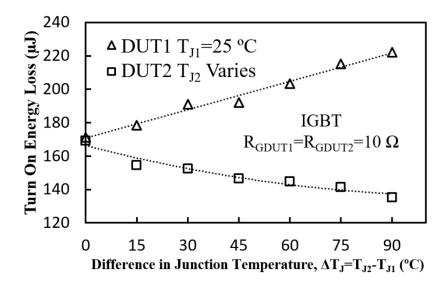

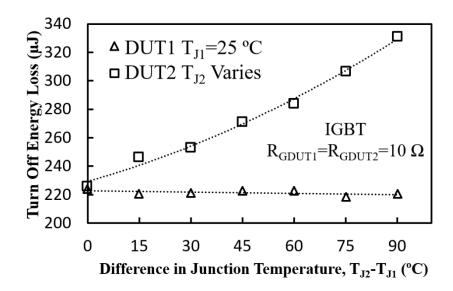

| Figure 4.37: The measured turn-ON switching energies of the parallel-connected IGBT            |

| devices with the DUTs set at different junction temperatures140                                |

| Figure 4.38: The measured turn-off switching energies of the parallel-connected IGBT           |

| devices with the DUTs set at different junction temperatures                                   |

| Figure 4.39: Measured (a) turn-on and (b) turn-off current waveform for parallel               |

| connected IGBTs with different switching rates141                                              |

| Figure 4.40: Measured turn-ON switching energy for the parallel connected IGBT devices         |

| with the DUTs driven at different switching rates                                              |

| Figure 4.41: Measured turn-off switching energy for the parallel-connected IGBT devices        |

| with the DUTs driven at different switching rates                                              |

| Figure 4.42: The measured case temperature rise for the parallel-connected IGBTs               |

| switched at different rates                                                                    |

| Figure 4.43: The measured case temperature rise for the parallel connected CoolMOS             |

| devices switched with different heatsinks                                                      |

| Figure 4.44: The measured case temperature rise for the parallel connected SiC                 |

| MOSFETs switched with different heatsinks                                                      |

| Figure 4.45: The measured case temperature rise for the parallel connected SiC                 |

| MOSFETs switched with different heatsink                                                       |

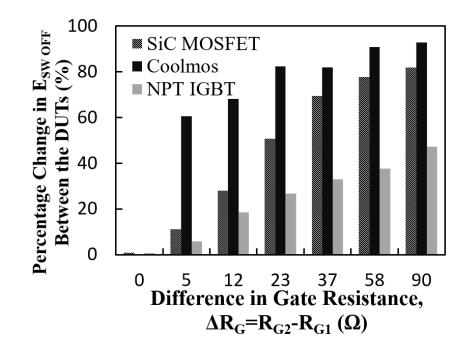

| Figure 4.46: Percentage change in the turn-ON switching energy $(E_{SWON})$ as a function of   |

| the switching rate difference ( $\Delta R_G$ ) between the parallel DUTs                       |

| Figure 4.47: Percentage change in the turn-OFF switching energy ( $E_{SW OFF}$ ) as a function |

| of the switching rate difference ( $\Delta R_G$ ) between the parallel DUTs                    |

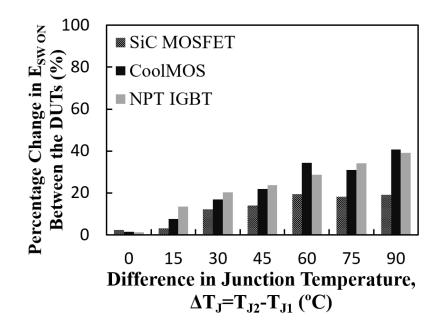

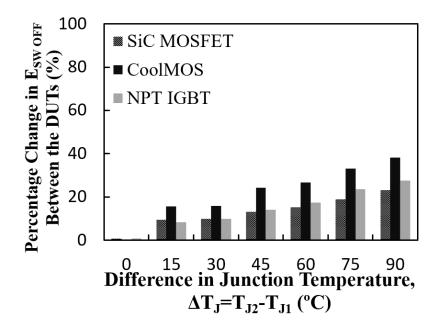

| Figure 4.48: Percentage change in the turn-ON switching energy $(E_{SWON})$ as a function of   |

| the junction temperature difference $(\Delta T_J)$ between the parallel DUTs                   |

|                                                                                                |

| Figure 4.49: Percentage change in the turn-OFF switching energy $(E_{SW OFF})$ as a function |

|----------------------------------------------------------------------------------------------|

| of the junction temperature difference $(\Delta T_J)$ between the parallel DUTs151           |

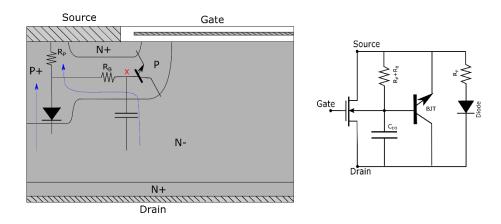

| Figure 5.1: MOSFET structure with parasitic components and equivalent circuit157             |

| Figure 5.2: Power MOSFET cell (a) without and (b) with deep-body implant161                  |

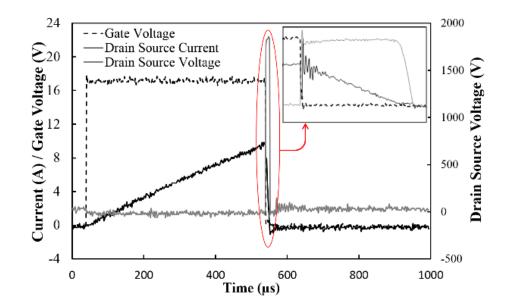

| Figure 5.3: (c) Typical avalanche characteristics showing the gate voltage, drain voltage    |

| and drain-source current during the charging and avalanche conduction phases 165             |

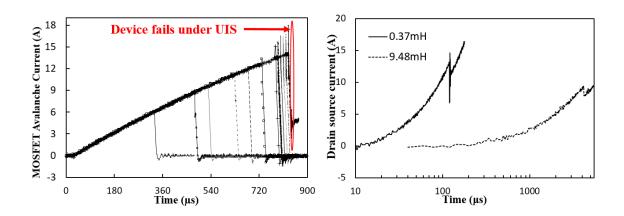

| Figure 5.4: (a) UIS measurements of a 1.2kV/10A SiC MOSFET drain-source currents             |

| during the inductor charging and avalanche phases with different gate pulse durations. (b)   |

| The peak avalanche current characteristics of a SiC MOSFET for 2 different inductor          |

| sizes166                                                                                     |

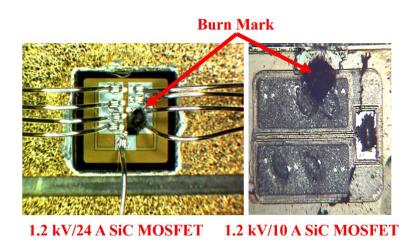

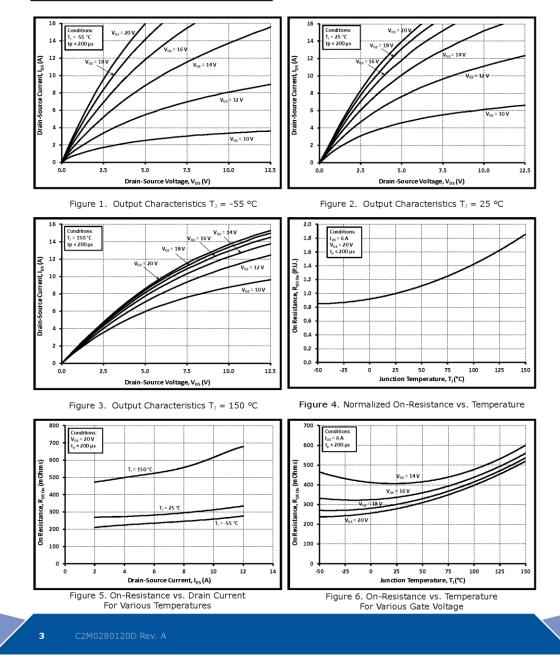

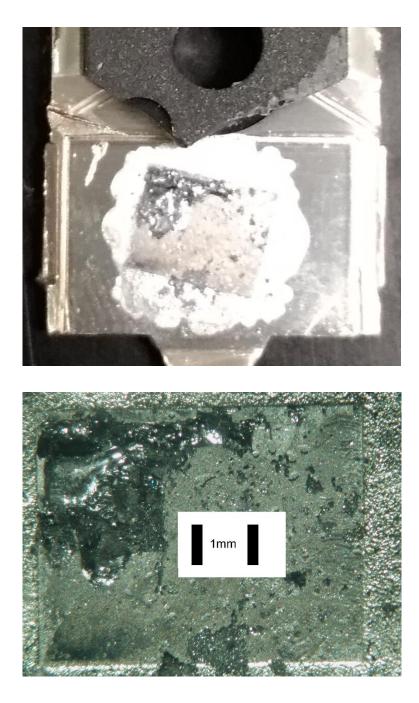

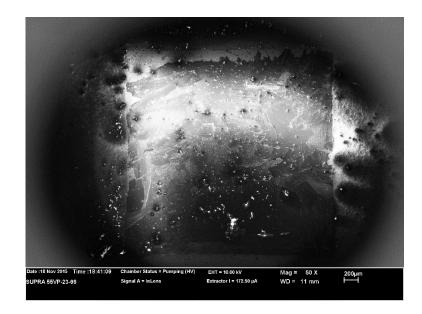

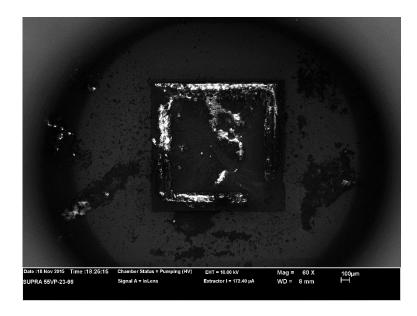

| Figure 5.5: Picture of the de-capsulated SiC MOSFETs showing burn mark resulting from        |

| failure under UIS166                                                                         |

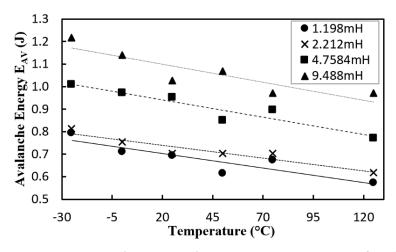

| Figure 5.6: The measured maximum sustainable avalanche energy before failure under           |

| UIS for different inductors as a function of temperatures. The device tested was a           |

| 1.2kV/24A SiC power MOSFET167                                                                |

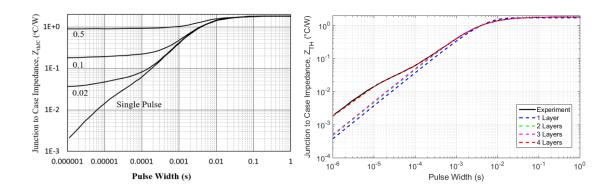

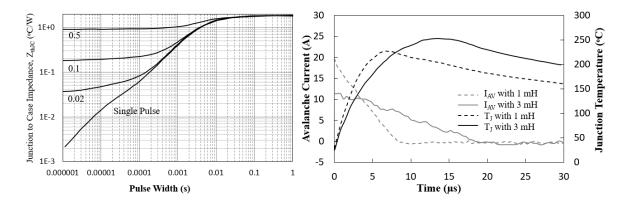

| Figure 5.7: (a) The transient thermal impedance of 1200V SiC MOSFET as a function of         |

| power pulse width; (b) The power dissipated and calculated junction temperature as a         |

| function of time during the avalanche test                                                   |

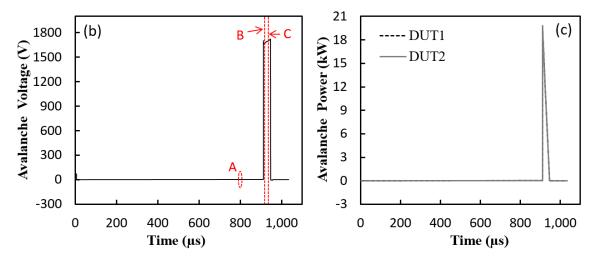

| Figure 5.8: (b) the drain voltage and (c) Avalanche power characteristics of 2 parallel      |

| connected DUTs with identical electro-thermal parameters under UIS                           |

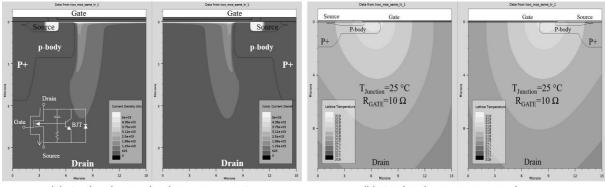

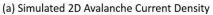

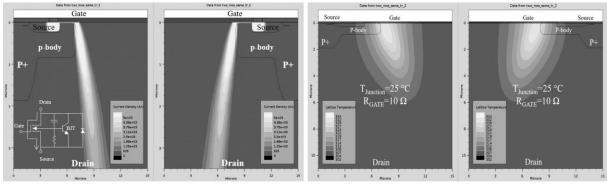

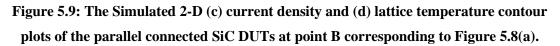

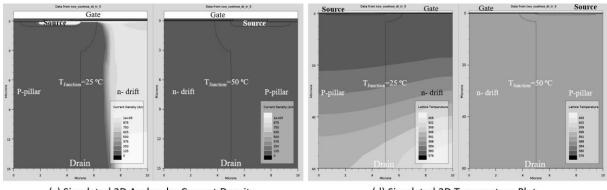

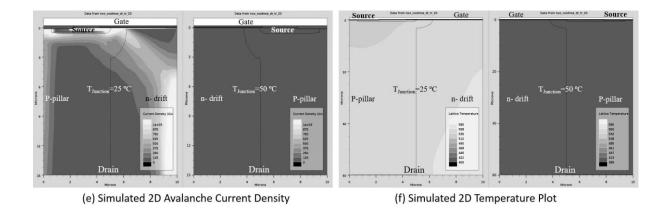

| Figure 5.9: The Simulated 2-D (a) current density and (b) lattice temperature contour        |

| plots of the parallel connected SiC DUTs at point A corresponding to Figure 5.8(a)173        |

| Figure 5.10: The simulated 2-D (a) current density and (b) lattice temperature contour       |

| plots of the parallel connected CoolMOS DUTs at point A corresponding to Figure 5.8(a).      |

|                                                                                              |

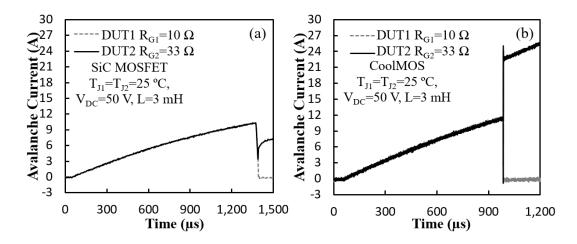

| Figure 5.11: (a) The measured inductor charging and avalanche characteristics for the        |

| parallel connected SiC MOSFETs with different initial junction temperatures. (b)Similar      |

| characteristics for the CoolMOS177                                                           |

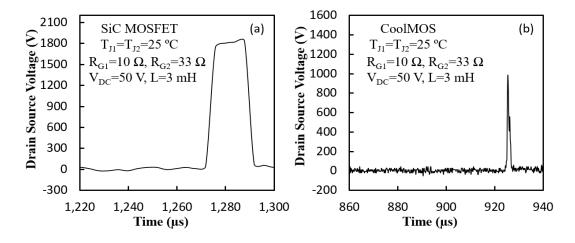

| Figure 5.12: (a) The measured drain source voltage during the charging and avalanche         |

| conduction for the parallel connected SiC MOSFETs with different initial junction            |

| temperatures. (b). Similar characteristics for the CoolMOS177                                |

| Figure 5.13: (a) The measured power loss during charging and avalanche conduction for        |

| the parallel connected SiC MOSFETs with different initial junction temperatures. (b).        |

| Similar characteristics for the CoolMOS177                                                   |

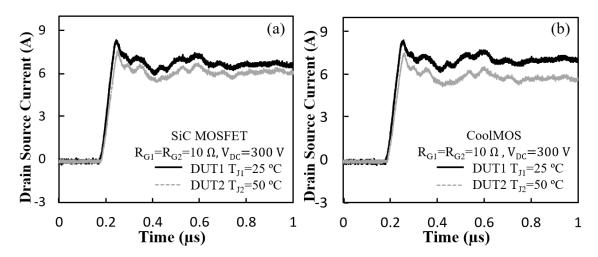

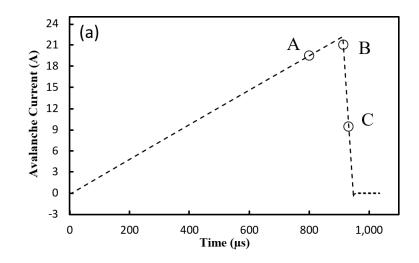

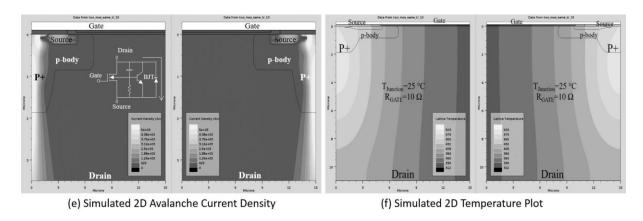

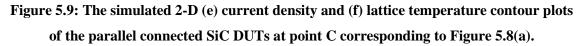

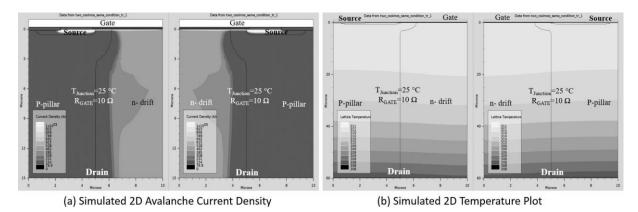

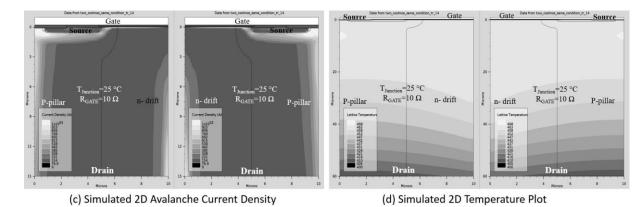

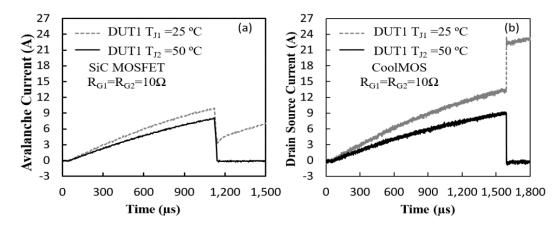

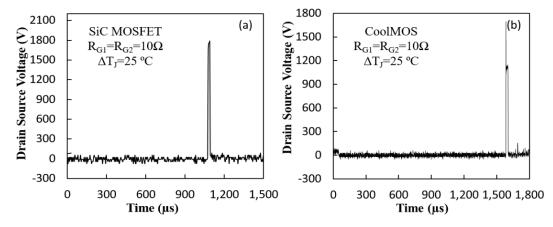

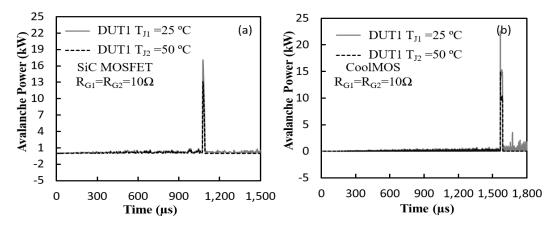

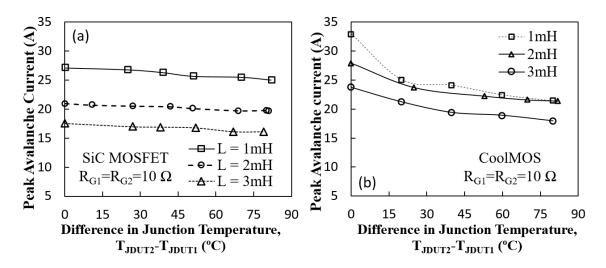

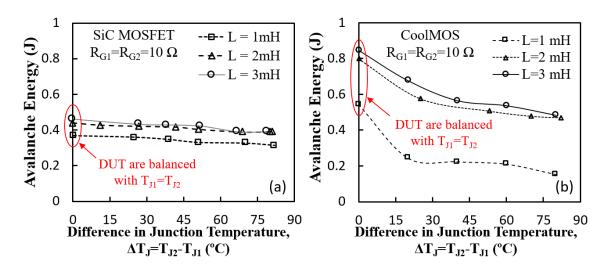

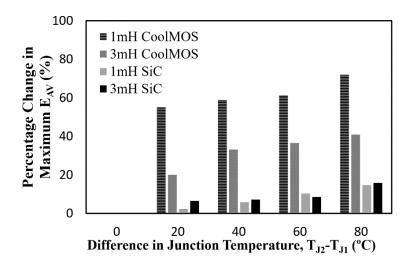

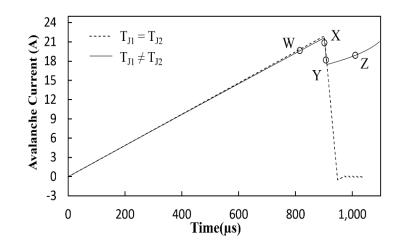

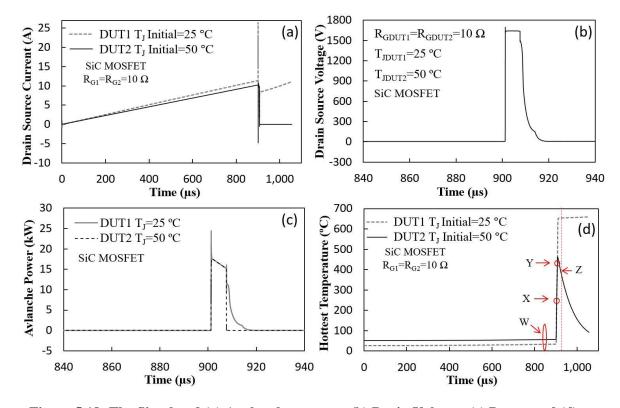

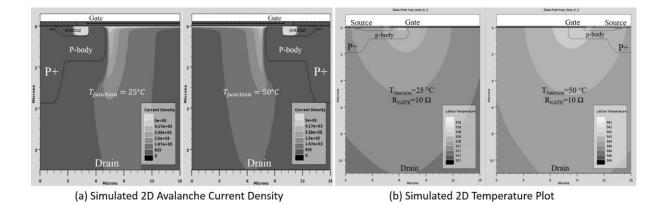

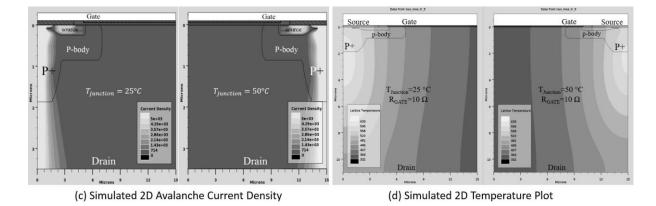

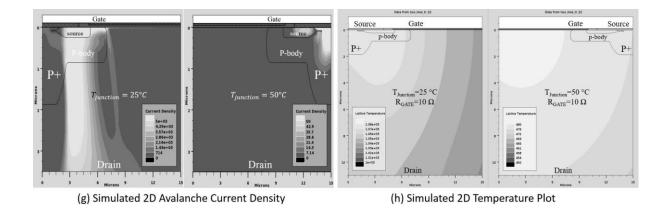

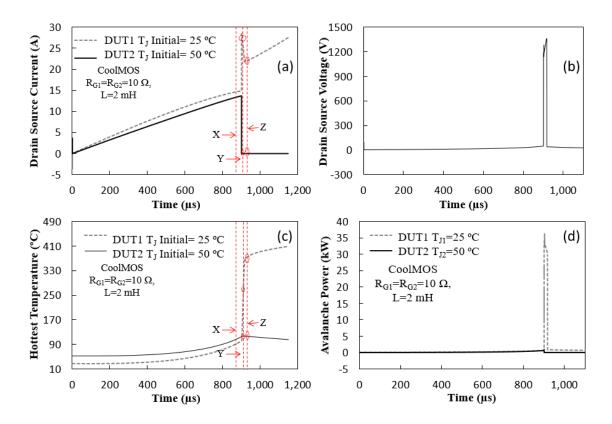

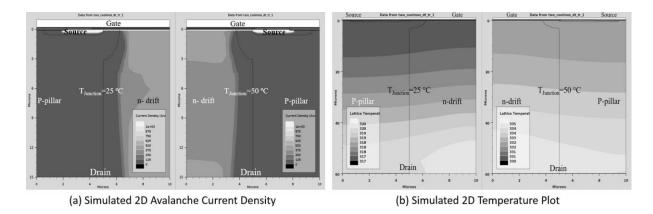

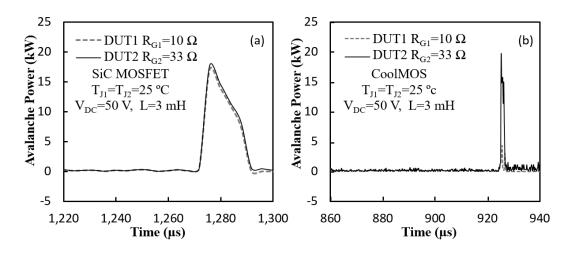

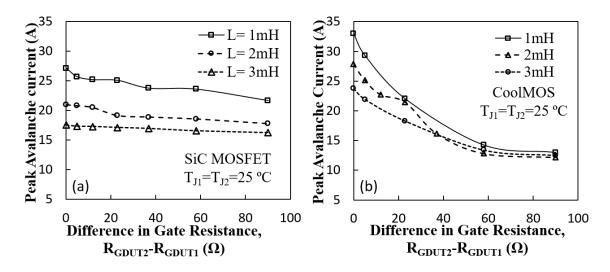

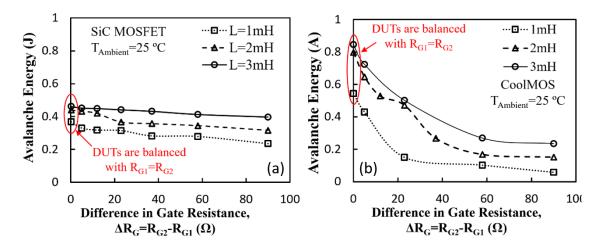

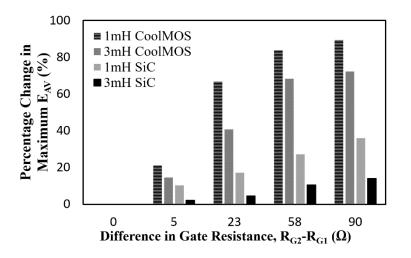

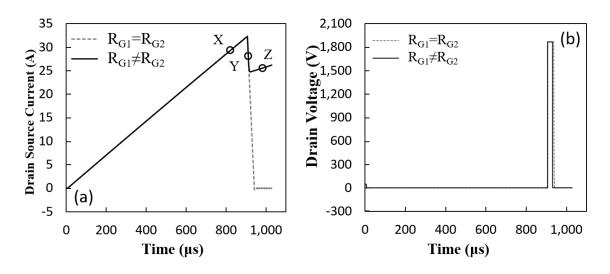

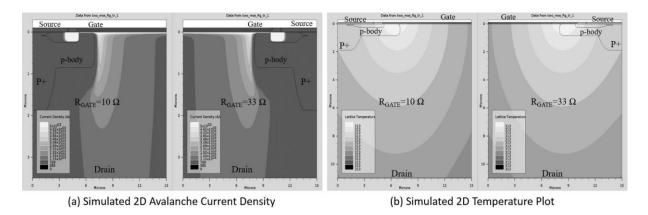

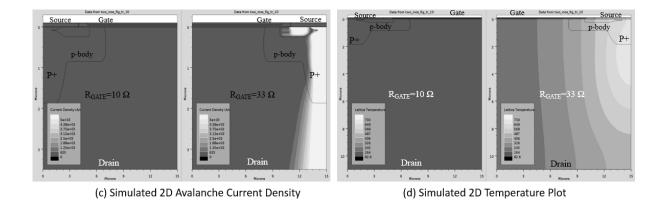

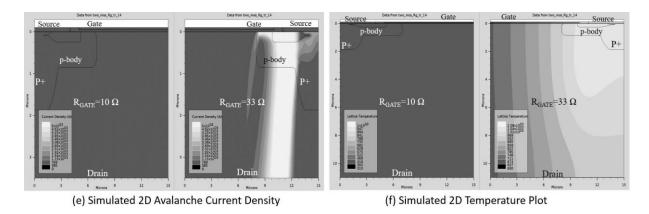

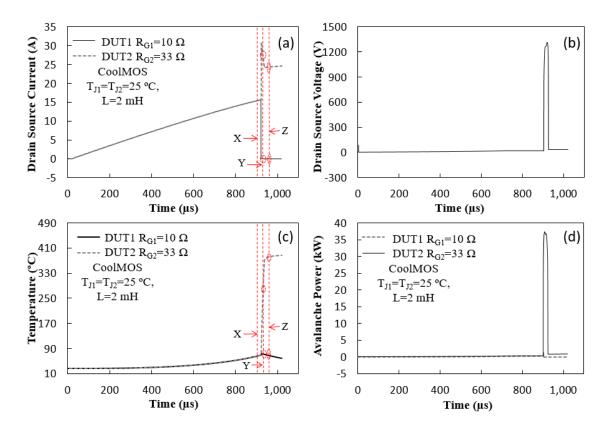

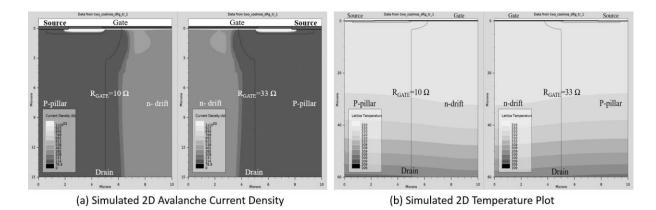

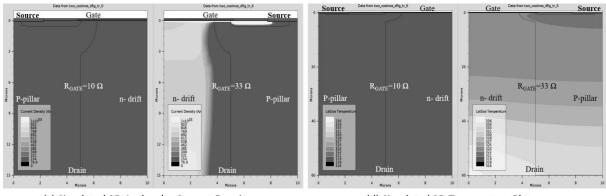

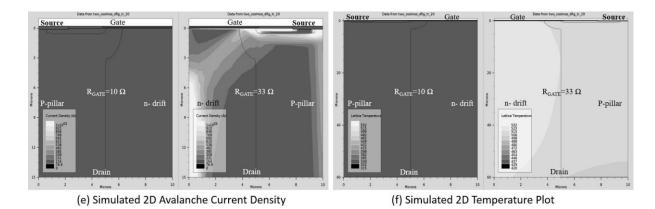

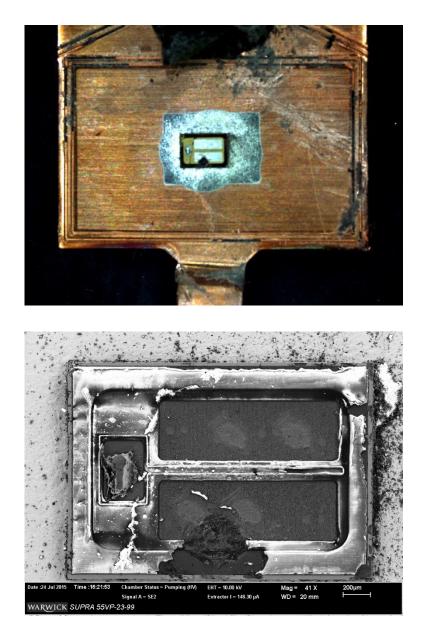

Figure 5.14: (a) The measured peak avalanche currents conducted by the DUTs as a function of the temperature difference between the parallel connected SiC MOSFETs for 3 avalanche durations (inductance sizes). (b) Similar characteristic for the CoolMOS. Figure 5.15: (a) The measured avalanche energy successfully dissipated by the combined SiC MOSFETs as a function of the temperature difference between the DUTs for 3 avalanche durations (inductor sizes). (b) Similar characteristic for the CoolMOS devices. Figure 5.16: Percentage change in the peak avalanche energy  $(E_{AV})$  as a function of the Figure 5.17: The simulated UIS characteristics of 2 parallel connected DUTs at identical Figure 5.18: The Simulated (a) Avalanche current; (b) Drain Voltage; (c) Power and (d) Temperature of the parallel connected DUTs respectively during the UIS......182 Figure 5.19: The simulated (a) 2-D current density and (b) lattice temperature contour plots for devices with different initial junction temperatures at point W corresponding to Figure 5.20: The simulated (a) avalanche current, (b) drain voltage (c) Lattice temperature and (d) Avalanche power characteristics for parallel connected CoolMOS devices under Figure 5.21: The simulated 2-D (a) current density and (b) lattice temperature contour plots for parallel connected CoolMOS devices with different initial junction temperatures Figure 5.22: (a) Avalanche current characteristics for the parallel connected SiC Figure 5.23: (a) The measured drain voltage for parallel connected SiC MOSFETs with Figure 5.24: (a) The measured avalanche power for parallel connected SiC MOSFETs with different R<sub>G.</sub> (b) Similar characteristics for CoolMOS......191 Figure 5.25: The measured peak combined avalanche currents conducted by the DUTs as a function of the switching rate difference between the DUTs for 3 avalanche durations Figure 5.26: The measured avalanche energy safely dissipated by the combined DUTs as a function of the switching rate difference between the DUTs for 3 avalanche durations

| Figure 5.27: Percentage change in the peak avalanche energy $(E_{AV})$ as a function of the |

|---------------------------------------------------------------------------------------------|

| switching rate difference between the parallel DUTs193                                      |

| Figure 5.28: Simulated UIS characteristics of 2 parallel connected DUTs at the same and     |

| different switching rates194                                                                |

| Figure 5.29: The simulated 2-D (a) current density and (b) lattice temperature contour      |

| plots for the parallel-connected devices with different switching rates at point X          |

| corresponding to Figure 5.28(a)                                                             |

| Figure 5.30: The (a) simulated avalanche current (b) drain voltage (c) Temperature and      |

| (d) dissipated power for the parallel connected CoolMOS devices switched with different     |

| gate resistance                                                                             |

| Figure 5.31: The simulated (a) 2-D current density and (b) lattice temperature contour      |

| plots of the parallel connected CoolMOS with different gate resistances under UIS. This     |

| corresponds to point X in Figure 5.30 where the DUTs are under normal conduction mode.      |

|                                                                                             |

| Figure 6.1: 1.2 kV/150 A CREE half-bride Power Module implemented in SiC power              |

| MOSFETs and Schottky Barrier Diodes207                                                      |

| Figure 6.2: 1.2 kV/150 A Fairchild half-bride Power Module implemented in a silicon         |

| IGBT and PiN diode for each switching cell                                                  |

## Acknowledgements

The very first and foremost, I would like to sincerely thank my supervisor, Dr. Olayiwola Alatise, in the University of Warwick. He has been a great teacher, mentor and friend throughout since four years ago Prof. J. Wang introduced us. I thank you for offering the PhD opportunity in this group. He has been supportive for this research work with his extensive and depth knowledge. Moreover, he has showed so much care about my work and give advises at the right time. And I thank you for so much time and effort you have spent to revise my papers. I thank you for the time we have been working very hard together in the summer of 2015 and the outcome is very encouraging.

I would like to thank Jose Angel Ortiz Gonzalez, for not only the technical support but also the knowledge he has shared with me. He is an expert in long distance running and swimming, in the meantime with great enthusiasm for his PhD work. I thank you for propose the idea for my chapter 3, and thank you for the rapid designing of the PCBs and those machining works in the workshop.

I would like to thank my colleagues, friends in the science city office: Roozbeh Bonyadi, Petros Alexakis, Fan Li, Han Qin, Ruizhu Wu, Tianxiang Dai and Tianqu Hao. I thank you for these years of companionship, the fun time we had together, the discussion we had together, the dinner we had together and the issues we have solved together. I would like to thank the technicians in the workshop for their rapid and effective work.

Finally, I would like to thank my parents for their support either in moral or in finance. I would like to thank my girl friend Chenyao Bai for her meticulous care in my daily lives and encouragement of my PhD work in the past three years. Thank you all!

Ji Hu

September 2016

## Declaration

This thesis is submitted in partial fulfilment for the degree of Doctor of Philosophy under the regulations formulated by the School of Engineering of the University of Warwick. I herewith declare that this thesis contains my own research performed under the supervision of Dr. Olayiwola Alatise and Prof. Li Ran, without assistance of third parties, unless stated otherwise. The research materials have not been submitted in any previous application for a degree at any other university. All sources of information are specifically acknowledged in the content. The work presented in Chapter 2 has been partly published in J3, J4 and C5. Majority of the work presented in Chapter 3 has been published in C2 and C3. The work presented in Chapter 4 has been published in J2 and C7. The work presented in Chapter 5 has been published in J1, C1 and J2.

## **List of Publications**

This section presents the complete list of 1<sup>st</sup> and co-authored published journal and conference papers by Ji Hu. The 1<sup>st</sup> author papers result directly from the work presented here.

- J1. J. Hu, O. Alatise, J. A. O. González, R. Bonyadi, L. Ran and P. Mawby, "The Effect of Electrothermal Nonuniformities on Parallel Connected SiC Power Devices Under Unclamped and Clamped Inductive Switching," *IEEE Trans. Power Electron.*, vol. 31, pp. 4526-4535, 2016.

- J2 J. Hu, O. Alatise, J. A. O. González, R. Bonyadi, P.Alexakis, L. Ran and P. Mawby, "Robustness and Balancing of Parallel-Connected Power Devices: SiC Versus CoolMOS," *IEEE Trans. Ind. Electron.*, vol. 63, pp. 2092-2102, 2016.

- C1 J. Hu, O. Alatise, J. A. O. González, P.Alexakis, L. Ran and P. Mawby, "Finite element modelling and experimental characterisation of paralleled SiC MOSFET failure under avalanche mode conduction," *Power Electronics and Applications* (EPE'15 ECCE-Europe), 2015 17th European Conference on, 2015, pp. 1-9.

- C2 J. Hu, O. Alatise, J. A. O. González, L. Ran and P. Mawby, "Avalanche Ruggedness of Parallel Connected Diodes: SiC Schottky Diodes vs Silicon PiN Diodes," submitted to *Power Electronics, Machines and Drives (PEMD), the 8<sup>th</sup> IET International conference on*, accepted 9<sup>th</sup> Mar. 2016.

- C3 J. Hu, O. Alatise, J. A. O. González, L. Ran and P. Mawby, "Comparative Electrothermal Analysis between SiC Schottky and Silicon PiN Diodes: Paralleling and Thermal Considerations," submitted to *Power Electronics and Applications (EPE'16 ECCE-Europe), 2016 18th European Conference on,* accepted on 1<sup>th</sup> Mar. 2016.

- R. Bonyadi, O. Alatise, S. Jahdi, J. Hu, J. A. O. González, L. Ran and P. Mawby,

"Compact Electrothermal Reliability Modeling and Experimental Characterization of Bipolar Latchup in SiC and CoolMOS Power MOSFETs," *IEEE Trans. Power Electron.*, vol. 30, pp. 6978-6992, 2015.

- J4 P. Alexakis, O. Alatise, J. Hu, S. Jahdi, L. Ran, P. Mawby, "Improved Electrothermal Ruggedness in SiC MOSFETs Compared With Silicon IGBTs," *IEEE Trans. Electron Devices*, vol. 61, pp. 2278-2286, 2014.

- P. Alexakis, O. Alatise, J. Hu, S. Jahdi, J. A. O. González, L. Ran and P. Mawby., "Analysis of power device failure under avalanche mode Conduction," in *Power Electronics and ECCE Asia (ICPE-ECCE Asia), 2015 9th International Conference on*, 2015, pp. 1833-1839.

- R. Bonyadi, O. Alatise, S. Jahdi, J. Hu, L. Evans, and P. A. Mawby, "Investigating the reliability of SiC MOSFET body diodes using Fourier series modelling," in Energy Conversion Congress and Exposition (ECCE), 2014 IEEE, 2014, pp. 443-448.

- C6 J. A. O. González, O. Alatise, N. Nobeen, J. Hu, L. Ran and P.Mawby, "Electrothermal Considerations for Power Cycling in SiC Technologies," in *Integrated Power Electronics Systems (CIPS), 2016 8th International Conference* on, 2016, pp. 1-7.

- C7 R. Bonyadi, O. Alatise, J. Hu, Z. Davletzhanova, J. A. O. González, L. Ran and P.Mawby, "Compact Temperature Dependent Physics-Based IGBT Model for Parallel IGBTs in Clamped Inductive Switching Circuit," in *Applied Power Electronics Conference and Exposition (APEC), 2016 IEEE*, 2016.

- C8 J. A. O. González, O. Alatise, J. Hu, L. Ran and P. Mawby, "Temperature Sensitive Electrical Parameters for Condition Monitoring in SiC Power MOSFETs," submitted to *Power Electronics, Machines and Drives (PEMD), the* 8<sup>th</sup> IET International conference on, accepted 9<sup>th</sup> Mar. 2016.

- Y. Bonyadi, P. Gammon, R. Bonyadi, O. Alatise, J. Hu, V. Shah and P. Mawby,

"The Impact of Triangular Defects on Electrical Characteristics and Switching

Performance of 4H-SiC PiN Diodes," submitted to *the 8th Annual IEEE Energy Conversion Congress & Exposition (ECCE 2016).*

## Abstract

Power modules typically comprise of several power devices connected in parallel for the purpose of delivering high current capability. This is especially the case in SiC where small active area and low current MOSFETs are the only option due to defect density control and yield issues in the epitaxial growth of SiC wafers. Electrothermal variations between parallel connected devices can emerge from manufacturing variability, nonuniform degradation rates, variation in gate driving just to mention a few. The impact of electrothermal variation between parallel-connected devices as a function of device technology is thus important to consider especially since failure of the power module requires only failure in a single device. Furthermore, the impact of these electrothermal variations in parallel-connected devices on the total electrothermal ruggedness of the power module under anomalous switching conditions like unclamped inductive switching is important to consider for the different device technologies. In this thesis, the impact of initial junction temperature variation, switching rates and thermal boundary conditions between parallel-connected diodes have been evaluated for SiC Schottky and silicon PiN diodes under clamped and unclamped inductive switching. Finite element simulations have been used to support the experimental measurements. Similar studies have been performed in CoolMOS super-junction MOSFETs, silicon IGBTs and SiC power MOSFETs. New insights regarding the failure of parallel connected devices under unclamped inductive switching have been revealed from the models and measurements. Overall, the thesis makes a major contribution in the understanding of the electrothermal performance of parallel connected devices for different transistor and diode technologies.

## Abbreviations

| $N_D$              | background doping concentration                                      |  |

|--------------------|----------------------------------------------------------------------|--|

| р                  | Hole concentration                                                   |  |

| $	au_{HL}$         | Ambipolar carrier lifetime                                           |  |

| D                  | Ambipolar diffusivity                                                |  |

| $D_{n(p)}$         | Diffusivity for electrons (holes).                                   |  |

| $\mu_{n(p)}$       | Carrier mobility for electrons (holes).                              |  |

| Wd                 | Drift region width                                                   |  |

| $n_i$              | Intrinsic carrier concentration                                      |  |

| $A_R$              | Effective Richardson's constant                                      |  |

| Т                  | Absolute temperature in Kelvin.                                      |  |

| $V_{FS}$           | Bias voltage                                                         |  |

| $arPhi_{BN}$       | Schottky barrier height                                              |  |

| k                  | The Boltzmann's constant                                             |  |

| $J_s$              | Saturation current density                                           |  |

| RCONT              | Schottky contact resistance                                          |  |

| $R_{SUB}$          | The resistance in the substrate                                      |  |

| $R_D$              | The resistance of the drift region                                   |  |

| $t_{OX}$           | Thickness of the gate oxide                                          |  |

| $\varepsilon_{OX}$ | The oxide dielectric constant                                        |  |

| $\mathcal{E}_{S}$  | Semiconductor dielectric constant                                    |  |

| $N_A$              | Doping concentration in the p-base region                            |  |

| $n_i$              | Intrinsic carrier concentration                                      |  |

| LCH                | Channel length                                                       |  |

| $W_{cell}$         | Cell pitch width                                                     |  |

| $\mu_{ni}$         | Inversion layer mobility                                             |  |

| $C_{OX}$           | Specific capacitance of gate oxide                                   |  |

| $x_{JP}$           | The P-base junction depth                                            |  |

| $\mu_{nJ}$         | The bulk mobility appropriate to the doping level of the JFET region |  |

| $N_{DJ}$           | Doping concentration in the JFET region                              |  |

| $W_0$              | Zero-bias depletion width for the JFET region                        |  |

| $W_G$              | Gate width                                                           |  |

| $ ho_D$            | Resistivity of the drift region                                      |  |

| а                  | JFET region width                                                    |  |

| $x_{PL}$           | Overlap length of gate oxide and p-body region                       |  |

| $t_{IEOX}$         | Oxide thickness between the gate and the source metal                |  |

| $J_C$              | Total current flow                                                   |  |

| $W_N$              | Width of the lightly doped N-drift region                            |  |

| Won                | The depletion width                                                  |  |

- *L<sub>a</sub>* Ambipolar diffusion length

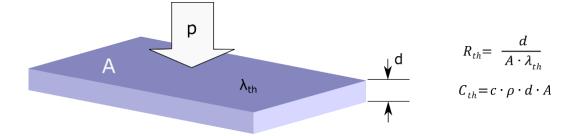

- $\lambda_{th}$  Specific heat conductance

- *c* Thermal capacitance

- $\rho$  The density of material

- *x* The coordinate distance in the direction of heat transfer

- $G_{n(p)}$  Generation rates for electrons (holes)

- $R_n$  Recombination rates for electrons (holes)

- $T_L$  Lattice temperature

- $\varepsilon$  Local permittivity

- $\psi$  Electrostatic potential

- *E*<sub>*G*</sub> Bandgap energy

- $N_C$  Effective density of state in the conduction band

- $\rho_L$  Local space charge density

- $N_V$  Effective density of state in the valence band

- *U* Recombination rate

- *E*<sup>*t*</sup> Trapping energy level

- $C_{A\Delta n}$  High-level injection Auger coefficient

- $V_{bi}$  The built-in potential

- *E<sub>FC</sub>* Fermi level position in the semiconductor

- $E_C$  Conduction band of semiconductor

# Chapter 1. INTRODUCTION

#### 1.1 Background

Power electronics has enabled the more efficient and flexible use of electricity. This has been of benefit to all levels of power conversion ranging from a few watts in low voltage hand-held electronic devices, to several kilowatts in medium voltage electric drivetrains for electric vehicles and several giga watts in grid connected converters used in applications like high voltage direct current (HVDC) converters and flexible AC transmission systems (FACTS) [1-8].

The increased electrification of heat and transportation coupled with the need to reduce the reliance on fossil fuels so as to mitigate global warming has made power efficiency and power electronics a very critical technology. Traditional coal and gas based power stations are well known for their significant contributions to global warming, hence, there has been a proliferation of alternate sources of renewable energy including solar and wind energy conversion systems [9-11]. Connecting these renewable sources of energy to the power grid requires power electronics to convert a variable voltage variable frequency AC source to a fixed frequency fixed voltage rating AC delivered to the grid

in the case of wind energy conversion systems. Older HVDC systems were based on thyristor technologies implemented as line commutated current source converters, however, newer HVDC systems use self-commutated voltage source converters based on IGBT technology [12-14]. In the case of solar power, a grid tie inverter is required to convert the DC power generated by the solar cells into single or 3 phase AC power for grid connection. Furthermore, for long distance power transmission over land or connection of off-shore wind-farms, HVDC is preferred technology [15, 16]. Power electronic converters are also useful for connecting asynchronous power systems or even power systems operating at different frequencies.

Power electronic converters are also the core technology behind the electrification of vehicle transportation [17]. Traditional internal combustion engines are a key contributor to greenhouse gas emissions; hence, the drive towards electric vehicles is important to mitigate climate change. The 2 level 3 phase voltage source converter is required in electric vehicles for converting the DC electrochemical power stored in the lithium ion battery to a controllable 3 phase AC voltage for controlling the electrical machine used for traction [18, 19]. The bi-directional capability of voltage source converters means that power generating from regenerative breaking can be transferred back to the battery. The converter is used to control the speed and torque of the machine through modulation [20]. Power electronic converters are also critical in electric rail transportation where AC machines are driven and controlled by converters [21]. The power rating of these converters are typically higher than electric vehicle converters since greater torque is required. Medium voltage electric drives comprising of back-to-back 2 level 3 phase voltage source converters are also used in ship propulsion [22]. To improve the efficiency and reduce the carbon emissions of shipping, electric drivetrains are increasingly being used in large ships [23]. Here, the diesel or gas turbine powered engine initially used for direct propulsion is instead used to power a generator which supplies electric power to an electrical motor through a back-to-back power electronic converter. With increased efficiency and controllability of the electrical motor, energy consumption can be significantly reduced. Power electronics is also critical in the drive for increased electrification of aircraft. This is called the More-Electric-Aircraft (MEA) where functions initially implemented by pneumatic and hydraulic power are increasingly being replaced with electric power [24, 25]. As aircrafts move towards higher degrees of electrification, power electronic controllers, breakers and converters will be required for connecting loads and increasing controllability of the power system.

At the heart of power electronic converters, are the power semiconductor devices that control power flow to the load through energy storage components like inductors and capacitors. Power semiconductors act as switches in this manner. Ideally, power semiconductor devices should have zero on-state loss, zero off-state loss and instantaneous switching speed, however, this is not possible. The devices have conduction losses due to series resistances, blocking losses due to leakage current and finite switching speeds due to parasitic resistances, inductances and capacitances. Power semiconductor devices can be 2 terminal devices like diodes or 3 terminal devices like transistors and thyristors. Diodes are passive elements that rectify by conducting in one direction while blocking in the opposite direction. Transistors are switches that can be controlled either by current as is the case in a BJT or a voltage as is the case in an FET. While the other three terminal devices like thyristors are semi-controllable in the sense that they can be turned ON but not turned OFF [26, 27]. Power semiconductor devices can also be unipolar devices meaning that carrier flow is due to a majority carrier or they can be bipolar meaning that carrier flow is due to both majority and minority carriers [26, 28]. Unipolar devices include MOSFETs and Schottky diodes while bipolar devices include Thyristors, IGBTs, BJTs and PiN diodes. Power devices can also be classified according to the semiconductors used to fabricate them. Historically, power devices have been exclusively silicon based, however, now there are wide bandgap devices based on silicon carbide and gallium nitride [29, 30].

It is generally well recognised that high power applications use low switching frequencies while low power applications use high switching frequencies [31-33]. For example, a switch mode power supply used for connecting a laptop to the mains can run at switching frequencies in megahertz, while the kilowatt rated converter used in an electric vehicle will run at a few kHz and the megawatt rated converter used in a modular multi-level HVDC converter will run at grid frequency (50 Hz or 60 Hz). Hence, high power low speed applications are usually implemented by thyristors, while low voltage high speed applications are implemented by discrete power MOSFETs. IGBTs have become popular for medium voltage medium frequency applications [34]. Thyristors with voltage ratings as high as 8 kV and current ratings as high as 4 kA are available as phase controlled thyristors and as typically deployed to line commutated current source converters for multi-gigawatt HVDC systems [33, 35, 36]. However, wide bandgap materials like SiC have pushed MOSFETs into the medium voltage arena. Thanks to SiC, 1.2 kV and 1.7 kV power MOSFETs and diodes are now available in TO-247 packages and as power modules. SiC MOSFETs with breakdown voltages as high as 10 kV and even 15 kV have been demonstrated by Wolfspeed (formerly CREE) [37, 38]. Gallium nitride is another wide bandgap semiconductor, however, due to processing issues and the lack of availability of a bulk GaN substrate, GaN devices are limited in scope and application.

#### 1.2 A Brief History of Power Electronics

Solid state power electronic devices were first proposed as a point contact germanium transistor by Bardeen and Brattain in 1947 [39, 40]. The bipolar junction transistor (BJT), which was formed as a variable resistance with a third terminal to control the current flow, was proposed by Shockley [41]. Eventually, such solid state devices were developed and fabricated in silicon for low cost, hence, vacuum tubes were replaced to improve the cost performance balance. In the 1950s, power conversion performed by semiconductor switching devices became a reality. In 1956, the silicon controlled rectifier (SCR) was introduced by General Electric [42-44]. In the same year, the thyristor became commercially available. These greatly increased the range of power electronic applications. In 1976, the vertical power Metal-Oxide-semiconductor field effect transistor (MOSFET) became commercially available. Due to the insulating gate and increased controllability, it was an improvement over BJTs. In 1979, the Insulated Gate Bipolar Transistor (IGBT) was introduced as a hybrid between a MOSFET and a BJT. It has a MOS input and a bipolar output, thus taking advantages of the ease of controllability of the MOSFET and the current density capability of the BJT. In 1999, the super-junction MOSFET became commercially available. This improved the conduction loss performance of the MOSFET by using the concept of charge balance from alternating p and n columns to reduce the drift layer thickness. More recent research interest has been paid to the wide band gap material silicon carbide as it shows superb performance in fabricating high power devices than the silicon. Table 1-1 shows the comparison of fundamental property between silicon and SiC. In 2011, the very first SiC power MOSFET became commercially available by CREE although the Schottky barrier diode was first released in 2002. The Schottky diode exhibited significantly reduced switching losses compared to the PiN diode due to its unipolar nature, hence, no stored charge and

no reverse recovery current. Today SiC power MOSFET devices and modules are commercially available from CREE and ROHM. GE also make SiC MOSFETs although they are not commercially available likewise Mitsubishi. Low current SiC thyristors are also available from GeneSiC. It is envisaged that over the coming years, the power handling capability of SiC modules will increase and the cost will decrease, however, this will be driven by market forces. Nevertheless, there are still significant technology barriers impeding the realisation of low cost SiC wafers and devices. Stacking faults, basal plane defects and other crystalline defects associated with SiC limit the wafer yield and the reduced epitaxial growth rate limits the wafer-line production throughput.

| Properties                                               | Silicon               | 4H-SiC                |

|----------------------------------------------------------|-----------------------|-----------------------|

| Energy Band Gap (eV)                                     | 1.11                  | 3.26                  |

| Electron Affinity (eV)                                   | 4.05                  | 3.7                   |

| Relative Dielectric<br>Constant                          | 11.7                  | 9.7                   |

| Thermal Conductivity $(W/cm \cdot K^{-1})$               | 1.5                   | 3.7                   |

| Density of States<br>Conduction Band (cm <sup>-3</sup> ) | 2.8×10 <sup>19</sup>  | 1.23×10 <sup>19</sup> |

| Density of States Valence<br>Band (cm <sup>-3</sup> )    | 1.04×10 <sup>19</sup> | 4.58×10 <sup>18</sup> |

Table 1-1: Fundamental material properties.

#### 1.3 Research Objectives and Contribution

This thesis focusses on the finite element modelling and experimental characterisation of different power semiconductor devices ranging from silicon PiN diodes, to SiC Schottky diodes, silicon IGBTs, CoolMOS super-junction MOSFETs and SiC power MOSFETs. The electrothermal characteristics of these devices under clamped and unclamped inductive switching conditions have been considered both as single devices and as parallel-connected devices. When power devices are implemented in converters, they are

typically connected in parallel to deliver higher current ratings. They can also be connected in series for high voltage blocking capability however, this has not been considered in this thesis. Parallel connection is more so the case for silicon carbide devices where small area MOSFETs with low current conduction ratings are the only option. These devices can exhibit electrothermal non-uniformities arising from several factors including manufacturing variability, gate drive variability, non-uniformities in circuit parasitic inductances, variability in packaging and non-uniformities in the rate of device degradation. How these electrothermal variabilities impact energy balance between the devices will vary from technology to technology. For instance, if parallelconnected MOSFETs have different switching speeds arising from different gate resistances, how will this impact the balance of the switching losses between the devices in transients and in steady state. This is important to consider because it will determine the overall reliability of the converter since the devices will not be equally stressed, hence, one device will degrade faster than another. Furthermore, in potentially destructive switching conditions like unclamped inductive switching, the impact of device-to-device variability between parallel-connected devices on the overall ruggedness of the power converter is very important to be considered since the devices are working beyond the safety operation area (SOA). This thesis also uses finite element simulations to investigate the electrothermal dynamics between parallel connected devices under balanced and unbalanced conditions. Lattice temperature and current density plots extracted from the finite element simulator are used to understand the electrothermal characteristics of the parallel devices. Specifically, this thesis has

Finite Element modelling of power semiconductor devices including silicon

PiN diodes, SiC Schottky diodes, silicon MOSFET, CoolMOS, IGBT and SiC

MOSFET. This modelling includes avalanche mode conduction for silicon

MOSFET, CoolMOS, IGBT and SiC MOSFET. The internal physics of these device in avalanche mode conduction is used to understand the experimental measurements.

- A comparison evaluation of the avalanche ruggedness for silicon 600V/20A

MOSFET and silicon 600V/20A CoolMOS device.

- (3) A comparative electrothermal analysis between parallel connected SiC Schottky diodes and parallel connected silicon PiN diodes. The impact of variation in the switching speed of the complimenting transistor and initial junction temperature of the devices is investigated for both technologies.

- (4) A comparative avalanche ruggedness evaluation between parallel connected SiC Schottky diodes and silicon PiN diodes. The impact of variation in the thermal boundary conditions, switching speed and initial junction temperature on the avalanche ruggedness of the parallel diodes is investigated. Alongside with finite element modelling characterise the diode failure mode in avalanche mode conduction.

- (5) A comparative electrothermal balancing analysis between parallel connected CoolMOS, NPT IGBT and SiC MOSFET under clamped inductive switching conditions. The impact of variation between the thermal boundary conditions (heatsink thermal resistance), the initial junction temperature and the switching speed has been analysed for the different technologies for single and repetitive switching events. Experimental measurements have been confirmed with finite element modelling of each technology.

- (6) A comparative electrothermal ruggedness evaluation between parallel connected CoolMOS devices and parallel connected SiC MOSFETs. The impact of variation in initial junction temperature and switching speed on the

overall ruggedness performance of the parallel pair is investigated for both technologies. The failure mechanism and internal physics is modelled and extracted by the finite element simulator.

#### 1.4 Outline of Thesis

**Chapter 2** provides a brief introduction to the physics of power semiconductor devices for the different device types. Compact modelling and finite element modelling of the power devices are introduced. This section of the thesis focuses on finite element modelling and experimental characterisation of single power devices (transistors and diodes) under clamped and unclamped inductive switching conditions. The finite element simulator is used to explain certain characteristics peculiar to certain devices and experimental measurements are used for confirmation.

**Chapter 3** presents the impact of electrothermal imbalance between parallel connected silicon PiN and SiC Schottky diodes under clamped and unclamped inductive switching conditions. Switching and conduction loss balance between the diodes as a function of electrothermal variation is investigated for both technologies. Also, the avalanche ruggedness of the parallel diodes is investigated as a function of electrothermal variation between the parallel connected pair for both technologies. The results of this chapter have been reviewed, critiqued and accepted as conference publications and will be presented in the IET Power Electronics Machines and Drives (PEMD) conference in Glasgow 2016 as well as the IEEE European Power Electronics (EPE) conference held in Karlsruhe, Germany in 2016.

**Chapter 4** presents the investigation of electrothermal balancing performance between parallel connected devices for silicon IGBTs, SiC MOSFETs and CoolMOS super-

junction MOSFETs. The impact of variation in the thermal boundary conditions, initial junction temperature and switching speeds between the parallel pair have been investigated for the different technologies. This is supported by finite element simulations that give insight into the internal physics of the device through 2-D current density and lattice temperature plots. The methods, analysis and results of this chapter have been published in the IEEE transactions of power electronics and industrial electronics as first author papers by the author is this thesis. The results have also been presented in the IEEE European Power Electronics Conference (EPE) held in Geneva Switzerland in 2015.

In chapter 5, the experimental measurements on the impact of electrothermal variation between parallel connected SiC MOSFETs and parallel connected CoolMOS devices are presented. This chapter investigates how electrothermal variations affects the avalanche ruggedness of the parallel connected devices for different technologies. It explores how this electrothermal variation between the parallel pair degrades the avalanche ruggedness for different avalanche pulses i.e. high power low duration pulses and low power high duration pulses. Electrothermal variations between the parallel pair are introduced by varying the switching rate and initial junction temperature between them. Finite element simulations are used to support the experimental observations and explain the results. The methods, analysis and results of this chapter have been reviewed, critiqued and published as first author journal papers in the IEEE Transactions on Power Electronics and IEEE Transactions on Industrial Electronics by the author of this thesis. The results have also been presented in the IEEE European Power Electronics Conference (EPE) held in Geneva Switzerland in 2015.

**Chapter 6** concludes the thesis and states where further work can improve the results presented here.

10

# Chapter 2. **Power Device Modelling**

#### 2.1 Introduction to Modelling of Power Semiconductor Devices

Power semiconductor devices are at the heart of power electronic converters. They are typically two terminal devices like diodes or three terminal devices like transistors or thyristors. They can be bipolar devices like PiN diodes, BJTs, IGBTs and thyristors or unipolar devices like MOSFETs and Schottky diodes. The modelling of power devices is critical for understanding and predicting the energy conversion losses as well improving reliability. The design loop can be simplified and significant cost saving ensured by using predictive modelling. Since power devices generate heat as a result of conduction and switching losses, and device electrical parameters like threshold voltage, on-state resistance and breakdown voltage are all temperature sensitive, then the device models must account for the feedback loop between the electrothermal. Electrothermal models can be realized in two major ways: by using (a) behavioural-based model, or by (b) physics-based model. Behavioural models are empirical in that they are typically derived from experimental measurements. They can also be reduced forms of more complicated

simulations. Behavioural models are computationally inexpensive and are particularly useful when large systems are simulated in a manner that does not require detailed physical knowledge of the power device [47, 48]. For example, if a wind energy conversion system comprised of the rotating electrical generator, gearbox, converter and transformer were to be simulated, given the time constants of the mechanical components of the system, a behavioural model of the power devices in the converter will suffice. On the other hand, the physics based model requires detailed knowledge of the semiconductor physics behind the operation of the device. This is important for low level device fabrication, converter design and device reliability modelling. Physics based models vary in complexity and speed. For example, SPICE models as less computationally expensive than finite element models, however, cannot account for certain physical phenomena that finite element models can explain. In general, there is a trade-off between simulation accuracy and computational cost. The more accurate a model is, the more computationally expensive it will be.

#### 2.1.1 Compact Device Models

Compact models are more accurate and computationally intensive than behavioural models but not as accurate as finite element models. The mathematical compact model is based on solving physics-based equations with varying degrees of complexity thereby resulting in analytical expressions describing carrier and electrical behaviour.

In the lumped-charge models, carrier dynamics are divided into discrete charges within the device with the charge of each region being considered as its average charge [49, 50]. This offers rapid simulation time however at the cost of reduced accuracy. The lumped-charge model initially developed for simulation of the power diode has also been

exploited for the MOSFET [51] and IGBT [52]. The model is capable of simulating the reverse recovery of the power diode [50].

## 2.1.2 Numerical models

The ambipolar diffusion equation (ADE) model used in compact model implemented the semiconductor equations based on the assumption of quasi-neutrality or principle of the ideal depletion layer behaviour. However, certain non-linear characteristics like the exponential dependence of carrier density on potential limits the accuracy of compact models. Therefore, for a high degree of accuracy, numerical schemes such as finite element or finite difference are good candidates. There are several commercial device simulators including ATLAS, Sentaurus and Medici [47, 53]. These simulators decompose the device under study into a pre-defined mesh with each mesh point investigated individually based on doping level, potential and lattice temperature, etc. During static and dynamic simulations, the hole and electron carrier density at each mesh point is used to derive the electric field and current, and is fed back into the neighbouring mesh points to generate a distributed model. The mesh size must be implemented carefully to avoid numerical instability due to the discrete nature of the model. The mesh size also determines the accuracy of the simulation. Fine meshes will result in higher accuracy but at a cost of reduced computational speed and increased computational cost. ATLAS from SILVACO is typically used by the semiconductor designers for designing devices as well as modelling static and dynamic characteristics. Hence in this thesis, all the simulations are carried out from ATLAS.

## 2.2 Compact Models for Power Semiconductor devices