#### Secure Cryptographic Algorithm Implementation on Embedded Platforms

Michael Tunstall

Technical Report RHUL–MA–2007–5 29 May 2007

Department of Mathematics Royal Holloway, University of London Egham, Surrey TW20 0EX, England http://www.rhul.ac.uk/mathematics/techreports

#### SECURE CRYPTOGRAPHIC ALGORITHM IMPLEMENTATION ON EMBEDDED PLATFORMS

Michael Tunstall

Royal Holloway, University of London

Thesis submitted to The University of London for the degree of Doctor of Philosophy 2006

### Declaration

These doctoral studies were conducted under the supervision of Prof. Chris Mitchell. The equipment for all of the experiments detailed in this thesis was provided *in situ* by Gemalto (formerly Gemplus Card International).

The work presented in this thesis is the result of original research carried out by myself, in collaboration with others, whilst enrolled in the Department of Mathematics as a candidate for the degree of Doctor of Philosophy. This work has not been submitted for any other degree or award in any other university or educational establishment.

> Michael Tunstall October 2006

### Abstract

Sensitive systems that are based on smart cards use well-studied and well-developed cryptosystems. Generally these cryptosystems have been subject to rigorous mathematical analysis in an effort to uncover cryptographic weaknesses in the system. The cryptosystems used in smart cards are, therefore, not usually vulnerable to these types of attacks. Since smart cards are small objects that can be easily placed in an environment where physical vulnerabilities can be exploited, adversaries have turned to different avenues of attack.

This thesis describes the current *state-of-the-art* in side channel and fault analysis against smart cards, and the countermeasures necessary to provide a secure implementation. Both attack techniques need to be taken into consideration when implementing cryptographic algorithms in smart cards.

In the domain of side-channel analysis a new application of using cache accesses to attack an implementation of AES by observing the power consumption is described, including an unpublished extension.

Several new fault attacks are proposed based on finding collisions between a correct and a fault-induced execution of a secure secret algorithm. Other new fault attacks include reducing the number of rounds of an algorithm to make a differential cryptanalysis trivial, and fixing portions of the random value used in DSA to allow key recovery.

Countermeasures are proposed for all the attacks described. The use of random delays, a simple countermeasure, is improved to render it more secure and loss costly to implement. Several new countermeasures are proposed to counteract the particular fault attacks proposed in this thesis. A new method of calculating a modular exponentiation that is secure against side channel analysis is described, based on ideas which have been proposed previously or are known within the smart card industry. A novel method for protecting RSA against fault attacks is also proposed based on securing the underlying Montgomery multiplication. The majority of the fault attacks detailed have been implemented against actual chips to demonstrate the feasibility of these attacks. Details of these experiments are given in appendices. The experiments conducted to optimise the performance of random delays are also described in an appendix.

### List of Publications

The following papers covering work discussed in this thesis have been published.

- H. Bar-El, H. Choukri, D. Naccache, M. Tunstall, and C. Whelan, *The sor-cerer's apprentice guide to fault attacks*, Workshop on Fault Diagnosis an Tolerance in Cryptography, in association with DSN 2004 — The International Conference on Dependable Systems and Networks, June 2004.

- D. Naccache, P. Q. Nguyen, M. Tunstall, and C. Whelan, *Experimenting with faults, lattices and the DSA*, Public Key Cryptography PKC 2005 (S. Vaudenay, ed.), Lecture Notes in Computer Science, vol. 3386, Springer-Verlag, 2005, pp. 16–28.

- D. Naccache, M. Tunstall, and C. Whelan, Computational improvements to differential side channel attacks, NATO Security through Science Series D: Information and Communication Security, vol. 2, IOS Press, 2006, pp. 26–35.

- [4] H. Choukri and M. Tunstall, Round reduction using faults, Workshop on Fault Diagnosis and Tolerance in Cryptography 2005 — FDTC 05 (L. Breveglieri and I. Koren, eds.), 2005, pp. 13–24.

- H. Bar-El, H. Choukri, D. Naccache, M. Tunstall, and C. Whelan. *The sor-cerer's apprentice guide to fault attacks*, Proceedings of the IEEE 94 (2006), no. 2, 370–382.

- [6] H. Choukri and M. Tunstall. *Fault attacks*. In H. Bidgoli, editor, Handbook of Information Security, Wiley, 2006, pp. 230–240.

- [7] M. Tunstall, S. Petit, S. Porte. Smart card security. In H. Bidgoli, editor, Handbook of Information Security, Wiley, 2006, pp. 326–341.

- [8] C. Clavier and M. Tunstall. Explaining differential fault analysis on DES. Workshop on Coding and Cryptography, Cork, May 2006.

- [9] J. Fournier and M. Tunstall, Cache based power analysis attacks on AES, 11<sup>th</sup> Australasian Conference on Information Security and Privacy — ACISP 2006 (L. M. Batten and R. Safavi-Naini, eds.), Lecture Notes in Computer Science, vol. 4058, Springer-Verlag, 2006, pp. 17–28.

- F. Amiel, C. Clavier and M. Tunstall. Fault analysis of DPA-resistant algorithms. Fault Diagnosis and Tolerance in Cryptography 2006 FDTC 06 (L. Breveglieri, I. Koren, D. Naccache and J.-P. Seifert, eds.), Lecture Notes in Computer Science, vol. 4236, Springer-Verlag, 2006, pp. 223–236.

- [11] O. Benoit and M. Tunstall. *Efficient use of random delays*, Cryptology ePrint Archive, Report 2006/272, 2006, http://eprint.iacr.org/.

- [12] K. Markantonakis, K. Mayes, M. Tunstall, D. Sauveron and F. Piper. Smart card security. Computational Intelligence in Information Assurance and Security (N. Nedjah, A. Abraham, and L. M. Mourelle, eds.), Studies in Computational Intelligence, vol. 57, Springer-Verlag, 2007, pp. 201-233.

- M. Tunstall and O. Benoit. Efficient use of random delays in embedded software. Workshop on Information Security Theory and Practices 2007

— Smart Cards, Mobile and Ubiquitous Computing Systems — WISTP 2007 (D. Sauveron, K. Markantonakis, A. Bilas and J.-J. Quisquater, eds.), Lecture Notes in Computer Science, vol. 4462, Springer-Verlag, 2007, pp. 27–38.

### Acknowledgements

A debt of gratitude is owed to David Naccache without whom this thesis would never have been written. When I joined Gemplus in 1998, David tried to motivate me to further my education as far as possible. He even tried to tried to appeal to my Anglo-Saxon roots by pointing out that salaries generally increase in a logarithmic fashion, and that extra qualifications shift this curve upwards. David also helped with the progression of this thesis by involving me in several research projects. These were instrumental in starting the creative process that led to other publications.

I would like to thank Nathalie Feyt and Chris Mitchell for the help and encouragement they gave me during my research, particularly when I was unsure whether certain ideas were worth pursuing.

I would like to thank Konstantinos Markantonakis and Keith Mayes from Royal Holloway's Smart Card Centre for their support. In particular, for the position of Research Assistant afforded to me in the last year of my research.

I would like to thank everyone with whom I worked at Gemplus, who taught me an immense amount about cryptography, side channel analysis and fault attacks. Without their help, support and friendship this thesis could not have been written. In particular, I would like to thank: Frederic Amiel, Philippe Anguita, Bruno Baronnet, Olivier Benoit, Julien Brouchier, Eric Brier, Benoit Chevalier-Mames, Hamid Choukri, Christophe Clavier, Nora Dabbous, Jean-Francois Dhem, Jacques Fournier, Laurent Gauteron, Pascal Guterman, Helena Handschuh, Marc Joye, Laurent Bonnet, Nathalie Feyt, Philippe Loubet-Moundi, Pascal Moitrel, Christophe Mourtel, Johan Pascal, David Naccache, Khanh Nguyen, Francis Olivier, Pascal Pailler, Sebastien Petit, Florence Ques, Stephanie Porte, Philippe Proust, Alexei Tchoulkine, Lionel Victor, and Karine Villegas.

I would also like to thank my co-authors, with whom it has been educational and inspirational to work with. They are Frederic Amiel, Hagai Bar-el, Olivier Benoit, Hamid Choukri, Jacques Fournier, Konstantinos Markantonakis, Keith Mayes, Fred Piper, David Naccache, Khanh Nguyen, Phong Q. Nguyen, Sebastien Petit, Stephanie Porte, Damien Sauveron, and Claire Whelan.

I would like to thank Benoit Chevalier-Mames, Chris Mitchell, Will Sirett and John Tunstall for their help in proof reading this thesis and the other articles that I have published. In particular, I would like to thank Chris Mitchell for the sterling effort he put into helping me prepare the final version of this thesis.

I would like to thank Kenny Paterson and Mike Scott for the time they committed to examining this thesis. Their comments and suggestions have made a significant contribution to increasing the quality of this thesis.

Lastly, I would like to thank my family for their support, and for putting up with me while I was writing up this thesis.

## Contents

| D             | eclar                         | ation                            | 2  |

|---------------|-------------------------------|----------------------------------|----|

| A             | bstra                         | ıct                              | 3  |

| $\mathbf{Li}$ | st of                         | Publications                     | 5  |

| A             | ckno                          | wledgements                      | 7  |

| C             | ontei                         | nts                              | 9  |

| $\mathbf{Li}$ | st of                         | Tables                           | 15 |

| $\mathbf{Li}$ | st of                         | Figures                          | 16 |

| $\mathbf{Li}$ | st of                         | Algorithms                       | 18 |

| N             | Notation and Abbreviations 20 |                                  |    |

| 1             | Intr                          | roduction                        | 23 |

|               | 1.1                           | Summary of Contributions         | 25 |

|               | 1.2                           | Structure                        | 26 |

| <b>2</b>      | Cry                           | ptographic Algorithms            | 29 |

|               | 2.1                           | Data Encryption Standard         | 29 |

|               | 2.2                           | Advanced Encryption Standard     | 31 |

|               | 2.3                           | RSA                              | 33 |

|               | 2.4                           | The Digital Signature Standard   | 36 |

| 3             | $\mathbf{Sm}$                 | art Card Architecture            | 38 |

|               | 3.1                           | What is a Smart Card?            | 38 |

|               | 3.2                           | Microprocessors                  | 41 |

|               |                               | 3.2.1 Cryptographic Coprocessors | 42 |

|   |      | 3.2.2 Random Number Generators             |

|---|------|--------------------------------------------|

|   |      | 3.2.3 Cache                                |

|   |      | 3.2.4 Anomaly Sensors                      |

|   |      | 3.2.5 Chip Features                        |

|   | 3.3  | Summary and Conclusions                    |

| 4 | Side | e Channel Analysis Techniques 48           |

|   | 4.1  | Timing Analysis                            |

|   | 4.2  | Simple Power Analysis                      |

|   | 4.3  | Statistical Power Analysis                 |

|   |      | 4.3.1 Modelling the Power Consumption      |

|   |      | 4.3.2 Differential Power Analysis          |

|   |      | 4.3.3 Correlation Power Analysis           |

|   |      | 4.3.4 Comparing the Different Methods      |

|   | 4.4  | Electromagnetic Analysis                   |

|   | 4.5  | Summary and Conclusions                    |

| 5 | Fau  | It Injection Techniques 62                 |

|   | 5.1  | Injection Techniques                       |

|   | 5.2  | The Types of Fault                         |

|   |      | 5.2.1 Provisional Faults (Taxonomy)        |

|   |      | 5.2.2 Destructive Faults (Taxonomy)        |

|   | 5.3  | Fault Models    6'                         |

|   | 5.4  | Combining Faults with Side Channel Attacks |

|   | 5.5  | Summary and Conclusions                    |

| 6 | Ger  | eric Attacks 71                            |

|   | 6.1  | Simple Power Analysis of Key Manipulation  |

|   | 6.2  | Cache-Based Power Analysis                 |

|   |      | 6.2.1 The First ByteSub Function           |

|   |      | 6.2.2 Finding the Rest of the Key          |

|   |      | 6.2.3 Other Algorithms                     |

|   | 6.3 | Fault Attacks on Key Transfer or NVM82      |

|---|-----|---------------------------------------------|

|   | 6.4 | Round Reduction Using Faults                |

|   | 6.5 | Summary and Conclusions                     |

| 7 | Gen | neric Countermeasures 88                    |

|   | 7.1 | The Basic Principles                        |

|   | 7.2 | Desynchronisation Techniques                |

|   |     | 7.2.1 Desynchronisation in Software         |

|   |     | 7.2.2 Desynchronisation in Hardware         |

|   | 7.3 | Execution Randomisation                     |

|   | 7.4 | Data Whitening                              |

|   | 7.5 | Integrity Checks                            |

|   | 7.6 | Summary and Conclusions                     |

| 8 | Blo | ck Cipher Implementations 100               |

|   | 8.1 | Power Analysis of Block Ciphers             |

|   | 8.2 | Differential Fault Analysis                 |

|   |     | 8.2.1 The Fifteenth Round                   |

|   |     | 8.2.2 Faults in Earlier Rounds              |

|   |     | 8.2.3 Triple DES                            |

|   |     | 8.2.4 Other Algorithms                      |

|   | 8.3 | Collision Fault Analysis                    |

|   |     | 8.3.1 Attacking DES                         |

|   |     | 8.3.2 DPA-Resistant Algorithms              |

|   |     | 8.3.3 Other Algorithms                      |

|   | 8.4 | Changing S-Box Values                       |

|   |     | 8.4.1 Modifying Known S-Box Values of DES   |

|   |     | 8.4.2 Modifying Unknown S-Box Values of DES |

|   |     | 8.4.3 Other Algorithms                      |

|   | 8.5 | Countermeasures                             |

|   | 8.6 | Summary and Conclusions                     |

| 9  | Imp  | lement  | tations of RSA                                | 129 |

|----|------|---------|-----------------------------------------------|-----|

|    | 9.1  | Simple  | Power Analysis of RSA                         | 130 |

|    | 9.2  | Statist | ical Power Analysis of RSA                    | 131 |

|    | 9.3  | Fault A | Attack on RSA Signature with CRT              | 132 |

|    | 9.4  | Fault A | Attack on RSA Signature Without CRT           | 132 |

|    | 9.5  | Faults  | in the Modulus                                | 136 |

|    |      | 9.5.1   | Forging a Signature                           | 136 |

|    |      | 9.5.2   | Recovering the Key                            | 138 |

|    | 9.6  | Expon   | entiation Algorithms                          | 139 |

|    |      | 9.6.1   | Side Channel Resistant Algorithms             | 141 |

|    |      | 9.6.2   | Fault Resistant Algorithms                    | 146 |

|    |      | 9.6.3   | Attacking Side Channel Resistant Algorithms   | 147 |

|    | 9.7  | Secure  | Exponentiation Using CRT                      | 147 |

|    |      | 9.7.1   | Side Channel Resistant Algorithms             | 148 |

|    |      | 9.7.2   | Fault Resistant Algorithms                    | 148 |

|    | 9.8  | Secure  | Montgomery Multiplication                     | 150 |

|    |      | 9.8.1   | Side Channel Resistant Algorithms             | 151 |

|    |      | 9.8.2   | Fault Resistant Algorithms                    | 153 |

|    |      | 9.8.3   | Modified Montgomery Algorithm with Redundancy | 154 |

|    |      | 9.8.4   | RSA Computation using CRT with Redundancy     | 156 |

|    | 9.9  | Compa   | aring the Fault Protection Methods            | 159 |

|    | 9.10 | Counte  | ermeasures                                    | 161 |

|    | 9.11 | Summa   | ary and Conclusions                           | 162 |

| 10 | Imp  | lement  | tations of DSA                                | 164 |

|    | 10.1 | Power   | Attacks on DSA                                | 164 |

|    | 10.2 | Faults  | in the Private Key                            | 165 |

|    |      |         | in the Nonce                                  |     |

|    |      |         | ermeasures                                    |     |

|    |      |         | ary and Conclusions                           |     |

|    |      |         | •                                             |     |

| 11           | Conclusion                                       | 172 |

|--------------|--------------------------------------------------|-----|

|              | 11.1 Summary of Contributions                    | 172 |

| A            | Optimising the Differential Calculation          | 175 |

|              | A.1 The Global Sum                               | 176 |

|              | A.2 Formation of Waveform Equivalence Classes    | 177 |

|              | A.3 Combining Waveforms                          | 179 |

|              | A.4 Chosen Plaintext Differential Power Analysis | 182 |

|              | A.5 Optimisation Results                         | 183 |

|              | A.6 Remarks                                      | 184 |

| в            | Finding Glitch Parameters                        | 186 |

| С            | Attacking a Key Transfer                         | 189 |

| D            | Round Reduction of AES                           | 192 |

|              | D.1 The Possible Effects                         | 193 |

|              | D.2 Experimental Results                         | 194 |

| $\mathbf{E}$ | Efficient Use of Random Delays                   | 197 |

|              | E.1 Design Criteria                              | 197 |

|              | E.2 Deriving a Suitable Distribution             | 198 |

|              | E.3 Reverse Engineering the Distribution         | 203 |

|              | E.3.1 Potential Attack Scenarios                 | 203 |

|              | E.3.2 Hypothesis Testing                         | 205 |

|              | E.4 Remarks                                      | 206 |

| $\mathbf{F}$ | Differential Fault Analysis on DES               | 207 |

| G            | CFA of the First XOR of DPA-Resistant AES        | 210 |

| н            | CFA of the Key Masking of DPA-Resistant AES      | 214 |

| Ι            | S-Box Modification in DPA-Resistant DES          | 217 |

| J            | Security Analysis of Montgomery Multiplication with Redundancy | y   |

|--------------|----------------------------------------------------------------|-----|

|              | Check                                                          | 219 |

| K            | Implementation of Montgomery Multiplication with Redundancy    | y   |

|              | Check                                                          | 222 |

| $\mathbf{L}$ | Glitching k During DSA Computations                            | 227 |

| Bi           | bliography                                                     | 232 |

## List of Tables

| 6.1  | The Biham–Shamir Attack                                                      | 82  |

|------|------------------------------------------------------------------------------|-----|

| 7.1  | Parameter characteristics for tables of $2^9$ entries $\ldots \ldots \ldots$ | 94  |

| 8.1  | Frequency of input and output pairs for the first S-box                      | 104 |

| 8.2  | The expected number of hypotheses per S-box for one faulty cipher-           |     |

|      | text block                                                                   | 105 |

| 8.3  | The expected number of hypotheses per S-box for two faulty cipher-           |     |

|      | text blocks                                                                  | 105 |

| 8.4  | The expected number of hypotheses per S-box when $L_{15} \neq L_{15}'$       | 108 |

| 8.5  | The fraction of possible differentials per S-box. $\ldots$                   | 112 |

| 8.6  | The hypotheses generated by attacking a compressed S-box                     | 121 |

| 9.1  | The number of faulty signatures required to identify one byte                | 136 |

| 10.1 | Experimental attack percentage success rates: $n$ is the number of           |     |

|      | bytes reset in $k$ , and $d$ is the number of signatures                     | 169 |

| A.1  | Optimisation results                                                         | 183 |

| C.1  | The Biham–Shamir attack                                                      | 189 |

| E.1  | Parameter Characteristics for Tables of $2^9$ Entries $\ldots \ldots \ldots$ | 202 |

| E.2  | Parameter Characteristics for Tables of $2^{10}$ Entries                     | 203 |

| F.1  | The breakdown of hypotheses per ciphertext block                             | 209 |

| G.1  | Information derived from 72 collisions                                       | 210 |

| H.1  | Information derived from 60 collisions                                       | 214 |

| K.1  | Speed comparisons                                                            | 224 |

# List of Figures

| 2.1 | The DES round function for round $n$                                                     | 30 |

|-----|------------------------------------------------------------------------------------------|----|

| 3.1 | Classic shape and dimensions of a smart card                                             | 39 |

| 3.2 | A front and rear view of a micromodule before it is set into a plastic                   |    |

|     | card                                                                                     | 39 |

| 3.3 | Communication initialisation between a smart card and a reader                           | 41 |

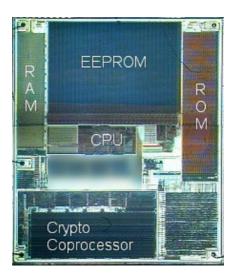

| 3.4 | A chip surface with readily identifiable features                                        | 46 |

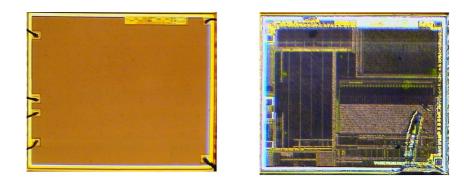

| 3.5 | A chip with a shield present and removed. Removing a shield us-                          |    |

|     | ing hydrofluoric acid renders the chip non-functional but allows the                     |    |

|     | layout to be determined                                                                  | 47 |

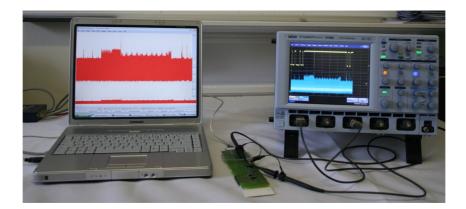

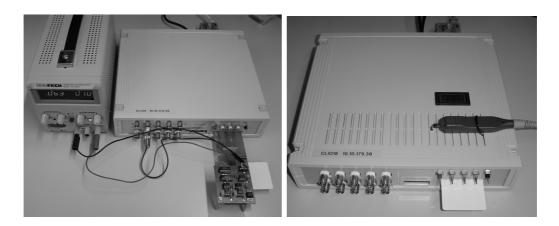

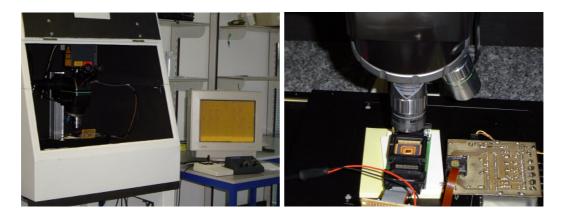

| 4.1 | Data acquisition tools.                                                                  | 49 |

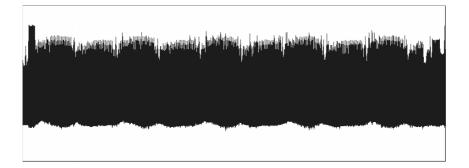

| 4.2 | The power consumption of an unprotected modular exponentiation                           |    |

|     | implemented using the square and multiply algorithm                                      | 50 |

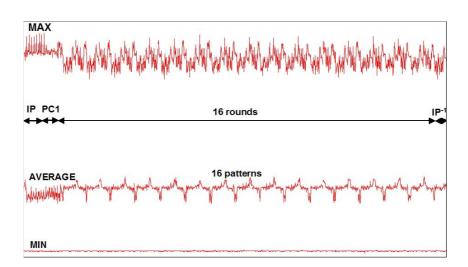

| 4.3 | The power consumption of a DES implementation showing the rounds                         |    |

|     | of the algorithm.                                                                        | 51 |

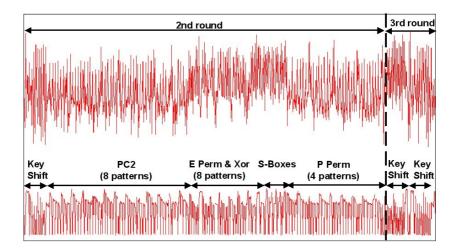

| 4.4 | The power consumption of a DES implementation showing the round                          |    |

|     | functions.                                                                               | 52 |

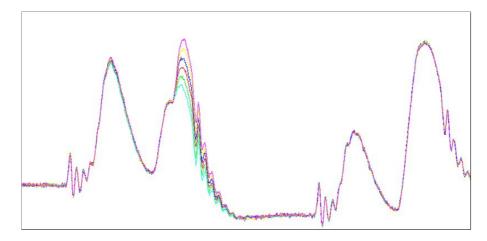

| 4.5 | Overlaid acquisitions of the power consumption produced by the same                      |    |

|     | instruction but with varying data.                                                       | 54 |

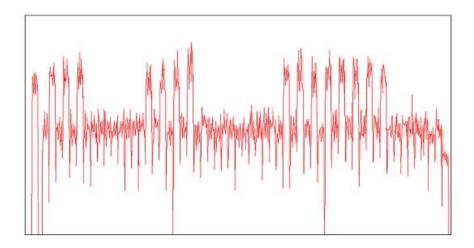

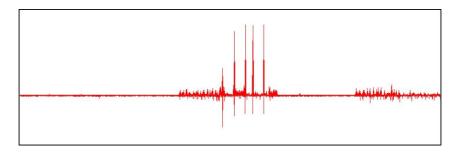

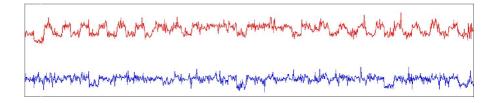

| 4.6 | A DPA trace                                                                              | 56 |

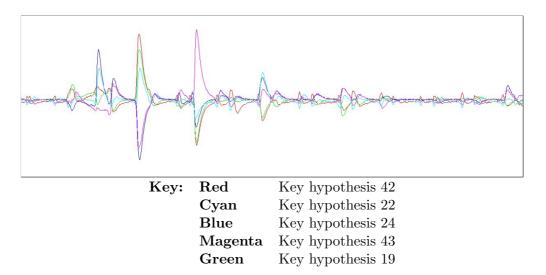

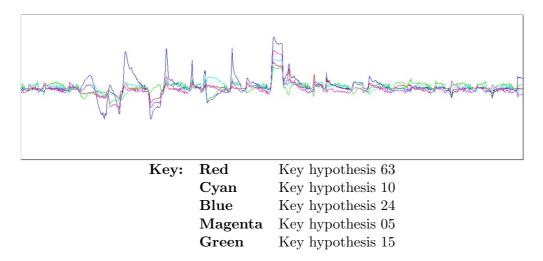

| 4.7 | DPA traces on bit 1 of S-box <sub>1</sub> for various guesses (correct guess is 24).     | 58 |

| 4.8 | CPA traces on 4 bits of S-box <sub>1</sub> for various guesses (correct guess is $24$ ). | 59 |

| 4.9 | Electromagnetic probing of a chip                                                        | 61 |

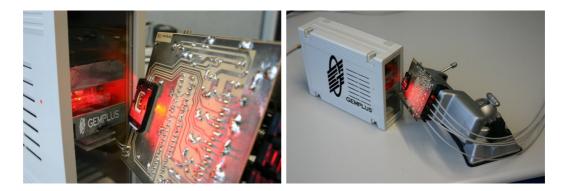

| 5.1 | Supply voltage glitch fault injection equipment.                                         | 63 |

| 5.2 | White light fault injection equipment.                                                   | 64 |

| 5.3 | Laser fault injection equipment                                                          | 65 |

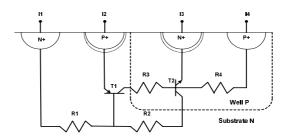

| 5.4 | Single event latch-up — parasitic transistors T1 and T2 67                      |

|-----|---------------------------------------------------------------------------------|

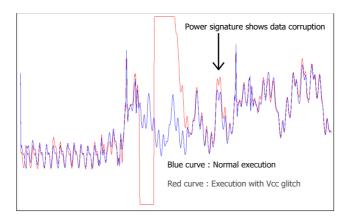

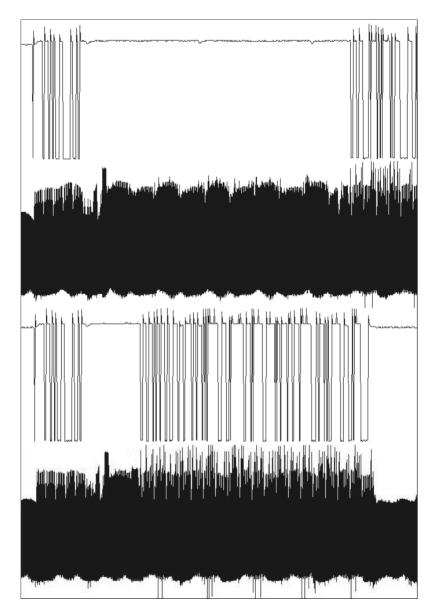

| 5.5 | The effect of a glitch on data being manipulated by a chip, as visible          |

|     | in the power consumption                                                        |

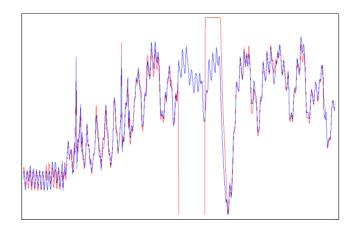

| 5.6 | The effect of a glitch on an instruction, where the instruction during          |

|     | the glitch is affected                                                          |

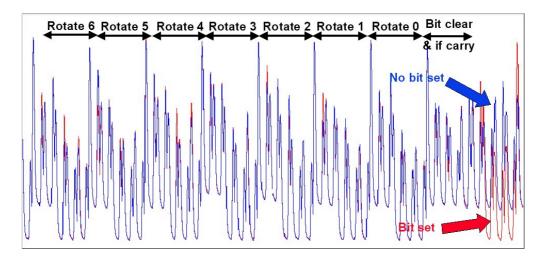

| 6.1 | Two power consumption acquisitions showing the difference produce               |

|     | by a conditional bit set                                                        |

| 6.2 | The effect of a successful round-reducing fault on the $\mathrm{I/O}$ and power |

|     | consumption                                                                     |

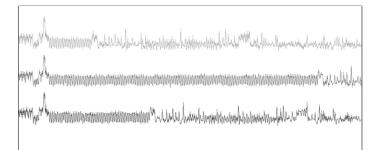

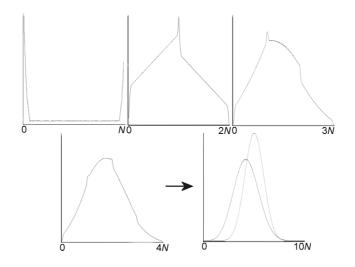

| 7.1 | Random delays visible in the power consumption over time 91                     |

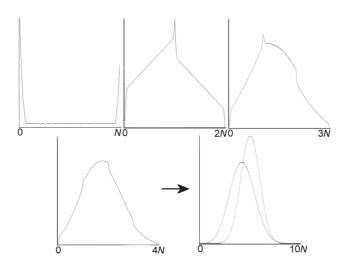

| 7.2 | The cumulative random delay                                                     |

| 7.3 | The cumulative random delay using a modified distribution 95                    |

| 7.4 | Unstable internal clock generation, as visible in the power consumption. 96     |

| 9.1 | The electromagnetic emanations of an RSA implementation 130                     |

| 9.2 | An example calculation path for the square and multiply algorithm. 131          |

| B.1 | A modified Clio reader                                                          |

| D.1 | A power consumption waveform that shows the rounds of AES visible               |

|     | as a repeating pattern                                                          |

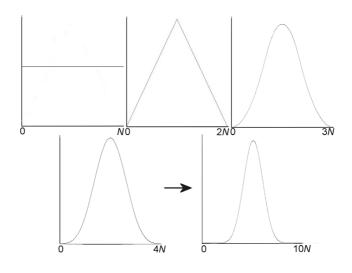

| E.1 | An example of a modified probability function                                   |

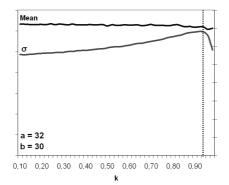

| E.2 | The mean and the standard deviation against $k$ for approximately               |

|     | equal values of $a$ and $b$                                                     |

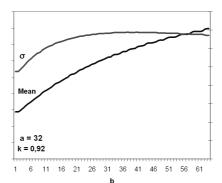

| E.3 | The mean and the standard deviation against $b$ for fixed values of $a$         |

|     | and $k$                                                                         |

| E.4 | The cumulative random delay using a modified distribution 204                   |

| L.1 | Experimental set up                                                             |

| L.2 | $\mathrm{I/O}$ and power consumption (beginning of the trace of the command     |

|     | used to generate signatures)                                                    |

# List of Algorithms

| 2.1  | Advanced Encryption Standard                                                                                     | 31  |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | The <b>MixColumn</b> Function                                                                                    | 32  |

| 2.3  | The <b>xtime</b> function                                                                                        | 33  |

| 2.4  | The AES Key Schedule                                                                                             | 33  |

| 4.1  | The Square and Multiply Algorithm                                                                                | 51  |

| 6.1  | Insecure bitwise permutation function                                                                            | 72  |

| 6.2  | Secure bitwise permutation function                                                                              | 73  |

| 6.3  | One Round of the Advanced Encryption Standard                                                                    | 84  |

| 7.1  | Randomised Data Transfer                                                                                         | 97  |

| 7.2  | Randomising S-Box Values                                                                                         | 97  |

| 8.1  | The First XOR                                                                                                    | 115 |

| 8.2  | Masking the Key                                                                                                  | 119 |

| 9.1  | Predicting $d \mod p$ by counting $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 138 |

| 9.2  | The Square and Multiply Algorithm                                                                                | 140 |

| 9.3  | The $(M, M^3)$ Algorithm                                                                                         | 141 |

| 9.4  | The 2-ary Algorithm                                                                                              | 142 |

| 9.5  | Side Channel Atomic Square and Multiply Algorithm                                                                | 143 |

| 9.6  | The Square and Multiply Always Algorithm                                                                         | 144 |

| 9.7  | Randomised Exponentiation Algorithm                                                                              | 144 |

| 9.8  | Secure 2-ary Algorithm                                                                                           | 146 |

| 9.9  | Randomised Exponentiation Algorithm using CRT                                                                    | 148 |

| 9.10 | Verifying the computation of the RSA algorithm using CRT $\ \ . \ . \ .$                                         | 149 |

| 9.11 | Infective computation of RSA                                                                                     | 150 |

| 9.12 | Montgomery Multiplication                                                                                        | 151 |

| 9.13 | Time Constant Montgomery Multiplication                                                                          | 152 |

| 9.14 | Montgomery Multiplication with Redundancy                                                                        | 155 |

| 9.15 | Modular Multiplication with Redundancy                                                                           | 157 |

| 9.16 | Montgomery Exponentiation with Redundancy                                                                   | 158 |

|------|-------------------------------------------------------------------------------------------------------------|-----|

| 9.17 | RSA Computation with Redundancy                                                                             | 159 |

| K.1  | Calculate $\mathbf{A} \leftarrow \mathbf{A} + u_i \mathbf{N} \mod (b-1) \ldots \ldots \ldots \ldots \ldots$ | 223 |

### Notation and Abbreviations

- | Divides, i.e. A|B means that A divides B.

- $\wedge$  the logical AND function.

- $\neg$  the logical NOT function.

- $\vee$  the logical OR function.

- $\lambda$  the Carmichael function, where  $\lambda(n)$  is defined for n as the smallest integer m such that  $a^m \equiv 1 \pmod{n}$  for every integer a that is coprime to n.

- $\phi$  Euler's Totient function, where  $\phi(x)$  equals the number of positive integers less than x which are coprime to x.

- 3G This refers to the third generation mobile standards developed by 3GPP. These standards seek to address the security problems encountered with the GSM standards.

- **ALU** Arithmetic Logic Unit, the part of a chip's CPU that conducts arithmetic and logical calculations.

- **BNC** A BNC connector is commonly used to terminate coaxial cable, and is often used on oscilloscopes.

- **Comp128** the original authentication algorithm for 2G GSM networks, although this algorithm was never standardised nor officially recommended for use. The details of this algorithm are not officially in the public domain.

- Coprime two numbers are said to be coprime if they share no common divisors.

- CDMA Code Division Multiple Access, a form of multiplexing. This is used in a U.S. standard defined by QUALCOMM for mobile communications.

- **CRT** Chinese Remainder Theorem.

- **EEPROM** Electrically Erasable and Programmable Read Only Memory, used to store code and personalisation data such as cryptographic keys.

- gcd Greatest Common Divisor.

- **GSM** Global System for Mobile Communications, the most common system used for mobile phones.

- Hamming distance the number of bits that differ between two binary strings (of equal length), or, equivalently, the Hamming weight of the XOR of the two strings.

- $\mathbf{GF}$  Galois field.

Hamming weight — the number of bits set to 1 in a given bit string.

- LFSR Linear Feedback Shift Register, often used to generate pseudo-random numbers.

- **NVM** Non-Volatile Memory, such as EEPROM, flash memory or ROM.

- **OS** Operating System.

- Pr Probability function.

- **ROM** Read-Only Memory, used in smart cards to contain the operating system that is unchanging from one user to another.

- **S-box** Used to refer to a substitution table in a cryptographic algorithm; these are a common feature of block ciphers.

- **Smooth** Describes a number whose factors consist solely of relatively small numbers.

- **Subscripts** The base of a value is determined by a trailing subscript, which is applied to the whole word preceding the subscript. For example,  $FE_{16}$  is 254 expressed in base 16, and  $d = (d_x, d_{x-1}, \ldots, d_0)_2$  gives a binary expression for d.

- **XOR** Exclusive-OR, or a bitwise addition with no carry propagation. This is also denoted by the  $\oplus$  symbol.

- $\mathbbm{Z}$  The ring of integers under addition and multiplication.

- $\mathbb{Z}_p$  The ring of integers modulo p.

# Chapter 1 Introduction

In recent years, smart cards have become one of the most common secure computing devices. Their uses include such diverse applications as: providing a secure wireless communication framework (GSM, CDMA or 3G), banking and identification. The secure microprocessors used in smart cards are also starting to appear in other devices, such as Dongles used to protect software from unauthorised reproduction [103]. The security of cryptographic algorithms implemented on embedded devices is discussed in terms of smart cards in this thesis. However, the attacks and countermeasures are potentially relevant to all devices that make use of cryptographic algorithms on secure microprocessors.

Direct threats to smart card security include invasive attacks (that alter the chip inside the card), analysis of a side channel (data leaked from inside the card), induced faults, as well as more traditional forms of attack. A variety of countermeasures can be implemented in a smart card to prevent successful attacks that are particular to secure microprocessors.

This thesis describes the current *state-of-the-art* in side channel and fault analysis against smart cards. A brief description of these topics is given below.

Side channel Attacks: Side channel analysis is a class of attacks that seek to deduce information in an indirect manner. This is achieved by extracting secret information held inside a device, such as a smart card, via the monitoring of information that leaks naturally during its operation.

The first publicly described attack of this type was a timing attack against

RSA and certain other public key cryptographic primitives [60]. Publication of this initial result was followed by attacks using power consumption [61] and electromagnetic emanations [39] as a side channel to extract information.

Fault Attacks: In recent years fault analysis has come to the foreground as a possible means of attacking devices such as smart cards. This idea was originally proposed in 1997 [23], in the form of a fault attack against RSA.

The vast majority of papers written on this subject involve very specific faults (usually a bit-flip in a specific variable) that are extremely difficult to produce in practice. However, several attacks have been published that have enough flexibility in the type of fault required that they can be realised with current fault injection methods.

Fault attacks have been implemented against chips that could be used in smart cards [8]. This has meant that countermeasures against this type of attack need to be implemented in embedded devices to protect against this class of attack, which have predominantly been implemented against secure devices such as smart cards. However, it has been shown that some of these attacks can also be applied to standard computers [44].

Both attack techniques need to be taken into consideration when implementing cryptographic algorithms in smart cards. The attacks detailed in this thesis are discussed in terms of smart cards, but it is reasonable to assume that other forms of secure portable devices will also be vulnerable to these attacks. Attacks on embedded platforms, and the necessary countermeasures, that require multi-threaded systems [14] or large memories [44] will not be considered.

The attacks and countermeasures are discussed in terms of software implementations. It is assumed at all times that the underlying hardware is vulnerable to side channel and fault attacks when an algorithm is implemented in a naïve manner. Hardware countermeasures are mentioned where necessary, but it is not always possible to include such functionality in a chip, and little detail is therefore given regarding hardware aspects.

#### **1.1 Summary of Contributions**

The following summarises the contributions discussed in this thesis.

- An implementation of a key transfer attack specified in Section 6.1 is described in Appendix C.

- A novel way of applying cache-based side channel analysis to an implementation of AES on smart cards is given in Section 6.2.

- An implementation of a fault attack that reduces the number of rounds of a block cipher is discussed in Section 6.4, and the implementation details are given in Appendices B and D. These were implemented on a Microchip Silvercard.

- Random delays can be used to increase the difficulty of implementing an attack. This is described in Section 7.2, along with a method for optimising the performance and efficiency of this countermeasure. Appendix E shows how this optimisation was derived, and how this can be applied to random delays of any length.

- Four novel attacks based on injecting faults into DPA countermeasures are described in Sections 8.3.2, 8.4.1 and 8.4.2. The implementations of these four attacks are discussed in Appendices G, H, and I.

- In Section 9.4 the currently accepted specification of a fault attack on the private exponent of RSA (when calculated without using the Chinese Remainder Theorem) was shown to be false when more than one bit of the private exponent is changed. An alternative fault model is proposed in which the attack is valid.

- A new modular exponentiation algorithm is given in Algorithm 9.8, in Section 9.6.1, although this is based on previously published countermeasures.

- A novel method of securing the Montgomery multiplication algorithm against fault attacks is given in Section 9.8. This includes how the algorithm can be

securely used to calculate a modular exponentiation. An informal analysis of this suggests that this algorithm is robust against a range of fault attacks. A description of an implementation of this algorithm on 32-bit chip and the results of attempting to overcome the countermeasure by injecting faults with a laser are given in Appendix K.

- An application of a fault attack that fixes certain values of the random value used in DSA is described in Section 10.3, and an implementation of this attack is described in Appendix L. This is the first published practical implementation of an attack of this type.

- Methods for optimising the calculation of DPA traces are described in Appendix A.

#### 1.2 Structure

The initial chapters of this thesis concern themselves with the background to side channel and fault attacks. Chapter 2 details the commonly used cryptographic algorithms that are found in most smart cards. Chapter 3 explains what a smart card is, and why there is interest in using smart cards to calculate cryptographic algorithms. Some of the chip features used for performance or security, are also detailed, and will be referred to in later chapters. Chapter 4 describes the side channels that are available when attacking a smart card. Timing and Simple Power Analysis attacks are briefly discussed, and the capabilities of each type of attack are described. A more detailed study is made of statistical power analysis, and a comparison of two methods used to extract information is given. Electromagnetic Power Analysis is also briefly described. Chapter 5 describes the various methods of injecting faults that could be used by an attacker. The effects that these faults could have on the execution of a cryptographic algorithm are also given, and a fault model is proposed.

The following chapters contain generic attacks and countermeasures that need to be taken into account when implementing cryptographic algorithms on smart cards. Chapter 6 details generic attacks that could be applied to any implementation of a cryptographic algorithm on a smart card. These include manipulating the key, transferring a key from NVM to RAM, and cutting short repeating loops. Accessing S-boxes via a cache is also considered and extended further in this thesis. Chapter 7 details the countermeasures required to prevent the attacks already described, and that should be applied to every embedded implementation of cryptographic algorithms to prevent side channel and fault attacks. This includes an optimisation to the use of random delays to improve the performance and security of systems.

Chapters 8–10 are more concerned with specific algorithms. Chapter 8 details certain attacks that are predominantly applicable to block ciphers. The application of the previously described power attacks is discussed in terms of block ciphers. The first fault attack described is Differential Fault Analysis, followed by Collision Fault Analysis. The modification of S-box elements is then discussed separately, as it draws upon both Differential and Collision Fault Analysis. A list of countermeasures required to protect an implementation of a block cipher is also given.

Chapter 9 contains a similar analysis to that given in Chapter 8, but for the RSA algorithm when implemented using either a simple modular exponentiation or using the Chinese Remainder Theorem (CRT) [58]. The procedure of applying Simple and Statistical Power Analysis to the RSA signature is described. The numerous fault attacks that can be applied to the RSA signature scheme by modifying different variables of the algorithm are described. This is followed by a description of the various modular exponentiation algorithms that can be used to calculate the RSA algorithm. Methods of rendering these algorithms secure against power analysis are then discussed, including a new algorithm, followed by a description of how the algorithm can be defended against fault attacks. This discussion is then repeated for the RSA signature scheme when computed using the CRT. The security of the underlying multiplication algorithm is also addressed by proposing a secure Montgomery multiplication algorithm that is resistant to side channel and fault attacks. Some discussion of the various fault countermeasure techniques is also given and, as previously, a list of countermeasures is given for a secure implementation of the RSA signature scheme on an embedded chip.

Chapter 10 describes the security issues surrounding the implementation of DSA

on an embedded device. This chapter is relatively brief, as a large portion of the attacks and countermeasures are already discussed in Chapter 9, but the use of a random value in the algorithm requires a different type of countermeasure. An attack based on modifying the random value is described. This is followed by a discussion of the possible countermeasures that can be applied to protect the generation of the random value. This is followed by the Conclusion in Chapter 11.

Appendix A describes how the calculation of DPA traces can be optimised. Appendix B details how glitch parameters for a smart card can be determined, using Microchip's Silvercard as an example. Appendix E shows how the use of random delays can be optimised, and how this can be applied to random delays of any length. Appendices C, D, F, G, H, I, and L describe various fault attacks and how they are implemented. Appendix K describes experiments performed to validate the countermeasure proposed for Montgomery multiplication.

### Chapter 2

## **Cryptographic Algorithms**

Numerous cryptographic algorithms are in use today. In this chapter some of the most commonly used cryptographic algorithms are detailed. These descriptions cover algorithms that can be used as examples in generic attacks and countermeasures. Later in this thesis a description of how implementations of these algorithms can be made to resist side channel and fault attacks is given. DES and AES are also used as examples of generic attacks before the algorithm specific attacks are discussed.

The Data Encryption Standard is described in Section 2.1, the Advanced Encryption Standard is described in Section 2.2, RSA is detailed in Section 2.3, and a description of the Digital Signature Standard is given in Section 2.4.

#### 2.1 Data Encryption Standard

The Data Encryption Standard (DES) was introduced by NIST in the mid 1970s [78], and was the first openly available cryptography standard. It has since become a worldwide *de facto* standard for numerous purposes. It is only in recent years that it has been practically demonstrated that an exhaustive search of the keyspace is possible, leading to the introduction of triple DES and the development of the Advanced Encryption Standard (AES) (see Section 2.2).

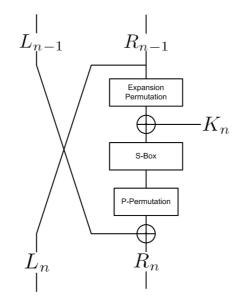

DES can be considered as a transformation of two 32-bit variables  $(L_0, R_0)$ , i.e. the message block, through sixteen iterations of the Feistel structure, shown in Figure 2.1, to produce a ciphertext block  $(L_{16}, R_{16})$ . The Expansion and Ppermutations are bitwise permutations. For clarity of expression, these permutations will not always be considered and the round function will be written as:

$$R_n = S(R_{n-1} \oplus K_n) \oplus L_{n-1}$$

$$L_n = R_{n-1}$$

where S is the S-box function. The eight different S-boxes are applied in each round to sets of six bits. The subkeys  $K_n$   $(1 \le n \le 16)$  are each 48 bits generated from the 56-bit key, by permuting the bits of the initial key.

Figure 2.1: The DES round function for round n.

The algorithm also includes an initial and final permutation. These are also bitwise permutations and will be ignored, as they do not contribute to the security of the algorithm.

#### Triple DES

In order to mitigate the key length problem, a modification to DES was proposed to make an exhaustive key search prohibitively complex. Triple DES is a construction using two different DES keys and is defined in [78]. In the algorithm below these are labelled  $K_1$  and  $K_2$ , and in order to generate a ciphertext block C from a plaintext block M the following calculation is performed:

$$C = \text{DES}(\text{DES}^{-1}(\text{DES}(M, K_1), K_2), K_1)$$

where DES(M, K) denotes the output of the DES encryption algorithm applied to message block M with key K. Deciphering the ciphertext block C uses the function,

$$M = \text{DES}^{-1}(\text{DES}(\text{DES}^{-1}(C, K_1), K_2), K_1)$$

Another version of triple DES is proposed in [78], in which three different keys are used rather than two.

#### 2.2 Advanced Encryption Standard

The Advanced Encryption Standard (AES) [79] was introduced in 2001 as a replacement to DES. This was because it became apparent that the key used in DES is too short, as an exhaustive search had become feasible. The key used in AES can have a bit length of 128, 192 or 256 bits. For simplicity of presentation, in this thesis only the simplest case of a 128-bit key will be considered.

| Algorithm 2.1: Advanced Encryption Standard |

|---------------------------------------------|

| Input: M, K                                 |

| Output: C                                   |

| $X \leftarrow M \oplus K$                   |

| for $i \leftarrow 1$ to 10 do               |

| $X \leftarrow \mathbf{ShiftRow}(X)$         |

| $X \leftarrow \mathbf{ByteSub}(X)$          |

| if $i \neq 10$ then                         |

| $X \leftarrow \mathbf{MixColumn}(X)$        |

| end                                         |

| $K \leftarrow \mathbf{KeySchedule}(K)$      |

| $X \leftarrow X \oplus K$                   |

| end                                         |

| $C \leftarrow X$                            |

| return C                                    |

The structure of this algorithm is given in Algorithm 2.1, where a message block (M) is enciphered using a key (K) to produce a ciphertext block (C). The

ShiftRow function is a bytewise permutation of the input data. This is followed by the **ByteSub** function that is a substitution table applied to each byte of the input data. This table is an inversion over  $GF(2^8)$  followed by a bitwise permutation. The XOR with the subkey is also referred to as the **AddRoundKey** function. The **MixColumn** function is given in Algorithm 2.2, where • represents polynomial multiplication over  $GF(2^8)$  modulo the irreducible polynomial  $x^8 + x^4 + x^3 + x + 1$ .

| Algorithm 2.2: The MixColumn Function                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input: $X = (x_0, x_1, \dots, x_{15})_{256}$                                                                                                                                                                                                   |

| <b>Output</b> : $Y = (y_0, y_1, \dots, y_{15})_{256}$                                                                                                                                                                                          |

| $\begin{array}{l} \mathbf{for} \ i \leftarrow 0 \ \mathbf{to} \ 15 \ \mathbf{do} \\ y_i = 2 \bullet x_i \oplus 3 \bullet x_{(i+4) \ \mathrm{mod} \ 16} \oplus x_{(i+8) \ \mathrm{mod} \ 16} \oplus x_{(i+12) \ \mathrm{mod} \ 16} \end{array}$ |

| end                                                                                                                                                                                                                                            |

| return Y                                                                                                                                                                                                                                       |

The **xtime** function, as described in Algorithm 2.3, is given in [79] as a function that calculates a polynomial multiplication by the polynomial x over  $GF(2^8)$  modulo the polynomial given above. The first part of the function is a left bit shift of the input value, which represents multiplication by the polynomial x. The most significant bit is then tested. If the bit is equal to one then the result of the bit shift needs to be reduced to provide the result modulo the polynomial  $x^8 + x^4 + x^3 + x + 1$ . This is done by subtracting  $11B_{16}$  (the hexadecimal representation of the polynomial  $x^8 + x^4 + x^3 + x + 1$ ), which is equivalent to an XOR as no carry is produced in polynomial subtraction. The function described in Algorithm 2.3 is optimised so that the whole calculation can take place in eight bits, i.e. if the most significant bit is equal to one then it will be removed by the XOR and is therefore only required for testing purposes.

The **KeySchedule** is a function that generates a subkey from the previous subkey. The first subkey is the key with no changes, and subsequent subkeys are generated using this function. This function is described in Algorithm 2.4, where z is a constant that varies from one round to another. This function can be inverted, so the key can be generated given any of the subkeys.

A permutation is sometimes also used on the message and key on entry to the

Algorithm 2.3: The xtime function

```

Input: X = (x_7, x_6, \dots, x_0)_2

Output: Y = \text{xtime}(X)

Y \leftarrow (X << 1) \land \text{FF}_{16}

if x_7 = 1 then

Y \leftarrow Y \oplus 1B_{16}

end

return Y

```

Algorithm 2.4: The AES Key Schedule

```

Input: X = (x_0, x_1, ..., x_{15})_{256}, z

Output: X = (x_0, x_1, ..., x_{15})_{256}

for i \leftarrow 0 to 3 do

x_{i < <2} \leftarrow x_{i < <2} \oplus ByteSub(x_{(((i+1)\land 3) < <2)+3})

end

x_0 \leftarrow x_0 \oplus z

for i \leftarrow 0 to 15 do

if i \neq 0 \mod 4 then

x_i \leftarrow x_i \oplus x_{i+1}

end

end

return X

```

algorithm, to convert the array format to the grid format used in the specification [79]. This is an optional bytewise permutation that changes the way bytes are addressed within an implementation.

#### 2.3 RSA

RSA was first published in 1978 [94], and was the first published example of a public key encryption algorithm. The security of RSA depends on the difficulty of factorising large numbers. This means that RSA keys need to be quite large, because of advances in factorisation algorithms and the constantly increasing processing power available in modern computers.

To generate a key pair for use with RSA, two prime numbers, p and q, typically of equal bit length, are generated; they are then multiplied together to create a value N, the modulus, whose bit length is equal to that desired for the cryptosystem. That is, in order to create a 1024-bit modulus,  $2^{511.5} < p, q < 2^{512}$ . A public exponent, e, is chosen that is coprime to both (p-1) and (q-1). A private exponent, d, is generated from the parameters previously calculated, using the formula:

$$ed \equiv 1 \pmod{(p-1)(q-1)}$$

, or equivalently

$ed \equiv 1 \pmod{\phi(N)}$

where  $\phi$  is Euler's Totient function.

In the RSA cryptosystem, to encrypt a message, M, and create ciphertext, C, one calculates:

$$C = M^e \bmod N$$

The value of e is often chosen as 3 or  $2^{16} + 1$ , as these values are small and have a low Hamming weight, which means that the encryption process is fast. However, the value 3 is rarely used, as if the result of an encryption is less than N then the message can be retrieved by taking the integer cube root of the ciphertext [67]. Another example of an attack against RSA encryption when a small exponent is used applies when an attacker can obtain several ciphertexts for the same message computed using different values for the modulus [67]. For example, suppose an attacker obtains the ciphertexts

$$C_1 = M^3 \mod N_1$$

$$C_2 = M^3 \mod N_2$$

$$C_3 = M^3 \mod N_3.$$

An attacker can then use the Chinese Remainder Theorem to compute an integer X that satisfies

$$X \equiv C_1 \pmod{N_1}$$

$$X \equiv C_2 \pmod{N_2}$$

$$X \equiv C_3 \pmod{N_3},$$

where  $0 \le X < N_1 N_2 N_3$ . Since  $M^3 < N_1 N_2 N_3$  (as  $M < N_1$ ,  $N_2$ , and  $N_3$ ) then  $X = M^3$ , and M can be recovered by taking the integer cube root of X. A similar attack applies if e is any small value.

To decrypt the ciphertext, the same calculation is carried out but using the private exponent, d, which generally has the same bit length as N:

$$M = C^d \bmod N$$

The digital signature scheme involves use of the inverse operations. By convention, this is expressed as:

$$S = M^d \mod N$$

The generation of a signature, S, uses the private exponent d. The verification therefore uses the public exponent and is expressed as:

$$M \stackrel{?}{=} S^e \bmod N$$

For simplicity the above notation will be used in the attacks described in subsequent sections.

Applying the RSA primitive to the message, as described above, will not yield a secure signature scheme (for reasons beyond the scope of this thesis). To achieve a secure scheme it is necessary to apply the RSA operation to a transformed version of the message, e.g. as can be achieved by hashing the message, adding padding, and/or masking the result.

In the attacks presented in this thesis, it is assumed that the attacker is able to completely manipulate the message being signed. This is clearly a strong attack model, but it allows for a more complete exploration of the attacks that could be applied to the RSA primitive.

Some of the attacks presented in this thesis will not be realistic when a padding scheme is used. However, it is important that the calculation of RSA is secure against all possible attacks. If a given implementation does not use padding or, more realistically, contains a bug that allows an attacker to remove the padding function the implementation should still be able to resist all known side channel and fault attacks.

#### Using the Chinese Remainder Theorem

The RSA calculation using the private exponent (i.e. where  $S = M^d \mod N$  and  $N = p \cdot q$ ) can be performed using the Chinese Remainder Theorem (CRT) [58]. Initially, the following values are calculated,

$$S_p = (M \mod p)^{(d \mod (p-1))} \mod p$$

$$S_q = (M \mod q)^{(d \mod (q-1))} \mod q$$

which can be combined to form the RSA signature S using the formula  $S = aS_p + bS_q \mod N$ , where:

$$\begin{array}{ll} a \equiv 1 \pmod{p} & \text{and} & b \equiv 0 \pmod{p} \\ a \equiv 0 \pmod{q} & \text{and} & b \equiv 1 \pmod{q} \end{array}$$

This can be implemented in the following manner:

$$S = S_q + \left( (S_p - S_q) q^{-1} \bmod p \right) \cdot q$$

This provides a method of calculating an RSA signature that is approximately four times quicker than a generic modular exponentiation algorithm. This advantage is offset by an increase in the key information that needs to be stored. Rather than storing just the value of d, the values of  $(p, q, d \mod (p-1), d \mod (q-1), q^{-1} \mod p)$  need to be precalculated and stored.

## 2.4 The Digital Signature Standard

The Digital Signature Standard (DSS) is a U.S. standard for generating digital signatures introduced by NIST in 1991 [83]. The algorithm specified in the standard is often referred to as the Digital Signature Algorithm (DSA).

The system parameters for DSA are (p, q, g), where p is a prime (typically of at least 1024 bits), q is a 160-bit prime dividing p - 1, and  $g \in \mathbb{Z}_p^*$  has order q. The private key is an integer  $\alpha \in \mathbb{Z}_q^*$  and the public key is the group element  $\beta = g^{\alpha} \mod p$ .

To sign a message M, the signer generates a random value, referred to as a nonce, k < q and computes:

$$r = g^k \mod p \mod q \text{ and}$$

$$s = \frac{h(M) + \alpha r}{k} \mod q$$

where h is a hash function. The signature of M is the pair: (r, s). To check (r, s) the verifier checks whether:

$$r \stackrel{?}{=} \left( g^{wh(M)} \beta^{wr} \bmod p \right) \bmod q$$

where  $w = s^{-1} \mod q$ .

## Chapter 3 Smart Card Architecture

Smart cards are plastic cards containing an embedded microprocessor that are used as secure devices in a wide range of applications. This chapter describes some of the main features of smart cards. Particular attention is paid to features that have importance to subsequent chapters of this document. Further information on smart card architectures can be found in [91].

This chapter describes the characteristics of smart card architectures. This is not a complete description, but focuses on the features that are important for implementing secure cryptographic algorithms.

Section 3.1 describes what a smart card is, and where the definition of a smart card can be found. The various features of smart card microprocessors are described in Section 3.2.

## 3.1 What is a Smart Card?

In the late 1980s, the growing number of smart card applications led to the emergence of international standards for this technology. The International Organization for Standardization (ISO) has published standards that define all the basic characteristics of smart cards. The main body of smart card specifications is contained in the ISO/IEC 7816 series of standards.

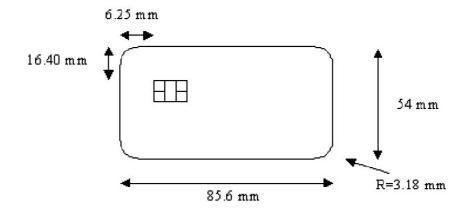

**Physical Properties** A smart card, as defined in the ISO/IEC standards, is a rectangular card with round corners. A chip is inserted in the front side, and it can have one (or more) magnetic stripes on the back. The card's form and

contact positions specified in the ISO/IEC 7816-1 [53] and ISO/IEC 7816-2 [54] standards, respectively, and are shown in Figure 3.1.

Figure 3.1: Classic shape and dimensions of a smart card.

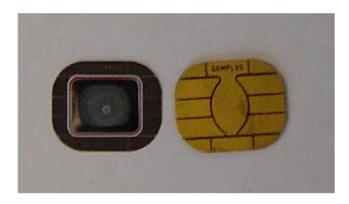

Electrical Properties The integrated circuit is a 1 to 30 mm<sup>3</sup> silicon chip. This circuit is located in a micromodule and the chip is not visible (see Figure 3.2). In accordance with ISO/IEC 7816-2, the micromodule contains an array of eight contacts, only five of which are connected to the chip.

Figure 3.2: A front and rear view of a micromodule before it is set into a plastic card.

The standard voltage supplied to the smart card is 5 volts, with a possible variation of approximately 10%. For GSM applications a voltage range between 3 and 5 volts is required, as cellular phone components function with a

3 volt power supply. Smart cards rely totally on a card reader for their power supply. They do not have their own power supply because of size constraints.

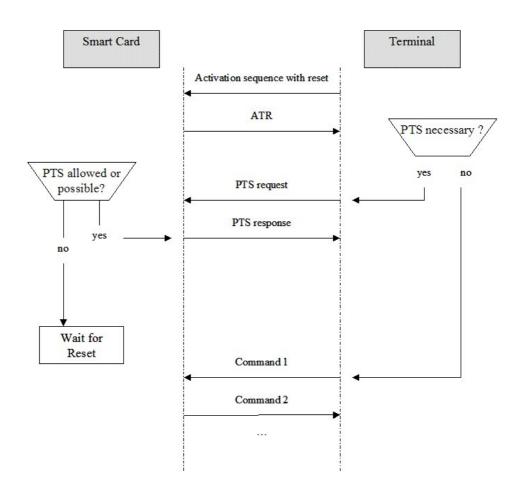

- **Communication** Smart card terminals use a simple protocol to communicate with the microchip embedded in smart cards. Every time the card is inserted into a terminal it is reset. After the voltage supply, the clock, and the reset signal have been applied, the card sends an Answer To Reset (ATR) to the terminal via the I/O pin. This ATR contains a series of bytes that define the parameters and communication protocol that can be used by the card during the session (as specified in the ISO/IEC 7816-3 standard [52]). The terminal has the ability to change the communication protocol, transaction speed or other parameters by sending a Protocol Type Selection (PTS) command to the card. The PTS will specify a set of parameters within the boundaries set by the card in the ATR. After the protocol has been established, the terminal can begin to send commands to the card using the Application Protocol Data Unit format (APDU). These exchanges are depicted in Figure 3.3.

- **Operating System (OS)** At present, smart card Operating Systems fall into one of two classes: either an OS especially designed for a dedicated application (also called a native OS) or a Java Card OS that can host several applications. In the latter case, each application is handled by an applet, and several applets can be loaded onto the Java Card at a given time. The OS chosen is closely related to the chip's characteristics; for example, Java Cards require much more memory to house the virtual machine, applets, and all the functions the applet could call. The Java Card OS corresponds to a proprietary implementation of a standardised API defined by SUN Microsystems [102].

All the implementations discussed in this document will be based on smart cards with a native OS. This is so that the card can be strictly controlled and its behaviour from one execution to another remains constant. Despite this, the attacks and countermeasures described in this thesis still apply to Java Card implementations. However, it is more difficult to determine when a given algorithm is performed, as the CPU spends a large percentage of its

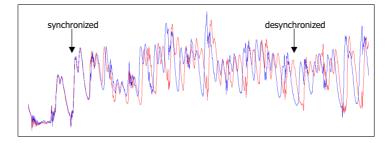

Figure 3.3: Communication initialisation between a smart card and a reader.

time executing the virtual machine. There are also events that occur intermittently, e.g. memory defragmentation, that can desynchronise events from one acquisition to another. This can make things more difficult for an attacker, but can often be overcome, as described in Section 7.2. The specific problems surrounding Java Card implementations and applets are beyond the scope of this thesis.

## 3.2 Microprocessors

Unlike memory cards and magnetic stripe cards, that are totally passive, the microprocessor embedded in a smart card can manipulate and control all the data present in the card. These processors usually employ well-known architectures. The 8-bit microprocessors traditionally used in smart cards are based on Complex Instruction Set Computer (CISC) architectures [75]. These are often typically based on by Motorola's 6805 or Intel's 8051 core, with improvements to permit further optimisation of the embedded software. Continuing technological advances, along with the growing need for more sophisticated applications, are currently generating a significant shift in the hardware platforms used in smart cards. More sophisticated smart cards are emerging based on 32-bit Reduced Instruction Set Computer (RISC) architecture chips, containing dedicated peripherals (cryptographic coprocessors, memory managers, large memories, ...) [51, 71]. In this thesis, both types of architecture are analysed with regard to the differences in countermeasure requirements.

#### 3.2.1 Cryptographic Coprocessors

Traditionally smart cards have been based around 8-bit architectures. In order to manipulate large numbers, e.g. to calculate the RSA algorithm described in Section 2.3, dedicated coprocessors can be appended to the CPU. In more modern 32-bit chips [51, 71] a coprocessor is not necessary to compute the RSA algorithm, as efficient software implementations can be achieved.

DES is also often implemented in a coprocessor to help increase performance, and AES implementations should be available in the near future. These coprocessors can increase the smart card's performance, as hardware implementations of secret key algorithms can be expected to require 1 or 2 clock cycles per round of the block cipher. However, the inclusion of coprocessors also increases the size of the chip and the overall power consumption. This means that chips with coprocessors are usually more expensive and are not ideal in environments where the amount of available current is severely limited, e.g. GSM Subscriber Identity Modules.

#### 3.2.2 Random Number Generators

Random number generators are usually included in smart cards, as unpredictable numbers are an important element in many secure protocols. A true random number generator is typically based on a signal generated by an analog device (e.g. a noisy resistor) which is then treated to remove any bias that may exist, or has been induced, in the bits generated. The correct functioning of all aspects of a smart card chip under varied environmental conditions is important, but is critical for random number generation because the quality of the generated random values can have a profound effect on cryptographic schemes. Random number generators are therefore designed to function correctly in a large range of environmental conditions, including temperature, supply voltage, and so on. However, if an attacker succeeds in modifying the environmental conditions such that the physical source of randomness is affected, the subsequent treatment is included so that an attacker will not be able to determine if the change in conditions had any effect.

Pseudo-random number generators are also often included. These are typically based on Linear Feedback Shift Registers (LFSRs) that are able to generate a new pseudo-random value every clock cycle, but are deterministic over time and are not usually used for critical security functions.

Where random values are required in cryptographic algorithms, a true random number generator is used when the quality of the random value is important, e.g. the generation of the nonce in DSA (see Section 2.4). Where the quality of the random value is less important, a pseudo-random number generator can be used, e.g. to govern the lengths of random delays (see Section 7.2). In some microprocessors only pseudo-random number generators are available. In this case, mechanisms that combine a random seed (that can be inserted into the chip during manufacture) with pseudo-random values can be used to provide random values.

An example of this latter type of random number generator is given in the ANSI X9.17 [3] standard, that uses DES to provide random values based on a random seed and another source of pseudo-random information. This functions by taking a 64-bit pseudo-random input (X), a 64-bit random seed (S) and a DES key (K). X is usually generated by calculating X = DES(D, K), where D is a the date and/or time, but this information is not available to a smart card and is therefore replaced with values provided by a pseudo-random number generator. To output a random value R the following calculation takes place:

$$R = \text{DES}(X \oplus S, K),$$

and the random seed is updated using:

$$S = DES(R \oplus X, K).$$

For increased security the DES function can be replaced with triple DES, as the key length used by DES has proven to be too short to entirely resist an exhaustive key search.

#### 3.2.3 Cache

Sophisticated smart cards are emerging based on 32-bit CPUs, containing dedicated mechanisms designed to compensate for time-consuming operations or long data paths. Details of these sophisticated mechanisms are given, for example, in [49, 72]. Two mechanisms that are important in the context of this thesis are pipelining and caching, and are detailed below.

- **Pipelining:** Pipelining is a technique whereby the execution of each instruction is decomposed into elementary and independent steps. Each step is implemented as a separate hardware block that can work in parallel. Typically, a 3-stage pipeline can be decomposed into an Instruction Fetch (IF), an Execute (EX) stage and a Write Back (WB) stage. More sophisticated 5-stage pipelines, such as that discussed in [72], can involve an IF stage, a DC (Decode) stage, an EX stage, a MEM (Memory access) stage and a WB stage. Each stage is designed to be completed within one clock cycle, which means that, even though each instruction takes 5 clock cycles in the case of a 5-stage pipeline, a new instruction can be issued at every clock cycle.

- **Caching:** Smart card architectures include embedded Non-Volatile Memory (NVM) such as EEPROM or Flash to store code or data. Such memory usually has high read latency where, for example, reading one byte involves reading a whole line that takes several clock cycles. This would mean that the IF stage and the MEM stage would take more than one clock cycle, which would stall

the pipeline. This would considerably reduce the rate at which instructions can be issued. To compensate for these "slow" memories, cache mechanisms are implemented. A cache is a small, fast RAM whose role is to buffer the lines of NVM being fetched. Because of the technology used to implement them, and their small size (leading to faster decode and access times), caches allow a word to be fetched in one clock cycle.

When the data is to be fetched from the NVM, the CPU will first check whether this particular word is already in the cache: if yes (this is a *cache hit*), the word is fetched directly from the cache. If, on the contrary, this particular word is not cached, then this is a *cache miss*. The CPU will then fetch a whole line (e.g. 16 bytes) within which the targeted word can be found. This means that, even if fetching this word takes more than one clock cycle, the other words of this line will already be in the cache when required.

This mechanism considerably increases the instruction issue rate and, therefore, performance. Detailed studies of the performance enhancements of cache mechanisms are given in [49]. In order to keep power consumption low, smart card CPUs usually only have one level of cache, with a granularity in the order of 8 to 16 bytes.

#### 3.2.4 Anomaly Sensors

There are usually a number of different types of anomaly detectors present in smart cards. These are used to detect unusual events in the voltage and clock supplied to the card, and the environmental conditions (e.g. the temperature). These enable a smart card to detect when it is exposed to conditions that are outside the parameters within which it is known to function correctly. When unusual conditions are detected, the chip will cease to function until the effect has been removed (i.e. initiate a reset or an infinite loop when the sensor is activated). However, these measures cannot be relied upon to defend against all fault attacks. For example, sensors that detect intense light (such as laser light) will only protect a small area of the chip's surface; an attacker could potentially find an area were a fault can be injected and remain undetected.

#### 3.2.5 Chip Features

The surface of the chip used in a smart card can be uncovered by exposing the micromodule to fuming nitric acid<sup>\*</sup> that will remove the resin visible in Figure 3.2. Once the chip has been revealed the easiest form of analysis is to simply look at it. The various different blocks can often be identified, as shown in Figure 3.4.

Figure 3.4: A chip surface with readily identifiable features.

Reverse engineering can target the internal design to understand how a given chip or block functions. A malicious attacker can use such information to improve their knowledge of chip design and find potential weaknesses in the chip, which may allow them to compromise the chip's integrity.

In modern smart cards, various features used to inhibit reverse engineering are implemented using glue logic: important blocks are laid out in a randomised fashion that makes reverse engineering difficult. This technique increases the size of the block, and is therefore not used in the design of large blocks such as the ROM and EEPROM.

A common technique to prevent this sort of identification and targeting is to overlay the chip with another metal layer that prevents the chip's features being identified. This can be removed using hydrofluoric acid that eats through the metal

<sup>\*</sup>Fuming nitric acid is nitric acid with a concentration of over 86%.

layer; this reaction is then stopped using acetone before further damage is done and the chip surface can be analysed. The chip becomes non-functional but the layout of the chip can be determined, so that other chips of the same family can be attacked. The result of such a process is shown in Figure 3.5.

Figure 3.5: A chip with a shield present and removed. Removing a shield using hydrofluoric acid renders the chip non-functional but allows the layout to be determined.

Discovering the layout and functioning of a chip is particularly important when using a laser as a fault injection mechanism. Different areas of a chip can be targeted through the metal layer once the layout of a chip is known.

#### **3.3** Summary and Conclusions

This chapter describes some of the features that are present in smart cards. The physical characteristics of a smart card are defined in the ISO/IEC 7816 series of standards, some features of which are described above. Common security features of smart cards are also described. The features described in this chapter will be referred to in later chapters where appropriate.

## Chapter 4

## Side Channel Analysis Techniques

Sensitive systems that are based on smart cards use protocols and algorithms that have usually been subjected to rigorous analysis by the cryptographic community. Attackers have therefore sought other means to circumvent the security of protocols and algorithms used in smart card based systems. As smart cards are small devices, they can easily be put in a situation where their behaviour can be observed and analysed. The simplest form of analysis of this type is intercepting the communication between a smart card and its reader. Tools are readily available on the Internet [7] that allow the commands to and from a smart card to be logged. This problem is relatively easy to solve using secure session key generation to encipher subsequent communication, as proposed in [43], but highlights the ease of man-in-the-middle attacks against smart cards.