### UAB

#### Universitat Autònoma de Barcelona

Departament de Microelectrònica i Sistemes Electrònics

#### Low-Power and Compact CMOS Circuit Design of Digital Pixel Sensors for X-Ray Imagers

Roger Figueras i Bagué

Memòria de Tesi presentada per optar al títol de

Doctor en Microelectrònica i Sistemes Electrònics

**Abril** 2015

Dr. Lluís Terés Terés, Científic Titular del Consejo Superior de Investigaciones Científicas, i Dr. Francesc Serra Graells, Professor Titular del Departament de Microelectrònica i Sistemes Electrònics,

## Certifiquen

que la Memòria de Tesi Low-Power and Compact CMOS Circuit Design of Digital Pixel Sensors for X-Ray Imagers presentada per Roger Figueras i Bagué per optar al títol de Doctor en Microelectrònica i Sistemes Electrònics s'ha realitzat sota la seva direcció a l'Institut de Microelectrònica de Barcelona pertanyent al Centre Nacional de Microelectrònica del Consejo Superior de Investigaciones Científicas i ha estat tutoritzada en el Departament de Microelectrònica i Sistemes Electrònics de la Universitat Autònoma de Barcelona.

| Dr. Francesc Serra Graells |       |

|----------------------------|-------|

|                            |       |

| <br>, a d                  | le de |

$a\ la\ Bet,\ al\ Marc\ i\ a\ l'Anna$

#### Resum

La obtenció d'imatges utilitzant raigs-X ha esdevingut una tecnologia clau per a un ampli rang d'aplicacions tant industrials com mèdiques o científiques, doncs permet estudiar l'interior dels objectes sense necessitat de destruir-los o desmantellar-los. En aquest sentit, hi ha un creixent interès en la recerca en aquests camps, com demostra la literatura, per desenvolupar sistemes avançats de raig-X capaços d'obtenir imatges d'alta qualitat a la vegada que es redueix la dosi total de radiació.

Actualment, els imagers de raig-X estan dominats per sistemes híbrids, basats en matrius de píxels en detectors de conversió directa de raig-X i els seus corresponents circuits integrats de lectura (ROICs). Tot i el seu elevat cost i les seves limitacions en àrea en comparació amb els clàssics sensors de conversió indirecta, els avantatges que ofereixen aquests sistemes són clars en quant a la reducció de la dosi de radiació necessària, la millora de la integritat del senyal i l'escalat en la resolució espacial. Pel que fa al mètode de lectura que empren els ROICs, l'estratègia més estesa es basa en el conteig de fotons, degut als avantatges en termes d'immunitat al soroll i de classificació dels fotons. No obstant, aquests sistemes d'imatge per raig-X pateixen de pèrdues d'informació degut a efectes com el charge-sharing i el pile-up.

És en aquest context que l'objectiu d'aquest treball de tesi és proposar tècniques específiques de disseny analògic i mixte de circuits per al desenvolupament de píxels digitals sensors (DPS) compactes i de baix consum per a ROICs focalitzats a imagers de raig-X híbrids de conversió directa.

L'arquitectura del píxel proposat, basada en el mètode de lectura per integració de càrrega, evita la pèrdua d'informació que pateixen els sistemes basats en el conteig de fotons i contribueix a la qualitat de les imatges per raig-X amb una àrea de píxel compacta i un baix consum per millorar la resolució de la imatge i reduir l'escalfament del detector, respectivament. En aquest sentit, el circuits CMOS del DPS proposat inclouen una conversió de la càrrega sense pèrdues a nivell de píxel per extendre el rang dinàmic, ajust individual del guany per compensar el FPN de la matriu de píxels, capaci-

tat d'autopolarització i comunicacions exclusivament digitals per reduir el crosstalk entre píxels, capacitat d'auto-test per reducció de costos, selecció de la càrrega col·lectable per ampliar el rang d'aplicacions i cancel·lació del corrent d'obscuritat a nivell de píxel. A més, les tècniques de disseny proposades s'orienten al desenvolupament futur de sistemes d'imatge de raig-X modulars 2D amb grans àrees escalables i contínues de sensat.

Aquesta recerca en disseny de circuits s'ha materialitzat en diverses generacions de demostradors DPS, amb valors de pitch des de  $100\mu m$  baixant fins a  $52\mu m$ , integrades utilitzant una tecnologia CMOS estàndard de  $0.18\mu m$  i 1P6M.

S'ha fet una anàlisi exhaustiva de les mesures tant elèctriques com amb raigs-X dels prototips de circuits proposats per a la seva validació. Els resultats experimentals, alineen aquest treball inclús més enllà de l'estat de l'art en píxels actius en termes de resolució espacial, consum, linealitat, SNR i flexibilitat del píxel. Aquest últim punt adequa les tècniques de disseny de circuits proposades a una àmplia gamma d'aplicacions d'imatges de raigs-X.

#### Abstract

X-ray imaging has become a key enabling technology for a wide range of industrial, medical and scientific applications since it allows studying the inside of objects without the need to destroy or dismantle them. In this sense there is a growing research interest in literature to develop advanced X-ray systems capable of obtaining high quality images while reducing the total radiation dose.

Currently, X-ray imagers are dominated by hybrid systems, built from a pixel array of direct conversion X-ray detectors and its corresponding read-out integrated circuit (ROIC). Despite their higher cost and limited area compared to classical indirect counterparts, the advantages of these systems are clear in terms of radiation dose reduction, signal integrity improvement and spatial resolution scaling. Concerning the readout method used by the ROICs, the most common design strategy is based on photon-counting, due to its advantages regarding circuit noise immunity and photon classification. However, these X-ray imaging systems tend to experience from information losses caused by charge-sharing and pile-up effects.

In this context, the goal of the presented thesis work is to propose specific analog and mixed circuit techniques for the full-custom CMOS design of low-power and compact pitch digital pixel sensors (DPS) for ROICs targeting hybrid and direct conversion X-ray imagers.

The proposed pixel architecture, based on the charge-integration readout method, avoids information losses experienced by photon-counting and contributes to X-ray image quality by a compact pixel area and low-power consumption to improve image resolution and reduce heating of X-ray detectors, respectively. In this sense, the proposed CMOS DPS circuits feature in-pixel A/D lossless charge conversion for extended dynamic range, individual gain tuning for pixel array FPN compensation, self-biasing capability and digital-only interface for inter-pixel crosstalk reduction, built-in test capability for costs reduction, selectable electron/hole collection to wide the applications range and in-pixel dark current cancellation. Furthermore, the proposed design techniques are oriented to the future development of truly

2D modular X-ray imager systems with large scale and seamless sensing areas.

All the above circuit design research has been materialized in several generations of DPS demonstrators, with pitch values ranging from  $100\mu m$  down to  $52\mu m$ , all of them integrated using standard  $0.18\mu m$  1P6M CMOS technology.

Extensive analysis of both electrical and X-ray measurements on the pixel circuit prototypes have been done to proof their validity. Experimental results align this work not only within but also beyond the state-of-the-art active pixels in terms of spatial resolution, power consumption, linearity, SNR and pixel flexibility. This last point makes the proposed pixel design techniques specially suitable for a wide range of X-ray image applications.

#### Acknowledgments

My greatest acknowledgments are for Lluís Terés and Paco Serra, as professors, as directors and as colleagues, for what they taught me, for their trust in me, for the opportunities they have given to me, and for all the time they have dedicated to me and to this work.

I want to thank all ICAS group people, and in general all IMB staff. In particular, my gratitude to Justo Sabadell, for what he taught me on microelectronics design and for his work on pixels design at the beginning of this thesis. Also to Ricardo Martínez for his support on the design of the test setup for radiation experiments and for sharing all his knowledge on X-ray fields. Likewise, the comments of Mokhtar Chmeissani have been very useful.

Regarding the fabrication and assembling of the complete X-ray imaging systems, the development of the direct conversion Si detectors employed has been possible thanks to Giulio Pellegrini and all the IMB clean room staff. Equally important, Enric Cabruja has had a key role regarding the UBM process, the management of the bump-growing process and the flip-chip. Finally, concerning the PCBs fabrication and the wire-bonding process, I want to thank Joan Puertas and Alberto Moreno for their work.

All experiments using X-ray tube radiation have been possible thanks to

Albert Sancho, who has invested a lot of his time in helping me to obtain results and guiding me through this intricate experimentation. Likewise, the synchrotron experiments have been done thanks to Celeste Fleta. These experiments were performed at the BL11-NCD beamline at the ALBA Synchrotron Light Facility with the collaboration of the ALBA staff, specially of the beamline scientist Juan Carlos Martinez.

My most special acknowledgment to my family: Bet, Marc, Anna, my brother Jordi and my parents Jordi and Magda. You mean everything to me.

# Contents

| 1 | Intr | oduction                                          | 1  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Motivation                                        | 1  |

|   | 1.2  | X-Ray Imaging                                     | 3  |

|   |      | 1.2.1 Fundamentals                                | 3  |

|   |      | 1.2.2 Figures of Merit                            | 0  |

|   |      | 1.2.3 Direct Conversion Semiconductor Detectors 1 | 4  |

|   |      | 1.2.4 Charge Integration versus Photon Counting 1 | 7  |

|   | 1.3  | State-of-the-Art Technologies                     | 2  |

|   | 1.4  | Objectives and Scope                              | :5 |

|   |      |                                                   |    |

| 2 | Pix  | Architecture 2                                    | 9  |

|   | 2.1  | DPS Architecture and Operation Proposal           | 29 |

|   | 2.2  | Charge-Integration and Digital Conversion         | 3  |

|   | 2.3  | Individual Gain Programmability 4                 | 1  |

|   | 2.4                    | Built-In Test Capability                           | 44 |

|---|------------------------|----------------------------------------------------|----|

|   | 2.5                    | Digital Interface                                  | 46 |

| 3 | $\mathbf{C}\mathbf{M}$ | IOS Pixel Circuits                                 | 51 |

|   | 3.1                    | Asynchronous A/D Conversion                        | 51 |

|   |                        | 3.1.1 Full Scale                                   | 56 |

|   |                        | 3.1.2 Equivalent Noise Charge                      | 57 |

|   |                        | 3.1.3 Integrated versus Counted Charge             | 60 |

|   |                        | 3.1.4 Phantom Event Issues                         | 61 |

|   | 3.2                    | Dark Current Cancellation                          | 64 |

|   | 3.3                    | ADC Gain Tunning                                   | 67 |

|   | 3.4                    | Built-In Test Mechanism                            | 71 |

|   | 3.5                    | Local Reference and Biasing Generation             | 73 |

|   | 3.6                    | Digital I/O Block                                  | 77 |

| 4 | DP                     | S Designs in $0.18 \mu \mathrm{m}$ CMOS Technology | 81 |

|   | 4.1                    | DPS Specifications                                 | 81 |

|   | 4.2                    | Pitch Downscaling                                  | 82 |

|   |                        | 4.2.1 $100\mu\text{m-pitch DPS}$                   | 84 |

|   |                        | 4.2.2 $70\mu$ m-pitch DPS                          | 87 |

|   |                        | 4.2.3 55 $\mu$ m-pitch DPS                         | 88 |

|   | 4.3                    | 2D Modular X-Ray Imagers                           | 90 |

|   | 4.4                    | Pixel Test Chips                                   | 93 |

|   |                        | 4.4.1 $100\mu$ m-pitch DPS Test Vehicle            | 94 |

|   |                        | 4.4.2 70µm-pitch DPS Test Vehicle                  | 95 |

|   |     | 4.4.3 55 $\mu$ m-pitch DPS Test Vehicle 97    |

|---|-----|-----------------------------------------------|

|   | 4.5 | Array Test Chips                              |

| 5 | Exp | perimental Results 101                        |

|   | 5.1 | Custom Si-Based X-Ray Detector Arrays         |

|   | 5.2 | Hybrid Packaging and Lab Setup                |

|   | 5.3 | Electrical Tests                              |

|   | 5.4 | X-Ray Tests                                   |

|   | 5.5 | Comparison with State-of-the-Art X-Ray Pixels |

| 6 | Cor | nclusions 131                                 |

|   | 6.1 | Contributions                                 |

|   | 6.2 | Future Work                                   |

# List of Figures |

| 1.1 | Simplified scheme for an X-ray imaging system                                                                                                                    | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Typical spectrum obtained from X-ray tubes with fluorescence peaks and Bremsstrahlung effects [9]                                                                | 4  |

| 1.3 | Attenuation coefficient vs photons energy for different elements or materials [12]                                                                               | 5  |

| 1.4 |                                                                                                                                                                  | 8  |

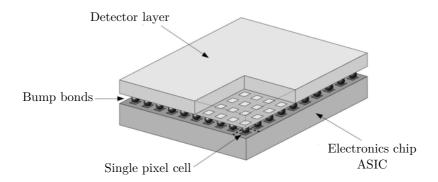

| 1.5 | X-ray sensor consisting on the bump-bonding hybridization of a direct conversion detector with its readout circuitry                                             | 9  |

| 1.6 | Typical MTF behavior                                                                                                                                             | 12 |

| 1.7 | Representation of a direct X-ray detector consisting in an array of reverse biased p-n junctions                                                                 | 15 |

| 1.8 | Comparison of absorption efficiency for detector materials of Table 1.2 versus X-Ray photon energy. Detector material and thickness are shown in the legend [29] | 16 |

| 1.9  | Simplified schematic of a photon counter and operation waveforms when sensing electrons                                                                                                                                                                                                                                                                              | 18 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.10 | Explanatory example of the information losses in photon-counting due to the pile-up effect. In this study case, 5 photons reach the detector, but only 3 are counted. Moreover, if multiple thresholds were available, the obtained energy resolving information would also be erroneous [39]                                                                        | 19 |

| 1.11 | Charge-sharing effects description: mid-energy X-ray photon and low charge dispersion (a), mid-energy X-ray photon and high charge dispersion (b), high-energy X-ray photon and low charge dispersion (c) and high-energy X-ray photon and high charge dispersion. In (b) situation, no events are registered while in (d) situation, multiple events are registered | 21 |

| 1.12 | General arrangement for $2 \times N$ tiling of 3-side buttable small X-Ray imagers to obtain larger imaging areas. Dead zones between detector arrays are evident [19]                                                                                                                                                                                               | 23 |

| 1.13 | A more sophisticated arrangement of $M \times N$ tiling multiple X-ray imagers to cover a large area [19]                                                                                                                                                                                                                                                            | 24 |

| 1.14 | Schematic process of scanning a large area with an array of single small detectors [76]                                                                                                                                                                                                                                                                              | 24 |

| 1.15 | General parts of an X-ray digital direct hybrid system                                                                                                                                                                                                                                                                                                               | 25 |

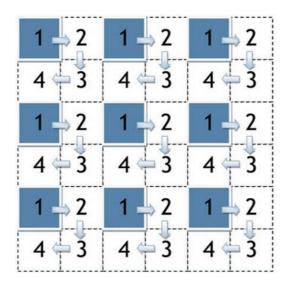

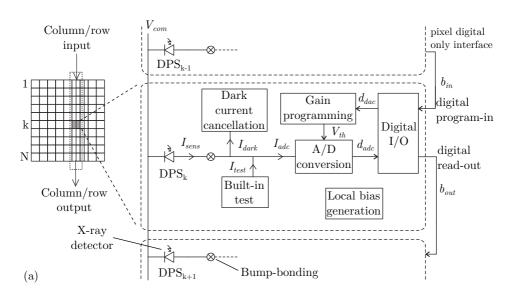

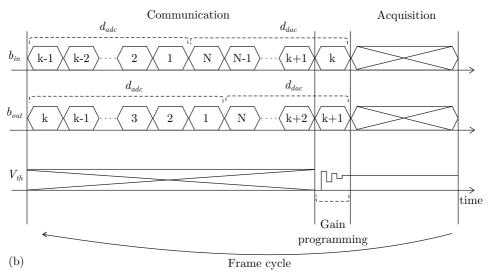

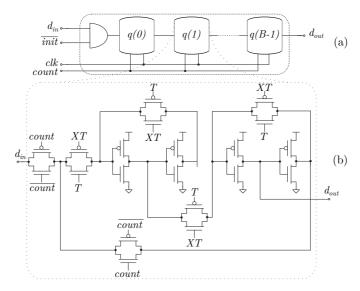

| 2.1  | Overall architecture (a) and operation (b) of the proposed DPS for digital X-ray imaging                                                                                                                                                                                                                                                                             | 32 |

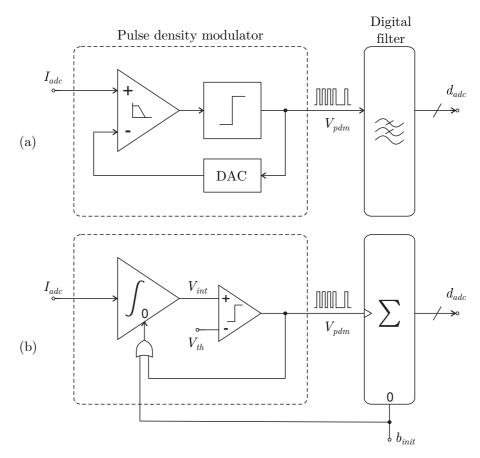

| 2.2  | General scheme (a) of a PDM predictive ADC, and asynchronous application to active pixel design (b)                                                                                                                                                                                                                                                                  | 34 |

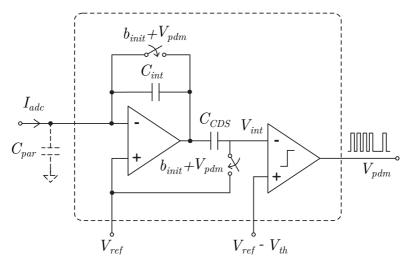

| 2.3  | Classical scheme for the PDM part of the in-pixel integrate-<br>and-fire ADC ( $I_{adc} > 0$ case)                                                                                                                                                                                                                                                                   | 35 |

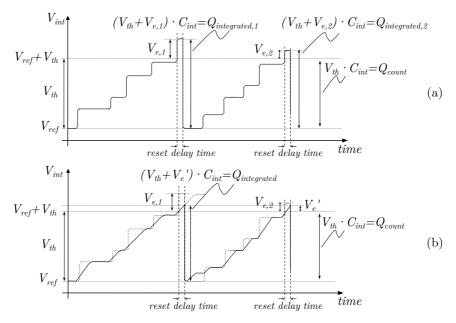

| 2.4  | Ideal (a) and real (b) operation of the classical PDM scheme of Fig. 2.3 ( $I_{adc} > 0$ case). In this example, 1 spike is lost in real operation (6 spikes) compared to the ideal behavior (7 spikes)                                                                                                                                                              | 36 |

|      | spikes)                                                                                                                                                                                                                                                                                                                                                              | 90 |

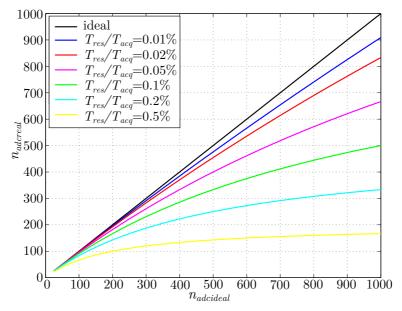

| 2.5  | Ideal and real $n_{adc}$ curves for different $T_{res}/T_{acq}$ ratios according to Eq. 2.5                                                                                                      | 38 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.6  | Novel scheme proposed for the PDM part of the in-pixel integrate-and-fire ADC ( $I_{adc}>0$ case)                                                                                                | 39 |

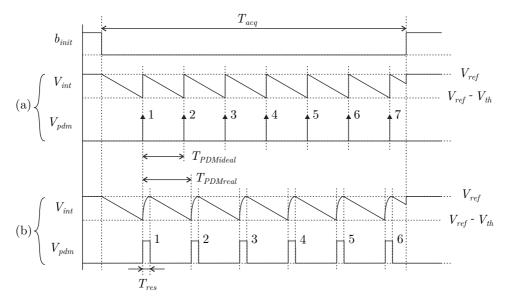

| 2.7  | Ideal (a) and real (b) operation of the novel PDM scheme of Fig. 2.6 ( $I_{adc} > 0$ case). As shown, no spikes are lost in real operation (7 spikes) compared to the ideal behavior (7 spikes). | 40 |

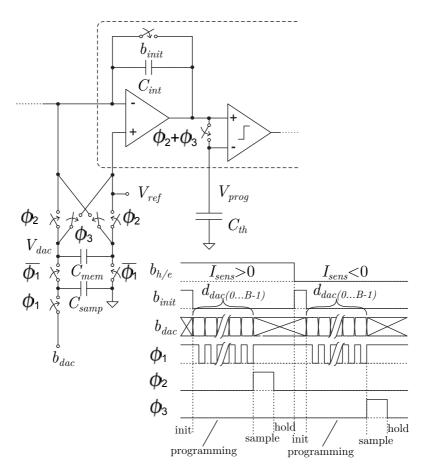

| 2.8  | Simplified scheme and operation of the proposed in-pixel gain programming. Boxed blocks are reused from the PDM stage of Fig. 2.6                                                                | 42 |

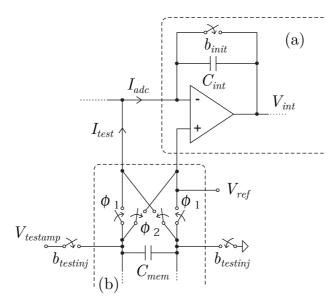

| 2.9  | Proposed scheme for the in-pixel built-in test. Boxed elements are reused from the PDM stage (a) of Fig. 2.6 and the gain programming scheme (b) of Fig. 2.8                                     | 45 |

| 2.10 | Examples of hardwired test pattern maps using the built-in pixel test mechanism of Fig. 2.9 in two pixel groups                                                                                  | 45 |

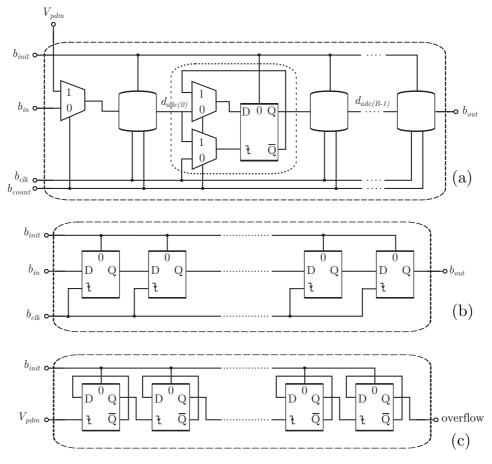

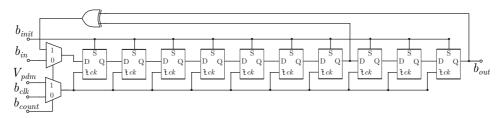

| 2.11 | Reconfigurable digital I/O block scheme (a) proposed for pixel communication (b) and acquisition (c). $\dots$                                                                                    | 46 |

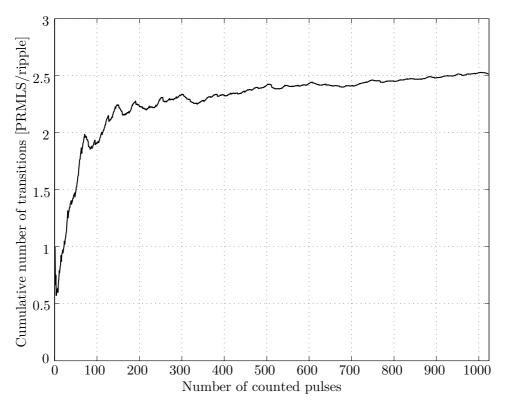

| 2.12 | 10-bit PRMLS reconfigurable counter. For $b_{count}$ low, the structure behaves as a shift register                                                                                              | 47 |

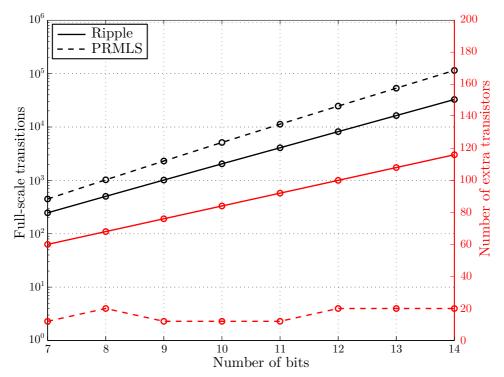

| 2.13 | Ratio between transitions of PRMLS and ripple counters for the 10-bits case design                                                                                                               | 48 |

| 2.14 | Full-scale transitions (black) and extra transistors (red) in reconfigurable ripple (solid line) and PRMLS (dashed line) counters for 7 to 14-bit design cases                                   | 49 |

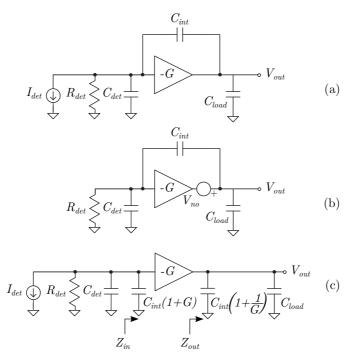

| 3.1  | General model of CTIA-based detector current-reading for STF (a), NTF (b) and impedance splitting (c)                                                                                            | 52 |

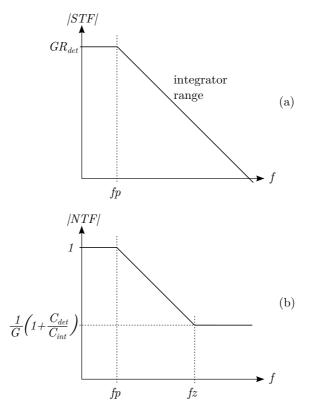

| 3.2  | Bode magnitude representation of STF (a) and NTF (b) for<br>the corresponding models of Fig. 3.1                                                                                                 | 53 |

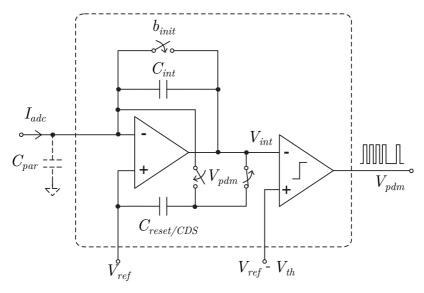

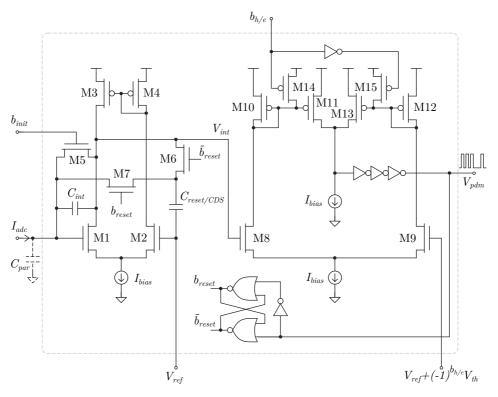

| 3.3  | CMOS circuit proposal for the lossless PDM stage of the inpixel integrate-and-fire ADC                                                                                                                                                                        | 55 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4  | Charge information losses due to comparator delay for ideal (a) and slew-rate limited (b) CTIA                                                                                                                                                                | 61 |

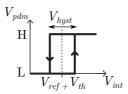

| 3.5  | Mathematical model of the hysteresis cycle to be introduced in the quantization function against phantom events. Hole collection $(b_{h/e}=0)$ case                                                                                                           | 62 |

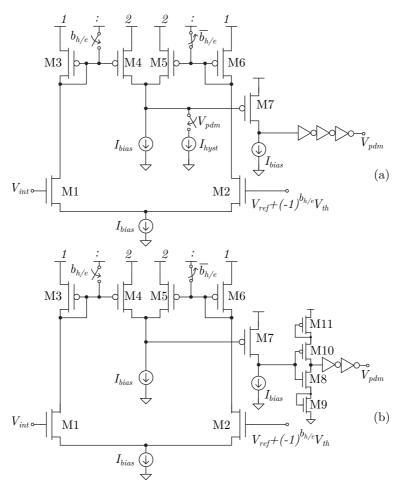

| 3.6  | Circuit modifications to the Fig. 3.3 comparator to incorporate Fig. 3.5 hysteresis based on current feedback (a) and voltage threshold stacking (b)                                                                                                          | 63 |

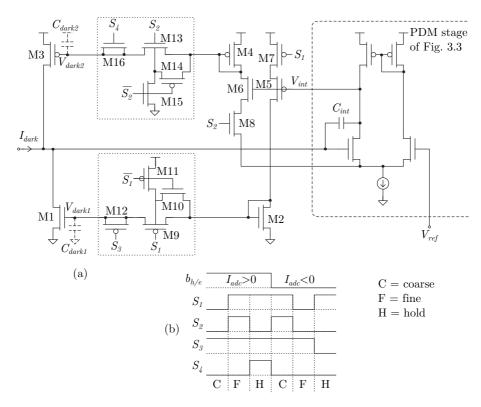

| 3.7  | Proposed CMOS implementation (a) and operation (b) of the in-pixel dark current cancellation circuit (chronogram not in scale)                                                                                                                                | 65 |

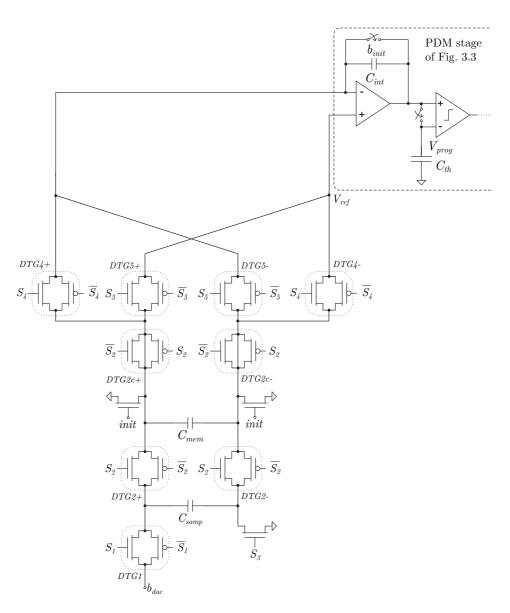

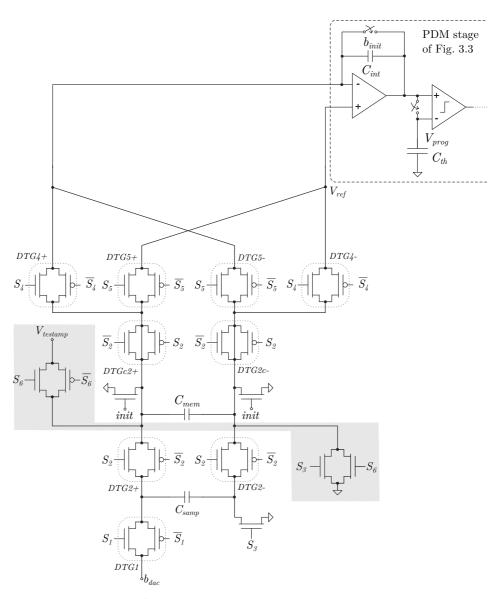

| 3.8  | Proposed CMOS implementation for the in-pixel gain tuning based on a switched capacitor DAC                                                                                                                                                                   | 68 |

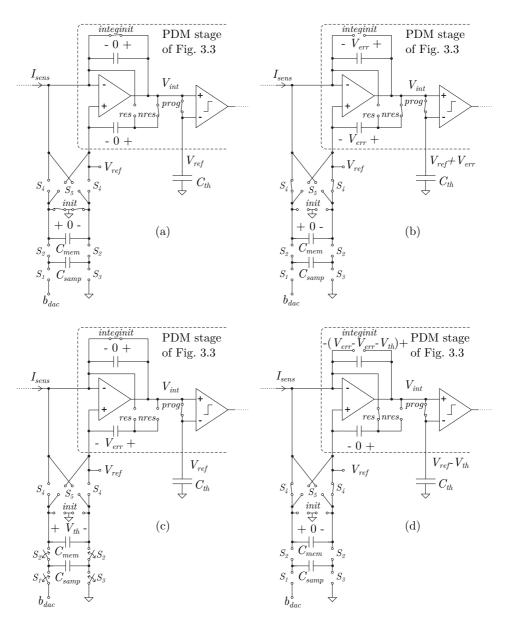

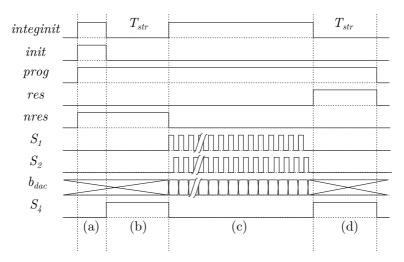

| 3.9  | Procedure of DAC precalibration for $V_{th} < 0$ case: initialization (a); error sampling (b); threshold value programming and error holding (c); threshold value storing and error compensation (d)                                                          | 69 |

| 3.10 | Operation of the DAC precalibration procedure proposed in Fig. 3.9 for $V_{th} < 0$ case (for simplicity, $S_3 = S_1$ ): initialization (a); error sampling (b); threshold value programming and error holding (c); error free threshold voltage storing (d). | 70 |

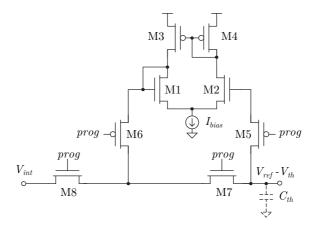

| 3.11 | Proposed low-leakage S/H switch to avoid ADC $V_{th}$ drift in Fig. 3.9                                                                                                                                                                                       | 71 |

| 3.12 | Minor adjustments (highlighted) to the circuit of Fig. 3.8 in order to include the built-in test capability of Fig. 2.9                                                                                                                                       | 72 |

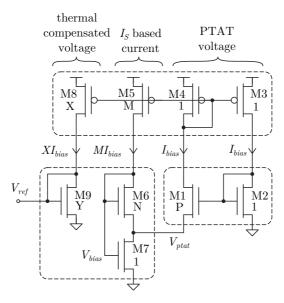

| 3.13 | Low-voltage all-MOS pixel circuit proposed for the generation of thermally compensated voltage references $(V_{ref})$ and $I_S$ -based biasing currents $(I_{bias})$ . Dashed boxes indicate device matching                                                  | 74 |

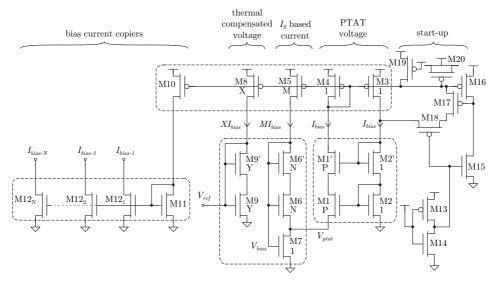

| 3.14 | CMOS implementation of the in-pixel reference voltage and biasing currents generator circuit based on the proposal of Fig. 3.13                                                                   | 77 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

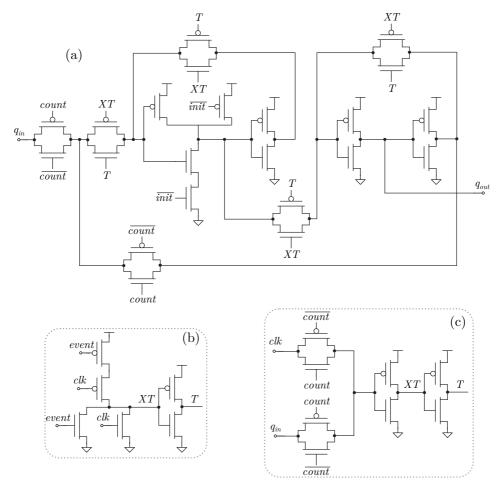

| 3.15 | Proposed CMOS implementation of each register bit module (a) and signals $T$ and $XT$ obtaining circuits for the LSB (b) and the MSB (c) modules                                                  | 78 |

| 3.16 | Simplified scheme for the reconfigurable I/O block of Fig. 2.11 modified with the alternative reset scheme (a) and CMOS implementation of each reconfigurable bit module (b)                      | 79 |

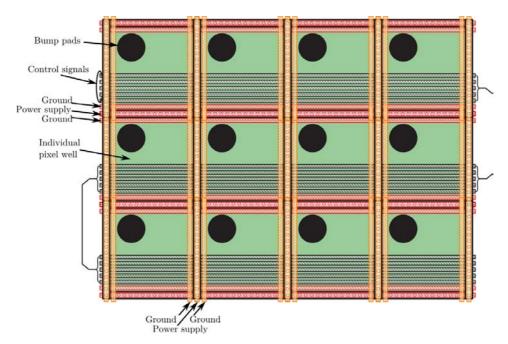

| 4.1  | General floorplan of pixel physical interconnectivity and daisy chain arrangement followed in all pixel generations                                                                               | 84 |

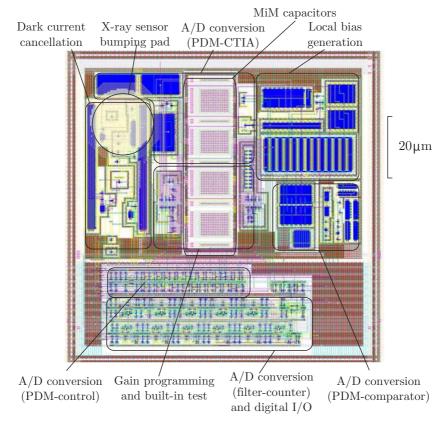

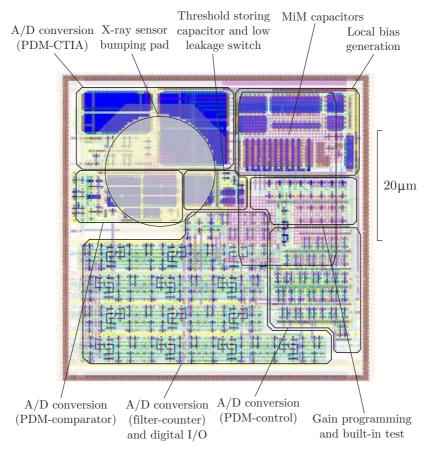

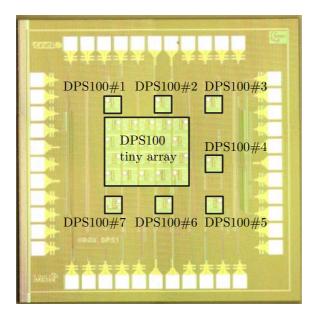

| 4.2  | DPS100 pixel layout and main circuit blocks. Bounding box is $100\mu\text{m}\times100\mu\text{m}$ while bumping pad diameter is $20\mu\text{m}$                                                   | 85 |

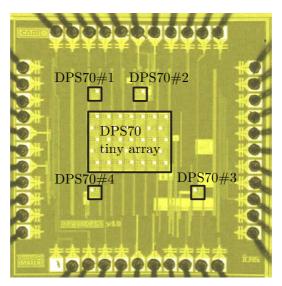

| 4.3  | DPS70 pixel layout and main circuit blocks. Bounding box is $70\mu\text{m}\times70\mu\text{m}$ while bumping pad diameter is $20\mu\text{m}$                                                      | 87 |

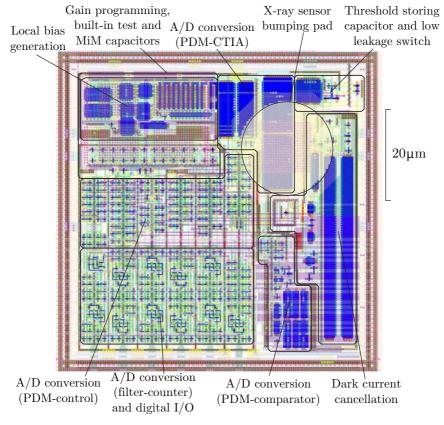

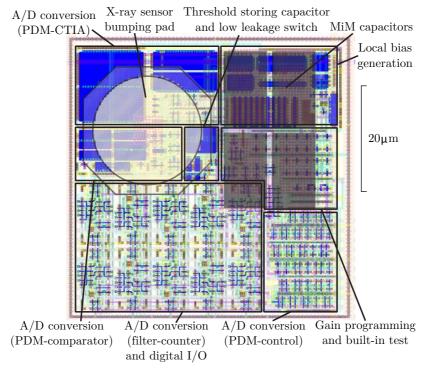

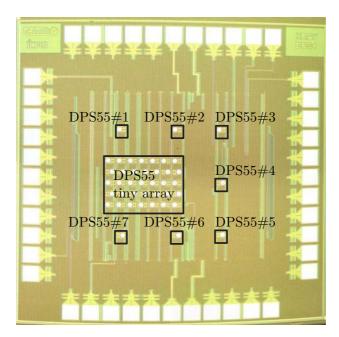

| 4.4  | DPS55 pixel layout and main circuit blocks. Bounding box is $55\mu\text{m}\times55\mu\text{m}$ . Bumping pad diameter is $20\mu\text{m}$                                                          | 89 |

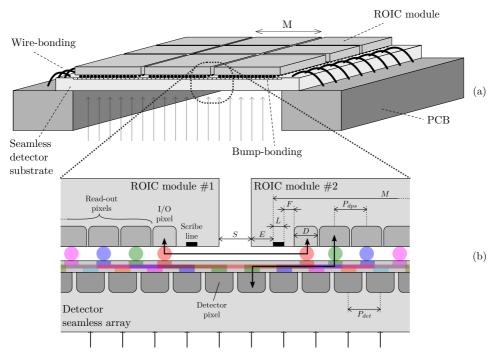

| 4.5  | General concept of the hybrid 2D modular assembly (a) and detailed cross section (b)                                                                                                              | 91 |

| 4.6  | DPS52 pixel layout and main circuit blocks. Bounding box is $52\mu\text{m}\times52\mu\text{m}$ while bumping pad diameter is $20\mu\text{m}$                                                      | 92 |

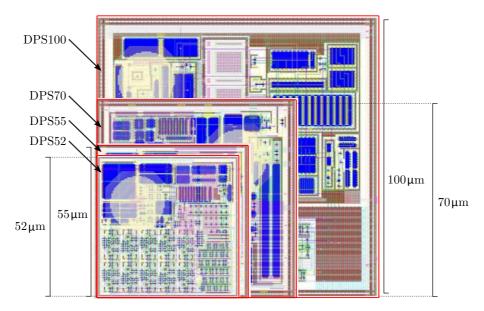

| 4.7  | Physical comparison of all CMOS DPS designs developed in UMCL180 technology                                                                                                                       | 93 |

| 4.8  | Microscope photography of the test chip integrated in UMCL180 technology for the exhaustive electrical characterization of the DPS100 pixel. Bounding box is $1.5 \text{mm} \times 1.5 \text{mm}$ | 94 |

| 4.9  | Microscope photography of the test chip integrated in UMCL180 technology for the exhaustive electrical characterization of the DPS70 pixel. Bounding box is 1.5mm×1.5mm.                          | 96 |

| 4.10 | Microscope photography of the test chip integrated in UMCL180 technology for the exhaustive electrical characterization of the DPS55 pixel. Bounding box is $1.5 \text{mm} \times 1.5 \text{mm}$ 97                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

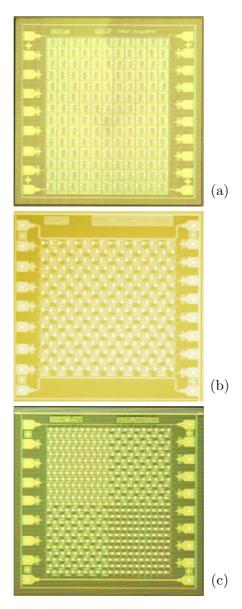

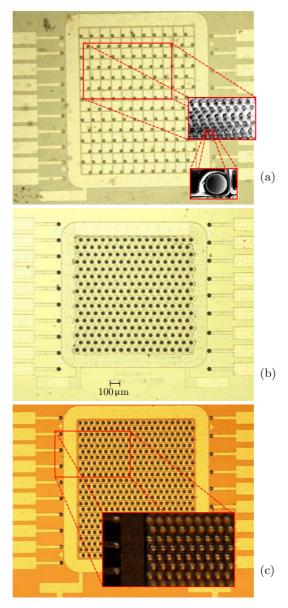

| 4.11 | Microscope photographs of the DPS100 (a), DPS70 (b) and DPS55 (c) array test chips integrated in UMCL180. Bounding boxes are $1.5 \text{mm} \times 1.5 \text{mm}$                                                                                                                                |

| 5.1  | Microscope photographs of backsides of Si-based pixelated X-ray detectors with grown bumps to be hybridized with DPS100 (a), DPS70 (b) and DPS55/52 (c) CMOS ROICs of Fig. 4.11                                                                                                                  |

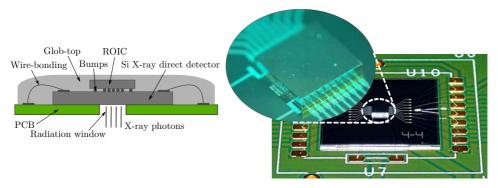

| 5.2  | Cross-section scheme (left) and photograph (right) of the X-ray hybrid imager after flip-chip wire-bonding to the windowed PCB                                                                                                                                                                   |

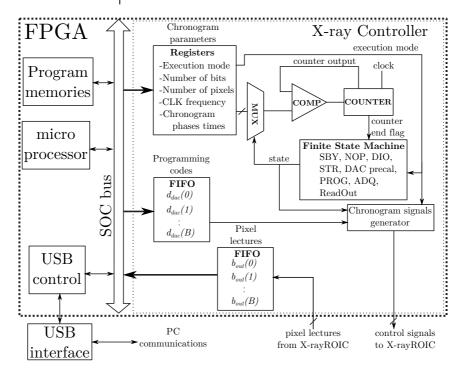

| 5.3  | Simplified scheme of the FPGA-based interface for the radiation tests of X-ray hybrid imagers                                                                                                                                                                                                    |

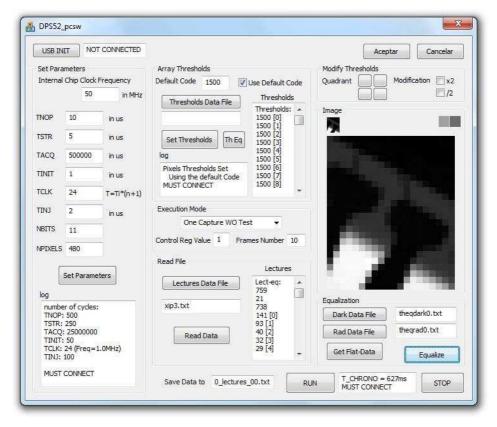

| 5.4  | Screenshot of the custom HMI developed for the radiation tests of X-ray hybrid imagers                                                                                                                                                                                                           |

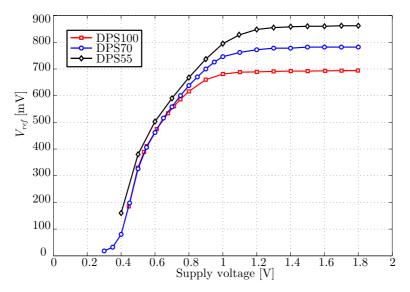

| 5.5  | Experimental voltage supply sensitivity of the in-pixel reference voltage for the three DPS generations                                                                                                                                                                                          |

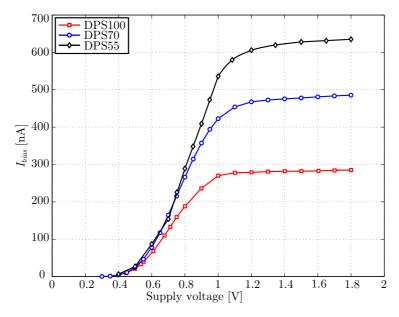

| 5.6  | Experimental voltage supply sensitivity of the in-pixel bias reference for the three DPS generations                                                                                                                                                                                             |

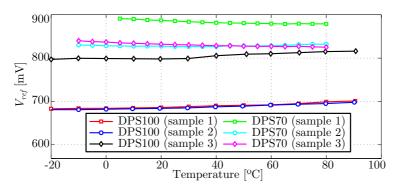

| 5.7  | Experimental thermal sensitivity of in-pixel reference voltage extracted from several samples of DPS100 and DPS70 designs (DPS55 design is similar)                                                                                                                                              |

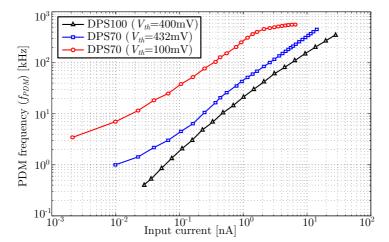

| 5.8  | Experimental PDM transfer function of the in-pixel ADC measured in DPS100 and DPS70 pixel generations. In the case of DPS70, data for two different gain programming levels is shown. Results are obtained using a DC input current to standalone pixel experiments of Fig. 4.8 and Fig. 4.9 110 |

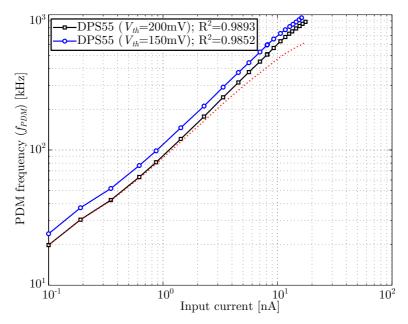

| 5.9  | Experimental PDM transfer function of the in-pixel ADC measured in the DPS55 pixel design for two different gain programming levels. The red dashed line represents the transfer function using classic charge integration for $T_{res}=0.5\mu \rm s$ . The classic schemes coefficient of determination ( $R^2\approx 0.95$ ) is clearly improved. Results are obtained using DC current as input to standalone pixel experiments of Fig. 4.10 11 | 1 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

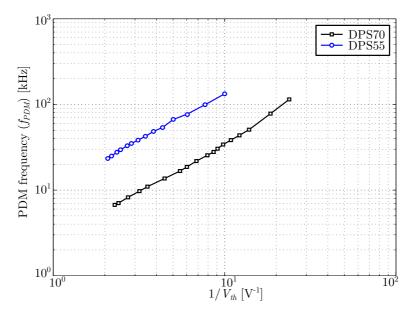

| 5.10 | Experimental in-pixel ADC gain programming range under constant input currents for DPS70 and DPS55 pixel generations                                                                                                                                                                                                                                                                                                                               | 2 |

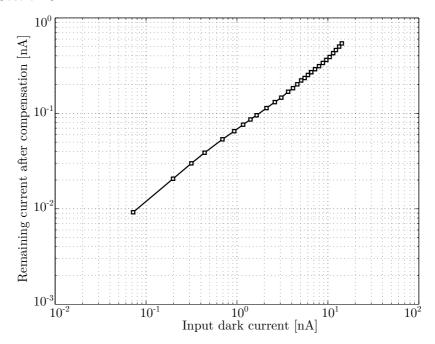

| 5.11 | Experimental remaining current after dark current compensation for DPS70 pixel generation. Over 95% of the input dark current is canceled                                                                                                                                                                                                                                                                                                          | 3 |

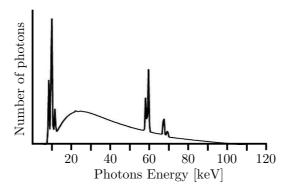

| 5.12 | Unfiltered spectrum of a typical X-ray tube with Tungsten anode [101]                                                                                                                                                                                                                                                                                                                                                                              | 4 |

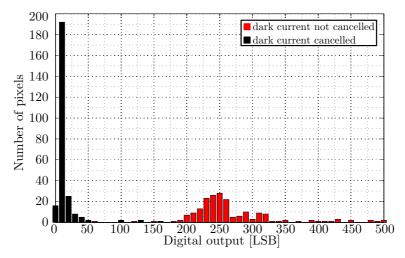

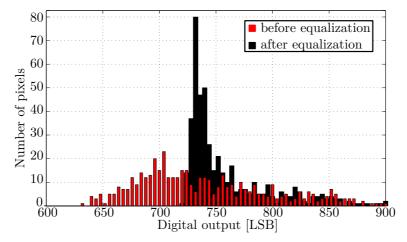

| 5.13 | Experimental distribution of all pixel readings for the DPS70 $16 \times 16$ pixel array under no X-ray illumination with and without in-pixel dark current cancellation. Detector is biased at $V_{com} = 50 \text{V}$ and large integration times are used ( $T_{acq} = 3 \text{s}$ ) without equalization ( $q_{dac} = 1000 \text{LSB}$ for all pixels) 11                                                                                      | 5 |

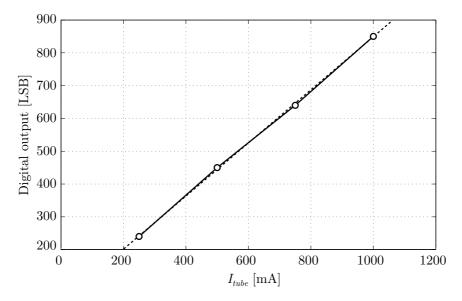

| 5.14 | Experimental DPS52 digital output versus X-ray tube intensity for $T_{acq}$ =1000ms and $q_{dac}$ =2047LSB. Obtained coefficient of determination is $R^2=0.9996$                                                                                                                                                                                                                                                                                  | 6 |

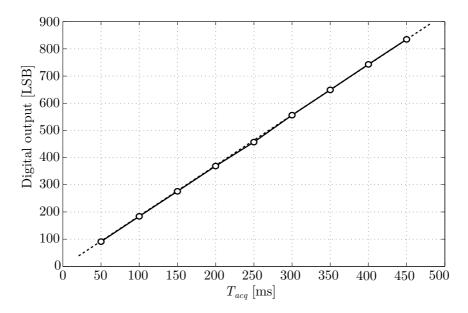

| 5.15 | Experimental DPS52 digital output versus acquisition time for $q_{dac}$ =1024LSB. Obtained coefficient of determination is $R^2=0.9999.$                                                                                                                                                                                                                                                                                                           | 7 |

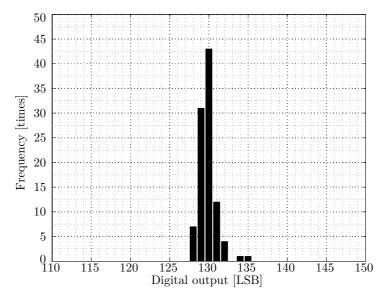

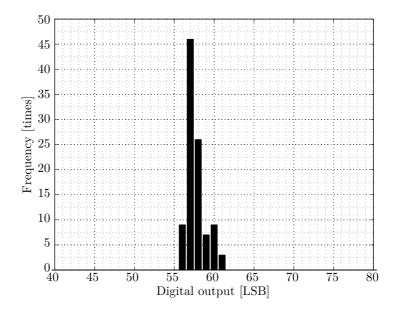

| 5.16 | Experimental digital outputs distribution of a DPS70 pixel for 100 different dark current acquisitions. $V_{com}=50\mathrm{V},$ $T_{acq}=1625\mathrm{ms}$ and $q_{dac}=2047\mathrm{LSB}.$                                                                                                                                                                                                                                                          | 8 |

| 5.17 | Experimental digital outputs distribution of a DPS52 pixel for 100 different dark current acquisitions. $V_{com}=80\text{V},$ $T_{acq}=1000\text{ms}$ and $q_{dac}=2047\text{LSB}.$                                                                                                                                                                                                                                                                | 8 |

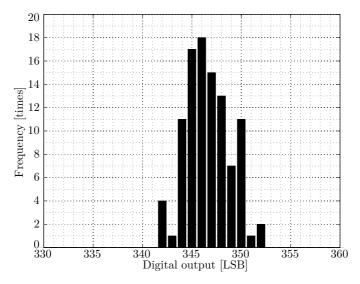

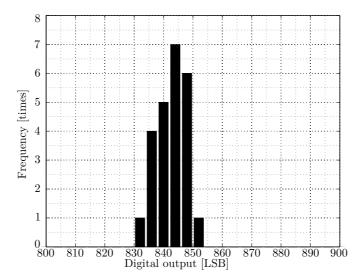

| 5.18 | Experimental digital outputs distribution of a DPS70 pixel for 100 different radiation acquisitions. $V_{com} = 80 \text{V}$ , $T_{acq} = 325 \text{ms}$ and $q_{dac} = 2047 \text{LSB}$                                                                                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.19 | Experimental digital outputs distribution of a DPS52 pixel for 24 different radiation acquisitions. $V_{com}=80\mathrm{V},T_{acq}=1000\mathrm{ms}$ and $q_{dac}=2047\mathrm{LSB}.$                                                                                                                                                                                             |

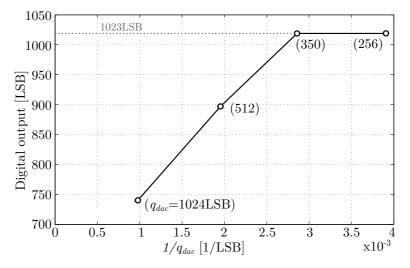

| 5.20 | Experimental digital output versus gain programming of a DPS52 pixel for $T_{acq}$ =400ms                                                                                                                                                                                                                                                                                      |

| 5.21 | Experimental distribution of all DPS52 $20 \times 24$ pixel array under flat radiation before and after in-pixel threshold equalization. Initial $q_{dac}=1000 \text{LSB}$ is adapted for equalization in the course of 10 iterated captures $(T_{acq}{=}400 \text{ms})$ 121                                                                                                   |

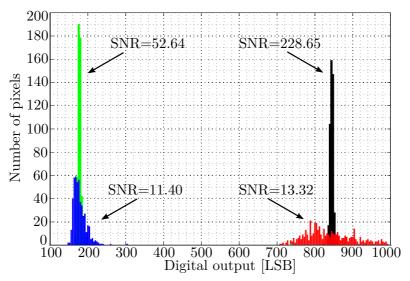

| 5.22 | Experimental distribution of the DPS52 pixel array digital output under flat non-attenuated radiation before (red) and after (black) post-processing equalization. Distributions attenuating X-ray radiation with a 0.4mm thick Al sheet are additionally presented before (blue) and after (green) equalization. In both cases, $T_{acq}$ =1000ms and $q_{dac}$ = 2047LSB 122 |

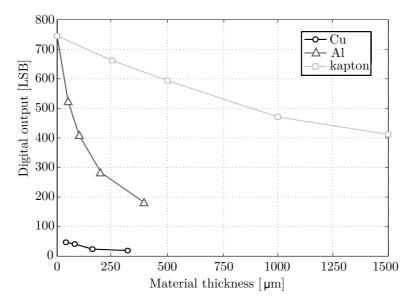

| 5.23 | Experimental DPS52 pixel digital output obtained under radiation attenuation with several materials and thickness values for $T_{acq}$ =400ms and $q_{dac}$ =1024LSB                                                                                                                                                                                                           |

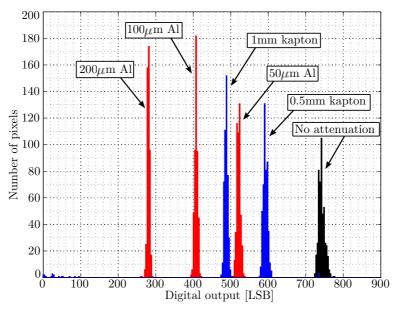

| 5.24 | Experimental equalized distributions from DPS52 pixel array readings under flat non-attenuated radiation (black), and attenuation with 0.5mm and 1mm thickness of kapton (blue) and with $50\mu\text{m}$ , $100\mu\text{m}$ and $200\mu\text{m}$ thickness of Al (red). In all cases, $T_{acq}{=}400\text{ms}$ and $q_{dac}{=}1024\text{LSB}$                                  |

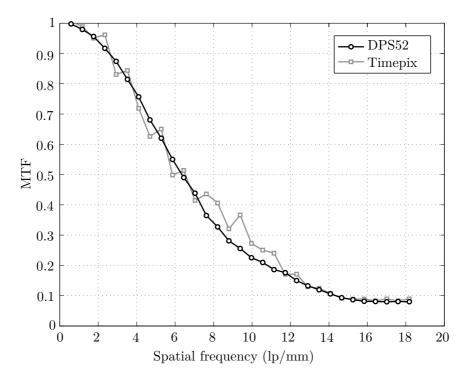

| 5.25 | Experimental MTF from DPS52 pixel array compared to Timepix [103]. In both cases, the slanted edge MTF extraction algorithm described in Section 1.2.2 is used 125                                                                                                                                                                                                             |

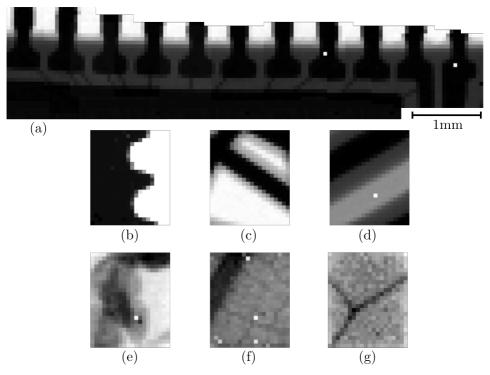

| 5.26 | 26 Experimental composition of several single equalized shots                               |  |

|------|---------------------------------------------------------------------------------------------|--|

|      | to obtain an equivalent larger area image of an encapsulated                                |  |

|      | chip (a), and small single images of the profile of a small                                 |  |

|      | screw (b), metal wires covered with plastic (c), small region                               |  |

|      | of a flat cable (d), part of an ant (e), a low contrast leaf                                |  |

|      | (f) where the stem can be distinguished, and a bug wing                                     |  |

|      | (g) where considerably small and low contrast veins can be                                  |  |

|      | distinguished. For all cases, $T_{acq}$ =400ms                                              |  |

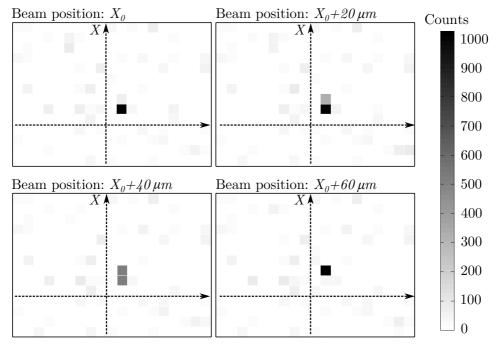

| 5.27 | Experimental images captured from DPS52 pixel array with                                    |  |

|      | $50\mu$ m-pitch, by moving a $15\mu$ m× $15\mu$ m focused X-ray beam                        |  |

|      | through X axis direction in $20\mu \text{m}$ steps. For all cases, $T_{acq} = 17 \text{ms}$ |  |

|      | and $q_{dac}$ =2047                                                                         |  |

# List of Tables |

| 1.1 | Main requirements for X-ray detectors targeting mammography applications [9]                                                                                               |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Main characteristics at room temperature of the most common materials for X-ray direct detection                                                                           |

| 1.3 | Comparison of state-of-the-art ROIC pixels for direct X-ray imaging. Readout methods are charge-integration (Ch-I) and photon-counting (Ph-C)                              |

| 4.1 | Initial specifications for the DPS design example 82                                                                                                                       |

| 4.2 | UMC 0.18 $\mu$ m CMOS technology characteristics 83                                                                                                                        |

| 4.3 | Developed array properties for each pixel generation 99                                                                                                                    |

| 5.1 | Comparison of CMOS DPS parameters for the three design generations developed in this work                                                                                  |

| 5.2 | Comparison of DPS52 generation to the state-of-the-art ROIC pixels for direct X-ray imaging. Read-out methods are charge-integration (Ch-I) and photon-counting (Ph-C) 129 |

# List of Acronyms

| ADC analog to digital converter              | 9  |

|----------------------------------------------|----|

| APS active pixel sensor                      | 7  |

| ASIC application specific integrated circuit | 8  |

| BJT bipolar junction transistor              | '3 |

| CCD charge coupled device                    | 8  |

| CDS correlated double sampling               | 5  |

| CMOS complementary metal oxide semiconductor | 3  |

| CTIA capacitive transimpedance amplifier     | 5  |

| DAC digital to analog converter              | 1  |

| <b>DFM</b> design for manufacturing9         | 9  |

| <b>DIL</b> dual in-line                      | 4  |

| <b>DPS</b> digital pixel sensor9                   |

|----------------------------------------------------|

| <b>DQE</b> detective quantum efficiency            |

| DTG dual transmission gate                         |

| ENC equivalent noise charge                        |

| EP europractice                                    |

| ESF edge spread function                           |

| FIFO first-in first-out                            |

| FOM figure of merit                                |

| FPA focal plane array                              |

| FPD flat panel detector6                           |

| FPGA field programmable gate array                 |

| FPN fixed pattern noise                            |

| <b>HMI</b> human machine interface                 |

| IC integrated circuit82                            |

| IMB-CNM Institut de Mictroelectrònica de Barcelona |

| LUT look-up-table                                  |

| LSB least significant bit                          |

| <b>LSF</b> line spread function                    |

| MiM metal in metal                                         |

|------------------------------------------------------------|

| MOS metal oxide semiconductor                              |

| MOSFET metal oxide semiconductor field effect transistor65 |

| MPW multi project wafer83                                  |

| MTF modulated transfer function                            |

| MSB most significant bit                                   |

| <b>NPS</b> noise power spectrum14                          |

| NTF noise transfer function                                |

| OSR oversampling ratio                                     |

| PC personal computer                                       |

| PCB printed circuit board                                  |

| PDM pulse density modulation                               |

| PRMLS pseudo-random maximum length sequence                |

| <b>PSF</b> point spread function                           |

| PTAT proportional to absolute temperature                  |

| <b>PWM</b> pulse width modulation                          |

| ROI region of interest                                     |

| ROIC read-out integrated circuit                           |

| SC switched-capacitor                     | 58  |

|-------------------------------------------|-----|

| S/H sample and hold                       | 70  |

| SNDR signal-to-noise and distortion ratio | 58  |

| SNR signal-to-noise ratio                 | 10  |

| SR spatial resolution                     | 12  |

| STF signal transfer function              | 52  |

| TFT thin film transistor                  | 6   |

| UBM under bump metalization               | 102 |

| USB universal serial bus                  | 104 |

## Introduction | 1

This chapter introduces the main motivation of the presented work together with the required background in terms of X-ray imaging fundamentals, existing technologies, practical metrics and state-of-the-art techniques. Also, the target objectives and scope of this thesis are exposed.

#### 1.1 Motivation

X-ray imaging is a key technology in many application fields such as physics [1], medicine [2], industry [3], security [4], chemistry [5] or even art [6]. This is due to the ability of X-ray particles to pass through matter with a penetrating power related to their energy and matter properties. For example, water or fat are easily penetrated compared with bones or calcifications, which are more dense. This feature makes X-rays extremely useful to non-destructively image the inside of objects which are usually opaque to visual light. However, X-ray photons can also ionize atoms, which could damage living tissues. Therefore, and especially in medical applications, the compromise between radiation dose and image quality leads to a very intense and extensive research on this topic.

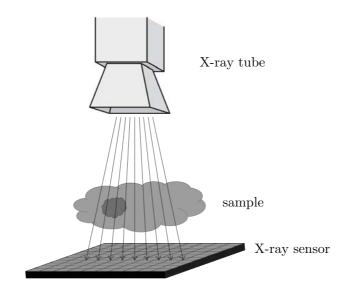

An X-ray imaging system can be schematized as in Fig. 1.1. It is mainly composed of an X-ray source, which generates the X-ray photons, and the X-ray sensor. The spatial distribution of X-ray photons after the interaction with the sample is captured by the X-ray sensor, which converts this information into image data. The X-ray sensor is composed of basic image units

called pixels (picture elements), whose size is related to the system spatial resolution. For each application, the sensor must meet certain performance figures in terms of X-ray photons energy, limited radiation dose, imager size or spatial resolution. For example, concerning X-ray imaging applications, mammography is probably one of the most demanding fields due to its large area and high resolution requirements at low radiation doses. Proof of this interest is the number of references in the literature, specially due to the social importance of the early detection of breast cancer in women [7, 8]. Table 1.1 summarizes some of these requirements. In this particular case, pixel pitch under  $50\mu$ m are not advantageous since smaller microcalcifications do not provide useful information for diagnosis [9].

Figure 1.1 | Simplified scheme for an X-ray imaging system.

Current research in X-ray imaging systems is mainly focused in improving image quality at low radiation doses. In this sense, digital direct hybrid systems are one of the most promising technologies. As it will be discussed later in this chapter, obtaining large sensing areas with these systems is challenging, since the limited yield of technology tends to increase their costs. Also, pixel functionality and power efficiency are opposed to the spatial resolution and image quality.

| Parameter           | Requirement                                |

|---------------------|--------------------------------------------|

| Imager size         | $18\text{cm} \times 24\text{cm}$           |

| Pixel pitch         | $> 50 \mu \text{m} \times 50 \mu \text{m}$ |

| Acquisition time    | < 5s                                       |

| X-ray photon energy | $20 \mathrm{keV}$ to $50 \mathrm{keV}$     |

| Exposure dose       | $0.6 \mathrm{mR}$ to $240 \mathrm{mR}$     |

**Table 1.1** Main requirements for X-ray detectors targeting mammography applications [9].

This thesis presents novel low power complementary metal oxide semiconductor (CMOS) pixel circuits for digital direct X-ray imaging targeting low-cost and modular imaging systems.

# 1.2 X-Ray Imaging

#### 1.2.1 Fundamentals

X-rays, which were discovered by Wilhelm Conrad Röntgen in 1895, are referred to the electromagnetic radiation with energies between 100eV and 100keV, corresponding to spectrum frequencies between  $3 \times 10^{16} \rm Hz$  and  $3 \times 10^{19} \rm Hz$ , and to wavelengths between 10nm and 0.01nm.

X-rays can be generated in a so-called X-ray tube by the acceleration of electrons applying high voltage potentials (typically tens of kV) between the hot cathode and the metal target (the anode) usually made of tungsten or molybdenum. The amount of applied voltage determines the maximum energy of the resulting X-ray photons. The collision of these accelerated electrons with the target generate X-rays due to the combination of two atomic processes: the X-ray fluorescence and the Bremsstrahlung. The former occurs when the accelerated electron kicks out an orbital electron of the target atoms and the electrons of high level energies fill the left vacancy and emit X-rays. The spectrum produced by this process is composed by discrete frequencies that depend on the target material properties. The Bremsstrahlung process consists on the accelerated electron being scattered,

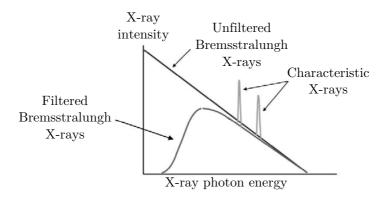

which produces a continuous spectrum. Filters are usually employed to cut off a fraction of this part of the spectrum. Fig. 1.2 shows the typical spectrum obtained from an X-ray tube [9]. In order to generate X-rays with narrower spectrum windows and better linear polarizations and collimation, particle accelerators can be used for synchrotron radiation.

Figure 1.2 Typical spectrum obtained from X-ray tubes with fluorescence peaks and Bremsstrahlung effects [9].

As for the interaction of X-rays with matter, in terms of penetrating power and absorbed dose, it depends on both X-rays properties and matter themselves. Basically, this interaction is dominated by three different processes, depending on photon energy  $(h\nu)$  and atomic number (Z) of the material [9]. First, the photoelectric effect occurs when a low-energy photon is absorbed by an atomic electron, which will be ejected. Second, the Compton scattering takes place when a high-energy photon transfers part of its energy to an electron, which will be emitted. Finally, the Rayleigh scattering happens when the photon simply varies its trajectory, with no energy transfer.

The absorbed dose is the radiation energy deposited in a material (e.g. human tissues) and it is measured in Grays (Gy) or rads (1rad= 0.01Gy), which are equivalent to the units of energy in Joules deposited in one kilogram of material. The biological effect of the radiation on a living tissue is different depending on its nature. Therefore, the equivalent or effective dose is quantified by weighting the absorbed dose with a factor  $(w_R)$  that depends on the type of radiation and tissue, and it is measured in Sieverts (Sv). The limit of effective dose, which is legally fixed by each country, is

around 1mSv/year. In comparison, the dose of a screening mammography or a chest radiography are around 3mSv and 0.1mSv respectively [10].

The distance traveled by an X-ray photon before interacting is called the mean free path and depends on the photon energy and the atomic number of the material. Once inside the material, the beam intensity at a depth x presents an exponential behavior following the Lambert-Beer law [11]:

$$I(x) = I_0 e^{-\mu(h\nu, Z)x}$$

(1.1)

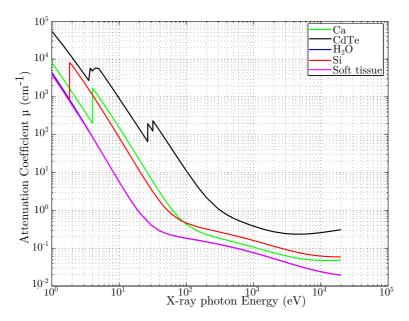

where  $I_0$  is the beam intensity before reaching the material and  $\mu(h\nu, Z)$  (in  $cm^{-1}$ ), which is proportional to the inverse of the mean free path, is the so-called linear attenuation coefficient and represents the fraction of incident photons interacting with the material per unit length. Attenuation increases with Z and decreases with  $h\nu$ . Fig. 1.3 shows the behavior of the attenuation coefficient of different elements versus the photon energy.

Figure 1.3 Attenuation coefficient vs photons energy for different elements or materials [12].

In conclusion, the intensity of X-rays after crossing the sample in Fig. 1.1 depends on their energy and on the particular matter of the region they are passing through, thus an image is generated. For example, using X-rays of about 20keV, a beam passing through a soft tissue, which contain large quantities of water, will experience less absorption than a beam passing through a calcification tumor, which is mainly composed of calcium.

In practice, different beam intensities in different areas will reach the detector of Fig. 1.1 generating an image of the studied sample. Although image magnification is possible by modifying distances between the source generating the X-ray conic beam, the imaged sample and the detector, optical amplification is not feasible since X-rays are not easily focused [13].

Therefore, the detector must capture most of the incoming photons to obtain good quality image at low radiation doses. I.e. it must show a high efficiency, which is the ratio between absorbed and incoming photons.

Regarding the method to record the high energy photons, X-ray imaging systems have evolved through the following technologies:

Film systems. The earliest X-ray system was based on photographic film, which is composed of a sheet of plastic covered with a photosensitive emulsion. After being exposed to radiation and chemical processing, a visible image is created. Despite its low quantum detection efficiency, typically 1% to 2%, which translates into high radiation doses, this method is still in use thanks to its low cost, high resolution and the possibility of obtaining large sensitive areas. Efficiency can be improved by covering the emulsion with phosphor, which converts the incident X-rays to visible light, but at the cost of resolution losses.

Flat panel detectors. The introduction of pixelated flat panel detectors (FPDs) brought an improvement in the efficiency, contrast and dynamic range, as well as the possibility of image digitization. In short, they consist on a converter material coated or deposited on an array of thin film transistors (TFTs). Two types of FPDs can be distinguished: indirect conversion and direct conversion detectors.

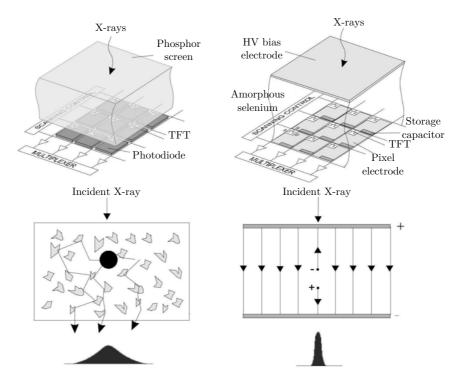

Indirect conversion detectors convert X-rays to visible spectrum light through a scintillating material (typically cesium iodide) deposited over an array of photodiodes in amorphous silicon substrates. The scintillator illuminates the photodiodes, which then convert the light into electronic charge and are connected to the readout circuitry. This photodiode together with the readout circuitry form the basic element called active pixel sensor (APS). This type of detectors tend to experience lateral light diffusion in the scintillator, lowering significantly the spatial resolution. Direct conversion detectors, on the other hand, exploit amorphous or polycrystalline semiconductor materials (typically amorphous selenium) to directly convert X-ray photons into electronhole pairs avoiding the lateral diffusion issue at pixel level. Fig. 1.4 shows the operating principle and the signal profile for indirect and direct detection [14]. In both cases, the sensitive material is deposited directly over the readout circuit array. However, a large amount of energy is needed to create electron-hole pairs. Since the pixel circuitry area usually includes a photodiode or a capacitance together with at least a switching thin film transistor plus connectivity routing, the fill factor may be poor, weakening signal in tiny pixel sizes. The amount of generated charge, which is somehow proportional to the photon energy, is stored locally at each pixel and sent to the readout circuit, where information is processed and digitized. There are many advantages in digital imaging: images can be stored and displayed electronically with no need for material support, they can be shared easy and quick, and computer assisted post processing is also available [15, 16].

With this technology, large area X-ray imagers have been obtained with sizes up to  $40\text{cm} \times 40\text{cm}$  and pixels pitchs down to  $150\mu\text{m}$  [17].

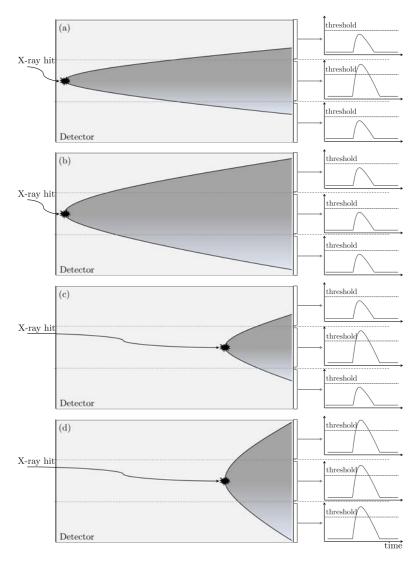

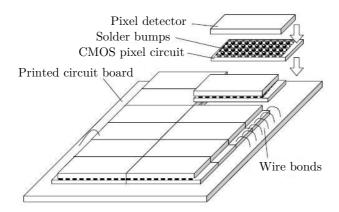

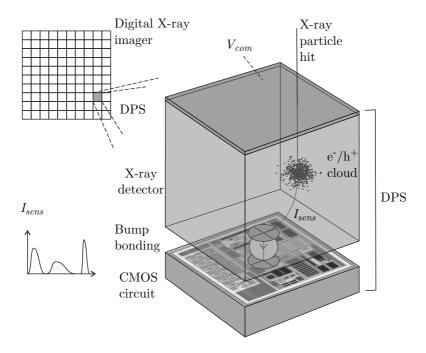

Hybrid systems. In order to achieve a sensitive area of almost 100% filling factor and improve resolution and efficiency, a crystalline semiconductor direct conversion detector pixelated in an array of p-n junctions can be hybridized with the readout circuit. This hybridization is usually completed employing bump-bonding and flip-chip packaging techniques, which connect pixel-by-pixel the readout circuitry with its corresponding X-ray detector. Another advantage of this kind of sensors compared with monolithic solutions is that different detector and readout circuit technologies can be mixed, allowing the use of the same readout circuit with a wide range of detector materials. Hence,

Figure 1.4 | Operation principle and signal profile given by indirect (left) and direct (right) X-ray detectors [18].

both parts can be chosen independently to satisfy the requirements of a particular application. Fig. 1.5 shows a representation of a direct conversion detector hybridized with the readout circuitry using bump-bonding and flip-chip techniques. A more detailed description of direct semiconductor detectors for hybrid systems can be found in Section 1.2.3.

Regarding the readout circuit technology for hybrid systems, it is usually composed of an application specific integrated circuit (ASIC) formed by an array of pixel readout circuits. These dedicated ASICs are called read-out integrated circuits (ROICs). The continuous advances of CMOS technologies, have made possible to increase the pixel functionality of these ROICs from the simplicity of charge coupled devices (CCDs), to highly complex

Figure 1.5 X-ray sensor consisting on the bump-bonding hybridization of a direct conversion detector with its readout circuitry.

APS cells including analog to digital converters (ADCs), programmability and data storage at a pixel level resulting in digital pixel sensors (DPSs).

The reading method of these pixels can be classified into two categories: charge-integration and photon-counting. The charge-integration method accumulates all the charge generated by X-rays, but also including circuit noise, over a certain time interval. On the other hand, photon-counting consists on counting only those individual photons whose energy exceeds a certain threshold. This alternative approach is more immune to circuit noise, but it can experience charge-sharing and pile-up effects. The first undesired effect occurs when the charge generated by an X-ray photon that should be counted is spreaded among some neighboring pixels either without exceeding the threshold in any of them causing the system to discard this photon, or exceeding this threshold in some of them causing multiple counts. Pile-up effect happens when photons arrive so close to each other that they can not be distinguished in time. A more detailed discussion about charge-integration versus photon-counting can be found in Section 1.2.4.

Nevertheless, and despite all the advantages of X-ray imagers based on the hybridization of direct conversion detectors with CMOS ROICs, large and seamless sensing areas can only be obtained at a high costs due to restrictions in technology yields [17], as explained in Section 1.2.3.

## 1.2.2 Figures of Merit

This section introduces the main metrics applied to X-ray imaging which will be used as figure of merits (FOMs) for evaluating the proposed work.

#### **Contrast**

The radiographic contrast, which quantifies the variation between different areas of the X-ray image, is defined according to Eq. 1.2, where  $\Delta I_{ROI}$  is the variation of signal intensity in the region of interest (ROI) with respect to the background signal intensity  $I_{bkgnd}$ . The contrast depends on the difference of the attenuation coefficients of materials (areas), but not on the number of incident photons (dose). Therefore, it is affected by photons and charge scattering on the detector.

$$C \doteq \frac{\Delta I_{ROI}}{I_{bkgnd}} \tag{1.2}$$

## Signal-to-Noise Ratio

The noise level determines the floor of the image quality, since at levels below this threshold true signal fluctuations are confused with noise fluctuations. For example, medical applications like mammography, show small contrast between the different soft tissues, so the higher the power signal-to-noise ratio (SNR) the better the image quality. The fluctuation of the number of photons absorbed in the detector per unit area is called the photonic noise, or quantum mottle, and it has a Poisson distribution behavior with the incoming signal power. The power SNR at the input of an imaging system for a monoenergetic X-ray beam can be written as:

$$SNR_{in} \doteq \frac{S_{in}}{\sqrt{N_{in}}} \equiv \frac{S_{in}}{\sqrt{S_{in}}} = \sqrt{S_{in}}$$

(1.3)

Hence, SNR is increased with higher doses, which leads to a compromise between image quality and radiated dose. It can also be argued that scaling down pixel area, smaller details of an image become noticeable, but also SNR is reduced since the dose per pixel is smaller.

In a direct conversion detector, if  $\eta$  is the X-ray absorption efficiency of the detector and G is the conversion gain, signal power after the conversion of photons into charge is:

$$S_{conv} = \eta G S_{in} \tag{1.4}$$

On the other hand, noise power after the conversion is the uncorrelated sum of:

$$N_{conv} = \sqrt{S_{conv}G + S_{conv}F} = \sqrt{\eta G^2 S_{in} + F \eta G S_{in}}$$

(1.5)

where F stands for the Fano factor, the ratio between the variance of the observed mean energy and the variance predicted from Poisson statistics. F is specific for each material but almost independent of the photon energy [19]. For example the Fano Factor for Si is 0.115, while for GaAs is about 0.18 [20]. As a result, SNR at the output of the detector is given by

$$SNR_{conv} = \frac{\eta GS_{in}}{\sqrt{\eta GS_{in}}\sqrt{G+F}} \equiv \sqrt{\frac{\eta GS_{in}}{G+F}}$$

(1.6)

which equals  $SNR_{in}$  for the ideal case of G >> F and  $\eta = 1$ . Other noise sources are related to inhomogeneities in the detector, and the electronic noise of the read-out circuit itself. The inhomogeneities in both the detector and the readout circuit produce fixed pattern noise (FPN), which is proportional to the signal power and can be reduced by calibration.

#### **Modulation Transfer Function**

The modulated transfer function (MTF) describes the spatial frequency response of an imaging system. In other words, MTF quantifies how the contrast is transmitted. It can be expressed as the ratio of the modulation of a sinewave at the input and output of the detector at a given spatial frequency:

$$MTF \doteq \frac{C_{out}}{C_{in}} \equiv \frac{\left(\frac{A_{max} - A_{min}}{A_{max} + A_{min}}\right)_{out}}{\left(\frac{A_{max} - A_{min}}{A_{max} + A_{min}}\right)_{in}}$$

(1.7)

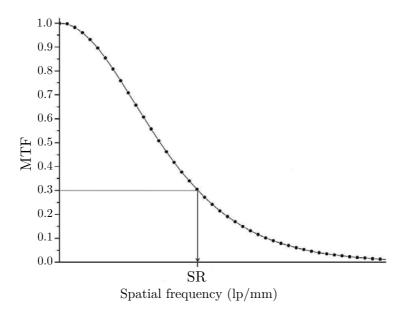

where A is the amplitude of the sinewave, and the spatial frequency is given in lines per millimeter (lp/mm). MTF is usually normalized to 1 at 0 spatial frequency and it decreases as the spatial frequency increases as shown in Fig. 1.6. The spatial frequency where MTF equals to 0.3 defines the spatial resolution (SR).

Figure 1.6 | Typical MTF behavior.

In multistage systems, the total MTF is the product of the individual MTFs.

The point spread function (PSF) is defined as the response of an imaging system to a point light source. Its degradation, which is observed as image unsharpness, is mainly caused by charge diffusion in the detector. Due to the

difficulty of its generation and measurement, the line spread function (LSF) is used instead and defined as the response of the imaging system to an infinite long and narrow line. Also, edge spread function (ESF) is defined as the distribution in absorbed energy per unit area that can be extracted from the image of a sharp edge of a total absorbing material.

The MTF is also defined as the Fourier transform of the LSF. Therefore, it can be measured by imaging a precision edge slightly tilted to the pixel column or row. The data along the direction of the edge gives the ESF figure, which leads to the LSF performance by differentiation, and to the MTF characteristic using the Fourier transformation.

The theoretical limit of MTF for squared shape pixels is determined by the pixel size L and the Fourier transform of a step function with a width of one pixel as:

$$MTF_{lim} = \frac{1}{L} \left| \int_{-L/2}^{L/2} e^{i2\pi f x} dx \right| = \frac{\sin(\pi f L)}{\pi f L} = \operatorname{sinc}(\pi f L)$$

(1.8)

where f stands for the spatial frequency. The Nyquist frequency is the maximum spatial frequency that can be reconstructed. In pixelated systems it is given by:

$$f_{Nyq} = \frac{1}{2L} \tag{1.9}$$

In images with spatial frequency contents higher than  $f_{Nyq}$ , aliasing creates distortion. Thus, it is important to have the highest possible MTF at this frequency.

## **Detective Quantum Efficiency**

The detective quantum efficiency (DQE) of an image system is described at each spatial frequency by the ratio of the input to output SNRs:

$$DQE = \left(\frac{SNR_{out}}{SNR_{in}}\right) \tag{1.10}$$

In complex imaging systems, the overall DQE is the product of the DQEs of each stage. Therefore, it is never better than the worst DQE. For direct detecting systems it becomes critical the absorption efficiency  $\eta$  of the detector, as can be extracted from the ideal case of Eq. 1.6 and Eq. 1.3.

DQE can also be expressed in terms of MTF and the noise power spectrum (NPS), which is the variance of the signal for different spatial frequencies:

$$DQE = \frac{\overline{S}^2 \cdot MTF^2}{\Phi \cdot NPS} \tag{1.11}$$

where  $\overline{S}$  is the average image signal and  $\Phi$  is the entering X-ray fluence [19].

#### 1.2.3 Direct Conversion Semiconductor Detectors

As introduced in Section 1.2.1, the most promising results in X-ray imaging are obtained from digital direct hybrid systems [21–24]. In general, they involve a ROIC hybridized through bump-bonding and flip-chip techniques with an X-ray detector material, which converts photons directly to the electronic charge to be read by the ROIC.

Direct conversion detectors for hybrid X-ray imaging systems usually employ high resistivity crystalline semiconductor materials to take benefit of the small amount of energy needed to create electron-hole pairs while still keeping this threshold high enough to avoid thermally generated charge carriers. Thanks to this property, the incoming X-ray photons generate photoelectrons in the detector material, which in turn will excite other electrons creating a charge cloud.

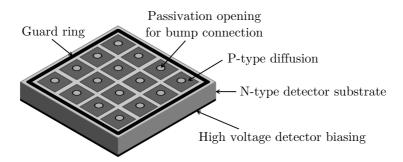

In order to locally collect this charge, the detector is designed as an array of reverse biased p-n junctions or Schottky diodes with a small opening in the passivation for the bump-bonding connection to the ROIC by flip-chip as shown in Fig. 1.7. Another advantage of crystalline semiconductors is that carriers lifetime is orders of magnitude higher than in amorphous or polycrystalline structures, allowing higher thickness and/or lower biasing voltages for the detectors [25]. Unfortunately, large area crystalline structures are difficult to obtain.

Figure 1.7 Representation of a direct X-ray detector consisting in an array of reverse biased p-n junctions.

In practice, the polarization must be high enough to fully deplete the detector of free carriers to ensure the collection of almost all the generated charge, avoid charge recombination and minimize lateral charge diffusion. Furthermore, with the purpose of reducing leakage current and avoid undesired lateral effects on the peripheral pixels, the use of guard rings is strongly recommended [26, 27].

The most common materials in direct conversion X-ray detectors are Si, CdTe and GaAs [24], with different results in each case [28]. Their main characteristics are summarized in Table 1.2.

| Property                       | $\mathbf{Si}$ | CdTe  | $\mathbf{GaAs}$ |

|--------------------------------|---------------|-------|-----------------|

| Atomic number $(Z)$            | 14            | 48/52 | 31/33           |

| Density (g/cm <sup>3</sup> )   | 2.33          | 6.20  | 5.31            |

| Band Gap (eV)                  | 1.12          | 1.56  | 1.42            |

| Ionization energy (eV)         | 3.63          | 4.45  | 4.20            |

| Electrons mobility $(cm^2/Vs)$ | 1500          | 1050  | 8500            |

| Holes mobility $(cm^2/Vs)$     | 450           | 100   | 400             |

Table 1.2 | Main characteristics at room temperature of the most common materials for X-ray direct detection.

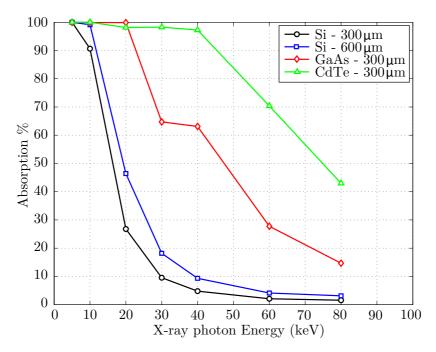

Since ionization energy, which is the energy needed to create an electron-hole pair, is similar in all of them, nearly the same performance is expected in terms of the generated charge per photon. The most important difference in performance is given by their behavior in terms of X-ray photon absorption efficiency at different energies, as shown in Fig. 1.8.

Figure 1.8 | Comparison of absorption efficiency for detector materials of Table 1.2 versus X-Ray photon energy. Detector material and thickness are shown in the legend [29].

From Fig. 1.8 and Fig. 1.3, CdTe and GaAs detectors seem to be a better choice compared to Si. On the contrary, Si detectors are widely used thanks to their lower cost, mature technology, and higher yield in terms of purity.

In principle, higher thickness values should give better performance at the cost of higher biasing potentials to fully deplete the detector. However, this high voltage bias increases the diode inverse current, called dark current, which in turn increases with detector heating [30].

Lateral charge diffusion causes splitting of the generated charge cloud among several neighboring pixels of the array. This effect, called charge-sharing, is pronounced in small pitch pixels, and it might cause a problem for readout circuits based on single photon-counting [31–33], as discussed in next section. This issue has been addressed with novel detector design approaches [34].

Regarding the sensing area, state-of-the-art technologies allow the fabrication of crystal silicon ingots for detectors which can reach 400mm diameter as best case. For GaAs and CdTe detectors, this area is much smaller. However, the larger the detector area, the more reduced the purity and uniformity.

In practice, the most limiting factor is the maximum size of ROIC dices due to the photolitographic stepper reticles of CMOS technologies [35]. Although this limitation may be overcome by stitching techniques at mask level [35], CMOS technology yield still dominates the maximum ROIC size.

## 1.2.4 Charge Integration versus Photon Counting

As already mentioned in Section 1.2.1, two processing strategies can be chosen to create an image from the collected charge generated in the direct X-ray detection: charge-integration or photon-counting modes [9].

Photon-counting systems are based on the comparison of the charge generated by a single X-ray photon with a given threshold to determine whether this photon contributes to the output image or is discarded. Thus, each counted photon contributes with the same weight and the lowest measurable signal is a single photon. Since the threshold is set above the noise, the background is eliminated, and large acquisition times are allowed. The dynamic range is therefore limited by the capacity of the digital counter. Furthermore, using multiple threshold levels or sweeping this threshold in consecutive acquisitions, information of the spectrum of the incoming X-ray photons can be obtained, at the expense of a more complex DPS.

On the other hand, charge-integrating systems count all the charge reaching the front-end ROIC, including the dark current itself. This strategy reduces the SNR and the dynamic range. Moreover, since the amount of charge is somehow proportional to the photon energy, the contribution of higher energy photons, which in some cases can carry less useful information show more weight in the output image.

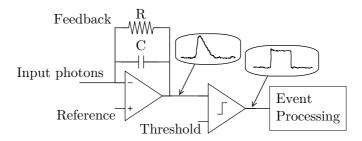

Regarding the circuit complexity, the charge-integrating pixels can be very simple, for example including only few switching transistors and a capacitor as storing element. Generally, photon-counting require front-end electronics with higher complexity. The simplest implementation of Fig. 1.9 includes a pulse shaper amplifier with an RC feedback network and a discriminator to compare amplifier output with the given threshold. Finally, the corresponding event from the comparison result can be either sent outside the array for further processing or stored in the pixel built-in digital counter.

Figure 1.9 | Simplified schematic of a photon counter and operation waveforms when sensing electrons.

The principle of operation is as follows: the incoming charge is accumulated in the amplifier feedback capacitor and is continuously removed by the RC feedback. If the dynamic output temporally exceeds the threshold level, the comparator toggles, generating a single count event. Thanks to the scaling capabilities of CMOS technologies, it is possible to improve this basic circuit functionality at pixel level by adding more threshold levels to obtain spectral information, threshold programmability for calibration and to avoid mismatching in the response of different pixels under the same conditions.

From the above analysis it could be argued that despite the higher circuit complexity needed, photon-counting is superior to charge-integration. However, two practical undesired effects must be taken into account:

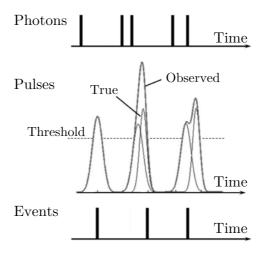

**Pile-up.** First, close in time individual photons can become indistinguishable, thus loosing their information. This effect, known as pile-up, increases at high fluxes, when photons arrive closer than the temporal resolution of the readout circuitry and can not be resolved, as in the

example of Fig. 1.10. The main drawback that this effect presents is the deviation of the response of the pixel from the linear behavior [29, 36]. Furthermore, the unregistered photons can increase up to the point where no photons are counted at all [37, 38].

Figure 1.10 Explanatory example of the information losses in photon-counting due to the pile-up effect. In this study case, 5 photons reach the detector, but only 3 are counted. Moreover, if multiple thresholds were available, the obtained energy resolving information would also be erroneous [39].

Charge-sharing. Another drawback of photon-counting systems extensively studied is charge-sharing [31–33, 40]. Basically, this effect occurs when the charge cloud generated by an X-ray photon expands as a consequence of charge diffusion due to Coulomb repulsion between charges. As a consequence, the generated charge can be shared between two or more neighbored pixels. If the charge cloud that should be counted is highly dispersed, each pixel collects a portion of charge below the required to cause the output of the amplifier to exceed the threshold level. Hence no events are generated and the information carried by the X-ray photon is lost, degrading the image resolution and the spectrometric performance. On the other hand, if a high energy

X-ray photon generates a charge cloud shared by some neighboring pixels, multiple events could be recorded.

Fig. 1.11 summarizes the possible situations combining the energy and charge dispersion cases. Here, the X-ray photon energy level is illustrated as the depth where the X-ray photon interacts and the charge cloud dispersion is shown along with the width of the shadow. The output of the amplifier, which generates an event if the threshold level is exceeded, is also shown.