### Open Archive TOULOUSE Archive Ouverte (OATAO)

OATAO is an open access repository that collects the work of Toulouse researchers and makes it freely available over the web where possible.

This is an author-deposited version published in: <a href="http://oatao.univ-toulouse.fr/Eprints ID">http://oatao.univ-toulouse.fr/Eprints ID</a>: 17302

To link this article: <a href="http://dx.doi.org/10.1109/JEDS.2015.2509606">http://dx.doi.org/10.1109/JEDS.2015.2509606</a>

**To cite this version**: Pelamatti, Alice and Goiffon, Vincent and De Ipanema Moreira, Alexis and Magnan, Pierre and Virmontois, Cedric and Saint-Pe, Olivier and Breart de Boisanger, Michel *Comparison of Pinning Voltage Estimation Methods in Pinned Photodiode CMOS Image Sensors*. (2016) IEEE Journal of the Electron Devices Society, vol. 4 (n° 2). pp. 99-108. ISSN 2168-6734

Any correspondence concerning this service should be sent to the repository administrator: <a href="mailto:staff-oatao@listes-diff.inp-toulouse.fr">staff-oatao@listes-diff.inp-toulouse.fr</a>

# Comparison of Pinning Voltage Estimation Methods in Pinned Photodiode CMOS Image Sensors

A. Pelamatti, V. Goiffon, *Member, IEEE*, A. De Ipanema Moreira, P. Magnan, *Member, IEEE*, C. Virmontois, *Member, IEEE*, O. Saint-Pé, M. Breart de Boisanger

Abstract—The pinning voltage is a key design parameter in Pinned Photodiode CMOS Image Sensors which significantly affects the device performances and which is often used by manufacturers to monitor production lines and for the optimization of technological processes. This work presents a comparative study of pinning voltage estimation methods, which are based both on electrical measurements performed on isolated test structures (or on test structures arrays) and on in-pixel measurements. It is shown, with the support of simulations and experimental measurements, that not all the estimation methods provide an absolute value of the pinning voltage. Moreover, this work demonstrates that the commonly accepted theoretical definition of the pinning voltage does not correspond to the physical parameter which is measured with the existing methods.

Index Terms—CMOS Image Sensor, CIS, pinned photodiode, PPD, Pinning Voltage, characterization.

### I. INTRODUCTION

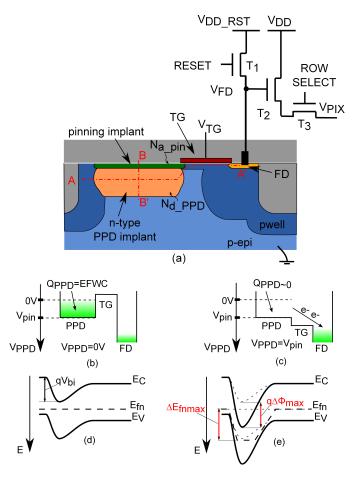

PInned Photodiode (PPD) CMOS Image Sensors (CIS) [1], are currently the main imaging technology for both scientific and commercial applications. The extremely fast ascent of these devices over more mature imaging technologies can be explained by both their low cost (with respect to Charge Coupled Devices) and outstanding noise performances compared to standard 3-transistors active pixel sensors (3T APS). A schematic drawing of a 4-transistors (4T) PPD-CIS pixel is shown in Fig. 1a. The pixel is composed of a PPD, which is the photosensitive element, a floating diffusion (FD) which is responsible for the charge-to-voltage conversion, and four other transistors (T1, T2, T3 and TG in Fig. 1a), which correspond to the reset transistor, the source follower transistor, the column selection transistor and the transfer gate, respectively. The latter enables charge confinement within the PPD (TG off) during charge integration and charge transfer from the PPD toward the FD (TG on) for readout of the signal. The peculiar "sandwiched" structure of the PPD (formed by a double p+np junction) brings two main advantages with respect to 3T APS:

• It strongly reduces the dark current of the device (by isolating the PPD depletion region from the generation

A. Pelamatti (email: alice.pelamatti@isae.fr), V. Goiffon, A. De Ipanema Moreira and P. Magnan are with ISAE-SUPAERO, Université de Toulouse, Toulouse, France. C. Virmontois is with CNES, Toulouse, France. O. Saint Saint-Pé and M. Brèart de Boisanger are with Airbus Defence&Space, Toulouse.

The authors would like to thank CNES and Airbus Defence&Space for supporting the Ph.D of A. Pelamatti. They would also like to thank Mr. A. Lahav (TowerJazz, Israel) and Mrs. X. Cao (XFab, UK) for the interesting discussions on pinning voltage estimation methods that are currently used in the industry.

Fig. 1. (a) Schematic representation of a PPD pixel. The schematic potential diagrams along the cut A-A' at equilibrium and after charge transfer are shown in (b) and (c), respectively. The schematic energy band diagrams along the cut B-B' at equilibrium and at full depletion conditions are shown in (d) and (e), respectively. The dashed curves in (e) represent the bands at equilibrium condition. FD stands for floating diffusion and TG for transfer gate.  $N_{\rm a\_pin}$  and  $N_{\rm d\_PPD}$  are the doping concentrations of the p-type pinning implant and of the n-type PPD implant, respectively. p-epi stands for p-type epitaxy. $V_{\rm bi}$  is the built-in voltage,  $\Delta\Phi_{\rm max}$  and  $\Delta E_{\rm fnmax}/q$  are the maximum variations of the electrostatic potential of the electron quasi-Fermi levels between equilibrium and full-depletion conditions, respectively [2]. q is the elementary charge.

centers located at the  $S_i$ - $S_iO_2$  interface).

• It enables a "confinement" of the PPD potential between the substrate potential and the pinning voltage  $(V_{\rm pin})$ , which therefore represents the maximum PPD potential. As a result, true charge transfer can be implemented, whereas only charge sharing is possible in 3T APS.

The  $V_{\rm pin}$  plays a crucial role in the design of PPD CIS

and often involves design trade-offs depending on the target application. In particular:

- A large  $V_{\rm pin}$  value results in a large equilibrium full well capacity (EFWC) [3], which represents the maximum charge that can be stored by the PPD in dark conditions with the TG in accumulation mode (Fig. 1b and 1c).

- On the other hand, a small  $V_{\rm pin}$  value often results in better charge transfer efficiency performances for given  $V_{\rm DDRST}$  and TG biasing conditions.

This work addresses the definition and physical modelling of  $V_{\rm pin}$  and discusses the working principle and the physical foundation of  $V_{\rm pin}$  estimation methods used in the CIS community. In particular, it is shown that some methods provide arbitrary  $V_{\rm pin}$  values, which depend on the experimental setup. Moreover this study showed that the commonly accepted theoretical definition of the pinning voltage does not correspond to the physical parameter which is measured with the existing methods. This study is supported by both TCAD simulations and experimental data.

### II. PINNING VOLTAGE: PHYSICS AND DEFINITION

The pinning voltage is commonly defined as the maximum deviation of the electron quasi-Fermi potential  $\Delta E_{\rm fnmax}/q$  between equilibrium (the PPD is as full as it can be in dark conditions) and full depletion conditions [4] (where it is assumed that the PPD is fully empty of minority carriers).The electron quasi-Fermi level  $E_{\rm fnmax}$  is related to the concentration of minority carrier in the PPD  $n_{\rm PPD}$  as [2]:

$$n_{\rm PPD} = n_i e^{(E_{\rm fn} - E_i)/kT} \tag{1}$$

with  $n_i$  the intrinsic carrier concentration,  $E_i$  the intrinsic Fermi level (at equilibrium), k the Boltzmann constant and T the temperature. In TCAD simulations, however,  $V_{\rm pin}$  is often retrieved as the maximum variation of the electrostatic potential  $\Delta\Phi_{\rm max}$  [1], [5] (i.e. the deviation of the conduction band). As shown in the band diagrams in Fig. 1d and 1e, these two parameters ( $\Delta E_{\rm fnmax}/q$  and  $\Delta\Phi_{\rm max}$ ) represent two very different physical parameters which can differ, as discussed in this work, of several hundreds of mV.

### A. TCAD simulations

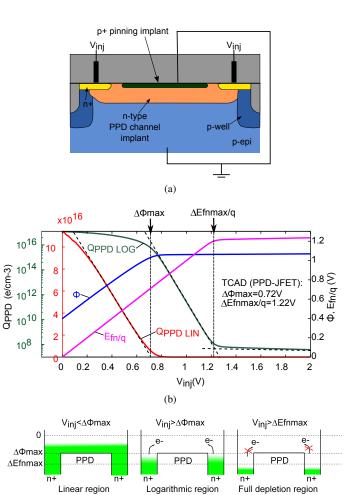

To gain a better insight on how the PPD potential  $(V_{\rm PPD})$  and the PPD charge  $(Q_{\rm PPD})$  change as a function of the biasing potential applied to the PPD, a possible approach is to simulate the structure in Fig. 2a, which corresponds to a PPD biased by means of two n+ implants located at both sides of the photodiode, i.e. to a Junction Field Effect Transistor (JFET) implemented with typical PPD implants (which will be referred to here as PPD-JFET structure). With respect to a full pixel (PPD+TG+FD), simulating a PPD-JFET structure has the advantage of allowing a symmetrical biasing of the PPD channel and guarantees that the potential applied to the PPD is not affected by the non-idealities of the TG. As addressed in this work, such JFET test structures represent a useful experimental tool to gain a better insight in the PPD physics and to optimize PPD technological processes. For this reason,

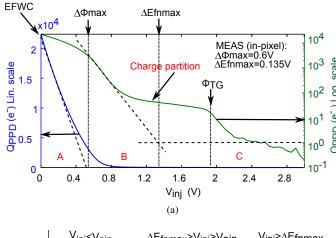

Fig. 2. (a) Cross section of the simulated PPD-JFET structure. The device is a 3D partially pinned PPD biased by means of two n+implants located at both side of the PPD channel, with  $W_{\rm JFET}=2\mu{\rm m}$  and  $L_{\rm JFET}=10\mu{\rm m}$ . (b) PPD maximum electrostatic potential  $\Phi$ , maximum  $E_{\rm fn}$  and maximum electron density  $Q_{\rm PPD}$  (plotted in linear and logarithmic scales) as a function of the injection potential applied to the PPD by means of two n+ implants. Three main working regions can be identified: a linear region  $(V_{\rm inj} < \Delta\Phi_{\rm max})$ , a logarithmic region  $(E_{\rm fnmax} > V_{\rm inj} > \Delta\Phi_{\rm max})$  and a full depletion region  $(V_{\rm inj} > E_{\rm fnmax})$ . The corresponding potential diagrams are schematized in (c).

$V_{\rm pin}$  is sometimes referred to as "pinch-off voltage" in analogy to the pinch-off voltage  $V_p$  of JFETs [6].

Figure 2b shows the maximum PPD electrostatic potential  $\Phi$ , maximum electron quasi-Fermi level  $E_{\rm fn}$  (divided by qfor unit consistency) and maximum electron density  $Q_{PPD}$ (plotted in linear and logarithmic scales) as a function of the injection potential  $(V_{ini})$  applied to a 3D PPD-JFET structure, such as the one in Fig.2a. At small injection potentials, both  $\Phi$  and  $E_{\rm fn}$  increase as the reverse voltage  $V_{\rm inj}$  applied to the p-n junction is increased [2]. As discussed in [7], the PPD capacitance can be considered roughly constant in this region, which explains the linear drop of  $Q_{PPD}$  with  $V_{inj}$ . If  $V_{\rm ini}$  is further increased, the n-region of the PPD becomes eventually fully depleted and the electrostatic potential cannot increase any more. The saturation of the electrostatic potential corresponds to the biasing condition  $V_{\rm inj} = \Delta \Phi_{\rm max}$ . Note that the depletion condition does not imply that all minority carriers have been removed from the PPD, but only that the minority

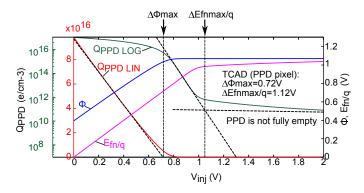

Fig. 3. PPD maximum electrostatic potential  $\Phi$ , maximum  $E_{\rm fn}$  and maximum electron density  $Q_{\rm PPD}$  (plotted in linear and logarithmic scales) as a function of the injection potential applied to the FD of a PPD pixel with the TG on. The photodiode is a square  $2.5\mu{\rm m}\times2.5\mu{\rm m}$  PPD. The TG is  $2.5\mu{\rm m}$  large and  $0.7\mu{\rm m}$  long. Both the FD and the TG are biased at  $3.3{\rm V}$ .

carrier concentration is negligible with respect to the impurity concentration [2]. In particular, residual electrons can be injected in the PPD due to thermionic emission of carriers [8] from the n+ regions toward the PPD channel (or from the TG channel, in the case of a full PPD pixel). For  $V_{\rm inj} > \Delta \Phi_{\rm max}$ , as long as the PPD is not empty,  $E_{\rm fn}/q$  still increases linearly with  $V_{\rm inj}$  ( $E_{\rm fn}$  comes closer to the conduction band [2]). Since thermionic emission is an exponential function of the electrostatic barrier seen by electrons, in this region  $Q_{\rm PPD}$  is an exponential function of  $V_{\rm inj}$ . Eventually, thermionic emission becomes negligible and the PPD becomes empty of minority carriers. This point corresponds to  $V_{\rm inj} = \Delta E_{\rm fnmax}/q$  on the simulated characteristic ( $Q_{\rm PPD}$  and  $E_{\rm fn}$  plateaus).

As a comparison, figure 3 shows the TCAD simulation of the maximum PPD electrostatic potential  $\Phi$ , the maximum electron quasi-Fermi level  $E_{\rm fn}$  and the maximum electron density  $Q_{PPD}$  (plotted in linear and logarithmic scales) as a function of the injection potential  $(V_{\rm inj})$  applied to the FD of a 3D PPD pixel structure (with the TG on and biased at 3.3V). By comparing Fig. 3 to Fig. 2b, it can be observed that very similar  $\Delta\Phi$ max (here about 0.72V) can be estimated by simulating a PPD pixel and a PPD-JFET structure. However, it can also be observed that in the simulated PPD pixel all charges cannot be successfully extracted from the PPD. This can be explained by the presence of a residual potential barrier at the PPD TG interface due to a non perfect tuning of the doping implants profiles and overlaps [9], [10]. As a result, the  $\Delta E_{\rm fnmax}/q$  estimated in Fig. 3 does not correspond to a fully empty condition. Because of the dependence of the simulation results on the TG characteristics and on the applied biasing voltages, the simulation of the simpler symmetrically biased PPD-JFET structure is probably to be preferred for the optimization of the PPD doping profiles or when the detailed technological characteristics of the TG are unknown.

### B. Definition

Based on the TCAD simulations, it can be inferred that defining the pinning voltage as  $\Delta E_{\rm fnmax}/q$  is suitable when referring to the condition at which all charges have been removed from the PPD. In particular,  $\Delta E_{\rm fnmax}/q$  corresponds

to the TG channel potential that must be applied to completely empty the PPD. However, due to the presence of design traps [9], such as a potential barrier or a potential pocket, which prevent the transfer of electrons from the PPD to the FD, this parameter is strongly affected by the design of the TG. Therefore  $\Delta E_{\rm fnmax}/q$  does not truly represents a "PPD parameter". Note also that if we assume that the PPD is "empty" when the PPD charge is about (or below)  $1e^-$ , the value of  $\Delta E_{\rm fnmax}/q$  (which is a function of the electron density in the PPD), will vary depending on the PPD size since the larger is the PPD, the lower is the charge density corresponding to the condition when  $1e^-$  is left in the PPD.

On the other hand  $\Delta\Phi_{\rm max}$  mainly depends on the PPD design (geometry and doping profiles) and on the working temperature [3]. In particular, on the condition that the PPD width and length are large enough to neglect geometrical modulation effects [11],  $\Delta\Phi_{\rm max}$  does not depend on the PPD surface. Secondly, this parameter corresponds to the PPD potential floor, which can be a useful reference to adjust the TG and FD doping profiles and biasing voltages to ensure an optimum charge transfer. Furthermore, as discussed in section III, most of the existing pinning voltage estimation methods allow measurement of  $\Delta\Phi_{\rm max}$  and not of  $\Delta E_{\rm fnmax}/q$ . Based on these considerations, in the following,  $V_{\rm pin}$  has been defined as  $\Delta\Phi_{\rm max}$ .

## III. REVIEW OF THE MAIN PINNING VOLTAGE ESTIMATION METHODS

Pinning voltage measurements are often used in the industry to monitor production lines and for the optimization and development of technological processes. As none of the existing  $V_{\rm pin}$  estimation methods has yet been officially identified as a "golden standard", each manufacturer measures the pinning voltage with custom developed techniques. In particular, in the CIS community,  $V_{\rm pin}$  is estimated based on:

- Electrical measurements performed on isolated test structures or on test structures arrays. These methods can be divided into:

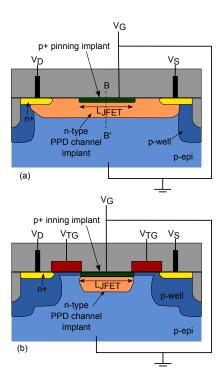

- JFET-based extraction methods [12]–[14], where  $V_{\rm pin}$  is extracted as the pinch-off voltage  $V_{\rm p}$  [6] of JFET test structures implemented with typical PPD implants (such as the ones in Fig.4a and Fig.4b).

- Capacitance measurements [15].

- 2) In-pixel measurements [7], [16]–[18], where  $V_{\rm pin}$  is measured directly on full PPD pixels arrays.

### A. Devices under test

All the tested devices have been designed in commercially available 0.18  $\mu m$  PPD CIS technologies. For practical reasons, the tested PPD-JFET structures have been designed on two different foundries, which will be referred to as foundry A and foundry B. The experimental data presented is section III-B5 have been obtained on a third PPD technology and are a courtesy of Lahav Assaf, from TowerJazz. When known, the geometrical details and the dimensions of the tested JFET structures are specified in the different sections. Inpixel measurements have been performed on a 4T  $64 \times 128$ ,

Fig. 4. Schematic drawing of a PPD-JFET structure (a) and of a TG-PPD-JFET structure (b), both implemented with typical PPD implants.  $V_{\rm D}$ ,  $V_{\rm S}$  are the biasing voltages applied to the source and drain of the JFETs.  $V_{\rm TG}$  is the biasing voltage applied to the TG of TG-PPD-JFET.

7  $\mu m$ -pitch, pixels array (designed in foundry A) with a square 2.5  $\mu m \times 2.5 \ \mu m$  PPD, a long TG and a long FD (both 2.5  $\mu m$  wide) on one side. The TG is 0.7  $\mu m$  wide. The charge-to-voltage (CVF) conversion factor is about  $20 \ \mu V/e^-$ .

### B. Test structure methods

Different approaches, based on very different physical principles, are used today to estimate  $V_{\rm pin}$  on isolated test structures. This section discusses the physical principle of some of the most commonly used methods.

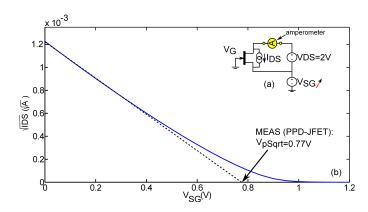

1) The Square root method: The square root (Sqrt.) method [12] is a well established JFET pinch-off voltage ( $V_{\rm p}$ ) characterization technique. The corresponding experimental set-up is shown in Fig. 5a. The method is based on the resolution of JFET equations at saturation [6]:

$$I_{\rm DS} = I_{\rm DSS} \left( 1 - \frac{V_{\rm SG}}{V_{\rm p}} \right)^2 \tag{2}$$

where  $V_{\rm SG}$  is the source-to-gate biasing voltage (with  $V_{\rm G}$  the substrate biasing voltage and  $V_{\rm SG}>0$ ),  $I_{\rm DS}$  is the saturation drain-to-source current, and  $I_{\rm DSS}$  is the  $I_{\rm DS}$  saturation current measured for  $V_{\rm SG}=0$ . Note that for the purpose of clarity,  $V_{\rm p}$  is defined here as a positive quantity (whereas in [6] it is defined as a negative quantity). Figure 5b shows the experimental extraction of  $V_{\rm p}$  from the square root characteristic obtained on a PPD-JFET (Fig. 4a).  $V_{\rm p}$  is estimated as the intersection of the tangent to the square root characteristic with the x-axis. The linear fitting is performed at small  $V_{\rm SG}$  biasing voltages (of the order of a hundred mV), which correspond to high current values (here of the order of a few  $\mu A$ ), therefore this

Fig. 5. (a) Equivalent circuit of the test set-up used in the Sqrt. method [12]. (b) Square root of the drain to source current  $(I_{\rm DS})$  as a function of the gate to source biasing voltage  $V_{\rm SG}$  measured on a PPD-JFET structure (square root characteristic). A constant biasing voltage  $V_{\rm DS}=2\,\rm V)$  is applied between drain and source. The pinch-off voltage  $V_{\rm P}$  of the JFET is extracted as the x-intercept of the tangent to  $\sqrt{I_{\rm DS}}$  at small  $V_{\rm SG}$  values. The tested device is a PPD-JFET (foundry A) with  $\frac{W_{\rm JFET}}{L_{\rm JFET}}=\frac{2\,\mu\rm m}{20\,\mu\rm m}$ .

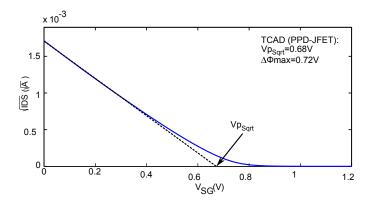

measurement should not be affected by the current resolution of the set-up (here about 100 fA). Note however, that since a large voltage (2 V) is applied between source and drain, the Sqrt. method should be used only on long PPD-JFET structures to avoid the drain potential affecting the potential at the source (equivalent of short channel effects in MOS transistor [8]). This can be considered as a strong limitation of this technique, as designers aim at estimating  $V_{\rm pin}$  in structures which are as close as possible to real pixels. However, since standard JFET structures usually include n+ implants at both sides of the PPD (to implement the source and the drain of the JFET), none of the JFET-based methods discussed in this work truly allows to observe the effect of the PPD length on  $V_{\rm pin}$ . Therefore only  $V_{\rm pin}$  variations with the PPD width [11] can be monitored with PPD-JFET devices. Figure 6 shows a square root characteristic simulated in TCAD. The PPD-JFET structure is the same as the one simulated Fig. 2. It is important to note that TCAD simulations have not been calibrated to match experimental data, therefore absolute  $V_{\rm pin}$ values should not be compared. As it can be observed, the pinning voltage estimated with the Sqrt. method gives a good estimate of the  $\Delta\Phi_{max}$  value of the simulated structure (here  $\Delta\Phi_{max} \approx 0.72 \mathrm{V}$  and  $V_p \approx 0.68 \mathrm{V}$ ) and can thus be considered as a suitable technique for the estimation of the absolute value of  $V_{\rm pin}$ .

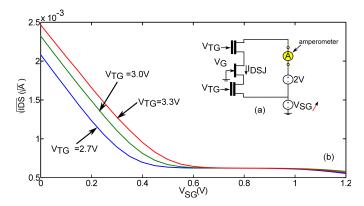

To respect design rules and to approach as much as possible in-pixel conditions, PPD-JFET isolated structures can be designed with a TG on both source and drain sides<sup>1</sup> (Fig. 4b). These structures are referred to here as TG PPD-JFET structures. Figure 7 shows the square root characteristic measured on a TG-PPD-JFET. As can be observed, the measured current varies significantly with the TG biasing voltage. This behaviour is due to the fact that the JFET is in series with two TGs, which are often designed with an asymmetrical channel doping (to avoid charge spill back [19] toward the PPD) and present a strong channel resistance when electrons move from

<sup>&</sup>lt;sup>1</sup>Or with only one TG on one side. In this case the PD is partially pinned.

Fig. 6. Square root of the drain to source current  $(I_{\rm DS})$  as a function of the gate to source biasing voltage  $V_{\rm SG}$  simulated for the same JFET structure as in Fig. 2  $(W_{\rm JFET}=2\mu{\rm m}$  and  $L_{\rm JFET}=10\mu{\rm m})$ .

Fig. 7. (a) Equivalent circuit of the experimental set-up when measuring the pinning voltage on a TG-PPD-JFET structure with the Sqrt. method. (b) Square root of the drain to source current  $I_{\rm DS}$  as a function of the gate to source voltage ( $V_{\rm SG}$ ) measured on a TG-PPD-JFET (foundry A) for different TG biasing potentials ( $V_{\rm TG}$ ). The TG and the JFET dimensions are  $\frac{W_{\rm TG}}{L_{\rm TG}} = \frac{10~\mu\rm m}{0.7~\mu m}$  and  $\frac{W_{\rm JFET}}{L_{\rm JFET}} = \frac{10~\mu\rm m}{20~\mu m}$ , respectively. As can be observed,  $I_{\rm DS}$  always depends on  $V_{\rm TG}$ , therefore no meaningful  $V_{\rm pin}$  can be extracted on this type of devices.

the FD toward the PPD (maximum currents of the order of a few  $\mu A$  have been measured on TG test transistors with  $\frac{W_{\rm TG}}{U_{\rm TG}} = \frac{10~\mu{\rm m}}{0.7~\mu{\rm m}}$ ). This means that depending on the tuning of the technology and of the current gains (i.e. of the W/L ratios) of both the TG and the JFET, the measured output current can be either limited by the JFET or the TG. In the latter case, the estimated  $V_{\rm pin}$  values are meaningless. Therefore these structures are not recommended for the estimation of the pinning voltage.

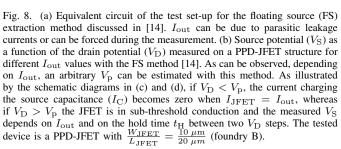

2) The Floating Source Method: The floating source (FS) method [14] consists in leaving the source of a PPD-JFET structure floating and in monitoring its source potential  $V_{\rm S}$  as a function of the biasing voltage applied to the drain  $(V_{\rm D})$ . During the measurement, a current  $I_{\rm out}$  is forced at the source<sup>2</sup>. The equivalent circuit of the test set-up is shown in Fig. 8a. This method is based on the assumption of a "on-off" behaviour of the JFET. In particular it is assumed that, as long as  $V_{\rm SG} < V_{\rm p}$ , the JFET is "on" and  $V_{\rm S}$  follows  $V_{\rm D}$  (since the capacitance of the floating source is charged by a current

voltmeter

Channel

(c)

Channel

$I_{\rm DS}>0$ ).  $V_{\rm S}$  eventually stops following  $V_{\rm D}$ . Since the JFET is considered to be "off" ( $I_{\rm DS}=0$ ) at pinch-off (i.e. when  $V_{\rm SG}\geq V_{\rm p}$ ),  $V_{\rm p}$  is extracted as the  $V_{\rm S}$  potential at saturation.

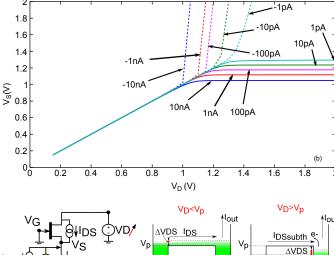

Figure 8b shows the  $V_{\rm S}$  potential as a function of  $V_{\rm D}$  measured for different  $I_{\rm out}$  values. As can be observed, arbitrary  $V_{\rm p}$  values can be estimated with this method depending on  $I_{\rm out}$ . This behaviour is due to the fact that, in practice,  $I_{\rm DS}$  is never zero, as there is always a sub-threshold current flowing in the JFET due to the net thermionic emission of electrons from the source toward the channel [20]. As a result,  $V_{\rm S}$  will follow the  $V_{\rm D}$  potential even after pinch-off. In particular:

- For  $V_{\rm D} < V_{\rm p}$  (Fig. 8c), the current charging the source capacitance ( $I_{\rm C}$ ) becomes zero when  $I_{\rm JFET} = I_{\rm out}$ .

- For  $V_{\rm D} > V_{\rm p}$  (Fig. 8d), the JFET is in sub-threshold conduction and the measured  $V_{\rm S}$  depends on  $I_{\rm out}$  (and on the hold time before the sampling of the  $V_{\rm S}$  value).

It should also be noted that since the saturation of the  $V_{\rm S}$  curve depends on a current balance (and therefore on the amount of current flowing in the JFET), different  $V_{\rm P}$  values are to be expected for two devices with the same width and different lengths (whereas they should have the same  $V_{\rm P}$  if  $L_{\rm JFET}$  was larger than a few  $\mu{\rm m}$ ).

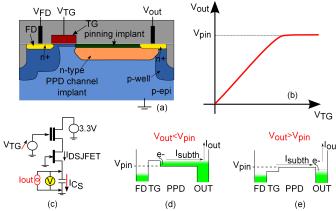

3) Current Method: In the extraction method used in [13], a small voltage difference is applied between  $V_{\rm D}$  and  $V_{\rm S}$  (10 mV), and  $I_{\rm DS}$  is monitored while the  $V_{\rm D}$  potential is increased with respect to  $V_{\rm G}$ .  $V_{\rm p}$  is estimated as the  $V_{\rm S}$  potential at which the  $I_{\rm DS}$  current reaches a certain percentage (for example 1%) of the initial current value [21]. The equivalent

$<sup>^{2}</sup>$ Note that if  $I_{\text{out}}$  is too small, the effective output current will be the leakage current of the experimental set-up.

Fig. 9. (a) Drain to source current  $I_{\rm DS}$  characteristic measured as a function of the source to gate voltage  $V_{\rm SG}$  for  $V_{\rm DG}=10~\rm V$ . The tested PPD-JFET is the same as the one tested in Fig. 5. In [13] the pinch-off voltage (indicated here as  $V_{\rm pCM}$ ) is estimated as the  $V_{\rm SG}$  potential at which the  $I_{\rm DS}$  current is zero.  $V_{\rm pSqrt}$  corresponds to the pinning voltage estimated with the Sqrt. method in Fig 7. (b) Equivalent circuit of the test set-up discussed in [13]. Schematic potential diagram for (c)  $V_{\rm D} < V_{\rm p}$  and (d)  $V_{\rm D} < V_{\rm p}$ .

circuit of the test set-up is shown in Fig. 9a. This method is referred to here as the Current (Cu.) method. Unlike the Sqrt. method, the Cu. method is not based on the resolution of JFET equations and like the FS method, it is based on the assumption of an "on-off" behaviour of the JFET. By looking at the  $I_{\rm DS}$  characteristic in Fig. 9b in logarithmic scale, we can see that the zero current condition cannot be reached (as the minimum measurable current corresponds to the accuracy of the test set-up). Furthermore, since the characteristic is non-linear, the "zero" value cannot be estimated by a linear fit of the curve (while it is the case for the Sqrt. method). In can also be observed that the Cu. method provides an overestimation of  $V_{\rm p}$  with respect to the one estimated with the Sqrt. method (indicated as  $V_{psqrt}$  in the figure). In addition, it can also be observed that the biasing condition at which  $V_{\rm SG} = V_{\rm psqrt}$  roughly corresponds to the transition of the  $I_{\rm DS}$  characteristic into the sub-threshold region. This transition corresponds to the moment when the conduction between source and drain starts to be dominated by the thermionic emission of electrons from the source toward the JFET channel (i.e. when  $V_{\rm PPD}$  reaches  $V_{\rm pin}$ ). Therefore, the experimental set-up proposed in [13] is suitable for the estimation of  $V_p$ , as long as the pinch-off voltage is estimated as the potential at which the I-V characteristic enters the logarithmic region and not when the current becomes "zero". This approach does not provide an accurate and unique  $V_{\rm p}$  value (as there is no net transition between the two working regions), however it has the advantage, with respect to the Sqrt. method of being compatible with shorter JFET lengths (given the small applied  $V_{\rm DS}$ ) and to be based on a "symmetrical biasing" of the JFET.

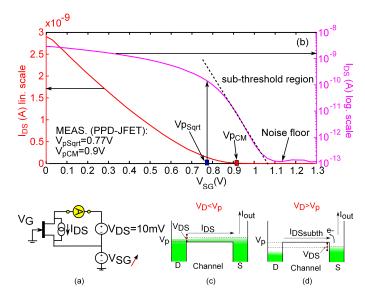

4) The "Rectangle" method: The "rectangle" method [21] is a pinning voltage estimation technique based on the "rectan-

Fig. 10. (a) Schematic drawin of the "rectangle" structure used for the estimation of  $V_{\rm pin}$ . (b) Schematic circuit of the test set-up of the rectangle method. A current  $I_{\rm out}$  is forced at the output. (c) Method working principle:  $V_{\rm FD}$  is biased at 3.3 V and  $V_{\rm pin}$  is retrieved as the  $V_{\rm out}$  at saturation (as it is assumed that no current flows in the structure once  $V_{\rm out} > V_{\rm pin}$ ). In practice, there is always a current flowing in the structure due to the thermionic emission of carriers across the potential barrier at the PPD-TG interface (d) or the barrier between the n+ output electrode and the PPD (e). As a result, arbitrary pinning voltage values can be obtained depending on the chosen  $I_{\rm out}$ .

gle" structure shown in Fig. 10a. The equivalent circuit of the test set-up and a schematic explanation of the method working principle are also illustrated in Fig. 10. The FD is biased at 3.3 V, whereas the PPD is left floating, and the output potential  $V_{\rm out}$  is monitored as a function of the TG biasing voltage. A constant current  $I_{\text{out}}$  is injected in the PD. The pinning voltage is extracted as the  $V_{\rm out}$  potential at saturation. No experimental data are available for the rectangle method. However, like the FS method, this method is also based on the assumption that measured output voltage corresponds to the PPD potential and that once the PPD potential has reached  $V_{\rm pin}$ , no more current can flow in the structure. The same considerations drawn for the FS method can be extended to the "rectangle" method. In particular, as shown in Fig. 10e, saturation is reached only when the sub-threshold current  $I_{\rm subth}$  of the device formed by the series of the TG and of the PPD JFET becomes equal to  $I_{\rm out}$ . Therefore  $V_{\rm out}$  can become larger than  $V_{pin}$ . With respect to the floating diffusion method, results obtained on "rectangle" devices can be even harder to interpret, as measurements can be significantly affected by the design of the TG. Therefore this method is not suitable for the estimation of  $V_{pin}$ .

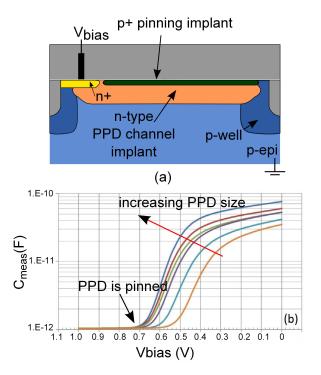

5) C-V method: Another approach which is used in the industry to measure the pinning voltage is based on C-V (capacitance-voltage) measurements on large arrays of partially pinned photodiodes [15], [21] such as the one shown in Fig.  $11a^3$ . The method consists in measuring the variation of the capacitance  $C_{\rm meas}$  of a partially pinned diode as a function of the applied biasing voltage  $V_{\rm bias}$ . The working principle is as following: as  $V_{\rm bias}$  is increased, both the PPD charge and  $C_{\rm PPD}$  decrease; when the PPD potential reaches its maximum value ( $V_{\rm pin}$ ),  $C_{\rm PPD}$  becomes zero and  $C_{\rm meas}$

<sup>&</sup>lt;sup>3</sup>A TG can also be included in the structure between the PPD and the biasing electrode.

Fig. 11. (a) Cross-section of a partially pinned PD structure used for the estimation of  $V_{\rm pin}$  based C-V measurements. Structure can also include a TG. (b) C-V measurements obtained on arrays of partially pinned photodiodes with increasing PPD areas.  $V_{\rm pin}$  is extracted as the biasing potential at which  $C_{\rm tot}$  reaches a plateau [15]. These data are a courtesy of A. Lahav, from TowerJazz.

reaches its minimum value. Therefore  $V_{\rm pin}$  is extracted as the biasing voltage at which  $C_{\rm meas}$  reaches a plateau. An example of experimental measurements obtained for different PPD sizes is shown in Fig. 11b. With respect to JFET methods, this approach has the disadvantage of requiring large test-structure arrays (in order to reach a high enough output capacitance). Furthermore, like in the CM, the pinning voltage is retrieved from the saturation of a non linear characteristic, leading to large value uncertainties depending on when one estimates that the curve has "reached the plateau". Finally, experimental measurements can be significantly affected by the numerous parasitic capacitances involved in such set-up.

### C. In-pixel methods

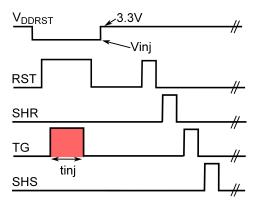

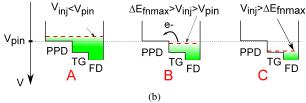

The in-pixel  $V_{\rm pin}$  extraction method has been proposed by Tan et al. in [16], then further discussed in [7], [17], [18]. The method consists in monitoring the electrical injection of carriers in the PPD as a function of the injection potential  $V_{\rm inj}$  applied to the FD (by modulating  $V_{\rm DDRST}$  while the TG and RST transistors are on). The timing diagram is shown in Fig. 12. After the injection phase, the TG is turned off, the FD is reset (to sample the reference), then the TG is turned on again to transfer the injected charge back to the FD and the signal is sampled.

Figure 13 shows an example of an experimental pinning voltage characteristic (output charge  $Q_{\rm out}$  as a function of  $V_{\rm inj}$ ).  $V_{\rm pin}$  is estimated as the  $V_{\rm inj}$  potential above which direct charge injection becomes zero. Whereas in [16], this potential

Fig. 12. Timing diagram for the in-pixel estimation of the pinning voltage (reproduced from [7]). SHR and SHS are the signal for the sampling of the reference and of the signal, respectively. The injection time is  $40\mu s$ .

is retrieved by means of a linear fit of the pinning voltage characteristic at small  $V_{\rm inj}$  (linear method), the integral method proposed in [7] takes into account the integration of charges on the PPD capacitance. As was expected from the simulation in Fig. 2 and Fig. 3, the PPD is far from being empty when  $V_{\rm inj} = V_{\rm pin}$ . In particular, by looking at the pinning voltage characteristic in logarithmic scale, it can be observed that the PPD still contains a few percent of the initial charge.

Four main working regions can be identified on the characteristic:

- In region A  $(V_{\rm inj} < V_{\rm pin})$  charges are directly injected in the PPD and  $Q_{\rm out}$  is a linear function of  $V_{\rm inj}$ . This is due to the fact that, as discussed in [7], in this region the capacitance is a very weak function of the PPD potential (and can therefore be approximated as constant). The PPD charge measured at  $V_{\rm inj} = 0$  corresponds to the Equilibrium Full Well capacity (EFWC) [3].

- In region B ( $\Delta E_{\rm fnmax}/q > V_{\rm inj} > V_{\rm pin}$ ) charges are injected in the PPD by thermionic emission. Since the thermionic emission is an exponential function of the potential barrier seen by electrons, the pinning voltage characteristic is a logarithmic function of  $V_{\rm inj}$ .

- In region C  $(V_{\rm inj} > \Delta E_{\rm fnmax}/q)$  the thermionic emission is negligible  $(Q_{\rm out} \approx 1e^-)$ , thus the PPD can be considered empty.  $\Delta E_{\rm fnmax}/q$  can be estimated by finding the intercept between the charge plateau (here  $\approx 1e^-$ ) and the fit of the logarithmic region.

- A forth working region, corresponding to the charge partition regime [7] can be identified on the characteristic. Whereas the other three regions mainly depend on the injection phase, charge partition is due to the partition of charge (that was located in the TG channel during charge injection) between the FD and the PPD when the TG is turned off to sample the reference.

As indicated in Fig. 13a, different parameters can be estimated from the pinning voltage characteristic:  $V_{\rm pin}$  (i.e.  $\Delta\Phi_{\rm max}$ ),  $\Delta E_{\rm fnmax}/q$  (which corresponds to the minimum potential that must be applied to a well adjacent to the PPD to completely empty the latter from minority carriers, i.e. to the minimum TG channel to ensure a good charge transfer efficiency), the Equilibrium Full Well Capacity (EFWC) [3]

Fig. 13. (a) Pinning voltage characteristic plotted in linear and logarithmic scales: injected charge  $Q_{\rm inj}$  vs. injection potential  $V_{\rm inj}$  measured in the dark at  $T=60~{}^{\circ}{\rm C}$ . (b) Schematic potential diagram in regions A, B and C. The curve has been measured on a  $64\times128~4.5~\mu{\rm m}$ -pitch PPD CIS pixel-array. The PPD size is  $2.5~\mu{\rm m}\times2.5~\mu{\rm m}$ . The charge to voltage conversion factor is about  $20~\mu{\rm V/e^-}$ .

and the TG channel potential  $\Phi_{\rm TG}$  [7]). Note however, that  $V_{\rm pin}$  values estimated with this method should be handled with care, since if the pixel presents a low CTE or if the experimental conditions and the timing diagram are not set carefully, wrong  $V_{\rm pin}$  might be estimated [7].

### IV. CONCLUSIONS

This work was dedicated to the definition of the pinning voltage and to a comparative study of different methods that are used in the CIS community to estimate the pinning voltage. It has been shown that the definitions that are used in the literature to indicate the pinning voltage ( $\Delta\Phi_{\rm max}$  and  $\Delta E_{\rm fnmax}$ ) correspond to two very different physical parameters, which can differ by several hundreds of  ${\rm mV}$ :

- $\Delta\Phi_{\rm max}$  corresponds to the maximum PPD electrostatic potential, and is the pinning voltage definition which should be used to estimate the PPD EFWC [3].

- $\Delta E_{\mathrm{fnmax}}$  represents the minimum TG channel potential that must be induced to fully empty the PPD of minority carriers (neglecting charge partition phenomena and the effect of the potential barrier between the PPD and the TG).

In this study,  $V_{\rm pin}$  was defined as  $\Delta\Phi_{\rm max}$ .

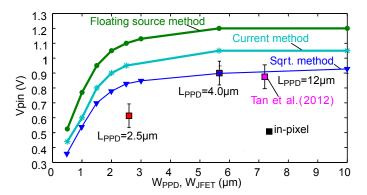

Fig. 14 presents the  $V_{\rm pin}$  values estimated with the floating source method, the current method and the square root method for different PPD-JFET lengths. The figure also shows the  $V_{\rm pin}$  values estimated with the in-pixel methods on PPD CIS arrays with different photodiode sizes. As expected, in-pixel measurements are in good agreement with the Sqrt. method, as they both provide an absolute value of the pinning voltage

Fig. 14.  $V_{\rm pin}$  as a function of the PPD-JFET channel width  $W_{\rm JFET}$  (or minimum PPD width  $W_{\rm PPD}$ ) extracted with the in-pixel method [16], with the floating source method ( $I_{\rm out}=1~{\rm pA}$ ), with the current and with the Sqrt. method. All the tested PPD-JFETs have a channel length  $L_{\rm JFET}=20~\mu{\rm m}$  and have been designed in foundry A.

(therefore of  $\Delta\Phi_{\rm max}$ ). The lower in-pixel  $V_{\rm pin}$  value extracted at  $W_{\rm PPD}=2.5~\mu{\rm m}$  can be explained by additional 3D effects [11], [13] due to the combination of a small  $W_{\rm PPD}$  and a small  $L_{\rm PPD}$ . It can also be observed that, even if the FS method and the Cu. method do not provide an absolute value of the pinning voltage (100 mV-300 mV higher here), they still allow to observe relative pinning voltage variations resulting from geometrical variations.

Test structure methods have the advantage of being based on simple I-V or C-V measurements, that can be performed by wafer probe. They also allow easy monitoring of the effect of process variations and testing of many different PPD widths. However, because of the presence of n+ implants on both sides of the PPD channel, JFET measurements do not allow to observe  $V_{\rm pin}$  variations with  $L_{\rm PPD}$ . On the other hand, the in-pixel approach gives less freedom in terms of the number of variations that can be tested but provides an estimate of  $V_{\rm pin}$  in a real in-pixel environment, allowing observation of both the effect of the width and length of the PPD. In addition, other PPD CIS parameters , such as  $\Delta E_{\rm fnmax}/q$ , the EFWC and the TG channel potential [7] can be estimated from the pinning voltage characteristic. For these reasons, the two approaches should be considered complementary.

#### REFERENCES

- E. Fossum and D. Hondongwa, "A Review of the Pinned Photodiode for CCD and CMOS Image Sensors," *Electron Devices Society, IEEE Journal of the*, vol. 2, no. 3, pp. 33–43, May 2014.

- [2] A. S. Grove, Physics and technology of semiconductor devices. New York: Wiley, 1967.

- [3] A. Pelamatti, J.-M. Belloir, C. Messien, V. Goiffon, M. Estribeau, P. Magnan, C. Virmontois, O. Saint-Pe, and P. Paillet, "Temperature Dependence and Dynamic Behavior of Full Well Capacity in Pinned Photodiode CMOS Image Sensors," *IEEE Transactions on Electron Devices*, vol. 62, no. 4, pp. 1200–1207, Apr. 2015.

- [4] A. Krymski and K. Feklistov, "Estimates for Scaling of Pinned Photodiodes," in *Image Sensor Workshop*, 2005.

- [5] J. Michelot, F. Roy, J. Prima, C. Augier, F. Barbier, S. Ricq, P. Boulenc, Z. Essa, L. Pinzelli, H. Leininger, and others, "Back illuminated vertically pinned photodiode with in depth charge storage," in *International Image Sensor Workshop*, 2011.

- [6] D. A. Neamen, Semiconductor Physics And Devices: Basic Principles, 4th ed. New York, NY: McGraw-Hill, Jan. 2011.

- [7] V. Goiffon, M. Estribeau, J. Michelot, P. Cervantes, A. Pelamatti, O. Marcelot, and P. Magnan, "Pixel Level Characterization of Pinned Photodiode and Transfer Gate Physical Parameters in CMOS Image Sensors," *Electron Devices Society, IEEE Journal of the*, vol. 2, no. 4, pp. 65–76, Jul. 2014.

- [8] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, 2nd ed. New York, NY, USA: Cambridge University Press, 2009.

- [9] J. R. Janesick, Scientific Charge-coupled Devices. SPIE Press, Jan. 2001.

- [10] J. R. Janesick, T. Elliott, J. Andrews, and J. Tower, "Fundamental performance differences of CMOS and CCD imagers: part V," Proc. SPIE, vol. 8659, pp. 865902-865902-35, 2013.

- [11] H. Takeshita, T. Sawada, T. Iida, K. Yasutomi, and S. Kawahito, "High-speed charge transfer pinned-photodiode for a CMOS time-of-flight range image sensor," in *IS&T/SPIE Electronic Imaging*, 2010, pp. 75 360R–75 360R.

- [12] W. Sansen and C. Das, "A simple model of ion-implanted JFETs valid in both the quadratic and the subthreshold regions," *IEEE Journal of Solid-State Circuits*, vol. 17, no. 4, pp. 658–666, Aug. 1982.

- [13] S. Park and H. Uh, "The effect of size on photodiode pinch-off voltage for small pixel CMOS image sensors," *Microelectronics Journal*, vol. 40, no. 1, pp. 137–140, Jan. 2009.

- [14] P. Coudrain, "Contribution au dveloppement d'une technologie d'intgration tridimensionnelle pour les capteurs d'images CMOS pixels actifs," Electronic Thesis or Dissertation, Text, Oct. 2009.

- [15] A. Lahav, R. Reshef, and A. Fenigstein, "Enhanced X-ray CMOS sensor panel for radio and fluoro application using a low noise charge amplifier wixel with a Partially Pinned PD," in *International Image* Sensor Workshop (IISW 2011), 2011.

- [16] J. Tan, B. Buttgen, and A. Theuwissen, "Analyzing the Radiation Degradation of 4-Transistor Deep Submicron Technology CMOS Image Sensors," *IEEE Sensors Journal*, vol. 12, no. 6, pp. 2278 –2286, Jun. 2012.

- [17] Y. Xu and X. G. A. J. Theuwissen, "Investigating Transfer Gate Potential Barrier by Feed-Forward Effect Measurement," Jun. 2015.

- [18] C.-P. Chao, Y.-C. Chen, K.-Y. Chou, J.-J. Sze, F.-L. Hsueh, and S.-G. Wuu, "Extraction and Estimation of Pinned Photodiode Capacitance in CMOS Image Sensors," *Electron Devices Society, IEEE Journal of the*, vol. 2, no. 4, pp. 59–64, Jul. 2014.

- [19] L. Bonjour, N. Blanc, and M. Kayal, "Experimental Analysis of Lag Sources in Pinned Photodiodes," *IEEE Electron Device Letters*, vol. 33, no. 12, pp. 1735 –1737, Dec. 2012.

- [20] R. J. Brewer, "The barrier mode behaviour of a junction FET at low drain currents," *Solid-State Electronics*, vol. 18, no. 11, pp. 1013–1017, Nov. 1975.

- [21] A. Lahav, "TowerJazz, (Personal communication)," Jun. 2015.

Alice Pelamatti received the Masters degree in Electrical Engineering (2009) from Politecnico di Milano (Italy). After an internship in the HealthCare R&D department at Siemens (Knoxville, USA), she worked as a research engineer in the ISAE-SUPAERO Image Sensor Research Team, Toulouse, France. She is currently a third year Ph.D. student at ISAE-SUPAERO, supported by the French Spatial Agency (CNES) and Airbus Defence&Space.

Alexis De Ipanema graduatedin 2015 in Aerospace Engineering at ISAE-Supaero, Toulouse, France. He worked on the experimental comparison between pinning voltage estimation methods during his second year and third year student projects under the direction of the Image Sensor Research Team of ISAE-Supaero. He is currently doing his internship at PYXALIS Semiconductors (Grenoble

Pierre Magnan (M'99) graduated in E.E. from University of Paris in 1980. After being a research scientist involved in analog and digital CMOS design up to 1993 in LAAS-CNRS, he moved to image sensors research in SUPAERO, now called ISAE-SUPAERO, in Toulouse, France. Since 2002, he is Full Professor there and Head of Image Sensor Research Group involved in CMOS Image Sensor basic and applied research. He has supervised 15 PhDs and co-authored more than 70 scientific papers. He has served in IEEE IEDM Display Sensors and MEMS

subcommittee in 2011, 2012, and in the International Image Sensor Workshop (IISW) TPC in 2007, 2009, 2011, being the General Technical Chair of 2015 IISW

Cédric Virmontois (S10M12) received the Engineering degree in Physics from INSA of Toulouse in 2008 and the Ph.D. degree in Microelectronic from ISAE-SUPAERO, Toulouse, in 2012. Cédric presently works for the Centre National d'Études Spatiales (CNES) in Toulouse, France, as Detection Chain Architect in the Science Payload and Imaging Division. His work involves the development of imagers for future space missions.

Olivier Saint-Pé is currently Airbus Defence&Space expert in photon detectors. Since 1986, he has been involved in numerous projects requiring high performances detectors/focal planes. He has authored and co-authored more than 50 scientific/technical papers. Since 2003, he is chairing the "Focal Plane Technologies" session within SPIE Remote Sensing symposium. He is member of CNES Technical Competence Center and of ESA Photonics Working Group.

Vincent Goiffon (S'08-M'09) received his M.S. (2005) and Ph.D. (2008) degrees in E.E. respectively from SUPAERO and Univ. of Toulouse. Since then, he has been working as an Associate Professor in the ISAE-SUPAERO Image Sensor Research Team. His research interests focus on solid-state image sensors and especially on radiation effects. He has co-authored more than 30 journal papers, including one Outstanding Conference Paper Award and one Outstanding Student Paper Award (both at IEEE NSREC).

Michel Breart de Boisanger graduated from Ecole Centrale de Paris in 1989, after a third year focused on aerospace systems. Since 1990, he works in space industry inside Airbus Group and is in charge since 2007 of the development of CMOS Image Sensors for Airbus Defence and Space Earth Observation Optical Instrument division, in Toulouse, France. In strong cooperation with ISAE (Institut Suprieur de l'Aronautique et de l'Espace), he develops custom CIS devices for Earth Observation optical instruments, with currently two in orbit successful mis-

sions, for COMS/GOCI (Geostationary Ocean Colour Imager in orbit since July 2010) and S2/MSI (Multi Spectral Imager in orbit since June 2015)