**High Resolution Fabrication of Nanostructures using Controlled**

**Proximity Nanostencil Lithography**

T. Jain<sup>1</sup>, M. Aernecke<sup>2</sup>, V. Liberman<sup>2</sup>, and R. Karnik<sup>1\*</sup>

<sup>1</sup> Department of Mechanical Engineering, Massachusetts Institute of Technology, Cambridge, Massachusetts, 02139,

**USA**

<sup>2</sup> Massachusetts Institute of Technology, Lincoln Laboratory, Lexington, Massachusetts, 02127, USA

**Abstract**

Nanostencil lithography has a number of distinct benefits that make it an attractive

nanofabrication processes, but the inability to fabricate features with nanometer precision has

significantly limited its utility. In this paper, we describe a nanostencil lithography process that

provides sub-15 nm resolution even for 40-nm thick structures by using a sacrificial layer to control

the proximity between the stencil and substrate, thereby enhancing the correspondence between

nanostencil patterns and fabricated nanostructures. We anticipate that controlled proximity

nanostencil lithography will provide an environmentally stable, clean, and positive-tone candidate

for fabrication of nanostructures with high-resolution.

Significant advances in device physics across optical, electrical, and magnetic modalities have

been enabled by the ability to fabricate structures with nanoscale precision. There is currently a large

variety of top-down nanostructure fabrication methods available, such as electron beam lithography<sup>1</sup>,

\* Correspondence:

Rohit Karnik, Massachusetts Institute of Technology, Cambridge MA 02139, USA. Email:

karnik@mit.edu, Phone: 617-324-1155.

1

direct ion beam milling<sup>2</sup>, ultraviolet interference lithography<sup>3</sup>, beam induced material deposition<sup>4</sup>, nanoimprint lithography<sup>5</sup>, and nanostencil lithography<sup>6</sup>, and each has their own process compatibility and advantages.

Nanostencil lithography, a process in which nanostructures are deposited onto, or etched into, a substrate through a stencil mask, provides a number of distinct benefits. First, nanostencil lithography allows for fabrication of nanostructures on substrates with topography. Second, stencils are patterned independently of the target substrate, enabling parallel processing of the stencil and substrate which, in turn, allows for higher process yields and increases in production throughput<sup>7</sup>. The independent patterning of the stencil also ensures that the nanostructure deposited through the stencil is free from any ion-beam contamination and ion-beam induced sputtering. Furthermore, nanostencil lithography decouples the patterning resolution of the mask from the thickness of the structure, making it particularly useful for thick nanostructures. Finally, nanostencil lithography does not require treatment with acids, bases, or high temperatures, thereby making the technique particularly suitable for sensitive substrates<sup>8</sup>.

Over the past few years, significant advances in nanostencil lithography have enabled the routine fabrication of ~200 nm feature sizes<sup>6</sup>. However, the inability of nanostencil lithography to fabricate features with nanometer precision has significantly limited its utility. In one instance, nanostencil lithography has reported sub-20 nm dot resolution<sup>9</sup>, the large distance between the stencil and substrate led to significant feature broadening, limited the thickness of patterned structures to 10 nm, and would prove exceedingly challenging for the creating of sub-20 nm nanogap resolution. In this paper, we report a process for performing nanostencil lithography fabrication down to a feature and gap resolution of 15 nm for the patterning of nano-gap structures. We chose to demonstrate the effectiveness of the developed nanostencil lithography process by fabricating nanostructures with nanogaps, which are typically more challenging to fabricate compared to stand-alone structures.

Nanogap structures are important in a broad range of devices, including surface enhanced Raman spectroscopy (SERS)<sup>10</sup>, single molecule fluorescence sensing<sup>11,12</sup>, transverse electrodes for nanopore sensing<sup>13</sup>, spin<sup>14</sup> and ultrafast<sup>15</sup> transistors, molecular electronics<sup>16,17</sup>, magnetic tunneling junctions<sup>18</sup>, and

nanomagnetics<sup>19</sup>. In many of these applications, device performance depends critically on both the gap size as well as the feature dimensions<sup>20</sup>, and is sensitive to geometric and surface imperfections that often lead to a significant deterioration in performance<sup>21</sup>. Most methods for achieving sub-15 nm gaps, such as electromigration break junction<sup>22</sup>, direct ion beam milling<sup>23</sup>, and controlled electroplating<sup>24</sup> require performing active feedback control processes to achieve the desired gap size, thereby significantly limiting throughput and process compatibility. Alternatively, sub-10 nm resolution has been achieved directly with electron beam lithography; however, obtaining this patterning resolution requires use of the high contrast resist, hydrosilsesquioxane (HSQ)<sup>1</sup>. There are a number of drawbacks associated with the use of HSQ, including its environmental stability issues<sup>25</sup> as well as dose and development sensitivity<sup>26</sup>. Furthermore, as a negative tone resist, HSQ may not be suitable for the patterning of some structures. Herein, we demonstrate the ability of our nanostencil lithography process to achieve sub-15 nm resolution on nanogap structures. The improvement in resolution is achieved by addressing the dominant limitations of nanostencil lithography, foremost of which are geometric blurring of deposited features due to insufficient proximity of the stencil mask and the substrate, and the patterning resolution of the stencil mask itself.

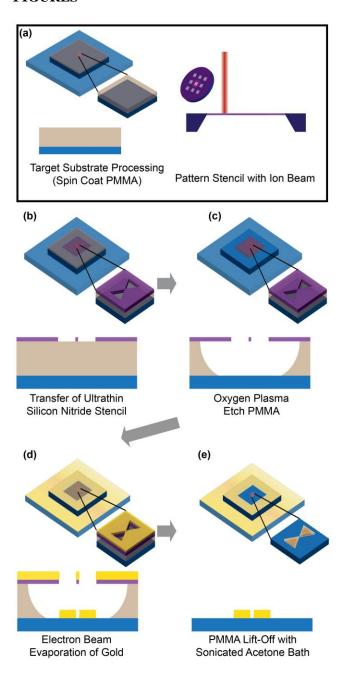

We first describe the nanostencil lithography process flow to pattern nanostructures onto a target silicon substrate (Fig. 1). A photolithographically patterned 100 µm thick SU-8 layer was first used as a mask to etch a raised square platform into the target silicon substrate (*Surface Technology Systems*, Inductively Coupled Plasma Reactive Ion Etch). A piranha bath (3 H<sub>2</sub>SO<sub>4</sub> : 1 H<sub>2</sub>O<sub>2</sub>, at 80 °C for 60 min) removed the remaining SU-8 from the wafer. A 200 nm thick sacrificial poly-methyl methacrylate layer (PMMA 950 A4) was spin coated onto the raised square platform on the substrate (Fig. 1a, left). The thickness of the sacrificial PMMA layer determined the final distance between the stencil and the substrate. In parallel to substrate preparation, ultrathin freestanding silicon nitride membranes (TEMwindows) were patterned using a Ga<sup>†</sup> focused ion beam (FEI Helios 600 Dualbeam) with the desired nanostructures corresponding to milled-through areas in the silicon nitride (Fig. 1a, right). The focused ion beam was then used to mill a set of cuts<sup>27</sup> (Fig. 2a,b) in the membrane, enclosing the desired

features in a much larger 50 μm square area defined by the cuts. The stencil mask was then aligned over, brought into contact with, and consequently detached onto, the raised platform on the silicon substrate (Fig. 1b). The PMMA exposed by the stencil pattern was then removed by treatment of the substrate with oxygen plasma for 20 min at a pressure of 800 mT of air at a power of 29.6 W (Harrick Plasma, Fig. 1c). The patterns in the stencil were converted into metallic nanostructures on the target substrate by evaporating 4 nm of titanium and 35 nm of gold through the apertures in the stencil mask, and onto the target substrate (Denton Electron Beam Evaporator, Fig. 1d). The remaining sacrificial PMMA layer, along with the stencil on top of the PMMA, was removed by sonication in an acetone bath for 40 s, leaving behind only gold nanostructures on the silicon platform (Fig. 1e).

The nanostencil lithography method described above improves the resolution by controlling the proximity of the stencil to the substrate through direct deposition of the stencil mask on top of a sacrificial PMMA layer. Owing to the direct transfer of the stencil, the thickness of the spin-coated PMMA spacer allows for precise control of the gap between the stencil and the substrate. The gap size has been reported to have a significant impact on the achievable resolution with nanostencil lithography, which is traditionally limited by geometric blurring (blurring from non-normal angle of incidence of material evaporated through the stencil), halo blurring (blurring from surface diffusion of deposited material), and stencil clogging (reduction in stencil aperture size due to deposition of material onto the stencil). For example, feature sizes of ~ 100 nm, and feature resolution down to 25 nm, were reported when the stencil is contacted directly with a flexible substrate, indicative primarily of the potential benefits of reductions in the gap between stencil and substrate<sup>30</sup>.

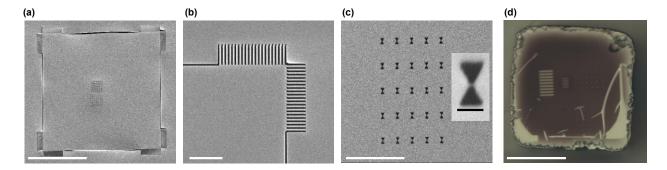

The pre-patterned set of cuts in the stencil mask (Fig. 2a,b) facilitates the stencil mask's detachment from its own carrier substrate onto the PMMA layer with high yield. Deposition of the stencil to the substrate is further assisted by aligning and contacting it with the PMMA coated raised platform on the target silicon substrate (Fig. 2b)<sup>27</sup>. The raised platform reduces the sensitivity of the deposition process to the intrinsic curvature of, and orientational misalignments between, the stencil and the substrate. However, deposition of the stencil does not critically rely on transfer to raised platforms: an

alternative method for high yield transfer is to mount the stencil onto a flexural stage that can correct for orientational misalignments<sup>31</sup>. The membrane transfer process is also extremely effective when used with flexible substrates<sup>32</sup>.

Following transfer of the stencil, areas of the sacrificial PMMA layer exposed through the stencil mask are selectively removed using an oxygen plasma etch. Since the oxygen plasma etch is isotropic, it leads to an undercut of the PMMA under each feature in the stencil mask. This undercut allows for an additional (optical) confirmation that the ion beam milling of the stencil mask penetrated completely through the membrane (Fig. 2d).

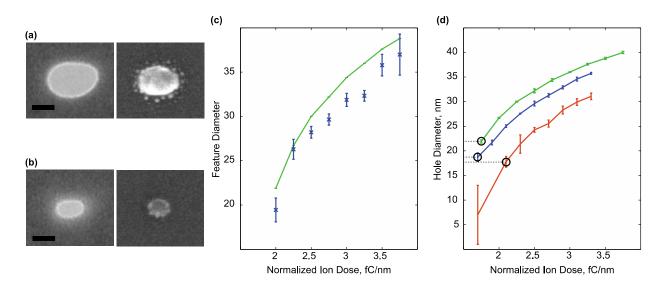

To test the achievable resolution with the controlled proximity stencil mask, a 20 nm-thick stencil was patterned with an array of holes varying from 20 nm to 40 nm in diameter (geometric mean of the major and minor axis lengths). A comparison of transmission electron microscope (TEM) images of the stencil holes to scanning electron microscope (SEM) images of the gold nanodots formed after evaporation suggests minimal geometric blurring (Fig. 3a,b). However, small gold particles, attributed to surface diffusion of gold following deposition, are visible <sup>6,33</sup>. If needed, previous reports have demonstrated the ability to selectively remove these smaller gold particles with a short dry etch<sup>34</sup>. The gold nanodot size was found to be consistently 2 – 3 nm smaller than the corresponding hole in the stencil mask (Fig. 3c). As deposition of metal onto the stencil reduces the size of the hole, the difference in size is likely attributable to stencil mask clogging. Nonetheless, the correspondence between the stencil hole and metallic nanodot structure down to ~20 nm indicates that the dominant limitation in resolution when using controlled proximity nanostencil lithography is the patterning resolution of the stencil mask.

Patterning of the stencil masks was performed by direct  $Ga^+$  focused ion beam (FIB) milling of silicon nitride (SiN<sub>x</sub>) membranes. The patterning resolution of the  $Ga^+$  ion beam is limited not only by the diameter of the focused ion beam (8 – 10 nm Full Width Half Max<sup>35</sup>), but a non-trivial interplay between multiple effects that include sputtering, atomic recoil, redeposition, and ion implantation<sup>36,37</sup>. While holes with diameters as small as 3 nm have been reported with  $Ga^+$  ion beams, the fabrication of holes with diameters smaller than the beam width is often less repeatable due to a significant increase in sensitivity

of the hole diameter to the ion beam dose<sup>38</sup>. To explore the trade-off between feature resolution and reproducibility with the  $Ga^+$  ion beam, we measured the ion dose – hole diameter profile for holes milled in a 20 nm-thick  $SiN_x$  stencil mask (green line, Fig. 3b). At the chosen ion dose step size of 0.25 fC / nm (the ion dose is normalized by the stencil thickness), the change in the milled hole diameter with each dose step was typically between 1-3 nm. However, decreasing the dose from 1.75 fC / nm to 1.5 fC / nm led to a sharp transition from a hole diameter of 22 nm to an incompletely milled through hole, indicating that the hole diameters produced for ion doses below the threshold dose of 1.75 fC / nm are extremely dose sensitive. We call the hole diameter just above the threshold dose as the *effective reproducible patterning resolution* of ion beam milling, which defines not only the minimum feature size, but is likely to determine the resolution with which curved elements or sharp corners can be fabricated on larger structures. Therefore, we further investigated methods for improving the *effective reproducible patterning resolution*.

Simulations of ion trajectories and atomic recoil in materials clearly suggest that the effective diameter over which the ion beam damages the substrate increases with distance from the top surface<sup>39</sup>. We therefore reasoned that reducing the SiN<sub>x</sub> membrane thickness would allow for higher resolution patterning of the stencil masks. To test this hypothesis, the Ga<sup>+</sup> FIB was used to make a dose array of holes in 20 nm, 10 nm, and 5 nm thick SiN<sub>x</sub> membranes, and the resulting ion dose – hole diameter profiles were measured in a TEM (Fig. 3b, green, blue, and red lines respectively). The results indicate thinner stencil masks have a slightly higher *effective reproducible patterning resolution* (22, 19, and 17 nm for 20, 10, and 5 nm thick membranes, respectively) (indicated by circles in Fig. 3d). As thickness related beam broadening effects are suppressed in the 5 nm thick membrane, further improvements in patterning resolution, potentially down to the 5 nm regime, likely require the use of lighter ion beams, such as Ne<sup>+40</sup> or He<sup>+41</sup>.

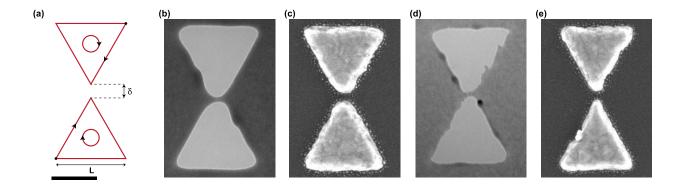

The improved patterning resolution of the stencil was further verified by characterizing the fabrication of bowtie nanogap structures. Bowtie nanoantennas are a geometry that exhibit particularly advantageous plasmonic properties for the collection of SERS spectra<sup>42</sup>. Arrays of bowties were

fabricated using both 20 nm-thick and 5 nm-thick silicon nitride stencils (Fig. 4a). SEM images of the fabricated bowtie stencil mask (Fig. 2c) were taken directly after milling with the ion beam in the same instrument without the need to unload and reload the sample. The *in situ* SEM visualization allows for verification of the milling process, and enables immediate optimization of the milling parameters including the ion beam dose and the programmed nanogap, δ, between the two triangles in the bowtie. A comparison between the TEM images of the stencil (Fig. 4c,e) and the SEM images of the structures after gold deposition (Fig. 4d,f) indicates excellent correspondence between the stencil shape and the resulting metal structure for both the 20 nm and 5nm-thick stencils. Similarly, a direct comparison between gold structures fabricated from different stencil thicknesses revealed that the thinner 5 nm stencil more accurately resolved the corner (11 nm radius of curvature, compared to the 21 nm radius of curvature for the 20 nm-thick stencil). For both membrane thicknesses, sub-15 nm gaps were achieved (Fig. 4c,e with gaps of 12 nm and 14 nm respectively).

Controlled proximity nanostencil lithography can easily allow for deposition of nanostructures of at least 70 nm thickness, as the PMMA spacer layer thickness can be varied to ensure successful lift-off without affecting the patterning resolution of the stencil mask. The use of the sacrificial PMMA layer is reminiscent of developed bilayer HSQ-PMMA electron beam lithography techniques<sup>43,44</sup>, which allow for patterning of nanostructures with similar thickness, and have been recently reported to achieve < 10 nm resolution<sup>45</sup>. However, HSQ-PMMA bilayer electron beam patterning still relies on the negative tone HSQ as the high-resolution electron beam resist. In contrast, the presented controlled proximity nanostencil lithography process provides patterning resolution approaching HSQ electron beam lithography, while retaining several distinct advantages of nanostencil lithography, including parallel processing of the stencil, environmental stability of the stencil to fluctuations in humidity or temperature, the lack of contamination from ion beam deposition and implantation, and the absence of any harsh acid or solvent treatment. Controlled proximity nanostencil lithography provides users with an environmentally stable, dose insensitive, positive tone fabrication method that is likely to be preferable to HSQ-PMMA bilayer electron beam patterning in many circumstances. The presented method also allows

the precision patterning step to be performed in parallel to any processing that the target substrate requires. As a result, higher throughput can be achieved using nanostencil lithography. For applications that have particularly tight patterning tolerances, the stencils can also be inspected with SEM or TEM prior to deposition.

While the controlled proximity nanostencil lithography method presented herein achieves higher gap resolution compared to other nanostencil lithography methods, it does so at the expense of using a sacrificial PMMA resist. Resist-free alternatives for high point resolution (sub-20 nm) for thin (sub-15 nm resolution) metallic nanostructures do exist<sup>9</sup>, and should be seriously considered if the cleanliness of the substrate is critical. However, the advances in stencil mask fabrication with ion beam milling presented in this paper are generally compatible with all nanostencil lithography procedures.

In conclusion, we report a process that advances the achievable resolution for nanostencil lithography. The achievable size, shape, and gap resolutions were characterized through the deposition of thick gold nanodots and bowtie nanogap structures. The fabricated structures revealed that controlled proximity of the stencil and the use of ultrathin stencils allowed the patterning resolution to approach the limit of the Ga<sup>+</sup> ion beam diameter. We anticipate that the present fabrication strategy will enable nanostencil lithography to be an effective technique for fabrication of high-precision nanostructures.

## Acknowledgments

This work was sponsored by the Department of the Air Force under Air Force Contract FA8721-05-C-0002. Opinions, interpretations, conclusions, and recommendations are those of the authors, and do not necessarily represent the view of the United States Government. This research made use of the MRSEC Shared Experimental Facilities supported by the National Science Foundation under award number DMR-0819762 at MIT.

## **FIGURES**

Fig. 1. Schematic process for controlled proximity nanostencil lithography. (a) PMMA is spin coated onto an elevated platform on a silicon target substrate, while in parallel, an ultrathin silicon nitride membrane is patterned with a Gallium focused ion beam (FIB) to produce the stencil mask. (b) The stencil is aligned and transferred onto the raised platform. (c) Oxygen plasma is used to etch the PMMA underneath the patterns in the stencil. (d) Electron beam evaporation deposits gold through the stencil patterns onto the silicon substrate. (e) The stencil is lifted off by dissolving the PMMA layer in a sonicated acetone bath

Fig. 2. (a) Scanning electron microscope (SEM) image of a 20 nm-thick silicon nitride (SiN $_x$ ) stencil mask after patterning cuts and bowties. Scale bar is 30  $\mu$ m. (b) SEM image of the cut pattern made in each corner of the membrane. Scale bar is 2  $\mu$ m. (c) SEM image of the bowtie array. Scale bar is 5  $\mu$ m. The inset shows a close-up of a single bowtie, with a gap between the two triangles clearly visible. Scale bar is 200 nm. (d) Optical image of the raised silicon platform with stencil membrane after the plasma etch step. The undercut of the PMMA allows the patterns in the stencil to be visualized. Scale bar is 40  $\mu$ m.

Fig. 3. Characterization of the achievable resolution with controlled proximity nanostencil lithography. (a) TEM image of a large stencil hole and SEM image of the corresponding gold dot. Scale bar is 20 nm. (b) TEM image of a small stencil hole and SEM image of the corresponding gold dot. Scale bar is 20 nm. (c) Comparison of the stencil hole size measured using TEM (green line), and the size of the resulting 40 nm-thick gold dots measured using SEM (blue crosses). (d) Dependence of the stencil hole size as a function of the normalized ion dose. Diameters corresponding to the highlighted data points mark the *effective reproducible patterning resolution*. Below the corresponding doses, hole diameters either did not break through, or exhibited high variability in breakthrough. All error bars denote  $\pm$  one standard deviation of measurements on three different stencils.

Fig. 4. Characterization of bowties with nanogaps. (a) Programmed raster pattern for gallium ion beam machining of bowties. Scale bar is 100 nm throughout the entire figure. (b) TEM image of a bowtie patterned into a 20 nm-thick  $SiN_x$  membrane stencil with the gallium ion beam. (c) SEM image of the gold structure resulting from the pattern shown in (b). (d) TEM image of a bowtie patterned into a 5 nm thick  $SiN_x$  membrane stencil. (c) SEM image of the gold structure resulting from pattern shown in (d).

## REFERENCES

- <sup>1</sup> H. Duan, H. Hu, K. Kumar, Z. Shen, and J.K.W. Yang, ACS Nano 5, 7593 (2011).

- <sup>2</sup> E.J.R. Vesseur, R. de Waele, H.J. Lezec, H.A. Atwater, F.J. García de Abajo, and A. Polman, Appl. Phys. Lett. **92**, 083110 (2008).

- <sup>3</sup> B. Päivänranta, A. Langner, E. Kirk, C. David, and Y. Ekinci, Nanotechnology **22**, 375302 (2011).

- <sup>4</sup> J.C. van Oven, F. Berwald, K.K. Berggren, P. Kruit, and C.W. Hagen, Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures **29**, 06F305 (2011).

- <sup>5</sup> L.J. Guo, Adv. Mater. **19**, 495 (2007).

- <sup>6</sup> O. Vazquez-Mena, T. Sannomiya, L.G. Villanueva, J. Voros, and J. Brugger, ACS Nano **5**, 844 (2010).

- <sup>7</sup> O. Vazquez-Mena, G. Villanueva, V. Sayu, K. Sidler, M.A.F. van den Boogaart, and J. Brugger, Nano Lett 8, 3675 (2008).

- <sup>8</sup> N.C. Lindquist, P. Nagpal, K.M. McPeak, D.J. Norris, and S.-H. Oh, Rep. Prog. Phys. **75**, 036501

- 9 M.M. Deshmukh, D.C. Ralph, M. Thomas, and J. Silcox, Appl. Phys. Lett. **75**, 1631 (1999).

- <sup>10</sup> H.M. Lee, S.M. Jin, H.M. Kim, and Y.D. Suh, Phys. Chem. Chem. Phys. **15**, 5276 (2013).

- <sup>11</sup> T. Lohmüller, L. Iversen, M. Schmidt, C. Rhodes, H.L. Tu, W.C. Lin, and J.T. Groves, Nano Lett **12**,

- <sup>12</sup> A. Kinkhabwala, Z. Yu, S. Fan, Y. Avlasevich, K. Müllen, and W.E. Moerner, Nature Photonics **3**, 654 (2009).

- <sup>13</sup> K. Healy, V. Ray, L.J. Willis, N. Peterman, J. Bartel, and M. Drndić, Electrophoresis **33**, 3488 (2012).

- <sup>14</sup> R. Vincent, S. Klyatskaya, M. Ruben, W. Wernsdorfer, and F. Balestro, Nature **488**, 357 (2012).

- <sup>15</sup> A.D. Franklin, M. Luisier, S.-J. Han, G. Tulevski, C.M. Breslin, L. Gignac, M.S. Lundstrom, and W. Haensch, Electron Devices Meeting (IEDM), 2011 IEEE International 12, 758 (2011).

- <sup>16</sup> P. Motto, A. Dimonte, I. Rattalino, D. Demarchi, G. Piccinini, and P. Civera, Nanoscale Research Letters 7, 113 (2012).

- <sup>17</sup> S. Lindsay, J. He, O. Sankey, P. Hapala, P. Jelinek, P. Zhang, S. Chang, and S. Huang, Nanotechnology **21**, 262001 (2010).

- <sup>18</sup> S. Yuasa, T. Nagahama, A. Fukushima, Y. Suzuki, and K. Ando, Nat Mater **3**, 868 (2004).

- <sup>19</sup> J.K. Yang, Y. Chen, T. Huang, H. Duan, N. Thiyagarajah, H.K. Hui, S.H. Leong, and V. Ng, Nanotechnology 22, 385301 (2011).

- <sup>20</sup> S. Dodson, M. Haggui, R. Bachelot, J. Plain, S. Li, and Q. Xiong, J. Phys. Chem. Lett. **4**, 496 (2013).

- <sup>21</sup> C. Moosmann, G.S. Sigurdsson, M.D. Wissert, K. Dopf, U. Lemmer, and H.-J. Eisler, Optics Express **21**, 594 (2013). <sup>22</sup> A.K. Mahapatro, S. Ghosh, and D.B. Janes, Nanotechnology, IEEE Transactions on **5**, 232 (2006).

- <sup>23</sup> T. Nagase, K. Gamo, T. Kubota, and S. Mashiko, Thin Solid Films **499**, 279 (2006).

- <sup>24</sup> Y. Kashimura, H. Nakashima, K. Furukawa, and K. Torimitsu, Thin Solid Films **438-439**, 317 (2003).

- <sup>25</sup> H.W. Ro and C.L. Soles, Materials Today **14**, 20 (2011).

- <sup>26</sup> A.E. Grigorescu and C.W. Hagen, Nanotechnology **20**, 292001 (2009).

- <sup>27</sup> A.A. Patel, C.P. Fucetola, E.E. Moon, and H.I. Smith, Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures 29, 06F402 (2011).

- <sup>28</sup> O. Vazquez-Mena, L.G. Villanueva, V. Savu, K. Sidler, P. Langlet, and J. Brugger, Nanotechnology **20**, 415303 (2009).

- <sup>29</sup> M. Lishchynska, V. Bourenkov, M.A.F. van den Boogaart, L. Doeswijk, J. Brugger, and J.C. Greer, Microelectronic Engineering 84, 42 (2007).

- <sup>30</sup> S. Aksu, M. Huang, A. Artar, A.A. Yanik, S. Selvarasah, M.R. Dokmeci, and H. Altug, Adv. Mater. 23, 4422 (2011).

- <sup>31</sup> B.J. Choi, S.V. Sreenivasan, S. Johnson, M. Colburn, and C.G. Wilson, Precision Engineering 25, 192 (2001). <sup>32</sup> T. Jain, R.J.S. Guerrero, C.A. Aguilar, and R. Karnik, Analytical Chemistry **85**, 3871 (2013).

- <sup>33</sup> T.N. Tun, M.H.T. Lwin, H.H. Kim, N. Chandrasekhar, and C. Joachim, Nanotechnology **18**, 335301

- (2007).

34 S. Aksu, A.E. Cetin, R. Adato, and H. Altug, Advanced Optical Materials n (2013).

35 Tachnology R: Microelectronics and Nanot <sup>35</sup> J. Gierak, Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures 15, 2373 (1997).

- <sup>36</sup> A.A. Tseng, J. Micromech. Microeng. **14**, R15 (2004).

- <sup>37</sup> S. Lindsey and G. Hobler, Nuclear Inst. and Methods in Physics Research, B **282**, 12 (2012).

- <sup>38</sup> J. Gierak, A. Madouri, A.L. Biance, E. Bourhis, G. Patriarche, C. Ulysse, D. Lucot, X. Lafosse, L. Auvray, L. Bruchhaus, and R. Jede, Microelectronic Engineering 84, 779 (2007).

- <sup>39</sup> D.C. Bell, M.C. Lemme, L.A. Stern, J.R. Williams, and C.M. Marcus, Nanotechnology **20**, 455301 (2009).

- <sup>40</sup> D. Winston, V.R. Manfrinato, S.M. Nicaise, L.L. Cheong, H. Duan, D. Ferranti, J. Marshman, S. McVey, L. Stern, J. Notte, and K.K. Berggren, Nano Lett 11, 4343 (2011).

- <sup>41</sup> M.M. Marshall, J. Yang, and A.R. Hall, Scanning **34**, 101 (2012).

- <sup>42</sup> D.P. Fromm, A. Sundaramurthy, A. Kinkhabwala, P.J. Schuck, G.S. Kino, and W.E. Moerner, J. Chem. Phys. **124**, 061101 (2006).

- <sup>43</sup> H. Yang, A. Jin, Q. Luo, J. Li, C. Gu, and Z. Cui, Microelectronic Engineering **85**, 814 (2008).

- <sup>44</sup> M. Rommel, B. Nilsson, P. Jedrasik, V. Bonanni, A. Dmitriev, and J. Weis, Microelectronic Engineering **110**, 123 (2013).

- <sup>45</sup> H. Duan, H. Hu, H.K. Hui, Z. Shen, and J.K.W. Yang, Nanotechnology **24**, 185301 (2013).