### Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

Spring 2015

# Architectural techniques to extend multi-core performance scaling

Hamza Bin Sohail *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

Part of the Computer Engineering Commons, and the Computer Sciences Commons

#### Recommended Citation

Sohail, Hamza Bin, "Architectural techniques to extend multi-core performance scaling" (2015). *Open Access Dissertations*. 559. https://docs.lib.purdue.edu/open\_access\_dissertations/559

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

| By Hamza Bin Sohail                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Entitled Architectural Techniques to Extend Multi-core Performance Scaling                                                                                                                                                                                                                                                     |

| For the degree of Doctor of Philosophy                                                                                                                                                                                                                                                                                         |

| Is approved by the final examining committee:                                                                                                                                                                                                                                                                                  |

| T. N. VIJAYKUMAR                                                                                                                                                                                                                                                                                                               |

| MITHUNA S. THOTTETHODI                                                                                                                                                                                                                                                                                                         |

| SAMUEL P. MIDKIFF                                                                                                                                                                                                                                                                                                              |

| VIJAY S. PAI                                                                                                                                                                                                                                                                                                                   |

| To the best of my knowledge and as understood by the student in the Thesis/Dissertation Agreement, Publication Delay, and Certification/Disclaimer (Graduate School Form 32), this thesis/dissertation adheres to the provisions of Purdue University's "Policy on Integrity in Research" and the use of copyrighted material. |

| T. N. VIJAYKUMAR Approved by Major Professor(s):                                                                                                                                                                                                                                                                               |

| Approved by: Michael R. Melloch 03/05/2015                                                                                                                                                                                                                                                                                     |

| Head of the Department Graduate Program Date                                                                                                                                                                                                                                                                                   |

## ARCHITECTURAL TECHNIQUES TO EXTEND MULTI-CORE PERFORMANCE SCALING

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Hamza Bin Sohail

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2015

Purdue University

West Lafayette, Indiana

This dissertation is dedicated to my parents.

#### TABLE OF CONTENTS

|    |      |               |                                                                     | Page    |

|----|------|---------------|---------------------------------------------------------------------|---------|

| LI | ST O | F TAB         | BLES                                                                | V       |

| LI | ST O | F FIG         | URES                                                                | vi      |

| AI | BSTR | ACT           |                                                                     | viii    |

| 1  | INT  | RODU          | CTION                                                               | 1       |

| 2  | COF  | PING V        | VITH THE SLOWING OF DENNARD'S SCALING                               | 5       |

|    | 2.1  | Introd        | luction                                                             | 5       |

|    | 2.2  | Multio        | core power and performance                                          | 9       |

|    |      | 2.2.1         | Intuition                                                           | 9       |

|    |      | 2.2.2         | Model                                                               | 11      |

|    |      | 2.2.3         | Model's predictions                                                 | 20      |

|    | 2.3  | Exper         | rimental Methodology                                                | 24      |

|    | 2.4  | Exper         | rimental Results                                                    | 29      |

|    |      | 2.4.1         | Performance                                                         | 29      |

|    |      | 2.4.2         | Impact of out-of-order issue                                        | 31      |

|    |      | 2.4.3         | Impact of processor-memory bandwidth and faster, 3-D stacked memory | 33      |

|    |      | 2.4.4         | Impact of ITRS (FinFETS) and leakage                                | 33      |

|    |      | 2.4.5         | Memory-unintensive Workloads                                        | 36      |

|    |      | 2.4.6         | Single Thread Latency                                               | 37      |

|    | 2.5  | Relate        | ed Work                                                             | 39      |

| 3  |      | TADAT<br>CHES | A ORGANIZATIONAL TECHNIQUES FOR 3-D DIE-STACKEI                     | D<br>41 |

|    | 3.1  | Introd        | luction                                                             | 41      |

|    | 3.2  | Oppor         | rtunity and Challenges                                              | 46      |

|    |      |        |                                          | Page |

|----|------|--------|------------------------------------------|------|

|    |      | 3.2.1  | Technology constraints                   | 46   |

|    |      | 3.2.2  | Access characteristics                   | 47   |

|    |      | 3.2.3  | Tag Metadata Bandwidth Challenge         | 47   |

|    |      | 3.2.4  | Opportunity                              | 48   |

|    |      | 3.2.5  | Previous proposals                       | 50   |

|    | 3.3  | Beta ( | Cache $(\beta \$)$ and Tag Cache $(T\$)$ | 52   |

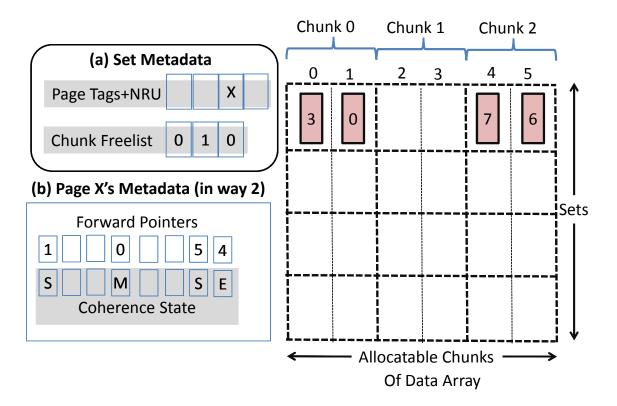

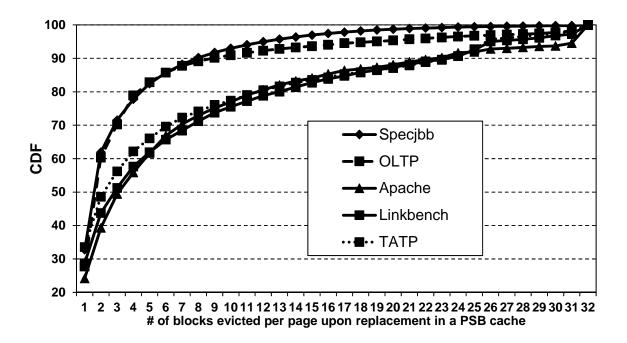

|    |      | 3.3.1  | Beta Cache $(\beta \$)$                  | 52   |

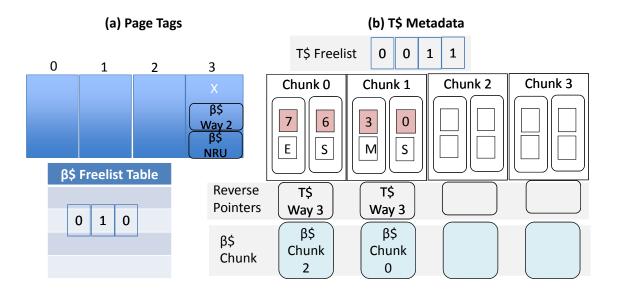

|    |      | 3.3.2  | Tag Cache ( $T$ \$)                      | 58   |

|    | 3.4  | Exper  | imental Methodology                      | 66   |

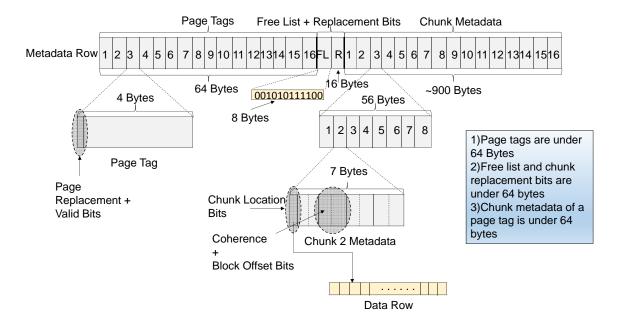

|    |      | 3.4.1  | Tag Overhead                             | 68   |

|    | 3.5  | Result | ts                                       | 70   |

|    |      | 3.5.1  | Performance                              | 70   |

|    |      | 3.5.2  | Comparison with SPEC2006 workloads       | 73   |

|    |      | 3.5.3  | Other Comparisons                        | 75   |

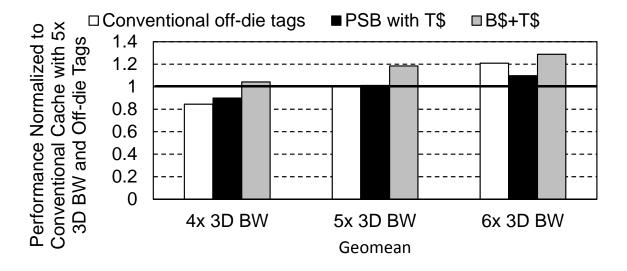

|    |      | 3.5.4  | Sensitivity to 3-D DRAM bandwidth        | 77   |

|    | 3.6  | Relate | ed work                                  | 78   |

| 4  | CON  | ICLUS: | IONS                                     | 81   |

| Rl | EFER | ENCE   | S                                        | 84   |

| V  | ТА   |        |                                          | 87   |

#### LIST OF TABLES

| Tab. | le                                                                                                      | Page |

|------|---------------------------------------------------------------------------------------------------------|------|

| 2.1  | Clock and active core scaling with technology generations ( $c = 1.07$ , $p = 0.73$ , $\alpha = 0.68$ ) | 21   |

| 2.2  | Scaling factors relative to Gen0 (45nm)                                                                 | 24   |

| 2.3  | Invariant parameters across generations                                                                 | 26   |

| 2.4  | Parameter scaling with technology generations                                                           | 26   |

| 2.5  | Workloads: Description and Characteristics                                                              | 27   |

| 2.6  | Measured average number of parallel memory accesses                                                     | 31   |

| 2.7  | Controlled SFU Configurations                                                                           | 37   |

| 3.1  | DRAM cache design issues                                                                                | 43   |

| 3.2  | Comparing 3-D DRAM accesses across cache designs                                                        | 51   |

| 3.3  | $\beta$ \$ Configuration                                                                                | 57   |

| 3.4  | Benchmarks                                                                                              | 65   |

| 3.5  | Common System Configuration Parameters                                                                  | 67   |

| 3.6  | Tag Overhead (MB)                                                                                       | 68   |

| 3.7  | DRAM Cache Misses per thousand instructions (MPKI)                                                      | 74   |

| 3.8  | Bandwidth demand at 3-D DRAM and Main Memory                                                            | 75   |

#### LIST OF FIGURES

| Figu | ire                                                                                                                                                                                                                                                                                                           | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

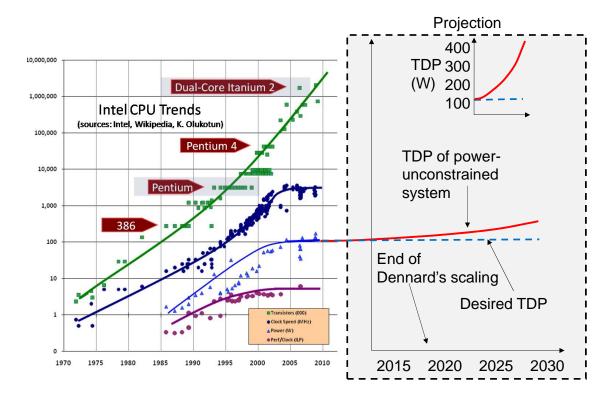

| 1.1  | Power projections (The trends have been extrapolated from the power trends figure courtesy of Kunle Olukotun and Lance Hammond)                                                                                                                                                                               | 2    |

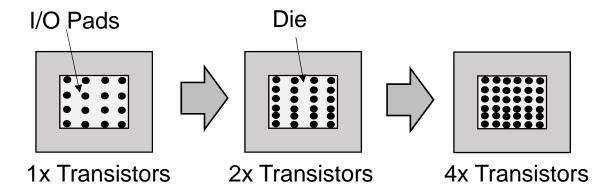

| 1.2  | Pin count increase with double the cores                                                                                                                                                                                                                                                                      | 4    |

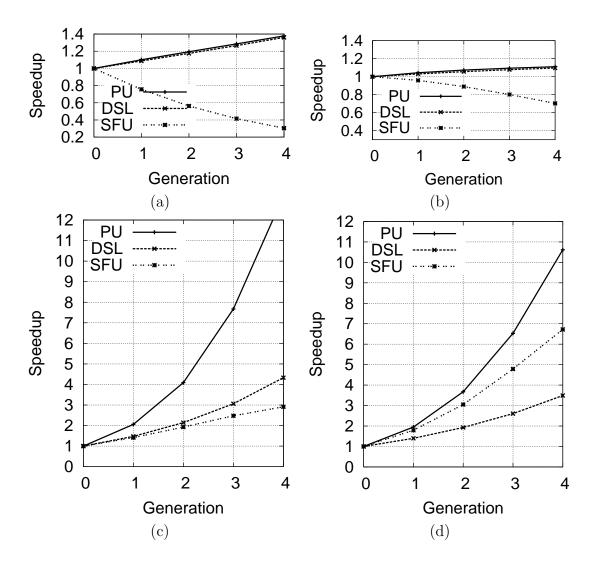

| 2.1  | Speedups across generations of PU, DSL, and SFU multicores over a four-core multicore (generation 0) for the following workloads: (a) mostly serial and memory-unintensive, (b) mostly serial, and memory-intensive, (c) mostly parallel and memory-unintensive, and (d) mostly parallel and memory-intensive |      |

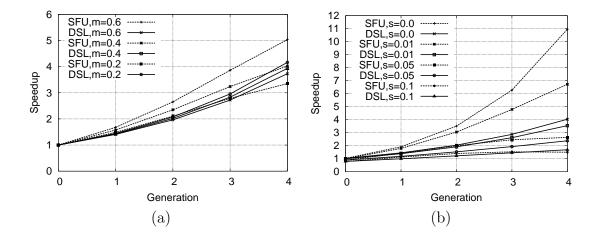

| 2.2  | Sensitivity to model parameters (speedup relative to generation 0, 4-core configuration) for the different values of m and s: (a) Variable memory intensity with $s=0.01$ , (b) Variable parallelism with $m=0.8$                                                                                             |      |

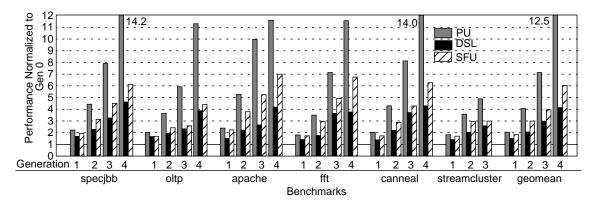

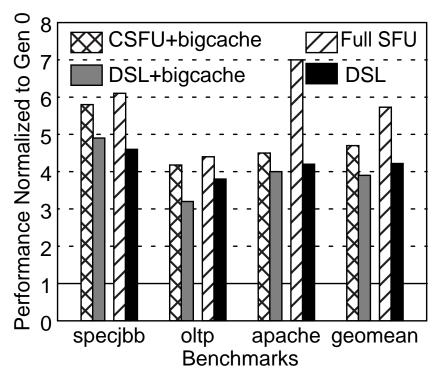

| 2.3  | Speedups of PU, DSL, and SFU multicores over a generation-0, four-core, PU multicore                                                                                                                                                                                                                          | 30   |

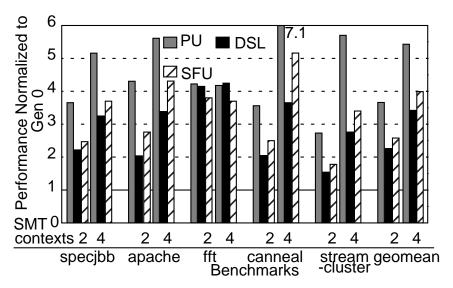

| 2.4  | Impact of out-of-order issue                                                                                                                                                                                                                                                                                  | 32   |

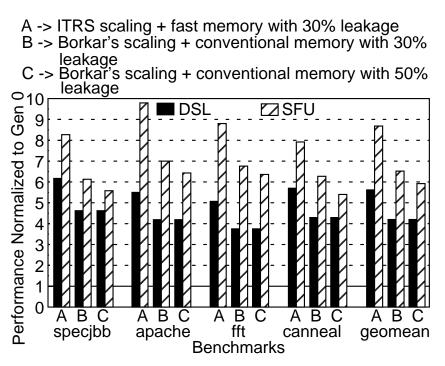

| 2.5  | Impact of memory bandwidth and latency                                                                                                                                                                                                                                                                        | 34   |

| 2.6  | Impact of ITRS projections and higher leakage                                                                                                                                                                                                                                                                 | 35   |

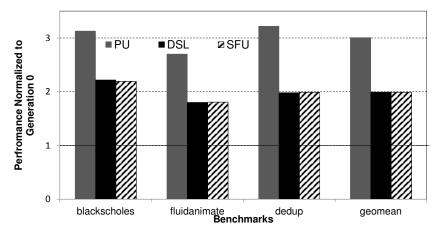

| 2.7  | Speedups of PU, DSL, and SFU generation-2 multicores over a generation-0, four-core, PU multicore for compute-intensive workloads                                                                                                                                                                             | 36   |

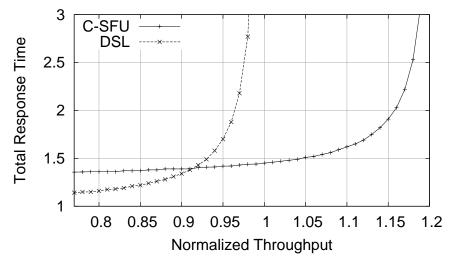

| 2.8  | Normalized throughput                                                                                                                                                                                                                                                                                         | 38   |

| 2.9  | Total response time versus throughput                                                                                                                                                                                                                                                                         | 39   |

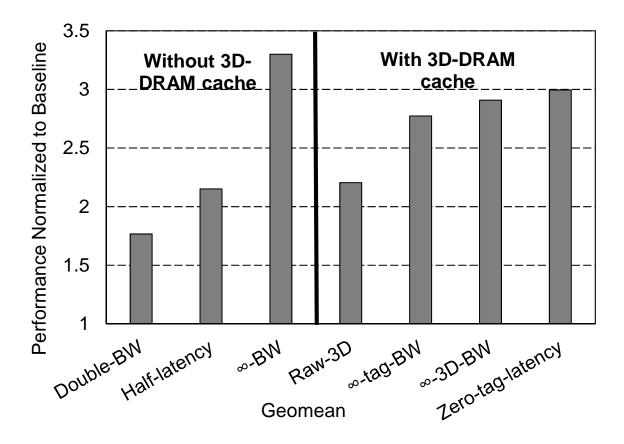

| 3.1  | Impact of bandwidth and latency                                                                                                                                                                                                                                                                               | 49   |

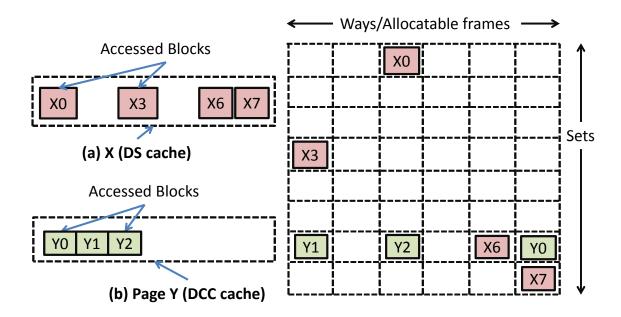

| 3.2  | Impact of organization on DRAM cache bandwidth (Example assumes 8 blocks per page)                                                                                                                                                                                                                            | 53   |

| 3.3  | Beta Cache ( $\beta$ \$) Organization                                                                                                                                                                                                                                                                         | 54   |

| 3.4  | Block density distribution                                                                                                                                                                                                                                                                                    | 55   |

| 3.5  | Tag Cache ( $T$ \$) Organization                                                                                                                                                                                                                                                                              | 59   |

| 3.6  | Metadata layout in the 3-D DRAM row                                                                                                                                                                                                                                                                           | 60   |

| Figu | re                                                      | Page |

|------|---------------------------------------------------------|------|

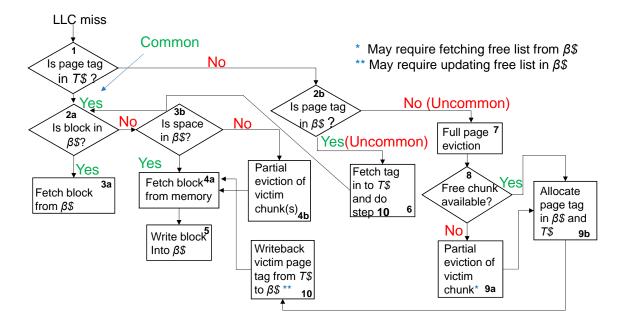

| 3.7  | Sequence of Operations on a $T$ \$ Access               | 64   |

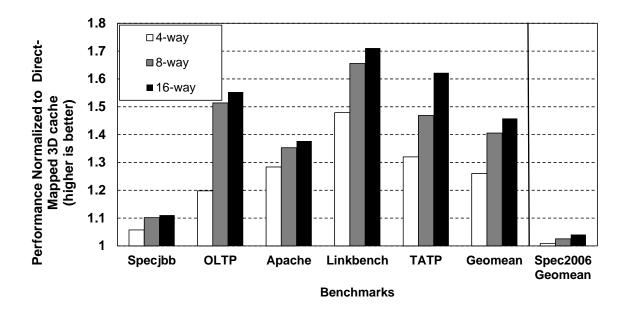

| 3.8  | Impact of Associativity on Performance                  | 66   |

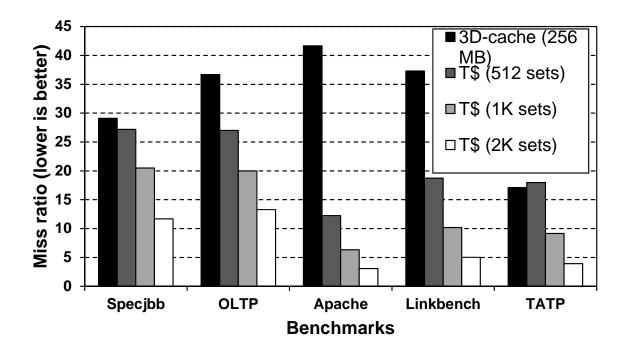

| 3.9  | T\$ miss rate                                           | 69   |

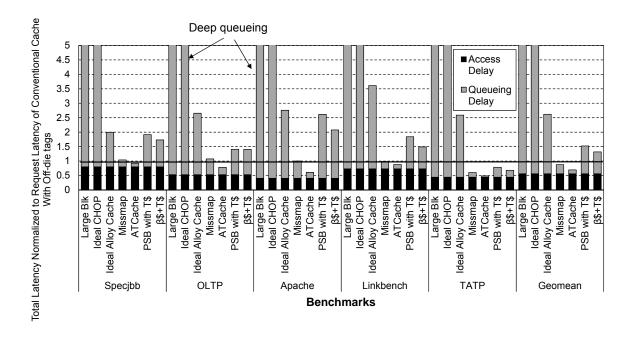

| 3.10 | Performance                                             | 71   |

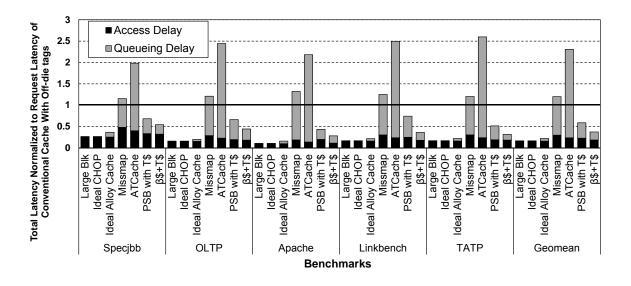

| 3.11 | Queuing delay for DRAM cache                            | 71   |

| 3.12 | Queuing delay for main memory                           | 72   |

| 3.13 | Spec Performance                                        | 73   |

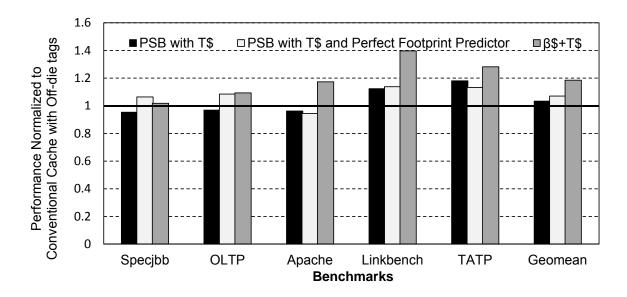

| 3.14 | Perfect Footprint Prefetch                              | 76   |

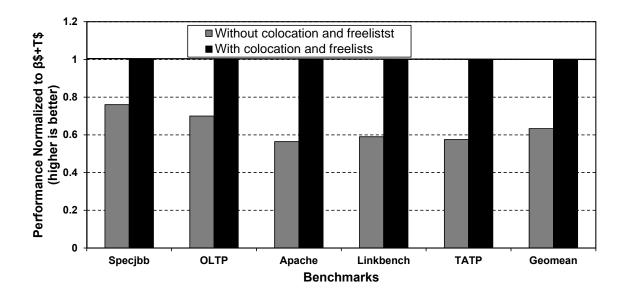

| 3.15 | Impact of $\beta$ \$'s features and comparison with DCC | 77   |

| 3.16 | Sensitivity to 3-D DRAM bandwidth                       | 78   |

#### ABSTRACT

Sohail, Hamza Bin PhD, Purdue University, May 2015. Architectural Techniques to Extend Multi-core Performance Scaling. Major Professor: T. N. Vijaykumar.

Multi-cores have successfully delivered performance improvements over the past decade; however, they now face problems on two fronts: power and off-chip memory bandwidth. Dennard's scaling is effectively coming to an end which has lead to a gradual increase in chip power dissipation. In addition, sustaining off-chip memory bandwidth has become harder due to the limited space for pins on the die and greater current needed to drive the increasing load. My thesis focuses on techniques to address the power and off-chip memory bandwidth challenges in order to avoid the premature end of the multi-core era.

In the first part of my thesis, I focus on techniques to address the power problem. One option to cope with the power limit, as suggested by some recent papers, is to ensure that an increasing number of cores are kept powered down (i.e., dark silicon) due to lack of power; but this option imposes a low upper bound on performance. The alternative option of customizing the cores to improve power efficiency may incur increased effort for hardware design, verification and test, and degraded programmability. I propose a gentler evolutionary path for multi-cores, called successive frequency unscaling (SFU), to cope with the slowing of Dennard's scaling. SFU keeps powered significantly more cores (compared to the option of keeping them 'dark') running at clock frequencies on the extended Pareto frontier that are successively lowered every generation to stay within the power budget.

In the second part of my thesis, I focus on techniques to avert the limited off-chip memory bandwidth problem. Die-stacking of DRAM on a processor die promises to continue scaling the pin bandwidth to off-chip memory. While the die-stacked DRAM is expected to be used as a cache, storing any part of the tag in the DRAM itself erodes the bandwidth advantage of die-stacking. As such, the on-die space overhead of the large DRAM cache's tag is a concern. A well-known compromise is to employ a small on-die tag cache (T\$) for the tag metadata while the full tag stays in the DRAM. However, tag caching fundamentally requires exploiting page-level metadata locality to ensure efficient use of the 3-D DRAM bandwidth. Plain sub-blocking exploits this locality but incurs holes in the cache (i.e., diminished DRAM cache capacity), whereas decoupled organizations avoid holes but destroy this locality. I propose Bandwidth- $Efficient\ Tag\ Access\ (BETA)\ DRAM\ cache\ (<math>\beta$ \$) which avoids holes while exploiting the locality through various metadata organizational techniques. Using simulations, I conclusively show that the primary concern in DRAM caches is bandwidth and not latency, and that due to  $\beta$ \$'s tag bandwidth efficiency,  $\beta$ \$ with a T\$ performs 15% better than the best previous scheme with a similarly-sized T\$.

#### 1. INTRODUCTION

For the past several decades, Moore's law has been the driving force behind the computing industry. The doubling of transistors every 2 years and increasing transistor speed at the same dollar cost delivered exponential performance improvement. In 1974, Robert Dennard presented the scaling theory for CMOS which postulated that transistors can be shrinked, and key figures of merit such as operating speed, layout density and energy efficiency can be improved as long as voltages, geometric dimensions and doping concentrations are consistently scaled to maintain constant electric field [1]. Dennard's scaling has been the major enabling factor in delivering the promise of Moore's law. During the earlier process generations, constant voltage scaling was employed but with almost a linear increase in power consumption, the industry switched to constant electric field scaling.

However, the slowing of Dennard's scaling during the last decade due to higher static power at lower threshold voltages forced the industry to move to multi-cores. Multi-cores were inevitable since uniprocessor performance improvements were only sustainable if Dennard scaling had continued. Multi-cores ushered the era in which higher performance necessitated greater parallelism in applications. Going parallel to sustain Moore's law was a major change in the landscape of computing. Multi-core performance came through exploitation of thread-level parallelism and small improvements in clock frequency. While multi-cores have successfully delivered performance improvements over the past decade, they now face problems on two fronts: power and off-chip memory bandwidth. Figure 1.1 shows chip power consumption over the years and extrapolates the effects of Dennard's scaling coming to an end. Purportedly, the imminent end of Dennard scaling will result in multi-cores hitting a utilization wall – a direct implication of the power wall. With supply voltage no longer scaling, many architects feel a significant number of transistors simply cannot be activated because

Fig. 1.1. Power projections (The trends have been extrapolated from the power trends figure courtesy of Kunle Olukotun and Lance Hammond)

of stringent power constraints.

In Chapter 2, I present an alternate evolutionary path for multi-core scaling in the absence of Dennard's scaling that can alleviate the power problem and extend the life-span of the multi-core era. I argue that architects, so far, have ignored the fact that memory plays a central role in today's applications; from databases to webservers and beyond, memory plays a crucial role in limiting the achievable performance. Because the power limits are harsh for memory-unintensive application behavior, the memory-intensive nature of a vast number of today's applications can act as a boon rather than a bane for multi-cores.

Fig. 1.2. Pin count increase with double the cores

In addition to the power conundrum, today's multi-cores have an increasing demand of memory bandwidth. Doubling the cores, even with double the cache capacity, increases the memory bandwidth demand by a factor of 2 which necessitates increasing the off-chip memory bandwidth. However, increasing off-chip memory bandwidth requires increase in pin count as well as device bandwidth. While heavy banking of DRAM will increase the device bandwidth, bus bandwidth requires an increase in pin count of the processor chip. Since die sizes do not change, it has become increasingly difficult to add more pins to increase bus bandwidth due to the limited space for pins on the die and greater current needed to drive the increasing load. 3-D Die-stacking aims to alleviate the pin-bandwidth problem. 3-D Die-stacked DRAM is stacked on top of the chip while Through-Silicon-Vias (TSVs) act as the interface between the chip and DRAM. Because the vias are on the surface of the chip and not the edges, it allows for more and wider buses. Even if DRAM is not stacked on top of the processor die, it can still offer high bandwidth by being off-die but in the same package (e.g., Intel's Haswell GT3e integrates a 128 MB DRAM in the same package). 3-D Die-stacking is meant to reduce the off-chip traffic which reduces the off-chip memory bandwidth demand. Consequently, the need to increase pin count can be avoided. However, the effectiveness of 3-D Die-stacking depends on how well its main feature (i.e., bandwidth) is used. As conventional wisdom suggests, researchers have proposed designing 3-D Die-stacked caches that reduce the off-chip memory traffic. The primary reason for this choice is that the capacity of 3-D Die-stacked DRAM is still far less than what off-chip DDR3/DDR4 modules have to offer; it adds negligible capacity to the physical address space if it were to be added as on-package physical memory.

In Chapter 3, I explore the design challenges associated with 3-D Die-stacked caches. The main advantage of 3-D Die-stacked caches is its high bandwidth. While it may provide some latency benefits (the smaller size of arrays and shorter delays on TSVs may reduce access delay), it is really the bandwidth of 3-D-Die stacked DRAM which enables it to serve the memory demands of multi-cores. First, I conclusively show how bandwidth (and not latency) is the real feature of 3-D Die stacked caches, contrary to some recent papers which tend to argue otherwise. Second, I show the importance of metadata organization in 3-D Die-stacked DRAM in order to preserve the bandwidth advantages that 3-D Die-stacking has to offer. Chapter 3 shows that plain-subblocking, a cache design technique invented back in the 1960s, tends to exploit spatial locality in a way that helps in cutting down the bandwidth demand due to metadata accesses. However, plain sub-blocking exploits this locality but incurs holes in the cache (i.e., diminished DRAM cache capacity), whereas decoupled organizations avoid holes but destroy this locality. To satisfy these seemingly opposing contraints, Chapter 3 will describe Bandwidth-Efficient Tag Access (BETA) DRAM cache ( $\beta$ \$), a cache design which avoids holes while exploiting the locality through various metadata organizational techniques with the aim to preserve the bandwidth advantage provided by 3-D Die-stacked DRAM.

Chapter 4 wraps up the thesis with conclusions drawn from the earlier chapters, and ends with greater optimism for the future of multi-cores.

### 2. COPING WITH THE SLOWING OF DENNARD'S SCALING

#### 2.1 Introduction

Historically, CMOS scaling has reduced transistor area and per-transistor dynamic power by about half and has improved switching speed by about 40% from one technology generation to the next. Specifically, Dennard's scaling of the supply voltage has allowed doubling the number of transistors without significantly worsening the dynamic power [1]. Recently, however, on one hand, Dennard's scaling has slowed down significantly due to its undesirable side-effects of higher leakage, narrower noise margins, and worse reliability (e.g., supply voltage reduces only by 2% now). On the other hand, transistor count, and hence the number of cores in a multicore, continue to double. Consequently, there is an exponential divergence between the core count and the per-core power. Unfortunately, the total chip power budget cannot be increased due to limits on cooling and power delivery (i.e., the total chip power will remain constant). These trends imply an increasing power shortage in future generations.

The imminence of dark silicon – silicon that must be kept deactivated because of power shortage – has been presaged<sup>1</sup> for some time now [2]. A recent paper [3] analyzes these trends and asserts that an increasing number of cores must be deactivated in future generations and that future multicore performance is fundamentally limited by dark silicon. I refer to the previously shown, dark-silicon induced multicore performance limit in [3] as (DSL). Alternatively, to alleviate the resulting performance loss, other papers [4–6] have suggested customizing the cores for specific functionalities to improve power efficiency and activate more cores with the same power budget. Unfor-

<sup>&</sup>lt;sup>1</sup>ARM CTO Mike Muller appears to have coined the term "dark silicon". [2]

tunately, the customization option puts multicores on a potentially arduous path of (i) requiring customization to provide exponential improvements of power efficiency (i.e., every generation better than the previous), (ii) incurring increased effort for hardware design, verification, and test, and (iii) potentially degraded programmability.

In this paper, I show that DSL performance bounds can be exceeded for memory-intensive applications, and that a gentler, evolutionary path exists where customization may be optional but not essential. Previous dark silicon papers [3,5] examine design points along the power-performance Pareto frontier covering a large space of large and small core designs and voltage-frequency-scaled operating points. The papers assert that the DSL configurations, in which a subset of the cores run at the Pareto-optimal clock speed while the rest are deactivated, achieves the best possible performance for a given technology generation and power budget. I emphasize that DSL deactivates cores and thereby bounds the *peak power* to be within the budget.

I make three key observations: First, because voltage-scaling has slowed down considerably, the Pareto frontier extends to a new region derived by frequency scaling alone. Second, because memory lags far behind processor clocks in speed, performance of most realistic workloads for future multicores will be dominated by memory latency and not processor clock speed (most future multicores with 16 or more cores are destined for servers with memory-intensive workloads). Finally, because cores wait for memory in such workloads and thereby dissipate far less power than the peak, DSL's average power is well below the budget. Our key result combines the first two observations to show that lower frequencies on the new extended Pareto frontier enable powering of more or, in many cases, all cores of a multicore which achieve more memory-latency overlap and better performance than DSL limits. I show that our results hold despite techniques for reducing, hiding, or tolerating memory latency via 3-D stacked memory, out-of-order issue, and simultaneous multithreading, respectively. While the DSL configuration bounds its peak power by deactivating cores (i.e., in space), I do so by lowering the clock frequencies (i.e., in time). However, our multicores' better performance does imply higher average power than DSL's well-belowthe-budget average. Nevertheless, as I show later in Section 2.2.2, our multicores' average power is guaranteed to be within the budget.

I arrive at our key result by exploiting two known non-linear effects, the first of which is captured by a simple analytical model for multicore performance. Our model shows that in the degenerate case of absence of memory latency, more cores running at slower clocks perform similarly to fewer running at faster clocks under the same power budget as long as the workloads are sufficiently parallel (a condition also necessary for multicores in general). In the presence of memory latency, however, more cores running at slower clocks perform better than fewer cores running at faster clocks. This reversal occurs because of the non-linear impact of clock speed on performance in the presence of memory latency where more active cores achieve more overlap of memory latency so that the dominant memory component of execution time reduces far more than the slight increase in the smaller non-memory component due to the slower clock. While our extra cores do incur more leakage than the DSL cores (cache capacity, and therefore cache leakage, is the same in both cases), SFU's advantage over DSL remains for memory-intensive workloads even after accounting for this extra leakage in all but extreme cases (e.g., 90% of the chip power is in leakage). However, because adjusting for the extra-leakage does modestly degrade memory-unintensive workloads, I propose to revert to the DSL configuration for such workloads. Thus, our key insight is that, for a broad range of memory-intensive commercial and scientific workloads, slow silicon is better than DSL's dark silicon as long as the slow silicon makes memory accesses. While voltage scaling has historically exploited the non-linear (cubic) relationship between power and voltage, I propose that clock-performance non-linearity be exploited in the post-Dennard era. Due to this fundamental non-linearity, DSL's performance limit can be exceeded for many realistic and important multicore workloads.

Based on our model's predictions, I propose a gentler, evolutionary path for multicores than customization, called *successive frequency unscaling (SFU)*. In SFU, more cores than DSL (and in many cases, all cores) are kept activated and run at *succes*- sively slower clocks every generation to bridge the exponential divergence between the core count and per-core power in the post-Dennard era. While the linear relationship between power and frequency is well known, this paper is the first to propose successively slower clocks; dynamic voltage and frequency scaling (DVFS) dynamically changes the clock speed up or down for good power-performance within a technology generation but does not employ successively slower clocks from one generation to the next.

I employ SFU in two contexts with different performance metrics. In the first context of workloads where job execution time is the only metric (e.g., scientific applications), I employ full SFU wherein I unscale frequency to power all the cores. Surprisingly, despite considerably slower clocks in later generations (e.g., sub-GHz) full SFU exceeds the DSL performance limit. Not surprisingly, however, SFU does not completely close the gap between a DSL configuration and a power-unconstrained system due to the slower clock. In the other context of enterprise workloads (e.g., online transaction processing) where both throughput and response latency matter, the slower clock of full SFU would degrade single-thread performance, and hence response latency. Accordingly, I employ controlled successive frequency unscaling (C-SFU) which moderately slows down the clock and powers many, if not all, cores to achieve better throughput than DSL. C-SFU avoids degrading response latency despite the clock slowdown by exploiting the second non-linearity that the higher throughput of C-SFU non-linearly reduces the queuing component of response latency and thereby compensates for the slower clock. Finally, SFU's simplicity implies better performance at virtually no design effort or complexity, enabling a viable evolutionary path for multicores.

The key contributions of this paper are:

• I propose the unusual idea of successively slower cores to stay within the power budget in the post-Dennard era.

• I show that, for memory-intensive applications (which includes important commercial benchmarks) our approach can exceed the DSL's performance limits.

The key results of this paper are:

- for memory-intensive workloads, SFU performs 46% better than DSL's limits at the 11 nm technology node whereas for memory-unintensive, workloads I revert to the DSL configuration; and

- for response-time-sensitive enterprise workloads, C-SFU achieves 21% better throughput than DSL at the 11 nm technology node while maintaining the total response latency including queuing delays to be within +/- 10%.

- while out-of-order cores partially reduce opportunity for SFU by reducing the

exposed memory latency, there remains ample opportunity for SFU to improve

performance compared to DSL (e.g., SFU with out-of-order cores achieves 18%

better performance then DSL with out-of-order cores at the 22nm technology

node).

The rest of the paper is organized as follows. Section 2.2 discusses our intuition and qualitative arguments behind SFU, and then presents a simple power-performance model for multicores to provide quantitative corroboration of our intuition. Sections 2.3 and 3.5 validate our model using simulations of commercial and scientific workloads. Finally,

#### 2.2 Multicore power and performance

I start with the intuition behind SFU followed by an analytical model.

#### 2.2.1 Intuition

The two key claims by Esmailzadeh et al. [3] are that (1) the limit on performance achievable in practical multicore systems of future technology generations is

significantly lower than the performance of a power-unconstrained multicore system in the equivalent technology generation, and (2) dark-silicon is inevitable for optimal performance. Esmailzadeh et al.do not examine frequency scaling alone because, where both voltage and frequency scaling are possible, scaling frequency alone is not Pareto-optimal. However, in regions where further voltage scaling is infeasible, frequency-scaling alone can be used to extend the power-performance Pareto frontier. Even in this extended Pareto frontier, frequency scaling alone cannot improve upon DSL for memory-unintensive applications (i.e., applications with little exposed memory latency) because both techniques offer the same linear improvement (degradation) in performance for linear increase (reduction) in power. However, I observe that when I include the effect of exposed memory latency, the power-performance tradeoff due to frequency unscaling becomes sub-linear because the exposed memory latency does not scale. Such sublinearity is advantageous because a large reduction in frequency (which reduces power linearly) results in less-than-proportional reduction in performance. This difference in the impact of frequency scaling on dynamic power (linear) and performance (sub-linear) is central to enabling our design to achieve higher performance than the DSL limits would imply.

Recent work [7] reveals that near-threshold operation is performance-per-watt optimal for perfectly parallelizable programs. Given that the dark-silicon problem is to maximize performance under a fixed power-budget, one may think that such performance-per-watt optimality is ideal. However, near-threshold-computing's energy optimality results in very slow speed (e.g., 3-MHz Intel Claremont). As such, even though individual cores may be performance-per-watt optimal, the system as a whole will run into other bottlenecks (e.g., area, application scalability) which can prevent the utilization of the full power budget and hence degrade performance. Further, the paper does not consider memory effects which is the main focus of our work.

Next, to support the above qualitative reasoning, I develop a simple analytical model of the combined impact of SFU's frequency unscaling and memory latency effects on overall multicore power-performance.

#### 2.2.2 Model

Our model is derived from Amdahls' Law [8] and more recent revisits of Amdahl's Law in the context of multicores [3,9]. However, recall from Section 3.1 that the key reason for our better performance is more cores achieving higher overlap of memory latency. Accordingly, our model specifically includes memory latency effects in addition to the usual serialization effects.

I first describe our model for a multicore that is not constrained by power. Then, I modify this model to include power constraints either via the DSL configuration or successive frequency unscaling (SFU). Let

- s be the serial portion of sequential execution time (i.e., 1-s is the parallel portion);

- c be the factor by which the clock frequency improves every technology generation (e.g., if the clock speed improves by 20% then c = 1.2); and

- m be the fraction of sequential execution time due to memory latency (i.e., 1-m is the non-memory, compute fraction).

I derive m as follows: Assuming the number of off-chip misses per kilo instructions (MKPI) is r, the per-access average exposed main memory latency is  $mem_{lat}$  in processor cycles, and the processor cycles per instruction (CPI) with 0% off-chip miss rate is  $instr_{lat}$  then

$$m = r \times mem_{lat}/(1000 \times instr_{lat} + r \times mem_{lat}).$$

For example, assuming an off-chip miss rate of 2% which usually corresponds to r of 5,  $mem_{lat}$  of 400, and  $instr_{lat}$  of 0.5 gives m = 0.80. I note that  $mem_{lat}$  denotes exposed memory latency, and hence covers both in-order- and out-of-order-issue cores though the latter's  $mem_{lat}$  and m values would be smaller than the former's.

To simplify the model, I assume that

- both the parallel and serial portions of the application incur the same fraction m of execution time due to memory latency;

- employing more parallel cores does not change the fraction m of execution time due to memory (our experimental evaluation avoids these two assumptions by using real workloads);

- the factor c is constant across generations while in reality clock speed improvements may reduce in later generations resulting in an overall average of c (our experimental evaluation uses actual, non-constant factors);

- the cores do not employ simultaneous multithreading (SMT) (I include SMT later); and

- memory bandwidth scales with the number of cores (I revisit this assumption in our results).

Defining the execution time on the generation-0 system as 1 (i.e., our normalization base), the breakdown of the total execution time may be expressed as:

$$s \times ((1-m)+m) + (1-s) \times ((1-m)+m)$$

Over n technology generations, the non-memory, compute fraction 1-m scales as  $(1-m)/c^n$  due to clock speed improvements while the memory fraction m remains unchanged. This scaling occurs for both the serial and parallel portions so that the serial portion scales as  $s \times (\frac{1-m}{c^n} + m)$  and the parallel portion scales as  $(1-s) \times (\frac{1-m}{c^n} + m)$ . In addition, the parallel portion gets further sped up by a factor of 2 every generation due to the doubling of the core count so that the parallel portion scales overall as

$$\frac{(1-s)\times(\frac{1-m}{c^n}+m)}{2^n}.$$

Thus, after n generations since the last uniprocessor, a power-unconstrained (PU) multicore achieves a net speedup of

$$\frac{1}{s \times (\frac{1-m}{c^n} + m) + \frac{(1-s) \times (\frac{1-m}{c^n} + m)}{2^n}}$$

(2.1)

I note that while the 1-m compute terms in both the serial and parallel portions diminish exponentially over generations due to faster clocks, the m memory term

in the parallel portion diminishes exponentially due to more cores' higher memory-level parallelism. For memory-intensive workloads, m is generally greater than 1-m making the number of cores more important than the clock speed for performance (from the above example, m is 0.80). As I will see shortly, this difference is the key contrast between DSL and SFU where the former keeps only a subset of the available cores powered whereas the latter keeps all the cores powered albeit at a slower clock.

For the DSL multicore which is constrained by power, let p be the factor by which the per-core dynamic power scales every technology generation due to a combination of feature size scaling, slow scaling of voltage, and transistor engineering (e.g., if power reduces by 20% then p = 0.8). To simplify the model, I assume that

- the dynamic power of the on-chip (non-L1) caches and network for a core's accesses are included in the core's dynamic power (an accounting simplification that does not affect the model's predictions);

- leakage is zero (I add in leakage in the next section); and

- p, like c, is constant across generations while in reality dynamic power improvements may reduce in later generations resulting in an overall average of p.

To stay within the constant power budget across generations, DSL bounds its peak power by limiting the number of cores after n generations to  $(2 \times 0.5/p)^n = 1/p^n$  (i.e., bound in space). DSL differs from PU only in the number of active cores —  $1/p^n$  versus  $2^n$ ; DSL enjoys identical clock speed and last-level, shared cache size improvements, and incur similar memory latency effects. Therefore, the DSL multicore's net speedup after n generations is

$$\frac{1}{s \times (\frac{1-m}{c^n} + m) + \frac{(1-s) \times (\frac{1-m}{c^n} + m)}{1/p^n}}$$

(2.2)

I see that DSL exploits significantly less memory-level parallelism than PU due to fewer active cores. This limitation considerably degrades performance for realistic multicore workloads which are memory-intensive.

SFU achieves the same peak bound by successively scaling down the clock over generations so that the per-core power from one generation to the next is half allowing twice as many cores to be powered (i.e., bound in time). Let  $\alpha$  be the factor by which the clock speed is unscaled every generation on top of the factor c provided by technology scaling, so that  $\alpha \times p = 0.5$ . To account for the dynamic power of the on-chip (non-L1) caches and network, this unscaling applies to those components as well. SFU differs from PU only in the scaling of the clock speeds —  $c^n$  versus  $(\alpha \times c)^n$ , while maintaining the same number of active cores (i.e.,  $2^n$ ) and cache size. Consequently, the SFU multicore's net speedup after n generations is

$$\frac{1}{s \times (\frac{1-m}{(\alpha \times c)^n} + m) + \frac{(1-s) \times (\frac{1-m}{(\alpha \times c)^n} + m)}{2^n}}$$

(2.3)

Comparing DSL and SFU, I consider all four components of execution time (the denominators in the above performance expressions): serial-non-memory  $(s \times (1-m))$  terms), serial-memory  $(s \times m)$  terms), parallel-non-memory  $((1-s) \times (1-m))$  terms), and parallel-memory  $((1-s) \times m)$  terms). DSL reduces the serial-non-memory component by the factor of  $c^n$  and is better than SFU which reduces by the smaller factor of  $(\alpha \times c)^n$ . However, this component is likely to be small for parallel, memory-intensive workloads. DSL and SFU are equal in the serial-memory and parallel-non-memory (the second and third) components. The equality in the second component is obvious. To see the equality in the third component, DSL reduces the component by a factor of  $p^n/c^n$  whereas SFU reduces by a factor of  $2^n/(\alpha \times c)^n$  where  $\alpha \times p = 0.5$ . DSL reduces the (fourth) parallel-memory component by a factor of  $(1/p)^n$  which is worse than SFU's factor of  $2^n$ , highlighting our insight that slow silicon is better than dark silicon in the presence of memory latency (e.g., if p = 0.8, then DSL's and SFU's factors are  $1.25^n$  and  $2^n$ , respectively, giving SFU a significant advantage in memory-level parallelism). As discussed above, in memory-intensive parallel workloads, the

parallel-memory component is likely to dominate the other components, magnifying SFU's advantage. Therefore, DSL's limit can be exceeded.

#### Impact of leakage:

The above analysis ignores leakage power, which generally increases with lower supply voltage and higher transistor count. In the post-Dennard generations, however, leakage as a fraction of the total power budget will either remain a constant (e.g., 25-30%) or increase only slowly (e.g., under 5% per generation) due to two reasons: (1) voltage scaling has slowed down considerably and (2) the rate of growth of transistor speed over generations is reduced to compensate for the doubling of transistor count every generation (e.g., by fine-tuning the transistor threshold voltage). Recent commercial microprocessors follow this methodology to keep leakage under check [10]. Note, I assume SFU and DSL use the same fast, leaky transistors (i.e., per-transistor leakage is the same for SFU and DSL). This assumption enables us to operate a subset of processors with the same maximum frequency as DSL which is important to allow for memory-unintensive workloads.

Let l be the leakage budget as a fraction of the total power budget in the last uniprocessor generation and  $\lambda$  be the rate at which the total chip leakage budget increases every generation. Then, the chip leakage budget scales as  $\lambda^n \times l$  after n generations (to be meaningful,  $\lambda^n \times l < 1$  for any n), whereas the chip dynamic power budget scales as  $(1 - \lambda^n \times l)$ . To make room for leakage, this new dynamic power budget is lower than our previously-assumed full budget. Let  $f_l$  be the core leakage as the fraction of the total chip leakage, the remainder of which is the cache leakage. This scaling implies that (1) the core counts and clock frequencies for DSL and SFU, respectively, should be adjusted for this new dynamic power budget at every generation; and (2) DSL's fewer cores incur less leakage than the allotted budget (and also less than SFU), allowing more cores to be added (the DSL paper does not discuss such compensation).

Because the new, lower dynamic power budget is the same for DSL and SFU, both designs are affected similarly. Both DSL's core count for generation n, given by  $1/p^n$ , and SFU's clock frequency, given by  $(\alpha \times c)^n$  in Equations 2.2 and 2.3, respectively, reduce by the factor  $(1-\lambda^n \times l)$ . Therefore, SFU maintains its advantage in memory-level parallelism, and hence performance, over DSL.

To account for DSL's leakage budget surplus, I observe that the budget for the core leakage, total dynamic power, and cache leakage scale as  $f_l \times \lambda^n \times l$ ,  $(1 - \lambda^n \times l)$ , and  $(1 - f_l) \times \lambda^n \times l$ , respectively. I analyze each of these terms for DSL. Because there are  $2^n$  cores in all, the per-core leakage in DSL is  $f_l \times \lambda^n \times l/2^n$ . Because  $1/p^n$  DSL cores account for the full dynamic power budget, the per-core dynamic power for DSL is  $(1 - \lambda^n \times l) \times p^n$ . Because both DSL and SFU have the same cache capacity, the cache leakage is the same in the two designs. Therefore, assuming x DSL cores use the full power budget, the total core leakage (= per-core leakage  $\times x$ ), total dynamic power (= per-core dynamic power  $\times x$ ) and the cache leakage add up to 1. That is,

$$\left(\frac{f_l \times \lambda^n \times l}{2^n} + (1 - \lambda^n \times l) \times p^n\right) \times x = 1 - (1 - f_l) \times \lambda^n \times l \tag{2.4}$$

To tie leakage and performance together, the number of DSL cores in Equation 2.2 should be changed from  $1/p^n$  to the value of x from Equation 2.4. To analyze Equation 2.4, I observe that the caches' large transistor counts (e.g., 75% of all on-chip transistors) are offset only partly by the fact that they can use slower, less-leaky transistors than the cores. As such, caches account for a large part of the chip leakage (e.g., the core leakage fraction  $f_l$  is 0.4). This large part forces the right hand side of Equation 2.4 not to be large. Further, compensating for DSL's leakage surplus by adding extra DSL cores adds both their small leakage and their large dynamic power (including the accompanying dynamic power for the on-chip (non-L1) caches and network). These two components make the left term of the product in the left hand side large. Consequently, x is not large (i.e., not much larger than  $1/p^n$ ), implying that DSL's leakage surplus can accomodate only a few extra cores.

I illustrate this point with some realistic examples based on known scaling trends [4]. Assume a constant 30-70 split of the total budget for leakage and dynamic power (i.e., l=0.3 and  $\lambda=1$ ) and a 40-60 split of the leakage budget for the cores and caches (i.e.,  $f_l=0.4$ ). Assume generation 6 with 64 cores (i.e., n=6) and DSL's p=0.646(i.e.,  $p^6 = 0.073$ ). While SFU runs all the 64 cores at a slower clock, DSL runs  $1/p^6$ = 13.7 cores at the full clock speed. SFU splits a total budget of 100 as 12, 70, and 18 for the core leakage, dynamic power, and cache leakage, respectively. DSL has the same dynamic power (70) and cache leakage (18) as SFU. Because each DSL core's leakage is 12/64, DSL's total budget with 13.7 cores is (12/64) \* 13.7 + 18 + 70 =90.57, and not 100 as it is for SFU. Therefore, a few more DSL cores can be accomodated. Assuming x DSL cores and plugging in our values in Equation 2.4 gives (12/64 + 70/13.7) \* x + 18 = 100, giving x = 15.5. DSL's leakage surplus is equivalent to only 15.5 -13.7 = 1.8 extra DSL cores. Thus, I see that SFU's advantage of memory-level parallelism remains. However, the advantage exists solely for memory intensive applications where the parallel memory component (fourth term in the denominator of Equation 2.2 and Equation 2.3) reduces with memory-level parallelism. For memory-unintensive applications, where m is negligible, DSL is better because of the additional cores due to leakage compensation.

Increasing the the total chip leakage budget from 30% to as much as 50% (i.e., l=0.3 and  $\lambda=1.09$ ) implies that the core leakage, dynamic power, and cache leakage are 20, 50, and 30 in SFU, respectively. The DSL calculations change to (20/64+50/13.7)\*x+30=100, giving x=17.7, or 4 extra DSL cores. Now, the number of extra DSL cores can be much larger. For example, if the total chip leakage budget goes to 90% (i.e., l=0.9) and core leakage is also 90% of all leakage (i.e.,  $f_l=0.9$ ), then (81/64+10/13.7)\*x+9=100, giving x=45.6. In this extreme case, SFU has fewer than 2x cores than DSL (45.6 versus 64) but a much slower clock, so that SFU's memory-level parallelism advantage may not offset its clock disadvantage. As an aside, I note that higher leakage (from 30% to 90%) leads to more DSL cores (from 15.48 to 45.6). The dark silicon problem diminishes because dynamic power,

which is worsensed considerably by the slowing down of Dennard's scaling, is now the minor component whereas leakage, the major component, increases only slowly. In our experiments, I show the more realistic cases of 30% and 50% leakage.

Finally, I discuss a subtle point: One might think that if DSL has a 25-75 split of per-core leakage versus per-core dynamic power (this ratio is different from any of the above), then SFU having 4x more cores than DSL would imply zero dynamic power for SFU cores (Amdahl's leakage limit). While true, this limit is rarely reached. Although chip leakage is 50% in our second example above, DSL's per-core leakage versus per-core dynamic power ratio is 20/64 versus 50/13.7 or 1 versus 11.67 which is drastically different than the starting assumption of 20 in core leakage and 50 in dynamic power (or 1 versus 2.5). Because Dennard's scaling has slowed significantly while leakage stays constant or increases only slowly, DSL's per-core dynamic power far exceeds the per-core leakage in future generations, making the leakage limit irrelevant in realistic scenarios. I note that while DSL's ratio of core leakage to core dynamic power, and not SFU's ratio, is relevant for this limit, SFU's ratio in this example is 20/64 versus 50/64 or 1 versus 2.5 because SFU scales down the clock to reduce the per-core dynamic power.

#### SFU's peak power bound:

After adjusting for leakage, DSL and SFU have the same peak power though DSL bounds its peak power to be within the budget by deactivating cores (i.e., in space) whereas SFU does so by lowering the clock frequencies (i.e., in time). However, SFU's higher performance in memory-intensive workloads means higher average power than DSL. Nevertheless, SFU's average power is still within the budget. To validate this claim, I note that due to exposed memory latency, DSL's average power for these memory-intensive workloads falls below its peak by a factor determined by the latency. (There is no such power slack for memory-unintensive workloads.) Because SFU can at most eliminate this latency through higher memory-level parallelism,

SFU's performance, and hence average power, can increase at most by this factor. Therefore, SFU's average power is within the budget.

#### Effect of SMT:

The above model does not include SMT. It may seem that because SMT reduces each core's exposed memory latency via better thread overlap, SFU's opportunity would decrease with SMT. However, SMT increases the number of threads to improve thread ovelap but does not change each thread's compute-memory overlap or performance (ignoring any extra cache misses due to SMT's increased cache pressure). SMT's thread overlap is no different than that achieved by the cores of a multicore (i.e., one core's memory latency is overlapped by the other cores' computation and memory accesses) and the non-linear impact of memory latency on power-performance tradeoff holds in a multicore irrespective of the number of cores, as seen in Equation 2.1. Therefore, the non-linearity holds for SMT as well, implying that the above model stays valid for SMT. One may think that DSL, like SFU, can also increase its memory-level parallelism via SMT. However, adding SMT contexts to a core would linearly increase its activity factor, and hence dynamic power, and would force the number of DSL cores to be cut by the same factor. Therefore, DSL's performance, and hence SFU's opportunity, would remain unchanged with SMT. In reality, SMT's increased cache pressure may actually increase cache misses and thereby increase SFU's opportunity. I include SMT in all our results.

As an aside, I note that unlike SMT, out-of-order issue does increase each thread's compute-memory overlap and therefore, may decrease SFU's opportunity. I evaluate this point in our results.

#### Controlling single-thread latency:

SFU, as proposed, improves (1) overall execution time of parallel workloads (e.g., scientific workloads) and (2) throughput of enterprise workloads (e.g., on-line trans-

action processing). However, full SFU requires scaling the clock by  $(\alpha \times c)$  every generation which may degrade single-thread performance, and hence response latency, of enterprise workloads. This degradation may be considerable despite the sub-linear impact of clock on performance particularly in later generations where the clock is slowed down significantly with full unscaling. To address this issue, I exploit the other non-linear impact of throughput on queuing delays where higher throughput super-linearly reduces the queuing delay component of response latency as dictated by queuing theory, and thereby compensates for the slower clock. Based on this non-linear relationship, I propose to reduce the unscaling factor  $\alpha$  compared to full SFU, still allowing more cores to be powered than DSL, though not all the cores like full SFU. I choose  $\alpha$  so that the resultant degradation of single-thread execution time is matched by the gain in the queuing delay due to higher throughput, resulting in similar total response latency and higher throughout as compared to DSL. I propose to apply such controlled SFU (C-SFU) only for response-latency-sensitive workloads and not for others.

Because C-SFU allows only a subset of the cores to be powered, I consider the option of converting the area and leakage of the remaining unpowered cores, which would otherwise be dark silicon, into additional last-level cache (unlike core customization, this option does not worsen design/programmability costs). While the same design can choose dynamically between full or controlled SFU based on the workload, this option cannot be applied dynamically and, if employed, would require different designs for full and controlled SFU. Though DSL's surplus core leakage budget is already used up for extra cores (Section 2.2.2), I still consider this conversion option for DSL as well.

#### 2.2.3 Model's predictions

To illustrate our model's predictions, I analyze four regions of the workload-characteristics space in Figures 2.1(a) through (d), respectively: (1) mostly serial

Table 2.1. Clock and active core scaling with technology generations (c=1.07, p=0.73,  $\alpha=0.68$ )

| Parameter    | Arch.  | G0  | G1   | G2   | G3    | G4    |

|--------------|--------|-----|------|------|-------|-------|

|              | PU,DSL | 3.2 | 3.42 | 3.66 | 3.92  | 4.19  |

| Clock (GHz)  | SFU    | 3.2 | 2.33 | 1.69 | 1.23  | 0.90  |

|              | PU,SFU | 4   | 8    | 16   | 32    | 64    |

| Active cores | DSL    | 4   | 5.61 | 7.79 | 10.69 | 14.67 |

and memory-unintensive (s = 0.8 and m = 0.02), (2) mostly serial and memory-intensive (s = 0.8 and m = 0.8), (3) highly and memory-unintensive (s = 0.01 and m = 0.02), and (4) highly parallel and memory-intensive (s = 0.01 and m = 0.8).

The figure compares the PU (Equation 2.1), DSL, (Equation 2.2 with the adjustment for the number of cores from Equation 2.4), and SFU (Equation 2.3) multicores across technology generations. The Y axis shows the speedups for the multicores over our generation-0 4-core multicore; and the X axis shows the technology generations 1 through 4. I assume that the clock and power improvement factors across generations, c and p, are 1.07 and 0.73, respectively, in line with the conservative scaling trends in [4]. Based on this p, the frequency unscaling factor,  $\alpha$ , is 0.68. I assume a chip leakage budget of 30% of which 40% is core leakage (i.e., l = 0.3,  $\lambda = 1$ , and  $f_l = 0.4$ ). Using these scaling values, Table 2.1 shows the clock frequencies and the number of active cores across generations (G0 through G4) for PU, DSL, and SFU multicores.

Figure 2.1(a) shows that for serial workloads (s = 0.8), the active core count does not matter and DSL performs as well as PU. On the other hand, SFU performs worse due to its slower clock. However, serial workloads are unimportant for future multicores which are destined for servers where multi-threaded workload is the norm. As such, the speedups are low even for PU due to the highly-serial workload, placing SFU within normal range. Further, power is not a problem for such workloads which need only a few cores.

Fig. 2.1. Speedups across generations of PU, DSL, and SFU multicores over a four-core multicore (generation 0) for the following workloads: (a) mostly serial and memory-unintensive, (b) mostly serial, and memory-intensive, (c) mostly parallel and memory-unintensive, and (d) mostly parallel and memory-intensive

The same analysis holds for Figure 2.1(b) though the speedups are even lower compared to those of Figure 2.1(a) because of the higher impact of memory latency which does not scale.

In Figure 2.1(c) which shows parallel, memory-unintensive workloads, PU performs better than both DSL and SFU. However, DSL outperforms SFU because (1)

Fig. 2.2. Sensitivity to model parameters (speedup relative to generation 0, 4-core configuration) for the different values of m and s: (a) Variable memory intensity with s=0.01, (b) Variable parallelism with m=0.8

SFU's memory parallelism offers no advantage for memory-unintensive worklands and (2) DSL enjoys the benefit of added cores to compensate for SFU's added leakage, as mentioned in Section 2.2.2.

Finally, Figure 2.1(d) shows that for parallel, memory-intensive workloads, PU performs better than DSL for the same reason as Figure 2.1(c). Despite the lack of power constraints, PU does not achieve linear speedups with the number of cores due to the serial portions (Amdahl's Law effect). SFU performs better than DSL due to higher memory-level parallelism achieved by SFU's more, albeit slower, cores in the major parallel-memory component of this workload. Nevertheless, SFU does not fully close the gap between PU and DSL due to SFU's slower clock (Table 2.1) which affects both the serial-non-memory and parallel-non-memory components in the workload. I show in Section 3.5 that our real-world commercial and scientific workloads closely track Figure 2.1(d).

**Sensitivity to model parameters:** Figure 2.2 illustrates the sensitivity of SFU's speedups to the two parameters s and m. Figure 2.2(a) confirms that SFU remains faster than DSL with m as low as 0.5 which is well below the expected exposed miss

Table 2.2. Scaling factors relative to Gen0 (45nm)

| Parameter                   | Gen0 | Gen1 | Gen2 | Gen3 | Gen4 |

|-----------------------------|------|------|------|------|------|

| Tech Node (nm)              | 45   | 32   | 22   | 16   | 11   |

| $\operatorname{Clock}(c^i)$ | 1.00 | 1.10 | 1.19 | 1.25 | 1.30 |

| Vdd                         | 1.00 | 0.93 | 0.88 | 0.86 | 0.84 |

| Capacitance                 | 1.00 | 0.75 | 0.56 | 0.42 | 0.32 |

| Dyn. Power $(p^i)$          | 1.00 | 0.71 | 0.52 | 0.39 | 0.29 |

| SFU factor $(\alpha^i)$     | 1.00 | 0.70 | 0.48 | 0.32 | 0.22 |

latency given miss-rates (2%) and given current memory latency trends. Similarly, Figure 2.2(b) confirms that SFU performs better than DSL at s < 0.1. Note that with s >= 0.1 the Amdahl's speedup limit is 10X and thus serialization is a tighter bottleneck than the power constraint.

#### 2.3 Experimental Methodology

I run full-system simulations using Wisconsin GEMS [11] built on top of Simics [12]. I simulate SPARC-based multicores running Solaris 10.

Technology Scaling: While our main results use technology scaling parameters from the conservative projections for planar transistors by Borkar *et al.* [4], I also show some brief results using ITRS's more aggressive projections for FinFETs [13]. Based on Borkar's projections, Table 2.2 shows the improvement factors over 45nm technology node for clock frequency ( $c^i$  for the *ith* generation, in Section 2.2.2), supply voltage (Vdd), capacitance, and per-core power ( $p^i$ ). The table also shows SFU factors ( $\alpha^i$  in Section 2.2.2 where  $\alpha^i * p^i = 0.5^i$ ).

Multicore organization: I assume a tiled organization in which each multicore "tile" comprises a core, private L1 I- and D-caches using MESI coherence protocol, and a local bank of the shared, unified L2. The tiles are connected via an on-chip network with memory controllers at the network edges.

Core: While our baseline generation assumes in-order-issue, two-way SMT cores (line 1 in Table 2.3), I also show some brief results for out-of-order-issue cores. I use two-way SMT cores which are common in Intel designs to match our scaling numbers in Table 2.2 which are based on Intel designs [4]. Based on the per-core power and clock factors from Table 2.2, I list the number of active cores and the actual clock frequencies for PU, DSL and SFU in Table 2.4. While c and p are assumed to be constants in Section 2.2.2, Borkar's scaling assumes that the factors vary from one generation to the next (Table 2.2). Consequently, clock frequencies in Table 2.1 and Table 2.4 differ slightly.

Cache Capacity and Access Latency: I hold key parameters of the L1 cache and the per-core L2 bank (capacity, block size, associativity and access latency in cycles) constant across generations (lines 2 – 8 in Table 2.3). The aggregate L1 and L2 capacities double every generation as per Moore's Law. Though DSL keeps many of its cores powered down, it uses *all* of the shared L2 cache including the banks in the inactive cores' tiles (i.e., all three designs, PU, DSL, and SFU, have the same amount of L2 cache in each generation). Consequently, a deeper on-chip hierarchy (e.g., L3) will improve DSL and SFU to similar extents.

I conservatively assume that the access latencies in ns of L1 and L2 bank scale at the same rate as frequency improvement. Consequently the access latencies in cycles, stays constant across generations for PU, DSL, and SFU (line 8 in Table 2.3), though SFU's slower clock implies longer latencies in ns.

On-chip Network: I assume a dimension-order routed, 2D mesh network (line 9 in Table 2.3) which grows across generations (line 7 in Table 2.4). Our simulator models a simple 1-cycle router delay per hop where the link latency scales slower than logic due to the well-known wire-delay effects. Accordingly, I assume a modest 1-cycle increase in latency at Gen3 for PU, DSL, and SFU (line 8 in Table 2.4). Here again, SFU's slower clock implies longer latencies in ns.

DRAM Latency and Bandwidth (including impact of die-stacking): There are two sources of DRAM latency improvement: technology scaling every gen-

Table 2.3. Invariant parameters across generations

|    | Parameter                    | Values  |

|----|------------------------------|---------|

|    |                              |         |

| 1  | SMT contexts per core        | 2       |

| 2  | Private L1D size (KB)        | 64      |

| 3  | Private L1I size (KB)        | 64      |

| 4  | Private L1 associativity     | 4       |

| 5  | L1 access (cycles)           | 3       |

| 6  | Shared L2 associativity      | 32      |

| 7  | Shared L2 block size (bytes) | 64      |

| 8  | L2 bank (cycles)             | 17      |

| 9  | Network Topology             | 2D mesh |

| 10 | Channel width (bits)         | 64      |

| 11 | Mem. Ctrl. Queue (entries)   | 32      |

| 12 | Page mode                    | closed  |

Table 2.4. Parameter scaling with technology generations

|    | Parameter                    |      |      |      | Val  | ues  |                         |

|----|------------------------------|------|------|------|------|------|-------------------------|

|    |                              | Gen0 | Gen1 | Gen2 | Gen3 | Gen4 | Scaling Comments        |

| 1  | Number of cores (PU/SFU)     | 4    | 8    | 16   | 32   | 64   | 2X per gen              |

| 2  | Number of cores (DSL)        | 4    | 6    | 8    | 12   | 16   | Power-limited           |

| 3  | Clock (GHz) (PU/DSL)         | 3.2  | 3.52 | 3.81 | 4    | 4.16 | As per Table 2.2        |

| 4  | Clock (GHz) (SFU)            | 3.2  | 2.48 | 1.73 | 1.28 | 0.89 | As per Table 2.2        |

| 5  | Shared L2 size (MB)          | 4    | 8    | 16   | 32   | 64   | 2X per gen              |

| 6  | Shared L2 banks              | 4    | 8    | 16   | 32   | 64   | 2X per gen              |

| 7  | Network                      | 2x2  | 2x4  | 4x4  | 4x8  | 8x8  |                         |

| 8  | Link latency (cycles)        | 2    | 2    | 2    | 3    | 3    | Slower than $f$ scaling |

| 9  | Memory (DSL/PU) cycles       | 320  | 344  | 368  | 380  | 400  | 2% reduction per gen    |

| 10 | Memory (SFU) cycles          | 320  | 240  | 180  | 124  | 86   | 2% reduction per gen    |

| 11 | Number of DRAM banks         | 16   | 32   | 64   | 128  | 256  | 2X per gen              |

| 12 | Number of memory channels    | 1    | 2    | 4    | 8    | 16   | 2X per gen              |

| 13 | Number of instances (DSL)    | 1    | 1    | 2    | 4    | 4    | Problem size scaling    |

| 14 | Number of instances (SFU/PU) | 1    | 1    | 2    | 4    | 8    | Problem size scaling    |

Table 2.5. Workloads: Description and Characteristics

| Commercial Workloads                                                       | MPKI |

|----------------------------------------------------------------------------|------|

| SPECjbb: version 2005, Java-based 3-tier client/server system workload     | 7.1  |

| with emphasis on the middle tier. Java server VB version 1.5 with parallel |      |

| garbage collection. I simulate a system with 24 warehouses (~600 MB).      |      |

| Online Transaction Processing (OLTP): models database transactions of      | 5.1  |

| a wholesale parts supplier. I use PostgreSQL 8.3.7 database system and     |      |

| DBT-2 test suite which implements TPC-C benchmark. I use a database of     |      |

| 25,000 warehouses (~5GB). I simulate 128 concurrent database connections.  |      |

| Apache: version 2.2.9, a static web server workload with repository of     | 17.9 |

| 20,000 files (~500 MB). SURGE is used to generate web requests by simu-    |      |

| lating 1600 clients, each with 25ms think time between requests.           |      |

| Scientific Workloads (memory-intensive)                                    |      |

| FFT: is a Splash benchmark that computes Fourier transforms. I run the     | 10.2 |

| transpose computation of 4 Million complex numbers (~64 MB) for gener-     |      |

| ation 0 to 2 and 16 Million complex numbers for generation 3 and 4.        |      |

| canneal: is a Parsec benchmark that models cache-aware annealing to op-    | 4.0  |

| timize routing cost of a chip design. I use the native dataset (~100 MB).  |      |

| Systems for generations 0 to 2, 3 and 4 optimize 1, 2 and 4 chips respec-  |      |

| tively.                                                                    |      |

| Streamcluster: is a Parsec benchmark that performs online clustering of    | 4.8  |

| an input stream. I use 1 million 128-dimensional points, 5000 intermediate |      |

| centers (~100 MB) for generation 0 to 3 and and 2 million 128-dimensional  |      |

| points , 20000 intermediate centers (~ 275 MB) for generation 4.           |      |

eration and one-time move to 3-D die-stacking. I assume that the former yields the usual 2% per generation (optimistic estimate as trends indicate no improvement in DRAM latency [14]) and show the resultant memory latency in cycles for PU, DSL, and SFU in lines 9-10 in Table 2.4. I assume that the latter achieves the expected 30% latency reduction [5,15] which I evaluate in Section 2.4.3.

I assume that the number of DRAM banks (i.e., the internal DRAM bandwidth) doubles every generation, in line with the scaling of DRAM density (line 11 in Table 2.4). I assume closed page mode which works best for multi-threaded workloads (line 12 in Table 2.3) [16]. I show our main results assuming that processor-memory bandwidth (i.e., the number of memory channels) scales across generations (line 12 in Table 2.4). This assumption is in anticipation of the imminent deployment of 3-D stacking technology. Further, a recent paper [17] shows that compression and other

techniques can allow conventional pin bandwidth to scale beyond 100 cores, covering many future generations. Nevertheless, I include results constraining the number of memory channels in Section 2.4.3.

Leakage: As explained in Section 2.2.2, recent commercial microprocessors increase transistor threshold voltages and decrease transistor speeds to hold leakage at a constant 25-30% of the constant total power budget [10]. Consequently, the total dynamic power budget is also a constant. Borkar's conservative scaling, and therefore Table 2.2, include the effects of such adjustments. While our main results assume a chip leakage budget of 30% held constant across generations (i.e., l = 0.3 and  $\lambda = 1$ ), I also show brief results for leakage growing from 30% to 50% across our four generations (i.e., l = 0.3 and  $\lambda = 1.15$ ). Based on our reasons in Section 2.2.2, I assume that 40% of the chip leakage is in the cores (i.e.,  $f_l = 0.4$ ).