## Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

Fall 2014

# Material and device aspects of semiconducting two-dimensional crystals

Han Liu Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Liu, Han, "Material and device aspects of semiconducting two-dimensional crystals" (2014). *Open Access Dissertations*. 324. https://docs.lib.purdue.edu/open\_access\_dissertations/324

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

| By_   | Han Liu          |                                                         |

|-------|------------------|---------------------------------------------------------|

| Enti  | tled             |                                                         |

| ΜΑΊ   | FERIAL AND DE    | VICE ASPECTS OF SEMICONDUCTING TWO-DIMENSIONAL CRYSTALS |

| For   | the degree of    | Doctor of Philosophy                                    |

| Is ap | pproved by the f | nal examining committee:                                |

| Pe    | ide D. Ye        |                                                         |

| Ма    | rk S. Lundstrom  |                                                         |

| Mu    | hammad A. Ala    | n                                                       |

| Yo    | ng P. Chen       |                                                         |

|       |                  |                                                         |

To the best of my knowledge and as understood by the student in the *Thesis/Dissertation Agreement*. *Publication Delay, and Certification/Disclaimer (Graduate School Form 32)*, this thesis/dissertation adheres to the provisions of Purdue University's "Policy on Integrity in Research" and the use of copyrighted material.

| Peide D. Ye                     |            |

|---------------------------------|------------|

| Approved by Major Professor(s): |            |

|                                 |            |

| Approved by: Michael R. Melloch | 08/11/2014 |

Head of the Department Graduate Program

Date

## MATERIAL AND DEVICE ASPECTS OF SEMICONDUCTING

## TWO-DIMENSIONAL CRYSTALS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Han Liu

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2014

Purdue University

West Lafayette, Indiana

To my parents, Dajian Liu and Bingyi Pan

#### ACKNOWLEDGMENTS

First and foremost, I would like express my deepest gratitude to my thesis advisor, Prof. Peide D. Ye. Looking back to the day I arrived at Purdue, every single step of my progress I have made in the past years is with his continuous support and efforts. He is one of the smartest people I have ever met in my pursuit of knowledge. His kind and cheerful demeanor has been an inspiring guidance to my life. Remarkably, I was fully impressed by his encouragement for the students to explore a range of new topics. I have been very fortunate to have been part of his illustrious research group. The years with his group has been an enjoyable experience in my life.

I would also like to express my sincere gratitude to Prof. Mark S. Lundstrom, Prof. Muhammad A. Alam and Prof. Yong P. Chen, who have been serving as my committee members. I have been greatly benefited from their experimental help and valuable discussions during my graduate study at Purdue.

I am indebted to Prof. Xianfan Xu, Prof. Jun Lou (Rice University), Prof. David Tománek (Michigan State University) and Prof. Lance Li (Academia Sinica) for their support in experiments and simulations. I really enjoy the collaborations.

I have been fortunate to have the support of all my group members I have been working with: Dr. Min Xu, Dr. Jiangjiang Gu, Dr. Chen Wang, Dr. Lin Dong, Dr. Xuefei Li, Dr. Adam T. Neal, Kun Xu, Nathan J. Conrad, Heng Wu, Jingyun Zhang, Mengwei Si, Yuchen Du, Hong Zhou, Lingming Yang, Yexin Deng and Wei Luo. It has been a good memory for me to share the years with you at Purdue.

Finally, no words would ever do justice to express my deepest thanks and gratitude to my parents and my family. Their unconditional love, tolerance, sacrifice and encouragement have been the best supports in my life ever.

## TABLE OF CONTENTS

|     |      |                                                                                    | Page |

|-----|------|------------------------------------------------------------------------------------|------|

| LIS | ST O | F TABLES                                                                           | vi   |

| LIS | ST O | F FIGURES                                                                          | vii  |

| AF  | BBRE | VIATIONS                                                                           | х    |

| AE  | BSTR | ACT                                                                                | xii  |

| 1   | INTI | RODUCTION                                                                          | 1    |

|     | 1.1  | Scaling of Si MOSFETs                                                              | 1    |

|     | 1.2  | Semiconducting 2D Crystals                                                         | 2    |

|     | 1.3  | $MoS_2$ Transistors: Opportunities and Challenges                                  | 5    |

|     | 1.4  | Main Achievements                                                                  | 6    |

| 2   | INTI | EGRATION of HIGH-K DIELECTRIC ON 2D CRYSTALS                                       | 8    |

|     | 2.1  | Introduction                                                                       | 8    |

|     | 2.2  | Growth Mechanism of ALD                                                            | 9    |

|     | 2.3  | ALD Growth on 2D Crystals                                                          | 10   |

|     | 2.4  | Summary                                                                            | 18   |

| 3   | N-TY | YPE $MOS_2$ TRANSISTORS AND DIMENSION SCALING                                      | 19   |

|     | 3.1  | N-type Double-Gate $MoS_2$ Transistors $\ldots \ldots \ldots \ldots \ldots \ldots$ | 19   |

|     | 3.2  | Channel Length Scaling of $MoS_2$ Transistors $\ldots \ldots \ldots \ldots \ldots$ | 24   |

|     | 3.3  | Channel Width Scaling of $MoS_2$ Transistors $\ldots \ldots \ldots \ldots \ldots$  | 34   |

|     | 3.4  | Summary                                                                            | 40   |

| 4   | MET  | CAL CONTACTS ON 2D SEMICONDUCTORS                                                  | 42   |

|     | 4.1  | Contact Resistance on $MoS_2$                                                      | 42   |

|     | 4.2  | Metal Contacts on $WSe_2$                                                          | 47   |

|     | 4.3  | Fermi-level Pinning at Metal/2D Interface                                          | 52   |

|     | 4.4  | Summary                                                                            | 56   |

Page

| 5  | DEVICE PERFORMANCE AND SWITCHING MECHANISM IN CVD $MOS_2$ TRANSISTORS |                                                                              |     |  |

|----|-----------------------------------------------------------------------|------------------------------------------------------------------------------|-----|--|

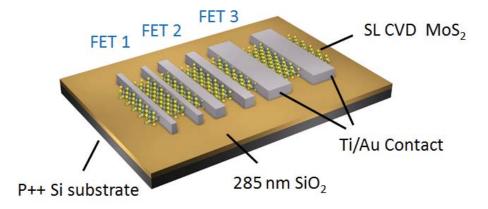

|    | 5.1                                                                   | CVD Synthesis of Single Layer $MoS_2$ Crystals $\ldots \ldots \ldots \ldots$ | 57  |  |

|    | 5.2                                                                   | Device Characteristics in $MoS_2$ Transistors on Single Layer CVD Crystals   | 59  |  |

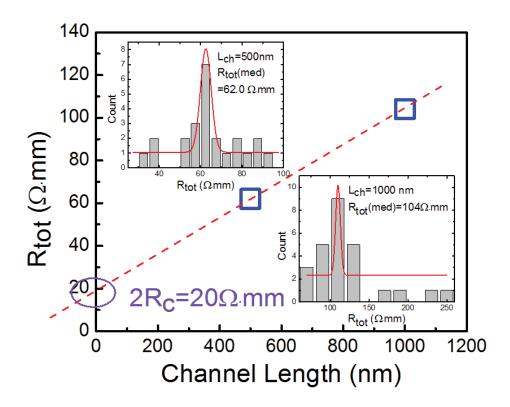

|    | 5.3                                                                   | Extraction of $R_c$ in Single Layer CVD MoS <sub>2</sub> Transistors         | 66  |  |

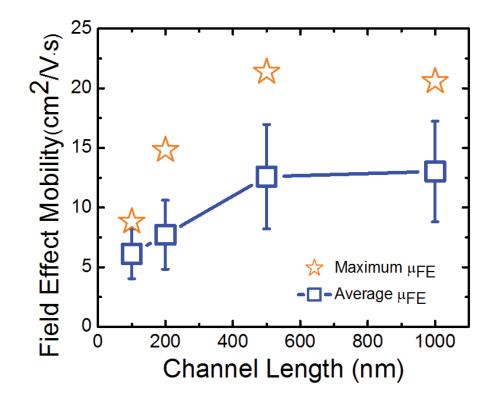

|    | 5.4                                                                   | Field Effect Mobility in Single Layer CVD $MoS_2$ Transistors $\ldots$       | 70  |  |

|    | 5.5                                                                   | Transfer length in CVD $MoS_2$ Transistors                                   | 74  |  |

|    | 5.6                                                                   | Switching mechanism in single layer CVD $\mathrm{MoS}_2$ transistors         | 82  |  |

|    | 5.7                                                                   | Summary                                                                      | 87  |  |

| 6  | PHC                                                                   | SPHORENE: A NOVEL P-TYPE 2D SEMICONDUCTOR                                    | 89  |  |

|    | 6.1                                                                   | Crystal and Band Structures of Black Phosphorus and Phosporene .             | 89  |  |

|    | 6.2                                                                   | Evolution of Optical Characteristics of Single to Few-layer Phosphorene      | 91  |  |

|    | 6.3                                                                   | Transport Properties in Few-layer Phosphorene                                | 94  |  |

|    | 6.4                                                                   | Device Performance of Phosphorene Transistors                                | 100 |  |

|    | 6.5                                                                   | CMOS Logic based on All-2D Channel Materials                                 | 103 |  |

|    | 6.6                                                                   | Summary                                                                      | 104 |  |

| 7  | CON                                                                   | ICLUSIONS                                                                    | 107 |  |

| LI | ST O                                                                  | F REFERENCES                                                                 | 109 |  |

| VI | TA                                                                    |                                                                              | 117 |  |

| Ρl | JBLI(                                                                 | CATIONS                                                                      | 118 |  |

## LIST OF TABLES

| Tabl | e                                                                                                                                                   | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | Binding Energy $(E_{ads} = E_a + E_b - E_{ab})$ in kcal/mol                                                                                         | 13   |

| 2.2  | Atomic charges, polarizabilities, and frontier molecular orbital levels of the interaction atoms in $H_2O$ , TMA, h-BN, and $MoS_2$ in atomic unit. | 15   |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                       | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

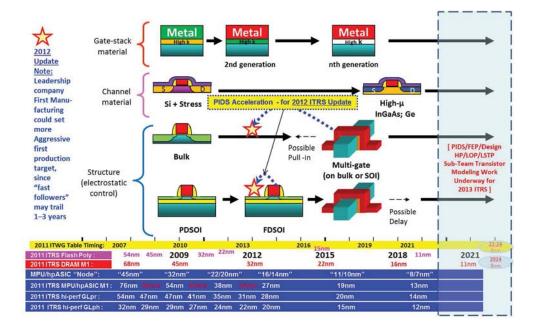

| 1.1  | Scaling trend of Si MOSFETs from ITRS 2012                                                                                                                                                                                               | 2    |

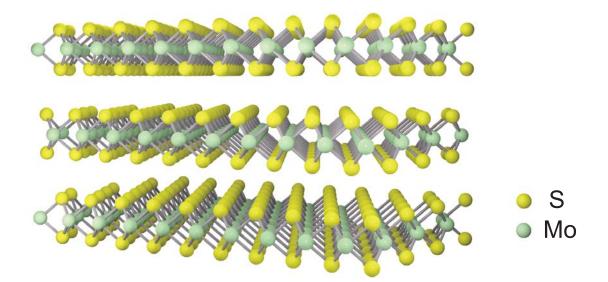

| 1.2  | Crystal structure of $MoS_2$                                                                                                                                                                                                             | 3    |

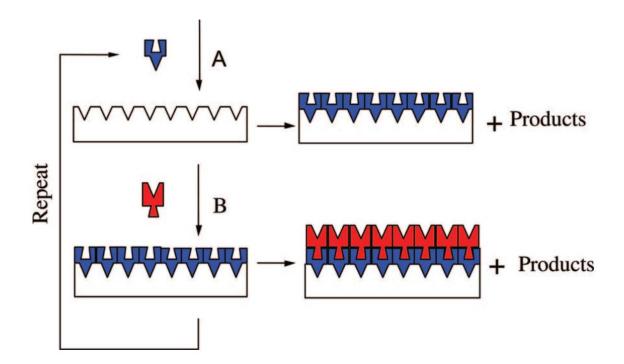

| 2.1  | A schematic illustration of ALD growth mechanism $[45]$                                                                                                                                                                                  | 9    |

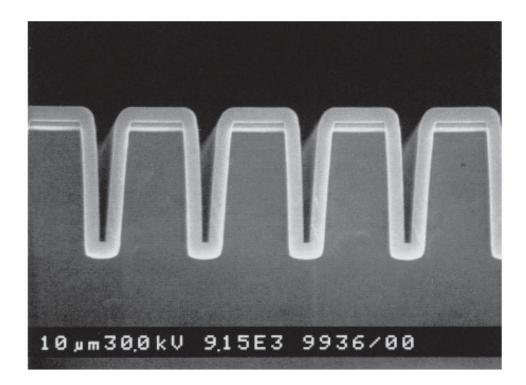

| 2.2  | Cross-sectional SEM image of an $Al_2O_3$ ALD film with a thickness of 300 nm on a Si wafer with a trench structure [46] $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                     | 10   |

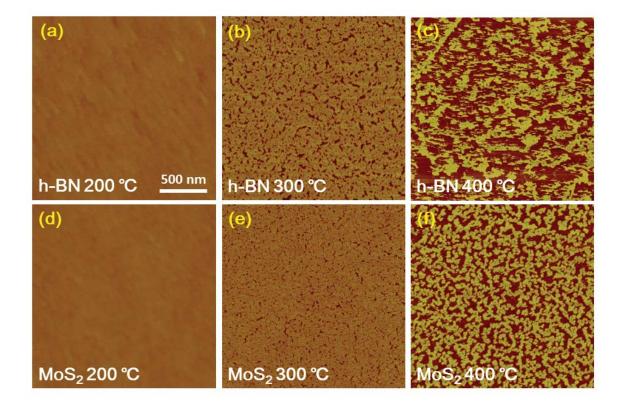

| 2.3  | AFM images of h-BN or $MoS_2$ surface after 111 cycles of ALD $Al_2O_3$ at 200 °C, 300 °C and 400 °C                                                                                                                                     | 11   |

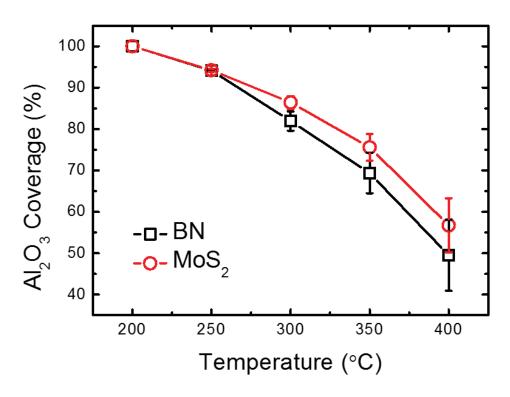

| 2.4  | $\mathrm{Al}_2\mathrm{O}_3$ coverage estimation from MATLAB analysis by Otsu method                                                                                                                                                      | 12   |

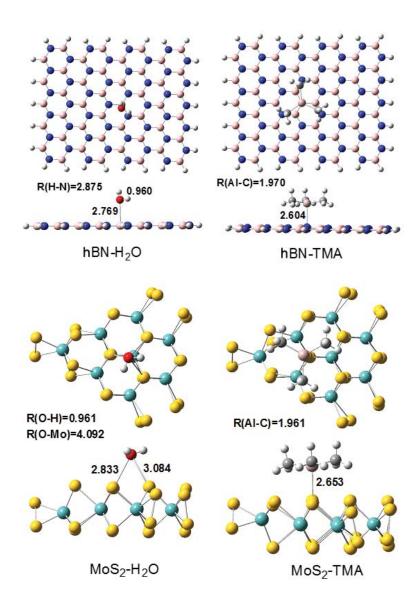

| 2.5  | Binding structure models of $\mathrm{H_2O}$ and TMA on h-BN and $\mathrm{MoS}_2$                                                                                                                                                         | 14   |

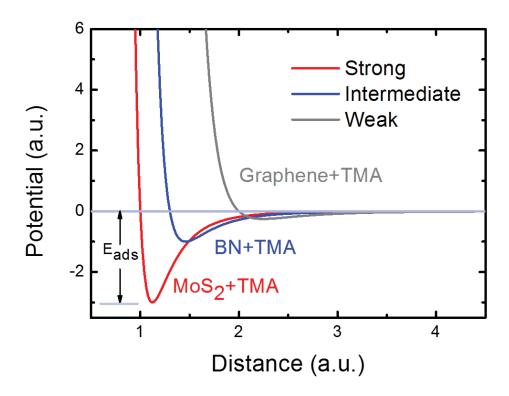

| 2.6  | An illustrative Lennard-Jones potential Model for physical adsorption at 2D crystal surfaces                                                                                                                                             | 17   |

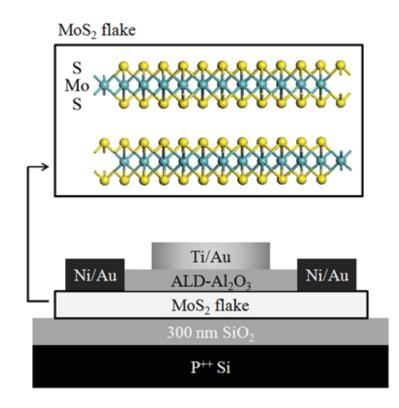

| 3.1  | Device structure of $MoS_2$ double gate MOSFET                                                                                                                                                                                           | 20   |

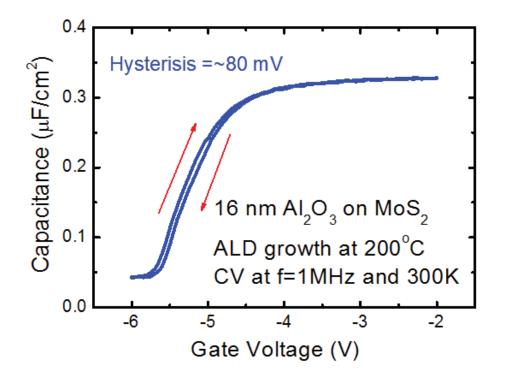

| 3.2  | 1 MHz high-frequency C-V characteristic of the MOSFET device measured at room temperature in darkness                                                                                                                                    | 21   |

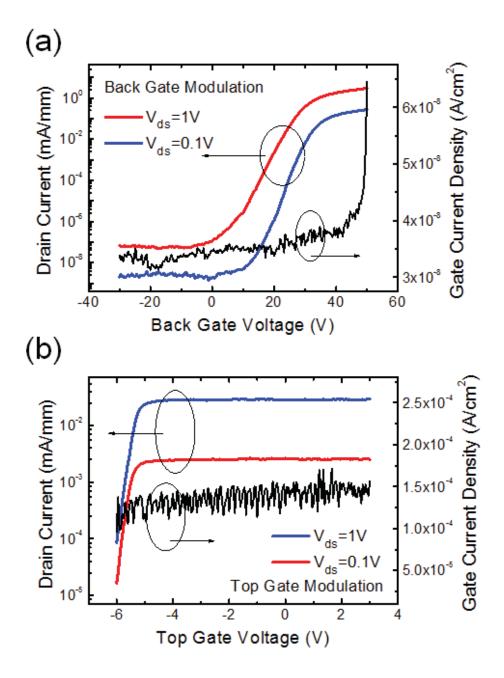

| 3.3  | Transfer characteristics of the $MoS_2$ double gate MOSFET from back-gate<br>and top-gate controls with leakage current density from 300 nm SiO <sub>2</sub> and<br>16 nm $Al_2O_3$                                                      |      |

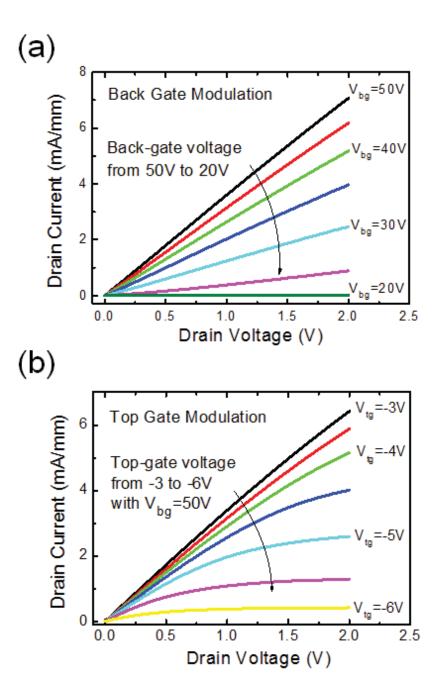

| 3.4  | Output characteristics of the $MoS_2$ double gate MOSFET from back-gate and top-gate controls                                                                                                                                            | 24   |

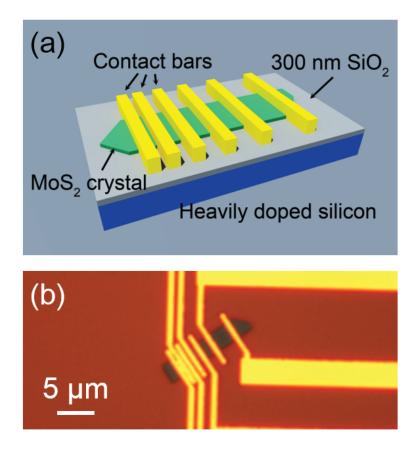

| 3.5  | Schematic diagram and optical image of the back-gated $MoS_2$ MOSFETs with various channel length $\ldots \ldots \ldots$ | 25   |

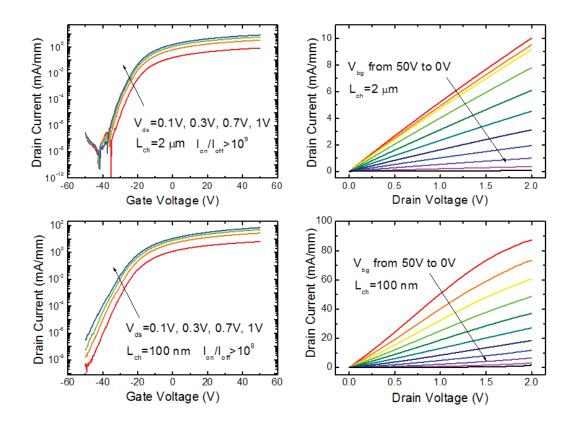

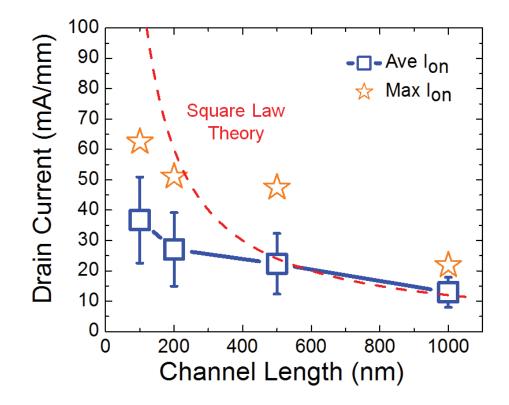

| 3.6  | Device performance of long channel and short channel $MoS_2$ transistors                                                                                                                                                                 | 26   |

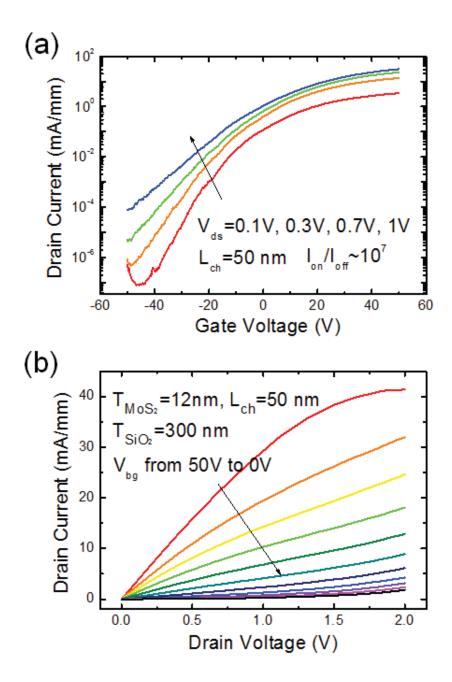

| 3.7  | Device performance of the $\mathrm{MoS}_2$ transistors of 50 nm channel length                                                                                                                                                           | 29   |

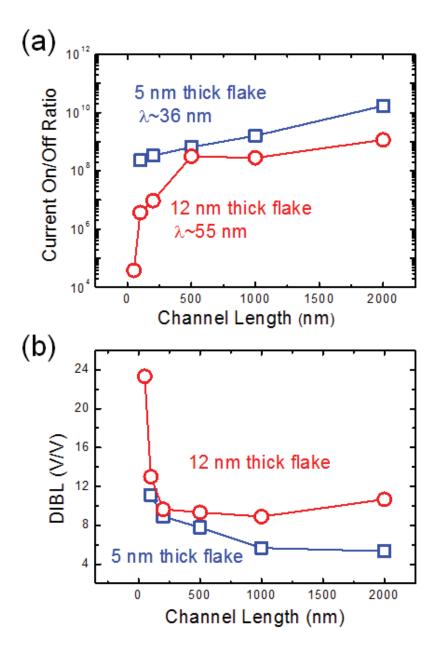

| 3.8  | Current on/off ratio and DIBL in $MoS_2$ transistors at various channel<br>length                                                                                                                                                        | 30   |

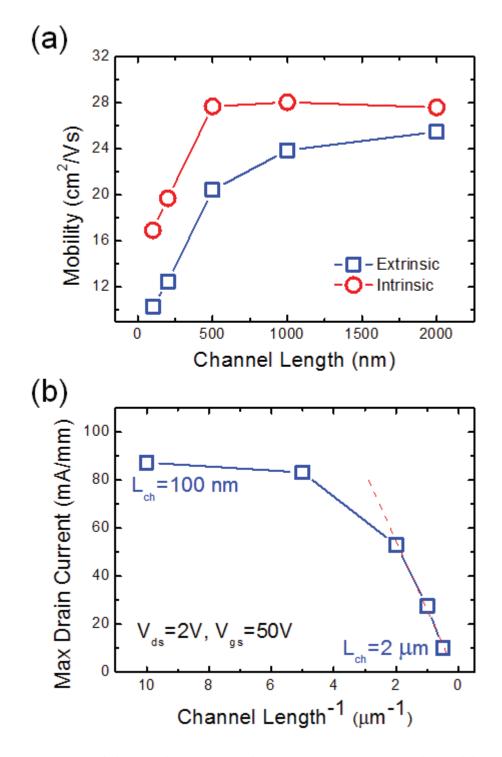

| 3.9  | Mobility and maximum drain current at various channel length $\ldots$ .                                                                                                                                                                  | 33   |

| Figu | re                                                                                      | Page |

|------|-----------------------------------------------------------------------------------------|------|

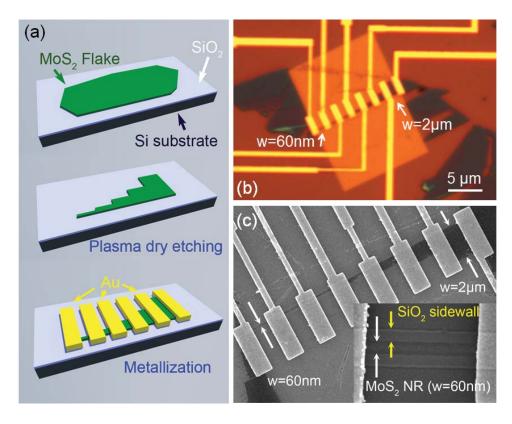

| 3.10 | Fabrication process and device images of $MoS_2$ transistors with various channel width | 35   |

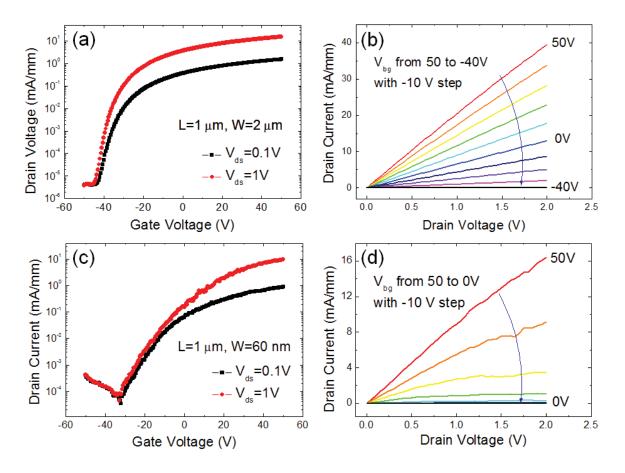

| 3.11 | Transfer and output characteristics of 2 $\mu$ m and 60 nm channel width devices        | 36   |

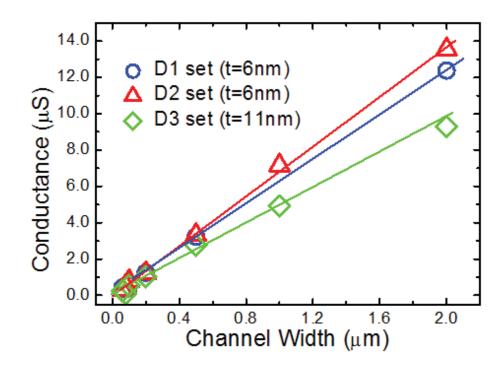

| 3.12 | Channel conductance of all sets of devices versus channel width $\ldots$                | 38   |

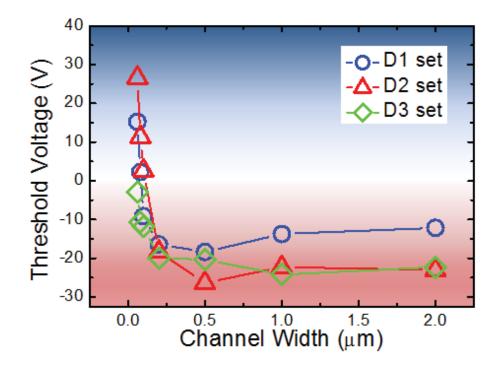

| 3.13 | Threshold voltage of all sets of devices versus channel width $\ldots$ .                | 39   |

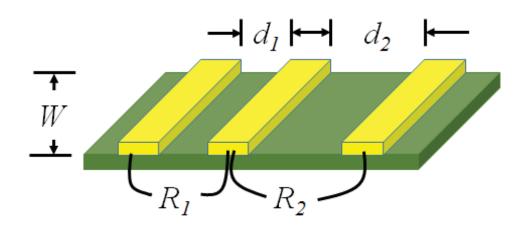

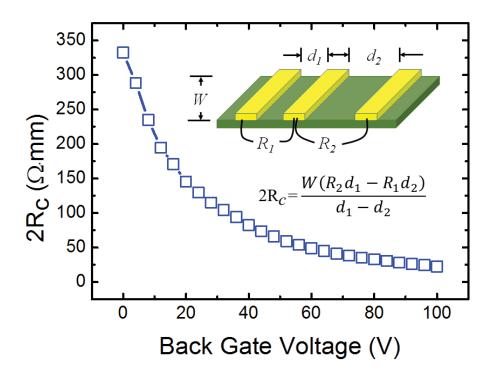

| 4.1  | Illustrative picture of transmission line method                                        | 42   |

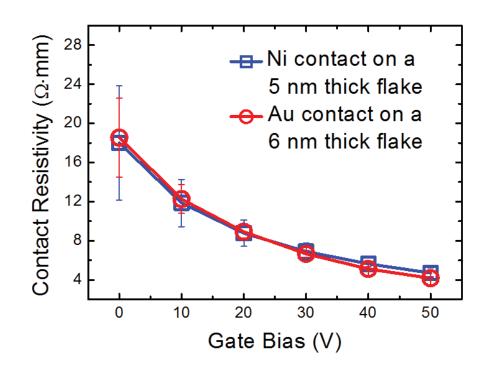

| 4.2  | Gate voltage dependent contact resistance of Ni and Au on $\mathrm{MoS}_2$              | 43   |

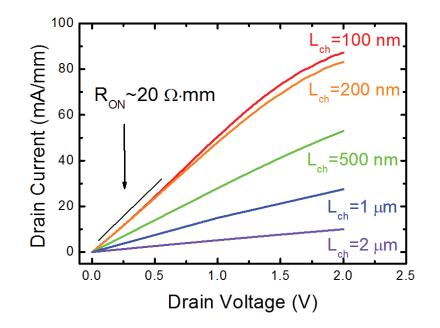

| 4.3  | Output curves at the same 50 V gate bias with different channel length                  | 45   |

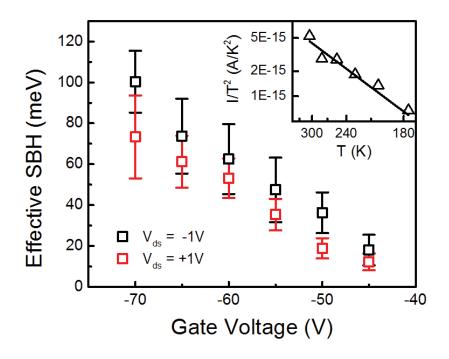

| 4.4  | Effective Schottky barrier height $\rm Ni/MoS_2$ as a function of back gate voltage     | 47   |

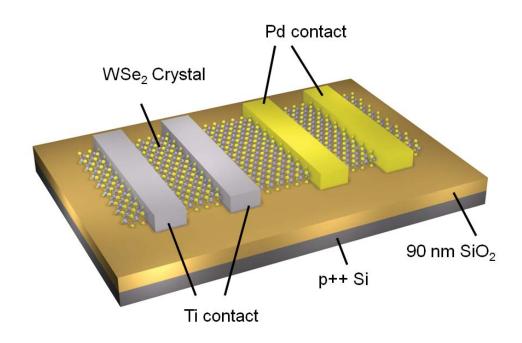

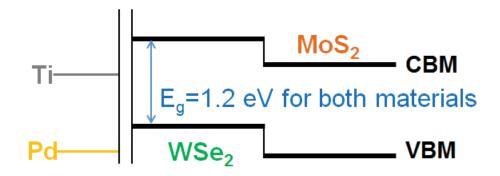

| 4.5  | Schematic image of $WSe_2$ devices with Ti and Pd contacts $\ldots \ldots$              | 48   |

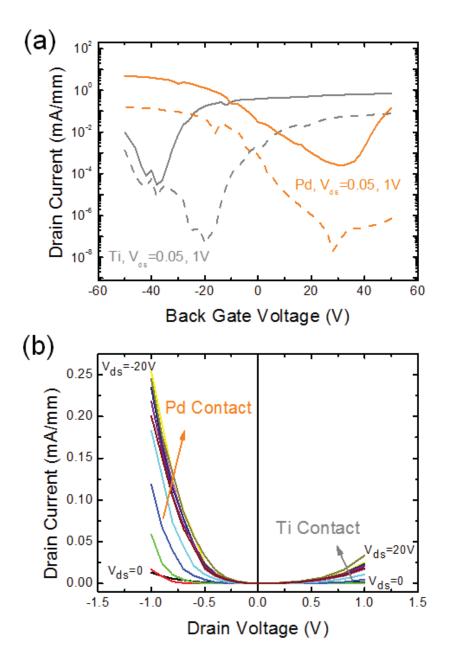

| 4.6  | Band edge alignment for Ti and Pd contacts on $\mathrm{MoS}_2$ and $\mathrm{WSe}_2$     | 49   |

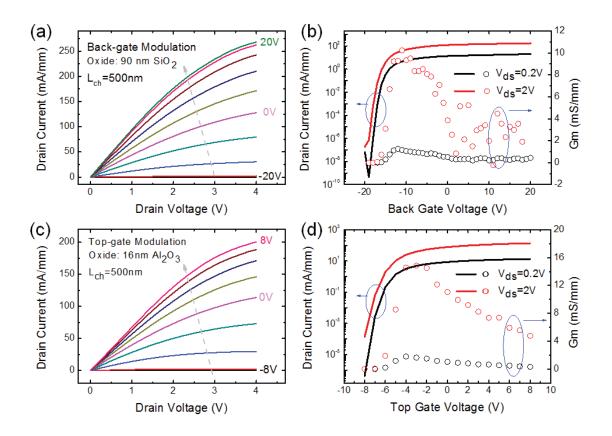

| 4.7  | Device characteristics for Ti and Pd contacted $WSe_2$ transistor                       | 50   |

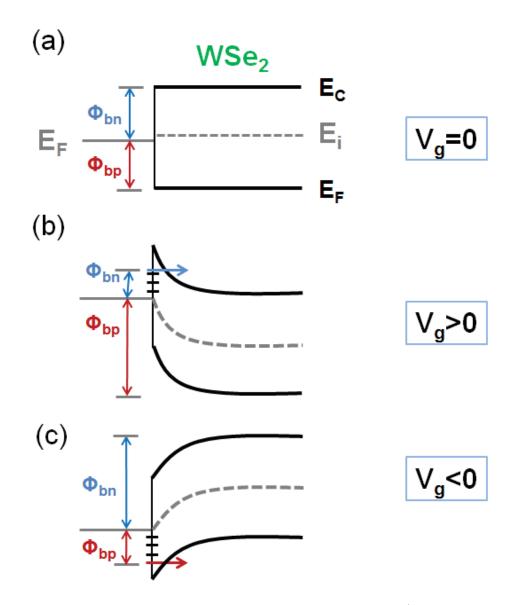

| 4.8  | Schematic diagram of carrier transport at metal/WSe $_2$ interface                      | 51   |

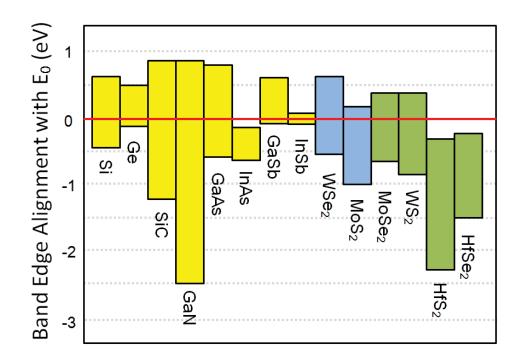

| 4.9  | Band edge alignment of conventional semiconductors and layered semicon-<br>ductors      | 53   |

| 4.10 | High performance $MoS_2$ transistor with low work-function Ti contacts .                | 55   |

| 5.1  | CVD setup for $MoS_2$ growth                                                            | 58   |

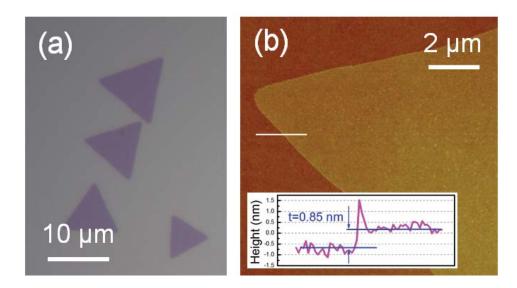

| 5.2  | Optical and AFM image of CVD single layer $MoS_2$ crystal $\ldots \ldots$               | 59   |

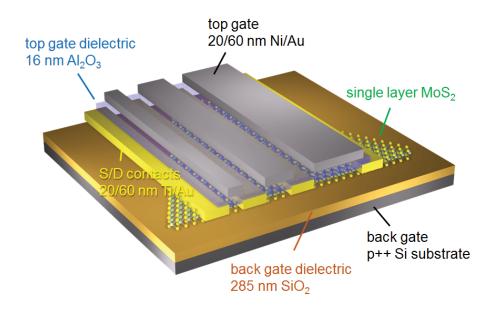

| 5.3  | Double gate device structure on CVD single layer $MoS_2$ crystal $\ldots$               | 60   |

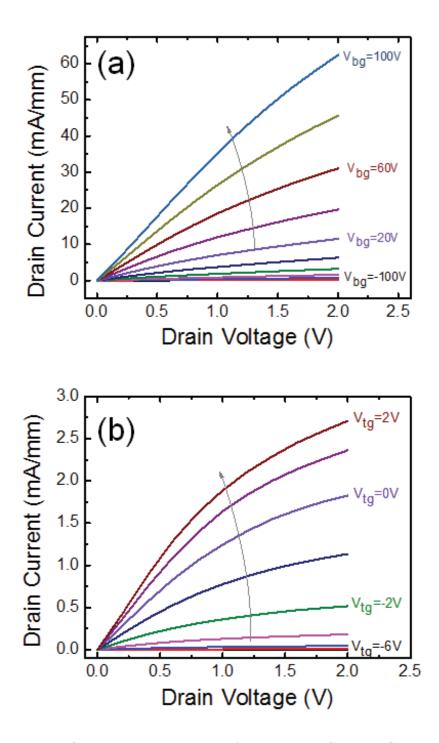

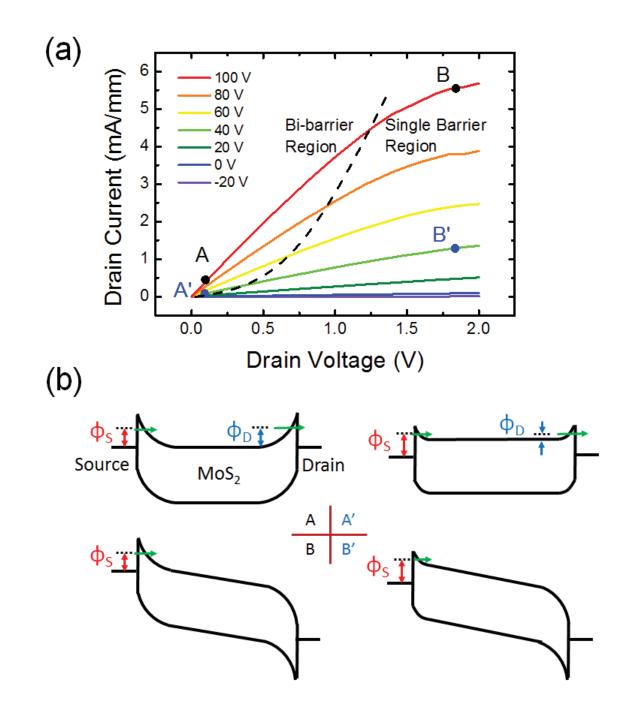

| 5.4  | Output characteristics of single layer CVD $MoS_2$ transistors $\ldots \ldots$          | 62   |

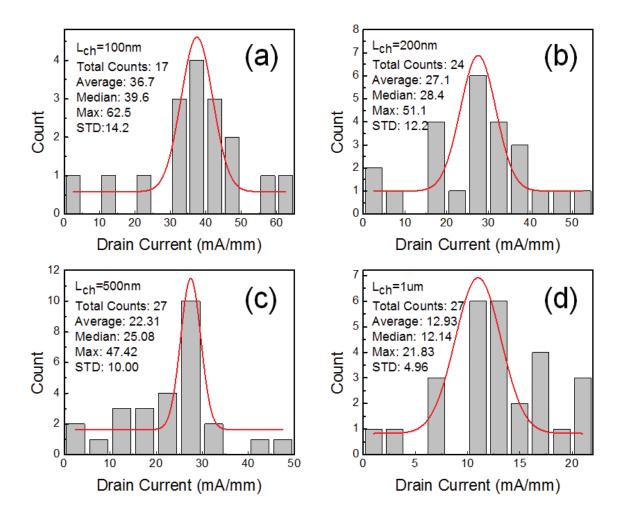

| 5.5  | Maximum drain current distributions of the devices with various channel length          | 64   |

| 5.6  | Averaged values of maximum drain current at all channel lengths                         | 65   |

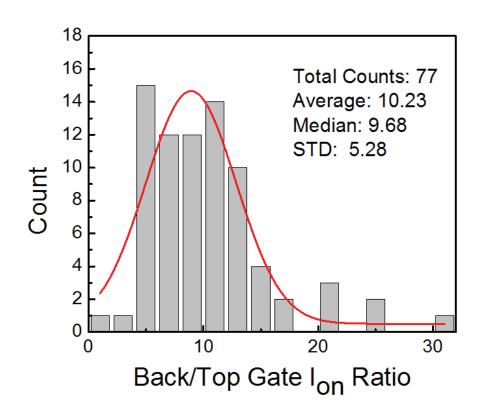

| 5.7  | Distribution of on-current ratio from back/top gate devices                             | 67   |

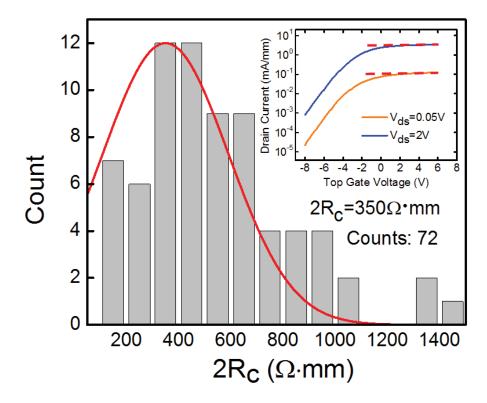

| 5.8  | Intrinsic contact resistance distribution in all top-gated $MoS_2$ devices .            | 68   |

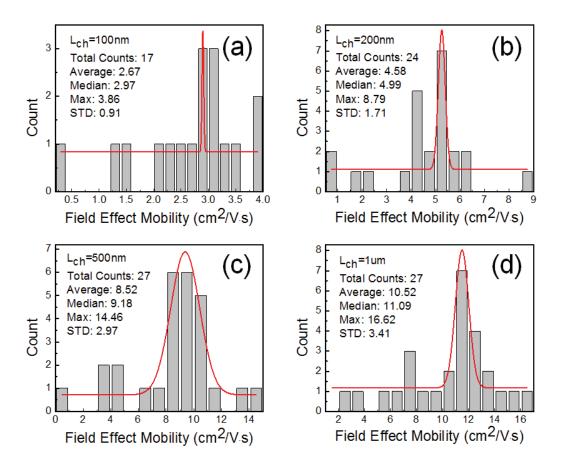

| 5.9  | Extrinsic field-effect mobility distributions in devices with various channel length    | 71   |

| 5.10 | Contact resistance on CVD single layer $MoS_2$ at various gate bias $\ldots$            | 72   |

| 5.11 | Saturation of contact resistance on CVD single layer $MoS_2$ at $V_{gs} = 100 V$        | 73   |

| Figu | re                                                                                                                                                                                                                        | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.12 | Intrinsic field effect mobility in $MoS_2$ transistors at various gate length                                                                                                                                             | 74   |

| 5.13 | $MoS_2$ transistors with various contact length                                                                                                                                                                           | 74   |

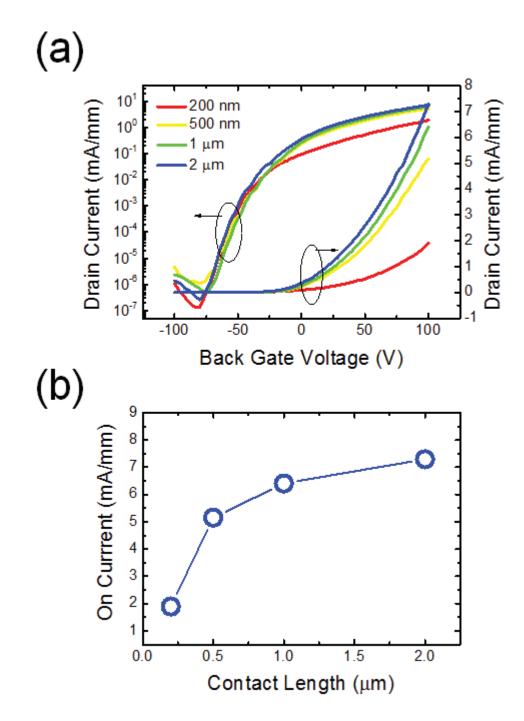

| 5.14 | Transfer characteristics and maximum drain current in $MoS_2$ transistors<br>with various contact length $\ldots \ldots \ldots$                            | 76   |

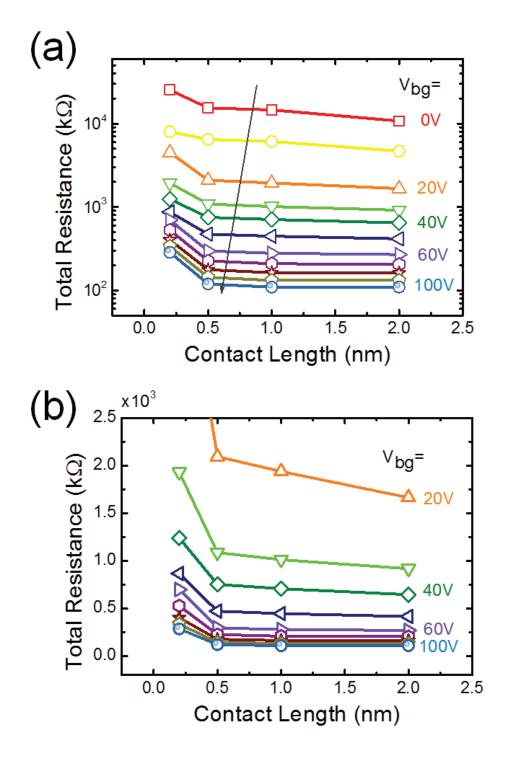

| 5.15 | Gate dependent total resistance in $MoS_2$ transistors with various contact length $\ldots \ldots \ldots$ | 78   |

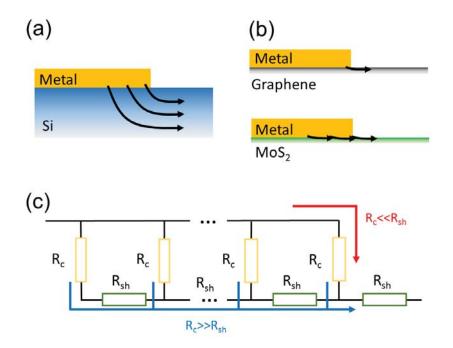

| 5.16 | Current flow path in metal/semiconductor junction $\ldots \ldots \ldots \ldots$                                                                                                                                           | 79   |

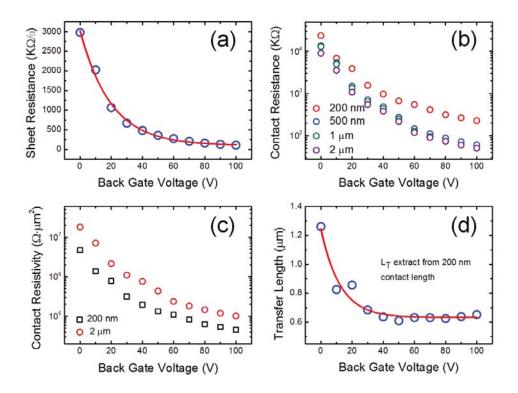

| 5.17 | Gate dependent sheet resistance, contact resistance, contact resistivity and transfer length                                                                                                                              | 81   |

| 5.18 | Schematic of switching mechanism in CVD $MoS_2$ transistors                                                                                                                                                               | 85   |

| 6.1  | Equilibrium structure of black phosphorus                                                                                                                                                                                 | 90   |

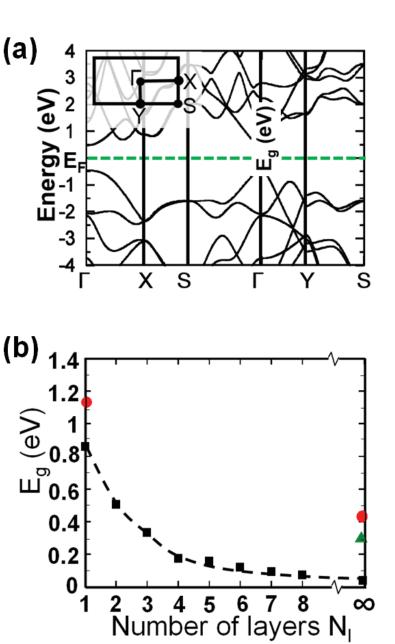

| 6.2  | Band structure and band gap evolution in phosphorene and few-layer black phosphorus                                                                                                                                       | 92   |

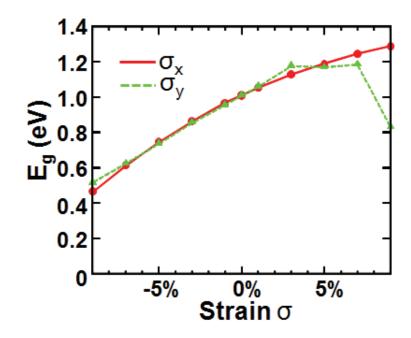

| 6.3  | Strain along the x- and y-direction related band gap evolution within single layer phosphorene                                                                                                                            | 93   |

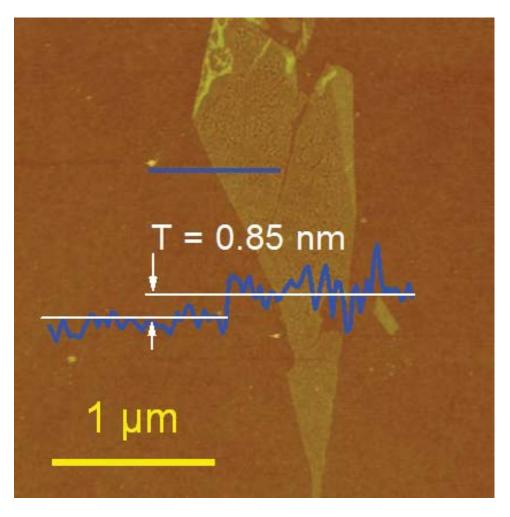

| 6.4  | AFM image of a single layer phosphorene                                                                                                                                                                                   | 94   |

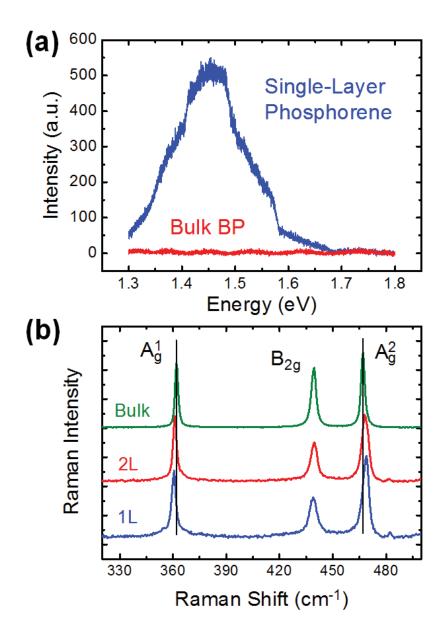

| 6.5  | PL and Raman spectra of single to few layer phosphorene                                                                                                                                                                   | 95   |

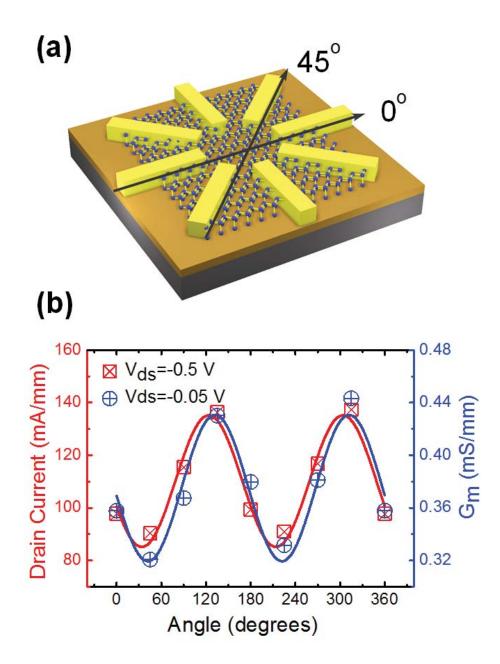

| 6.6  | Anisotropic transport in few-layer phosphorene                                                                                                                                                                            | 96   |

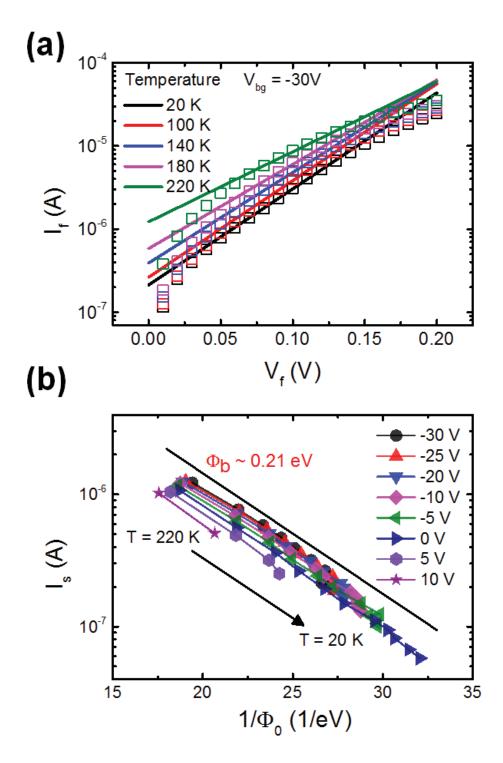

| 6.7  | Schottky barrier determination of Ti/black phosphorus junction $\ldots$                                                                                                                                                   | 98   |

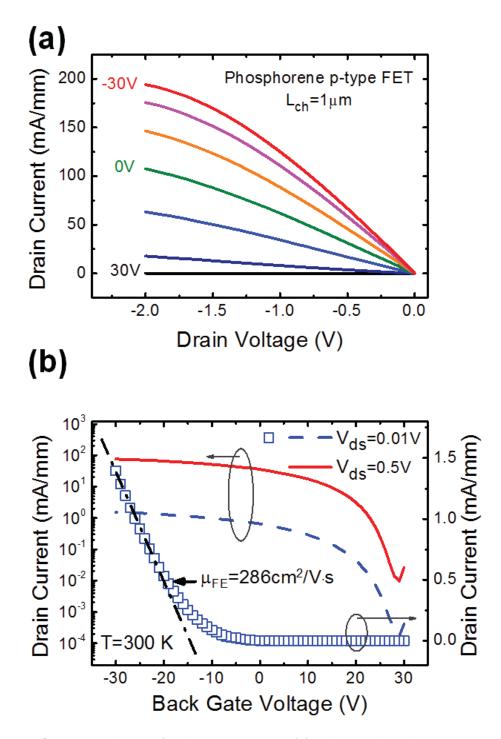

| 6.8  | Output and transfer characteristics of few-layer phosphorene transistors                                                                                                                                                  | 100  |

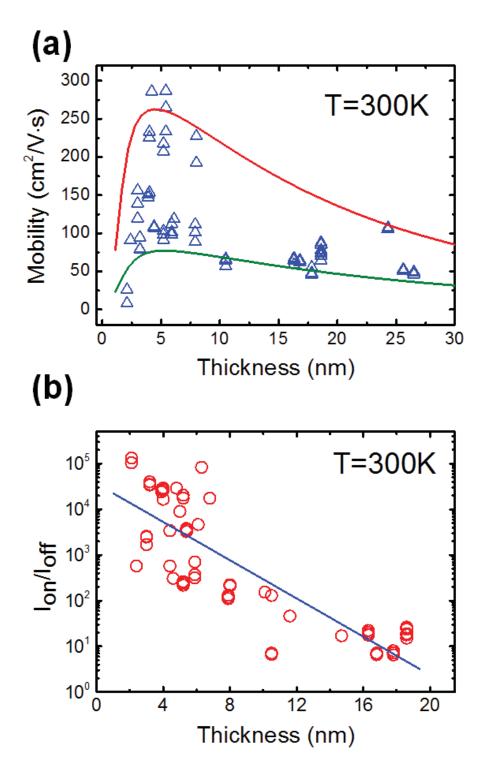

| 6.9  | Channel thickness dependent field-effect mobility and current on/off ratio<br>in phosphorene transistors                                                                                                                  | 105  |

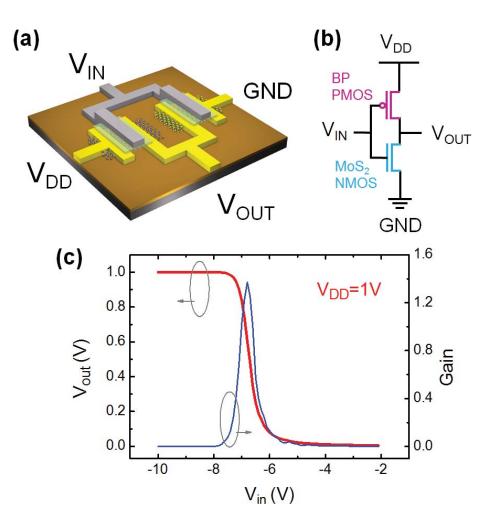

| 6.10 | CMOS inverter based on 2D channel materials                                                                                                                                                                               | 106  |

### ABBREVIATIONS

| TMD    | transition metal dichalcogenides                  |

|--------|---------------------------------------------------|

| SCE    | short channel effect                              |

| MOSFET | metal-oxide-semiconductor field-effect transistor |

| ALD    | atomic layer deposition                           |

| FLP    | Fermi-level pinning                               |

| CVD    | chemical vapor deposition                         |

| CMOS   | complimentary metal-oxide-semiconductor           |

| EOT    | equivalent oxide thickness                        |

| CNT    | carbon nanotube                                   |

| SS     | subthreshold swing                                |

| S/D    | source/drain                                      |

| UTB    | ultra-thin body                                   |

| EOT    | equivalent oxide thickness                        |

| h-BN   | hexagonal boron nitride                           |

| TMA    | trimethylaluminum                                 |

| AFM    | atomic force microscope                           |

| SEM    | scanning electron microscope                      |

| DFT    | density function theory                           |

| NEGF   | non-equilibrium Green function                    |

| CNL    | charge neutrality level                           |

| DIBL   | drain induced barrier lowering                    |

| BOE    | buffered oxide etchant                            |

| TLM    | transmission line method                          |

| SBH    | Schottky barrier height                           |

- MBE molecular beam epitaxy DIBN drain induced barrier narrowing

- PL photoluminescence

- VTC voltage transfer characteristics

#### ABSTRACT

Liu, Han Ph.D., Purdue University, December 2014. Material and Device Aspects of Semiconducting Two-Dimensional Crystals. Major Professor: Peide D. Ye.

Two-dimensional (2D) crystals have attracted much attention in recent years due to their unique physical, chemical, and mechanical properties. Semiconducting 2D crystals with van der Waals structures, such as transition metal dichalcogenides, are considered promising candidates for future device applications, as many have large band gaps, high carrier mobilities, and enable devices with immunity to short channel effects in addition to compatibility with silicon CMOS processes.

In this thesis, the fundamental device implications of using semiconducting 2D crystals are investigated. This includes: 1) the optimization of device fabrication processing for better device performance, 2) comparing the device physics in 2D semiconductors based transistors and silicon MOSFET, and 3) circuit-level integration of devices using 2D semiconductors. A direct atomic layer deposition process was developed and investigated on various 2D crystals which allowed for the development of 2D semiconductor transistors. N-type MoS<sub>2</sub> transistors with top and back gates were fabricated. The device performance of MoS<sub>2</sub> transistors with various channel lengths down to 50 nm was studied. Metal contacts on MoS<sub>2</sub> and other TMD materials were also studied. They showed a strong Fermi-level pinning at the metal MoS<sub>2</sub> interface. Device performance based on single layer CVD MoS<sub>2</sub> channel was studied and the device on/off switching was revealed to be dominated by Schottky barriers at metal contacts. Finally, the transport properties and device performance of p-type phosphorene crystals were investigated. Semiconducting 2D crystals are very promising candidates for future electronic and optoelectronic device applications.

#### 1. INTRODUCTION

This chapter provides an introduction to the motivation of research on 2D crystals, the current status of device research on 2D crystals, and key findings in this thesis.

#### 1.1 Scaling of Si MOSFETs

In the past several decades, the development of semiconductor industry has tremendously changed the lifestyles of human beings. The size of our electronic devices, such as cellphones, laptops, tablets, is getting smaller, while more functionalities are implanted. This is benefited from the more advanced fabrication techniques, where more transistors can be integrated in one chip. This trend was predicted early in the 1960s by Gordon Moore, one of the co-founder of the Intel Corporation. The "Moore's Law", described as "the number of transistors on integrated circuits doubles approximately every two years", has been serving as the guideline of semiconductor industry in the past fifty years. The number of transistors in a processor has been ramped up from 2,300 with a feature size ~10  $\mu$ m (Intel 4004, 1969) to 5 billions with a feature size down to 22 nm (Intel Core i7, 2013).

As the feature size of silicon transistors is approaching the quantum limit, new approaches have been made to further extend the "Moore's Law". Figure 1.1 shows the process technologies as we continue the pace in scaling down of the transistors from the ITRS road map. [1] Three changes have been made on the device level. The first change is the gate stack, where metal gate and high-k dielectric has replaced conventional poly-Si/SiO<sub>2</sub>. This decreases equivalent oxide thickness (EOT) while maintain similar physical oxide thickness to restrain leakage current. Second, the device structure has been changed from planar devices to 3D transistors, or FinFETs, to enhance the electrostatic control. The third change comes from the substitution

Fig. 1.1. Scaling trend of Si MOSFETs from ITRS 2012

of channel material. Given the ITRS prediction, Ge and InGaAs will replace stressed silicon in 2018, due to their higher carrier mobilities than those in silicon.

#### 1.2 Semiconducting 2D Crystals

The layered material family has provided more options to the channel material for future electronics. The typical example of 2D material is graphene, first discovered in 2004, and has been demonstrated with ultra-high carrier mobility up to 200,000  $\text{cm}^2/\text{V}\cdot\text{s}$ . [2,3] However, the absence of a band gap in graphene limits its further application in digital circuits. Semiconducting 2D crystals, such as transition metal dichalcogenides, have bridged this gap. They usually appear in the form of MX<sub>2</sub>, where M represents a transition metal, such as Sc, Ti, Mo, or Ni; and X represents an element from column VI: either S, Se or Te. The physical and chemical properties of TMD materials are greatly diversified. They can be either metallic, semiconducting, or even superconducting. [4]

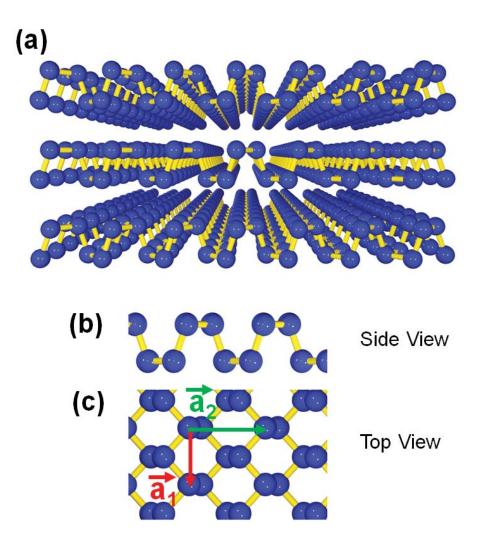

Fig. 1.2. Crystal structure of  $MoS_2$

Figure 1.2 shows the crystal structure of a typical 2D semiconductor,  $MoS_2$ . The bulk crystal is consisted of individual layers. These layers are bonded by van der Waals force instead of covalent bonds. In each layer, a sandwiched structure can be identified, consisting with S-Mo-S atoms. The thickness of each layer is 0.65 nm. Due to the weak van der Waals force between the layers, the bulk crystal can be easily cleaved into thinner layers. Single layer  $MoS_2$  transistors was first demonstrated in 2011 by Radisavljevic *et al.* [5] High electron mobility up to 200 cm<sup>2</sup>/V·s, high current on/off ratio up to  $10^8$ , and small subthreshold swing (SS) down to 74 mV/dec was determined. Despite the possibility of mobility overestimation due to capacitance coupling, these results were still inspiring, as it first demonstrated a high-performance transistor based on single-layer crystal instead of bulk semiconductor. [6] In the meantime, researches also revealed that single-layer  $MoS_2$  has different properties than its bulk counterparts. Single layer  $MoS_2$  was determined to be a direct gap semiconductor with a 1.8 eV band gap, where bulk  $MoS_2$  had an only 1.2 eV indirected one. [7,8]

Shifts in Raman peaks and different vibration modes were also identified between single layer and bulk  $MoS_2$ . [9]

These 2D semiconductors are much favored in device aspects. To take  $MoS_2$  as an example, first of all, it has a large band gap between 1.2 to 1.8 eV, thus it is also considered as "graphene with a band gap". Though graphene has a much higher carrier mobility, the absence of a band gap places a serious restraint in digital applications. [10] This large band gap guarantees low off-state current for the transistors, hence reduce the static power consumption in logic circuits. Second,  $MoS_2$  has a moderate mobility. A typical value would be around several dozens to a hundred  $cm^2/V \cdot s$  at room temperature, and this can be further boosted up to 1000 cm<sup>2</sup>/V  $\cdot s$ at low temperature. [2, 11–13] Thirdly, the 2D semiconductors are innately resistive to SCE. Generally speaking, SCE happens when the channel length is comparable to the depletion width in S/D junctions. In this case, the S/D capacitance is comparable to the gate capacitance,

$$C_{sd} = C_{ox}$$

consider the geometry in a transistor, this can be further written as,

$$C_{sd} = \frac{\epsilon_o \epsilon_s}{L_{ch}} t_{ch} W_{ch} = \frac{\epsilon_o \epsilon_{ox}}{t_{ox}} L_{ch} W_{ch} = C_{ox}$$

Here,  $\epsilon_0$  is the vacuum permittivity,  $\epsilon_s$  and  $\epsilon_{ox}$  are the dielectric constant of that in semiconductor and gate oxide,  $L_{ch}$ ,  $t_{ch}$  and  $W_{ch}$  are the channel length, thickness and width. The above equation can be simplified as,

$$L_{ch} = \sqrt{\frac{\epsilon_s}{\epsilon_{ox}} t_{ch} t_{ox}} = \lambda \tag{1.1}$$

This  $\lambda$  is defined as "characteristic screening length". [14] It represents a feature size where S/D electrostatic control starts to overshadow gate control in further scaling down of the channel length of transistors. With lower  $\lambda$  the device is expected to have better performance at shorter channel length. A conventional method to lower  $\lambda$  is to increase the dielectric constant of gate oxide,  $\epsilon_{ox}$ , or to reduce the thickness of the gate oxide,  $t_{ox}$ , which is the reason that high-k material is used. However, the advent of 2D semiconductors have provided a new approach in this issue. On one hand, the physical thickness of the channel can be greatly reduced. In UTB Si MOSFETs, the devices will suffer from a drastic mobility degradation and  $V_T$ shift due to strong surface roughness once body thickness is reduce to sub-5 nm. [15] However, the body thickness of MoS<sub>2</sub> can be continuously reduced down to atomic scale level with perfectly flat surface. [5] On the other hand, the dielectric constant in MoS<sub>2</sub> is as low as ~3.3, approximately a quarter of that in silicon, which further reduces the characteristic screening length in MoS<sub>2</sub> based transistors. [16] This means, for a single layer MoS<sub>2</sub> transistor, if we have an equivalent oxide thickness (EOT) down to 1 nm, the characteristic screening length would only be 0.8 nm. This is a surprising low number that has never been seen in transistors based on conventional bulk semiconductors.

#### **1.3** MoS<sub>2</sub> Transistors: Opportunities and Challenges

Owing to the great potentials for electronic/optoelectronic applications,  $MoS_2$  transistors have been intensively studies in the past years. Not only limited in transistors, a variety of applications, such as integrated circuits, photo detectors, chemical sensors, have been widely investigated. [17–21] However, in order to achieve real industrial applications, there is still a long way to go for  $MoS_2$  transistors, as it still suffers from a list of bottlenecks that need to be urgently addressed.

The first problem comes from dielectric integration on 2D surface. In conventional CMOS process for bulk semiconductors, this is realized by ALD process. Due to the lack of dangling bonds on the 2D surface, the nucleation of ALD precursors is getting harder at the initial stage, resulting in the difficulty in direct ALD growth. [22,23] To avoid this problem, a practical way is to insert a seeding layer, such as Al, prior to ALD growth. [24] Though this utilizes a uniform dielectric layer on top of 2D crystals, this seeding layer enhanced the dielectric thickness, and further makes it difficult to achieve a low EOT for aggressively scaled devices.

The second issue is related with metal contacts. For silicon MOSFETs, the low contact resistance is realized by heavy doping of the S/D regions, leading to a direct tunneling from metal contacts to the semiconductor. However, no mature doping technique, such as ion implantation, has been developed for 2D semiconductors. Therefore, the contact resistance strongly depends on the Schottky barrier height at the metal/2D interface, leading to a large contact resistant. [11, 12] Various methods have been applied to lower the contact resistance, including molecular doping of the 2D crystal, heterojunction contact, insertion of an oxide layer, and etc. [25–30] But still there is a long way ahead to reduce the contact resistance down to 0.1  $\Omega$ -mm to meet the requirement for industrial applications.

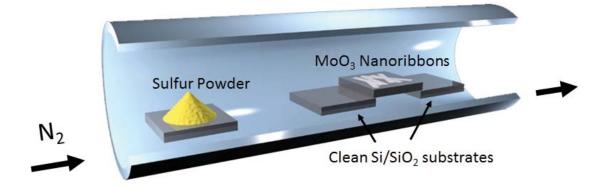

The third question is how to achieve wafer scale, high quality  $MoS_2$  thin film. There have been numerous attempts so far to synthesis single- or multi-layer  $MoS_2$ thin films on various substrates *via* CVD process. [31–35] These CVD synthesized films show similar physical and transport properties as exfoliated ones. However, they are still restrained by limited grain size, and lack of mature doping during synthesis.

#### 1.4 Main Achievements

This dissertation will be focusing on the device aspects on  $MoS_2$  and other semiconducting 2D crystals to address the challenge mentioned in previous section. The main results achieved in this thesis are listed as follows:

**Chapter 2** will focus on dielectric integration on  $MoS_2$  and other semiconducting crystals. For the first time, a direct ALD process is realized on 2D crystals.

**Chapter 3** will report on n-type  $MoS_2$  transistors and its dimension scaling properties. Resistivity to SCE is demonstrated with channel length scaling, while a  $V_T$  adjustment technique will be demonstrated with channel width scaling.

Chapter 4 will briefly go through metal contacts on semiconducting 2D crystals. Fermi-Level pinning is identified at metal/2D interface.

Chapter 5 will summarize the CVD process for single layer  $MoS_2$  synthesis. A

statistical study of the transistor behavior will be performed. Also, the switching mechanism in single layer  $MoS_2$  transistor will be investigated to show its difference from conventional Si MOSFETs.

**Chapter 6** will present a novel p-type 2D semiconductor, black phosphorus and phosphorene. Transport properties will be studied and a simple CMOS inverter based on 2D channel materials will be demonstrated.

# 2. INTEGRATION OF HIGH-K DIELECTRIC ON 2D CRYSTALS

In this chapter, the integration of  $Al_2O_3$  high-k dielectric by ALD on 2D crystals of h-BN and MoS<sub>2</sub> will be investigated. The feasibility of direct ALD growth with trimethylaluminum (TMA) and water as precursors on both 2D crystals will be demonstrated. Both theoretical and experimental studies will be performed to show the initial ALD cycles play the critical role, during which physical adsorption dominates precursor adsorption at the semiconductor surface. The initial ALD growth stages at the 2D surface will be modeled by analyzing Lennard-Jones Potentials, which could guide future optimization of the ALD process on 2D crystals.

#### 2.1 Introduction

The application of ALD techniques to metal gates and high-k dielectrics in the past decade has triumphantly extended Moores Law for the continued scaling down of silicon based CMOS devices. [36] In addition, the integration of high-k materials on other semiconductors, such as Ge, GaAs, InGaAs, GaSb, etc., has also been comprehensively studied in the pursuit of alternative channel materials to replace silicon at the 10 nm node and beyond. [37] In 2004, graphene, a fascinating material labeled as a perfect 2D crystal with an electron mobility approaching 200,000 cm<sup>2</sup>/V·s at room temperature, was realized and has shown promise as a silicon replacement. [2,3] Furthermore, following research has unveiled other similar materials that exist as layered 2D-materials, including BN, Bi<sub>2</sub>Te<sub>3</sub>, Bi<sub>2</sub>Se<sub>3</sub>, MoS<sub>2</sub>, and etc. These other materials can also be isolated to a single atomic layer via mechanical exfoliation. [5, 38–40] However, researchers have noticed that the deposition of high-k dielectric onto 2D crystals, such as graphene, is not as easy as deposition onto Ge or III-V bulk mate-

rials. A typical example is the failure of  $Al_2O_3$  deposition on graphene basal plane with trimethylaluminum (TMA) and water as ALD precursors, which is the most reliable ALD process with a wide process window. This failure has been understood to be caused by the difficulty of forming chemical bonds on the graphene basal plane due to existing global sp<sup>2</sup>-hybridation. [41,42] Despite several successful attempts to integrate high-k dielectrics onto 2D systems, the integration of high-k dielectric onto such 2D crystals has not been thoroughly studied. [5,43,44]

#### 2.2 Growth Mechanism of ALD

Fig. 2.1. A schematic illustration of ALD growth mechanism [45]

First of all, the growth mechanism of ALD will be briefly discussed. A schematic showing the sequential, self-limiting surface reactions during ALD process is shown in Figure 2.1. [45] In such an ALD cycle, precursor A is first introduced into the reaction chamber. Due to the existence of surface dangling bonds of the substrate, an atomic layer of precursor A is adsorbed on the substrate. Extra precursors will be purged by nitrogen. After that, precursor B is introduced into the chamber. It reacts with precursor A and then forms an atomic layer of the products. Extra precursor B and by-products would be purges by nitrogen again. By repeating this cycle, a uniform, thickness-controlled layer will be achieved. Figure 2.2 shows the cross-section SEM image of an ALD  $Al_2O_3$  layer with perfect edge coverage on a silicon trenched structure. [46]

Fig. 2.2. Cross-sectional SEM image of an  $Al_2O_3$  ALD film with a thickness of 300 nm on a Si wafer with a trench structure [46]

#### 2.3 ALD Growth on 2D Crystals

In this section, the growth of ALD  $Al_2O_3$  on two typical 2D materials is studied: hexagonal boron nitride (h-BN), a sister material of graphene and previously used as a graphene dielectric; and  $MoS_2$ , a promising layer-structured semiconducting material with a satisfying band gap. [47] h-BN and  $MoS_2$  2D crystals were thinned from bulk crystals by mechanical exfoliation, and then transferred to 300 nm SiO<sub>2</sub> covered Si substrates. After being cleaned in solvents to remove tape residue, the samples were loaded into an ASM F-120 ALD system. TMA and water were used as precursors. Pulse times of 0.8 and 1.2 seconds were used for TMA and water, respectively, with a purge time of 6 seconds for both. Al<sub>2</sub>O<sub>3</sub> was deposited with a range of substrate temperatures from 200 °C to 400 °C by 50 °C steps.

Fig. 2.3. AFM images of h-BN or  $MoS_2$  surface after 111 cycles of ALD  $Al_2O_3$  at 200 °C, 300 °C and 400 °C

Figure 2.3 shows selected AFM images on h-BN and  $MoS_2$  surfaces after 111 ALD cycles at 200 °C, 300 °C and 400 °C, with an expected  $Al_2O_3$  thickness of ~10 nm. The  $Al_2O_3$  growth rate on SiO<sub>2</sub> substrates remained similar at various tem-

peratures; however, its growth on h-BN and MoS<sub>2</sub> flakes was strongly temperature dependent. A uniform Al<sub>2</sub>O<sub>3</sub> layer formed at 200 °C on both h-BN and MoS<sub>2</sub> substrates is observed. Previous study have shown that the leakage current density was relatively small ( $\sim 2 \times 10^{-4}$  A/cm<sup>2</sup> under 1 V gate bias) for MoS<sub>2</sub> based metal-oxidesemiconductor structure, suggesting that the ALD Al<sub>2</sub>O<sub>3</sub> thin film on MoS<sub>2</sub> was of good quality [48]. With elevated growth temperatures, it was obvious that the Al<sub>2</sub>O<sub>3</sub> film was not uniform on both h-BN and MoS<sub>2</sub> substrates. When the growth temperature was increased to 250 °C, pinhole defects started to appear at the 2D surface. With further increase of growth temperatures, these pinholes tended to expand and finally connect with each other, leaving island like Al<sub>2</sub>O<sub>3</sub> clusters on the 2D basal plane. In contrast to the growth on basal plane, the growth on edges remain constant at the range between 200 °C to 400 °C, due to the existence of dangling bonds at the basal edges. [17, 41]

Fig. 2.4.  $Al_2O_3$  coverage estimation from MATLAB analysis by Otsu method

The AFM data is further analysed with a MATLAB script to quantify the  $Al_2O_3$  coverage, and used this as a metric for the ease of ALD growth, although the coverage percentage may have evident run-to-run variance due to fluctuations of chamber pressure, which has a significant impact to the surface adsorption. The Otsu method was applied to distinguish the boundary between the regions on h-BN or MoS<sub>2</sub> flakes "with" or "without"  $Al_2O_3$  growth. [49] As shown in Figure 2.4, the  $Al_2O_3$  coverage was monotonically decreasing with increased temperature, and had a slightly increased coverage ratio on MoS<sub>2</sub> than that on h-BN at higher temperatures. Such temperature dependent growth indicates that the growth is controlled by physical adsorption of the precursors at the substrate surface, and will be further discussed later.

Table 2.1. Binding Energy  $(E_{ads} = E_a + E_b - E_{ab})$  in kcal/mol

| Adsorption                                | $E_{ads}$ |

|-------------------------------------------|-----------|

| $\rm hBN + H_2O \rightarrow \rm hBN-H_2O$ | 4.1       |

| $hBN + TMA \rightarrow hBN-TMA$           | 12.8      |

| $MoS_2 + H_2O \rightarrow MoS_2-H_2O$     | 11.1      |

| $MoS_2 + TMA \rightarrow MoS_2$ -TMA      | 33.0      |

In order to achieve insight in the understanding of the interactions at the substrate surfaces and hence understand the initial ALD cycles for 2D crystals, density function theory (DFT) studies were performed by using the M06-2x method with basis sets 3-21G(d) for Mo and 6-311G+(d,p) for H, O, C, B, N, and Al. [50] Table 2.1 shows the calculated adsorption energies of the two ALD processes. It can be seen that the binding energy of TMA on h-BN is 8.7 kcal/mol greater than that of H<sub>2</sub>O on h-BN and the binding energy of TMA on MoS<sub>2</sub> is 21.9 kcal/mol greater than that of H<sub>2</sub>O on MoS<sub>2</sub>. This implies that TMA is more easily physically absorbed on both types of crystals.

Fig. 2.5. Binding structure models of  $\rm H_2O$  and TMA on h-BN and  $\rm MoS_2$

Figure 2.5 shows the four adsorption structural models. For the h-BN system, the O atom of  $H_2O$  is adsorbed at the B atom while the Al atom of TMA is adsorbed at the N atom. The calculated distances of O-B and Al-N are 2.769 and 2.604 Å, respectively. These distances are greater than the corresponding covalence bonds. Therefore, the adsorption energies include the front molecular orbital interaction and van der Waals contribution. For MoS<sub>2</sub>, H<sub>2</sub>O and TMA are all adsorbed at the S

atom. The length of Al-S bonds is predicted to be 2.653 Å while the shortest length of O-S bonds is 2.833 Å. Apparently the distances of Al-S and Al-N are shorter than that of O-S and O-B, respectively, though the atomic volume of Al is greater than that of O. Therefore, compared to the H<sub>2</sub>O adsorption, the TMA adsorption is more stable. Table 2 lists the atomic charges, polarizabilities, and frontier molecular orbital levels of the interaction atoms in H<sub>2</sub>O, TMA, h-BN, and MoS<sub>2</sub>. It can be seen that O atoms with negative charges would have electrostatic interactions with the positively charged B and Mo atoms, while Al atoms with positive charges would be interacting with the negatively charged N and S atoms. Also, one can see that the polarizability of TMA is much greater than that of H<sub>2</sub>O, while the polarizability of MoS<sub>2</sub> is much greater than that of h-BN. This implies that the interactions of TMA-MoS<sub>2</sub> would have the largest dispersion energy and the interactions of H<sub>2</sub>O-hBN would have the least. In addition to this van der Waals interaction, the frontier molecular orbitals of these model molecules may take an important role in the combination.

| unit.                     |                  |       |         |        |         |        |         |        |

|---------------------------|------------------|-------|---------|--------|---------|--------|---------|--------|

|                           | H <sub>2</sub> O |       | TMA     |        | h-BN    |        | $MoS_2$ |        |

| $\epsilon_i(\text{LUMO})$ | 0.1933           |       | -0.0068 |        | 0.0363  |        | -0.1672 |        |

| $\epsilon_i(\text{HOMO})$ | -0.4009          |       | -0.3210 |        | -0.2972 |        | -0.2823 |        |

| $P_i$                     | 6.140            |       | 48.996  |        | 34.666  |        | 112.316 |        |

|                           | 0                | Н     | Al      | С      | В       | Ν      | Мо      | S      |

| $Q_{\alpha}$              | -0.582           | 0.291 | 1.337   | -0.481 | 0.991   | -0.924 | 2.176   | -1.088 |

Table 2.2. Atomic charges, polarizabilities, and frontier molecular orbital levels of the interaction atoms in  $H_2O$ , TMA, h-BN, and  $MoS_2$  in atomic unit.

From Table 2, the gaps between the LUMO and HOMO level are 0.5942 au for  $H_2O$ , 0.3142 au for TMA, 0.3335 au for h-BN, and 0.1151 au for  $MoS_2$ . Thus, the orbital interactions of  $H_2O$  with h-BN and  $MoS_2$  would be less than that of TMA with h-BN and  $MoS_2$ , respectively. This analysis supports the predicted result of

adsorption energies. In classical ALD theories, deposition with precise thickness control is determined by self-limited precursor adsorption at substrate surfaces, and is classified into two types: physical and chemical adsorption surface. During the initial ALD cycles on 2D crystals, excepting a few chemically active materials such as the topological insulators  $Bi_2Te_3$  and  $Bi_2Se_3$  which are easily oxidized at growth temperatures and hence facilitate the formation of chemical bonds for precursors at the surface, chemical adsorption is rarely observed. [22] This is due to the absence of dangling bonds at their basal planes. Consequently, physical adsorption is the dominant adsorption method at the 2D surface. This view is also supported by the result that such deposition is strongly temperature dependent. It is interesting to note that ALD  $Al_2O_3$  can be deposited on h-BN at 200 °C, while  $Al_2O_3$  can only grow at graphenes edges, even though h-BN is extremely structurally similar to graphene. Such a difference between  $Al_2O_3$  deposition on graphene and BN can be explained using the framework of the Lennard-Jones potential model, which has been generally used to model the molecular adsorption on graphene and carbon nanotube surfaces. [51–53]

As shown in Figure 2.6, for each ALD pulse-purge cycle, the pulse action pushes the precursor molecules to the vicinity of substrate where the molecule has the lowest potential energy; while the purge action pushes the molecule away from the substrate, to the x-axis infinity, where the molecules encounter an energy barrier. There are two factors that determine the ultimate molecular state: One is the depth of the potential well, shown as the adsorption energy and determined by the polarizability of the substrate and molecules. Using h-BN as an example, nitrogen serves as a positive charge center while boron serves as a negative charge center, while graphene has no polarization due to perfect symmetry, the interaction between the h-BN molecule and ALD precursors would be stronger than that of graphene and ALD precursors. That is to say, the depth of the potential well in the h-BN system will be larger than that in the graphene counterpart. The other reason is the growth temperature, which is near the thermal energy of the precursor molecules. At lower temperatures, the thermal energy that the precursors can obtain from the environment is not large enough so that the

Fig. 2.6. An illustrative Lennard-Jones potential Model for physical adsorption at 2D crystal surfaces

molecules are trapped in the potential well, despite the purge action; while at higher temperatures where the thermal energy is greater than the depth of the potential well, the excited molecule can escape, thus resulting in incomplete ALD cycles. Therefore, the ALD window for deposition on 2D crystals is different from previous studies on bulk materials. For bulk substrates, the lower temperature limit of the ALD growth window is determined by precursor condensation and incomplete reaction at lower temperatures, and the high temperature limit is determined by precursor decomposition as well as desorption. [54] For 2D substrates, the low temperature limit still remains similar as it is only related to the precursors, regardless of the substrate material. However, the high temperature limit, since desorption is much easier at 2D surfaces, is at a dramatically lower temperature. This creates a large challenge to dielectric integration for high performance devices, such as  $V_T$  shifts observed in the study on MoS<sub>2</sub> top-gated MOSFETs. [48] Given the discussion above, it is clearly seen that the first several ALD cycles is critical, not only for properties related to interface quality, but to allowing further deposition as  $Al_2O_3$  can provide dangling bonds for the chemical adsorption of the precursors. One way to optimize the ALD process is to change the pulse and purge times in to better control the surface adsorption/desorption at the initial stages of deposition. Alternatively, a seeding layer, such as an ultrathin Al film, or  $Al_2O_3$  film deposited by ALD at lower temperature, can also provide a solution for high quality dielectric growth as played with graphene. [55] Another related question is the "interface" issue, as it has been generally accepted that the origin of interface states is attributed to unpassivated dangling bonds. [56] In the absence of dangling bonds at surface of 2D crystals, the definition of "interface states" between 2D crystals and dielectrics may need to be reconsidered, and such an issue may need further investigation.

#### 2.4 Summary

In summary, a direct ALD growth of  $Al_2O_3$  with TMA and water as precursors on 2D crystals of h-BN and MoS<sub>2</sub> is demonstrated. A DFT study is also performed on surface adsorption of 2D crystals at different geometric substrate locations. Both experimental and theoretical results show that the ALD growth on 2D crystals is determined by physical absorption, and is enhanced by in-plane polarization of the substrate. These results have shown provided insight into growth mechanisms and will allow better solutions for high-quality dielectric integration to be found, and provides a big step forward for novel devices based on 2D crystals in the future.

# 3. N-TYPE MOS<sub>2</sub> TRANSISTORS AND DIMENSION SCALING

Research in MoS<sub>2</sub> electronics is still in its infancy. The first experimentally demonstrated single-layer MoS<sub>2</sub> transistor has already shown a mobility of over 200 cm<sup>2</sup>/V·s, a SS of 74 mV/decade and on/off ratio of  $10^8$ . [5] Following NEGF simulations theoretically predicted the perfect performance limits of MoS<sub>2</sub> thin film transistors. [16] In this chapter, the device properties of MoS<sub>2</sub> transistors will be investigated. A top-gated MoS<sub>2</sub> MOSFET with Al<sub>2</sub>O<sub>3</sub> as gate dielectric will be demonstrated. Furthermore, scaling properties, such as channel length scaling and width scaling will also be discussed.

#### 3.1 N-type Double-Gate MoS<sub>2</sub> Transistors

After a successful demonstration of direct ALD process, as discussed in chapter 2, MoS<sub>2</sub> transistors with top gate dielectric is going to be fabricated. To begin with, MoS<sub>2</sub> thin flakes were mechanically exfoliated by the classical scotch-tape technique and then transferred to a heavily doped Si substrate capped with 300 nm SiO<sub>2</sub>. Al<sub>2</sub>O<sub>3</sub> was deposited on MoS<sub>2</sub> flakes within an ASM F120 ALD reactor. TMA and water were used as precursors. A 16 nm ALD Al<sub>2</sub>O<sub>3</sub> was deposited on MoS<sub>2</sub> flakes at 200 °C. After Al<sub>2</sub>O<sub>3</sub> growth, source and drain regions were defined using optical lithography with a spacing of 9  $\mu$ m. After source/drain regions etched with BOE, a 20/50 nm Ni/Au was deposited as the source/drain contacts and Ti/Au was used for gate. The gate length is ~3  $\mu$ m with ~3  $\mu$ m spacings to source/drain.

The  $MoS_2$  MOSFET was fabricated on a ~15 nm thick flake which contains about 23 individual  $MoS_2$  layers. Final device structure is shown in Figure 3.1. The flake thickness was not reduced to a single layer since the band gap of  $MoS_2$  crystal increases

Fig. 3.1. Device structure of  $MoS_2$  double gate MOSFET

to 1.8 eV for single layer, leading to a reduced density of states. [7] C-V measurement was carried out in order to evaluate the interface quality between ALD Al<sub>2</sub>O<sub>3</sub> and MoS<sub>2</sub> crystals, as shown in Figure 3.2. Source and drain were grounded, while a voltage bias on the top-gate is applied. The area of the capacitor was only  $\sim 12 \ \mu m^2$ , making the low frequency C-V curve rather noisy. The high frequency C-V at 1 MHz showed a clear transition from accumulation to depletion for a typical n-type MOS capacitor. A moderate hysteresis of  $\sim 80 \ mV$  exhibited in the curves, showing that the ALD Al<sub>2</sub>O<sub>3</sub> film grown at 200 °C on MoS<sub>2</sub> and the interface were both of good quality.

Figure 3.3 show the transfer characteristics and transconductance of the device from both the top-gate and the back-gate. The charge neutrality level (CNL) of  $MoS_2$  is located slightly under the conduction band, thus making it easy for an accumulation-type nMOSFET. [57, 58] The transfer characteristics of the top-gate

Fig. 3.2. 1 MHz high-frequency C-V characteristic of the MOSFET device measured at room temperature in darkness

suffer from a very large negative threshold voltage (V<sub>T</sub>) shift, as attributed to the existence of large amount of positive fixed charges in the bulk oxide, due to the comparatively lower deposition temperature. [59] The leakage current was also measured in the same device, and was determined to be less than  $2 \times 10^{-4}$  A/cm<sup>2</sup> in the measurement range from -6 V to 3 V. The highest drain current density achieved at  $V_{ds} = 1 V$  using back-gate modulation is 7.07 mA/mm and an on/off ratio greater than 10<sup>8</sup>. This superior on/off ratio compared to graphene is attributed to the 1.2 eV large band gap. The greatest current density from top-gate is about 2 orders of magnitude smaller than that from the back-gate. This big difference comes from the non-self-aligned top-gate device structure. From Figure 3.1, it can be seen that the heavily doped Si substrate has a "global" control over the entire flake. With increasing back-gate voltage, the carriers in the MoS<sub>2</sub> flake are accumulated and thus

Fig. 3.3. Transfer characteristics of the  $MoS_2$  double gate MOSFET from back-gate and top-gate controls with leakage current density from 300 nm SiO<sub>2</sub> and 16 nm Al<sub>2</sub>O<sub>3</sub>

the contact resistance between the Ni/Au source/drain and the  $MoS_2$  flake would be reduced, as the flake is electrostatically doped by the electric field, while the topgate can only modulate part of the channel under the top-gate. The peak extrinsic transconductance ( $g_m$ ) from back-gate control is 0.165 mS/mm at  $V_{ds} = 1 V$ . The hysteresis of the top-gate transfer curves is much smaller than that of the back-gate curves, similar to the C-V curves. The subthreshold swing (SS) for top-gate is ~140 mV/dec at  $V_{ds} = 1 V$ . The interface trap density is estimated to be  $2.4 \times 10^{12}/\text{cm}^2 \cdot \text{eV}$ at MoS<sub>2</sub> and ALD Al<sub>2</sub>O<sub>3</sub> interface and would be further reduced by optimizing the process. Considering that there is minimal process refinement, such as no surface passivation and the low ALD growth temperature, this may imply the interface states issue between 2D crystals and ALD high-k dielectrics is very forgiving.

Figure 3.4 shows the drain current versus drain voltage under a variety of backand top-gate biases. The gate biases range from 50 V to 20 V with a -5 V step for back-gate, and from -3 V to -6 V with a -0.5 V step for top-gate. For the top-gate measurement, a back-gate voltage of 50 V is applied to reduce the contact resistance and access resistance. Consequently, the maximum current density for top-gate modulation has now been increased to 6.42 mA/mm, back to the same level of that from back-gate modulation. The maximum extrinsic  $g_m$  at  $V_{ds} = 2 V$  are 0.318 mS/mm and 2.83 mS/mm for back-gate and top-gate modulation, respectively.

Fig. 3.4. Output characteristics of the  $MoS_2$  double gate MOSFET from back-gate and top-gate controls

## 3.2 Channel Length Scaling of MoS<sub>2</sub> Transistors

In this section, device performance of  $MoS_2$  transistors with various channel length will be presented. Immunity to SCE of  $MoS_2$  transistors will be evaluated at short channel regions.

Fig. 3.5. Schematic diagram and optical image of the back-gated  $MoS_2$  MOSFETs with various channel length

Sets of MoS<sub>2</sub> devices with various channel length were fabricated on exfoliated MoS<sub>2</sub> crystals. Each set of the device was fabricated on the same rectangular MoS<sub>2</sub> flake, so the scaling effect can be directly observed and compared without the correction for geometry and thickness variations. The MoS<sub>2</sub> flakes were mechanically exfoliated with 3M scotch tapes from a bulk ingot purchased from SPI Inc. A heavily p-doped silicon wafer (0.01–0.02  $\Omega$ ·cm) with 300 nm SiO<sub>2</sub> capping layer was used as back gate and gate dielectric. After flake transfer, the samples were soaked in acetone for overnight to remove the tape residues on SiO<sub>2</sub> substrate, followed by methanol and isopropanol rinse. The thickness of the flakes was measured by Dimension 3100 AFM systems. MOSFETs structures were defined by electron beam lithography, followed by the electron beam evaporation of Ni/Au for 30/50 nm or only 50 nm Au

for different sets of devices with the deposition rate of  $\sim 1$  Å/s. Metallization was performed by electron beam evaporation afterwards. The width of the contact bars are 500 nm. Electrical characterizations were carried out with Keithley 4200 system at room temperature. The schematic and corresponding optical microscope image of the 5 nm thick devices are shown in Figure 3.5.

Fig. 3.6. Device performance of long channel and short channel  $MoS_2$  transistors

First, the transistor characteristics of both long-channel and short-channel  $MoS_2$ MOSFETs are examined. Considering that the single layer  $MoS_2$  has a larger band gap and hence a lower mobility and larger contact resistance, the devices on a fewlayer crystal were fabricated for a better trade-off between the on/off ratio and device performance. Note that the dielectric constant of  $MoS_2$  is only around 3.3, a 5 nm thick crystal would be thin enough for short channel devices to turn off completely. [16]

Figure 3.6 shows the transfer and output curves for the 2  $\mu$ m and 100 nm channel length  $(L_{ch})$  devices. Because of the large band gap of 1.2 eV of MoS<sub>2</sub>, these devices, unlike graphene, can be easily turned off. Even though the thickness of gate dielectric is extremely large (300 nm), which results in a much degraded electrostatic control, still no evident short channel effects were observed with channel lengths down to 100 nm. For this short channel device, the on-current is reaching 70 mA/mm at  $V_{ds} = 1 V$ , and the current on/off ratio is over  $10^7$  for  $V_{ds} = 1 V$ , and is able to maintain an on/off ratio of  $10^9$  at  $V_{ds} = 0.1 V$ . Benefiting from its ultrathin body, the on/off ratio does not drop much compared to the 2  $\mu$ m long device which has a current on/off ratio up to  $\sim 10^{10}$ , showing good immunity to short channel effects. Note that significant short channel effects could be observed on other planar devices, such as InGaAs or Ge, when the gate length was scaled down to 150 nm. [60] The intrinsic mobility extracted from the 2  $\mu$ m long device is ~28 cm<sup>2</sup>/V·s. It could be further increased up to several hundred by dielectric passivation on the top. [5, 48] The observation of transistor behavior without evident short channel effects with 300  $nm SiO_2$  indicates that the enhancement of electrostatic control by reducing the gate dielectric thickness down to several nanometers would significantly push the scaling of channel length down to sub-10 nm for  $MoS_2$  devices. This is beyond the range of conventional semiconductors. The superior immunity to short channel effects of  $MoS_2$ not only originates from its ultrathin body nature, but is also due to the low dielectric constant of  $MoS_2$  itself. The characteristic length of short channel transistors with planar structures is:

$$\lambda = \sqrt{\frac{\epsilon_s}{\epsilon_{ox}} t_{ch} t_{ox}} \tag{3.1}$$

where  $\lambda$  is the characteristic screening length,  $\epsilon_s$  and  $\epsilon_{ox}$  are the permittivity of semiconductor and gate oxide,  $t_{ch}$  and  $t_{ox}$  are the thickness of semiconductor channel and gate oxide. The characteristic length for this 5 nm thick MoS<sub>2</sub> transistor is 35.6 nm, much shorter than the channel length of the shortest device. If the 300 nm SiO<sub>2</sub> gate oxide is replaced by 6 nm HfO<sub>2</sub> with an EOT of ~1 nm, the characteristic length would be expected to be reduced to only 2 nm, which is far beyond the technical consideration of 10 nm node with alternative channel materials for logic applications. This formula was first proposed by Yan *et al.* to calculate the characteristic lengths of silicon MOSFETs, where the carrier transport is almost isotropic. [14] For layered structures, the layer-to-layer transport is less efficient as in-plane transport. [12] Therefore, the effective  $t_{ch}$  for 2D crystals could be even smaller, further reducing characteristic screening length of MoS<sub>2</sub> transistors.

To make a comparison of the short channel effects related to the  $MoS_2$  flake thickness, another set of devices on a 12 nm thick  $MoS_2$  crystal was fabricated. The characteristic length of this transistor is calculated to be  $\sim 55.2$  nm, on the same 300 nm  $SiO_2$  as back gate dielectric. The channel length is further scaled down to 50 nm, so that the channel length would be comparable to  $\lambda$ . The transfer and output characteristics of the device with 50 nm channel length are presented in Figure 3.7. Short channel effects start to appear in this device. The drain current on/off ratio  $(I_{on}/I_{off})$  dropped down to  $\sim 10^7$  at  $V_{ds} = 0.1 V$ , and  $\sim 5 \times 10^4$  at  $V_{ds} = 1 V$ . A severe drain induced barrier lowing (DIBL) was also observed. The upward bending in the output characteristics in Figure 3.7(b) at high drain biases also indicates a degraded electrostatic control from the gate. However, the  $MoS_2$  transistors differ from traditional silicon transistors as they are majority carrier transistors, also they do not have heavily implanted source/drain regions, as mentioned above. These two features makes the  $MoS_2$  transistor slightly different from bulk silicon or silicon on insulator transistors for their short channel behaviors. Since no space charge region are formed between source/drain and channel, there should be much less threshold shift. Meanwhile, due to the absence of heavily doped source/drain regions, the hot electrons degradation at drain end can be eliminated and would not be a severe problem. Also, the atomic flat surface of the 2D crystal would greatly reduce surface scattering. Therefore, in this section, the SCE would be mostly focused in DIBL and current on/off ration as criteria for short channel degradation of the  $MoS_2$  transistors.

Fig. 3.7. Device performance of the  $MoS_2$  transistors of 50 nm channel length

The channel length dependent  $I_{on}/I_{off}$  and DIBL of the two sets of devices are plotted in Figure 3.8. For the set of devices with 5 nm thick MoS<sub>2</sub> crystal, the  $I_{on}/I_{off}$ ratio is nearly constant, with a minor decrease as the channel becomes shorter, while

Fig. 3.8. Current on/off ratio and DIBL in  $MoS_2$  transistors at various channel length

the total change remains within one order of magnitude of its long-channel value. The set of devices on the 12 nm thick crystal was observed to have a lower  $I_{on}/I_{off}$  ratio as expected, following the same slightly decreasing trend with scaling down, until the channel length approaches the characteristic length, where it experiences a sharp drop down to less than  $10^5$ . Similar behavior was also observed in the DIBL. Due to the weaker electrostatic control from the global back gate with 300 nm gate dielectric, the DIBL is relatively large even at long channel devices compared to top gate devices with sub-10 nm high-k dielectric. It is observed from Figure 3.8(b) that the DIBL for the sets of devices fabricated on the 5 nm thick flake is smaller than that of devices with 12 nm thick crystal. At long channel lengths, (e.g.  $L_{ch} = 2 \ \mu m$ ), it is  ${\sim}4$  V/V for the thinner devices and  ${\sim}10$  V/V for the thicker ones. However, these values are not completely correlated with short channel effects because the channel lengths are long enough at this region but could be attributed to the shifts in threshold voltage. In Chapter 2, it was pointed out that the  $MoS_2$  is very sensitive to polarized molecules (such as  $H_2O$ ) in the environment, and these molecules would be physically adsorbed as  $MoS_2$  surface, and causing threshold voltage shift. That is to say, the DIBL measurement is also influenced by the hysteresis in  $MoS_2$  transistors. Though several attempts were made to eliminate this factor, which included maintaining the temperature and humidity at a constant level in the measurement, and also the transfer curves were measured all through the fixed direction of voltage change (constantly from depletion to accumulation), but still minor fluctuations are existed in the extraction of DIBL, where the DIBL starts to increase at larger channel length for the sets of transistors fabricated on the thinner flake. Another observation from Figure 3.8(b) is that the DIBL from both sets of devices experience a rapid increase once the channel length approaches the characteristic length. If the 300 nm gate oxide be replaced with state-of-art high-k dielectric and scaled down to an EOT of 1-3 nm, one would expect that there would be no short channel effects even the  $L_{ch}$  is reduced to sub-10 nm, which shows the superior immunity to short channel effects of  $MoS_2$  transistors, as discussed above. Though these sets of devices have large contact resistance which is comparable to the channel resistance at short channel length scales (which will be discussed later), which will reduce the lateral electric field in the transport direction, the weak electrostatic control of the gate (a maximum of 1.67 MV/cm) compared to top gate devices ( $\sim$ 4–6 MV/cm) still makes the immunity to short channel effects convincing.

For long channel devices, where  $L_{ch}$  is much larger than the length of electron mean free path, the transistors are fully operated in the diffusive regime, where field-effect mobility should remain constant, while the maximum drain current and the transconductance keep increasing with continuous scaling, which is inversely proportional to  $L_{ch}$ . Both extrinsic/intrinsic field dependent mobility and maximum on-state current at  $V_{gs} = 50 V$  and  $V_{ds} = 2 V$  for all devices with various  $L_{ch}$  are plotted in Figure 3.9. The peak transconductance is extracted by differentiating the transfer curve, and then calculated the extrinsic field-effect mobility by simply using the equation:

$$g_m = \mu_n C_{ox} \frac{W}{L} V_{ds} \tag{3.2}$$

where  $\mu_n$  is the electron mobility,  $C_{ox}$  is the MOS capacitance, W and L are the width and length of the channel, and  $V_{ds}$  is the drain voltage. The intrinsic values of the field mobility are further corrected by calculating the channel resistance at the voltage point where transconductance is at its peak, and then amended the drain voltage  $V'_{ds} = V_{ds}(R_{tot} - R_c)/R_{tot}$ , where  $V'_{ds}$  is the actual drain voltage applied on the channel,  $R_{tot}$  is the total resistance and  $R_c$  is the contact resistance, as both  $R_{tot}$  and  $R_c$  are known. Here, if diffusive transport for all sets of devices regardless of their channel lengths is assumed, the change of field-effect mobility at different channel length scale can be observed. It can be seen from Figure 3.9 that in the long channel regions  $(L_{ch} > 500 nm)$ ,  $\mu_n$  remains constant at around 28 cm<sup>2</sup>/V·s. With further scaling,  $\mu_n$  starts to decrease, and drops to around 17 cm<sup>2</sup>/V·s at 100 nm channel length. Also, it can be learned from the classical square-law model that the drain current is inversely proportional to channel length, which means, the  $I_d$ - $L_{ch}^{-1}$  relationship should present a linear characteristic. However, in Figure 3.9(b), as indicated by the red dashed line, this linear relationship applied only at long channel region  $(L_{ch} > 500 \text{ nm})$ . With continuous scaling down, it comes to saturate at ~90 mA/mm at  $L_{ch} = 100 nm$ . The decrease of field-effect mobility and non-

Fig. 3.9. Mobility and maximum drain current at various channel length

linearity of drain current could be attributed to two reasons. One reason is the substantial contact resistance which does not scale with channel length but is present in the device when the contact resistance is comparable to channel resistance. The second reason, if the contact resistance is ignored, is that mobility decreases since the carriers are approaching their saturated velocities at shorter channel length. [61] In general, the electric field in the channel is reversely proportional to the channel length, leading to higher carrier velocities at reduced channel length, as defined by  $\nu = \mu E$ . As a result, the drain current increases with reduced channel length, while field effect mobility remains constant. However, at very short channel lengths, the velocity of the carrier is getting saturated even with increase electric field. Therefore, as the velocity is approaching saturation with increased electric field, the field effect mobility calculated from the same formula would result in a decreased number, as well as the drain current is also getting saturated. By excluding the contact resistance, the field-effect mobility still shows a descending trend when  $L_{ch}$  is less than 500 nm, indicating that the contact resistance is not the only dominant factor for the scaled short channel devices, and that these short channel transistors with  $L_{ch} < 500 \ nm$ are showing carrier velocity saturation behaviors, which is consistent with what was observed in classical short channel silicon devices.

## 3.3 Channel Width Scaling of MoS<sub>2</sub> Transistors

In this section, the width scaling properties of  $MoS_2$  transistors by forming nanoribbon channels will be investigated. Also, by proper width selection, the  $V_T$  of the  $MoS_2$ transistors can be modulated to be both positive and negative will be demonstrated.

The fabrication process of sets of  $MoS_2$  transistors is shown in Figure 3.10, as described below.  $MoS_2$  flakes were first mechanically exfoliated and transferred to a heavily p-doped silicon substrate (0.01–0.02  $\Omega$ ·cm) with a 300 nm SiO<sub>2</sub> capping layer. The silicon substrate served as a global back gate, while the 300 nm SiO<sub>2</sub> served as the gate dielectric. After the flake transfer, electron beam lithography was

Fig. 3.10. Fabrication process and device images of  $MoS_2$  transistors with various channel width

used to pattern the flake, followed by plasma dry etching (BCl<sub>3</sub>: 15 sccm, Ar: 60 sccm, Pressure: 0.6 Pa, RF source power: 100 W, RF Bias Power: 50 W, time: 5 min) to remove the excess parts of the flakes, leaving connected rectangles with a fixed length (2  $\mu$ m) but various widths to be used as device channels. The widths of these rectangles varied from 2  $\mu$ m down to 60 nm. Finally, contacts were defined by electron beam lithography, followed by a 50 nm Au metallization by electron beam deposition. The contact bars were 1  $\mu$ m wide, centered on the edge between two neighboring channel areas. The final set of devices have a fixed channel length of 1  $\mu$ m and widths of 2  $\mu$ m, 1  $\mu$ m, 500 nm, 200 nm, 100 nm, 80 nm and 60 nm. Three sets of devices were fabricated on three large flakes with thickness of 6, 6 and 11 nm, as determined by AFM. The optical image and SEM image of these sets of devices are shown in Figures 3.10(b) and (c). Over-etching of the MoS<sub>2</sub>, in order to guarantee

complete removal of excess  $MoS_2$  crystals, created a rectangular step in the SiO<sub>2</sub> capped substrate surrounding the flake, and also created SiO<sub>2</sub> sidewalls at the edges of the  $MoS_2$  channels (Figure 3.10(c) inset). Smooth edges without obvious damage by dry etching was observed at the  $MoS_2$  nanoribbons.

Fig. 3.11. Transfer and output characteristics of 2  $\mu{\rm m}$  and 60 nm channel width devices