### Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

Summer 2014

## On variability and reliability of poly-Si thin-film transistors

Chih-Hsiang Ho

Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

Part of the Electrical and Electronics Commons

#### Recommended Citation

Ho, Chih-Hsiang, "On variability and reliability of poly-Si thin-film transistors" (2014). *Open Access Dissertations*. 286. https://docs.lib.purdue.edu/open\_access\_dissertations/286

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

| • •                                                                                                                                                                                                                                               |                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| By Chih-Hsiang Ho                                                                                                                                                                                                                                 |                           |

| Entitled On Variability and Reliability of Poly-si Thin-film Transistors                                                                                                                                                                          |                           |

| For the degree of Doctor of Philosophy                                                                                                                                                                                                            |                           |

| Is approved by the final examining committee:                                                                                                                                                                                                     |                           |

| KAUSHIK ROY                                                                                                                                                                                                                                       |                           |

| Chair<br>ANAND RAGHUNATHAN                                                                                                                                                                                                                        |                           |

| BYUNGHOO JUNG                                                                                                                                                                                                                                     |                           |

| MUHAMMAD A. ALAM                                                                                                                                                                                                                                  |                           |

| To the best of my knowledge and as understood by the student in the <i>Research Copyright Disclaimer (Graduate School Form 20)</i> , this thesis/dissertation adhe Purdue University's "Policy on Integrity in Research" and the use of copyright | eres to the provisions of |

| Approved by Major Professor(s): KAUSHIK ROY                                                                                                                                                                                                       | -                         |

| Approved by: M. R. Melloch                                                                                                                                                                                                                        | 08-11-2014                |

### ON VARIABILITY AND RELIABILITY OF POLY-SI THIN-FILM TRANSISTORS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Chih-Hsiang Ho

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2014

Purdue University

West Lafayette, Indiana

To my family and friends near and far.

#### ACKNOWLEDGMENTS

There is no way that I could have completed my Ph.D. without the love and support from so many people. First, I would like to offer my sincere thanks to my adviser, Prof. Kaushik Roy, for his guidance and support. From him, I have learned not only knowledge and skills, but also mentality and ethics of being a researcher. I am so fortunate to have him as my adviser.

I would also like to acknowledge my committee members, Prof. Muhammad A. Alam, Prof. Byunghoo Jung and Prof. Anand Raghunathan for mentoring me and providing valuable suggestions and technical comments to this work.

I sincerely thank to all the amazing NRL labmates for valuable inputs. Specially, I would like to acknowledge Georgios Pagagoupolous, Chao Lu, Sooyoun Kim, Debabrata Mohapatra, Dong Soo Lee, Yusung Kim, Selin Baytok, Sri Harsha Choday, Xuanyao Fong, Kon-Woo Kwon, Deliang Fan, Sumeet Kumar Gupta, Charles Augustine and Sang Phill Park for helpful discussions.

Finally, I would like to thank my parents, my brother and my wife for their patience, loving care and support, and for bringing happiness to my life.

#### TABLE OF CONTENTS

|    |      |         |                                                                                                  | Page    |

|----|------|---------|--------------------------------------------------------------------------------------------------|---------|

| LI | ST O | F TAB   | LES                                                                                              | vii     |

| LI | ST O | F FIGU  | URES                                                                                             | viii    |

| AI | BSTR | ACT     |                                                                                                  | xii     |

| 1  | INT  | RODU    | CTION                                                                                            | 1       |

|    | 1.1  | Overv   | riew                                                                                             | 1       |

|    | 1.2  | Poly-S  | Si TFT Variation due to GBs                                                                      | 2       |

|    | 1.3  | Poly-S  | Si TFT Degradation due to NBTI                                                                   | 3       |

|    | 1.4  | AMO     | LED Pixel Circuit Design for Variation Compensation                                              | 3       |

|    | 1.5  | Self-re | epair Design Methodology for Variation Compensation                                              | 4       |

|    | 1.6  | Circui  | it-Level Reliability Test Optimization                                                           | 5       |

|    | 1.7  | Organ   | nization                                                                                         | 5       |

| 2  |      | VOLT    | EL MODEL FOR GRAIN BOUNDARY INDUCED THRESH-<br>CAGE VARIATION IN POLY-SILICON THIN-FILM TRANSIS- |         |

|    | 2.1  | Introd  | luction                                                                                          | 7       |

|    | 2.2  | The F   | ramework                                                                                         | 9       |

|    |      | 2.2.1   | Input Parameters                                                                                 | 10      |

|    |      | 2.2.2   | Modeling Electrostatic Potential due to Boundary Conditions                                      | 10      |

|    |      | 2.2.3   | Modeling Electrostatic Potential due to GBs                                                      | 12      |

|    |      | 2.2.4   | Modeling Surface Potential                                                                       | 15      |

|    |      | 2.2.5   | Modeling Threshold Voltage                                                                       | 17      |

|    | 2.3  | Simula  | ation Results & Discussions                                                                      | 17      |

|    | 2.4  | Concl   | usions                                                                                           | 22      |

| 3  |      |         | ONSISTENT ELECTRO-THERMAL MODEL FOR ANALYZ-<br>EFFECT IN P-TYPE POLY-SI THIN-FILM TRANSISTORS    | -<br>23 |

|   |                                                                                                                                                            | Page |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 3.1 Introduction                                                                                                                                           | 23   |

|   | 3.2 The Framework for Modeling LTPS TFTs                                                                                                                   | 25   |

|   | 3.3 Thermal-Diffusion Model                                                                                                                                | 26   |

|   | 3.4 NBTI Model for TFTs                                                                                                                                    | 29   |

|   | 3.5 Simulation Results & Discussions                                                                                                                       | 31   |

|   | 3.6 Conclusions                                                                                                                                            | 37   |

| 4 | AN ENHANCED VOLTAGE PROGRAMMING PIXEL CIRCUIT FOR COMPENSATING GB-INDUCED VARIATIONS IN POLY-SI TFTs FOR AMOLED DISPLAYS                                   |      |

|   | 4.1 Introduction                                                                                                                                           | 38   |

|   | 4.2 Conventional and Proposed Pixel Structure                                                                                                              | 42   |

|   | 4.3 Derivation of Design Parameters                                                                                                                        | 45   |

|   | 4.4 Simulation Results and Discussion                                                                                                                      | 47   |

|   | 4.5 Conclusions                                                                                                                                            | 56   |

| 5 | VARIATION-TOLERANT AND SELF-REPAIR DESIGN METHODOLOGY FOR LOW TEMPERATURE POLYCRYSTALLINE SILICON LIQUID CRYSTAL AND ORGANIC LIGHT EMITTING DIODE DISPLAYS |      |

|   | 5.1 Introduction                                                                                                                                           | 57   |

|   | 5.2 Related Work                                                                                                                                           | 58   |

|   | 5.3 Proposed System                                                                                                                                        | 59   |

|   | 5.4 Device Modeling and Panel Simulation                                                                                                                   | 65   |

|   | 5.4.1 Device Modeling                                                                                                                                      | 66   |

|   | 5.4.2 LCD Panel Simulation                                                                                                                                 | 68   |

|   | 5.5 Conclusions                                                                                                                                            | 73   |

| 6 | THE IMPACT OF HOT CARRIER INJECTION (HCI) ON VOLTAGE CONTROL OSCILLATOR LIFETIME PREDICTION                                                                | 74   |

|   | 6.1 Introduction                                                                                                                                           | 74   |

|   | 6.2 Experiments                                                                                                                                            | 75   |

|   | 6.3 Results and Discussions                                                                                                                                | 76   |

|   | 6.4 Conclusions                                                                                                                                            | 82   |

|            | Page |

|------------|------|

| 7 SUMMARY  | 84   |

| REFERENCES | 86   |

| VITA       | 95   |

#### LIST OF TABLES

| Table |                                                                        | Page |

|-------|------------------------------------------------------------------------|------|

| 3.1   | Material Parameters for Thermal Analysis                               | 28   |

| 4.1   | Values of Circuit Parameters for the Proposed and Prior Pixel Circuits | 49   |

| 5.1   | Characteristics of LTPS TFT-LCD panels                                 | 69   |

. . .

#### LIST OF FIGURES

| Figu | ire                                                                                                                                                                                                                                                                                                                                      | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

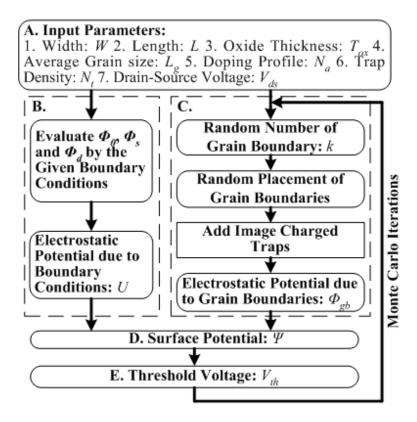

| 2.1  | Flowchart showing the simulation methodology for statistical analysis of $V_{th}$ variation induced by GBs                                                                                                                                                                                                                               | 10   |

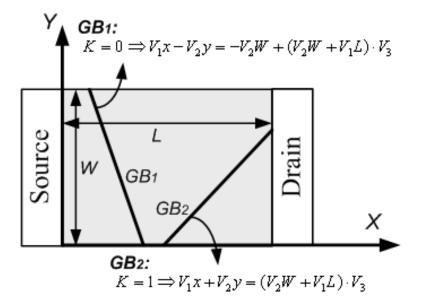

| 2.2  | Illustration of the randomly assigned plane equations for GBs in the channel of poly-Si TFT                                                                                                                                                                                                                                              | 14   |

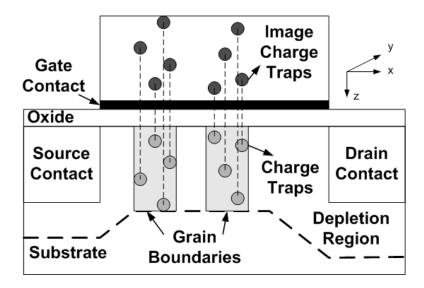

| 2.3  | Vertical cross section of TFT illustrating real and image charge traps in randomly distributed GBs                                                                                                                                                                                                                                       | 15   |

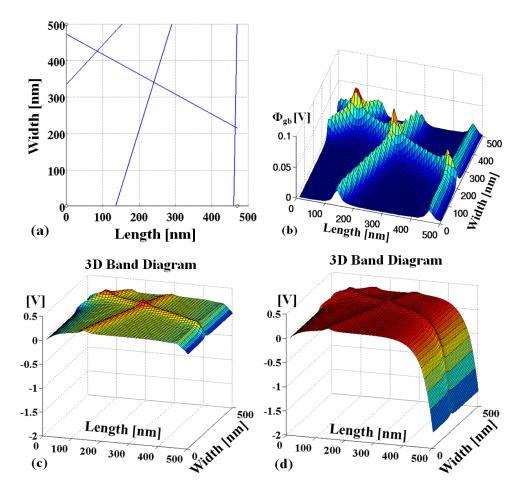

| 2.4  | (a) Vectors in random location and direction indicating the random orientation of four GBs in the TFT channel ( $W=L=0.5\mu m$ ), (b) surface potential due to charged traps in the GBs ( $\Phi_{gb}$ ) evaluated by Coulomb's law. 3-D Band diagram evaluated using the proposed model for (c) low $V_{ds}$ and (d) high $V_{ds}$       | 16   |

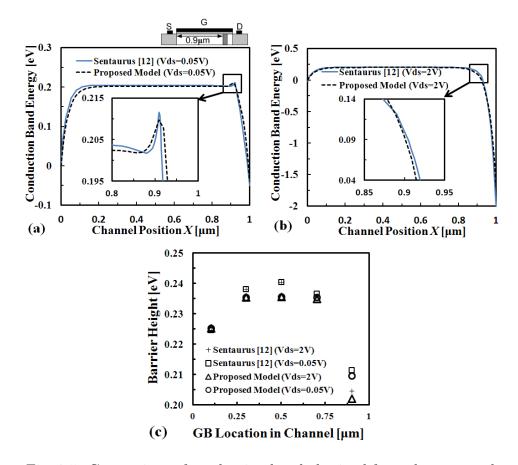

| 2.5  | Comparison of conduction band obtained from the proposed model and 3-D device simulator [15] for (a) low $V_{ds}$ and (b) high $V_{ds}$ with a GB 0.9 $\mu$ m from the source. ( $W=L=1\mu$ m) (c) Comparison of maximum barrier height from the proposed model and 3-D device simulator [15] for various $V_{ds}$ and locations of a GB | 18   |

| 2.6  | Comparison of conduction band obtained from the proposed model and 3-D device simulator [15] with different device length $L$                                                                                                                                                                                                            | 19   |

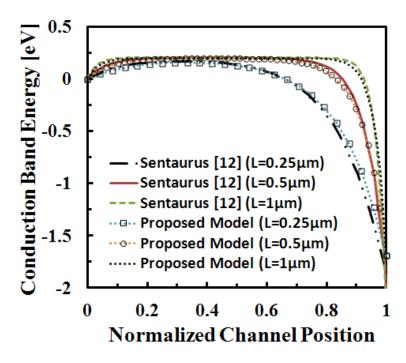

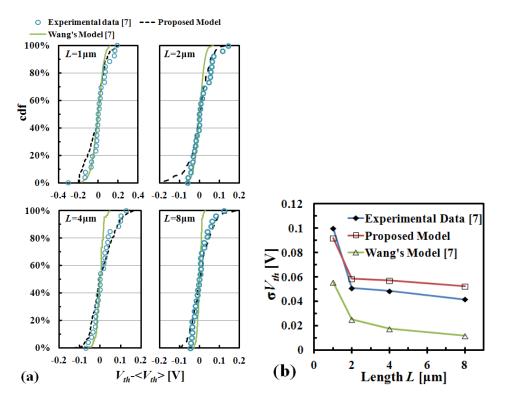

| 2.7  | Comparison of (a) cumulative distribution function and (b) standard deviation of $V_{th}$ obtained from the proposed model, experimental data [12] and Wang's model [12] with various device length $L$ . ( $t_{ox}$ =30nm, $W$ =8 $\mu$ m, mean $L_g$ =0.4 $\mu$ m, $V_{ds}$ =2 $V$ )                                                   | 20   |

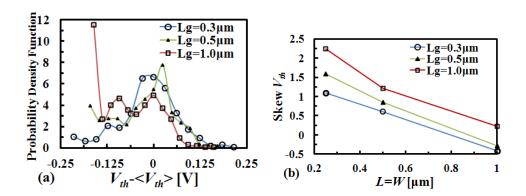

| 2.8  | (a) Comparison of threshold voltage distributions with different grain sizes using the proposed model. ( $L=W=1\mu m$ ) (b) Comparison of skew of threshold voltage with different grain sizes and device sizes for a sample set of 4500 TFTs using the proposed model                                                                   | 20   |

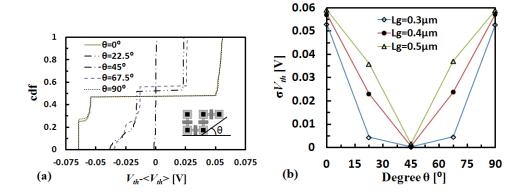

| 2.9  | Comparison of (a) cumulative distribution and (b) standard deviation of $V_{th}$ with different angle of periodic GBs and grain sizes using the proposed model                                                                                                                                                                           |      |

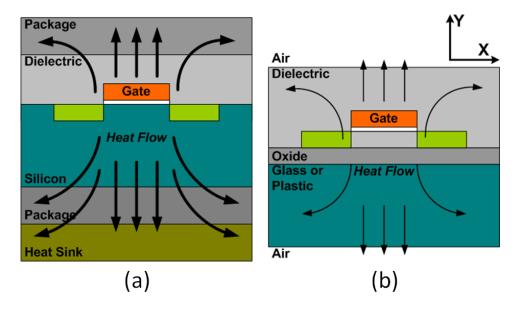

| 3.1  | Schematic of heat flow, denoted by arrows in (a) conventional bulk CMOS and (b) TFT technology                                                                                                                                                                                                                                           | 24   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

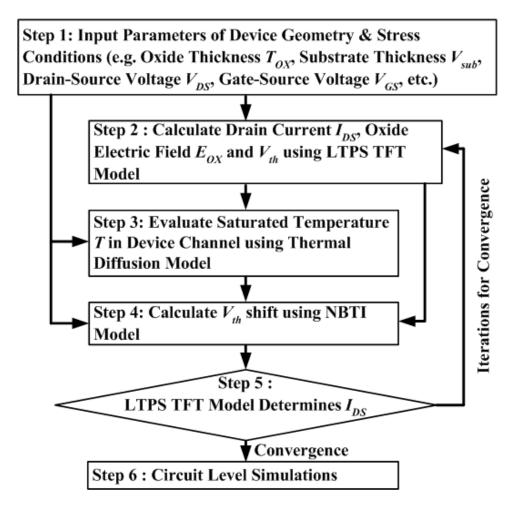

| 3.2  | Flowchart of the proposed self-consistent electro-thermal modeling methodology.                                                                                                                                                                                                                                                                                                                           | 27   |

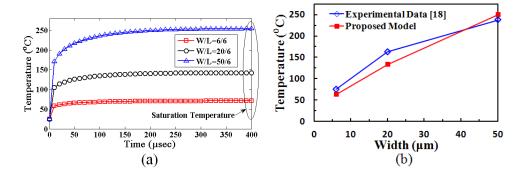

| 3.3  | (a) Transient temperature of device channel with three different device widths. Under the same stress condition $(V_g = V_d = -15V)$ , the channel temperature increases as the device width increases and saturates within microseconds. (b) Comparison of simulated channel temperature and experimental data [11] with different device width                                                          | 29   |

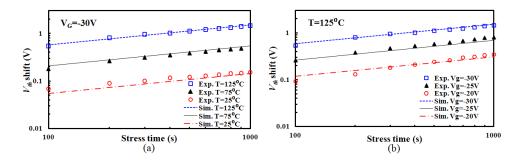

| 3.4  | Experimental [71] and simulated time evolution of threshold voltage shift for various temperature (a) and supply voltage (b). The used parameters are $n=0.42,E_a=0.404 \mathrm{eV}$ and $K_{ox}=3.84 \times 10^{10}.$                                                                                                                                                                                    | 30   |

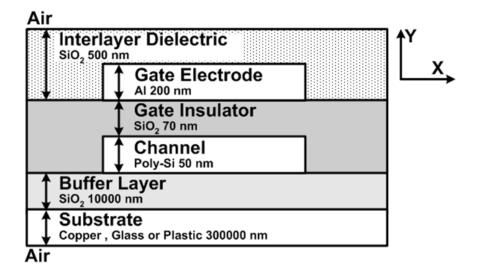

| 3.5  | Cross-sectional view of the simulated LTPS TFT. (X: width direction, Y: thickness direction)                                                                                                                                                                                                                                                                                                              | 31   |

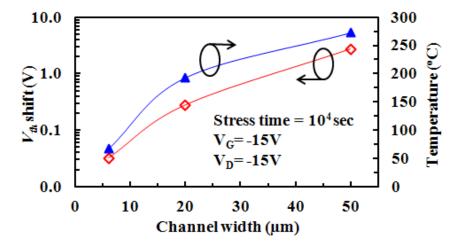

| 3.6  | Temperature and threshold voltage shift as a function of channel width. The dependence of channel temperature on channel width affects overall threshold voltage shift and must be taken into account for proper estimation of the lifetime of TFT-based circuits                                                                                                                                         | 32   |

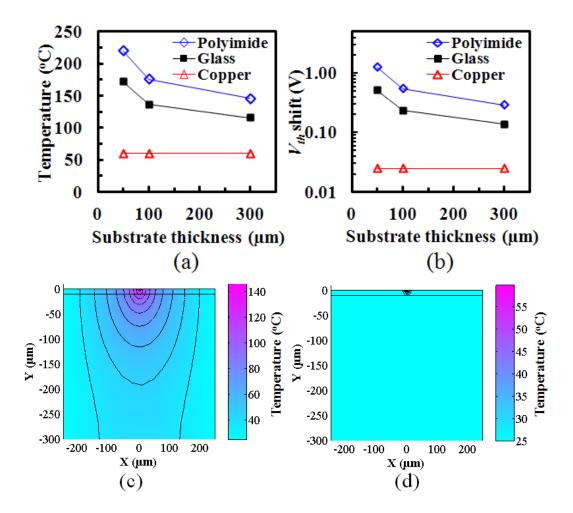

| 3.7  | Substrate material and thickness dependence of (a) channel temperature and (b) threshold voltage degradation of TFT with W/L=6 $\mu$ m/6 $\mu$ m under a dc bias stress ( $V_G$ = $V_D$ =-15V, stress time=10 <sup>4</sup> s). Spatial distribution of temperature in an LTPS TFT on (c) polyimide and (d) copper substrate with thickness of 300 $\mu$ m. (X: width direction, Y: thickness direction) . | 34   |

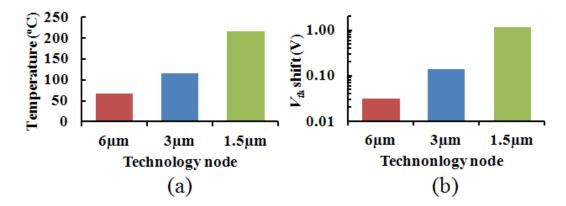

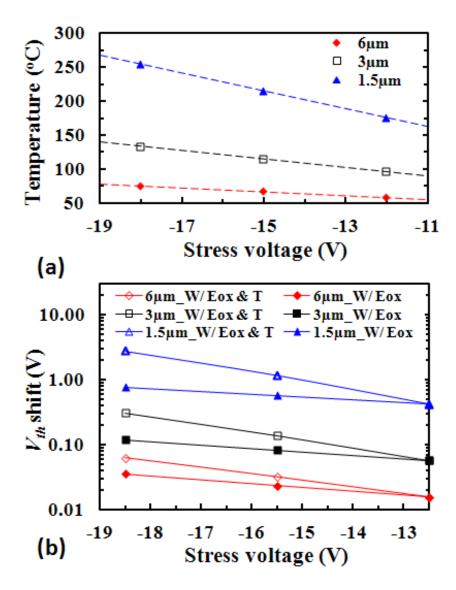

| 3.8  | Technology dependence of (a) temperature and (b) threshold voltage degradation of TFT with W/L=1 under a DC bias stress ( $V_G=V_D=-15$ V, stress time= $10^4$ s)                                                                                                                                                                                                                                         | 35   |

| 3.9  | (a) Stress voltage dependence of the temperature in LTPS TFTs (W/L=1) at different technology nodes. (b) Comparison of threshold voltage shift under various stress voltages (i.e. $-12V$ , $-15V$ and $-18V$ ) considering the effect of temperature and electric field                                                                                                                                  | 36   |

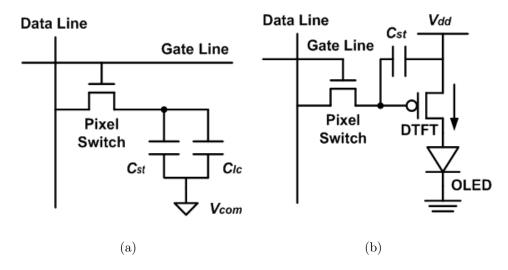

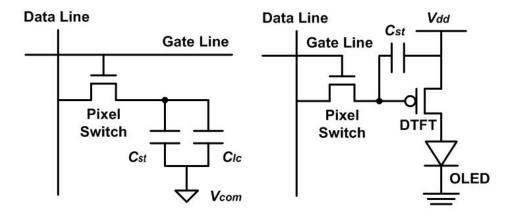

| 4.1  | Conventional pixel structure of (a) AMLCD and (b) AMOLED display.                                                                                                                                                                                                                                                                                                                                         | 39   |

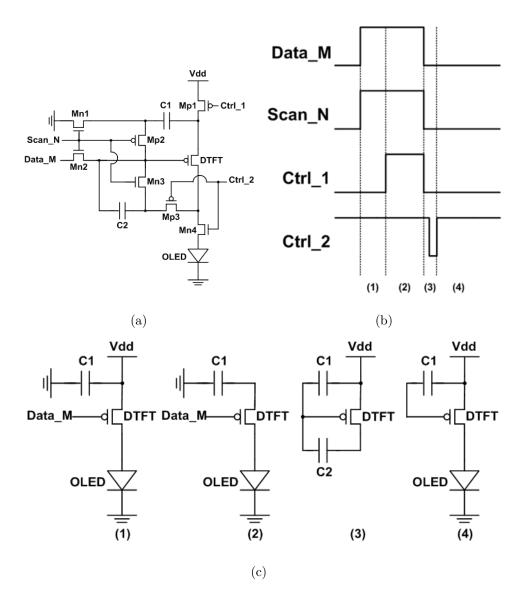

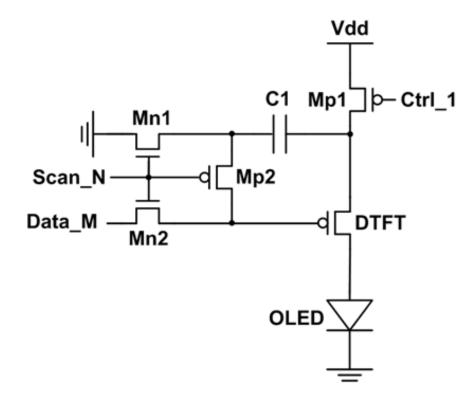

| 4.2  | (a) Proposed VPM pixel structure (b) Timing chart for the applied signals (c) Equivalent circuit of the proposed VPM pixel in each phase                                                                                                                                                                                                                                                                  | 43   |

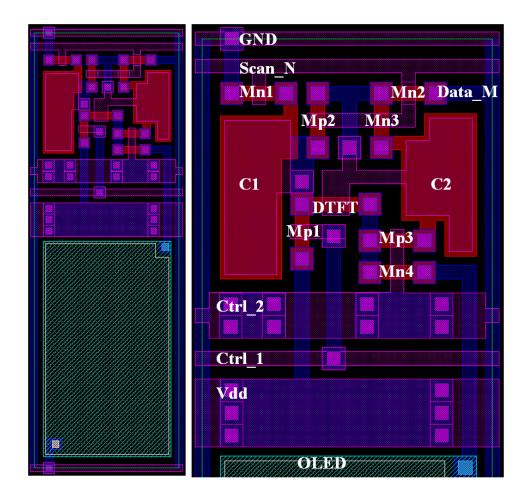

| 4.3  | The layout for the proposed pixel circuit. The subpixel size is $64\mu m \times 192\mu m$ which is suitable for 9.7 inches display with the resolution of 1024 x 768. The estimated aperture ratio is approximately 41%. Note that some layers have been hided for better illustration (e.g., $n+$ and $p+$ ).                                                                                            | 48   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

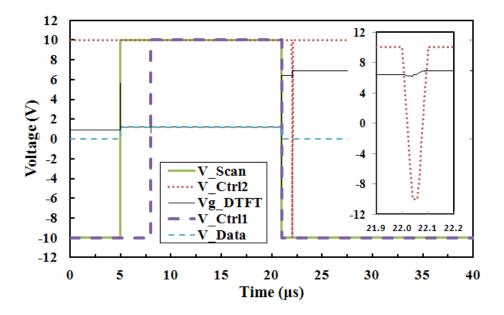

| 4.4  | The timing diagrams for the applied signals and $V_{g\_DTFT}$ for the proposed pixel circuit                                                                                                                                                                                                                                                                                                                                                                                                              | 49   |

| 4.5  | Prior VPM pixel structure in [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50   |

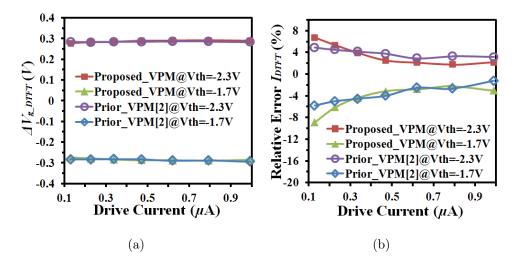

| 4.6  | (a) $\Delta V_{g\_DTFT}$ in the proposed and prior VPM pixel [18] with respect to nominal drive current for different threshold voltage shift. $\Delta V_{g\_DTFT}$ is the gate voltage difference between DTFT with and without $V_{th}$ shift in the display phase. (b) Relative error of drive current as a function of nominal drive current for different threshold voltage shift in DTFT of the proposed and prior VPM pixel [18]                                                                   | 51   |

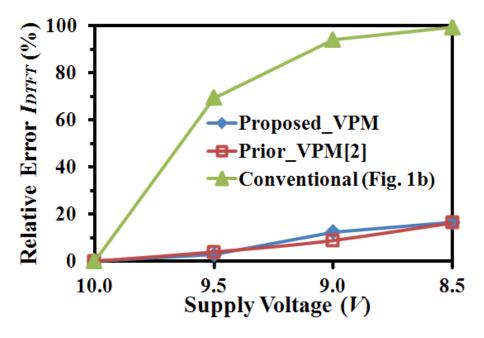

| 4.7  | Relative error of drive current as a function of supply voltage for the conventional, the prior VPM [18], and the proposed VPM pixel circuit.                                                                                                                                                                                                                                                                                                                                                             | 52   |

| 4.8  | (a) $\Delta V_{g\_DTFT}$ with respect to nominal drive current for different mobilities (60 and $140cm^2/V \cdot s$ ) of DTFT in the proposed VPM pixel circuit. (b) $\Delta V_{g\_DTFT}$ and the relative error of drive current as a function of mobility for the proposed and prior VPM pixel circuit [18]. (c) The relative error of drive current with respect to drive current for different mobility shift (60 and $140cm^2/V \cdot s$ ) of DTFTs in the proposed and prior VPM pixel circuit [18] | 53   |

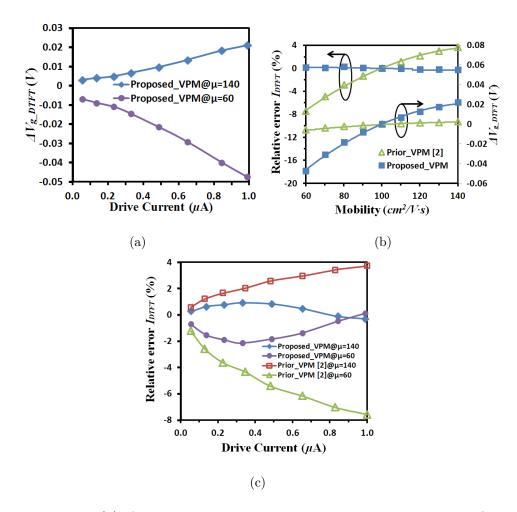

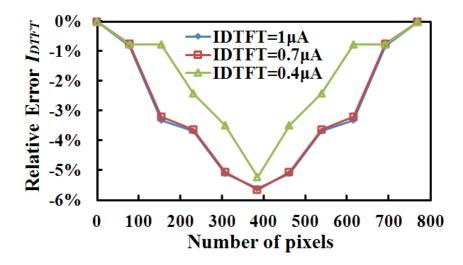

| 4.9  | (a) Statistical drive current distribution and (b) standard current deviation as a function of nominal drive current for DTFTs of the proposed and prior VPM pixel circuit [18], under combinational effect of threshold voltage and mobility shift.                                                                                                                                                                                                                                                      | 55   |

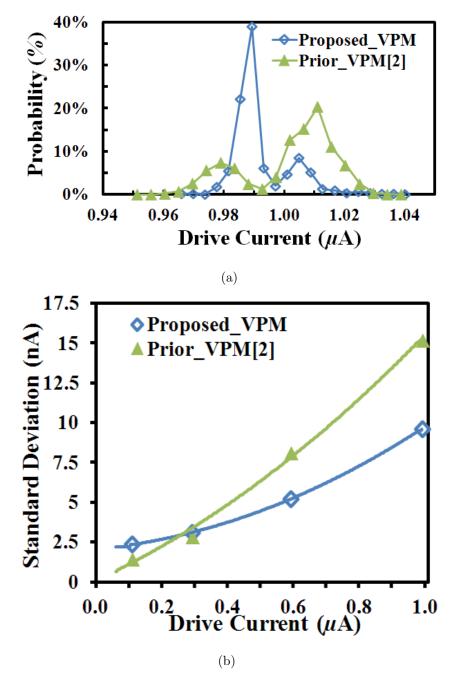

| 4.10 | The deviation of drive current with respect to the pixel number due to the parasitic capacitance and resistance of Crtl_2                                                                                                                                                                                                                                                                                                                                                                                 | 56   |

| 5.1  | Pixel structure of (a) LCD and (b) AMOLED display                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60   |

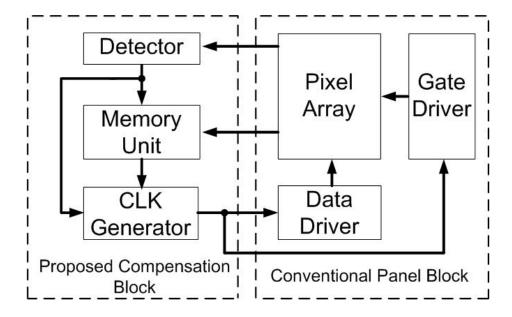

| 5.2  | Block diagram of proposed LTPS LCD panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61   |

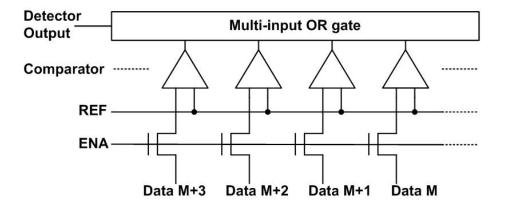

| 5.3  | Detector block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62   |

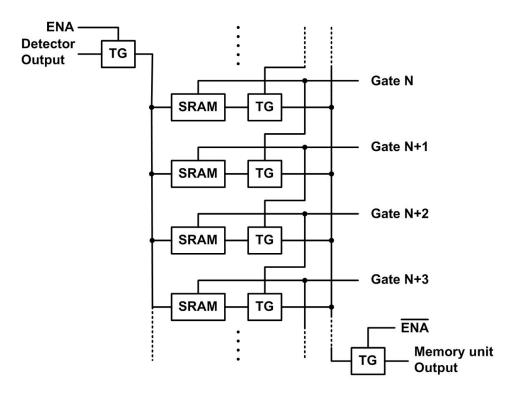

| 5.4  | Memory unit block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63   |

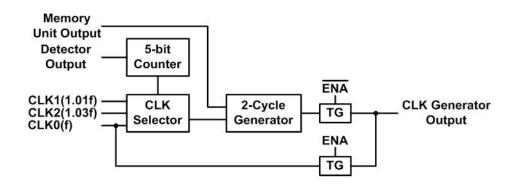

| 5.5  | CLK generator block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63   |

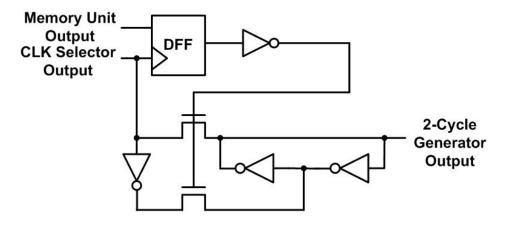

| 5.6  | Two-cycle generator block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64   |

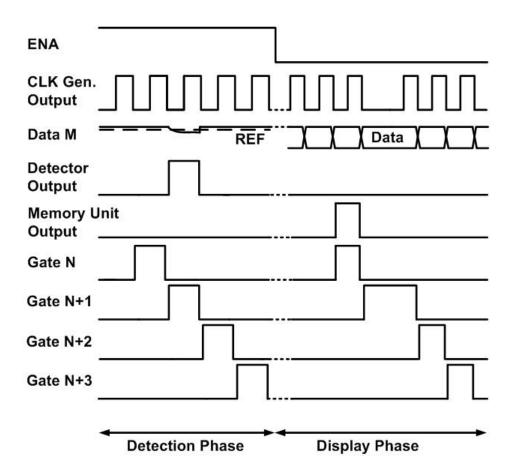

| 5.7  | Timing chart of proposed circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 64   |

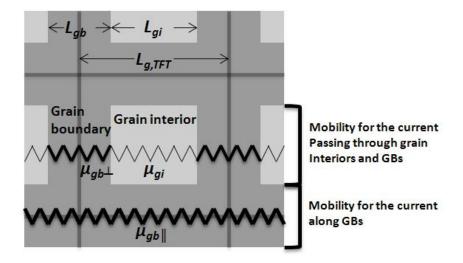

| 5.8  | Schematic of mobility model                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67   |

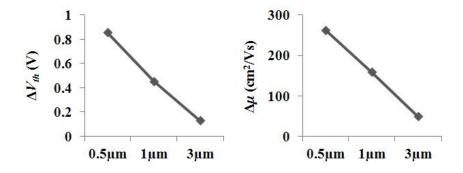

| 5.9  | Standard deviations of the threshold voltage and mobility at different technology nodes                                                                                                                                                                                                                                                                                                                                                                                                                   | 68   |

| Figu | re                                                                                                                                                                                                                                                                                      | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

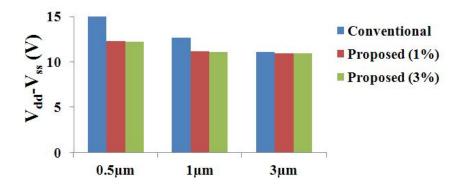

| 5.10 | The $V_{dd}$ - $V_{ss}$ of conventional and proposed methodology (1% and 3% increase of CLK frequency)                                                                                                                                                                                  | 71   |

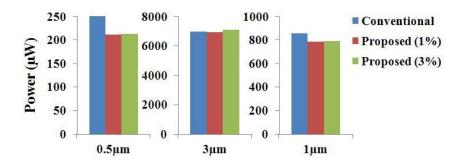

| 5.11 | Power consumption of conventional and the proposed methodology (1% and 3% increase of CLK frequency)                                                                                                                                                                                    | 71   |

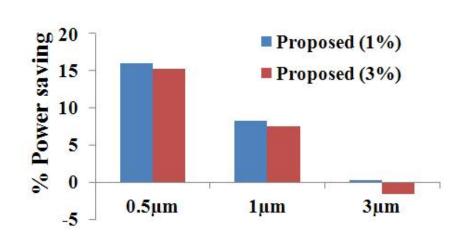

| 5.12 | Power saving of proposed methodology with $1\%$ and $3\%$ increase of CLK frequency at different technology nodes                                                                                                                                                                       | 71   |

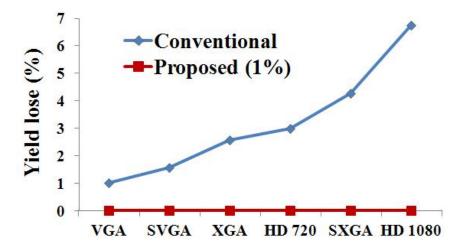

| 5.13 | Yield loss of conventional and proposed design with 1% increase of CLK frequency at different resolutions                                                                                                                                                                               | 72   |

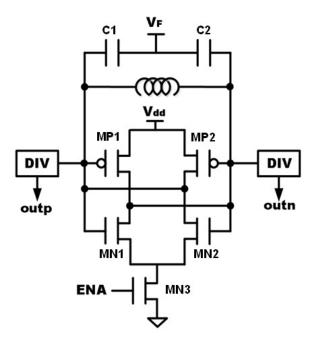

| 6.1  | Schematic of testing circuit, LC VCO. The circuit is implemented in 45nm SOI technology                                                                                                                                                                                                 | 76   |

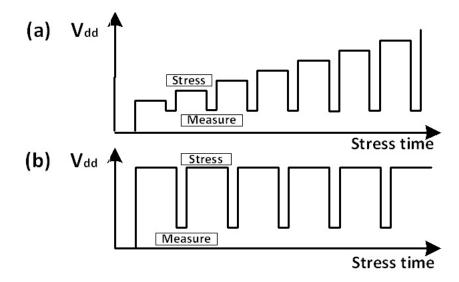

| 6.2  | Vdd-time traces for (a) RVS (ramped voltage stress) and (b) CVS (constant voltage stress) tests. Vdd is altered between stress and measurement. Operating frequency and startup voltage is measured to track the evolution of the performance degradation                               | 77   |

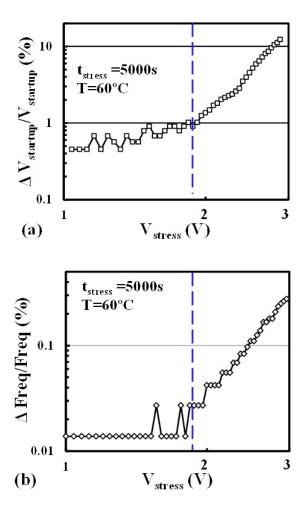

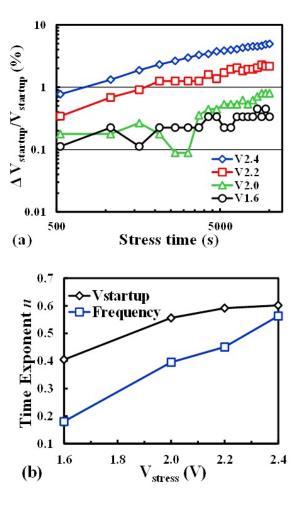

| 6.3  | Experimental results for (a) startup voltage degradation and (b) operating frequency degradation in RVS tests. A break in slope divides the degradation curve into high and low stress voltage regimes. The stress temperature is 60°C                                                  | 79   |

| 6.4  | (a) Startup voltage degradation with different operating frequency in RVS tests. Frequency dependence of degradation is shown in high voltage regime. (b) Linear dependence of startup voltage degradation on operating frequency at $V_{stress}{=}2.6\mathrm{V}.$                      | 80   |

| 6.5  | (a) Degradation of startup voltage as function of time for different stress voltages in CVS tests. (b) Time exponent of startup voltage and frequency degradation as function of stress voltage in CVS tests                                                                            | 81   |

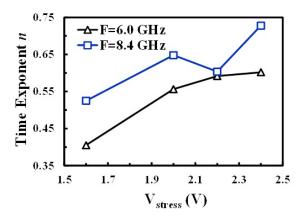

| 6.6  | Time exponent of startup voltage as function of stress voltage with different operating frequency in CVS tests                                                                                                                                                                          | 82   |

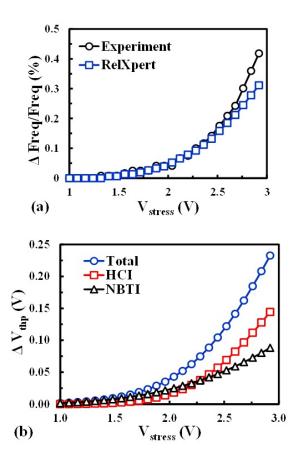

| 6.7  | (a) Comparison of frequency degradation from the simulation and the experimental data in RVS test. (b) Comparison of total threshold voltage degradation and HCI induced and NBTI-induced threshold voltage degradation and HCI induced and NBTI-induced threshold voltage degradation. |      |

|      | dations in the pMOS of differential pair from RelXpert results                                                                                                                                                                                                                          | 83   |

#### ABSTRACT

Ho, Chih-Hsiang Ph.D., Purdue University, December 2014. On Variability and Reliability of Poly-Si Thin-film Transistors . Major Professor: Kaushik Roy.

In contrast to conventional bulk-silicon technology, polysilicon (poly-Si) thin-film transistors (TFTs) can be implanted in flexible substrate and can have low process temperature. These attributes make poly-Si TFT technology more attractive for new applications, such as flexible displays, biosensors, and smart clothing. However, due to the random nature of grain boundaries (GBs) in poly-Si film and self-heating enhanced negative bias temperature instability (NBTI), the variability and reliability of poly-Si TFTs are the main obstacles that impede the application of poly-Si TFTs in high-performance circuits. The primary focus of this dissertation is to develop new design methodologies and modeling techniques for facilitating new applications of poly-Si TFT technology. In order to do that, a physical model is first presented to characterize the GB-induced transistor threshold voltage  $(V_{th})$  variations considering not only the number but also the position and orientation of each GB in 3-D space. The fast computation time of the proposed model makes it suitable for evaluation of GB-induced transistor  $V_{th}$  variation in the early design phase. Furthermore, a self-consistent electro-thermal model that considers the effects of device geometry, substrate material, and stress conditions on NBTI is proposed. With the proposed modeling methodology, the significant impacts of device geometry, substrate, and supply voltage on NBTI in poly-Si TFTs are shown. From a circuit design perspective, a voltage programming pixel circuit is developed for active-matrix organic light emitting diode (AMOLED) displays for compensating the shift of  $V_{th}$  and mobility in driver TFTs as well as compensating the supply voltage degradation. In addition, a self-repair design methodology is proposed to compensate the GB-induced variations for liquid crystal displays (LCDs) and AMOLED displays. Based on the simulation results, the proposed circuit can decrease the required supply voltage by 20% without performance and yield degradation. In the final section of this dissertation, an optimization methodology for circuit-level reliability tests is explored. To effectively predict circuit lifetime, accelerated aging (i.e. elevated voltage and temperature) is commonly applied in circuit-level reliability tests, such as constant voltage stress (CVS) and ramp voltage stress (RVS) tests. However, due to the accelerated aging, shifting of dominant degradation mechanism might occur leading to the wrong lifetime prediction. To get around this issue, we proposed a technique to determine the proper stress range for accelerated aging tests.

#### 1. INTRODUCTION

#### 1.1 Overview

Recently, TFTs have drawn increasing attention due to their unique advantages over the mono-crystalline silicon counterpart, such as low process temperature and low manufacturing cost. The low process temperature of TFT technology leads to flexibility in selection of the substrate material. Hence, TFTs can expand the application space of traditional silicon technology by enabling both fabrication of large-area electronics and device integration directly on transparent, light-weight and flexible substrates. Furthermore, the manufacturing cost of TFT-based circuit is significantly lower compared to conventional bulk CMOS technology because of the low temperature process, cheap and large substrate, and low-mask count [1]. These attributes make TFT technology attractive and suitable for several new applications including bio-sensors for real time personal health monitoring, flexible displays for portable electronic devices, radio frequency identification (RFID) for inventory and supply chain management, and smart clothing for home healthcare [2]- [5]. In particular, poly-Si TFT technology is expected to be one of the most promising candidates for such applications because of the higher mobility and the better reliability as compared with other TFT technologies [1]. However, suffering from the nature of the diverse and complicated grain distribution, a spread in the electrical characteristics of individual poly-Si TFTs (e.g.,  $V_{th}$  and mobility) is unavoidable [6] [7]. This not only results in high leakage and low drivability transistors, but also leads to large variations between adjacent poly-Si TFTs. Furthermore, since NBTI-induced degradation is triggered by the combined effects of high channel temperature and electric field, the device degradation due to NBTI in poly-Si TFT is more severe as compared to mono-crystalline silicon devices because of the low heat conductance of TFT substrates (e.g. glass and polyimide substrates). The heat generated from the device on silicon substrate can be easily spread and dissipated due to the excellent heat conductivity of the silicon substrate and the presence of heat sink. Conversely, the heat generated by a poly-Si TFT, is hard to exchange or diffuse through the substrate due to the poor heat conductivity of substrate and the absence of heat sink. Consequently, the temperature of poly-Si TFTs is expected to be higher, more localized and sensitive to device geometry, as verified by experiments [8]- [11]. Besides, it is experimentally observed that the spread of device characteristics due to GBs and NBTI deteriorates with device scaling [12]. Accordingly, such severe device variations and reliability concern not only limit the application of poly-Si technology in high performance circuits, but also inhibit the TFT scaling for low power, higher density, and higher integration. The purpose of this dissertation is to facilitate the poly-Si TFT technology for future applications by proposing new modeling and design methodologies in different levels of hierarchy (device and circuit).

#### 1.2 Poly-Si TFT Variation due to GBs

As we mentioned in the previous subsection, aggressive transistor scaling has aggravated the GB-induced  $V_{th}$  variation in poly-Si TFTs. These fluctuations are attributed to the random number, location and orientation of GBs in the device channel. This means that, GB-induced  $V_{th}$  modeling not only requires the knowledge of the number of GBs, but also the location and orientation of the individual GBs in the channel region. Hence, development of a  $V_{th}$  model considering GB in 3-D space is essential to capture the effects of GB on  $V_{th}$  of TFTs.

The existing simulation methods, which are based on drift-diffusion model [13] and ignore the impact of GB location [12], fail to meet efficiency and accuracy. In this work, we proposed a modeling framework which captures the effect of GBs on the  $V_{th}$  variations considering the number, the position, and the orientation of GBs and is based on fundamental laws of physics [14]. Compared to the existing literature,

the salient features of the proposed model are as follows: 1) it takes into account the position of GBs in the channel, 2) it is applicable to both long and short channel devices, 3) the model can consider different crystallization methods (i.e. periodic or randomly distributed GBs), 4) it is analytical (i.e. the threshold voltage are derived in closed form) and, 5) it is computationally fast ( 200x faster compared to 3-D device simulator [15] ).

#### 1.3 Poly-Si TFT Degradation due to NBTI

In addition to GB-induced  $V_{th}$  variations, NBTI causes severe time-dependent  $V_{th}$  degradations due to the low heat conductivity of TFT substrate. Therefore, to ensure robust and stable functionality for future poly-Si TFT-based circuits, it is essential to properly model and mitigate the effects of self-heating induced NBTI. In this thesis, an electro-thermal model which helps in accurately modeling NBTI degradation in poly-Si TFTs is developed [16]. One of important features of the proposed model is self-consistency. To have more accurate degradation prediction, self-consistency in degradation prediction model is needed. This is due to the fact that self-heating power and electrical field in the oxide decrease with time as the threshold voltage increases. Using the proposed framework, the significant impacts of device geometry, substrate material and thickness, and supply voltage on NBTI in poly-Si TFTs are shown. The simulation results reflect on the main obstacles for future flexible electronics and validate the need for integration of thermal-diffusion model and NBTI model for precisely predicting NBTI-induced degradation in poly-Si TFTs.

#### 1.4 AMOLED Pixel Circuit Design for Variation Compensation

AMOLED display features light weight, slim form factor and fast response time as compared to AMLCD. However, AMOLED is limited to small-sized applications due to 1) OLED degradation and 2) the high sensitivity of the drive current to the device variation and degradation of driving TFTs. OLED degradation refers to the progressive and spatial loss of efficiency over time during operation. To improve OLED degradation, research groups focus on (i) thermal stability, (ii) trap luminescence quencher formation, (iii) interface degradation, and (iv) anode instability of OLED [17]. On the other hand, to tackle the variation and degradation of driving TFTs, various compensation approaches have been investigated at the circuit level. Voltage programming methodology (VPM) is one of most common techniques for addressing the non-uniformity issue associated with AMOLED displays [18]. Although this methodology can effectively eliminate the effect of  $V_{th}$  shift in driving TFTs (DTFTs) and supply voltage degradation, it fails to mitigate the current variation induced by the mobility variation in DTFTs. The dependence of drive current to the mobility variation in poly TFTs is approximately 10\% [19], and hence, is not acceptable for high performance display applications. To cope with this problem, an improved VPM pixel circuit, which is capable of addressing mobility variation,  $V_{th}$ shift and supply voltage degradation, is proposed and verified [20]. Consequently, the immunity to device variations, fast programming time, and the simplicity of peripheral circuits, make the proposed VPM pixel circuit a promising candidate for large sized and high resolution AMOLED display applications.

#### 1.5 Self-repair Design Methodology for Variation Compensation

To ensure sufficient drivability in all pixel switches of LCD and AMOLED, increasing the supply voltage is the most commonly applied technique to account for the worst-case combination of variabilities. However, high supply voltage greatly increases the power consumption and worsens the reliability of TFTs [21]. Moreover, as the panel size or resolution is increased, yield loss, due to GBs and global variation, becomes more and more significant, even with a high supply voltage. Therefore, it is important to develop a new design methodology to properly deal with the variations in charging time of pixel switches and to reduce the resultant yield loss. In this thesis, a self-repair circuit is proposed to detect the locations and extend the charging time

of defective pixels (i.e. pixels with insufficient drivability) at the expense of slight increase in the operating frequency of peripheral circuits [22]. In other words, to maintain the same refresh rate, the charging time of each row of pixel array is slightly decreased for creating timing slacks which allow a few rows to execute two-cycle operation. Therefore, a lower supply voltage can be used while maintaining the same yield since defective pixels are allowed to have longer charging time. Consequently, with the proposed circuit, reliability and power consumption of LCD and AMOLED display can be improved.

#### 1.6 Circuit-Level Reliability Test Optimization

In nominal operating conditions, NBTI is expected as the dominant mechanism for circuit performance degradation, while hot carrier injection (HCI) can be neglected. However, accelerated aging which is commonly applied in reliability tests, such as constant voltage stress (CVS) and ramp voltage stress (RVS) tests [23]- [24], might shift the dominant degradation mechanism from NBTI to HCI leading to the wrong lifetime predictions. To distinguish HCI effects on a differential voltage controlled oscillator (VCO), different stress voltages and frequencies are applied in CVS and RVS tests [25]. Based on the results, we validated that the dominant degradation mechanism shifts from NBTI to HCI as stress voltage and frequency increase. Furthermore, a methodology defining proper stress conditions for accelerated circuit reliability tests is proposed for better lifetime prediction. Note that, although the tested circuit is based on SOI technology, the conclusions and the proposed optimization methodology in this study should also apply to TFT-based circuits.

#### 1.7 Organization

The rest of this thesis is organized as follows. In chapter 2, the physics-based 3-D model for GB-induced  $V_{th}$  variation is presented and statistical analysis for different electrical quantities and device and grain size is provided. Chapter 3 describes the

self-consistency electro-thermal model for NBTI effect in p-type poly-Si TFT with different substrate materials and device geometries. The proposed enhanced VPM pixel circuit for AMOLED display is discussed in Chapter 4. In Chapter 5, a new self-repair design methodology to compensate the GB-induced variations for poly-Si TFT based LCD and AMOLED display is reported. A methodology for optimizing circuit-level reliability tests is proposed in Chapter 6. Finally, Chapter 7 summarizes the contributions of this research and concludes the dissertation.

# 2. A PHYSICEL MODEL FOR GRAIN BOUNDARY INDUCED THRESHOLD VOLTAGE VARIATION IN POLY-SILICON THIN-FILM TRANSISTORS

Grain boundaries (GBs) in the channel region of poly-silicon thin-film transistors (Poly-Si TFTs) lead to large variations in the performance of TFTs (delay and power). In this work, we present a physical model to characterize the GB-induced transistor threshold voltage variations considering not only the number but also the position and orientation of each GB in the 3-D space. The estimated threshold voltage variations show a good agreement with experimental data and simulations performed by a numerical 3-D drift-diffusion device simulator. Using the proposed model, the impact of GBs on TFTs for various grain sizes, device sizes and source-drain voltages, is discussed in detail. Specifically, when the grain size is comparable to the size of the device, we observed that threshold voltage  $(V_{th})$  variations increase significantly and  $V_{th}$ -distributions are non-Gaussian. Finally, using our model we predict and demonstrate the GB-induced variations under different crystallization methods, such as sequential lateral solidification.

#### 2.1 Introduction

In contrast to conventional bulk-silicon technology, TFT features low manufacturing cost and flexibility in selection of the substrate material (i.e. glass and plastic). These attributes make TFT technology more attractive for new applications, such as flexible displays, bio-sensors and smart clothing [1]. In particular, poly-Si TFT technology is expected to be one of the most promising candidates for such applications because of higher mobility and better reliability as compared with other TFT technologies [1]. However, due to the random nature in the number, the position and the

orientation of grain boundaries (GBs) in poly-Si films, the device variation between adjacent poly-Si TFTs is large and cannot be modeled using current compact models. This can impede the application of poly-Si TFTs in high performance circuits and advanced displays (e.g. active matrix organic lighting diode display). Furthermore, it is evident that the continuing demand for device and supply voltage scaling aggravates GB-induced variations [12]. As a result, to design circuits with poly-Si TFTs for future applications, fast and accurate models that predict the GB-induced statistical fluctuations are essential [12].

For the analysis of statistical variations induced by GBs, there have been several models proposed by different research groups. The authors in [12] and [27] estimate mobility and  $V_{th}$  variations assuming that each GB has the same impact independent of the position and the orientation in the channel region. However, this assumption is valid only when the device size is larger than the average grain size. When the grain size is comparable to the device size, the number of GBs in the channel region decreases making the position of GBs more significant in determining the characteristics of a poly-Si TFT [28]. Thus, modeling threshold voltage variations accounting only the number of GB underestimates the real distribution [12]. For solving this issue, authors in [13] investigated the influence of GBs using a 2-D drift-diffusion device simulator. Although the position dependence of GB-induced variations can be precisely predicted, this methodology is not suitable for large-scale circuits due to significant computational cost to simulate a device. Furthermore, a 2-D device simulator is not able to capture the effects of GB orientation, which is a 3-D effect. Hence, there is a need for a new model which can efficiently capture the GB-induced statistical variability in scaled poly-Si TFTs.

In this section, a physics-based model is proposed for characterizing the threshold voltage variations for poly-Si TFTs which simultaneously takes into account the number, the position and the orientation of GBs [14]. The highlights of this model are:

1) it takes into account the exact position of GBs in the 3-D space, 2) it is applicable for both long and short channel devices, 3) the model is adaptive and can consider

different crystallization methods (i.e. different distribution of GBs, such as periodic or random distribution), 4) it is analytical, since expressions for the threshold voltage are derived in closed form, 5) it is computationally fast (200x faster) compared to 3-D drift-diffusion simulator [15]. The above features make the proposed model suitable for estimation of the parametric yield of poly-Si TFT-based circuit at the early design phase.

The rest of the paper is organized as follows. In subsection II we present in detail the proposed simulation framework. Then, the fundamental laws of physics and detailed statistical modeling methodology for evaluating GB-induced potential barrier, surface potential, and threshold voltage are explained. In subsection III, we verify the proposed model with both numerical 3-D drift-diffusion simulator [15] and experimental data [12]. The simulated statistical results for different device sizes, supply voltages and crystallization processes are also presented and discussed. Finally, we conclude this work in subsection IV.

#### 2.2 The Framework

The proposed approach determines the GB-induced threshold voltage variation by the evaluation of surface potential in the channel. The estimation of surface potential in this work is divided into two parts; a contribution that comes from the effect of the applied voltages, and a contribution, which is from the charge traps in the distributed GBs. Note that, the trap states in the grain and oxide-silicon interface are neglected, since the threshold voltage of poly-Si TFT is dominated by GBs in the channel region [1]. The flowchart of the proposed simulation framework is shown in Fig. 2.1. The details of the individual steps are presented in the following subsections.

Fig. 2.1. Flowchart showing the simulation methodology for statistical analysis of  $V_{th}$  variation induced by GBs.

#### 2.2.1 Input Parameters

In the beginning of the simulation, basic input parameters are necessary to define the geometry and the characteristic behavior of a poly-Si TFT. These input parameters include: 1) device width W, 2) device length L, 3) oxide thickness  $T_{ox}$ , 4) average grain size  $L_g$ , 5) doping profile  $N_a$ , 6) trap density of GBs  $N_t$  and 7) drain-source voltage  $V_{ds}$ .

#### 2.2.2 Modeling Electrostatic Potential due to Boundary Conditions

In this sub-section, the analytical solution of the electrostatic potential, which satisfies the boundary conditions at the gate, source and drain electrodes, is presented. The solution technique makes use of the superposition principle and divides the solution into the following terms [29]:

$$U(x,z) = \Phi(x,z) + \Phi_s(x,z) + \Phi_d(x,z) + \Phi_b(x,z)$$

(2.1)

where x is along the direction of device length, z is along the direction of substrate thickness,  $\Phi$  is the solution of the Poisson equation that satisfies the boundary conditions in the gate electrode,  $\Phi_s$ ,  $\Phi_d$  and  $\Phi_b$  are the solutions to Laplace equation that satisfy the boundary conditions at the source, the drain and the body electrodes, respectively. Note that  $\Phi_b$  is neglected in this work, since it is one order smaller than  $\Phi_s$  and  $\Phi_d$  [30]. By solving the following two equations, one can obtain  $\Phi$  [29]:

$$\Phi(x,z) = \Phi_0 \left( 1 - \sqrt{\frac{qN_a}{2\varepsilon_{si}\Phi_0}} z \right)^2$$

(2.2)

$$\frac{V_g - V_{fb} - \Phi_0}{3t_{ox}} = \sqrt{\frac{2qN_a\Phi_0}{\varepsilon_{si}}}$$

(2.3)

where  $\Phi_0$  is the long channel surface potential,  $V_g$  is the gate voltage and  $V_{fb}$  is the flatband voltage. The solutions for  $\Phi_s$  and  $\Phi_d$  are derived in [29] and can be expressed in the following forms:

$$\Phi_s(x,z) = \frac{b_1 \sinh\left(\frac{\pi(L-x)}{W_d + 3t_{ox}}\right) \sin\left(\frac{\pi(z+3t_{ox})}{W_d + 3t_{ox}}\right)}{\sinh\left(\frac{\pi L}{W_d + 3t_{ox}}\right)}$$

(2.4)

$$\Phi_d(x,z) = \frac{c_1 \sinh\left(\frac{\pi x}{W_d + 3t_{ox}}\right) \sin\left(\frac{\pi(z + 3t_{ox})}{W_d + 3t_{ox}}\right)}{\sinh\left(\frac{\pi L}{W_d + 3t_{ox}}\right)}$$

(2.5)

$$b_1 = \frac{4}{\pi} \Phi_{bi} - \frac{2}{\pi} \left( 1 - \frac{4}{\pi^2} \right) \left( 1 + \frac{6t_{ox}}{W_d} \Phi_0 \right)$$

(2.6)

$$c_1 = \frac{4}{\pi} \left( \Phi_{bi} + V_{ds} \right) - \frac{2}{\pi} \left( 1 - \frac{4}{\pi^2} \right) \left( 1 + \frac{6t_{ox}}{W_d} \Phi_0 \right)$$

(2.7)

where  $\Phi_{bi}$  is the built-in potential and  $W_d$  is the depletion width. Although these are the analytical solutions for 2-D devices, we applied it in 3-D devices by assuming identical electrostatic potential along y-axis (device width direction).

#### 2.2.3 Modeling Electrostatic Potential due to GBs

The GBs in the channel statistically affect the device performance through the concurrent fluctuations in the number, the position and the orientation [12]. Hence, for accurate prediction of threshold voltage variation, one of the most important steps is to determine the statistical distribution of GBs in the device channel since it dominates the statistical behavior of the device ensemble. In this subsection, we first model the number of GBs in the channel. Then, we present a statistical modeling methodology to capture the random placement of GBs. Finally, the method for evaluation of the electrostatic potential contributed by GBs ( $\Phi_{gb}$ ) is introduced.

#### Random Number of GBs

The number of GBs in the channel is statistically modeled using Poisson distribution which is normally used to express the probability of a given number of events occurring in a given area. Accordingly, the probability of having exactly k GBs (where k is a non-negative integer) in the channel can be expressed as:

$$P(k,\lambda) = \frac{e^{-\lambda} \cdot \lambda^k}{k!} \tag{2.8}$$

$$\lambda = \frac{L}{L_q} + \frac{W}{L_q} \tag{2.9}$$

where  $\lambda$  is the expected mean of the number of GBs in the channel, L and W are the device length and width respectively,  $L_g$  is the average grain size.

#### Random Placement of GBs

The GBs degrade the channel conductance by capturing free carriers in the trap states inside the GB area and creating a repulsive Coulomb blockade well surrounding the trap (i.e. potential barrier) [31]. Furthermore, the height of the potential barrier is not uniform along GB and depends on the applied voltage and the position of the

GB along the channel. This is attributed to the fact that, when large drain voltage is applied, the bottom of conduction band is lower near the drain edge [31]. As a result, the potential barrier formed by the GBs closed to the drain side becomes insignificant and has less impact on the peak of band diagram in the channel. On the other hand, if GB is positioned in the middle of channel, the peak of band diagram will increase significantly by the potential barrier induced by the GB. Hence, GBs near the center of channel have the largest influence on the current degradation [31]. In addition, different orientation of GBs resulting in different length and position of GBs in the channel would also cause different impact. As a result, we can expect that each GB in the channel has different effect on the device degradation due to its own position and orientation and should be taken into account for precise modeling of GB-induced degradation. To simulate the random placement of GB, a sequence of four random numbers  $(V_i)$  is generated. Three random numbers  $(V_1, V_2 \text{ and } V_4)$  are responsible for deciding the direction of the GB. Specifically,  $V_1$  and  $V_2$  decide the angle between the vector and x-axis  $(\theta)$ , while  $V_4$  is responsible for the incline direction of the vector (as illustrated in Fig. 2.2). The other random number  $(V_3)$  is for the location of the cross point between the GB and x-axis. The randomly distributed GBs are, therefore, related to these computer-generated random numbers by:

$$V_1 x + (1 - 2K) \cdot V_2 y = -KV_2 W + (V_2 W + V_1 L) \cdot V_3$$

(2.10)

$$0 < V_4 \le 0.5 : K = 0 \tag{2.11}$$

$$0.5 < V_4 \le 1 : K = 1 \tag{2.12}$$

The above plane equation describes the random position and direction of grain boundaries inside the channel region. Note that,  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  are random numbers uniformly distributed between 0 and 1. Hence, Eqs. 2.11-2.12 for  $V_4$  imply that the probability that the vector inclines to positive x-direction is the same as that for negative x-direction.

Fig. 2.2. Illustration of the randomly assigned plane equations for GBs in the channel of poly-Si TFT.

#### Evaluation of $\Phi_{gb}$

Having specified the location of each GB in the device channel, we can evaluate the electrostatic potential contributed by GBs ( $\Phi_{gb}$ ). Different from  $\Phi$ ,  $\Phi_s$ , and  $\Phi_d$ ,  $\Phi_{gb}$  is calculated using Coulomb's Law. By applying the method of images in which mirror charges are symmetrically added in the gate side (as illustrated in Fig. 2.3), the sum of the potential contribution of each charge trap to the evaluated point can be obtained [32]- [33]:

$$\Phi_{gb}(x, y, z) = \sum_{i=1}^{N} \left( \Phi_i(x, y, z) + \Phi'_i(x, y, z) \right)$$

(2.13)

$$\Phi_i(x, y, z) = \frac{-qD_{tr}}{4\pi\varepsilon_{si}R_i(x, y, z)}$$

(2.14)

$$\Phi_i'(x, y, z) = \frac{qD_{tr}}{4\pi\varepsilon_{si}R_i'(x, y, z)}$$

(2.15)

where  $R_i$  is the distance of the charge trap in the GB to the evaluated point,  $R'_i$  is the distance between the image charge trap and the evaluated point, and  $D_{tr}$  is

Fig. 2.3. Vertical cross section of TFT illustrating real and image charge traps in randomly distributed GBs.

the density of the charge trap. The assumption of  $\delta$ -function energy distribution for trap in GB is applied because of its efficiency and simplicity in addressing the essential features of poly-Si films [34]. However, it should be noted that other energy distributions for trap, such as exponential and Gaussian distribution [35]- [38], can easily be applied in the proposed framework. Fig. 2.4b shows the evaluated  $\Phi_{gb}$  with the specific placement of GBs (Fig. 2.4a). One can observe that the higher value of potential barrier in the intersection of two GBs which reflects the higher charge trap density of the crossing point.

#### 2.2.4 Modeling Surface Potential

Having determined the electrostatic potential induced by the applied voltages and the charge traps in GBs, we are now able to evaluate the surface potential. By applying superposition principle, the surface potential  $(\Psi)$  can be expressed as:

$$\Psi(x,y) = U(x,y,0) + \Phi_{ab}(x,y,0)$$

(2.16)

Fig. 2.4. (a) Vectors in random location and direction indicating the random orientation of four GBs in the TFT channel ( $W=L=0.5\mu m$ ), (b) surface potential due to charged traps in the GBs ( $\Phi_{gb}$ ) evaluated by Coulomb's law. 3-D Band diagram evaluated using the proposed model for (c) low  $V_{ds}$  and (d) high  $V_{ds}$ .

The evaluated band diagram with low and high  $V_{ds}$  are shown in Fig. 2.4c and 2.4d, respectively. It can be observed that, for high  $V_{ds}$ , the potential barrier induced by  $GB_4$ , which is located close to the drain contact, is nullified by the lateral drain-source electric field. As a result, the contribution of  $GB_4$  is negligible with regard to threshold voltage determination with high  $V_{ds}$ , which also verifies the position dependence of GB effect in our proposed model.

#### 2.2.5 Modeling Threshold Voltage

After obtaining the surface potential of a TFT (Fig. 2.4), the transistor threshold voltage can be determined. To define threshold voltage, the channel is divided into parallel "lanes" where the electrons move from source to drain contact laterally. Note that, if the current along the width direction becomes comparable to the current along the length direction (can occur if the device sizes are aggressive scaled), then the assumption that the current in each channel maintains the same direction from source to drain has to be corrected [39]. With such 1-D channel model (Gate slicing method [39]- [42]), the local threshold voltage  $(V_t)$  is determined by the maximum surface potential across the "lane".

$$V_t(y) = \max_{x=(0...L)} \left( \Psi(x,y) + \frac{\sqrt{2\varepsilon_{si}qN_a\Psi(x,y)}}{C_{ox}} \right)$$

(2.17)

Finally, threshold voltage is defined as the average of all the local threshold voltage and can be described mathematically by the following equation:

$$V_{th} = \frac{1}{W} \int_{0}^{W} V_{t}(y) dy$$

(2.18)

This process is repeated for all the samples (Monte Carlo analysis) which have different number and location of GBs in the channel region. Thus, the distribution of threshold voltage in ploy-Si TFTs is acquired.

#### 2.3 Simulation Results & Discussions

In this subsection, we first demonstrate the efficacy of the proposed framework with 3-D drift-diffusion device simulator [15] and experimental data [12]. The comparison with the previous statistical model [12] is also shown. Then, the discussions for simulated statistical results under various conditions are presented.

In Fig. 2.5 the conduction band diagrams (with one GB located close to the drain) obtained by our model and 3-D drift-diffusion simulator [15] are compared. It

Fig. 2.5. Comparison of conduction band obtained from the proposed model and 3-D device simulator [15] for (a) low  $V_{ds}$  and (b) high  $V_{ds}$  with a GB  $0.9\mu$ m from the source. ( $W=L=1\mu$ m) (c) Comparison of maximum barrier height from the proposed model and 3-D device simulator [15] for various  $V_{ds}$  and locations of a GB.

is evident that, as shown in Fig. 2.5a and 2.5b, the band diagram from the proposed model agrees well with that of a 3D device simulator under different  $V_{ds}$ . Furthermore, as depicted in Fig. 2.5c, the location dependence of barrier height is evident in both models; the lower barrier height can be observed when the GB is close to the source or drain side while the barrier heights are higher and have relatively the same value as the GB's move closer to the center of the channel. In addition, to demonstrate the applicability of the proposed model, we compared the conduction band diagrams for a wide range of technology nodes, sweeping the gate length from 250nm to  $1\mu$ m. It

Fig. 2.6. Comparison of conduction band obtained from the proposed model and 3-D device simulator [15] with different device length L.

is evident that the proposed model can be applied for both long and short channel devices, as shown in Fig. 2.6.

In Fig. 2.7, we show our statistical analysis in comparison with the analysis by previous works [12] and experimental data [12]. It is evident that the distribution and standard deviation of  $V_{th}$  from the proposed model follow the trend of experimental data closely for different device lengths with the same parameters (as shown in Fig. 2.7a). On the other hand, in Fig. 2.7b, the results obtained by the previous work show significantly smaller standard deviation in both large and scaled TFTs. This is attributed to the fact that the position dependence of GB-induced variation is not included in the previous model.

In addition, due to the large number of transistors in modern circuits, the knowledge of third order moment of the threshold voltage distribution is needed. Using the proposed model with statistical ensembles of 4500 TFTs, the real shape of threshold voltage distribution is observed. In Fig. 2.8, the results show that the GB-induced

Fig. 2.7. Comparison of (a) cumulative distribution function and (b) standard deviation of  $V_{th}$  obtained from the proposed model, experimental data [12] and Wang's model [12] with various device length L.  $(t_{ox}=30\,\text{nm},\,W=8\,\mu\text{m},\,\text{mean}\,L_g=0.4\,\mu\text{m},\,V_{ds}=2V)$

Fig. 2.8. (a) Comparison of threshold voltage distributions with different grain sizes using the proposed model. ( $L=W=1\mu m$ ) (b) Comparison of skew of threshold voltage with different grain sizes and device sizes for a sample set of 4500 TFTs using the proposed model.

Fig. 2.9. Comparison of (a) cumulative distribution and (b) standard deviation of  $V_{th}$  with different angle of periodic GBs and grain sizes using the proposed model.

threshold voltage distribution is positively skewed with increasing asymmetry as the grain size increases. The same situation occurs when the device size shrinks as shown in Fig. 2.8b. This analysis leads to the conclusion that the assumption of Gaussian distribution of threshold voltage may not be valid as we further scale the device size or enlarge the grain size.

The above simulation results (Fig. 2.8) indicate that the threshold voltage distributions are non-Gaussian when the device and grain size are comparable. For solving this issue, considerable research has been carried out for non-random grain growth [43]- [46], such as sequential lateral solidification (SLS) [43],  $\mu$ -Czochralski method [44], optical phase shift mask [45], and excimer laser irradiation with a-Si spacers [46]. Although these novel crystallization techniques are expected to suppress the device variation due to the spread in the number of GBs, the variation induced by different position and orientation of GBs cannot be avoided. As a result, it is crucial to predict the effect of the position and the orientation of the non-random GBs on device variation for ensuring the robust and stable functionality of poly-Si TFT circuitry. Due to the flexibility of proposed methodology, the effect of non-random GBs to  $V_{th}$  variation can be predicted by simply using periodic vectors for modeling the placement of GBs. Fig. 2.9 shows the cumulative distribution function (cdf) and

standard deviation of  $V_{th}$  for different orientation ( $\theta$ ) and grain sizes of periodic GBs induced by SLS process. It is evident that  $V_{th}$  variation has minimal value when  $\theta$ =45°, which agrees with the experimental results observed by the authors in [43].

#### 2.4 Conclusions

An efficient physical model for GB-induced threshold voltage variations in poly-Si TFTs has been developed by simultaneously considering the impact of the number, the position and the orientation of GBs. We verified the proposed model with 3-D drift-diffusion device simulator and experimental data and showed the effectiveness of the proposed model for different technology nodes and supply voltages. Using the proposed model, we have shown that, when the device size is comparable to the size of grain, the spread of threshold voltage increases significantly and the distribution is not Gaussian. These statistical attributes pose an intrinsic barrier to further scaling of the supply voltage and channel length. Furthermore, we have shown that the proposed simulation framework is flexible and can predict the effect of GBs for different crystallization process. The fast computation time of the proposed model makes it suitable for evaluation of GB-induced transistor  $V_{th}$  variation in the early design phase.

# 3. A SELF-CONSISTENT ELECTRO-THERMAL MODEL FOR ANALYZING NBTI EFFECT IN P-TYPE POLY-SI THIN-FILM TRANSISTORS

The electrical performance of low-temperature poly silicon (LTPS) thin-film transistor (TFT) has improved considerably in the last decade, due to the flourishing AMLCD (active-matrix liquid crystal display) industry. However, there is a need to further scale down LTPS TFT devices on flexible substrates to explore other application domains. In order to realize this goal, self-heating induced negative bias temperature instability (NBTI) in LTPS TFTs needs to be modeled to determine its effect on transistor degradation and to develop mitigation techniques. Although the characteristics of NBTI for TFTs are widely known, the effects of device geometry and substrate on temperature-dependent NBTI have not been considered. In this section, for the first time, a self-consistent electro-thermal model that considers the effects of device geometry, substrate, and stress conditions on NBTI is proposed. With the proposed modeling methodology, we show the significant impact of device geometry, substrate, and supply voltage on NBTI in LTPS TFTs.

#### 3.1 Introduction

It is obvious that, to facilitate LTPS TFT technology for new applications, further device scaling and integration of robust LTPS TFTs on flexible substrates are required [47]- [51]. Although several techniques have been explored for device scaling and fabrication processes allowing integration of LTPS TFTs directly on flexible substrates, degradation of LTPS TFTs due to self-heating induced NBTI [52] and ambient light [53] remains a critical issue. One of the most crucial reliability issues related to device scaling and flexible substrates is attributed to NBTI [54]- [57]. Experimen-

Fig. 3.1. Schematic of heat flow, denoted by arrows in (a) conventional bulk CMOS and (b) TFT technology.

tal data for TFTs has shown that the NBTI-induced degradation is triggered by the combined effect of high channel temperature and electric field [54]- [57]. Hence, as dimensions of TFTs are reduced to the submicron regime, the NBTI effect is expected to be more pronounced due to self-heating because of the increased power density. Furthermore, the flexible substrates, which usually have lower heat conductance (e.g. the heat conductance of plastic is about two orders of magnitude lower than that of silicon), aggravate the heat dissipation from the device, and therefore, the transistors show worse NBTI-induced transistor degradation. As shown in Fig. 3.1(a), the heat generated from the device on silicon substrate can be easily spread and dissipated due to the excellent heat conductivity of the silicon substrate and the presence of heat sink. Conversely, the heat generated by an LTPS TFT, as shown in Fig. 3.1(b), is hard to exchange or diffuse through the substrate due to poor heat conductivity of the substrate and the absence of heat sink. Consequently, the temperature of LTPS TFTs on flexible substrate is expected to be higher, more localized, and sensitive to device geometry, as verified by experiments [8], [9]- [11]. Therefore, to ensure robust

and stable functionality for future LTPS TFT-based circuits, it is essential to properly model and mitigate the effects of self-heating induced NBTI.

In this section, we develop a self-consistent electro-thermal model which helps in accurately modeling NBTI degradation in LTPS TFTs [16]. The impact of different substrate material and thickness, device geometry, and stress conditions on NBTI are incorporated in this model by integrating a 2D thermal-diffusion model and an empirical NBTI model [58]. Using the proposed framework, we investigate the impact of: (a) device geometry, (b) substrate, and (c) supply voltage on NBTI induced transistor degradation.