# Purdue University Purdue e-Pubs

**Open Access Theses**

Theses and Dissertations

Summer 2014

# A Lightweight N-Cover Algorithm For Diagnostic Fail Data Minimization

Shraddha Ghanshyam Bodhe *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_theses

Part of the <u>Electrical and Computer Engineering Commons</u>

Recommended Citation

Bodhe, Shraddha Ghanshyam, "A Lightweight N-Cover Algorithm For Diagnostic Fail Data Minimization" (2014). Open Access Theses. 405.

https://docs.lib.purdue.edu/open\_access\_theses/405

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

| By Shraddha Bodhe                                                                                                                                                                              |                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Entitled A Lightweight N-cover Algorithm for Diagnostic Fail Data Minimization                                                                                                                 |                                           |

| For the degree of Master of Science in Electrical and Computer                                                                                                                                 | Engineering                               |

| Is approved by the final examining committee:                                                                                                                                                  |                                           |

| IRITH POMERANZ                                                                                                                                                                                 |                                           |

| Chair<br>ANAND RAGHUNATHAN                                                                                                                                                                     |                                           |

| VIJAY RAGHUNATHAN                                                                                                                                                                              |                                           |

|                                                                                                                                                                                                |                                           |

| To the best of my knowledge and as understood by the student <i>Copyright Disclaimer (Graduate School Form 20)</i> , this thesis/Purdue University's "Policy on Integrity in Research" and the | dissertation adheres to the provisions of |

| Approved by Major Professor(s): IRITH POMERANZ                                                                                                                                                 |                                           |

| Approved by: M. R. Melloch  Head of the Graduate Program                                                                                                                                       | 07-24-2014<br>Date                        |

# A LIGHTWEIGHT N-COVER ALGORITHM FOR DIAGNOSTIC FAIL DATA MINIMIZATION

A Thesis

Submitted to the Faculty

of

Purdue University

by

Shraddha Bodhe

In Partial Fulfillment of the

Requirements for the Degree

of

Master of Science in Electrical and Computer Engineering

August 2014

Purdue University

West Lafayette, Indiana

#### **ACKNOWLEDGMENTS**

First of all, I would like to thank my research advisor, Prof. Irith Pomeranz, for providing me with the opportunity to work with her. She has been a source of inspiration and motivation throughout this research. I am deeply grateful to her for her patience, encouragement and support. The work done in this thesis would not have been possible without her guidance in my research, presentation and writing.

I would like to thank Prof. Anand Raghunathan for mentoring me throughout my Masters degree. I also owe a debt of gratitude to Prof. Vijay Raghunathan for his guidance and for serving on my thesis committee.

I would also like to thank Dr. Srikanth Venkataraman, Dr. Enamul Amyeen and other members of the diagnosis team at Intel for their support and feedback. Working with them has been a great learning experience. This research work has been sponsored by the Semiconductor Research Corporation (SRC). I am very grateful for their financial support.

I am also greatly thankful to my friends Vinayak Gokhale, Atreyee Ghosh-Pathe and Saurabh Wyawahare for always being there to encourage me. Finally, I would like to express my deepest gratitude to my parents for their love and support. They are my pillars of strength and have always inspired me to follow my dreams.

## TABLE OF CONTENTS

|                                                    | Page |

|----------------------------------------------------|------|

| LIST OF TABLES                                     | iiv  |

| LIST OF FIGURES                                    | v    |

| ABSTRACT                                           | vi   |

| 1. INTRODUCTION                                    | 1    |

| 1.1. Overview                                      | 1    |

| 1.2. Diagnostic fail data analysis                 | 4    |

| 1.3. Organization                                  |      |

| 2. LITERATURE REVIEW                               |      |

| 2.1. Test data reduction.                          |      |

| 2.2. Diagnostic fail data reduction                | 10   |

| 3. FAIL DATA MINIMIZATION                          |      |

| 3.1. Challenges posed by large volume of fail data |      |

| 3.2. Fail data minimization problem defined        |      |

| 3.3. Motivation behind our approach                |      |

| 3.4. Evaluation metrics                            | 16   |

| 4. THE N-COVER ALGORITHM                           |      |

| 4.1. The value of N                                |      |

| 4.2. Implementation of the N-cover algorithm       | 21   |

| 4.3. An illustrative example                       | 24   |

| 5. PERFORMANCE ANALYSIS                            | 29   |

| 5.1. Data set                                      | 29   |

| 5.2. Experimental results                          | 29   |

| 5.2.1. Diagnosis accuracy                          | 31   |

| 5.2.2. Decrease in diagnosis resolution            | 31   |

| 5.2.3. Fail data size reduction                    | 32   |

| 5.2.4. Increase in diagnosis speed                 | 32   |

| 6. FUTURE WORK AND CONCLUSION                      | 35   |

| 6.1. Future work                                   | 35   |

| 6.2. Conclusion                                    | 36   |

| LIST OF REFERENCES                                 | 37   |

## LIST OF TABLES

| Table     4.1 Sample fail data collected from the tester                                                                                                                                                                                                                                      | Page 25 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4.2 Output failure frequencies and their corresponding values for the sample fail dat of Table 4.1                                                                                                                                                                                            |         |

| 4.3 Updated values of covdiff after inclusion of every test in $T_{\text{red}}$                                                                                                                                                                                                               | 26      |

| 4.4 Tests selected by the N-cover algorithm to be included in the reduced test set $T_{re}$ are highlighted                                                                                                                                                                                   |         |

| 5.1 Evaluation metric values for 11 wafers from different fabrication labs. The last row gives the average values of diagnosis runtime before and after fail data reduction, diagnosis accuracy, decrease in resolution and the fail data size reduction over all the failing dies in a wafer | 30      |

## LIST OF FIGURES

| Figure                                                                                                                                                                 | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 Principle of Testing                                                                                                                                               | 1    |

| 1.2 Bitmapped failure response                                                                                                                                         | 2    |

| 1.3 Indexed failure response                                                                                                                                           | 2    |

| 1.4 Comparison of the number of failing test vectors that are collected by the tester and the number of failing test vectors that are enough for an accurate diagnosis | 5    |

| 1.5 N-cover algorithm as a preprocessing step between the tester data logs and the diagnosis procedure                                                                 | 6    |

| 4.1 Monotonically increasing relationship between the output failure frequencies and the absolute N values                                                             | 19   |

| 4.2 Monotonically decreasing relationship between output failure frequencies and the percentage of required goal coverage                                              | 21   |

| 4.3 Pseudocode for the N-cover algorithm for diagnostic fail data minimization                                                                                         | 22   |

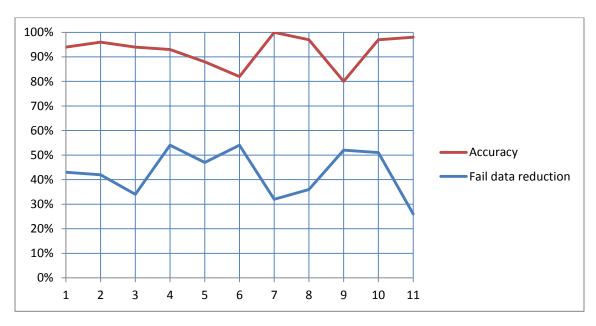

| 5.1 Summary of diagnosis accuracy and fail data size reduction results for 624 failing dies over 11 wafers                                                             | 34   |

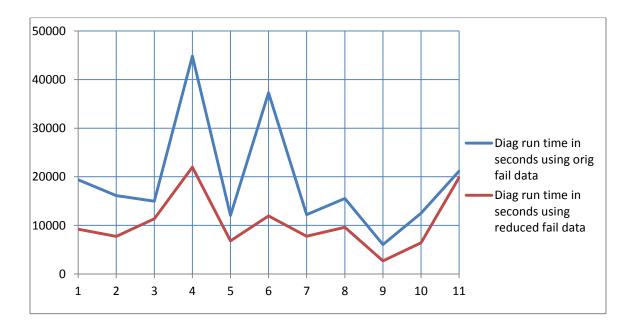

| 5.2 Summary of diagnosis run time using original fail data and reduced fail data for 624 failing dies over 11 wafers                                                   | 34   |

#### **ABSTRACT**

Bodhe, Shraddha G. M.S.E.C.E., Purdue University, August 2014. A lightweight N-cover algorithm for diagnostic fail data minimization. Major Professor: Irith Pomeranz.

The increasing design complexity of modern ICs has made it extremely difficult and expensive to test them comprehensively. As the transistor count and density of circuits increase, a large volume of fail data is collected by the tester for a single failing IC. The diagnosis procedure analyzes this fail data to give valuable information about the possible defects that may have caused the circuit to fail. However, without any feedback from the diagnosis procedure, the tester may often collect fail data which is potentially not useful for identifying the defects in the failing circuit. This not only consumes tester memory but also increases tester data logging time and diagnosis run time. In this work, we present an algorithm to minimize the amount of fail data used for high quality diagnosis of the failing ICs. The developed algorithm analyzes outputs at which the tests failed and determines which failing tests can be eliminated from the fail data without compromising diagnosis accuracy. The proposed algorithm is used as a preprocessing step between the tester data logs and the diagnosis procedure. The performance of the algorithm was evaluated using fail data from industry manufactured ICs. Experiments demonstrate that on average, 43% of fail data was eliminated by our algorithm while maintaining an average diagnosis accuracy of 93%. With this reduction in fail data, the diagnosis speed was also increased by 46%.

#### 1. INTRODUCTION

#### 1.1. Overview

The design and manufacture of an Integrated Circuit (IC) is a very involved and complicated process. Silicon in the form of a single-crystal wafer is the building block of IC fabrication. Typically, integrated circuits are produced in large batches on a single wafer. After manufacture the resultant wafer is cut into pieces, each containing a copy of the desired integrated circuit. Each of these pieces is called a *die* [1].

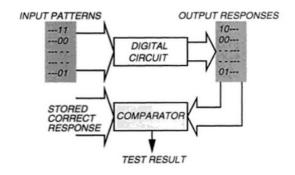

Due to the fabrication process variations and the translation of design to an actual chip on silicon, the manufactured dies may have defects. These defects are unintended differences between the implemented hardware and the intended design. Once an IC is manufactured, it has to go through a series of post-production tests to verify its functionality. This is called manufacturing testing [2]. It involves using binary patterns, also called as *test vectors*, which are applied at the inputs of the circuit. A collection of such test vectors is called *test set*. The response of the circuit to these test vectors is compared with the expected response. The circuit is said to pass if the responses match else the circuit fails. Figure 1.1 shows the basic principle involved in testing.

Figure 1.1 Principle of testing

VLSI testing is performed by automatic test equipments (ATEs). Modern ATEs are extremely powerful computers that are operated by test programs written in a high level language. For those chips that fail during testing, the location and cause of the failure needs to be determined so that remedial actions can be taken to improve the number of good chips being manufactured. Once a circuit fails, the ATE, referred to as *tester*, collects the failure responses of the circuit. A *failure response* comprises of a failing test and the corresponding list of outputs of the circuit where the test response was not as expected. A full failure response reports not only which tests failed but also at which outputs (flip-flops and primary outputs) the failures were observed. As with test vectors, circuit outputs are usually indexed to help with easy identification. Figures 1.2 and 1.3 give a simple example of bitmapped and indexed failure responses respectively. Each failing test number in the indexed failure response has a corresponding list of failing outputs. In the bitmapped failure response, a second dimension has been added for failing outputs.

|         |   |   | Tests |   |   |   |  |  |

|---------|---|---|-------|---|---|---|--|--|

|         |   | 1 | 2     | 3 | 4 | 5 |  |  |

|         | 1 | 1 | 0     | 0 | 1 | 0 |  |  |

|         | 2 | 0 | 0     | 1 | 0 | 0 |  |  |

| Outputs | 3 | 0 | 1     | 1 | 0 | 1 |  |  |

|         | 4 | 1 | 0     | 1 | 0 | 0 |  |  |

|         | 5 | 0 | 0     | 0 | 0 | 1 |  |  |

Figure 1.2 Bitmapped failure response

|              |    | Outputs |

|--------------|----|---------|

|              | 1: | 1, 4    |

|              | 2: | 3       |

| <b>Tests</b> | 3: | 2, 3, 5 |

|              | 4: | 1, 3    |

|              | 5: | 5       |

Figure 1.3 Indexed failure response

The tester records the actual responses measured at circuit outputs, and any differences between the observed responses and the expected responses are stored in the *tester data log*. In this thesis we assume that the tester data log records the indexed failure response for the failing chip. The set of all the failure responses for a failing circuit is called the *fail-data* of the circuit.

Diagnosis is the process of identification of the actual defects in the circuit. It attempts to derive from fail data the location inside the chip where the problem most likely started. In order to identify the systematic defects, a large volume of failed chips need to be diagnosed. This process of diagnosing a large number of failing dies or chips is called *large volume diagnosis*. The diagnosis procedure analyzes the fail data of the failing chips one at a time and gives a set of circuit elements, called *fault candidates*, which are identified as potential causes of failure for that particular chip. These candidates are further analyzed to identify and fix the problem.

The continual increase in the design complexity along with the technology scaling has enabled the designers to utilize a high level of integration in modern ICs. However, this has also made the use of complicated methodologies imperative for testing these chips. Every component in a circuit has a given set of test vectors needed to test it. As more and more components are placed on the chip, the number of test vectors required to test the chip proportionally increases. Execution of this large number of test vectors and collecting their corresponding failure responses increases the time required to test the chip substantially. Also, the tester memory size limits the amount of fail data that can be collected by the tester. One of the most challenging problems in the semiconductor industry today is dealing with the large amount of test data that is transferred between the tester and the chip [3] and the resultant increase in the test cost. An estimate of test cost on an ATE is given in [4] and the cost model in [5] gives an explanation of the cost metrics. Although the specific issues involved are different for test and diagnosis, both have to deal with large amounts of test data. The issues in diagnosis procedure are described next.

Following Moore's Law, the modern IC technology keeps shrinking and allows a single die to integrate millions of transistors. Because of this ever increasing design density, a large

volume of fail data is collected by the tester for a single die. The diagnosis procedure analyzes this fail data to provide valuable information about the type of defects and the possible defect locations that may be causing the chip to fail. The inspection of the large volume diagnosis results may also help point out any systematic issues in the fabrication process. Utilizing the diagnosis information, the yield can be improved by modifying the design rules for the chip or tuning the fabrication parameters. Therefore, improvement in the production quality of a circuit depends on effective diagnosis of the failures. However, with the increase in the amount of fail data, the tester data logging time and the time required for diagnosing a single failing die has increased. In addition it has also resulted in higher memory consumption by the diagnosis procedure. This adversely affects the diagnosis throughput which is defined as the number of failing dies diagnosed within a time frame using given computational resources.

#### 1.2. Diagnostic fail data analysis

The main motive for improving quality is economics. Ensuring high quality of integrated circuits is important for increasing the production yield and the reliability of the manufactured chips. With better production quality, the yield increases giving more good dies per the same wafer cost. A high quality product provides customer satisfaction and profitability of the business. Providing high quality diagnosis of failures is therefore essential for improving production, reducing time-to-market and increasing profits.

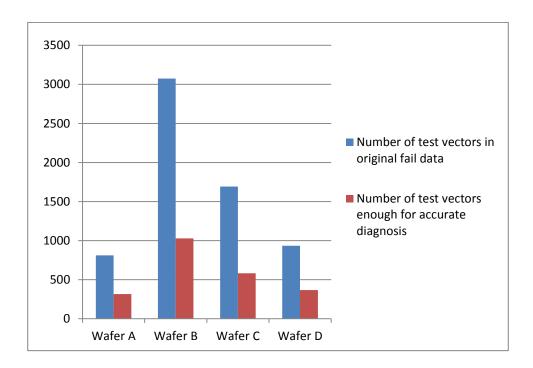

We analyzed a large amount of industry fail data and observed that without any feedback from the diagnosis procedure the tester collects data that is potentially not useful for diagnosis, consuming data logging time, tester memory and diagnosis time. Figure 1.4 shows the relationship between the number of failing test vectors identified by the tester and the minimum number of failing test vectors actually required by the diagnosis procedure to give the same fault candidates. The wafers A, B, C and D have 43, 84, 104 and 30 dies respectively. We see that without any loss of diagnosis accuracy (defined in section 3.4), on average about 36% of the original fail data is enough to diagnose the failures. Thus, it is reasonable to conclude that even though a large volume of fail data is being collected by the tester, only a small fraction of it actually contributes to the identification of the defects by the

diagnosis. This small subset of fail data when used for diagnosis would increase its speed and enable effective memory usage without impacting diagnosis quality. It would also point to ways to reduce the tester time that was spent in the collection of unnecessary fail data.

Figure 1.4 Comparison of the number of failing test vectors that are collected by the tester and the number of failing test vectors that are enough for an accurate diagnosis

The run time and the memory requirements of the diagnosis procedure are also dependent on the amount of fail data for that chip. The reason for this is that as the number of failing vectors in the fail data increases, the time required to simulate those failing vectors by the diagnosis procedure becomes high. So we can reasonably assume that if the amount of fail data used by diagnosis for correct defect identification is reduced, then the diagnosis would be faster. Thus, the focus of our research is to improve the performance of diagnosis by eliminating some part of the fail data collected from the tester such that the runtime of the diagnosis procedure are reduced without compromising the diagnosis quality. We call this approach *diagnostic fail data minimization*.

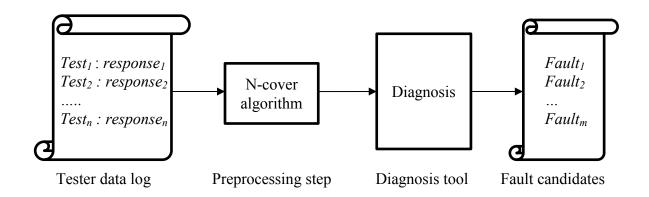

This thesis proposes an *N-cover algorithm* which is used as a preprocessing step for the diagnosis procedure. Figure 1.5 gives an overview of the implementation of the algorithm. The tester data log contains information about the failing test vectors and their corresponding failure responses. The algorithm processes the tester data log and gives the minimized fail data as an output. This minimized fail data is then used by the diagnosis procedure to generate a list of fault candidates. The N-cover algorithm ensures that the minimized fail data is such that high quality diagnosis of the failures is obtained. The proposed algorithm is designed to be independent of the chip design specifications, testing mechanism and the diagnosis procedure. Thus, it can be easily used for fail data minimization of different chip designs using various types of diagnosis tools.

Figure 1.5 N-cover algorithm as a preprocessing step between the tester data logs and the diagnosis procedure

#### 1.3. Organization

This section gives an overview of the organization of this document. In the next chapter we discuss some related works done in the field of test data reduction and fail data reduction for improving the throughput of manufacturing testing. In Chapter 3 we define the fail data minimization problem with respect to high performance diagnosis of the failing chips. We describe the motivation behind our approach to solve this minimization problem and introduce some related concepts. We also define the evaluation metrics used in this work to gauge the performance of our algorithm. Chapter 4 focuses on the development and

implementation of the N-cover algorithm. It describes each step of the algorithm in detail and provides an illustrative example for better understanding. The performance analysis of the N-cover algorithm is provided in Chapter 5. We describe in detail the results obtained when the N-cover algorithm was used for the fail data minimization for industry fabricated chips. Chapter 6 concludes this thesis by presenting conclusions from this research and discusses areas of further work.

#### 2. LITERATURE REVIEW

In recent times, management and analysis of large volume of data for test and diagnosis has become a major contributor to the test cost of an IC. Past approaches for improving throughput using reduction of data can be broadly classified in two categories, namely, data reduction for test and fail data reduction for diagnosis. The test data reduction techniques focus on reducing the test application time and tester storage requirements for a chip. Some test data reduction techniques enhance diagnosis performance while others deteriorate it. The diagnosis based approaches aim at minimizing the amount of fail data required to diagnose a single failing die without impacting the diagnosis quality. The diagnostic fail data minimization may or may not help in reducing the tester data collection time. Thus, these two categories are not mutually exclusive. The work done in this thesis belongs to the second category as our aim is to reduce the amount of fail data required for accurate diagnosis of failing ICs to improve diagnosis speed and performance.

#### 2.1. Test data reduction

Researchers have explored various techniques for test data reduction in the past. *Test stimulus compression* [6-16] has been at the forefront of solutions to reduce test costs through reduction in tester storage and test application time. The idea of test stimulus compression is to compress the amount of input test data that is stored on the tester. It reduces the amount of tester memory required and also the test time because less data has to be transferred between the tester and the chip. Test stimulus data is inherently highly compressible because of the presence of don't cares (unspecified values) in the test vectors that can be filled with any value without impacting fault coverage. As a result, lossless compression techniques can be used to significantly reduce the test stimulus data that must be stored on the tester. The test stimulus compression makes use of various encoding

techniques to compress data for test volume reduction. State-of-the-art techniques for data compression such as Mentor Graphics EDT [6], Synopsys DFTMAX Ultra [7] and other vendor tools use structural information for fault simulation, scan chain synthesis and test generation with compression. Other techniques for test stimulus compression like dictionary coding [8, 9], and Huffman coding [10] have also been studied in the literature.

Another important approach for test data reduction is *compaction*. In the context of test generation, the test set compaction [17-26] approach works on the notion that if smaller number of test vectors is applied to test the IC, the execution time of the tester and the amount of data generated will be less. Static compaction [22-24] attempts to combine and remove certain vectors after the test set has been generated whereas the dynamic compaction [25, 26] is integrated in the test generation procedure itself. Compaction can also be performed at the outputs of the circuit when test vectors are applied to it during test. The purpose is to reduce the amount of test response that needs to be transferred back to the tester. While the test stimulus compression is lossless, test response compaction is lossy. Test response compaction converts long output responses into short signatures. Because the compaction is lossy, some of the fault coverage can be lost due to aliasing when a faulty output response signature is identical to the fault-free output response signature. This would adversely affect the diagnosis performance. Three types of test response compactors are proposed in the literature [25]: time compactors [26], space compactors [27], and finite memory compactors [25]. Time compactors are sequential circuits that combine the current test response with previous test responses to generate signatures for fault detection [26]. Time compaction is usually performed by finite state machines such as linear feedback shift registers (LFSRs) and multiple input shift registers (MISRs). Space compactors [27] are combinational circuits which accommodate unspecified values (X). They combine the outputs of the chip under test to reduce the data volume and the number of output pins to as few as one pin. Finite memory compactors use feed forward sequential circuits and can also accommodate Xs in the test responses [25].

#### 2.2. Diagnostic fail data reduction

The analysis of large volume of production fail data is necessary to identify the systematic defects in the dies. Diagnosis procedure helps to locate the root cause of failures which can then be analyzed and fixed. Previous research in the field of fail data volume minimization for diagnosis has shown that it is possible to reduce the fail data significantly without severe loss of diagnosis accuracy. The work done in [28] showed that fail data collected by the tester can be reduced by about 30% while maintaining diagnosis accuracy greater than 90%. Their work uses various statistical learning methods to predict the minimal amount of fail data that is sufficient to obtain a good quality diagnosis. The prediction model is learned from a history of fail data collected for a set of failing ICs. The learned model is then used in production to predict the termination point of fail data collection for ICs resulting in the reduction of tester data logging time. In this work, the use of statistical learning makes it imperative for the algorithm to spend a significant amount of time learning and developing the prediction model. Even with the use of these complex learning techniques, a size reduction of more than 30% leads to a significant decrease in diagnosis accuracy.

It is remarkable that throwing away almost a third of the fail data generally retains the original data's ability to diagnose failures. This retention of failure detection ability can also be observed by the use of some other technique for reduction. In another research presented in [29], they propose an incremental strategy for reducing the cost and efforts for diagnosis by implementing a step-by-step selection of the tests to be executed from the set of available tests. Their selection criterion is based on a metric derived from the maximization of diagnostic information. They use probabilistic reasoning engines to stop the test execution when additional test outcomes would not provide further useful information for identifying the faulty candidate. Thus, with less number of tests being executed, the amount of fail data collected by the tester is reduced. This approach achieves the reduction in number of tests executed ranging from 32% to 88%. The entry point of their algorithm utilizes the model of the circuit under test which gives a summary of the relationship between the components of the circuit, the tests to be executed and the fail data from the tester. As a result, this approach

is heavily dependent on the fault model abstraction, diagnostic information and system specifications.

Despite these encouraging results for fail data minimization, there is clearly more room for improvement. The goal of our work is to explore methods to reduce the fail data further without sacrificing diagnosis accuracy or resolution.

#### 3. FAIL DATA MINIMIZATION

One of the major challenges in the semiconductor industry today is to establish a correlation between the fail data collected by the tester to the underlying defects in the chips. The diagnosis procedure plays a major role in the analysis of large volume of fail data in order to locate the actual defects in the chip.

#### 3.1. Challenges posed by large volume of fail data

The large fail data volume causes major concerns for achieving high performance testing and diagnosis. In order to test high density complex ICs, the tester needs more number of test vectors. The application of large number of test vectors results in the generation of huge amount of fail data and an increased test application time. To facilitate better analysis, additional fail information beyond a simple pass/fail is collected into a fail log. The fail log typically contains information about when (tester cycle), where (at what output), and how (logic value) the test failed. The increase in the generation of fail data volume is proportional to the time required by the tester to collect it in the fail logs. High test execution and data logging time causes a considerable increase in the overall tester run time, which in turn increases the test cost.

Also, the collection of large volume of fail data for diagnosis is limited by tester buffer sizes. The storage of fail data of a typical modern IC with millions of gates will require up to hundreds of giga-bytes of memory. If the tester buffers are inadequate for the storage of fail data, the test execution may either get terminated without collecting enough information for diagnosis or the tester will wait for the buffers to free up so that it can resume the data collection.

Furthermore, the time required to diagnose the failures of a single die keeps increasing with the increase in the amount of fail data. More the fail data volume, higher is the number of test vectors that need to be simulated. Consequently, more failure responses are generated and analyzed by the diagnosis procedure. Typically the diagnosis procedure can be made more efficient by processing multiple dies together. However, the physical memory does not increase as fast the amount of fail data generated creating a bottleneck. In spite of using multiple processors, the numbers of diagnosis programs that can run parallel are limited. Thus, the diagnosis throughput and performance suffers because of large volume of fail data.

#### 3.2. Fail data minimization problem defined

With the increasing demand for high performance volume diagnosis, it has become essential to improve its throughput. The diagnosis procedure should be able to process a large number of failing chips within a short period time using reasonable computational resources and without deteriorating the diagnosis accuracy. Various techniques have been proposed to improve the performance of the diagnosis procedure, such as fault dictionaries [30-32], machine learning [33], pattern sampling [34], design partitioning [35] and GPU-based simulation [36]. The purpose of this work is to improve diagnosis performance by minimizing the amount of fail data that it needs to analyze to identify the defects in the chip. This would enable the diagnosis of large number of failing chips in a short time frame.

Diagnostic fail data minimization is an optimization problem with the following goal: to find a minimum cardinality subset of the fail data which when used for diagnosis of the failing chip will not have any negative impact on the diagnosis accuracy or resolution. In general, the diagnostic fail-data minimization problem has two aspects:

- 1. Minimize the amount the fail data required to diagnose the failures of a chip

- 2. Maintain the quality of diagnosis after the fail data is reduced.

The minimization algorithm when applied dynamically while the tester is collecting the fail data, results in the reduction of tester data logging time. However, if the minimization is performed after all the fail data has been collected in the tester data logs then it will only help

improve diagnosis speed and not tester time. The formal definition of the diagnostic fail data minimization problem is as follows:

**Given:** A set of failing test vectors  $T = \{t_1, t_2, t_3... t_n\}$  such that each vector  $t_i$  in T produces a fail response  $r_i$ . Using T for diagnosis gives the fault candidate list  $CAND_{golden}$ .

**Find:** A minimal subset of failing test vectors  $T_{red} \subseteq T$ , comprising of test vectors  $m_0$ ,  $m_1$ ,  $m_2$ ...  $m_s$  such that each  $m_i$  has a fail response  $p_i$ . The fault candidate list  $CAND_{new}$  generated by the diagnosis procedure using  $T_{red}$  is such that  $CAND_{new} = CAND_{golden}$ .

Each of the fail responses  $r_i$ ,  $p_i$  constitutes a list of outputs that failed after the application of the test vectors  $t_i$ ,  $m_i$  respectively. For example if  $t_0$  has a fail response  $r_0 = \{o_1, o_2, o_3\}$ , it means that the test  $t_0$  failed at outputs  $o_1$ ,  $o_2$  and  $o_3$ .

Part of the process of minimization is to identify the fail data that is potentially not useful for the diagnosis of failures. In other words we need to identify the failing tests that are redundant. Redundancy can be identified by considering the failing tests to be *covering* the failing outputs. In the previous example we can say that the test  $t_0$  covers the outputs  $o_1$ ,  $o_2$  and  $o_3$ . As we are discussing the concept of covering of a set of elements, it is important to discuss the *set cover problem* [37]. The mathematical definition of set cover problem is as follows:

Given a set of elements  $\{1, 2, 3, ..., m\}$  (called the universe) and a set S of n sets whose union equals the universe, the set cover problem is to identify the smallest subset of S whose union equals the universe. For example, consider the universe  $U = \{1, 2, 3, 4, 5\}$  and the set of sets  $S = \{\{1, 2, 3\}, \{2, 4\}, \{3, 4\}, \{4, 5\}\}$ . Clearly the union of S is U. However, we can cover all of the elements with the following, smaller number of sets:  $\{\{1, 2, 3\}, \{4, 5\}\}$ .

The set-cover problem is proved to be NP-complete [38]. Researchers in the area of computing have proposed varied exact and heuristic approaches to get a near optimum solution of the set-cover problem. Some complex approximation algorithms have been studied in [39, 40]. For most of the approaches, improvements come with a significant increase in computation cost. The *greedy approximation algorithm* [37] picks the set *S* that

covers the greatest number of remaining elements that are uncovered at each stage in polynomial time complexity.

#### 3.3. Motivation behind our approach

A crucial part of the diagnostic fail data minimization problem is ensuring that the quality of diagnosis does not deteriorate with the use of reduced fail data. This implies that when covering fail responses, we need to exercise some constraints for maintaining diagnosis accuracy and resolution. Using the basic concepts of the greedy set covering discussed above, we developed a sophisticated fail data minimization algorithm which strives to achieve failure response coverage, maintain the quality of the diagnosis and also provide substantial fail data volume reduction. We will now discuss the rationale behind our approach for solving this problem.

In this work, we analyzed the fail data collected by the tester and tried to find the subset of fail data that maintained the diagnosis quality. For this purpose, it is important to evaluate each failing test according to its ability to identify the actual defect locations in the chip. For example, suppose a test  $t_1$  produces failures at the outputs  $\{p, q, r\}$  and a test  $t_2$  at outputs  $\{q, r\}$ . A traditional cover would include  $t_1$  in the reduced test set as it covers all the failures in the universe and drop  $t_2$ . However, for diagnosis purpose it may be important to include  $t_2$  as it gives the information that the outputs q and r are more susceptible to failure than p. Dropping  $t_2$  from the test set would result in the diagnosis procedure losing out on an opportunity to give a more accurate list of fault candidates. As our aim is to have no loss in the accuracy of diagnosis, we need to identify diagnostically relevant information and include it in the reduced fail data set. From the above example we see that the test  $t_2$  gives us the knowledge that some outputs are more likely to fail than others. As this information may be important for diagnosis, we may need to include  $t_2$  in the reduced fail data.

Intuitively, if a certain output is observed to fail repeatedly, then it has high probability of being related to the actual defect in the chip. This information being diagnostically important, the minimization of fail data should incorporate some means of *multiple coverage* of the same failing output as against the concept of single cover. We refer to this multiple

coverage as *N-cover*, N being a variable greater than or equal to 1. The method to determine a good N value for a given failing output is discussed in detail in Chapter 4.

#### 3.4. Evaluation metrics

Recent research done in the field of fail data minimization point to the conclusion that the fail data can be reduced significantly using various reduction techniques [28, 29]. The logical question that follows is how well this minimized data performs with respect to the original raw fail data when evaluated on the basis of metrics other than the fail data size. For a comparative study, we need to define a few evaluation metrics.

As the purpose of collection of fail data is to diagnose the failures of the ICs, one measure of performance can be the quality of the diagnosis results. With the removal of failing tests and failure information, the reduced data set may be weaker than the full-response fail data in identifying the possible defect locations.

Diagnosis accuracy is the measure used in this work to measure the diagnosis quality of the reduced fail data. We first use the original fail data from the tester for diagnosis to obtain a reference list of fault candidates. We call them *golden candidates*. This is followed by using the minimized fail data for diagnosis to get a new fault candidate list, called *new candidates*. Higher the intersection of these lists, higher is the diagnosis accuracy. However, if the set of new candidates misses some of the candidates from the golden candidates, then the diagnosis accuracy is reduced. A comparison of these two candidate lists is used to mathematically formulate the definition of diagnosis accuracy as follows:

Diagnosis accuracy =

$$\frac{|(\text{golden candidates} \cap \text{new candidates})|}{|\text{golden candidates}|} \times 100$$

Because of the reduction in the amount of information available to the diagnosis procedure, there is a possibility that the number of new candidates is more than the number of golden candidates. This happens when the analysis of fail data has many potential candidates and the diagnosis procedure does not have further information to narrow them down. This reduces the resolution of the diagnosis results and decreases its effectiveness. We

need another measure to keep track of this loss in resolution. Thus, we define the percent decrease in diagnosis resolution as:

Decrease in diagnosis resolution =

$$\frac{|\text{new candidates} - \text{golden candidates}|}{|\text{golden candidates}|} \times 100$$

Besides diagnosis accuracy and the reduction in diagnosis resolution we need another metric to quantify how much fail data we have reduced. This will give us an idea of the percentage of data eliminated from the original fail data set. For a given wafer, after the fail data minimization is performed, the fail-data size reduction is calculated as:

Fail-data size reduction =

$$(1 - \frac{\text{Size in bytes of the reduced fail data}}{\text{Size in bytes of the original fail data}}) \times 100$$

In addition to these metrics, we need another term to evaluate the increase in the speed of diagnosis because of the reduction in fail data that the minimization achieves. The increase in diagnosis speed is defined as:

Increase in diagnosis speed =

$$(1 - \frac{\text{Run time of diagnosis with reduced fail data}}{\text{Run time of diagnosis with original fail data}}) \times 100$$

#### 4. THE N-COVER ALGORITHM

In the last chapter we discussed the motivation behind our approach for dealing with the fail data minimization problem. We also described the concepts involved in the development of N-cover. In this chapter we will delve deeper into the implementation of the N-cover algorithm for fail data minimization.

When we talk about reduction of fail data, a reasonable question is how to decide which data to throw out. To determine if one test is better than the other in identifying defects, we need some quality measure. Consider a sample fail data collected by the tester for a failing die. Suppose a test  $t_1$  produces failures at 10 out of 15 observable outputs of the given die. Another test  $t_2$  is found to fail at 8 outputs for the same die. We may assume that the test  $t_1$  is "superior" to test  $t_2$  in terms of *output coverage* as it produces more failing outputs. Of course the determination of the superiority of one test over the other in this manner is highly dependent on the set of failing dies used, the number of failing tests being compared and the type of defects actually present in the die. That being said, the concept of *output coverage* will give us a measure to compare between the effectiveness of two tests with respect to the number of failing outputs being covered by them.

#### 4.1. The value of N

In this work we propose that the fail data minimization algorithm should include tests that provide N-cover with respect to all the observed failing outputs. If an output fails more often, it should be covered by more number of tests in the fail data, implying higher value of N. Similarly, if an output fails less often, it should have a lower value of N. Once each output 'o' is covered  $N_o$  times, the remaining tests can be eliminated.

In order to determine how often an output fails we use the term *output failure frequency* which is defined as the number of tests that are observed to fail at a particular output once the tester has completed fail data collection. As the failure frequency of an output tells us

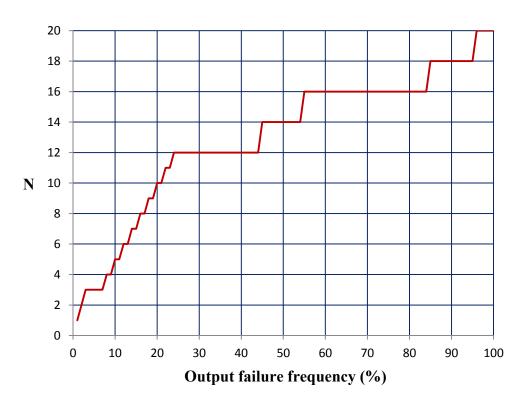

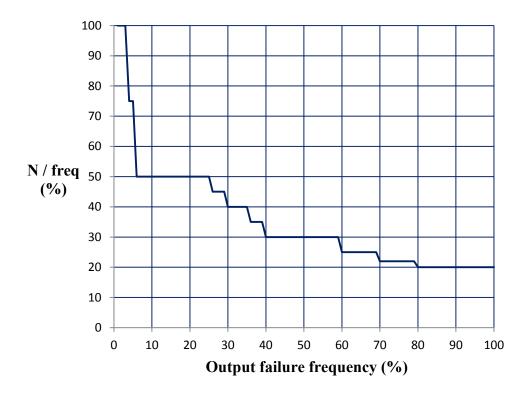

how susceptible it is to failure, we need to establish a relationship between the frequency and the corresponding N value for that output. For this purpose, we conducted extensive experiments with real fail data from industry fabricated chips. We analyzed the fail data of various wafers and by trial and error determined a suitable value of N for a given output failure frequency. The values of N were fixed such that once all the outputs are covered N times, the elimination of remaining tests would not adversely affect diagnosis accuracy. In addition we ensured that the N values are flexible, in the sense that N is large enough to accommodate fail data trends of different chip designs but also small enough to provide substantial fail data reduction. This evaluation led to the development of a monotonically increasing relationship between the output failure frequencies and the values of N as shown in the Figure 4.1.

Figure 4.1 Monotonically increasing relationship between the output failure frequencies and the absolute N values

For example, if the fail data of a die consists of 100 failing tests and 40 of them were observed to fail at output *a* and 90 were observed to fail at output *b* then the output failure frequencies of *a* and *b* are 40% and 90% respectively. Looking at the graph in Figure 4.1, we see that for output *a*, out of 40 failing tests only 12 are enough for the diagnosis procedure to correctly diagnose the failures in the die. Similarly for output *b* only 18 failing tests out of 90 suffice for high quality diagnosis.

In other words, for output a the goal coverage is only 30% (12 out of 40) of the original coverage and for output b the goal coverage is 20% (18 out of 90). Another interesting observation is that as the frequencies increase, more fail data can be eliminated while maintaining the frequency vs. N relationship between all the outputs. So if output b has higher failure frequency than output a, then the absolute value of N for b would be equal to or higher than the N value for a but at the same time the percent of goal coverage required for b would be less than or equal to that required for output a. When represented mathematically:

If

$$freq(a) \le freq(b)$$

Then  $N(a) \le N(b)$  and  $\frac{N(a)}{freq(a)} \ge \frac{N(b)}{freq(b)}$

Such that  $N(a) \le freq(a)$  and  $N(b) \le freq(b)$

The monotonically decreasing relationship between failure frequency and its required goal coverage (N/freq) can also be represented as shown in Figure 4.2. So if the output a has frequency 40% then from Figure 4.2, N should be 30% of frequency that is, 0.3\*40 = 12. Similarly, if b has frequency 90% then from Figure 4.2, its N value is found to be 20% of 90, that is, 18. Once we have the complete fail data collected by the tester, we can obtain the failure frequencies of all the outputs and determine the corresponding values of N by referring to the Figures 4.1 or 4.2. The N-cover algorithm will then cover each of the failing outputs N times and the remaining tests will be eliminated. In the next section we will discuss the implementation details of the N-cover algorithm.

Figure 4.2 Monotonically decreasing relationship between output failure frequencies and the percentage of required goal coverage

#### 4.2. Implementation of the N-cover algorithm

In our approach, a test will be selected for inclusion in the reduced fail data only if it helps in providing N-cover for the failing outputs. The key to the N-cover algorithm is the relationship between the output failure frequencies and the values of N as described in the previous section. Our approach for fail data minimization using N-cover algorithm is presented in the pseudocode in Figure 4.3.

We start with the original fail data from the tester as an input. This raw fail data consists of a set of failing test vectors  $T = \{t_0, t_1... t_n\}$ , each test vector covering some outputs from the set of failing outputs  $Z = \{z_0, z_1... z_m\}$ . After the termination of the algorithm we will obtain  $T_{red}$  as an output which is the subset of failing test vectors from T that can be used for

diagnosis without compromising its quality. The main steps of our approach for fail data minimization are as follows:

input: A set of failing tests T Each test in T covers some outputs from the set of failing outputs Z output:  $T_{red}$ : A subset of failing tests from Talgorithm FailDataMinimization begin  $T_{red} = \{\}$ Step 1: Analyze T to obtain failure frequencies of all outputs Step 2: Determine N for all outputs using frequency versus N relationship Compute *cov<sub>diff</sub>* for all outputs Step 3: Step 4:  $max \ out = output \ with \ max \ cov_{diff}$ *nextTest* = greedily select a test that covers the output *max out*  $T_{red} = T_{red} \cup \{nextTest\}$  $T = T - \{nextTest\}$ Step 5: Repeat steps 3 and 4 till  $cov_{diff} \le 0$  for all outputs Step 6: return  $T_{red}$ end FailDataMinimization

Figure 4.3 Pseudocode for the N-cover algorithm for diagnostic fail data minimization

#### Step 1: Start running the minimization algorithm

We first allow the fail data minimization algorithm to run by providing the required inputs. The algorithm initializes  $T_{red}$  to be empty and analyzes the raw fail data to obtain the failure frequencies of all the outputs as described in section 4.1. Currently the algorithm uses complete fail data collected by the tester to extract the output failure frequencies.

#### **Step 2: Determine N values for all outputs**

Once we have obtained the failure frequencies of all outputs, we can use the graphs shown in figures 4.1 and 4.2 to obtain the corresponding N values for each output. These N values provide us with the information about the minimum coverage requirement for each of the failing output.

#### **Step 3: Find the coverage difference for all outputs**

The term coverage difference ( $cov_{diff}$ ) represents the difference between the goal coverage and the current actual coverage provided by the tests in  $T_{red}$  for every failing output. In the first iteration of the algorithm,  $T_{red}$  is empty and so in this case the  $cov_{diff}$  will be equal to the goal coverage. This term tells us about how many more tests are required to provide the required coverage for a failing output at a given point of time during the algorithm application.

### Step 4: Select the next test to be included depending on maximum covdiff

After computing the  $cov_{diff}$  values for all the failing outputs, the algorithm finds the output  $max\_out$  which has the maximum value of  $cov_{diff}$ . This is the output which requires maximum coverage at that stage of the algorithm. The selection of next test depends on the greedy set covering concept discussed in section 3.2. Once we have obtained  $max\_out$ , the algorithm looks for the tests that failed at that output. Out of these tests, the algorithm selects the test that has the maximum number of failing outputs as compared to other tests that failed at  $max\_out$ . This is called greedy covering of the failing output.

#### Step 5: Continue iterations till $cov_{diff} \le 0$ for all outputs

After adding a test to  $T_{red}$ , the algorithm recomputes the values of  $cov_{diff}$ . It again finds  $max\_out$  and greedily selects tests from  $T_{red}$  to cover it. This procedure continues till the  $cov_{diff}$  values for all outputs become less than or equal to zero.  $cov_{diff}$  equal to zero implies that the current coverage provided by the tests in  $T_{red}$  is equal to the goal coverage for that particular output. A negative  $cov_{diff}$  means that the actual coverage for that output was more

than the goal coverage. In this case, even though more than required coverage was obtained, it actually adds to the diagnosis quality.

#### Step 6: Return $T_{red}$ and terminate the fail data minimization procedure

Once the  $cov_{diff}$  requirements are met for all the failing outputs, no more tests need to be added to  $T_{red}$  and the fail data minimization procedure is terminated. The set of failing vectors  $T_{red}$  gives the final reduced test set that can be used for diagnosis.

#### 4.3. An illustrative example

In this section we will work through a small but meaningful example that describes each step of the N-cover algorithm for diagnostic fail data minimization in. A sample fail data is provided as shown in Table 4.1. For each test in the table, all the outputs at which it is observed to fail are marked with 'X' in their respective columns. Using this information, we will describe how the N-cover algorithm will compute the reduced set of failing tests.

According to the pseudocode described in Figure 4.3, the first step of the algorithm is to initialize  $T_{red}$  to be empty and to extract the failure frequencies of all the outputs from the fail data. For this example, the failure frequencies of all outputs are shown in the 'Frequencies' row of Table 4.2. The second step is to determine the N values for every failing output by referring to the frequency versus N relationship described in section 4.1. Let us assume that for this particular example, the N values obtained from the frequencies are as shown in the 'Required N' row of Table 4.2.

The next step involves finding the  $cov_{diff}$  values for all outputs. As mentioned before, in the first iteration, the  $cov_{diff}$  values are the same as goal coverage. So the  $cov_{diff}$  values are as shown in the fourth row of Table 4.3. Next the algorithm finds the output with maximum  $cov_{diff}$ . At this stage that output is  $z_1$  with  $cov_{diff}$  value of 4 (highlighted in orange). So the algorithm needs to greedily select a test to cover  $z_1$ .

Table 4.1 Sample fail data collected from the tester

**Failing outputs**

|    |                         |                              |    | ·· 8 |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----|-------------------------|------------------------------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | z0                      | z1                           | z2 | z3   | z4                                                                                                                                                                                | z5                                                                                                                                                                                                                                                                                      | z6                                                                                                                                                                                                                                                                                                            | z7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | z8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | z9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| t0 |                         | Χ                            | Х  | Х    |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| t1 |                         | Х                            |    |      | Х                                                                                                                                                                                 | Х                                                                                                                                                                                                                                                                                       | Х                                                                                                                                                                                                                                                                                                             | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| t2 |                         | Χ                            |    |      |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| t3 |                         |                              |    |      |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |