### Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

Fall 2013

### Non-Silicon MOSFETs and Circuits with Atomic Layer Deposited Higher-k Dielectrics

Lin Dong

Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

Part of the <u>Electrical and Computer Engineering Commons</u>, and the <u>Nanoscience and Nanotechnology Commons</u>

#### Recommended Citation

Dong, Lin, "Non-Silicon MOSFETs and Circuits with Atomic Layer Deposited Higher-k Dielectrics" (2013). *Open Access Dissertations*. 203.

https://docs.lib.purdue.edu/open\_access\_dissertations/203

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

| · ·                                                                                                                                                                                                     |                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| By Lin Dong                                                                                                                                                                                             |                                          |

| Entitled<br>Non-Silicon MOSFETs and Circuits with Atomic Layer Deposited Higher-k Diele                                                                                                                 | ctrics                                   |

| For the degree of                                                                                                                                                                                       |                                          |

| Is approved by the final examining committee:                                                                                                                                                           |                                          |

| PEIDE YE                                                                                                                                                                                                |                                          |

| Chair<br>DAVID B. JANES                                                                                                                                                                                 |                                          |

| MINGHAO QI                                                                                                                                                                                              |                                          |

| MUHAMMAD A. ALAM                                                                                                                                                                                        |                                          |

| To the best of my knowledge and as understood by the student in <i>Copyright Disclaimer (Graduate School Form 20)</i> , this thesis/dipurdue University's "Policy on Integrity in Research" and the use | issertation adheres to the provisions of |

| Approved by Major Professor(s): PEIDE YE                                                                                                                                                                |                                          |

| Approved by: M. R. Melloch                                                                                                                                                                              | 09-24-2013                               |

| Head of the Graduate Program                                                                                                                                                                            | Date                                     |

## NON-SILICON MOSFETS AND CIRCUITS WITH ATOMIC LAYER DEPOSITED HIGHER- $\kappa$ DIELECTRICS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Lin Dong

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2013

Purdue University

West Lafayette, Indiana

| 11 |  |

|----|--|

|    |  |

To my beloved parents Qingchi Dong and Juxiang Cai, and my wife Man Wang.

#### ACKNOWLEDGMENTS

In the very beginning, I would like to express my deepest gratitude to my supervisor, Professor Peide Ye, for his valuable guidance, encouragement and support throughout my whole Ph.D. program. I also thank my committee members, Professor Muhammad Ashraful Alam, Professor David B. Janes and Professor Minghao Qi for their kindness and helpful advice. Many thanks to Dr. Min Xu, Dr. Jiangjiang Gu, Adam Neal, Han Liu, Nathan Conrad, Jingyun Zhang, Heng Wu, Xuefei Li, because without the tremendous help from our group members my work would not be possibly done, they are diligent, creative, skillful and cooperative and I would never forget the days and nights we fought together. I also want to send my thanks to dear friends who helped me a lot during my experiment and measurement. They are Masud, Sambit, Jifa Tian and Yi Xuan. Special thanks to John Coy, Kenny Schwartz, Dave Lubelski, Dan Hosler, Bill Rowe, Mike Courtney, Bill Sheldon and Geoff Gardner, the technical staffs of the cleanroom facilities, and Mary Jo Totten, Angie Sigo and Heather Anthrop, the clerical staffs in the Birck Nanotechnology Center.

Particularly I would like to express my gratitude to my co-workers in Harvard University, Professor Gordon Roy, who is so knowledgable and enthusiastic in research, and gave me many valuable suggestion and advice. Special thanks to Yiqun Liu, Xinwei Wang and Xiabing Lou, who gave me enormous help in my Ph.D. program and I will be nowhere near the excellent work without their help.

Finally, I would like to thank my parents and my wife for their everlasting love. It was your company who helped me to get thorough all those difficult times and I would not complete my Ph.D program without your utmost support.

#### TABLE OF CONTENTS

|    |      |        |                                                                                                                          | Page    |

|----|------|--------|--------------------------------------------------------------------------------------------------------------------------|---------|

| LI | ST O | F TAB  | LES                                                                                                                      | vii     |

| LI | ST O | F FIGU | URES                                                                                                                     | viii    |

| Al | BSTR | ACT    |                                                                                                                          | xviii   |

| 1  | INT  | RODU   | CTION                                                                                                                    | 1       |

|    | 1.1  | CMOS   | S scaling down and novel technologies                                                                                    | 1       |

|    | 1.2  | High-  | κ dielectrics and Atomic Layer Deposition                                                                                | 4       |

|    | 1.3  | Thesis | soutline                                                                                                                 | 6       |

| 2  |      |        | F LA-BASED HIGHER- $\kappa$ OXIDE ON HIGH MOBILITY SUBWITH ATOMIC LAYER DEPOSITION                                       | 8       |

|    | 2.1  | Introd | uction                                                                                                                   | 8       |

|    | 2.2  | Atomi  | c Layer Deposition experimental process and methods                                                                      | 10      |

|    | 2.3  | GaAs,  | oxide epitaxial atomic structures                                                                                        | 12      |

|    | 2.4  |        | c Layer Epitaxial (ALE) interface material and electrical prop-<br>cudy                                                  | 15      |

|    | 2.5  | Summ   | ary                                                                                                                      | 24      |

| 3  | ANI  | ) CIRC | TRATION OF HIGH PERFORMANCE GAAS CMOS DEVICES UITS ENABLED BY LA-BASED HIGHER- $\kappa$ EPITAXIAL DISS                   | 26      |

|    | 3.1  |        | (111)A MOSFETs nMOSFETs and pMOSFETs with $La_{1.8}Y_{0.2}O_{3.6}$ (111)A epitaxial interface                            | /<br>26 |

|    |      | 3.1.1  | Introduction                                                                                                             | 26      |

|    |      | 3.1.2  | ${\rm La_{1.8}Y_{0.2}O_3/GaAs(111)A}$ Epitaxial Structure Study                                                          | 27      |

|    |      | 3.1.3  | Epitaxial $La_{1.8}Y_{0.2}O_3/GaAs(111)A$ interface enabled high performance GaAs nMOSFETs study                         | 29      |

|    |      | 3.1.4  | Epitaxial La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs(111)A interface enabled high performance GaAs pMOSFETs | 36      |

|   |      |                    |                                                                                             | Page |

|---|------|--------------------|---------------------------------------------------------------------------------------------|------|

|   |      | 3.1.5              | $\rm La_{1.8}Y_{0.2}O_{3}/GaAS(111)A$ MOS Capacitance-Voltage Study .                       | 43   |

|   |      | 3.1.6              | Summary                                                                                     | 51   |

|   | 3.2  |                    | kial $La_2O_3/GaAs$ (111)A interface enabled high performance GaAs devices                  | 52   |

|   |      | 3.2.1              | Introduction                                                                                | 52   |

|   |      | 3.2.2              | GaAs CMOS devices and circuits fabrication process                                          | 54   |

|   |      | 3.2.3              | Electrical characterizations and analysis of GaAs CMOS devices                              | 57   |

|   | 3.3  | First (            | GaAs CMOS digital circuits demonstration                                                    | 66   |

|   | 3.4  | Summ               | ary                                                                                         | 73   |

| 4 | GE I | MOSFE              | ETS WITH EPITAXIAL $LA_2O_3/GE(111)$ INTERFACES                                             | 74   |

|   | 4.1  | Introd             | uction                                                                                      | 74   |

|   | 4.2  |                    | MOSFETs and nMOSFETs with $La_2O_3/Ge(111)$ epitaxial inter-                                | 75   |

|   | 4.3  | Summ               | ary                                                                                         | 81   |

| 5 | SRT  | IO <sub>3</sub> M( | OSFETS WITH ALD LAAIO <sub>3</sub> GATE DIELECTRICS                                         | 85   |

|   | 5.1  | Introd             | uction                                                                                      | 85   |

|   | 5.2  |                    | c Impact on LaAlO <sub>3</sub> /SrTiO <sub>3</sub> NMOSFETs Interface: Initial Re-<br>Study | 86   |

|   |      | 5.2.1              | $SrTiO_3$ Device Structure and Fabrication Process flow                                     | 87   |

|   |      | 5.2.2              | Device Characterization                                                                     | 89   |

|   | 5.3  | Interfa            | acial Layer Effect Study on SrTiO <sub>3</sub> NMOSFETs                                     | 91   |

|   |      | 5.3.1              | Device structure and fabrication                                                            | 91   |

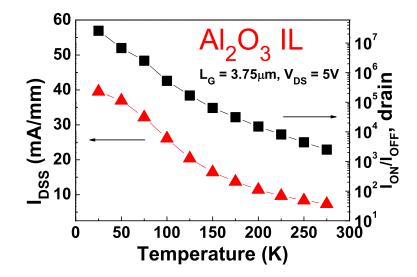

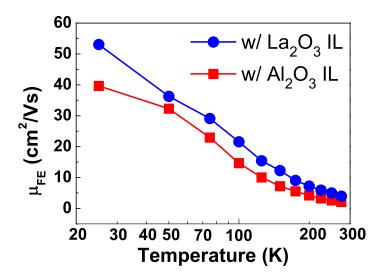

|   |      | 5.3.2              | Device Characterization: A Temperature Dependence Study                                     | 93   |

|   | 5.4  | Metal-             | -Insulator-Transition at LaAlO <sub>3</sub> -SrTiO <sub>3</sub> interface                   | 101  |

|   |      | 5.4.1              | Introduction                                                                                | 101  |

|   |      | 5.4.2              | Metal-Insulator-Transition Observation at LaAlO <sub>3</sub> /SrTiO <sub>3</sub> Interface  | 102  |

|   |      | 5.4.3              | Mechanism Investigation of Metal-Insulator-Transition                                       | 104  |

|   | 5.5  | Summ               | eary and Conclusion                                                                         | 107  |

|                       | Page |

|-----------------------|------|

| 6 SUMMARY AND OUTLOOK | 109  |

| LIST OF REFERENCES    | 111  |

| VITA                  | 118  |

#### LIST OF TABLES

| Tabl | Table                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.1  | Carrier transport properties and energy bandgaps of semiconductor materials of interest under room temperature.                                                                                                                                                                                                                                                                                                                                          | 2 |

| 3.1  | Process sequence for the fabrication of GaAs(111)A NMOSFETs. 7.5nm ${\rm LaYO_3}$ or ${\rm La_{1.8}Y_{0.2}O_3}$ was epitaxially grown by ALE, forming a single crystalline oxide-single crystalline semiconductor interface, whose electrical quality could be further improved by a high temperature annealing.                                                                                                                                         |   |

| 3.2  | Comparison of C-V curve frequency dispersion, $\Delta V_{fb}$ from 5kHz to 1MHz and $V_{fb}$ of p-type Ni/Al <sub>2</sub> O <sub>3</sub> /La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs(111)A and p-type Ni/Al <sub>2</sub> O <sub>3</sub> /LaYO <sub>3</sub> /GaAs(111)A capacitors under different annealing conditions. The reduction of frequency dispersion suggests that the interface quality is improved by high temperature annealing |   |

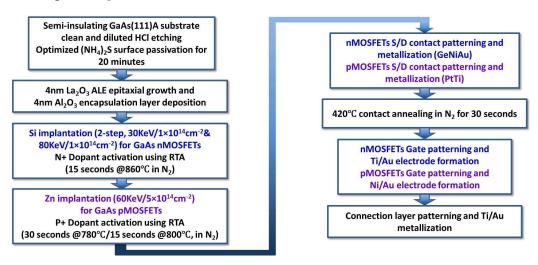

| 3.3  | Process sequence for the fabrication of GaAs (111)A CMOS circuits. The epitaxial interface is formed by ALE 4nm single crystalline ${\rm La_2O_3}$ , followed by 4nm ALD amorphous ${\rm Al_2O_3}$ as an encapsulation layer. Si and Zn were used for N+ region and P+ region ion implantation, respectively                                                                                                                                             |   |

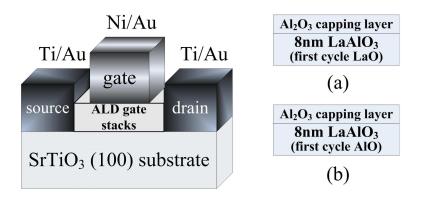

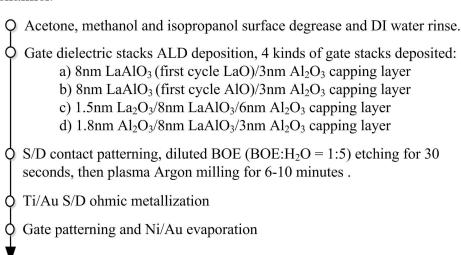

| 5.1  | Process flow for SrTiO <sub>3</sub> NMOSFETs with ALD high-k dielectric. 2 types of LaAlO <sub>3</sub> gate stacks were employed. Plasma argon milling removes LaAlO <sub>3</sub> at S/D regions and also generates O vacancies on SrTiO <sub>3</sub> surface to ensure Ti/Au Ohmic contacts to the conducting channel                                                                                                                                   |   |

#### LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

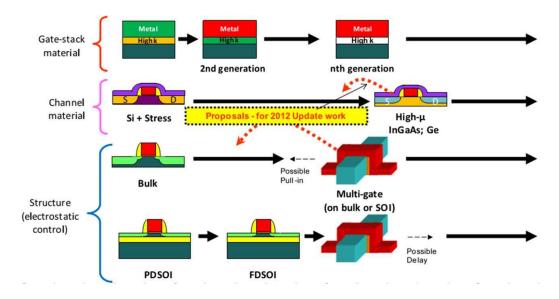

| 1.1  | 2011 ITRS equivalent scaling process technologies including high mobility channel materials, high- $\kappa$ gate dielectrics and novel device structures.                                                                                                                                                                                                                                                                                                                                                                                 | 2    |

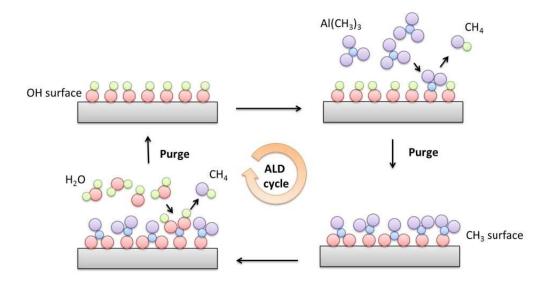

| 1.2  | Schematics of aluminum oxide deposition by ALD technique. $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5    |

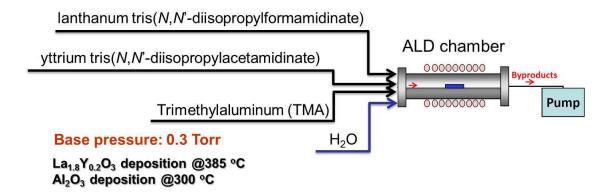

| 2.1  | Schematic illustration of the Atomic Layer Epitaxy process. The epitaxial $\text{La}_{2-x}Y_xO_3$ oxide film is deposited at 385 °C while the amorphous $\text{Al}_2O_3$ oxide encapsulation layer is grown at 300 °C. The relative long time purging during the process is the key to realize uniform and single crystalline oxide structure. The base pressure of the deposition is maintained at around 0.3 Torr                                                                                                                       |      |

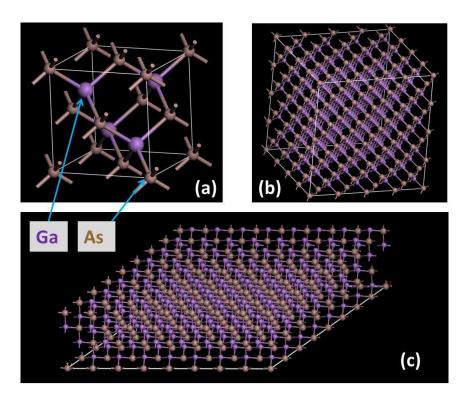

| 2.2  | (a) A typical GaAs zincblende lattice unit cell with (100) surface. The purple and brown balls represent Ga and As atoms, respectively (b) A GaAs super lattice with 4×4×4 GaAs unit cell. (c) Illustration of GaAs(111)A surface with Ga termination                                                                                                                                                                                                                                                                                     |      |

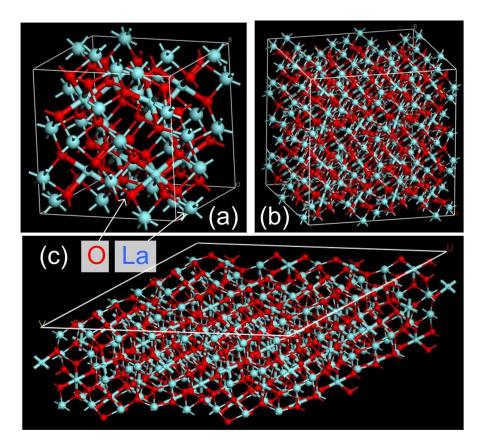

| 2.3  | (a) An atomic structural view of a $La_2O_3$ cubic cell. The light blue and red balls represent La and Oxygen atoms, respectively (b) A $La_2O_3$ super lattice with $2\times2\times2$ $La_2O_3$ unit cell. (c) Illustration of $La_2O_3(111)$ surface with Oxygen termination                                                                                                                                                                                                                                                            |      |

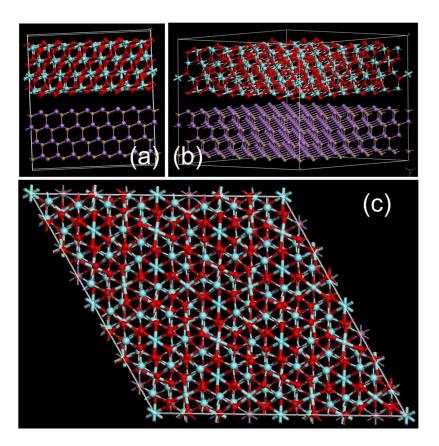

| 2.4  | (a) and (b) Atomic structural views of the epitaxial interface between $La_2O_3$ and $GaAs$ . (c) A top view of the stacked atomic structure of epitaxial interface between $La_2O_3$ and $GaAs$ , the hexagonal structures can be clearly observed                                                                                                                                                                                                                                                                                       |      |

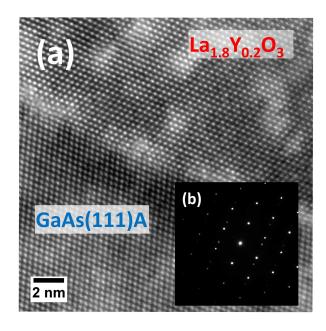

| 2.5  | (a) Cross-sectional TEM image of $La_{1.8}Y_{0.2}O_3/GaAs(111)A$ interface, and (b) the corresponding electron diffraction patter with the electron beam aligned along the [011] direction of GaAs                                                                                                                                                                                                                                                                                                                                        |      |

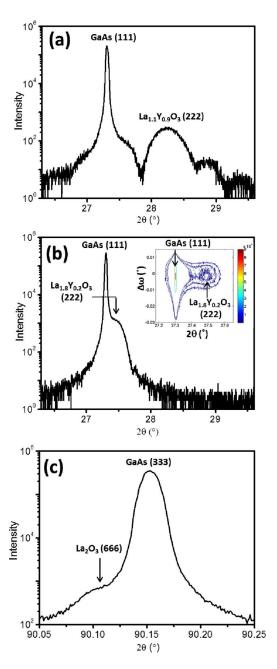

| 2.6  | HRXRD couples $2\theta$ - $\omega$ scans of (a) La <sub>1.1</sub> Y <sub>0.9</sub> O <sub>3</sub> , (b) La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> , and (c) La <sub>2</sub> O <sub>3</sub> on GaAs(111)A. The scans of (a) and (b) were performed around the GaAs(111) reflection, and the scan of (c) was performed around the GaAs(333) reflection. The inset of (b) shows the $2\theta$ - $\Delta\omega$ reciprocal space map around the GaAs(111) peak for the La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs sample |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

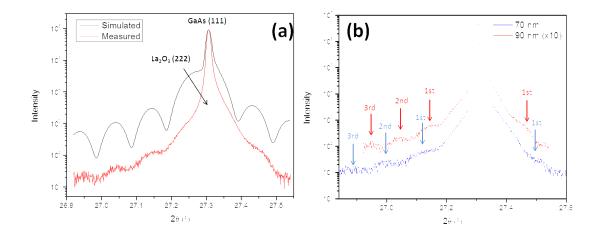

| 2.7  | (a) HRXRD coupled 2 $\theta$ - $\omega$ scan of a 90 nm La <sub>2</sub> O <sub>3</sub> film grown on GaAs(111)A, compared with a simulated diffraction curve from LEPTOS (Bruker). (Lattice mismatch used in simulation was +0.037% for La <sub>2</sub> O <sub>3</sub> /GaAs.) The good matching of the Laue oscillations indicates that the main peak of La <sub>2</sub> O <sub>3</sub> (222) is indeed overlapping with GaAs (111). (b) By the comparing the 2 $\theta$ - $\omega$ curves measured on two La <sub>2</sub> O <sub>3</sub> /GaAs samples with different thickness (70 nm and 90 nm), we noticed that all of the side-band peaks shifted, suggesting that these side-band peaks all belong to the thickness fringes (Laue oscillations) of the La <sub>2</sub> O <sub>3</sub> (222) main peak. This again indicates that the La <sub>2</sub> O <sub>3</sub> (222) main peak is overlapping with GaAs (111) peak | 19   |

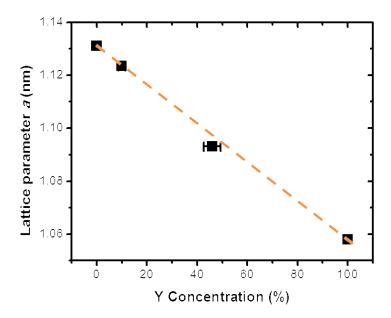

| 2.8  | Vegards law plot of the lattice parameters of $La_{2-x}Y_xO_3$ . The Y concentration was determined by Rutherford backscattering spectroscopy. The obtained lattice constants of $La_2O_3$ and $Y_2O_3$ are comparable with the reference values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20   |

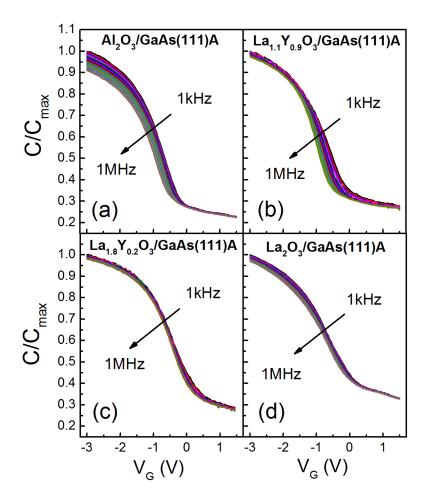

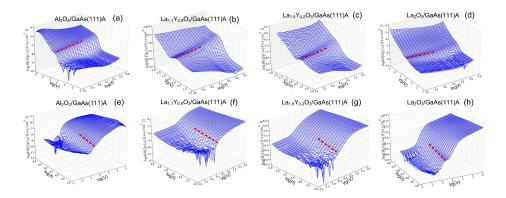

| 2.9  | C-V characteristics of p-type GaAs MOS capacitors with stacks of (a) Ni/8nm Al <sub>2</sub> O <sub>3</sub> /GaAs(111)A, (b) Ni/6.5 nm Al <sub>2</sub> O <sub>3</sub> 3/7.5 nm La <sub>1.1</sub> Y <sub>0.9</sub> O <sub>3</sub> /GaAs(111)A, (c) Ni/6.5 nm Al <sub>2</sub> O <sub>3</sub> /7.5 nm La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs(111)A, and (d) Ni/6.5 nm Al <sub>2</sub> O <sub>3</sub> /9 nm La <sub>2</sub> O <sub>3</sub> /GaAs(111)A, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21   |

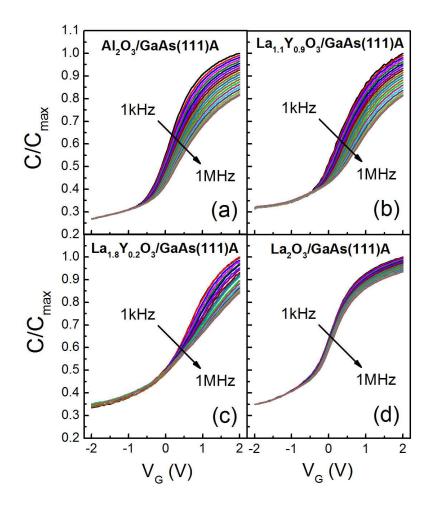

| 2.10 | C-V characteristics of n-type GaAs MOS capacitors with stacks of (a) Ni/8nm Al <sub>2</sub> O <sub>3</sub> /GaAs(111)A, (b) Ni/6.5 nm Al <sub>2</sub> O <sub>3</sub> /7.5 nm La <sub>1.1</sub> Y <sub>0.9</sub> O <sub>3</sub> /GaAs(111)A, (c) Ni/6.5 nm Al <sub>2</sub> O <sub>3</sub> /7.5 nm La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs(111)A, and (d) Ni/6.5 nm Al <sub>2</sub> O <sub>3</sub> /9 nm La <sub>2</sub> O <sub>3</sub> /GaAs(111)A, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22   |

| 2.11 | Frequency-dependent conductance-voltage (Gp/ $\omega$ Vg f) plots measured on p-type and n-type (a, e) Al <sub>2</sub> O <sub>3</sub> /GaAs, (b, f) La <sub>1.1</sub> Y <sub>0.9</sub> O <sub>3</sub> /GaAs, (c, g) La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs, and (d, h) La <sub>2</sub> O <sub>3</sub> /GaAs MOS capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23   |

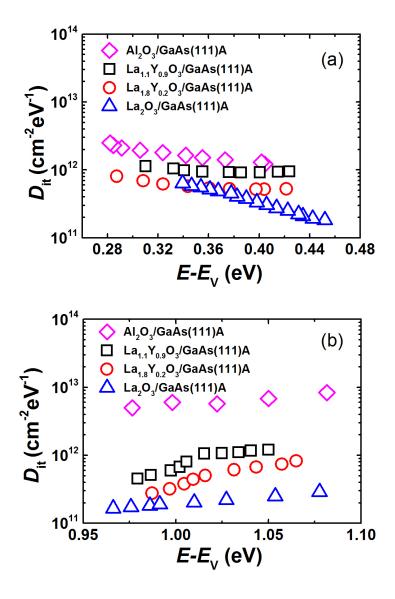

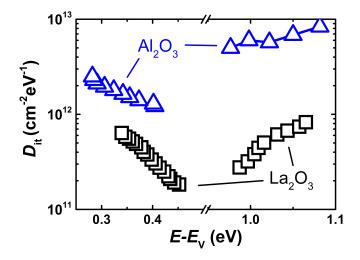

| 2.12 | $D_{it}$ distribution in GaAs band gap obtained on both (a) p-type and (b) n-type MOS capacitors with $Al_2O_3/GaAs(111)A$ , $La_{1.1}Y_{0.9}O_3/GaAs(111)A$ , $La_{1.8}Y_{0.2}O_3/GaAs(111)A$ and $La_2O_3/GaAs(111)A$ as the interfaces, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25   |

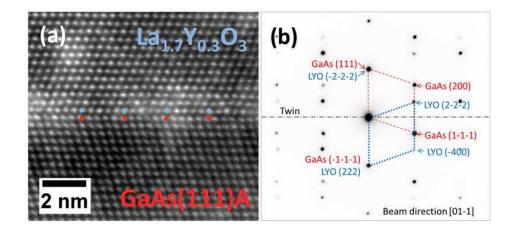

| 3.1  | (a) High-resolution cross-section TEM picture of a ${\rm La_{1.8}Y_{0.2}O_3/GaAs(111)}$ epitaxial interface. A flat and sharp interface (denoted by red and blue dots) can be observed. (b) The electron diffraction pattern taken from the same cross-sectional TEM sample along the (110) zone axis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A 27 |

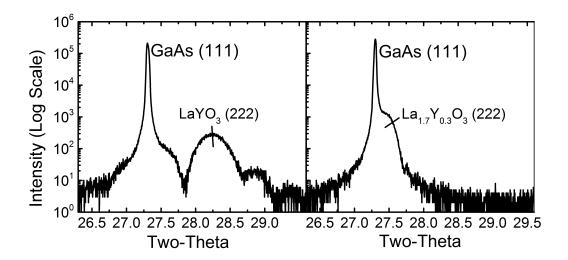

| 3.2  | High-resolution X-ray omega-two theta coupled scan for (a) LaYO <sub>3</sub> and (b) La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> on GaAs(111)A. The partial overlap of GaAs(111) and La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> (222) peaks indicates they are lattice-matched better than GaAs (111) and LaYO <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                      | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

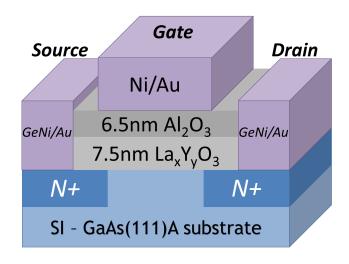

| 3.3  | Schematic view of an inversion-mode NMOSFET on a semi-insulating GaAs(111)A substrate with ALE $\rm La_{1.8}Y_{0.2}O_3$ as gate dielectric                                                                                                                                                                                              | 29   |

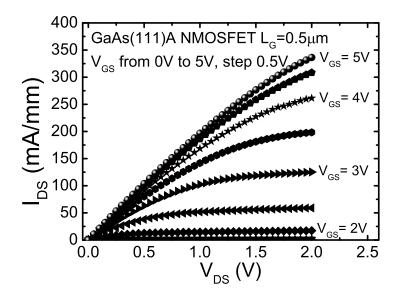

| 3.4  | Output characteristic ( $I_{DS}\sim V_{DS}$ ) for a $L_G=0.5\mu m$ GaAs(111)A NMOSFET with $Al_2O_3/La_{1.8}Y_{0.2}O_3$ as gate dielectric                                                                                                                                                                                              | 31   |

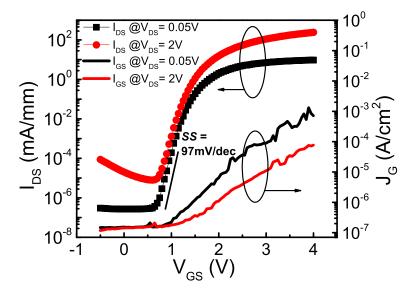

| 3.5  | Transfer characteristic ( $I_{DS} \sim V_{GS}$ ) and gate leakage current density ( $J_G$ ) for the same device of Fig. 3.4                                                                                                                                                                                                             | 32   |

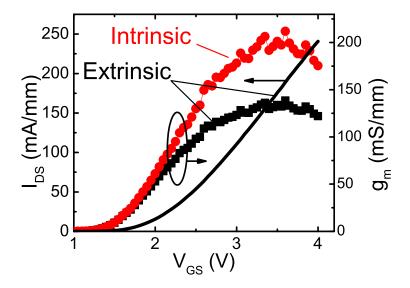

| 3.6  | Transfer characteristic, extrinsic and intrinsic transconductance $(G_m)$ versus $V_{GS}$ for the same device of Fig. 3.4                                                                                                                                                                                                               | 32   |

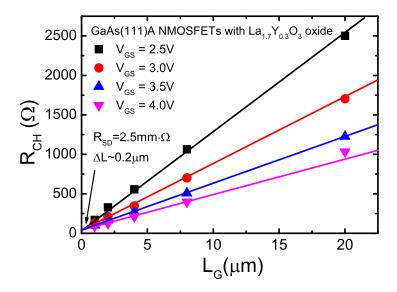

| 3.7  | Channel resistance ( $R_{CH}$ ) versus gate length ( $L_G$ ) under different gate biases ( $V_{GS}$ ) in the linear region ( $V_{DS}$ =10mV) on GaAs(111)A NMOSFETs with different $L_G$ . Linear scaling is obtained as expected                                                                                                       | 34   |

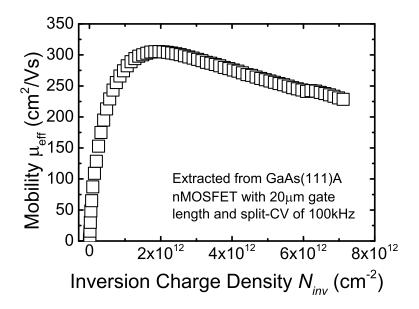

| 3.8  | Effective electron mobility extracted from a $L_G$ =20 $\mu$ m GaAs(111)A NMOS-FET with Al <sub>2</sub> O <sub>3</sub> /La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> as gate dielectric                                                                                                                                            | 35   |

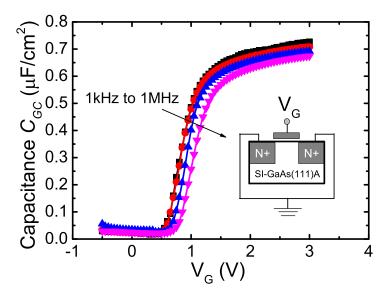

| 3.9  | Split C-V characteristics of a GaAs (111)A NMOSFET with $Al_2O_3/La_{1.8}Y_{0.2}$ $O_3$ as gate dielectric, showing very small frequency dispersion, indicating a good interface quality. Inset: measurement configuration                                                                                                              | 36   |

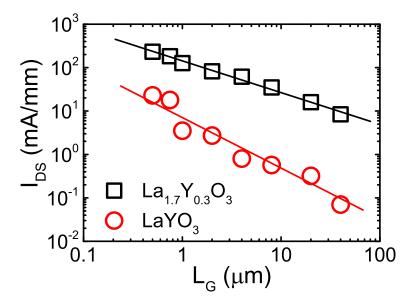

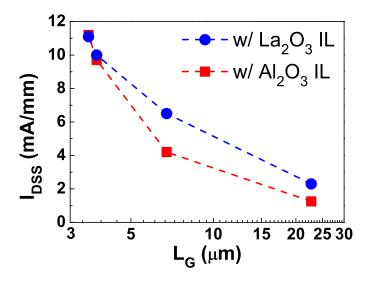

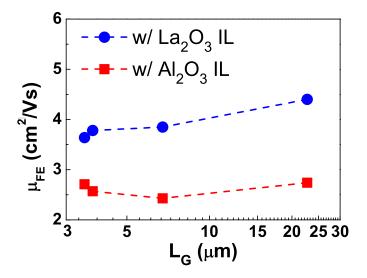

| 3.10 | Scaling characteristics of $I_{DS}$ versus different gate lengths $L_G$ for GaAs(111) A NMOSFETs with two different gate oxides                                                                                                                                                                                                         | 37   |

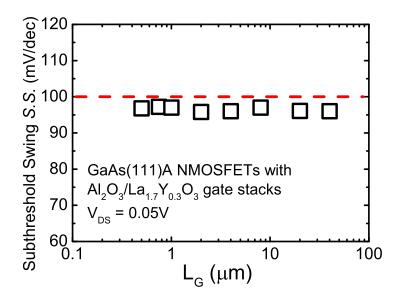

| 3.11 | Scaling metrics of subthreshold swing $(SS)$ versus different gate lengths $L_G$ for GaAs(111)A NMOSFETs with $Al_2O_3/La_{1.8}Y_{0.2}O_3$ gate dielectric.                                                                                                                                                                             | 37   |

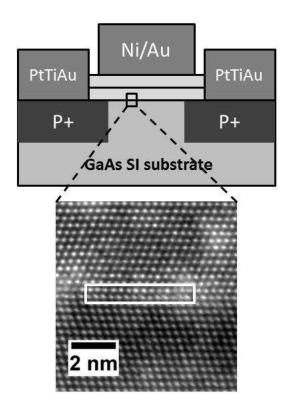

| 3.12 | (a) The cross sectional view of a GaAs(111)A pMOSFET. (b) High-resoluti on TEM image of the single epitaxial $GaAs(111)A/La_{1.8}Y_{0.2}O_3$ interface after 860oC RTA annealing. The white box is denoting the flat interface for eye reference                                                                                        | 39   |

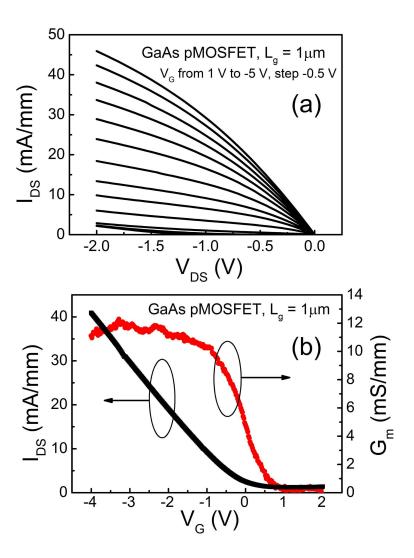

| 3.13 | (a) Current-voltage (I-V) characteristic and (b) extrinsic transconductance $(G_m)$ and drain current versus gate bias of a 1m-gate-length GaAs pMOS-FET with ALE La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> gate oxide. This device shows a maximum drain current of 46 mA/mm and a peak extrinsic transconductance of 12 mS/mm | 40   |

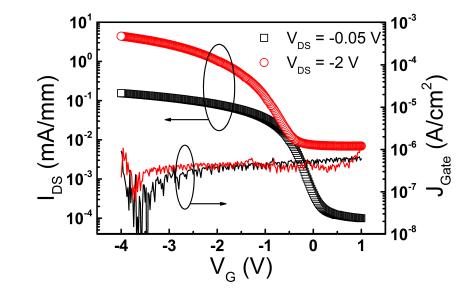

| 3.14 | Transfer characteristics and gate leakage current density of a $8\mu$ m-gate-length GaAs pMOSFET fabricated in this work                                                                                                                                                                                                                | 41   |

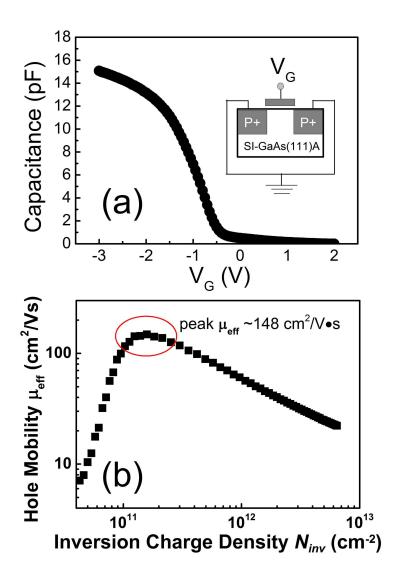

| 3.15 | (a) Split C-V characteristics and measurement setup of a Lg = $8\mu$ m GaAs (111)A pMOSFET fabricated in this work (b) effective hole mobility extracted from the same GaAs(111)A pMOSFET as in (a), using the split CV results                                                                                                         | 42   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

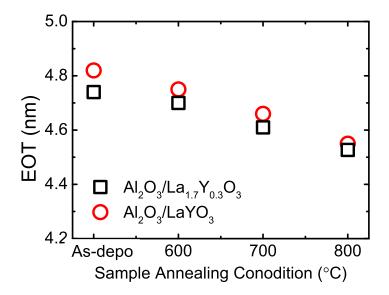

| 3.16 | EOT as a function of annealing condition on $Al_2O_3/La_xY_yO_3/GaAs(111)A$ systems. Samples are annealed at 600°C, 700°C and 800°C for 30 seconds in $N_2$ , respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46   |

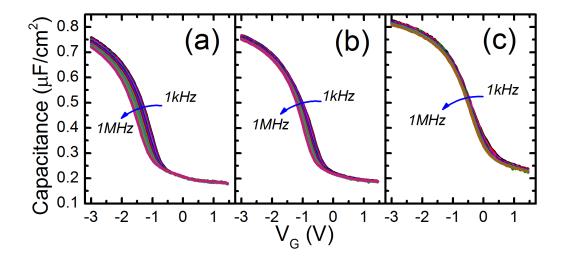

| 3.17 | Capacitance-Voltage characteristics of p-type Ni/Al $_2$ O $_3$ /La $_{1.8}$ Y $_{0.2}$ O $_3$ /GaAs (111)A capacitors measured from 1kHz to 1MHz at different annealing conditions (a) As-deposited (b) 600°C annealed and (c) 800°C annealed in N $_2$ for 30seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47   |

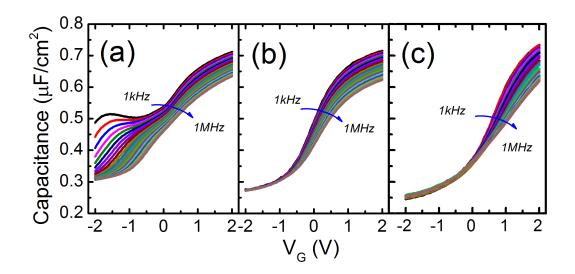

| 3.18 | Capacitance-Voltage characteristics of n-type Ni/Al $_2$ O $_3$ /La $_{1.8}$ Y $_{0.2}$ O $_3$ /GaAs (111)A capacitors measured from 1kHz to 1MHz at different annealing conditions (a) As-deposited (b) 600°C annealed and (c) 800°C annealed in N $_2$ for 30seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47   |

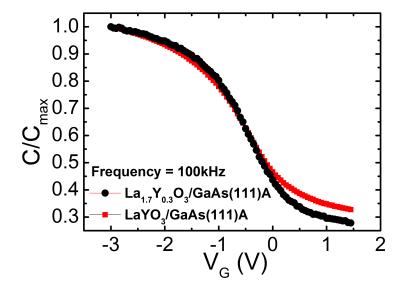

| 3.19 | A comparison of p-type 100 kHz C-V characteristics of Ni/Al $_2$ O $_3$ / La $_{1.8}$ Y $_{0.2}$ O $_3$ /GaAs(111)A and Ni/Al $_2$ O $_3$ /LaYO $_3$ /GaAs(111)A annealed at 800°C. A more stretched-out behavior is observed from the LaYO $_3$ /GaAs(111)A interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48   |

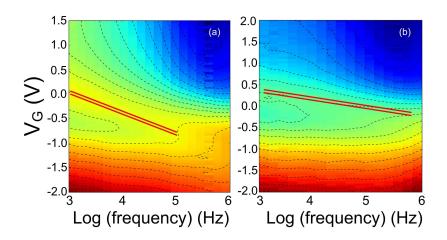

| 3.20 | Conductance spectroscopy in the plane of VG versus frequency from p-type C-V of (a) Ni/Al <sub>2</sub> O <sub>3</sub> /LaYO <sub>3</sub> /GaAs(111)A capacitors and (b) Ni/Al <sub>2</sub> O <sub>3</sub> /La <sub>1.8</sub> Y <sub>0.2</sub> O <sub>3</sub> /GaAs(111)A capacitors. Both samples were annealed at 800°C in N <sub>2</sub> for 30 seconds. The Fermi level traces are denoted by the double red lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49   |

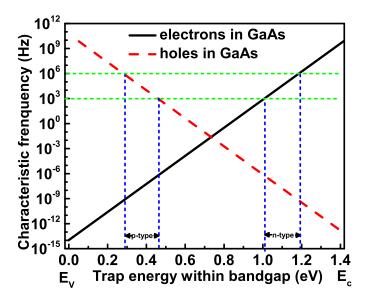

| 3.21 | Charge trapping characteristics for GaAs at room temperature (300K).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50   |

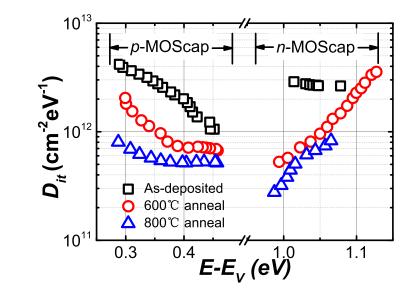

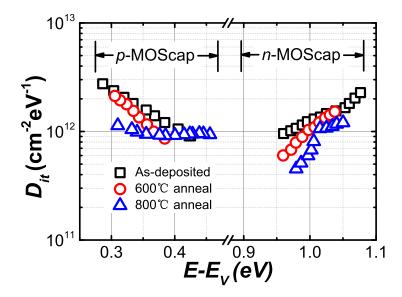

| 3.22 | $D_{it}$ distribution in GaAs band gap obtained on p-type and n-type capacitors with $La_{1.8}Y_{0.2}O_3/GaAs(111)A$ interface. The values are calculated by the conductance method at room temperature. A better interface is shown than the $D_{it}$ in Fig. 3.23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51   |

| 3.23 | $D_{it}$ distribution in GaAs band gap obtained on p-type and n-type capacitors with LaYO <sub>3</sub> /GaAs(111)A interfaces. The values are calculated by the conductance method at room temperature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52   |

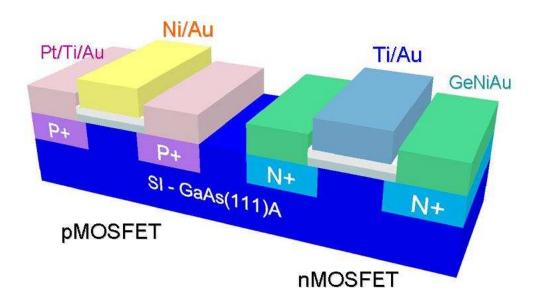

| 3.24 | Schematic view of a GaAs pMOSFET and an nMOSFET in the GaAs CMOS integrated circuits fabricated here. GeNiAu alloy is employed as S/D Ohmic contact metal for nMOSFETs and PtTi alloy is employed for pMOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54   |

|      | Pritoni minor in the contraction of the contraction | 01   |

| Figu | re P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

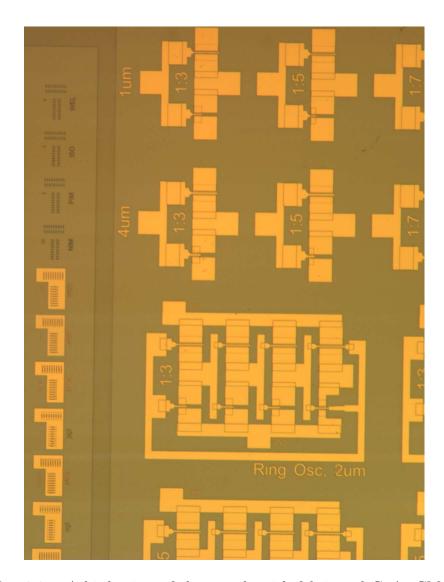

| 3.25 | A birds view of the sample with fabricated GaAs CMOS devices and circuits. The alignment marks are on the left part of the picture, which was used for alignment during the photolithography process for each layer. GaAs CMOS inverters are on the top right of the picture, and 1- $\mu$ m-gatelength and 4- $\mu$ m-gate-length pMOSFETs and nMOSFETs devices with different gate width ratios can be observed. Ring oscillators are at the bottom right part, and a complete 3-stage ring GaAs CMOS oscillator, with devices gate length of $2\mu$ m and gate width ratio of 1:3 (nMOSFETs to pMOSFETs), is shown. | 57  |

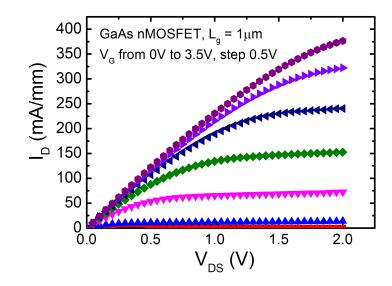

| 3.26 | Output characteristics ( $I_{DS} \sim V_{DS}$ ) for a $L_G = 1 \mu m$ GaAs(111)A nMOS-FET with GaAs/ $La_2O_3$ epitaxial interface. The maximum drain current can reach $\sim 376$ mA/mm with a gate bias of 3.5 V and a drain bias of 2 V                                                                                                                                                                                                                                                                                                                                                                             | 58  |

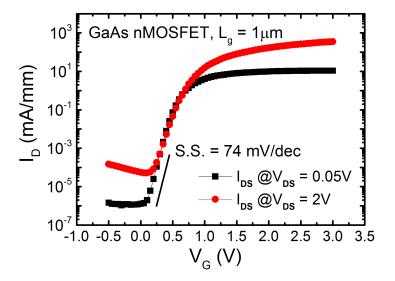

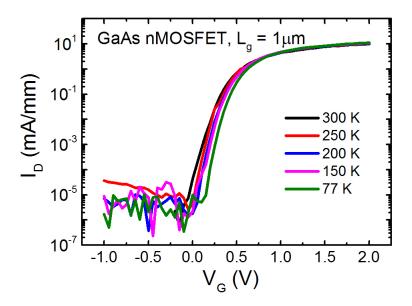

| 3.27 | Transfer characteristics ( $I_{DS} \sim V_{GS}$ ) for the same device shown in Fig. 3.26. A low subthreshold (SS) of 74 mV/dec is obtained from the transfer curve measured with $V_{DS} = 0.05$ V. The current on/off ratio is $\sim 10^7$ , showing the advantage of relative wide band gap of GaAs comparing to the narrower band gap semiconductors like InGaAs                                                                                                                                                                                                                                                    | 59  |

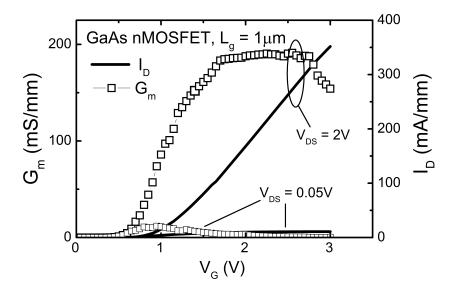

| 3.28 | Linear transfer characteristics and extrinsic transconductance $(g_m)$ versus $V_{GS}$ for the same device of Fig. 3.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60  |

| 3.29 | Effective electron mobility extracted from a $L_G=8~\mu m$ GaAs(111)A nMOSFET with GaAs/La <sub>2</sub> O <sub>3</sub> epitaxial interface. The peak mobility reaches 1150 cm <sup>2</sup> /V·s                                                                                                                                                                                                                                                                                                                                                                                                                        | 60  |

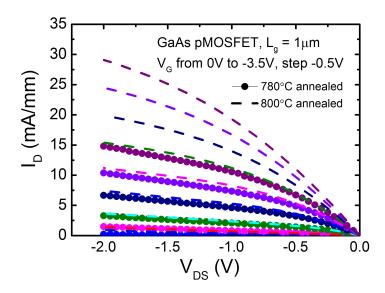

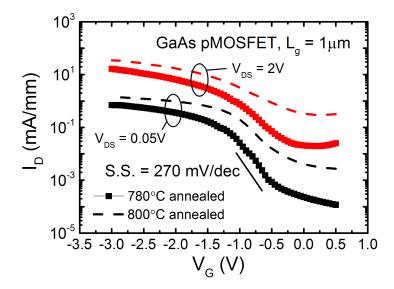

| 3.30 | Output characteristics ( $I_{DS} \sim V_{DS}$ ) for $L_G = 1 \mu m$ GaAs(111)A pMOSFETs with GaAs/ $La_2O_3$ epitaxial interface annealed with P+ ion activation at 780 °C for 30s and 800 °C for 15s. The maximum drain current is $\sim 30$ mA/mm with a gate bias of -3.5 V and a drain bias of -2 V from the pMOSFET device with 800 °C annealing                                                                                                                                                                                                                                                                  | 61  |

| 3.31 | Transfer characteristics ( $I_{DS} \sim V_{GS}$ ) for the same devices shown in Fig. 3.30. A subthreshold (SS) of 270 mV/dec is obtained from the transfer curve measured with $V_{DS} = 0.05$ V, for the GaAs pMOSFET with 780 °C ion activation annealing                                                                                                                                                                                                                                                                                                                                                            | 62  |

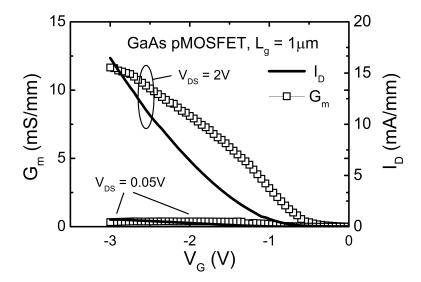

| 3.32 | Linear transfer characteristics and extrinsic transconductance $(g_m)$ versus $V_{GS}$ for the same device annealed at 780 °C for 30s of Fig. 3.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63  |

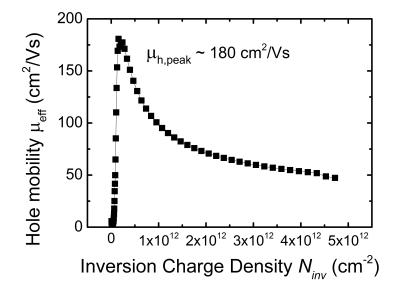

| 3.33 | Effective electron mobility extracted from a $L_G=8~\mu m$ GaAs(111)A pMOSFET with GaAs/La <sub>2</sub> O <sub>3</sub> epitaxial interface. The peak mobility reaches $180~{\rm cm^2/V \cdot s.}$                                                                                                                                                                                                                                                                                                                                                                                                                      | 63  |

| Figu | re                                                                                                                                                                                                                        | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

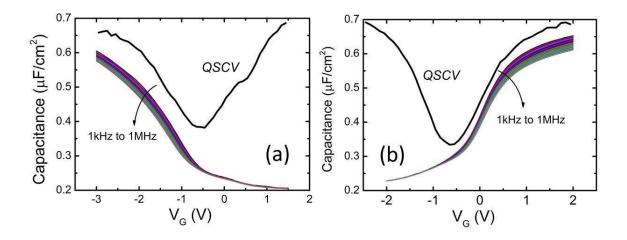

| 3.34 | Quasistatic and high-frequency Capacitance-Voltage characteristics measured from both p-type and n-type capacitors with ${\rm La_2O_3/GaAs}$ epitaxial interface                                                          | 64   |

| 3.35 | Comparison of Dit distribution of amorphous $Al_2O_3/GaAs(111)A$ and epitaxial $La_2O_3/GaAs(111)A$ interfaces in the GaAs band-gap. The values were deter-mined by the conductance method                                | 64   |

| 3.36 | Measured temperature dependent transfer characteristics of a 1 $\mu$ m-gatelength GaAs nMOSFET with La <sub>2</sub> O <sub>3</sub> /GaAs(111)A interface. The drain bias applied is 0.05 V                                | 65   |

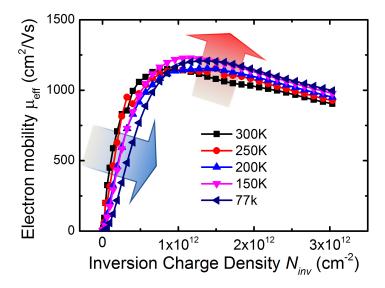

| 3.37 | Effective electron mobility versus inversion charge density is plotted in the 77K to 300K temperature range. The mobility increased at low temperature due to less phonon scattering                                      | 66   |

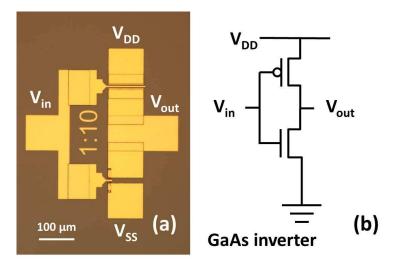

| 3.38 | (a) Optical micrograph of a GaAs CMOS inverter. The devices gate width ratio of nMOSFET to pMOSFET in this inverter is 1:10. (b) Circuit schematic of a CMOS inverter.                                                    | 67   |

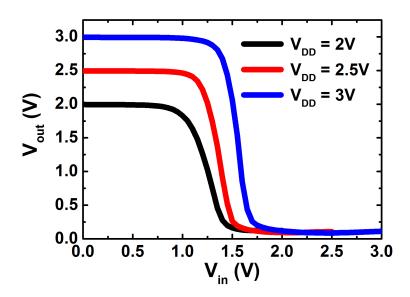

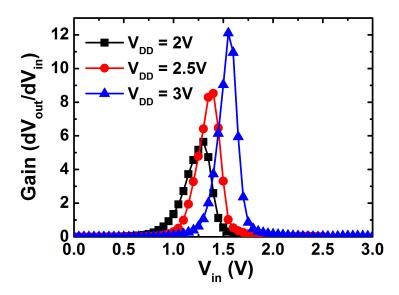

| 3.39 | Transfer characteristics of a GaAs CMOS inverter, measured with different supply voltages $V_{DD}=2V,2.5V$ and $3V.\ldots\ldots\ldots\ldots\ldots$                                                                        | 68   |

| 3.40 | GaAs CMOS inverter gain (dVout/dVin) as a function of input voltage. A gain of $\sim 12$ is achieved with $V_{DD}=3V.$                                                                                                    | 69   |

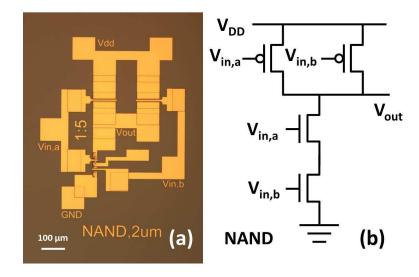

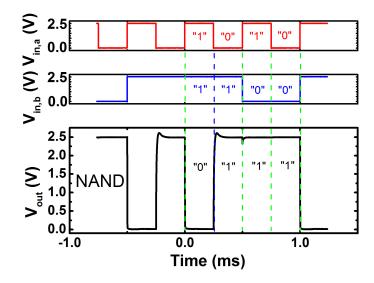

| 3.41 | (a) Optical micrograph of a GaAs CMOS NAND logic gate. The devices gate width ratio of nMOSFET to pMOSFET in this inverter is 1:5. (b) Circuit schematic of a CMOS NAND gate                                              | 69   |

| 3.42 | Input $V_{in}$ and output voltage $V_{out}$ of the GaAs CMOS NAND logic gate in Fig. 15. Four combinations of input states 1 1, 0 1, 1 0 and 0 0 and corresponding output states are marked                               | 70   |

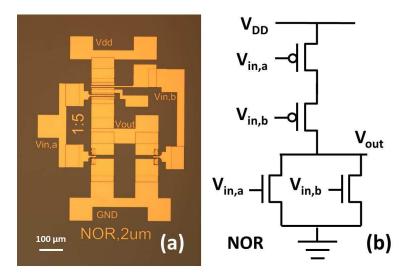

| 3.43 | (a) Optical micrograph of a GaAs CMOS NOR logic gate. The devices gate width ratio of nMOSFET to pMOSFET in this inverter is 1:5. (b) Circuit schematic of a CMOS NOR gate                                                | 71   |

| 3.44 | Input $V_{in}$ and output voltage $V_{out}$ of the GaAs CMOS NOR logic gate in Fig. 15. Four combinations of input states 1 1, 0 1, 1 0 and 0 0 and corresponding output states are marked                                | 71   |

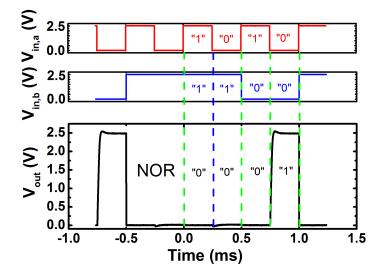

| 3.45 | (a) Schematic illustration, (b) circuit schematic, (c) optical micrograph and (d) output characteristics of a GaAs CMOS five-stage ring oscillator. The dash line denotes the five stage inverters in the ring oscillator | 72   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                      | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

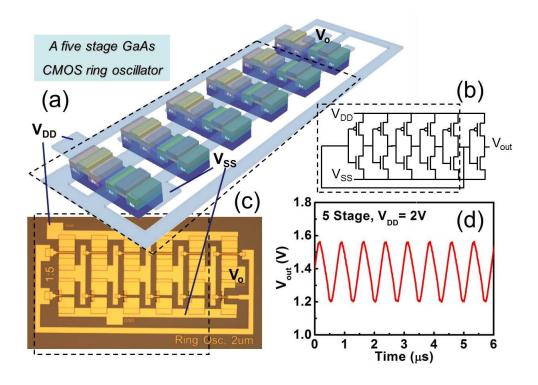

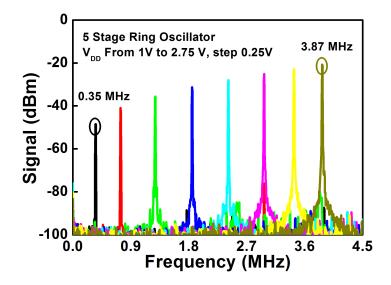

| 3.46 | Measured output power spectrum of a five-stage GaAs CMOS ring oscillator. The fundamental oscillation frequency increases from 0.35 MHz to 3.87 MHz as $V_{DD}$ increases from 1 V to 2.75 V                                                                                                                                                            | 73   |

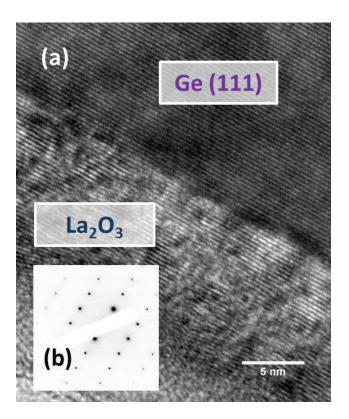

| 4.1  | (a) Cross-sectional TEM image of $La_2O_3/Ge(111)A$ epitaxial interface, and (b) the corresponding electron diffraction pattern taken from the same sample as shown in (a).                                                                                                                                                                             | 75   |

| 4.2  | (a) Cross-sectional TEM image of $La_2O_3/Ge(111)A$ epitaxial interface, and (b) the corresponding electron diffraction pattern taken from the same sample as shown in (a)                                                                                                                                                                              | 76   |

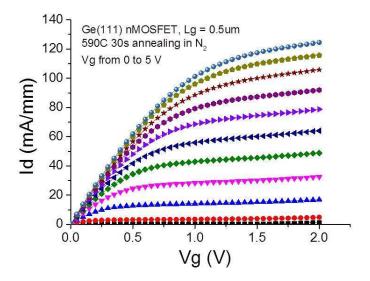

| 4.3  | Output characteristics ( $I_{DS} \sim V_{DS}$ ) for a $L_G = 0.5 \mu m$ Ge(111) nMOSFET with Ge/La <sub>2</sub> O <sub>3</sub> epitaxial interface. The maximum drain current is around $\sim$ 124 mA/mm with a gate bias of 5 V and a drain bias of 2 V                                                                                                | 77   |

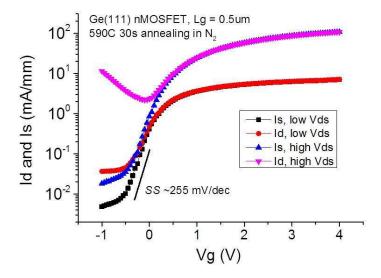

| 4.4  | Transfer characteristics ( $I_D$ and $I_S \sim V_{GS}$ ) for the same device shown in Fig. 4.3. A subthreshold (SS) of 255 mV/dec is obtained from the transfer curve $I_S \sim V_G$ measured with $V_{DS} = 0.05$ V. The difference between drain current and source current is due to the junction leakage induced by unoptimized fabrication process | 78   |

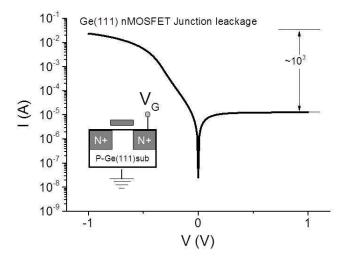

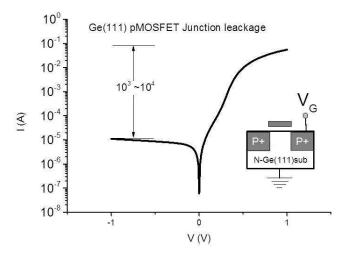

| 4.5  | I-V characteristics of the Ge N <sup>+</sup> -P junctions formed by phosphorous ion implantation and activation annealing at 590 °C for 30 seconds. Relative high junction leakage current and low current ratio $\sim 10^3$ is obtained due to the un-optimized fabrication process                                                                    |      |

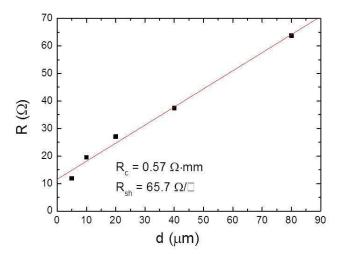

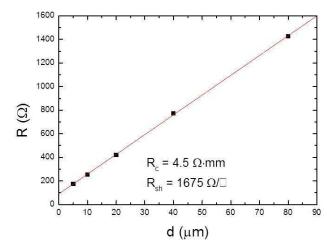

| 4.6  | The contact resistance $R_c$ of the Ge nMOSFETs and sheet resistance of the implanted areas (N+) extraction with the transmission line methods (TLM)                                                                                                                                                                                                    |      |

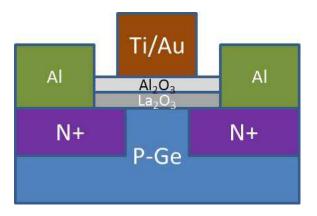

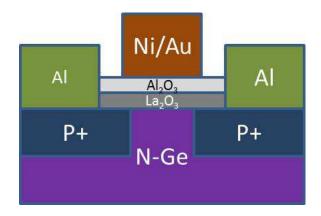

| 4.7  | Schematic view of an $Ge(111)$ inversion-mode pMOSFET with ALE $La_2O_3$ as gate dielectric.                                                                                                                                                                                                                                                            | 80   |

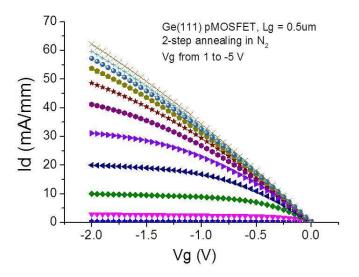

| 4.8  | Output characteristics ( $I_{DS} \sim V_{DS}$ ) for a $L_G = 0.5 \mu m$ Ge(111) pMOSFET with Ge/La <sub>2</sub> O <sub>3</sub> epitaxial interface. The maximum drain current is around $\sim$ 124 mA/mm with a gate bias of 5 V and a drain bias of 2 V                                                                                                | 81   |

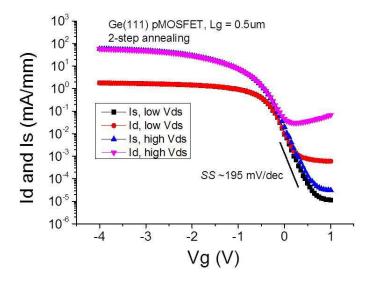

| 4.9  | Transfer characteristics ( $I_D$ and $I_S \sim V_{GS}$ ) for the same device shown in Fig. 4.3. A subthreshold (SS) of 255 mV/dec is obtained from the transfer curve $I_S \sim V_G$ measured with $V_{DS} = 0.05$ V. The difference between drain current and source current is due to the junction leakage induced by unoptimized fabrication process | 82   |

| 4.10 | Rectifying characteristics of the Ge $P^+$ -N junctions formed by phosphorous ion implantation and two-step annealing process. Better junction performance is obtained comparing to the $N^+$ -P junctions                                                                                                                                              | 83   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                 | Page    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

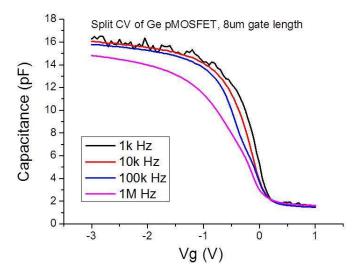

| 4.11 | Split-CV characteristics measure from a $L_G=8\mu m$ Ge(111) pMOSFET with Ge/La <sub>2</sub> O <sub>3</sub> epitaxial interface. Small frequency can be observed from the 1 kHz to 1 MHz CV characteristics, indicating low density of traps at the Ge/La <sub>2</sub> O <sub>3</sub> interface                                                                    | 83      |

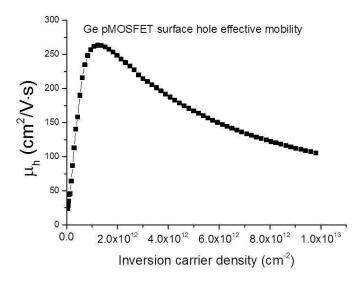

| 4.12 | Effective electron mobility extracted from a $L_G=8\mu m$ Ge(111) pMOSFET with Ge/La <sub>2</sub> O <sub>3</sub> epitaxial interface. The peak hole mobility is $\sim 270$ cm <sup>2</sup> /V·s, obtained at low inversion charge region (N <sub>inv</sub> $\sim 1 \times 10^1 2$ cm <sup>-2</sup> )                                                               | 84      |

| 4.13 | The contact resistance $R_c$ of the Ge pMOSFETs and sheet resistance of the implanted areas (P+) extraction with the transmission line methods (TLM)                                                                                                                                                                                                               | 84      |

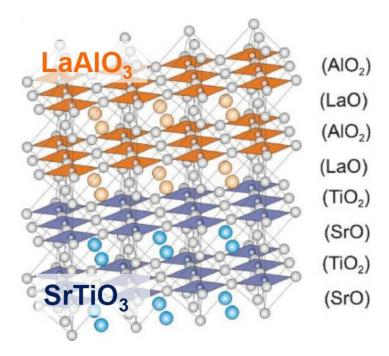

| 5.1  | Schematic view of crystalline LaAlO $_3$ oxide on Ti-terminated SrTiO $_3$ substrate. The 2 dimensional electron gas forms at the interface of the two oxide layers $[55, 56]$                                                                                                                                                                                     | 86      |

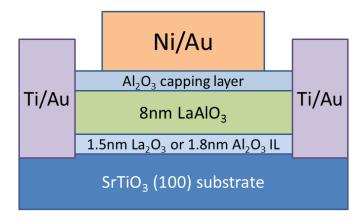

| 5.2  | Schematic view of an accumulation-mode NMOSFET on Ti-terminated $SrTiO_3$ substrate with 2 types of ALD LaAlO $_3$ gate stacks                                                                                                                                                                                                                                     | 87      |

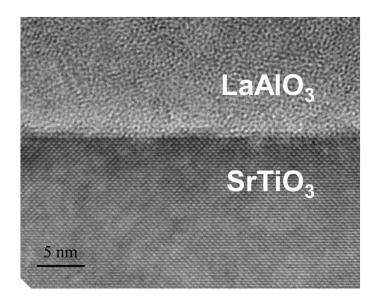

| 5.3  | Cross-section High Resolution Transmission Electron Microscopy (HRTEM image of ALD LaAlO $_3$ /SrTiO $_3$ interface. A sharp and clean interface is obtained between the top Atomic Layer Deposited (ALD) amorphous LaAlO $_3$ layer and the bottom single crystalline SrTiO $_3$ (100) sbustrate.                                                                 | )<br>89 |

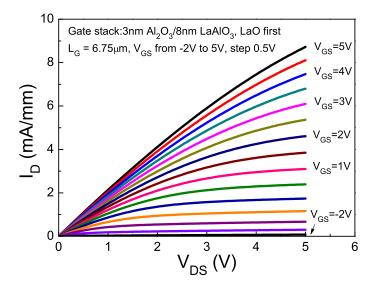

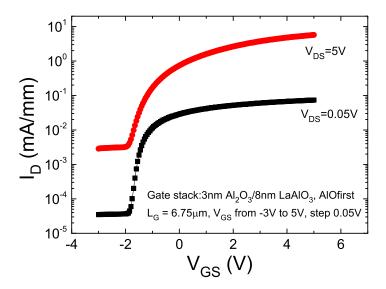

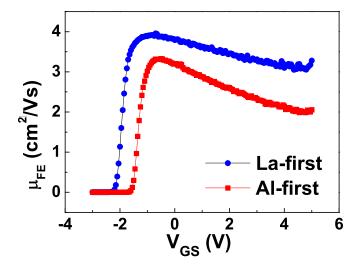

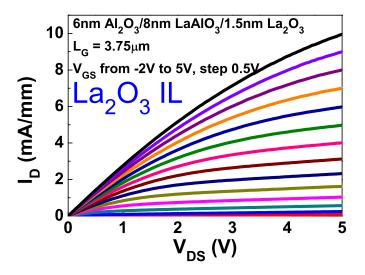

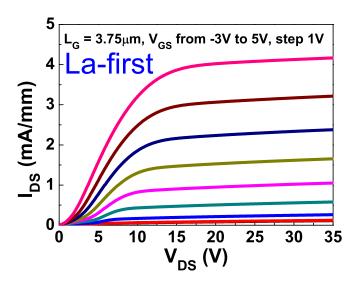

| 5.4  | The output characteristics of a SrTiO <sub>3</sub> MOSFET with La-first cycle LaAlO <sub>3</sub> as gate dielectric. The gate length of the device is 6.75 $\mu$ m                                                                                                                                                                                                 | 90      |

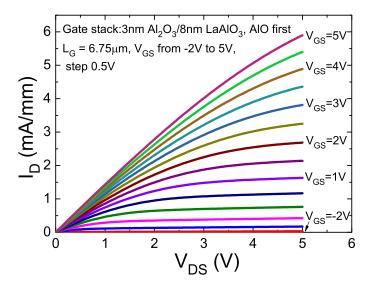

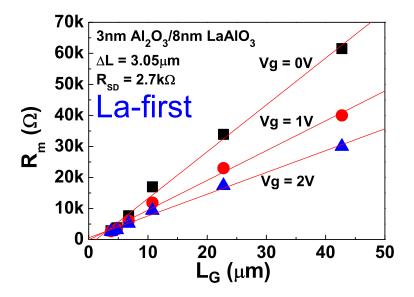

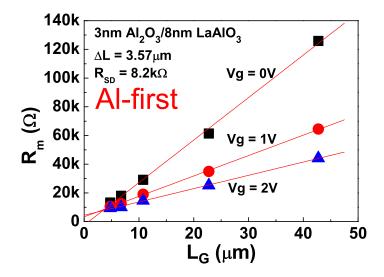

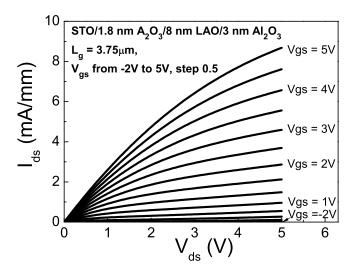

| 5.5  | The output characteristics of a SrTiO <sub>3</sub> MOSFET with Al-first cycle LaAlO <sub>3</sub> as gate dielectric. The gate length of the device is $6.75~\mu m$                                                                                                                                                                                                 | 91      |

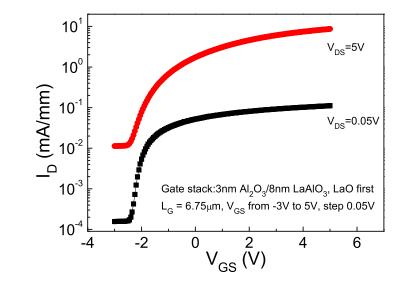

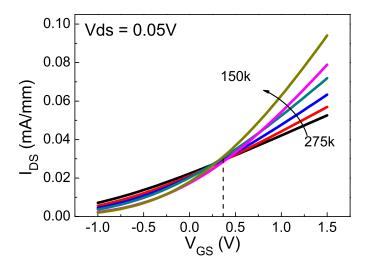

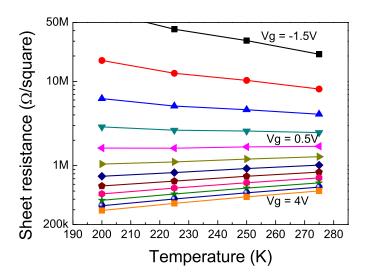

| 5.6  | The transfer characteristics of a SrTiO_3 MOSFET with La-first cycle LaAlO_3 as gate dielectric. The gate length of the device is 6.75 $\mu m$ .                                                                                                                                                                                                                   | 92      |

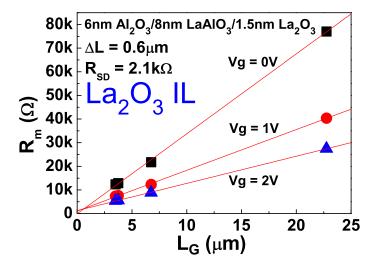

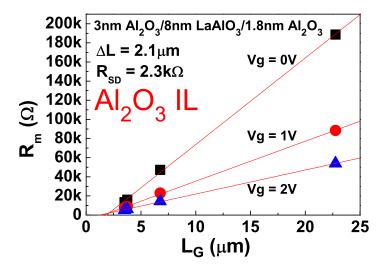

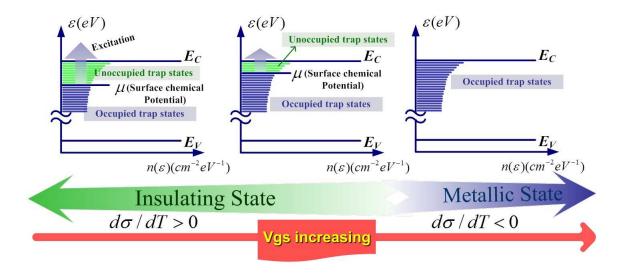

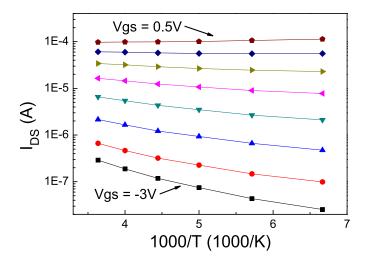

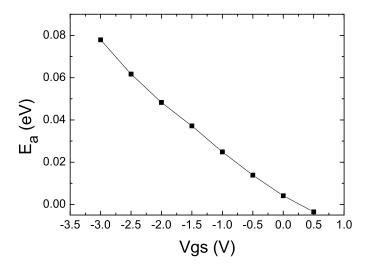

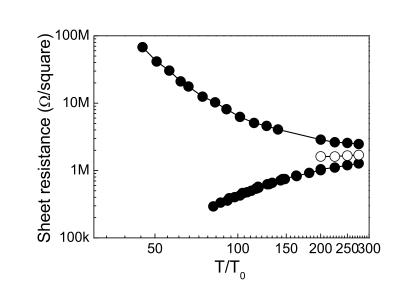

| 5.7  | The transfer characteristics of a SrTiO_3 MOSFET with Al-first cycle LaAlO_3 as gate dielectric. The gate length of the device is 6.75 $\mu m$ .                                                                                                                                                                                                                   | 93      |