# University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

July 2016

# Development of a Portable CMOS Time-Domain Fluorescence Lifetime Imager

Hongtao Wang University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

#### **Recommended Citation**

Wang, Hongtao, "Development of a Portable CMOS Time-Domain Fluorescence Lifetime Imager" (2016). *Doctoral Dissertations*. 670. https://doi.org/10.7275/8391959.0 https://scholarworks.umass.edu/dissertations\_2/670

This Campus-Only Access for Five (5) Years is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# DEVELOPMENT OF A PORTABLE CMOS TIME-DOMAIN FLUORESCENCE LIFETIME IMAGER

A Dissertation Presented

by

HONGTAO WANG

Submitted to the Graduate School of the

University of Massachusetts Amherst in partial fulfillment

of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2016

Electrical and Computer Engineering

© Copyright by Hongtao Wang 2016

All Rights Reserved

# DEVELOPMENT OF A PORTABLE CMOS TIME-DOMAIN FLUORESCENCE

# LIFETIME IMAGER

A Dissertation Presented

by

## HONGTAO WANG

Approved as to style and content by:

Christopher D. Salthouse, Chair

Robert W. Jackson, Member

Deepak K. Ganesan, Member

C.V. Hollot, Department Head Department of Electrical and Computer Engineering

# DEDICATION

To my parents.

## ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to Professor Christopher Salthouse. Working in Biomedical Electronics Laboratory directed by Professor Salthouse was one of the greatest experiences in my life. He spent significant amount of time teaching me engineering skills hand by hand. He offered me as many as brainstorm ideas in solving challenging research problems. He provided me funding resources to guarantee a good focus on implementing creative solutions. In my "painful" days working in lab testing circuits and debugging codes, it was him who appreciated my little progress, and kept encouraging me to persistently and independently working things out. His nice personality made me feel he was not a rigorous mentor, but a friend who cares about my career and life in all ways.

I own my sincere gratitude to Professor Robert Jackson. He was the defense committee member for both my M.S. and Ph.D., my teaching assistant advisor for Electronics I and II, and the lecturer of my "Analog IC Design" course. Back to 2011, he recommended me to join in Biomedical Electronics Laboratory. I express my sincere appreciation to him for his recognition and encouragement.

I also own my sincere gratitude to Professor Deepak Ganesan. He provided me valuable funding resources and lab resources in developing a low power imager tape-out. I would like to thank him for his generous support, and the time serving as my Ph.D. committee member.

V

I appreciate my labmates Dr. Akshaya Shanmugam and Mrs. Shuo Li for their kind help in the past 5 years. I would extend my gratitude to Mr. Addison Mayberry, who helped me build instruments to test the low power imager IC. I hope all of them will build successful careers and end up with happy lives.

In the end, I own the deepest gratitude to my lovely parents. They gave me strongest emotional care that supported me to overcome many difficult periods throughout my Ph.D. Forever they are the most important people in my life.

## ABSTRACT

# DEVELOPMENT OF A PORTABLE CMOS TIME-DOMAIN FLUORESCENCE LIFETIME IMAGER

MAY 2016

HONGTAO WANG B.E., XIDIAN UNIVERSITY M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS, AMHERST Ph.D., UNIVERSITY OF MASSACHUSETTS, AMHERST

Directed by: Professor Christopher D. Salthouse

Modern laboratory equipments to measure the excited-state lifetime of fluorophores usually include an expensive picosecond pulsed-laser excitation source, a fragile photomultiplier tube, and a large instrument body for optics. A portable and robust device to make fluorescence lifetime measurement in nanosecond scale is of great attraction for chemists and biologists.

This dissertation reports the development of a portable LED time-domain fluorimeter from an all-solid-state discrete-component prototype to its advanced CMOS integrated circuit implementation. The motivation of the research is to develop a multiplexed fluorimeter for point-of-care diagnosis. Instruments developed by this novel method have higher fill factor, are more portable, and are fabricated at lower cost.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                            | v    |

|-----------------------------------------------------------------------------|------|

| ABSTRACT                                                                    | vii  |

| LIST OF TABLES                                                              | xiii |

| LIST OF FIGURES                                                             | xiv  |

| CHAPTER                                                                     |      |

| 1. INTRODUCTION                                                             | 1    |

| 2. ALL-SOLID-STATE TIME-DOMAIN FLUORIMETER DISCRETE-<br>COMPONENT PROTOTYPE | 11   |

| 2.1 Discussion on existing fluorescence lifetime sensing method             | 11   |

| 2.2 Time-gated photon integration sensing method                            | 12   |

| 2.3 Hardware architecture and circuit implementations                       | 15   |

| 2.3.1 System block diagram                                                  | 15   |

| 2.3.2 Ring oscillator                                                       | 16   |

| 2.3.3 Delay circuit                                                         | 18   |

| 2.3.4 Excitation circuit                                                    | 19   |

| 2.3.5 Sensing circuit                                                       | 21   |

| 2.4 Experimental results                                                    | 24   |

| 2.4.1 Fluorimeter prototype overview                                                        | . 24 |

|---------------------------------------------------------------------------------------------|------|

| 2.4.2 Characterization result                                                               | . 26 |

| 2.4.3 Improvement on the detection limit                                                    | . 28 |

| <b>3.</b> ACTIVE PIXEL SENSOR CHARACTERIZATION UNDER TSMC 0.35 μ<br>HIGH VOLTAGE TECHNOLOGY |      |

| 3.1 Motivation to characterize sensor on the targeting technology                           | . 33 |

| 3.2 CMOS active pixel sensor in TSMC 0.35 µm high voltage technology                        | . 34 |

| 3.3 Sensor characterization method                                                          | . 37 |

| 3.4 Experimental results                                                                    | . 41 |

| 3.4.1 LED light power characterization                                                      | . 42 |

| 3.4.2 Sensitivity and linearity of the CMOS 3-T APS with PMOS FET reset                     | . 42 |

| 3.4.3 Sensitivity and linearity of the CMOS 3-T APS with NMOS FET reset                     | . 50 |

| 3.4.4 Reset speed                                                                           | . 51 |

| 3.4.5 Summary                                                                               | . 60 |

| 4. MIXED-SIGNAL BUILDING BLOCKS OF CMOS TIME-DOMAIN<br>FLUORIMETER IC                       | . 61 |

| 4.1 Design consideration                                                                    | . 61 |

| 4.2 System architecture of the Imager IC                                                    | . 62 |

| 4.3 Individual functional block design and verification                                     | . 64 |

| 4.3.1 Gating controller                                                                     | . 65 |

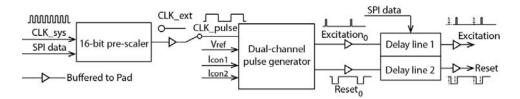

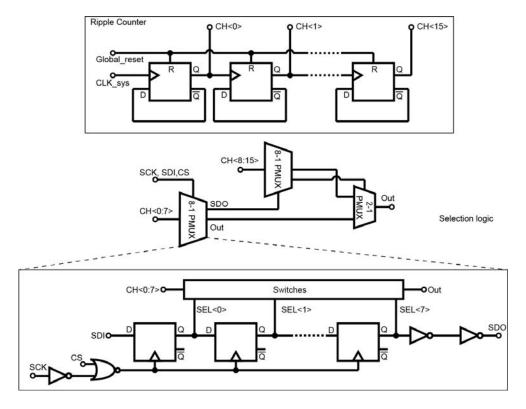

| 4.3.1.1 16-bit pre-scalar design and the measurement                                        | . 65 |

| 4.3.1.2 Dual-channel pulse generator design and measurement                                 | . 67 |

| 4.3.1.3 Delay line design and measurement                                                   | . 71 |

| 4.3.2 Switched-capacitor programmable-gain amplifier (SC-PGA) design and measurement        | . 74 |

| 4.3.2.1 Circuit design and closed-loop gain analysis                    |     |

|-------------------------------------------------------------------------|-----|

| 4.3.2.2 Noise analysis                                                  |     |

| 4.3.2.3 Layout and post-layout simulation                               |     |

| 4.3.2.4 Post-silicon measurement results and discussion                 |     |

|                                                                         |     |

| 4.3.3 10-bit column-parallel overlapping-subrange SAR ADC (CPOSSAR ADC) |     |

| 4.3.3.1 CPOSSAR ADC architecture                                        |     |

| 4.3.3.2 Overlapping subrange technique                                  |     |

| 4.3.3.3 ADC I/O                                                         | 101 |

| 4.3.3.4 10-bit CPOSSAR ADC measurement                                  | 103 |

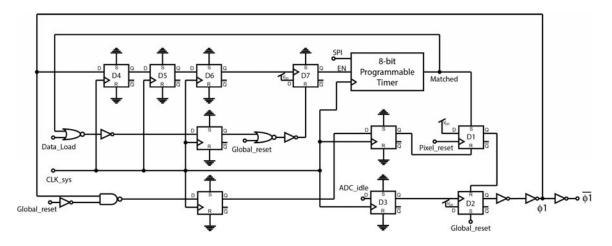

| 4.3.4 Timing controller                                                 | 105 |

| 4.3.4.1 Top-level control logic                                         | 106 |

| 4.3.4.2 Lower-level control logic                                       | 109 |

| 4.3.4.3 Design and testing on timing controller                         |     |

| 4.3.4.4 Full custom design of the top and lower-level controllers       | 115 |

| 4.3.4.4.1 Pulse synchronizer                                            | 116 |

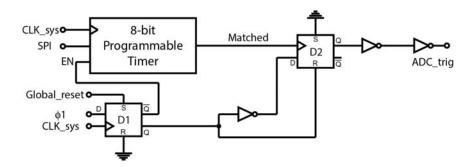

| 4.3.4.4.2 SC-PGA sampling timer                                         | 116 |

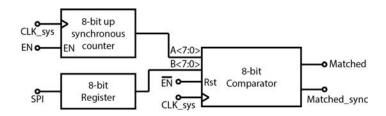

| 4.3.4.4.3 8-bit programmable timer                                      | 117 |

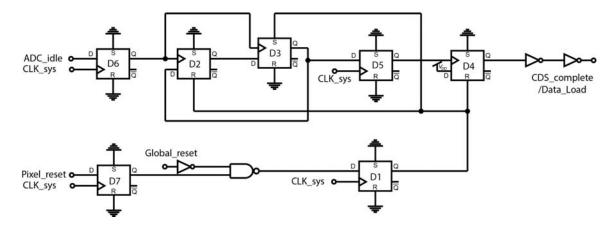

| 4.3.4.4 CDS Completed/Data Load                                         | 118 |

| 4.3.4.4.5 SC-PGA amplification timer                                    | 119 |

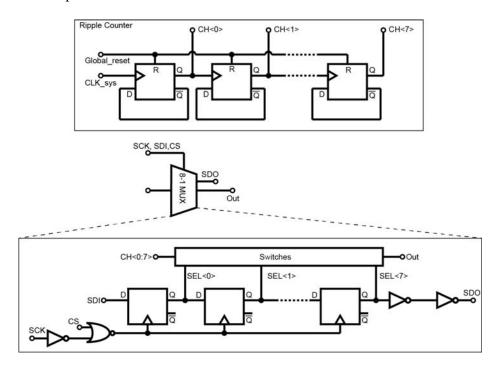

| 4.3.4.4.6 8-bit pre-scalar                                              | 120 |

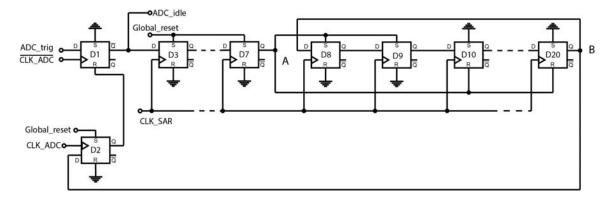

| 4.3.4.4.7 ADC state register                                            | 121 |

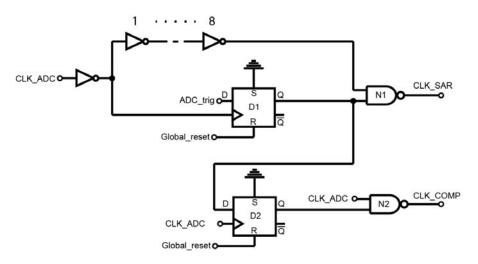

| 4.3.4.4.8 ADC clock synchronizer                                        | 122 |

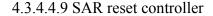

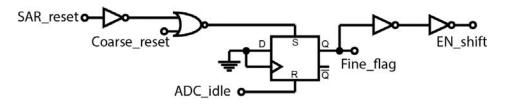

| 4.3.4.4.9 SAR reset controller                                          | 123 |

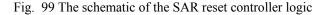

| 4.3.4.4.10 Coarse control                                               | 124 |

| 4.3.4.4.11 MSB load                                                     | 125 |

| 4.3.4.4.12 Fine control and shift enable                                | 125 |

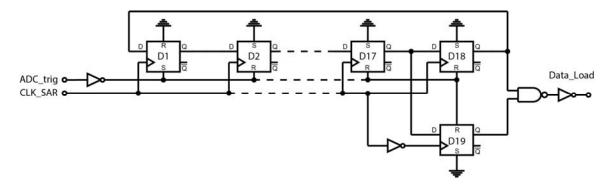

| 4.3.4.4.13 ADC data load                                              | 126   |

|-----------------------------------------------------------------------|-------|

|                                                                       |       |

| 5. FLUORESCENCE LIFETIME IMAGER CAMERA MODULE                         | 1.0.0 |

| INTEGRATION                                                           |       |

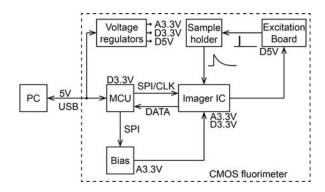

| 5.1 Chip controller hardware                                          | 128   |

|                                                                       |       |

| 5.1.1 PIC32 microcontroller                                           | 128   |

| 5.1.2 Xilinx Cool Runner II CPLD                                      | 129   |

| 5.1.3 Programmable voltage and current reference                      | 130   |

| 5.1.4 Excitation circuit                                              | 131   |

| 5.1.5 Power supply                                                    | 131   |

| 5.1.6 CMOS fluorimeter integration                                    |       |

| 5.2 Testing of portable CMOS time-domain fluorescence lifetime imager | 133   |

| 5.2.1 Measuring 405 nm excitation pulse decay time                    | 133   |

| 5.2.2 Measurement on commercial fluorophores by a single pixel        | 135   |

| 5.2.3 Single pixel measurement detection limit                        | 138   |

| 5.2.4 Fluorescein lifetime measured with well spaced pixels           |       |

| 6. CONCLUSION                                                         | 152   |

| BIBLIOGRAPHY                                                          | 156   |

# LIST OF TABLES

| Table                                                                                       |    |

|---------------------------------------------------------------------------------------------|----|

| 1. The comparison of various types of fluorimeters                                          | 6  |

| 2. 16-bit pre-scalar circuit post-simulation data and the post-silicon measurement data     | 67 |

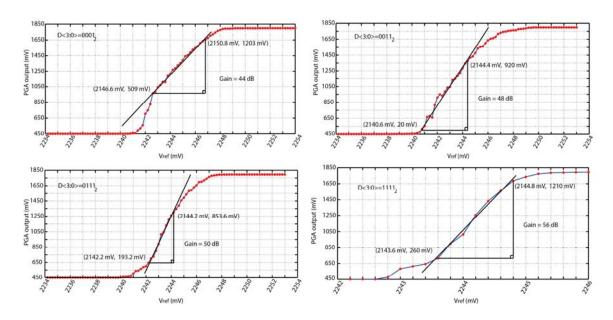

| 3. Summary of post-layout simulated gains and measured gains for all types of gain settings | 95 |

# **LIST OF FIGURES**

| Figure     Pag                                                                                                  | e  |

|-----------------------------------------------------------------------------------------------------------------|----|

| 1. The illustration of fluorescence in energy level diagram (a) and time domain (b)                             | 1  |

| 2. The system architecture of time-correlated single-photo counter (TCSPC)                                      | 2  |

| 3. The system architecture of the phase-modulation fluorimeter (a) and its time-domain response (b)             | 3  |

| 4. The illustration of integration by part fluorescence lifetime sensing mechanism 1                            | 3  |

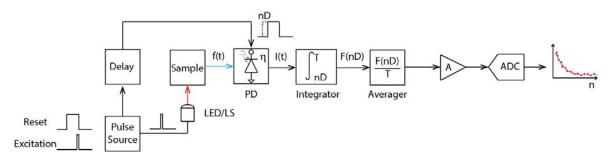

| 5. The behavior model of the time-domain solid-state fluorimeter discrete-component prototype                   | 3  |

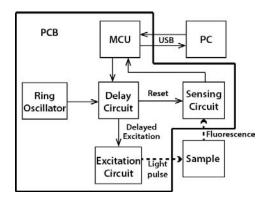

| 6. The block diagram of the discrete-component based fluorimeter prototype 1                                    | 6  |

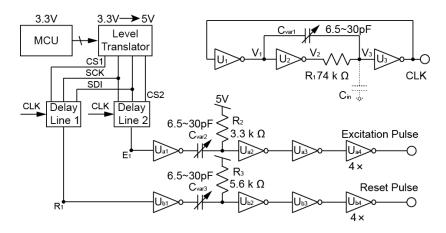

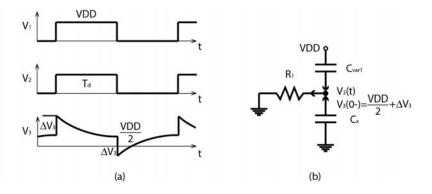

| 7. The schematic of the pulsing circuit[66] 1                                                                   | 6  |

| 8. The analysis on ring oscillator 1                                                                            | 7  |

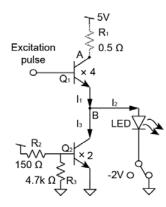

| 9. The schematic of the high speed LED driver circuit [66]                                                      | 20 |

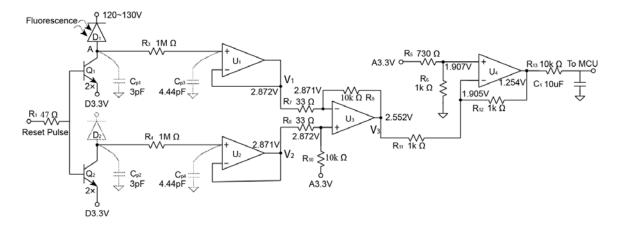

| 10. The schematic of the sensing circuit[66]                                                                    | 21 |

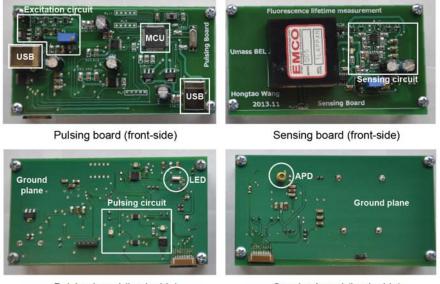

| <ol> <li>The fabricated printed circuit boards of the discrete-component fluorimter<br/>prototype[66]</li></ol> | 24 |

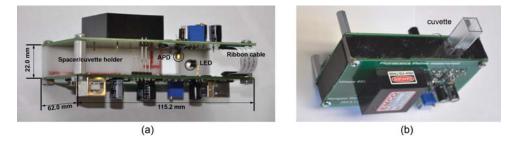

| 12. The assembled discrete-components based fluorimeter prototype [66] 2                                        | 25 |

| 13. The measurement result of 5 $\mu$ M/L 'lucifer yellow' dissolved in PBS[66]2                                | 26 |

| 14. The measurement results for 3 commercial fluorophores[66]                                                   | 27 |

| 15. The detection limit measurement of the discrete-component fluorimeter prototype[66]. 2                      | 27 |

| 16. The fabricated PCBs of the second version discrete-component fluorimeter                                    | 28 |

| 17. The assembled second version discrete-component fluorimeter                                                 | 30 |

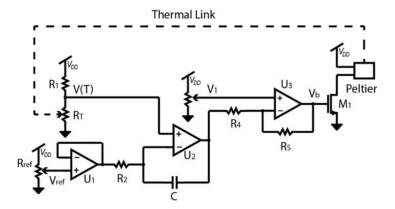

| 18. | The proportional-integral temperature control circuit used to control the instrument temperature                                                                          | . 31 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

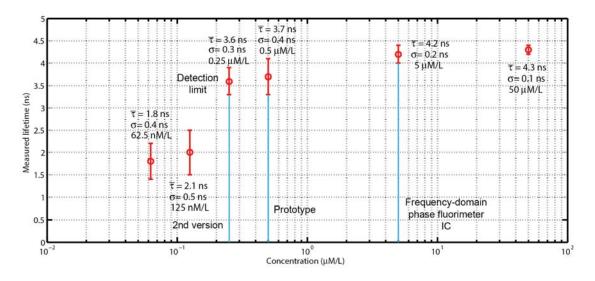

| 19. | The detection limit measurement result of the second version discrete component fluorimeter.                                                                              | . 32 |

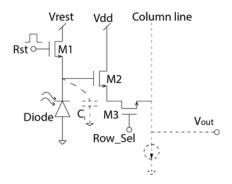

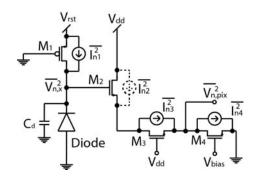

| 20. | The schematic of a CMOS 3-T active pixel sensor                                                                                                                           | . 35 |

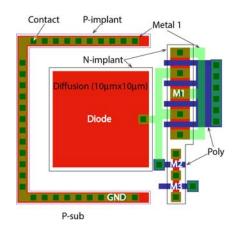

| 21. | A typical 3-T CMOS active pixel sensor layout                                                                                                                             | . 37 |

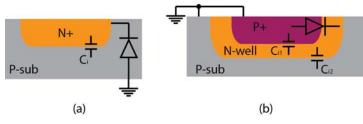

| 22. | The cross-sectional view of photodiode fabricated on p-type substrate (a) and on n-well (b)                                                                               |      |

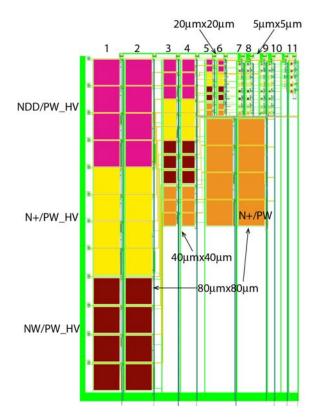

| 23. | The layout of the 3-T CMOS APS testing array                                                                                                                              | . 39 |

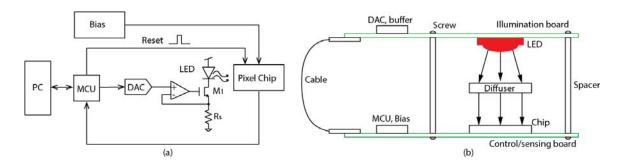

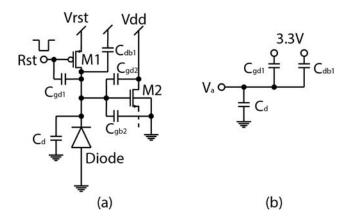

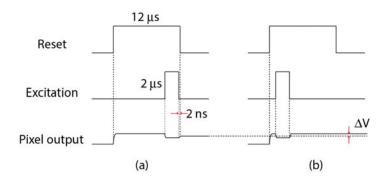

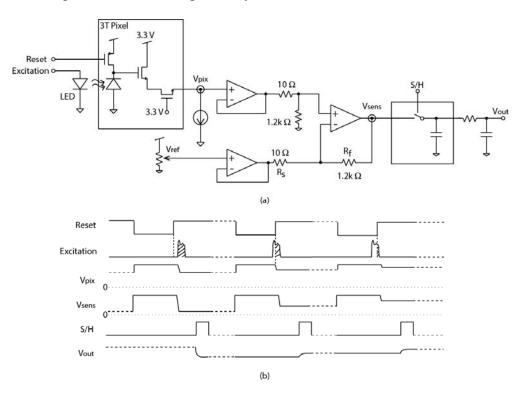

| 24. | The schematic of the CMOS 3-T APS array testing board (a) and board connection (b)                                                                                        | . 40 |

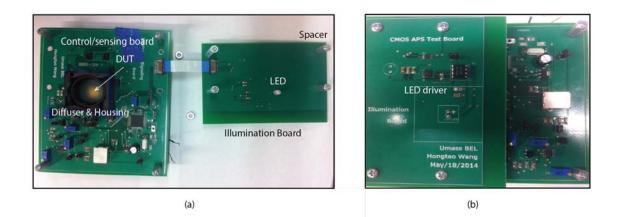

| 25. | The assembled CMOS 3-T APS array testing boards                                                                                                                           | . 41 |

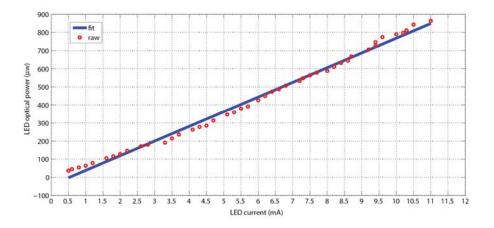

| 26. | The characterization curve of LED light power vs. LED current                                                                                                             | . 42 |

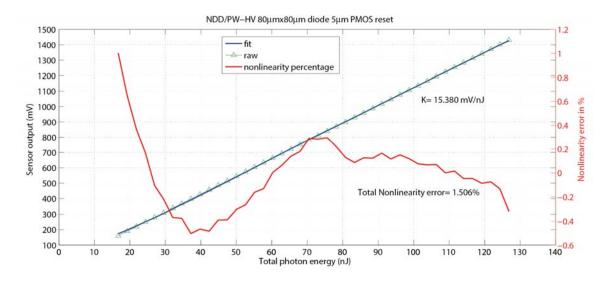

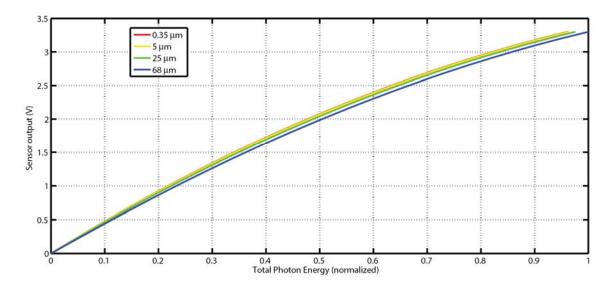

| 27. | The response of the 80 $\mu$ m × 80 $\mu$ m NDD/PW_HV PMOS FET-reset 3-T APS to light energy.                                                                             |      |

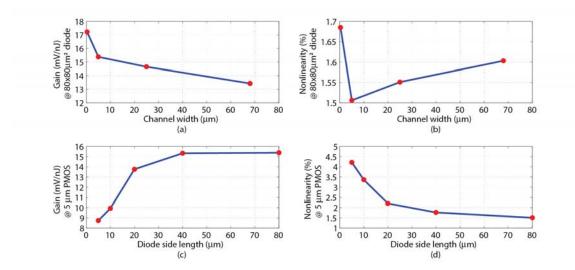

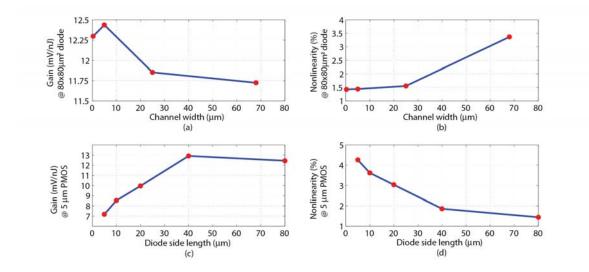

| 28. | The sensitivity (Gain) and the total non-linearity of NDD/PW_HV PMOS FET reset APSs                                                                                       | . 44 |

| 29. | The parasitic capacitors at the cathode of photodiode (a), and the dominant capacitors used to quantitatively analyze the sensitivity and the nonlinearity of the APS (b) | . 45 |

| 30. | The photon-energy transfer curve plotted according to analytical expression with different sizes of the reset transistors                                                 | . 46 |

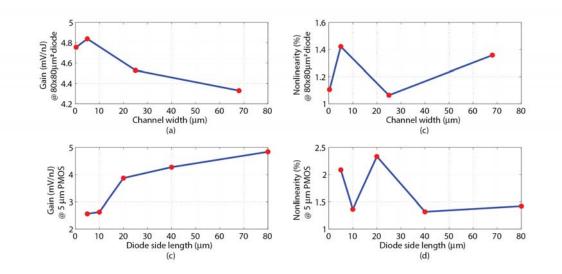

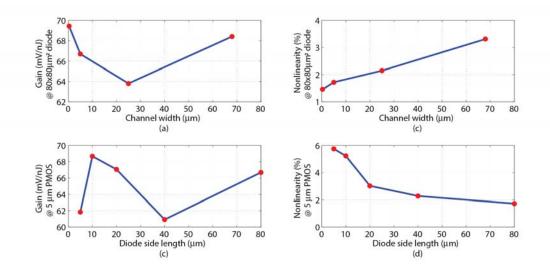

| 31. | The sensitivity (Gain) and the total non-linearity measurement results for N+/PW_HV PMOS FET reset APSs.                                                                  | . 48 |

| 32. | The sensitivity (Gain) and the total non-linearity measurement results for N+/PW PMC FET reset APSs.                                                                      |      |

| 33. | The sensitivity (Gain) and total non-linearity measurement results for NW/PW_HV PMOS FET reset APSs.                                                                      | . 49 |

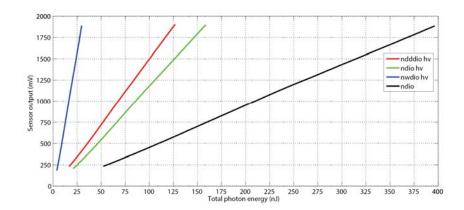

| 34. | The linear response to light energy for four types of APS with 80 $\mu$ m $\times$ 80 $\mu$ m photodiode                                                                  | . 50 |

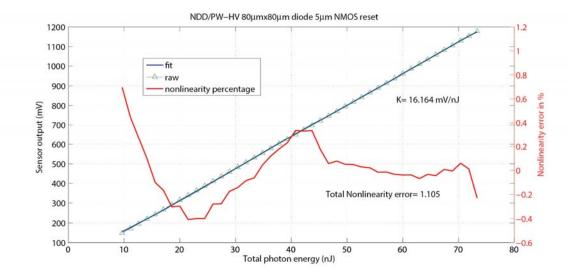

| 35. | The sensitivity (Gain) and nonlinearity measurement result of the $80\mu m \times 80 \mu m$ NDD/PW_HV APS with 5 $\mu m$ wide NMOS FET reset transistor.                   | . 50 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

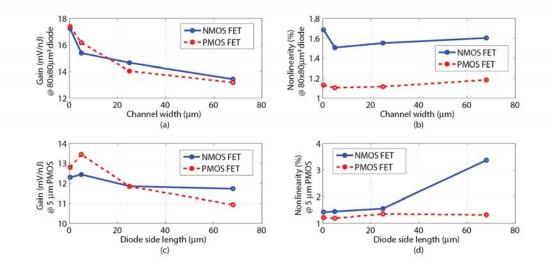

| 36. | The comparison of sensitivity (Gain) and nonlinearity of NMOS FET and PMOS FET reset APSs with 80 $\mu$ m × 80 $\mu$ m diode and different reset transistor channel widths | . 51 |

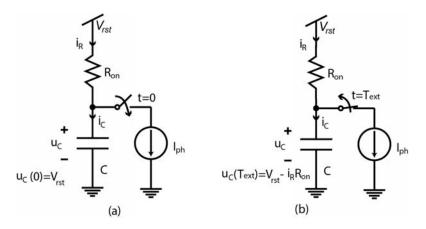

| 37. | The equivalent circuit models of the APS during and after the excitation light interference in reset phase.                                                                |      |

| 38. | The coarse measurement on the reset speed of the APS                                                                                                                       | . 54 |

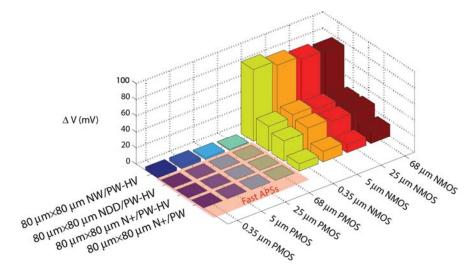

| 39. | The coarse reset speed measurement results for various types of APSs                                                                                                       | . 55 |

| 40. | The fine measurement on the reset speed of the APS                                                                                                                         | . 56 |

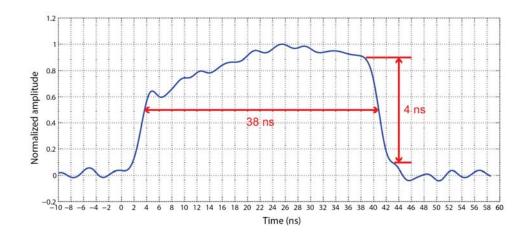

| 41. | The excitation light pulse measured by an avalanche photodiode (Hamamatsu, S2382) and a 5GS/s Oscilloscope                                                                 | . 57 |

| 42. | The fine measurement result of the 80 $\mu m$ $\times$ 80 $\mu m$ NDD/PW_HV APS with 0.35 $\mu m$ wide PMOS-FET-reset.                                                     | . 58 |

| 43. | The fine measurement result on 80 $\mu$ m × 80 $\mu$ m NDD/PW_HV APS with 68 $\mu$ m PMO FET-reset.                                                                        |      |

| 44. | The fine measurement result on the 80 $\mu$ m × 80 $\mu$ m N+/PW_HV APS with 0.35 $\mu$ m PMOS reset transistor                                                            | . 59 |

| 45. | The fine measurement result for 80 $\mu m$ $\times$ 80 $\mu m$ N+/PW_HV type APS with 68 $\mu m$ PMOS reset transistor                                                     | . 59 |

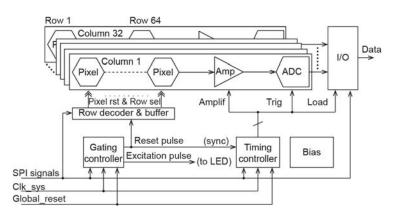

| 46. | The system architecture of the proposed monolithic fluorimeter IC                                                                                                          | . 62 |

| 47. | The block diagram of a complete imager system for one selected pixel                                                                                                       | . 64 |

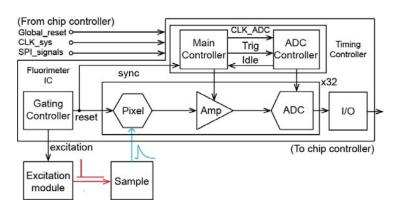

| 48. | The block diagram of the gating controller                                                                                                                                 | . 65 |

| 49. | The RTL block diagram of the 16-bit pre-scalar                                                                                                                             | . 66 |

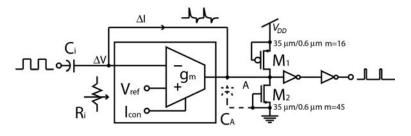

| 50. | The schematic of pulse generator                                                                                                                                           | . 68 |

| 51. | The schematic of the trans-conductance amplifier used in the pulse generator                                                                                               | . 68 |

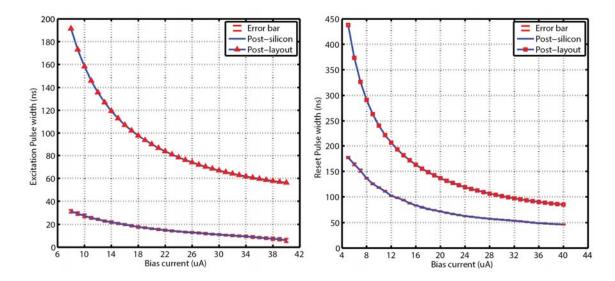

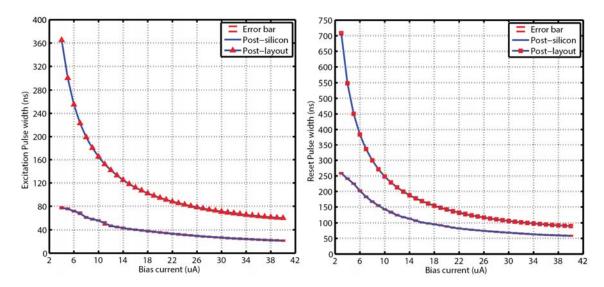

| 52. | The tuning range of the excitation and reset pulse when $V_{ref}$ was 1.25 V                                                                                               | . 70 |

| 53. | The tuning range of the excitation and reset pulse when $V_{ref}$ was 1.3 V                                                                                                | . 70 |

| 54. | The tuning range of the excitation and reset pulse when $V_{ref}$ was 1.4 V                                                                       | 71   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

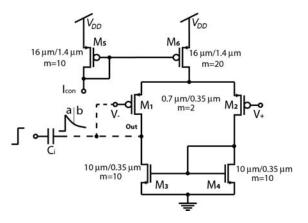

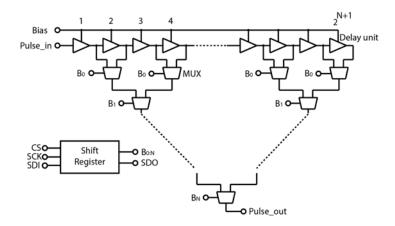

| 55. | The schematic of the delay line circuit[78]                                                                                                       | . 72 |

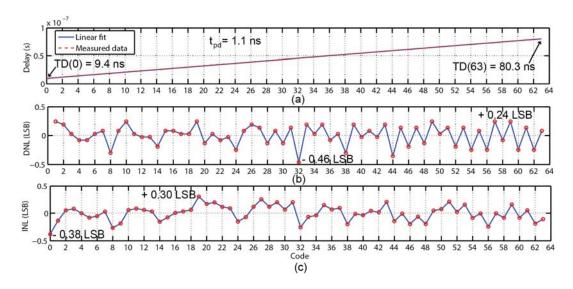

| 56. | The measurement results on the 64-stage delay line that delays the reset pulse                                                                    | 73   |

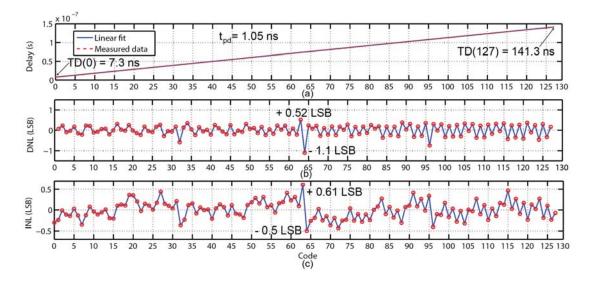

| 57. | The measurement results on the 128-stage delay line that delays the excitation pulse                                                              | 74   |

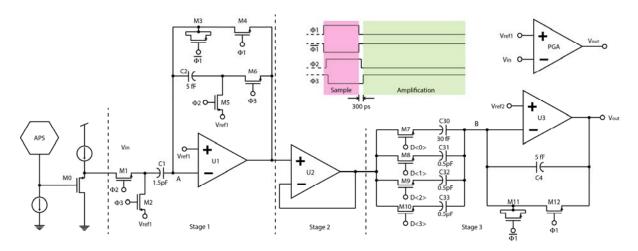

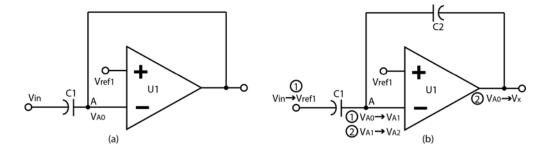

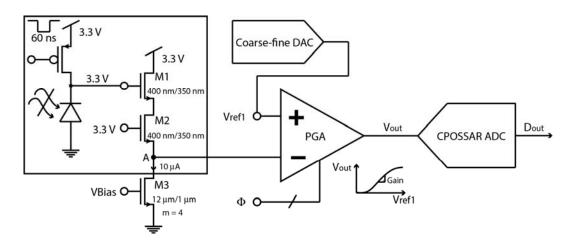

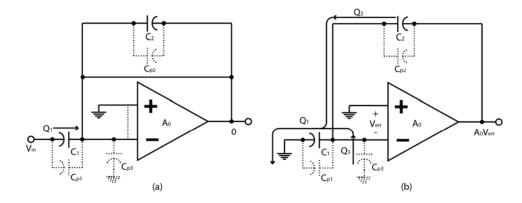

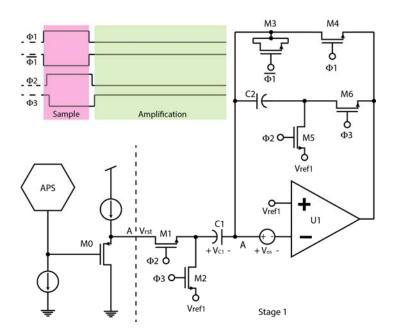

| 58. | The schematic of the switched-capacitor variable gain amplifier circuit                                                                           | 75   |

| 59. | The equivalent circuits of stage 1 in sampling phase (a) and in amplification phase (b)                                                           | . 76 |

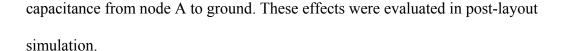

| 60. | Frequency response of op amps used in switched-capacitor PGA based on post-layout simulation                                                      | . 78 |

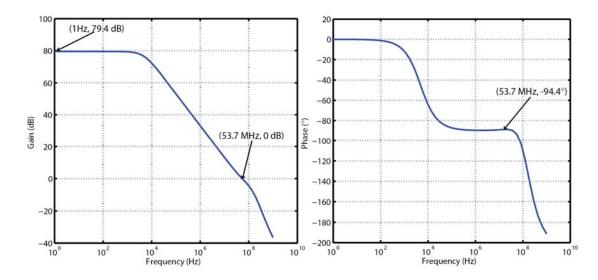

| 61. | The noise sources of stage 1 amplifier during sampling mode                                                                                       | 80   |

| 62. | The noise sources of the SC-PGA in amplification phase                                                                                            | 81   |

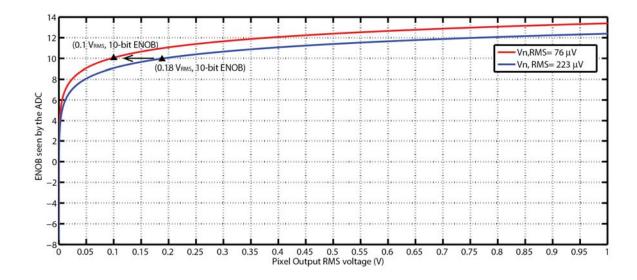

| 63. | The effective number of bit (ENOB) of the signal at the output of the amplifier vs. pixe output for different input referred RMS noise of the PGA |      |

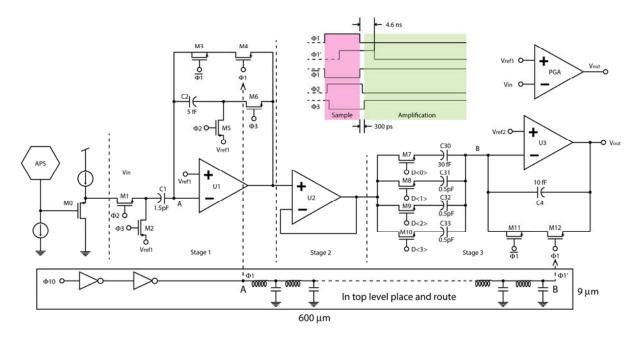

| 64. | The post-layout simulation test bench for a single channel PGA                                                                                    | 86   |

| 65. | The post-layout simulation result for a single channel PGA matched the hand-calculation results.                                                  |      |

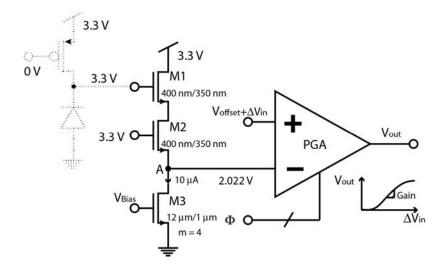

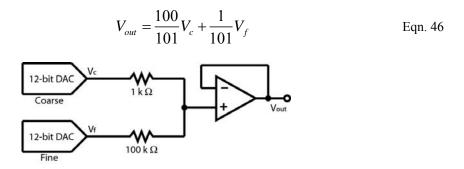

| 66. | In the schematic of the dual-12-bit coarse-fine DAC                                                                                               | 88   |

| 67. | The lab test bench to measure the single channel PGA gain                                                                                         | . 88 |

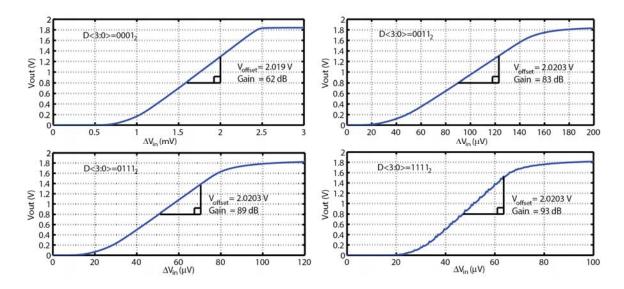

| 68. | The measured transfer function of a PGA channel                                                                                                   | . 89 |

| 69. | post-layout simulation result on a single-channel PGA layout without clock skew                                                                   | . 90 |

| 70. | post-layout simulation result on a single-channel PGA in 32-channel PGA array withou clock skew                                                   |      |

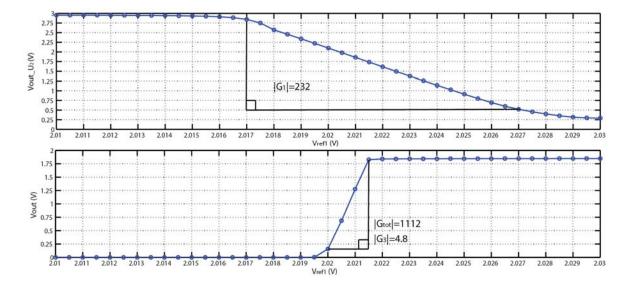

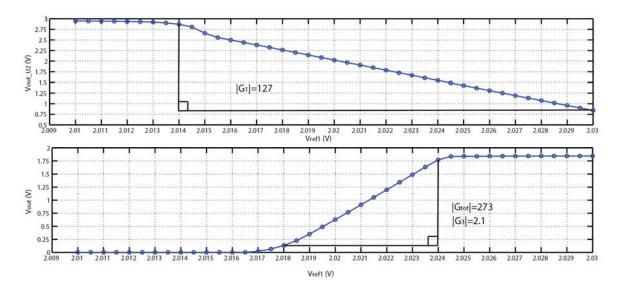

| 71. | The parasitic capacitance model of the stage 1 when a single-channel layout is place in the array                                                 |      |

| 72. | The illustration of clock skew on affecting the gain of the SC-PGA                                                                                | 93   |

| 73. | post-layout simulation results on a single-channel PGA in 32-channel PGA array when clock skew was included                                       |      |

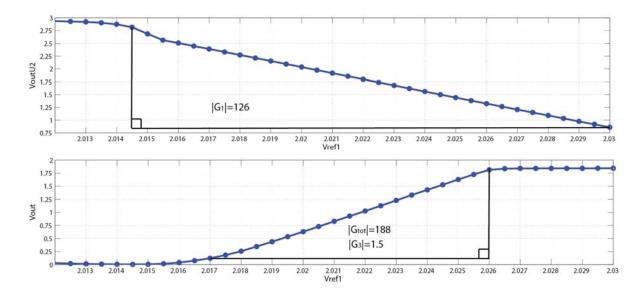

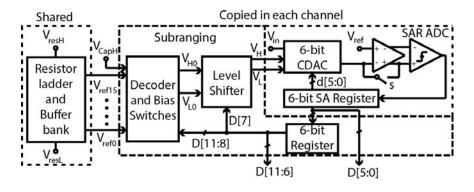

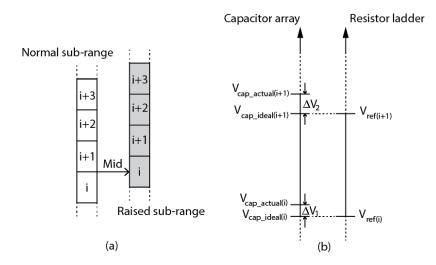

| 74. | The block diagram of the CPOSSAR ADC                                                             | 97  |

|-----|--------------------------------------------------------------------------------------------------|-----|

| 75. | The overlapping subranges used to remove the error produced in coarse conversion cycle           | 100 |

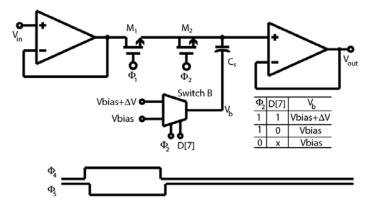

| 76. | A level shifter circuit used to produce the redundant overlapping subranges                      | 100 |

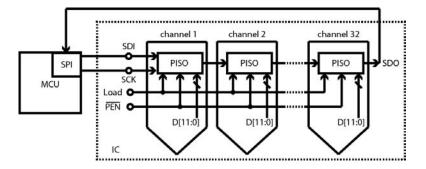

| 77. | The block diagram of the serial data I/O of in CPOSSAR ADCs                                      | 102 |

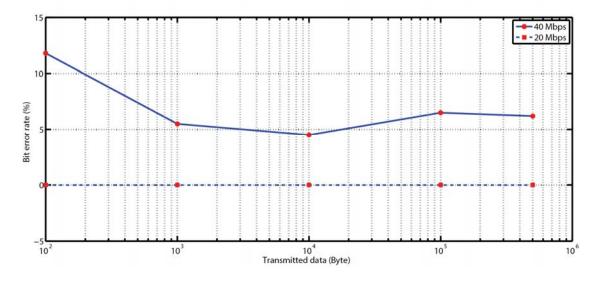

| 78. | The measured bit error rate of the ADC I/O under two different transmission bandwidth            | 103 |

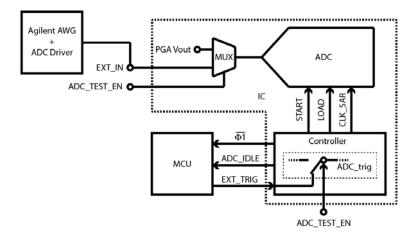

| 79. | The test bench to measure an individual ADC channel                                              | 104 |

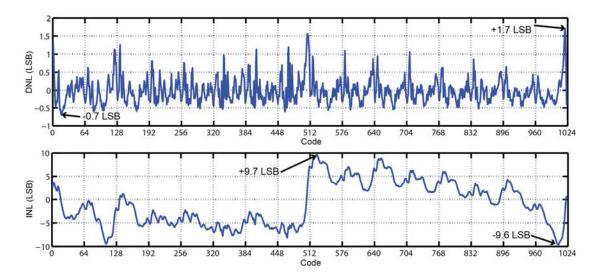

| 80. | The measured DNL and INL on the single channel CPOSSAR ADC                                       | 105 |

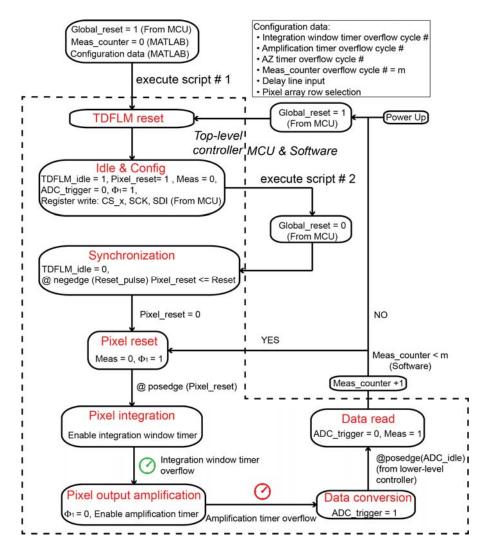

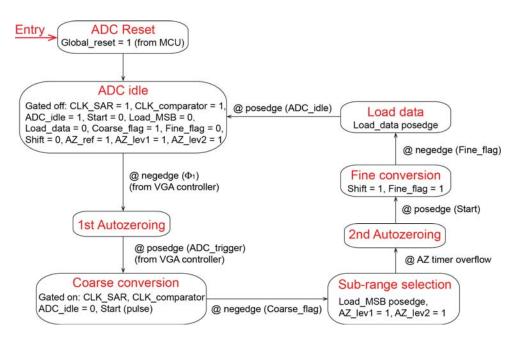

| 81. | The finite state machine of the full custom top-level controller circuit                         | 106 |

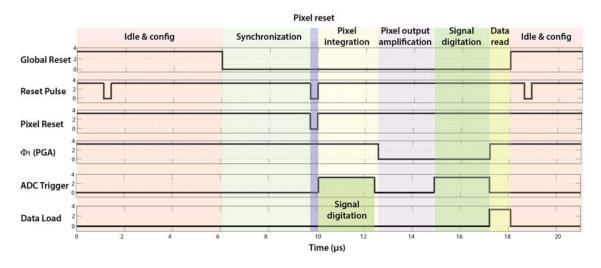

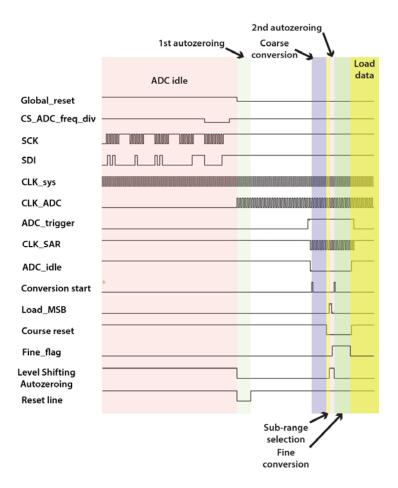

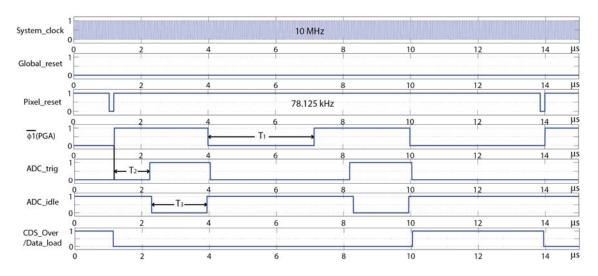

| 82. | The typical output waveform of the top-level controller for a single measurement                 | 108 |

| 83. | The finite state machine of the lower-level controller                                           | 109 |

| 84. | The typical timing waveform of the lower-level control logic                                     | 110 |

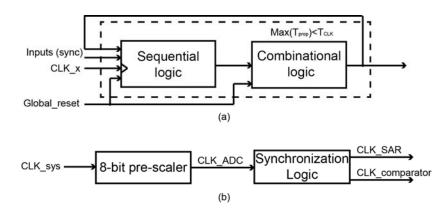

| 85. | The synchronous pipeline units used in the controller design                                     | 110 |

| 86. | The block diagram of the top-level controller                                                    | 111 |

| 87. | The tested waveform that verified the correct functional behavior of the top-level control logic | 113 |

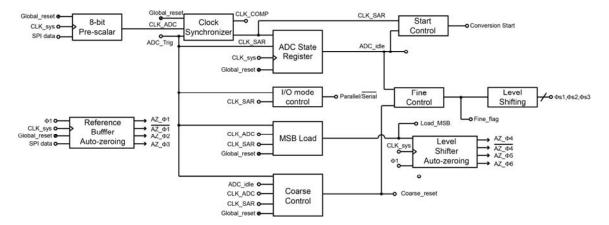

| 88. | The block-level interconnect of the lower-level controller                                       | 113 |

| 89. | The measured waveform of the lower-level controller when the "Global_reset" is high.             | 114 |

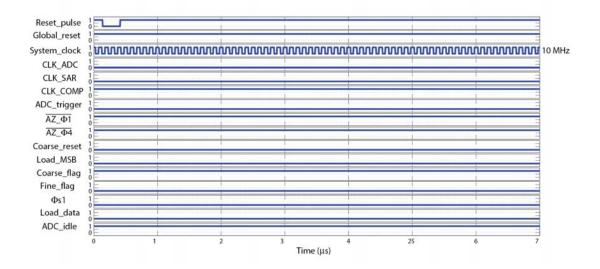

| 90. | The measured waveform of the lower-level controller after the "Global_reset" signal pulled low   |     |

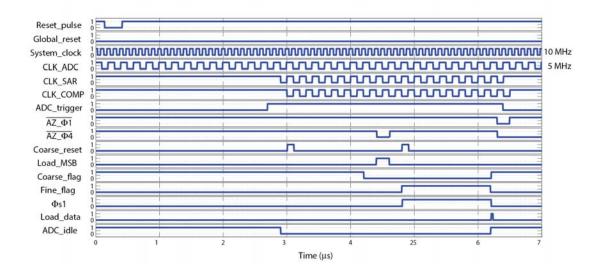

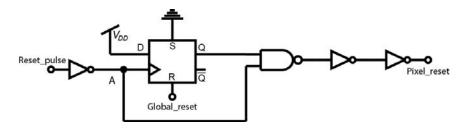

| 91. | The pulse synchronizer is used to gate off the "Pixel_reset" in reset phase                      | 116 |

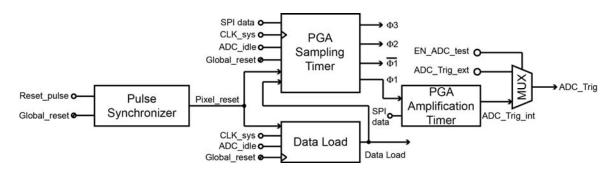

| 92. | The RTL block diagram of the PGA sampling timer                                                  | 117 |

| 93. | The implementation of the 8-bit programmable timer                                               | 118 |

| 94. The schematic of the Data Load logic                                                                | 119 |

|---------------------------------------------------------------------------------------------------------|-----|

| 95. The schematic of the PGA amplification timer.                                                       | 120 |

| 96. The schematic of the 8-bit programmable pre-scalar                                                  | 120 |

| 97. The schematic of the ADC state register logic                                                       | 121 |

| 98. The schematic of the ADC clock synchronizer                                                         | 122 |

| 99. The schematic of the SAR reset controller logic                                                     | 123 |

| 100. The schematic of Coarse Control logic                                                              | 124 |

| 101. The schematic of the Fine Control logic                                                            | 126 |

| 102. The schematic of the ADC data load logic                                                           | 127 |

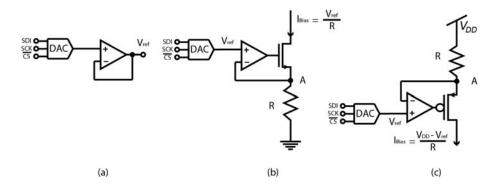

| 103. Three different reference generation circuits used in the chip controller board                    | 131 |

| 104. The block diagram of the prototype imager device implementing the CMOS imager IC                   | 132 |

| 105. The assembled portable lensless fluorimeter built by the CMOS imager IC                            | 133 |

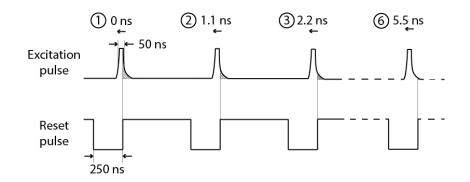

| 106. The delayline controlled excitation pulse and reset pulse for optical decay measurement            | 134 |

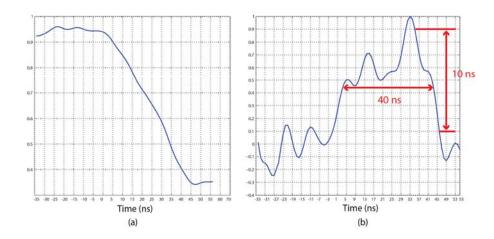

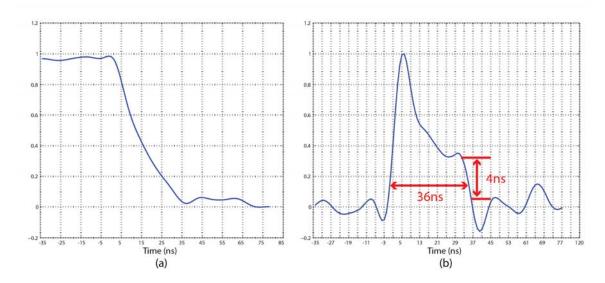

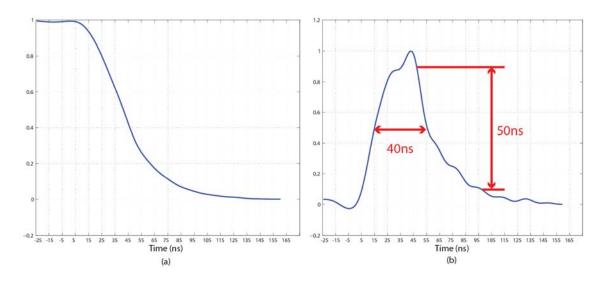

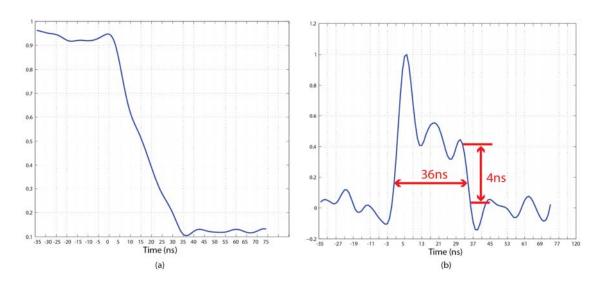

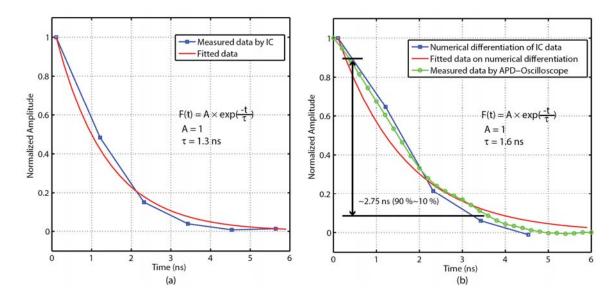

| 107. The measured (fitted) 405 nm excitation pulse falling edge (a) and the differentiated data (b)     |     |

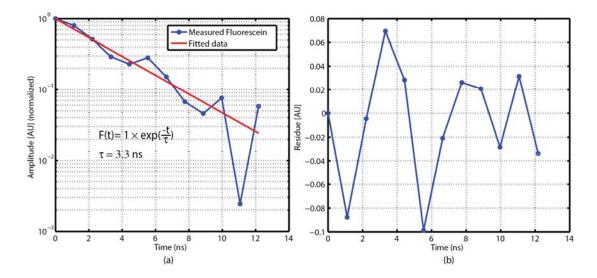

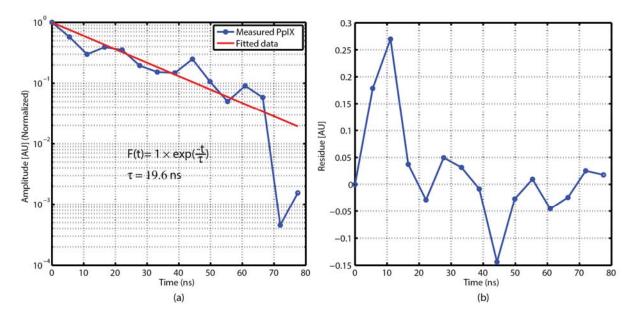

| 108. The measured lifetime of 500 $\mu$ M/L fluorescein sodium salt dissolved in PBS                    | 136 |

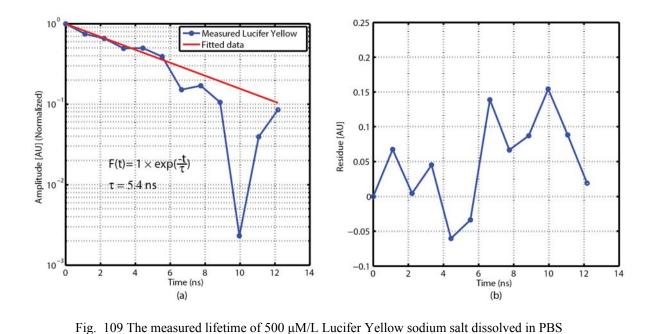

| 109. The measured lifetime of 500 $\mu$ M/L Lucifer Yellow sodium salt dissolved in PBS                 | 137 |

| 110. The measured lifetime of 10 $\mu$ M/L Protoporphyrin IX dissolved in PBS                           | 137 |

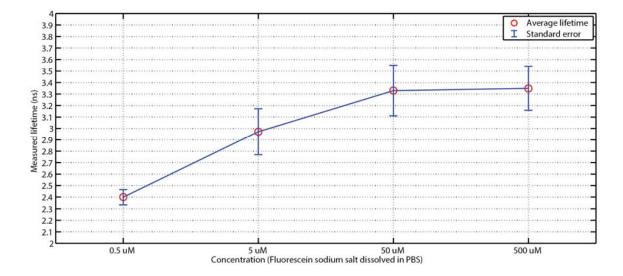

| 111. The measured lifetime of fluorescein sodium salt dissolved in PBS at different concentrations      | 138 |

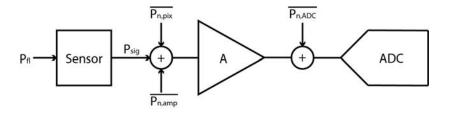

| 112. The noise model of one sensing channel in the fluorimeter IC                                       | 139 |

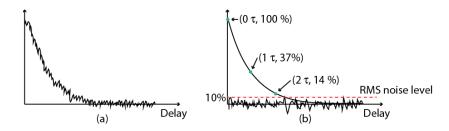

| 113. The generalized time-domain measurement data on a fluorophore sample (a) and its decomposition (b) | 141 |

| 114. The noise model of a 3-T active pixel sensor                                                       | 142 |

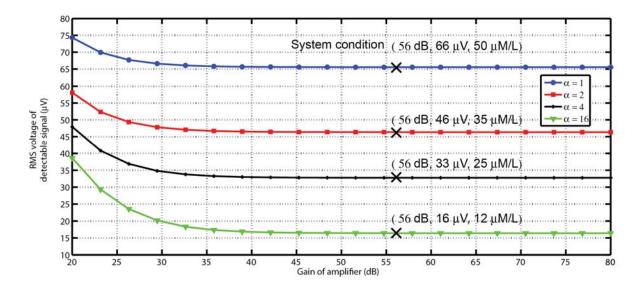

| 115. The RMS voltage of the detectable signal vs. the amplifier gain under different improvement factors                                                          | 145 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 116. The first stage of the PGA connected to a pixel sensor                                                                                                       | 147 |

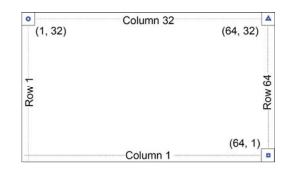

| 117. The coordinate of pixels at the corner of pixel array                                                                                                        | 148 |

| 118. The measured fluorescence lifetime data by three pixels located at the corner                                                                                | 149 |

| 119. The modified first stage PGA circuit with the dynamic biasing function                                                                                       | 149 |

| 120. The connection of the stage 1 amplifier in (a) pixel reset phase, (b) pixel integration/first A-D-conversion phase, and (c) pixel output amplification phase | 150 |

#### **CHAPTER 1**

#### INTRODUCTION

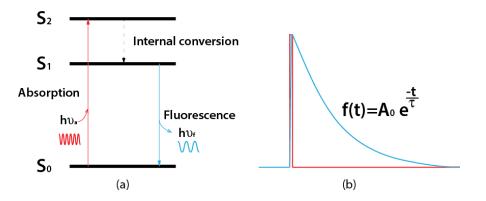

Fluorescence lifetime spectroscopy is the technique of measuring the excited-state lifetime of fluorophores[1], molecules that emit lower energy light upon the excitation by higher energy light, as shown in Fig. 1 (a). The technique is frequently used in chemistry to investigate the steady-state property of molecules and to study their behaviors in chemical reactions[2]–[5]. It is also a useful tool in biochemical environmental monitoring, because lifetimes of fluorophores can be modulated by environmental parameters, such as pH and other ion concentrations [6]–[10].

The fundamental understanding of fluorescence lifetime can be made by realizing that fluorescence is a stochastic process. The average time a molecule spends in excited state before releasing its energy, in the form of light, is called the fluorescence lifetime [11]. The fluorescence reaches the maximum intensity within a pico-second timescale after the fluorophore molecule is excited by a short pulse light, as shown in Fig. 1 (b). It decays exponentially after the excitation light is removed. The time constant,  $\tau$ , associated with the decay is called the fluorescence lifetime of that fluorophore.

Fig. 1 The illustration of fluorescence in energy level diagram (a) and time domain (b)

Commercial fluorophores exhibit lifetimes in the range from tens of picoseconds to tens of nanoseconds[12]. Such a small timescale requires high speed imaging devices to make accurate measurement. Modern fluorescence lifetime imaging microscopes (FLIM) rely on two mainstream methods, one based on time-domain photon counting, another based on frequency-domain modulation[13].

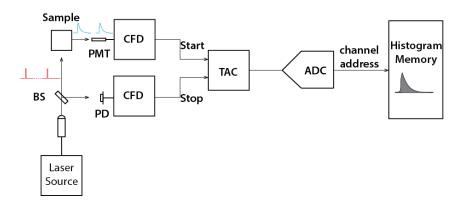

Fig. 2 The system architecture of time-correlated single-photo counter (TCSPC)

In the time-domain method, the fluorescence decay profile is recorded in timedomain directly. This type of instruments includes time-gated image intensifiers[14], [15], directly time-gated CCDs[16], [17], time-gated photon counters[18], [19], and the most prevalent time-correlated single-photon counters (TCSPC)[20]. Fig. 2 illustrates the block diagram of a typical TCSPC system. In the instrument, fluorophores are periodically excited by a train of laser pulses to produce periodic fluorescence decays. The fluorescence is received by a photomultiplier tube (PMT) that converts light signal to an electric signal. At the first observation of a photon in each cycle, the PMT is triggered and that time point is registered by a constant fractional discriminator (CFD). In a parallel path, a photodiode (PD) detects the excitation pulse as a time reference. Here the CFD reduces noise and generates a sharp-edged trigger signal. The outputs from two CFDs start and stop a time-to-amplitude-converter (TAC), which converts the time interval between the first-photon event and registered time reference into a voltage. An analog-todigital converter (ADC) is then used to digitize the voltage, and its subsequent circuit decodes the binary into a memory address. The content in that memory location is incremented by one when the channel address is sensed. Because each memory space represents a time bin, the overall amplitude across all time bin channels represents the total number of photons observed at the entire time window. Fluorescence lifetime can be calculated performing a least square fit on the histogram constructed by the entire memory contents.

An alternative method to measure the fluorescence lifetime is called frequencydomain method. It is an indirect measurement of the lifetime by characterizing the frequency response of the fluorophore detector system. Two types of modulation are commonly used, one with a continuous-time sinusoidal wave[21]–[25], another with a laser pulse train[26]–[28]. Sinusoidal modulation is simpler but has limited modulation frequency range usually from 1 MHz to 200 MHz. Pulsed modulation can improve the range up to 1 GHz by utilizing high-order harmonic components in high-repetition-rate square pulses[29]. A wider modulation frequency scanning range is meaningful, because some useful fluorophores only produce significant phase change between its fluorescence and excitation signal for sufficient signal to noise ratio at high modulation frequency.

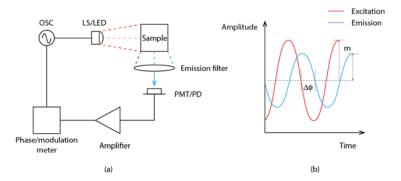

Fig. 3 The system architecture of the phase-modulation fluorimeter (a) and its time-domain response (b)

As depicted in Fig.3 (a), in continuous-time frequency-domain fluorimeter, the sample is excited by a laser diode (LS) or an LED modulated with a single-tone sine wave electric signal (OSC). A band-pass filter, called emission filter, removes the excitation wavelength in the emission angle. The filtered emission light is a time-varying signal that follows sinusoidal function. Its frequency is the same as the modulation signal, but the phase is shifted by an offset for that frequency. The filtered emission light is linearly converted into the electric signal by a photodetector (photo-multiplier-tube, PMT or photodiode, PD), as shown in Fig. 3 (b). The phases of the emission signal and the excitation signal are compared. Their difference is used to calculate the lifetime of the fluorophore using Eqn. 1.

where  $\Delta \phi$  is the phase shift,  $\tau$  is the lifetime, and  $\omega$  is the angular frequency of the modulating signal. When more than one fluorophores are involved in the measurement, multi-exponential decay needs to be examined, called fluorescence lifetime multiplexing. The measurement is performed by scanning the modulation frequency across a broad range and fitting the phase-shift-modulation-frequency response to a set of equations[26], so that the multiple lifetimes can be extracted from the data. Frequency-domain fluorimeters generally provide relatively shorter data acquisition time than time-domain instruments, because the steady state of the excitation-emission is established in picosecond time scale, and the phase information can be read out immediately.

TCSPC systems are the leading technology in photon counting area. The state-ofthe-art commercial TCSPC bench-top (as of March 2016) performs a detection limit down to 50 fM (fluorescein, Fluorolog-3<sup>®</sup>, HORIBA Scientific), and the minimum lifetime detection of less than 40 ps (PicoMaster<sup>TM</sup>, HORIBA Scientific). However, because of the requirement on complicated optics, high-power lasers, high voltage (>1000V) photo-multiplier tube, and the large instrument body, TCSPC are expensive and bulky. Although frequency-domain fluorimeters are less complicated and can measure faster lifetimes (20 ps, K2<sup>TM</sup>, ISS) than time-domain fluorimeters built with similar components, samples excited by continuous-time sinusoidal wave or highrepetition-rate pulses suffer from more significant photo-bleaching, the effect that molecules tend to reduce their emission intensity after long time excitation.

This dissertation builds upon work in both discrete circuit and integrated circuit devices for fluorescence lifetime measurement. An early fluorescence lifetime instrument was reported in 1974. It was based on a photo-multiplier tube connected to a sampling oscilloscope[30]. This time-resolved system could measure fluorophores with 1.5 ns and 17.1 ns lifetime. But it used a LINC computer to average the data, magnetic tapes for data collection, and a \$2.9 billion IBM 7090 for post data processing. In addition to the TCSPC and frequency-domain methods previously introduced, a number of discrete imagers have been built using a CCD coupled with a time-gated image intensifier[15], [31]–[35]. The temporal resolution of these instruments can be as low as 10 ps, but all of them require high power pico-second-scale laser and complicated optics, making them hardly portable. The above instruments are usually only accessible in research laboratories and have limited access for point-of-care diagnosis.

A portable time-domain fluorimeter achieved a compact size of  $21 \times 40 \times 50$  cm<sup>3</sup>[36], but it used expensive electronics and laser driver as in a TCSPC system. Joanneum Research in Austria developed a low-cost semiconductor based portable

fluorimeter to measure their oxygen sensor, but the detection range is in microsecond scale[37]. The portable filterless discrete circuit fluorimeter was able to measure ~ 5  $\mu$ M dye solution with lifetime of 1 ns, 2 ns, and 4 ns[38], but it used expensive laser diode as the excitation source, which also restricts the excitation wavelengths. Apparently, these portable fluorimeters can not satisfy nanosecond scale lifetime standards more widely used in research and industry[12].

Time-domain fluorimeters previously reported were either fast but expensive, making them only suitable to detect nanosecond-scale to sub-nanosecond-scale lifetime, or cheap but slow, which can be applied in most of the non-critical applications that requires microsecond-scale measurements. The fluorimeters built in this work was aimed at measuring nanosecond-scale fluorescence lifetime on a portable device, but their manufacturing cost are significantly reduced from the commercial high speed fluorimeters. A table is listed to compare the cost, speed, and portability for all types of fluorimeters.

| Works      | Technique            | Cost | Resolution | Detection limit   | Portable |

|------------|----------------------|------|------------|-------------------|----------|

|            | Photomultiplier tube |      |            |                   |          |

| [30]       | + oscilloscope       | High | 1.5 ns     | 2 µM/L            | No       |

|            | CCD + time-gated     |      | 185 ps     |                   |          |

| [15], [31] | image intensifier    | High | 150 ps     | N/A               | No       |

| [35]       | Streak camera        | High | 50 ps      | N/A               | No       |

| [36]       | TCSPC                | High | 200 ps     | $<1000 \ \mu M/L$ | Yes      |

| [37]       | Frequency-domain     | Low  | 1 µs       | N/A               | Yes      |

| [38]       | Time-domain          | High | 0.8 ns     | 1 μM/L            | Yes      |

| This work  | Time-domain          | Low  | 3.6 ns     | 0.25 µM/L         | Yes      |

Table. 1 The comparison of various types of fluorimeters

The time-domain instruments reported in this work trade off between cost and speed, as shown in Table. I. To improve the portability of instruments in conventional

sampling oscilloscope, TCSPC systems, frequency-domain instruments, and time-gated image intensifier-CCD instrument, the discrete-component fluorimeter presented in this work is filterless and requires no optics. It applies electric shutter to reject the excitation light from fluorescence emission in time domain. To improve its performance compared to existing portable fluorimeters, the presented device employs totem pole circuit in the LED driver for fast excitation. A novel sensing circuit is built in the instrument to integrate the nanosecond fluorescence decay by part in a time-gated mode.

After the discrete-component fluorimeter ptototype was built and verified, its advanced version, the integrated circuit based fluorescence lifetime imagers, were built. They was designed to capture images across an sensor array, measuring the fluorescence lifetime at each pixel. These compact imagers are also divided into time-domain and frequency-domain operation modes. In frequency domain, silicon photodiodes and custom trans-impedance-amplifiers have been integrated on a CMOS IC for fluorescence lifetime detection[25]. The power consumption and cost of such portable device are improved over existing discrete circuit fluorimeters, but the detection limit is limited to 7.5  $\mu$ M/L for fluorescein. It also requires filters to separate excitation light from emission fluorescence, because sample is excited continuously.

In time-domain, TCSPC imager ICs utilizing silicon single-photon-avalanchediode (SPAD) are able to detect single-photon events after excitation the same as in discrete-component instruments[39]–[45]. But these conventional TCSPC imagers suffer from pile-up effect[46], [47], the loss of photons due to the dead-time of the device. Time-gated TCSPC imagers count the total number of photons in multiple observation windows to eliminate pile-up effect[48]–[56], but pixels designed for this purpose include

digital circuits for gating and counting, making their fill factors usually only a few percent low. This can be improved by creating micro-lens above the pixel, but additional cost is needed based on the standard CMOS fabrication[57].

Another type of time-domain fluorimeter ICs utilizes silicon photodiode to integrate photons in an observation window rather than digitally count them. A timedomain imager used the differential photo-diode to build a pixel[58]. By gating on the sensor only in programmable time windows, photons within the window is converted into the differential component for read, while the rest of the light is in common mode that is rejected[59]–[61]. The fill factor, however, is less than 25%, because the dummy structure occupies half of the pixel area, and the limited reset current requires wide reset transistor for fast operation.

Later, based on conventional pinned photo-diode active-pixel-sensor (APS), an additional charge transfer gate was implemented in the pixel to achieve gating, charge storage, and in-pixel amplification[62]. But the experimental result showed that fluorescence lifetime measured by the IC varied with samples' concentration, contradictory to the common belief that the fluorescence lifetime is not a function of concentration. One charge transfer gate of the sensor can be removed by a special doping profile to simplify the control[63], but the optimized doping concentration is not supported in the standard technology, and a calibrated turn-on voltage for an efficient charge transfer is required.

Photodiode compatible with CMOS technology has been used in pixel sensors to measure fluorescence lifetime[64]. Its pixel circuit, however, includes a 3mm-wide reset transistor, a 1.5 mm-wide isolation transistor, and a differential amplifier. The resultant

fill factor is less than 14% for a large  $180 \times 415 \,\mu\text{m}^2$  pixel area. This limited the array size to be only 8 × 4 in that work. The fabricated IC was able to measurement the falling time of the excitation pulse varying from 1 ns to 5 ns, but no actual fluorescence decay measurement was performed. The real measurement on the fluorescence can be much more challenge, because of the very weak light intensity of the fluorescence compared to the excitation light.

The integrated circuit based fluorimeter presented in this work is able to measure fluorescence lifetime in time-domain. It removes filters required by frequency-domain imager IC to make the final device more portable. It overcomes the low fill factor issue associated with SPAD by using compact 3-T APSs compatible with the standard CMOS technology. The reduced sensitivity of APS compared to SPAD is overcome by high gain switch capacitor column amplifier and large number of averaging (~10,000). The gating controll of sensors, pulse generation, delay control, data conversion, global timing circuits, and data transmission are all integrated on a single chip to minimize the off-chip discrete components. This allows for a more portable imager than existing fluorimeters.

In summary, the motivation of this work is to leverage the cost, portability, and the performance of CMOS integrated circuits to build a time-domain fluorimeter that is suitable for point-of-care diagnostics. It was designed to demonstrate accurate measurement and low detection limit required in biochemistry laboratories. The project was partitioned into four development phases starting from May 2013. The detail in each phase will be discussed in the subsequent chapters.

In chapter 2, the novel time-domain sensing principle is described and first implemented in a single-pixel solid-state discrete-component device. Chapter 3 then

presents the characterization of a family of active pixel sensors (APS) fabricated in 0.35 µm CMOS technology for use in an integrated circuit version of the time-domain fluorimeter. In chapter 4, the mixed-signal processing units are designed and partially characterized in silicon. The circuits were finally integrated into a monolithic imager IC with an array of sensors, all signal conditioning circuits, timing controllers, and the data transmission interface. Chapter 5 describes how the IC was integrated into a board-level camera module used to carry out real measurements on commercial fluorophores. The experimental results will be presented and discussed. Chapter 6 summarizes the dissertation and proposes the future work.

#### **CHAPTER 2**

# ALL-SOLID-STATE TIME-DOMAIN FLUORIMETER DISCRETE-COMPONENT PROTOTYPE

#### 2.1 Discussion on existing fluorescence lifetime sensing method

Time-domain fluorimeters can be more portable and can achieve higher performance than phase-domain fluorimeters. As explained in chapter I, time-domain fluorimeters involve more complicated electronics, because of the gated excitation and the discrete-time electronics. However, gating circuits can separate the excitation light from the emission in time-domain better than a filter does for frequency-domain instruments, so that filters are no longer needed. Second, the improved discrimination between the excitation and emission improves the signal-to-noise ratio, allowing a better detection limit (lower detectable fluorophore concentration). Third, excitation pulses in time-domain fluorimeters need not to have a high-repetition rate. This allows the use of light-emitting-diode (LED) that usually responds slower, but is able to provide more wavelength options at the much lower cost than solid-state laser sources.

Based on the above discussion, the fluorimeter developed in this work measures the fluorescence in time domain. However, the TCSPC method imposes many challenges to make the instrument portable. First, single-photon counting is most frequently performed using photo-multiplier tubes. These vacuum-tubes generate up to  $\sim 1 \times 10^6$ electrons per incidental photon, but the body is many times larger than a solid-state electric competent, such as solid-state photo-diode that senses the light. Silicon photomultiplier (SiPM), the solid-state version of the vacuum-tube photo-diode, provides an

alternative solution. It behaves similarly to a vacuum-tube photo-multiplier, but TCSPC instruments rarely choose SiPM, because of the high dark count rate, and the lower peak avalanche current[65].

Second, the histogram recording in TCSPC requires high-speed circuits to process data in each excitation cycle. As an example, the pico-second-to-nano-second time interval between the end of the excitation and the first arrival photon event should be first converted into a voltage by an TDA. This voltage is digitized by an ADC to generate the binary data. The data is finally decoded to perform a memory write. The time consumed by the entire signal processing limits the period of the excitation, and that will limit the measurement time because a large number of excitation cycles need to be carried out to generate enough data point in the histogram to approximate the time-resolved fluorescence decay.

Third, high-end TCSPC instruments use filters to reduce the excitation-emission interference. However, the design of optics usually leads to a bulky instrument.

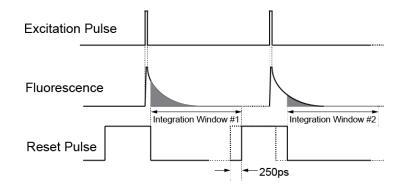

## 2.2 Time-gated photon integration sensing method

The above drawback presented in TCSPC instrument can be improved by using the time-gated photon integration method[38]. In this method, the fluorescence decay profile is measured by time-domain integration rather than histogram recording. In Fig. 4, a pulsed reset signal gates off the photodetector when it is logic high, and gates on the detector to integrate the fluorescence as it falls down. A delay is implemented between the excitation falling edge and the reset falling edge to start a time window called integration window. If using the first time window, almost the entire decay profile is integrated, as shown in the shaded area on the left. Then the reset pulse is delayed by 250

ps with respect to the excitation pulse, so that the integration window is delayed by 250 ps, and less fluorescence decay is integrated, as can be visualized by a smaller shaded area. If the delay of the reset pulse is further increased by a step of 250 ps, the fluorescence decay profile is essentially partitioned in many segment, and the area underneath each segment is measured by the electronics. Measurement data can be used to calculate the fluorescence lifetime by numerical method.

Fig. 4 The illustration of integration by part fluorescence lifetime sensing mecnanism

Fig. 5 The behavior model of the time-domain solid-state fluorimeter discrete-component prototype

The behavioral model of the time-domain solid-state fluorimeter discretecomponent prototype is presented in Fig. 5 to realize the time-gated photon integration method. Two synchronized pulses are produced by a pulse source. A programmable delay circuit generates the delayed reset pulse relevant to the excitation pulse. The delay value can be an integer multiple of the unit delay, D (250 ps), and can vary from 0 ns to 63 ns, nD, where n is an integer from 0 to 255. After the fluorophore sample is excited, fluorescence in the defined integration window is received by the photo-detector, PD, and converted into a time varying current, I(t). It is integrated into a voltage, called F(nD) because the voltage is a function of the delay between excitation and reset pulses noted by nD. This transient signal is averaged over time to produce a DC voltage. It is then amplified and digitized to create one data point indexed by the delay index, n. In the next step, n is increased by 1 to create one more data point, and so forth. In continuous-time mode, where the delay step is infinitely small, the integration of the fluorescence decay can be written as

$$F(t) = \int_{t}^{\infty} f(u) du$$

Eqn. 2

the lower limit, t, represents the start point of the integration window, and f(u) is the time-resolved fluorescence after the excitation pulse

$$f(u) = Ae^{\frac{-u}{\tau}}$$

Eqn. 3

The integration upper limit in Eqn. 2 can be set infinity large as long as the reset pulse period is much larger than the lifetime of the fluorophore sample. The continuous variable, t, in Eqn. 2 can be replaced by the discrete delay value, nD. So Eqn. 2 in combination of Eqn. 3 can be rewritten as

$$\frac{F(nD)}{T} = \frac{\int_{nD}^{\infty} f(u)du}{T} = \frac{A\tau e^{\frac{-nD}{\tau}}}{T}$$

Eqn. 4

where T is the duration of the integration window, or the total amount of time when the reset pulse stays low in one cycle. Eqn. 4 suggests that despite the fact that the output from the averager circuit is not the raw fluorescence signal that comes from the chemical, the time constant remains the same. Based on this the data measured at the output of the

fluorimeter can be directly used to fit to a single-exponential function to extract the lifetime. In the following section, the detailed circuit implementations for each behavior model block will be discussed.

#### 2.3 Hardware architecture and circuit implementations

## 2.3.1 System block diagram

The time-domain fluorimeter discrete-component prototype is partitioned into several functional blocks, as shown in Fig. 6. A tunable ring oscillator produces a 1 MHz system master clock. It is converted into two short pulses in a delay circuit. One pulse is used to reset the sensing circuit; another one is delayed from the reset pulse and used for excitation. Although in Fig. 5 the reset pulse is the one to be delayed for illustration purposes, it turns out delaying the excitation phase can be easier to be made with out changing the phase of control signal of the more complicated sensing circuit than the excitation circuit. The sample is excited by this variable-phase excitation signal in each delay step, and the fluorescence is measured by the sensing circuit that is operated under a reset signal with a constant phase. Finally a microcontroller unit (MCU) controls the excitation pulse delay and digitizes the sensing circuit's output. The functional blocks are built on a PCB to act as a slave device controlled by a personal computer (PC). Command and data are transmitted between PC and the MCU through an USB cable. A complete measurement is performed by first setting an excitation delay and recording 100 digitalized outputs from the MCU for averaging. Then the same process is repeated with a different excitation pulse delay, and so forth.

Fig. 6 The block diagram of the discrete-component based fluorimeter prototype

# 2.3.2 Ring oscillator

The clock used to produce the excitation and the reset pulse is generated from a 3stage ring oscillator shown in Fig. 7. Each stage includes an inverter, labeled by U<sub>1</sub>, U<sub>2</sub>, and U<sub>3</sub>. A 74 k  $\Omega$  resistor connects the output of U<sub>2</sub> and the input of U<sub>3</sub> to form a slow signal path. A variable capacitor, C<sub>var1</sub>, is connected between the inputs of U<sub>2</sub> and U<sub>3</sub> to form a fast signal path. The frequency of the output clock is adjusted by the value of C<sub>var1</sub>.

Fig. 7 The schematic of the pulsing circuit[66].

The waveform at node  $V_1$ ,  $V_2$ , and  $V_3$  in the ring-oscillator circuit are plotted in Fig. 8(a) for an analysis. Inverter  $U_3$  acts as a single ended comparator. As its input,  $V_3$ , moves across the threshold voltage, VDD/2, the output of  $U_3$  toggles, and the signal is propagated to node V<sub>1</sub> through inverter U<sub>2</sub>. At the rising edge of V<sub>1</sub>, the step input of U<sub>2</sub> is transmitted through the fast signal path involving C<sub>var1</sub> and C<sub>x</sub>, so that the voltage at node V<sub>3</sub> has a corresponding step voltage,  $\Delta V_3$

$$\Delta V_3 = \frac{C_{\text{var1}}}{C_{\text{var1}} + C_x}$$

Eqn. 5

Because the left terminal of  $R_1$  is driven to ground by inverter  $U_2$ , and its right terminal is above the ground, current flows through  $R_1$  to discharge capacitors. This process is ended when  $V_3$  is decreased to below VDD/2, when the state of  $U_3$  and  $U_1$  toggles, and a falling edge appears at  $V_1$ . At this point,  $V_3$  also falls by a voltage equals to Eqn. 5, and the current through resistor  $R_1$  now charges capacitors to drive  $V_3$  high. The charging process continues until  $V_3$  is increased above VDD/2, when  $U_3$  and  $U_1$  toggles, and a rising edge appears at node  $V_1$ . After this point the state of the circuits returns to the initial condition where  $V_1$  trips to VDD. So the waveforms in each node repeat the above behavior to produce the large signal clock at the output of the ring oscillator. The times spent on both charging and discharging processes on capacitors are identical, called  $T_d$ .

Fig. 8 The analysis on ring oscillator

To calculate  $T_d$ , the equivalent circuit for discharging capacitors after the rising edge of V<sub>1</sub> is plotted in Fig. 8(b). The differential equation associated with the circuit is

$$\frac{V_3(t)}{R_1} = C_{\text{var1}} \frac{d(VDD - V_3(t))}{dt} + C_x \frac{d(0 - V_3(t))}{dt}$$

Eqn. 6

Solving the equation by using the initial condition listed in Fig. 8(b), and equating the result to the threshold voltage of  $U_3$ , VDD/2, the clock frequency of the pulse is

$$f_{pulse} = \frac{1}{2T_d} = \frac{1}{2R_1(C_{var1} + C_x)\ln(1 + \frac{2\Delta V_3}{VDD})}$$

Eqn. 7

The calculated range of frequency by adjusting  $C_{var1}$  from 30 pF to 6.5 pF is from 195 kHz to 1.5 MHz, and the measurement result was from 212 kHz to 1.5 MHz. The error at the low end is less than 8%. The reason could be for a large ratio of  $C_{var1}$  to  $C_x$ , since this node is connected to a pin of the IC, the step at  $V_3$  is limited by the ESD circuit of the inverter IC, so it takes less time for the RC circuit to charge and discharge, leading to a faster oscillating frequency observed at the output. However, because it is non-linear in nature, and is dependent on the particular inverter IC being used, the modeling of such effect is out of the scope of study. In real measurement, the clock frequency was chosen 1 MHz by adjusting  $C_{var1}$  to a proper value.

# 2.3.3 Delay circuit

Two delay lines receive the clock generated from the oscillator and produce two sub-clocks that are synchronized but are delayed from the raw clock. They are produced at node  $E_1$  and  $R_1$ , as shown in Fig. 7. The succeeding circuit for each signal includes a high-pass filters and inverter buffers. The full width at half minimum (FWHM) of the high-pass filter satisfies

$$t_{FWHM} = RC\ln(2)$$

Eqn. 8

R and C are the resistance and the capacitance associated with the filter. In the measurement, the pulse width of the excitation pulse can be adjusted between 20 ns to 70 ns. Because a larger resistor is used in the high-pass filter that produces the reset pulse, the pulse width is tunable between 30 ns and 100 ns. In the real measurement, excitation pulse width was chosen 20 ns, and the result pulse width was 84 ns. The difference in between fits the delay line range of ~64 ns, so that in time domain the envelope of the excitation pulse can be shifted from the rising edge of the reset pulse to the falling edge of the result pulse, supporting the maximum detection range.

### 2.3.4 Excitation circuit

Because the signal to drive the LED is a pulsed signal, with its active high state lasting only 20 ns in a 1000 ns clock period, a temporary biasing voltage, ~ 4.3 V more than the normal constant biasing voltage , 3.8 V, used for the selected LED according to the data sheet (Bivar Inc/UV5TZ-405-15), can be chosen to maximum the peak light power in just 20 ns in one period. This is feasible because after the LED is over driven in a 20 ns time window, in the following 980 ns the PN junction is able to cool down. This was verified by observing no circuit failure after operating the circuit in a long term experiment over 1 week. Excitation light exhibits a higher power when the LED is biased at a higher voltage. It is helpful to generate stronger fluorescence from the fluorophore chemicals, so that it can improve the signal-to-noise ratio at the front-end of the fluorimeter.

Fig. 9 The schematic of the high speed LED driver circuit [66]

The LED driver to excite the fluorophore samples in nanoseconds time interval and stop the excitation within sub-nanosecond scale requires fast switching and the ability to deliver high power. In this design, the push-pull driver stage is modified into the circuit shown in Fig. 9 to drive the LED. It is built by stacking two NPN UHF power transistors (NXP Semiconductors /BFG21W, 115,  $f_T$ =18 GHz),  $Q_1$  and  $Q_2$ , and driving the LED at node B. Both  $Q_1$  and  $Q_2$  are built with 4 and 2 parallel connected transistors to increase the peak current. A resistor  $R_1$  is connected between the power supply and the collector of  $Q_1$  for current sensing purpose. It was shorted in normal operation. Instead of using a PNP transistor at the lower part,  $Q_2$  is constantly biased by a voltage divider. The use of an NPN transistor eliminates the effect that the base-emitter junction of a PNP transistor will be very weakly biased as the voltage at node B approximates 0.6 V. This effect will limit the sink current to shut down the LED at the end of each excitation cycle.

$Q_1$  is switched on at the rising edge of the excitation pulse to provide current  $I_1$ .  $Q_2$  delivers a constant current  $I_3$  when  $Q_1$  is turned on. The difference between  $I_1$  and  $I_3$  supplies the LED. The cathode of the LED can be grounded or biased at a negative voltage to further increase the peak biasing voltage for a higher peak light power. The measured peak power from the LED was 42 mW and 106 mW in each case when power

supply was 5 V. At the falling edge of the excitation pulse,  $Q_1$  is turned off, and charges at node B is sunk to ground by  $Q_2$  to shut off the LED as fast as possible.  $Q_2$  initially stays in the active region because voltage at node B is larger than the base voltage, ~ 0.6 V. In the end of discharging,  $Q_2$  moves to the saturation region with a constant resistance.

### 2.3.5 Sensing circuit

Fig. 10 The schematic of the sensing circuit[66]

The schematic of the sensing circuit is shown in Fig. 10. Fluorescence is received by an avalanche photodiode (APD),  $D_1$ , with its cathode biased by a high voltage source. The anode of  $D_1$  is connected to the collector of the bipolar transistor  $Q_1$ . It is the same UHF power transistor used in the excitation circuit. The transistor used in sensing circuit is to reset node A to 3.3 V when it is turned on. At the reset state, the reversed voltage across APD is ~ 130 V to achieve a photo-multiplication gain of 100 at 20°C, according to the device data sheet (Hamamatsu s2382). When  $Q_1$  is turned off, node A becomes a high-impedance node, and photo-current generated by the APD is integrated on its parasitic capacitor,  $C_{p1}$ , to produces a voltage signal with its amplitude proportional to the amount of received photon from the fluorescence. The voltage signal at node A is periodic, because  $Q_1$  is reset by the reset pulse at 1 MHz clock frequency. A low-pass filter, consisting of  $R_3$  and  $C_{p4}$ , averages the periodic voltage signal and produces a DC signal at the non-inverting input of op amp U<sub>1</sub>. Then U<sub>1</sub> buffers the voltage to the next stage. A replicated circuit is put in parallel at the bottom to create the differential signal seen at node V<sub>1</sub> and V<sub>2</sub>. The error voltage is amplified by a subtractor, realized by U<sub>3</sub> and resistors  $R_7 \sim R_{10}$ . The subtractor is an inverting amplifier when regarding its non-inverting input biased at a constant DC voltage. This is true because the dummy APD, D<sub>2</sub>, does not receive any light during the operation. The small signal output of the subtractor satisfies

$$V_3 = -V_1 \frac{R_9}{R_7} + V_2 \frac{R_{10}}{R_8 + R_{10}} \frac{R_7 + R_9}{R_7}$$

Eqn. 9

By defining  $R_9=R_{10}$ , and  $R_7=R_8$ , Eqn. 9 is reduced to

$$V_3 = -(V_1 - V_2)\frac{R_9}{R_7}$$

Eqn. 10

The value of  $R_7$  and  $R_9$  was chosen to be 33  $\Omega$  and 10 k  $\Omega$ , resulting in a differential gain of ~ 303. The succeeding stage involving U<sub>4</sub>, resistors  $R_5 \sim R_6$ , and  $R_{11} \sim R_{12}$  is a unity gain inverting amplifier. Its output is further filtered by an R-C low-pass filter with the -3dB band width of ~1.6 Hz.

The power spectrum density (PSD) of the thermal noise, contributed from all resistors, at the output of  $U_4$  follows

$$\overline{V_{n,R}^2} = 4kT \cdot \left[2R_3 \cdot \left(\frac{R_9}{R_7}\right)^2 + \frac{R_9^2}{R_7} + R_9 + \left(R_8 \parallel R_{10}\right) \cdot \left(1 + \frac{R_9}{R_7}\right)^2 + \left(R_5 \parallel R_6\right) \cdot \left(1 + \frac{R_{12}}{R_{11}}\right)^2 + \frac{R_{12}^2}{R_{11}} + R_{12}\right]$$

Eqn. 11

The PSD contributed from the input referred noise PSD of all op amps satisfies

$$\overline{V_{n,U,tot}^2} = \overline{V_{n,U}^2} \cdot \left[\frac{R_9}{R_7} + \frac{R_{10}}{R_8 + R_{10}} \cdot \frac{R_7 + R_9}{R_7} + \left(1 + \frac{R_9}{R_7}\right) + \left(1 + \frac{R_{12}}{R_{11}}\right)\right]$$

Eqn. 12

Where  $\overline{V_{n,U}^2}$  is the input referred noise PSD of each op amp.

After substituting resistor values into Eqn. 12, it is found out that the dominant resistor thermal noise comes from  $R_3$  and  $R_4$ , and the value of the PSD is 3.06 nV<sup>2</sup>/Hz. The total RMS value of resistor thermal noise voltage at sensing circuit output is

$$V_{n,R,RMS} = \sqrt{\int_0^\infty \frac{3.06 \times 10^{-9}}{1 + (2\pi R_{13} C_1 f)^2} df} = 87.5 \,\mu V$$

Eqn. 13

Substituting resistor values to Eqn. 13, the resulting noise PSD due to op amp is  $1214 \overline{V_{n,U}^2}$ . Therefore, the sensing circuit will amplify the input referred noise power spectrum of an op amp by a factor of ~1000 at the output. Because of the narrow bandwidth of the low-pass filter, 1.6 Hz, the actual noise source due to op amps is the flick noise. In real measurement, this part of noise is reduced by averaging the sensing circuit output 100 times at each delay step. The averaging operation is capable of reducing the noise power by a factor of 100, or improving the SNR by 20 dB.

As can be observed from above analysis, because the sensing circuit processes the fast dynamics of the nano-second-scale fluorescence decay into a series of DC signals, the electronic noise contributed from the multi-stage circuit can be effectively reduced by adding a simple R-C low pass filter at the output stage. This advantage is not available by discrete-time circuits that dynamically sample the fast fluorescence decay, such as the time-domain TCSPC instrument.

# 2.4 Experimental results

# 2.4.1 Fluorimeter prototype overview

The time-domain solid-state fluorimeter discrete-component prototype was designed and fabricated on two printed-circuit-boards (PCBs). Both sides of each board are shown in Fig. 11. All circuits handling large swing digital signals, including the MCU operating at 3.3 V, ring oscillator operating at 5 V, delay line circuits operating at 5 V, inverters operating at 5 V, and the excitation circuit operating at 5V, were distributed on a pulsing board on the left figures in Fig. 11. The sensing circuit that processes small signal analog voltages, and the high-voltage bias generator used for the avalanche photodiode, were placed on a sensing board on the right. The bottom plate of each board is made ground plane to form the microstrip structure on the FR-4 material. To make the fluorimeter portable, each board was designed with only an area of 62 mm × 115 mm.

Pulsing board (back-side)

Sensing board (back-side)

Fig. 11 The fabricated printed circuit boards of the discrete-component fluorimter prototype[66]

After solid-state components were manually soldered on each board, they were assembled into a portable device, shown in Fig. 12. Board-to-board communication is performed through a 5 cm ribbon cable. Black colored spacers were custom fabricated in machine shop, and were placed between two boards at the edge to form an enclosed measurement chamber. In the measurement, a 1.5 mL disposibal cuvette (Fisherbrand<sup>TM</sup> 14-955-127) is plugged into the device to hold the liquid sample. An avalanche photodiode (Hamamatsu S2382) is soldered on the sensing board and it attaches to the surface of the cuvette. Right angle illumination is provided by a though-hole 405 nm LED (Bivar Inc/UV5TZ-405-15) that is bent at 90° angle to illuminate the cuvette from the side.

Fig. 12 The assembled discrete-components based fluorimeter prototype [66] The MCU in the portable fluorimeter was programmed by a C code to enable an embedded system. The system is a slave device controlled by a personal computer through USB communication. In the personal computer, a user interface was created in MATLAB. In the user interface, users can define parameters to specify a measurement. In particular, the sequence of the delay values can be set to define the integration window in each step; the repetition rate is used to measure one delay step multiple times; the averaging number defines how many data is recorded for one delay step in one single measurement; the initial amplitude set the peak sensing output at the beginning of the

measurement, and the bias voltage of the APD is automatically adjusted by the MCU to satisfy this requirement at the beginning of the measurement.

When the MATLAB user interface issues a measurement command to the slave device, it sends measurement parameters to the MCU. Then the C code programmed in the MCU is executed to controls the fluorimeter to perform the specified measurement. The DC voltage output from the sensing circuit is digitized by a 10-bit ADC in the MCU in each delay step. The data is first stored in the 128 k RAM. It is eventually transmitted to the personal computer at the end of the measurement. Once the data is captured, the MATLAB user interface fits the data to a single exponential function to find out the lifetime of the chemicals under test.

#### 2.4.2 Characterization result

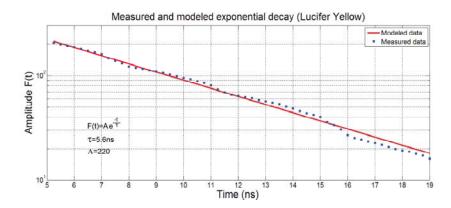

Fig. 13 The measurement result of 5  $\mu$ M/L 'lucifer yellow' dissolved in PBS[66]

The performance of the time-domain solid-state fluorimeter discrete-component prototype was characterized by testing commercial fluorophores. The measurement result on a 5  $\mu$ M/L 'lucifer yellow' (MP Biomedicals/M3415) dissolved in PBS is plotted in Fig. 13. The raw data is fitted into a single-exponential curve with solid line. Fitting result for the measurement is a 5.6 ns lifetime. This is sufficiently close to the reported 5.7 ns found in literature[67].

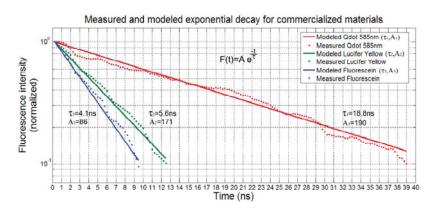

Then the 10  $\mu$ M 'fluorescein' (Online science mall/CAD# 518-47-8) dissolved in PBS was measured with a lifetime of 4.1 ns. The 0.2  $\mu$ M Qdot 585 (Life technologies/Qtracker 585) dissolved in PBS exhibited 18.8 ns lifetime. Both results matches the lifetime standards reported in literatures (4 ns, and 19.5 ns±1.6 ns)[67], [68]. Fig. 14 is the normalized fluorescence decay data before and after the least square fit.

Fig. 14 The measurement results for 3 commercial fluorophores[66]

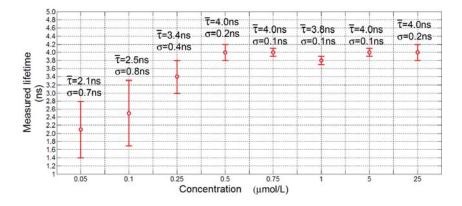

The detection limit of the fluorimeter was determined by measuring a group of fluorescein PBS solutions under different concentrations. As shown in Fig. 15, the average lifetime and the standard error deviate from the correct value as the concentration becomes lower than 0.5  $\mu$ M/L. This detection limit is a factor of 10 smaller than a frequency-domain fluorimeter implemented in IC[69] developed in 2011.

Fig. 15 The detection limit measurement of the discrete-component fluorimeter prototype[66]

# 2.4.3 Improvement on the detection limit

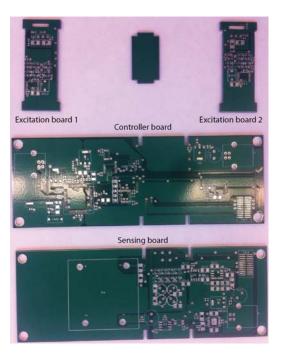

Fig. 16 The fabricated PCBs of the second version discrete-component fluorimeter The prototype of the discrete-component fluorimeter was re-designed to improve its detection limit performance, as shown in Fig. 16. Because a smaller detection limit requires more sensitive sensing circuit optoelectronics front-end, in the second version, 2 avalanche photodiode were implemented on the board. The principle is to increase the photo sensitive area of the sensor by 2, so that double amount of photons from the fluorescence can be collected to improve the signal-to-noise ratio.

The second change on the board is separating the excitation board from the board mounted with the MCU and the delay circuit. By implementing two excitation boards with smaller areas, they can be installed in the slots fabricated on the sensing board and the controller board shown in Fig. 16. This enables direct soldering the through-hole LEDs on the excitation boards without bending their package leads. The excitation and sensing angle is 90° guaranteed by this method. The parasitic effect from the LED

package is reduced for a faster response time. By implementing two excitation boards on both sides of the cuvette, 2 LEDs excites the chemical sample placed with a greater area. In this method total fluorescence can be doubled for the additional avalanche photodiode to sense additional part of fluorescence that is unavailable in the prototype fluorimeter.

The third change is the removal of the ring oscillator circuit that was used to produce clock signals for generating pulses. Clock signal produced by the inverter based ring oscillator is subjected to temperature variation and supply noise. A simpler and more effective way of implementing the clock is to use the MCU. The PIC32 MCU is equipped with several serial peripheral interface (SPI) modules. When operating in framed mode, the SCK port generates a continuous clock signal. The clock is pre-scaled from the output of an internal PLL, which receives an 8 MHz reference clock from an external crystal oscillator. Clock frequency of the SPI module can be programmed in software. Because of the well behaved stability nature of a crystal oscillator, PLL output synchronized with the reference exhibits improved low-jitter quality over the ring oscillator used in the prototype fluorimeter.

The re-designed printed circuit boards with above modifications were assembled into the device shown in Fig. 17. Two LEDs were put apart from each other to generate 2 separate excitation beams. Two avalanche photodiodes were soldered closely on the sensing board. After stacking the controller board and the sensing board, two APDs sense two separate excitation beam paths at a 90 ° angle.

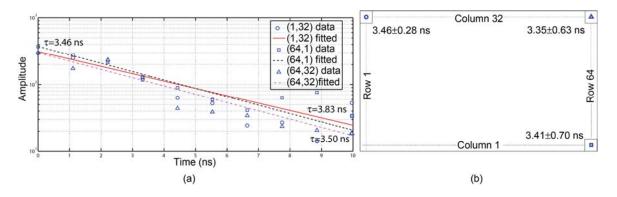

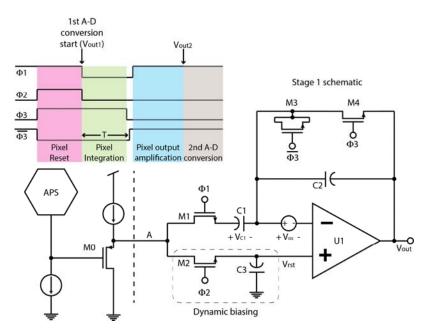

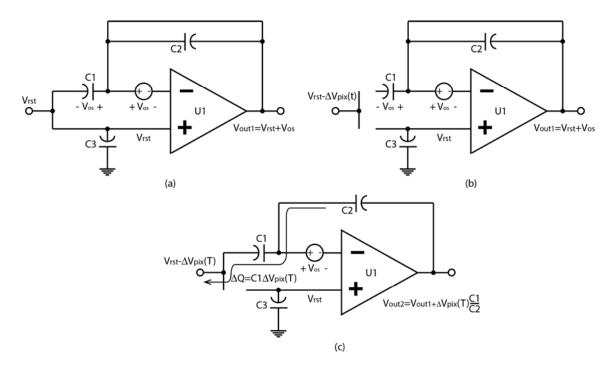

Fig. 17 The assembled second version discrete-component fluorimeter