# DESIGN AND ANALYSIS OF FEEDBACK CONTROLLERS FOR A DC BUCK-BOOST CONVERTER

Murdoch University: The Murdoch School of Engineering & Information Technology

Author: Jason Chan

Supervisors: Martina Calais & Simon Glenister

# Abstract

In Murdoch University, students majoring in Electrical Power Engineering have the opportunity to learn about the basics of power electronic systems. ENG349 Power Electronic Converters and Systems is a unit where students are exposed to a range of industrial electronics. The power pole board provided by the University of Minnesota is used for laboratory teaching on how DC converters operate [1, 2]. This thesis topic gives an opportunity for Electrical Power students to further expand their basic knowledge on power electronics.

Additionally, Instrumentation and Control System Engineering students will have a better understanding of dynamic control systems, which are essential in designing and analysing feedback control on DC converters. Industrial computer systems students are able to design and implement external hardware to enhance power board components. Renewable Energy students will be interested in how DC converters are applied to renewable energy systems. This thesis provides project expansion for all types of electrical engineering majors taught at Murdoch University.

The main focus of this thesis is to design and analyse different feedback controllers for the converter system. The literature review and steps into designing feedback controllers are adapted from Ned Mohan's approach in designing feedback controllers for DC converters [3]. The results presented are based on the author's knowledge learnt from Electrical Power and Instrumentation and Control Systems Engineering.

Computer simulations from *Pspice* and *MATLAB* are used for testing the feedback responses of implementing different feedback compensators. The most difficult task in this thesis is to produce accurate results from the power pole board, especially with the peak current controller circuit. Although the simulated results are successful, it is hard to compare these to the experimental results due to the ways of how the power board components are connected. This thesis will further explain the process in exploring these feedback controllers.

# Acknowledgements

I would like to acknowledge my supervisors, Dr Martina Calais and Simon Glenister, for providing guidance and assistance in this project, and helping me to overcome difficulties I've experienced during the year. I would also like to thank Iafeta Laava for technical support in the laboratory work, which was essential in completing this thesis.

I would like to acknowledge the lecturers of Murdoch University for their valuable teaching time and encouragements which have helped me to complete my degree. Finally, I would like to thank my family and friends for their support.

23 November, 2014 Jason Chan

# Contents

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table of Figures9                                                                                                                                                                                                                                                                                                                                                                                                                  |

| List of Tables11                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chapter 1 - Introduction                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.1 Objectives and Aim12                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.2 Report Overview12                                                                                                                                                                                                                                                                                                                                                                                                              |

| Chapter 2 - Buck-boost converter review                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1 DC converters                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2 Buck-boost Converter Components13                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.3 Buck-boost Operation in Continuous Conduction Mode14                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 3 - Control Aspects of DC Converters17                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1 Dynamic Average Model17                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1.1 Ideal Transformer19                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2 Regulation with pulse width modulation21                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapter 4 - Linearisation                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1 Pulse Width Modulator Linearisation22                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2 Power Stage Linearisation23                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2 Power Stage Linearisation                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3 Equivalent Circuit and Transfer Function of Converter25                                                                                                                                                                                                                                                                                                                                                                        |

| 4.3 Equivalent Circuit and Transfer Function of Converter25<br>Chapter 5 - Bode Plots and Computer simulations                                                                                                                                                                                                                                                                                                                     |

| 4.3 Equivalent Circuit and Transfer Function of Converter       25         Chapter 5 - Bode Plots and Computer simulations       26         5.1 Bode plots Review       27                                                                                                                                                                                                                                                         |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map29                                                                                                                                                                                                                                                                  |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$ 30                                                                                                                                                                                           |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$ 305.3.1 Open loop transient response32                                                                                                                                                       |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$ 305.3.1 Open loop transient response32Chapter 6 - Feedback control compensator design34                                                                                                      |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$ 305.3.1 Open loop transient response32Chapter 6 - Feedback control compensator design346.1 Electronic control systems34                                                                      |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$ 305.3.1 Open loop transient response32Chapter 6 - Feedback control compensator design346.1 Electronic control systems346.2 K Factor Method35                                                 |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{d}$ 305.3.1 Open loop transient response32Chapter 6 - Feedback control compensator design346.1 Electronic control systems346.2 K Factor Method356.2.1 Type 2 Amplifier35                                 |

| 4.3 Equivalent Circuit and Transfer Function of Converter25Chapter 5 - Bode Plots and Computer simulations265.1 Bode plots Review275.2 Buck-boost Pole Zero Map295.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$ 305.3.1 Open loop transient response32Chapter 6 - Feedback control compensator design346.1 Electronic control systems346.2 K Factor Method356.2.1 Type 2 Amplifier356.2.2 Type 3 Amplifier36 |

| C 4.1 Deale surrout reads controller design                            | 10 |

|------------------------------------------------------------------------|----|

| 6.4.1 Peak current mode controller design                              |    |

| Chapter 7 PSpice Feedback Controller Testing                           |    |

| 7.1 Voltage Mode Control                                               |    |

| 7.2 Peak Current Mode Control                                          |    |

| 7.3 Performance Criteria Calculations                                  |    |

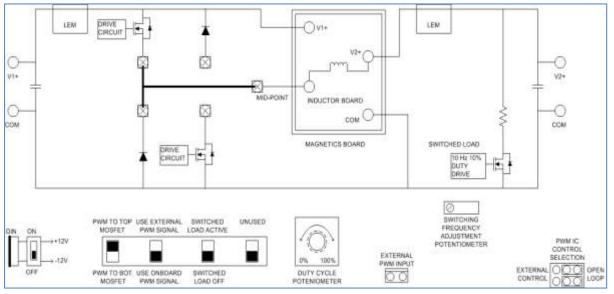

| Chapter 8 – Power Pole Board                                           |    |

| 8.1 Technical Specifications                                           | 51 |

| 8.1.1 Signal Supply                                                    | 51 |

| 8.1.2 Load                                                             |    |

| 8.1.3 Frequency Analysis                                               |    |

| 8.1.4 Controller Selection Jumpers                                     |    |

| 8.1.5 Current Measurement                                              | 52 |

| 8.1.6 PWM Signal Generation                                            | 52 |

| 8.2 Open Loop Operation in CCM                                         | 53 |

| 8.3 Finding the Transfer Function of the Buck-boost Power Board        | 55 |

| 8.4 Closed loop Operation (Peak current control mode)                  |    |

| Chapter 9 – Power Pole Board Testing                                   |    |

| 9.1 Buck-boost Transfer Function Findings                              |    |

| 9.2 Peak Current Mode Control                                          |    |

| Chapter 10 – Conclusion                                                | 61 |

| Chapter 10.1 Future Work                                               | 62 |

| References                                                             | 63 |

| Appendix A - Power pole board                                          | 65 |

| A-1 Power board part locations                                         | 65 |

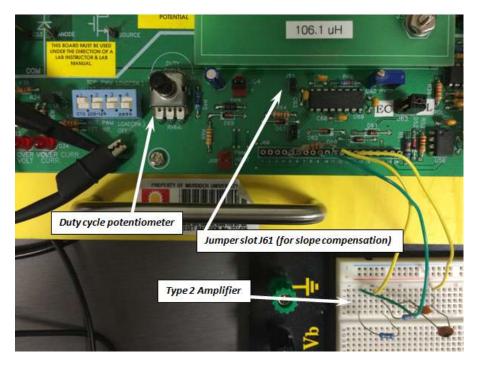

| A-2 Type 2 Amplifier Breadboard and PWM Connections                    | 68 |

| Appendix B – MATLAB Code for Buck-boost Analysis and Controller Design | 69 |

| B-1 Buck-boost Type 3 Amplifier Transfer Function                      | 69 |

| B-2 Buck-boost Type 2 Amplifier Transfer Function                      |    |

|                                                                        |    |

# Nomenclature

$V_{in} - DC$  input voltage  $V_{out} - DC$  output voltage  $I_{in} - DC$  input current  $I_{out} - DC$  output current  $P_{in} - DC$  input power  $P_{out} - DC$  output power V<sub>primary</sub> – Ideal transformer primary voltage  $V_{secondary}$  – Ideal transformer secondaryvoltage Iprimary - Ideal transformer primary current Isecondary - Ideal transformer secondary current D - duty ratio $i_{Drain}$  – Drain Current (MOSFET)  $V_{GS}$  – Gate to Source Voltage (MOSFET)  $V_{DS}$  – Drain to Source Voltage (MOSFET) R-resistorL-inductorC - capacitor $L_e$  – power stage inductor (Buck Boost) r - Equivalent Series Resistance (ESR)q(t) – switching function variable  $v_A$  – diode voltage  $i_L$  – inductor current  $\Delta i_L - peak$  to peak inductor current *i<sub>L,ripple</sub>* – *inductor ripple current*  $i_{diode}$  – diode current *i*<sub>diode,ripple</sub> - diode ripple current  $i_c$  – capacitor current  $\widehat{V}_r$  – peak ramp voltage amplitude  $v_c$  – small signal control voltage  $v_r$  – small signal ramp voltage  $V_{cp}$  – Current port voltage  $V_{vp}$  – Voltage port voltage  $I_{cp}$  – Current port current

$I_{vp}$  – Voltage port current

$\bar{\iota}_{vp}$  – average current at voltage port of ideal transformer of converter  $\bar{\iota}_{cp}$  – average current at current port of ideal transformer of converter  $\bar{v}_{vp}$  – average voltage at voltage port of ideal transformer of converter  $\bar{v}_{cn}$  – average voltage at current port of ideal transformer of converter  $\tilde{\iota}_{vp}$  – small signal current at voltage port of ideal transformer of converter  $\tilde{\iota}_{cp}$  – small signal current at current port of ideal transformer of converter  $\tilde{v}_{vp}$  – small signal voltage at voltage port of ideal transformer of converter  $\tilde{v}_{cp}$  – small signal voltage at current port of ideal transformer of converter  $G_{control}(s)$  – Controller Transfer Function  $G_{PS}(s)$  – Power Stage Transfer Function  $G_{PWM}(s)$  – Pulse Width Modulation (PWM) Transfer Function  $G_{PWM UC3824}(s) - PWM of UC3824 Transfer Function$ V<sub>o,ref</sub> - Reference output voltage  $k_F$  – sensing equipment feedback gain  $\tilde{d}$  – small signal PWM duty cycle  $\tilde{\mathbf{I}}_{\mathbf{L}}$  – small signal inductor current  $\tilde{v}_o$  – small signal output voltage  $\tilde{v}_{o,ref}$  – small signal reference output voltage  $T_{\rm s}$  – MOSFET Switching cycle time  $f_s - MOSFET$  switching frequency  $f_c$  – crossover frequency AC – Alternating Current DC – Direct Current Q – quality factor  $M_{peak}$  – Bode magnitude peak (for quality factor)  $M_{low f}$  – Bode magnitude for low frequency asymptote K - K factor calculation  $f_{zero}$  – zero frequency (Hz)  $f_{pole}$  – zero frequency (Hz)  $\omega_{zero}$  – zero frequency (rad/s)

$f_{pole}$  – zero frequency (rad/s)

$\theta_{rise}$  – phase rise

||M|| - Bode plot absolute magnitude

$\|M\|_{dB}$  – Bode plot magnitude (dB)

R<sub>SC</sub> – Slope Compensation Jumper Resistor C<sub>SC</sub> – Slope Compensation Jumper Capacitor R<sub>6-11</sub> – Resistor (Daughter pin connection pin 6 to 11) IAE – Integral of Absolute Error ISE – Integral of Squared Error MATLAB – Coding Program by MathWorks PSpice – Circuit simulator by OrCAD SIMULINK – Simulator by MathWorks

# **Table of Figures**

| Figure 1 DC Converter Block Diagram                                                                   | 13 |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2 Buck-boost Converter                                                                         | 14 |

| Figure 3 n channel MOSFET                                                                             | 14 |

| Figure 4 Buck-boost Conduction MOSFET states and Waveforms                                            | 15 |

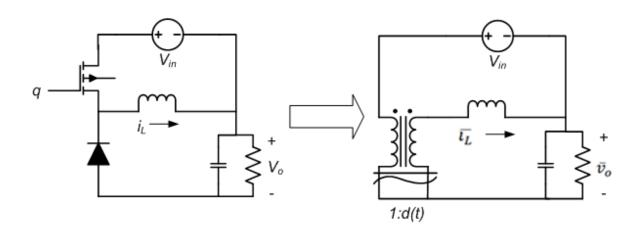

| Figure 5 Dynamic Average Model Configurations                                                         | 18 |

| Figure 6 Buck-boost Dynamic Average Model                                                             | 19 |

| Figure 7 DC Converter Equivalent Model                                                                | 20 |

| Figure 8 DC Ideal Transformer Model                                                                   | 20 |

| Figure 9 Pulse Width Modulation Output Regulation                                                     | 21 |

| Figure 10 PWM Amplifier and Comparator Block Diagram                                                  | 21 |

| Figure 11 PWM UC3824 Linearisation                                                                    | 22 |

| Figure 12 Switching Power Pole Linearisation                                                          | 24 |

| Figure 13 Linearised Buck-boost Model                                                                 | 25 |

| Figure 14 DC Converter Equivalent Circuit                                                             | 26 |

| Figure 15 Magnitude Bode plot linear relationships                                                    | 27 |

| Figure 16 Buck-boost Transfer Function P-Z Map Code                                                   | 29 |

| Figure 17 Poles and Zeros Locations for Buck-boost Transfer Function                                  | 29 |

| Figure 18 Pspice Drawing of Buck-boost Dynamic Model                                                  |    |

| Figure 19 PSpice frequency response of buck-boost power stage $\frac{\widetilde{v}_o}{\widetilde{d}}$ | 31 |

| Figure 20 Buck-boost Open Loop Dynamic Circuit                                                        | 32 |

| Figure 21 Buck-boost Open Loop Transient Response                                                     | 33 |

| Figure 22 Type 2 Amplifier (a) and Bode Plot (b)                                                      | 35 |

| Figure 23 Type 3 Amplifier (a) and Bode Plot (b)                                                      | 36 |

| Figure 24 Voltage mode controller block diagram                                                       | 37 |

| Figure 25 MATLAB Bode Plot of Type 3 Amplifier Transfer Function                                      | 38 |

| Figure 26 Peak current mode controller block diagram                                                  | 42 |

| Figure 27 Peak Current Control with Slope Compensation                                                | 42 |

| Figure 28 PSpice Bode Plot for Power Stage $\frac{\tilde{v}_o}{\tilde{\iota}_L}$                      | 43 |

| Figure 29 MATLAB Bode Plot of Type 2 Amplifier Transfer Function                                      | 43 |

| Figure 30 Pspice Buck-boost Voltage Mode Controller Circuit                                           | 46 |

| Figure 31 Voltage Mode Control Transient Response                                                     | 47 |

| Figure 32 Pspice Buck-boost Peak Current Controller Circuit                                           | 48 |

| Figure 33 Peak Current Control Transient Response                                                     | 49 |

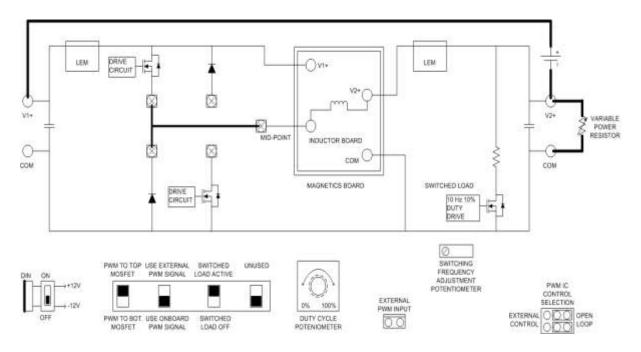

| Figure 34 Power Pole Board Diagram                                                                    | 51 |

| Figure 35 Buck-boost Power Board Configuration Diagram                                                | 54 |

| Figure 36 Power Pole Board Equipment Set Up                                                           | 56 |

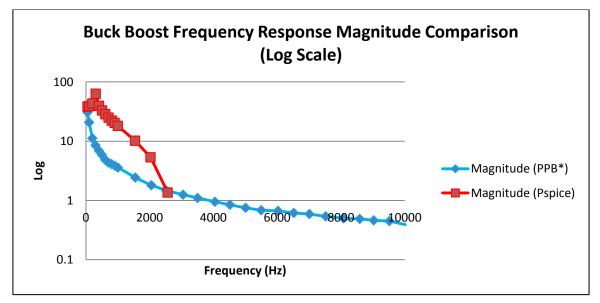

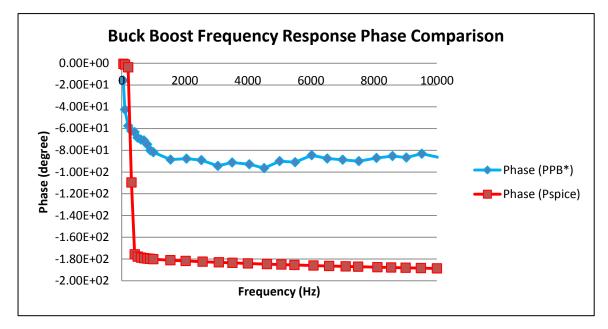

| Figure 37 Buck-boost Power Pole Board Magnitude Log Scale Plot                                        | 57 |

| Figure 38 Buck-boost Power Pole Board Phase Plot                                                      | 58 |

| Figure 39 Type 2 Amplifier Breadboard Connections                                                     | 58 |

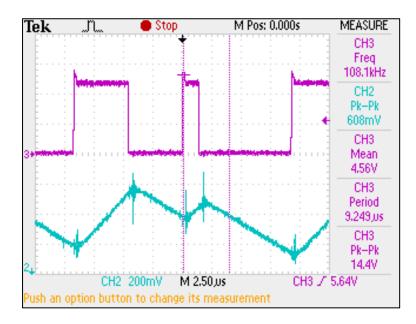

| Figure 40 Unstable PWM(purple) and Inductor Current(blue) Oscilloscope Waveforms (Output              |    |

| Voltage=10.28V)                                                                                       | 59 |

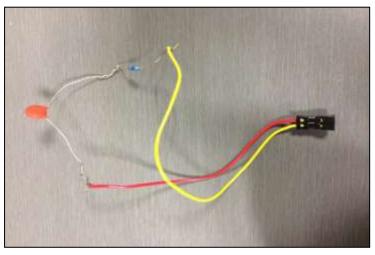

| Figure 41 Slope Compensation Jumper                                                  | 60 |

|--------------------------------------------------------------------------------------|----|

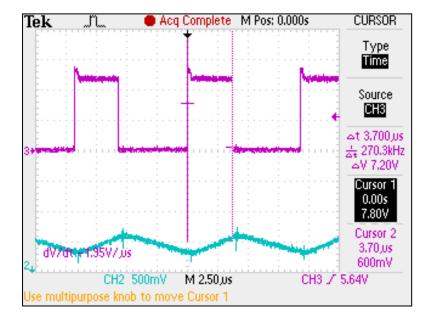

| Figure 42 PWM(purple) and Inductor Current(blue) Oscilloscope Waveforms - with slope |    |

| compensation                                                                         | 61 |

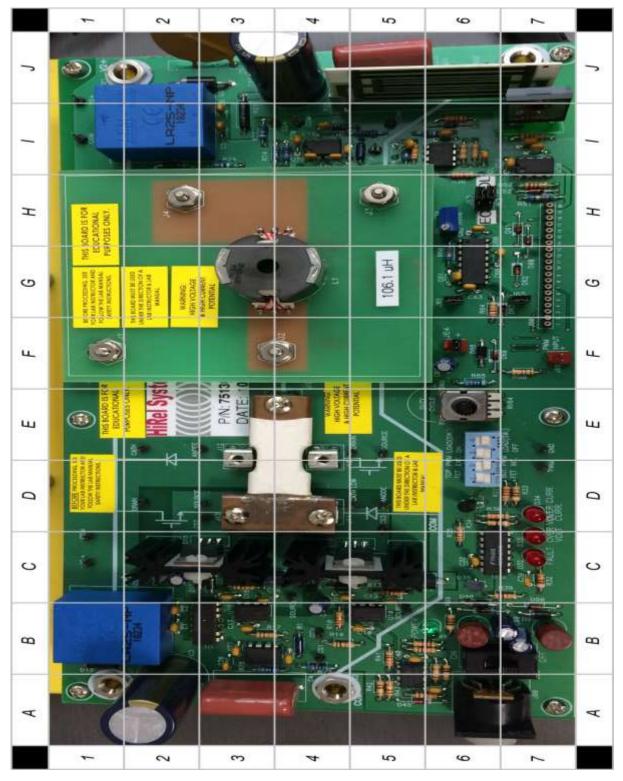

| Figure 43 Power Pole Board Component Locations                                       | 65 |

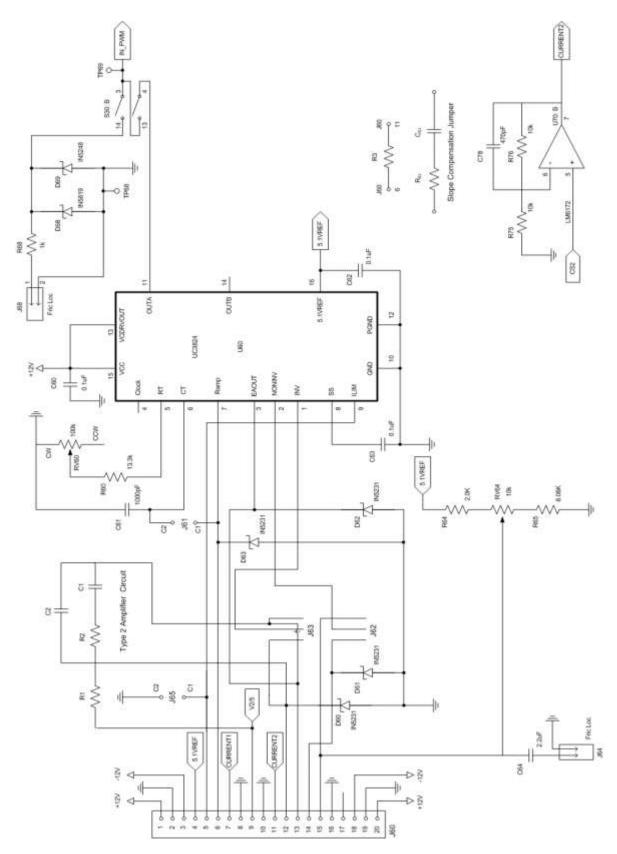

| Figure 44 Power pole Board Circuit Drawing with Peak Current Control Board           | 68 |

# **List of Tables**

| Table 1 Buck-boost Converter Parameter Parts and Values                     | 26 |

|-----------------------------------------------------------------------------|----|

| Table 2 Open loop transient response data                                   | 33 |

| Table 3 Type 3 Amplifier Parameters for Voltage Mode Control Implementation | 41 |

| Table 4 Type 2 Amplifier Parameters for Peak Current Control Implementation | 45 |

| Table 5 Voltage Mode Control Transient Response Data                        | 47 |

| Table 6 Peak Current Control Transient Response Data                        | 49 |

| Table 7 Control System Performance Criteria Values                          | 50 |

| Table 8 Type 2 Amplifier Breadboard Components                              | 59 |

| Table 9 Slope Compensation Jumper Values                                    | 61 |

| Table 10 Component locations on Power pole Board                            | 66 |

| Table 11 Test points on the Power pole Board                                | 67 |

# **Chapter 1 - Introduction**

This chapter will introduce the overall structure of this thesis report. This includes the objectives in completing different tasks and how to analyse the final results.

# **1.1 Objectives and Aim**

The aim of this project is to develop and analyse different feedback concepts for the buck-boost converter. This project represents an expansion of Luke Morrison's thesis, including the voltage mode controller for the buck converter [4]. The literature background is reviewed for the buck-boost converter, as well as the steps in completing feedback controllers for the closed loop system.

Computer simulations are used to model the buck-boost model and the feedback controllers. A simple comparison is made to determine which feedback concept is more effective. The parameter values are calculated from *MATLAB* coding, and implemented from an external source. The final task of the project is to implement a peak current compensator onto the power pole board, and analyse the effects it has on the hardware.

## **1.2 Report Overview**

The report begins in Chapter 2 with a literature review on the buck-boost converter in continuous conduction mode. Chapter 3 explains the DC control aspects which can affect the final feedback responses. Chapter 4 covers linearisation techniques required for transfer functions of the DC converter and feedback controllers. Chapter 5 shows a description of Bode plots for analysing transfer functions. Simulated results of the buck-boost converter are included in the chapter. Chapter 6 covers the literature review of designing feedback controllers for the buck-boost converter. This chapter also includes the final calculations of the feedback controller parts. The feedback controller results produced from *Pspice* schematics are in Chapter 7. Chapter 8 include descriptions of the Power Board components and how to obtain laboratory results. Chapter 9 includes the results for the buck-boost converter configured on the board, as well as the peak current control compensator testing. Finally, Chapter 10 concludes this thesis report with recommendations on further improvements and project expansion in the future.

# **Chapter 2 - Buck-boost converter review**

This chapter provides the theoretical background on the buck-boost converter selected for project analysis.

# 2.1 DC converters

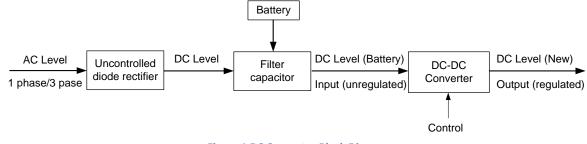

DC converters are used to regulate DC power levels similar to the role of a transformer. A block diagram indicating how it is possible to obtain a regulated DC level is shown in Figure 1 [5].

The DC input voltage unregulated and the raw energy are acquired from the diode rectified AC value, for either single phase or 3 phase sources. The converter output is assumed to supply an equivalent resistance load which is required for ripple effect. The filter capacitor is used to minimise the ripple in the DC voltage. A small filter is used as an integral component for the regulated value. [5].

There are several types of DC converters including Buck, Boost, Buck-Boost, Ćuk and Full- bridge topologies. The buck and boost are the most basic DC converters because they simply step down and step up DC levels respectively [5]. For this project, the buck-boost model is selected as the main converter for analysis because it has a more complex design than the basic DC converters.

# 2.2 Buck-boost Converter Components

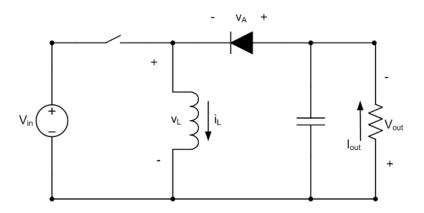

The buck-boost converter consists of a voltage source  $V_{in}$  connected with a switch in series. The output load is connected in parallel to a capacitor, with the inductor and diode connected with the load as given in Figure 2 [3, 5]. The switch duty ratio D can vary from 0 and 1, which directly controls the output voltage. For the buck-boost topology, the output voltage can be lower or higher than the input voltage. This is due to the converter's design which is formed with a combined buck and boost topology. When D = 0.5, the input and output voltage have the same value, since the output to input ratio is 1, as shown in Equation 1 [3, 5].

Figure 2 Buck-boost Converter

$$\frac{V_o}{V_{in}} = \frac{D}{1 - D}$$

Equation 1

MOSFETs are selected for switches in DC converters. The symbol for an n-channel MOSFET is shown in Figure 3 [6]. The advantages of using MOSFETs are that they have high impedance gates and use less switching time and power to change operating states. The gate terminal is used to control the power flow of the MOSFET with the switch signal control. When the switch signal q is 1, the MOSFET is conducting and current flows from the drain terminal to the source. This is the "ON" state for the transistor. The MOSFET does not conduct when switch signal is zero, which is the "OFF" state [6].

## 2.3 Buck-boost Operation in Continuous Conduction Mode

The buck-boost converter is operated in continuous conduction mode. It is assumed the design specifications for the converter are as follows [3]:

- 1. Diodes, transistors, and the passive components are all ideal unless explicitly state otherwise.

- 2. Losses in the inductor and capacitor are neglected.

3. Switching frequency and duty ratio need to be constant over each cycle.

Figure 4 displays the buck-boost converter under various MOSFET operating conditions and the waveforms of different components [3]. The capital letters signify average values, while lower case letters represent time domain values. When the MOSFET is closed (ON), power flows from the voltage source to the inductor. This makes the inductor voltage the same as the source voltage. The diode does not build up energy as it is reverse-biased. When the switch is open (OFF), inductor current flows through the diode and builds up power from the previous transistor state to the output. Both states occur in each cycle timed by the switching frequency  $f_s$ . The switching time  $T_s$  of one cycle is the reciprocal of the switching frequency, as given in Equation 2. The operating time of the converter is given in Equations 3 and 4 [3].

#### Figure 4 Buck-boost Conduction MOSFET states and Waveforms

$$T_s = \frac{1}{f_s} = T_{on} + T_{off}$$

Equation 2

$$T_{on} = DT_s$$

Equation 3

$$T_{off} = (1 - D)T_s$$

Equation 4

During the ON state, the diode voltage  $v_A$  equals the sum of the input and output voltages as given in Equation 5. The average diode voltage has the same value as the output voltage for DC steady state conditions due to no power being dissipated in the inductor. When the MOSFET is in the OFF state, the diode voltage drops to zero from the ON state. Figure 4(c) displays the diode voltage waveform [3].

$$v_A(q=1) = V_{in} + V_{out}$$

Equation 5

Figure 4(d) displays the inductor voltage waveform which changes instantaneously between the ON and OFF state [3]. During the ON state, the power flow causes the inductor to have the same voltage as the input supply, as given in Equation 6. During the OFF state, the inductor voltage is equal to the negative polarity of the output voltage, as given in Equation 7. The negative polarity is cause by the fixed direction of the current flowing through the capacitor and output load [7]. The voltages for the diode and inductor remains constant during each MOSFET state, whereas the currents have time based linear relationships [3].

$$v_L(q=1) = V_{in}$$

Equation 6

$$v_L(q=0) = -V_{out}$$

Equation 7

By applying the Kirchhoff's current law in the converter, the inductor current is obtained from the addition of the input and output currents as given in Equation 8. The output current is obtained from the ohm's law relationship between the output voltage and load, which can be substituted into the inductor current equation with Equation 1. In DC steady state, the average capacitor current is zero [3].

$$I_L = I_{in} + I_o = \frac{1}{1 - D} \frac{V_o}{R}$$

Equation 8

Over time, the inductor current is obtained from the sum of the average inductor current and the time domain ripple inductor current as given in Equation 9. The inductor current has average value

of zero and experiences ripple through each state (rises when  $v_L$  is positive and drops when  $v_L$  is negative). The peak-peak ripple value can be calculated from Area A or B as given in Equation 10 [3].

$$i_L(t) = I_L + i_{L,ripple}(t)$$

Equation 9

As displayed in Figure 4(d), area A and B has must possess the same scale and opposing polarity, which represent volt-second areas. This is because the average inductor current is zero. It is possible to obtain the ratio for input/output voltage values from the  $v_A$  or  $v_L$  since the average value of the inductor voltage is zero [3].

$$\Delta i_L = \underbrace{\frac{1}{L} V_{in}(DT_s)}_{\text{Area A}} = \underbrace{\frac{1}{L} V_o(1-D)T_s}_{\text{Area B}}$$

It is necessary for the capacitor to possess a very large value in order to achieve a constant output voltage. The capacitor has lower impedance in the ripple inductor current than the load resistance, therefore it is presumed the ripple diode current passes through the capacitor, as shown in Equation 11 [3]. When forming the equivalent circuit, the capacitor will be connected with an equivalent series resistance (ESR) for dispersing heat power [8].

$$i_c(t) \cong i_{diode,ripple}(t)$$

Equation 11

The buck-boost configuration on the power pole board should display these waveforms to confirm the components are not malfunctioning.

## **Chapter 3 - Control Aspects of DC Converters**

This chapter covers control aspects which can affect the feedback analysis of DC converters. This includes the dynamic average model required for DC converters, DC ideal transformer, and the pulse width modulation (PWM) implemented on the converter simulations and hardware.

## **3.1 Dynamic Average Model**

Dynamic average models are preferable for analysing feedback control in DC converters. The dynamic conditions are determined by the change in output load and input voltage. It is assumed

the operating time is relatively slow and frequencies of average values are lower than the switching frequency  $f_s$  [3].

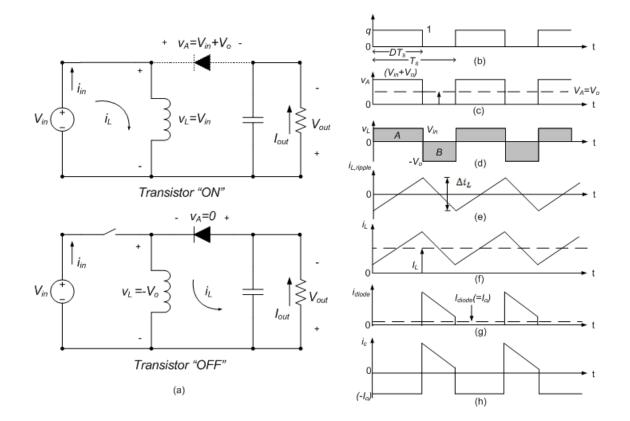

Figure 5 Dynamic Average Model Configurations

Figure 5 displays the configuration in implementing a dynamic average model into DC converters. The figures have voltages and currents with the following subscript meanings: voltage port ('vp') and current-port ('cp'). The voltage port refers to the input terminals, while the current port refers to the output terminals [3].

Figure 5(a) is the MOSFET switching power pole connected with the diode. The switching signal q is based on the ratio between the control voltage  $v_c$  and ramp voltage  $v_r$ , which are further explained in Chapter 3.2. The switching states make it difficult to perform analysis with any change of input voltage or output load.

Figure 5((b) displays an ideal transformer for the DC steady state average model. This model is suitable for performing transient analysis on the converter. The DC steady state values are represented by capital letters: *V* and *I*, while lower case represents the full dynamic time varying quantities [3].

The voltage-port voltage should not have a negative polarity as the duty ratio *D* has to be within the range 0 to 1. Assuming the switching power pole is functional for DC and AC applications, the ideal transformer is theoretical and recommended for mathematical problems. The disadvantage of using a real transformer is that it cannot perform the same behaviour. This is signified by the parallel straight and curved line below the transformer. There is no electrical isolation between the voltage-

port and the current-port, as signified by the connection at the bottom of the windings of the transformer in Figure 5(b) [3].

The MOSFET and diode devices are replaced by the ideal transformer model, which completes the dynamic average model in Figure 5(c). Equations for time domain average values are formed from the model, as given in Equations 12 and 13. The DC average values are represented by a bar over the lowercase letters [3].

$$\bar{v}_{cn}(t) = d(t)\bar{v}_{vn}(t)$$

Equation 12

$$\bar{\iota}_{vn}(t) = d(t)\bar{\iota}_{cn}(t)$$

Equation 13

#### Figure 6 Buck-boost Dynamic Average Model

Figure 6 displays the conversion from the buck-boost MOSFET/switching pole circuit to the dynamic average model, which is applied in simulations and tested for output transient response. The ideal transformer replaces the MOSFET/diode switching pole in the buck-boost configuration which eliminates the switching conditions for dynamic analysis [3].

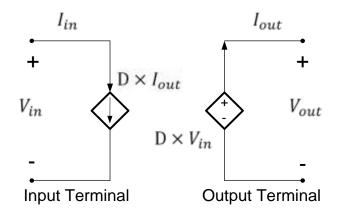

### **3.1.1 Ideal Transformer**

The ideal transformer is the main component of the dynamic average model. It is responsible for cancelling the DC switching ripple, as required for DC performance analysis [9]. This makes the circuit a switching electronic converter rather than a simple transformer [10]. Figure 7 displays the DC converter equivalent model which has dependent sources for manipulating the input current and

output voltage. The circuit relationships are distinguished in Equations 14 and 15, which applies for all types of converters [9].

Figure 7 DC Converter Equivalent Model

$$V_{out} = D \times V_{in}$$

Equation 14

$$I_{in} = D \times I_{out}$$

Equation 15

When examining these converters, there are three main variable terminals: the input, output and the controlled terminal which is the duty ratio. The input variables are controlled by the duty ratio, which determines the output variables. The DC ideal transformer illustrates this operating behaviour in Figure 8, assuming the system will ideally operate at 100% capability [9].

Figure 8 DC Ideal Transformer Model

$$V_{sec} = D \times V_{prim}$$

Equation 16

$$I_{prim} = D \times I_{sec}$$

Equation 17

The advantage of using an ideal transformer is that it does not disturb the energy going through the model [10]. Therefore, the input and output terminals should experience the same amount of power as shown in Equations 18 and 19.

$$P_{in} = P_{out}$$

Equation 18

$$V_{in} \times I_{in} = V_{out} \times I_{out}$$

Equation 19

When simulating the buck-boost converter with the ideal transformer, the input and output voltages should be based on the relationship that is given by equations in Chapter 2.2.

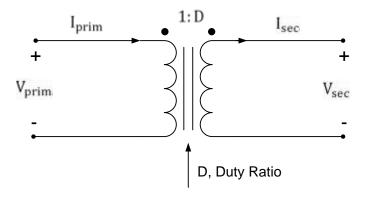

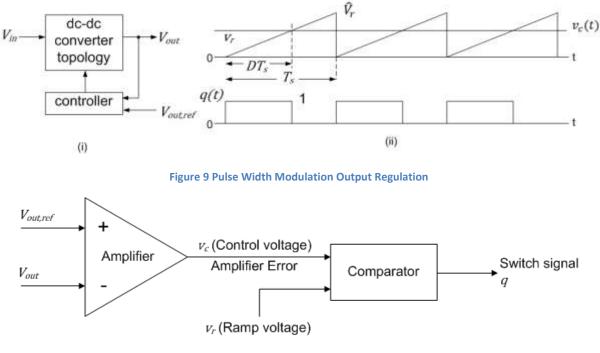

## 3.2 Regulation with pulse width modulation

Pulse width modulation (PWM) is used for manipulating DC output at a constant switching frequency. It modulates the pulse width to control the average value of the switching cycle output. The duty ratio *D* is directly related to the pulse width and the output voltages to match their desired values and range. It will react to any changes in the input voltage and output load disturbances [3].

Figure 9 displays a block diagram and waveforms of an output regulated DC converter for this case [3]. In the PWM controller, the output voltage is measured and contrasted with its reference value. An amplifier is used to measure the error between the two values, as shown in Figure 10 [5]. The output value of the amplifier is the control voltage  $v_c$ . The comparator is used for comparing the control voltage with the ramp voltage  $v_r$  to determine the switch control signal q. When the ramp voltage exceeds the control voltage, the MOSFET switch signal will go to zero (OFF state). The ramp peak  $\hat{V}_r$  is the final ramp value at the end of each MOSFET cycle [3].

# **Chapter 4 - Linearisation**

This chapter covers linearisation in order to obtain transfer functions required for the closed loop converter system. The purpose of linearisation is to take in account all DC components operating around dc steady state points and obtain the small signal model for the DC equivalent circuit.

# 4.1 Pulse Width Modulator Linearisation

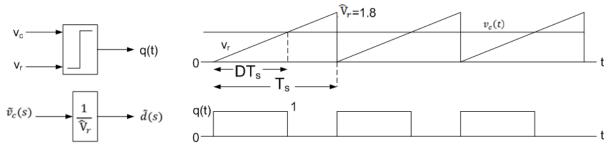

The PWM linearisation is based on the Power Pole Board configuration of the PWM UC3824 designed by the University of Minnesota, as shown in Figure 11 [1, 3]. The device generates a pulse modulated signal to control the MOSFET. It is assumed the switching frequency is kept constant. The ramp signal  $v_r$  has the maximum amplitude  $\hat{V}_r$ . The control voltage to ramp voltage ratio will be used to obtain the MOSFET switching function q(t). If the control voltage is larger than the ramp voltage, the digital switch signal will be 1 which activates the MOSFET. The MOSFET switch will automatically turn off when the control voltage intersects the linear ramp signal. The switch dutyratio d(t) is as given in Equation 20 [3].

$$d(t) = \frac{v_c(t)}{\hat{V}_r}$$

Equation 20

The time domain control voltage is based on the addition of small signal disturbance and the DC steady state operating point, as given in Equation 21 [3].

$$v_c(t) = V_c + \tilde{v}_c(t)$$

Equation 21

Using the relationships in Equations 20 and 21, it is possible to substitute these variables into the power stage duty cycle equation, which makes up Equation 22 [3].

$$d(t) = D + \tilde{d}(t) = \frac{V_c}{\hat{V}_r} + \frac{\tilde{v}_c(t)}{\hat{V}_r}$$

Equation 22

Equation 22 is easily separated into the small signal variable for obtaining the PWM unit transfer function. The transfer function is the small signal ratio of the duty ratio to the control voltage, as given in Equation 23. This proves the PWM has a pure gain value as the final equation is a reciprocal of the ramp to peak amplitude [3].

$$\tilde{d}(t) = \frac{\tilde{v}_c(t)}{\tilde{v}_r} \to \tilde{d}(s) = \frac{\tilde{v}_c(s)}{\tilde{v}_r}$$

$$G_{PWM}(s) = \frac{\tilde{d}(s)}{\tilde{v}_c(s)} = \frac{1}{\hat{V}_r}$$

Equation 23

The Unitrode/Texas Instruments has provided a datasheet listing the characteristics of different high speed PWM controllers. The UC3824 ramp valley to peak is 1.8*V* [11], which is substituted into Equation 23 to calculate the PWM gain, as given in Equation 24 [3].

$$G(s)_{PWM,UC3824} = \frac{1}{\hat{V}_r} = \frac{1}{1.8} = 0.556$$

Equation 24

This completes the linearisation for the PWM controller configured on the Power Pole board.

## **4.2 Power Stage Linearisation**

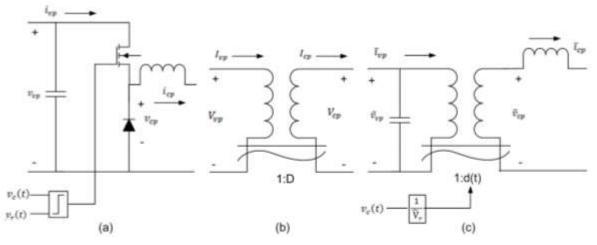

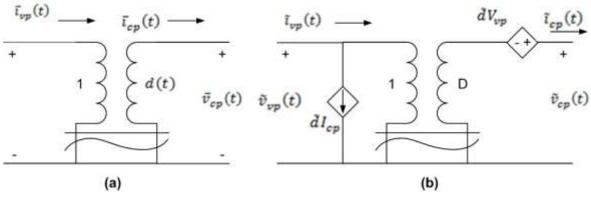

Before creating feedback compensators for the DC converter, linearisation must be applied to the buck-boost power stage. It is assumed a small signal disturbance will occur on the DC switching power pole. The linearised average model of the switching power pole is shown in Figure 12(a).

Small signal perturbations are represented by a tilde over the lowercase letters, as shown in Figure 12(b) [3].

Figure 12 Switching Power Pole Linearisation

The time-domain dynamic average values in Figure 12(a) can be expressed as the sum of the small signal perturbations and the DC steady state values, which are represented in uppercase letters. Equation 25 shows a set of DC average value equations in the time domain [3].

$$\bar{d}(t) = D + \tilde{d}(t)$$

$$\bar{v}_{vp}(t) = V_{vp} + \tilde{v}_{vp}(t)$$

$$\bar{\iota}_{vp}(t) = I_{vp} + \tilde{\iota}_{vp}(t)$$

$$\bar{v}_{cp}(t) = V_{cp} + \tilde{v}_{cp}(t)$$

$$\bar{\iota}_{cp}(t) = I_{cp} + \tilde{\iota}_{cp}(t)$$

Equation 25

It is possible to create sum equations of small signal and steady state values by analysing the relationships between the duty ratio and the current and voltage. The DC average value equations are substituted and rearranged to obtain Equations 26 and 27 [3].

$$V_{cp} + \tilde{v}_{cp} = (D + \tilde{d})(V_{vp} + \tilde{v}_{vp})$$

$$I_{vp} + \tilde{\iota}_{vp} = (D + \tilde{d})(I_{cp} + \tilde{\iota}_{cp})$$

Equation 26

$$\begin{split} V_{cp} + \tilde{v}_{cp} &= DV_{vp} + D\tilde{v}_{vp} + \tilde{d}V_{vp} + \tilde{d}\tilde{v}_{vp} \\ I_{vp} + \tilde{\iota}_{vp} &= DV_{cp} + D\tilde{v}_{cp} + \tilde{d}V_{cp} + \tilde{d}\tilde{v}_{cp} \end{split} \tag{Equation 27}$$

Assuming that the products of the small signal quantities are very small, these can be ignored in the final equations. Therefore,  $\tilde{d}\tilde{v}_{vp}$  and  $\tilde{d}\tilde{v}_{cp}$  are removed from Equation 27. For the converter model,

Equation 26 is decomposed to form equations for the DC steady state variables (Equation 28) and small signal linear representation given by steady state conditions (Equation 29) [3].

$$V_{cp} = DV_{vp}$$

$I_{vp} = DI_{cp}$  Equation 28

$$\begin{split} \tilde{v}_{cp}(t) &= D\tilde{v}_{vp} + V_{vp}\tilde{d} \\ \tilde{\iota}_{vp}(t) &= D\tilde{\iota}_{cp} + I_{cp}\tilde{d} \end{split} \tag{Equation 29}$$

The small signal equations can be used to find the converter's power stage transfer function, which is discussed in a later chapter.

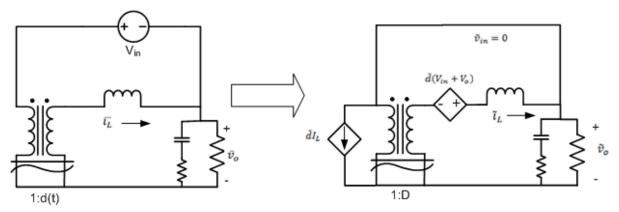

Figure 13 Linearised Buck-boost Model

The linearised small signal average model of the Buck-boost circuit is shown in Figure 13 [3]. The switching power pole is replaced by the small signal components. The model includes an equivalent series resistance (ESR) for the output capacitor and two dependent sources to indicate switching relationships. The perturbation  $\tilde{v}_{in}$  becomes zero in the linearised model since the DC input voltage is assumed to be a constant [3].

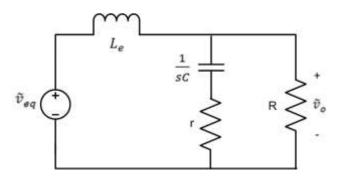

## 4.3 Equivalent Circuit and Transfer Function of Converter

A small signal equivalent circuit is used in the derivation of the power stage transfer function derivation  $(G_{PS}(s))$ , as shown in Figure 14. The equivalent circuit is applicable to all types of DC converter. The input voltage is a small signal equivalent  $\tilde{v}_{eq}$  and is equal to  $\tilde{d} \times V_{in}$ . The buck-boost power stage transfer function  $\tilde{v}_o/\tilde{d}$  is given in Equation 30 [3].

Figure 14 DC Converter Equivalent Circuit

$$\frac{\tilde{v}_o}{\tilde{d}} = \frac{V_{in}}{(1-D)^2} \left(1 - s\frac{DL_e}{R}\right) \frac{1 + srC}{L_e C \left(s^2 + s\left(\frac{1}{RC} + \frac{r}{L_e}\right) + \frac{1}{L_e C}\right)}$$

Equation 30

It is important to note that Equation 30 is the small signal transfer function of the output voltage to duty ratio. The equivalent model is a low pass LC filter, and the buck-boost converter has two poles and a RHP zero [3]. Furthermore, the capacitor ESR will introduce a LHP zero at higher frequency [12]. Unlike the buck converter, the buck-boost converter uses the duty ratio D for calculating the power stage transfer function. Since the inductor and the capacitor are not always connected in the equivalent circuit, the inductance L is replaced by the effective inductance as illustrated in Equation 31 [3].

$$L_e = \frac{L}{(1-D)^2}$$

Equation 31

| Parameter Part        | Value           |

|-----------------------|-----------------|

| Input Voltage (Vin)   | 20V             |

| Output Voltage (Vout) | 12V             |

| Resistor (R)          | 10Ω             |

| Capacitor (C)         | 680uF           |

| Inductor (L)          | 106.1 <i>uH</i> |

| Duty ratio (D)        | 0.375           |

**Table 1 Buck-boost Converter Parameter Parts and Values**

Table 1 lists the buck-boost parameter values which are applied to computer simulations and configured on the power pole board.

# **Chapter 5 - Bode Plots and Computer simulations**

This chapter covers the necessary background of Bode plots used for designing feedback controllers for the buck-boost converter. Simulation plots produced from *MATLAB* and *PSpice* are analysed using the theoretical knowledge of Bode plots.

## **5.1 Bode plots Review**

Bode plots can be used to illustrate the frequency response of DC converters as magnitude and plots. The magnitude is in decibels, and phase is in degrees. Before conducting simulation runs on the system, it is useful to review how these plots should appear based on the transfer function [9].

The magnitude in decibels is defined in Equation 32, where M can be dimensionless.

$$||M||_{dB} = 20 log_{10}(||M||)$$

Equation 32

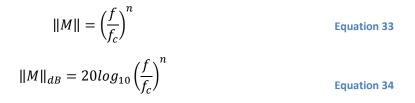

The bode plot defines a crossover frequency  $f_c$ , where the magnitude is 0 or 1 dB. Given the magnitude ||M|| is a dimensionless quantity with n and  $f_c$  which are constants (Equation 33), Equation 32 is rearranged to Equation 34 [9].

Figure 15 Magnitude Bode plot linear relationships

Figure 15 signifies how different values of n affects the Bode plot magnitude over several decades in frequencies. As indicated in Equation 34, an increase of  $n \times 20 \ dB$  is due to a decade increase in frequency. Therefore, the gradient of the magnitude is  $n \times 20 \ dB/decade$  [9].

By using Bode plots to display the frequency response of various transfer functions, it is possible to analyse how a single pole and single zero affect the magnitude and phase individually. For  $\left(\frac{f}{f_c}\right)^{-1}$ , the value of n is -1 which makes the magnitude gradient  $-20 \ dB/decade$ . This is the asymptote for a single real pole transfer function. The magnitude consists of a low frequency asymptote of  $0 \ dB$  and decreases by approximately  $-20 \ dB \ per \ decade$  after intersection with crossover frequency. The phase is  $0^{\circ}$  for a low frequency asymptote, and  $-45^{\circ}$  at crossover frequency. The phase gradient is  $-45^{\circ}/decade$  until the higher frequency asymptote phase is  $-90^{\circ}$ . [9].

For  $\left(\frac{f}{f_c}\right)^1$ , the value of *n* is 1 which makes the magnitude gradient 20 *dB*/*decade*. This is the asymptote for a single real zero transfer function. The magnitude consists of a low frequency asymptote of 0*dB* and increases by approximately 20 *dB per decade* after intersection with crossover frequency. The phase is 0° for the low frequency asymptote, and 45° at crossover frequency. After the crossover frequency, the phase angle decreases each decade until it reaches 90° at larger frequency. Therefore, the phase gradient is  $45^\circ/decade$  [9].

For  $\left(\frac{f}{f_c}\right)^{-2}$ , the value of *n* is -2 which makes the magnitude gradient  $-40 \ dB/decade$ . This is the asymptote for a two pole transfer function. The magnitude consists of low frequency asymptote of 0 dB and decreases by  $40 \ dB \ per \ decade$  after intersection with crossover frequency. The phase is  $0^\circ$  for low frequency asymptote, and  $-90^\circ$  at crossover frequency. After the crossover frequency, the phase angle decreases each decade until it reaches  $-180^\circ$  at larger frequencies. At the crossover frequency (Equation 35), there maybe a peak which is determined by the quality factor Q. It measures the amount of dissipation in the system, which can be calculated using Equation 36. When increasing the value of Q, it makes the phase change sharper between the  $0^\circ$  and  $-180^\circ$  asymptote [9].

1

$$f_c = \frac{1}{2\pi\sqrt{LC}}$$

Equation 35

$$Q(dB) = R \sqrt{\frac{C}{L}}$$

Equation 36

# 5.2 Buck-boost Pole Zero Map

It is easily possible to generate a bode plot the buck-boost transfer function using *MATLAB*. Additionally, the syntax '*pzmap*' allows the user to map the pole and zero locations of transfer functions [13]. Using the equations and parameters introduced from Chapter 4.3, the equivalent *MATLAB* code script has created and is shown in Figure 16.

| clc         |                                                           |

|-------------|-----------------------------------------------------------|

| a=11('#')   | 1                                                         |

| Buck Boo    | st Parameter Values                                       |

| Vin=20: k   | Input Voltage (V)                                         |

| Vo=12; 50   | utput Voltage (V)                                         |

| C=680*10*   | -6/ VCapacitor (F)                                        |

| 1-106.1*1   | 0^-6; %Inductor (N)                                       |

| Rload=10:   | WOutput resistor (chm)                                    |

| z=0.01; %   | ESD                                                       |

| D=Vo/(Vin-  | +Vo); %Buck Boost Duty Ratio                              |

| Le-1/((1-)  | 5)"2); %Small Signal Equivalent Inductance Le             |

| NBuck Boo   | st Output to Duty Ratio Transfer Function                 |

| a=Vin/((I   | -D) ^2) ;                                                 |

| b=1-((s*D   | *Le)/Rload);                                              |

| c={1+x*z*(  | C) / (Le*C*((s*2)*(s*((1/(Rload*C))*(r/Le)))+(1/(Le*C)))) |

| vod=a*b*c   | r                                                         |

| WFoles and  | t seros plot                                              |

| pamap (vod) |                                                           |

|             |                                                           |

Figure 16 Buck-boost Transfer Function P-Z Map Code

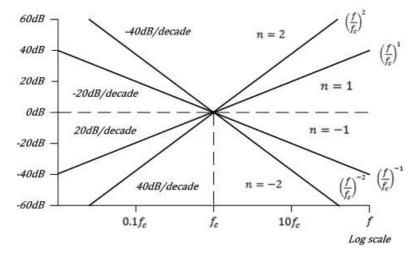

Figure 17 Poles and Zeros Locations for Buck-boost Transfer Function

Figure 17 shows the locations of the poles and zeros of the configured buck-boost converter. The two complex poles are located at frequency 370.8Hz which will result in the buck-boost magnitude decreasing at -40dB/decade and the phase shift lags by  $180^{\circ}$  [9]. Both poles are lying near the imaginary axis, but are located on different real axis points. This signifies the buck-boost open loop transient response will be oscillatory and takes a significant amount of time to reach steady state [14].

The capacitor ESR creates the LHP zero at 23.3kHz. The RHP zero is introduced from the buck-boost circuit at 15.6kHz which makes the magnitude to fall at 20dB/decade, and introduce an additional 90° phase lag [9]. The contact between the two zeros will neglect the RHP zero effects on higher frequencies [15]. Despite this condition, it is likely that the RHP zero will still cause problems when designing feedback compensators to control the buck-boost system [16].

# 5.3 PSpice Simulation on Power Stage $\frac{\tilde{v}_o}{\tilde{d}}$

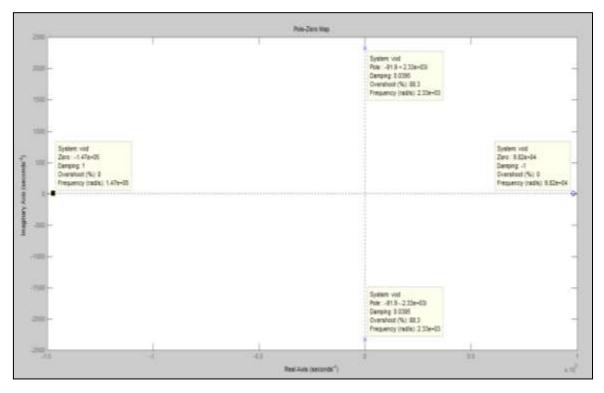

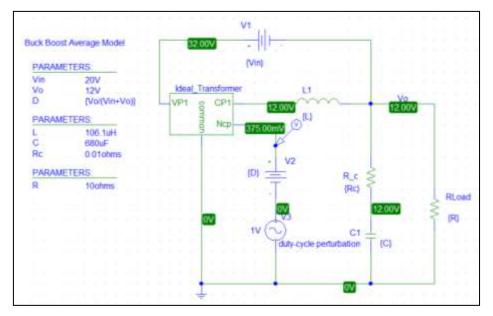

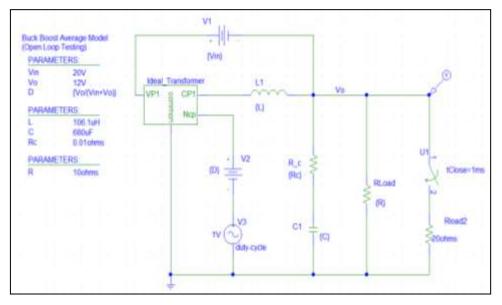

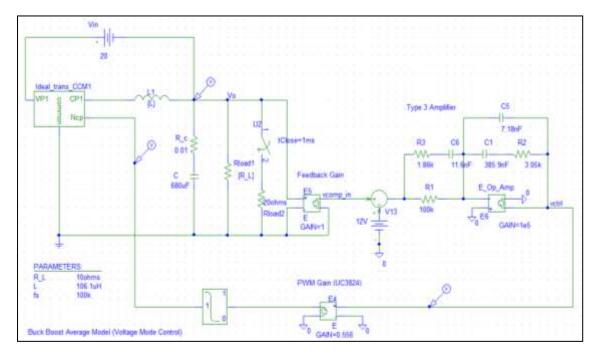

*PSpice* Schematic is a very effective simulation package for drawing and analysing electrical circuits. The University of Minnesota have created a schematic file of circuit components for designing the DC converters [2, 3]. The buck-boost dynamic model is adapted from Ned Mohan's research on designing the peak current compensator, as shown in Figure 18 [3]. Through this simulation package, it is possible to obtain the frequency response for the power stage transfer function  $\frac{\tilde{v}_o}{\tilde{d}}$  [2].

Figure 18 Pspice Drawing of Buck-boost Dynamic Model

The buck-boost dynamic model makes use of an ideal transformer, which includes dependent sources for the voltage and current. The duty ratio D is determined by the DC voltage source V2. An AC voltage source is connected in series for small signal perturbations. It has an amplitude of 1V because the model is linearised before AC analysis. The parameter values are entered into the program and located on the side of the circuit in Figure 18 [3].

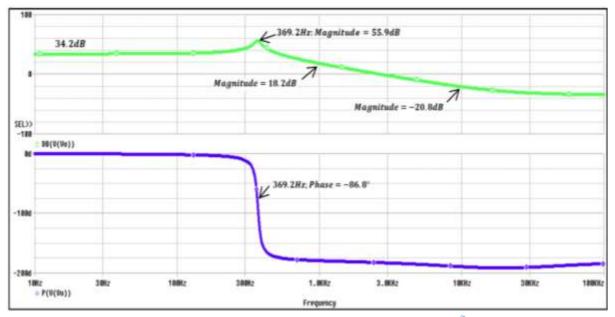

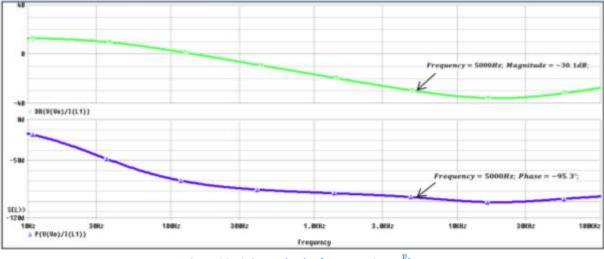

Figure 19 PSpice frequency response of buck-boost power stage  $\frac{v_o}{d}$

$$Q = M_{peak} - M_{low,f}$$

$$= 55.9 - 34.2 = 21.7 dB$$

Equation 37

$$Q = R \times \sqrt{\frac{C}{L}} = 10 \times \sqrt{\frac{680 \times 10^{-6}}{106.1 \times 10^{-6}}} = 25.3 dB$$

Equation 38

Figure 19 shows the frequency response for the buck-boost power stage transfer function ( $\frac{\tilde{v}_o}{\tilde{d}}$ ). The plot shows the low frequency asymptote has a magnitude of 34.2*dB* and phase angle 0°. Since the power stage has two poles in the transfer function, the power exhibits a resonant peak of 55.9*dB* at frequency 369.2*Hz*, where the phase drops to  $-180^\circ$ . According to Robert W. Erikson's explanation on two pole transfer function, the quality factor *Q* on the Bode plot is the difference between the peak magnitude and the low frequency asymptote, as calculated in Equation 37 [9]. *Q* is also calculated with the buck-boost component values in Equation 38. The calculated magnitude gives results which are quite similar to the Bode plot.

For moderate frequency ranges, the magnitude gradient is calculated using the values from 1000Hz and 10000Hz. This will ensure the gradient is expressed in dB/decade, since one decade is a 10 fold increase in frequency [9]. The magnitude gradient is calculated in Equation 39, which the value is very similar to the expected result.

$$M_{Pspice} = y_2 - y_1 = -20.8 - 18.2 = -39 dB/decade$$

Equation 39

For designing a feedback controller, the design frequency has to be as large as possible for a quick closed loop response. The value should exceed the resonant frequency  $f_r$ , as calculated in Equation 40.

$$f_r = \frac{1}{2\pi\sqrt{LC}}$$

$$= \frac{1}{2\pi\sqrt{106.1 \times 10^{-6} \times 680 \times 10^{-6}}} = 592.5Hz$$

Equation 40

The phase angle should not exceed  $-180^{\circ}$  before the magnitude and phase angle intersects the crossover frequency [3]. Furthermore, the instability effect caused by the RHP zero can be neglected with larger frequencies [16].

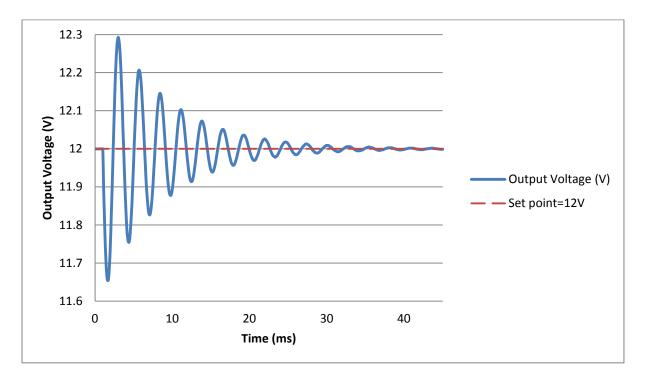

Figure 20 Buck-boost Open Loop Dynamic Circuit

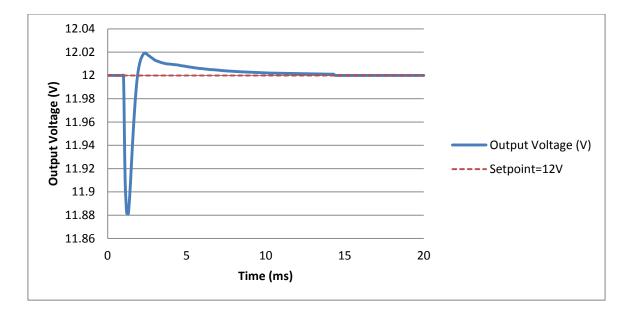

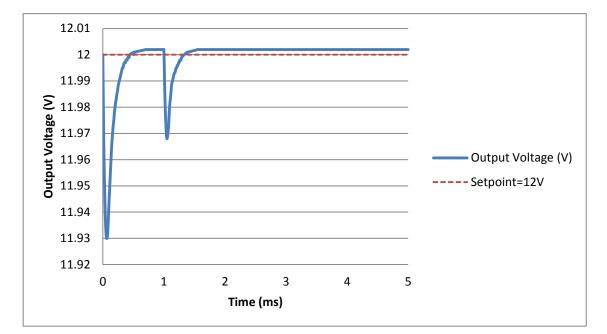

Figure 20 shows the buck-boost dynamic model which is extended with a second resistor and switch in parallel to the output load [2, 3]. The additional components will introduce a transient response after the switch is closed at 1ms. Before the switch is closed, the output terminal will remain constant at the desired set point of 12V. The parallel connections will alter the output load from  $10\Omega$  to  $6.67\Omega$ . The transient response of the output voltage is shown in Figure 21, and Table 2.

#### Figure 21 Buck-boost Open Loop Transient Response

| Maximum Overshoot          | 12.293V        |

|----------------------------|----------------|

| Time of Maximum Overshoot  | 3ms            |

| Maximum Undershoot         | 11.655V        |

| Time of Maximum Undershoot | 1.6 <i>ms</i>  |

| Settling Time              | 38.8 <i>ms</i> |

#### Table 2 Open loop transient response data

Since there is no feedback controller applied in this circuit, the transient response represents the open loop behaviour of the buck-boost circuit. After 1ms, the output voltage oscillates and the amplitude decreases over time. The maximum amplitude of the open loop system is 12.293V at 3ms, and slowly decreases. The waveform indicates the output voltage is slowly reaching the desired set point and finally becomes stable after 38.8ms. Despite the output voltage having a very small oscillatory pattern about the set point, the open loop system is considered to be stable since the offset is small. However, this does demonstrate that the buck-boost converter can be altered in terms of oscillation behaviour and the time for reaching stable state. This circuit will be further

expanded and analysed after a description of designing different feedback controllers in the next chapter.

# **Chapter 6 - Feedback control compensator design**

This chapter covers the concept of feedback control systems, and techniques in designing different feedback controllers for the buck-boost converter. There are two feedback systems applied in this thesis: voltage mode control and peak current control. This chapter includes the steps in designing and implementing the desired feedback compensators. The purpose of designing feedback controllers is to apply and test closed loop operation in the Power Pole board and computer simulations.

## **6.1 Electronic control systems**

The buck-boost converter is a form of electronic control system, since it consists of a system formed by electrical components [17]. These components create the DC input and output relationships, as explained in earlier chapters. In terms of control systems, there are two different types which will be used in this thesis: open loop and closed loop.

The open loop system does not have any feedback relationships between the output and input terminals, creating an unregulated process. This makes it difficult to control the amount of oscillations and time to reach the set point. This was already discussed in Section 5.3.1. The closed loop system is designed to overcome these issues by comparing the output variable to the desired set point. This will automatically regulate the output until the desired value is reached [18]. These control systems are designed based on the transfer functions of the DC converter.

The power pole board is configured with most of the relevant transfer functions able to be measured from the lab exercises created by the University of Minnesota. The control system is considered successful if the following conditions are satisfied for the output voltage [3]:

- Gets close to zero steady state error.

- Responds quickly to changes in input voltage and output load. This means any oscillations in the system response dissipate quickly.

- Produce minimal overshoot and noise susceptibility from the hardware.

## 6.2 K Factor Method

To design feedback control compensators, the K Factor method is the one method which can be used. It is a technique invented by H. Dean Venable in the 1980's and uses the phase rise for stability observations in control loops [19]. Higher frequencies tend to cause stability problems in the system as well as large amplifier gain values. For a stable system, the phase lag must be less than  $180^{\circ}$  at the crossover frequency  $f_c$ . The K factor uses the gain and phase margins obtainable from any amplifier transfer function. The gain margin is the measured magnitude below 0dB when the phase angle equals  $-180^{\circ}$ . It responds quickly by increasing to 10dB. This prevents the system from becoming significantly oscillatory because of any change in parameters and other disturbances. When performing any analysis at the crossover frequency, the phase angle is compared with  $-180^{\circ}$ . The phase margin is the gap between the loop transfer function phase angle and  $-180^{\circ}$  [3]. For control loop design, a phase margin of  $60^{\circ}$  is preferable because smaller phase margins result in large overshoots and oscillates for longer times, and larger phase margins produce slower and flatter responses. The crossover frequency needs to be as large as possible to ensure the closed loop response is not being affected by the RHP zero [3]. The amplifier bode plots are obtained in *MATLAB* simulations, using syntax code 'bode' [20].

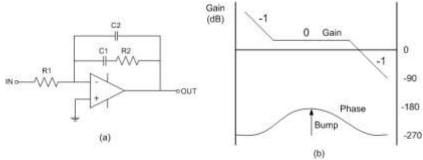

#### 6.2.1 Type 2 Amplifier

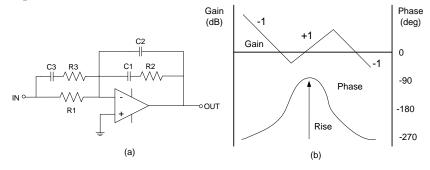

Figure 22 Type 2 Amplifier (a) and Bode Plot (b)

The components and bode plots for a Type 2 Amplifier are displayed in Figure 22 [19]. It is used for controller loops where the converter has a -1 gain margin slope and phase rise is close to  $-90^{\circ}$ . This Type 2 amplifier has a zero-pole pair and a pole located at the origin. The zero-pole pair causes the gain margin to become steady, and exhibits a phase margin rise as shown in Figure 22(b). The rise height is the desired phase rise  $\theta_{rise}$  which can increase up to 90°. After the phase reaches its peak, the gain margin returns to the non-zero gain slope and phase margin slowly returns to the initial phase [3, 19].

Equation 41 gives the Type 2 Amplifier transfer function by Ned Mohan. The Type 2 K factor is calculated using Equation 42 [3, 19]. The pole and zero frequency of the controller transfer function are based on the desired crossover frequency  $f_c$  and the K factor value. This amplifier is suitable for current control systems, and so can be used for designing the peak current compensator [3, 19].

$$G_{control} = \frac{k_{control}}{s} \times \frac{1 + \frac{s}{\omega_{zero}}}{1 + \frac{s}{\omega_{nole}}}$$

Equation 41

$$K = \tan \left( 45^\circ + 0.5\theta_{rise} \right)$$

Equation 42

#### 6.2.2 Type 3 Amplifier

Figure 23 Type 3 Amplifier (a) and Bode Plot (b)

The components and bode plots for a Type 3 Amplifier are displayed in Figure 23 [19]. It is used for a controller loop where the converter has a phase rise below 180°. This Type 3 amplifier has a single pole located at the origin, and two zero-pole pairs. These zero-pole pairs causes the positive gain margin slope with the phase rise, and exhibits a phase rise of 180° as shown in Figure 23(b). After the phase reaches its peak, the gain returns to -1 gain slope and the phase slowly returns to the initial phase. Equations 43 and 44 are for calculating the Type 3 Amplifier transfer function and K factor adapted from Ned Mohan [3, 19].

$$G_{control} = \frac{k_{control}}{s} \times \frac{\left(1 + \frac{s}{\omega_{zero}}\right)^2}{\left(1 + \frac{s}{\omega_{pole}}\right)^2}$$

Equation 43

$$K = \tan \left( 45^\circ + 0.25\theta_{rise} \right)$$

Equation 44

#### 6.3 Voltage mode control in Continuous Conduction Mode

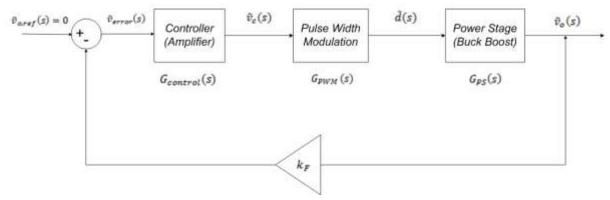

Figure 24 Voltage mode controller block diagram

The voltage mode control is designed to control the output voltage by varying the duty ratio. The small signal block diagram is shown in

Figure 24 [3]. The block diagram consists of the transfer functions which can affect the output voltage: amplifier controller  $G_{control}(s)$ , pulse width modulation  $G_{PWM}(s)$  and the buck-boost power stage model  $G_{PS}(s)$ . There is a sensing network  $k_F$  on the feedback loop which is less than one. The error between the output voltage and reference voltage is given in Equation 45. The value of  $\tilde{v}_{o,ref}$  is zero due to the output voltage regulation [3].

$$\tilde{v}_{error}(s) = \tilde{v}_o(s) - \tilde{v}_{o,ref}(s)$$

Equation 45

The voltage error is used as an input for the controller block, where the small signal control voltage is amplified from the controller transfer function. The pulse width modulation block is produced from the linearisation of UC3824 explained in Chapter 4.1. The small signal duty ratio enters the power stage block, where the output voltage is produced. The open loop transfer function of the voltage mode loop is given in Equation 46.

$$G_{loop}(s) = k_F \times G_{control}(s) \times G_{PWM,f_c}(s) \times G_{PS,f_c}(s)$$

Equation 46

#### 6.3.1 Voltage Mode Controller Design

The compensator design for the voltage mode control is adapted from Luke Morrison's simulation on the buck converter [4].

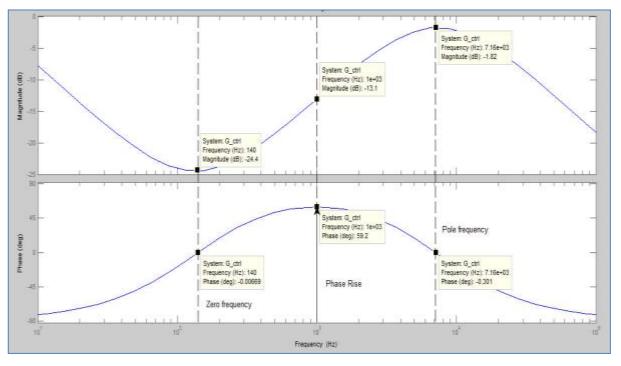

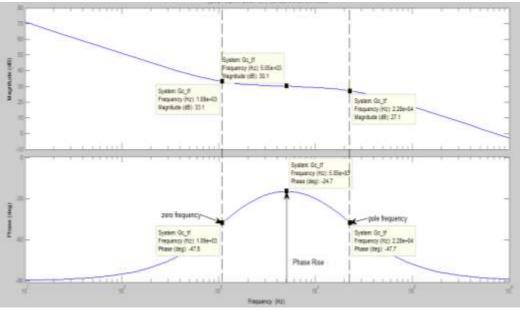

Figure 25 shows the Bode plot of the Type 3 Amplifier used as the controller transfer function. The Bode plot is obtained from the *MATLAB* code in Appendix B-1. Following Ned Mohan's method in

designing the feedback controller for voltage mode control, the desired phase rise is calculated using the equations given below. The feedback path gain is 1 [3].

Figure 25 MATLAB Bode Plot of Type 3 Amplifier Transfer Function

The absolute gain of the closed loop system is equivalent to 1 at the crossover frequency. It requires the multiplication of the other transfer functions as given in Equation 47. While the feedback path and PWM gain values are a constant ( $k_F = 1$ ,  $|G_{PWM,f_c}(s)| = 0.556$ ), the crossover frequency magnitude of the power stage needs to be converted from decibels to absolute value, as given in Equation 48. The absolute controller transfer gain is calculated in Equation 49 [3].

$$\left|G_{loop,f_{c}}(s)\right| = k_{F} \times \left|G_{control,f_{c}}(s)\right| \times \left|G_{PWM,f_{c}}(s)\right| \times \left|G_{PS,f_{c}}(s)\right| = 1 \qquad \text{Equation 47}$$

$$|G_{PS,f_c}(s)| = 10^{\frac{|G_{PS,f_c}(s)|_{dB}}{20}}$$

$$= 10^{\frac{18.2}{20}} = 8.13$$

Equation 48

$$1 \times |G_{control,f_c}(s)| \times 0.556 \times 8.13 = 1$$

$$|G_{control,f_c}(s)| = \frac{1}{0.556 \times 8.13 \times 1} = 0.2214$$

Equation 49

Equation 50 is for calculating the control loop transfer function phase, which is obtained from the power stage and feedback compensator transfer function. The PWM Gain and feedback path are not included because both are constant values. Equation 51 ensures the control loop phase does not go below  $-180^{\circ}$  with respect to the desired phase for loop stability. There is an angle of  $-90^{\circ}$  which is compared with the phase rise for finding the phase angle in the controller transfer function (Equation 52) [3].

$$\angle G_{loop,f_c}(s) = \angle G_{PS,f_c}(s) + \angle G_{control,f_c}(s)$$

Equation 50

$$\angle G_{loop,f_c}(s) = \theta_{PM} - 180^{\circ}$$

Equation 51

$$\angle G_{control,f_c}(s) = \theta_{rise} - 90^{\circ}$$

Equation 52

It is possible to rearrange the equations in terms of the phase rise and calculate the value as given in Equation 53.

$$\angle G_{loop,f_c}(s) = 60^\circ - 180^\circ = -120^\circ$$

$$-120^\circ = \angle G_{PS,f_c}(s) + \theta_{rise} - 90^\circ$$

$$\theta_{rise} = -\angle G_{PS,f_c}(s) + 90^\circ - 120^\circ$$

$$\theta_{rise} = 179.2^{\circ} + 90^{\circ} - 120^{\circ} = 149.2^{\circ}$$

Equation 53

According to H. Dean Venable, the maximum phase rise for the Type 3 Amplifier is  $180^{\circ}$  at the crossover frequency [19]. Since the phase rise for the voltage mode controller is less than  $180^{\circ}$  and above  $90^{\circ}$ , the Type 3 Amplifier is the most suitable compensator for voltage mode control. The maximum phase peak is  $59.2^{\circ}$ , while the phase is  $-90^{\circ}$  for decreasing magnitudes. The controller phase rise is the difference between the two phases, which is  $149.2^{\circ}$ .

The K factor method is used to determine the pole and zero frequencies required to achieve the desired controller phase rise. Using Equation 44 from Section 6.2.2, the K factor value is 7.396 as given in Equation 54. The pole and zero frequencies can be calculated using the crossover frequency and K factor, given in Equations 55 and 56. In the Bode plot, the pole and zero frequencies are the points where the magnitude reaches its peak and the phase angle is near 0°.

$K = \tan (45^{\circ} + 0.25\theta_{rise})$  $= \tan(45^{\circ} + 0.25 \times 149.2^{\circ}) = 7.396$ Equation 54

$$f_{pole} = K \times f_c = 7.396 \times 1000 Hz = 7396 Hz$$

Equation 55

$$f_{zero} = \frac{f_c}{K} = \frac{1000Hz}{7.396} = 135.2 Hz$$

Equation 56

The frequencies calculated from Equations 55 and 56 are converted from Hz to rad/s for calculating Type 3 components (Equations 57 and 58). The Type 3 controller gain is calculated as shown in Equation 59.

$$\omega_{pole} = 2 \times \pi \times f_{pole} = 46471 \, rad/s \qquad \text{Equation 57}$$

$$\omega_{zero} = 2 \times \pi \times f_{zero} = 849.5 \, rad/s \qquad \text{Equation 58}$$

$$k_{control} = |G_{control,f_c}(s)| \times \frac{\omega_{zero}}{K} = 25.43$$

Equation 59

Using the values calculated, it is possible to perform calculations for the Type 3 resistors and capacitors required for the voltage feedback compensator.  $100k\Omega$  is selected as the resistor value for *R*1, while the other component values are calculated through Equation 60 to 64 [3].

$$C2 = \frac{\omega_{zero}}{k_{control} \times \omega_{pole} \times R1}$$

$$=\frac{849.5}{25.43\times46471\times100\times10^3}=7.18nF$$

**Equation 60**

$$C1 = C2 \times \left(\frac{\omega_{pole}}{\omega_{zero}} - 1\right)$$

= 7.18 × 10<sup>-9</sup> ×  $\left(\frac{46471}{849.5} - 1\right)$  = 385.9*nF* Equation 61

$$R2 = \frac{1}{\omega_{zero} \times C1}$$

$$=\frac{1}{849.5 \times 77.2 \times 10^{-9}} = 3.05k\Omega$$

Equation 62

$$R3 = \frac{R1}{\left(\frac{\omega_{pole}}{\omega_{zero}} - 1\right)}$$

$$=\frac{100 \times 10^{3}}{\left(\frac{46471}{849.5} - 1\right)} = 1.86 \ k\Omega$$

Equation 63

$$C3 = \frac{1}{\omega_{pole} \times R3}$$

$$=\frac{1}{46471 \times 1.86 \times 10^3} = 11.6nF$$

**Equation 64**

| Parameter Part | Value           |  |

|----------------|-----------------|--|

| R1             | $100k\Omega$    |  |

| R2             | $3.05k\Omega$   |  |

| R3             | $1.86k\Omega$   |  |

| С1             | 385.9 <i>pF</i> |  |

| <i>C</i> 2     | 7.18nF          |  |

| СЗ             | 11.6 <i>pF</i>  |  |

Table 3 Type 3 Amplifier Parameters for Voltage Mode Control Implementation

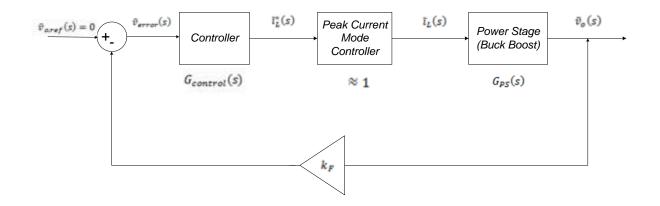

### 6.4 Peak current control in Continuous Conduction Mode

The peak current mode compensator is designed to control the desired output voltage with the inductor current. The current control block diagram is given in Figure 26. Unlike the voltage mode control, the block diagram consists of the outer voltage loop and the inner current control loop. The peak current mode block replaces the PWM block from the voltage mode loop [3, 21].

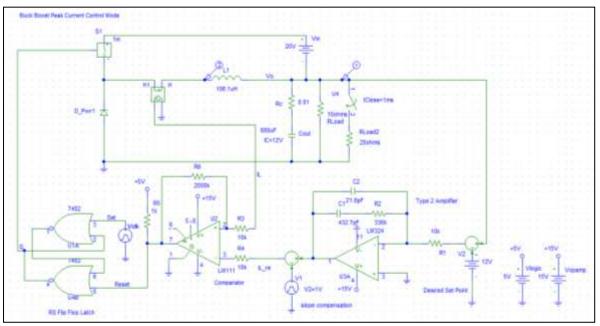

#### Figure 26 Peak current mode controller block diagram

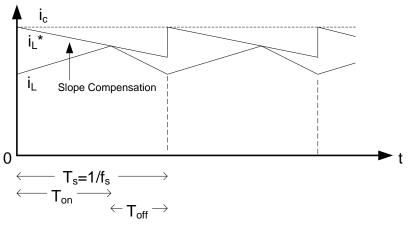

The slope compensation is the most unique feature of the peak current control. In Figure 27, the desired inductor current  $i_L^*$  is compared with the measured inductor current  $i_L$ . Unlike the voltage mode control, the current loop uses the slope compensation to limit the inductor current  $i_L$  and avoid oscillations produced from sub-harmonic frequencies. This is the case for duty ratios larger than 0.5 [3].