### IMPACT OF MATERIALS DISORDER ON GRAPHENE

## **HETEROSTRUCTURE DEVICES**

A Dissertation Presented to The Academic Faculty

By

Corey Alexander Joiner

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Materials Science and Engineering

> Georgia Institute of Technology December, 2016

## **COPYRIGHT © 2016 BY COREY JOINER**

## IMPACT OF MATERIALS DISORDER ON GRAPHENE

### **HETEROSTRUCTURE DEVICES**

Approved by:

| Dr. Eric Vogel, Advisor<br>School of Materials Science<br>Engineering<br>Georgia Institute of Technology | and | Dr. Lin<br>School of Materials Science and<br>Engineering<br>Georgia Institute of Technology |

|----------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------|

| Dr. Vladimir Tsukruk<br>School of Materials Science<br>Engineering<br>Georgia Institute of Technology    | and | Dr. Jiang<br>College of Physics<br>Georgia Institute of Technology                           |

| Dr. Faisal Alamgir<br>School of Material Science<br>Engineering<br>Georgia Institute of Technology       | and |                                                                                              |

Date Approved: August 08, 2016

Dedicated to my wife and family

### ACKNOWLEDGEMENTS

I would like to express my gratitude and appreciation for all of the support and guidance I have received. First, I would like to thank my advisor, Dr. Eric M. Vogel, for being a constant source of guidance and support. I also want to thank Dr. Vladimir V. Tsukruk, Dr. Faisal M. Alamgir, Dr. Zhiqun Lin, and Dr. Jiang Zhigang who devoted their time and energy to serving on my PhD proposal and defense committees. I would like to thank Dean C. Sutter and John Pham for being invaluable resources in the cleanroom.

I would like to thank the previous and current members of the research group for providing insightful conversations and enjoyable moments. Special thanks to Dr. Tania Roy and Dr. Zohreh Razavi Hesabi for helping establish the framework for my studies. I would like to thank Dr. Alexi Tarasov, Philip Campbell, Chris Perini, Brian Beatty, and Meng-Yen Tsai for sharing their expertise, passion, and patience to help me get this far.

I would like to thank my parents for all the support and love over the years. Lastly, I would like to thank my wife, without whose unconditional support I would not be here.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                  | IV    |

|---------------------------------------------------|-------|

| LIST OF TABLES                                    | VIII  |

| LIST OF FIGURES                                   | IX    |

| LIST OF SYMBOLS AND ABBREVIATIONS                 | XVIII |

| SUMMARY                                           | XX    |

| CHAPTER 1: INTRODUCTION                           |       |

| 1.1 Moving Beyond Si                              |       |

| 1.2 Physics of Graphene                           |       |

| 1.3 Graphene Synthesis                            |       |

| 1.3.1 Exfoliation                                 |       |

| 1.3.2 Epitaxial Growth                            |       |

| 1.3.3 Reduced Graphene Oxide                      |       |

| 1.3.4 Chemical Vapor Deposition                   |       |

| 1.4 Current status and limitations                |       |

| 1.4.1 Single Layer Graphene                       |       |

| 1.4.2 Bilayer Graphene                            |       |

| 1.4.3 Vertical Heterostructures for Tunneling Dev |       |

| 1.5 Sources of materials disorder                 |       |

| 1.5.1 Processing Induced Disorder                 |       |

| 1.5.2 Physical Structure Induced Disorder         |       |

| 1.5.3 Disorder at the Interfaces                  |       |

| 1.6 Other applications of graphene                |       |

| 1.6.1 Photodetectors                              |       |

| 1.6.2 Interconnects                               |       |

| 1.6.3 Diffusion Barrier                           |       |

| 1.6.3 Chemical Sensors                            |       |

| CHAPTER 2: GOALS AND ORGANIZATION                 | 40    |

| 2.1 Goals                                         |       |

| 2.1 Obais                                         |       |

|                                                   |       |

| CHAPTER 3: EXPERIMENTAL METHODS                   |       |

| 3.1 Materials Synthesis                           |       |

| 3.1.1 Graphene Synthesis                          |       |

| 3.1.2 Molybdenum Disulfide Synthesis              |       |

| 3.1.3 Hexagonal Boron Nitride Synthesis           |       |

| 3.2 Sample Fabrication                            |       |

| L                                                 |       |

| 3.2.1 Transfer of 2D materials                                           | 55  |

|--------------------------------------------------------------------------|-----|

| 3.2.1.1 Graphene                                                         | 55  |

| $3.2.1.2 \text{ MoS}_2$                                                  | 56  |

| 3.2.1.3 hBN                                                              | 57  |

| 3.2.2 Spin Coating                                                       | 57  |

| 3.2.3 Photolithography                                                   | 58  |

| 3.2.4 Metal Deposition                                                   | 58  |

| 3.2.5 Dielectric Deposition                                              |     |

| 3.3 Characterization                                                     | 59  |

| 3.3.1 Ellipsometry                                                       | 59  |

| 3.3.2 Atomic Force Microscopy (AFM)                                      |     |

| 3.3.3 Scanning Kelvin Probe Microscopy (SKPM)                            |     |

| 3.3.4 Raman Spectroscopy                                                 |     |

| 3.3.5 X-ray Photoelectron Spectroscopy (XPS)                             |     |

| 3.3.6 Electrical Measurements                                            |     |

|                                                                          |     |

| CHAPTER 4: CLEANING GRAPHENE                                             | 63  |

| 4.1 Introduction                                                         | 63  |

| 4.2 Thermal Cleaning                                                     | 63  |

| 4.3 Titanium Cleaning                                                    | 73  |

| 4.4 Conclusion                                                           | 79  |

|                                                                          |     |

| CHAPTER 5: ALD BASED TUNNELING HETEROSTRUCTURES                          |     |

| 5.1 Introduction                                                         |     |

| 5.2 Band Engineering                                                     |     |

| 5.3 Thickness Dependence                                                 |     |

| 5.4 Grain Size Dependence                                                |     |

| 5.5 Conclusion                                                           | 91  |

|                                                                          |     |

| CHAPTER 6: GRAPHENE – MOLYBDENUM DISULFIDE – GRAPHENE<br>HETEROJUNCTIONS | 02  |

| 6.1 Introduction                                                         |     |

|                                                                          |     |

| 6.2 Materials Characterization                                           |     |

| 6.3 Electrical Performance                                               |     |

| 6.4 Conclusion                                                           | 108 |

| CHAPTER 7: HEXAGONAL BORON NITRIDE – GRAPHENE – HEXAGONA                 | 11  |

| BORON NITRIDE – GRAPHENE HETEROJUNCTIONS                                 |     |

| 7.1 Introduction                                                         |     |

| 7.2 Physical Characterization of Materials                               |     |

| 7.3 Graphene on hexagonal boron nitride                                  |     |

| 7.5 Graphene on nexagonal boron murde<br>7.4 Conclusions                 |     |

|                                                                          | 110 |

| CHAPTER 8: FUTURE WORK                                                   | 119 |

|                                                                          |     |

| CHAPTER 9: CONCLUSIONS                                                   | 121 |

| REFERENCES . |  | 124 | ł |

|--------------|--|-----|---|

|--------------|--|-----|---|

## LIST OF TABLES

Page

| Table 1:  | Peak area | a ratios | (referenced | to peak | at 284.8 | eV) f | from t | the XPS | fittings | shown |

|-----------|-----------|----------|-------------|---------|----------|-------|--------|---------|----------|-------|

| in Figure | 25        |          |             |         |          |       |        | •••••   |          | 67    |

### LIST OF FIGURES

Page

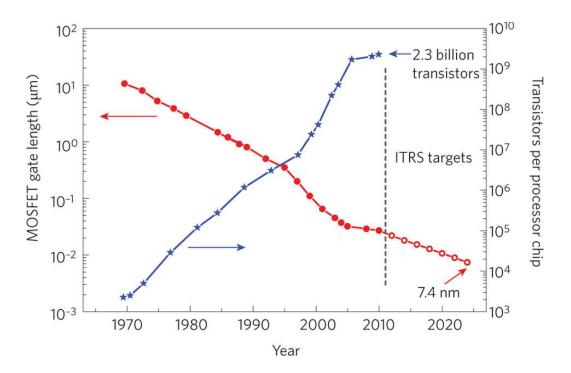

- Figure 1: Evolution of the gate length of commercial MOSFETs (filled red circles) and projected targets (open red circles). As a result of reduced size, the transistor count per chip (blue stars) has increased. Reprinted by permission from Macmillan Publishers Ltd: *Nature Nanotechnology* 5, 487-496 (2010).<sup>[9]</sup>.....2

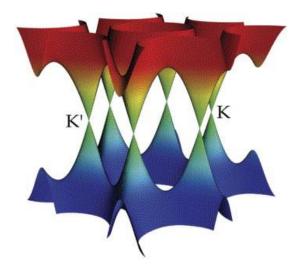

- Figure 5: Graphene Brillouin zone depicting equivalent K and K' positions. Equivalent points are connected by reciprocal lattice vectors......10

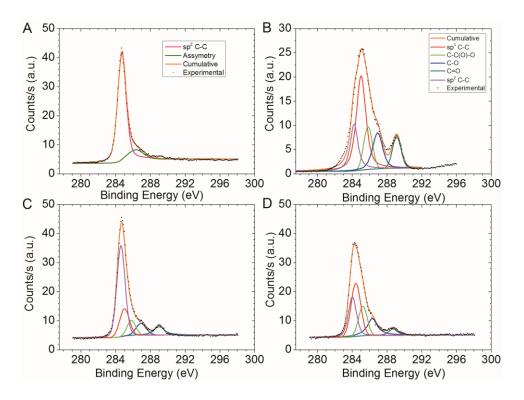

- Figure 6: (A) C 1s XPS spectrum of graphene oxide. (B) C 1s XPS spectra after chemical reduction.Reprinted with permission from G. Sobon, *et al.* Optics Express, 20 (17), 19463-19473 (2012). Copyright (2012) The Optical Society.<sup>[84]</sup>......14

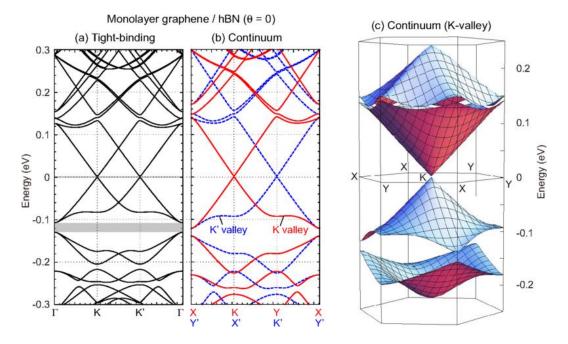

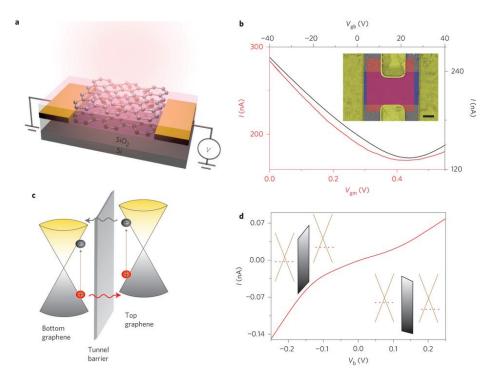

- Figure 22: (A) Schematic of device structure. (B) Black (right and top axes): transfer curve for bottom graphene layer using a silicon back gate ( $V_{gb}$ ). Red (left and bottom axes): transfer curve for top graphene layer using the bottom graphene as the gate  $(V_{\rm gm})$ . From these transport curves, we calculate the Fermi energies of the top and bottom graphene layers to be 4.756 eV and 4.655 eV, respectively. Inset: False-color scanning electron microscopy (SEM) image of the device. The gold areas indicate the metal electrodes and the purple and red areas the bottom and top graphene layers, respectively. Scale bar, 1 µm. (C) Schematic of band diagram and photo excited hot carrier transport under light illumination. Electrons and holes are represented by grey and red spheres, respectively. Vertical arrows represent photoexcitation, and lateral arrows represent tunneling of hot electron (grey) and hole (red). (D) Vertical tunneling current as a function of bias voltage applied across two graphene layers. The bottom layer is grounded, and bias voltage is applied to the top layer. Inset: Schematic band diagrams under forward and reverse bias. Red dashed lines indicate the Fermi levels of the graphene layers. Reprinted by permission from Macmillan Publishers Ltd: Nature Nanotechnology C.H. Liu et al. Volume 9,

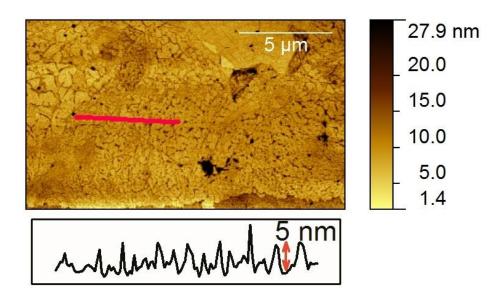

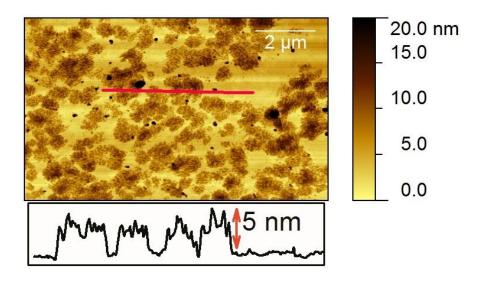

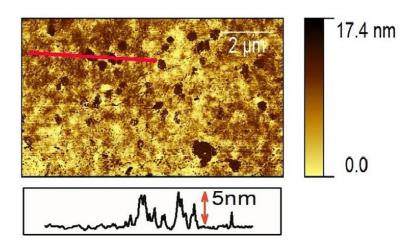

- Figure 26: AFM topology of graphene after processing without any additional cleaning procedures. The height profile is taken from the line scan outlined in red. ....67

Figure 28: AFM topography of graphene after exposure to a forming gas environment at 300°C for 3 hours. The height profile is taken from the line scan shown in red.

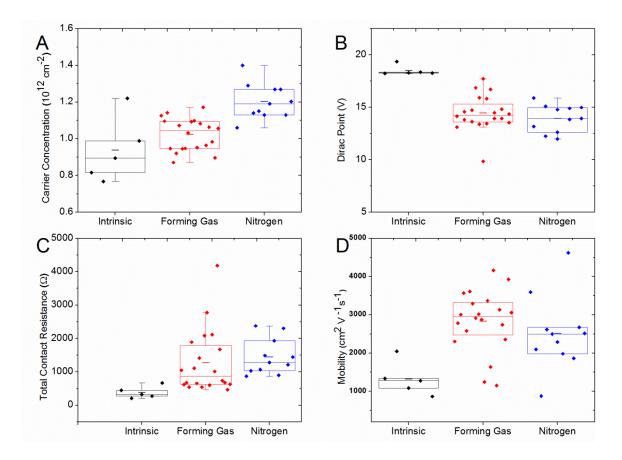

- Figure 30: (A) Induced carrier concentration (n<sub>0</sub>) before and after cleaning. (B) Dirac point of the graphene before and after cleaning. (C) Total contact resistance before and after cleaning. (D) Mobility before and after cleaning.......73

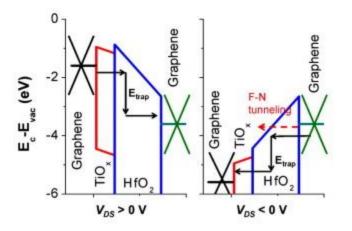

- Figure 36: Energy band diagram of the TiO<sub>x</sub> (1 nm)/Al<sub>2</sub>O<sub>3</sub> (5 nm) tunneling barrier.

Energy loss due to traps is not drawn to scale. Reprinted from Microelectronic Engineering, 109, T. Roy et al, Barrier Engineering for Double Layer CVD Graphene Tunnel FETs, 117-119, Copyright (2013), with permission from Elsevier.

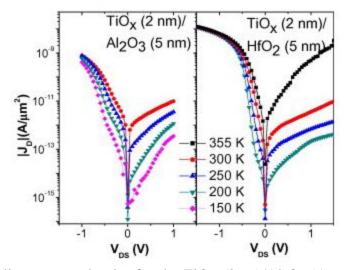

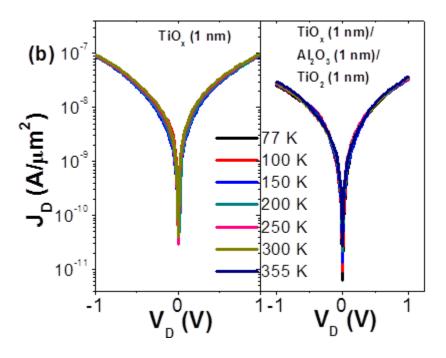

- Figure 39: Tunneling current density for the  $TiO_x$  (1 nm) and  $TiO_x$  (1 nm)/Al<sub>2</sub>O<sub>3</sub> (1 nm)/TiO<sub>2</sub> (1 nm) tunneling barriers. The temperature independent tunneling current indicates direct tunneling is the dominant tunneling mechanism. ......88

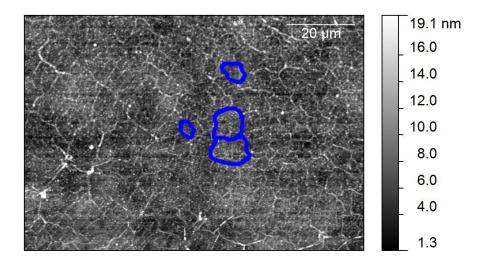

- Figure 40: Atomic force microscopy image after deposition of  $Al_2O_3$  on the graphene grain boundaries. Several graphene domains are outlined in blue as an aid to the eye. The graphene domains are of ~10 µm in size.....90

- Figure 44: (A) The Mo 3d XPS spectra normalized to an empirical sensitivity factor of 2.75. (B) S 2p XPS spectra normalized to an empirical sensitivity factor of 0.54. The high temperature synthesis (High Temp; red) shows increased sulfur content.(C) The C 1s spectra normalized to the C 1s peak height. The C 1s spectrum of the high temperature sulfurization (High Temp; red) shows broadening on the high energy side of the C 1s spectra. (D) Deconvolution of the high temperature synthesis C 1s spectrum corrected with a Shirley background. The spectrum is consistent with a C-C component (red) at 284.7 eV and a C-S component (green) at 285.6 eV.

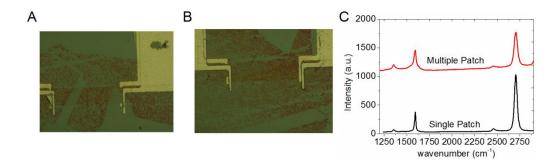

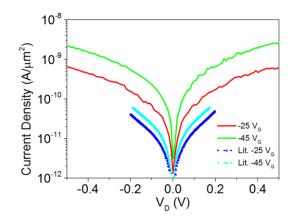

- Figure 51: (A) Transfer curve comparison between a graphene device on a single patch of hBN to a device that straddles three separate patches. (B) Transfer curve comparison between a graphene device on a single patch of hBN to a device that straddles two patches. (C) Mobility of 10 measured graphene on hBN devices compared to graphene on SiO<sub>2</sub>. (D) Mobility comparison between graphene on a single patch of hBN (single patch), graphene straddling two patches (double patch), and graphene straddling three or more patches (multiple patch).

## LIST OF SYMBOLS AND ABBREVIATIONS

| AFM     | Atomic Force Microscopy                                  |

|---------|----------------------------------------------------------|

| ALD     | Atomic Layer Deposition                                  |

| APS     | Ammonium Persulfate                                      |

| BiSFET  | Bilayer Pseudo-Spin Field-Effect Transistor              |

| BTBT    | Band to Band Tunneling                                   |

| CMOS    | Complementary Metal Oxide Semiconductor                  |

| CNP     | Charge Neutral Point or Dirac Point                      |

| CVD     | Chemical Vapor Deposition                                |

| DI      | Deionized Water                                          |

| DOS     | Density of States                                        |

| FET     | Field-Effect Transistor                                  |

| FWHM    | Full Width at Half Maximum                               |

| GFET    | Graphene Field-Effect Transistor                         |

| hBN     | Hexagonal Boron Nitride                                  |

| HOPG    | Highly Oriented Pyrolytic Graphite                       |

| IPA     | Isopropyl Alcohol                                        |

| IR      | Infra-Red                                                |

| MOSFET  | Metal Oxide Semiconductor Field-Effect Transistor        |

| NDR     | Negative Differential Resistance                         |

| NMOSFET | n-type Metal Oxide Semiconductor Field-Effect Transistor |

| РММА    | Poly(methyl methacrylate)                                |

| RF      | Radio Frequency                                          |

| SEM     | Scanning Electron Microscopy                             |

| SKPM   | Scanning Kelvin Probe Microscopy              |

|--------|-----------------------------------------------|

| SymFET | Symmetric (tunneling) Field-Effect Transistor |

| TDMAH  | Tetrakis(dimethylamido) Hafnium               |

| TDMAT  | Tetrakis(dimethylamido) Titanium              |

| TEM    | Transmission Electron Microscopy              |

| TFET   | Tunneling Field-Effect Transistor             |

| ТМА    | Trimethyl Aluminum                            |

| TMD    | Transition Metal Dichalcogenide               |

| XPS    | X-Ray Photoelectron Spectroscopy              |

### SUMMARY

This work is focused on characterizing the impact of material based disorder on the properties of graphene based vertical tunneling heterostructures. The motivation and challenges for replacing silicon for low power digital electronics has been presented. The status of the research on graphene based digital electronics is critically reviewed. Scalable methods for synthesizing large area two dimensional materials including graphene, molybdenum disulfide, and hexagonal boron nitride are integrated into a complex CMOS fabrication process to investigate the impact of disorder on the properties of vertical graphene based heterostructures for low power digital electronics.

The foci for this study were 1) reducing the disorder in the form of contaminants and defect generation in the graphene structure introduced during the CMOS fabrication process 2) elucidating the impact of disorder on vertical tunneling in a graphene based vertical heterostructure 3) investigating the impact of sequential two dimensional material synthesis on the disorder and electrical performance of the fabricated heterostructures. The major findings of this work can be summarized by the following:

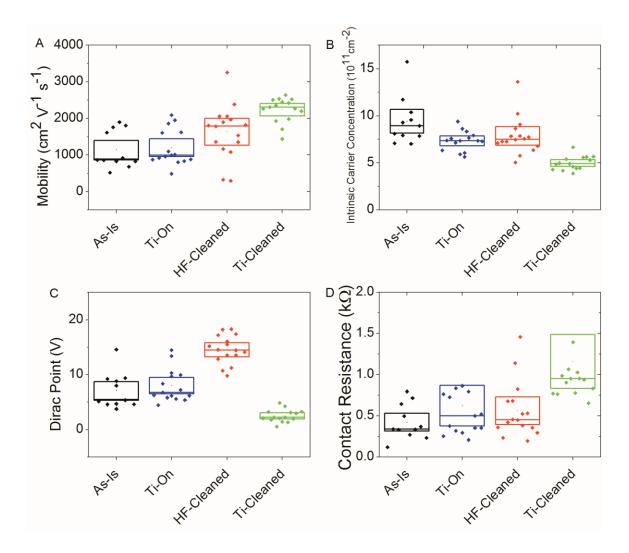

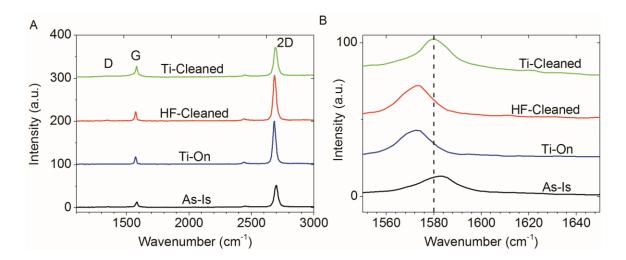

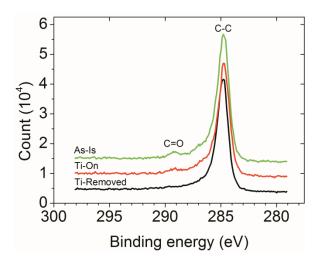

- The CMOS fabrication process was found to introduce contaminants in the form of polymeric residues that reduced the lateral conduction of the graphene. Thermal decomposition of the residues resulted in the introduction of defects in the graphene. A chemical etching method utilizing a sacrificial titanium layer removed via HF etching effectively removed the contaminants without damaging the graphene.

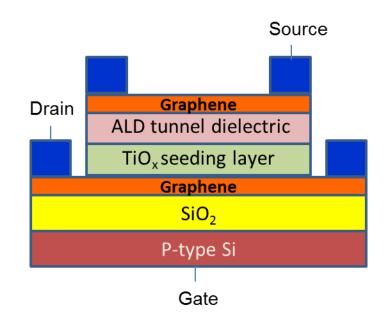

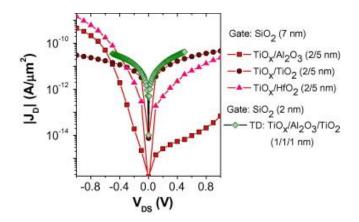

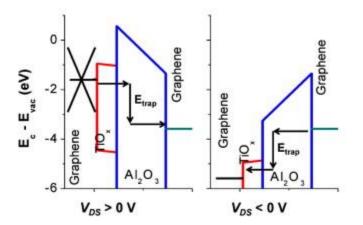

- Dielectric tunneling barriers were deposited by atomic layer deposition (ALD). The tunneling mechanism of the deposited barriers was found to be

defect mediated tunneling which is undesirable for the graphene based heterostructures. By reducing the thickness of the tunneling barriers, direct tunneling became the dominant tunneling mechanism. By altering the tunneling barrier, the possibility of barrier engineering to tailor the electrical characteristics of the graphene heterostructure device was experimentally shown. Despite direct tunneling being the dominant tunneling mechanism for thin dielectric barriers, the electrical properties with ALD deposited dielectrics was found to be inadequate. Graphene of various domain sizes was used to assess the impact of disorder induced by the graphene on the heterostructure electrical properties. No change in the electrical properties was observed indicating the underlying substrate and interlayer dielectric are the limiting sources of disorder suppressing the heterostructure electrical properties.

• Following recent reports utilizing exfoliated materials, two dimensional materials (molybdenum disulfide and hexagonal boron nitride) complimentary to graphene were utilized as tunneling dielectrics to further improve the device performance over conventional dielectric materials. The direct synthesis of complimentary two dimensional materials on graphene was shown to introduce defects into the graphene structure and to suppress the electrical properties of the graphene. Trapping of electrons due to the large number of trap states in the as synthesized molybdenum disulfide was shown to drastically suppress the tunneling current in the graphene vertical heterostructure compared to exfoliated materials.

xxi

• Hexagonal boron nitride was used as a buffer layer between the graphene electrode and underlying SiO<sub>2</sub> substrate to determine the impact of the substrate on the graphene heterostructure performance. A large area synthesized hexagonal boron nitride buffer layer was shown to improve the lateral conduction of the graphene. Contrary to reports of exfoliated materials, the introduction of a hexagonal boron nitride tunneling barrier was shown to reduce the mobility of the graphene due to increased scattering as a result of defects in the hexagonal boron nitride as well as contamination introduced during the transfer process. The lateral conductance of the graphene was shown to be improved in the graphene vertical heterostructure with a hexagonal boron nitride buffer layer, but was insufficient to improve the vertical tunneling of the heterostructure. Improved synthesis methods to reduce the intrinsic defects in the as synthesized hexagonal boron nitride is necessary to further improve the graphene heterostructure performance.

Overall, the research presented here provides important insights into the use of graphene based heterostructures for digital electronic applications. We provided methodology for integrating graphene into a CMOS fabrication process, suggest potential pathways for tailoring the device characteristics through barrier engineering, and demonstrate the current limitations of two dimensional heterostructures. We find the limiting factor to be the materials used in support of graphene.

### **CHAPTER 1: INTRODUCTION**

#### 1.1 Moving Beyond Si

The 1956 Nobel Prize in physics was awarded for the discovery of transistor action in germanium. Discovered in 1948<sup>[1-3]</sup>, the transistor soon began replacing vacuum tubes in a wide variety of applications due to its small size and high reliability of operation. Germanium remained the material of choice for semiconductors until ~1960, when silicon began to dominate as the semiconducting material of choice.<sup>[4]</sup>

Silicon overtook germanium as the material of choice for several main reasons. First, germanium has a band gap of 0.67 eV, diminishing the reliability of germanium based transistors at elevated temperatures. The 1.1 eV bandgap of silicon allows for reliable operation at typical operating temperatures of up to 100°C.<sup>[5]</sup> Second, processing breakthroughs in silicon purification and diffusional doping at Bell Labs in the 1950s drastically improved the yield and ease of fabrication for silicon based transistors.<sup>[4]</sup> Third, silicon oxide forms a high quality interface with silicon with a low concentration of interfacial traps and serves as an excellent electrical insulator.<sup>[6]</sup> Fourth, silicon is extremely abundant in the Earth's surface allowing for cheaper acquisition of the material. Fifth, the development of the integrated circuit in 1960 allowed manufacturing of many interconnected devices on a single surface of silicon paving the way for the modern computer chip.<sup>[7]</sup>

The advent of silicon as the semiconducting material of choice and the integrated circuit gave rise to an ever increasing demand for increased computing power. This demand for more computing power requires manufacturers to continually increase the number of transistors on a single silicon chip. The need to produce silicon chips at lower prices further pushes manufacturers to reduce the size of the transistor, allowing for more transistors per unit area. This drive for reducing the size of the transistor gave rise to what has become known as Moore's Law.

In 1965, a cofounder of Intel, Gordon Moore, observed that in response to this demand the silicon electronics industry doubled the number of devices per chip every 18 months.<sup>[8]</sup> The doubling of devices per chip was managed by scaling devices, increasing the chip size, and ever more inventive chip designs to utilize space more efficiently. Gordon Moore's observation has since become prophetic as the semiconductor industry has maintained this steady pace of innovation for the last 50 years as shown in Figure 1.

**Figure 1** Evolution of the gate length of commercial MOSFETs (filled red circles) and projected targets (open red circles). As a result of reduced size, the transistor count per chip (blue stars) has increased. Reprinted by permission from Macmillan Publishers Ltd: *Nature Nanotechnology* 5, 487-496 (2010).<sup>[9]</sup>

Maintaining Moore's law has not come without challenges. In the 1970's, Moore's law was said to be reaching its end due to the limitations imposed by contact lithography and the wavelength of visible light.<sup>[10]</sup> In response, Perkin-Elmer developed the projection scanner in 1973.<sup>[11]</sup> Rather than relying on direct contact to achieve the patterning, a lens is used to project an image of the pattern. Initial designs projected a 1:1 scale image of the pattern. Five years later with the introduction of the stepper, photolithography was able to be performed on sections of the wafer by projecting a mask image on one area then moving to the next as opposed to the entire wafer at once. The combination of the stepper and projection lithography allowed the semiconductor industry to project mask patterns at much higher resolutions enabling projected patterns to be smaller than the physical mask used to create them. The limitations of using visible light for patterning were overcome in 1982, with the development of photoresists sensitive to ultra-violet light at IBM.<sup>[12]</sup> The development of new photoresists and a switch from mercury lamps to ultra violet excimer lasers allowed the semiconductor industry to continue downscaling.

In the mid 80's, 500 nm was proclaimed the ultimate scaling limit as source/drain resistance increased to non-feasible values. In response, the semiconductor industry developed silicides with the first silicide made out of tungsten reducing the resistivity by an order of magnitude.<sup>[13]</sup> The introduction of silicides marked the first limitation overcome by a change in material used for the transistor. A decade later and 100 nm is proclaimed as the ultimate scaling limit due to reduced mobilities in the silicon with scaling and reduced performance of the aluminum interconnects. This limitation was overcome by the introduction of germanium in the silicon channel and the replacement of

aluminum interconnects with copper.<sup>[14, 15]</sup> The introduction of germanium strains the silicon, increasing the mobility by up to 25% while using copper resulted in a reduction in the resistivity of the interconnect by half.

By 2004 the industry had yet again reached a fundamental limit on the technology used to pattern devices leading to the development of immersion lithography which allows patterning up to an order of magnitude smaller than the wavelength of light used.<sup>[16]</sup> Yet another limitation was reached by 2007 at the 50 nm scale with the inability of the silicon dioxide to prevent gate tunneling at the dimensions needed. In response, Intel announced the use of hafnium oxide as the gate dielectric. The higher dielectric constant of hafnium allows thicker gate dielectrics while maintaining the same electric field in the channel. The thicker gate drastically reduced the gate leakage current allowing the continuation of downscaling of silicon based devices we see today.<sup>[17]</sup>

The semiconductor industry is facing another challenge in the continued downscaling of transistors and adherence to Moore's law. With transistors approaching dimensions of sub 10 nm, short channel effects and gate leakage can no longer be overcome with the material systems in use today.<sup>[18-20]</sup> The continued scaling of devices has resulted in leakage from tunneling currents through the oxide no longer being negligible,<sup>[21-24]</sup> reduced device reliability due to short channel effects,<sup>[25-30]</sup> and a substantial increase in power dissipation.<sup>[31, 32]</sup>

As the MOSFET is scaled to smaller dimensions, the magnitude of the electric field applied between the source and drain approaches the magnitude of the electric field applied at the gate causing short channel effects. This results in the gate no longer controlling the transistor behavior. This is further exacerbated by variability in the device processing. As the device dimensions begin to approach single nanometers in size, a change of 1 nm in the device dimensions can significantly alter the device behavior.

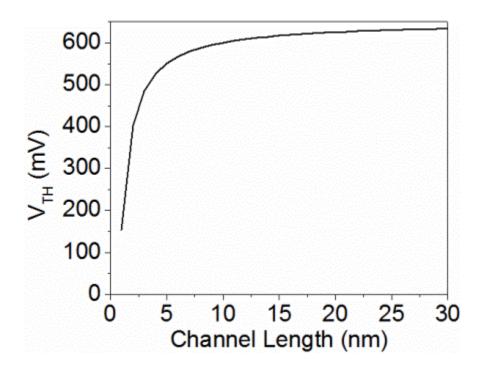

Figure 2 shows threshold voltage as a function of gate length for a NMOSFET with a  $V_T = 0.65$  V, doping concentration of  $1 \times 10^{18}$  cm<sup>-3</sup>, 2 nm oxide thickness, and at 1 µm channel length as the NMOSFET approaches single nanometer channel lengths. The change in threshold voltage is calculated from equation 1.<sup>[33]</sup>

$$V_{Tnew} = V_T - \frac{q_{N_a}W_{dm}r_j}{c_{ox}L} \left(\sqrt{1 + 2\frac{W_{dm}}{r_j}} - 1\right)$$

(1)

Where  $V_{Tnew}$  is the reduced threshold voltage,  $V_T$  is the threshold voltage for an equivalent long channel device, q is the charge of an electron,  $N_a$  is the dopant concentration,  $W_{dm}$  is the depletion width which is a function of  $C_{ox}$  and  $N_a$ , and  $r_j$  is the implantation depth of the source and drain wells (20 nm as shown).

Figure 2 Threshold voltage of a MOSFET as a function of channel length.

Short channel effects currently limit the scalability of the Si MOSFET.<sup>[18, 19, 34]</sup> Short channel effects limit the scalability of the silicon transistor by making the methods used to reduce the impact of short channel effects prohibitively expensive to continue as the device scales.<sup>[19]</sup> These effects arise in the traditional MOSFET from the increasing electric field in the device channel as the device becomes smaller. Traditional methods for combating short channel effects include scaling of the oxide thickness, increasing the substrate donor concentration, and halo implanting.<sup>[18-20, 24, 34-36]</sup> Combating short channel effects becomes more difficult and expensive as scaling continues.

Despite significant efforts, solutions addressing the difficulties of continuing traditional scaling of the MOSFET have not been found. Even if solutions are found to address random dopant fluctuations and reduce device variations in patterning, the subthreshold swing of the traditional MOSFET cannot be scaled below 60 mV/decade at room temperature.<sup>[33, 37]</sup> Alternative methods for achieving a performance increase for digital logic applications are required. Two of the most promising methods currently being developed are high mobility channels and alternative transistor designs.<sup>[38-45]</sup> Graphene is a promising material for both methods of moving past the traditional Si based MOSFET.<sup>[46-50]</sup>

### **1.2 Physics of Graphene**

Graphene is a two-dimensional material comprised of carbon atoms arranged in a honeycomb lattice. Theoretically discussed as early as 1947<sup>[51-53]</sup>, with attempts to isolate a single layer of graphite in the form of ultra-thin graphite carried out as early as 1966<sup>[54]</sup>, graphene is a promising material for future electronic applications. With the isolation of a single atomic layer of graphite using the "scotch tape method" in 2004<sup>[55]</sup>, research into

the unique electrical properties of graphene and its future use in electronics has been researched heavily over the past decade.

Large efforts into graphene growth on the wafer scale have been carried out due to graphene's promise as a material for future electronics due to a number of unique qualities arising from the electronic structure and 2D nature of graphene. These qualities include mobilities as high as 10,000 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> reported on SiO<sub>2</sub><sup>[56]</sup>, mobilities in excess of 200,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for suspended graphene<sup>[57]</sup>, and observations of the quantum hall effect near room temperature<sup>[56, 58]</sup>. Due to the unique properties of graphene, graphene is being researched for applications in a variety of fields including spintronics due to long spin injection lifetimes in graphene<sup>[59]</sup>, gas sensors able to detect single gas molecules<sup>[60]</sup>, nanoribbon interconnects with resistivity comparable to copper<sup>[61]</sup>, ballistic transport devices due to large mean free paths and relativistic charge carriers<sup>[62]</sup>, and RF applications due to the high mobility of graphene resulting in large cutoff frequencies.<sup>[63]</sup>

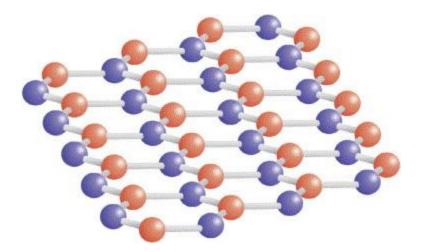

A two-dimensional allotrope of carbon with a bond distance of 1.42 Å, graphene is composed of two trigonal sub lattices, labelled A and B, which results in graphene having two atoms per unit cell, as seen in Figure 3.<sup>[64]</sup>

**Figure 3** Graphene lattice showing the A and B sub lattice (blue and red respectively). Reprinted from Materials Today, Vol 10, M.I. Katsnelson, Graphene: Carbon in Two Dimensions, Pages 20-27, Copyright (2007), with permission from Elsevier.<sup>[64]</sup>

Graphene is comprised of  $sp^2$  hybridized carbon atoms arranged in a hexagonal lattice formed by a  $\sigma$  bond from the hybridization of the  $2s^2$  orbital and the  $2p_x$  and  $2p_y$ orbitals forming the in plane bonds. The out of plane  $2p_z$  orbital is the only orbital involved in conduction within graphene, forming a  $\pi$  band with the neighboring carbon atoms.<sup>[65]</sup> The electronic structure of graphene arising from the hybridization of the orbitals and symmetry of the sub lattices can be described by a tight-binding approximation and gives two points in which band crossing occurs in the Brillouin zone, labelled K and K', around which the dispersion relation is linear, as seen in Figure 4.<sup>[64]</sup>

**Figure 4** Graphene Brillouin zone showing the Dirac points at the K and K' points. The linear dispersion and touching of the valence and conduction band can be seen at the K points. Reprinted from Materials Today, Vol 10, M.I. Katsnelson, Graphene: Carbon in Two Dimensions, Pages 20-27, Copyright (2007), with permission from Elsevier.<sup>[64]</sup>

The dispersion relation is given by

$$E(k) = \pm t \sqrt{3 + h_o(\vec{k})}$$

<sup>(2)</sup>

$$h_o(\vec{k}) = 2\cos(\sqrt{3}k_y a) + 4\cos\left(\frac{\sqrt{3}}{2}k_y a\right)\cos\left(\frac{3}{2}k_x a\right)$$

(3)

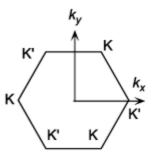

Where t is the nearest neighbor interaction energy and a is the interatomic bond length with magnitudes of 2.9 eV and 1.42 Å respectively. The positive sign in the dispersion relation corresponds to the conduction band and the negative sign corresponds to the valence band.<sup>[64]</sup> Setting  $E(\vec{k})$  to zero in the E(k) dispersion relation results in six points in which the bands coincide on the Brillouin zone (K and K' points). The six points can be sub divided into two sets of three points separated by reciprocal lattice vectors as shown in Figure 5.

**Figure 5** Graphene Brillouin zone depicting equivalent K and K' positions. Equivalent points are connected by reciprocal lattice vectors.

The lattice vectors for these points, also known as the Dirac points, are given by

$$\vec{K} = \left(\frac{2\pi}{3a}, \frac{2\pi}{3\sqrt{3}a}\right) \tag{4}$$

$$\vec{K'} = \left(\frac{2\pi}{3a}, -\frac{2\pi}{3\sqrt{3}a}\right) \tag{5}$$

Around the Dirac points(*within* ~  $\pm$  1 *eV*), the dispersion relation can be represented in a simpler form as given by

$$E = hv_f |\vec{k}| \tag{6}$$

$$v_f = \frac{1}{\hbar} \left( \frac{3at}{2} \right) \tag{7}$$

Where  $v_f$  is the Fermi velocity, a is the atomic spacing of 1.42 Å, t is the nearest neighbor interaction energy of 2.9 eV. The density of states is given by

$$DOS = \frac{E}{2\pi\hbar^2 v_f^2} \tag{8}$$

The linear dispersion relation results in unique properties such as the vanishing of the density of states at the Dirac point and charge carriers behaving as massless Dirac fermions traveling at a Fermi velocity of  $10^6$  m/s.<sup>[66]</sup> The electric field effect can be used to induce charges into the graphene channel as well.<sup>[67]</sup> Depending on the applied field,

the Fermi level can be moved into the conduction or valence band, resulting in an ambipolar graphene channel. Under ideal circumstances, graphene would have a Fermi energy and density of states of zero (E = 0 in the DOS equation). Under real circumstances, graphene exhibits induced charge carriers from the underlying substrate, impurity charges introduced from the atmosphere or device processing, as well as thermally generated carriers. These induced charge carriers present without an electric field effectively result in graphene based devices which are always on. With a typical  $I_{on}/I_{off}$  ratio, the ratio of the measurable current in a device in the on state and off state respectively, of 5-10 (typically orders of magnitude larger for a silicon based transistor), novel device architectures are required for graphene to find an application in digital electronics.

### **1.3 Graphene Synthesis**

### 1.3.1 Exfoliation

The exfoliation of a single layer of graphene was first reported by Novoselov and Geim in 2004<sup>[55]</sup> and resulted in the awarding of the Nobel Prize in 2010. Using what has become known as the scotch tape method, crystals of graphite are repeatedly peeled apart in order to thin the crystal and yield monolayer to few layer graphene. There are several sources of graphite used for the exfoliation method including highly oriented pyrolytic graphite (HOPG), Kish graphite, and natural graphite. HOPG and Kish graphite are synthetically formed graphite with typical domain sizes of ~10µm while naturally occurring graphite can have domains of several millimeters.

A single layer of graphene absorbs 2.3% of incident light. This makes a single layer of graphene unobservable by the naked eye. Exfoliated flakes of graphene are identified

using optical interference and Raman spectroscopy.<sup>[68, 69]</sup> A 300 nm thermal SiO2 has a violet-blue coloration. The addition of a graphene layer introduces interference of the light which shifts the coloration to a true blue. This shifting of color allows the identification of single to few layer graphene based off of the contrast.<sup>[68]</sup> Raman spectroscopy also allows the identification of single to few layer graphene.<sup>[69]</sup>

While easy to produce and yielding exceptional quality graphene, exfoliated flakes are often too small for TEM, XPS, etc. The small size of the flakes and the random distribution disallows large scale fabrication of exfoliated devices.<sup>[70]</sup> Individual patterning of each flake is required which results in a large time commitment for fabricating exfoliated devices. For this reason, exfoliated graphene is commonly used for proof of concept and physics experiments where "perfect" graphene is a necessity. The stochastic nature of the exfoliated flakes makes exfoliated graphene unsuitable for manufacturing purposes.

### **1.3.2** Epitaxial Growth

An alternative method for graphene synthesis is the epitaxial growth of graphene on SiC. First reported in 2004<sup>[71]</sup>, the epitaxial growth of graphene on SiC is formed by sublimating the Si out of 6H-SiC at ~1300 °C.<sup>[72, 73]</sup> An indeterminate number of graphene layers (controlled by time) are formed on the C face of the 6H-SiC while a self-limiting formation of graphene occurs on the Si face. While multiple layers form on the C face, the layers have been reported to be decoupled from each other and behave as individual layers of graphene.<sup>[74, 75]</sup>

Epitaxial growth of graphene results in large single crystalline sheets of graphene. Epitaxial growth of graphene can result in exceptional quality graphene with mobilities greater than 100,000 cm<sup>2</sup>/Vs being reported.<sup>[76]</sup> While epitaxial growth from SiC does allow for large scale synthesis of graphene devices, the use of SiC for graphene growth would require a full paradigm shift in the electronics industry making SiC based graphene economically prohibitive for use in digital electronics.

#### **1.3.3 Reduced Graphene Oxide**

The third common method for producing graphene is reduced graphene oxide. Graphene oxide is an oxidized graphene product capable of being dispersed in an aqueous environment.<sup>[77-79]</sup> This dispersal into an aqueous environment allows graphene oxide to be cast onto a surface at ease by methods such as spin coating. After dispersing the graphene oxide flakes across the surface, the graphene oxide can be reduced to yield a conductive continuous film.<sup>[80-82]</sup>

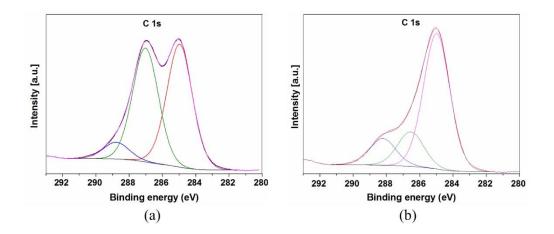

Chemical reduction of graphene oxide is a common means of producing reduced graphene oxide. Hydrazine monohydrate is one of the most common reductants used due to a lack of side reactions with solvents typically used for graphene oxide dispersal.<sup>[83]</sup> The reduction from chemical methods is often incomplete as shown by the C 1s XPS spectra shown in Figure 6 which shows the presence of C-N, C-O, C=O, and C(O)O groups still present after chemical reduction.<sup>[84]</sup> These residual chemical groups attached to the graphene drastically change the electrical performance of the graphene. Currently, no simple pathway exists for the removal of these groups which reduces the usability of chemical reduction for the production of pristine graphene from graphene oxide.

**Figure 6** (A) C 1s XPS spectrum of graphene oxide. (B) C 1s XPS spectra after chemical reduction. Reprinted with permission from G. Sobon, *et al.* Optics Express, 20 (17), 19463-19473 (2012). Copyright (2012) The Optical Society.<sup>[84]</sup>

Thermal reduction is another common method for the reduction of graphene oxide. Graphene oxide heated to 1050 °C will produce carbon oxide species which leave the graphene oxide as carbon dioxide gas.<sup>[85]</sup> The gas generates pressure between the stacked layers aiding in the exfoliation of the layers.<sup>[86]</sup> One result of the thermal reduction of graphene oxide is a high degree of structural damage to the graphene. Up to 30% of the graphene oxide mass is lost during thermal reduction resulting in a porous graphene network.<sup>[87, 88]</sup> The increased defect density results in increased scattering centers and reduced conductivity of the reduced films compared to pristine graphene.

The final commonly used method for the reduction of graphene oxide is electrochemical reduction.<sup>[81]</sup> Graphene oxide is dispersed between two electrodes and linear sweep voltammetry in a buffer solution is used to reduce the film. The resultant films have conductivities comparable to pristine graphene and show negligible defect generation in the graphene films.<sup>[89-91]</sup> While effective at producing high quality graphene films, the reduction of graphene oxide by electrochemical reduction has not been shown

on a large scale. The lack of scalability for the electrochemical method precludes its use for high performance electronics.

### **1.3.4** Chemical Vapor Deposition

The most common method for large scale high quality graphene synthesis is chemical vapor deposition.<sup>[92-94]</sup> In this method, a metallic substrate is heated to ~1050 °C before introducing a carbon source. The s carbon source, in most cases methane, is cracked at the hot metal surface providing a source of activated carbon.<sup>[95]</sup> The growth method of the graphene is dependent upon the metal substrate used. For example, Cu and Ir substrates result in nucleation and growth of graphene while Ni, Co, and Ru substrates result in an absorption and precipitation process.<sup>[95-103]</sup> Cu is the most prevalent choice of substrate as it results in a self-limiting reaction at the surface of the Cu allowing for highly uniform large area monolayers of graphene.<sup>[104-109]</sup>

The transition metal synthesis substrate acts as a catalyst. Either the partially filled dorbitals or the formation of intermediate compounds provide a pathway for the formation of graphene. Co, Ni, and Cu have progressively filled 3d shells suggesting progressively less reactive configurations.<sup>[110]</sup> Co and Ni provide intermediate compounds in the form of metastable carbide phases at high temperature while Cu forms only soft bonds by transferring charge from the  $\pi$  electrons in the sp<sup>2</sup> hybridized carbon to the empty 4s shell of the Cu. In a typical synthesis process,<sup>[111]</sup> Co and Ni result in multilayer graphene formation while Cu is limited to a monolayer of graphene on the surface.<sup>[111-113]</sup>

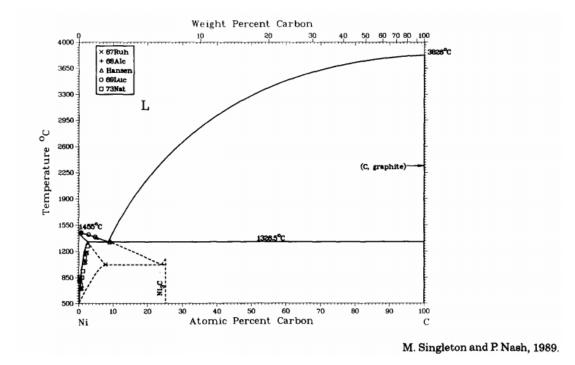

The Ni-C phase diagram is shown in Figure 7. At typical graphene growth temperatures of 800-1000°C, carbon forms a metastable solid solution with Ni. As the temperature decreases, the carbon solubility in the Ni decreases. This results in carbon

segregating out of the metastable Ni<sub>3</sub>C phase to form Ni metal and graphene/graphite.<sup>[114]</sup> The carbon preferentially diffuses at the Ni grain boundaries leading to an increased graphene growth rate. This causes polycrystalline Ni to exhibit a large variance in the number of graphene layers grown across the Ni substrate.<sup>[111, 115]</sup> Control over the number of formed layers can be achieved by using a single crystalline synthesis substrate such that the diffusion rate of the carbon is homogeneous across the entire substrate.<sup>[116]</sup> The large lattice mismatch between graphene and Ni results in polycrystalline graphene formation. For substrates such as Co with a small lattice mismatch with the graphene, the synthesized graphene is in registry with the underlying substrate allowing for single crystalline graphene synthesis.<sup>[117]</sup> The growth process for Co and Fe is similar to the Ni growth process as predicted by the similarities in the metal-carbon phase diagrams.

**Figure 7** Ni-C (graphite) and metastable Ni-Ni<sub>3</sub>C phase diagram. Reproduced from Bulletin of Alloy Phase Diagrams, The C-Ni (Carbon-Nickel) System, volume 10, 1989, pages 121-126, M. Singleton and P. Nash with permission of Springer.<sup>[114]</sup>

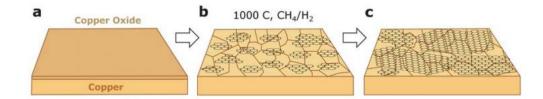

In contrast, the low solubility of carbon in Cu of 0.008% by weight and lack of carbide formation leads to a surface mediated growth of graphene on copper. Typically, methane gas is introduced over a heated copper substrate (~1000°C).<sup>[110, 113]</sup> The carbon precursor cracks upon contact with the catalytic substrate. Carbon diffuses across the surface of the copper and forms graphene islands at high energy sites (Cu grain boundaries, impurity atoms, defect sites, etc.) on the copper surface.<sup>[95, 118, 119]</sup> A schematic representation of the growth process is shown in Figure 8. As additional carbon is added, it either diffuses across the copper surface and attaches to a pre-existing graphene island or forms a new nucleation site and the hydrogen is desorbed. Eventually, the graphene islands coalesce into a single patchwork of graphene domains.<sup>[118-121]</sup> The growth of graphene stops after the Cu surface is completely covered. This results in predominantly single layer graphene (~95%) growth on copper.<sup>[122]</sup> The domain size of graphene on Cu can be controlled primarily by controlling the high energy states on the Cu surface, changing the pressure of the reactor, and changing the temperature of the reactor.

**Figure 8** Schematic illustrating the three main stages of graphene growth on copper by CVD: (A) copper foil with native oxide; (B) the exposure of the copper foil to CH4/H2 atmosphere at 1000 C leading to the nucleation of graphene islands; (C) enlargement of the graphene flakes with different lattice orientations Reproduced from C. Mattevi *et al. J. Mater. Chem.* 21, 3324-3334 (2011) with permission of The Royal Society of Chemistry.<sup>[110]</sup>

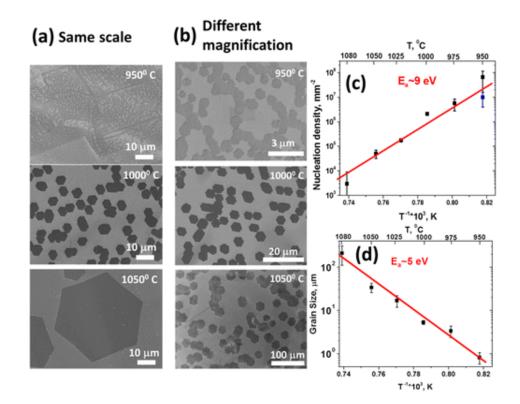

The system background pressure and temperature play a critical role in determining the domain size of the synthesized graphene on copper.<sup>[112, 113, 123]</sup> The synthesis temperature and pressure impact the copper catalyst annealing, carbon diffusion on the copper surface, formation of stable graphene nuclei, and the graphene crystal growth. Figure 9 shows the impact of temperature on the graphene nucleation density/domain size at atmospheric pressure. As seen, the nucleation density is strongly influenced by the synthesis temperature. The nucleation density of graphene changes by 5 orders of magnitude across a temperature span of 130°C corresponding to an activation energy of ~ -9eV as shown in Figure 9C. The dependence of the graphene domain size on temperature is shown in Figure 9D. The activation energy for graphene crystal growth is found to be ~5 eV.<sup>[123]</sup>

**Figure 9** Temperature dependence of the nucleation density and graphene domain sizes for atmospheric pressure CVD:  $P_{H2}/P_{CH4} = 1800$  (A) SEM images of graphene grains grown at different temperatures for constant partial pressures of H<sub>2</sub> (19 Torr) and CH<sub>4</sub> (10.5 mTorr). (B) Same as in A at different magnification. (C) Arrhenius plot for the nucleation density. Blue point shows nucleation density at 950°C for sample annealed at 1080°C. (D) Arrhenius plot for the grain size. Reprinted with permission from I. Vlassiouk *et al. The Journal of Physical Chemistry C.* 117, 18919-18926 (2013). Copyright (2013) American Chemical Society.<sup>[123]</sup>

Similar temperature trends are seen for low pressure (less than 500 mTorr) CVD synthesis of graphene. A strong temperature dependence with an activation energy of ~ -4 eV is found for low pressure CVD.<sup>[123]</sup> The nucleation density and grain size is found to be strongly dependent on the methane partial pressure. The graphene nucleation process is dependent on gas precursor adsorption, dehydrogenation of the carbon, diffusion of carbon on the surface, and formation of graphene nuclei which is in competition with the carbon desorption process.<sup>[110, 112, 123]</sup>

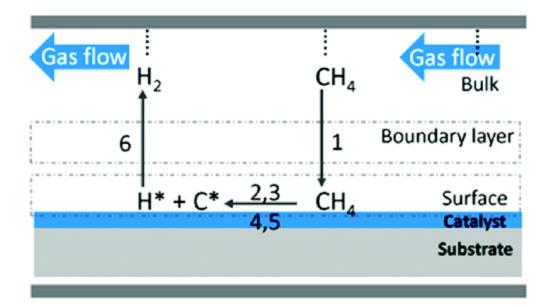

**Figure 10** Schematic representation of the graphene synthesis process on Cu. Reprinted with permission from S. Bhaviripudi *et al. Nano Letters*. 10, 4128-4133 (2010) Copyright (2010) American Chemical Society.<sup>[112]</sup>

As shown in Figure 10, the gas flow in a graphene CVD process creates a boundary layer above the surface of the catalytic substrate. The carbon precursor introduced in the main gas flow must diffuse across the boundary layer, attach to the surface of the copper, diffuse across the surface of the copper, and attach/form a graphene nucleation site.<sup>[110, 112, 123, 124]</sup> After the activated carbon attaches to the graphene lattice, the hydrogen must desorb from the surface and diffuse back through the boundary layer. Hydrogen which does not diffuse back across the boundary layer (or diffuses to the substrate surface again) can react with carbon species on the surface to reform Volatile  $C_xH_y$  gas species. This synthesis process of graphene can ultimately be controlled by (i) the flux across the boundary layer or (ii) the flux across the surface of the catalytic substrate. The equations describing these fluxes are shown in equation 9 and 10.<sup>[112]</sup>

$$F_{ms} = \frac{D_g}{\delta} \left( C_g - C_s \right) \tag{9}$$

$$F_{sr} = K_s C_s \tag{10}$$

Where  $F_{ms}$  is the flux across the boundary layer,  $F_{sr}$  is the flux at the substrate surface,  $D_g$  is the gas diffusion coefficient,  $\delta$  is the thickness of the boundary layer,  $K_s$  is the surface reaction constant,  $C_g$  is the concentration of the carbon source in the gas flow, and  $C_s$  is the concentration of active carbon at the substrate surface. At steady state, the mass transport across the boundary layer is equal to the consumption of active carbon at the substrate surface. Setting equation 9 equal to equation 10 and eliminating  $C_s$  gives equation 11 where  $F_{tot}$  is the steady state total flux.

$$F_{tot} = \left[\frac{K_s D_g}{\delta \left(K_s + \frac{D_g}{\delta}\right)}\right] C_g \tag{11}$$

From this equation it can be seen that there are three possible synthesis regimes for graphene. The first regime,  $D_g/\delta >> K_s$  results in a surface controlled reaction.<sup>[110, 112, 113, 123, 125]</sup> When  $D_g/\delta << K_s$ , mass transport through the boundary layer is limiting and multiple graphene layers can form.<sup>[126, 127]</sup> When  $D_g/\delta << K_s$  a mixed regime occurs. For typically graphene synthesis at atmospheric,  $D_g/\delta << K_s$  resulting in a mass transport limited synthesis process. In this regime, the geometric effects of the gas flow and chamber design strongly influence the graphene synthesis process.<sup>[112]</sup> A variation in the thickness of the boundary layer results in a reduction in the active carbon species concentration at the surface. As gas transport through the boundary layer is more difficult in this regime, it is also more difficult for hydrogen species to leave the substrate surface after carbon adsorption. The hydrogen concentration at the substrate surface will reattach to the carbon species effectively etching the formed graphene. The reduced concentration of active carbon and increased hydrogen etching result in a smaller critical nuclei size.

This results in an increase in nucleation density and reduction in grain size for graphene growth at atmospheric pressure.

Early reports of graphene on copper showed reduced electrical performance compared to exfoliated graphene.<sup>[95, 119, 128]</sup> The reduced electrical performance was due to smaller domain sizes, wrinkles, contamination, etc. More recent reports of graphene growth show that the domain size can be controlled by controlling the nucleation density on the copper foil.<sup>[104-106, 129]</sup> Step edges created in the copper rolling process, contamination, and defect sites provide high energy sites for the nucleation of graphene. By treating the copper foil in acetic acid prior to growth, step edges can be reduced and surface contaminants removed. Introducing hydrogen annealing of the copper foil prior to growth removes step edges and defects by restructuring the surface of the copper foil. Introducing oxygen prior to the growth binds oxygen to the defect sites and reduces the nucleation density of the graphene. By incorporating these various methods, high quality graphene of variable grain size can be synthesized.<sup>[104-106]</sup>

Low pressure CVD growth of graphene on copper foils is the growth method used for the synthesis of graphene used in this study. A complex processing and integration scheme utilizing standard CMOS processes is used in fabricating the graphene based devices and only large-area synthesized materials are used.

# **1.4 Current status and limitations**

### **1.4.1** Single Layer Graphene

Significant efforts have been made in creating FETs to replace Si utilizing single layer graphene. Research efforts into graphene FETs has been motivated by the scalability of graphene to nanometer sizes, potential for ballistic transport, linear current-voltage characteristics, and high current densities.<sup>[55]</sup>

In order to be a viable replacement for the Si MOSFET in digital electronics, future replacement technologies need to offer switching ratios between  $10^4$  and  $10^7$ , n- and p-channel FETs with symmetrical threshold voltages, and low static power dissipation.<sup>[9, 18, 130, 131]</sup> Graphene is a gapless semimetal which means devices with channels made of graphene cannot be turned off. The switching ratio of a single layer graphene transistor is ~10.<sup>[46, 119, 128, 132-134]</sup> This is well below the minimum switching ratio of  $10^4$  needed to compete with Si based MOSFETs.

Significant efforts have been made to introduce a bandgap into graphene in order to increase the switching ratio. These efforts can be classified into three categories: (i) graphene nanoribbons <sup>[135, 136]</sup> (ii) functionalization <sup>[137-140]</sup> (iii) strain engineering.<sup>[141-145]</sup> The most promising method is currently the fabrication of graphene nanoribbons.

As a graphene channel is reduced to widths below 20 nm, a bandgap greater than 200 meV is formed that is inversely proportional to the width of the ribbon. Nanoribbons with widths down to 2 nm have been reported with a switching ratio of 10<sup>6</sup>.<sup>[146, 147]</sup> While promising, real devices will have some degree of rough edges and widths which will cause the bandgap to change along the length of the device.<sup>[148]</sup> The edge roughness further impacts the variability in graphene nanoribbons as graphene nanoribbons of similar design but slightly different edge states can have significant differences in electronic behavior.<sup>[9, 149]</sup>

In order for graphene single layers to be a viable replacement for Si, very narrow nanoribbons with atomically smooth edges will be needed. Reducing the edge roughness

of the graphene nanoribbon will be a significant challenge for modern semiconductor fabrication processes. A perfect edge state of the graphene nanoribbon may not work either. The valence and conduction band of the graphene becomes more parabolic as the bandgap increases. The effective mass of the carriers increases as the bands become more parabolic and the mobility is reduced. By opening a bandgap in the graphene, the material properties that make graphene promising (ultra-high mobility and massless carriers) begin to diminish or disappear. If a bandgap of 1.1 eV similar to Si were introduced into graphene, the graphene mobility would be lower than the mobility of Si.<sup>[150]</sup> While the scalability of graphene nanoribbons has been shown to be superior to traditional MOSFETs, it has not be determined if the improved scalability will offset the reduced mobilities of the graphene nanoribbon.

## **1.4.2 Bilayer Graphene**

A bandgap can be introduced by application of an electric field when two graphene layers have a Bernal stacking arrangement.<sup>[151]</sup> In the Bernal stacking arrangement, the second graphene layer is offset from the first layer such that half of the carbon atoms are located above the atoms of the first layer and the other half lie in the center of the hexagon of the first layer.<sup>[152]</sup> The electrostatic control of a bilayer graphene FET has been reported. By using a dual gated structure, the Fermi level can be controlled electrostatically and a non-zero bandgap can be opened.<sup>[153]</sup>

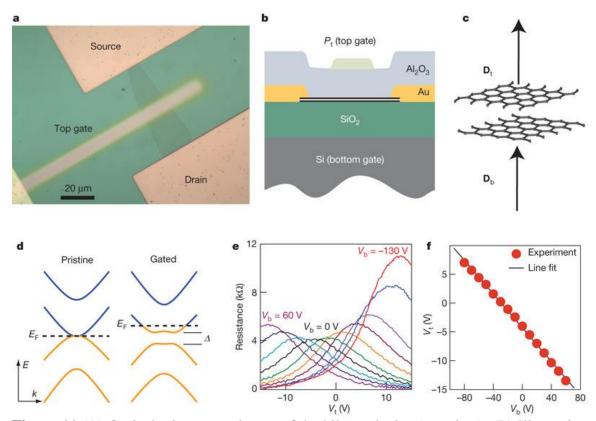

Bilayer graphene in its natural state is a gapless semiconductor as seen in Figure 11D. By using a dual gated structure as shown in Figure 10A-B, two electrostatic effects can be induced which are dependent on the two induced electric fields shown in Figure 10C. The difference between the top and bottom electrical displacement fields leads to a shifting of the Fermi energy. The average of the two fields breaks the inversion symmetry and opens a bandgap as shown in Figure 11D. By applying voltages to the top and bottom gate such that the net difference in the fields is 0, the bandgap of the bilayer graphene FET can be varied up to 250 meV without changing the Fermi level of the graphene.<sup>[153]</sup>

**Figure 11** (A) Optical microscopy image of the bilayer device (top view). (B) Illustration of a cross-sectional side view of the gated device. (C) Sketch showing how gating of the bilayer induces top (Dt) and bottom (Db) electrical displacement fields. (D) Left, the electronic structure of a pristine bilayer has zero bandgap. (k denotes the wave vector.) Right, upon gating, the displacement fields induce a non-zero bandgap  $\Delta$  and a shift of the Fermi energy EF. (E) Graphene electrical resistance as a function of top gate voltage Vt at different fixed bottom gate voltages Vb. The traces are taken with 20 V steps in Vb from 60 V to -100 V and at Vb = -130 V. The resistance peak in each curve corresponds to the CNP ( $\delta D = 0$ ) for a given Vb. (F) The linear relation between top and bottom gate voltages that results in bilayer CNPs. Reprinted by permission from Macmillan Publishers Ltd: Y.Zhang *et al. Nature.* 459, 820-823 (2009) copyright (2009).<sup>[153]</sup>

The report for the dual gated control of the bilayer graphene bandgap was reported in 2009. Since then, no significant advancements have been made. The largest switching ratios achieved for bilayer FETs are only ~100, much lower than the 10<sup>4</sup> minimum of conventional MOSFETs. This limits the viability of bilayer graphene for digital logic applications. Furthermore, bilayer graphene structures have been predominantly fabricated from exfoliated graphene. While some reports of Bernal stacked graphene have been reported by CVD growth, a reliable scalable synthesis method for Bernal stacked graphene remains elusive.<sup>[154, 155]</sup>

# **1.4.3** Vertical Heterostructures for Tunneling Devices

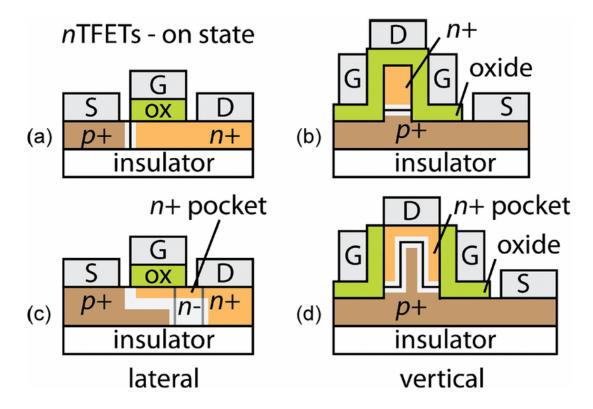

One subset of graphene devices proposed for digital logic applications are the tunneling field effect transistors (TFETs). TFETs can either be fabricated in a lateral planar geometry as in a traditional MOSFET or in a vertically stacked structure as shown in Figure 12.<sup>[156]</sup> Previous reports of lateral TFETs have shown to be incapable of providing large enough on currents.<sup>[157, 158]</sup> The current in a TFET is proportional to the active tunneling area in the device. For a scaled lateral TFET, the cross sectional area of the device limits the maximum current. As the length of the active area is larger than the thickness, a vertical geometry provides a relatively larger tunneling current compared to a lateral geometry due to the increased tunneling area.<sup>[159]</sup> Graphene based vertical TFETs incorporate a graphene/insulator/graphene junction where a potential is applied across the insulating layer to the other graphene sheet. Due to the electronic structure of graphene, the TFETs using graphene layers as the source of the charge carriers can exhibit unique

electronic characteristics. Several vertical tunneling based devices have been proposed to take advantage of the electronic structure of graphene.

**Figure 12** Two approaches for n TFETs. The upper row shows (A) single-gate lateral and (B) double-gate vertical structures in which the gate field originates from the surface, perpendicular to the orientation of the tunnel junction internal field. The lower row n TFETs have an n+ pocket under the gate in a (C) lateral and (D) vertical geometry. The pocket acts to increase the area of the tunnel junction and aligns the tunnel junction internal field with the gate field to lower the subthreshold swing. Copyright (2010) IEEE. Reprinted, with permission, from A.C. Seabaugh, Q. Zhang, Low-Voltage Tunnel Transistors for Beyond CMOS Logic, Proceedings of the IEEE, Dec. 2010.<sup>[156]</sup>

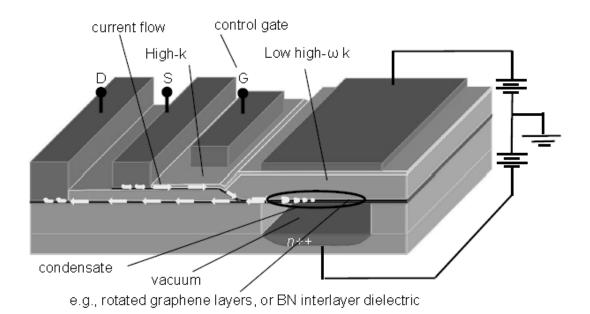

One such device proposed is the bilayer pseudospin field effect transistor (BiSFET) shown in Figure 13.

**Figure 13** BisFET structure. Decoupled graphene layers oppositely doped (n and p type) by the source and drain contacts can generate a Bose-Einstein condensate when close enough and properly biased. Reproduced with permission from *ECS Transactions*, **45**, (4) 3-14 (2012). Copyright 2012, The Electrochemical Society<sup>[160]</sup>

The BiSFET is based off of the formation of a Bose-Einstein condensate, a state of matter predicted by Einstein and Bose in which the wave functions of all particles in the system (behaving as bosons) collapse into a single quantum state with overlapping wave functions.<sup>[160]</sup> The Bose-Einstein condensate has been experimentally shown to exist in other systems in temperatures ranging from  $\mu$ K to nK.<sup>[161, 162]</sup> In graphene, the Bose-Einstein condensate has been theoretically predicted in temperatures approaching 300K.<sup>[163]</sup> The BiSFET is made from two independently contacted graphene monolayers separated by a thin dielectric. The top and bottom gates allow for one graphene sheet to be n type doped while the other is p type doped. By applying an external field via the control gate, the opposite charge carriers in the two graphene sheets can form a condensate, greatly reducing the tunneling resistance between the two layers. This results

in a switch like behavior in which all of the charge carriers in the graphene sheets can be moved from one sheet to the other with the application of an external field.<sup>[163]</sup>

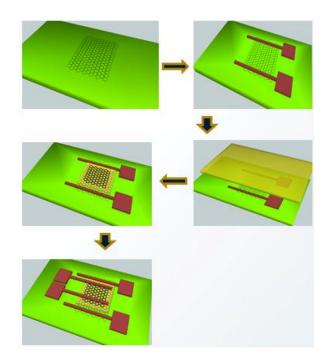

**Figure 14** Process flow and final device structure for the fabrication of the SymFET architecture. First a graphene monolayer is transferred to the substrate of choice and patterned. Metal contacts for the first layer are deposited followed by the deposition of the tunneling barrier. The second graphene layer is deposited, patterned, and independently contacted.

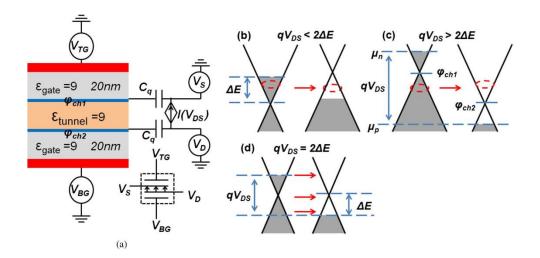

Another proposed device for digital logic application is the SymFET shown in Figure 14 and 15A. The SymFET is a tunneling field effect transistor utilizing single-particle direct tunneling as a means for operation.<sup>[50]</sup> Using two independently contacted graphene layers separated by a dielectric, one graphene layer can be n type doped while the other is p type doped. The tunneling current between the two graphene sheets can be modulated using an external electrical field. Due to the linear dispersion relation in graphene, when the Dirac point of the graphene layers is not aligned, only a small number of carriers

satisfy momentum conservation and can tunnel from one sheet to the next. Shown in figure 6b-d, there is a large peak in the current resulting in negative differential resistance in the SymFET structure when the Dirac points of the two graphene sheets align allowing for a large number of carriers to satisfy momentum conservation and tunnel through the tunneling barrier.<sup>[164]</sup>

**Figure 15** (A) SymFET device architecture and operation. Two graphene sheets (blue) separated by an interlayer dielectric with a potential placed between the sheets. The dopant level of the sheets is modulated by their respective gates and the potential between the sheets aligns the Dirac point. (B) When the potential applied is less than the energy difference between the graphene Fermi levels, only a small number of carriers can conserve momentum and tunnel through the barrier. (C) When the potential applied is greater than the energy difference. Only a small number of carriers can satisfy momentum conservation. (D) When the potential equals the energy difference every carrier in the energy states between the Fermi levels of the two graphene sheets can obey momentum conservation and tunnel through the barrier. Copyright (2013) IEEE. Reprinted, with permission, from P. Zhao, R.M. Feenstra, G. Gu, D. Jena, SymFET: A Proposed Symmetric Graphene Tunneling Field-Effect Transistor, IEEE Transactions on Electron Devices, March . 2013.<sup>[50]</sup>

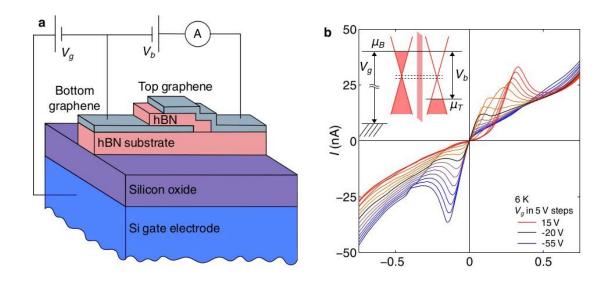

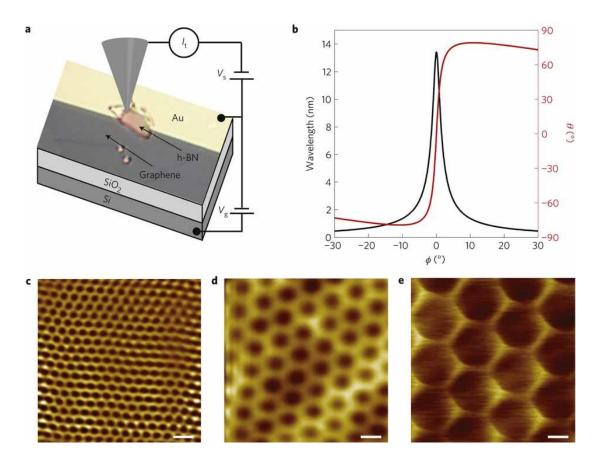

This negative differential resistance (NDR) and device operation has been experimentally shown using exfoliated graphene sheets separated by a hexagonal boron nitride (hBN) layer as seen in Figure 16A and 16B.<sup>[165]</sup>

**Figure 16** (A) Device structure exhibiting negative differential resistance. Two independently contacted graphene sheets separated by an hBN tunneling barrier. The substrate acts as a gate to modulate the Fermi level of the bottom graphene sheet. (B) Id-Vd curve at various back gate voltages showing the NDR of these devices. NDR was shown at temperatures of 6K to 300K. Reproduced with permission from L. Britnell *et al. Nature Communications.* 4, 1794 (2013). <sup>[165]</sup>

The presence of NDR using exfoliated graphene and hBN serves as a proof of concept for the device architecture. Future work will need to be done utilizing scalable processes such as CVD grown graphene/hBN.

One common trait between the two presented structures for digital logic is their reliance on well-ordered materials. For both the BiSFET and SymFET, the device operation is greatly influenced by the presence of disorder in the system. In the case of the BiSFET, disorder quenches the formation of the Bose-Einstein condensate.<sup>[166]</sup> In the

case of the SymFET, disorder can result in reduced tunneling currents and an unobservable negative differential resistance.<sup>[50]</sup> For both structures, disorder can arise from the materials used in the system.

## 1.5 Sources of materials disorder

# 1.5.1 Processing Induced Disorder

The most obvious source of disorder in the graphene films arises from the processing of the graphene films to be used in these devices. During the processing of devices, graphene is typically exposed to a variety of chemicals which have been shown to be difficult to remove, such as poly (methyl methacrylate) (PMMA) and the photoresists used in standard photolithography processes.<sup>[167-169]</sup> A wide variety of techniques have been developed for removal of these residues with varying degrees of success. The most common method used in the removal of residues is thermal decomposition of the contaminants.<sup>[132, 170, 171]</sup> Thermal decomposition has been studied in ultra-high vacuum, atmospheric conditions, forming gas conditions, and under an inert atmosphere. Atmospheric, forming gas, and inert atmosphere conditions have been shown to be ineffective at completely removing residues from the graphene channel while ultra-high vacuum annealing has been shown to return graphene to its intrinsic state.[132, 172] Recently, concerns on the effects of thermal decomposition have been raised. Reports of thermal decomposition resulting in a closer bond between graphene and the underlying substrate have been presented.<sup>[172, 173]</sup> The shortened bond distance results in increased phonon scattering from the underlying substrate, resulting in more disorder introduced into the system. Further concerns with thermal decomposition involve scission of the polymers used during processing and the reactivity of the radicals formed from polymer scission reacting with the defect sites of the graphene.<sup>[172, 173]</sup>

Electric current annealing of fabricated devices is another common method of residue removal. Effective at the individual device level, electric current annealing is inadequate for wafer scale cleaning.<sup>[174]</sup> While systematic studies of these cleaning methods as they effect individual graphene layers has been performed, little information is available to describe how these cleaning methods impact the remainder of the device architecture. Alternative cleaning methods that do not degrade the graphene performance are required.

## 1.5.2 Physical Structure Induced Disorder

Another source of disorder arising from the graphene grown utilizing CVD processes are the grain boundaries formed due to the nucleation and growth process of the graphene domains.<sup>[92, 95, 122, 128, 175, 176]</sup> Transport across the grain boundaries is slightly reduced within the graphene layer.<sup>[177-181]</sup> The varying size of the graphene domains also has an additional effect beyond the introduction of the grain boundaries themselves. For two polycrystalline sheets of graphene, there will be a random distribution of orientations between the two layers for operation in the SymFET and BiSFET. This random distribution of orientations will result in varying degrees of interaction between the two layers for the BiSFET and will result in greater dispersion in the negative differential peak position of the SymFET as well as reduce the overall tunneling current of the device.<sup>[160]</sup>

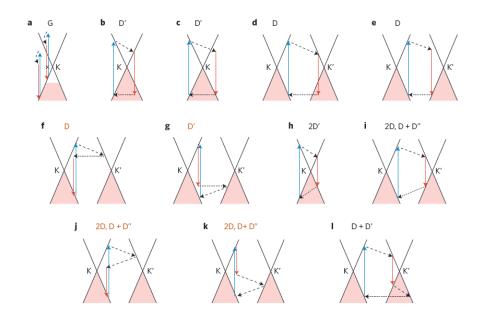

A wafer scale method for the mapping of the orientation on a wafer scale has been proposed in which Raman spectroscopy is used in the determination of the orientation between layers.<sup>[182]</sup> Raman spectroscopy is a technique in which a photon is absorbed by the specimen of interest, promoting an electron.<sup>[69]</sup> The electron can then undergo a variety of pathways to relax back into the unexcited state, emitting a photon in the process. The energy of the emitted photon is dependent on the relaxation pathway followed, which is in turn dependent on the electronic structure being probed. By measuring the energy of the emitted photon, detailed information pertaining to the electronic structure of the specimen can be derived. In the case of graphene, three dominant phonon modes are typically used for characterization. The first of these phonon modes is the D peak. The D peak can be a double resonance or single resonance process, where the resonance refers to the number of phonon interactions in the pathway. Another aspect of the D peak is the requirement of a defect in order for the transition to occur. In intrinsic graphene, the D peak occurs at ~1350 cm<sup>-1</sup>.<sup>[69, 183, 184]</sup> The second peak in the graphene Raman spectrum is the G peak. The G peak is a single resonance process and results from the excitation and relaxation of an electron in which only a single point in K-space is involved. The G peak occurs at ~1580 cm<sup>-1</sup>.<sup>[69, 183, 184]</sup> The Third peak in the graphene Raman spectrum is the 2D peak. The 2D peak is a double resonance process in which two opposite wave vectors are involved. The 2D peak is the overtone of the D peak, but due to the involvement of two opposite wave vectors, no defects are required for the presence of the 2D peak. The 2D peak occurs at ~2700 cm<sup>-1</sup>.<sup>[69, 183, 184]</sup> A schematic of the relaxation pathways associated with each Raman peak can be seen in Figure 17.

**Figure 17** Raman modes of graphene. The prominent peaks in graphene are the G, D, and 2D peaks generated by Raman modes a, d, e, f, i, j, k, and l. Gold labels represent minimal contributions to the Raman signal. The D', 2D', and D'' peaks are low intensity Raman peaks which are not typically used in characterizing graphene via Raman spectroscopy. Reprinted by permission from Macmillan Publishers Ltd: Nature Nanotechnology Vol 8, Issue 4, Pages 235-246, copyright (2013).<sup>[183]</sup>

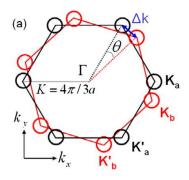

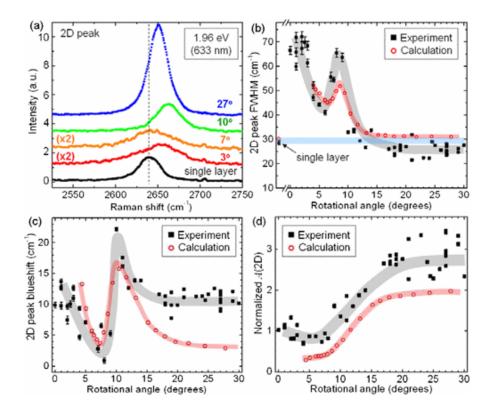

A detailed analysis of the 2D peak position, Full width half max (FWHM), and relative intensity to a single layer of graphene can be used to determine the distribution of orientations, Figure 18 depicts a "misoriented" bilayer within graphene devices.

**Figure 18** Two graphene sheets depicted by their Brillouin zones. An oriented graphene layer would fall directly on top of the previous layer. The misorientation angle as measured by Raman is the rotation of the Dirac points from the center position. Reprinted with permission K. Kim *et al*, Physical Review Letters, Volume 108, 246103 (2012). Copyright (2012) by the American Physical Society.<sup>[182]</sup>

As can be seen in Figure 19D, the area of the 2D peak for a graphene bilayer can be compared to the 2D peak area of a single layer allowing for orientations between 10 and 20 degrees to be mapped. The 2D area can also be used to determine an orientation less than 10 degrees or more than 20 degrees. Orientations less than 10 degrees can then be determined by analyzing the FWHM and blue shift of the 2D peak as seen in Figure 19B and 19C.<sup>[182]</sup>

**Figure 19** Rotational-angle dependence of Raman 2D peak. (a) Graphene 2D peak for rotated double-layer and single-layer graphene. The vertical dashed line represents the center of single-layer 2D peak. (b) Rotated double-layer graphene 2D peak FWHM. We have fitted the 2D peaks with a single Lorentzian peak for simplicity. The black squares and red circles are the experimental and theoretical calculation values. The blue horizontal area represents the experimental value from single-layer graphene. The grey (experiment) and red (calculation) areas are guides to the eye. (c) Rotated double-layer graphene. (d) Integral intensity of 2D peak. Experimental and calculation values were normalized to the single-layer value. Reprinted with permission K. Kim *et al*, Physical Review Letters, Volume 108, 246103 (2012). Copyright (2012) by the American Physical Society.<sup>[182]</sup>

Raman spectroscopy can also be used to determine the number of graphene layers, doping concentrations in the graphene, strain, edge states, and defect concentration in the graphene layer using the position and FWHM of the 2D, G, and D peaks together.<sup>[183]</sup> The effect of the orientation on the electrical properties of bilayer devices, and more specifically the SymFET/BiSFET, has not been experimentally determined.

### **1.5.3** Disorder at the Interfaces

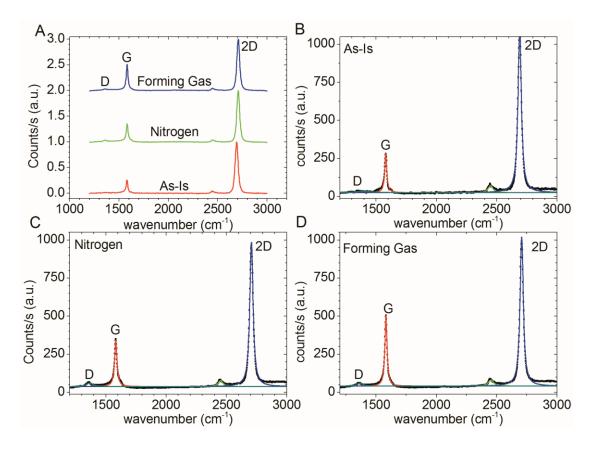

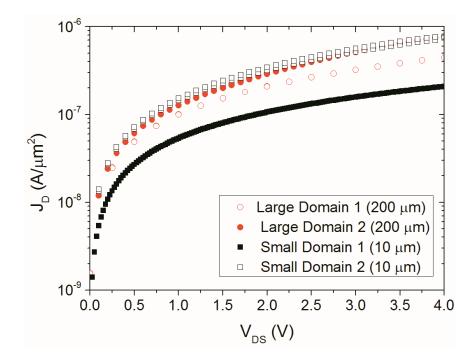

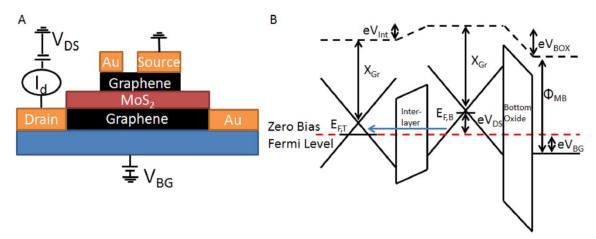

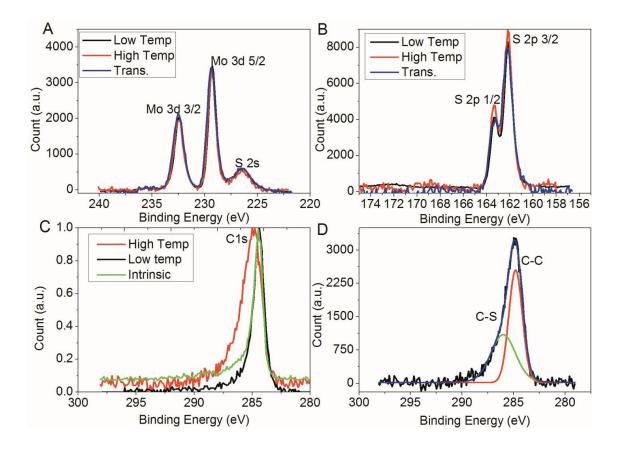

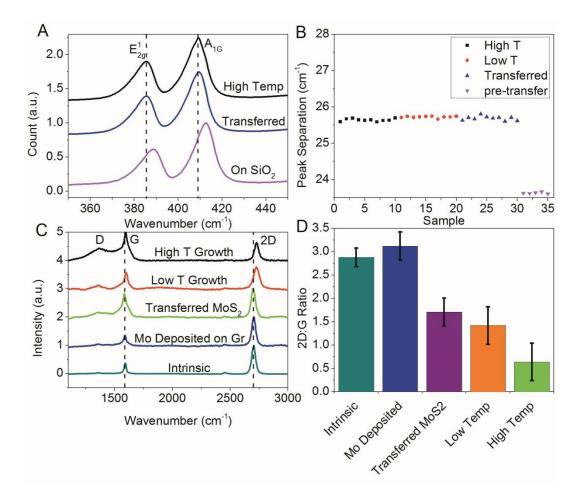

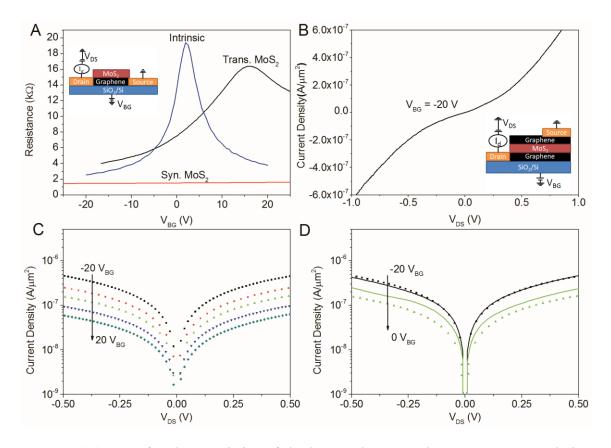

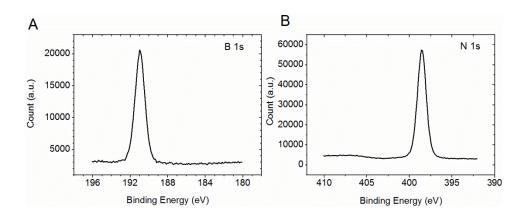

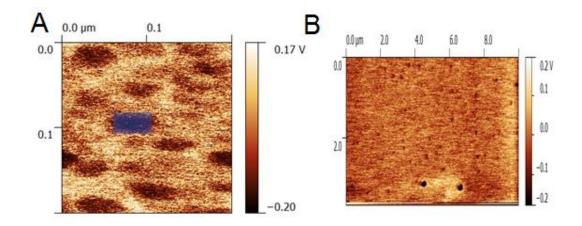

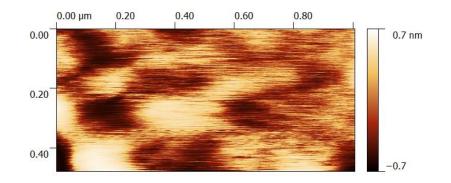

Graphene is a one atom thick layer of carbon. The electrical properties of the graphene are highly influenced by the interaction of the graphene surface with any adjacent materials.<sup>[132, 185-187]</sup> In the case of graphene on SiO<sub>2</sub>, the electrical properties of the graphene can become limited due to the scattering of carriers in the graphene by charged impurities and surface phonons.<sup>[188, 189]</sup> For this reason, the mobility of graphene on SiO<sub>2</sub> is reduced by several orders of magnitude compared to suspended graphene.<sup>[189]</sup> The silanol groups at the surface of the SiO<sub>2</sub> also degrade the performance of the graphene FET by causing unintentional p-doping and hysteresis in the graphene FET.<sup>[190]</sup> This makes the development of buffer layers which can be integrated into a CMOS fabrication process necessary for graphene electronics.