# CAN MY CHIP BEHAVE LIKE MY BRAIN? OR RECONFIGURABLE MIXED SIGNAL NEUROMORPHIC ARCHITECTURES

A Thesis Presented to The Academic Faculty

by

Suma George

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2015

Copyright © 2015 by Suma George

# CAN MY CHIP BEHAVE LIKE MY BRAIN? OR RECONFIGURABLE MIXED SIGNAL NEUROMORPHIC ARCHITECTURES

#### Approved by:

Professor Jennifer Hasler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor David Anderson School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Omer Inan School of Electrical and Computer Engineering Georgia Institute of Technology Professor Hua Wang School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Michael Pfeiffer Institute of Neuroinformatics University of Zurich and ETH Zurich

Date Approved: 6 April 2015

To my parents,

Suju and Ami

Because You're mine I walk the Line!

#### ACKNOWLEDGEMENTS

I want to thank all the people who make my life wonderful. There are many people who have been with me throughout my journey through graduate school and it has been much easier because of them. First and foremost I would like to thank my advisor Jennifer Hasler who has been my guide, teacher, friend and even therapist at times. I have always admired her technical prowess and the breadth of her knowledge. She has also taught me many life lessons on how to manage time and stress. I will be forever grateful for all your guidance. It has truly helped me grow both professionally and personally. I would also like to thank my committe members. David Anderson, who has been on my committe since my MS Thesis days. Omer Inan, and Hua Wang for all the wonderful feedback and support. Michael Pfeiffer for all your technical feedback both for the thesis and at the neuromorphic workshops at Capocaccia and Telluride.

I would like to thank my dearest parents. Mom and Dad you have always been my source of unconditional love and support. Mom, for helping me believe nothing is impossible if I set my mind to it. Dad, for teaching me the value of hard work and diligence. Your prayers and blessings have helped me achieve and become all that I am today. Thank you with all my heart! Suju, my elder sister for always blindly believing in me and egging me on. Ami, my younger brother for always helping me 'keep it real'! This journey would be incomplete without you. Aneesh Jiju, Annie and Joey my nieces, for keeping me on my toes! Leela aunty and Matchu for all their help. Fr. Matthew and Joy Uncle for being my guardian angels in the US. Joy uncle for all wonderful Halloween breaks at Disney. I'm truly blessed to have such a wonderful family.

Friends are the family we choose and I have been blessed with some really great people as friends. Smriti Chopra for being my sister in arms while we both pursued our PhDs. Through all my ups and downs you have been a constant, helping me navigate the craziness and celebrate the victories. It would not be any fun without you! Sudipto Das, for being chirpy, comical, and cynical. I know it is hard for one person to be all that, but you helped me see the lighter side of difficult moments. I'm very grateful to count you as one of my best friends. Michelle Collins for being the younger sister I never had. You are one of the sweetest people I know. I admire your integrity and strength. I'm cheering to see you succeed! Aishwarya Sarath, you always believed in me and would hear me out. You are truly cherished. Koshu, for being my strength and heart. You are an angel! KD, for being my rock and hearing me through countless sob stories. Aman Praji for being such a big support for me throughout, lucky to have a brother like you. Also would like to thank Amritha Arakali and Anjali Ashok for being awesome roommates and the countless karaoke nights. Samina Jamil, for your poetry and wonderful company.

Labmates are not just friends but an extension to your family as well, who help you keep it all going smoothly. I had the unique opportunity of being in the middle of the transition of old and new Integrated Computational Electronics (ICE) members. Richie Wunderlich for being my mentor, friend and counselor. Stephen Nease for being a great friend, I learned so much from you. Scott Koziol, for your positive attitude and advice and being an excellent collaborator. Shubha Ramakrishnan for being a guide, friend and an awesome chef feeding me Sambhar and other south Indian delicacies. Farhan Adil, for being a guide and a good friend. Craig Schlottmann for being extremely helpful and patient. Stephen Brink for the awesome technical discussions and advice. Arindam Basu, for getting me interested in neuromorphic circuits. As for new icicles Michelle Collins, Sihwan Kim and Sahil Shah, thanks for all the support while testing the ICs. I have really enjoyed our discussions both

technical and not. Sahil, keep laughing- it is refreshing to see you have a rather sensitive funny bone! Alex Cardwell, for being my punching bag, friend, and correcting my grammar. I have enjoyed our discussions on wide range of topics from religion, philosophy to neuromorphic systems. Andrew Freedman, your perseverance has been a stellar example for me. I wish all the Icicles past and present all the very best! Also would like to thank Dean Walker, my manager at Blackberry. You are one of the most amazing people I have met. I have learned a lot from you. Sudha Jha ma'am, you have been an inspiration for me throughout. Thank You all for being part of my journey!

# TABLE OF CONTENTS

| $\mathbf{DE}$ | DIC                    | ATIO                                       | N                                                             | iii |  |

|---------------|------------------------|--------------------------------------------|---------------------------------------------------------------|-----|--|

| $\mathbf{AC}$ | KNO                    | OWLE                                       | DGEMENTS                                                      | iv  |  |

| LIS           | вт О                   | F TAI                                      | BLES                                                          | xi  |  |

| LIS           | т о                    | F FIG                                      | URES                                                          | xii |  |

| SU            | MM.                    | ARY .                                      |                                                               | xv  |  |

| Ι             |                        | CONFIGURABLE MIXED SIGNAL NEUROMORPHIC AR- |                                                               |     |  |

|               | 1.1                    | Neuro                                      | omorphic Systems                                              | 5   |  |

|               |                        | 1.1.1                                      | Dendritic Computation                                         | 6   |  |

|               |                        | 1.1.2                                      | Neuromorphic Integrated Circuits (ICs)                        | 6   |  |

|               |                        | 1.1.3                                      | Modeling the Brain                                            | 6   |  |

|               |                        | 1.1.4                                      | Applications of Neuromorphic and Analog Systems               | 7   |  |

|               | 1.2                    | Recon                                      | figurable Mixed Signal Architectures                          | 8   |  |

|               |                        | 1.2.1                                      | Low Power IC Design:                                          | 8   |  |

|               |                        | 1.2.2                                      | Hardware Software CoDesign/ CAD tools:                        | 8   |  |

|               | 1.3                    | Overv                                      | iew                                                           | 9   |  |

| II            | RE                     | CONF                                       | IGURABLE SOC: RASP 3.0                                        | 12  |  |

|               | 2.1                    | Archit                                     | tecture Description of the FPAA SOC IC                        | 14  |  |

|               | 2.2                    | SOC I                                      | FPAA Routing Fabric Characterization and Computation          | 17  |  |

|               | 2.3                    | Repre<br>FPAA                              | sentative Circuit and Signal Processing Components in the SOC | 22  |  |

|               | 2.4                    | Repre                                      | sentative System Application in the SOC FPAA                  | 24  |  |

|               | 2.5                    | Summ                                       | nary Discussion and Comparisons                               | 26  |  |

| III           | $\mathbf{C}\mathbf{A}$ | D SYN                                      | NTHESIS TOOLS FOR HETEROGENEOUS SOCS                          | 29  |  |

|               | 3.1                    | CAD                                        | Tools for Reconfigurable Hardware: Overview                   | 31  |  |

|               | 3.2                    | x2c: I                                     | Design Suite on FPAA SoCs                                     | 33  |  |

|              |     | 3.2.1 sci2blif: Tool for XCOS to BLIF                                 | 4   |

|--------------|-----|-----------------------------------------------------------------------|-----|

|              | 3.3 | vpr2swcs: Targeting Heterogenous SoCs                                 | 1   |

|              |     | 3.3.1 VPR                                                             | 38  |

|              |     | 3.3.2 Challenges to make VPR work for Heterogeneous systems $4$       | .(  |

|              |     | 3.3.3 Macroblocks: Encapsulating complex circuits 4                   | .1  |

|              |     | 3.3.4 vpr2swcs design flow                                            | . 1 |

|              |     | 3.3.5 Efficiency question for routing                                 |     |

|              | 3.4 | Routing resources for computation                                     |     |

|              | 3.5 | System Example: Speech Classifier                                     | 4   |

|              | 3.6 | Conclusions and Future Directions                                     |     |

| IV           | HA  | RDWARE SOFTWARE CODESIGN 4                                            | 7   |

|              | 4.1 | Analog-Digital Design Tool Overview                                   | .0  |

|              | 4.2 | Integrating Analog–Digital Design Tool with an FPAA Platform 5        | 2   |

|              | 4.3 | Methodology for Implementing the Tool Set                             | 5   |

|              |     | 4.3.1 Macromodel Simulation                                           | (   |

|              |     | 4.3.2 $sci2blif$ : Xcos to VPR                                        | įĆ  |

|              | 4.4 | System Examples                                                       | (   |

|              | 4.5 | Summary, Comparisons, and Approaches for Analog–Digital Co-Design $6$ | 12  |

| $\mathbf{V}$ | МО  | DELING VOLTAGE-MODE CMOS DENDRITES 6                                  | ç   |

|              | 5.1 | The Silicon Channel                                                   | '(  |

|              | 5.2 | Implementing the Linear Cable Model with Analog CMOS Circuits . 7     | 2   |

|              | 5.3 | Demonstrating Equivalence to the Linear Cable Model                   | '8  |

|              |     | 5.3.1 Steady-State Experiments                                        | ;(  |

|              |     | 5.3.2 Dynamic Experiments                                             | ;]  |

|              |     | 5.3.3 Effects of a Reconfigurable Testbed                             | ) _ |

|              | 5.4 | Simulink Model for simulating CMOS dendrites and FPAA configuration   | 35  |

|              |     | 5.4.1 Dendrite Simulink Block                                         | 34  |

|              |     | 5.4.2 Behavioral modeling                                             | 32  |

|     | 5.5 | Nonlin                                   | near Behavior of Dendrites                           | 88  |

|-----|-----|------------------------------------------|------------------------------------------------------|-----|

|     |     | 5.5.1                                    | Math Modeling                                        | 89  |

|     |     | 5.5.2                                    | Demonstration of Impact on Dendrite Circuit Behavior | 90  |

|     | 5.6 | Impler                                   | menting Dendrites in Large Reconfigurable Systems    | 91  |

| VI  | DEN | NDRIT                                    | ΓΙC COMPUTATION                                      | 94  |

|     | 6.1 | Dendri                                   | ites for Wordspotting                                | 94  |

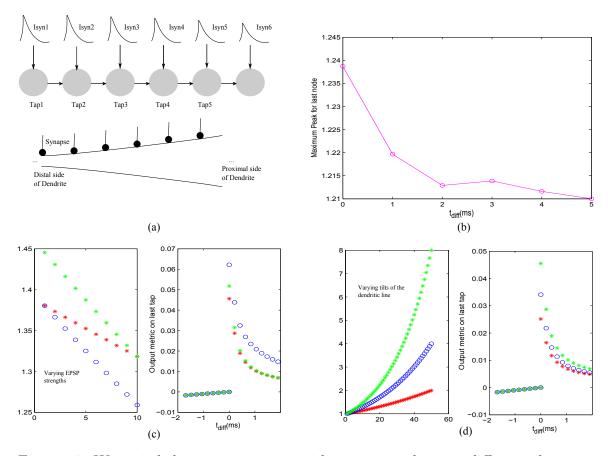

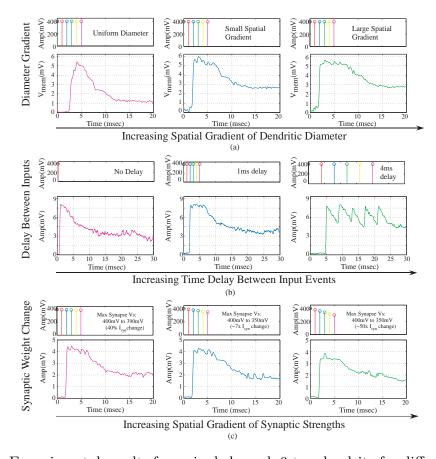

|     | 6.2 | Dendritic computation and the HMM branch |                                                      | 100 |

|     |     | 6.2.1                                    | RC delay line without taper                          | 103 |

|     |     | 6.2.2                                    | RC delay line with taper                             | 105 |

|     | 6.3 | CMOS                                     | S Dendrite                                           | 107 |

|     | 6.4 | Dendri                                   | ites: Behavioral Modeling                            | 109 |

|     | 6.5 | Single                                   | Line CMOS dendrite                                   | 110 |

|     |     | 6.5.1                                    | Inputs to the PFET source                            | 112 |

|     |     | 6.5.2                                    | Single line dendrite results                         | 113 |

|     |     | 6.5.3                                    | Dendrite on the routing fabric                       | 115 |

|     |     | 6.5.4                                    | Simulating CMOS dendrites                            | 116 |

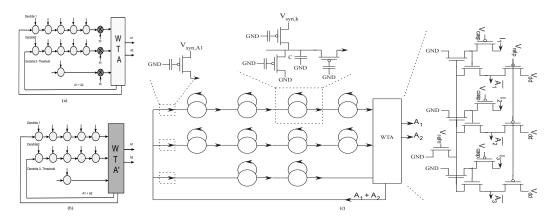

|     | 6.6 | Analog                                   | g Classifier for Word-spotting                       | 117 |

|     | 6.7 | Recont                                   | figurable platform to build Neuromorphic circuits    | 121 |

|     | 6.8 | Classif                                  | fier:Computational efficiency                        | 122 |

|     | 6.9 | Conclu                                   | usion                                                | 123 |

| VII | BUI | LDIN                                     | G RECONFIGURABLE NEUROMORPHIC SYSTEMS                | 125 |

|     | 7.1 | Neuro                                    | n2 chip                                              | 126 |

|     | 7.2 | Dendri                                   | itic Modeling and Computation                        | 129 |

|     | 7.3 | RASP                                     | 3.0N                                                 | 129 |

| VII |     | NCLU                                     | SION                                                 | 135 |

|     | 8.1 | Summ                                     | ary of Research so far                               | 135 |

|     | 8.2 | Summ                                     | ary of Work Completed                                | 137 |

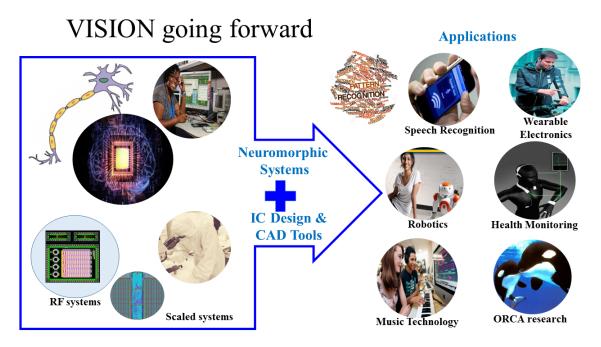

|     | 8.3 | Vision                                   | going forward                                        | 138 |

| 8.3.1     | Neuromorphic Systems                      | 139 |

|-----------|-------------------------------------------|-----|

| 8.3.2     | Applications of Neuromorphic systems      | 140 |

| 8.3.3     | Reconfigurable Mixed Signal Architectures | 141 |

| REFERENCE | ES                                        | 143 |

| VITA      |                                           | 164 |

# LIST OF TABLES

| 1 | Comparing HMM PDE and RC Delay Line Terms w/Assumptions              | 106 |

|---|----------------------------------------------------------------------|-----|

| 2 | Comparing computational efficiency of Digital, Analog and Biological |     |

|   | systems                                                              | 122 |

| 3 | Comparison of RASP chips                                             | 132 |

# LIST OF FIGURES

| 1  | Neuromorphic Systems                                                                                                 | 1  |

|----|----------------------------------------------------------------------------------------------------------------------|----|

| 2  | Reconfigurable Mixed Signal Neuromorphic Architectures                                                               | 3  |

| 3  | Computationally Efficiency                                                                                           | 4  |

| 4  | Limitations when using Analog vs Digital Systems                                                                     | 5  |

| 5  | Applications possible with Neuromorphic and Analog Solutions                                                         | 7  |

| 6  | Reconfigurable SoC RASP 3.0 block diagram and die photo                                                              | 13 |

| 7  | RASP 3.0 functional block diagram illustrating the resulting computational blocks and resulting routing architecture | 14 |

| 8  | RASP 3.0 FPAA IC enables integration of Analog and Digital Blocks in the routing fabric                              | 16 |

| 9  | Experimental measurements for characterizing the capacitances of the routing fabric                                  | 18 |

| 10 | Additional aspects of our FPAA Routing Fabric                                                                        | 20 |

| 11 | Vector-Matrix Multiplication (VMM) as a computational block                                                          | 21 |

| 12 | Compiled Analog-to-Digital Converters (ADC) with experimental results $$                                             | 23 |

| 13 | VMM and WTA classifier block                                                                                         | 24 |

| 14 | Analog auditory word classification application                                                                      | 25 |

| 15 | Comparison of RASP 3.0 to other devices                                                                              | 28 |

| 16 | Typical iterative flow for CAD tools to design Integrated Circuits $$ . $$                                           | 30 |

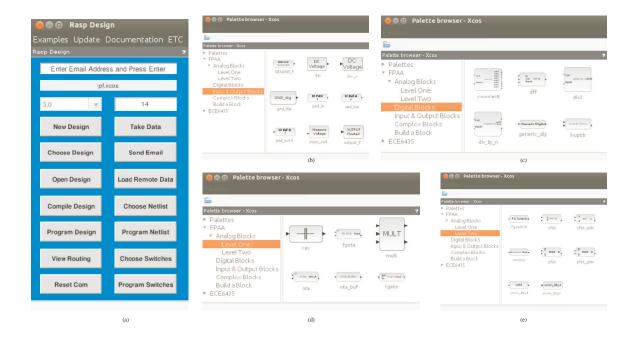

| 17 | x2c Design Suite for FPAAs                                                                                           | 33 |

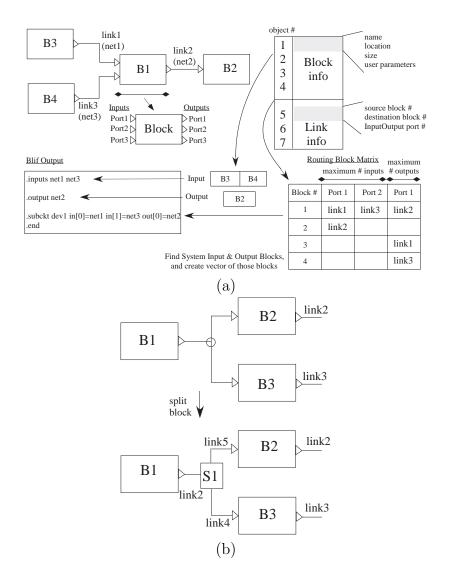

| 18 | System example of the tools to demonstrate Hardware-Sofware Codesign                                                 | 34 |

| 19 | vpr2swcs synthesis tool flow                                                                                         | 35 |

| 20 | Configuration settings in $x2c$                                                                                      | 36 |

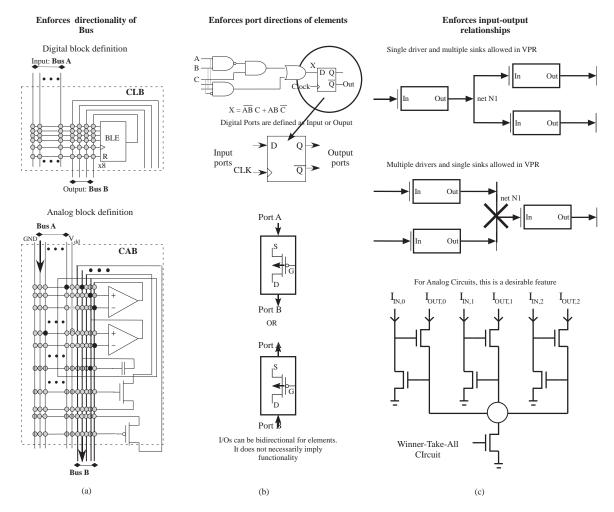

| 21 | Challenges one faces when using VPR                                                                                  | 37 |

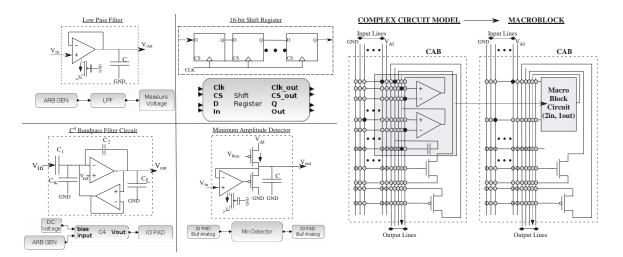

| 22 | Macroblocks                                                                                                          | 38 |

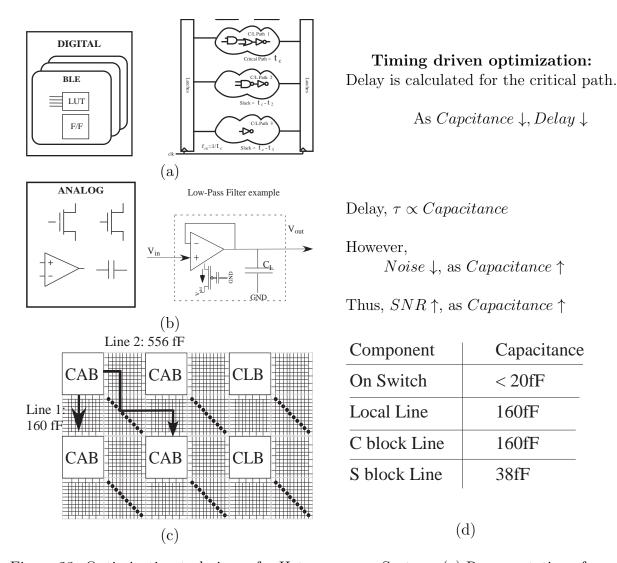

| 23 | Optimization techniques for Heterogeneous Systems                                                                    | 39 |

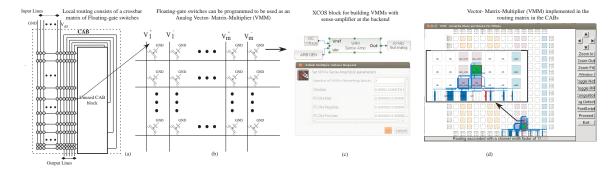

| 24 | Utilizing routing for VMMs                                                                                           | 44 |

| 25 | Universal Approximator system example                                                                                | 45 |

| 26 | Speech Classifier System example                                                                          | 46 |

|----|-----------------------------------------------------------------------------------------------------------|----|

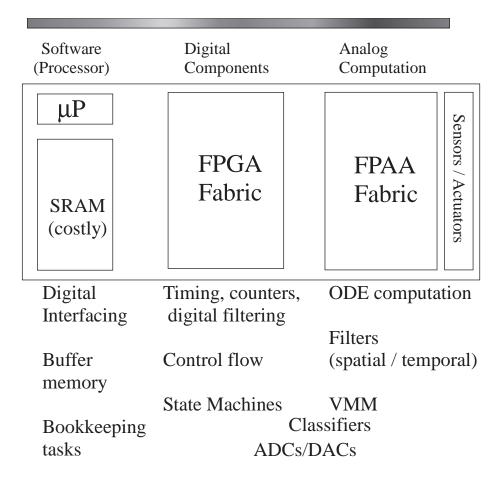

| 27 | Hardware Software CoDesign                                                                                | 48 |

| 28 | x2c Tool Design Overview                                                                                  | 49 |

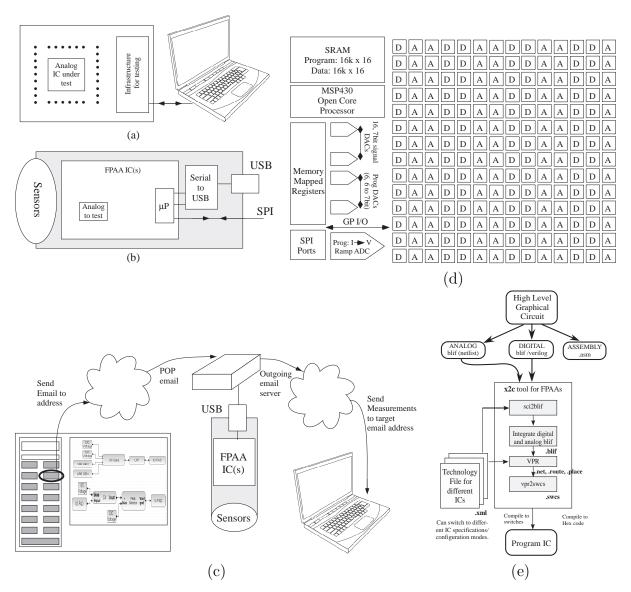

| 29 | An example of the entire tool flow                                                                        | 51 |

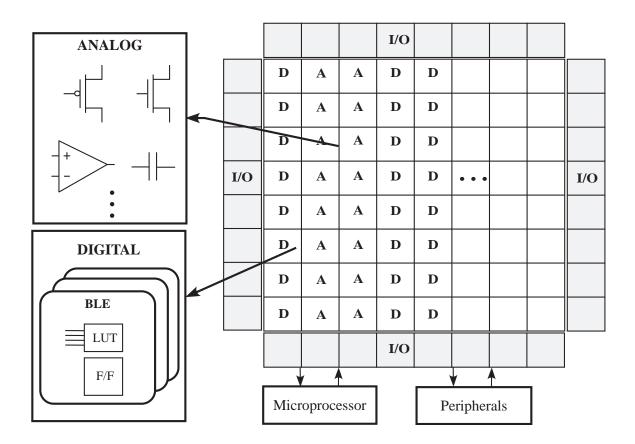

| 30 | Illustration of the structure of FPAA devices                                                             | 53 |

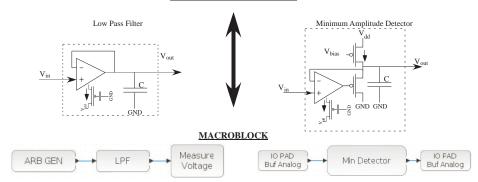

| 31 | Low level cicuits as macroblocks                                                                          | 54 |

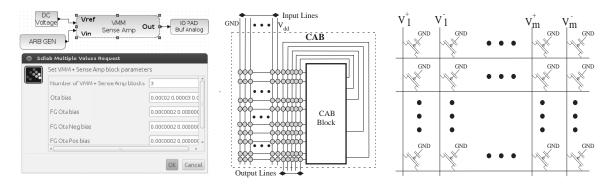

| 32 | Approach to build a MacroModel                                                                            | 55 |

| 33 | sci2blif fundamentals                                                                                     | 58 |

| 34 | VMM blocks in $sci2blif$                                                                                  | 60 |

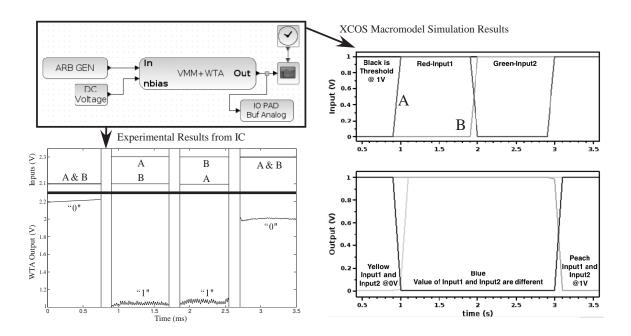

| 35 | A system example showing a basic circuit classifier                                                       | 61 |

| 36 | Possible approaches for mixed-mode computing systems                                                      | 62 |

| 37 | Spectrum of Codesign computation                                                                          | 63 |

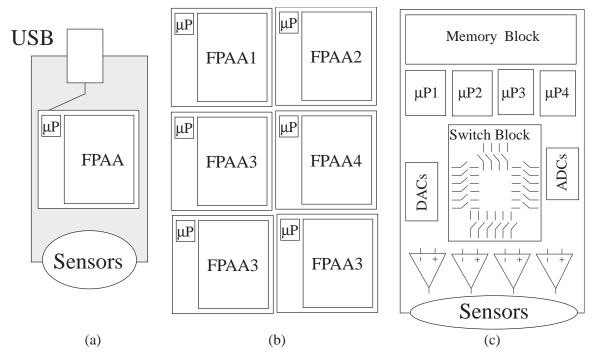

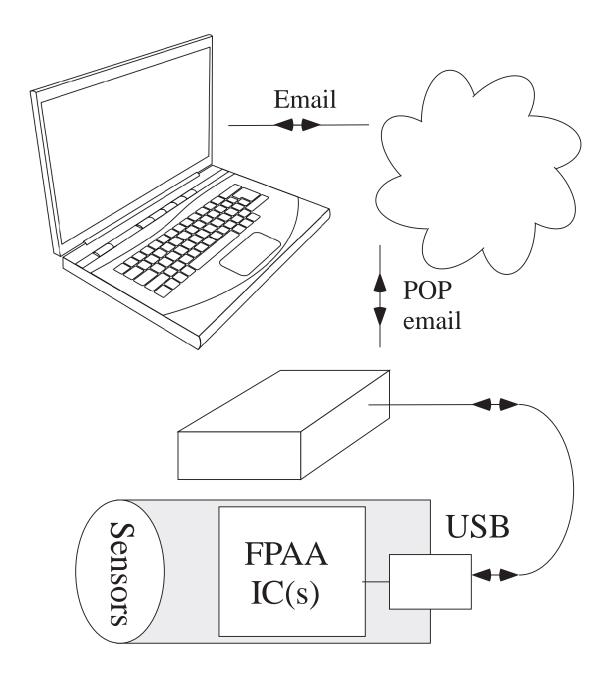

| 38 | Remote system concept                                                                                     | 67 |

| 39 | System perspective using a remote test system to utilize mixed-signal configurable systems                | 68 |

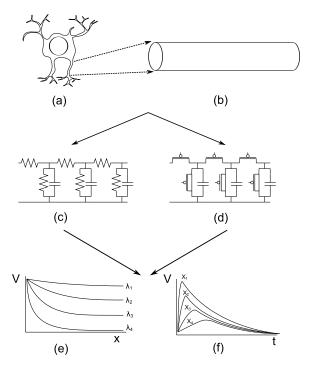

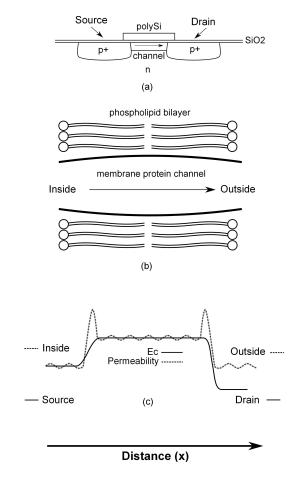

| 40 | Dendrites and their description based on Linear Cable Theory                                              | 70 |

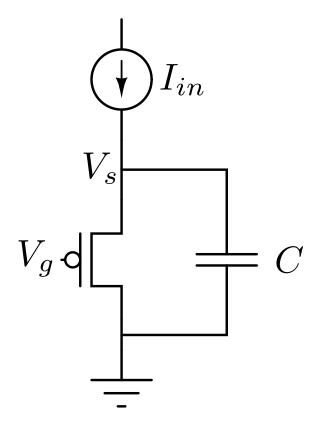

| 41 | The Silicon Channel                                                                                       | 71 |

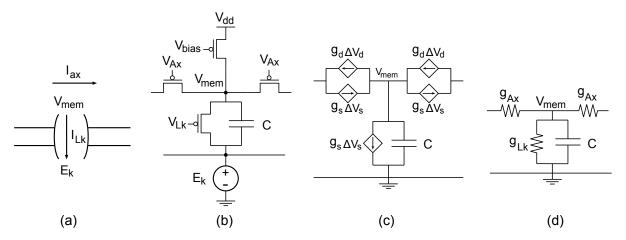

| 42 | Various models of a dendrite                                                                              | 73 |

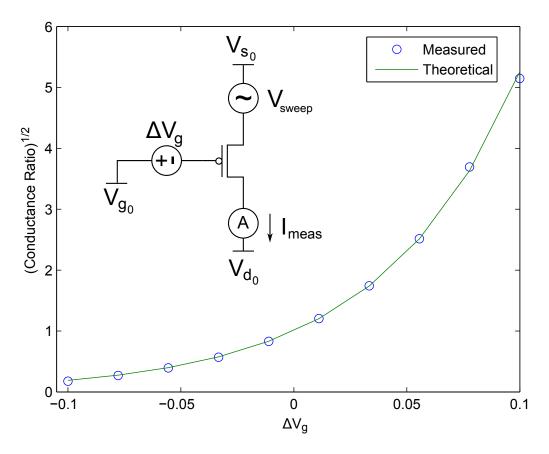

| 43 | Demonstration that the ratio of source conductances is a function of the difference between gate voltages | 78 |

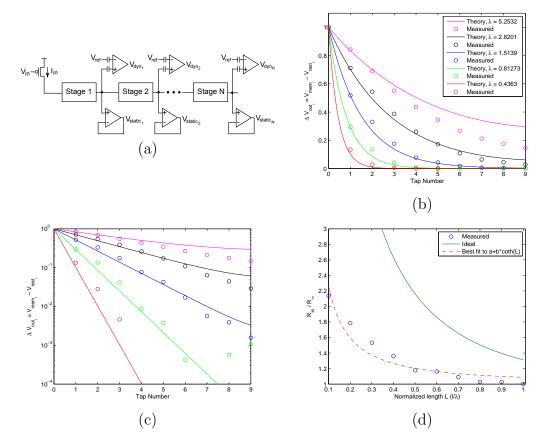

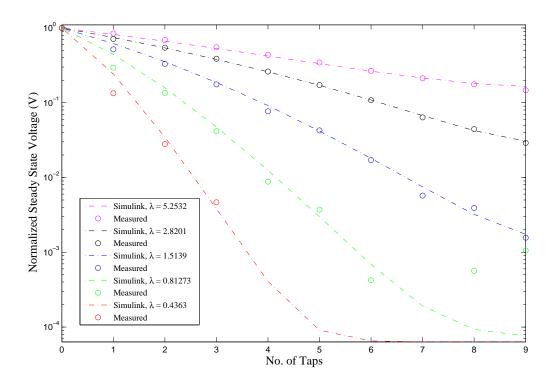

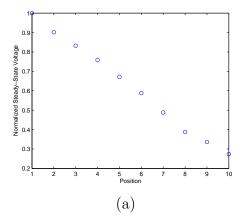

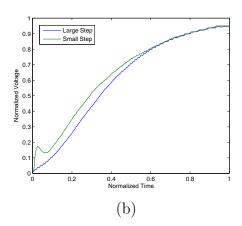

| 44 | Steady State Experiments for a dendrite                                                                   | 79 |

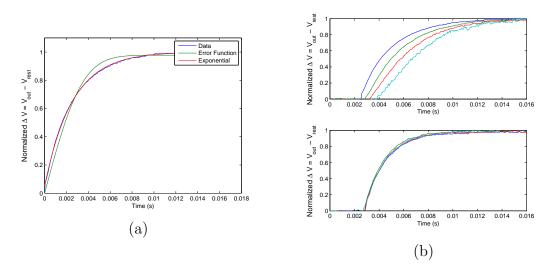

| 45 | Dynamic Plots                                                                                             | 81 |

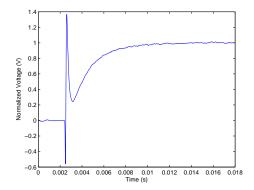

| 46 | Parasitic Non-idealities                                                                                  | 83 |

| 47 | Dendrite Simulation Model                                                                                 | 85 |

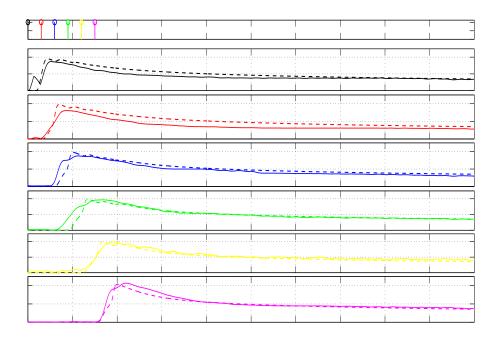

| 48 | Comparing Simulation results to experimental results                                                      | 87 |

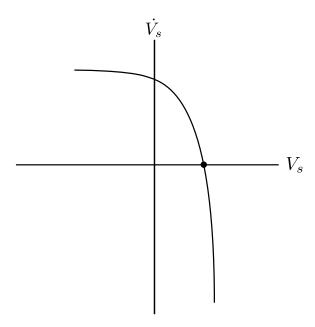

| 49 | Non-linear behavior of dendrites                                                                          | 88 |

| 50 | Illustration of nonlinear dynamics in dendrite circuit                                                    | 89 |

| 51 | Illustration of the phase portrait                                                                        | 90 |

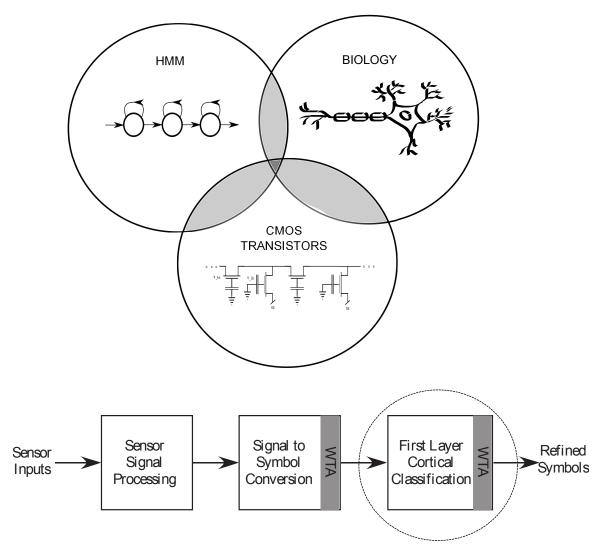

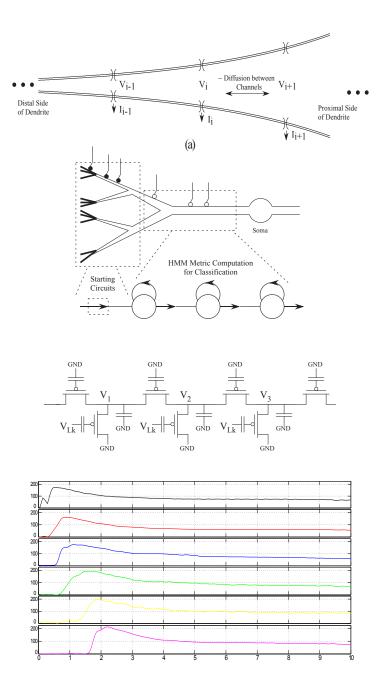

| 52 | Illustration of interlinks between the fields of neurobiology, HMM structures and CMOS transistors        | 95 |

| 53 | High level overview of FPAAs                                                            | 9   |

|----|-----------------------------------------------------------------------------------------|-----|

| 54 | Basic auditory feature extraction and probability generation stage                      | 98  |

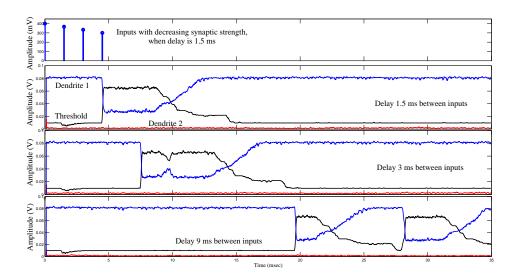

| 55 | Simulation results for an HMM state machine based on a Mathematical HMM model           | 100 |

| 56 | CMOS implementation for a dendritic branch and experimental results.                    | 101 |

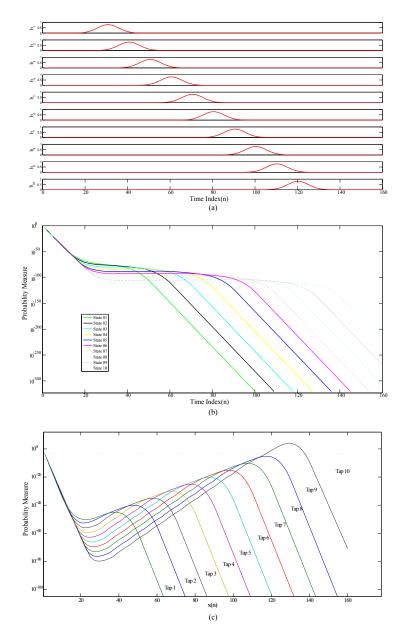

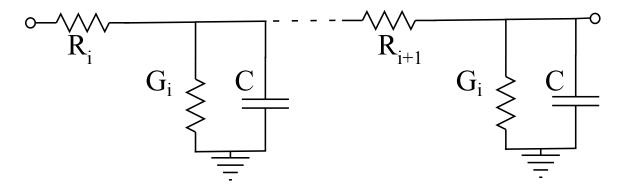

| 57 | RC delay line representing a dendrite                                                   | 104 |

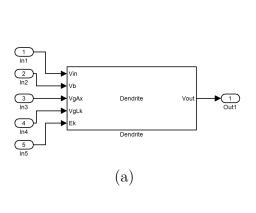

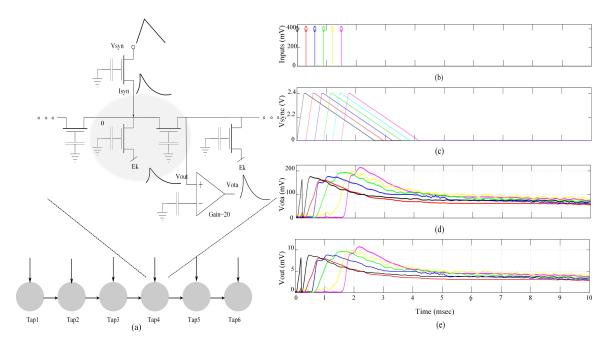

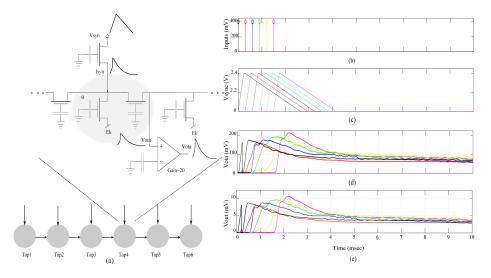

| 58 | System overview for a dendrite branch                                                   | 107 |

| 59 | Experimental results, simulation results and trends observed for a single line dendrite | 108 |

| 60 | System overview for a dendrite branch                                                   | 110 |

| 61 | Simulation Data vs. experimental data comparison                                        | 111 |

| 62 | Experimental results for a single branch 6-tap dendrite                                 | 112 |

| 63 | The dendrite classifier structure                                                       | 114 |

| 64 | Experimental results for the classifier system                                          | 115 |

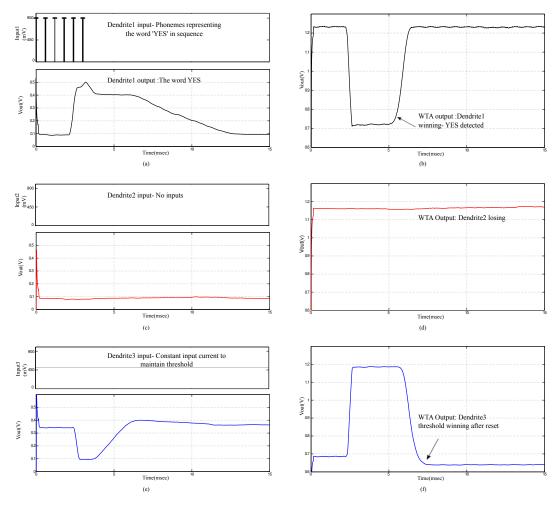

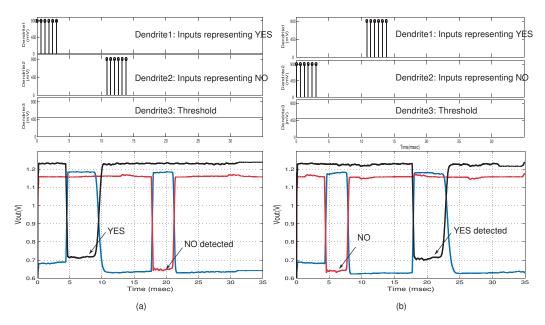

| 65 | Experimental results for the YES/NO classifier system                                   | 119 |

| 66 | Experimental results for the classifier system when a sequence of words is detected     | 120 |

| 67 | Digital efficiency Wall                                                                 | 126 |

| 68 | Comparison of current silicon systems                                                   | 127 |

| 69 | Neuromorphic ICs                                                                        | 128 |

| 70 | Dendritic Structure on Neuron2                                                          | 129 |

| 71 | Different applications using the Pattern Recognition system                             | 130 |

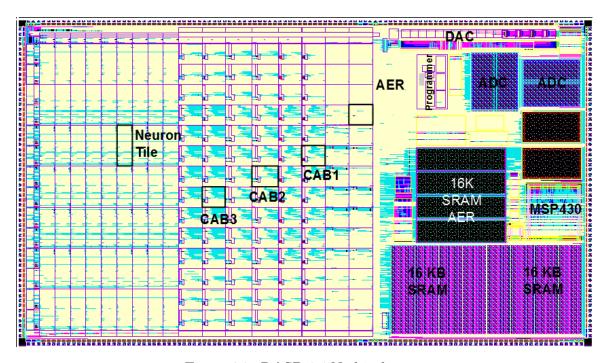

| 72 | RASP $3.0N$ chip layout                                                                 | 130 |

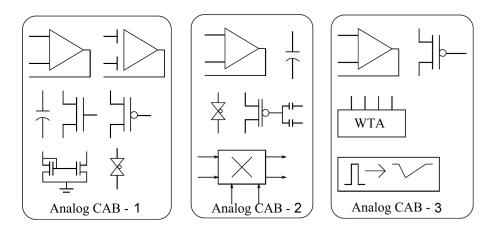

| 73 | RASP $3.0N$ CAB elements                                                                | 131 |

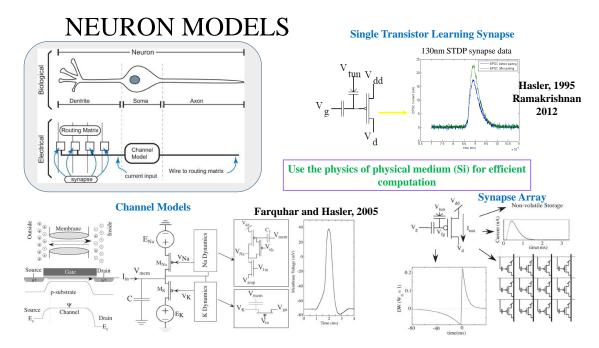

| 74 | RASP $3.0N$ Neuron Models                                                               | 131 |

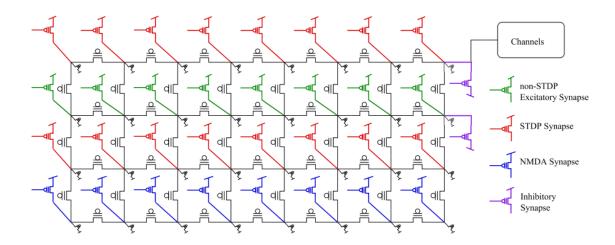

| 75 | RASP 3.0N Neuron CAB                                                                    | 132 |

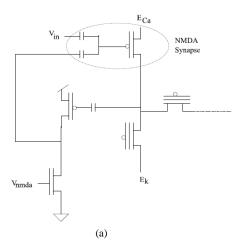

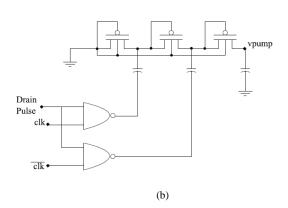

| 76 | NMDA Synapse and a Negative Charge Pump                                                 | 133 |

| 77 | Research Vision                                                                         | 141 |

#### SUMMARY

'Can My Chip Behave Like My Brain?' As a young graduate student at Georgia Tech looking at Prof. Hasler's research, this was the first query I had. Coming from a Very Large Scale Integration (VLSI) background, it was very exciting for me to see biophysical models of neurons using CMOS transistors! My research goal thereon has been to investigate how to build efficient neuromorphic systems using mixed signal reconfigurable architectures. Many decades ago, Carver Mead established the foundations of Neuromorphic Systems. Neuromorphic systems are analog circuits that emulate biology. They utilize sub-threshold dynamics of CMOS transistors to mimic biology. The objectives are to emulate biological processes, and also build useful applications using these bio-inspired circuits.

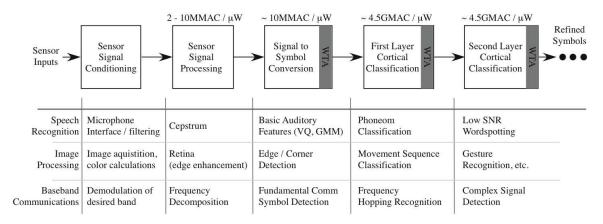

In this research we will learn how we can achieve this by using reconfigurable hardware like field programmable analog arrays(FPAA). FPAAs enable configuring/prototyping different systems on a unified platform. As digital systems saturate in terms of power efficiency, this alternate approach has the potential to improve computational efficiency by about eight orders of magnitude. These systems include analog, digital and neuromorphic elements as building blocks; an amalgamation of all of the above results in a very powerful processing machine. These systems can then be used to implement complex algorithms like Artificial Neural Networks, Winner-Take-All (WTA) and word-spotting to build ultra low-power applications.

This body of work is divided into three main parts. First we will discuss reconfigurable systems and talk about the latest FPAA System-on-a-chip (SoC) built. We will discuss some mixed signal, analog and digital examples as well as demonstrate a command word classifier. Second, we will discuss the VLSI CAD tools developed to make system design feasible on these SoCs. Third, we will talk about neuromorphic

architectures and applications one can build using these systems. We will go over bioinspired modeling of dendrites and how along with other bio-physically based models of the soma, synapse and channels we can make a neuron block. We will discuss how combining all these approaches enables us to build efficient low power systems.

Why is this important? Modern day technology relies heavily on silicon devices to do computation. These systems have however hit an energy efficiency wall and hence we need to look at different solutions that will help break this efficiency barrier. This can be done by using reconfigurable and programmable analog solutions and we can further this approach by using bio-inspired systems. Together with existing mixed signal systems and neuromorphic models, we can build ultra efficient low power systems. Thus, along with in vivo studies, in silico studies are also very important. Building a neuromorphic supercomputer is within our grasp, and is a grand challenge of our times.

#### CHAPTER I

# RECONFIGURABLE MIXED SIGNAL NEUROMORPHIC ARCHITECTURES

"The brain is a monstrous, beautiful mess. Its billions of nerve cells called neurons lie in a tangled web that displays cognitive powers far exceeding any of the silicon machines we have built to mimic it."

William F. Allman [99]

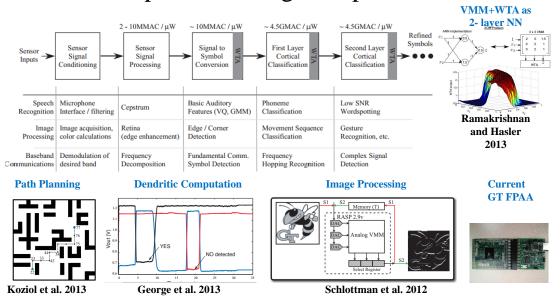

Figure 1: (a) Typical PhD student's 'brain' (b) Efficient System On Chip(SoC) that can perform complex tasks like the brain aka "what we want"!

The human brain, though studied a lot, is still a mystery when it comes to its functioning. Scientists are yet to determine what the intricate relationships and functions among various parts of the brain are. Merely knowing all the components of the brain doesn't lead to a sound understanding of how they interact with each other [103]. Numerous comparisons have been made between the brain and a digital computer; the biggest similarity being they both process information. What sets the brain's neural

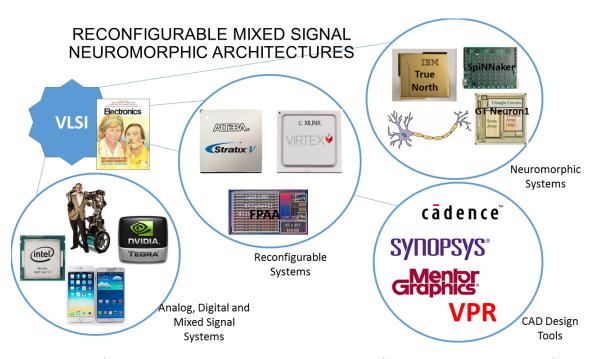

networks apart is a very high computational efficiency, robustness and the ability to solve structured as well as ill-structured problems. The digital computer has advantages of being very precise for well-structured problems. However, most real-world problems are not structured in nature. Therefore, even though a lot of progress has been made to develop systems that tackle real world problems, for example IBM Watson; we haven't yet designed a system that can function or adapt like the human brain and do so with minimal power. One can joke about a young graduate student's brain as shown in Fig. 1(a) with our sole focus being our thesis but it is only natural to draw comparisons between Very Large Scale Integrated (VLSI) chips which are ubiquitous as shown in Fig. 1(b). In this thesis we will explore how to combine different areas under VLSI system design and use it to build computationally efficient machines. Thus a more technical title for this thesis would be 'Reconfigurable Mixed Signal Neuromorphic Architectures'. VLSI systems pioneered by Carver Mead and Lynn Conway has spawned into multiple areas as shown in Fig. 2. This thesis will cover discussion about mixed signal systems reconfigurable systems, neuromorphic systems as well as CAD tools that help us design such complex systems.

Neuromorphic engineering is an area pioneered by Carver Mead in the late 1980s which endeavors to do this. Silicon devices operating in the sub-threshold regime and biological structures share similar physical principles of operation. This implies that silicon devices can be used to *emulate* biological systems. The consequences of this statement are two-fold. First, we can use Neuromorphic circuits to emulate biological systems and second, we can use these systems to perform novel computation. Neuromorphic engineering though considered a non-traditional approach, has a lot of potential to look into real world problems as well as model biology. I have focused my research on building systems that leverage digital, analog and bio-inspired circuits. The goal is to build a powerful prototype for a neuromorphic processor. These low-power reconfigurable systems, can be used to solve different problems like image

Figure 2: VLSI systems were pioneered by the Mead-Conway approach. Its defining Characteristics were top-down design, stress on system-level concepts, merging separate disciplines to create a new, simplified methodology, Present a small set of key concepts from a range of topics, to carry along the least amount of mental baggage as well as focus on Starting with education. Now VLSI systems are ubiquitous. This revolution spawned many different areas. You have analog, digital and mixed mode system chips driving computation on our smartphones, electronic gadgets, robots etc with industry leaders like Intel, Qualcomm, Nvidia, Apple, Samsung to name a few. We have reconfigurable systems like Field Programmable Gate Arrays (FPGAs) with market leaders like Xilinx, Altera etc. and FPAAs [153–158] that enable quick prototyping of digital and analog systems respectively. We have neuromorphic systems which propose novel physical algorithms that can be used to build efficient machines. We have digital implementations like the IBM True North, University of Manchester's SpiNNaker, Georgia Tech's Neuron ICs [164,165]. Last but not the least we have CAD design tools that actually make the implementation of systems possible on hardware and make design easier. Prominent industry leaders are Cadence, Synopsys, Mentor Graphics as well as open source tool efforts like Virtual Place and Route(VPR) [121].

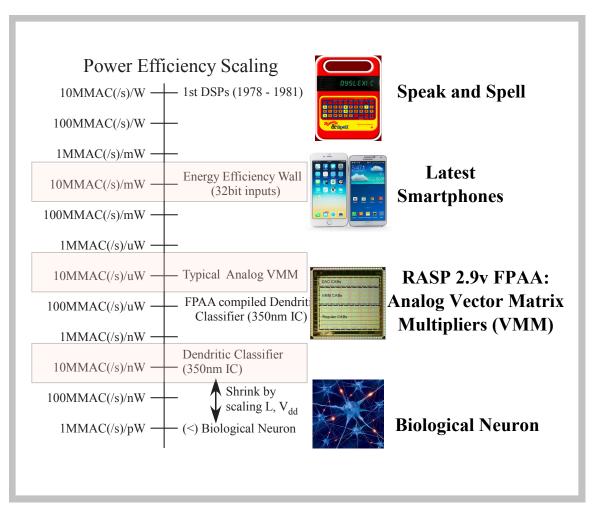

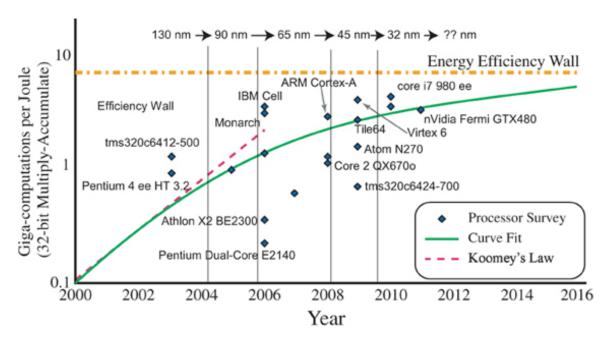

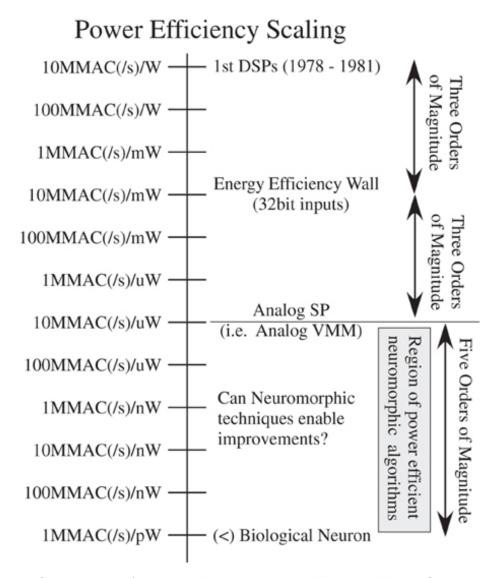

processing, speech processing applications, prototyping and build simple circuits in the classroom. A technology evolution roadmap for neuromorphic engineers has been proposed by Hasler et al. as seen in Fig. 3, to get the same foresight that IC designers gained from Moore's law many years ago. Scaling of energy efficiency, performance,

Figure 3: Power efficiency scaling has hit an efficiency wall in recent times with state of art digital processors as shown in a survey in 2012 in [16, 101]. Analog as well as bio-inspired solutions can help us further scale to ultra low power systems.

and size is discussed as well as how the implementation and application space of neuromorphic systems is expected to evolve over time [101]. This work endeavors to be a step in the direction of building such large-scale neuromorphic systems.

My research goal is to build computationally efficient bio-inspired systems and applications. As an engineer, I believe building bio-inspired systems gives me a unique outlook to not just understand the brain, but also utilize my findings to build bio-inspired systems for real world applications. In the process of doing so I cover multiple areas like neuromorphic systems, reconfigurable architectures, low power system design, mixed signal CAD tools, and application of these technologies for speech

Solve the parts of the problem in the domain most efficient for that problem.

Reconfigurable systems enable that.

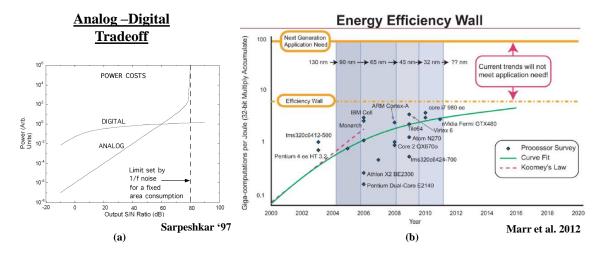

Figure 4: Limitations when using Analog vs Digital Systems. (a) Here is a plot demonstrating the tradeoff in terms of energy and SNR. We want to perform computation in the most efficient domains depending on our requirements. We can leverage analog processing to enable lower power systems while using digital systems when we need more precision. We build reconfigurable architectures to enable this flexibility. (b) Survey done by Marr et al. [16] demonstrating an enery efficiency wall for current state of the art digital processors.

processing, pattern recognition and robotics.

# 1.1 Neuromorphic Systems

Neuromorphic systems are analog circuits that utilize subthreshold dynamics of CMOS transistors to mimic biology. The objective is not just to simulate the human brain, but also to build useful applications using this knowledge for speech recognition, image processing, and robotics. As digital systems saturate in terms of power efficiency as shown in Fig. 4, this alternate approach becomes more attractive.

Neuromorphic hardware models the behavior of biological neural systems to enable efficient computational modeling. It leads to a significant reduction in size and power compared to the traditional approaches of modeling based on numerical integration on a digital computer.

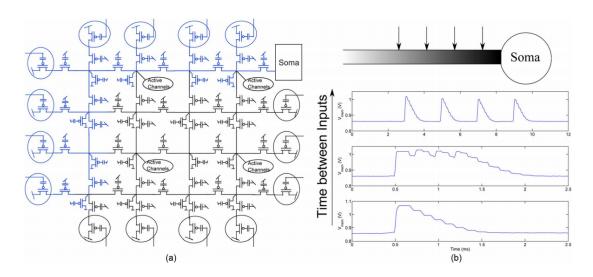

#### 1.1.1 Dendritic Computation

I focus my research on a much smaller yet important component of the nervous system- dendrites. Dendrites are essentially tree-like structures that connect neurons. Dendritic computation is often ignored and a point neuron model is typically adopted. However, studies show dendrites perform operations such as nonlinear filtering, spatial and temporal summation of synaptic inputs, coincidence detection, synaptic scaling and sequence detection. I have demonstrated that by exploiting the directional selectivity and coincidence detection properties of dendrites, we can implement a word-spotting network that can be used in many classifier applications using our VLSI chip. The word-spotting network is similar to a Hidden Markov Model (HMM) classifier that is often used in speech and pattern recognition.

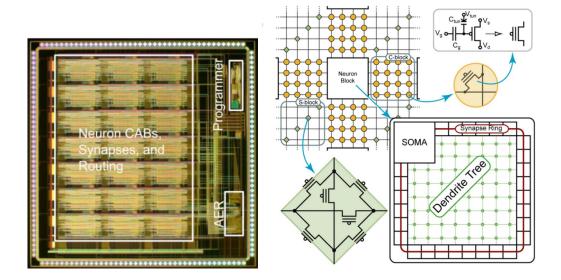

#### 1.1.2 Neuromorphic Integrated Circuits (ICs)

I was the co-architect in building a reconfigurable neuromorphic IC with neurons and a mixed signal fabric to further study these architectures. I developed an efficient and scalable hardware system for studying dendritic computation in large scale networks with programmable learning synapses and dendrites that support arbitrarily branched dendrites. This architecture also includes active channels in the dendrite for non linear filtering. Effectively, it is a multilayer neural network within each neuron. This system is a way to study and gain insight into building larger computationally efficient systems in the future.

#### 1.1.3 Modeling the Brain

The ultimate goal is to build a system that matches or exceeds the complexity of the human brain. It is advantageous to build smaller applications emulating functionality of basic elements using silicon models of the neurons, synapses, and dendrites to build networks. Learning can be implemented on these networks using floating gate (FG) transistor technology, which can be used as a memory element that simulates learning.

# Neuromorphic + Analog Computation

Figure 5: Applications like image processing, path planning for robots, wordspotting using dendritic classifier and a VMM+WTA circuit as a universal approximator have been demonstrated using neuromorphic and analog solutions on FPAAs.

Modern day technology relies heavily on silicon devices to do computation. However, there is a critical need to invest in silicon to build bio-inspired systems. With existing mixed signal systems and neuromorphic models, we can build ultra efficient low power systems. Thus, in silico studies are very important as are in vivo studies. Building a neuromorphic supercomputer, or a "Silicon Brain" is within our grasp, and is a grand challenge of the twenty-first century.

#### 1.1.4 Applications of Neuromorphic and Analog Systems

One of the goals of my research is to not only to mimic biology in silicon, but also utilize these bio-inspired systems to solve real world problems like speech classification, pattern recognition, robotics etc. as shown in Fig. 5 I have demonstrated a YES/NO classifier using dendrites and a Winner Take All (WTA) circuit using our VLSI chip. I believe that by using this dendrite based neuromorphic classifier and other front end techniques, I can build an effective audio recognition system which

can be used for a wide variety of applications in speech/audio processing particularly for phoneme recognition. We will discuss more about this model in chapters 3 and 4.

#### 1.2 Reconfigurable Mixed Signal Architectures

The backbone of my research that enables building such systems is reconfigurable hardware and a software CAD toolset. Reconfigurable hardware for digital computation is the norm these days, namely the Field Programmable Gate Arrays (FPGAs). Similarly for analog solutions, we have Field Programmable Analog Arrays (FPAAs). In such a platform, analog components are embedded in a switch fabric that enables arbitrary connections between them. We use FG as the switch element, as this adds the properties of non-volatility and compactness. Combining both analog and digital components into a FG switch fabric, we can leverage the best of both worlds.

#### 1.2.1 Low Power IC Design:

I have been instrumental in developing and testing a new generation of Reconfigurable Analog Signal Processor (RASP) 3.0 family of SoCs designed by our research group, fabricated in the 350 nm technology. This design effort addressed a lot of the interfacing questions and made our systems more compact. The SoC has a processor, memory, ADCs, DACs and other peripherals on chip. The neural IC is a variation of this as it contains not just analog and digital blocks, but neuron blocks as well. The global interconnect between all tile elements is FPGA-style manhattan routing. These are very powerful SoCs that I plan to use. I also hope for students to learn IC design by building chips through MOSIS. I hope to build RASP peripherals for these chips that can specialize as sensor blocks that interface with the existing IC.

#### 1.2.2 Hardware Software CoDesign/ CAD tools:

I was instrumental in developing a new CoDesign environment x2c for simulating and programming reconfigurable FG based mixed signal SoCs. These SoCs consist

of an integrated processor, I/O peripherals, and a FPAA comprised of analog and digital components. This novel open source tool platform empowers the user to seamlessly CoDesign low power analog and digital systems in a single environment. This approach integrates multiple open source tools to develop a coherent user friendly design flow. Scilab is the graphical front end for system level block design, which invokes Verilog to Routing (VTR)/ Versatile Place and Route (VPR) tools.vpr2swc-VPR to switches tool handles analog component packing, integrates the system, then generates switches to program and test the IC. We demonstrated several mixed signal examples, as well as how to perform useful computation using the routing fabric. This is a very powerful open source platform that will be open to a wider audience post publication and will be very effective for teaching in the classroom. The tool can be extended to any new family of heterogeneous ICs.

#### 1.3 Overview

In chapter 2, I will present an System-on-a-chip (SoC) that integrates divergent concepts from previous multiple large-scale FPAA designs along with low-power digital computation and interface circuitry (i.e. DACs, ADCs). This unified structure enables a wide range of a system-on-a-chip computing options that can be optimized for a wide range of parameters (i.e. Power); the resulting IC architecture is the most sophisticated FPAA device built to date.

In chapter 3, I will talk about the CAD synthesis tool vpr2swcs for targeting floating gate (FG) based mixed-signal SoCs of the RASP 3.0 family. These SoCs consist of a digital processor, Field Programmable Analog Array (FPAA) fabric, DACs, ADCs and peripherals. The tool is used for building parametric FPAA architectures that consist of both digital and analog blocks. I will discuss here the modifications, challenges and novel solutions proposed while doing mixed signal system design. Mixed signal examples will be demonstrated. Also we will see how the routing fabric can be

leveraged for computation.

In chapter 4, An Analog-Digital Hardware-Software CoDesign environment for simulating and programming reconfigurable systems will be presented. For this thesis, we will focus on a large-signal SoC Field Programmable Analog Array (FPAA) comprised of analog and digital components, consist of an integrated processor with I/O peripherals, and based on Floating-Gate (FG) devices and circuits, although the approaches can be extended to other platforms. The open-source tool platform, integrating multiple open source codes, empowers the user to do seamless low-power analog-digital CoDesign in a single environment that generates and implements high-level simulation and experimental measurement of the resulting hardware system. The tool flow will be demonstrated with multiple mixed signal examples through this configurable system.

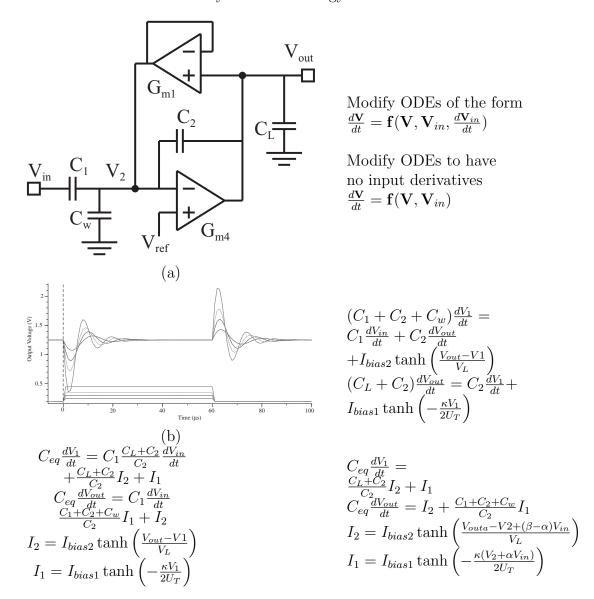

In chapter 5, we will foray into the world of neuromorphic systems especially dendrites. Many decades ago, Wilfrid Rall and others laid the foundations for mathematical modeling of dendrites using cable theory. With reconfigurable analog architectures, we are now able to accurately program different circuit architectures to emulate dendrites. Our work has shown that these circuits accurately reproduce results predicted from cable theory when inputs to the system are small. For large inputs, interesting nonlinear effects begin to take hold.

In chapter 6, we will talk about how a network of dendrites can be used to build the state decoding block of a wordspotter similar to a Hidden Markov Model (HMM) classifier structure. Simulation and experimental data will be presented for a single line dendrite and also experimental results for a dendrite-based classifier structure. This work builds on previously demonstrated building blocks of a neural network: the channel, synapses and dendrites using CMOS circuits. These structures can be used for speech and pattern recognition. The advantage of such a structure over digital systems is ultra low power consumption. In chapter 7, we will discuss how to build neuromorphic systems to be able to mimic biology and also solve more complex problems. To this end, we design neuromorphic chips using biologically inspired circuits. We build a neuron chip embedded in FPGA style routing architecture which models dendrites using transistors as discussed in previous chapters. I will discuss the Neuron2 chip in this chapter as well as the RASP 3.0N SoC, which belongs to the RASP 3.0 family but in addition to analog and digital components has neuron blocks as well.

In chapter 8, I will summarize the work done so far as well as future directions for this research which I hope to pursue.

#### **CHAPTER II**

#### RECONFIGURABLE SOC: RASP 3.0

Reconfigurable Analog Signal Processor (RASP) 3.0 is an integrated Ultra-Low Power System-On-Chip (SOC) enabling configurable and programmable analog and digital computation and interfacing. The potential of energy efficiency improvement over current computing approaches (i.e. a factor of 1000 or better) [34,35], as well as the saturation of energy efficiency in digital computation [36], puts this IC at an important industrial pain point for the embedded systems industry for a range of applications such as acoustic, vision, communications, and small robotics. We see this IC as both an analog-digital computational device as typical expected from a microprocessor ( $\mu$ P), as well as enabling analog and digital interfacing and control of an embedded system. We demonstrate this IC in a 350nm CMOS process; such approaches could be possible in scaled down IC processes as well.

This SoC integrates early concepts of rapid reconfigurable analog computation [37], along with early demonstration of configurable fabric of interdigitated analog and digital computing blocks [38], along with resulting  $\mu$ P (open-source MSP430 [39]) based computing and control, to address a wide range of ultra-low power embedded system computational needs. This large-scale Field-programmable analog array (FPAA) still enables analog computational energy efficiencies of 1000X as well as area efficiencies of 100X over digital solutions. The following sections describe this FPAA IC architecture, basic analog and digital computational approaches, capacitance, timing, and rapid reconfigurability of the configurable routing fabric, implementation of data converters in the mixed mode fabric, computation and classification utilizing the routing fabric as part of the computation, and system examples. The SoC is

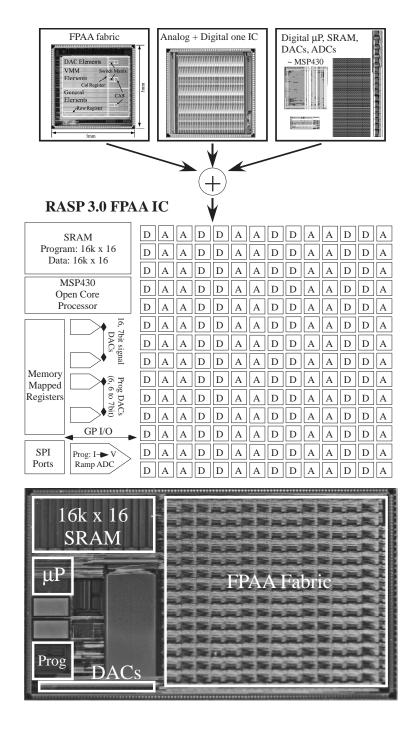

Figure 6: The RASP 3.0 integrates divergent concepts from previous multiple FPAA designs [37, 38, 40] along with low-power digital computation and interface circuitry (i.e. DACs, ADCs). This unified structure enables a wide range of a system-on-a-chip computing options that can be optimized for a wide range of parameters (i.e. Power); the resulting IC architecture is the most sophisticated FPAA device built to date. We show the die photo of the 12mm x 7mm FPAA device fabricated in a 350nm standard CMOS process.

### 2.1 Architecture Description of the FPAA SOC IC

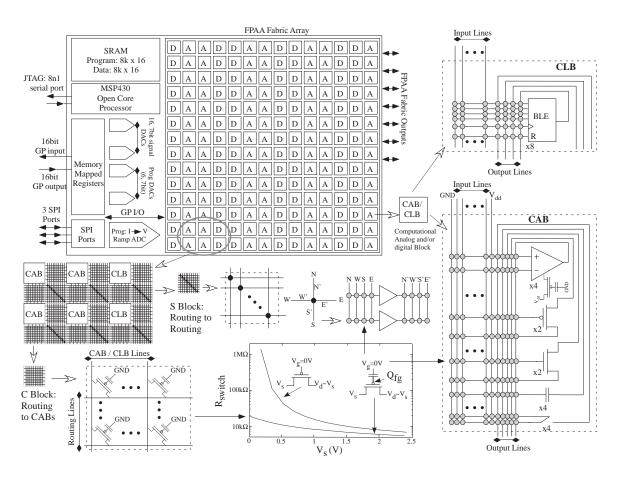

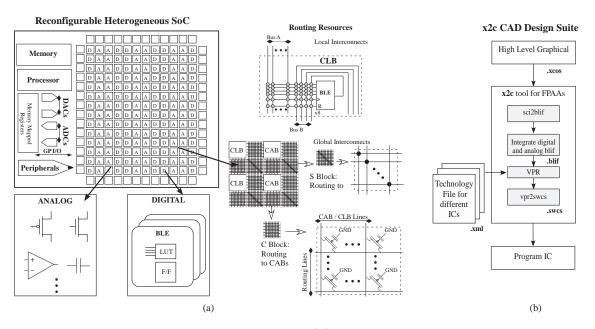

Figure 7: RASP 3.0 functional block diagram illustrating the resulting computational blocks and resulting routing architecture. We start showing the block diagram of the FPAA IC. The infrastructure control includes a  $\mu$ P developed from an open-core MSP 430 processor [39], as well as on chip structures include the on-chip DACs, current-to-voltage conversion, and voltage measurement, to program each Floating-Gate (FG) device. This configurable fabric device utilizes a manhattan geometry architecture to both effectively integrate analog (A) and digital (D) components, as well as build a compiler tool-friendly hardware platform. The floating-gate switches in the Connection (C) Blocks, the Switch Blocks (S), and the local routing are a single pFET Floating-Gate (FG) transistor programmed to be a closed switch over the entire fabric signal swing of 0 to 2.5V [69]. The Computational Analog Blocks (CAB) and Computational Logic Blocks (CLB) are similar to previous approaches [38]. Eight, 4 input Boolean Logic Element (BLE) lookup tables with a latch comprise the CLB blocks.

Figure 7 shows the block diagram for the RASP 3.0 FPAA IC based on a manhattan FPAA architecture, including the array of computation blocks and routing, composed of Connection (C) and Switch (S) blocks. The computation is a combination of the components in the Computational Analog Blocks (CAB) and Computational Logic Blocks (CLB), as well as utilizing the devices in the routing architectures that are programmed to non-binary levels. We use data-flow architectures for power-efficient computing to merge as much as possible computation and memory, minimizing the amount of external memory access required.

The architecture is based on Floating-Gate (FG) device, circuit, and system techniques. The programming approach, based on previous all-digital infrastructure concepts [41], is fully integrated on-chip. The  $\mu$ P and other control infrastructure allow all programming of FG devices on-chip by simply downloading the list of switches to be programmed. The code for programming is eliminated when the processor is executing, efficiently utilizing the on-chip SRAM capabilities. The external system, through a serial port interface, first loads the programming code, and then executes the programming code on the downloaded data. The details of the FG programming approach will be explained in further sections of this chapter.

The processor is able to send information to and from the array through memory mapped I/O special purpose peripherals. These peripherals include ADCs and DACs, allowing measurements to be performed on chip, with the data taken by and stored in the processor. There are 16 memory mapped 7bit signal DACs for the architecture, as well as additional DACs / ADC for the FG programming. The processor supplements the processing power of the digital portion of the system and increase overall implementation flexibility; portions of a problem can be mapped to reconfigurable analog, reconfigurable digital, or a general purpose digital processor.

This FPAA SOC, with a highly programmable, fine grain fabric enabling signal-processing approaches, practically requires a toolset for system design in a reasonable design timeframe. Using manhattan geometry enables the use and direct modification of open-source tools, like VPR [42], for the place and route approaches, a huge

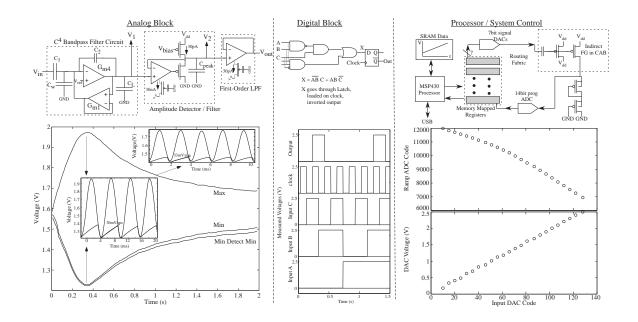

Figure 8: Approach for the RASP 3.0 FPAA IC enables integration of Analog and Digital Blocks in the routing fabric, as well as resulting standard digital computation (i.e. uP) and infrastructure. Analog Blocks: Compilation of single signal processing chain, including a second-order bandpass filter, amplitude detection, and smoothing of the output signal. Digital Blocks: We can compile digital blocks using the look-up tables in the CLB, the resulting latches in the CLB, as well as the routing fabric. We demonstrate basic capability in a single BLE element in a CLB for a simple combinatorial function. Digital Computation / Infrastructure: The  $\mu$ P design is an open-core MSP 430 processor with on-chip structures for 7-bit signal DACs, a ramp ADC, memory mapped General Purpose (GP) IO and related components. We show a measurement through a FG transistor in a CAB utilizing the processor, signal DACs and memory mapped register. We often instrument similar loops for instrumenting and measuring analog and digital blocks; in general we utilize all of these capabilities as part of the FPAA computation.

improvement over previous home grown tools [43] in both dense (system-level) compilation as well as optimizing routing infrastructure for digital and analog constraints. Our high level toolframework is recently built in Scilab / Xcos based on our earlier tool development in MATLAB / Simulink [44–46]. The graphical (i.e. Simulink) based compilation and macromodeling tool enables the FPAA to be an embedded system where the user has control over the resulting analog-digital co-design problem. The rest of the user control is through GUI interfaces. The detailed discussion of the recent tool flow is followed by this chapter. Higher-level tools also enable the use of these systems in educational experiences [47, 48], which will be essential to educating engineers to design for system applications.

Figure 8 shows our SOC FPAA approach enables integrated analog interfacing and computation, with digital blocks, both FPGA and  $\mu$ P blocks. We show the compilation of auditory processing chain for subband signal detection. Where possible, one wants to compile key blocks into a single CAB to minimize parasitic capacitances as well as minimize global routing requirements. The analog computation, utilizing significant innovations enabling integration of previous heterogeneous concepts [37,38,40], would seem familiar given our earlier FPAA designs. What is unique is the integration of digital low-power programmable and configurable FPGA fabric, first attempted in [38], to fully enable the routing of analog and digital signals through a continuous fabric. Further, we integrate these capabilities with an on-chip  $\mu P$  component and a range of digital communication ports (i.e. SPI ports), completing the picture that this FPAA device is a SoC computing device, not just a device for analog processing. Further, the interaction of analog computation, digital FPGA like components, and a  $\mu P$  infrastructure integrated together creates, in general, a significant co-design problem between these three domains, requiring significant innovations in design tools. Presenting our revised design tools is beyond the scope of this discussion, which is an entire discussion in its own right.

### 2.2 SOC FPAA Routing Fabric Characterization and Computation

From a classical FPGA approach, one considers the capability of the device to be in its components (CLBs, specialized blocks), and the routing fabric is simply a capability to interconnect these components. In such an approach, we want to minimize the effect of the routing fabric that from a circuit perspective is dead weight that can only degrade the circuit. That approach requires minimizing the amount of switches, each of which add resistance, as well as minimize the resulting capacitance of the routing. The routing infrastructure can effectively be modeled as a distributed RC line. The architecture choices look at the relationship of the resulting switch resistances, or

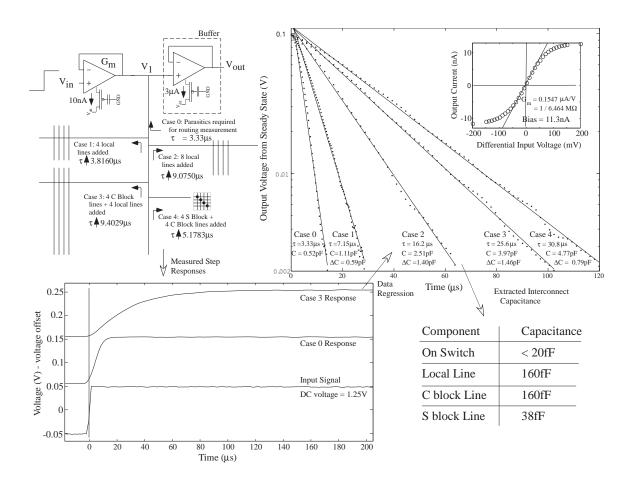

Figure 9: Experimental measurements for characterizing the capacitances of the routing fabric. These FPAAs enable programming experiments that characterize the fundamental properties of the configurable fabric. We first measure the current-voltage relationship for a specific OTA device, shown in the inset, to exactly find the resulting Gm  $(0.1547\mu\text{A/V})$  of the device. Then we use that exact OTA with the same programmed current to measure the time-constant of the step response (on a 1.2V dc for the 2.5V supply) for different (additive) routing combinations. In the presented measurement, we measure the resulting step responses, and from that we can linearly curve fit to the time constant after removing the effect of the steady state voltage. The resulting measurements give a measurement of the resulting routing capacitance, as well as enables, through the routing fabric, a range of tunable capacitor blocks. We summarize multiple measurement configurations for our values of routing capacitances.

other circuit uses of the FG switch devices, as a function of the number of CAB inputs and number of tracks, as well as the typical number of switches needed for a connection.

This FPAA structure enables directly characterizing the resulting capacitance; coupled with the resistance of an on-switch  $(5-10k\Omega)$  programmed at the maximum conductance point) we can directly predict delays along each of these lines. Figure

9 illustrates we can compile circuits to characterize precisely the behavior of these circuits, including load capacitance of the fabric itself. Every experiment is same voltage bias, so expect that p-n junction capacitances would be similar through this experiment. Precise measurement of routing capacitances enable tuning, through programming switches, for precise capacitances where needed for matching. Matching of capacitances and programmability of current sources by FG techniques dramatically reduces the effect of mismatch in small cell sizes.

But our approach further moves away from the classical FPGA approach, in a radical perspective that, because we can program FG devices to analog levels, our routing fabric is no longer dead weight, as we first hypothesized previously [49] and fully implemented in our SOC FPAA.

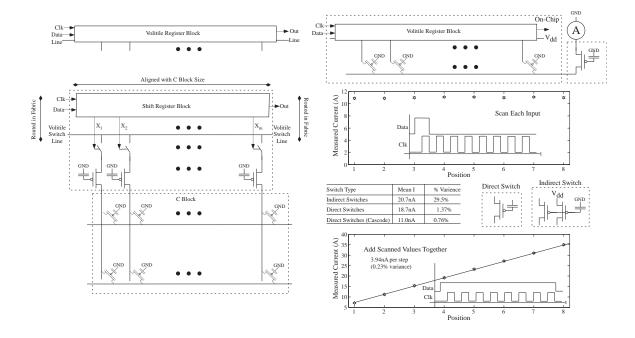

We begin by describing one aspect of our routing fabric used for computation tied with capability for rapid reconfigurability. Figure 10 shows additional routing structure enabling rapid reconfigurability in the FPAA fabric. Essential to analog structures, typically data flow, and want to configure the computation to optimally minimize the amount of intermediate data storage. Intermediate data storage often the largest power and complexity cost for a system development. We have developed rapid reconfigurability in the fabric such that we can change between programmed aspects in a single clock cycle or asynchronous request—acknowledge loop. SOC FPAA shift register control signals are controlled by locally routed signals in the fabric controlling the clock (CK) and data signals. Data stored in the FG fabric would be as optimal as data stored in an off-chip nonvolatile memory without the complexity of loading the resulting computation. We also see the first illustration of using the routing fabric elements, this time as a bank of parallel current sources, as well as a cascading transistor. One easily sees an Arbitrary Waveform Generator that could be compiled into the fabric; the circuit also becomes the non-volatile memory for the

Figure 10: Additional aspects of our FPAA Routing Fabric. We include a set of T-gate based switch elements in the routing fabric to enable rapid reconfigurability. These switches are accessed through a shift register that enables rapid change of configuration on a single clock cycle; different lines of the resulting C block and/or local routing store the different configurations. We represent the resulting switches, resulting shift register, and switches connecting the block to the routing fabric as a single volatile routing block. We illustrated this capability utilizing routing elements programmed as precision current source elements, both using an input to the shift register input to scan through the individual signals, as well as using an input to the shift register to accumulate the resulting outputs through the individual signals. It is straight-forward to imagine a range of arbitrary waveform generation based on patterns stored in routing fabric. This measurement gives a metric of programming accuracy in operational mode. The accuracy for these switches ranged 0.2 to 0.76 percent for programmed subthreshold currents for uncorrected FG values; the resulting accuracy can be improved after such an initial measurement. Further, some switches in the routing fabric use only a single pFET transistor (Direct Switches), while some use two pFET transistors (Indirect Switches), where one device is used for computation and one device is used for programming. The Indirect switches show characteristically higher mismatch for uncorrected FG programming due to the threshold voltage mismatch of the two pFET devices. GND is signal GND; we bias the gate terminal for the FG devices at 0.6V.

function, eliminating outside memory and resulting complexity and energy requirements. The measurements show the accuracy of the FG transistor programming, either in the FG voltage or resulting channel current. We notice accuracy tighter than 1 percent in sub threshold, relating to less than  $250\mu\text{V}$  variation.

The difference between directly programmed and indirectly programmed floatinggates is whether or not current measurements are made on the circuit transistor or

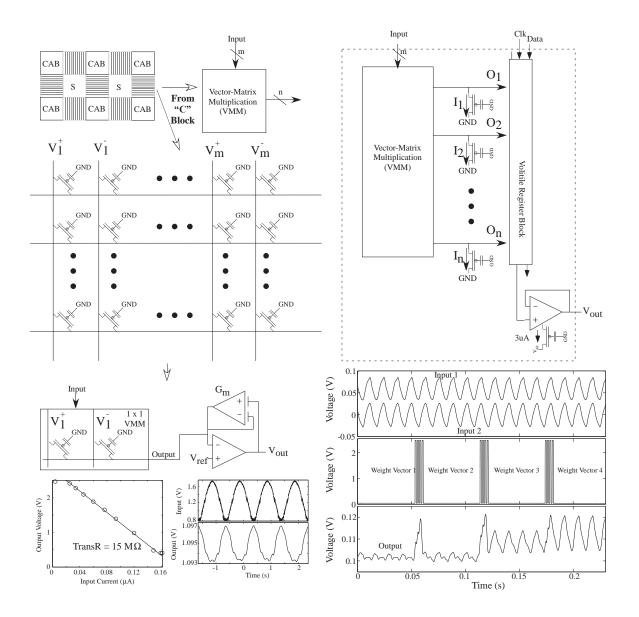

Figure 11: Vector-Matrix Multiplication (VMM) as a computational block instantiated in C Block routing fabric. The C Block forms a natural crossbar network typical for a VMM computation. We show the data for a single VMM element through routing fabric to illustrate the basic behavior; two pFET transistors are required for source-input 4-quadrant multiplication. We independently measure the resulting transresistance as  $15\mathrm{M}\Omega$ . Further, we show an application of VMM integrated with the volatile switch register block to enable rapid (single-clock) switching between weight vectors.

the injection transistor during the programming algorithm. In the direct case, both the circuit and injection transistor are the same transistor. In the indirect case, they are two separate transistors. The indirect FG device leads to a more efficient switch (fewer parasitics), but one must account for the  $V_{T0}$  mismatch between the two pFET devices. The direct FG device programs, measures, and computes through the same

device, eliminating any  $V_{T0}$  mismatch, requires additional transmission gates in the signal path for programming.

Computing Vector-Matrix Multiplication (VMM) solidifies the radical use of routing fabric as a computational element. Figure 11 shows implementation of a VMM in the routing fabric of our FPAA structure. We implement this functionality either in the C block or in the local CAB / CLB routing fabric, being that both structures are naturally crossbar arrays. Longer discussion on VMMs in early FPAA routing fabric is described elsewhere [50]. Further, we are effectively computing through our memory device, effectively the EEPROM storage of our values, directly in routing fabric, enabling the VMM computation; other approaches, including traditional FPGA approaches, require additional memory elsewhere from the resulting computations required. Further, we show integrated VMM and rapid reconfigurability enabling switching between metrics in the FPAA architecture. This feature further enables data flow architectures to do a particular computation right when data arrives, reducing the need for short-term storage.

# 2.3 Representative Circuit and Signal Processing Components in the SOC FPAA

After considering the basic computation of the key components as well as the behavior and computation of the routing fabric, we move to looking at the behavior for some basic mixed-signal processing circuits compiled and experimentally measured in this system. The circuits illustrate some of the analog-digital co-design in these approaches.

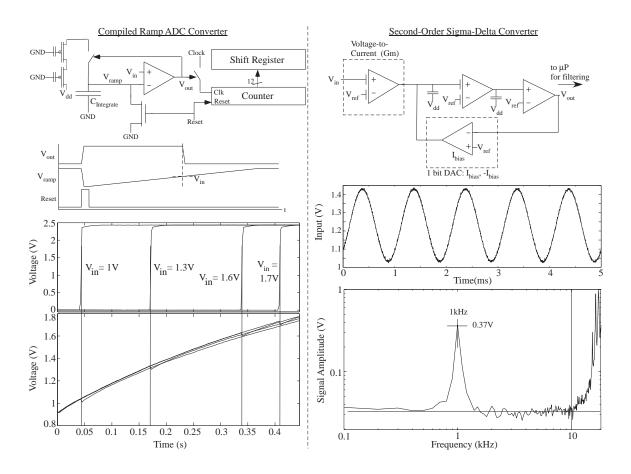

Our first example is compiling two basic ADC devices in the routing fabric. Figure 12 shows circuit compilation at the analog-digital boundary through compilation of multiple forms of ADCs as an example of integration of the capabilities. Being able to compile an ADC, and the particularly needed ADC both allows for optimal power computation, heavy IP block reuse, as well as allowing the system lines to be blurred

Figure 12: Two compiled Analog-to-Digital Converters (ADC) with experimental results. These approaches show the mixed signal structure compiled on our analog and digital enabled routing fabric. One example shows a compiled Ramp ADC converter. The second example shows a compiled second-order Sigma-Delta ( $\Sigma$  -  $\Delta$ ) converter.

between analog and digital for more effective approaches of classifying raw analog data. The design of the routing fabric was not a block of analog components and a block of digital components with hard-build data converters in between, but rather a mixed fabric to explicitly allow the lines to be blurred as the application requires.

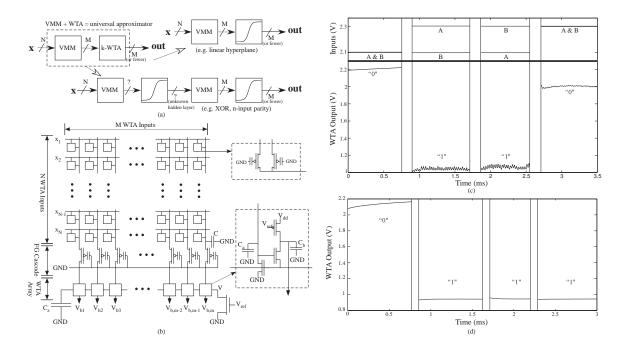

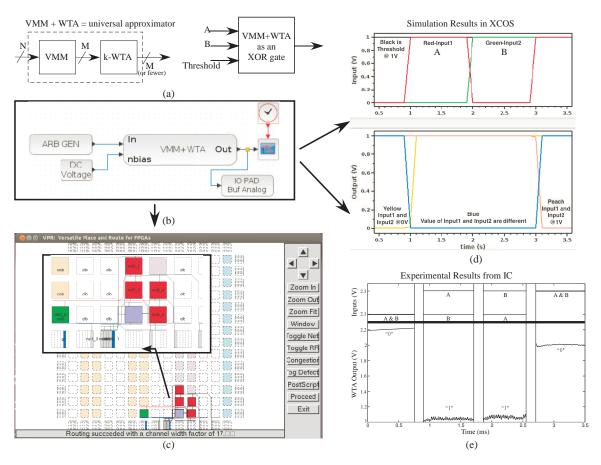

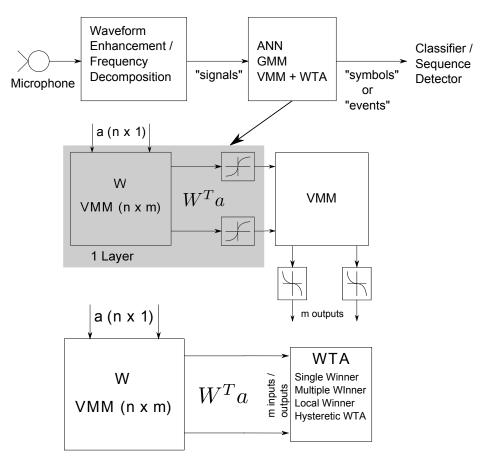

Our second example is a basic FPAA classifier using a single Layer VMM + Winner-Take-All (WTA) circuit as a non-ADC conversion between analog and digital signals. Figure 13 shows a one-layer classifier approach based on the combination of a VMM and a k-winner Winner-Take-All (WTA) circuit [51], that elegantly compiles into routing fabric [52]. The one layer architecture can perform standard one-layer hyperplane classifiers, while also performing tasks considered impossible for

Figure 13: Instantiated FPAA classifier block based on a combination of VMM with a Winner-Take-All (WTA) block enabling a compiled one-layer universal approximator that efficiently compiles into an FPAA device. We show the circuit block for the one-layer VMM + WTA classifier block for N inputs and M outputs. The WTA circuit is operated as a single winner circuit, or as a k-WTA circuit, where upto K winners are possible if their metric is above a basic threshold, as originally described in [12]. We show an example of a single hyperplane classification, as well as an example of an n-input parity classification, experimentally verifying the universal approximator approach. (need a block diagram of VMM + WTA type block)

typical one-layer Neural Network architectures (i.e. XOR). Figure 13 shows experimental measurements for both of these cases, both an XOR function, as well as a linear approximator function. The result experimentally verifies that this one-layer VMM+WTA architecture, compiled on this RASP 3.0 FPAA structure is a universal approximator.

## 2.4 Representative System Application in the SOC FPAA

Following the example of signal processing circuits compiled in the SOC FPAA, we move in this section to discussing two representative applications compiled and measured on this SOC FPAA. The goal of this section is showing two possible application opportunities; we expect the wider range of applications for sound / acoustics / speech applications, image processing and vision sensors, robotics applications, and wireless

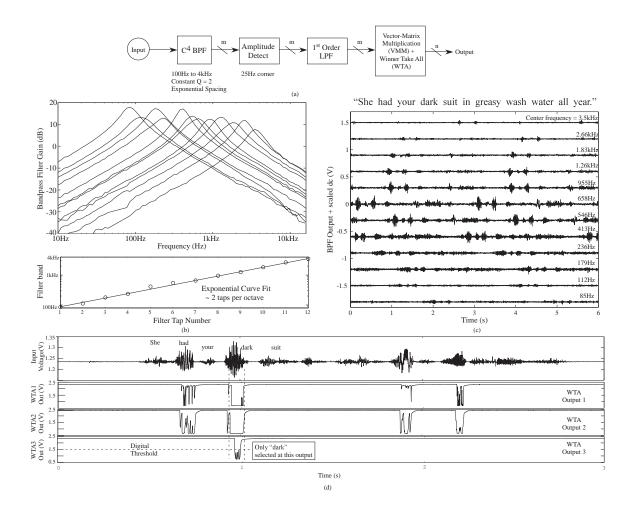

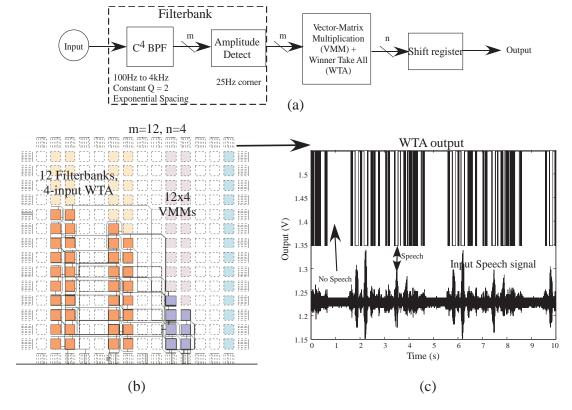

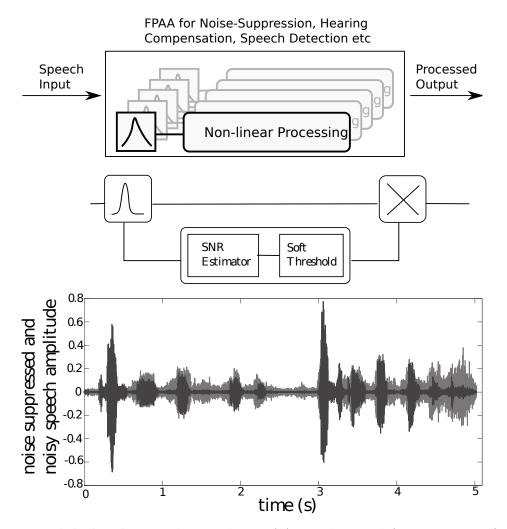

Figure 14: Analog auditory word classification application, compiled into the RASP 3.0, showing the experimental waveforms from the IC. (a) Block diagram for the classifier algorithm, in a similar representation used for our tool framework. (b) We use BPF center frequencies that are scaled evenly on a log-frequency scale between 100Hz and 4kHz with a constant Q filters (Q=2). (c) We show BandPass Filter (BPF) outputs and Amplitude Detection for a single phrase from the TIMIT database. (d) Classification of word and components for a TIMIT waveform. We use a k-WTA with three outputs to detect the ford "dark" in the resulting phrase.

communication applications, will be the subject of many future research where each system itself is a significant circuit and system design that can be experimentally implemented in this SOC FPAA IC.

We show an example application of auditory / speech classification looking at detecting a command word in a sentence. Figure 14 shows the first application example of an auditory classifier structure for a limited phrase, like a command word, that can be classified through features in the averaged signal spectrum. We start using a

continuous-time spectrum decomposition using a bank of constant Q filters, using a bank of amplitude detection and filtering operations, and then using a VMM+WTA classifier block to classify each of the resulting spectrum into simple symbols. In a more complex speech recognition system, we might have the spectrum correspond to phonemes or part of phonemes and build up the temporal representations using temporal classification (i.e. HMM classification) to word spot the resulting phonemes, syllables and words. In a simple command word application, we only need to distinguish between a few simple symbols, directly computed as a state machine on the MSP430 processor; a next level of computation, say as a simple Viterbi decoder, could be directly implemented on the MSP430 processor as well.

## 2.5 Summary Discussion and Comparisons

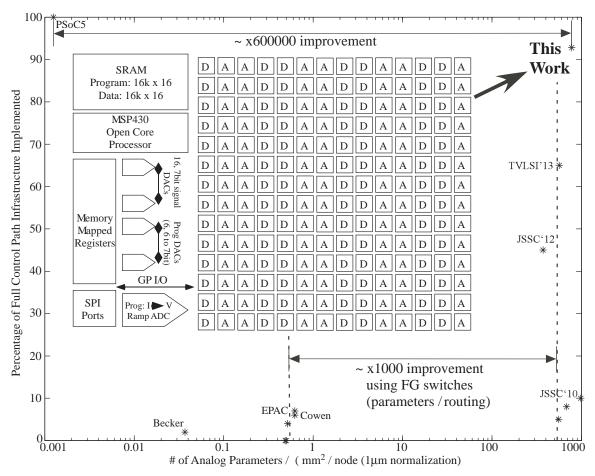

We presented an IC that integrates divergent concepts from previous multiple FPAA designs along with low-power digital computation and interface circuitry (i.e. DACs, ADCs). We showed through discussion and measured data that this unified structure enables a wide range of SoC computing options that can be optimized for a wide range of parameters, showing the most sophisticated FPAA capability built to date; we hope that the success of this IC inspires additional devices build in the near future. Figure 15 shows the table of parameters for the resulting SOC FPAA. Largest signal processing functions shown to date [37, 38, 65], where each are only taking a small percentage of the available IC.

Using data from generations of FPAA devices, built at GT and elsewhere, we plot various FPAA devices showing the (Percentage of Control Path implemented) vs. Analog Parameter Density. Figure 15 shows two key metrics for FPAA approaches based on a wide range of published FPAA devices [37,38,40,58–69]. We define analog parameter density as the number of programmable parameters per mm<sup>2</sup>, normalized

to a  $1\mu$ m CMOS node. Analog parameter density determines critically the IC computation complexity, particularly when using routing as computation. Figure 15 shows FG based FPAAs enable  $\approx 1000$  improvement in parameter density, enabling orders of magnitude potential computation on a single device; alternatives to FG devices require a DAC at every node or similar dynamic techniques.

One could imagine a second metric of maximum measured frequency, normalized to  $1\mu m$  process. The result is very predictable and we find maximum analog frequency response being directly related to process technology; we have compared FPAA devices from  $1\mu$  CMOS to 40nm CMOS. Detailed discussions about frequency scaling will be discussed in a further discussion and demonstration of FPAA scaling and is beyond the scope of this discussion.

For an SOC FPAA device, we would want to maximize both metrics, so that we have a large number of programmable parameters, and resulting computation, as well as having the infrastructure to get data communicated to these processing devices. We develop the second metric to describe the the amount of control flow (mostly digital) relative to the amount of analog and digital data flow capability. Practically, the ability to get data to all of the processors can be a primary limitation for a range of application spaces, such as image processing, where data does not always arrive in the desired order for the computation. Recent RASP based FPAA designs [37,38] have started to focus on improving this second metric while not losing the analog parameter density efficiency. The presented SOC FPAA device maximizes both metrics, being nearly a factor of 500 improvement in area efficiency as typical of other analog FPAA devices, but with high utilization of the resulting computational resources; the closest high utilization structure (i,e, like PSoC5) is nearly a 300,000 factor improvement. This work resulted in the journal [126].

| Parameter           | Value              | Parameter               | Value      |

|---------------------|--------------------|-------------------------|------------|

| Number of CABs      | 98                 | Number of CLBs          | 98         |

| On Chip $\mu P$     | Open Source MSP430 | $\mu$ P clock frequency | 0 - 50MHz  |

| C block Line Cap.   | 160fF              | S Block Line Cap.       | 160fF      |

| $V_{dd}$ (analog)   | 2.5V               | $V_{dd}$ (digital)      | 2.5V, 3.3V |

| $V_{dd}$ Injection  | 6.0V               | $V_{dd}$ Tunneling      | 12V        |

| Program Memory      | 16k x 16           | Data Memory             | 16k x 16   |

| CMOS Process        | Standard 350nm     | Die Size                | 12mm x 7mm |

| General Digital I/O | 16 (in), 16(out)   | SPI ports               | 5          |

| General Analog I/O  | 125                | Analog Parameters       | 359,014    |

Figure 15: Using data from generations of FPAA devices, built at GT and elsewhere, we plot various FPAA devices showing the Percentage of Control Path implemented versus Analog Parameter Density. Recent FPAA ICs, like the dynamically reconfigurable FPAA or FPAADD device begin to effectively maximize both parameters. Analog Parameter Density is the number of analog parameters per mm<sup>2</sup>, normalized to a  $1\mu$ m process (or analog parameter density). Analog parameters directly sets the complexity possible by the particular FPAA device. Further, we include a table of relevant parameters for our SOC FPAA device.

## CHAPTER III

## CAD SYNTHESIS TOOLS FOR HETEROGENEOUS SOCS

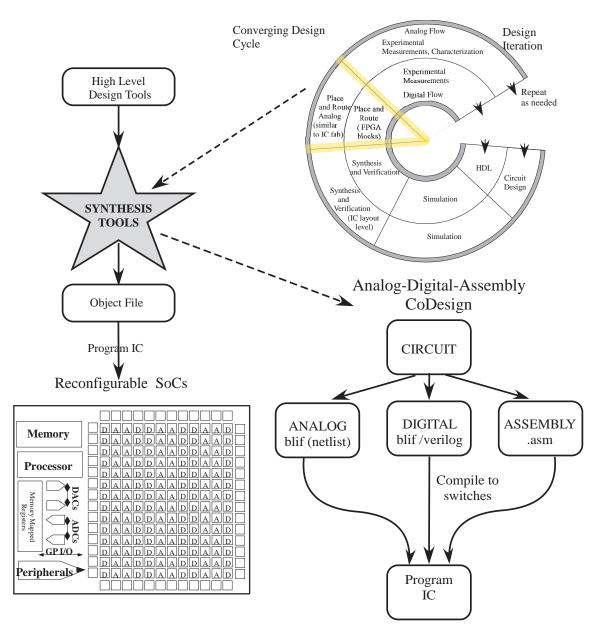

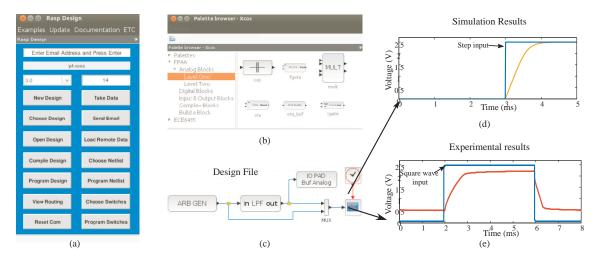

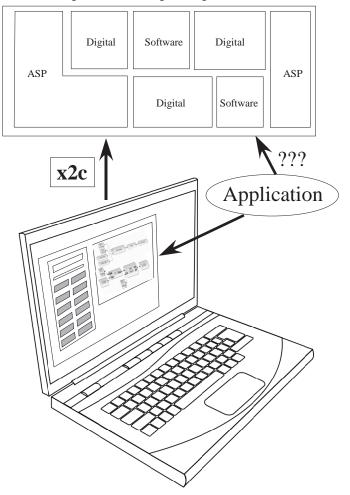

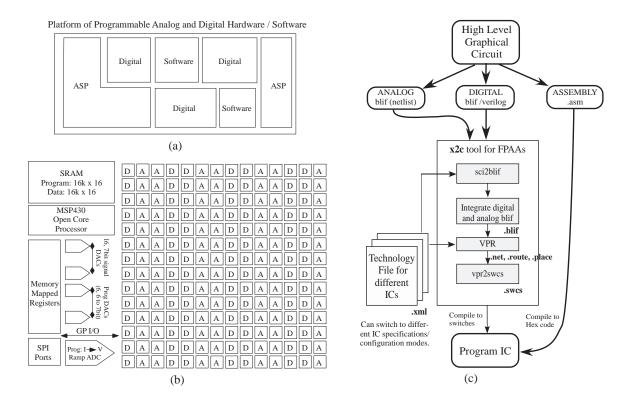

Field Programmable Gate Arrays (FPGAs) have evolved a lot over the past twenty years and have been rapidly adopted in industry, academia as well as by end users worldwide for a variety of applications. This has been possible due to powerful CAD tools for architectural exploration, CAD algorithm research and open source efforts [121, 148–150]. On the other hand, reconfigurable analog technologies have been lagging behind because of lack of such a rich toolset. Our endeavor is to build an integrated CAD tool framework that is a trailblazer for analog tool solutions for Field Programmable Analog Arrays (FPAAs) for shorter design turnaround times as shown in Fig. 16. Typically analog design is considered niche. We believe this will revolutionize analog design as we know it and enable a wider group of people to test analog, digital and mixed signal designs. Our tool suite **x2c** -Xcos to Chip, generates and integrates these tools to program and test an FPAA SoC. It enables fast and accurate co-simulations in both hardware and software. This methodology empowers the user to do seamless low power analog, digital and mixed signal design in a single environment from a graphical frontend to a switch list to target the SoC and test design.

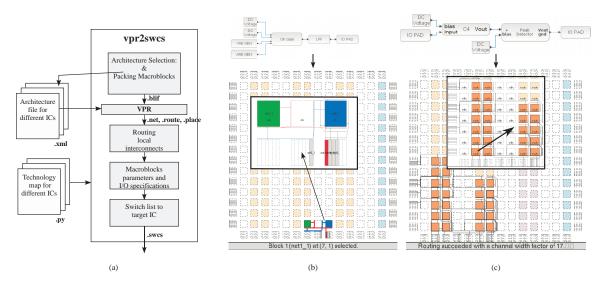

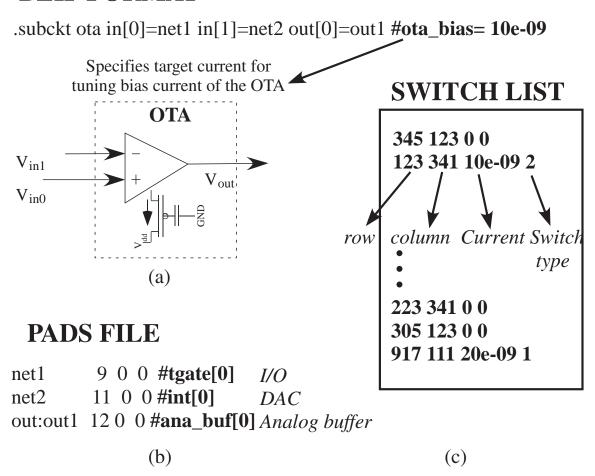

In this chapter, I present a new synthesis, place and route tool called **vpr2swcs** which is a part of this tool suite and converts a netlist to an object file needed to program the FPAA SoC. These SoCs consist of a digital processor, an FPAA consisting of both digital and analog blocks in a reconfigurable switch fabric, DACs, ADCs and peripherals. This approach is novel as it enables, analog, digital and assembly codesign in the same environment. It also allows advanced synthesis by converting

Figure 16: Typical iterative flow for CAD tools to design Integrated Circuits is illustrated here. Consider one such cycle, showing the design, simulation, synthesis, and testing for the analog and digital flows of the design. Reconfigurable ICs enable rapid turnaround time for testing. We have developed a software tool suite **x2c**, enabling design, simulation, verification, and experimental testing for configurable heterogeneous SoCs in a single environment.

a netlist to a programmed system on the hardware. Our approach embeds existing Virtual Place and Route (VPR) tool typically used for FPGAs in the modular python based tool *vpr2swcs* to develop a coherent user friendly design flow for heterogeneous

architectures. Though VPR treats analog blocks as a blackbox, *vpr2swcs* contains detailed descriptions of analog blocks. It effectively combines digital solutions from VPR along with custom techniques for analog circuits.

In this chapter, the focus is on the synthesis, place and route aspect of these heterogeneous SoCs and the tool called vpr2swcs that was developed to target FPAA SoCs. Previously a tool called Generic Reconfigurable Architecture Specification and Programming Environment or GRASPER was used for FPAA ICs which were based on a more crossbar routing structure [151]. This tool is a significant improvement over the previous tool. It can now be used for exploring heterogeneous architectures as well as for scaling systems. One particular novel piece of vpr2swcs is the ability to build useful computation out of routing resources. The synthesis and place and route of circuits containing Vector Matrix Multiplier (VMMs) [152] built out of floating-gate switches will also be highlighted in this chapter.

## 3.1 CAD Tools for Reconfigurable Hardware: Overview