# ARCHITECTING HETEROGENEOUS MEMORY SYSTEMS WITH 3D DIE-STACKED MEMORY

A Dissertation Presented to The Academic Faculty

by

Jaewoong Sim

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2015

Copyright © 2015 by Jaewoong Sim

# ARCHITECTING HETEROGENEOUS MEMORY SYSTEMS WITH 3D DIE-STACKED MEMORY

Approved by:

Dr. Hyesoon Kim, Advisor School of Computer Science *Georgia Institute of Technology*

Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Milos Prvulovic School of Computer Science Georgia Institute of Technology Dr. Moinuddin K. Qureshi School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Gabriel H. Loh AMD Research Advanced Micro Devices

Date Approved: 16 July 2015

### ACKNOWLEDGEMENTS

First of all, I would like to express my sincere gratitude to my advisor, Hyesoon Kim, for her guidance, support, and encouragement. She is the definition of a great advisor. She has provided me with every opportunity to conduct the highest quality of research while allowing me the freedom to pursue research topics that I was interested in. Her technical creativity, insightful feedback, and high standards for research have tremendously helped me focus on important problems, refine ideas, and write strong papers with a high level of clarity. I am extremely fortunate to have her as my advisor, and I can only hope that someday I will be as good as her.

I am also very fortunate to have the opportunity to work with Gabriel Loh at AMD Research. He has been a fantastic mentor, and I had great fun working with him. His sharp intellect and superb mentoring skills had a profound influence on my graduate career, and I have great respect for him as a mentor, a researcher, and a friend.

I would like to thank other members of my dissertation committee, Moinuddin Qureshi, Sudhakar Yalamanchili and Milos Prvulovic, for invaluable comments and feedback to improve this dissertation. In particular, I am grateful to Moinuddin Qureshi for motivating me with interesting research ideas and providing me with valuable advice and help during my graduate studies.

At Georgia Tech, I had great moments with my friends and colleagues. In particular, I owe many thanks to the HPArch members: Jaekyu Lee, Nagesh Lakshminarayana, Sunpyo Hong, Joo Hwan Lee, Minjang Kim, Pranith Kumar, Hyojong Kim, Jen-Cheng Huang, Dilan Manatunga, Prasun Gera, and Lifeng Nai. I also thank Sungkap Yeo, Seungjoon Paik, Daehyun Kim, Davide Pluda, Aaron Ciaghi, Seunghwa Kang, Nimit Nigania, Puyan Lotfi, Andrei Bersatti, Manoj Athreya, Jungju Oh, Ching-Kai Liang, and Sunjae Park.

I am fortunate to work with wonderful researchers outside of Georgia Tech. I would like to thank Chris Wilkerson, Alaa Alameldeen, Zeshan Chishti, and Shih-Lien Lu for their mentorship and friendship at Intel Labs. I also thank Vilas Sridharan, Mike O'Connor, and Mithuna Thottethodi for their help on my research.

Above all, I am deeply thankful to my parents, Wonsub Sim and Jungsoon Park. They have given me unconditional love and always supported my decisions throughout my life. Thank you and I love you.

# TABLE OF CONTENTS

| AC  | KNO          | WLED    | GEMENTS                                                                                | iii |

|-----|--------------|---------|----------------------------------------------------------------------------------------|-----|

| LIS | T OF         | TABL    | ES                                                                                     | X   |

| LIS | T OF         | FIGUI   | RES                                                                                    | xi  |

| SUI | MMA          | RY.     |                                                                                        | XV  |

| Ι   | INTRODUCTION |         |                                                                                        |     |

|     | 1.1          | The Pr  | roblem: Unpromising Conventional Memory Systems                                        | 1   |

|     | 1.2          |         | Contributions: Efficiently Architecting Die-Stacked Memory and ogeneous Memory Systems | 2   |

|     | 1.3          | Thesis  | Statement                                                                              | 6   |

|     | 1.4          | Disser  | tation Organization                                                                    | 6   |

| II  | BAC          | CKGRO   | OUND AND RELATED WORK                                                                  | 7   |

|     | 2.1          | DRAN    | A Architecture                                                                         | 7   |

|     | 2.2          | Error ( | Correcting Code for Conventional DRAM                                                  | 8   |

|     | 2.3          | Die-St  | acked DRAM Organization                                                                | 9   |

|     | 2.4          | DRAN    | A Failure Modes                                                                        | 10  |

|     | 2.5          | Die-St  | acked DRAM Caches                                                                      | 11  |

|     | 2.6          | Relate  | d Work                                                                                 | 13  |

|     |              | 2.6.1   | Related Work on Heterogeneous Memory Systems                                           | 13  |

|     |              | 2.6.2   | Related Work on RAS Support                                                            | 15  |

| III | AN           | EFFIC   | IENT DIE-STACKED DRAM CACHE                                                            | 17  |

|     | 3.1          | The Pr  | oblems                                                                                 | 17  |

|     |              | 3.1.1   | The Overkill of the MissMap                                                            | 17  |

|     |              | 3.1.2   | Under-Utilization of Aggregate System Bandwidth                                        | 18  |

|     |              | 3.1.3   | Obstacles Imposed by Dirty Data                                                        | 20  |

|     | 3.2          | DRAN    | A Cache Hit Speculation                                                                | 21  |

|     |              | 3.2.1   | Region-Based Hit-Miss Prediction                                                       | 21  |

|    |     | 3.2.2   | Multi-Granular Hit-Miss Predictor        | 23 |

|----|-----|---------|------------------------------------------|----|

|    |     | 3.2.3   | Predictor Operation                      | 24 |

|    |     | 3.2.4   | Implementation Cost                      | 25 |

|    | 3.3 | Exploi  | ting Unused Bandwidth                    | 25 |

|    | 3.4 | Mainta  | aining a Mostly-Clean Cache              | 27 |

|    |     | 3.4.1   | Write-Through vs. Write-Back             | 28 |

|    |     | 3.4.2   | The Dirty Region Tracker                 | 29 |

|    |     | 3.4.3   | Putting the DiRT to Work                 | 30 |

|    |     | 3.4.4   | Putting It All Together                  | 32 |

|    |     | 3.4.5   | DiRT Implementation Cost                 | 32 |

|    | 3.5 | Experi  | mental Methodology                       | 33 |

|    | 3.6 | Result  | s and Analysis                           | 35 |

|    |     | 3.6.1   | Performance                              | 35 |

|    |     | 3.6.2   | HMP: Prediction Accuracy                 | 37 |

|    |     | 3.6.3   | SBD: Percentage of Balanced Hit Requests | 38 |

|    |     | 3.6.4   | DiRT: Benefit and Traffic                | 39 |

|    |     | 3.6.5   | Sensitivity Results                      | 40 |

|    | 3.7 | Summ    | ary                                      | 43 |

| IV | AR  | ESILIE  | NT DIE-STACKED DRAM CACHE                | 44 |

|    | 4.1 | Applyi  | ing Conventional ECC to Stacked DRAM     | 44 |

|    | 4.2 | Object  | ive and Requirements                     | 45 |

|    | 4.3 | Isolate | d Fault Types in DRAM Caches             | 46 |

|    |     | 4.3.1   | Supporting Single-Bit Error Correction   | 46 |

|    |     | 4.3.2   | Supporting Multi-Bit Error Detection     | 48 |

|    |     | 4.3.3   | Discussions                              | 50 |

|    | 4.4 | Coarse  | e-Grain Failures in DRAM Caches          | 51 |

|    |     | 4.4.1   | Identifying Coarse-Grain Failures        | 52 |

|    |     | 4.4.2   | DOW: Duplicate-on-Write                  | 54 |

|    |     | 4.4.3   | Summary of Coverage                      | 57 |

|   |     | 4.4.4  | Optimizations for DOW                          | 58 |

|---|-----|--------|------------------------------------------------|----|

|   | 4.5 | Experi | mental Results                                 | 59 |

|   |     | 4.5.1  | Methodology                                    | 59 |

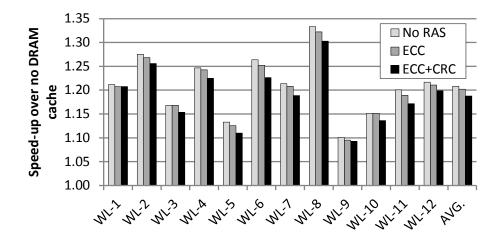

|   |     | 4.5.2  | Fine-Grain Protection                          | 63 |

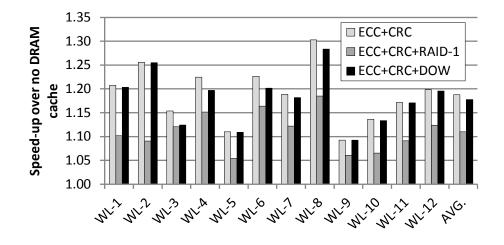

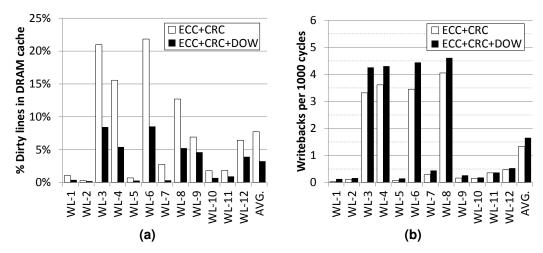

|   |     | 4.5.3  | Coarse-Grain Protection                        | 63 |

|   |     | 4.5.4  | Fault Coverage and Failure Rates               | 64 |

|   | 4.6 | Analys | sis and Discussions                            | 66 |

|   |     | 4.6.1  | Reliability Impact on Large System Sizes       | 66 |

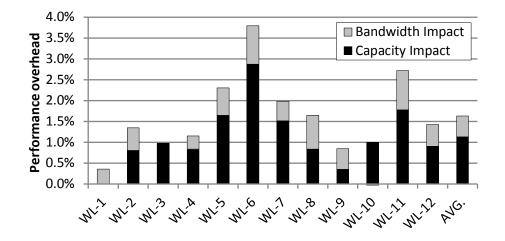

|   |     | 4.6.2  | Capacity and Bandwidth Impact                  | 66 |

|   |     | 4.6.3  | Impact of Early Data Return                    | 67 |

|   |     | 4.6.4  | Duplication Overheads of DOW                   | 68 |

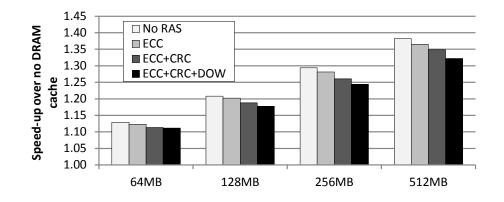

|   |     | 4.6.5  | Sensitivity to Cache Size                      | 69 |

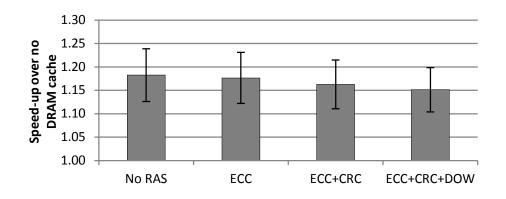

|   |     | 4.6.6  | Sensitivity to Different Workloads             | 69 |

|   |     | 4.6.7  | Value of Configurable RAS Levels               | 70 |

|   | 4.7 | Summ   | ary                                            | 71 |

| V | MA  | NAGEN  | MENT OF STACKED DRAM AS PART OF MEMORY         | 72 |

|   | 5.1 | Stacke | d DRAM as Part of Main Memory                  | 72 |

|   |     | 5.1.1  | Dynamic PoM Management                         | 73 |

|   |     | 5.1.2  | Potential of Hardware-Managed PoM Architecture | 74 |

|   | 5.2 | Challe | nges of Hardware-Managed PoM                   | 75 |

|   |     | 5.2.1  | Hardware-Managed Indirection                   | 75 |

|   |     | 5.2.2  | Swapping Overhead                              | 76 |

|   |     | 5.2.3  | Memory Activity Tracking and Replacement       | 77 |

|   |     | 5.2.4  | Objective and Requirements                     | 78 |

|   | 5.3 | A Prac | tical PoM Architecture                         | 78 |

|   |     | 5.3.1  | Design Overview                                | 78 |

|   |     | 5.3.2  | Segment-Restricted Remapping                   | 80 |

|   |     | 5.3.3  | Segment Allocation/Deallocation: Cache vs. PoM | 81 |

|   |     | 5.3.4  | Segment Remapping Table (SRT)                  | 84 |

|    |     | 5.3.5  | Segment Remapping Cache (SRC)                     |

|----|-----|--------|---------------------------------------------------|

|    |     | 5.3.6  | Segment Activity Tracking                         |

|    | 5.4 | Experi | mental Methodology                                |

|    | 5.5 | Experi | mental Evaluations                                |

|    |     | 5.5.1  | Performance Results                               |

|    |     | 5.5.2  | Effectiveness of Remapping Cache                  |

|    |     | 5.5.3  | Sensitivity to Remapping Cache Size               |

|    |     | 5.5.4  | Swapping Overhead                                 |

|    |     | 5.5.5  | Sensitivity to Swap Granularity                   |

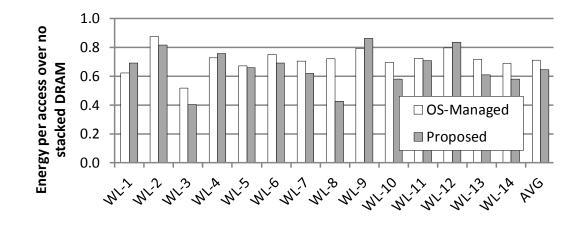

|    |     | 5.5.6  | Energy Comparison                                 |

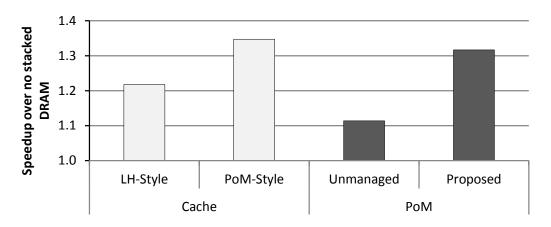

|    |     | 5.5.7  | Comparison to Hardware-Managed Cache              |

|    |     | 5.5.8  | Sensitivity to Fast to Slow Memory Capacity Ratio |

|    |     | 5.5.9  | Transparency to Virtual Memory Subsystem          |

|    | 5.6 | Summ   | ary                                               |

| VI | STA | CKED   | DRAM INTERACTING WITH OPEARTING SYSTEMS 101       |

|    | 6.1 | Stacke | d DRAM as Temporary Swap Space                    |

|    |     | 6.1.1  | Virtual Memory and Swap                           |

|    |     | 6.1.2  | Interaction of Stacked DRAM and Swapping          |

|    |     | 6.1.3  | Design Objectives                                 |

|    | 6.2 | Cache  | Swap: Swappable DRAM Cache                        |

|    |     | 6.2.1  | Overview                                          |

|    |     | 6.2.2  | Converting Cache Capacity to Interim Swap         |

|    |     | 6.2.3  | Reverting Interim Swap Back to Cache              |

|    |     | 6.2.4  | When to Convert Cache to Interim Swap (and Back)  |

|    |     | 6.2.5  | HW-SW Interfaces                                  |

|    | 6.3 | Cache  | vs. Interim Swap Sizing Options                   |

|    |     | 6.3.1  | All-or-Nothing                                    |

|    |     | 6.3.2  | Halving                                           |

|    |     |        |                                                   |

| REF | REFERENCES |         |                                         |  |  |

|-----|------------|---------|-----------------------------------------|--|--|

| VII | CON        | ICLUS   | IONS AND FUTURE WORK                    |  |  |

|     | 6.6        | Summa   | ary                                     |  |  |

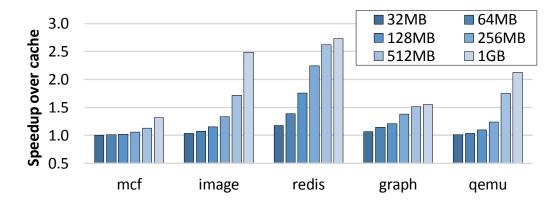

|     |            | 6.5.5   | Impact of Cache Capacities on CacheSwap |  |  |

|     |            | 6.5.4   | Sensitivity to DRAM Cache Performance   |  |  |

|     |            | 6.5.3   | Sensitivity to Fault Latency            |  |  |

|     |            | 6.5.2   | Sensitivity to Conversion Granularity   |  |  |

|     |            | 6.5.1   | Performance Under Memory Pressure       |  |  |

|     | 6.5        | Results | s and Analysis                          |  |  |

|     |            | 6.4.2   | Analytical Performance Model            |  |  |

|     |            | 6.4.1   | Evaluation Framework                    |  |  |

|     | 6.4        | Experim | mental Methodology                      |  |  |

# LIST OF TABLES

| 1  | Hardware cost of the Multi-Granular Hit-Miss Predictor.                                                                                                           | 25  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Hardware cost of the Dirty-Region Tracker.                                                                                                                        | 33  |

| 3  | System parameters used in this study.                                                                                                                             | 34  |

| 4  | L2 misses per kilo instructions (L2 MPKI)                                                                                                                         | 34  |

| 5  | Multi-programmed workloads                                                                                                                                        | 35  |

| 6  | System parameters used in the study.                                                                                                                              | 59  |

| 7  | L2 misses per thousand instructions (L2 MPKI)                                                                                                                     | 60  |

| 8  | Multi-programmed workloads                                                                                                                                        | 61  |

| 9  | Failure rates measured on external DRAM [80].                                                                                                                     | 61  |

| 10 | Detection coverage for each technique.                                                                                                                            | 64  |

| 11 | Correction coverage for each technique. Cases where correction coverage differs from detection coverage (Table 10) are marked with $\triangleright \triangleleft$ | 65  |

| 12 | Results using observed and $10 \times$ DRAM failure rates                                                                                                         | 65  |

| 13 | Baseline configuration used in this study                                                                                                                         | 90  |

| 14 | Evaluated multi-programmed workloads.                                                                                                                             | 91  |

| 15 | Performance impacts of different stacked DRAM employment approaches under over-committed/under-committed memory scenarios                                         | .05 |

| 16 | Evaluated workloads                                                                                                                                               | 22  |

| 17 | Recommended use cases for die-stacked memory                                                                                                                      | 35  |

# LIST OF FIGURES

| 1  | Organization of DRAM chips on a DIMM (one side, x8 chips) for (a) non-<br>ECC DRAM, and (b) ECC DRAM.                                                                                                              | 8  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Reading data from a die-stacked DRAM with (a) all data delivered from a single bank from a single layer (similar to JEDEC Wide I/O [34]), and (b) data distributed across banks from four layers.                  | 9  |

| 3  | DRAM cache organizations using (a) an SRAM tag array, (b) tags embedded in the DRAM, and (c) tags in DRAM with a MissMap                                                                                           | 12 |

| 4  | Example scenario illustrating under-utilized off-chip memory bandwidth in the presence of very high DRAM cache hit rates when considering (a) raw bandwidth in Gbps, and (b) in terms of request service bandwidth | 19 |

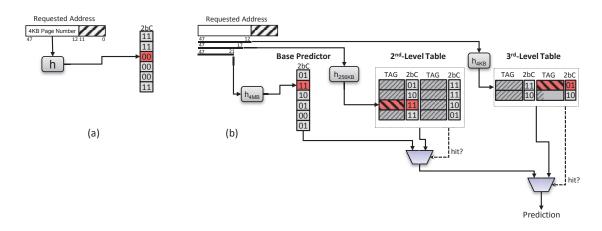

| 5  | Hit-Miss Predictor designs: (a) one-level $HMP_{region}$ , (b) multi-granular $HMP_{MG}$                                                                                                                           | 21 |

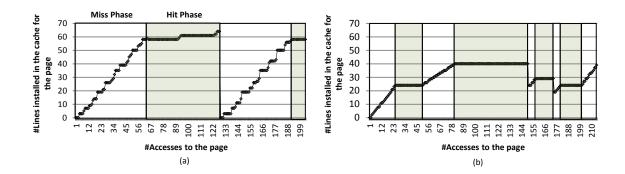

| 6  | Hit and miss phases for two example pages from leslie3d (when run as part of the multi-programmed workload WL-6).                                                                                                  | 22 |

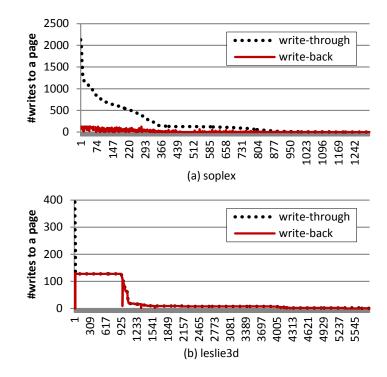

| 7  | Number of writes for each page with write-through and write-back policy.<br>The x-axis is sorted by top most-written-to pages.                                                                                     | 28 |

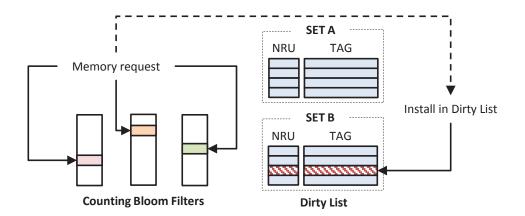

| 8  | Dirty Region Tracker (DiRT).                                                                                                                                                                                       | 30 |

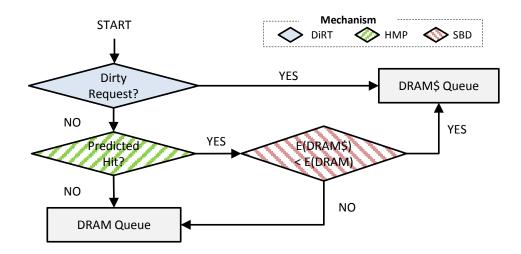

| 9  | Decision flow chart for memory requests.                                                                                                                                                                           | 32 |

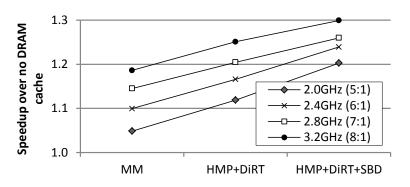

| 10 | Performance normalized to no DRAM cache for MissMap (MM), and combinations of HMP, SBD, and DiRT.                                                                                                                  | 36 |

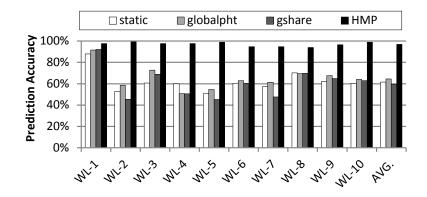

| 11 | Prediction accuracy of HMP and its comparison with other types of predictors.                                                                                                                                      | 37 |

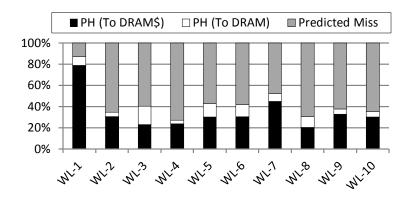

| 12 | Issue direction breakdown. PH indicates predicted hit requests                                                                                                                                                     | 38 |

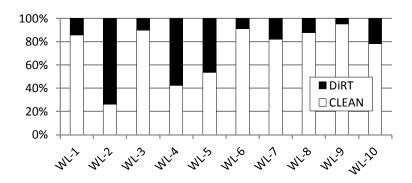

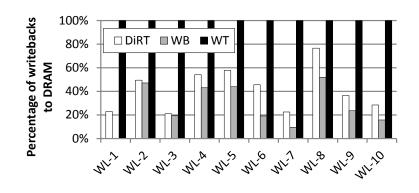

| 13 | Percentage distribution of memory requests captured in DiRT                                                                                                                                                        | 39 |

| 14 | Write-back traffic to off-chip DRAM between write-through, write-back, and DiRT (WL-1 does not generate WB traffic), all normalized to the write-through case.                                                     | 39 |

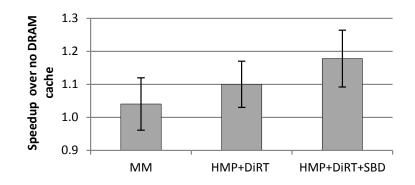

| 15 | Average performance of MissMap and our proposed mechanisms over no DRAM cache baseline with +/-1 std. deviation for 210 workloads                                                                                  | 40 |

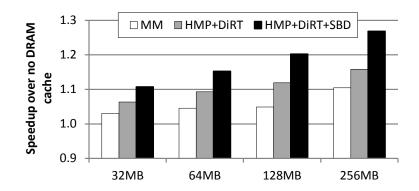

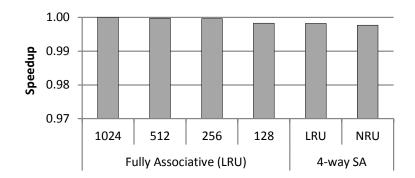

| 16 | Performance sensitivity of the proposed mechanisms to different DRAM cache sizes.                                                                                                                                  | 41 |

| 17 | Performance sensitivity to different ratios of DRAM cache bandwidth to off-chip memory.                                                                                                                            | 41 |

| 18 | Performance sensitivity to different DiRT structures and management policies.                                                                                                                                                                                                                                                                                                   | 42 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

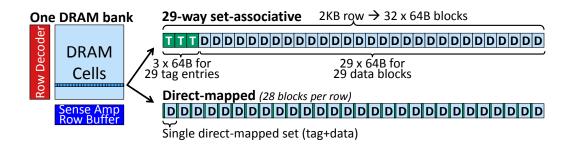

| 19 | A DRAM bank with 2KB row size. When used as a cache, the row can be organized (top) as a 29-way set-associative set, or (bottom) as 28 individual direct-mapped sets.                                                                                                                                                                                                           | 46 |

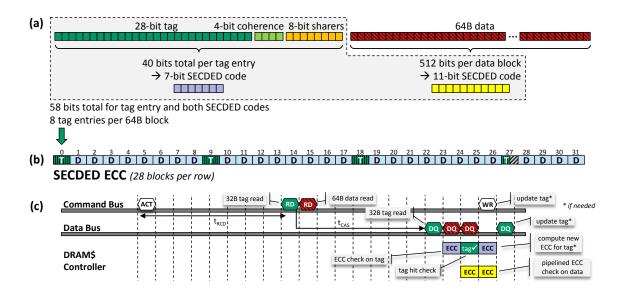

| 20 | (a) Contents of one tag entry and one 64B data block, along with SECDED ECC codes for each, respectively. (b) Contents of a 2KB DRAM row, with eight tag entries packed into a 64B block and the corresponding eight data blocks following. (c) Timing diagram for reading a 64B cache block                                                                                    | 47 |

| 21 | <ul> <li>(a) Contents of one tag entry and one 64B data block (treated as two 32B chunks for protection purposes), along with SEC ECC and CRC codes.</li> <li>(b) Contents of a 2KB DRAM row, with four tag entries (tag+SEC+CRC) packed into a 64B block and the corresponding four data blocks following.</li> <li>(c) Timing diagram for reading a 64B cache block</li></ul> | 50 |

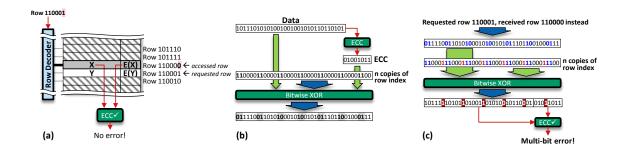

| 22 | (a) Row decoder error that selects the incorrect row, which is undetectable using within-row ECC. (b) Process for folding in the row index (row $110000_2$ ), and (c) usage of the folded row index to detect a row-decoder error.                                                                                                                                              | 52 |

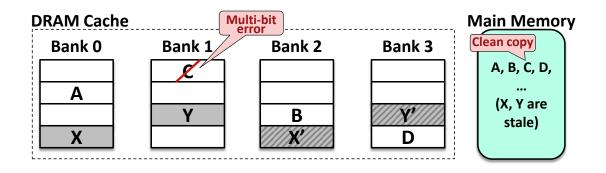

| 23 | Example DRAM cache contents in which clean data are backed-up by main memory, but dirty data are duplicated into other banks.                                                                                                                                                                                                                                                   | 54 |

| 24 | Performance comparison among no RAS, ECC, and ECC+CRC (normal-<br>ized to no DRAM cache).                                                                                                                                                                                                                                                                                       | 63 |

| 25 | Performance comparison between fine-grain (ECC+CRC) and coarse-grain (ECC+CRC+RAID-1 and ECC+CRC+DOW) schemes (normalized to the performance without the DRAM cache).                                                                                                                                                                                                           | 64 |

| 26 | Capacity and bandwidth impact of the ECC+CRC scheme                                                                                                                                                                                                                                                                                                                             | 67 |

| 27 | Impact of DOW on (a) the amount of dirty lines in the DRAM cache and (b) the writeback traffic from the DRAM cache                                                                                                                                                                                                                                                              | 68 |

| 28 | Sensitivity to different cache sizes (workloads in Table 8)                                                                                                                                                                                                                                                                                                                     | 69 |

| 29 | Average speed-up of no RAS, ECC+CRC and ECC+CRC+DOW over the 210 workloads.                                                                                                                                                                                                                                                                                                     | 69 |

| 30 | A high-level view of an OS-based PoM management.                                                                                                                                                                                                                                                                                                                                | 73 |

| 31 | Percentage of LLC misses serviced from fast memory across different intervals.                                                                                                                                                                                                                                                                                                  | 74 |

| 32 | Overview of the PoM architecture.                                                                                                                                                                                                                                                                                                                                               | 79 |

| 33 | Segment-restricted remapping.                                                                                                                                                                                                                                                                                                                                                   | 80 |

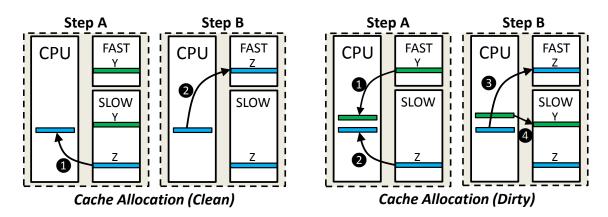

| 34 | Cache allocation                                                                                                                                                                             |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

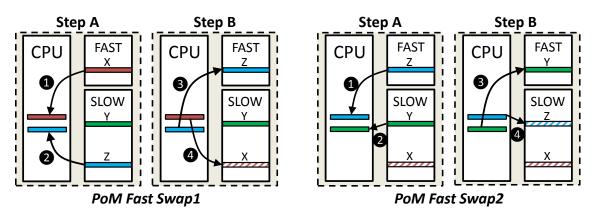

| 35 | Fast swap operation in the PoM architecture                                                                                                                                                  |

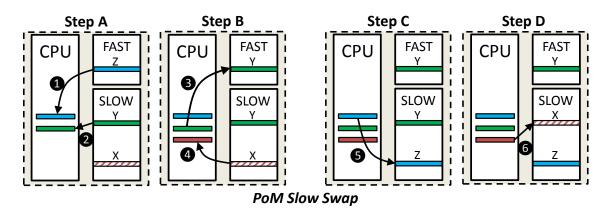

| 36 | Slow swap operation in the PoM architecture                                                                                                                                                  |

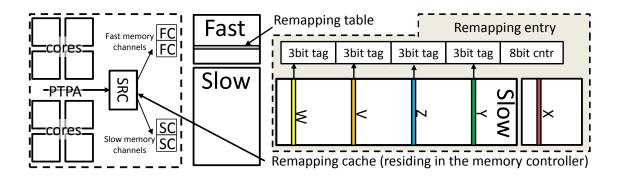

| 37 | Remapping table organization                                                                                                                                                                 |

| 38 | Competing counters                                                                                                                                                                           |

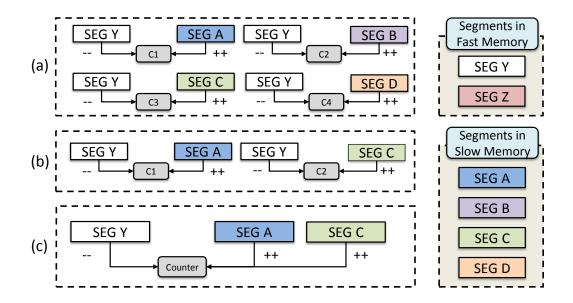

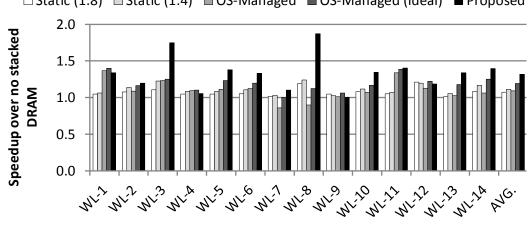

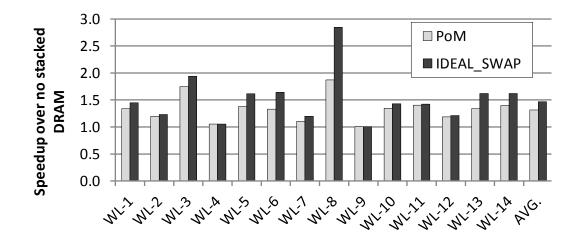

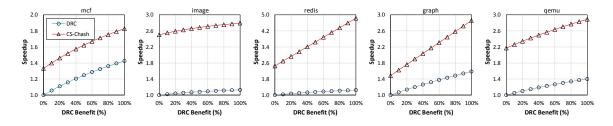

| 39 | Speedup with our proposed mechanism compared to other schemes (normalized to no stacked DRAM)                                                                                                |

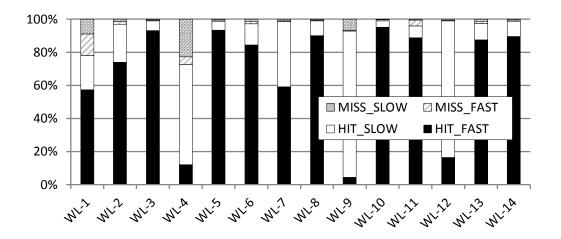

| 40 | Physical address translation breakdown                                                                                                                                                       |

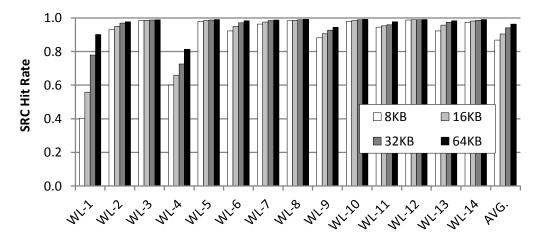

| 41 | SRC hit rate across different cache size                                                                                                                                                     |

| 42 | Comparison with ideal swapping                                                                                                                                                               |

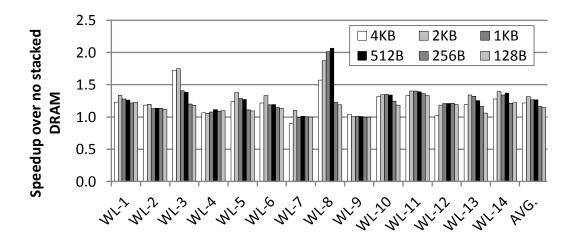

| 43 | Speedup across different segment granularity                                                                                                                                                 |

| 44 | Energy per memory access of OS-managed management and our PoM 98                                                                                                                             |

| 45 | Comparison to hardware-managed caches                                                                                                                                                        |

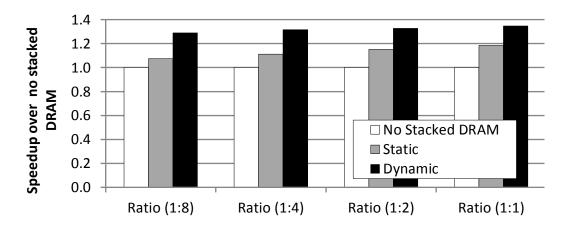

| 46 | Speedups of static mapping and our scheme across different ratios of fast to slow memory                                                                                                     |

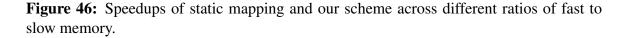

| 47 | Slowdowns of applications running on an over-committed system 103                                                                                                                            |

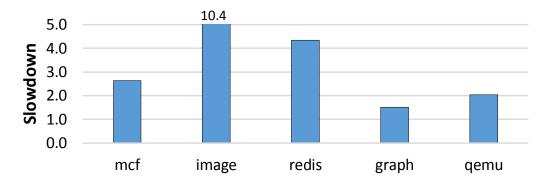

| 48 | High-level overview of (a) a conventional memory system with a large DRAM last-level cache, and (b) a CacheSwap memory system that cannibalizes LLC capacity to provide interim swap devices |

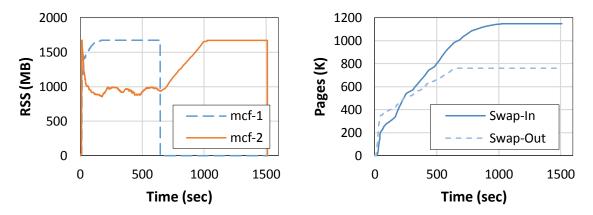

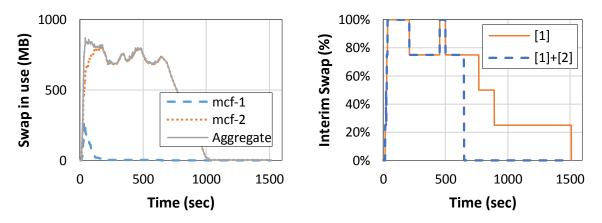

| 49 | Resident set size of each process and (system-wide) swap-in and swap-out pages for two active mcf processes                                                                                  |

| 50 | Swap space in use and the percentage of interim swap to total stacked DRAM size                                                                                                              |

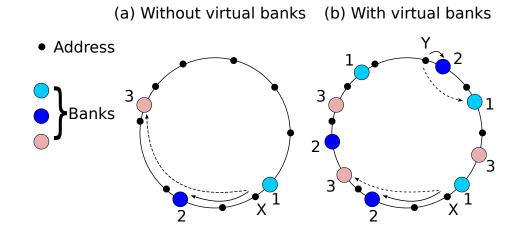

| 51 | Overview of consistent hashing                                                                                                                                                               |

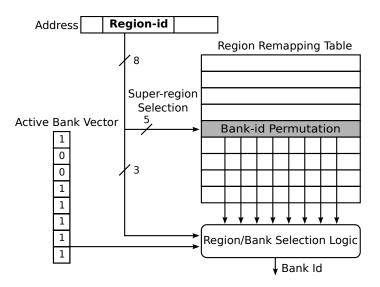

| 52 | Consistent hashing-based bank selection for DRAM caches                                                                                                                                      |

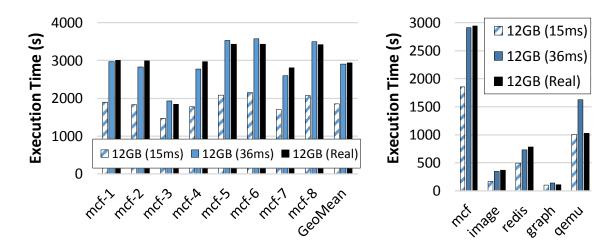

| 53 | Comparison of the execution time on the real machine and the computed time for each workload                                                                                                 |

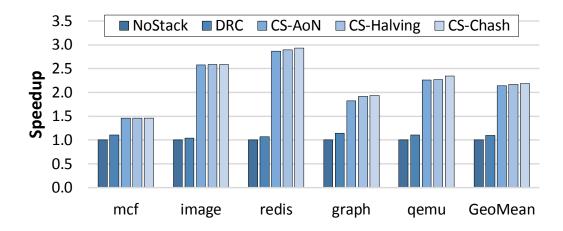

| 54 | Performance of CacheSwap and other systems for comparison over no stacked DRAM cache                                                                                                         |

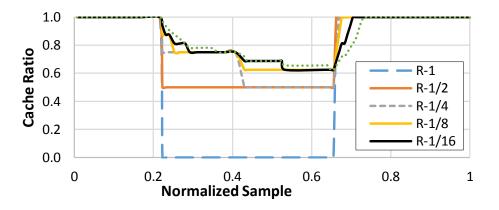

| 55 | Cache portions of graph during the execution with different conversion granularities                                                                                                         |

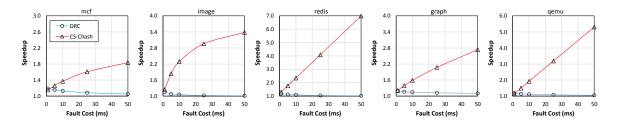

| 56 | Sensitivity to page fault latency                                                                                                                                                            |

| 57 | Sensitivity to cache performance.             | 129 |

|----|-----------------------------------------------|-----|

| 58 | Speedup of CacheSwap over the cache-only use. | 131 |

### SUMMARY

The main objective of this research is to efficiently enable 3D die-stacked memory and heterogeneous memory systems. 3D die-stacking is an emerging technology that allows for large amounts of in-package high-bandwidth memory storage. Diestacked memory has the potential to provide extraordinary performance and energy benefits for computing environments, from data-intensive to mobile computing. However, incorporating die-stacked memory into computing environments requires innovations across the system stack from hardware and software. This dissertation presents several architectural innovations to practically deploy die-stacked memory into a variety of computing systems.

First, this dissertation proposes using die-stacked DRAM as a hardware-managed cache in a practical and efficient way. The proposed DRAM cache architecture employs two novel techniques: hit-miss speculation and self-balancing dispatch. The proposed techniques virtually eliminate the hardware overhead of maintaining a multi-megabytes SRAM structure, when scaling to gigabytes of stacked DRAM caches, and improve overall memory bandwidth utilization.

Second, this dissertation proposes a DRAM cache organization that provides a high level of reliability for die-stacked DRAM caches in a cost-effective manner. The proposed DRAM cache uses error-correcting code (ECCs), strong checksums (CRCs), and dirty data duplication to detect and correct a wide range of stacked DRAM failures—from traditional bit errors to large-scale row, column, bank, and channel failures—within the constraints of commodity, non-ECC DRAM stacks. With only a modest performance degradation compared to a DRAM cache with no ECC support, the proposed organization can correct all single-bit failures, and 99.9993% of all row, column, and bank failures.

Third, this dissertation proposes architectural mechanisms to use large, fast, on-chip memory structures as part of memory (PoM) seamlessly through the hardware. The proposed design achieves the performance benefit of on-chip memory caches without sacrificing a large fraction of total memory capacity to serve as a cache. To achieve this, PoM implements the ability to dynamically remap regions of memory based on their access patterns and expected performance benefits.

Lastly, this dissertation explores a new usage model for die-stacked DRAM involving a hybrid of caching and virtual memory support. In the common case where system's physical memory is not over-committed, die-stacked DRAM operates as a cache to provide performance and energy benefits to the system. However, when the workload's active memory demands exceed the capacity of the physical memory, the proposed scheme dynamically converts the stacked DRAM cache into a fast swap device to avoid the otherwise grievous performance penalty of swapping to disk.

## **CHAPTER I**

## INTRODUCTION

The improvement of microprocessors allows for processing an ever increasing amount of data these days. Unfortunately, memory performance has not been improved at the same rate as microprocessor performance over the decades. Consequently, we have been facing the *Memory Wall* [85] and *Memory Bandwidth Wall* [8] problems, and system performance has been increasingly limited by memory performance in modern computing systems.

# 1.1 The Problem: Unpromising Conventional Memory Systems

To mitigate the *processor-memory performance gap*, both industry and academia have put enormous efforts into conventional memory systems. From industry, we have been improving DRAM—which has been used as main memory for the past four decades—to deliver large amounts of data faster to the processor. From academia, a significant amount of research has been focused on memory management including caching [84], prefetching [21], and memory scheduling [66]. Despite all these efforts, however, the processor-memory performance gap has become more widened, and today's memory system *truly* has become the fundamental bottleneck in computing systems. To make the problem worse, the recent explosion in data makes the memory system to have more stringent requirements on performance, power, and energy than ever before.

We now reached the point where it is not viable to meet such requirements with conventional memory systems anymore, *even if they are intelligently managed*. Given such a situation, we project that future memory systems will require employing emerging memory technologies and architectures (e.g., die-stacked DRAM) to streamline memory systems. These emerging memory architectures create a new problem space; they cannot simply be put in a memory hierarchy as a drop-in replacement for conventional memory. To

deploy them in commercial products, it is crucial to architecting them in an effective way that deals with the peculiarities of such emerging memory architectures (e.g., in die-stacked DRAM, all bits coming from the same DRAM chip, relatively long latency compared to SRAM). Furthermore, management techniques on conventional memory systems will also likely be ineffective for such emerging memory architectures; therefore, memory management techniques need to be redesigned for new memory architectures as well.

# 1.2 The Contributions: Efficiently Architecting Die-Stacked Memory and Heterogeneous Memory Systems

Among emerging memory architectures, this dissertation investigates using *3D die-stacked memory* and focuses on the question of how to manage resulting *heterogeneous memory systems*.<sup>1</sup> *3D* die-stacking is an emerging technology that allows for large amounts of high-bandwidth and energy-efficient memory storage within a processor package. This in-package die-stacked memory has the great potential to provide extraordinary performance and energy benefits for computing environments, from data-intensive to mobile computing. Consequently, it is gaining significant industrial traction, with activities in the memory standard bodies (e.g., JEDEC) and multiple companies (e.g., Intel, AMD, NVIDIA, Qualcomm) seriously considering the integration of die-stacked DRAM into their future products.

With the die-stacked memory within a processor package, future memory systems are expected to be *heterogeneous*—gigabytes of memory structures on-chip that provide higher bandwidth and faster access time than off-chip memory—and it is important to integrate the die-stacked memory *seamlessly* into current and future computing systems and enable heterogeneous memory systems in a practical manner. So, the question is *how to make efficient use of gigabytes of die-stacked memory in the heterogeneous memory system*.

In general, there will be a number of options of managing the stacked memory, and the

<sup>&</sup>lt;sup>1</sup>We define a *heterogeneous memory system* as a memory subsystem in which some portions of memory provide different performance and power characteristics than other portions of memory in the same node.

answers will likely to be varying depending on its deployment scenarios. For instance, the stacked memory could be better used as a large cache for the systems employing hundreds of gigabytes of off-chip memory (e.g., servers). However, for desktop or laptop systems where off-chip memory capacity is only a few gigabytes, the stacked memory may need to be managed as part of main memory (rather than as a cache) to fully utilize the memory capacity available in the system. Alternatively, for other scenarios where system's memory demands only occasionally exceed off-chip physical memory, we may want a hybrid design option of a cache and part of memory for the best use of the stacked memory.

To provide the benefits of die-stacked memory *across computing environments*, this dissertation proposes novel organizations and usage models while addressing the challenges of enabling die-stacked memory—scalability, resiliency, hardware management, and software interaction—in different deployment scenarios. The proposed organizations below would help system/chip vendors efficiently exploit die-stacked memory for their own needs.

#### Practical Die-Stacked DRAM Cache Architectures

To avoid dependencies on operating system vendors, maintain software transparency, and provide benefits to legacy software, using die-stacked DRAM as a large cache is one of the directions that both academia and industry are interested in. The key challenge in this direction is how to manage metadata when scaling to *gigabytes* of stacked DRAM caches. The prior state-of-the-art design requires a multi-megabyte SRAM structure (e.g., 8MB for a 2GB DRAM cache) in order to maintain *precise* information about the DRAM cache's contents, which is prohibitively costly to allow it to be deployed in commercial products. Furthermore, the design is also not scalable.

To make the cache approach more practical, this dissertation research proposes a DRAM cache architecture that employs two innovations [75], each of which exploits the bursty nature of memory requests. The first is a low-cost cache Hit-Miss Predictor (HMP) that *virtually eliminates* the hardware overhead of maintaining a multi-megabyte SRAM structure for precise metadata. We demonstrate that it is actually possible to *speculate* on

whether a request can be served by the DRAM cache or main memory, with 97% prediction accuracy and a hardware cost of less than 1KB, by exploiting spatial correlation and the bursty nature of cache traffic. The second is a Self-Balancing Dispatch (SBD) mechanism that dynamically sends some requests to off-chip memory even though the request may have hit in the die-stacked DRAM cache. This makes effective use of otherwise idle offchip bandwidth when the DRAM cache is servicing a burst of cache hits.

These techniques, however, are hampered by dirty data in the DRAM cache. We propose a hybrid write policy for the cache that simultaneously supports write-through and write-back policies for different pages. Only a limited number of pages are permitted to operate in a write-back mode at one time, thereby bounding the amount of dirty data in the DRAM cache. By keeping the majority of the DRAM cache clean, most HMP predictions do not need to be verified, and self-balancing dispatch has more opportunities to redistribute requests.

#### **Resilience Support for Die-Stacked DRAM Caches**

Many high-end markets (e.g., server, datacenter, high-performance computing) require superior reliability, availability and serviceability (RAS). Die-stacked memories will likely need to be more reliable than external memories because *DRAM stacks are not serviceable*. Compared to conventional dual-inline memory modules (DIMMs) that can be easily replaced, a die-stacked memory failure may require discarding the entire package including the perfectly functioning processor.

To address the reliability concerns, this dissertation proposes a series of modifications to a stacked-DRAM cache to provide both fine-grain protection (e.g., for single-bit faults) and coarse-grain protection (e.g., for row-, bank-, and channel-faults) while only utilizing commodity non-ECC stacked DRAM chips. Furthermore, these RAS capabilities can be selectively enabled to tailor the level of reliability for different market needs [76, 77].

#### **Die-Stacked DRAM as Part of Main Memory**

For some computing environments, depending on its deployment scenarios, making die-stacked DRAM invisible to overall system memory (i.e., used as a cache) could lead to a non-negligible loss of a performance opportunity. For stacked DRAM to be deployed in such computing environments, this dissertation conducts a study of how to effectively combine fast stacked DRAM and slow off-chip memory to create a single physical address space [72].

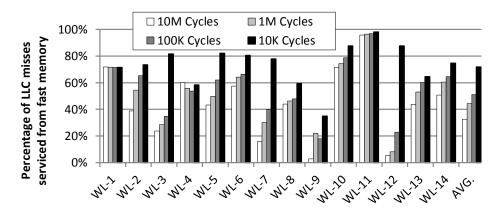

Such *heterogeneous main memory* is typically managed by the operating system (OS). To maximize the performance benefits of fast memory, the OS could allocate heavily used pages to the portion of the physical address space mapped to the fast memory. Alternatively, the OS could dynamically migrate memory pages between fast and slow memory runtime. However, this dissertation shows that an OS-managed heterogeneous system is often unable to capture pages that are highly utilized for short periods of time, thereby leading to a non-negligible loss of a performance opportunity.

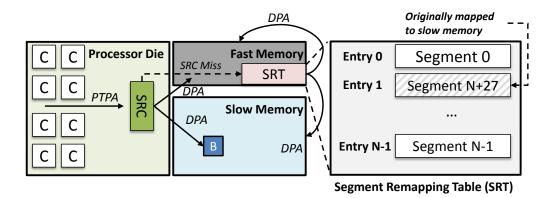

Consequently, this dissertation proposes a practical, low-cost architectural solution to efficiently enable using large stacked DRAM as Part-of-Memory (PoM) *without the involvement of the OS*. The hardware-managed PoM architecture dynamically remaps regions of memory, based on their access patterns and expected performance benefits, and performs even better than an ideal OS-based migration design that assumes zero-cost migration overheads.

#### **Stacked DRAM Interacting with Operating Systems**

This dissertation presents a new usage model for die-stacked DRAM involving a hybrid of caching and virtual memory support. In the common case where system's off-chip physical memory is not over-committed, die-stacked DRAM operates as a cache to provide performance and energy benefits to the system. However, when the workload's demands exceed the capacity of the physical memory, the proposed scheme can dynamically convert (part of) the stacked DRAM cache into a fast swap device, with minimum OS and hardware changes, in order to avoid the otherwise grievous performance penalty of swapping to disk.

This work increases the value proposition of stacked DRAM. In the common case, any of the previously proposed DRAM cache organizations can be used to increase system performance. However, the proposed scheme allows for tolerating a moderate level of memory over-commitment and thus opens up new opportunities for datacenter operators to more aggressively consolidate multiple workloads/virtual machines on to the same physical servers; or alternatively, the operators can maintain the current levels of consolidation but reduce the amount of overprovisioning of main memory. Such optimizations can have a direct impact on both operating expenses (e.g., more consolidation leads to more powered-down machines which saves on power costs) and/or capital expenses (e.g., purchasing less memory if less over-provisioning is needed).

## 1.3 Thesis Statement

Die-stacked memory can provide performance benefits across computing environments once it is effectively exploited with low-cost architectural innovations to address its challenges: scalability, resiliency, hardware management, and software interaction.

## 1.4 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter II provides background and summarizes related work. Chapter III discusses a practical die-stacked DRAM cache architecture. Chapter IV presents a design of providing resilience support for die-stacked DRAM caches. Chapter V proposes using large, on-chip memory as part of addressable physical memory space. Chapter VI proposes a hybrid scheme where the hardware and operating system cooperatively manage stacked DRAM. Lastly, Chapter VII concludes this dissertation and discusses future work.

## **CHAPTER II**

# **BACKGROUND AND RELATED WORK**

In this chapter, we provide an overview of conventional off-chip memory and die-stacked DRAM (Sections 2.1, 2.2, 2.3, and 2.4) and describe the prior state-of-the-art using die-stacked DRAM as a large cache (Section 2.5). We then discuss prior work related to this dissertation (Section 2.6).

### 2.1 DRAM Architecture

DRAM consists of arrays of bit-cells, where each bit-cell is comprised of a capacitor to store charge and an access transistor to enable reading or writing of the cell. Accessing bit-cells in a DRAM requires storing the bit-cell values in a row buffer, and all read and write operations effectively operate directly on the row buffer (rather than the actual bit-cells). When the row is no longer needed (or often when a different row is requested), the contents of the row buffer are written back into the original row of bit-cells and then a new row may be accessed.

The DRAM access mechanism is quite different from SRAM arrays. In the case of DRAM, an entire bank is occupied while the row is open, and therefore any requests to other rows in this bank will be delayed until the current operations complete (although operations in independent banks may proceed concurrently subject to DRAM timing and bus constraints). In an SRAM, the access paths are more easily pipelined, and so even if a request has been sent to a particular bank, subsequent requests need only wait a few cycles before they can proceed.

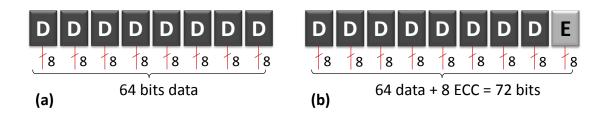

**Figure 1:** Organization of DRAM chips on a DIMM (one side, x8 chips) for (a) non-ECC DRAM, and (b) ECC DRAM.

# 2.2 Error Correcting Code for Conventional DRAM

Conventional off-chip memory is organized on dual-inline memory modules (DIMMs), with each side consisting of multiple DRAM chips. For the sake of simplicity, this discussion focuses on an organization in which each chip provides eight data bits at a time ("x8"), so the eight chips ganged together implement a 64-bit interface as shown in Figure 1(a). Typically a Hamming code [26] with seven check bits (or a similar code) is used to provide single-bit error correction (SEC) for 64 bits of data. In addition to the SEC code, an additional parity bit is provided to enable double-bit error detection (DED). This introduces eight bits of overhead per 64 bits of data, which is implemented by adding a ninth chip to the DIMM, as shown in Figure 1(b). All 72 bits are read in parallel, and the 8 bits of SECDED coding are used to check and possibly correct one of the 64 bits. Chipkill protection can be achieved in the same area overhead (although typically using x4 chips) by using a Reed-Solomon symbol-correction code and laying out the memory system so each DRAM chip contributes bits to exactly one error-correcting code (ECC) "symbol" [13].

A key advantage of the conventional ECC DIMM approach is that the silicon for each of the individual chips is identical, which allows the memory manufacturers to incur only the engineering expenses of designing a single memory chip. The difference comes from the design of the DIMM modules: the non-ECC version supports (for example) eight memory chips and the ECC version supports nine, but the engineering cost of designing and manufacturing multiple printed circuit boards is far cheaper than doing the same for multiple chip designs. Maintaining a single chip design also helps optimize a memory vendor's silicon inventory management.

### 2.3 Die-Stacked DRAM Organization

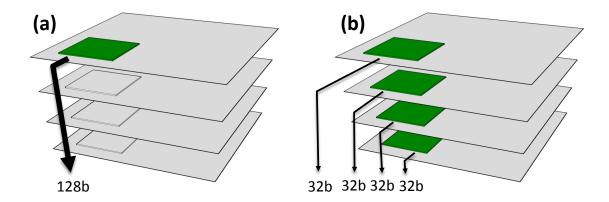

Die-stacked DRAM consists of one or more layers of DRAM with a very-wide data interface—using through-silicon vias (TSVs)—connecting the DRAM stack to whatever it is stacked with (e.g., a processor die). Whereas a conventional memory chip may provide only a four- or eight-bit data interface (the reason multiple chips are ganged together on a DIMM), a single layer of die-stacked memory can provide a much larger interface, such as 128 bits [17, 43]. Given this wider interface, all bits for a read request can be transferred across a single interface, and therefore all bits are sourced from a single chip in the stack, as shown in Figure 2(a).

**Figure 2:** Reading data from a die-stacked DRAM with (a) all data delivered from a single bank from a single layer (similar to JEDEC Wide I/O [34]), and (b) data distributed across banks from four layers.

In theory, the stacked DRAM could be organized to be more like a DIMM, in that each of the N chips in a stack provides  $\frac{1}{N}$ <sup>th</sup> of the bits, as shown in Figure 2(b). This approach is undesirable for a variety of reasons. Requiring the parallel access of N chips means activating banks on all chips. This reduces peak bank-level parallelism by a factor of N, which reduces performance [46]. In addition to the N bank activations, accessing all chips in parallel requires switching N row and column decoders and associated muxes on

each access, increasing both the power as well as the number of points of possible failure. Timing skew between different bits coming from different layers for the same request may also make the die-stacked I/O design more challenging. Distributing data across layers also limits flexibility in the design of the stacks. If, for example, data are spread across four layers, then DRAM stack designs will likely be constrained to have a multiple of four DRAMs per stack. In summary, a "DIMM-like" distribution of data across the layers of the DRAM stack is problematic for many reasons.

### 2.4 DRAM Failure Modes

Conventional DRAM exhibits a variety of failure modes including single-bit faults, column faults, row faults, bank faults, and full-chip faults [30, 80]. These faults can affect one or more DRAM sub-arrays and either be permanent or transient. Recent field studies on DDR-2 DRAM indicate that over 50% of DRAM faults can be large, multi-bit (row, column, bank, etc.) faults, and that DRAM device failure rates can be between 10-100 Failures in Time (FIT) per device, where 1 FIT is one failure per billion hours of operation [80]. Neutron beam testing also shows significant inter-device and inter-vendor variation in failure modes and rates [61].

The internal organization of a die-stacked DRAM bank is similar to an external DRAM, thus failure modes that occur in external DRAM devices are likely to occur in die-stacked DRAM. Die-stacked DRAM may also experience other failure modes, such as broken through-silicon vias (TSVs), and accelerated failure rates from causes such as negativebias temperature instability (NBTI) and electromigration due to elevated temperatures from being in a stack. Some of these new failure modes (e.g., broken TSVs) will manifest as a single failing bit per row, while others (e.g., electromigration) may cause multiple bits to fail simultaneously.

The cost of an uncorrectable/unrepairable DRAM failure in a die-stacked context may be significantly more expensive than for conventional DIMMs. In a conventional system, a failed DIMM may result in costly down time, but the hardware replacement cost is limited to a single DIMM. For die-stacked memory, the failed memory cannot be easily removed from the package as the package would be destroyed by opening it, and the process of detaching the stacked memory would likely irreparably damage the processor as well. Therefore, the entire package (including the expensive processor silicon) would have to be replaced.

To summarize, die-stacked DRAM RAS must provide robust detection and correction for all existing DRAM failure modes, should be robust enough to handle potential new failure modes as well, and will likely need to endure higher failure rates due to the reduced serviceability of 3D-integrated packaging.

### 2.5 Die-Stacked DRAM Caches

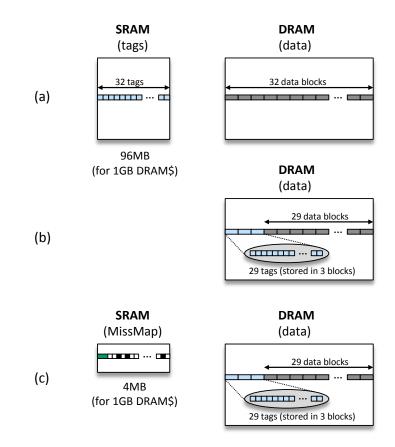

Caches store two types of information: tags and data. In conventional SRAM-based caches, these are stored in two physically distinct structures (the tag and data arrays, respectively). For a DRAM cache, one could consider an SRAM-based tag array, as shown in Figure 3(a), but previous estimates have shown that such a structure would require tens of megabytes of SRAM, and therefore this approach is not practical considering that current L3 cache sizes are typically only around 8 MB [11, 12].

Instead, recent research has considered organizations where the tags and data are directly co-located within the die-stacked DRAM, as shown in Figure 3(b) [15,51]. While this eliminates the unwieldy SRAM tag array, it introduces two more problems. First, naively accessing the cache could double the DRAM cache latency: one access to read the tags, followed by another access to read the data (on a hit). Second, for cache misses, the cost of the DRAM cache tag access is added to the overall load-to-use latency.

Loh and Hill observed that the tags and data reside in the same DRAM row, and so the actual latency of a cache hit can be less than two full accesses by exploiting row buffer locality [51]. That is, the DRAM row is opened or activated into the row buffer only

**Figure 3:** DRAM cache organizations using (a) an SRAM tag array, (b) tags embedded in the DRAM, and (c) tags in DRAM with a MissMap.

once, and then tag and data requests can be served directly out of the row buffer at a lower latency compared to two back-to-back accesses to different rows. They also proposed a hardware data structure called a MissMap that precisely tracks the contents of the DRAM cache, as shown in Figure 3(c). Before accessing the DRAM cache, the MissMap is first consulted to determine whether the requested cache block is even resident in the cache. If the block is not in the cache (i.e., miss), the request can be sent directly to main memory without incurring the tag-check cost of the DRAM cache. For a 512MB DRAM cache, the MissMap needs to be about 2MB in size (which provides tracking of up to 640MB of data), and a 1GB cache would need a 4MB MissMap. While Loh and Hill argue that part of the L3 cache could be carved out to implement the MissMap, using the AMD Opteron<sup>TM</sup> processor that consumes 1MB of its L3 to implement a "Probe Filter" as an example [11],

it seems unlikely that designers would be willing to sacrifice *half* of their L3 to implement the MissMap.<sup>1</sup>

#### 2.6 Related Work

#### 2.6.1 Related Work on Heterogeneous Memory Systems

**NUMA Systems:** Non-uniform memory architectures have been used in most largescale symmetric multiprocessors. In the CC-NUMA architecture, each processing node maintains a cache to reduce traffic to remote nodes [45]. Cache-only memory architectures (COMA) [24] use memory as a hardware-managed cache, like the ALLCACHE design in the KSR1 system [20]. An S-COMA system allocates part of the local nodes main memory to act as a large cache for remote pages [67]. Falsafi and Wood propose Reactive NUMA (R-NUMA) that reacts to program behavior and enables each node to use the best of CC-NUMA or S-COMA for a particular page [19]. The Sun WildFire prototype shows that an R-NUMA-based design can significantly outperform a NUMA system [23]. Although the heterogeneous memory system analyzed in Chapter V has properties similar to a NUMA system (with variable memory latencies), our work differs from traditional NUMA research since we treat both the fast and slow memory as local to a node.

**DRAM Caches:** Recent papers on heterogeneous memory systems have proposed the use of fast stacked memory as a cache for the slow memory [36, 51]. However, the previous designs had shortcomings when being deployed in commercial products due to hardware overhead. In contrast, the proposed approach in Chapter III greatly reduces hardware overhead and enables using gigabytes of die-stacked DRAM as a cache in a practical way.

In Chapter V, we present a Part-of-Memory (PoM) architecture. The key difference between PoM and all previous work on DRAM caches (including the work in Chapter III) is that PoM provides higher total memory capacity as compared to DRAM caches. The

<sup>&</sup>lt;sup>1</sup>Assuming a 4MB MissMap to support a 1GB DRAM cache and a baseline L3 cache size of 8MB. If such a system employed a Probe Filter as well, then only 3MB out of the original 8MB L3 would actually be available as a cache.

caching approach benefits from simple, fast allocation to fast memory (DRAM cache) but suffers from wasted capacity due to data duplication. Enabling PoM to maximize memory capacity requires quite different design approaches from previously described DRAM cache architectures, including support for complex swapping operations (Section 5.3.3) and memory permutation (Section 5.3.4 for fast-swap) that results when different memory locations are swapped. The benefits of the additional memory capacity provided by PoM extend beyond the performance benefits harvested through reduced disk swapping, directly impacting one of the attributes consumers use when making a purchase decision.

**Software-Managed Heterogeneous Memory:** Prior work has explored managing heterogeneous memory systems using software, as opposed to our hardware-based proposal. Loh et al. [52] studied the benefits and challenges of managing a die-stacked, heterogeneous memory system under software control. The authors discussed that even OS-managed heterogeneous memory systems require non-negligible hardware/software overheads for page activity monitoring and migration. Ekman and Stenstrom [16] also discussed a twolevel main memory organization in the server systems under OS control. As we discuss in Chapter V, all these techniques suffer from OS-related overheads and are less responsive to program phase changes.

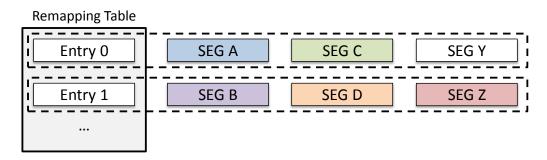

**Hardware-Managed Heterogeneous Memory:** Some recent papers have explored hardware implementations for supporting page migrations in heterogeneous memories [15, 63]. The work that is most closely related to the work in Chapter V is the one from Dong et al. [15]. Their hardware-only implementation maintains a translation table in the memory controller, which keeps track of all the page remappings. To keep the table size small, their implementation uses large 4MB pages, which incurs both high migration latencies and increased bandwidth pressure on the slow memory. In comparison, our approach supports small page sizes by keeping the remapping table in the fast memory and caching the recent remapping table accesses in a small remapping cache. Ramos et al. [63] propose

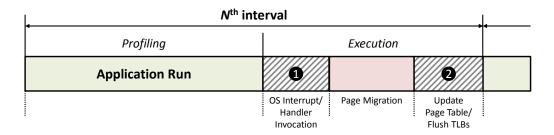

hardware support for OS-managed heterogeneous memories. In their work, the page table keeps a master copy of all the address translations, and a small remapping table in the memory controller is used to buffer only the recent remappings. Once the remapping table becomes full, the buffered remappings need to be propagated to the page table, requiring the OS to update the page table and flush all the TLBs. Thus, their approach requires costly OS interventions, which our technique avoids by maintaining page remappings in a dedicated hardware-managed remapping table in the fast memory. In Chapter V, we detail how to practically combine and manage fast die-stacked and slow off-chip memory through hardware.

#### 2.6.2 Related Work on RAS Support

Chapter IV is the first work to target increased RAS capabilities in die-stacked DRAM designs. However, several recent works target more power-efficient external DRAM implementations, and bear some similarities to the techniques described in this work. Single-subarray access (SSA) proposes fetching an entire cache line from a single DRAM device, using a RAID scheme to support chipkill [83]. LOT-ECC and virtualized ECC propose supporting chipkill with x8 DRAM devices by separating the error-detection and error-correction steps and storing some ECC information in data memory [82, 89]. The tiered coverage of memory-mapped ECC [88] and LOT-ECC share some similarities with the work in Section 4.4, but the structures and implementations are quite different.

Mini-rank proposes storing ECC bits along with the associated data bits to efficiently support RAS for their mini-rank design [92]. The embedded ECC complicates memory address translation (this technique is proposed for main memory), but the approach taken in our work does not affect the address translation as we store ECC information in the tag storage and thus do not change the data block size. Abella et al. propose adding hard-wired ROM entries to each row of an SRAM to provide a hard-wired row index when reading out data to detect row-decoder errors [1], but such an approach does not extend easily to

commodity DRAMs. All of these techniques would require significant modifications to support die-stacked DRAM architectures.

The idea of replicating cache blocks has been studied before, although in a different context. In-cache replication (ICR) improves the resiliency of level-one data (DL1) caches [90]. ICR differs from our proposed Duplicate-on-Write (DOW) scheme (Section 4.4.2) in which the structures, constraints, and performance implications of the DL1 force a very different design from DOW; ICR makes use of dead-line predictors, more complex indexing of duplicate copies (possibly with multiple locations), and in some variants ICR duplicates both clean and dirty data.

There has also been a significant amount of recent research in using die-stacked DRAM as large caches [5, 15, 36, 51, 62, 75], but none of these have addressed the problems of providing robust error correction and detection capabilities for such large, in-package storage arrays. Micron's Hybrid Memory Cube provides ECC support for its 3D DRAM stacks [60], but this requires custom DRAM chips, whereas the proposed approaches in Chapter V are compatible with commodity non-ECC DRAM.

# **CHAPTER III**

# AN EFFICIENT DIE-STACKED DRAM CACHE

As described in Section 2.5, while the MissMap provides a more practical approach than using a massive SRAM tag array, its implementation is prohibitively costly to allow it to be deployed in commercial products. Furthermore, the access latency of the MissMap is not trivial (the original work used a latency of 24 cycles, which is added to *all* DRAM cache hits *and* misses). In this chapter, we propose a practical DRAM cache organization while eliminating the inefficiencies of the previous DRAM cache design.

# 3.1 The Problems

In this section, we identify inefficiencies with the previously proposed DRAM cache organizations (Section 2.5). First, we explain why the MissMap is overly conservative, which ultimately leads us to consider more speculative techniques with significantly lower overheads (both in terms of hardware cost and latency). Second, we describe scenarios where a conventional cache organization under-utilizes the available aggregate system bandwidth, which motivates our proposal for a *Self-Balancing Dispatch* mechanism. Third, we discuss how the presence of dirty/modified data in the DRAM cache can potentially limit how aggressively we can speculate on or rebalance DRAM cache requests.

#### 3.1.1 The Overkill of the MissMap

The MissMap precisely maintains a bit-vector that records which cache blocks are currently resident in the DRAM cache. However, it is possible to allow the MissMap to have false positives. That is, if the MissMap says that a block is present in the DRAM cache when in fact it is not, then there is only a performance impact as the system needlessly pays for the latency of the DRAM cache before going to main memory. However, if the MissMap

reports that a line is *not* present when in fact it is (false negative), the request would be sent to main memory and returned to the processor. If the DRAM cache contains this block in a dirty state, then this can lead to incorrect program execution.

On a DRAM cache miss (whether the MissMap said so or not), the system sends the request to main memory. When the response returns, the data are sent back to the L3 and the processor, and the data are also installed into the DRAM cache.<sup>1</sup> Prior to the installation of a new cache block, a victim must be selected. Furthermore, if the victim has been modified, then it must also be written back to main memory.

Note that when selecting a victim, the DRAM tags are checked. Therefore, if the system issued a request to main memory even though a modified copy of the block is in the DRAM cache, this can still be detected at the time of victim selection. Given this observation, the constraint that the MissMap *must* not allow false negatives is overly conservative. False negatives are tolerable so long as responses from memory are not sent back to the processor before having verified that a dirty copy does not exist in the DRAM cache.

Based on these observations, we propose a DRAM cache organization that can speculatively issue requests directly to main memory regardless of whether the decisions are "correct" or not. Section 3.2 describes a predictor design that exploits spatial correlation and the bursty nature of cache traffic to provide a light-weight yet highly accurate DRAM cache hit-miss predictor.

#### 3.1.2 Under-Utilization of Aggregate System Bandwidth

Die-stacked DRAM can potentially provide a substantial increase in memory bandwidth. Previous studies have assumed improvements in latency of  $2\times$ ,  $3\times$  and as much as  $4\times$  compared to conventional off-chip DRAM [36,51,91]. At the same time, the clock speed can be faster, bus widths wider, and independent channels more numerous [43,51]. Even with a rough estimate of half the latency, twice the channels, and double-width buses

<sup>&</sup>lt;sup>1</sup>For this study, we assume that all misses are installed into the DRAM cache. Other policies are possible (e.g., write-no-allocate, victim-caching organizations), but these are not considered here.

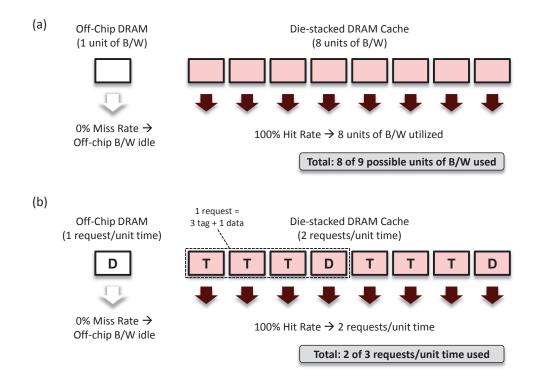

**Figure 4:** Example scenario illustrating under-utilized off-chip memory bandwidth in the presence of very high DRAM cache hit rates when considering (a) raw bandwidth in Gbps, and (b) in terms of request service bandwidth.

(compared to conventional off-chip memory interfaces), the stacked DRAM would provide an  $8 \times$  improvement in bandwidth. In an "ideal" case of a DRAM cache with a 100% hit rate, the memory system could provide an eight-fold increase in delivered bandwidth, as shown in Figure 4(a). However, the off-chip memory is completely idle in this scenario, and that represents 11% ( $\frac{1}{1+8}$ ) of the overall system bandwidth that is being wasted.

Figure 4(b) shows the same scenario again, but instead of raw bandwidth (in terms of Gbps), we show the *effective bandwidth* in terms of requests serviced per unit time. Note that a request to main memory only requires transferring a single 64B cache block, whereas a request to a tags-in-DRAM cache requires transferring three tag blocks (64B each) and finally the data block. Therefore, the sustainable effective bandwidth of the DRAM cache is only twice that of the off-chip memory ( $8 \times$  the raw bandwidth, but  $4 \times$  the bandwidth-consumption per request). In this case, a 100%-hit rate DRAM cache would leave 33%

of the overall effective bandwidth unused  $(\frac{1}{1+2})$ . While the DRAM cache typically does not provide a 100% hit rate, hits often come in bursts that can lead to substantial queuing delays from bank and bus contention.

Apart from the available bandwidth, bank and bus conflicts at the DRAM cache can lead to increased queuing delays, some of which could potentially be mitigated if some of these requests could be diverted to the off-chip memory. In practice, other timing constraints, resource conflicts, and specific access patterns and arrival rates would affect the exact amount of bandwidth available for both the DRAM cache and the off-chip memory. However, this simple example highlights that there will be times where the system will have some idle resources, and we propose a Self-Balancing Dispatch technique to capitalize on these resources.

#### 3.1.3 Obstacles Imposed by Dirty Data

Dirty data in the DRAM cache can severely restrict the aggressiveness of speculatively sending requests to main memory, as the copy in main memory is stale and its usage can result in incorrect executions. Likewise, dirty data prevents the system from exploiting idle main-memory bandwidth because accesses to dirty data must be sent to the DRAM cache regardless of how busy the DRAM cache or how idle the off-chip memory is. This also raises the question as to how the system can know ahead of time that a request targets a dirty cache line without having first looked up in the cache to see if the line is present and dirty. A key contribution of this work is a new way to operate the DRAM cache (which could be applied to other types of caches) such that most of the cache will be clean, and for the majority of the cache, we can guarantee its cleanliness without having to check the cache's tags. This removes major limitations for both cache hit speculation and Self-Balancing Dispatch.

Figure 5: Hit-Miss Predictor designs: (a) one-level HMP<sub>region</sub>, (b) multi-granular HMP<sub>MG</sub>.

# 3.2 DRAM Cache Hit Speculation

The previously proposed MissMap provides precise tracking of DRAM cache contents, but as a result, the size (2-4MB) and latency (tens of cycles) of the structure introduce significant overheads. Section 3.1 explained how the DRAM cache can check for the existence of a dirty block at the time of a cache fill, and how this allows the DRAM cache to speculatively send requests to main memory so long as we ensure that the data are not returned to the processor until it has been verified that a modified copy is not also in the DRAM cache. This section presents the designs for lightweight and accurate region-based predictors that exploit the bursty nature of cache hits and misses [49].

## 3.2.1 Region-Based Hit-Miss Prediction

Our region-based Hit-Miss Predictor (HMP<sub>region</sub>) is structurally similar to a classic bimodal branch predictor [78]. The predictor itself consists of a table of two-bit saturating counters. For a DRAM cache with millions of cache blocks, it is not practical to directly index into the HMP<sub>region</sub> table with a hash of the raw physical address; the aliasing and interference would render the predictor table nearly useless, or a gigantic table would be needed. Instead, we break up the memory space into coarser-grained regions (e.g., 4KB), and index into the HMP<sub>region</sub> with a hash of the region's base address as shown in Figure 5(a). This allows the HMP<sub>region</sub> table to be much smaller, but it also means that *all* accesses within a region will

**Figure 6:** Hit and miss phases for two example pages from leslie3d (when run as part of the multi-programmed workload WL-6).

follow the same prediction. The operation of the  $HMP_{region}$  is otherwise analogous to the bimodal predictor: DRAM cache hits increment the predictor, and misses decrement the predictor (saturating at 3 or 0, respectively).

The coarse-grained predictor organization of HMP<sub>region</sub> is actually a benefit rather than a shortcoming. Accesses tend to exhibit significant spatial locality, especially at lower-level caches such as a large DRAM cache. Figure 6(a) shows the number of cache blocks present in the DRAM cache for one particular 4KB page of leslie3d (from the WL-6 workload) with respect to the number of accesses to this page (our methodology is explained in Section 3.5). Initially, nothing from this page is in the DRAM cache, but as the page is used, more and more lines are installed. During this installation phase, most accesses result in cache misses, and a simple 2-bit counter corresponding to this region would mostly predict that these requests result in misses. After this "warm up" phase, the footprint from this region is stable, and all subsequent accesses to this region result in hits. Again, a simple 2bit counter would quickly switch over to predicting "cache hit" for this region and achieve high accuracy. When the application is finished with using this region, the contents will gradually get evicted from the cache, as shown by the drop back down to zero. At some future point, the page becomes hot again and the process repeats. Note that the figure's x-axis is based on accesses to the page. The time that elapses from the last access in the hit phase until the first access in the miss phase could easily span many thousands or even

millions of cycles, but this all gets compressed here.

Figure 6(b) shows another 4KB region taken from leslie3d (from the same workload WL-6). This is just to illustrate that different regions and different applications may show different types of patterns, but so long as there exist sustained intervals where the curve is consistently increasing (mostly misses) or is consistently flat (mostly hits), then the simple 2-bit counter approach will be effective for making hit-miss predictions for the region.

The HMP<sub>region</sub> approach is different from other previously proposed history-based hitmiss predictors. Past work has considered hit-miss predictors for L1 caches based on PC-indexed predictor organizations [87]; such an approach may not be as easy as to implement for a DRAM cache because PC information is not typically passed down the cache hierarchy, may not exist for some types of requests (e.g., those originating from a hardware prefetcher), or may not be well defined (e.g., a dirty cache block being written back to the DRAM cache that was modified by two or more store instructions may have multiple PCs associated with it).

## 3.2.2 Multi-Granular Hit-Miss Predictor