# COMPLIANT COPPER MICROWIRE ARRAYS FOR RELIABLE INTERCONNECTIONS BETWEEN LARGE LOW-CTE PACKAGES AND PRINTED WIRING BOARD

A Dissertation Presented to The Academic Faculty

by

Xian Qin

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Materials Science and Engineering

> Georgia Institute of Technology May, 2015

## **COPYRIGHT 2015 BY XIAN QIN**

# COMPLIANT COPPER MICROWIRE ARRAYS FOR RELIABLE INTERCONNECTIONS BETWEEN LARGE LOW-CTE PACKAGES AND PRINTED WIRING BOARD

Approved by:

Dr. Rao Tummala, Advisor School of Materials Science and Engineering *Georgia Institute of Technology*

Dr. P. Markondeya Raj School of Materials Science and Engineering *Georgia Institute of Technology*

> Dr. Suresh Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Preet Singh School of Materials Science and Engineering *Georgia Institute of Technology*

> Dr. Richard Neu Materials Science and Engineering Georgia Institute of Technology

Date Approved: March 10, 2015

Dedicated to my parents

## ACKNOWLEDGEMENTS

I would like to thank my advisor, Prof. Rao Tummala for the opportunity to work with him and learn from him. His vision and advice has always been the source of motivation and inspiration. It is a great fortune for me to have Prof. Tummala as my mentor and guide me over the years at Georgia Tech.

I would like to thank my mentors, Dr. Raj Pulugurtha and Dr. Vanessa Smet for their constant support and encouragement which is truly invaluable. Their deep technical insight has helped me in every step of my graduate study. I would also like to thank Nitesh Kumbhat, for his active guidance which helped me tremendously on starting the work and getting on the right path. I would like to express my sincere gratitude to Prof. Suresh Sitaraman, Prof. Preet Singh, and Prof. Richard Neu for serving on my committee and offering valuable advice and feedback.

I would like to thank all my colleagues and friends in the Packaging Research Center and the industry consortium, their friendship and support over the years have been invaluable in the completion of this work. Special thanks are due to Chris White, Jason Bishop, Toshitake Seki (NTK-NGK), Yoichiro Sato (AGC), Yuya Suzuki (Zeon Chemicals), Yutaka Takagi (NTK-NGK), Makoto Kobayashi (Namics Corporation), and Robin Taylor (Atotech GmbH, Berlin) for great lab support, cooperation, and discussion.

I would like to acknowledge Qualcomm Incorporated for the support of this work.

Finally, I owe everything to my parents, who have made me who I am today. I am extremely grateful for their unconditional love and support.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                  | iv     |

|-----------------------------------------------------------------------------------|--------|

| LIST OF TABLES                                                                    | viii   |

| LIST OF FIGURES                                                                   | ix     |

| LIST OF SYMBOLS AND ABBREVIATIONS                                                 | xvi    |

| SUMMARY                                                                           | xviii  |

| CHAPTER 1 INTRODUCTION                                                            | 1      |

| 1.1 Evolution of Electronic packaging                                             | 1      |

| 1.2 System drivers for large low-CTE packages                                     | 6      |

| 1.2.1 Drivers for large package size: 1) integration and 2) cost                  | 7      |

| 1.2.2 Drivers for low CTE: (1) first-level interconnection density and (2) reliab | bility |

| of ICs with ultra-low K dielectrics                                               | 9      |

| 1.3 Engineering and Scientific challenges in board-level interconnections with la | rge    |

| low-CTE packages                                                                  | 13     |

| 1.4 Objectives and approach                                                       | 16     |

| CHAPTER 2 Literature review                                                       | 19     |

| 2.1 Current technologies in manufacturing for board-level interconnections        | 19     |

| 2.2 Recent advances with solder interconnections                                  | 21     |

| 2.2.1 Metallurgical joint formation with solder alloys                            | 22     |

| 2.2.2 Evolution of solder microstructure and thermo-mechanical fatigue failure    | es 24  |

| 2.2.3 Advances in solders with microstructure and composition control             | 27     |

| 2.2.4 Advances in pad surface finish                                              | 30     |

| 2.3 Compliant interconnections with improved fatigue resistance              | 32    |

|------------------------------------------------------------------------------|-------|

| 2.3.1 Compliant metal structures for reliable interconnections               | 33    |

| 2.3.2 Low-modulus stress buffers for stress-relief                           | 37    |

| 2.3.3 Plastic core with metal shells for reliable interconnections           | 39    |

| 2.4 Electro-deposited copper wires for highly-reliable interconnections      | 40    |

| 2.4.1 Microstructure of electro-deposited copper                             | 41    |

| 2.4.2 Mechanical properties of submicrocrystalline and nanocrystalline coppe | er 42 |

| CHAPTER 3 Mechanical Design for reliability                                  | 45    |

| 3.1 Finite element modeling                                                  | 45    |

| 3.2 Material properties for finite element modeling                          | 47    |

| 3.3 Geometry optimization with one unit                                      | 49    |

| 3.3.1 "Double pads" structure for assembly convenience and higher bonding    |       |

| strength                                                                     | 49    |

| 3.3.2 The effect of copper wire diameter on the strain in interconnections   | 49    |

| 3.3.3 The effect of number of wires per interconnect                         | 50    |

| 3.4 Modeling with whole strip and estimation of fatigue life                 | 52    |

| 3.5 Fatigue life comparison against standard BGA SMT interconnections        | 58    |

| 3.6 Summary of the mechanical design                                         | 59    |

| CHAPTER 4 Materials and Processes for fabrication of the test vehicles       | 61    |

| 4.1 Summary of design inputs from finite element modeling                    | 61    |

| 4.2 Polymer Carrier                                                          | 61    |

| 4.3 Process development for copper wire fabrication                          | 62    |

| 4.3.1 Lithography optimization for high aspect ratio features                | 62    |

| 4.3.2 Electrolytic plating experiments for copper wire fabrication            | 64   |

|-------------------------------------------------------------------------------|------|

| 4.4 Fabrication process design                                                | 66   |

| 4.5 Fabrication of the Syron carrier                                          | 67   |

| 4.6 Fabrication of the copper wire arrays on the carrier                      | 70   |

| 4.7 Fabrication of the silicon package and the printed wiring board           | 75   |

| 4.8 Summary of the test vehicle fabrication                                   | 77   |

| CHAPTER 5 Assembly and reliability assessment                                 | 79   |

| 5.1 Assembly of the silicon package on PWB with MWA                           | 79   |

| 5.2 Challenges with assembly and processing defects observed after assembly   | 81   |

| 5.3 Reliability assessment                                                    | 86   |

| 5.3.1 Reliability performance analysis                                        | 86   |

| 5.3.2 Early failures induced by processing defects                            | 88   |

| 5.4 Analysis and discussion                                                   | 90   |

| 5.4.1 Analysis of critical material parameters                                | 91   |

| 5.4.2 Analysis of critical geometry parameters                                | 97   |

| 5.4.3 Effect of the change of material and geometry parameters on interconnec | tion |

| reliability                                                                   | 99   |

| 5.5 Summary                                                                   | 100  |

| CHAPTER 6 Summary and outlook                                                 | 102  |

| 6.1 Research summary                                                          | 102  |

| 6.2 Future work                                                               | 103  |

| References                                                                    | 105  |

# LIST OF TABLES

Page

| Table 1.1 Specific objectives of the study.                                                            | 17 |

|--------------------------------------------------------------------------------------------------------|----|

| Table 3-1 Anand constants for SAC 305.                                                                 | 47 |

| Table 3-2 Strain contour in copper wires with multiple wires per interconnect.                         | 51 |

| Table 3-3 Equivalent plastic strain range per cycle and corresponding fatigue life of interconnection. | 57 |

| Table 3-4 Fatigue life calculation for MWA and BGA interconnections.                                   | 59 |

| Table 4-1 Fatigue life of the interconnection with different carrier materials.                        | 62 |

| Table 5-1 Indentation test results from the as-assembled sample.                                       | 93 |

| Table 5-2 Anand model for SnAg eutectic solder [60].                                                   | 96 |

| Table 5-3 Effect of package thickness on interconnection reliability.                                  | 97 |

| Table 5-4 MWA fatigue life calculation with the refined model.                                         | 99 |

# LIST OF FIGURES

Page

| Figure 1.1 Evolution of electronic packaging                                                                                                                                                                                                               | 2  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 3D chip stacking with wire bonds (Courtesy of Palomar Technologies)                                                                                                                                                                             | 3  |

| Figure 1.3 3D ICs using TSVs (Courtesy of ST- Ericsson)                                                                                                                                                                                                    | 4  |

| Figure 1.4 Schematic of: (a) 2.5D packages, (b) 3D packages (Courtesy of Vijay Sukumaran of Georgia Tech PRC)                                                                                                                                              | 5  |

| Figure 1.5 Structure of large 3D package for direct attach to PWB                                                                                                                                                                                          | 6  |

| Figure 1.6 Growing I/O density and shrinking package interconnect pitch requesting low CTE packages (Courtesy of David McCann of Global Foundries)                                                                                                         | 7  |

| Figure 1.7 Demonstrator of GPU on interposer with on-interposer memories (Courtesy of Global Foundries)                                                                                                                                                    | 8  |

| Figure 1.8 Evolution of panel-based low CTE glass interposers for next-<br>generation packages. (Figure Courtesy: Prof. Rao Tummala, GT-PRC)                                                                                                               | 8  |

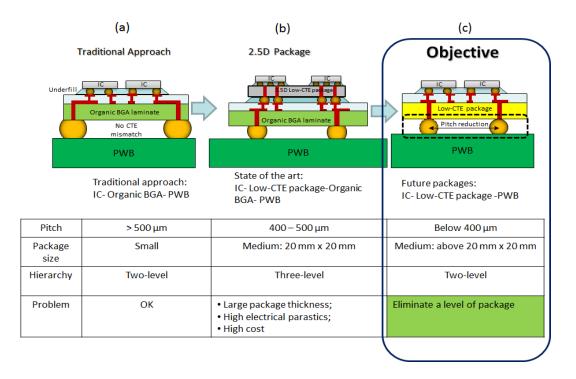

| Figure 1.9 Industry needs and challenges in board-level interconnections. (a) Traditional approach with organic package. (b) 2.5D low-CTE package with organic intermediate layer. (c) Direct interconnection from low-CTE package to printed wiring board | 12 |

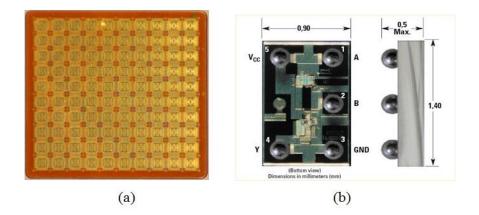

| Figure 1.10 Examples of low-CTE packages: (a) Pin Grid Array (PGA) package (Courtesy of IBM), (b) Wafer-level package (Courtesy of TI)                                                                                                                     | 13 |

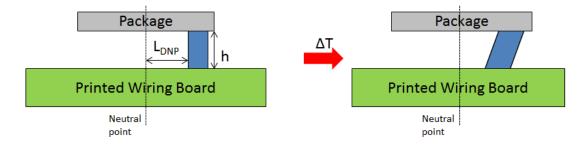

| Figure 1.11 Cyclic strain in solder joints induced by component CTE mismatch                                                                                                                                                                               | 14 |

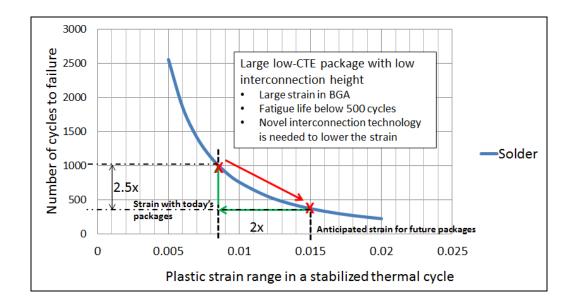

| Figure 1.12 Fatigue life of SnAgCu solder versus the plastic strain range in each                                                                                                                                                                          | 16 |

# thermal cycle

| Figure 1.13 Schematic of copper microwire array interconnections                                                                                          | 18 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 Pin grid array in high-performance computing applications for large low-CTE package to board interconnections [11]                             | 20 |

| Figure 2.2 Board level interconnections with ball grid array (Courtesy of Amkor)                                                                          | 21 |

| Figure 2.3 Wafer-level packaging process (Courtesy of IFC, Georgia Tech)                                                                                  | 21 |

| Figure 2.4 Material innovations in solder and base metals                                                                                                 | 22 |

| Figure 2.5 Equilibrium of surface tension at contact angle $\theta$                                                                                       | 23 |

| Figure 2.6 Optical microscopic images of (a) Sn-2.5%Ag-0.7%Cu, and (b) Sn-3.5%Ag-0.7%Cu (Courtesy of D.Q. Yu)                                             | 25 |

| Figure 2.7 SEM images for (a) Sn-2.5% Ag-0.7% Cu, and (b) Sn-3.5% Ag-0.7% Cu (Courtesy of D.Q. Yu)                                                        | 25 |

| Figure 2.8 Microstructure of $Ag_3Sn$ particles in SnAgCu (a) as-reflowed condition, (b) after 200 thermal cycles, and (c) after 1200 thermal cycles [16] | 27 |

| Figure 2.9 Cross section of a SAC105+0.25 Mn solder joint [20]                                                                                            | 29 |

| Figure 2.10 Effect of Bi addition on the microsturcture of SAC alloys [21]                                                                                | 30 |

| Figure 2.11 Crack at IMC/solder interface with ENIG surface finish                                                                                        | 31 |

| Figure 2.12 Cross section of solder joints after reflow and thermal aging: ENIG (a), (c), (e) and ENEPIG (b), (d), (f) [30]                               | 32 |

| Figure 2.13 Copper base with solder bump for first level interconnection [31]                                                                                          | 33 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.14 Super CSP by Fujitsu [33]                                                                                                                                  | 34 |

| Figure 2.15 G-Helix Interconnections [34]                                                                                                                              | 35 |

| Figure 2.16 WAVE <sup>TM</sup> Interconnections [35]                                                                                                                   | 36 |

| Figure 2.17 Microspring on silicon technology (MOST <sup>TM</sup> ) by FormFactor [36]                                                                                 | 36 |

| Figure 2.18 Au-MoCr-Au microspring fabrication and assembly [37]                                                                                                       | 37 |

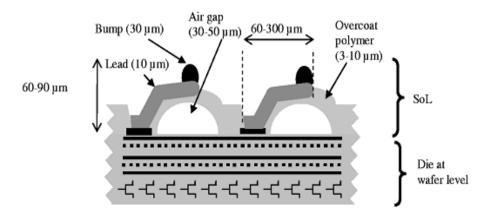

| Figure 2.19 Sea of leads interconnections [38]                                                                                                                         | 38 |

| Figure 2.20 Bump-on-polymer structure [40]                                                                                                                             | 38 |

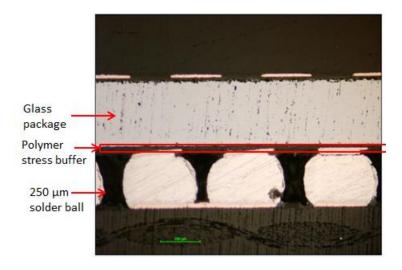

| Figure 2.21 Glass package to organic PWB interconnections with polymer stress buffer [41]                                                                              | 39 |

| Figure 2.22 Stress relief by polymer collars [42]                                                                                                                      | 39 |

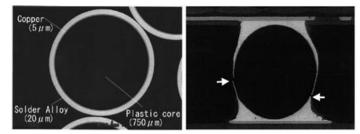

| Figure 2.23 Plastic core with solder shell interconnection [43]                                                                                                        | 40 |

| Figure 2.24 Polymer core with metal shell interconnection [44]                                                                                                         | 40 |

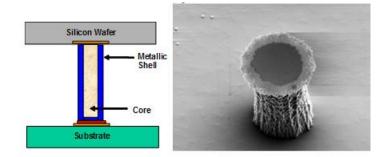

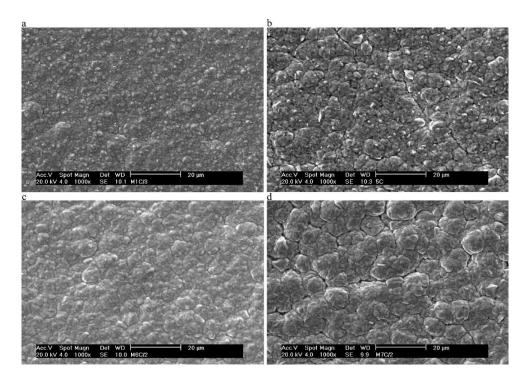

| Figure 2.25 SEM micrographs of the copper electrodeposits (a) direct current, (b) rectangular pulse current, (c) square pulse current and (d) triangular waveform [46] | 42 |

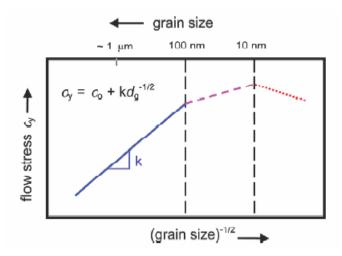

| Figure 2.26 Effect of grain size on yield stress [49]                                                                                                                  | 43 |

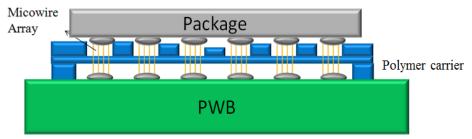

| Figure 3.1 Copper microwire array compliant interconnections                                                   | 45 |

|----------------------------------------------------------------------------------------------------------------|----|

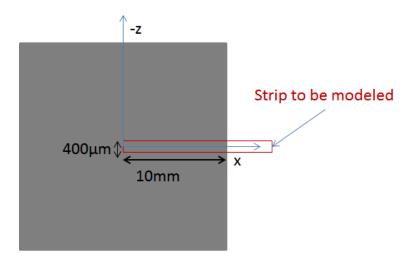

| Figure 3.2 Top view of the half-strip used in 2.5D modeling                                                    | 46 |

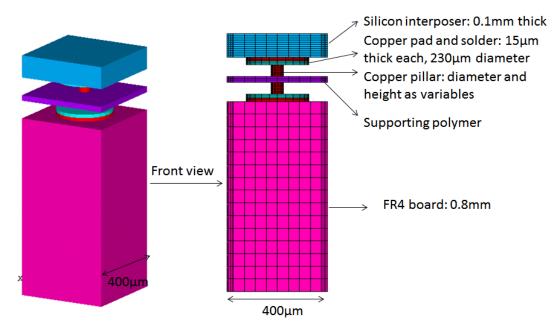

| Figure 3.3 Detailed structure of each interconnection unit for initial set up                                  | 46 |

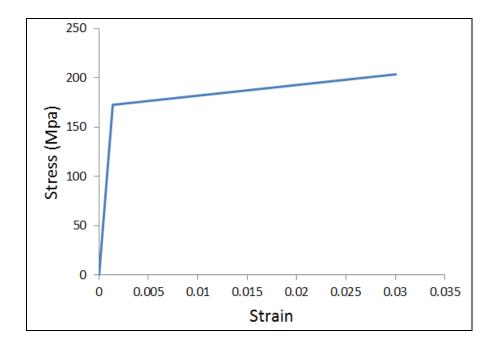

| Figure 3.4 Stress-strain curve of copper                                                                       | 48 |

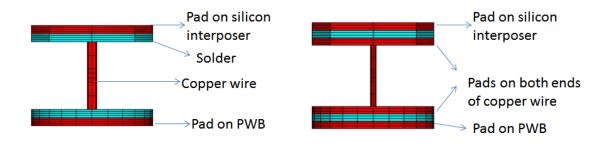

| Figure 3.5 "Double pads" structure                                                                             | 49 |

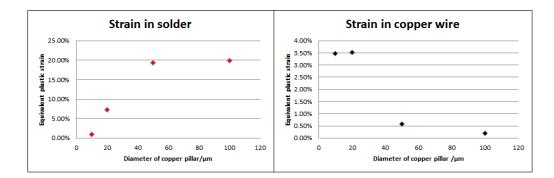

| Figure 3.6 Equivalent plastic strain in solder and copper microwire as a function of wire diameter             | 50 |

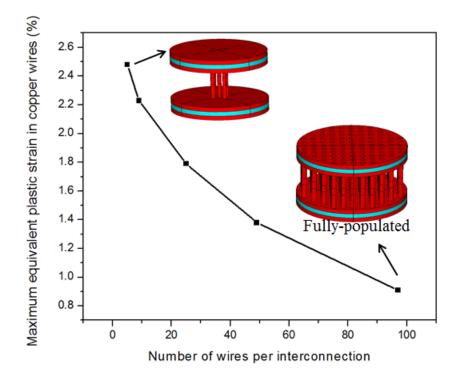

| Figure 3.7 Effect of number of copper wires on plastic strain.                                                 | 52 |

| Figure 3.8 (a) Detailed structure for edge units, (b) Simplified structure for inner units                     | 53 |

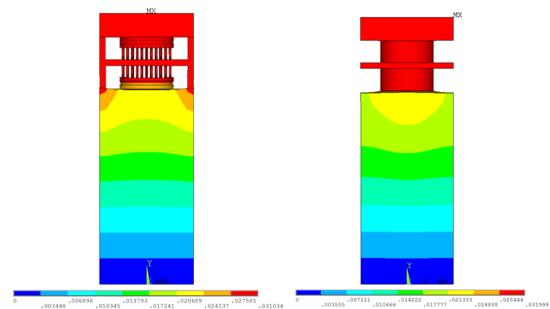

| Figure 3.9 Deformation in vertical direction under uniaxial load for microwire unit and simplified unit        | 54 |

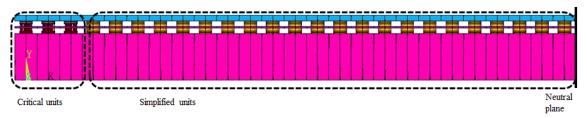

| Figure 3.10 Complete strip with simplified structure for inner units and detailed structure for critical units | 54 |

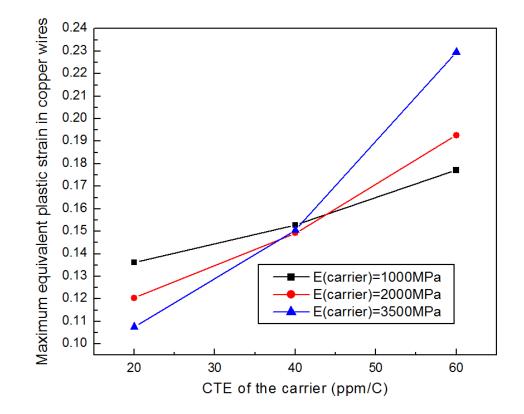

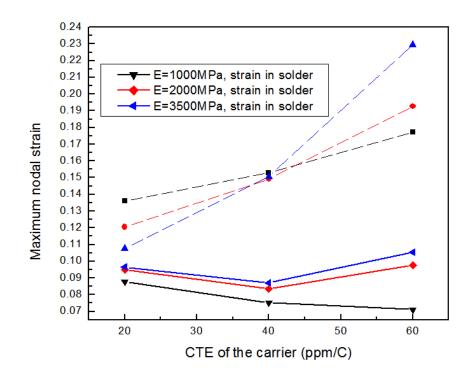

| Figure 3.11 The effect of modulus and CTE of the carrier                                                       | 55 |

| Figure 3.12 Corresponding strain in solder as a function of carrier property                                   | 56 |

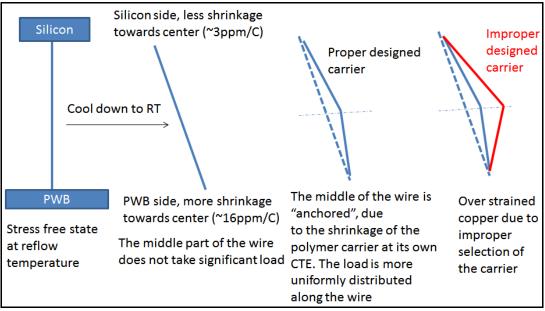

| Figure 3.13 Anchor effect of polymer carrier                                                                   | 58 |

| Figure 3.14 BGA interconnection unit                                                                           | 59 |

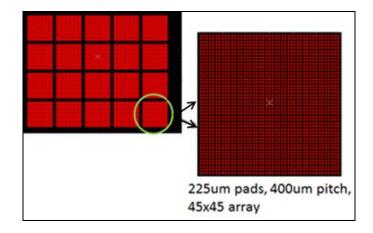

| Figure 4.1 Design of MWA Interconnection Insert                               | 61 |

|-------------------------------------------------------------------------------|----|

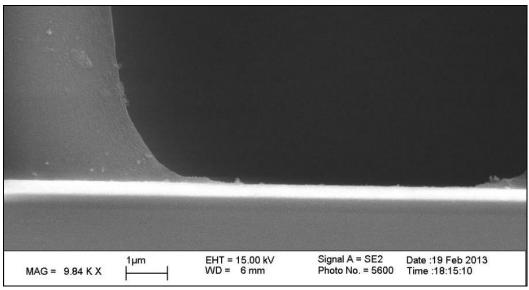

| Figure 4.2 Cross section of $15\mu m$ openings in $50\mu m$ thick resist      | 63 |

| Figure 4.3 Photoresist residue removal by plasma                              | 64 |

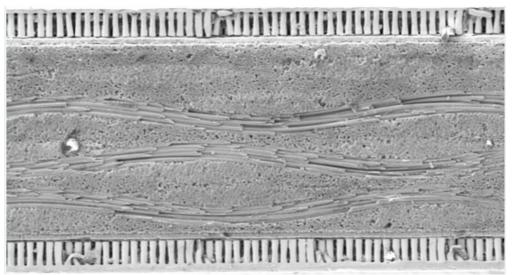

| Figure 4.4 Plated copper wires on both sides of a FR-4 substrate              | 65 |

| Figure 4.5 Copper wires fabricated from mask with 15 $\mu$ m features         | 66 |

| Figure 4.6 Wire dimension after microetching for (a) 3 minutes, (b) 6 minutes | 66 |

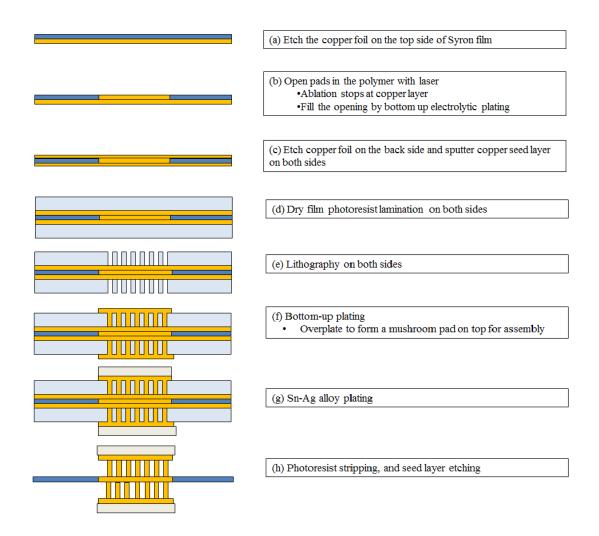

| Figure 4.7 Fabrication procedure for microwire array interconnections         | 67 |

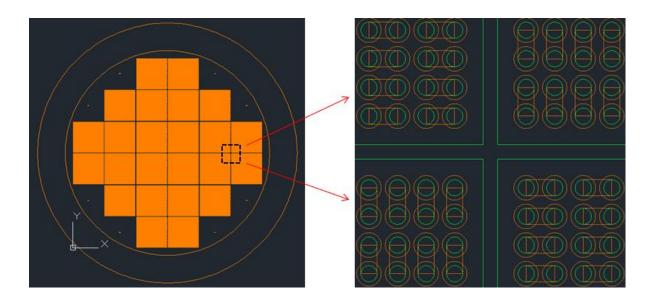

| Figure 4.8 Layout design for laser via drilling in the polymer carrier        | 68 |

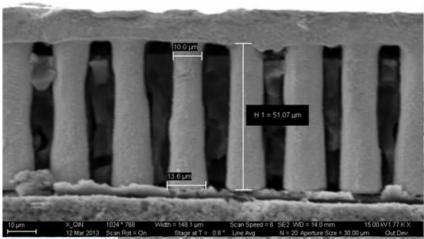

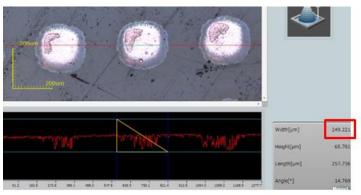

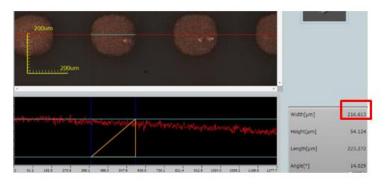

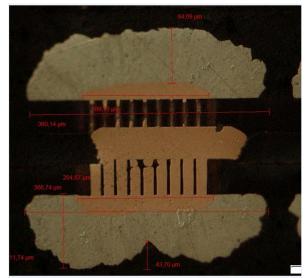

| Figure 4.9 Via dimension measurement                                          | 69 |

| Figure 4.10 Syron carrier with plated copper posts                            | 69 |

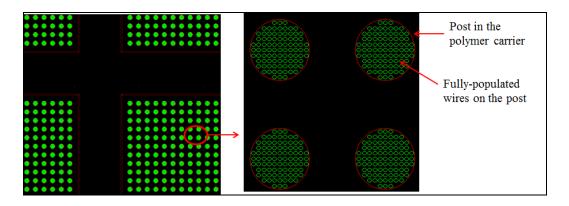

| Figure 4.11 Design of copper wires on the posts                               | 70 |

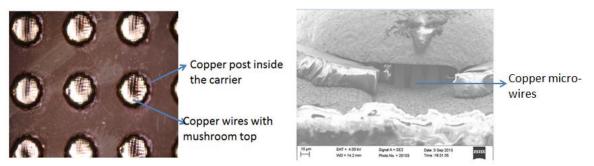

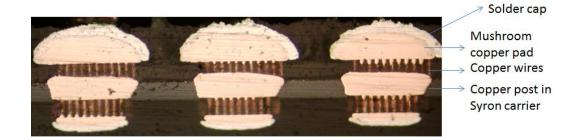

| Figure 4.12 Copper wires plated on the posts with overplated mushroom pads    | 71 |

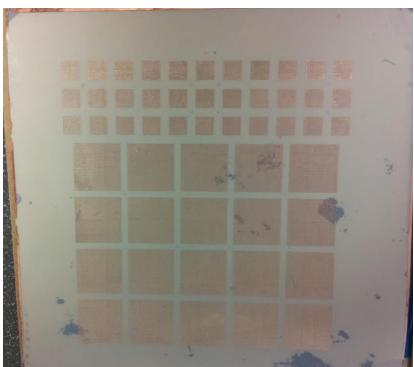

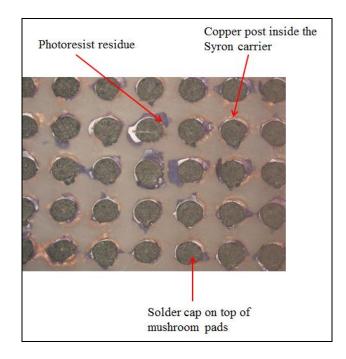

| Figure 4.13 Top view of the polymer carrier after solder plating              | 72 |

| Figure 4.14 Surface of plated copper posts in the Syron carrier               | 72 |

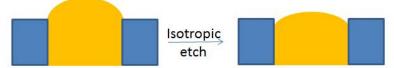

| Figure 4.15 Surfaces of the posts before and after isotropic microetch        | 73 |

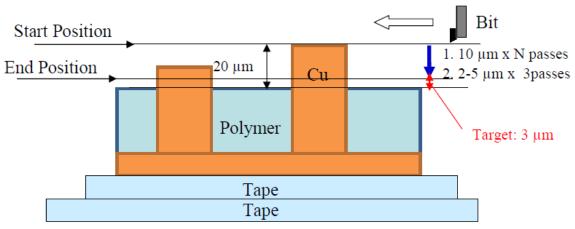

| Figure 4.16 Process illustration for mechanical planarization                                                                                      | 74 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

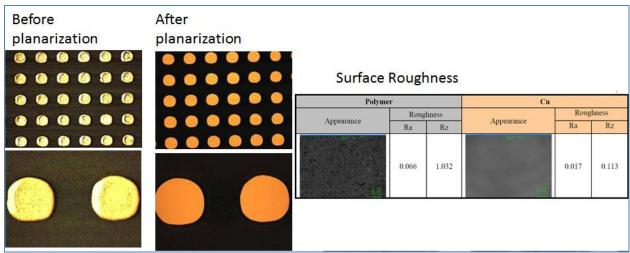

| Figure 4.17 Surface roughness before and after planarization                                                                                       | 74 |

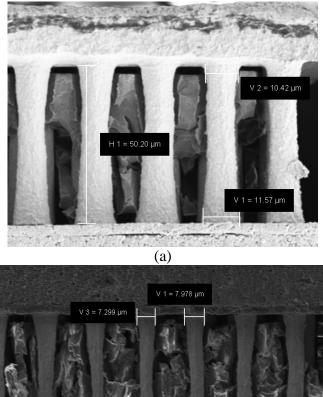

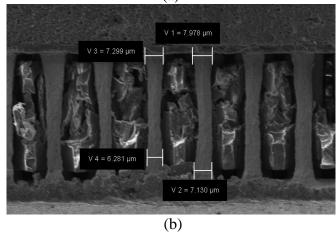

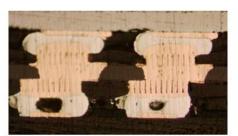

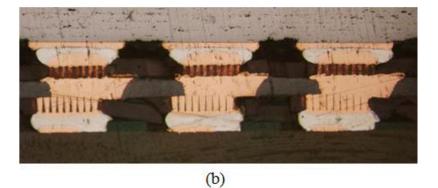

| Figure 4.18 Cross section of MWA interconnections                                                                                                  | 75 |

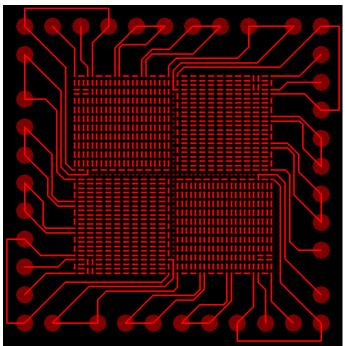

| Figure 4.19 Design of the silicon package                                                                                                          | 76 |

| Figure 4.20 Silicon package with ENIG surface finish                                                                                               | 77 |

| Figure 4.21 Design of the printed wiring board                                                                                                     | 77 |

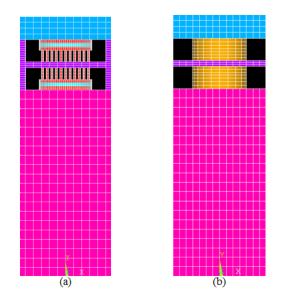

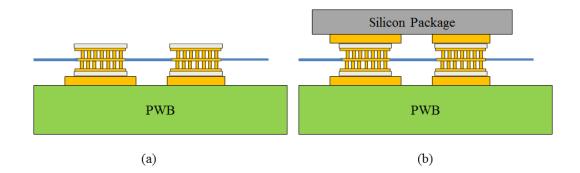

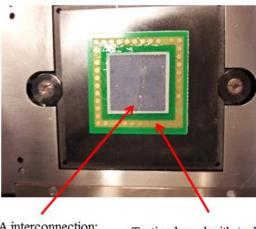

| Figure 5.1 Two-Step assembly process: (a) placement of the MWA interconnections onto the PWB, (b) placement of the silicon package, and reflow     | 80 |

| Figure 5.2 Syron carriers with MWA interconnections placed on PWB                                                                                  | 80 |

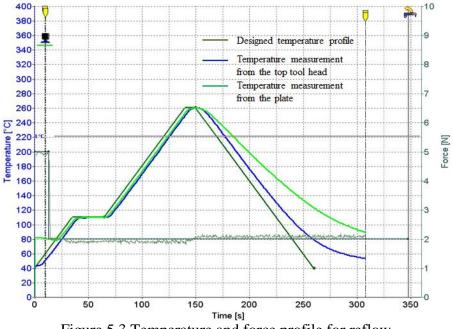

| Figure 5.3 Temperature and force profile for reflow                                                                                                | 81 |

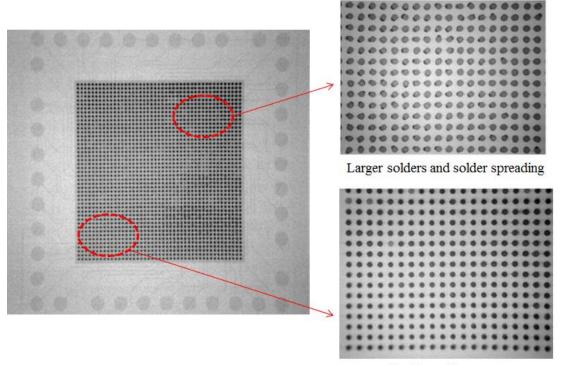

| Figure 5.4 Non-uniform and erratically plated solder                                                                                               | 83 |

| Figure 5.5 X-ray image of the solder bumps after assembly                                                                                          | 83 |

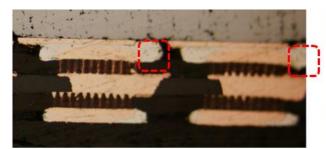

| Figure 5.6 Processing defects observed after assembly                                                                                              | 85 |

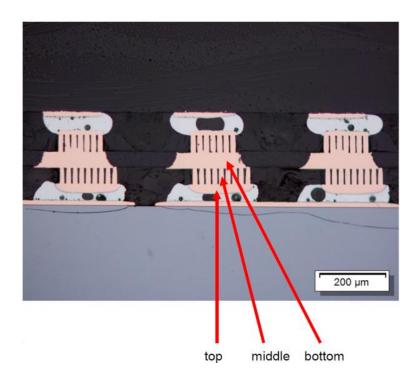

| Figure 5.7 Cross section of silicon package-MWA-PWB assembly (a) Sample without mechanical planarization, (b) Sample with mechanical planarization | 85 |

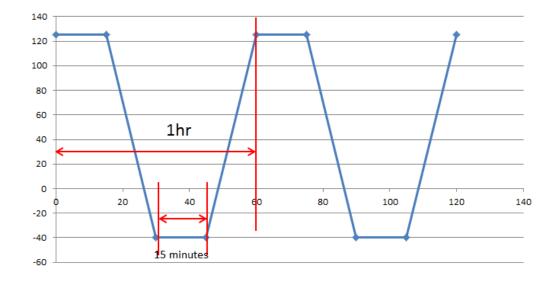

| Figure 5.8 Temperature profile of thermal cycling test                                                                                             | 86 |

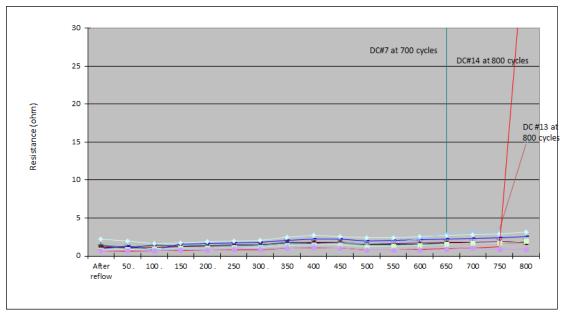

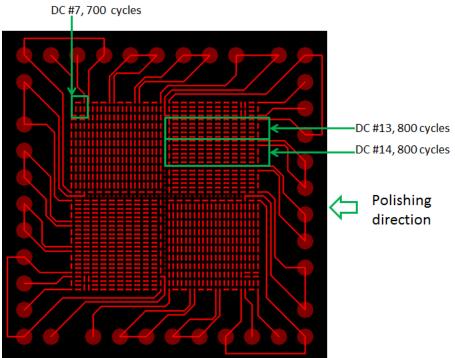

| Figure 5.9 Resistance measurement of sample #1                  | 87  |

|-----------------------------------------------------------------|-----|

| Figure 5.10 Location of failed daisy chains in sample #1        | 87  |

| Figure 5.11 Interconnections located in daisy chain #13         | 88  |

| Figure 5.12 Interconnections towards the middle                 | 88  |

| Figure 5.13 Resistance measurement of sample #2                 | 89  |

| Figure 5.14 Cross section of sample #2 at 400 cycles            | 90  |

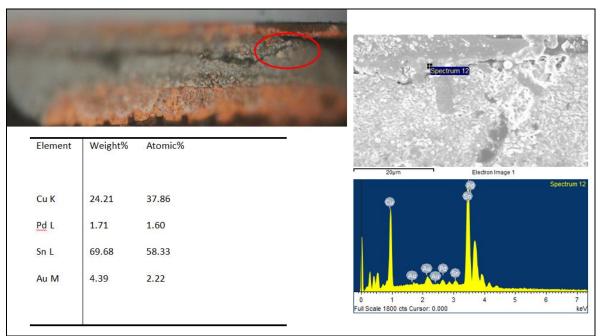

| Figure 5.15 SEM and EDS analysis on etched sample               | 90  |

| Figure 5.16 Indentation locations in the as-assembled sample    | 92  |

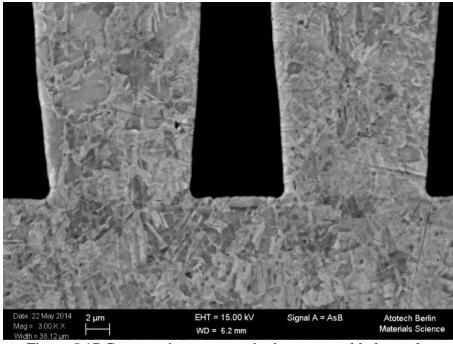

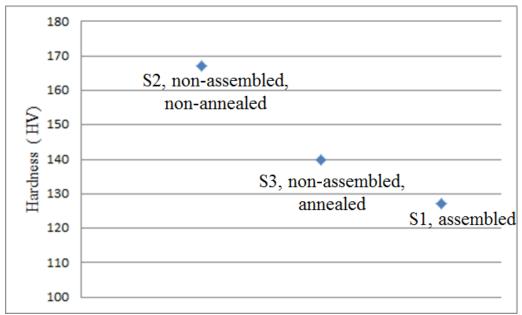

| Figure 5.17 Copper microstructure in the as-assembled sample    | 93  |

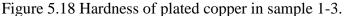

| Figure 5.18 Hardness of plated copper in sample 1-3             | 94  |

| Figure 5.19 Microstructure of plated copper in sample 1-3       | 94  |

| Figure 5.20 Effect of grain size on yield stress of copper [59] | 95  |

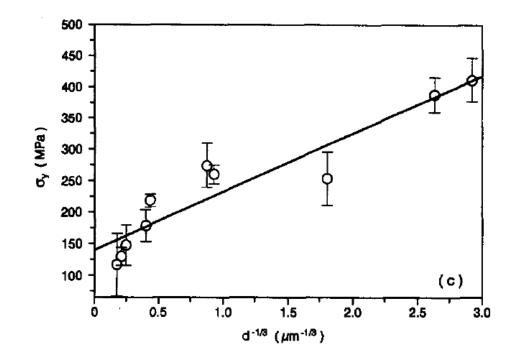

| Figure 5.21 Model with 600 µm silicon                           | 97  |

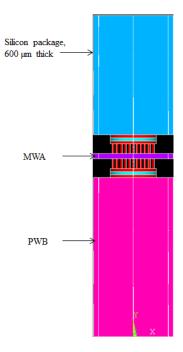

| Figure 5.22 MWA geometries in the original and refined models   | 99  |

| Figure 6.1 Single-sided MWA interconnections                    | 103 |

# LIST OF SYMBOLS AND ABBREVIATIONS

| BGA    | Ball grid array                                         |

|--------|---------------------------------------------------------|

| CMOS   | Complementary metal-oxide semiconductor                 |

| CTE    | Coefficient of thermal expansion                        |

| DRAM   | Dynamic random access memory                            |

| ENEPIG | Electroless nickel electroless palladium immersion gold |

| ENIG   | Electroless nickel immersion gold                       |

| FEM    | Finite element method                                   |

| FPGA   | Field-programmable gate array                           |

| HASL   | Hot air solder leveling                                 |

| IMC    | Intermetallic compound                                  |

| LTCC   | Low temperature co-fired ceramic                        |

| МСМ    | Multi-chip module                                       |

| MWA    | Microwire array                                         |

| OSP    | Organic solderability preservative                      |

| PGA    | Pin grid array                                          |

| PWB   | Printed wiring board             |

|-------|----------------------------------|

| RDL   | Redistribution layer             |

| SCP   | Single chip package              |

| SEM   | Scan electron microscope         |

| SIP   | Stacked ICs and packages         |

| SMT   | Surface mount technology         |

| SRAM  | Static random access memory      |

| ТАВ   | Tape automated bonding           |

| TSV   | Through-silicon via              |

| WLCSP | Wafer level chip scale packaging |

| WLP   | Wafer-level packaging            |

## **SUMMARY**

The trend to high I/O density, performance and miniaturization at low cost is driving the industry towards shrinking interposer design rules, requiring a new set of packaging technologies. Low-CTE packages from silicon, glass and low-CTE organic substrates enable high interconnection density, high reliability and integration of system components. However, the large CTE mismatch between the package and the board presents reliability challenges for the board-level interconnections. Novel stress-relief structures that can meet reliability requirements along with electrical performance while meeting the cost constraints are needed to address these challenges. This thesis focuses on a comprehensive methodology starting with modeling, design, fabrication and characterization to validate such stress-relief structures. This study specifically explores SMT-compatible stress-relief microwire arrays in thin polymer carriers as a unique and low-cost solution for reliable board-level interconnections between large low-CTE packages and printed wiring boards.

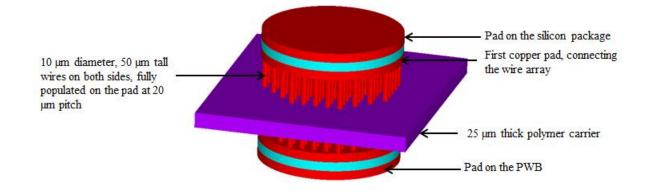

The microwire arrays are pre-fabricated in ultra-thin carriers using low-cost manufacturing processes such as laser vias and copper electroplating, which are then assembled in between the interposer and printed wiring board (PWB) as stress-relief interlayers. The microwire array results in dramatic reduction in solder stresses and strains, even with larger interposer sizes (20 mm  $\times$  20 mm), at finer pitch (400 microns), without the need for underfill. The parallel wire arrays result in low resistance and inductance, and therefore do not degrade the electrical performance. The scalability of the structures and the unique processes, from micro to nanowires, provides extendibility to finer pitch and larger package sizes.

Finite element method (FEM) was used to study the reliability of the interconnections to provide guidelines for the test vehicle design. The models were built

xviii

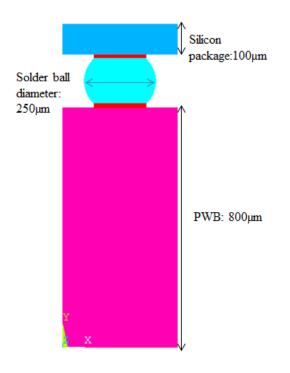

in 2.5D geometries to study the reliability of 400  $\mu$ m-pitch interconnections with a 100  $\mu$ m thick, 20 mm × 20 mm silicon package that was SMT-assembled onto an organic printed wiring board. The performance of the microwire array interconnection is compared to that of ball grid array (BGA) interconnections, in warpage, equivalent plastic strain and projected fatigue life.

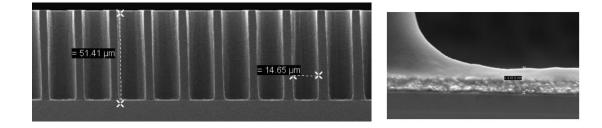

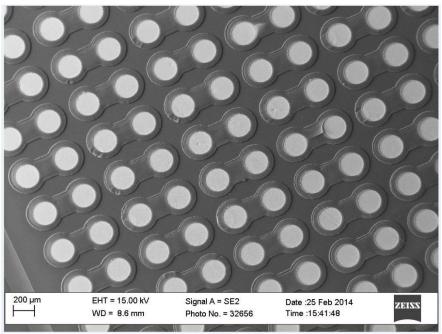

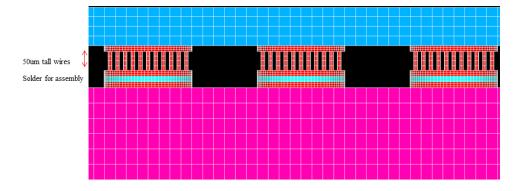

A unique set of materials and processes was used to demonstrate the low-cost fabrication of microwire arrays. Copper microwires with 12 µm diameter and 50 µm height were fabricated on both sides of a 50 µm thick, thermoplastic polymer carrier using dryfilm based photolithography and bottom-up electrolytic plating. The copper microwire interconnections were assembled between silicon interposer and FR-4 PWB through SMT-compatible process. Thermal mechanical reliability of the interconnections was characterized by thermal cycling test from -40°C to 125°C. The initial fatigue failure in the interconnections was identified at 700 cycles in the solder on the silicon package side, which is consistent with the modeling results. This study therefore demonstrated a highly-reliable and SMT-compatible solution for board-level interconnections between large low-CTE packages and printed wiring board.

## **CHAPTER 1**

## **INTRODUCTION**

#### **1.1 Evolution of Electronic packaging**

Moore's Law [1], which holds that the number of transistors on an IC doubles every 18 months, has driven the transistor scaling which enabled cost reduction and performance-enhancement at device level. However, this CMOS-based era is beginning to pose major barriers beyond 22 nm due to design complexity, minimal performance gain and escalating wafer costs. A new era focusing on packaging and architecture innovations, going beyond the shrinkage of single devices and single- or multichip wirebond and flipchip packages, is emerging to address these barriers. The future of electronic system performance, miniaturization and integration are driven by these packaging innovations.

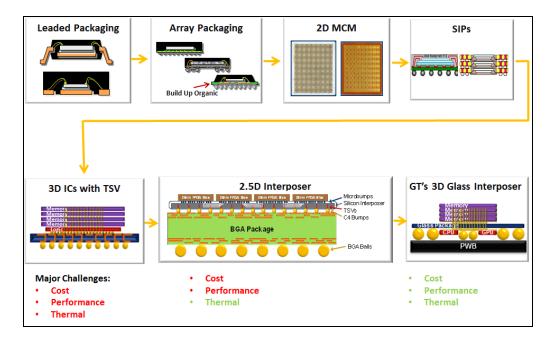

Figure 1.1 demonstrates the evolution of electronic packaging. Conventionally single chip packages (SCPs) are used to support each single device to ensure its electrical, mechanical and thermal performance, testability, and enable the device to be attached to the system board. One popular single chip package structure is the leaded package, where the interconnections are achieved by the metal leads located on the peripheral area of the package. The main challenge of leaded package is the low pin count, which limits its application to low-end microprocessors and memories including DRAMs and SRAMs. Area array packaging significantly improved the I/O count by using the whole area of the package for interconnections. Area array packages, such as pin grid arrays (PGAs) and ball grid arrays (BGAs) have been extensively used in microprocessors.

Figure 1.1 Evolution of electronic packaging.

Multi-chip packages, where multiple chips or a sub-system is packaged within one package unit, have become a major thrust because of the high performance and density compared to SCPs. Multi-chip packages allow the chips to be spaced more closely with less overall volume and weight than individually packaged parts [2]. Traditionally, multiple chips are assembled on a package in a 2D format for highperformance applications, pioneered by the ceramic MCM (multi-chip module) architecture of IBM [3]. Organic packaging, also pioneered by IBM, emerged as the next major packaging technology for these digital and also RF applications and is currently used as the primary workhorse in the industry. Such 2D systems have been limiting the system size and performance because of large interconnection lengths and package size.

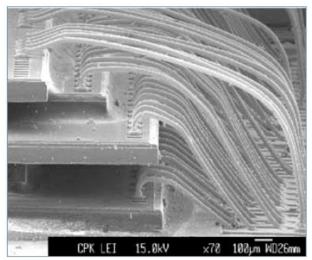

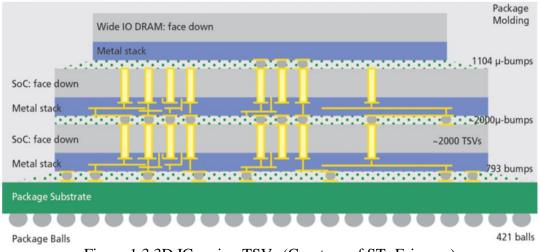

To reduce the system footprint and interconnection length, stacked ICs and packages (SIPs) are emerging, where two or more layers of chips are integrated vertically. Besides the benefits of footprint and bandwidth, the SIP also enables partitioning of a large chip into multiple smaller dies which improves the yield and reduces the cost. There are two categories of SIPs: (1) stacking by wire bonds, tape automated bonding (TAB), or flip-chip technologies, and (2) stacking by through-silicon vias (TSVs). Figure 1.2 shows an example of SIP with wire bonds. The wire bonds interconnection technology has high yield, mature infrastructure and low cost, but limits the interconnection density, since the wires are only located along the edges. Similar challenges apply to SIPs with TAB and flip-chip technologies. TSVs are being developed to enable vertical interconnection through the chips to further reduce the interconnection length and signal latency, to achieve ultra-high interconnection density and bandwidth, as illustrated in Figure 1.3. However, the 3D chip-stacking faces critical challenges including the fabrication of TSVs, process integration, management of stress and strain induced by the vias in silicon, and heat generation from the large chip stacks.

Figure 1.2 3D chip stacking with wire bonds (Courtesy of Palomar Technologies).

Figure 1.3 3D ICs using TSVs (Courtesy of ST- Ericsson).

To address the limits of 3D ICs, and achieve even higher performance, smaller formfactor, lower cost and higher functionality, novel concepts such as 2.5D and 3D packages are being explored.

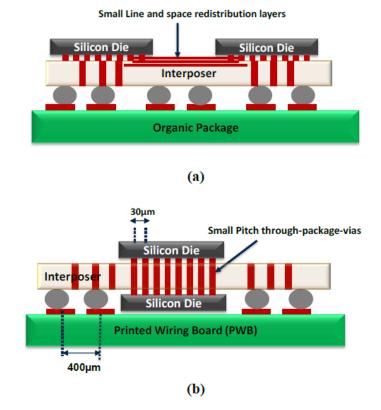

In a 2.5D package, the ICs are integrated side-by-side through the RDLs (redistribution layers), which are several layers of copper traces and microvias. The dies are then connected to the BGAs on the board level by through-package-vias, as shown in Figure 1.4a. Copper traces with ultra-fine line and space, and microvias with ultra-fine pitch can be achieved on the packages, which allows for short interconnections between the ICs and thus high bandwidth. By having the ICs side-by-side, 2.5D packages resolves the thermal issues posed by 3D ICs, but faces challenges including larger footprint of the system and therefore performance and cost concerns.

In a 3D package, the ICs are assembled on both sides of the interposers, as shown in Figure 1.4b. The 3D packaging scheme allows for vertical interconnection between the logical and memory chips by through-package-vias at extremely fine pitch (as low as 20-40  $\mu$ m), and promises even higher interconnection density and bandwidth, higher performance and lower cost compared to the 2.5D scheme.

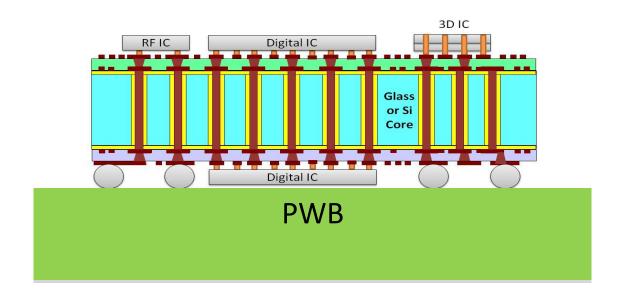

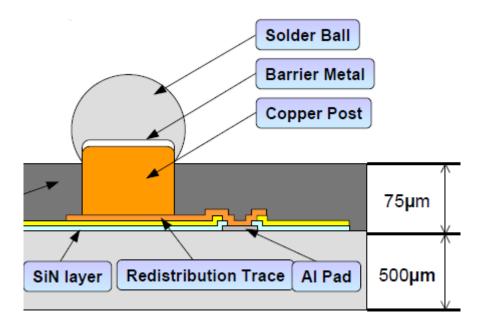

A closer look of the interconnection structures in 3D packages is shown in Figure 1.5. There are typically two levels of interconnections in the package, which connect the copper wiring on the chip with submicron dimensions, to the wiring on the board that is much larger, typically five hundred microns to several millimeters. The first level of interconnection is between the chip and the package. This interconnection is accomplished by a variety of methods, such as wire bonding and flip chip assembly. The wiring on top side of the package is then redistributed and connected to the bottom side using through-vias. The second level of interconnection is between the package substrate to organic printed wiring board. This connection is usually achieved with metallurgical bonding using solder alloys.

Figure 1.4 Schematic of: (a) 2.5D packages, (b) 3D packages (Courtesy of Vijay Sukumaran of Georgia Tech PRC).

Figure 1.5 Structure of large 3D package for direct attach to PWB.

### 1.2 System drivers for large low-CTE packages

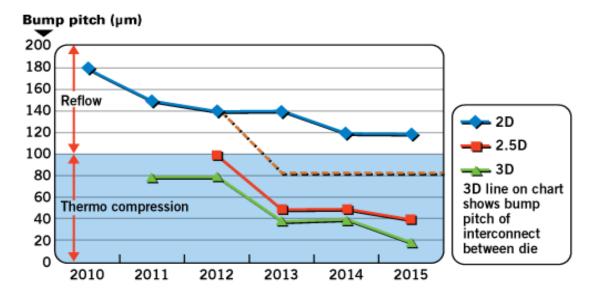

Both 2.5D and 3D packages aim at reducing interconnection length to lower power consumption and latency, as well as increase the number of interconnections to satisfy the demand for higher bandwidth [4]. Lower interconnection length and higher interconnection density can benefit mobile devices, such as smart phones, by enabling more sophisticated functions without increasing product size and power consumption; as well as high-performance computers, by providing 3D memory stacks close-by the processor cores. The increasing demand for heterogeneous integration, high bandwidth and computing power, therefore requires further shrinkage of the interconnection pitch at the package level (Figure 1.6), and new package materials and technologies with unprecedented wiring capability.

Figure 1.6 Growing I/O density and shrinking package interconnect pitch requesting low CTE packages (Courtesy of David McCann of Global Foundries).

### 1.2.1 Drivers for large package size: 1) integration and 2) cost

The need for high performance is also driving increase in package size. Such large package sizes are primarily needed for two reasons.

*Integration*: The packages for advanced smart systems are multifunctional subsystems which integrate RF chipset, passives, and mobile processors. With the growing complexity and increasing functionality, more chips and devices will be integrated on a package, thus driving the need for large mobile packages.

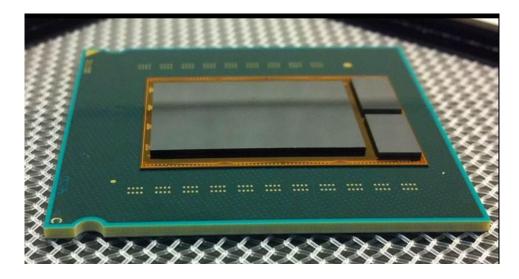

*Cost*: The requirements for high-speed computing and networking have boosted the number of transistors needed for the system. However integrating all the functions on a large chip is both extremely expensive and technically challenging. Integration at the package level by having multiple smaller dies allows for much lower cost and provides design convenience. The hybrid integration of memory-intensive and multi-core logic processors or multi-logic devices such as ASICs or FPGAs in 3D and 2.5D architectures within the packages, therefore drives the increase of package sizes. Xilinx has demonstrated a 2.5D silicon package which integrated four FPGA modules, each of 7

mm x 12 mm, and the packages size was 25 mm x 31 mm [5]. The recently released game console Sony PS4 utilizes a GPU on interposer with a 512-wide data bus and on-interposer memory, as shown in Figure 1.7.

Figure 1.7 Demonstrator of GPU on interposer with on-interposer memories (Courtesy of Global Foundries).

Figure 1.8 Evolution of panel-based low CTE glass interposers for next-generation packages. (Figure Courtesy: Prof. Rao Tummala, GT-PRC).

<u>1.2.2 Drivers for low CTE: (1) first-level interconnection density and (2) reliability</u> of ICs with ultra-low K dielectrics

*First-level interconnection density*: The demand for high interconnection density on the package requires small interconnection pitch and low stand-off height, which increases the strain in the first-level interconnections. To ensure good interconnection reliability at high density, low pitch and small geometrical dimension, package materials with low CTE which matches the CTE of the die is preferred.

*Reliability of ICs with ultra-low K dielectrics*: Organic packages have mismatched coefficient of thermal expansion (CTE) with the ICs, which induces high stress in the ultra-low-K on-chip dielectrics, and the warpage of the substrates. The elevated stress, adding on to the poor adhesion and low fracture strength of low-K materials, further causes delamination and fracture of the back end of the line (BEOL) stack [6]. The reliability demand therefore favors packages with lower CTEs.

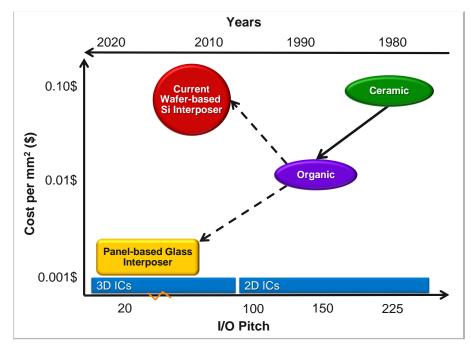

The need for reduced packaging costs and I/O pitch has, however, led to the replacement of low-CTE ceramic packages with organic packages as illustrated in Figure 1.8, contrary to the need described above. Organic materials are most commonly used for today's packages, as shown in Figure 1.9 (a). They are easily processable and cost efficient. However, organic substrate systems are known to have poor dimensional stability, which limits their miniaturization, as well as through-vias pitch and reliability for high density interconnections. Traditional organic packages also have a high CTE of 15-18 ppm/C. To enable higher interconnection density on the package, new package materials with low CTE and outstanding dimensional stability are required.

A new generation of silicon, glass and low-CTE organic packages are being developed to address these fundamental challenges associated with traditional organic substrates [7] as shown in the left side of Figure 1.. Compared to traditional organic substrates, the novel substrates have excellent dimensional and thermal stabilities, thereby, enabling ultra-high I/O densities. While their low coefficient of thermal expansion (CTE ~ 3ppm/°C), approaching that of the die helps to reduce the stresses in the chip-package interconnections and in the fragile low-K dielectrics, their CTE being so low compared to printed wiring boards (PWB, CTE~17 ppm/°C) on which they are assembled to form the final system, causes fatigue-related reliability failures for board-level interconnections.

Three types of such low-CTE packages are prevalent in R&D today. Silicon interposers provide high-density through-silicon vias (TSVs) and RDL using back-end-of-the-line (BEOL) processes to interconnect the ICs. Silicon has outstanding dimensional stability, surface smoothness and mature processing techniques to achieve high I/O density. However, the semi-conducting nature of silicon requires insulting liners in the TSVs for electrical isolation, which adds on processing complexity and limits the electrical performance. In addition, there are cost challenges with silicon packages, due to a) the wafer size is limited (200-300mm), which limits the number of large packages that can be yield per wafer, b) The BEOL processes, such as PVD, CVD and RIE, are costly.

Major progress has also been made in the leading-edge organic substrates with low CTE, high modulus and high Tg, which have achieved 12-15  $\mu$ m line and space, and 120  $\mu$ m I/O pitch. However, fundamental challenges exist for further miniaturization, including (1) the visco-plastic properties of organic materials limiting the dimensional stability and layer-to-layer registration, and (2) warpage of the package due to thermal processing in critical zones, such as dielectric lamination and curing, and assembly.

As an alternative, Georgia Tech PRC is pioneering glass-based 2.5D and 3D packages for unparalleled miniaturization, performance and cost, beyond today's integration approaches. The glass package consists a) of an ultra-thin substrate, b) made of glass with the ultra-low electrical loss, c) with ultra-short through-package via for double-sided assembly of active and passive components separated by only about 50

microns in interconnect length, d) embedded and surface-assembled ultrathin actives and passives, e) using ultra short, low-temperature and fine-pith Cu-Cu interconnections with high current handling, f) integrated thermal and shielding structures. The 3D glass substrate uses finer-pitch RDL wiring layers and TPVs, compared to the existing ceramic and organic substrates. It reduces the X-Y footprint of the module at least by half, by virtue of double-side mounting, enabled by low-cost and small-pitch through-vias, and by embedding of active and passive devices in high precision cavities, allowing for 3D stacking of multiple ICs and passives. The passives footprint is also reduced by direct deposition of thin-film passives or separately fabricating testable and yieldable ultra-thin glass substrates referred to as 3D IPDs, which are then diced and assembled onto the mother glass substrate. The reduction in thickness of the module, in addition to ultra-thin glass and ultra-thin RDL layers is due to ultra-short device-to-substrate interconnections that are about 10µm tall, compared to the flip-chip solder interconnections that are 100µm. Thermal management of ICs is addressed by incorporating thermal vias in the glass, or direct integration of heat-spreaders on the back of the die.

The current approach to achieve reliable interconnections for these low-CTE packages is to insert an intermediate organic ball-grid-array (BGA) laminate, as shown in Figure 1.9 (b). The additional organic package decouples the stress in the interconnections, at the same time however, increases the thickness of the system, enlarges the electrical parasitics and decreases the performance. The ultimate goal is to eliminate the organic BGA layer, and achieve direct and surface mount technology (SMT) compatible interconnections from the low CTE packages to the PWB, as shown in Figure 1.9 (c).

Figure 1.9 Industry needs and challenges in board-level interconnections. (a) Traditional approach with organic package. (b) 2.5D low-CTE package with organic intermediate layer. (c) Direct interconnection from low-CTE package to printed wiring board.

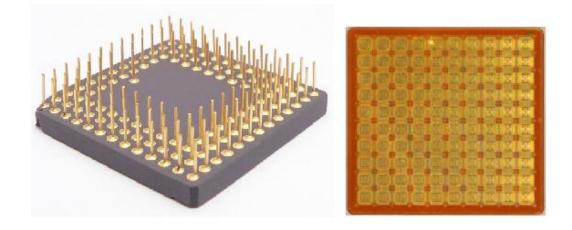

Direct assembly of low CTE packages on PWB has so far been accomplished with pin grid array (PGA) packages for high-performance computing applications (Figure 1.10 a). While PGA packages are not assembled by standard SMT processes at small pitch, they have the same fundamental problem, the mismatch-driven reliability. This problem is solved by using high aspect ratio pins to lower the interconnection strain and improve its reliability. Wafer level packaging of ICs for direct assembly on PWB without the need of an intermediate package forms another class of low CTE packages, as shown in Figure 1.10 b. WLPs are made of small silicon ICs and yet assembled on PWBs with acceptable reliability, because they are smaller in sizes, typically less than 7mm, and therefore smaller strains in the interconnections. The redistribution layers, in addition, serve as stress-buffer layers and help improve the reliability of interconnections.

Figure 1.10 : Examples of low-CTE packages: (a) Pin Grid Array (PGA) package (Courtesy of IBM), (b) Wafer-level package (Courtesy of TI).

## 1.3 Engineering and Scientific challenges in board-level interconnections with

#### large low-CTE packages

Solders are widely used as the interconnections between ICs and packages, as well as between packages and boards. Eutectic tin lead (SnPb) alloy has been the material of choice for SLI because it exhibits good mechanical properties and low-temperature processability. However, there has been a decline in the use of lead because of its toxicity, leading to the investigation of alternative Pb-free materials. Sn-based near eutectic or eutectic alloy systems such as SnAg, SnCu, SnSb, SnZn, SnIn, SnBi and SnAgCu are the primary candidates to replace traditional lead-bearing solders. Among these alloys, SnIn and SnBi have low melting points, but possess inferior mechanical properties. Wojciechowki et al. reported that SnZn does not provide good wettability, and has poor corrosion resistance compared to SnPb [8]. In addition, SnSb is not a good candidate due to the low ductility. Among the remaining candidates - SnCu, SnAg and SnAgCu - SnCu is the most inexpensive alloy available, but has highest melting point and poorest mechanical properties, as reported by Richards et al [9]. SnAg and SnAgCu have good mechanical properties and solderability, and are the most popular lead-free solder systems.

Lead-free alloy systems, which are invariably Sn-rich, are found to be less ductile and more prone to failures. When used for assembly of low-CTE packages on PWB, the reliability of lead-free solder interconnections becomes even more of a concern due to more aggressive thermo-mechanical loading. Therefore, traditional Pb-free alloys have fundamental limitations in addressing the thermo-mechanical reliability issue under high CTE mismatch.

Figure 1.11 Cyclic strain in solder joints induced by component CTE mismatch.

As shown in Figure 1.11, the difference in coefficient of thermal expansion (CTE) between the package (silicon or glass) and the organic printed wiring board induces cyclic thermomechanical loading in the solder joints when the device is in operation. When the system is powered on, the device heats up causing expansion, and when it is powered off, the device cools down causing contraction. The displacement of a solder joint due to temperature change ( $\Delta X$ ) is given by:

$$\Delta X = L_{DNP} (\alpha_{PWB} - \alpha_{pac}) \Delta T$$

(1.1)

$L_{DNP}$  is the distance to neutral point (DNP), which is the distance from the joint to the center of the package substrate.  $\Delta T$  is the temperature change during each loading cycle;  $\alpha_{pac}$  and  $\alpha_{PWB}$  are the CTEs of package and PWB, respectively. Due to the geometrical symmetry, the position of substrate center is not affected by thermal expansion. Therefore, this geometric center is also referred to as the neutral point. Assuming the height of joint to be h, the shear strain range for the temperature change is:

$$\Delta \gamma = \frac{L_{\text{DNP}}(\alpha_{\text{PWB}} - \alpha_{\text{pac}})\Delta T}{h}$$

(1.2)

From Equations (1.1) and (1.2), it can be seen that the cyclic strain induced on the solder joints is determined by the distance to neutral point, the difference in CTE, temperature range and the geometry of the joints.

Emerging packages aggravate the strain in solder joints in three ways. The trend towards low-CTE packages made of silicon, glass and low-CTE organic materials causes large CTE mismatch between the package and the board. The large package size of as much as 50mm in the emerging 2.5D and 3D multi-chip architectures for high-bandwidth applications in high-performance computing, networking and consumer products further increases the strains as seen in Equation (1.2). The third reason from high strains comes from the shrinking board level interconnection pitch, which is projected to reach below 300  $\mu$ m, requires lower stand-off height and interconnections and adds other reliability challenge. These three factors - the CTE mismatch at package-to-board level, large interposer size, and shrinking interposer-board interconnection pitch - create large thermo-mechanical strain in the board-level interconnections.

Current packages utilize solder ball arrays to provide electrical connections between the package and PWB, and also provide mechanical support. Eutectic SnAg and SnAgCu are the most common solders in use today. The plastic strain range in each thermal cycle is related the fatigue life of the solders by Coffin-Manson relationship:

$$N_{f} = 0.5 \left(\frac{2\varepsilon_{f}}{\Delta\gamma_{P}}\right)^{\frac{1}{c}}$$

(1.3)

where  $N_f$  is the number of cycles to failure,  $\Delta \gamma_P$  is the cyclic plastic strain range,  $\varepsilon_f$ and c are material-related constants [10]. Therefore, the fatigue performance deteriorates with larger plastic strain. For a given package, the solder at the corner has the maximum DNP, and is most likely to fail. Figure 1.12 shows the fatigue life of SnAgCu solder as a function of plastic strain in each thermal cycle. For traditional organic BGAs, the plastic strain per cycle in the solder is about 0.85%, which corresponds to 1000 cycles of fatigue life. However, with the application of large low-CTE packages and small interconnection pitches, the strain is anticipated to reach 1.5%. With close to 2X increase in the plastic strain, the projected fatigue life is below 500 cycles, far below the reliability requirement of the electronic systems.

This board-level interconnection reliability has been identified as a grand challenge by the semiconductor and electronics industry because it creates several bottlenecks for advances in ultra- high I/O 2.5D and 3D packages and systems.

Figure 1.12 Fatigue life of SnAgCu solder versus the plastic strain range in each thermal cycle.

### 1.4 Objectives and approach

The engineering objective of this research is to explore and demonstrate highlyreliable, SMT-compatible interconnections between large low CTE packages and organic boards. The specific objectives are benchmarked with prior art in terms of package size, pitch and height, as shown in Table 1-1.

Achieving the above engineering objectives requires addressing fundamental scientific challenges arising from the large strains in the solder-based interconnections as a result of large CTE mismatch, large interposer size and small pitch. A systematic and fundamental approach was undertaken, involving modeling, design, fabrication, and validation by model-to-hardware correlation.

| Performance Metrics        | Prior Art                  | Objectives                                    |

|----------------------------|----------------------------|-----------------------------------------------|

| Package size for SMT       | 7mm × 7mm (WLP)            | $20 \text{ mm} \times 20 \text{mm}$ and above |

| Scalability to small pitch | 500-800 μm                 | 400 µm and below                              |

| Interconnection height     | 250 μm                     | 150 µm and below                              |

| Manufacturability          | PGA for large package size | SMT-compatible                                |

Table 1-1. Specific objectives of the study.

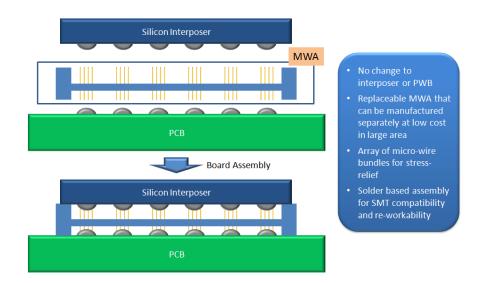

A novel interconnection technology using compliant copper microwire arrays (MWA) is proposed to address the reliability issue of lead-free solder joints, as shown in Figure 1.13. The MWA comprises of high aspect ratio copper pillars with inherent compliance that can accommodate the differential expansion between the package and the board, and therefore reduce the plastic-strain induced damage, both in the copper and solder joints during thermal cycling.

The proposed research, for the first time, explores micro-scale copper wires with high aspect ratio to address the reliability challenge of the board-level interconnections. The interconnection technology is SMT-compatible, scalable to small interconnection pitch, and can accommodate large low-CTE packages. It can be fabricated separately, which introduces minimum interruptions to the fabrication of package and the board. Finite element modeling with ANSYS will be used to optimize the geometrical and material parameters of the copper microwire arrays to achieve lowest plastic strains in the copper wires and solder. Parametric study will be carried out to understand the effect of each geometrical and material parameter on the reliability performance of the interconnection. Coffin-Manson relationship will then be used to calculate the projected fatigue life of the interconnection.

Based on the modeling result, a packaging-compatible and cost-efficient fabrication process will be designed. The silicon package, microwire array interconnection, and printed wiring board will then be fabricated to demonstrate the feasibility of the proposed technology. An SMT-compatible assembly approach will be presented for wider industry adoption. The reliability of the interconnection will be tested by accelerated thermal cycling, to prove the effectiveness of the MWA interconnection, and validate the models.

Figure 1.13 Schematic of copper microwire array interconnections.

## **CHAPTER 2**

# LITERATURE REVIEW

This chapter begins with an overview of state-of-the-art board-level interconnections, and then reviews two major innovations in interconnection materials and structures that are being pursued in order to address the reliability challenges with emerging large low-CTE packages on high-CTE boards. The first approach focuses on the ball grid array (BGA) interconnections, and is aimed at enhancing solder materials and solder-pad interfaces to increase their strength and fatigue resistance. The second approach deals with novel interconnection structures that provide stress-relief and, therefore, lower the effective strain-induced damage to improve their reliability. Copper is emerging as a strategic interconnection materials for providing stress-relief in board-level interconnections. The last section, therefore, reviews the recent findings in electrochemical processing - microstructure - mechanical property relations in fine-grained copper.

## 2.1 Current technologies in manufacturing for board-level interconnections

Three major categories of interconnection technologies are used for board-level assembly. The first one is a pin grid array (PGA) package, which utilizes high aspect ratio metal pins for reliable board level assembly, and has been widely used in manufacturing by IBM [11], to connect very large glass-ceramic LTCC ceramic modules of same CTE as silicon to the system board. As shown in Figure 2.1, the high aspect ratio pins accommodate the large CTE mismatch between the large low-CTE packages and the

boards. However, the interconnection pitch of PGAs has not scaled much below 1mm, which limits their application in today's high-end electronic systems.

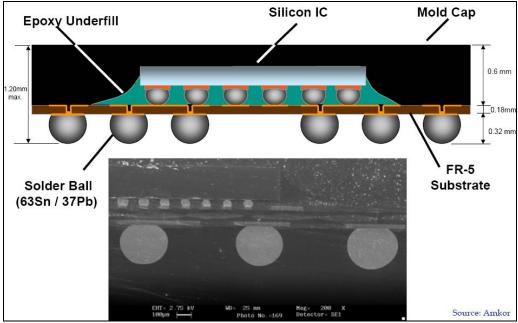

The second type is BGA interconnections, which uses an array of solder balls to connect the package onto the board, as shown in Figure 2.2. BGAs have been vastly successful, due to their scalability to low interconnections pitches, compatibility with surface mount technologies, outstanding electrical performance and low cost. However, as discussed in Chapter 1, the low fatigue resistance of solder alloys has become the bottleneck for the application of advanced low CTE packages. Major innovations in solder materials have been made to improve the interconnection reliability, and will be discussed in more detail in Section 1.2 of this chapter.

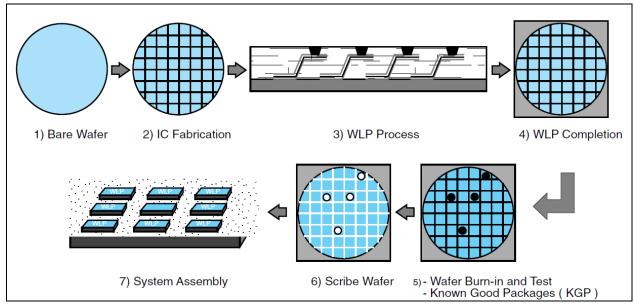

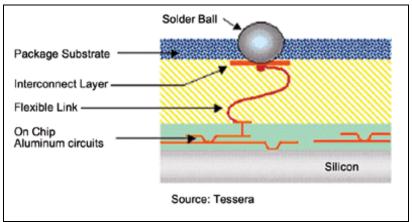

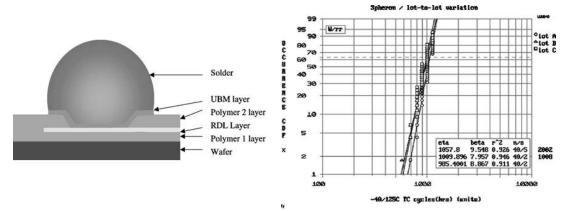

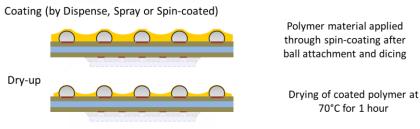

BGAs are formed on the backside of the package substrate with the chips mounted on the topside with flipchip or wirebonding. However, board-level interconnections are also formed directly at wafer level to achieve small system size and low cost. The dies are attached directly onto the board with flipchip technology. The wafer-level packaging process is demonstrated in Figure 2.3. Due to the CTE mismatch between the die and the board, only small die sizes (up to 5mm) have been demonstrated. R&D efforts targeting on improving the reliability of WLP are discussed in Section 1.3 of this chapter.

Figure 2.1 Pin grid array in high-performance computing applications for large low-CTE package to board interconnections [11].

Figure 2.2 Board level interconnections with ball grid array (Courtesy of Amkor).

Figure 2.3 Wafer-level packaging process (Courtesy of IFC, Georgia Tech).

# 2.2 Recent advances with solder interconnections

Solders are the dominant materials used for board-level interconnections. These interconnections consist of solders that comprise the bulk of the interconnections, and solder-pad interfaces that are predominantly intermetallics. Both have distinct microstructures and mechanical properties, which play critical roles in the reliability of

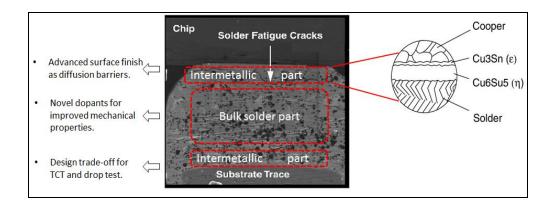

solder interconnections as illustrated in Figure 2.4. This section comprehensively reviews the formation of the metallurgical joints, the relationship between the solder microstructure and fatigue properties, the key advances in solders with composition and microstructural control to improve their mechanical properties, and pad surface finish with advanced diffusion barriers to form controlled intermetallics.

Figure 2.4 Material innovations in solder and base metals.

### 2.2.1 Metallurgical joint formation with solder alloys

Metallurgical joints are formed between solder alloy and the metallic surfaces on the package and the board. The copper pad on both the package and the board typically has a thin nickel and gold layer on top of it as surface finish, to provide a suitable surface for soldering. Initially, the solder balls are placed on the copper pad of the package, and then heated above solder liquidus to form a metallurgical bond via a process called reflow. During reflow process, the solder alloy undergoes melting, and the molten solder wets the copper pad. While wetting, the melt dissolves the protective gold layer and also a portion of the underlying nickel up to the solubility limits, thereby forming intermetallic compounds (IMCs) of Ni-Sn and Au-Sn. Nickel provides a flat and uniform surface and also acts as a diffusion barrier between solder and copper, to prevent excess growth and Cu-Sn intermetallic compounds (IMCs) [12]. Gold is used to protect the surface from oxidation, and also enhance the wettability. The package is then assembled onto the PWB

via a similar reflow process during which the bonding between solder and PWB pad is formed.

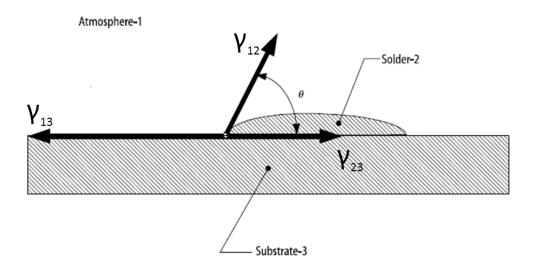

Wetting is crucial for joint formation. It involves melting, followed by spreading of the melt across the surface to be joined. During spreading, the solder will dissolve base metals from the wetted surfaces and form intermetallic compounds to achieve a proper metallurgical bond. Wetting characteristics are largely dependent on surface energy of the interfaces. The critical surfaces can be defined as: 1- soldering atmosphere; 2- the molten solder; and 3- the substrate. At equilibrium, the contact angle  $\theta$ , as shown in Figure 2.5, can be described by the following equation:

$$\gamma_{13} = \gamma_{12} \cos \theta + \gamma_{23} \tag{2.1}$$

where  $\gamma_{ij}$  represents the surface energy of annotated interfaces. A lower contact angle is favored for sufficient wetting and joint formation. Pb-free solders normally have deteriorated wetting behavior compared to traditional SnPb solders. Bukat et al. [13] compared the wetting behavior of various SnAgCu alloys and SnAg near-eutectics, presented in Table 2-1.

Figure 2.5 Equilibrium of surface tension at contact angle  $\theta$ .

| Alloy            | Melting<br>point (°C) | Surface<br>tension<br>(mN/m) | Wetting<br>force<br>(mN/m) | Wetting<br>time (s) | Wetting angle $(\theta^{\circ})$ |

|------------------|-----------------------|------------------------------|----------------------------|---------------------|----------------------------------|

| 96.5 Sn3.5Ag     | 221                   | 445                          | 50                         | 1.5                 | 70                               |

| 96.5Sn3.0Ag0.5Cu | 217-219               | 450                          | 110                        | 1.3                 | 55                               |

| 95.7Sn3.6Ag0.7Cu | 217-218               | 463                          | 110                        | 1.2                 | 55                               |

| 95.5Sn4.0Ag0.5Cu | 217-219               | 460                          | 120                        | 1.2                 | 55                               |

Table 2-1 Wetting data for SnAgCu alloys at 250°C on Cu substrates.

### 2.2.2 Evolution of solder microstructure and thermo-mechanical fatigue failures

Most of the Pb-free alloys studied are Sn-rich, and alloyed with elements such as Ag, Cu, Zn, Bi, In and Sb. Due to the high Sn content and generally low solid solubilities of most elements in solid Sn, the dominant phase in most Sn-base solder joints is body centered tetragonal Sn, or  $\beta$ -Sn [14]. The Sn phase may be present in several morphologies simultaneously, ranging from  $\beta$ -Sn dendrites to eutectic microstructures.

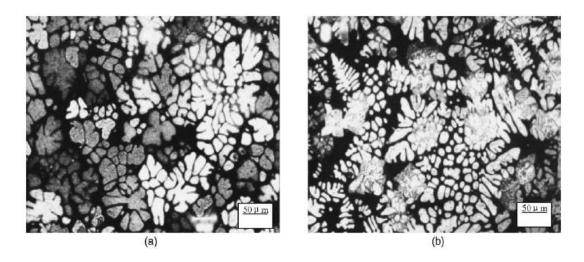

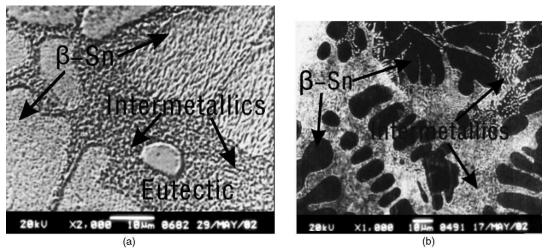

Yu et al. [15] showed that the microstructures of Sn–2.5Ag–0.7Cu, Sn–3.5Ag– 0.7Cu alloys have coarse  $\beta$ -Sn grains. As seen in Figure 2.6 (a) and (b), the light regions are the  $\beta$ -Sn grains with an average size of 20–30 $\mu$ m in Sn–2.5Ag–0.7Cu while they are slightly smaller (15–25 $\mu$ m) in Sn–3.5Ag–0.7Cu alloy. The dark eutectic regions consist of Ag<sub>3</sub>Sn, Cu<sub>6</sub>Sn<sub>5</sub> and Sn matrix with the width of about 10 $\mu$ m in both the alloys. As shown in Figure 2.7 (a), the size of Ag<sub>3</sub>Sn and Cu6Sn<sub>5</sub> intermetallic particles in Sn-2.5%Ag-0.7%Cu are about 1 $\mu$ m. With the increase in Ag content, the intermetallics become coarser, about 2–4 $\mu$ m in Sn-3.5%Ag-0.7%Cu as shown in Figure 2.7 (b).

Figure 2.6 Optical microscopic images of (a) Sn-2.5% Ag-0.7% Cu, and (b) Sn-3.5% Ag-0.7% Cu (Courtesy of D.Q. Yu).

Figure 2.7 SEM images for (a) Sn-2.5%Ag-0.7%Cu, and (b) Sn-3.5%Ag-0.7%Cu (Courtesy of D.Q. Yu).

The as-reflowed microstructure of Pb-free solder alloy is not stable under normal operational conditions. Significant coarsening takes place over time after assembly. Within the solder joints, the interface spacing between the constituents of microstructure increases and the intermetallic particles, or secondary phases within the Sn matrix increase in size. The major driving forces for the evolution of microstructures are high operating temperature and cyclic shear stress.

The first driving force for microstructure coarsening is the high homologous temperature. The homologous temperature  $T_h$ , is defined as the ratio of the operating temperature, T, to the melting temperature,  $T_m$ ,

$$T_h = \frac{T}{T_m} \tag{2.2}$$

Solder alloys are chosen to have low melting temperatures such that the joining process is compatible with other materials and processes used for semiconductor fabrication. Therefore, they are usually subjected to high homologous temperatures, exceeding 0.3-0.5 in operation. High temperature promotes diffusion; therefore diffusion-driven processes such as grain boundary diffusion and interface-boundary diffusion become more active. These processes drive thermal coarsening of solders, resulting in the growth of secondary-phase particles in the primary matrix, and morphological changes across the bulk microstructure.

The second driving force for coarsening is the mechanical loading. Cyclic mechanical loading induces strain energy, which, in turn, promotes boundary migration. The movement of boundaries increases the overall size of the grain, which is favored by strain energy reduction. Dutta et al. [16] investigated the combined effects of temperature-and strain-induced coarsening in 93.6Sn4.7Ag1.7Cu. In this study, an increase in intermetallic particle size and spacing was observed after the solder joints were cycled from -25°C to 125°C. As can be seen from Figure 2.8 (a)-(c), the average particle size of Ag<sub>3</sub>Sn intermetallics increased from about 0.3µm to about 2µm after 1200 cycles, and the spherical particles grew into platelets.

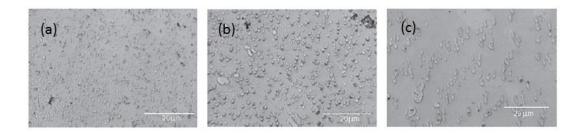

Figure 2.8 Microstructure of Ag<sub>3</sub>Sn particles in SnAgCu (a) as-reflowed condition, (b) after 200 thermal cycles, and (c) after 1200 thermal cycles [16].

The change in microstructure has a significant influence on the mechanical properties of the joints. The yield strength becomes lower as coarsening takes place, as predicted by Hall-Petch equation:

$$\sigma_{y} = \sigma_{0} + kD^{-1/2}$$

(2.3)

where <sup>o</sup>y is the yield strength, k is a constant and D is the mean grain diameter. As the applied stress goes beyond the yield stress, dislocation motion is onset, and plastic deformation occurs. More importantly, the grain size also affects the fatigue behavior of solder alloys under cyclic loading. Hall et al. showed that fine-grained solder joints exhibit fatigue lives larger than coarse-grained solder joints in accelerated tests [17]. Small grains tend to distribute the load evenly over the specimen and enhance both the strength and ductility. Fine intermetallic precipitates hinder dislocation motion, which strengthens the material as well as improves creep resistance.

#### 2.2.3 Advances in solders with microstructure and composition control

Recently, development of new solder materials has been reported by alloying of grain-refining elements into Sn-Ag and Sn-Cu-Ag systems to achieve better mechanical properties. Wu et al. reported that the doping of rare earth elements refined the size of grains and intermetallic particles, and improved the tensile strength and creep resistance of lead-free solders [18]. Aggarwal et al. showed improved solder properties shear strength of solders by adding organic derived nano reinforcements with appropriate

functional groups, which promoted bonding with the metallic matrix and helped pin the grain boundaries and constrain the grain boundary sliding [19].

The fatigue resistance of bulk solders is mathematically described using Coffin-Manson relationship as discussed in Chapter 1. Improved fatigue resistance is needed to meet the reliability targets with the high plastic strains seen with large low CTE packages. Lead-free solders have better fatigue resistance compared to lead-tin solders at lower strain ranges, and higher strength. Lead-free solders are also known to have a higher creep resistance compared to PbSn solders. The higher strength and creep resistance, however, comes at the expense of ductility. At higher strains, SAC cannot readily accommodate deformations and become more susceptible to crack propagation than ductile PbSn.

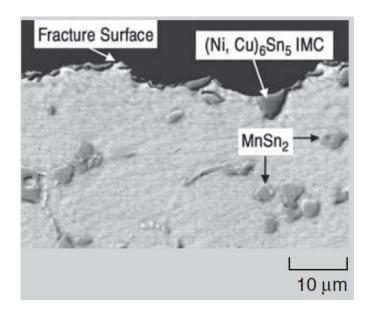

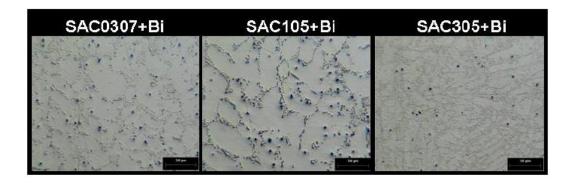

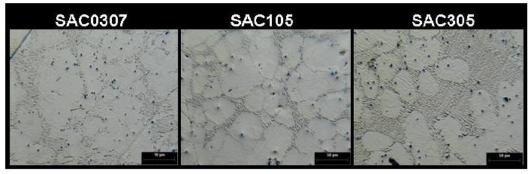

Strengthening and toughening agents are investigated to further increase the fatigue, creep and fracture resistance of Pb-free solders. Precipitation of particles along interfaces can significantly reduce grain boundary sliding. Ag<sub>3</sub>Sn platelets in tin are known to increase creep resistance by the same mechanism. However, as discussed previously, Ag<sub>3</sub>Sn platelets coarsen significantly during thermal cycles. The large Ag<sub>3</sub>Sn platelets, when formed nearby the solder-substrate interface, facilitate the propagation of fatigue cracks and deteriorate the reliability of solder interconnections. Liu et al. studied the effect of manganese doping in SAC solder [20]. They reported manganese-containing particles near the IMC layer, which enhanced the bonding strength between the IMC and the substrate, and therefore helped improve the fracture resistance along the interface, as shown in Figure 2.9. Pandher et al. demonstrated the benefits of bismuth doping in SAC solders [21]. As shown in Figure 2.10, Bi doping refines the grain structures in SAC alloys and is expected to improve the thermomechanical reliability of the SAC solder.

Reliable interconnections demand both thermal cycling test (TCT) and drop-test performance. However, TCT and drop-test have conflicting requirements for solders.

Terashima et al. showed that the SnAgCu solders with higher silver content (3%-4%) had better TCT performance [22]. They had finer Sn grains, due to the dispersion of Ag<sub>3</sub>Sn intermetallic particles, which hinders the microstructure coarsening and improves the strength of the solder. On the other hand, Lee et al. reported better drop-test performance with low silver content [23]. The solders with lower silver content (1%) had less Ag<sub>3</sub>Sn particles and thus softer bulk solder, which absorbs shock better and conveys less shockinduced strain at the interfacial stress concentration locations. Therefore it is challenging to select a solder which fulfills both the requirement for TCT and for drop-test.

Figure 2.9 Cross section of a SAC105+0.25 Mn solder joint [20].

Figure 2.10 Effect of Bi addition on the microsturcture of SAC alloys [21].

## 2.2.4 Advances in pad surface finish

Surface finish plays a crucial role in improving solderability and reliability of the joints. Some of the traditional coatings used on copper pads include hot air solder leveling (HASL) and organic solderability preservative (OSP). HASL has low cost, but has poor thickness control, and involves lead which is not preferred because of environmental considerations. OSP has been demonstrated as an alternative with good reliability. However, it does not withstand multiple reflows. Plated metal coatings have become more popular because of their good reliability, and compatibility with the requirement for small lines and spaces.

Two of the most popular surface finish technologies with plated metal used for packaging are ENIG (Electroless Nickel Immersion Gold) and ENEPIG (Electroless Nickel Electroless Palladium Immersion Gold).

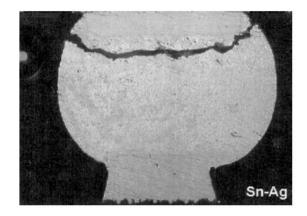

In the ENIG system, the gold layer is very thin (below  $0.2\mu m$ ), and dissolves readily in solder during the assembly process. Therefore the nickel dominates the interface reactions. As shown in Figure 2.4, a layer of IMC is formed during reflow. The IMC layer primarily consists of Cu-Sn intermetallic species (Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn), and it also contains Ni-Sn and Au-Sn due to the surface finish applied on top of the copper pad. The IMC layer serves as the bonding interface material, however, thick IMC layers have been found to be deleterious to the reliability of the interconnections. The thickness of the IMC layers depends on the reflow time and temperature [24], and longer reflow time and higher reflow temperature leads to thicker IMC layers. Tu et al. showed that the lifetime of solder joints degrades rapidly with the increase of IMC thickness, and the fatigue failure occurs mainly at the IMC/solder interfaces [25]. As shown in Figure 2.11, the crack initiated at the solder-IMC interface and propagated through the solder joints [26]. Despite the widespread implementation of ENIG, there are evidences that the ENIG finish may cause catastrophic, brittle, interfacial joint fractures [27][28]. The fracture mode is characterized as brittle nickel-gold interfacial fracture. One of the causes for the brittle interface is the high phosphorous (P) content (10-15%) of the electroless Ni, which leads to interfacial P segregation and promotes a brittle fracture [29].

Figure 2.11 Crack at IMC/solder interface with ENIG surface finish.

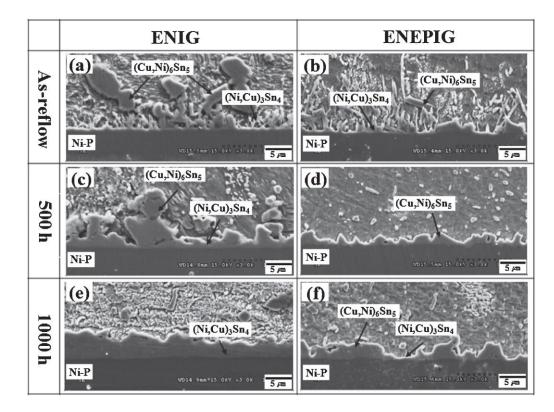

The ENEPIG system, on the other hand, adds a palladium (Pd) layer in between the Ni and the Au. The Pd layer controls the diffusion of Ni into the solder, and restricts the growth of IMC thickness. Ha et al. reported that the IMC layer formed on ENEPIG pads grows slower than that formed on ENIG pads in thermal aging, and the joints with ENEPIG surface finish had better reliability in both thermal cycling and drop test, as shown in Figure 2.12 [30].

Figure 2.12 Cross section of solder joints after reflow and thermal aging: ENIG (a), (c), (e) and ENEPIG (b), (d), (f) [30].

## 2.3 Compliant interconnections with improved fatigue resistance

In spite of the various innovations in the solder materials, only incremental improvements in solder joint fatigue resistance have been achieved. An alternative strategy that further alleviates the stresses and strains in the solders is hence widely investigated by industry and academia. These approaches have been primarily developed for large ceramic BGAs or wafer-level packages. The stress-relief (or strain-relief) is

achieved by providing compliant or mechanically flexible structures that are easily deformable, and therefore induce minimal plastic strains in the solder or copper interconnections. These are broadly classified as metal-based compliant structures or polymer-based compliant structures, or a combination of both.

## 2.3.1 Compliant metal structures for reliable interconnections

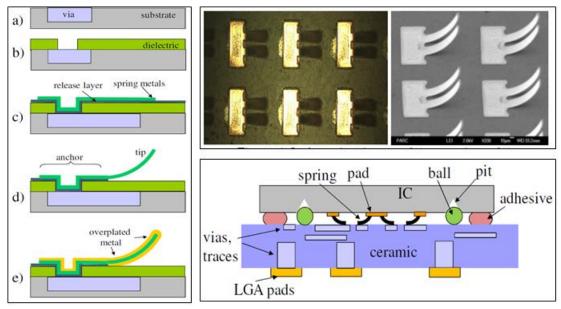

### 2.3.1.1 Copper posts with plated solder cap

Copper post with solder cap is one of the popular metal-based interconnection techniques which utilize both the fatigue resistance of copper, and the assembly convenience of solders. The copper posts can be achieved by electroplating through photoresist patterns, and are compatible with fine-pitch features, therefore they are widely adopted for first-level interconnections and wafer-level interconnections.

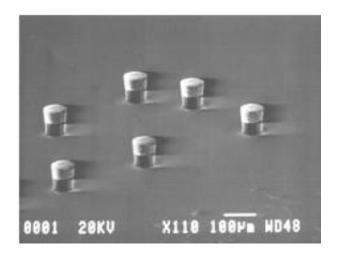

T. Wang et al. reported first-level interconnections from a 10 mm  $\times$  10 mm IC to organic substrate with copper base and plated solder bump [31]. The interconnections are at 200µm pitch with an overall height of about 105 µm, as shown in Figure 2.13. The assembly was underfilled for improved reliability. The interconnections survived 1000 cycles in accelerated thermal cycling test from -40°C to 125°C.

Figure 2.13 Copper base with solder bump for first level interconnection [31].

V. S. Rao et al. explored the copper-solder interconnection for even smaller pitch [32]. In their study, a 10 mm  $\times$  10 mm silicon chip was connected to organic substrate with copper pillars with aspect ratio of 3, without using underfills. The pillar height was 68 µm and the pitch was 100 µm. Initial failure was identified between 500-600 cycles in accelerated test.

Similar concept was also adopted by Fujitsu in wafer level chip scale packaging (WLCSP) [33]. The copper posts were embedded in an encapsulation, with solder cap plated on top, as shown in Figure 2.14. The interconnections are at the pitch of 700  $\mu$ m, and are shown to survive 500 cycles before the first fatigue failure.

From the above three examples, it can be observed that the copper pillar or copper bump based interconnections are still relatively stiff, and are subject to early failures without underfill.

Figure 2.14 Super CSP by Fujitsu [33].

#### 2.3.1.2 Compliant metal springs or leads

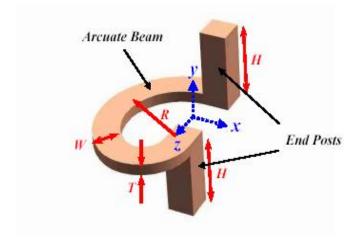

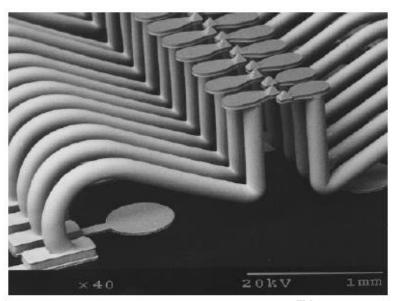

To achieve higher compliance and reliability, metal springs or leads with various geometries have been explored. George Lo et al. reported 'G-Helix' structure for silicon die to organic substrate interconnections [34]. As shown in Figure 2.15, a copper arch structure was used to provide helical compliance.

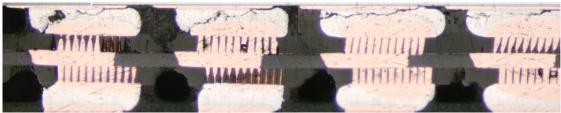

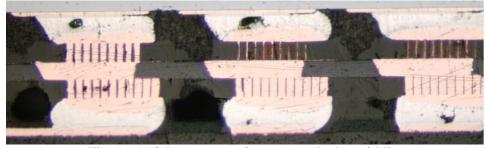

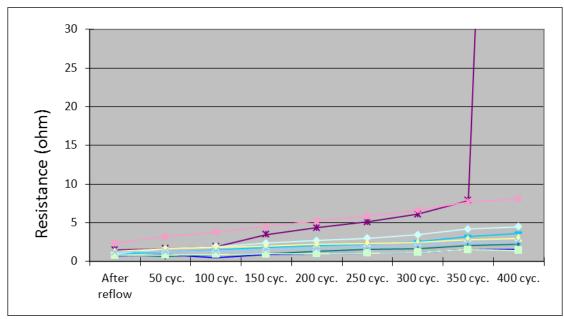

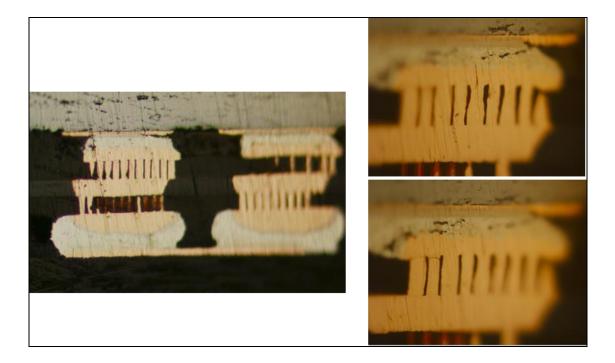

Figure 2.15 G-Helix Interconnections [34].