# DESIGN AND CHARACTERIZATION OF BICMOS MIXED-SIGNAL CIRCUITS AND DEVICES FOR EXTREME ENVIRONMENT APPLICATIONS

A Dissertation Presented to The Academic Faculty

By

Adilson Silva Cardoso

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology December 2014

Copyright © 2014 by Adilson Silva Cardoso

# DESIGN AND CHARACTERIZATION OF BICMOS MIXED-SIGNAL CIRCUITS AND DEVICES FOR EXTREME ENVIRONMENT APPLICATIONS

Approved by:

Dr. John D. Cressler, Advisor Professor, School of ECE Georgia Institute of Technology

Dr. Jeffrey A. Davis Associate Professor, School of ECE Georgia Institute of Technology

Dr. Edward Gebara Adjunct Professor, School of ECE Georgia Institute of Technology Dr. Raheem A. Beyah Associate Professor, School of ECE Georgia Institute of Technology

Dr. Pauline F. Paki Physicist, Program Manager Defense Threat Reduction Agency

Dr. Darnell J. Moore Senior Member of Technical Staff, Perception and Analytics Laboratory Texas Instruments, Inc.

Date Approved: November 13th, 2014

To my Lord and Savior, Jesus the Christ

Whose unconditional love,

and blessings has enabled me to complete this work. "Proverbs 3:5-6"

To my mother, Firmina, an epitome of selfless love. Eu te amo minha mãe.

To my "sweet" son, Samuel, a God answered prayer and,

To my wife, my "beauty", Dilvia.

## ACKNOWLEDGMENTS

All praise and honor to my Lord and Savior, Jesus Christ, whose unconditional love, and grace has enabled me to complete this work. I am grateful to my wife, Dilvia — a God given blessing; I am truly thankful for her patience, love, and more than 16 years of continual support on this journey. I am forever indebted to my mother, Firmina; for her uncompromising love and for all the sacrifices she made so that I could continue to pursue my education. I am thankful to my sisters, Katia and Dina, for their unceasing emotional and financial support, and most importantly, for their timely encouragement whenever I needed it the most. I would like to thank my late uncle, Ilidio "Eric" Silva who always encouraged me to continue to learn and to pursue an education. Many thanks to Mr. John Santos and the late Mr. John J. DePina Jr., for generously sharing their time when I needed the most, and for instilling godly values in me as a young man growing up in Brockton, Massachusetts.

I want to sincerely thank my advisor, Dr. John D. Cressler, for his invaluable guidance, encouragement, and support. Dr. Cressler is indeed the best advisor that God could have blessed me with. His contagious passion and enthusiasm for teaching and research has been a source of inspiration during my graduate studies. He allowed me to grow as a researcher and a leader. I also would like to thank my thesis committee members, Dr. Jeffrey Alan Davis, Dr. Edward Gebara, Dr. Raheem Beyah, Dr. Pauline F. Paki, and Dr. Darnell J. Moore for their valuable time, insightful feedback, and for agreeing to serve on my dissertation committee.

I am grateful to all of the members of the SiGe Devices and Circuit research team for their technical support and collaboration over the years. I must specially thank, Partha Chakraborty, who selflessly helped me with different aspects of my research work. Partha's friendship and collaboration played a major role in my success, and for that I will be always thankful. I would like to thank my current team members: Anup Omprakash, Nedeljko Karaulac, Adrian Ildefonso, Nelson Lourenco, Tikurete Bantu, Michael Oakley, Peter Song, Rob Schmid, Chris Coen, Zach Fleetwood, Brian Weir, Seungwoo Jung, Saeed Zeinolabedinzadeh, Uppili Raghunathan, and Ickhyun Song. Also, many thanks to my former team members for their guidance and assistance when I first joined the group: Dr. Laleh Najafizadeh, Dr. Kurt Moen, Dr. Prabir Saha, Dr. Tushar Thrivikraman, Dr. Stephen Horst, Dr. Ryan Diestelhorst, Dr. Anuj Madan, Dr. Troy England, Dr. Duane Howard, Ted Wilcox, Dr. John Poh, Dr. Stanley D. Philipps, Dr. Wei-Min Kuo, and Dr. Rao Rapeta. Aso, a special thanks to David Fleischhauer, Michael Kroger, Adrian Ildefonso, and Anup Omprakash for proofreading my entire dissertation for errors.

My deep appreciation to my brothers in Christ, Adam Tull, Ed Mitchell, Michael Maître, Amilcar Fontes, Dr. Lonnie T. Parker IV, Dr. J. Chris Ford, Stephen J. Mobley, Ivan Walker, Marcus A. Bellamy, Chu Meh Chu, Brandon L. Johnson, Billy M. Kihei, Dr. Douglas A. Brooks, D'Andre Bell, Dr. Scott Koziol, Dr. Jeremy Tolbert, Benedict Vani, Lucindo Fidalgo, Lorenzo Amaya, Larry Turner, Durrell Wheaton, and my Pastor Todd Briggs, for their spiritual wisdom, prayers, and accountability that have allowed me to continue to grow in reverence knowledge of our Lord Jesus, the Christ — Proverbs 27:17 "As iron sharpens iron, so a friend sharpens a friend."

I would like to acknowledge Texas Instruments Inc., the Defense Threat Reduction Agency, NASA Electronic Parts and Packaging, and the U.S. Department of Defense for their funding and support of this research work. Additionally, my two most avid champions and advocates, my Texas Instruments mentors, Dr. Darnell J. Moore and Mr. Chris Maxwell. I am truly appreciative of their timely mentoring and guidance.

# TABLE OF CONTENTS

| ACKN   | OWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | iv         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| LIST ( | OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix         |

| LIST ( | <b>DF FIGURES</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X          |

| SUMM   | (ARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>vii</b> |

| СНАР   | <b>FER 1 INTRODUCTION</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1          |

| 1.1    | Research Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2          |

| 1.2    | 2 Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3          |

| CHAP   | <b>FER 2 BACKGROUND AND LITERATURE REVIEW</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6          |

| 2.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6          |

| 2.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8          |

| 2.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10         |

| 2.4    | - <b>3</b> - <b>8</b> - <b>1</b> | 11         |

| 2.4    | 5 On the Operation of FETs for RF Switch Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13         |

| 2.6    | 6 RF Switches Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18         |

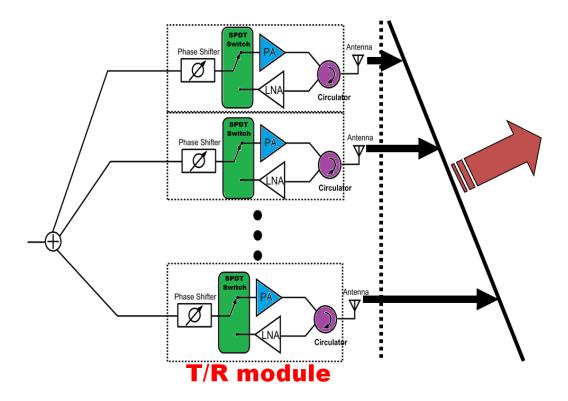

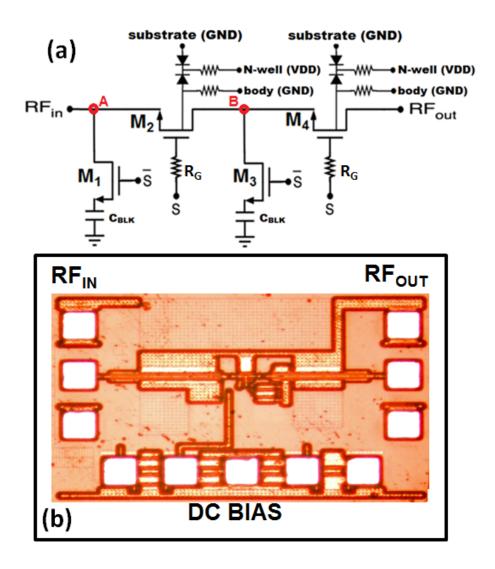

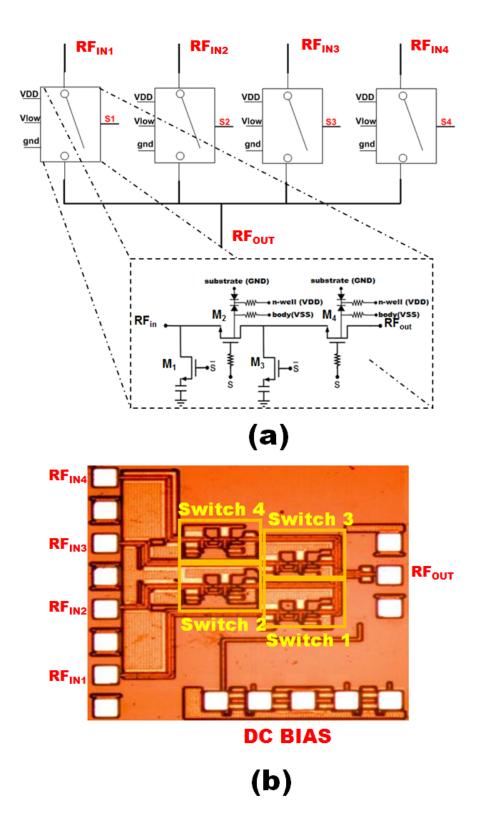

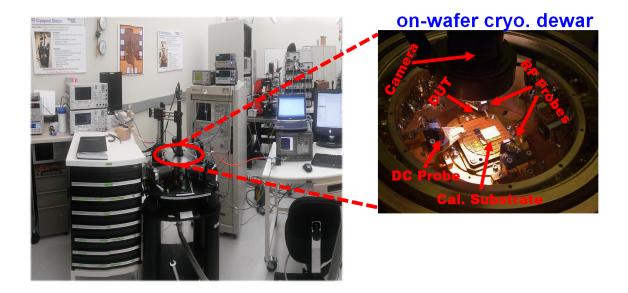

| CHAP'  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|        | SPST AND SP4T RF SWITCHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21         |

| 3.1    | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21         |

| 3.2    | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23         |

| 3.3    | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25         |