# Edinburgh Research Explorer

# **Cooperative Caching for GPUs**

Citation for published version:

Dublish, S, Nagarajan, V & Topham, N 2016, 'Cooperative Caching for GPUs' ACM Transactions on Architecture and Code Optimization, vol. 13, no. 4, 39, pp. 1-25. DOI: 10.1145/3001589

# **Digital Object Identifier (DOI):**

10.1145/3001589

## Link:

Link to publication record in Edinburgh Research Explorer

#### **Document Version:**

Peer reviewed version

# **Published In:**

ACM Transactions on Architecture and Code Optimization

## **General rights**

Copyright for the publications made accessible via the Edinburgh Research Explorer is retained by the author(s) and / or other copyright owners and it is a condition of accessing these publications that users recognise and abide by the legal requirements associated with these rights.

Take down policy

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh Has made every reasonable effort to ensure that Edinburgh Research Explorer

The University of Edinburgh Research Research Explorer

The University of Edinburgh Research Research Research Research Research Research content complies with UK legislation. If you believe that the public display of this file breaches copyright please contact openaccess@ed.ac.uk providing details, and we will remove access to the work immediately and investigate your claim.

# **Cooperative Caching for GPUs**

Saumay Dublish, University of Edinburgh Vijay Nagarajan, University of Edinburgh Nigel Topham, University of Edinburgh

The rise of general-purpose computing on GPUs has influenced architectural innovation on GPUs. The introduction of an on-chip cache hierarchy is one such innovation. High L1 miss rates on GPUs, however, indicate inefficient cache usage due to myriad factors such as cache thrashing and extensive multithreading. Such high L1 miss rates in turn place high demands on the shared L2 bandwidth. Extensive congestion in the L2 access path, therefore, results in high memory access latencies. In memory-intensive applications, these latencies get exposed due to a lack of active compute threads to mask such high latencies.

In this paper, we aim to reduce the pressure on the shared L2 bandwidth, thereby reduce the memory access latencies that lie in the critical path. We identify significant replication of data among private L1 caches, presenting an opportunity to reuse data among the L1s. We further show how this reuse can be exploited via an L1 Cooperative Caching Network (CCN), thereby reducing the bandwidth demand on the L2. In the proposed architecture, we connect the L1 caches with a lightweight ring network to facilitate inter-core communication of shared data. We show that this technique reduces traffic to the L2 cache by an average of 29%, freeing up the bandwidth for other accesses. We also show that CCN reduces the average memory latency by 24%, thereby reducing core stall cycles by 26% on average. This translates into an overall performance improvement of 14.7% on average (and up to 49%) for applications that exhibit reuse across L1 caches. In doing so, CCN incurs a nominal area and energy overhead of 1.3% and 2.5% respectively. Notably, the performance improvement with our proposed CCN compares favourably to the performance improvement achieved by simply doubling the number of L2 banks by up to 34%.

CCS Concepts: •Computer Systems Organization → Single Instruction, Multiple Data;

Additional Key Words and Phrases: GPGPU, Bandwidth Bottlenecks, Inter-Core Reuse

#### **ACM Reference Format:**

Saumay Dublish, Vijay Nagarajan and Nigel Topham, 2016. Cooperative Caching for GPUs. ACM Trans. Architec. Code Optim. 13, 4, Article 39 (December 2016), 25 pages.

DOI: 10.1145/3001589

#### 1. INTRODUCTION

Current GPUs are no longer perceived as accelerators solely for graphic workloads, and now cater to a much broader spectrum of applications. In a short time, GPUs have proven to be of substantive significance in the world of general-purpose computing. The massive compute power of GPUs and recent innovations in their architecture [Nvidia 2009][Nvidia 2012] have helped unleash the latent potential of several non-graphical applications, adding momentum to the rise of general-purpose computing on GPUs (GPGPU).

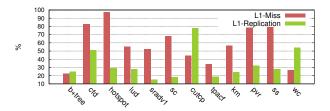

Motivated by the pervasive impact of GPUs in the field of general-purpose computing, manufacturers have introduced configurable on-chip cache hierarchies to their recent architectures to cater for the locality needs of non-streaming applications. Despite performance improvement for certain applications, however, the utilization of these caches is far from perfect; this is evident from the high cache miss rates seen on many GPUs. As shown in Figure 1(a), on NVIDIA's Fermi GPU, general-purpose applications across a variety of benchmark suites show high L1 miss rates, indicating that the current cache management techniques are unable to utilize these caches effectively. As a consequence of high L1 miss rates, pressure on the L2 bandwidth increases thereby increasing the memory access latencies due to congestion in the L2 access path. In our experiments (discussed later in Section 5), we observe that due to congestion in the L1-L2 interconnect and L2 access queues, L2 accesses take up to

39:2 S. Dublish et al.

Fig. 1: (a) L1-Miss: L1 cache miss rates (b) L1-Replication: Percentage of L1 misses cached in remote L1 caches.

2-3× more cycles compared to the normal access latency of L2. In memory intensive applications, due to lack of active compute threads to overlap such high memory access latencies, *increased latencies to the lower level get exposed* and appear in the critical path [Dublish et al. 2016], reducing system performance.

**Goal**: In this paper, our goal is to reduce the memory access latencies that cannot be hidden by multithreading in memory-intensive applications. Since one of the major reasons for such high latencies is the congestion in the L2 access path (due to the high number of requests sent to the lower level), we aim to reduce this congestion.

**Observation**: In streaming applications, cores work on independent data with little or no overlap in the working dataset. However, in general-purpose applications we observe a considerable potential for data reuse across different cores. Figure 1(b) shows that a significant percentage of miss requests generated by L1s is for data already present on a *non-local (or remote) L1 cache*. If we can exploit this reuse within the L1s, duplicate requests to the shared L2 can be potentially eliminated. This would result in reduced congestion and faster lower level access for the remaining requests.

**Proposal**: In this paper, we propose a Cooperative Caching Network (CCN) for L1 caches in GPUs to improve the efficiency of the L1 cache hierarchy in filtering the requests to the L2 cache. In our proposed scheme, we connect the private L1 caches in a lightweight ring network to facilitate communication of reusable data among the L1 caches. In doing so, we reduce the average memory access latency due to the following two reasons. A fraction of L1 load misses, with reusable data cached on remote L1s, can now completely bypass the high latency access path to L2. They are instead serviced by the CCN with significantly lower latencies (42 cycles on average based on our experiments) as compared to the L2 roundtrip access latencies, or simply L2 access latencies (which is  $\sim 300$  cycles due to congestion). Cooperatively sharing reusable data within the L1 caches via the CCN reduces the traffic to L2 cache. This relieves the pressure on the interconnect as well as on the L2 access queues thereby reducing the L2 access latencies (by 78 cycles on average). Thus, CCN provides a faster access to L2 for miss requests that do not find a sharer in the CCN.

In effect, our proposed architecture services a portion of L1 misses collaboratively within the L1 caches with much lower latencies than the L2 access latency. This leads to less congestion in the L2 access path, thereby accelerating memory response for requests that do not find a reusable copy in remote L1 caches. However, in the absence of reuse (such as in streaming applications), unsuccessful probes in the CCN adds an additional overhead to the L1 load misses. In such cases, due to no reduction in congestion, the CCN overhead does not get compensated and results in an overall performance penalty. Therefore, in our final scheme we propose CCN-RT, a Cooperative Caching Network with Request Throttling. It dynamically adapts to the coarse grained reuse patterns shown across an entire application, thereby bypassing

the CCN when there is little or no reuse.

In summary, we make the following contributions:

- We provide fresh insight into the inter-core reuse patterns within GPUs by profiling the communication characteristics over a diverse range of GPGPU applications.

- We propose the CCN, a cooperative caching architecture for GPUs that is cognizant of the inter-core reuse.

- By servicing reusable requests via the CCN, we reduce the overall bandwidth demand on L2 cache, boosting performance for memory-intensive applications that show high levels of sharing across L1s.

- With our final proposal CCN-RT, we show an average performance gain of 14.7% for applications that exhibit reuse, while being benign to applications with no reuse.

- We also reduce the average memory latency by 24%, L1 to L2 traffic by 29% and core stall cycles by 26%. Our proposal incurs nominal area and energy overheads of 1.3% and 2.5% respectively.

The remainder of the paper is organized as follows. Section 2 provides an overview of the baseline architecture for our study and characterizes the workloads. Section 3 investigates the reuse patterns for general purpose applications and assesses the efficacy of cooperative caching in GPUs. Section 4 presents CCN, a Cooperative Caching Network for L1 caches in GPUs. Section 5 evaluates the architecture and proposed optimizations to our baseline proposal. Section 6 compares CCN with alternate solutions. Section 7 discusses the related work and positions our findings in the current state-of-art and Section 8 concludes the paper by summarizing the findings and contributions of this work.

#### 2. BACKGROUND

#### 2.1. CUDA Programming Model

A typical CUDA program consists of data-parallel structures called *kernels*, that are executed on the GPU. Large number of threads of a kernel are organized into structured blocks of computation known as *thread blocks*. Each thread block consists of several smaller group of threads called *warps*— the smallest granularity of scheduling threads in a GPU core.

#### 2.2. Baseline Architecture

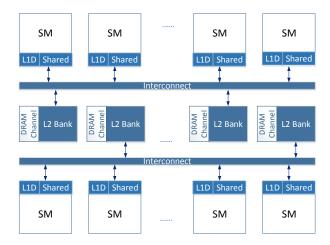

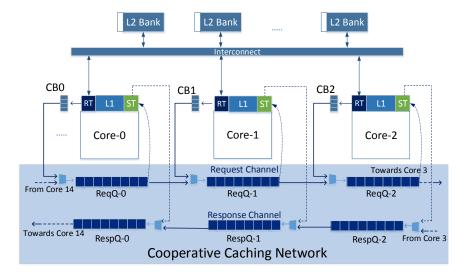

As shown in Figure 2, a typical GPU consists of several execution units organized in a set of highly multithreaded and pipelined cores that are referred to as Streaming Multiprocessors (SM¹). In this study, we consider a baseline similar to NVIDIA's Fermi architecture. Our baseline GPU consists of 15 SMs, each with a 32 lane SIMD unit. Each core consists of a private L1 data cache, shared memory (scratchpad) and read-only texture and constant caches. Private caches of a core are backed by a shared L2 cache that has an access latency of around 120 cycles for non-texture accesses. The L1 data caches are non-coherent and employ write-through, no-write-allocate policy. The baseline parameters are summarized later in Table II.

## 2.3. Benchmarks

For the purpose of this study, we use CUDA applications from three major general-purpose benchmark suites, viz., Rodinia (v3.0) [Che et al. 2009], MapReduce [He et al. 2008] and Parboil [Stratton et al. 2012]. We categorize the benchmarks according to

<sup>&</sup>lt;sup>1</sup>In this paper, we use the terms Core and SM interchangeably.

39:4 S. Dublish et al.

Fig. 2: Baseline GPU architecture.

their sensitivity to the memory hierarchy. Table I lists the benchmarks sorted by the speedup (PerfX) shown on a perfect memory system that has zero access latency to lower level memories and infinite bandwidth between memory hierarchies on a Fermilike GPU.

A program is said to be memory-intensive if it constitutes several threads comprising of long latency memory operations. The performance of memory-intensive applications is usually bounded by the bandwidth to lower level memories. This is because a large number of memory requests are kept waiting in each memory partition due to limited bandwidth, thereby delaying memory responses and causing the cores to potentially stall. Therefore, the magnitude of speedup on a perfect memory system essentially indicates the gravity of bandwidth problem in the benchmarks.

## 3. NEED FOR COOPERATION

Graphics and general-purpose workloads exhibit different memory access patterns. In graphics applications, kernels operate on independent data of streaming nature and therefore, different thread blocks are executed in considerable isolation. On the other hand, general-purpose applications show varying amounts of reuse within the thread blocks and also at the boundaries with neighbouring thread blocks. For instance, in scientific application such as computation of Coulombic Potential (cutcp), atoms are organized in a 3D lattice. A sub-group of atoms constitute a thread block and the entire lattice is divided into multiple thread blocks. In order to compute the potential difference on the atoms at the edges and corners of a sub-lattice (or thread block), coulombic potential contributed by atoms from surrounding sub-lattices needs to be read and hence requires sharing and reuse of data among neighbouring thread blocks. When such thread blocks are scheduled on different cores on a GPU, it results in intercore reuse. In current GPUs, reuse across thread blocks on different cores can only be exploited by localizing the data on the L2 cache and not any closer. But in doing so, cores have to incur the congestion delays in L1-L2 interconnect, as well as the delays in the L2 access queues. Thus, for those applications that are bounded by the bandwidth to the lower level, it degrades the overall performance by clogging the access path to the L2.

Table I: Benchmark characterization: (a) PerfX - speedup with perfect memory (b)  $\mu$ RC - percentage of total L1 load misses that have reusable data on a remote L1.

| S.No. | Suite     | Benchmark                | ABV.      | Dataset                                   | PerfX | $\mu$ RC |

|-------|-----------|--------------------------|-----------|-------------------------------------------|-------|----------|

| 1     | MapReduce | Matrix Multiplication    | mm        | 768 	imes 768 data points                 | 9.86  | 4%       |

| 2     | MapReduce | Similarity Score         | ss        | 1024 	imes 256 data points                | 6.18  | 28%      |

| 3     | Rodinia   | Computational Fluid      | cfd       | 200000 elements                           | 6.17  | 51%      |

| 4     | MapReduce | Page View Rank           | pvr       | 21 MB                                     | 5.93  | 32%      |

| 5     | Rodinia   | Stream Cluster           | sc        | 16384 points; 256 dimension               | 5.49  | 18%      |

| 6     | Rodinia   | Breadth-First Search     | bfs'      | 1000000 nodes                             | 5.18  | 3%       |

| 7     | Rodinia   | Wavelet Transform        | dwt2d     | $1024\times1024$                          | 4.96  | 7%       |

| 8     | Parboil   | Lattice-Boltzmann Method | lbm       | $120 \times 120 \times 150$ data points   | 4.49  | 0%       |

| 9     | MapReduce | K-Means                  | km        | 10000 	imes 3 data points; 24 clusters    | 3.85  | 24%      |

| 10    | Rodinia   | Hybrid Sort              | sort      | 4194304 floating points                   | 3.68  | 1%       |

| 11    | Parboil   | Breadth-First Search     | bfs       | 8500000 nodes                             | 3.57  | 6%       |

| 12    | Rodinia   | Particle Potential       | lavaMD    | 7 	imes 7 	imes 7 boxes                   | 2.81  | 1%       |

| 13    | Parboil   | 2-D Histogram            | histo     | $10000 \times 4$ dimension                | 2.63  | 1%       |

| 14    | MapReduce | String Match             | sm        | 4 MB                                      | 2.52  | 3%       |

| 15    | Rodinia   | Cardiac Myocyte          | myocyte   | 100 instances                             | 2.38  | 1%       |

| 16    | Rodinia   | Needleman-Wunsch         | nw        | $2048 \times 2048$ data points            | 2.31  | 8%       |

| 17    | Rodinia   | Graph Traversal          | b+tree    | 10000 nodes                               | 2.21  | 25%      |

| 18    | MapReduce | Inverted Index           | ii        | 28 MB                                     | 2.19  | 2%       |

| 19    | Rodinia   | Particle Filter          | pfloat    | $128\times128\times10$                    | 2.15  | 8%       |

| 20    | Rodinia   | Tracking Microscopy      | leukocyte | 176 MB                                    | 1.88  | 1%       |

| 21    | MapReduce | Word Count               | wc        | 96 KB                                     | 1.86  | 54%      |

| 22    | Parboil   | Sum of Absolute Diff.    | sad       | $52~\mathrm{KB}~vs.~52~\mathrm{KB}$ frame | 1.76  | 3%       |

| 23    | Rodinia   | Speckle Reduction        | sradv1    | 512 	imes 512 data points                 | 1.74  | 15%      |

| 24    | Rodinia   | Speckle Reduction        | sradv2    | $2048 \times 2048$ data points            | 1.70  | 16%      |

| 25    | Parboil   | Cartesian Gridding       | mri-g     | 61 MB                                     | 1.49  | 2%       |

| 26    | Rodinia   | K-Means                  | kmeans    | 204800 data points; 34 features           | 1.47  | 0%       |

| 27    | Rodinia   | Matrix Decomposition     | lud       | $2048 \times 2048$ data points            | 1.27  | 28%      |

| 28    | Parboil   | PDE Solver               | stencil   | 512 	imes 512 	imes 64 input              | 1.23  | 6%       |

| 29    | Rodinia   | Heart Wall Tracking      | heartwall | 49 MB                                     | 1.19  | 0%       |

| 30    | Rodinia   | Back Propagation         | backprop  | 65536 input nodes                         | 1.10  | 3%       |

| 31    | Rodinia   | Thermal Modeling         | hotspot   | 512 	imes 512 data points                 | 1.07  | 29%      |

| 32    | Parboil   | Coulombic Potential      | cutcp     | 96604 atoms                               | 1.00  | 78%      |

| 33    | Parboil   | MRI Reconstruction       | mri-q     | $64 \times 64 \times 64$ data points      | 1.00  | 0%       |

| 34    | Parboil   | Angular Correlation      | tpacf     | 10391 data points                         | 1.00  | 19%      |

## 3.1. Inter-core reuse

In order to quantify the degree of temporal and spatial reuse of global data between thread blocks, we analyse the L1 miss traffic of each core. In Table I, we show the Reuse Coefficient ( $\mu$ RC), which is the percentage of miss requests received by the L2 cache from private L1 caches for addresses that reside remotely on at least one L1 cache. We see a maximum  $\mu$ RC of up to 78% with an average of 14% across all benchmarks. High  $\mu$ RC for some benchmarks indicates that reuse requests from L1 caches form a large portion of traffic to L2. It is worth noting that we only consider it as reuse if the load miss address is cached on a remote L1 at the time of the miss.

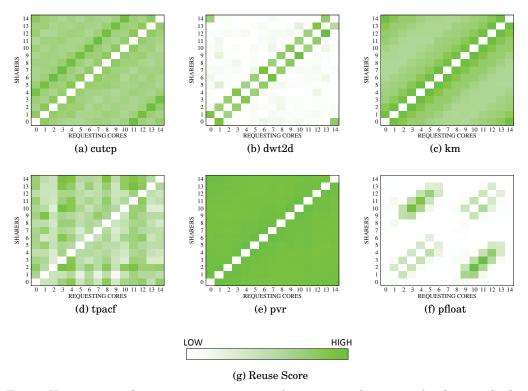

In Figure 3 we further characterize the inter-core reuse patterns at the granularity of each core with every other core, providing deeper insight into the reuse dynamics. For brevity, we show the set of distinct observed patterns and omit those that replicate the patterns shown here. The x-axis indicates the cores that incur an L1 load miss and the y-axis indicates the sharers for that miss. A dense area in the heat map at an (x,y) coordinate indicates that a high proportion of load miss requests by core-x are cached by the L1 at core-y. For instance, cutcp shows a prominent reuse of data cached at a distance of 4 cores from the location of the miss; dwt2d shows a strong reuse between neighbours; km shows a gradual decline in reuse as we go further from the core; and tpacf shows considerable levels of reuse across all cores.

39:6 S. Dublish et al.

Fig. 3: Heatmaps indicating inter-core reuse by cores on the x-axis for data cached on the cores on the y-axis. Dark spots in the heatmaps indicate high reuse between the corresponding cores at their x and y coordinates.

## 3.2. Efficacy of cooperation

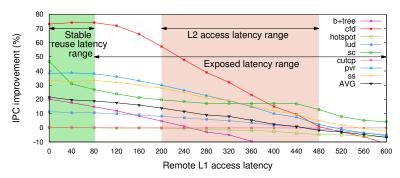

We have shown in the previous section that for general-purpose applications, there is considerable reuse across L1 caches. We refer to those load requests as reuse requests that miss in the local L1 but hit in a remote L1. By removing such reuse requests (also quantified as  $\mu$ RC) from the pool of total misses going to the L2 cache, we can reduce the pressure on L2 bandwidth. In order to assess the efficacy of reducing the bandwidth demand on the overall performance, we begin by examining the performance improvement when the reuse requests do not congest the access path to L2. In these cases, reuse requests are instead serviced cooperatively within the L1s with varying remote L1 access latencies, or reuse latencies. Since applications with low  $\mu$ RC are not expected to show any change, we focus on benchmarks with high  $\mu$ RC. Later, we demonstrate the effect of our final proposal on applications with low or zero  $\mu$ RC as well.

Figure 4 shows the speedup due to cooperation, and demonstrates a noticeable improvement in performance, specifically for memory-intensive applications with high  $\mu$ RC. For instance, cfd and pvr show performance improvements of up to 73% and 38% respectively. Both of these applications are severely bounded by the memory bandwidth and at the same time exhibit high reuse. On the other hand, despite high reuse in cutcp and hotspot, there is no significant gain in IPC since bandwidth is not critical for these benchmarks.

Fig. 4: Speedup of cooperation with varying remote L1 access latencies.

Another *key observation* in this study pertains to the variation of performance as a function of remote L1 access latency. We observe that the performance improvement in the region between 0-80 cycles is fairly stable, with the average IPC gain only changing from 21.5% to 18.8%. This is because in this region, latencies to remote L1s can be effectively hidden by the multithreading on the cores. Moreover, due to reduced congestion in the L2 access path and due to faster response to reuse requests (compared to L2 accesses), the average number of active compute threads on a core increases. This boosts the ability of the cores to further mask the memory access latencies. Due to these effects, reuse latencies up to 80 cycles are effectively hidden by multithreading and do not determine the execution time. However, on further increasing the reuse latencies, performance improvement starts to degrade more rapidly. In fact, the IPC gain returns to nearly 0% when the reuse latencies are varied in the range of L2 access latencies (around 300 cycles). This is because latencies for reuse requests get increasingly exposed and can no longer be hidden by multithreading, despite reduced congestion.

In summary, these initial results indicate that for memory-bound applications, when there is considerable reuse of data across L1 caches, cooperation among the private L1 caches can result in a considerable speedup (up to 21.5% on average). Notably, the observed performance improvement is fairly stable in the reuse latency range of 0-80 cycles.

## 4. COOPERATIVE CACHING

In the previous sections, we observed a potential for cooperative caching on GPUs and assessed its efficacy. We now propose a cooperative caching framework to use the private L1 data caches in an aggregate manner. We begin by formalizing the above discussion and analysing the parameters that contribute to the L2 access latencies for L1 miss requests. Later, we propose a cooperative caching scheme and discuss the architectural details.

## 4.1. Analytical Model

Here we present a simple analytical model to explain the conditions under which reuse delivers a performance gain. Firstly, in the absence of cooperation between L1s, let  $l_O$  be the average memory latency to access the shared L2 cache. Secondly, with cooperation between L1s, let  $h_{reuse}$  be the fraction of L1 misses that hit in a remote L1 cache. Furthermore, let  $l_{reuse}$  be the average hit latency for accesses to remote L1s. As a consequence of reduced congestion in the L2 access path due to remote L1 hits, let  $\delta_{cong}$  be the reduction in L2 access latency. And finally, let  $\delta_{overhead}$  be the coopera-

39:8 S. Dublish et al.

tion overhead borne by those requests that do not have a shared copy. Therefore, the new average memory latency to L2 upon enabling cooperation,  $l_C$ , can be obtained via Equation 1.

$$l_C = (l_O - \delta_{cong} + \delta_{overhead}).(1 - h_{reuse}) + l_{reuse}.h_{reuse}$$

(1)

$$\left. egin{align*} l_{reuse} < l_O \\ \delta_{overhead} < \delta_{cong} \end{array} \right\}$$

Criteria for useful cooperation (2)

In order to derive gain from cooperative caching,  $l_C$  must be minimized. Therefore, remote L1 accesses for reuse requests must take less time than a normal L2 access, i.e.,  $l_{reuse} < l_O$ . Additionally, we have already seen in Figure 4 that the maximum gain from cooperation is sustained in the lower reuse latency range, i.e.,  $l_{reuse} \in (0,80)$ . Finally, for the remaining L2 accesses, the cooperation overhead must be less than the benefit obtained from reducing the congestion in the L2 access path, i.e.,  $\delta_{overhead} < \delta_{cong}$ . A combination of above conditions will result in a lower average L2 access latency, i.e.,  $l_C < l_O$ .

How should we go about implementing the cooperative caching framework? Following the approach of traditional multicores, a central directory in the L2 cache [Lebeck and Wood 1995][Acacio et al. 2002][Kaxiras and Keramidas 2010] can be used to store information about the sharers. However, maintaining a directory as part of the L2 will not mitigate the existing bandwidth problem in accessing the L2, and instead, will only worsen it. This is because the additional control and update traffic to the central directory will further increase the bandwidth demand to the L2 cache. Alternatively, an approach along the lines of cooperative caching schemes for CPUs [Chang and Sohi 2006][Chang and Sohi 2007][Herrero et al. 2008] may be used. Such schemes aim to minimize hop latencies to find a sharer and retrieve data using a highly interconnected network of L1 caches. However, since we have demonstrated that we have a considerable leeway of around 80 cycles to fetch the shared data from a remote L1, such an aggressive scheme to find a sharer is an overkill for GPUs.

Therefore, we propose a lightweight ring-based Cooperative Caching Network. A ring topology is the lowest degree network and requires the fewest number of intercore connections. It is also lowest in terms of logical complexity and power consumption as all core-to-core connections will be near-neighbour, and therefore, the wires will be short. In addition, all routers in a ring are simple multiplexers, which are more energy efficient than complex crossbar routers. As we have shown that GPUs can tolerate reuse latencies gracefully up to 80 cycles, a ring topology appears to be a cost-effective solution, as it allows us to trade-off higher latencies for simplicity and short wires, *i.e.*, lower power consumption and die-area cost.

## 4.2. Architecture

In our proposed scheme, we facilitate the communication between neighbours by connecting the private L1 caches in a ring via our Cooperative Caching Network (CCN). The CCN comprises of two different channels, viz., request channel and response channel. The request channel comprises of a network of Request Queues or ReqQ while the response channel comprises of a network of Response Queues or RespQ. As shown in Figure 5, each L1 has an independent pair of the aforementioned queues to allow the cache to participate in cooperative caching. The L1 caches interact with their home queues via CCN Buffers (CB), which hold the tag and Core-ID for the load misses, until the CCN is ready to accept a request. A new miss request, upon entering the local Request Queue, travels around the request channel by hopping on other Request Queues and probing the different L1 caches on its way. If a remote copy is found on

Fig. 5: Cooperative Caching Network.

one of the nodes, the response from the hit node is sent back to the requesting core in a similar way by hopping in the reverse direction via the Response Queues at each core. Note that a remote L1 copy is considered for sharing only if it is not pending on a cache-fill for the requested data at the time of lookup. In other words, pending-hits due to outstanding miss requests are not considered for sharing in CCN.

Specifically, upon incurring a load miss for global data, instead of sending the miss directly to the L2, each core pushes the miss tag information into its CB along with the Core-ID, where the request waits until the corresponding ReqQ is ready to accept a new request. At every cycle, valid entries at the head of the ReqQ lookup the corresponding L1 cache (if it is not the home core of that request) before hopping on to the next ReqQ. If the request travels back to the requesting core without a reuse copy, it is finally sent to L2. However, if a sharer is found, the sharing core enqueues the response to its RespQ. The response travels back to the requesting core, thereby avoiding an L2 access. If the request queues get full due to congestion, CB eventually stops accepting new miss requests. In such a scenario, the L1 load misses go directly to L2 until the CCN can start accepting new requests again.

4.2.1. Prioritization policy for queues. Each queue in the CCN has a corresponding input multiplexer to select one of the entries out of the two possible input sources. In the request channel, a ReqQ can either accept a new miss request from the home core via CB, or a forwarded request from a preceding ReqQ. In our proposal, we prioritize an older request (from ReqQ) over a new one (from CB). This helps in preventing oversubscription of CCN to new L1 misses by allowing the previously accepted requests to pass-through and therefore, minimize the roundtrip overhead ( $\delta_{overhead}$ ) in CCN for subscribed requests. Repeated unsuccessful attempts to inject a new request in the CCN due to the above prioritization, thus causes the CB to get full and hence, deflects the L1 misses directly to L2, allowing the CCN to recover from congestion.

In response queues, however, we prioritize a new cache response (from Core) over an older response (from RespQ). This is because response queue latencies do not contribute to  $\delta_{overhead}$  but contribute to the reuse latencies  $l_{reuse}$ , which has comparatively more relaxed requirements (shown in Figure 4). More importantly, if the response of a

39:10 S. Dublish et al.

new remote hit is not accepted by the response queue, the tag entry at the head of the corresponding ReqQ that caused the hit is not popped, potentially stalling the entire request network and increasing the  $\delta_{overhead}$  in the request channel.

4.2.2. CCN Memory Consistency. The CCN mechanism conforms to the existing memory consistency model supported by Fermi. CUDA provides two types of load instructions [Nvidia 2016] – a normal load cached at L1 (ld.ca) and a direct load to L2 (ld.cq), bypassing the L1. Due to the write-through, no-write-allocate policy of the L1 cache, a write causes the matching cache line in L1 to be invalidated thereby causing the most recent value to reside in L2. However, due to a weak memory model [Alglave et al. 2015][Nvidia 2014] and absence of coherence in GPUs, an ld.ca accessing L1 on a different core can return a stale value. Litmus tests in [Alglave et al. 2015] have also shown that due to weak consistency, an ld.ca load may return a stale value on the same core as well, even if preceded by an ld.cq to the same address (CoRR). CCN adopts similar weak memory ordering semantics for ld.ca loads; indeed, an L1 miss can return a stale value by snooping other cores via CCN, instead of reading the L2 which may have the latest value. However, since a baseline GPU guarantees reading the most recent value for ld.cq loads, CCN does not intercept such loads and hence does not further weaken the memory model. In other words, when a programmer uses ld.cq loads to bypass the L1, the current memory model ensures the most recently written value is returned – a correctness guarantee also provided by CCN.

## 4.3. Shadow Tags

Since each L1 now services additional tag lookups for CCN requests, such remote lookups could affect the performance of local cache accesses. To eliminate the interference of remote lookups on local requests, we duplicate the tags of the L1 data cache in a separate set of Shadow Tags (ST) adjacent to each L1. The shadow tags always contain an identical copy of the L1 tags, which is achieved by always writing tag updates to both sets of tags simultaneously. As a result, concurrent reads at independent addresses can then take place to L1 tags and shadow tags, from the local core and remote lookups respectively. Therefore, the shadow tags dissociate the performance of each local cache from interference of CCN traffic. However, if a shadow tag lookup succeeds, then the remote access makes a regular L1 access to retrieve the data it needs. This steals a cycle from the L1 data cache, which is taken into account in our performance model.

**Overhead**: For the largest L1 data cache configuration of 48 KB with 128 byte line size, we require 24 upper address bits per tag, assuming 40-bit physical addresses[Nvidia 2009], plus one valid bit. As the L1 data cache is 4-way set-associative, the shadow tags are arranged as 96 sets of four 25-bit tags in  $96 \times 100$  single-ported tag memory.

| Way 0                   | Way 1                   | Way 2                   | Way 3                   |

|-------------------------|-------------------------|-------------------------|-------------------------|

| $V_0 \mid Tag_0[39:16]$ | $V_1 \mid Tag_1[39:16]$ | $V_2 \mid Tag_2[39:16]$ | $V_3 \mid Tag_3[39:16]$ |

Therefore, the net storage overhead of the shadow tags is 1200 bytes per SM and a total of 17.5 KB for a 15 core GPU that we consider in our study. Although, each remote access has to be checked in multiple shadow tags, these shadow tag memories are small and can be constructed from low-leakage high-density bit-cells without impacting the overall cycle time of the ring interconnect.

## 4.4. Request Throttler

In order to prevent those cores that do not exhibit any inter-core reuse from congesting the CCN, we introduce a Request Throttler (RT) at each core. The purpose of RT

is to throttle the remote lookup requests directly to L2 cache when prior routing of misses to CCN proves to be below a threshold level of effectiveness. In order to do this, each RT periodically samples the CCN performance parameters and at the end of the sampling period, computes the success rate in routing its load misses to CCN during the sampling interval. The success rate is determined by the ratio of hits in the CCN to the total number of requests injected in the CCN by the corresponding L1 cache. If the success rate is below the threshold, the L1 cache bypasses the CCN until the next sampling interval, and performs the load miss by sending the request directly to L2 cache. However, the shadow tags of the throttled cores still participate in the lookup for other requests in the CCN.

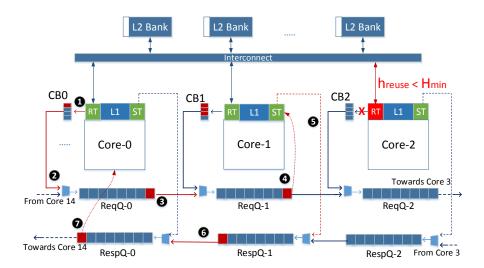

To illustrate the working of RT further, we define the sampling interval as  $t_S$  and the periodicity of sampling as  $t_P$  where  $t_S << t_P$ . Therefore, the entire period of execution is logically divided into multiple epochs of duration  $t_P$ . We also define  $H_{min}$  as the minimum hit rate required in the CCN in order to derive utility out of cooperation.

At the beginning of an epoch of interval  $t_P$ , each core begins by routing the load misses to CCN for a fixed sampling duration of  $t_S$ . During the  $t_S$  interval, RT collects the statistics about the number of requests injected in the CCN  $(N_{total})$  and the number of hits observed for its requests  $(N_{hits})$ . At the end of the sampling duration, RT computes the hit rate  $(h_{reuse})$  in the CCN, i.e.,  $h_{reuse} = N_{hits}/N_{total}$ . If  $h_{reuse} > H_{min}$ , RT continues to inject requests in the CCN for the remaining duration of  $(t_P - t_S)$  in the current epoch. On the other hand, if  $h_{reuse} < H_{min}$ , RT disables the routing of requests to CCN for the remaining duration of the epoch. After the current epoch ends,  $N_{hits}$  and  $N_{total}$  are reset and RT repeats the entire process again for the new epoch. Therefore, with the help of RT, we improve the average success rate of sending a load miss to CCN by preventing those cores from cooperating that are not working on potentially reusable data, during specific epochs of execution.

## 4.5. Working example

In this section, we further illustrate the working of CCN. Figure 6 shows the flow of requests within the CCN. In this example, Core-0 incurs a load miss for a global data in its private L1 cache. In the baseline architecture, this L1 miss would be directly routed to the L2 cache. However, with our scheme, the miss request can either go to the CCN or to the L2 cache. RT takes this decision for that particular core on the basis of the statistics collected over the most recent sampling interval,  $t_S$ . In this example, we assume that  $h_{reuse}$  for Core-0 and Core-1 suggests healthy reuse (>  $H_{min}$ ) and therefore, these cores continue to use CCN. However, Core-2 observes a low reuse in the recent  $t_S$  interval thereby routing all the requests directly to L2 cache for the current epoch.

Thus, in order to service the miss at Core-0 via CCN, the tag and Core-ID of the load request are pushed ① onto the corresponding CCN Buffer, CB0. Based on the input prioritization policy for ReqQ, the new tag waits in CB0 until it acquires the priority and is accepted ② by the ReqQ-0. Upon reaching the head of ReqQ-0, the miss request does not perform a lookup in the ST of Core-0 as it is the home core of the miss request and therefore, it is directly passed to ReqQ-1 ③. Upon reaching the head of ReqQ-1, it performs a lookup ④ in ST of Core-1. Assuming it is a hit in Core-1, the ST receives the cache line from the corresponding L1 cache and enqueues the response in RespQ-1, given that the RespQ-1 is not full. On the other hand, if the RespQ-1 is full, the response is stalled, thereby preventing the tag at the head of the ReqQ-1 from getting popped. Once the response reaches the head of the queue at RespQ-1 and acquires priority to enter the next queue, it is pushed into RespQ-0 ⑤. Since Core-0 is the home core of the response, the new entry to RespQ-0 is bypassed to the head of the

39:12 S. Dublish et al.

Fig. 6: Working of the Cooperative Caching Network with Request Throttling.

queue and the response is serviced **7** to the L1 cache of Core-0, hence completing the request-response cycle.

#### 5. EVALUATION

In this section, we discuss the implementation of our proposed architecture and demonstrate the results.

#### 5.1. Implementation

For the purpose of this study, we implement and evaluate two flavours of our proposed architecture, *i.e.*, CCN-B and CCN-RT. CCN-B is our baseline CCN architecture which includes a pair of queues and shadow tags at every node of the network. Whereas in CCN-RT, we add the request throttling feature to the baseline CCN architecture. Table II(b) summarizes the design parameters for CCN-B and CCN-RT.

In our implementation, we choose the sampling interval and the periodicity of sampling as 1 million and 10 million instructions respectively. This is based on the observation that most benchmarks show a single-phase sharing across the entire application. Hence, it allows us to sample for a short duration to get a fairly accurate hint for a large duration that follows the sampling interval. Further, on the basis of our sensitivity studies, we select the threshold hit rate  $(H_{min})$  as 5%, *i.e.*, the minimum number of hits required to derive benefit from cooperative caching. We also observe in our experiments that small 8-entry Request and Response Queues provide most optimal results.

Furthermore, the request and response channels in CCN are configured to flow in opposite direction. This is because our experiments show that in such a case, servicing reuse requests takes an average of 10 hops compared to a fixed 15 hops when both the channels propagate in the same direction.

## 5.2. Experimental setup

We model the Cooperative Caching Network on GPGPU-Sim (version 3.2.2) [Bakhoda et al. 2009] to simulate a Fermi-like GPU with the configuration parameters listed in Table II(a). For energy and area simulations, we use GPUWattch [Leng et al. 2013], a

| Parameter        | Value                                                             |  |  |  |  |

|------------------|-------------------------------------------------------------------|--|--|--|--|

| (a) GPGPU-Sim    |                                                                   |  |  |  |  |

| Core             | 15 SMs, Greedy-then-oldest (GTO) scheduler                        |  |  |  |  |

| Clock frequency  | Core @ 1.4 GHz; Interconnect/L2 @ 700 MHz                         |  |  |  |  |

| Threads per SM   | 1536                                                              |  |  |  |  |

| Warp width       | 32                                                                |  |  |  |  |

| SIMD lane width  | 32                                                                |  |  |  |  |

| Registers per SM | 32768                                                             |  |  |  |  |

| Shared Memory    | 48 KB                                                             |  |  |  |  |

| L1 Data Cache    | 16KB, 128 byte line, 4-way, LRU, write-through, no-write-allocate |  |  |  |  |

| L2 Cache         | 768 KB, 128 byte line, 8-way, LRU, write-back, 12 banks           |  |  |  |  |

| DRAM             | GDDR5 DRAM, 6 channel, 64-bits per channel, 924 MHz               |  |  |  |  |

| (b) CCN          |                                                                   |  |  |  |  |

| CCN Buffer       | 8-entry, 30 bits per entry (26 bits Tag + 4 bits Core-ID)         |  |  |  |  |

| Request Queue    | 8-entry, 30 bits per entry                                        |  |  |  |  |

| Response Queue   | 8-entry, $\sim$ 128 bytes per entry (cache line + Core-ID)        |  |  |  |  |

| CCN ring         | 4-byte request channel; 32-byte response channel; 1.4 GHz         |  |  |  |  |

| Shadow Tag       | 1200 bytes size (modelled upon 48 KB L1 data cache)               |  |  |  |  |

| $t_S$            | 1 million instructions                                            |  |  |  |  |

| $t_P$            | 10 million instructions                                           |  |  |  |  |

| $H_{min}$        | 0.05 (5 percent hits)                                             |  |  |  |  |

Table II: Configuration parameters for (a) GPGPU-Sim and (b) CCN.

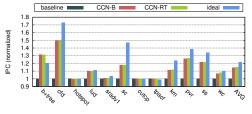

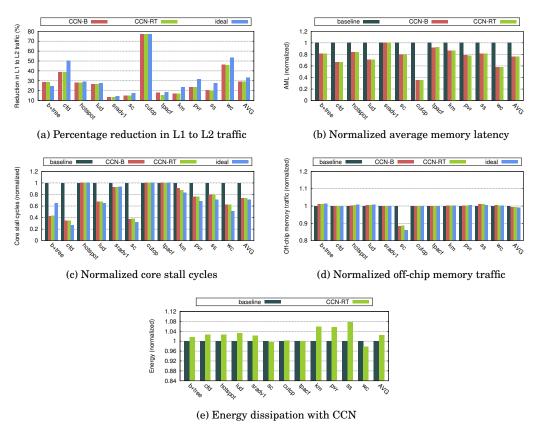

- (a) Speedup for applications with  $\mu RC > 10$

- (b) Percentage improvement in IPC for applications with  $\mu RC < 3$

Fig. 7: Performance variation with cooperative caching.

McPAT based power model integrated in GPGPU-Sim. All CCN transactions have been modelled at *cycle-by-cycle accuracy* in the simulator which includes queuing delays in the request and response channels, CCN congestion and L1 cycle stealing by shadow tag accesses. We run all the benchmarks to completion, or until they execute 16 billion instructions, whichever comes first.

# 5.3. Results

We begin by evaluating the overall performance improvement with our proposed schemes for benchmarks that exhibit inter-core reuse ( $\mu RC > 10$ ). We also show the neutrality of our scheme for benchmarks with little or no reuse ( $\mu RC < 3$ ). Later we assess the finer parameters for the former set of benchmarks, as applications with inter-core reuse are the primary motivation for this study. We do not show the benchmarks between this range as results of the above categories are good indicators of the trend in the rest of the benchmarks. We also compare the results of our proposed schemes, *i.e.*, CCN-B and CCN-RT, against an *ideal* cooperative caching configuration that services all of the remote hits with zero latency, without incurring any overheads of cooperative caching.

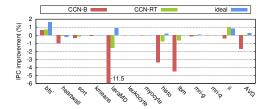

5.3.1. Performance. In Figure 7a, we show the speedup with CCN-B and CCN-RT for applications that exhibit reuse. Over the baseline configuration, we observe an average improvement of 14.5% with CCN-B and 14.7% with CCN-RT. Memory-bound applica-

39:14 S. Dublish et al.

tions such as cfd, ss and pvr show higher speedup compared to non-memory-bound applications as they are more sensitive to bandwidth bottlenecks. b+tree shows a higher improvement than ideal case due to the timing variations in scheduling warps. Such an aberration is also caused due to higher number of coalesced hits on cache lines allocated for on-going remote L1 accesses, which does not occur in the ideal scenario due to zero cycle latency for remote L1 accesses.

We also assess the impact of cooperative caching on applications that show little or no reuse. For such applications, cooperative caching adds an extra roundtrip overhead of going through the CCN. This is because due to low  $\mu$ RC, most requests end up going to L2 cache after an unsuccessful traversal in the CCN. In such cases, Request Throttler helps in preventing the L1 misses from incurring the CCN overhead when there is little or no reuse. In Figure 7b, we show that with CCN-B, we see a degradation of up to 11.5% and an average degradation of 1.7% compared to the baseline GPU. However, with CCN-RT, the maximum degradation reduces to 1.5% with an overall average of 0.1%.

5.3.2. L2 cache bandwidth demand. In Figure 8a, we demonstrate the effectiveness of our proposed technique in mitigating the L2 cache bandwidth bottleneck. On average, CCN-RT reduces the traffic to L2 cache by 29% compared to the baseline GPU. It is in close proximity to the ideal-case average of 33% indicating that most of the reuse hits on remote L1 caches are captured by the proposed architecture. Virtually no difference between CCN-B and CCN-RT demonstrates that while throttling diverts most of the non-productive traffic directly to L2 cache, it does not reduce the number of potential hits in the CCN. If it would divert the useful reuse requests to L2 cache bypassing the CCN, then we would see a lesser reduction in L2 traffic with CCN-RT compared to CCN-B.

5.3.3. Average Memory Latency (AML). In Figure 8b, we see an average reduction of 24% in AML with our proposed CCN-RT architecture for applications that show reuse. We observe that cutcp shows the maximum reduction of 65% in AML due to high  $\mu$ RC of 78%. However, it does not translate into performance gain due to its non-memory-bound nature.

5.3.4. Core stall cycles. We observed in the above results that the performance improved by mitigating the bandwidth problem (indicated by L2 traffic), and by servicing the misses in less time (indicated by AML). This is because cores now spend less time waiting for memory. Therefore, we assess the impact of our proposal on the total number of cycles for which the cores are stalled. In Figure 8c, we observe a significant reduction in core stall cycles for memory-bound applications such as *cfd* and *sc*, while no degradation is seen for non-memory-bound applications like *cutcp* and *tpacf*. On average, we reduce the core stall cycles by 26%, which is in close proximity to the ideal reduction of 28%.

5.3.5. Off-chip memory traffic. In order to dissociate the effects of L2 and off-chip bandwidths on the overall performance gain, we analyse the change in off-chip memory traffic. As shown in Figure 8d, we see that for most applications there is no visible difference in the traffic to off-chip memory, indicating that the entire performance improvement can be attributed to the mitigation of bandwidth bottleneck between private L1s and the shared L2. Therefore, it can be inferred for most benchmarks that in the baseline architecture without CCN, the reuse requests mostly hit in the L2 cache thereby only burdening the L2 cache bandwidth with duplicate requests. However, in sc we notice a reduction in DRAM traffic by 12% with CCN-RT. This indicates that for sc a significant portion of reuse requests to L2 also misses in the L2 cache, adding to the DRAM traffic. As a result, upon removing the reuse requests to L2 cache with

Fig. 8: Experimental results demonstrating the effect of cooperative caching.

the help of CCN in sc, not only the traffic to L2 cache is reduced, but also the traffic to DRAM is reduced. Therefore, the performance benefit in sc with CCN-RT can be attributed not only to the mitigation of L2 bandwidth bottleneck, but also to the mitigation of DRAM bandwidth bottleneck.

5.3.6. Summary. In the above results, we observed that for applications which exhibit reuse, we are able to reduce the traffic to L2 cache by 29% while also reducing the average memory latency by 24%. As a consequence of the above improvements, we reduce the average core stall cycles by 26% which translates into an average performance improvement of 14.7%.

#### 5.4. Hardware costs

5.4.1. Area. We use GPUWattch [Leng et al. 2013] to estimate the area of our proposed architecture. We use the existing components in GPUWattch to model the CCN components, after appropriate scaling wherever necessary. CCN adds an area overhead of  $4.38~mm^2$  for the ring interconnect and the shadow tags (corresponding to the largest L1 data cache configuration) at 40 nm technology. Other storage units such as CCN Buffers and Request/Response Queues add another  $4.82~mm^2$ . This amounts to an overall increase in die area by 1.3% with respect to baseline processor architecture area of  $700~mm^2$ .

39:16 S. Dublish et al.

(a) Speedup with varying L1 cache sizes

(b) Speedup with link latencies of 1, 3 and 5 cycles

(c) Speedup with varying width of SIMD lanes

Fig. 9: Sensitivity analysis.

5.4.2. Energy. With CCN, cores are stalled for fewer cycles, thereby reducing the leakage power. In addition, fewer packets require routing at the energy-inefficient crossbar routers. Also, lower traffic to L2 leads to lower energy consumption by the NoC. However, high shadow tag lookups for remote cache accesses normalizes other energy gains of the CCN, resulting in an average energy overhead of 2.5% (Figure 8e).

## 5.5. Sensitivity analysis

5.5.1. L1 cache size. As Fermi offers configurable L1 cache sizes of 16 KB and 48 KB, we analyse the sensitivity of our proposal to L1 cache size. As shown in Figure 9a, on increasing the L1 cache size to 48 KB, we observe an average IPC gain of 20.6% with CCN, compared to 14.7% with CCN on 16 KB L1 (over their respective baselines). This is due to the following reason. Although, increasing the L1 cache size reduces the number of capacity/conflict misses thereby reducing the opportunities to find remote L1 hits in the CCN, we observe that a larger L1 significantly increases the likelihood of finding a remote L1 sharer for a compulsory miss. Therefore, due to significant increase in utility of CCN for compulsory misses on increasing the L1 size (which dominates the decrease in utility of CCN due to lower conflict/ capacity misses), we observe a higher improvement in performance with larger L1s.

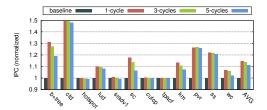

5.5.2. Link latency and frequency. In this study, we analyse the performance impact of interconnect latencies for every hop on the CCN ring. This is done by varying the coreto-core transfer latency from 1-5 cycles (i.e., 15-75 cycles for the entire ring). For a 700  $mm^2$  chip, each hop is approximately 3.5 mm of on-chip distance and therefore, 1-5 cycles at 1.4 GHz is a reasonable window to complete the transfer [Beckmann and Wood 2004]. It is worth noting that varying the CCN link latency also captures the effect of running the CCN ring at a fraction of core frequency. Therefore, this study shows the performance variation on using the CCN ring at up to  $1/5^{th}$  the core frequency (280 MHz).

In Figure 9b, we see that for most applications, the IPC gain is fairly resilient to increasing link latencies (or decreasing ring frequencies). For instance, *cfd* shows a

marginal reduction of 1% when the latency increases from 1 to 5 cycles. A minority of applications show visible reductions in the gain as link latency increases. For example, the IPC gain of b+tree drops from 31% to 19%, although it still maintains a modest overall improvement in performance. On the average, we see IPC improvements drop from 14.7% to 13.6% as latency is increased from 1 to 3 cycles, settling further at 11.2% when the link latency is increased to 5 cycles. These results indicate that our proposed scheme is fairly robust to increasing inefficiencies in the ring interconnect (as well as increasing distance between the neighbouring cores).

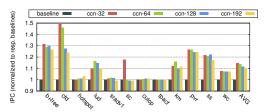

5.5.3. SIMD lane width. Each core in Nvidia's Fermi GPU consists of 32-lane SIMD unit, each lane capable of executing one floating-point or arithmetic instruction per clock. In this study, we analyse the utility of CCN on increasing the SIMD lane width. In Figure 9c, we plot the performance gain with CCN-RT on baseline configuration with varying SIMD lane width of 32 (ccn-32), 64 (ccn-64), 128 (ccn-128) and 192 (ccn-192), each normalized to their respective baselines. On average, the performance gain drops modestly from 14.7% to 13.6% on increasing the SIMD lane width from 32 to 64, settling further at 11.4% and 10.2% with SIMD lane widths of 128 and 192 respectively. Although the minor reduction in CCN gain is due to the increased latency tolerance provided by additional SIMD lanes, cooperative caching continues to provide considerable benefits for memory-intensive applications. This is due to the fact that by increasing the SIMD lanes or the compute capability of the cores, only compute-bound applications are expected to show significant speedups and a higher overlap of memory latencies with computation. In contrast, memory-intensive applications lack independent compute instructions and continue to be bottlenecked by memory resources. Therefore, additional compute resources for memory-intensive applications provides only limited additional latency tolerance to the cores due to which cooperative caching continues to be useful in reducing memory latencies that lie in the critical path. However, some benchmarks such as lud and km also show momentary improvement in performance gain with CCN on increasing the SIMD lane width. We observe that this is because with wider SIMD lanes, higher number of threads arrive at the memory instructions per cycle, issuing higher number of requests that may exhibit reuse, thereby amplifying the utility of CCN in reducing the traffic that could lead to even higher congestion.

#### 5.6. Discussion

In future, scalability of the CCN can be addressed by a hierarchical implementation of the proposed ring network [Holliday and Stumm 1994][Ravindran and Stumm 1997]. A sub-CCN-ring that contains the requesting core can inquire other sub-CCN-rings in *parallel*, thereby decomposing the serial latency of traversing the high number of cores into concurrent transactions to multiple rings. In addition, as coherent caches in GPUs are imminent with future architectures[Martin et al. 2012][Power et al. 2013][Singh et al. 2013], inter-core communication via CCN can also act as a substrate for implementing cache coherence.

#### 6. COMPARATIVE STUDY

In this section, we perform a quantitative and qualitative comparison of CCN with alternative techniques that address the bandwidth bottleneck in GPUs.

## 6.1. Increasing L2 banks

An alternative technique to increase the bandwidth to L2 is to increase the number L2 banks. However, increasing the banks only reduces the congestion in the access path to L2 whereas CCN, in addition to reducing pressure on L2 bandwidth, provides

39:18 S. Dublish et al.

Fig. 10: Comparative study.

a significantly faster response for a fraction of miss requests. In our experiments, we observe that CCN services the reuse requests in 42 cycles ( $l_{reuse}$ ) on average, for 29% misses ( $h_{reuse}$ ) that hit in CCN. For the remaining L2 accesses, CCN adds a roundtrip overhead of 54 cycles ( $\delta_{overhead}$ ). It also reduces the congestion overhead to L2 by 78 cycles ( $\delta_{cong}$ ). Considering that the average L2 access latency without the CCN is 300 cycles ( $l_O$ ) and substituting the above values in Equation 1, the average L2 access latency with CCN is computed to be 208 cycles (Equation 3).

$$l_{C(CCN)} = (300 - 78 + 54) \times 0.71 + (42) \times 0.29 = 208$$

(3)

$$l_{C(2\times)} = (300 - 80 + 0) \times 1.0 = 220$$

(4)

$$l_{C(CCN/2\times)} = (300 - 117 + 54) \times 0.71 + (42) \times 0.29 = 180$$

(5)

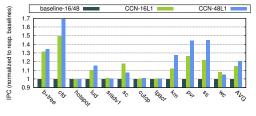

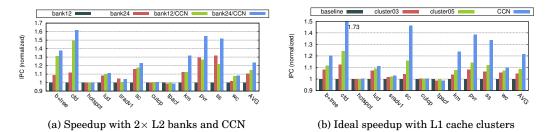

However, increasing the L2 banks only reduces  $\delta_{cong}$  (though marginally more than CCN for some benchmarks), but requires all accesses to go through the L2 access latency, albeit via reduced congestion. Upon substituting corresponding values in Equation 1, the reduced L2 access latency is computed to be 220 cycles (Equation 4). Therefore, in Figure 10a, we observe an average IPC improvement of 10.2% upon a 2× increase in L2 banks from 12 to 24. In contrast, CCN implemented with 12-bank L2 configuration shows a higher improvement of 14.7% (with cfd performing 34% better with CCN than with 2× L2 banks).

Importantly, CCN is partly orthogonal to increasing the banks at L2. This is because, in addition to reducing the  $\delta_{cong}$  further, CCN adds the benefit of faster access to reuse requests. The average L2 access latency in Equation 1 for a CCN architecture on a 24 L2 banks configuration is computed to be 180 cycles (Equation 5). In Figure 10a, our experiments show an average performance improvement of 23.5% with both the techniques combined.

With respect to the cost, increasing the L2 banks would require higher number of ports in the crossbar. As the area of a crossbar increases polynomially on increasing the ports, the area overhead will be significant. Energy demands also increase significantly as each router is more complex and need to arbitrate on higher number of nodes. In contrast, CCN only require simple multiplexers at each router and scales well with respect to area and energy overheads. Alternatively, increasing the L2 datapath width to provide more L2 bandwidth would also be area intensive as it entails increasing the area of 15x12 core-to-L2 connections in the crossbar, making the crossbar much bulkier. In contrast, CCN only requires 15 core-to-core connections. As core-to-L2 connections are typically longer (in addition to being higher) than core-to-core connections in CCN, there is a higher overhead in scaling the former.

#### 6.2. Sharing Tracker

Tarjan *et al.* [Tarjan and Skadron 2010] proposed a scheme to exploit reuse within the private caches by using a Sharing Tracker, a decomposed version of the coherence directory. It aims to reduce the *off-chip memory bandwidth* demand by diverting DRAM accesses to private caches that contain a shared copy.

Although we adopt this intuition to reuse shared copies in private caches, our aim is to reduce the bandwidth demand to the *shared cache* (and not the DRAM as in [Tarjan and Skadron 2010]). This is because in current scenario with recent GPU architectures, exploiting *reuse does not reduce off-chip memory traffic* (as shown in Figure 8d) and hence, a common directory in shared cache is not expected to show any benefit since there are not many off-chip memory accesses that it can avoid. In fact, since accessing and maintaining the sharing tracker in L2 cache adds to the bandwidth demand to L2 without relieving pressure on off-chip bandwidth, it will only exacerbate the problem by increasing the L2 access latencies and thereby worsening the IPC with respect to baseline. For those architectures where off-chip memory traffic is also reduced by exploiting sharing within private caches, CCN achieves the same, but in addition, it also reduces the traffic to L2 (which we have shown to be critical to performance), and therefore provides a significant advantage over a directory approach.

#### 6.3. Clustered sharing

Keshtegar *et al.* [2015] proposed an architecture to enable restricted sharing within core clusters. However, we have shown in Figure 3 that while some benchmarks show higher reuse with neighbouring cores, others show a uniform sharing with all cores. In Figure 10b, we show the ideal performance improvement (with no sharing overheads) obtained by sharing within cache clusters and we compare it with an ideal case of CCN (sharing among all cores). We observe an average IPC gain of 4% and 8% with ideal clusters of 3 and 5 L1s respectively, compared to an average IPC gain of 21% with ideal CCN. This suggests that for most benchmarks, upon restricting the sharing within cache clusters, SMs lose out on most of the reuse data.

Moreover, the cluster-based proposal by Keshtegar *et al.* [2015] employs a mesh-type network within a cluster and scales polynomially with the number of cores. Therefore, we expect the area overhead of clusters to exceed the area of ring-based connections in CCN which scales linearly with the number of cores. Furthermore, in current GPUs, SMs are placed linearly around the central L2 cache [Nvidia 2009][Nvidia 2012] and therefore, clusters would require longer wires to connect the far-ends of a cluster as compared to only near-neighbour connections in CCN.

## 6.4. Summary

In this section, we have shown that CCN fares well in comparison with alternative techniques. CCN performs better than simply increasing the number of L2 banks while also being partly orthogonal to the latter technique. Sharing tracker is expected to show negative performance gain with the baseline architecture; and restricted sharing within cache clusters significantly reduces inter-core reuse.

#### 7. RELATED WORK

While sharing across L1 caches is a common occurrence in multiprocessors, as emphasized by the prevalent use of sophisticated coherence infrastructure, we derive significant benefits by exploiting L1 sharing for GPGPU workloads, a property atypical in GPUs. Additionally, in contrast to earlier works [Yazdanbakhsh et al. 2016][Jog et al. 2016] where only the off-chip memory bandwidth is considered critical to performance, we identify the criticality of mitigating congestion in the on-chip cache hierarchy be-

39:20 S. Dublish et al.

tween L1 and L2 cache. In the following subsections, we further discuss several prior works related to the ideas presented in CCN and cite their key differences.

## 7.1. Cooperative Caching in CMPs

In the realm of CMPs, Chang *et al.* [Chang and Sohi 2006][Chang and Sohi 2007] proposed cooperative caching by adapting the coherence infrastructure. Subsequently, Herrero *et al.* [2008] proposed a scalable distributed cooperative caching scheme by redesigning the coherence engine to provide distributed directories. Both schemes aim to provide aggressive latency and capacity benefits for on-chip caches in CMPs. However, since GPUs are relatively more tolerant to latencies, in this paper we address the problem of bandwidth in GPUs. In addition, a directory-based scheme is not directly portable to GPUs due to the lack of coherence infrastructure and therefore, our solution proposes an independent lightweight network.

#### 7.2. Ring Network

Ring topologies have been used extensively in commercial multiprocessors to provide low cost inter-core communication. Larrabee [Seiler et al. 2008] employs a bidirectional ring network to allow on-chip communication between latency-sensitive CPU cores, coherent L2 caches and other blocks with each link being 64 bytes wide (net width of 128 bytes). Xeon-Phi [Chrysos, George 2012] also comprises of bidirectional rings with each ring comprising of three independent rings, viz., a 64 bytes data block ring for data transactions, an address/command ring, and an acknowledgement ring for coherence and flow control messages (net width >128 bytes). In contrast, CCN enables bidirectional communication between latency-tolerant GPU cores by connecting the incoherent L1 caches in a ring. Due to relaxed latency constraints in CCN compared to prior ring interconnects in multiprocessors, the bus width for inter-core transfers is smaller with each link being 8 bytes and 32 bytes wide respectively (net width of 40 bytes). Therefore, our proposal exploits the latency-tolerance property of multithreaded cores to provide low cost inter-core communication through a lightweight ring network.

Furthermore, Campanoni *et al.* [2014] proposed a ring cache for HELIX-RC that acts as a distributed first-level cache, preceding the private L1 cache. Each ring node has a cache array to cache shared data and satisfies the loads and stores received from its attached core. To avoid coherence complications, memory addresses are permanently mapped to the nodes of the ring cache. In contrast, each node in the CCN ring network comprises of a shadow tag array, needed only for lookups and not for storage of shared data. Subsequent loads to the shared data via CCN are performed directly in the corresponding L1 caches since there is no separate data array for the ring nodes. Therefore, the nodes in the CCN ring network are lighter than nodes in the ring cache proposed in HELIX-RC.

## 7.3. Shadow Tags

Prior proposals such as Piranha [Barroso et al. 2000] and Niagara [Kongetira et al. 2005] have replicated tag structures of the private L1 caches at the shared L2 cache. Such duplicate L1 tags stored centrally in the L2 cache are typically used to construct partial sharing information, thereby reducing indirections to the coherence engine. Duplicate tag structures are also used to reduce redundant write-back traffic to L2 cache from multiple L1s that cache the same shared data. However, in CCN we replicate the tags adjacent to the corresponding L1 caches and do not complicate the L2 cache control. It is used only to prevent deterioration of L1 cache performance due to remote lookups. Moreover, tag updates to shadow tags incur minimum communication overhead in CCN due to physical proximity of L1 caches and shadow tags.

#### 7.4. Cache Management

In the field of GPUs, prior proposals such as Sharing Tracker [Tarjan and Skadron 2010] and cluster-based schemes [Keshtegar et al. 2015] (discussed previously in Section 6) exploit reuse within GPU cores via central directory and clustered caches respectively.

Several other schemes have been proposed for GPUs to improve the effective on-chip cache capacity, to reduce cache thrashing and to improve locality in L1 & L2 caches. Rhu et al. [2013] proposed a locality-aware memory hierarchy which adaptively adjusts the memory access granularity to prevent over-fetching, providing better off-chip bandwidth utilization. Furthermore to adaptive memory access granularity, Li et al. [2016] proposed a tag-split cache to enable fine storage granularity to improve cache utilization while keeping a coarse access granularity to avoid excessive cache requests. Tarjan et al. [2009] proposed a scheme to tolerate memory miss latencies for SIMD cores by masking out threads in a warp which are waiting on data and allowing other threads to continue execution, hence utilizing the idle execution slots. Rogers et al. [2012,2013] proposed scheduling techniques which are conscious of the variations in the cache locality thereby dynamically altering the scheduling policies to maximize inter-warp locality on the L1 data cache. Jia et al. [2012] present a taxonomy for memory access locality and propose a compile-time algorithm to selectively utilize the L1 caches. Narasiman et al. [2011] propose large warp architecture and a two-level warp scheduling technique to make effective use of resources on GPU while Jog et al. [2013] propose a thread block aware scheduling policy to improve the cache hit rates of L1 cache. Choi et al. [2012] employ techniques such as write buffering and read bypassing to reduce DRAM traffic and improve the L2 cache utilization, thereby addressing the bandwidth constraint between shared memory and DRAM. There has also been work on cache management policies for heterogeneous CPU-GPU architectures. Yang et al. [2012] proposed a CPU-assisted prefetching scheme to improve the GPU memory latencies by localizing the data in the LLC cache while Lee and Kim [2012] proposed a TLP-aware cache management policy to effectively utilize the LLC for general-purpose workloads.

Broadly, the above cache management proposals focus on reducing the miss rate of independent caches by improving cache utilization. However, in CCN, without reducing miss rate of independent L1s, we reduce the collective bandwidth demand of L1 on L2 by diverting some of the misses to remote L1s. Hence, the mentioned techniques that reduce the miss rate itself are orthogonal to our work. Given the severity of the memory bottleneck in GPUs (as indicated by the magnitude of PerfX in Table I), no technique alone solves the entire problem, and hence such orthogonal techniques can be used in conjunction with CCN.

# 7.5. Cache bypassing

In order to mitigate the severity of cache thrashing, several cache bypassing techniques have been proposed. In CPUs, Gaur *et al.*[2011] proposed a bypass policy to selectively fill the exclusive last-level cache with evicted cache blocks from the higher level. Further, Duong *et al.* [2012] proposed a policy to protect reusable cache lines from eviction with a dynamically computed Protected Distance, and bypass the miss requests upon lack of unprotected cache lines in a set.

In GPUs, high multithreading and low on-chip cache capacity per thread present additional challenges due to severe cache thrashing. Chen *et al.* [2014] proposed a dynamic cache management policy that combines L1 cache bypassing and throttling. In their proposed scheme, warp throttling prevents over-saturation of on-chip cache resources while cache bypassing prevents cache contention, requiring lower number of

39:22 S. Dublish et al.

warps to be throttled in comparison to standalone warp throttling schemes. Li *et al.* [2015] proposed a locality-driven cache bypassing scheme that uses reuse frequency in a decoupled and extended tag memory to allow allocation in the data memory for only those cache lines that exhibit high reuse.

In summary, the cache bypassing schemes in GPU improve cache utilization by preserving hot cache lines with high reuse in the the available on-chip caches and bypassing the streaming requests directly to the L2 cache. By preventing eviction of cache lines with high reuse, it helps in eliminating repeated reuse requests from the *same* L1 cache to the L2 cache. However, in our proposed technique, we eliminate the reuse requests from *different* L1 caches to the L2 cache. In other words, cache bypassing techniques reduce *intra-core* reuse requests that access the L2 cache, whereas our proposed technique reduces *inter-core* reuse requests that access the L2 cache. Therefore, we expect our proposal to be complimentary to cache bypassing techniques as both techniques help in reducing mutually exclusive set of requests to the L2 cache.

#### 8. CONCLUSION

In this paper, we discuss the inefficiencies in the management of L1 caches in GPUs. We show that as a consequence of high L1 miss rates, high traffic to L2 cache presents a bandwidth bottleneck between L1 and L2 resulting in high L2 access latencies. In memory-intensive applications, multithreading is unable to hide such high latencies, making it critical to performance.

We discover considerable potential for data reuse within the L1 caches. We exploit this opportunity to reduce the miss traffic to the L2 cache and thereby reduce the L2 cache bandwidth demand. Therefore, we present a Cooperative Caching Network which services the L1 load misses cooperatively via a lightweight ring network. We show that GPUs can tolerate reuse latencies gracefully up to 80 cycles and therefore, a ring topology appears to be a cost-effective solution, as it allows us to trade-off higher latencies for simplicity and short wires, i.e., lower power consumption and die-area cost. We also use shadow tag memory, adjacent to each L1 data cache, to decouple the local L1 cache performance from remote L1 cache tag lookups. For applications that do not exhibit any inter-core reuse, we detect the lack of sharing at runtime and prevent the L1 miss requests from incurring the CCN overhead, sending them directly to the L2 cache. For applications that exhibit reuse, our technique improves the IPC by 14.7% while being neutral to applications that show little or no reuse. We likewise reduce the traffic to L2 cache by 29%, and reduce the average memory latency by 24%. As a result, we reduce the total core stall cycles by 26%. Alongside the above improvements, CCN presents an area and energy overhead of 1.3% and 2.5% respectively. CCN also compares favourably with alternative techniques that address the bandwidth issue.

# **REFERENCES**

Manuel E. Acacio, José González, José M. García, and José Duato. 2002. Owner Prediction for Accelerating Cache-to-cache Transfer Misses in a cc-NUMA Architecture. In *Proceedings of the 2002 ACM/IEEE Conference on Supercomputing (SC '02)*. IEEE Computer Society Press, Los Alamitos, CA, USA, 1–12. http://dl.acm.org/citation.cfm?id=762761.762762

Jade Alglave, Mark Batty, Alastair F. Donaldson, Ganesh Gopalakrishnan, Jeroen Ketema, Daniel Poetzl, Tyler Sorensen, and John Wickerson. 2015. GPU Concurrency: Weak Behaviours and Programming Assumptions. In Proceedings of the Twentieth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '15). ACM, New York, NY, USA, 577–591. DOI: http://dx.doi.org/10.1145/2694344.2694391

Ali Bakhoda, George L. Yuan, Wilson W. L. Fung, Henry Wong, and Tor M. Aamodt. 2009. Analyzing CUDA workloads using a detailed GPU simulator.. In *ISPASS* (2009-05-26). IEEE, 163–174.

- L. A. Barroso, K. Gharachorloo, R. McNamara, A. Nowatzyk, S. Qadeer, B. Sano, S. Smith, R. Stets, and B. Verghese. 2000. Piranha: a scalable architecture based on single-chip multiprocessing. In Computer Architecture, 2000. Proceedings of the 27th International Symposium on. 282–293.

- Bradford M. Beckmann and David A. Wood. 2004. Managing Wire Delay in Large Chip-Multiprocessor Caches. In *Proceedings of the 37th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO 37)*. IEEE Computer Society, Washington, DC, USA, 319–330. DOI:http://dx.doi.org/10.1109/MICRO.2004.21

- Simone Campanoni, Kevin Brownell, Svilen Kanev, Timothy M. Jones, Gu-Yeon Wei, and David Brooks. 2014. HELIX-RC: An Architecture-compiler Co-design for Automatic Parallelization of Irregular Programs. In *Proceeding of the 41st Annual International Symposium on Computer Architecture (ISCA '14)*. IEEE Press, Piscataway, NJ, USA, 217–228. http://dl.acm.org/citation.cfm?id=2665671.2665705

- Jichuan Chang and Gurindar S. Sohi. 2006. Cooperative Caching for Chip Multiprocessors. In *Proceedings* of the 33rd Annual International Symposium on Computer Architecture (ISCA '06). IEEE Computer Society, Washington, DC, USA, 264–276. DOI: http://dx.doi.org/10.1109/ISCA.2006.17

- Jichuan Chang and Gurindar S. Sohi. 2007. Cooperative Cache Partitioning for Chip Multiprocessors. In *Proceedings of the 21st Annual International Conference on Supercomputing (ICS '07)*. ACM, New York, NY, USA, 242–252. DOI: http://dx.doi.org/10.1145/1274971.1275005

- Shuai Che, Michael Boyer, Jiayuan Meng, David Tarjan, Jeremy W. Sheaffer, Sang-Ha Lee, and Kevin Skadron. 2009. Rodinia: A Benchmark Suite for Heterogeneous Computing. In *Proceedings of the 2009 IEEE International Symposium on Workload Characterization (IISWC) (IISWC '09)*. IEEE Computer Society, Washington, DC, USA, 44–54. DOI: http://dx.doi.org/10.1109/IISWC.2009.5306797

- Shuai Che, Michael Boyer, Jiayuan Meng, David Tarjan, Jeremy W. Sheaffer, and Kevin Skadron. 2008. A Performance Study of General-purpose Applications on Graphics Processors Using CUDA. J. Parallel Distrib. Comput. 68, 10 (Oct. 2008), 1370–1380. DOI: http://dx.doi.org/10.1016/j.jpdc.2008.05.014