# Strathprints Institutional Repository

Darwish, Ahmed and Wang, Yachao and Holliday, Derrick and Finney, Stephen (2016) Operation and control design of new Three-Phase inverters with reduced number of switches. In: 2016 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM). IEEE, Piscataway. ISBN 9781509020683 , http://dx.doi.org/10.1109/SPEEDAM.2016.7525993

This version is available at http://strathprints.strath.ac.uk/59695/

**Strathprints** is designed to allow users to access the research output of the University of Strathclyde. Unless otherwise explicitly stated on the manuscript, Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Please check the manuscript for details of any other licences that may have been applied. You may not engage in further distribution of the material for any profitmaking activities or any commercial gain. You may freely distribute both the url (<u>http://strathprints.strath.ac.uk/</u>) and the content of this paper for research or private study, educational, or not-for-profit purposes without prior permission or charge.

Any correspondence concerning this service should be sent to Strathprints administrator: <a href="mailto:strathprints@strath.ac.uk">strathprints@strath.ac.uk</a>

# Operation and Control Design of New Three-phase and Single-phase DC/AC inverters with Reduced Number of Switches

Abstract—Inverters with reduced number of switches have been proposed in the literature to improve the capability of cost reduction, total inverters size and switching losses of dc/ac inverter topologies. In addition, they have a lower probability of damaging the semi-conductor switches as well as lower commonmode currents. This paper proposes new designs for inverters with reduced number of switches. For three-phase systems, the proposed inverters use four switches instead of six in the traditional three-phase Voltage Source Inverter (VSI). Compared to the traditional Four-switch three-phase (FSTP) inverter, the proposed FSTP inverters improve the voltage utilization factor of the input dc supply. Classical controllers as well as sliding mode controller are used to discuss the dynamic response and robustness of the inverters. In addition, the paper presents new single-phase inverters with two switches instead of four in the traditional VSI. The capability of suppressing the 2<sup>nd</sup> order current harmonic from the input dc side is discussed. Equations explaining the control design, switches ratings, and the operation of the proposed inverters are presented in this paper. The basic structure, control design, and MATLAB/SIMULINK results are presented. Practical results substantiate the design flexibility of the proposed topologies when controlled by a TMSF280335 DSP.

#### Keywords-component; dc/ac inverters; sliding mode controllers; PR controllers; Four-switch three-phase inverter (FSTP)

#### I. INTRODUCTION

The governmental agencies insistence to reduce the CO2 generation created an international interest in power system and micro-grid research and development [1]. Recently, numerous inverter topologies are presented to improve the operation of micro-grid systems.

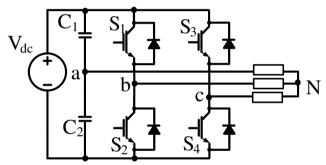

For a long period, the conventional six-switch three-phase (SSTP) two-level voltage source inverter (VSI) has been the most common converter topology for many applications such as renewable energy conversion systems, motor drives, and wind turbine systems. However, converter topologies with reduced switches number are demanded in some low power applications, such as photovoltaic, fuel cells and electric vehicles, in order to reduce the cost, size and increase the system's efficiency. A novel three-phase two-level VSI with only four switches was implemented in [2], see Fig.1. In this Four-switch three-phase (FSTP) inverter, two of the output load voltages are fed from the two legs of the inverters while the third phase is fed directly from the dc side.

In comparison with the conventional VSI, the FSTP inverter has important features such as lower cost, higher efficiency, reduced number of measurement boards, gate drives and the real-time calculations [3]. In addition, the FSTP

inverter reduces the maximum common mode voltage by 33% in comparison with the SSTP inverter [3, 4]. Because of the reduced interaction between the switches, the FSTP inverter decreases the probabilities of damaging the switches. The main disadvantage of the FSTP is that the maximum output voltage could be obtained across the load is limited to 28.28% of the input dc voltage [2]. Another disadvantage of the conventional FSTP is that the third phase of output load is fed from the dc side which may generate dc current components in the output three-phase currents. These dc current components are hazardous and a proper control effort should be conducted in order to suppress them. IEEE 1574 standards restrict the dc current components to < 0.5% of the rated RMS current while IEC 61727 standards limit them to <1%. In addition, the fluctuation of the dc-link capacitors at the fundamental frequency results in fluctuations of the output voltages and currents of the FSTP inverter [5]. The problem of dc-link voltage oscillation necessitates a modified pulse-width modulated (PWM) signals to control and create the desired output voltage during the switching period [3]. Practically, the dc-link split capacitors may not have exactly equal capacitance values. Consequently, over-modulation of switch PWM process may occur to keep the dc-link midpoint voltage constant [5]. The operation, control design, and performance of the FSTP have been discussed extensively in the literature [3]-[11]. In [12], a FSTP inverter based on the conventional SEPIC converter is implemented and controlled with sliding mode control. The reachable output voltage of the SEPICbased FSTP inverter has been shown to be double the voltage of the conventional FSTP inverter at the same conditions. In addition, the inverter solved the problem of the circulating current in the dc-link capacitors. However, like the conventional FSTP, the SEPIC-based inverter is fed from the input dc side directly and hence; dc currents components may be injected into the ac grid.

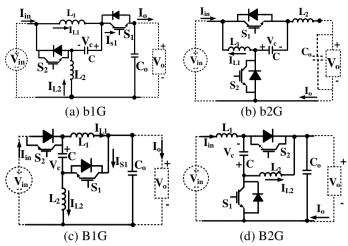

Out of the thirty three basic dc-dc converters, there are four bidirectional converters capable of providing output voltage with positive and negative polarities. These converters are shown in Fig.2 as two voltage buck and two voltage boost converters. Based on these converters, new three-phase inverters with four switches can be generated. Unlike the other FSTP inverters, the proposed inverters do not have direct connection between the ac phases and the dc side voltage. Consequently, the problem of dc currents injection in the ac grid does not exist. Moreover, because they do not require the direct connection between the ac and dc sides, the proposed converters can operate as dc/ac inverters and ac/dc rectifiers. In dc/ac inversion mode, the proposed inverters double the maximum output three-phase voltage in compare with the conventional FSTP inverter.

Unfortunately, the proposed converters are time variant systems where the overall transfer function describing the relation between the input and output voltages and currents depends on the switching periods of the switches. This results in a complex stable design because the converter poles and zeros travel through a long trajectory. Moreover, the timevarying transfer function leads to output voltage and current distortion [13, 14]. Converter stability and reliability decreases with increasing passive elements values. However, reducing the inductors and capacitors values results in larger high frequency ripple currents and voltages components and hence. increases the total harmonic distortion (THD) of the output current and voltage. On the other hand, increasing the passive elements values increases the stored energy inside the inverter producing third order harmonic component and its multiples in the input dc current.

This paper presents new inverter/rectifier topologies with reduced switches number based on the abovementioned bidirectional dc-dc converters. Moreover, the paper explains the normal operation and proposes beneficial comparisons and performance evaluation of the proposed inverters. In addition, the proper control design of the proposed converters is presented with sliding mode control techniques (SMC). Practical results substantiate the design flexibility of the proposed topologies when controlled by a TMSF280335 DSP.

Fig.1. Conventional Four-switch three-phase inverter (FSTP)

II. DC-DC CONVERTERS WITH POSITIVE AND NEGATIVE OUTPUT VOLTAGE

The four two-switch two-diode dc-dc converters with positive and negative output voltages are shown in Fig.2. Two of these converters are voltage buck converters (b1G and b2G) while the other two are voltage boost converters (B1G and B2G). The relation between output voltage ( $V_o$ ) and the input voltage ( $V_{in}$ ) is defined by voltage conversion ratio (M) as:

$$\mathbf{M}(\mathbf{D}) = \bigvee_{o} \bigvee_{in}$$

(1)

Where D is the converter duty ratio and can be defined as:

$$D = \frac{t_{on}}{t_s}$$

(2)

Where  $t_{on}$  is the duration when switch  $S_1$  is on while  $t_s$  is the total switching period.

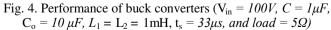

Fig.2. dc-dc converters with bidirectional output voltages: (a) and (b) voltage-buck converters, (c) and (d) voltage-boost converters.

The voltage conversion ratios of the converters can be expressed as:

$$M(D) = \frac{2D-1}{D} \quad \text{for b1G and b2G} \tag{3}$$

$$M(D) = \frac{1 - D}{1 - 2D} \quad \text{for B1G and B2G} \tag{4}$$

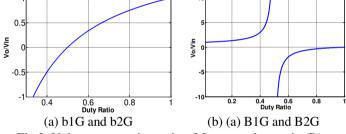

The voltage conversion ratios in equations (3) and (4) can be plotted against the duty ratio variation as shown in Fig.3

Fig.3. Voltage conversion ratios (M) versus duty ratio (D)

B1G and B2G have a discontinuous voltage ratio over the full operating range and cannot generate zero output voltage ( $V_o = 0$ ). However, b1G and b2G have continuous voltage ( $V_o/V_{in}$ ) versus the duty ratios.

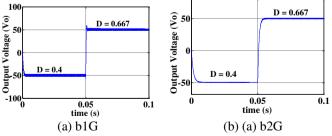

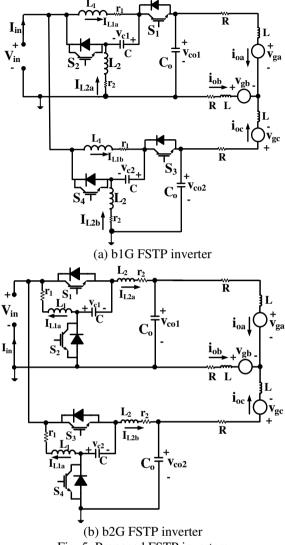

MATLAB simulation is shown in Fig. 4 at different duty ratios to show the buck converters, b1G and b2G, capabilities.

#### III. FOUR-SWITCH THREE-PHASE INVERTERS

Two converters can be connected deferentially across the three-phase load to form a FSTP inverter. The circuit diagrams of these inverters are shown in Fig. 5.

Fig. 5. Proposed FSTP inverters

Each converter produces sinusoidal voltage with peak  $V_{\!m}$  as follows:

$$v_{co1}(t) = V_{m} \sin(\alpha t + \theta)$$

$$v_{co2}(t) = V_{m} \sin(\alpha t + \theta + \frac{1}{3}\pi)$$

(5)

The output three-phase voltage can be expressed as:

$$v_{ga}(t) = V_g \sin \omega t$$

$$v_{gb}(t) = V_g \sin(\omega t - \frac{2}{3}\pi)$$

$$v_{gc}(t) = V_g \sin(\omega t + \frac{2}{3}\pi)$$

(6)

Where  $\omega = 2\pi f$  is the angular frequency. This causes the three-phase currents  $i_{oa}$ ,  $i_{ob}$  and  $i_{oc}$  to flow in the load as follows:

$$i_{oa}(t) = I_{o} \sin \omega t$$

$$i_{ob}(t) = I_{o} \sin(\omega t - \frac{2}{3}\pi)$$

$$i_{ab}(t) = I_{a} \sin(\omega t + \frac{2}{3}\pi)$$

$$(7)$$

Where:

$$\theta = \tan^{-1} \begin{cases} RI_{o} \left(\frac{3}{2}\sin(\gamma) + \sqrt{3}/2\cos(\gamma)\right) + \\ \frac{\omega LI_{o} \left(\frac{3}{2}\cos(\gamma) - \sqrt{3}/2\sin(\gamma)\right) + \sqrt{3}/2V_{g}}{RI_{o} \left(\sqrt{3}/2\cos(\gamma) - \sqrt{3}/2\sin(\gamma)\right) - \\ \omega LI_{o} \left(\sqrt{3}/2\sin(\gamma) + \sqrt{3}/2\cos(\gamma)\right) + \frac{3}{2}V_{g}} \end{cases}$$

(8)

$$RI_{o} \left(\frac{\sqrt{3}/2\cos(\gamma) - \sqrt{3}/2\sin(\gamma)}{2\cos(\gamma) - \sqrt{3}/2\sin(\gamma)}\right) - \\ \frac{\omega LI_{o} \left(\sqrt{3}/2\cos(\gamma) - \sqrt{3}/2\sin(\gamma)\right) - \\ \frac{\omega LI_{o} \left(\sqrt{3}/2\sin(\gamma) + \sqrt{3}/2\cos(\gamma)\right) + \frac{3}/2V_{g}}{\cos(\theta)} \end{cases}$$

(9)

The duty ratios of the converters  $\delta_1$  and  $\delta_2$  are calculated from (3) and (5) as:

$$\delta_{1}(t) = \frac{V_{in}}{2V_{in} - V_{co1}(t)}$$

$$\delta_{2}(t) = \frac{V_{in}}{2V_{in} - V_{co2}(t)}$$

(10)

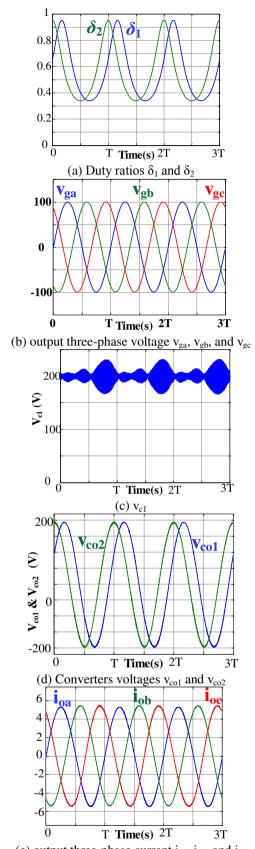

MATLAB simulations for the two converters open loop operations are shown in Fig. 6 and Fig. 7 using the components values in TABLE I.

TABLE I. PARASITIC COMPONENT VALUES AND CIRCUIT CONDITIONS

| f               | 50 Hz                      |

|-----------------|----------------------------|

| ts              | 33 µs                      |

| С               | 1 µF (b1G) and 5 µF (b2G)  |

| Co              | 20 µF (b1G) and 1 µF (b2G) |

| Lı              | 1 mH                       |

| $L_2$           | 1 mH                       |

| L               | 1 mH                       |

| R               | 0.5 Ω                      |

| $r_1$ and $r_2$ | 0.05 Ω                     |

| Vin             | 100 V                      |

To study the dynamics of the buck converters, each one can be modelled and represented in its state space average model as follows:

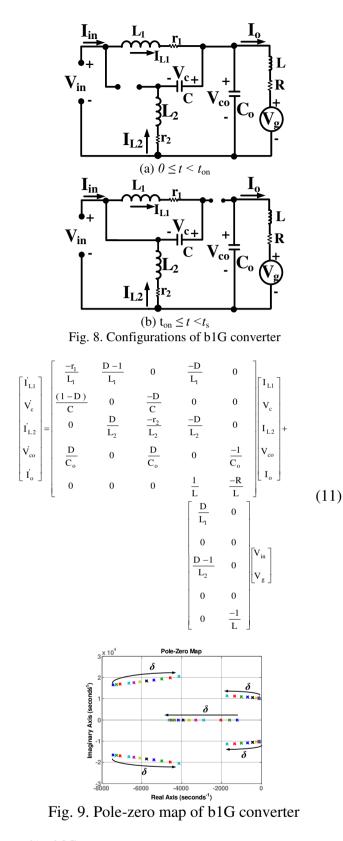

The circuit configurations of b1G converter are shown in Fig. 8, considering the inductors parasitic resistances  $(r_1, r_2)$  and the output inductance and resistance (L, R). The duration  $t_{on}$  defines the period that either S<sub>1</sub> or its anti-parallel diode are coducting. The average model of b1G is expressed in (11). The poles map of b1G converter in Fig. 9 shows that the dynamics of the converter is changing with the small-signal duty ratio  $\delta$ .

(e) output three-phase current  $i_{oa}$ ,  $i_{ob}$ , and  $i_{oc}$ Fig. 6. Output voltages and currents of b1G FSTP inverter

(e) output three-phase current  $i_{oa}$ ,  $i_{ob}$ , and  $i_{oc}$ Fig. 7. Output voltages and currents of b2G FSTP inverter

b) b2G

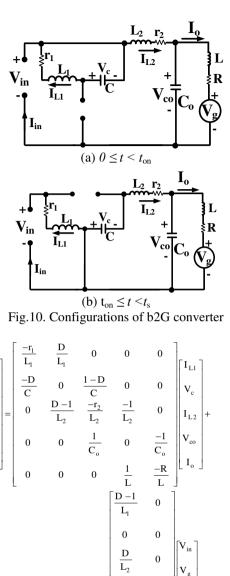

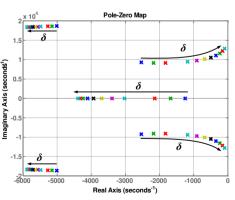

The circuit configurations of b2G converter are shown in Fig.10. The average model of b2G is expressed in (12). Based on the average model, the pole loci map is shown in Fig.11.

Same as b1G, the poles move along specified trajectories representing the non-linear natures of these converters.

Ι<sub>L1</sub>

v<sub>c</sub>

$\dot{I}_{L2}$

V<sub>co</sub>

İ.

0

0

0

$\frac{-1}{L}$

Fig.11. Pole-zero map of b2G converter

(12)

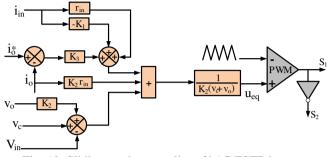

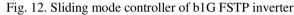

Because the proposed inverters are of high order systems, Variable Structure Control [15] (VSR) is an attractive solution. Sliding Mode Control (SMC) [15], which belongs to a family of VSR techniques, will be applied to the proposed inverters. The integral sliding mode controller for the proposed inverters is shown in Fig. 12.

Where  $r_1$  and  $r_2$  are the parasitic resistances of  $L_1$  and  $L_2$  respectively.  $K_1$ ,  $K_2$ ,  $K_3$  are the gain values of the controller.

#### IV. THREE-SWITCH BUCK-BOOST SINGLE-PHASE INVERTERS

From the previous discussion, b1G and b2G converters can provide sinusoidal output for each leg. Consequently, each leg can form a single-phase inverter with two switches instead of four switches in the traditional voltage source inverter. However, the single-phase inverter suffers from 2<sup>nd</sup> order harmonic current component in the input side which creates higher current stresses, and hence higher power losses, as well as problems for the Maximum Power Point Tracking (MPPT) system if the inverter is implemented with PV systems. This can be solved if a boost converter is implemented with b1G and b2G resulting in a three-switch single-phase inverter as shown in Fig. 13. This inverter has important advantages as:

- Reduced power loss as one switch and one diode are removed

- Ability for 2<sup>nd</sup> order harmonic current decoupling

- Buck-boost voltage transfer function: this is an important feature when the inverter is implemented with PV systems where the input voltage might be lower or greater than the grid voltage.

Fig. 13. Buck-boost single-phase b2G inverter

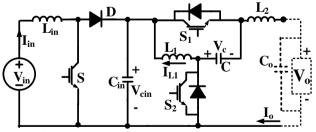

MATLAB simulation results in Fig. 14 show the closed loop operation when it is required to boost the input voltage  $(V_{in})$  from 100V to a sinusoidal output voltage  $(V_o)$  of 150V peak. The input current  $I_{in}$  is kept constant while the 2<sup>nd</sup> order power

component is decoupled by the capacitor  $C_{in}$ . ( $C_{in} = 200 \mu F$  and  $Z = 20\Omega$ )

Fig. 14. Simulation results of the inverter in Fig. 13.

An important feature of the proposed inverters in Fig. 13 is that the input current  $I_{in}$  is continuous due to the existence of an input inductor in the dc side. This mitigates the need for input electrolytic dc capacitor across the dc input side. Mitigating the electrolytic capacitors increases the reliability of the inverter to great extent [16].

#### V. EXPERIMENTAL RESULTS

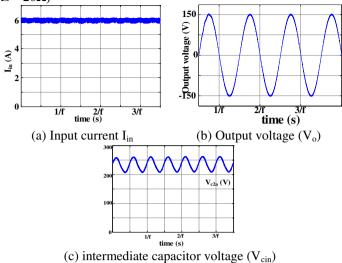

The system concept, presented mathematical analysis and simulations are validated with b1G FSTP inverter using the parameters in Table I and controlled using a TMS320F280335 DSP. The DC input voltage ( $V_{in}$ ) is fed from Sorensen SG A250X-10kW DC power supply. Four IRFPS40N60K MOSFET switches have been employed for the switches  $S_{1,4}$  with their freewheel diodes.  $D_{1,4}$ . Clairtronic CMV-28F3, 0-415 V, 3–ph, auto-transformer is used to match the ac voltage grid. Fig. 15 shows the voltages and the currents of the proposed inverter.

## VI. CONCLUSION

New dc-ac three-phase inverters with reduced number of switches are proposed in this paper. Reducing the switches number improves the efficiency and the reliability of the dc-ac inverters. The proposed three-phase inverters have greater maximum output peak voltages than the conventional FSTP. Unlike the conventional FSTP, the proposed inverters do not have dc bias in the converters' output voltages. However, the proposed inverters are high order systems where the poles of their transfer functions move with duty ratios variation. Consequently, the classical control strategies are not easy to be implemented. Sliding mode controllers for these inverters are proposed in order to generate pure sinusoidal voltages and currents. The paper presented as well new single-phase dc-ac inverter topologies with the ability to decouple the 2<sup>nd</sup> order harmonic components from the input dc side.

### REFERENCES

- Y. Xue, J. Deng, and S. Ma, "Power flow control of a distributed generation unit in micro-grid," in Proc. IEEE Int. Power Electron. Motion Control Conf., 2009, pp. 2122–2125

- [2] H. Broeck and J. D. V. Wyk, "A comparative investigation of a threephase induction machine drive with a component minimized voltage-fed inverter under different control options," IEEE Trans. Ind.

- [3] M. B. de R. Correa, C. B. Jacobina, E. R. C. da Silva, and A. M. N. Lima, "A general PWM strategy for four-switch three-phase inverters," IEEE Trans. Power Electron., vol. 21, no. 6, pp. 1618–1627, Nov. 2006.

- [4] El Badsi, B., Bouzidi, B., and Masmoudi, A., "DTC scheme for a fourswitch inverter-fed induction motor emulating the six-switch inverter operation," IEEE Trans. Power Electron., Vol. 28, No. 7, pp. 3528– 3538, July 2013.

- [5] S. Dasgupta, S. N. Mohan, S. K. Sahoo, and S. K. Panda, "Application of four-switch-based three-phase grid-connected inverter to connect renewable energy source to a generalized unbalanced microgrid system," IEEE Trans. Ind. Electron., vol. 60, no. 3, pp. 1204–1215, Mar. 2013.

- [6] C.-T. Lin, C.-W. Hung, and C.-W. Liu, "Position sensorless control for four-switch three-phase brushless DC motor drives," IEEE Trans. Power Electron., vol. 23, no. 1, pp. 438–444, Jan. 2008.

- [7] M. K. Metwally, and H. Z. Azazi, "Four-switch Three-phase Inverter Performance Fed Sensorless Speed Control Induction Motor Drives Using Model Reference Adaptive System", Electric Power Components and Systems, vol.42, no.7, 2014

- [8] X. Tan, Q. Li, H. Wang, L. Cao, and S. Han, "Variable parameter pulse width modulation-based current tracking technology applied to fourswitch three-phase shunt active power filter," IET Power Electron., vol. 6, no. 3, pp. 543–553, Mar. 2013.

- [9] S. B. Ozturk, W. C. Alexander, and H. A. Toliyat, "Direct torque control of four-switch brushless DC motor with non-sinusoidal back EMF," IEEE Trans. Power Electron., vol. 25, no. 2, pp. 263–271, Feb. 2010.

- [10] K. D. Hoang, Z. Q. Zhu, and M. P. Foster, "Influence and compensation of inverter voltage drop in direct torque-controlled four-switch threephase PM brushless AC drives," IEEE Trans. Power Electron., vol. 26, no. 8, pp. 2343–2357, Aug. 2011.

- [11] T.-S. Lee and J.-H. Liu, "Modeling and control of a three-phase fourswitch PWM voltage-source rectifier in d-q synchronous frame," IEEE Trans. Power Electron., vol. 26, no. 9, pp. 2476–2489, Sep. 2011.

- [12] M. S. Diab, A. Elserougi, A. M. Massoud, A. S. Abdel-Khalik, and S. Ahmed, "A Four-Switch Three-Phase SEPIC-Based Inverter", IEEE Trans. On Power Electron., vol.30, no.9, pp.4891-4905, Sept 2015

- [13] A. Darwish, D. Holliday, S. Ahmed, A. M. Massoud, and B. W. Williams, "A Single-Stage Three-Phase Inverter Based on Cuk Converters for PV Applications," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 2, pp. 797-807, 2014.

- [14] P. R. Prasanna and A. K. Rathore, "Analysis, Design, and Experimental Results of a Novel Soft-Switching Snubberless Current-Fed Half-Bridge Front-End Converter-Based PV Inverter," IEEE Transactions on Power Electronics, vol. 28, pp. 3219-3230, 2013.

- [15] V. Utkin, J. Guldner, and J. X. Shi, Sliding Mode Control in Electromechanical Systems. London, U.K.: Taylor and Francis, 1999

- [16] J. Knight, S. Shirsavar, and W. Holderbaum, "An improved reliability Cuk based solar inverter with sliding mode control," ' IEEE Trans. Power Electron., vol. 21, no. 4, pp. 1107–1115, Jul. 2006.