## Near Infra-red single-photon detection using Ge-on-Si heterostructures

**Giuseppe Intermite**

Submitted for the Degree of Doctor of Philosophy

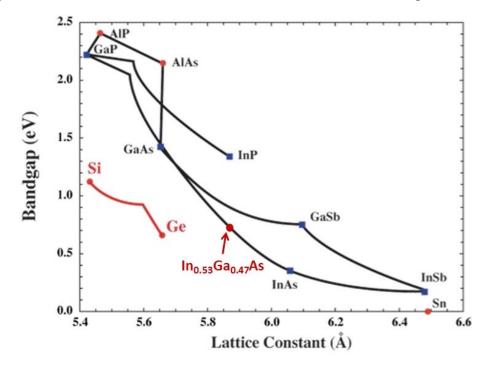

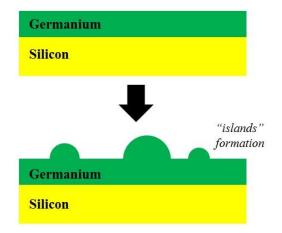

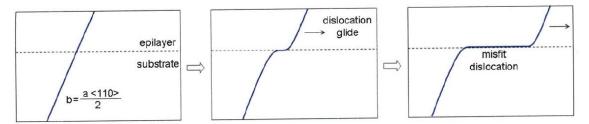

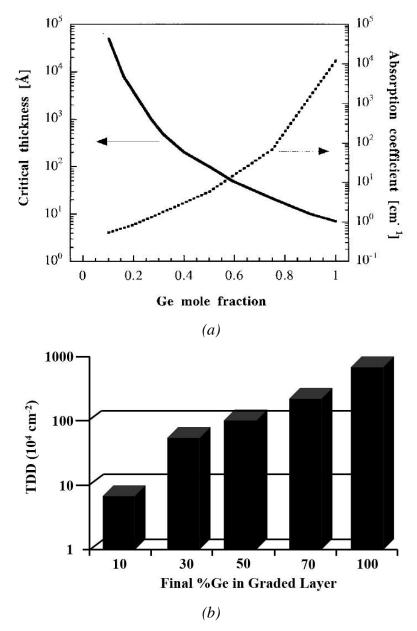

Heriot-Watt University

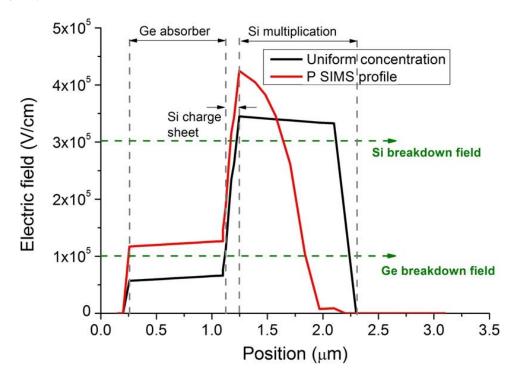

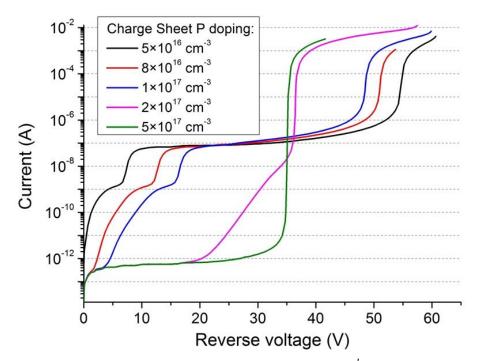

School of Engineering and Physical Science

July 2015

The copyright in this thesis is owned by the author. Any quotation from the thesis or use of any of the information contained in it must acknowledge this thesis as the source of the quotation or information.

## Abstract

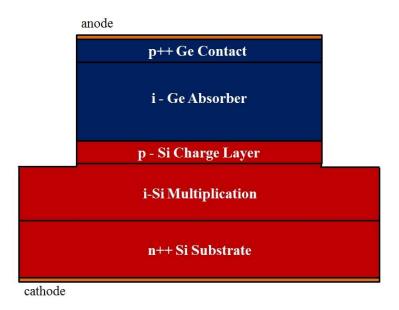

This Thesis investigates the design of Ge-on-Si single-photon avalanche diode (SPAD) detectors combining the many advantages of low-noise Si single-photon avalanche multiplication with the infrared sensing capability of germanium. The devices were simulated by using electric field modelling software to predict key aspects of the device behaviour in terms of the current-voltage characteristic and electric field.

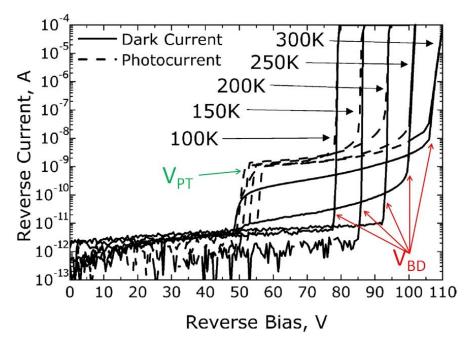

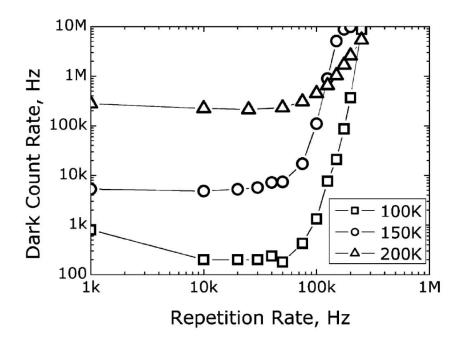

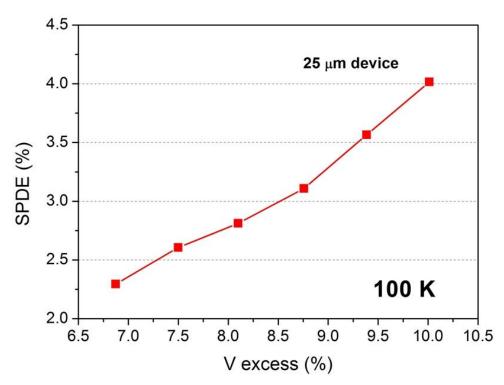

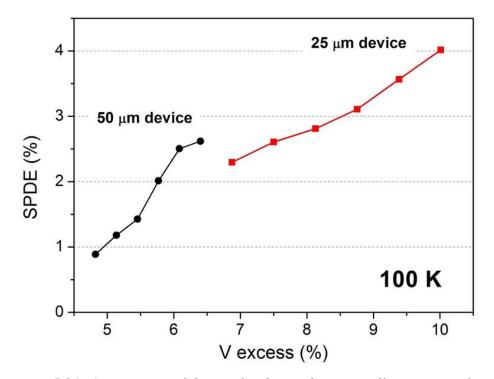

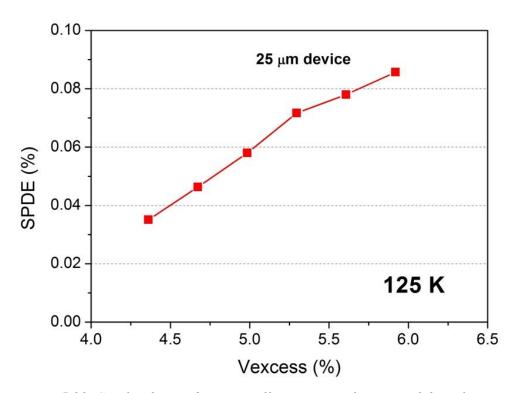

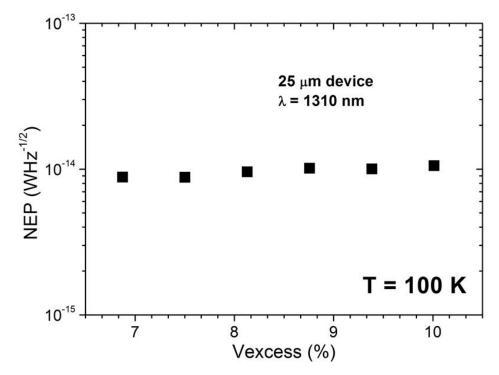

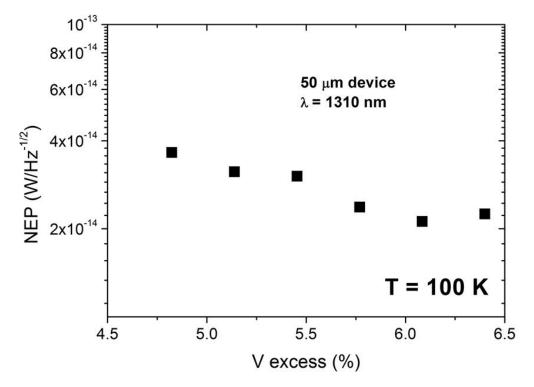

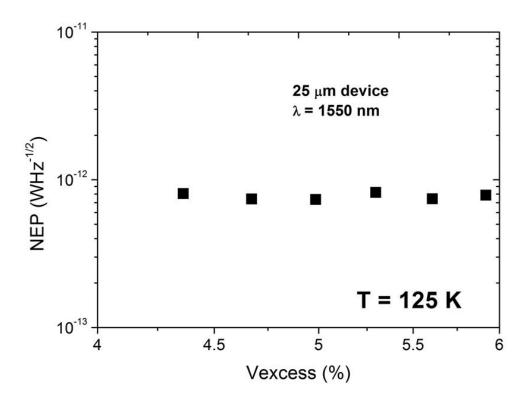

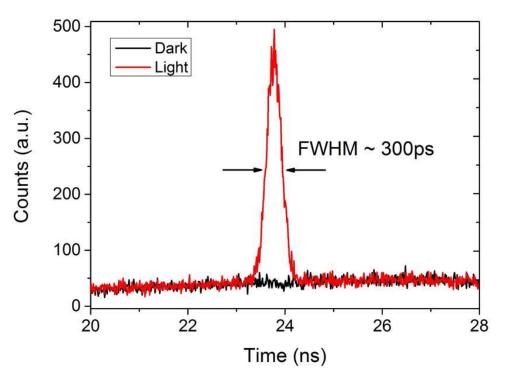

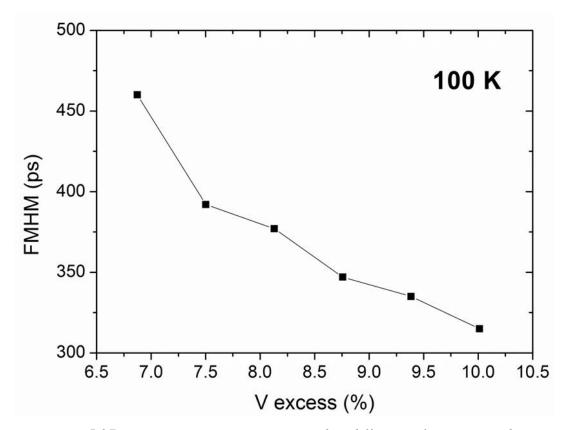

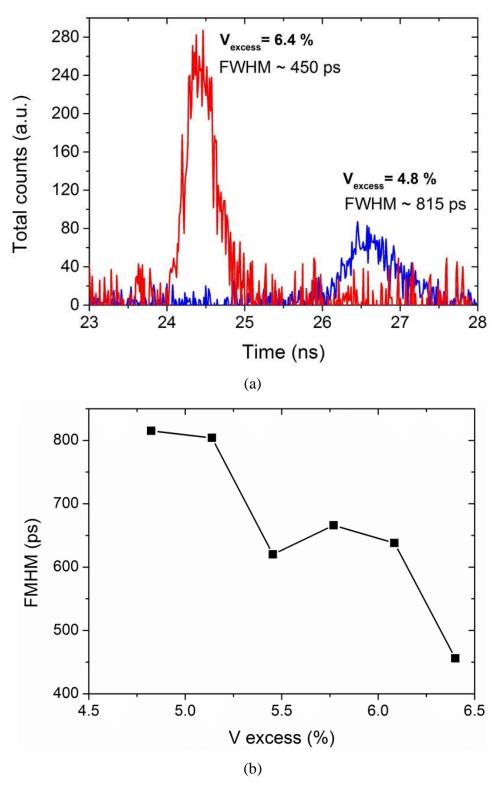

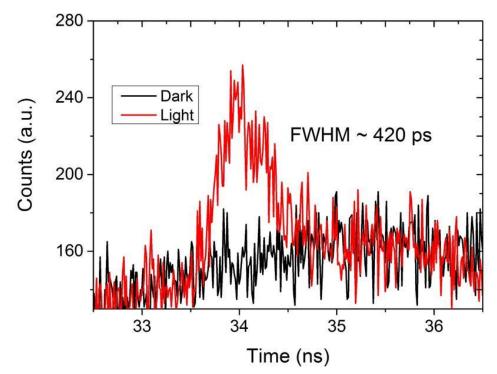

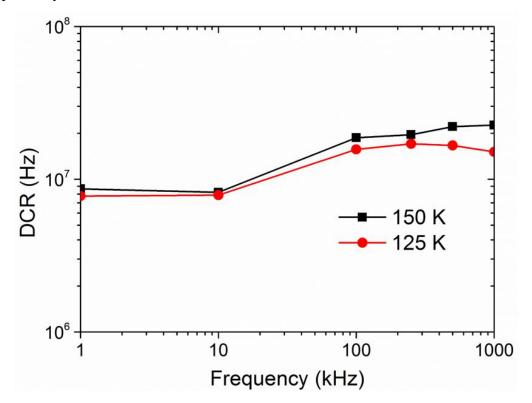

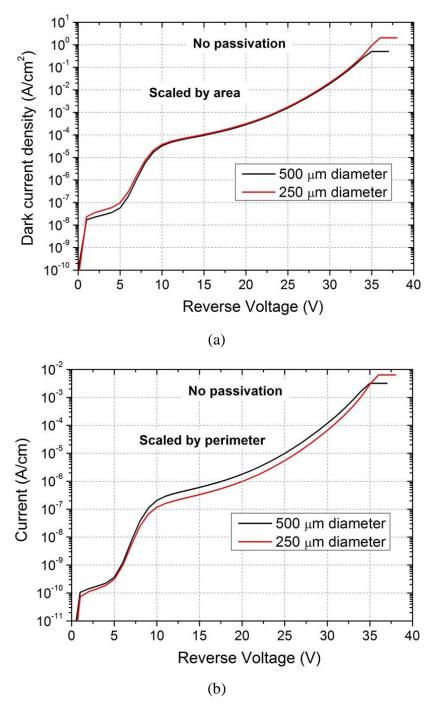

The devices were then characterised in terms of their single-photon performance. A 25  $\mu$ m diameter device showed a single-photon detection efficiency of ~ 4 % at a wavelength of 1310 nm and a temperature of 100 K when biased at 10 % above the breakdown voltage. In the same condition, a dark count rate of ~ 6 Mcs<sup>-1</sup> was measured. This resulted in the lowest noise equivalent power of ~ 1 × 10<sup>-14</sup> WHz<sup>-1/2</sup> of Ge-on-Si SPADs reported in the scientific literature. At the longer wavelength of 1550 nm, the single-photon detection efficiency was reduced to ~ 0.1 % at 125 K and 6 % of relative excess bias. Although further investigation needs to be carried out, a potential major advantage of these devices compared to the InGaAs/InP SPADs could be that of reduced afterpulsing since a small increase (a factor of 2) in the normalised dark count rate was measured when the repetition rate was increased from 1 kHz to 1 MHz.

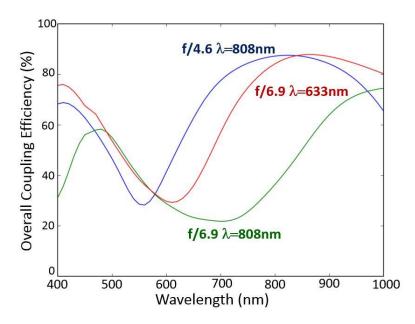

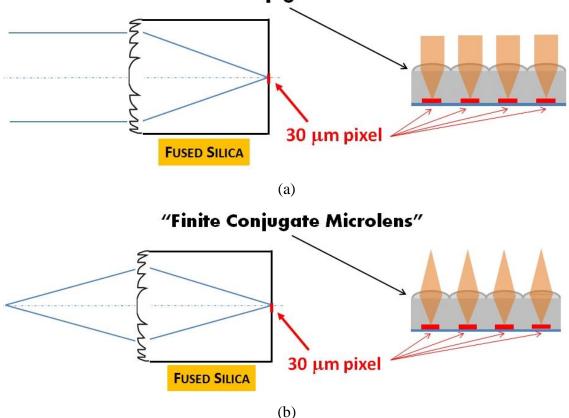

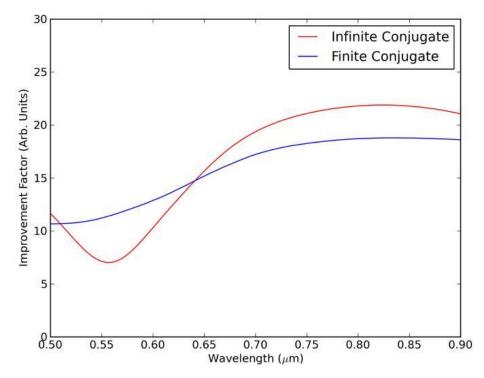

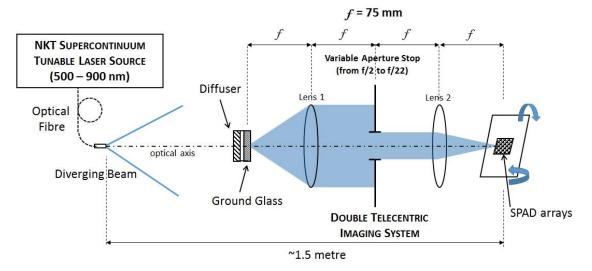

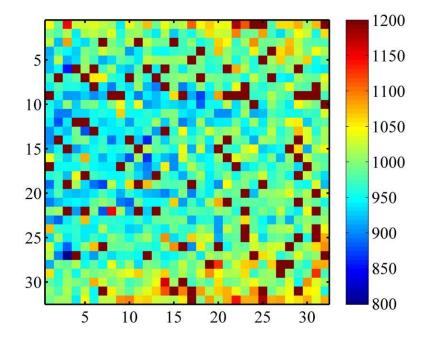

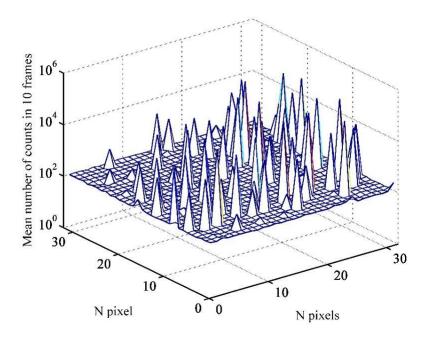

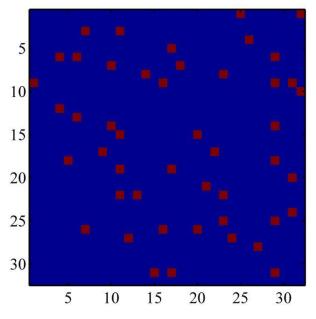

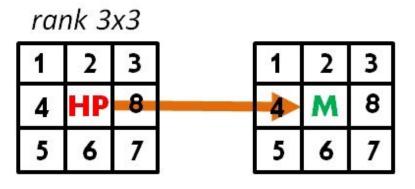

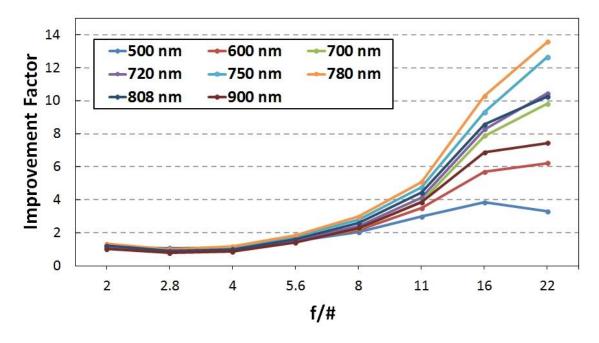

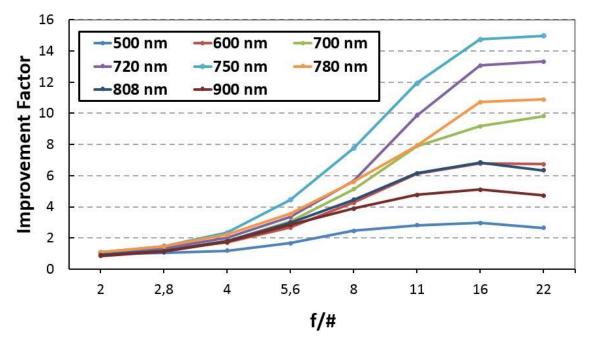

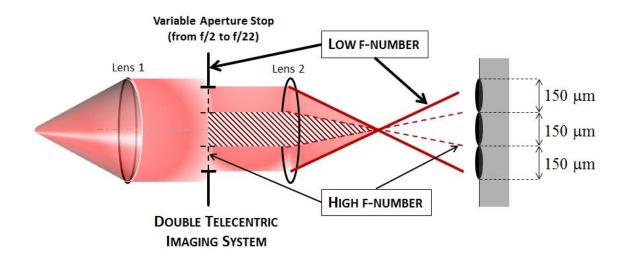

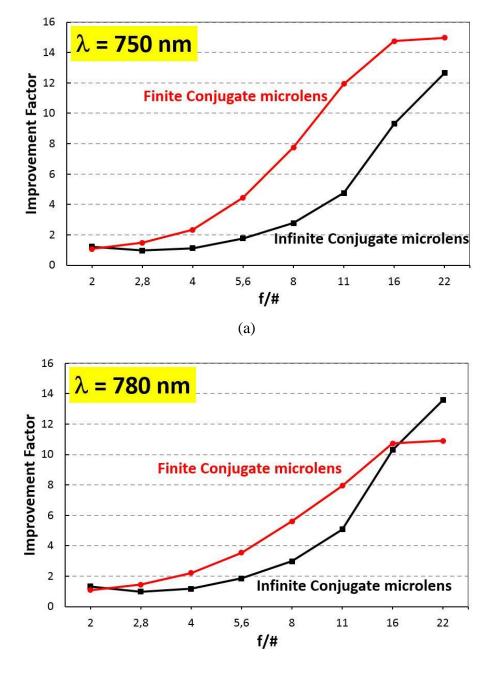

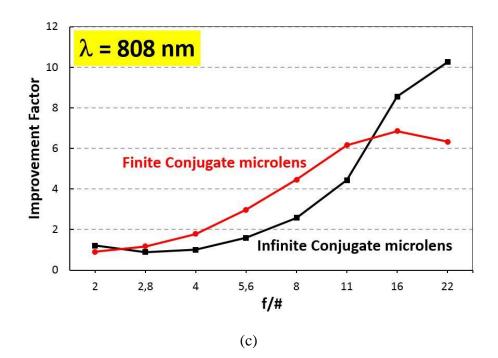

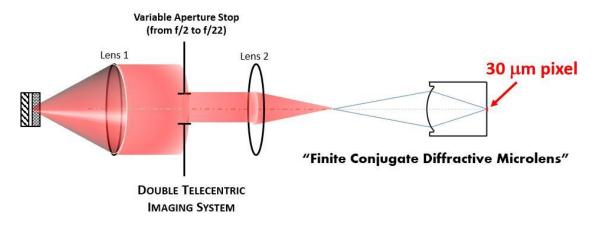

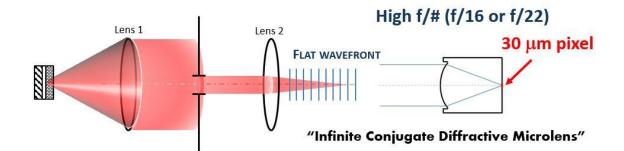

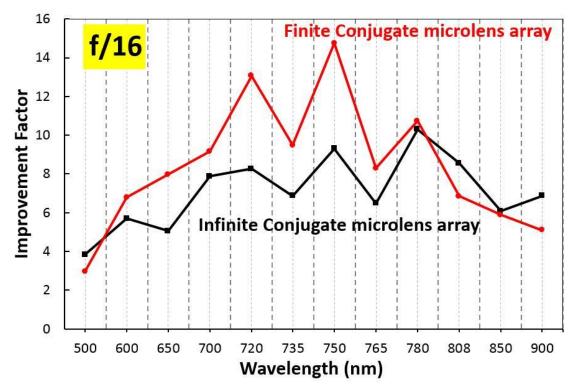

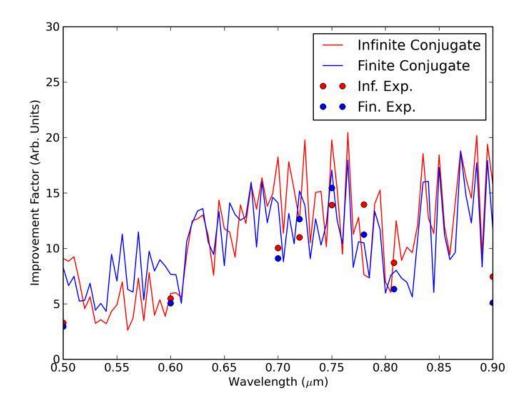

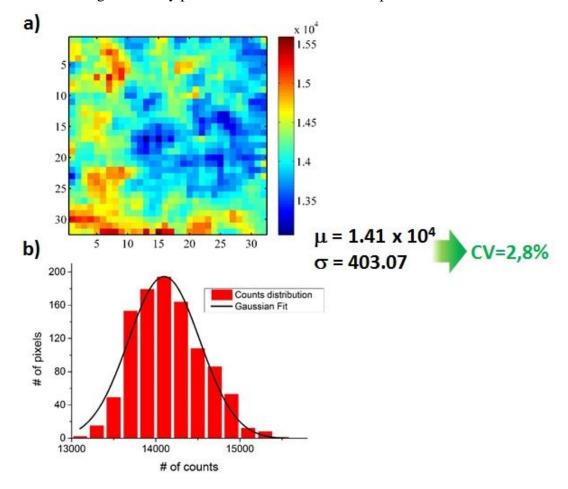

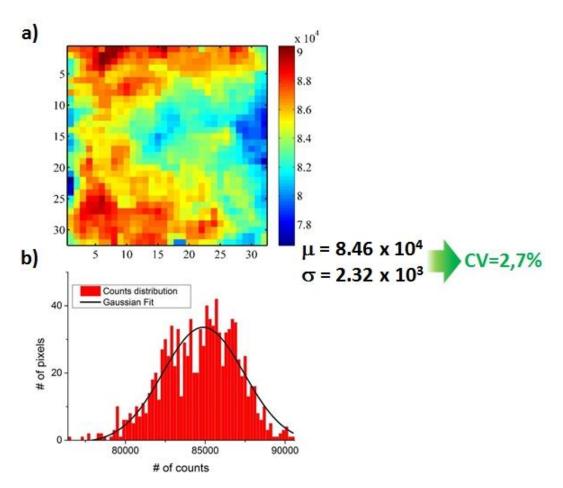

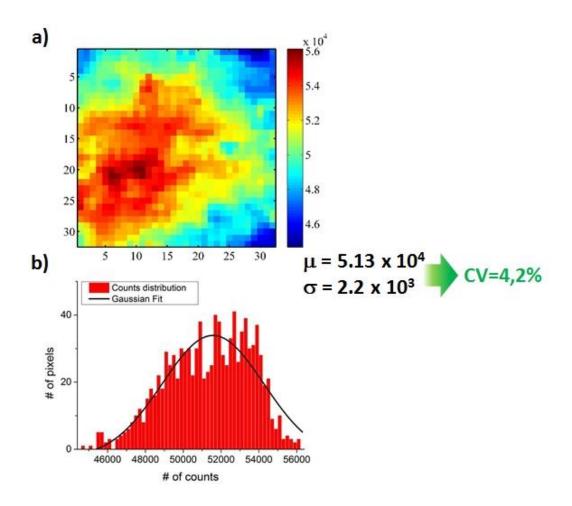

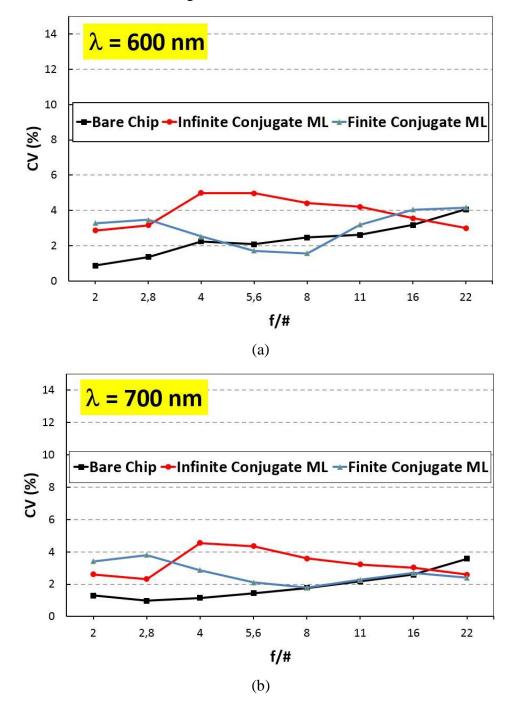

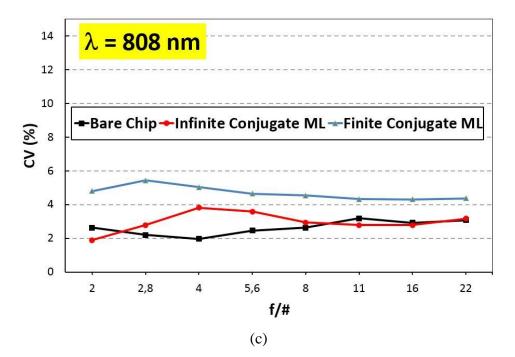

Finally, the fill-factor enhancement of  $32 \times 32$  Si CMOS SPAD arrays resulting from the integration of high efficiency diffractive optical microlens arrays was investigated. A full characterisation of SPAD arrays integrating microlens arrays in terms of improvement factor and spatial uniformity of detection is presented for the first time in the scientific literature in a large spectral range (500-900 nm) and different f-numbers (from f/2 to f/22) by using a double telecentric imaging system. The highest improvement factor of ~16 was measured for a SPAD array integrating microlens arrays, combined with a very high spatial efficiency uniformity of between 2–6%.

## Acknowledgements

One of the things that fascinating me about nature is, in general, its property of resilience. Because of this intrinsically positive property, the world around us evolves, changes, adapts and stands up. When I think to a single word that could fully describe my PhD, I then believe that "resilience" is the right one. It was the need of change that push me to start this wonderful but difficult, challenging but unpredictable experience. This thesis represents a scanning of my life in the recent years, and every chapter encodes a photograph of it which brought me to the beginning of a new growth. This was made possible thanks to the many people that I met during my way, and to which I will be forever grateful.

Firstly, my biggest thanks go to my supervisor Prof. Gerald S. Buller who believed in me from our first meeting and represented a reference point during the whole PhD. Thanks to him I had the opportunity to start this wonderful experience. Thanks for your support, guidance, persistence and for putting me on the right path when problems were behind the door.

A special thank goes to Dr. Ryan E. Warburton that guides me through the lab with a lot of patience. Thanks for your assistance, support and friendship. Thanks to Dr Peter Vines for his help, suggestion and patience. A big thanks goes to Dr. Aongus McCarthy, his passion for physics and his fairness let me understand which kind of scientist I would like to become in the future. A special thank goes to the rest of the Photon Counting group members present and past for many helpful discussion inside and outside the lab: Dr. Robert J. Collins, Aurora Maccarone, Nathan Gemmell, Ross J. Donaldson, Silvia Butera, Ximing Ren, Agata Pawlikowska, Kateryna Kuzmenko, Patrick J Clarke, Frauke Izdebsky and Dr. Nils Krichel.

Thanks also go out to the various collaborators with whom I have worked: Prof. Douglas J. Paul, Dr. Kevin Gallagher, and Ross J. Millar from the University of Glasgow, Dr Maksym Myronov and Phil Allred from the University of Warwick, Prof. Robert W. Kelsall from University of Leeds, Dr. Andrew Knights from McMaster University.

I would like to express my thanks to our collaborators at Politecnico di Milano, Prof. Franco Zappa and Dr. Federica Villa, for the Si CMOS SPAD arrays which were used for the work within Chapter 6 and for guidance on the operation of SPAD sensors. I would also like to express my thanks to Dr. Andrew Waddie for the microlens arrays design and simulations, then to my colleagues Dr. Aongus McCarthy and Ximing Ren for the flip-chip bonding and post-bonding inspection of the microlens arrays

I want to thanks all my friends, but in particular Ehsan and Harry for all the unforgettable moments spent together.

Last but not least, a heartfelt thanks goes to my wife, Francesca. She has been the light, the strength, the passion, the kindness that pushes me towards my objectives. Wherever we will go, whatever will happen, I know for sure that we will be always together.

Finally, I want to thanks my family. Although, we did not meet often in the last few years, their support, encouragement, love has also been deep in my heart and memory.

# ACADEMIC REGISTRY Research Thesis Submission

| Name:                                         | Giuseppe Intermite                |                                                     |              |

|-----------------------------------------------|-----------------------------------|-----------------------------------------------------|--------------|

| School/PGI:                                   | Engineering and Physical Sciences |                                                     |              |

| Version: (i.e. First,<br>Resubmission, Final) | Final                             | Degree Sought<br>(Award <b>and</b><br>Subject area) | PhD, Physics |

## **Declaration**

In accordance with the appropriate regulations I hereby submit my thesis and I declare that:

- 1) the thesis embodies the results of my own work and has been composed by myself

- 2) where appropriate, I have made acknowledgement of the work of others and have made reference to work carried out in collaboration with other persons

- 3) the thesis is the correct version of the thesis for submission and is the same version as any electronic versions submitted\*.

- 4) my thesis for the award referred to, deposited in the Heriot-Watt University Library, should be made available for loan or photocopying and be available via the Institutional Repository, subject to such conditions as the Librarian may require

- 5) I understand that as a student of the University I am required to abide by the Regulations of the University and to conform to its discipline.

- \* Please note that it is the responsibility of the candidate to ensure that the correct version of the thesis is submitted.

| Signature of Candidate: | Date: |  |

|-------------------------|-------|--|

|-------------------------|-------|--|

## **Submission**

| Submitted By (name in capitals):    | Giuseppe Intermite |

|-------------------------------------|--------------------|

| Signature of Individual Submitting: |                    |

| Date Submitted:                     |                    |

## For Completion in the Student Service Centre (SSC)

| Received in the SSC by (name in capitals):                                            |       |  |

|---------------------------------------------------------------------------------------|-------|--|

| Method of Submission<br>(Handed in to SSC; posted through<br>internal/external mail): |       |  |

| E-thesis Submitted (mandatory for final theses)                                       |       |  |

| Signature:                                                                            | Date: |  |

# **Table of Contents**

| Chapte         | r 1 – Introduction                                                 | 1         |

|----------------|--------------------------------------------------------------------|-----------|

| 1.1            | Reference                                                          | 6         |

| Chapte         | r 2 – Physics of photodiodes                                       | 8         |

| 2.1            | Introduction                                                       | 8         |

| 2.2            | Physics of p-n and p-i-n photodiodes                               | 8         |

| 2.3            | Avalanche photodiodes                                              | 16        |

| 2.3.1          | -                                                                  |           |

| 2.4            | Single-photon detectors                                            |           |

| 2.4.1          |                                                                    |           |

| 2.4.2          | The single-photon avalanche diode (SPAD)                           |           |

| 2.4            | 4.2.1 Figures of merit of a SPAD                                   |           |

| 2.4            | 4.2.2 Quenching techniques for SPADs                               |           |

| 2.5            | Conclusion                                                         |           |

| 2.6            | Reference                                                          |           |

| Chapte         | r 3 - Ge-on-Si Technology and Applications: Material selection, I  | Epitaxial |

| Growth         | and Review of Detectors                                            |           |

| 3.1            | Introduction                                                       |           |

| 3.2            | Choice of material for near-infrared photodetectors on Si          |           |

| 3.3            | Lattice mismatched near-infrared photodetectors on Si              | 42        |

| 3.3.1          | $Si_{1-x}Ge_x$ strained layer                                      |           |

| 3.3.2          | SiGeC structures                                                   |           |

| 3.3.3          | InGaAs structures                                                  |           |

| 3.3.4          | Pure Ge                                                            |           |

| 3.4            | Growth techniques for pure Ge-on-Si                                | 58        |

| 3.4.1          | Ge-on-Si heteroepitaxy                                             |           |

| 3.4            | 4.1.1 Two-temperature LT/HT Ge growth and cyclic thermal annealing |           |

|                | 4.1.2 Selective epitaxial growth of Ge-on-Si                       |           |

| 3.4.2          |                                                                    |           |

| 3.4.3          | J                                                                  |           |

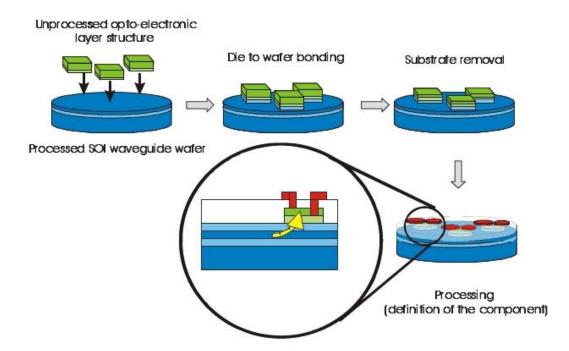

| 3.5            | Ge-on-Si by wafer bonding                                          |           |

| 3.6            | Ge-on-Si NIR photodetectors                                        |           |

| 3.6.1          |                                                                    |           |

| 3.6.2          |                                                                    |           |

| 3.6.3<br>3.6.4 |                                                                    |           |

| 3.6.5          |                                                                    |           |

| 3.6.6          |                                                                    |           |

| 3.7            | Conclusion                                                         |           |

| 3.8            | Reference                                                          |           |

| 2.0            |                                                                    |           |

| -             | r 4 - Ge-on-Si SACM structure: Design, modelling and SIMS<br>ements                | 121        |

|---------------|------------------------------------------------------------------------------------|------------|

| 4.1           | Introduction                                                                       |            |

| 4.1           |                                                                                    |            |

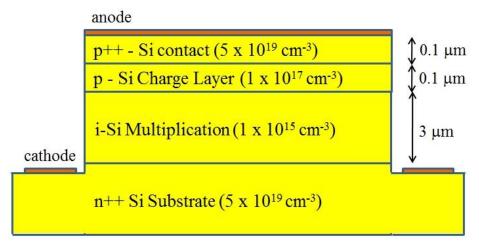

|               | Design of a Separate Absorption, Charge and Multiplication Ge-on-S<br>ure          |            |

| 4.3           | Ge-on-Si SPAD structure                                                            |            |

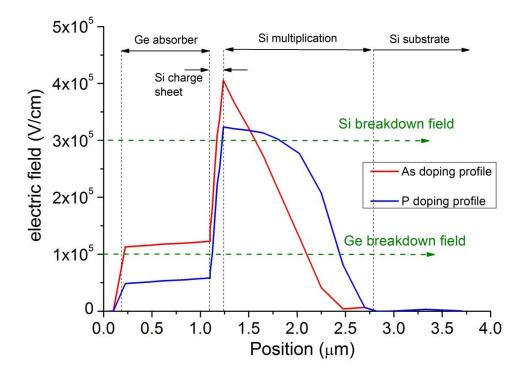

| 4.4           | Modelling of the Ge-on-Si hetero-structure                                         |            |

| 4.5           | Effect of temperature on the breakdown voltage                                     |            |

|               |                                                                                    |            |

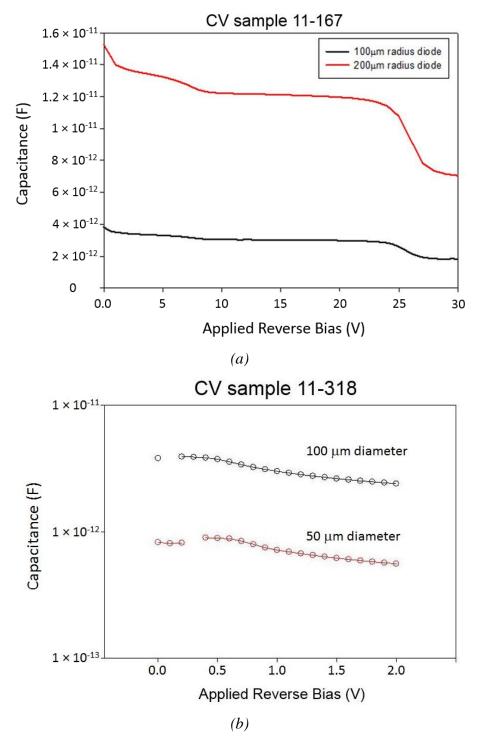

| 4.6<br>struct | Capacitance-Voltage Measurements on the 1 <sup>st</sup> generation of Ge-on-S ures |            |

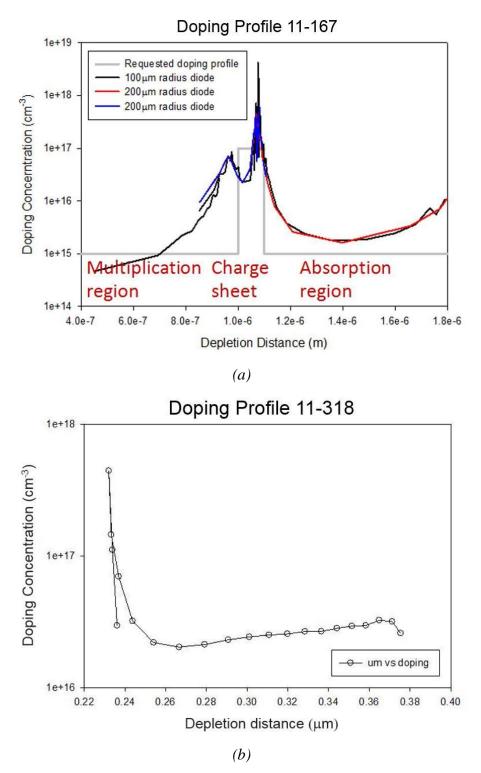

| 4.7           | Impact of the Ge absorber layer doping on the SPAD structure                       |            |

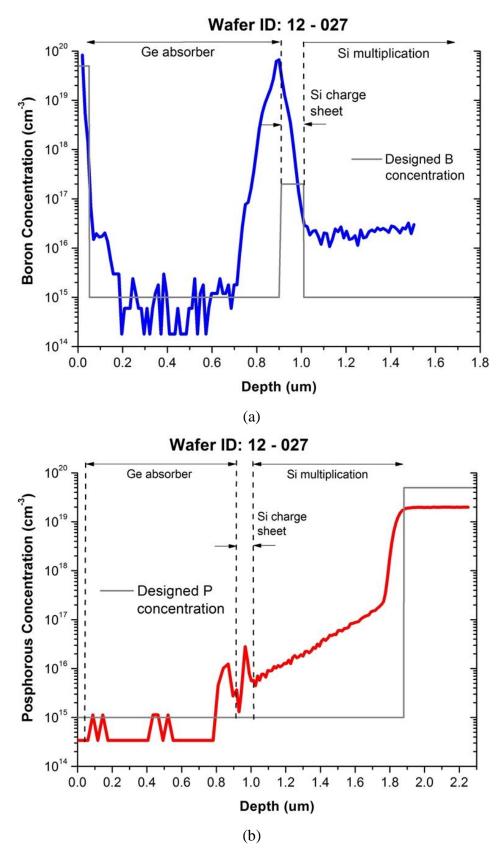

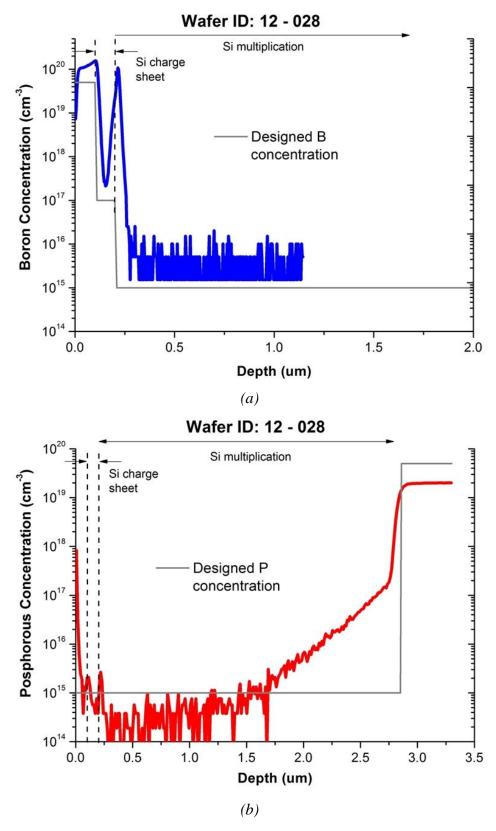

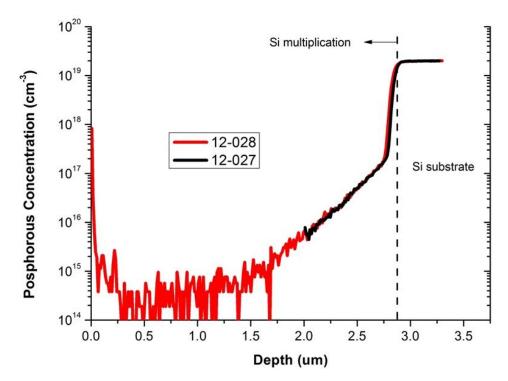

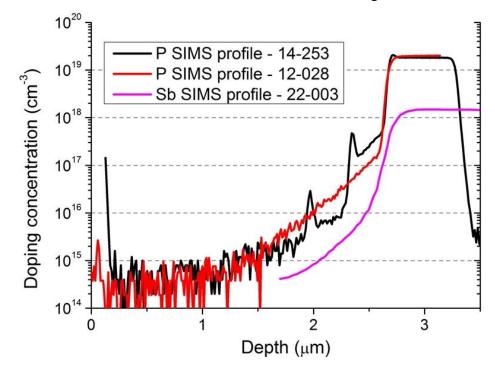

| 4.8           | SIMS measurements on the $2^{nd}$ generation of SPAD structure                     |            |

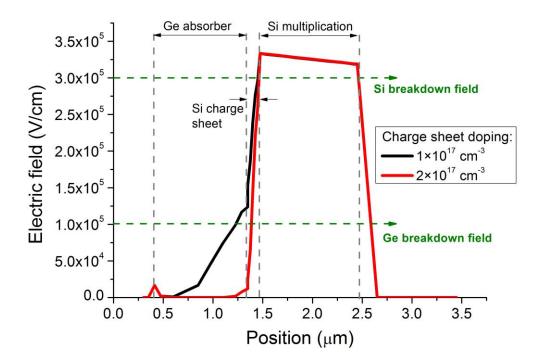

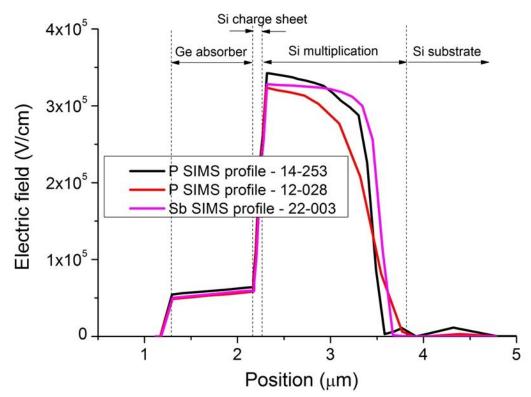

| 4.9           | Impact of the Si charge sheet and multiplication layer doping profile              |            |

|               | ) structure                                                                        |            |

| 4.10          | 3 <sup>rd</sup> Generation of Ge-on-Si SPAD structure: SIMS measurements and       | l          |

| mode          | lling                                                                              |            |

| 4.11          | Future development                                                                 | 161        |

| 4.12          | Conclusion                                                                         | 164        |

| 4.13          | Reference                                                                          | 165        |

| Chapte        | r 5 - Ge-on-Si Single-Photon Avalanche Diodes: Device fabrication                  | l <b>,</b> |

| Charac        | terisation and Performance                                                         | 167        |

| 5.1           | Introduction                                                                       | 167        |

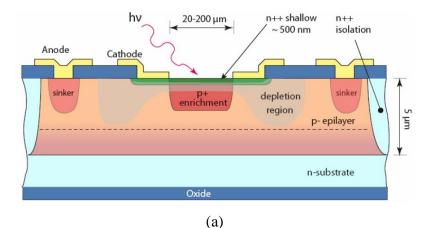

| 5.2           | Ge-on-Si SPAD growth                                                               | 168        |

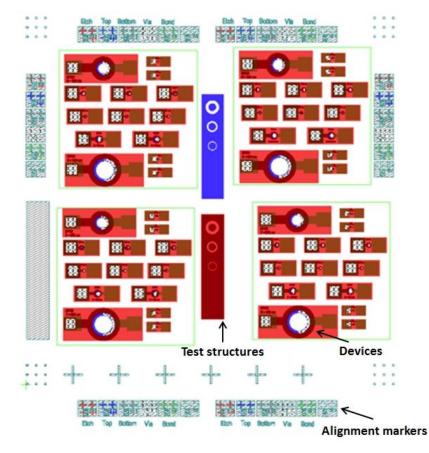

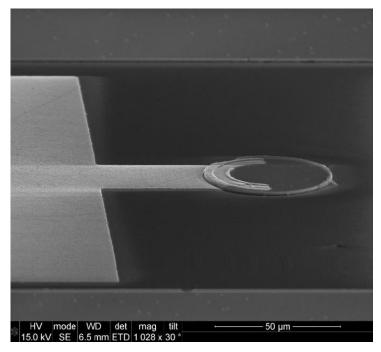

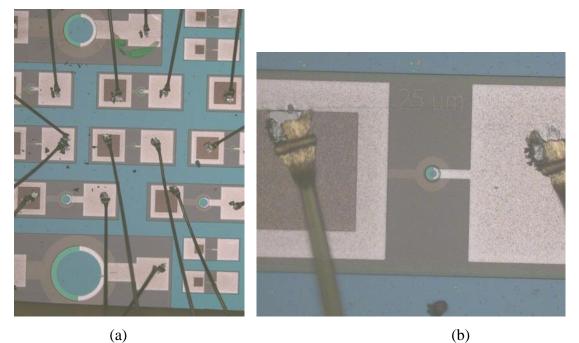

| 5.3           | Ge-on-Si SPAD fabrication                                                          | 169        |

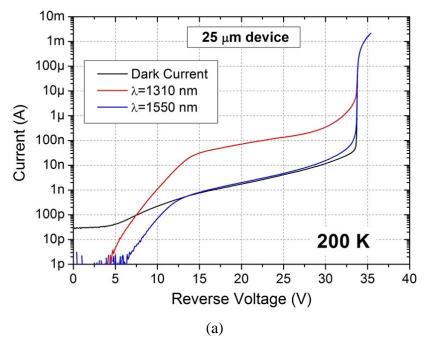

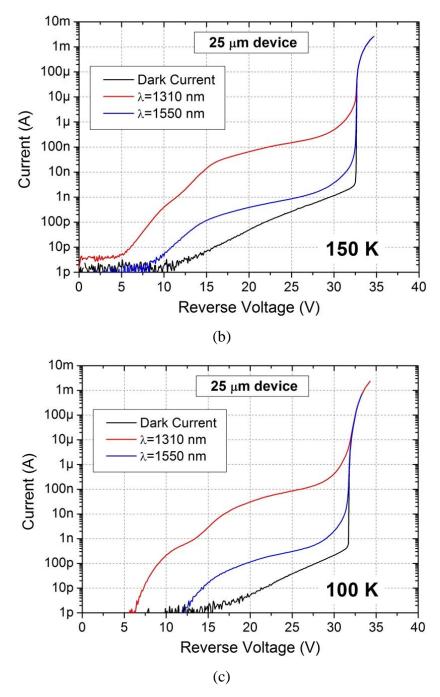

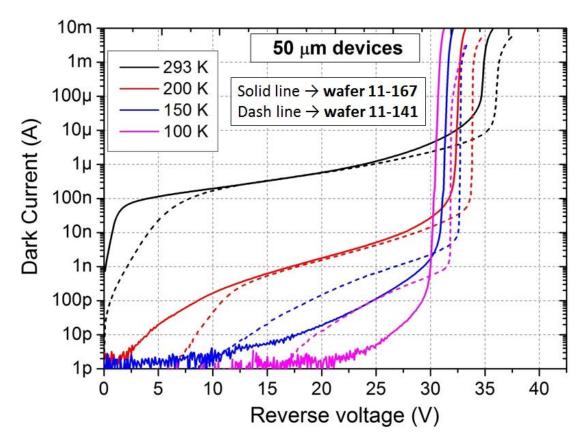

| 5.4           | The Current-Voltage Characteristic                                                 | 172        |

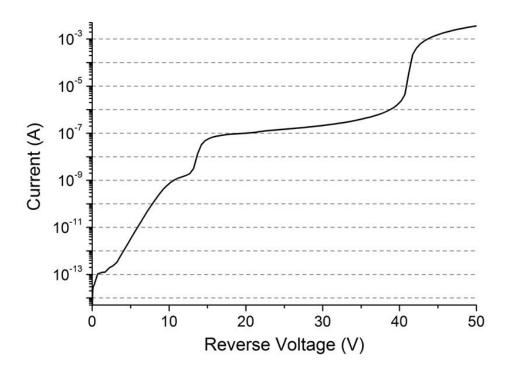

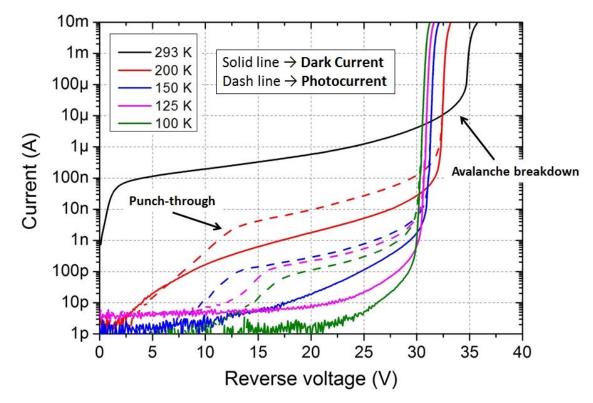

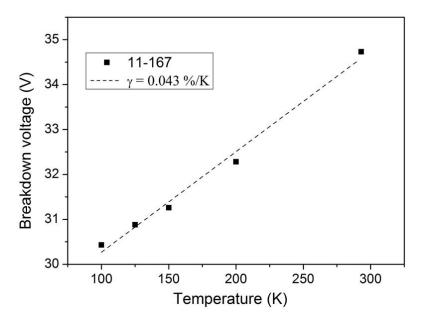

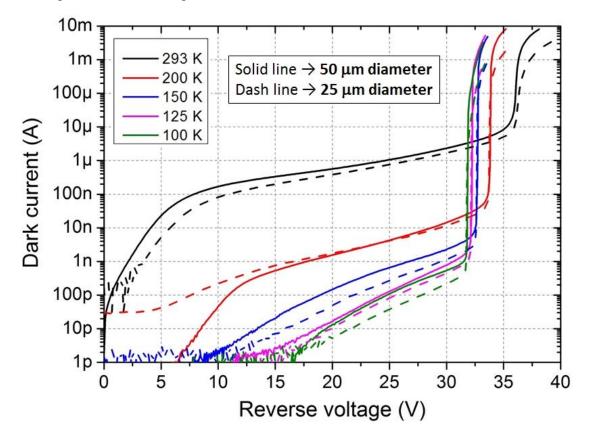

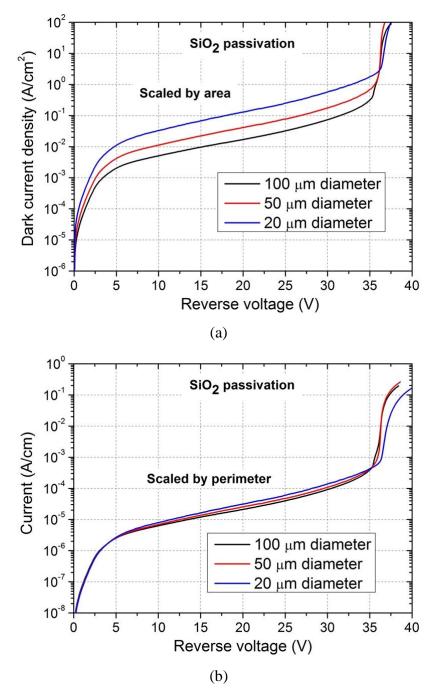

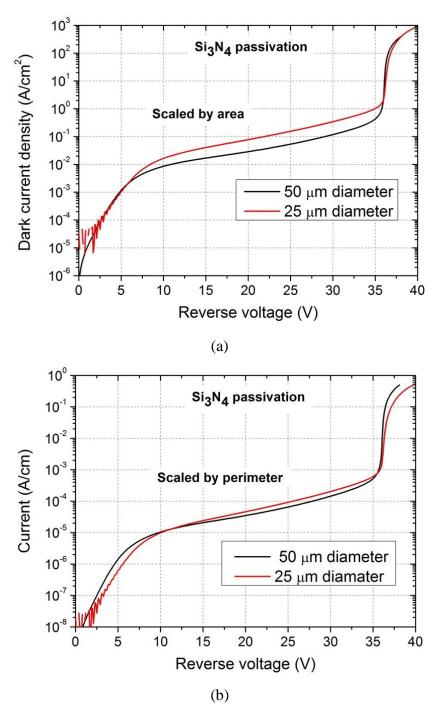

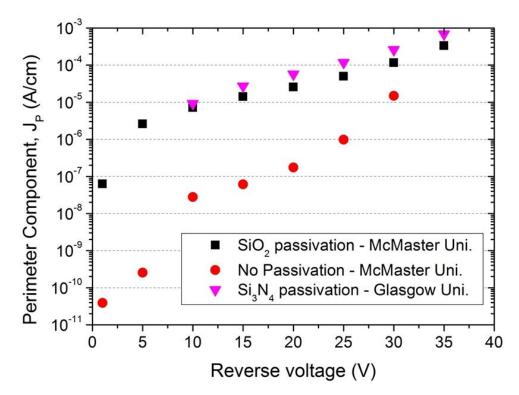

| 5.4.1         | I I-V characteristic of sample 11-167                                              | 173        |

| 5.4.2         | 2 I-V characteristic of sample 11-141                                              | 177        |

| 5.4.3         | <i>Comparison between devices from samples 11-167 and 11-141</i>                   |            |

| 5.5           | Single-Photon Characterisation                                                     |            |

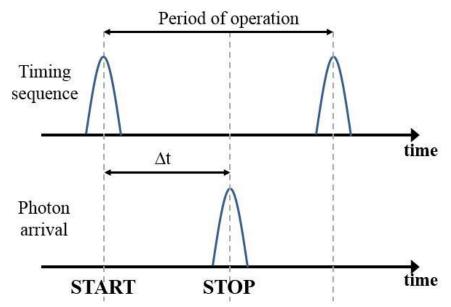

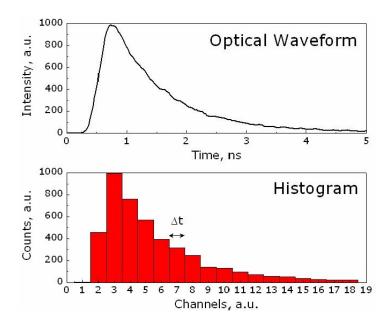

| 5.5.1         | TCSPC technique                                                                    | 184        |

| 5.5.2         | 2 Experimental Setup and Methodology                                               |            |

| 5.5.3         |                                                                                    |            |

| 5.5.4         |                                                                                    |            |

| 5.5.5         |                                                                                    |            |

| 5.5.6         |                                                                                    |            |

| 5.5.7         |                                                                                    |            |

| 5.5.8         |                                                                                    |            |

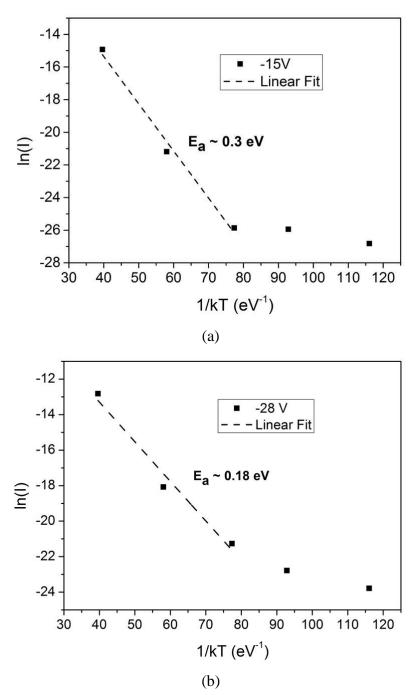

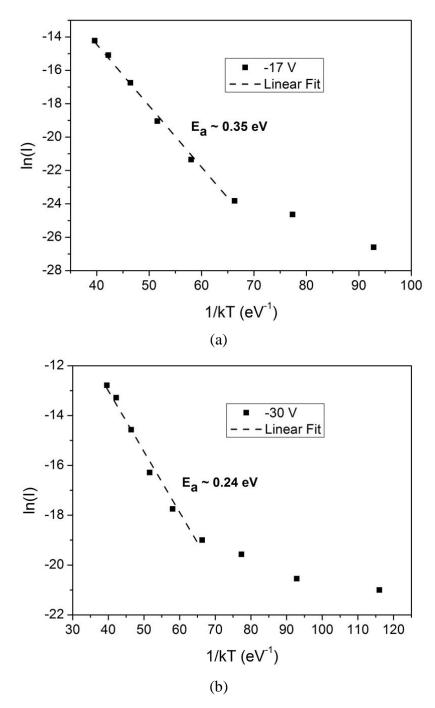

| 5.6           | Dark current analysis                                                              |            |

| 5.7           | Future work                                                                        |            |

| 5.8           | Conclusion                                                                         |            |

| 5.9           | Reference                                                                          | 215        |

| -       | r 6 - Fill-factor recovery of Si CMOS SPAD array by using microlens<br>ion: improvement factor and spatial uniformity characterisation |     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1     | Introduction                                                                                                                           | 217 |

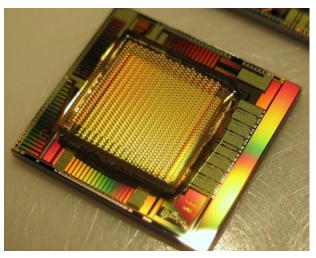

| 6.2     | Si SPAD: custom processing and CMOS fabrication                                                                                        | 218 |

| 6.3     | Single-photon Detection Efficiency and Fill-Factor recovery                                                                            | 220 |

| 6.4     | HV-CMOS Si SPAD                                                                                                                        | 223 |

| 6.4.1   | Photon-counting mode of operation                                                                                                      | 226 |

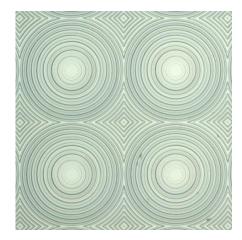

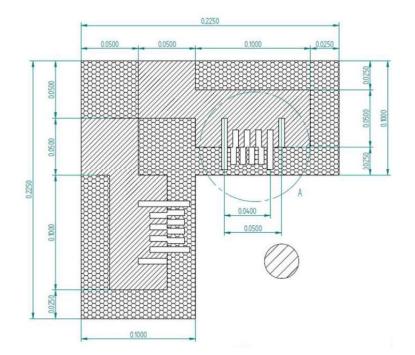

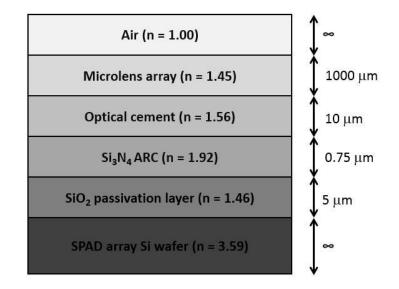

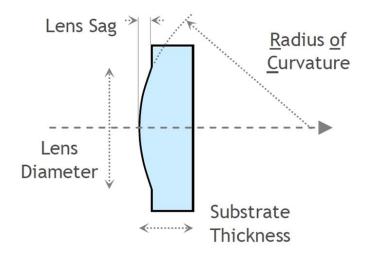

| 6.5     | Diffractive Microlens Array Design                                                                                                     | 228 |

| 6.5.1   | Microlens performance                                                                                                                  |     |

| 6.5.2   | Microlens integration                                                                                                                  |     |

| 6.6     | Characterisation setup                                                                                                                 | 237 |

| 6.7     | Improvement Factor (IF) measurements                                                                                                   | 242 |

| 6.7.1   | Methodology                                                                                                                            |     |

| 6.7.2   | Hot pixel removal                                                                                                                      |     |

| 6.7.3   | Results of the Improvement Factor                                                                                                      |     |

| 6.7.4   | Improvement Factor comparison                                                                                                          |     |

| 6.8     | Spatial Uniformity of the SPAD arrays                                                                                                  | 255 |

| 6.9     | Future Outlook                                                                                                                         | 260 |

| 6.10    | Conclusions                                                                                                                            | 262 |

| 6.11    | Acknowledgements                                                                                                                       | 263 |

| Refere  | ence                                                                                                                                   | 263 |

| Chapter | r 7 - Conclusions and Future work                                                                                                      | 266 |

| 7.1     | Reference                                                                                                                              | 270 |

## List of Publications by the Candidate

#### Papers published in peer reviewed Journals

R. E. Warburton, **G. Intermite**, M. Myronov, P. Allred, D. R. Leadley, K. Gallacher, D. J. Paul, N. J. Pilgrim, L. J. M. Lever, Z. Ikonic, R. W. Kelsall, E. Haunte-Cerón, A. P. Knights, and G. S. Buller, *Ge-on-Si Single-Photon Avalanche Diode Detectors: Design, Modeling, Fabrication, and Characterization at Wavelengths of 1310 and 1550nm*, IEEE Transactions on Electron Devices, Vol. 60, No. 11, November 2013.

**G. Intermite**, R. E. Warburton, A. McCarthy, X. Ren, F. Villa, A. J. Waddie, M. R. Taghizadeh, F. Zappa, A. Tosi, and G.S. Buller, *Integration of diffractive microlens arrays for fill-factor improvement of Si CMOS single-photon avalanche diode detector arrays*, To be submitted to Optics Express in July-August 2015.

#### Peer reviewed Conference paper

**G. Intermite**, R. E. Warburton, A. McCarthy, X. Ren, F, Villa, A. J. Waddie, M.R. Taghizadeh, A. Tosi, F. Zappa and G. S. Buller, *Enhancing the fill-factor of CMOS SPAD arrays using microlens integration*, INVITED PAPER to SPIE Optics and Optoelectronics, Prague, Czech Republic, April 13-16, 2015.

**G.** Intermite, R.E. Warburton, M. Myronov, P. Allred, D.R. Leadley, K. Gallagher, D.J. Paul, N.J. Pilgrim, L.J.M. Lever, Z. Ikonic, R.W. Kelsall, and G.S. Buller, *Design and performance of a prototype mesa–geometry Ge–on–Si single–photon avalanche diode detector at 1310 nm and 1550 nm wavelengths*, The IEEE 10th International Conference on Group IV Photonics (GFP), Seoul, Korea, August 28-30, 2013.

**G. Intermite**, R.E. Warburton, M. Myronov, P. Allred, D.R. Leadley, K. Gallacher, D.J. Paul, N.J. Pilgrim, L.J.M. Lever, Z. Ikonic, R.W. Kelsall, and G.S. Buller, *Ge-on-Si single-photon avalanche diode near-IR detectors*, UK Semiconductor 2013, Sheffield, UK, July 3 - 4,2013.

## **Chapter 1 – Introduction**

Exactly 50 years ago, Gordon Moore predicted that the number of transistors in an integrated circuit (IC) doubles roughly every eighteen months [1]. This prediction is better known as Moore's law. The main reason behind the success of the Moore's law is the technology scaling which has been favourably exploited from many silicon IC technologies, such as silicon complementary metal oxide semiconductor (Si-CMOS) technology. Therefore, technology scaling permits a high density of integration, tens of millions of CMOS transistor on chip, and today it is possible to speak of Deep Sub Micron (DSM) and Ultra-DSM technologies. However, as the feature size decreases below 100 nm, the gain in the performance obtained from shrinking the size of the devices is reduced. This is mainly due to two reasons: the RC delay and heat dissipation.

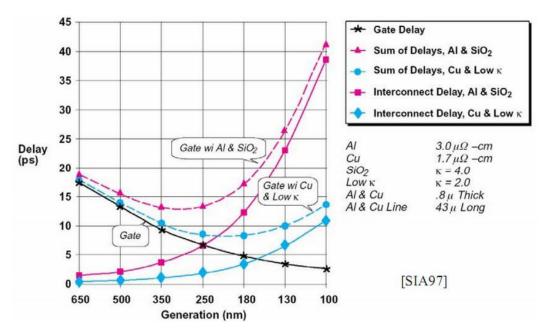

As predicted from the ITRS (International Technology Roadmap for Semiconductor), the metallic interconnection represents the main problem since the RC delay becomes very important, as shown in Figure 1 [2]. The RC time constant of a wire defines the maximum frequency (which is proportional to 1/RC) of the transmitted signal through a wire of a defined length. This depends on the resistance and capacitance per unit length. Both parameters, and hence the RC delay, increase with the shrinkage of the feature size. The RC delay does not only limit the overall frequency of the chip, but it also induces the de-synchronisation of the signals in the clock distribution, and increases the bit error rate [3].

The power dissipation in an information-processing system is a major limitation at many levels, including those related to CMOS chips. The ITRS stated that the amount of heat that can be removed from a chip in a cost-effective manner is about to saturate at approximately 200 W. Power dissipation is a problem that directly limits the performance of chips, and its increase is thus a significant factor in system economics and the environmental impact of information technology [4].

Figure 1. The gate delay and interconnect delay as a function of feature size for Al/SiO<sub>2</sub> and Cu/low k dielectric CMOS technology.

In this context, different solutions have been proposed to overcome these limitations. Silicon as emerged as an efficient material system for building photonics devices as well as electronic devices. The early applications of silicon photonics are in digital data communications. By substituting the metallic wires with optical waveguides, not only can the bandwidth of data transmission be increased, but the heat dissipation can be also greatly reduced, since, in principle, photons do not generate any heat when they propagate in a waveguide. The main advantage of silicon photonics that has emerged over the past 50 years is the possibility to develop processes that permit the re-use of CMOS fabrication infrastructure in order to build complex photonic circuits in which information is transferred seamlessly from the electronic to the optical domains and back again [5], [6]. The main constraints associated with CMOS refer to the materials that are not compatible with the CMOS process, and both process and circuits must be designed in such a way that processing them will not harm or contaminate the tools. Although different photonics devices have been fabricated and demonstrated separately, these devices can be interfaced to one another with standard optical fibres and connectors. However, high cost and loss emerge from the photonic packaging process which requires a severe alignment procedure with submicron accuracy. In order to achieve high performance and low-cost optical links, it is desirable to integrate optical components such as photodetectors, light sources and modulators on the same silicon chip, and silicon is a very attractive platform for photonic integrated circuits.

In addition, beyond data communications, there are a huge number of new applications that rely on silicon photonics being explored in both commercial and academic worlds such as quantum information and imaging technologies, condensed matter physics, biosensing, etc. Therefore, silicon photonics might offer a robust platform for the monolithic integration of optics and microelectronics on the same silicon chip by using the same fabrication facilities used for CMOS processes.

In particular, quantum technology exploits the quantum-mechanical phenomena to provide new techniques for sensing, measurements, information processing, data transmission and storage. This technology is driven by advances in technology and experimental capability obtained in the last decade or so. This is also confirmed by the considerable investment for the development of such technology. For example, it is worthwhile to mention the National Quantum Technology Programme from the UK Government with the aim of stimulating the development of commercial applications and markets for quantum technologies.

A direct consequence of this, is the demand of extremely sensitive devices capable of registering the elemental quantum of light, referred to as photons [7]. Such class of detectors, referred as single-photon detectors, are used in a wide range of time-correlated single-photon counting (TCSPC) applications such as quantum key distribution (QKD), time-of-flight, light detection and ranging (LiDAR), etc.. Different technologies have been used to detect single-photons such as photomultiplier tubes, microchannel plates, superconducting nanowires, and single-photon avalanche detectors (SPADs).

Among the various choices, SPADs tend to be preferred because of their intrinsic advantages that are typical of solid state devices, such as low power consumption, miniature size, low bias voltages, reduced magnetic field susceptibility, reliability, and low cost [8], [9]. Although Si represents the best material choice for all the aforementioned advantages, it is also the best material for avalanche multiplication due to its large ratio of electron to hole impact ionisation rates. Si SPADs now represent a commercially available technology, and can be classified into two distinct groups: those that are fabricated using customized processing techniques and those fabricated using CMOS compatible approaches.

Standard CMOS fabrication processes from the microelectronic industry offer significant advantages in terms of the routine on-chip integration with the electronics

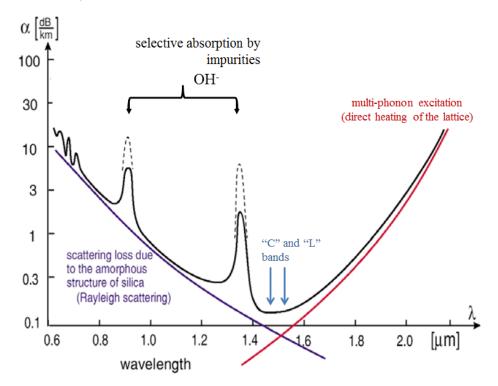

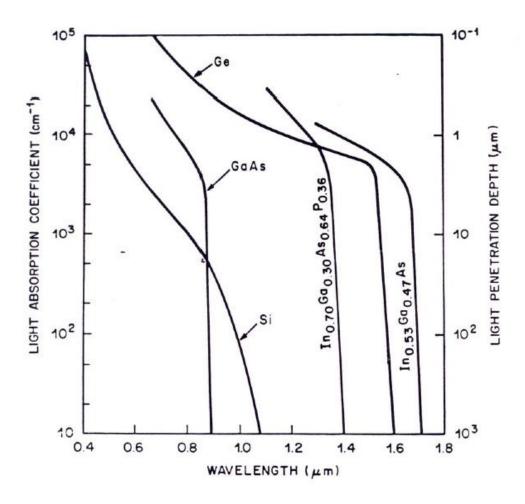

required for photon-counting and photon-timing techniques. This efficient integration allows the possibility of fabrication of two-dimensional SPAD-based focal plane arrays. However, the detection of light in silicon is intrinsically limited to wavelengths below 1  $\mu$ m. Therefore, for operation in the low loss fibre optical windows at around 1.3  $\mu$ m and 1.55  $\mu$ m other semiconductors must be used.

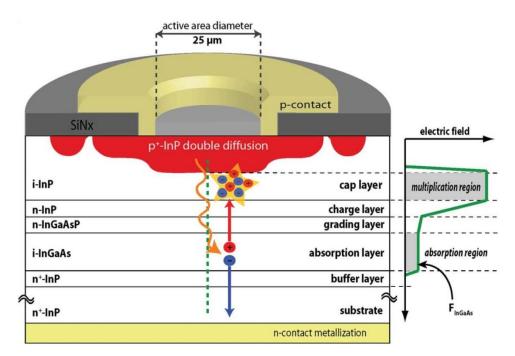

Near infrared single-photon detection is of interest in many applications. Although QKD can be accomplished at shorter wavelengths compatible with Si SPADs [10], it is preferable to work in the low attenuation windows of standard optical fibres [11]. Applications such laser ranging also benefit from the decreased attenuation through air as well as the low solar background radiation at these wavelengths [12]. Near-infrared is also used in the monitoring of microscopic biological system such as singlet oxygen generation  $({}^{1}O_{2})$  which fluoresces at a wavelength of 1270 nm beyond the detection range of Si SPADs [13]. Therefore, the development of low-noise SPADs in this spectral region is required. The best currently available practical detectors, operating at near-room temperature and a wavelengths in the range of  $1 - 1.7 \mu m$ , are InGaAs/InP SPADs. These devices have demonstrated good single-photon performance, and they are commercially available from different sources such as Princeton Lightwave, MicroPhoton Device (MPD), etc. However, this class of detectors is not compatible with CMOS technology, they are expensive and one of their major drawbacks is represented by the deleterious effect of afterpulsing which significantly reduces the frequency of operation of the devices to be below 100 kHz.

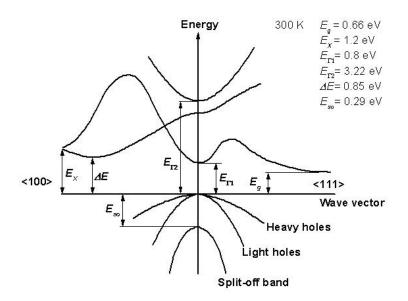

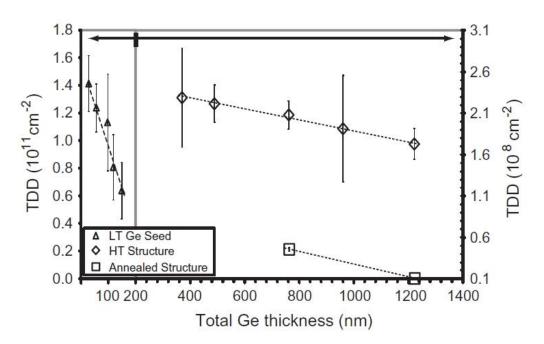

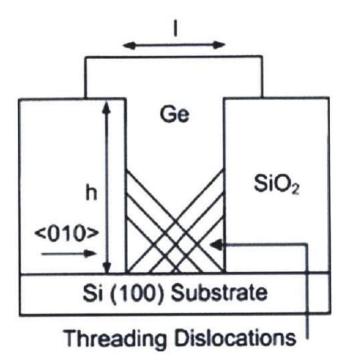

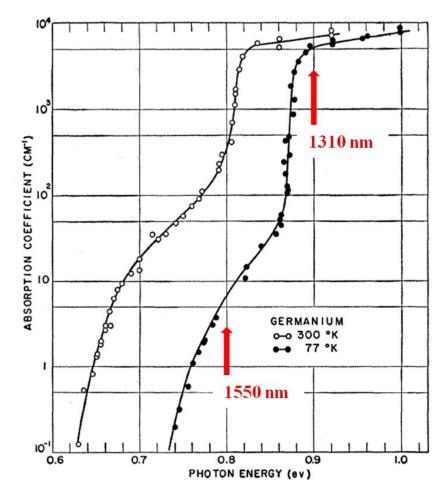

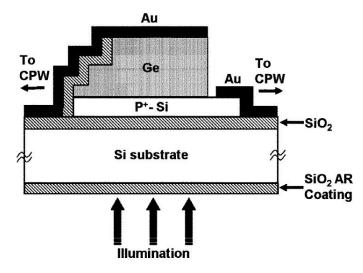

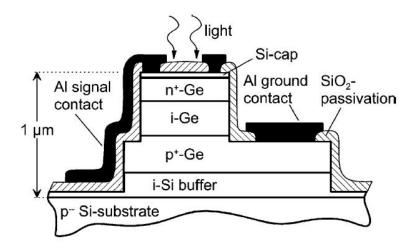

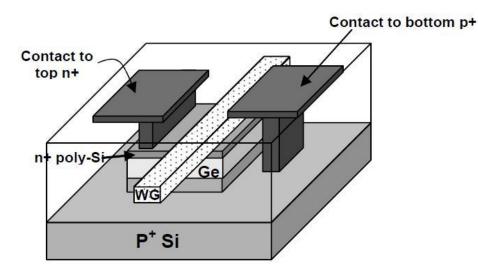

Germanium has been shown to be a promising material for near-infrared detection on Si. The direct band gap of Ge is 0.8 eV, corresponding to 1550 nm. SiGe technology has already been applied for bipolar transistors, and therefore the material has proved to be fully compatible with Si electronic technology. A big challenge for the integration of Ge on Si is represented by the 4% lattice mismatch between the two materials. However, the development of SiGe buffer layers and two-temperature steps of pure Ge on Si has been used to overcome this problem. In terms of single-photon detectors, the first Ge-containing Si SPAD was demonstrated by Loudon *et al.* [14], who showed an improvement of detection efficiency at 1200 nm (above the Si wavelength cut-off). Pure Ge-on-Si SPADs have been reported on only a few occasions. In this context, the research presented in this thesis is aimed at filling this gap by investigating the design of a Ge-on-Si SPADs in order to combine the several advantages of low-noise Si single-photon avalanche multiplication with the infrared sensing capability of germanium.

In addition, Ge does not suffer from the same contamination processes as InGaAs, and its compatibility with the CMOS technology (mainly to make high-speed transistors) has been already demonstrated. Furthermore, Ge-on-Si CMOS imagers (768×600 pixels) for near-infrared detection has been fabricated and commercialised by NoblePeak Vision which is a company based in USA [17]. A monolithic CMOS imager with Ge detectors (incorporate in the CMOS process using selective epitaxial growth) fabricated within a conventional 180 nm CMOS foundry process was demonstrated [17]. Although each pixel consisted of a lateral p-i-n whole Ge detector, the main advantage arising from the integration of Ge with standard CMOS technologies was successfully proved.

Chapter 2 describes the physics of different photodetector structures and outlines the main parameters that must be considered during their design. The main focus is given to the avalanche photodiodes and single-photon detectors. Although, there are many common points between these two structures, they have been designed to satisfy different performance requirements. In particular, the key figures of merit of a SPAD such as dark count rate, single-photon detection efficiency, noise equivalent power, afterpulsing and jitter are then introduced.

Chapter 3 firstly provides an explanation of the choice of materials for near-infrared detection and then focuses on the integration between these materials and Si. In particular, it discusses the several problems which arise from the lattice mismatch, and then reviews the different solutions used to overcome this problem. Hence, the main attention is given to the Ge-on-Si hetero-epitaxial system. Finally, a literature review on the integration of near-infrared photodetectors on silicon is presented with the main emphasis given to the single-photon detector technologies which are used in the near-infrared wavelength range.

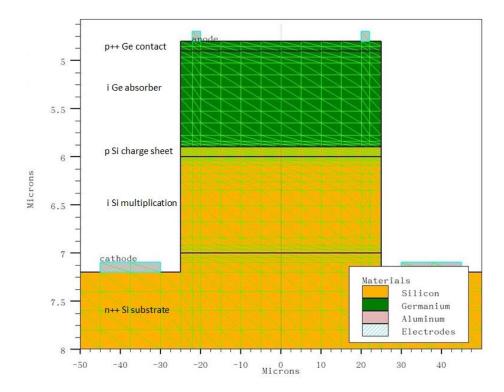

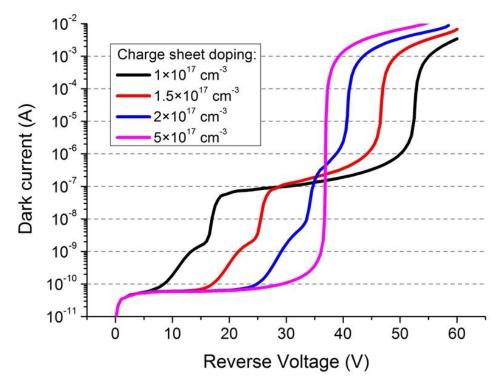

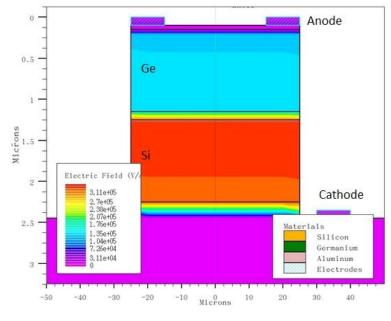

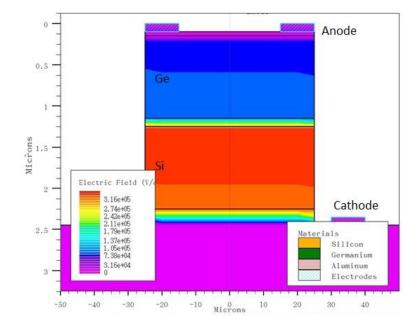

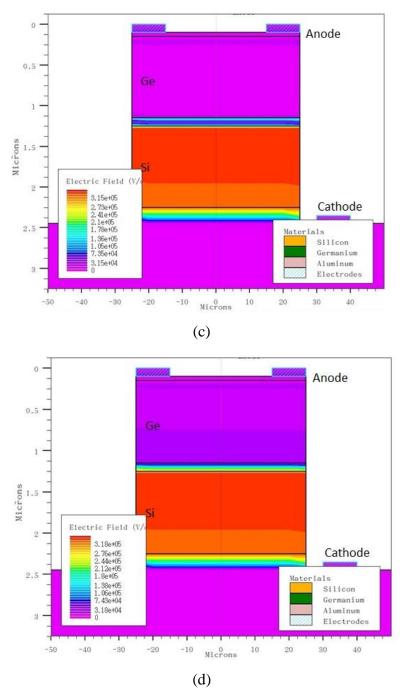

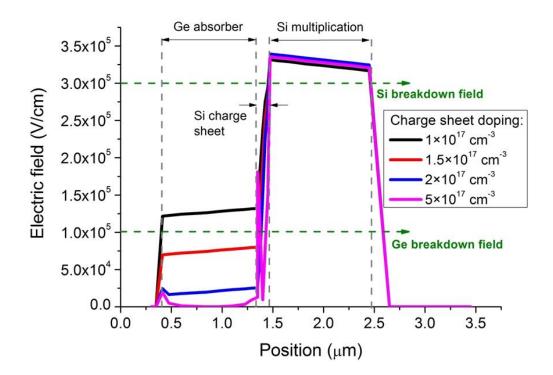

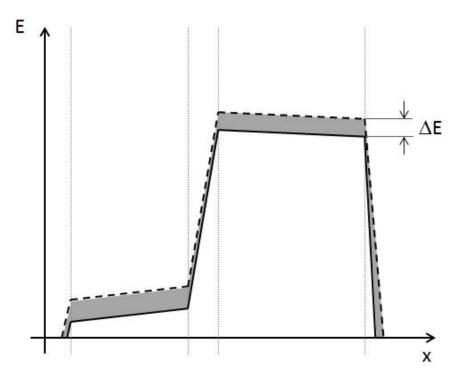

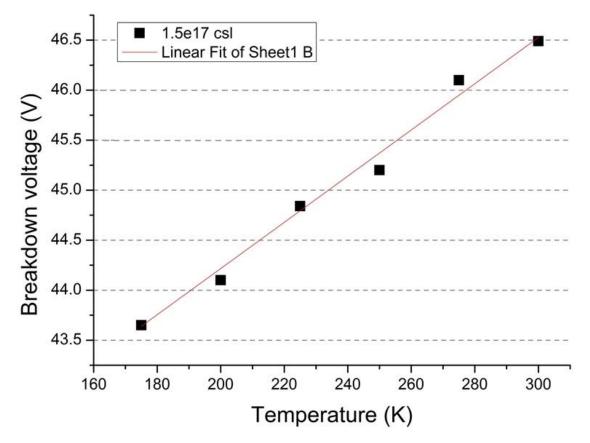

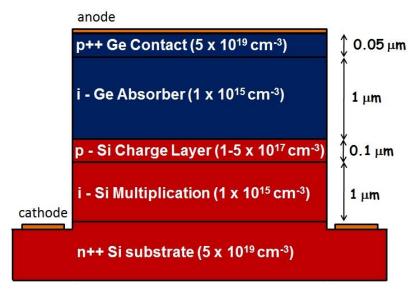

Chapter 4 describes the criteria that were used for the design of the Ge-on-Si SACM structure presented in this work. The devices were modelled using a commercially available software package (Silvaco ATLAS), and hence the results of simulations are presented. Since different Ge-on-Si SPAD generations were grown and analysed, experimental data are given for those obtained from the capacitance-voltage measurements and SIMS measurements used in the modelling software in order to evaluate their impact on the designed structure.

Chapter 5 firstly introduces the growth and fabrication process involved for the device development, and then describes the preliminary devices characterisation in terms of I-V characteristics in order to evaluate the main mechanisms which contributed to the leakage current. The Time Correlated Single-Photon Counting (TCSPC) setup used for the single-photon characterisation of these devices in terms of single-photon detection efficiency, dark count rate, noise equivalent power, time jitter and afterpulsing is then described.

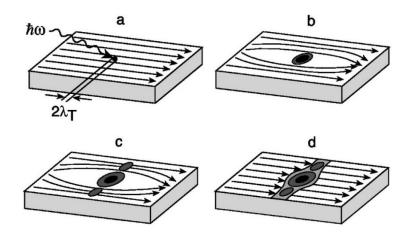

Chapter 6 describes the main advantages introduced by the fabrication of Si SPAD by using the standard CMOS fabrication processes. From the early 2000s, several research groups have explored the design of a monolithically integrated single-photon imaging system in high-voltage (HV) and standard deep-sub-micron (DSM) CMOS technologies [15], [16]. Two-dimensional CMOS SPAD-based focal plane arrays generally suffer from low fill-factor of the detector photo-sensitive area compared to the overall detector pixel area. Diffractive microlens arrays have been used in this work with the aim of recovering this loss of sensitivity, and the microlens design and integration process is so described in the chapter. Additionally, the experimental setup used for the characterisation of the SPAD arrays integrating the microlens array is given, and the main finding in terms of improvement factor and spatial uniformity of detection are finally presented.

Chapter 7 summarises the conclusions pointed out for each chapter and describes future work in these areas.

## 1.1 Reference

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *IEEE Solid-State Circuits Soc. Newsl.*, vol. 38, no. 8, 1965.

- [2] D. A. B. Miller and H. M. Ozaktas, "Limit to the Bit-Rate Capacity of Electrical Interconnects from the Aspect Ratio of the System Architecture," J. Parallel Distrib. Comput., vol. 41, no. 1, pp. 42–52, 1997.

- [3] R. Sridhar, "System-on-chip (SoC): clocking and synchronization issues," in *17th International Conference on VLSI Design*, 2004. *Proceedings*, 2004, pp. 520–527.

- [4] D. A. B. Miller, "Device Requirements for Optical Interconnects to Silicon Chips," *Proc. IEEE*, vol. 97, no. 7, pp. 1166–1185, 2009.

- [5] Y. Arakawa, T. Nakamura, Y. Urino, and T. Fujita, "Silicon photonics for next generation system integration platform," *IEEE Commun. Mag.*, vol. 51, no. 3, pp. 72–77, 2013.

- [6] M. Hochberg, N. C. Harris, R. Ding, Y. Zhang, A. Novack, Z. Xuan, and T. Baehr-Jones, "Silicon Photonics: The Next Fabless Semiconductor Industry," *IEEE Solid-State Circuits Mag.*, vol. 5, no. 1, pp. 48–58, 2013.

- [7] R. H. Hadfield, "Single-photon detectors for optical quantum information applications," *Nat. Photonics*, vol. 3, no. 12, pp. 696–705, 2009.

- [8] G. S. Buller and R. J. Collins, "Single-photon generation and detection," *Meas. Sci. Technol.*, vol. 21, p. 012002, 2010.

- [9] S. D. Cova and M. Ghioni, "Single-Photon Counting Detectors," *Breakthroughs*, p. 274, 2010.

- [10] K. J. Gordon, V. Fernandez, P. D. Townsend, and G. S. Buller, "A short wavelength GigaHertz clocked fiber-optic quantum key distribution system," *IEEE J. Quantum Electron.*, vol. 40, no. 7, pp. 900–908, 2004.

- [11] G. S. Buller and R. J. Collins, "Single-Photon Detectors for Infrared Wavelengths in the Range 1–1.7 μm," in *Advanced Photon Counting*, P. Kapusta, M. Wahl, and R. Erdmann, Eds. Springer International Publishing, pp. 43–69, 2014.

- [12] R. E. Warburton, "Infrared Time-Correlated Single-Photon Counting," Ph.D., Heriot-Watt University, 2008.

- [13] N. R. Gemmell, A. McCarthy, B. Liu, M. G. Tanner, S. D. Dorenbos, V. Zwiller, M. S. Patterson, G. S. Buller, B. C. Wilson, and R. H. Hadfield, "Singlet oxygen luminescence detection with a fiber-coupled superconducting nanowire singlephoton detector," *Opt. Express*, vol. 21, no. 4, pp. 5005–5013, 2013.

- [14] A. Y. Loudon, P. A. Hiskett, G. S. Buller, R. T. Carline, D. C. Herbert, W. Y. Leong, and J. G. Rarity, "Enhancement of the infrared detection efficiency of silicon photon-counting avalanche photodiodes by use of silicon germanium absorbing layers," *Opt. Lett.*, vol. 27, no. 4, pp. 219–221, 2002.

- [15] M. Gersbach, Y. Maruyama, R. Trimananda, M. W. Fishburn, D. Stoppa, J. A. Richardson, R. Walker, R. Henderson, and E. Charbon, "A Time-Resolved, Low-Noise Single-Photon Image Sensor Fabricated in Deep-Submicron CMOS Technology," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1394–1407, Jun. 2012.

- [16] F. Villa, R. Lussana, D. Bronzi, S. Tisa, A. Tosi, F. Zappa, A. Dalla Mora, D. Contini, D. Durini, S. Weyers, and W. Brockherde, "CMOS Imager With 1024 SPADs and TDCs for Single-Photon Timing and 3-D Time-of-Flight," *IEEE J. Sel. Top. Quantum Electron.*, vol. 20, no. 6, pp. 364–373, Nov. 2014.

- [17] C.A. King, C.S. Rafferty, US Patent 7,453,129, "Image sensor comprising isolated germanium photodetectors integrated with a silicon substrate and silicon circuitry"

## **Chapter 2 – Physics of photodiodes**

#### 2.1 Introduction

Photodiodes belong to the category of light sensors or detectors, whose task is to convert an optical signal into an electrical signal. As already discussed in Chapter 1, there are a huge number of applications that require that this conversion procedure is performed with certain requirements in terms of sensitivity, bandwidth, power, signal-to noise, etc. To meet these constraints in terms of performance, different photodiode structures have been proposed and demonstrated in the past century. Therefore, understanding the physics of these devices represents a key point for designing new structures that always satisfy more and more stringent requirements. Starting from the physics of the p-n junction, which represents the most basic semiconductor photodiode structure, this chapter will analyse the advantages or disadvantages of more complex structures, such as the p-i-n and the avalanche photodiodes. This analysis requires the introduction of their most important performance characteristics such as the leakage current, responsivity, bandwidth, signal-to-noise, etc. Finally, the single-photon detector will be introduced, which represents an avalanche photodiode operating in Geiger mode, that must satisfy new requirements in terms of dark count rate, single-photon detection efficiency, noise equivalent power, timing jitter and afterpulsing.

#### 2.2 Physics of p-n and p-i-n photodiodes

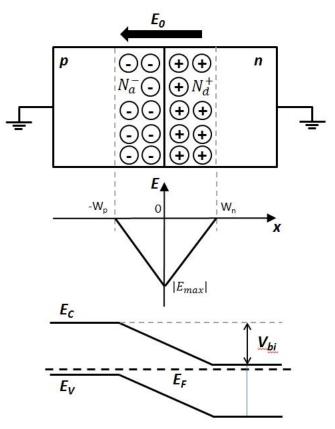

Photodiodes convert a light signal to an electrical signal such as a voltage or current pulse. This conversion is achieved by the creation of free electron hole pairs (EHPs) by the absorption of photons, that is, the creation of electrons in the conduction band and holes in the valence band. A basic photodiode is represented by the p-n junction, which is created by putting two pieces of semiconductor in contact, a p type (with an acceptor concentration  $N_a$ ) and an n type (with a donor concentration  $N_d$ ).

In the equilibrium condition, the strong difference of doping concentration at the interface between the two materials leads to a diffusion of the charge carriers. Holes diffuse from the p-side to the n-side, while electrons diffuse in the opposite direction. In proximity to the interface, holes and electrons on the p and n-side, respectively, leave negative ion acceptors  $(N_a^-)$  and positive ion donors  $(N_d^+)$ . Due to this phenomenon, a space charge region (or depletion region) is created at the junction, negative from the p-side, with an extension equal to  $W_p$  and, positive from the n-side  $(W_n)$ . Therefore, an

electric field (*E*) is generated in the vicinity of the interface between the two regions, as shown in Figure 2.1.

Figure 2.1. Schematic of a p-n junction at equilibrium.

Because of the effect of the electric field, two drift currents are created: holes drift from the right side to the left side (opposite to the hole diffusion component) and electrons drift in the opposite direction (opposite to the electron diffusion component). In equilibrium, the net flux of current through the junction is zero (there is a balance between the current drift component due to the electric field and, the current diffusion component due to different doping concentrations). The Fermi level is constant through the two semiconductor regions (Figure 2.1) and, this determines a built-in potential at the junction, which can be expressed by

$$V_{bi} = \frac{k_B T}{q} \ln\left(\frac{N_a N_d}{n_i^2}\right) \tag{2.1}$$

where  $k_B$  is the Boltzmann's constant, *T* the temperature and,  $n_i$  is the intrinsic carrier concentration. In one dimension, the profile of the electric field can be calculated by using Poisson's equation

$$\frac{dE}{dx} = \frac{\rho(x)}{\varepsilon}$$

(2.2)

where  $\rho$  is the density of space charge equal to  $qN_d$  and  $-qN_a$  for the n and p side, respectively and,  $\varepsilon$  is the dielectric permittivity of the semiconductor. The electric field is then obtained integrating equation 2.2 over the space charge region with boundary conditions of E = 0 in the neutral regions (outside the space charge region in the p and n side). Considering the condition for which  $N_a \gg N_d$  (asymmetric junction), the depletion region will be extended more on the n side than the p side leading to an electric field more confined in the n side.

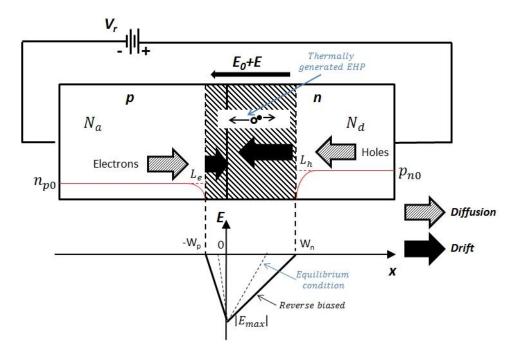

If an external reverse bias  $V_r$  (negative on the p side and positive on the n side) is applied, the negative terminal will cause holes in the p-side to move away from the depletion region, which results in more exposed negative acceptor ions and thus wider depletion region. Similarly, the positive terminal will attract electrons away from the depletion region, which exposes more positive charged ions. The depletion width on the n-side therefore also widens. The electric field dropping across the junction is, therefore, the sum of the electric field associated to the depletion region ( $E_0$ ) plus the electric field due to the external reverse bias (E), as shown in Figure 2.2. The voltage drops mainly across the resistive depletion region which becomes wider on both sides.

Figure 2.2. Schematic of a p-n junction with the associated electric field when a reverse bias  $V_r$  is applied.

There is a small reverse current due to two causes:

1. there is a small hole diffusion current from the bulk n-side, where the holes are at equilibrium with a concentration equal to  $p_{n0}$ , to the depletion region. The

reduction of the hole concentration near to the depletion region is related to their diffusion length  $L_h$ . Because of this small concentration gradient, a small hole diffusion current exists. Within the depletion region, these carriers are swept by the field across the depletion region over to the p-side. Similarly, for electrons on the p-side. This phenomenon leads to a reverse saturation current density, which can be expressed by

$$J_{s} = q\left(\frac{D_{e}}{L_{e}}n_{p0} + \frac{D_{h}}{L_{h}}p_{n0}\right) = q\left(\frac{D_{e}}{L_{e}N_{d}} + \frac{D_{h}}{L_{h}N_{a}}\right)n_{i}^{2}$$

(2.3)

Where  $D_e$  and  $D_h$  are the diffusion coefficients of electrons and holes, respectively. The value of this current depends only on the material properties via  $n_i$ ,  $\mu_e$ ,  $\mu_h$ , doping concentration.

2. The thermal generation of electron hole pairs (EHPs) in the depletion region contributes to this reverse current since the internal field in this layer will separate the electrons and holes and cause them to drift towards neutral regions. The value of this generation current ( $J_{gen}$ ) within the depletion region can be calculated by using the Shockley-Read-Hall model and by defining the mean thermal generation time,  $\tau_g$ , as

$$J_{gen} = \frac{qWn_i}{\tau_g} \tag{2.4}$$

It is dependent on the applied reverse bias through the depletion width W, which widens as the reverse bias is increased.

Therefore, the sum of these two contributions represents the total reverse current density, also called the leakage current. Considering a cross-sectional area equal to A, the total reverse current can be written as

$$I_{rev} = q \left(\frac{D_e}{L_e N_d} + \frac{D_h}{L_h N_a}\right) n_i^2 A + \frac{qW}{\tau_g} n_i A$$

(2.5)

It is important to note that both contributions depend on the area of the device, the intrinsic carrier concentration  $(n_i)$ , which is an intrinsic property of any semiconductor material and, on the temperature *T* since  $n_i \sim exp(-E_g/2k_BT)$  [1]. This dependence on the temperature is very important and will be analysed in more detail in the following chapters. In real structures, however, there are other sources which increase this current

such as the surface leakage and tunnelling components that will be considered in the following chapters.

Leakage current is also called dark current because it represents the current that flows through a photodiode even without the injection of photons. Leakage current is, therefore, a source of noise in an optical receiver [2], which can degrade the signal to noise (S/N) ratio. Leakage current is also a source of power dissipation. As pointed out previously, in Chapter 1, power dissipation is becoming a stringent factor for CMOS design due to the high level of integration. Controlling power dissipation is a good reason for reducing leakage current. Moreover, the level of dark current is also an indication of good material quality and device fabrication.

Considering the structure shown in Figure 2.2 under a reverse bias, when a photon with energy greater than the bandgap energy is incident, it is absorbed and a photogenerated EHP is created, which is an electron in the conduction band and a hole in the valence band. The field in the depletion region then separates the EHP and, causes the carriers to drift in opposite directions until they reach the neutral regions. This generates a current, called the photocurrent  $I_{photo}$ . The generation of EHPs is directly related to the absorption of light and it can be defined as the optical generation rate, *G*, given by

$$G = -\frac{1}{A} \frac{dP_{inc}}{dx} \frac{1}{hv} = \frac{\alpha P_{inc}}{Ahv}$$

(2.6)

Where  $P_{inc}$  is the incident optical power,  $\alpha$  is the absorption coefficient (see Chapter 3), and hv is the photon energy. If the light is absorbed in the depletion region, assuming no recombination of the photo-generated EHPs in this layer, the photocurrent is simply given by the integral of the generation rate over the depletion region:

$$I_{photo} = -qA \int_{-W_p}^{W_n} Gdx = q \, \frac{(1-R)P_{inc}}{h\nu} (1-e^{-\alpha W})$$

(2.7)

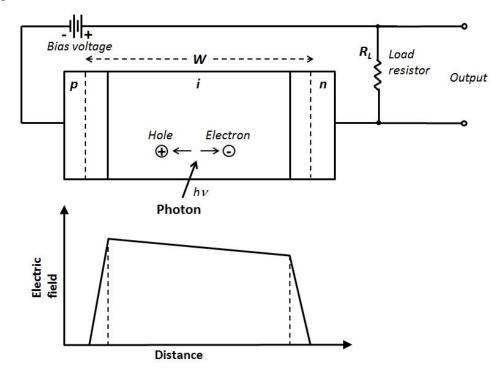

also allowing for the reflectivity R at the semiconductor surface. It should be noted that if the light is incident on the neutral region to calculate the photocurrent, the continuity equations should also be solved for holes and electrons in the n-side and p-side, respectively. Light absorbed in the neutral region leads, however, to a very low level of photocurrent due to free carrier absorption and high recombination rates in these regions. The basic p-n junction photodiode has, however, two main drawbacks (described below) that are substantially reduced by using the p-i-n photodiode configuration. A schematic of a typical p-i-n structure and the electric field profile in the device is shown in Figure 2.3.

*Figure 2.3. Schematic of a reverse biased p-i-n photodiode.*

The particular geometry of a p-i-n device includes an intrinsic "i" region between the p and n region. When it is illuminated with energy greater than or equal to the bandgap of the semiconductor, electron-hole pairs (EHP) are generated. Due to the built-in potential, or by applying an external reverse bias, the intrinsic region is depleted (due to fairly low background doping level) and it has a high resistivity [3]. Because of this, the entire voltage drop takes place mainly in the "i" region, giving rise to a high electric field for the collection of the photo-generated EHP.

The main difference between these p-n and p-i-n structures is in terms of the depletion region, which is generally much narrower in the p-n structure than in the p-i-n structure. In the p-n structure there is more likely to be a large diffusion component that is due to the photons absorbed outside the depletion region. Minority carriers generated, electrons in the p-side and holes in the n-side, have to diffuse into the depletion region before they can drift to the n-side or p-side, respectively. Because diffusion is intrinsically a slow process, carriers take a long time to diffuse (about a nanosecond over 1  $\mu$ m). In the p-i-n configuration, the depletion region can be designed to extend

across almost the whole length of the device, so that the drift component dominates over the diffusion component. In the depleted absorbing layer, the photo-generated carriers travel at their saturation velocity  $v_{sat}$ . The bandwidth of a p-i-n photodiode is determined by the carrier transit time, or by the RC time constant. Since transit time, junction capacitance, and quantum efficiency are interdependent, the design of a wide bandwidth p-i-n photodiode involves a performance tradeoff, and the depletion width W must be chosen depending on the requirements in terms on speed and sensitivity.

The performance of a photodiode is often characterised by the responsivity (R) that is defined as:

$$R = \frac{I_{photo}}{P_{optical}} = \frac{\eta q}{h\nu}$$

(2.8)

Where  $I_{photo}$  is the photogenerated current and  $P_{optical}$  is the input optical power. The responsivity takes into account the energy of the incident photon. So, it takes into account the variation in energy implied by different wavelengths [4]. It is also related to the quantum efficiency  $\eta$  by the relation shown in Eq. 2.8. The quantum efficiency is the number of electron – hole carrier pairs generated compared to the number of incident photons of energy hv. Here, q is electron charge, h the Planck's constant and v the frequency of the incident radiation.

In a p-n junction diode, the responsivity is limited by the diffusion lengths of the carriers. Minority carriers generated beyond a diffusion length from the depletion region recombine before they can reach the high field region.

In a p-i-n junction diode the responsivity is increased by adding an "i" region that will be always fully depleted so that any carriers generate in this region will be collected (assuming negligible recombination in the intrinsic region itself).

For a p-i-n photodiode with a totally depleted intrinsic layer, the external quantum efficiency,  $\eta_{ext}$ , can be written as

$$\eta_{ext} = (1 - R)(1 - e^{-\alpha d}) \tag{2.9}$$

where *d* is the width of the absorption region,  $\alpha$  is the absorption coefficient, *R* is the reflectivity at the surface. The transit time limited -3 dB component of the bandwidth for a p-i-n having total depletion thickness *W*, is given by [5]

$$f_{tr} \cong \frac{3.5\bar{v}}{2\pi W}$$

,  $\frac{1}{\bar{v}^4} = \frac{1}{2} \left( \frac{1}{v_e^4} + \frac{1}{v_h^4} \right)$  (2.10)

where  $\bar{v}$  is the average of saturation electron and hole velocity, and  $v_e$  and  $v_h$  are the electron and hole saturation velocities, respectively. The RC contribution to the bandwidth is given by

$$C = \frac{\varepsilon A}{W} \tag{2.11}$$

$$R = R_S + R_L \tag{2.12}$$

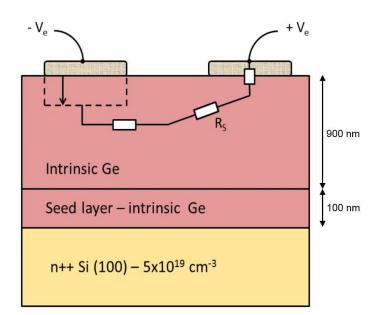

$$f_{RC} = \frac{1}{2\pi\tau_{RC}} = \frac{W}{2\pi R\varepsilon A} \propto \frac{W}{(R_S + R_L)A} , \qquad \tau_{RC} = RC$$

(2.13)

where  $\varepsilon$  is the dielectric constant of the intrinsic region and *C* is the intrinsic capacitance of the p-i-n structure.  $R_S$  is the series resistance including the semiconductor and the metal resistivity.  $R_L$  is the load resistance matching with the external circuit, which generally equates to 50  $\Omega$ . It is primarily determined by the photodiode junction capacitance thus can be controlled through adjusting the device area to a value that is consistent with a designed bandwidth. The total bandwidth of a p-i-n photodiode is expressed by the following equation

$$B = \frac{1}{\sqrt{\left(\frac{1}{f_{RC}}\right)^2 + \left(\frac{1}{f_{tr}}\right)^2}} \quad (Hz)$$

(2.14)

According to equation (2.9), both a low reflectivity R at the incident light surface and a large absorption region thickness are desirable to achieve a high quantum efficiency value and a low junction capacitance. However, a thicker absorber will decrease the photodiode bandwidth due to a longer carrier transit time. Therefore, as already mentioned, there exists a tradeoff between speed and quantum efficiency. This tradeoff can be addressed by decoupling light absorption from the carrier transport by using waveguide device structures or by increasing the responsivity by using a resonant cavity structure.

#### 2.3 Avalanche photodiodes

Avalanche photodiodes (APDs) are another type of photodetector widely used in telecommunications systems. By utilising the impact ionisation process to provide an internal gain, APDs have the advantage of higher sensitivity over conventional p-i-n photodiodes, since the photocurrent is multiplied, when the overall noise in the receiver module is dominated by electronic noise.

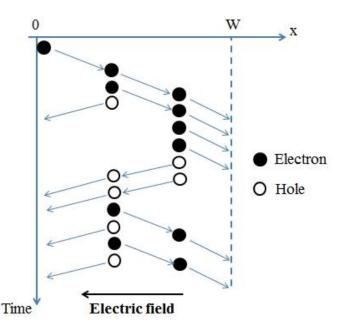

In order for carrier multiplication to take place, the photogenerated carriers must traverse a region where a very high electric field is present. In this high-field region a photogenerated electron or hole can gain enough energy so that it ionises bound electrons in the valence band by colliding with them, resulting in an electron in the conduction band, leaving a hole in the valence band, and the original electron. This carrier multiplication mechanism is known as impact ionisation. The newly created carriers are also accelerated by the high electric field, potentially gaining enough energy to cause further impact ionisation events. This phenomenon is the avalanche effect and it is schematically illustrated in Figure 2.4.

Figure 2.4. Schematic of multiplication process: a single carrier (electron) is injected at the edge of avalanche region under high electric field and a chain of impact ionisation events is triggered.

During the carrier acceleration process under the electric field, in addition to the impact ionisation process, the free carrier also encounters non-ionisation collisions with phonons, generally lowering the carrier's kinetic energy. Phonon scattering may involve carriers gaining energy (phonon absorption), losing energy (phonon emission) and exchanging momentum (elastic).

The impact ionisation characteristics of electrons and holes in a semiconductor are generally characterised by the impact ionisation coefficients,  $\alpha$  and  $\beta$  respectively. These electric field dependent coefficients describe the average number of electron-hole pairs created per unit distance travelled by an electron or hole in a uniform electric field and thus can be defined as the inverse of the mean distance between successive ionisation events. In general,  $\alpha$  and  $\beta$  increase with the applied electric field because the carrier achieves the required energy for an impact ionisation event over a smaller distance.

In its simplest form, an APD has a similar device structure to a p-i-n photodiode. However, unlike the p-i-n, the APD is always biased at a voltage that is close to its breakdown. Through the carrier impact ionisation process, an APD provides more electron-hole pairs from the same amount of photogenerated carriers, compared to a p-in photodiode. Therefore, if we assume the same optical absorption volume dimension for both a p-i-n and an APD, the external quantum efficiency of the APD can be written as

$$\eta_{ext} = M \cdot (1 - R)(1 - e^{-\alpha d}) \tag{2.15}$$

where M is the avalanche gain obtained through carrier impact ionisation. The gain M is given by the expression

$$M = \frac{i_{photo} - i_{dark}}{i_{primary,photo} - i_{primary,dark}}$$

(2.16)

where  $i_{photo}$  and  $i_{dark}$  are the multiplied photocurrent and dark current, while  $i_{primary,photo}$  and  $i_{primary,dark}$  are the primary photocurrent and dark current measured prior the onset of carrier multiplication (*M*=1).

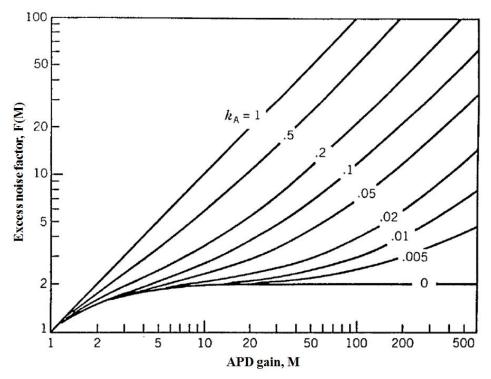

The stochastic nature of the impact ionisation process leads to a notable spread of the total number of carriers generated by an injected electron-hole pair under a specific electric field, giving rise to excess noise which is characterised by the excess noise factor, F. The statistical nature of this impact ionisation process results in fluctuations in the number of secondary carriers (electron – hole pairs) generated from each parent carrier, which in turn leads to fluctuations in the APD gain [6]. Thus, while M can be

very large, the actual usable value of M for fibre optic receivers is normally limited to between 10 and 20 depending on the materials and device structures used. This gain fluctuation will cause variation in the APD output current and increase the APD's total shot noise power above that of the multiplied shot noise power. The excess noise factor, F(M), is a measure of the standard deviation of the multiplication gain over its mean square value

$$F(M) = \frac{\langle M^2 \rangle}{\langle M \rangle^2}$$

(2.17)

According to the local impact ionisation model developed by McIntyre [6] in which carrier impact ionisation coefficients were assumed to be only a function of electric field strength, F(M) can be written as

$$F(M) = kM + (1-k)\left(2 - \frac{1}{M}\right)$$

(2.18)

Where  $k = \beta/\alpha$  ( $\beta < \alpha$ ) or  $k = \alpha/\beta$  ( $\alpha < \beta$ ). Based on the local field theory, larger difference between carrier impact ionisation coefficients leads to lower excess noise in an APD, as shown in Figure 2.5.

Figure 2.5. Excess noise factor predicted by McIntyre's local field theory as a function of gain (M) and various k ratios [3].

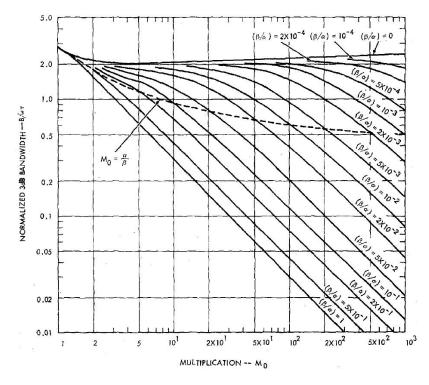

Another phenomenon associated with carrier multiplication is the effect of the gain process on bandwidth. Detailed research on this problem was performed by Emmons [7], who showed that the frequency-dependent gain can be approximated by the expression

$$M(\omega) = \frac{M_0}{\sqrt{1 + (\omega M_0 k \tau)^2}}$$

(2.19)

where  $M_0$  is the dc gain, and  $\tau$  is approximately (within a factor of ~2) the carrier transit time across the multiplication region. Figure 2.6 shows the 3-dB bandwidth of the photodiode plotted as a function of the multiplication gain M<sub>0</sub> and the parameter *k*. Superimposed on these curves is the curve  $M_0 = \alpha/\beta$ .

Above this curve, where  $M_0 < \alpha/\beta$ , multiplication has little effect on bandwidth and current multiplication is obtained without any substantial reduction in bandwidth. It is important to note that this condition, which maximises the bandwidth in the avalanche region, also minimises the noise produced by the avalanche multiplication mechanism.

On the other hand, for  $M_0 > \alpha/\beta$ , the curves are straight lines, indicating a constant gain-bandwidth product (GBP), and a dependence of multiplication on bandwidth. Therefore, Emmons's finding imposed an upper limit on the APD bandwidth, in terms of the gain-bandwidth product.

Figure 2.6. APD bandwidth as a function of multiplication gain and the parameter k, as predicted by local field theory [7].

According to the local field model, the performance of an APD is determined by its k value, which is an intrinsic property of each specific material. As the APD multiplication layer is thinned, a higher electric field is required to achieve a specific gain value than in a thicker device. The impact ionisation rate curves for electrons and holes merge at high electric field, causing k to approach unity. Therefore, it is expected that the excess noise would increase as the multiplication thickness decreases. The opposite, however, has been observed experimentally [8]. This discrepancy found a solution in the non-local model, which takes into account the history of the carrier prior to the impact ionisation event. The reduction of F(M) in thin multiplication layer APDs has been attributed to the pronounced dead-space effect [9]. When a carrier, either a hole or an electron, initially enters the high field region it must travel for a certain distance, the so-called dead-space, before it gains enough energy from the electric field to undergo a subsequent impact ionisation event. In thick devices this distance is negligible compared to the total device thickness; therefore the dead-space plays a minor role in the noise characteristic of thick APDs. The effect of dead-space starts to influence the performance in thin multiplication regions for which the dimension of the deadspace becomes comparable. As a result, the impact ionisation events are more localised in a specific spatial range in the gain region and the impact ionisation events are more deterministic [10]. This reduces the variation in numbers of impact ionisation events every carrier will cause, which lowers the excess noise related to the ionisation process.

Therefore, to achieve low noise and high-speed APDs materials must be used that have lower ionisation coefficient ratio (k) value and thin multiplication regions (dead-space effect).

Another important point is that the gain mechanism of an avalanche photodiode is very temperature-sensitive because of the temperature dependence of the electron and hole ionisation rates. This temperature dependence is particularly critical at high bias voltage, where a small change in temperature can cause large variation in gain [2]. As the temperature in the semiconductor device is reduced, the lattice vibrational energy is also reduced, and so is the scattering of electrons and holes. This increases the energy of the carriers and hence their ionisation rates. As a consequence of the change in ionisation coefficients for a given temperature decrease, the electric field will have to decrease to maintain breakdown. The value of the breakdown voltage drops with decreasing temperature, *T*, following the formula [11]

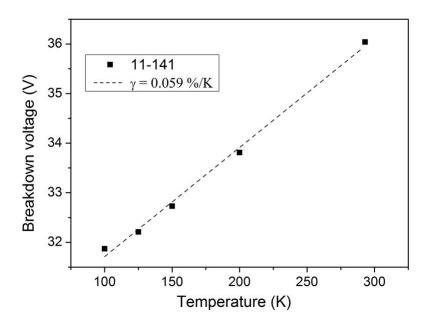

$$\frac{\Delta V_{BD}}{V_{BD,RT}} = \gamma T \tag{2.20}$$

where  $V_{BD,RT}$  is the breakdown voltage at room temperature and  $\gamma$  is an index typical of the device under observation.

#### 2.3.1 Advantage of an APD over a p-i-n photodiode

In fibre optic communication systems the photodiode is generally required to detect very weak optical signals. This requires the optimisation of the photodetector and its amplification circuit so that a given signal-to-noise ratio (S/N) is maintained. This ratio at the output of an optical receiver is defined by

$$\frac{S}{N} = \frac{\text{signal power from photocurrent}}{\text{photodetector noise power + amplifier noise power}}$$

(2.21)

It is clear that to obtain a high S/N ratio, the photodetector must have a high quantum efficiency to generate a large signal power and the photodetector and amplifier noise should be kept as low as possible.

For a p-i-n photodiode the mean square signal current  $\langle i_s^2 \rangle$  is

$$\langle i_s^2 \rangle = \langle i_{ph}^2(t) \rangle \tag{2.22}$$

Where  $i_{ph}(t)$  is the signal component related to the incident optical power by

$$i_{ph}(t) = \frac{q\eta_{ext}}{h\nu} P_{inc}(t)$$

(2.23)

For an APD

$$\langle i_s^2 \rangle = \langle i_{ph}^2(t) \rangle M^2 \tag{2.24}$$

the signal power term is boosted by a factor of  $M^2$ , representing the average of the avalanche gain, which greatly enhances the receiver sensitivity.

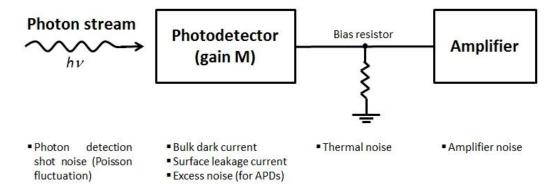

The noise current determines the minimum optical power level that can be detected, because the optical receiver must have the ability to discriminate between the minimum detectable input optical power and the noise generated by the integrated receiver itself within a working bandwidth. The noise is described in terms of noise power spectrum density  $\langle i^2 \rangle$ , which is the quadratic mean of the noisy current within a unity frequency bandwidth. Different noise sources affect the signal-to-noise ratio. For photodiodes operating at high frequencies, thermal noise and shot noise are two main types of noise sources.

Thermal or Johnson noise originates from the Brownian motion of carriers that exists in any type of resistive components. It is expressed by

$$\langle i_T^2 \rangle = \frac{4k_B T}{R_L} B \tag{2.25}$$

Where *B* is the operation bandwidth, *T* is the absolute temperature,  $k_B$  is Boltzmann's constant, and  $R_L$  is the load resistance.

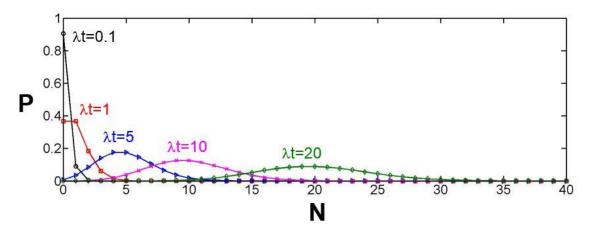

The shot noise arises from the statistical nature of the production and collection of photoelectrons when an optical signal is incident on a photodetector, and it follows a Poisson distribution. It can be expressed by

$$\langle i_Q^2 \rangle = 2qI_{ph}BM^2F(M) \tag{2.26}$$

Where *q* is the electron charge,  $I_{ph}$  is the average photocurrent due to the signal power, F(M) is the excess noise factor associated with the random nature of the avalanche process, and *M* is the avalanche gain. For p-i-n photodiodes *M* and F(M) are unity.

As already mentioned, the dark current in a photodiode is a source of noise. This current is a combination of bulk and surface currents. The bulk component  $(i_{DB})$  arises from electrons and holes which are thermally generated in the junction of a photodiode. In an avalanche photodiode these carriers also get accelerated by the high electric field, and are therefore multiplied. The mean square value of this current is given by

$$\langle i_{DB}^2 \rangle = 2qI_D M^2 F(M)B \tag{2.27}$$

where  $I_D$  is the primary (unmultiplied) detector bulk current. Regarding the noise associated to the surface leakage current ( $i_{DS}$ ), that depends on surface defects, bias voltage, and surface area, it can be expressed by

$$\langle i_{DS}^2 \rangle = 2qI_L B \tag{2.28}$$

where  $I_L$  is the surface leakage current. This component is not affected by the avalanche gain, since the avalanche multiplication is a bulk effect.

Figure 2.7 shows a schematic of a detection system with the associated noise sources.

Figure 2.7. Schematic of a detection system with the related noise sources for each component.

Based on the above discussion, for the basic detection system shown in Figure 2.7, it is possible to write the S/N ratio as

$$\frac{S}{N} = \frac{\left(\frac{q\eta_{ext}}{h\nu} P_{inc}\right)^2}{\left[2q(I_{ph} + I_D)F(M) + 2q\frac{I_L}{M^2} + \frac{4k_BT}{R_LM^2}\right]B}$$

(2.29)

In the case of a p-i-n photodiode, where F(M) and M are unity, the dominating source of noise current is that of the detector load resistor (*i*<sub>T</sub>). Therefore, it is desirable to have a high load resistance to reduce the thermal noise, but this increases the RC constant, which reduces the bandwidth of the detector and thus degrades the S/N ratio. For APDs, the thermal noise is reduced by a factor of  $M^2$  which also enhances the S/N ratio. The total shot noise term is, however, multiplied by a factor F(M). A noise penalty therefore will occur as F(M) increases with M. Thus for a given set of operating conditions, there exists an optimum value of M for which the S/N ratio is a maximum. This is mainly true for low level light,

where the APDs show a high S/N ratio compared to p-i-n photodiodes. Furthermore, higher dark and surface leakage current levels set a limit of achievable sensitivity of the APD receiver even if F(M) is low. Consequently, these terms must be minimised to achieve high APD receiver sensitivity.

#### 2.4 Single-photon detectors

A single-photon detector is an extremely sensitive device capable of registering the individual photons. Photons have so many properties that its detection can be employed in a wide range of applications such as quantum information, time-correlated single-photon counting (TCSPC) applications, etc. These applications demand stringent requirements in terms of signal-to-noise ratio, detection efficiency, spectral range, etc. It is because of all of these requirements that different technologies (photomultiplier tubes, semiconductor avalanche photodiodes, superconducting nanowires, etc.) have been employed to detect single-photons. In this section a review of these technologies is presented with a description of their main advantages and disadvantages, and is mainly focused on semiconductor single-photon detection in in the infrared spectral range.

## 2.4.1 Photomultiplier tube (PMT) and Microchannel plates

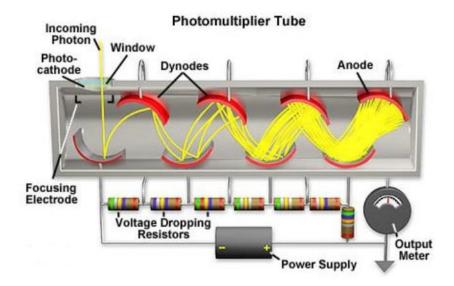

A basic PMT consists of a vacuum tube with a photocathode for light absorption, from which electrons are liberated through the photoelectric effect (the energy of the incident photon must exceed the work function of the photocathode material) [12], [13]. Depending on the material composition of the photocathode, PMTs can be effective for detection of light at varying wavelengths. A schematic representation of a typical PMT structure is shown in Figure 2.8.

Figure 2.8. Schematic representation of a photomultiplier tube (PMT) [12].

Photomultipliers acquire light through a glass or quartz window that covers a photosensitive surface, called a photocathode, which then releases electrons that are multiplied by electrodes known as metal channel dynodes. At the end of the dynode chain is an anode or collection electrode. Over a very large range, the current flowing from the anode to ground is directly proportional to the photoelectron flux generated by the photocathode. Each of dynodes is biased at a greater positive voltage than the one before, producing a macroscopic current pulse of  $> 10^6$  electrons.

There are, however, several disadvantages with such devices, including relatively large devices with poor mechanical stability and low SPDE (usually a few % in the infrared). PMTs also require high bias voltages in the order of 1 kV and their timing jitter (fluctuation of transit time) is typically in the region of 1 ns. Therefore, in many modern photon counting applications, PMTs are far from ideal where higher efficiencies and lower jitter are required. However, PMTs generally do not have a spectrally dependent instrumental response (unlike some semiconductor-based detectors), and much improvement has been seen in miniaturisation of the PMT packages [14].

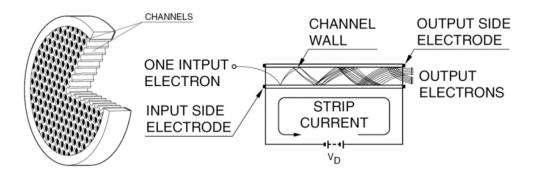

An alternative configuration is the microchannel plate photomultiplier tube, see Figure 2.9, where glass capillaries are fused in parallel and coated with a secondary electron emitting material to achieve a single continuous dynode under a bias voltage [15]. Microchannel plate PMTs offer improved timing jitter over basic PMTs, down to ~20 ps at FWHM [15].

Figure 2.9. Schematic representation of a Microchannel plate [15].

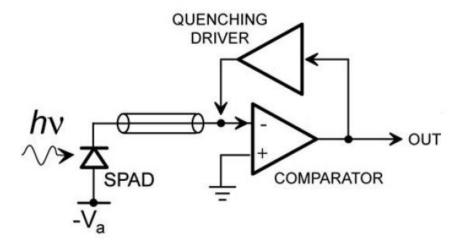

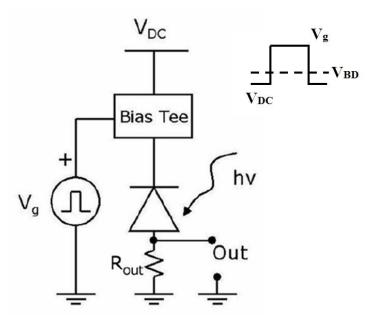

#### 2.4.2 The single-photon avalanche diode (SPAD)

avalanche photodiodes (APDs) Semiconductor have typical advantages the characterising the solid-state devices (small size, low bias voltage, low power consumption, and reliability). When the APD is operating in a linear mode (which means that the output current is proportional to the input optical power) it has an internal gain. However, this internal gain is not sufficient to detect single-photons. To overcome this problem the APD can be used above the avalanche breakdown, in the socalled Geiger mode of operation (since their operation principal is similar to that of the Geiger-Muller detectors, in which particle emission from radioactive materials gives rise to an avalanche of carriers from ionised gas atoms) [16]. When the APD is operating in Geiger mode it is called a Single Photon Avalanche Diode (SPAD) or triggered avalanche detector.

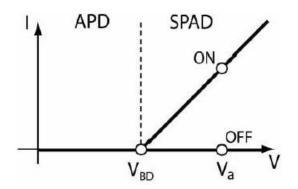

Investigation of the physics of avalanche breakdown in SPADs started back in the 1960s at the Shockley laboratory [17], [18], where it was observed that a p-n junction reverse biased above the breakdown level produced a macroscopic voltage pulse triggered by the absorption of single optical photons. Fundamental contributions to the understanding of the avalanche phenomenon and of its statistical properties were given by McIntyre and Webb in 1970s [19]–[21]. However, the first custom-designed SPAD was proposed and demonstrated by Cova *et al.* in 1981 [22], and it was a thin-junction Si SPAD. As pointed out in Figure 2.10, SPAD operation is radically different from that of ordinary APDs, which are biased near to the breakdown voltage  $V_{BD}$ , but below it. In APDs, avalanche multiplication is exploited to produce linear amplification of the primary photogenerated electrical signal.

Figure 2.10. Schematic of current-voltage characteristic for a APD and SPAD operation in the reverse I-V characteristic of a p-n junction [22].

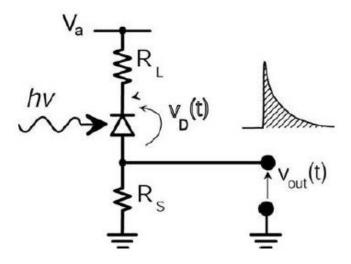

The behaviour of a SPAD is similar not to an amplifier, but to a bistable circuit as shown in Fig. 2.10. When the SPAD device is biased at voltage  $V_a$  above the  $V_{BD}$ (Geiger-mode) no current flows (OFF-STATE). In the junction depletion layer the electric field is very high, but no free carriers are present. When even a single carrier is injected into the high-field region, it is strongly accelerated and gains sufficient kinetic energy that, on collision with an atom in the lattice, it frees an electron from its bound state and promotes it into the conduction band, leaving a hole in the valence band. This phenomenon is known as impact ionisation, as described previously. These generated carriers may undergo further impact ionisation events, initiating an avalanche of carriers. A self-sustaining current (in the mA range) is then triggered (ON-STATE). The current is limited to a constant level by the space charge effect, which is proportional to the excess bias voltage  $V_{EX} = V_a - V_{BD}$ . The device remains in this ON-STATE until the avalanche is quenched by an external circuit, which drives the applied voltage down to below  $V_{BD}$ . The detector is insensitive to any subsequent photons arriving in the time interval from the avalanche onset to the voltage reset, which is the detector dead time. It is evident that describing the magnitude of the gain in the case of SPADs does not make sense, just as in the case of a bistable circuit.

It has already been shown in this chapter, that the performance of a photodiode is related to the intrinsic physical properties of the semiconductor material used (band gap, intrinsic carrier concentration, absorption coefficient, etc.). For a SPAD, these properties are also important in conjunction with other physical effects. It is possible to define key parameters for a SPAD as the single-photon detection efficiency (SPDE), dark count rate (DCR), noise equivalent power (NEP), afterpulsing and the timing jitter.

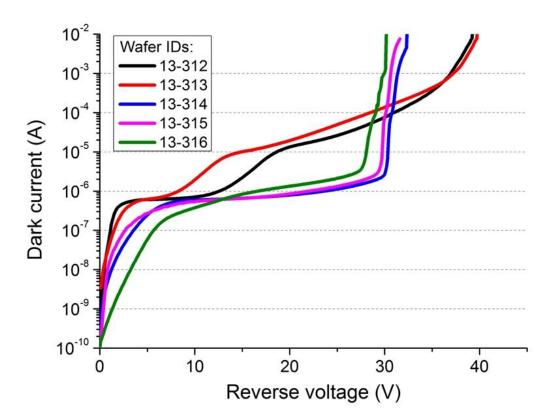

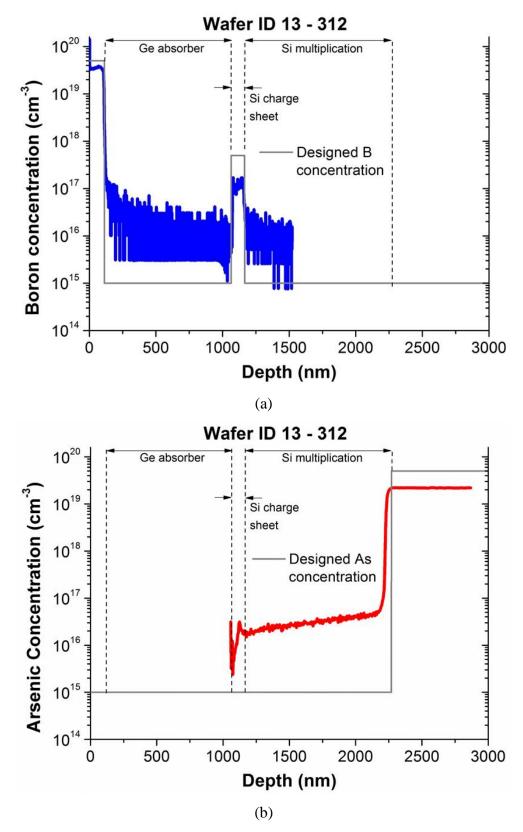

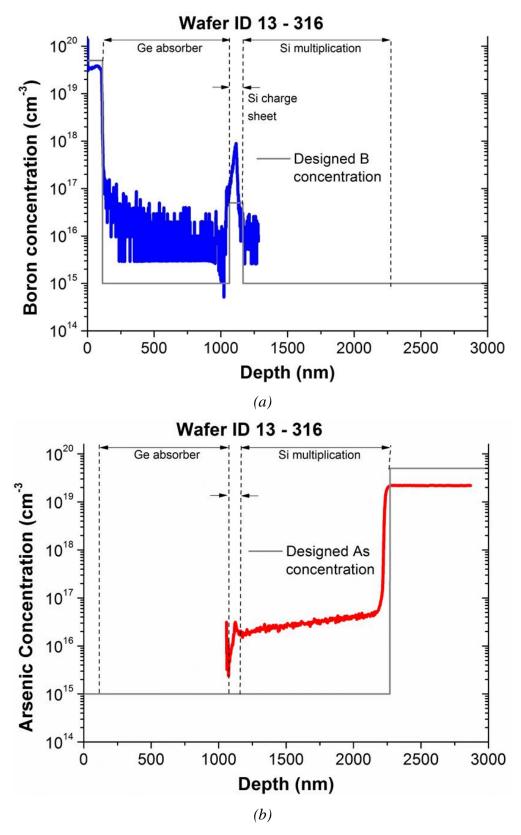

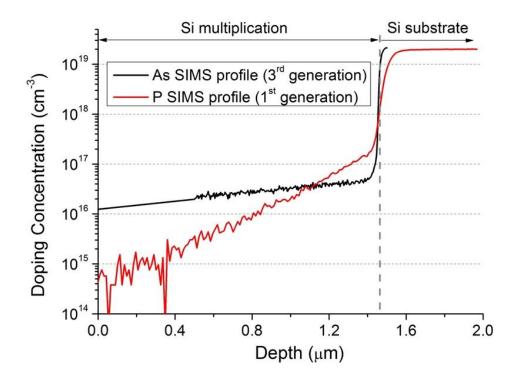

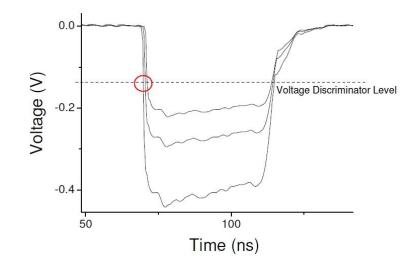

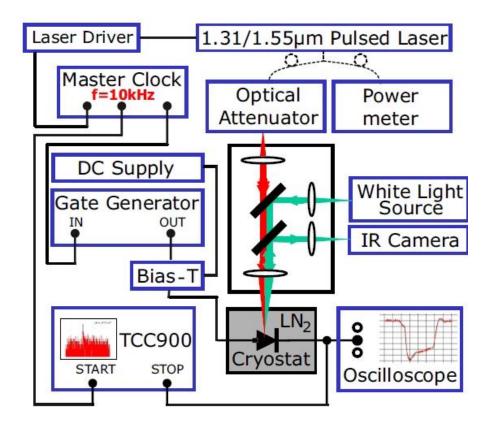

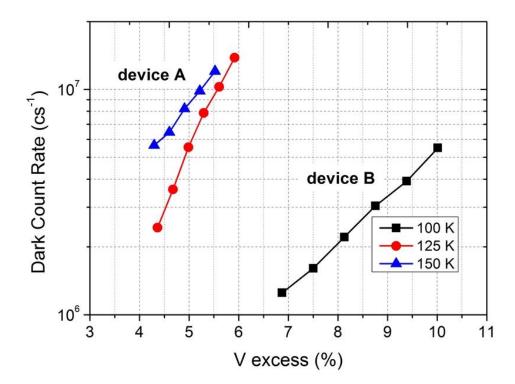

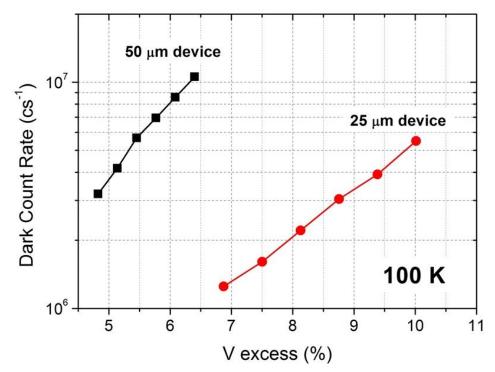

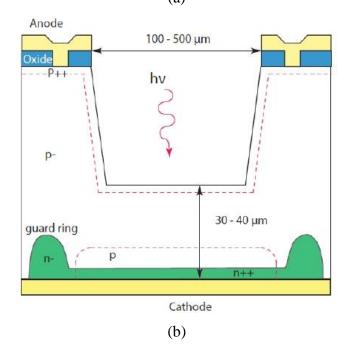

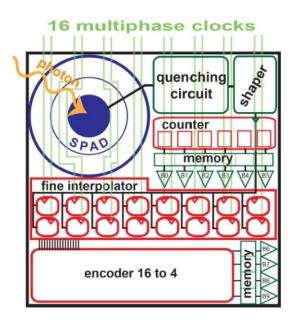

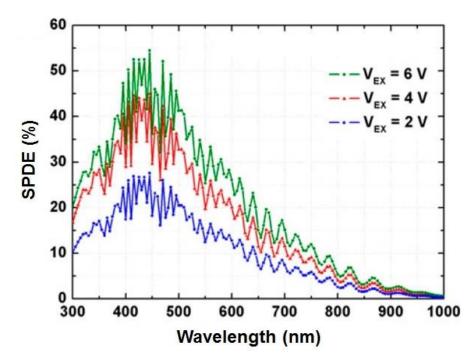

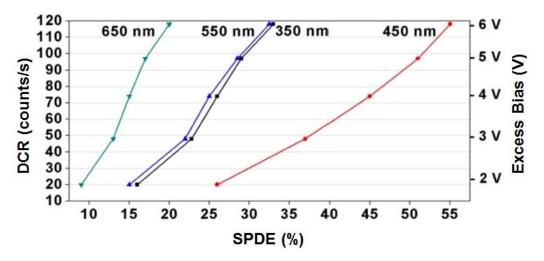

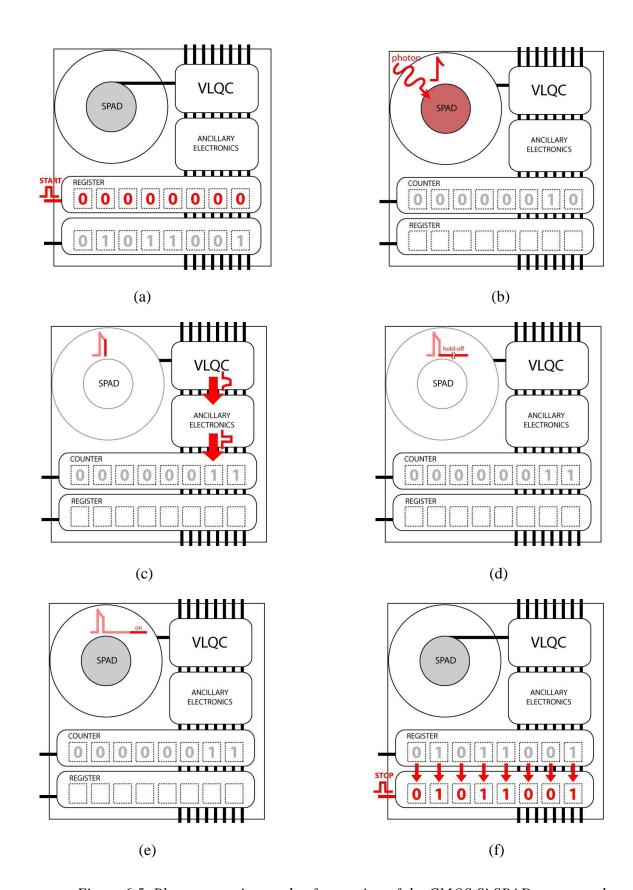

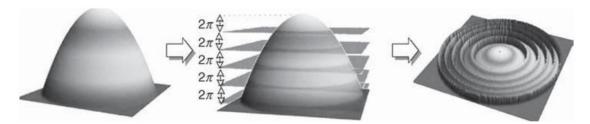

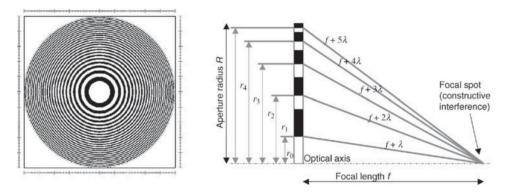

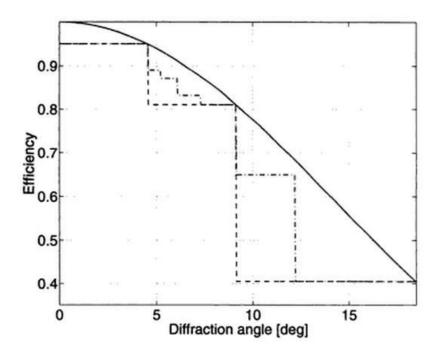

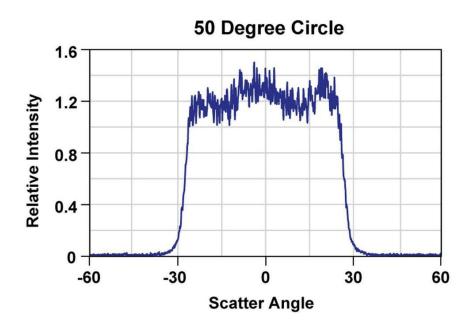

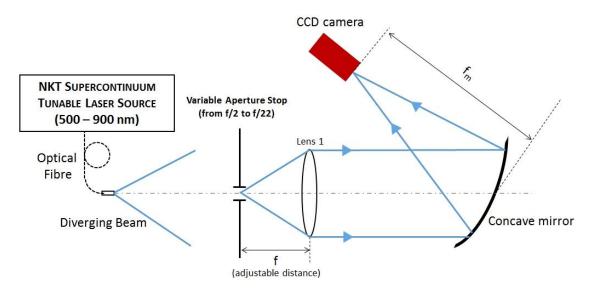

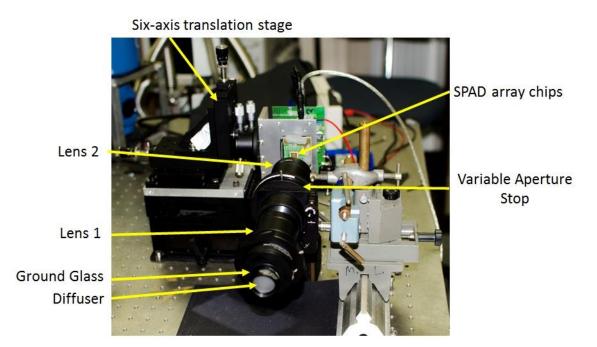

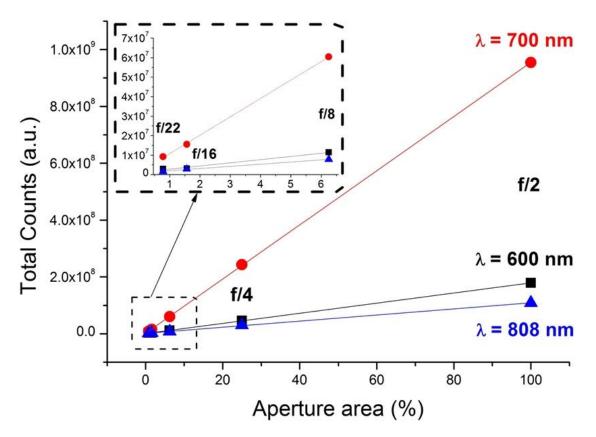

## 2.4.2.1 Figures of merit of a SPAD