## DATA LAYOUT TYPES: A TYPE-BASED APPROACH TO AUTOMATIC DATA LAYOUT TRANSFORMATIONS FOR IMPROVED SIMD VECTORISATION

by

Artjoms Šinkarovs

Submitted for the degree of Doctor of Philosophy at Heriot Watt University on Completion of Research in the School of Mathematical and Computer Sciences 5th August 2015

The copyright in this thesis is owned by the author. Any quotation from this thesis or use of any of the information contained in it must acknowledge this thesis as the source of the quotation or information.

## Abstract

The increasing complexity of modern hardware requires sophisticated programming techniques for programs to run efficiently. At the same time, increased power of modern hardware enables more advanced analyses to be included in compilers. This thesis focuses on one particular optimisation technique that improves utilisation of vector units. The foundation of this technique is the ability to chose memory mappings for data structures of a given program.

Usually programming languages use a fixed layout for logical data structures in physical memory. Such a static mapping often has a negative effect on usability of vector units. In this thesis we consider a compiler for a programming language that allows every data structure in a program to have its own data layout. We make sure that data layouts across the program are sound, and most importantly we solve a problem of automatic data layout reconstruction. To consistently do this, we formulate this as a type inference problem, where type encodes a data layout for a given structure as well as implied program transformations. We prove that type-implied transformations preserve semantics of the original programs and we demonstrate significant performance improvements when targeting SIMD-capable architectures. To *Elizabeth*,

Пожалуй, лучшей из всех Елизавет.

## Acknowledgements

I wish to thank both of my supervisors *Sven-Bodo Scholz* and *Greg Michaelson* for their valuable ideas and great patience.

Ideas presented in Chapter 3 are based on a project which started in terms of "Google Summer Of Code 2010", with Artjoms Šinkarovs being a student and Richard Güenther being a mentor. I wish to thank the GCC community for their help during the coding. Special thanks to Richard Güenther, Richard Henderson, Joseph S. Myers and Jakub Jelinek for their valuable comments and patch reviews.

Finally, many thanks to all my friends and family members who have supported me during my research.

# Contents

| 1 | Intr | roduction                                      | 1  |

|---|------|------------------------------------------------|----|

|   | 1.1  | Thesis                                         | 4  |

|   | 1.2  | Approach                                       | 4  |

|   | 1.3  | Contributions                                  | 4  |

|   | 1.4  | Thesis structure                               | 5  |

| 2 | Sta  | te of the art                                  | 6  |

|   | 2.1  | Vector hardware basics                         | 6  |

|   | 2.2  | History of parallel and vector hardware        | 7  |

|   | 2.3  | Vector architectures today                     | 9  |

|   |      | 2.3.1 CPUs 1                                   | 10 |

|   |      | 2.3.2 Graphics Processing Units (GPUs)         | 11 |

|   | 2.4  | SIMD functionality                             | 12 |

|   |      | 2.4.1 Classes of SIMD instructions             | 12 |

|   |      | 2.4.2 Known difficulties                       | 15 |

|   | 2.5  | Programming models 1                           | 16 |

|   |      | 2.5.1 Programming languages overview           | 16 |

|   |      | 2.5.2 Low-level approaches to SIMD programming | 17 |

|   |      | 2.5.3 Annotations                              | 19 |

|   |      | 2.5.4 Extensions of the existing languages     | 20 |

|   |      | 2.5.5 Fully implicit parallelism               | 21 |

|   |      | 2.5.6 New languages                            | 24 |

|   |      | 2.5.7 High productivity languages              | 25 |

|   | 2.6  | Data layout transformations                    | 26 |

|   |      | 2.6.1 Data distribution on clusters            | 26 |

|   |      | 2.6.2 Optimisation of cache misses             | 26 |

|   |      | 2.6.3 Vectorisation                            | 27 |

|   | 2.7  | Summary 2                                      | 29 |

| 3 | Por  | table vectorisation as a backend               | 80 |

|   | 3.1  | Introduction                                   | 30 |

|   | 3.2  | Motivation                                     | 31 |

|   |      | 3.2.1 Move To Front (MTF) Algorithm            | 31 |

|   | 3.3  | C vector extensions                            | 35 |

|   |     | 3.3.1 Vector types                                             |

|---|-----|----------------------------------------------------------------|

|   |     | 3.3.2 Vector value                                             |

|   |     | 3.3.3 Vector operations                                        |

|   |     | 3.3.4 Mixed vector/scalar operations                           |

|   |     | 3.3.5 Vector indexing                                          |

|   |     | 3.3.6 Vector comparisons                                       |

|   |     | 3.3.7 Vector permutation                                       |

|   |     | 3.3.8 Vector operation performance                             |

|   |     | 3.3.9 Still missing 39                                         |

|   | 3.4 | Case-study                                                     |

|   | 3.5 | Related work 41                                                |

|   |     | 3.5.1 New languages e.g. ISPC                                  |

|   |     | 3.5.2 Library-based solutions                                  |

|   |     | 3.5.3 Intrinsics to intrinsics mapping 42                      |

|   |     | 3.5.4 $C++$ standard proposal                                  |

|   |     | 3.5.5 Automatic vectorisation                                  |

|   |     | 3.5.6 Virtual instruction set                                  |

|   |     | 3.5.7 OpenCL                                                   |

|   | 3.6 | Extended standard                                              |

|   |     | 3.6.1 General principle                                        |

|   |     | 3.6.2 Vector types                                             |

|   |     | 3.6.3 Declaration and initialisation                           |

|   |     | 3.6.4 Vector subscript                                         |

|   |     | 3.6.5 Arithmetic operations                                    |

|   |     | 3.6.6 Future extensions                                        |

|   |     | 3.6.7 Things to consider                                       |

|   | 3.7 | Towards the existing instruction sets                          |

|   |     | <b>3.7.1</b> Intel                                             |

|   |     | <b>3.7.2</b> Altivec                                           |

|   |     | 3.7.3 Arm NEON extensions                                      |

|   | 3.8 | Conclusions                                                    |

|   | 3.9 | Future work                                                    |

|   |     |                                                                |

| 4 | · · | out-type system62Let a better65                                |

|   | 4.1 | Introduction                                                   |

|   | 4.2 | Core programming language                                      |

|   |     | 4.2.1 Map                                                      |

|   |     | 4.2.2 Reduce                                                   |

|   | 4.9 | 4.2.3 Vector operations                                        |

|   | 4.3 | Running example    70      4.2.1    The low ideas in a method! |

|   | 1 4 | 4.3.1 The key ideas in a nutshell                              |

|   | 4.4 | A type system for data layouts                                 |

|   |     | 4.4.1 Example                                                  |

|   |             | 4.4.2 Environments                                | 74  |

|---|-------------|---------------------------------------------------|-----|

|   |             | 4.4.3 Ownership of $idx(k)$ and $\triangle$ types | 75  |

|   |             | 4.4.4 Type rules                                  | 76  |

|   | 4.5         | Layout inference                                  | 79  |

|   |             | 4.5.1 The inference algorithm                     | 80  |

|   |             | 4.5.2 Sample layout inference                     | 90  |

|   |             | 4.5.3 Inference complexity                        | 93  |

|   |             | 4.5.4 Parameters of $idx$ and $\triangle$ types   | 94  |

|   | 4.6         | Initial evaluation                                | 94  |

|   |             | 4.6.1 N-body                                      | 96  |

|   |             | 4.6.2 Mandelbrot                                  | 100 |

|   |             | 4.6.3 Summary                                     | 102 |

|   | 4.7         | Related work                                      | 102 |

|   | 4.8         | Conclusions                                       | 105 |

| 5 | Pro         | gram transformation and proof of correctness      | 106 |

| 0 | 5.1         | Introduction                                      |     |

|   | 5.2         | Program transformation                            |     |

|   | 0.2         | 5.2.1 CONST                                       |     |

|   |             | 5.2.2 SEL                                         |     |

|   |             | 5.2.3 Primitive functions PRF                     |     |

|   |             | 5.2.4 MAP                                         |     |

|   |             | 5.2.5 REDUCE                                      |     |

|   |             | 5.2.6 IF                                          |     |

|   |             | 5.2.7 FUNDEF, APP, LET and LETREC                 | 117 |

|   |             | 5.2.8 Transformation summary                      |     |

|   | 5.3         | ·                                                 |     |

|   |             | 5.3.1 Correctness criteria                        | 121 |

|   | 5.4         | Proof of correctness                              | 122 |

|   | 5.5         | Application                                       | 130 |

|   | 5.6         | Related work                                      | 131 |

|   | 5.7         | Conclusions                                       | 132 |

| 6 | Imr         | plementation 1                                    | 133 |

| U | 6.1         | SAC and SAC- $\lambda$ relation                   |     |

|   | 0.1         | 6.1.1 De-sugaring SAC into SAC- $\lambda$         |     |

|   |             | 6.1.2 Non-de-sugarable differences                |     |

|   | 6.2         | Transformations in details                        |     |

|   | J. <b>.</b> | 6.2.1 Cost model                                  |     |

| _ | P           |                                                   |     |

| 7 |             |                                                   | 147 |

|   | 7.1         | Methodology                                       |     |

|   |             | 7.1.1 Presentation and measurements               | 148 |

|   | 7.2 | Vector addition                                                                                            |

|---|-----|------------------------------------------------------------------------------------------------------------|

|   | 7.3 | Vector sum                                                                                                 |

|   | 7.4 | Matrix multiplication                                                                                      |

|   | 7.5 | <b>N-body</b>                                                                                              |

|   | 7.6 | Mandelbrot                                                                                                 |

|   | 7.7 | Spectral norm                                                                                              |

|   | 7.8 | Reverse complement                                                                                         |

|   | 7.9 | Summary                                                                                                    |

|   |     | •                                                                                                          |

| 8 | Con | nclusions and future work 169                                                                              |

| 8 |     | Inclusions and future work     169       Layout types generalisations     170                              |

| 8 |     |                                                                                                            |

| 8 |     | Layout types generalisations                                                                               |

| 8 |     | Layout types generalisations1708.1.1Current types172                                                       |

| 8 |     | Layout types generalisations1708.1.1Current types1728.1.2Adding new type173                                |

| 8 |     | Layout types generalisations1708.1.1Current types1728.1.2Adding new type1738.1.3Reverse-friendly layout174 |

## Publications

Some ideas and figures have appeared previously in the following publications.

### Journal papers

- Artjoms Šinkarovs, Sven-Bodo Scholz, Robert Bernecky, Roeland Douma, and Clemens Grelck. SAC/C formulations of the all-pairs N-body problem and their performance on SMPs and GPGPUs. *Concurrency and Computation: Practice and Experience*, 26(4):952–971, 2014. http://ashinkarov.github. io/publications/sexynbody.pdf

- Artjoms Šinkarovs and Sven-Bodo Scholz. Type-driven data layouts for improved vectorisation. Concurrency and Computation: Practice and Experience, 2015. http://dx.doi.org/10.1002/cpe.3501 (visited on June 2015)

### **Conference** papers

- Artjoms Šinkarovs and Sven-Bodo Scholz. Portable support for explicit vectorisation in C. In 16th Workshop on Compilers for Parallel Computing (CPC'12), 2012

- Artjoms Šinkarovs and Sven-Bodo Scholz. Data layout inference for code vectorisation. In International Conference on High Performance Computing & Simulation, HPCS 2013, Helsinki, Finland, July 1-5, 2013, pages 527-534, 2013. http://ashinkarov.github.io/publications/data-layouts.pdf

- 3. Artjoms Šinkarovs and Sven-Bodo Scholz. Semantics-preserving data layout transformations for improved vectorisation. In *Proceedings of the 2Nd ACM SIGPLAN Workshop on Functional High-performance Computing*, FHPC '13, pages 59–70, New York, NY, USA, 2013. ACM

### Extended abstracts

Artjoms Šinkarovs and Sven-Bodo Scholz. Data layout inference for code vectorisation. In The 24th symposium on Implementation and Application of Functional Languages, IFL 2012, 2012  Artjoms Šinkarovs and Sven-Bodo Scholz. Functionally redundant declarations for improved performance portability. In *The 25th symposium on Implementation and Application of Functional Languages*, IFL 2013, 2013

# Notations and definitions

| N              | Natural numbers starting with zero: $0, 1, 2, \ldots$                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbb{Z}_+$ | Natural numbers starting with one: $1, 2, 3, \ldots$                                                                                                                                                                                                                                                                                                                                                                                                      |

| div            | A binary function denoting integer division. In the context of this thesis it is applied on $\mathbb{N}$ numbers only. Notation is: $a \operatorname{div} b$ , which denotes $\lfloor \frac{a}{b} \rfloor$ . For example: 7 div $3 \equiv 2$ .                                                                                                                                                                                                            |

| mod            | A binary function denoting modulo operation. In the con-<br>text of this thesis it is applied on $\mathbb{N}$ numbers only. Notation<br>is: $a \mod b$ , which denotes $a - \lfloor \frac{a}{b} \rfloor b$ . For example: $7 \mod 3 \equiv 1$ .                                                                                                                                                                                                           |

| data layout    | A mapping of a data structure into flat memory.                                                                                                                                                                                                                                                                                                                                                                                                           |

| $e :: \tau$    | An expression $e$ has data layout encoded by $\tau$ .                                                                                                                                                                                                                                                                                                                                                                                                     |

| $e$ : $\sigma$ | An expression $e$ is of type $\sigma$ , e.g. integer, a vector of integers, etc.                                                                                                                                                                                                                                                                                                                                                                          |

| CPU            | Central Processing Unit (CPU) is an electronic device<br>within a computer that executes instructions of the speci-<br>fied program performing arithmetic, logical, input/output<br>operations specified by the program.                                                                                                                                                                                                                                  |

| GPU            | Graphics Processor Unit (GPU) is an electronic device<br>within a computer that is designed to accelerate creation of<br>images that will be output on a display. Nowadays GPUs<br>are used not only for display-related graphics computa-<br>tions but also for general applications. This approach is<br>usually called General-Purpose computing on Graphics<br>Processing Units (GPGPU) and it is being actively used<br>in high-performance systems. |

| HPC  | High Performance Computing (HPC) is an area of research<br>and engineering that has to do with very high-level com-<br>putation capacities. Usually, the interest of HPC lies in<br>building supercomputers and running applications on them<br>efficiently. |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISA  | Instruction Set Architecture (ISA) specifies a set of com-<br>mands available for a given CPU.                                                                                                                                                               |

| SIMD | Single Instruction, Multiple Data (SIMD), is a class of<br>parallel computers in Flynn's taxonomy [43]. It describes<br>computers with multiple processing elements that perform<br>the same operation on multiple data points simultaneously.               |

| SIMT | Single Instruction, Multiple Thread (SIMT) is an execution<br>model and abstraction on top of SIMD where multiple<br>independent threads execute concurrently using a single<br>instruction. Used primarily in GPUs.                                         |

| SPMD | Single Program, Multiple Data (SPMD) is a technique of<br>parallel programming when one and the same task is being<br>executed in parallel on different input data.                                                                                          |

## Chapter 1

## Introduction

The problems are solved, not by giving new information, but by arranging what we have known since long.

Ludwig Wittgenstein [147]

According to the TOP500 (November 2014) [138] the world fastest supercomputer achieves about 60% of its peak performance. This figure is obtained using a set of benchmarks called LINPACK [37] which is considered by most supercomputer manufacturers while building the machines. Realistically, this number can be treated as performance upper bound of a given machine. Such a difference between the peak and sustained performances is usually referred as "performance gap" [118]. HPC machines cost millions of pounds, and in the light of exascale computing, such a price is likely to increase. Losing 40% of the performance is an economical waste, therefore there is an increasing need to tackle this problem and close the performance gap.

H. Seutter in his "Free lunch is over" manifesto [135] gives accounts for the roots of the problem in the context of CPUs. He demonstrates that the usual assumption that next generation CPUs will get faster does not hold anymore. Instead of CPUs with higher frequencies manufacturers switched to CPUs with higher number of cores. F. Pollack in [111] formulates his famous "rule" which says that performance of uni-processors increases with the square root of their complexity. R. Ronen et. al in [114] demonstrate that single-threaded performance does not scale with frequency and area. Memory latencies and bandwidth would not scale as well. Power density of a microprocessor is reaching levels close to nuclear reactors. As a consequence, old programs as they are, originally designed for sequential hardware, do not benefit from new multiprocessor architectures because the code is not aware of newly available resources.

Nowadays modern hardware trends propose even more radically diverse architecture designs. While GPUs or coprocessors offer higher computing power at lower costs, their success on the mass market suddenly makes the overall design of ordinary computers not that different from HPC machines. This brings all the existing HPC challenges, most importantly the performance gap, to ordinary machines.

The big questions are how to write new programs for diverse hardware architectures and how to make the existing programs run efficiently? When a supercomputer costs billions of pounds and is bought to run a single program, one can hire a team of programmers to optimise the application to perfection. Although, even in such idealistic scenario, at the example of TOP500 and LINPACK we can see how challenging such a task actually is. For the clusters built of multicores, the gap is relatively small: the machines three and four in the TOP500 list (as of November 2014) achieve 85% and 93% of their peak performance respectively. The machine number one in the same list is equipped with Xeon Phi [66] coprocessors, achieving 60% of the peak performance. The same percentage is achieved by the machine number two which is equipped with NVIDIA GPUs [146].

If we are required to "squeeze" some performance out of an ordinary machine, the manual optimisation of every program in most cases is not economically viable. Not only is it unrealistic to find a highly professional programmer for every existing program, but also hardware-specific manual optimisations proliferate the amount of code variants of an algorithm. Those variants have to be maintained, supported, tested, etc., which contradicts modern software engineering practices.

An alternative approach to manual optimisation is *compiler technology*. The power of compiler technology lies in its ability to replicate the effort of manual optimisations making them applicable to all the programs recognised by a compiler. To achieve the effects of manual optimisation from within a compiler is a very challenging task as the process has to be formalised not only for a single application but for as wide as possible class of applications. Nevertheless, we believe that at least for mainstream programs, this is the only way to preserve performance portability on diverse hardware and to make existing programs benefit from it.

This thesis focuses on the one particular aspect that contributes significantly to the performance gap, which is underutilisation of vector instructions. Vector instructions provide a way to apply an operation on a vector of values simultaneously. The length of such vectors depends on the type of the data the vector stores. Today vectors typically can accommodate four or eight values of 4-byte real values. Every core of a CPU is equipped with vector units. This means that if the core part of an application is left unvectorised, the consequences are twofold. First, performance may be n times slower than in the vectorised case, where n is a number of elements per vector. Secondly, such a slow-down will happen on every core, which means that the length of vector registers increases with new generations of hardware, such a penalty will grow larger.

There exists a number of limiting factors for getting full performance on a vectorcapable architecture. Considering past experiences of manual vectorisation of scientific and high performance applications, it can be seen that such a process often requires radical program rewrites [46, 68, 6]. Such rewrites are challenging. First of all, there is no widely adopted standard to target vector operations from within the program. Usually the choices are either to program vector devices directly using machine instructions (possibly in a form of intrinsics) or to rely on auto-vectorisers. Neither of the approaches are satisfactory. Direct programming in assembly is tedious, error-prone, and most importantly the result is non-portable. Auto-vectorisers tend to improve the portability problem by introducing an optimisation that analyses a program, identifies the parts that can be executed using vector instructions and rewrites the code accordingly. Despite the great advances in the algorithms used in auto-vectorisers [39, 96, 74] the performance of the resulting code is far beyond the processor peak.

Part of the reason for auto-vectorisers to fail is the inability to recognise a number of important patterns [88]. Secondly, fully implicit approach means that there is no way to help an auto-vectoriser to recover from failure. Finally, and this is going to be the main interest of our investigation, the way data structures are mapped in memory has a very large effect on an application's vectorisation potential.

Generally, for vector instructions to be efficient, the data that they operate on must be consecutive in memory. However, most programming languages directly relate type definitions and type declarations to one particular data layout in memory. For example, Fortran maps arrays in a column-major order into memory, whereas C uses a row major scheme. The fields of records or objects are typically adjacent in memory and algebraic data types such as those in many functional languages typically are mapped to pointer connected graphs in memory.

In languages that support an explicit notion of memory and pointers there is very little that can be done about this tight coupling between types and their corresponding mapping into memory. One can create yet another level of abstraction between objects/arrays and the way they are being accessed for further manual data layout manipulation. However, such a level of abstraction has to be maintained and for it to be efficient, the underlying compiler has to know how to eliminate it in the resulting binaries. In contrast, languages that completely abstract away from the notion of memory, such as purely functional languages, allow for almost arbitrary mappings of data into memory. While this opportunity may be less relevant in the context of algebraic data types, it can have a huge impact on the performance of programs that operate on arrays.

It is well known from the optimisation of compute-intensive applications in Fortran or C, that a reorganisation of order of data accesses can vastly improve the overall runtime [16, 139, 87]. Improvements typically do not only stem from better cache locality but also from improved chances of the utilisation of vector instructions. However, data dependencies in programs and a fixed data-layout often constrain what can be achieved. The high-performance computing literature provides many cases where re-writes for enforcing different *memory layouts* are crucial for achieving a sufficient level of performance [77, 107, 151, 150, 136].

## 1.1 Thesis

"The process of identifying data layouts that are better suited for vectorisation than those directly specified and corresponding semantic-preserving program transformations can be automated."

## 1.2 Approach

To modify data layouts in a systematic way we have to be able to track data layouts of all the data structures in a given program. As data structures in principle can be mapped in memory in various different ways, we have to find a way to choose the best configuration of data layouts for a given hardware. Our approach is to use types to encode constraints on the mapping of each data structure and employ a type system to resolve those constraints. By treating data layouts as types, cross-function optimisation becomes possible and type checking guarantees that data layouts in a program are consistent. Type inference techniques allow to reconstruct data layouts for every expression in a program with a programmer providing any data layout annotations.

The newly inferred layouts imply program transformation, as access and traversals of data structures depends on their mapping in memory. Furthermore, one and the same function may be applied in various contexts where its arguments may have different layout types. The implication is that several versions of one and the same function have to be created. Finally, external interfaces of a program may imply memory mappings for certain data structures. Such mappings must be preserved in the original form.

After the program is transformed we have to generate the code that will be able to target vector instructions of the underlying hardware. Our goal is to generate such a code in a portable fashion, yet guaranteeing performance portability across SIMD-capable hardware.

## 1.3 Contributions

The major contributions of this thesis are as follows:

- 1. We formalise the idea of data layout annotations using types and we introduce a type inference that is capable to generate all the valid layout configurations (according to the type system) for a given program.

- 2. We introduce automatic high-level program transformations based on the previously inferred layout types and prove that transformed programs preserve the semantics of the original programs.

- 3. We solve the vector portability problem by extending the C language with explicit vector operations, which we have implemented in the context of GNU

GCC.

- 4. We implement the proposed inference, transformations and vectorised code generation in terms of the programming language called SAC and its compiler called sac2c.

- 5. We evaluate our approach using a set of benchmarks which is known to be challenging to vectorise and demonstrate the effectiveness of vectorisation by comparing the runtimes with the automatically and manually vectorised C versions.

## 1.4 Thesis structure

The thesis consists of eight chapters.

Chapter two gives an overview of the existing vectorisation techniques and approaches and presents work done so far with respect to data layout mappings.

Chapter three presents an extension of the C language implemented in terms of the GNU GCC compiler providing performance portable means of expressing vector operations in C.

Chapter four introduces the input language and layout type system used to infer all the possible data layouts for a given program.

Chapter five introduces our program transformation scheme with respect to vectorcapable hardware.

Chapter six discusses technical details of the inference and transformations in terms of the sac2c compiler.

Chapter seven presents a performance evaluation before we conclude in Chapter eight.

## Chapter 2

## State of the art

History may not repeat itself but it does rhyme.

Joseph Anthony Wittreich [148]

In this chapter, we explore the context around vector hardware. We start with very basic principles, then, to understand design decisions and potential future developments, we consider the evolution of vector architectures starting from early machines till our time. Next we discuss what kind of vector hardware is available on the market today and classify functionality of commonly available vector operations. Then we consider the way vector hardware can be programmed and what are the main difficulties while doing so. Finally, we discuss the work in the area of data layout modification and its applications.

## 2.1 Vector hardware basics

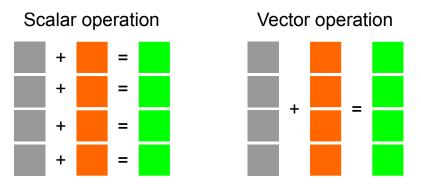

Figure 2.1: Scalar vs SIMD addition.

When we talk about vector hardware, technically we mean SIMD (Single Instruction Multiple Data) parallel hardware according to Flynn's taxonomy [43]. A distinctive feature of such a hardware is availability of multiple processing elements that are capable to perform one and the same operation simultaneously. Such a classification consider only macroscopic level of hardware organisation, therefore the exact implementation of SIMD processors may vary significantly. Nevertheless, to develop an intuition, let us consider a classical use case of SIMD hardware. As it can be seen from Fig. 2.1 a SIMD operation replaces multiple identical scalar operations with a semantically equivalent one, e.g. four additions are replaced with a single vector addition. Keep in mind that the performance of such a SIMD operation, the number of elements that can be processed simultaneously and programming interfaces fully depend on the architecture.

## 2.2 History of parallel and vector hardware

SIMD architectures are a special case of parallel architectures and their design has a lot of historical reasons. By looking at how parallel hardware appeared and evolved, we can explore the versatility of the existing designs and get a better understanding of why certain things are as they are and what we could expect in the future.

As a general observation, a lot of decisions in computer science are based on trade-offs. For some algorithms, memory consumption can be increased in favour of faster execution times. Sometimes we can decrease the precision of an answer in favour of faster computations, and so on. In hardware design, trends shift when a certain technology gets cheaper or simpler. Tannenbaum in [137] gives the following example when discussing the existence of caches:

In particular, it frequently happens that a change in technology renders some idea obsolete and it quickly vanishes. However, another change in technology could revive it again. This is especially true when the change has to do with the relative performance of different parts of the system. For instance, when CPUs became much faster than memories, caches became important to speed up the "slow" memory. If new memory technology someday makes memories much faster than CPUs, caches will vanish. And if a new CPU technology makes them faster than memories again, caches will reappear. In biology, extinction is forever, but in computer science, it is sometimes only for a few years. [137, Section 1.5.7, page 44]

As we shall see in the rest of this chapter, such a pattern is generic. In the context of our work it means that instead of focusing on hardware-specific solutions we want to understand basic underlying principles of the problem, as any specific hardware may be rendered obsolete in favour of future technologies.

The second observation is that early machines were designed for a restrictive application domain. The main purpose of first computers was to serve as large programmable calculators. Starting from Charles Babbage [52] designing a mechanical calculator to tabulate polynomial functions in the 19th century; continuing with early electro mechanical computers like the Harvard Mark I which were used for war-related calculations like problems associated with the protection of ships from the destructive action of magnetic mines [34]. Most of the later machines were reusing ideas and technologies of previous generations and even nowadays a large part of instructions of the modern CPUs have to do with numerical operations. We would rarely find instructions designed specifically for domains like text or sound processing.

After the success of early machines in 1940s, the diversity of tasks that could have been solved with later computers substantially increased. In the 1960s it became clear that for a number of real world problems like linear programming or solving sets of partial differential equations over grids the computing power of existing machines was several orders of magnitude lower than required. It became clear that strictly sequential computers would not be able to provide desirable computing speeds [11] because of the signal propagation speed barrier. This gave a rise to the idea of using multiple processing units on a single machine.

A variety of designs has been proposed in the early stages of research. For example, one of the earliest papers [130] presents a SOLOMON computer which proposes a design based on a 2-d array of processing units each of which is interconnected with its four neighbours, yet controlled by a single control unit. The SOLOMON itself was never actually built, but the ideas were used in further projects like ILLIAC IV [11].

Another kind of parallel design manifested itself in vector processors which still exist and are being actively developed nowadays. The first vector machines like TI-ASC [143] and STAR-100 [58] appeared in the early 1970s and gave rise to vector supercomputers. The main idea lies in having a vector unit that takes streams of data from memory, operates on them and puts results back into the memory. Conceptually such a vector operation was happening in a single instruction, although that individual scalar operations (steps of the vector operation) did not have to happen simultaneously. Such a design required advanced high-bandwidth memory systems together with long pipelines to make vector operations efficient. On the other hand, the entire loop could have been reduced to a single instruction. That in itself was a great advantage, as it removed the necessity to stall the pipeline at every element and spending time on fetching and decoding instructions of the loop body. Let us consider example codes taken from [54] to demonstrate the approach. This is a classic DAXPY benchmark which can be formulated as:

$$Y = a \cdot X + Y$$

where a is a scalar and X and Y are vectors.

| Loop: | L.D                                                               | F0, a                                                                                                                                                                                             | ; load scalar a                                                                                                                                                |

|-------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | DADDIU                                                            | R4, Rx, $\#512$                                                                                                                                                                                   | ; last address to load                                                                                                                                         |

|       | L.D                                                               | F2, 0 (Rx)                                                                                                                                                                                        | ; load X(i)                                                                                                                                                    |

|       | MUL.D<br>L.D<br>ADD.D<br>S.D<br>DADDIU<br>DADDIU<br>DSUBU<br>BNEZ | $\begin{array}{c} {\rm F2,F2,F0} \\ {\rm F4,0(Ry)} \\ {\rm F4,F4,F2} \\ {\rm 0(Ry),F4} \\ {\rm Rx,Rx,\#8} \\ {\rm Ry,Ry,\#8} \\ {\rm R20,R4,Rx} \\ {\rm R20,R4,Rx} \\ {\rm R20,Loop} \end{array}$ | ; a x X (i)<br>; load Y(i)<br>; a x X(i) + Y(i)<br>; store into Y(i)<br>; increment index to X<br>; increment index to Y<br>; compute bound<br>; check if done |

Listing 2.1: Scalar code implementing DAXPY

The scalar version is presented in Listing 2.1, the vector version of the same code is presented in Listing 2.2.

| L.D     | F0, a      | ;load scalar a           |

|---------|------------|--------------------------|

| LV      | V1, Rx     | ;load vector X           |

| MULVS.D | V2, V1, F0 | ; vector-scalar multiply |

| LV      | V3, Ry     | ;load vector Y           |

| ADDV.D  | V4, V2, V3 | ;vector add              |

| SV      | Ry, V4     | ; store the result       |

Listing 2.2: Vector code implementing DAXPY

The disadvantage though was the high latency of the vector unit and as a result very long switches between vector and scalar modes. This problem was addressed in the CRAY-1 [116], which according to [40] was the beginning of "Golden Era" of vector supercomputers. The solution was to introduce vector registers, very similarly to what we have nowadays. The advantage was that the data in registers could be reused, in case an algorithm performed multiple operations on the same data. Vector registers allowed one to save successive memory reads and writes. This approach had some limitations — vector registers were expensive in terms of circuitry, so only a limited number could be provided. That had an impact on the sizes of the vectors that could be processed. Vector operations had to be performed in chunks limited by the length of vector registers, but multiple operations could have been executed on each chunk.

**Complex instructions** Early machines were equipped with what is now called CISC<sup>1</sup> instructions. Some of the instructions were representing very complex operations. For example, TI-ASC provided matrix multiply in a single instruction, or IBM 3090 [18] vector load instruction which were combining multiple actions in one instruction. This is helpful in case one writes code in assembly directly, however, when targeting such an architecture from a compiler, it gets very hard to do so efficiently.

**Dawn of vector supercomputers<sup>2</sup>** In the early 1990s it became technologically possible to put many more transistors on a single die than earlier. Microprocessors made a significant progress, their clock frequency steadily increased every year and their performance started to be comparable with processors used in expensive vector supercomputers. Due to their mass production microprocessors also were substantially cheaper than tailor-made ones used in supercomputers. That introduced a shift in supercomputer design towards building machines using many microprocessors.

## 2.3 Vector architectures today

Despite the shift of technologies in supercomputers, the key ideas that were understood in vector supercomputers manifest themselves in modern CPUs and are

<sup>&</sup>lt;sup>1</sup>Complex Instruction Set Computing (CISC) is a CPU design where single instructions can execute several low-level operations.

<sup>&</sup>lt;sup>2</sup>This paragraph is based on [40].

known as SIMD extensions. Later the same SIMD extensions appeared on GPUs and accelerators like Intel Xeon Phi [66]. These extensions are the primary focus of our thesis.

The important property all the extensions share is that SIMD operations are just usual instructions, same as scalar arithmetic operations or data movement operations. To execute a SIMD instruction its operands have to be loaded into SIMD registers. SIMD registers are not very different from scalar registers, except for their size. For example, if we assume that the operation on Fig 2.1 uses registers, then SIMD registers on that picture can accommodate four scalar elements. The exact length of SIMD registers varies from platform to platform.

The length of a SIMD register is most commonly defined in bits, rather than in a number of scalar elements. Similarly to scalar registers, the type of its value is not fixed and may be interpreted differently depending on the instruction that is being executed. The same holds for SIMD registers — a 128-bit SIMD register can accommodate four 32-bit floats or 16 eight-bit characters.

All SIMD extensions provide instructions to load data from memory into SIMD registers and to store data from SIMD registers back into the memory. The way it works is that a SIMD register is mapped into a continuous region of memory of the size equal to the SIMD register. On some of the architectures, like for example Intel, load and store instructions can be of two kinds: aligned and unaligned. Aligned load/store implies that the memory address used to load/store a SIMD register is a multiple of the size of a SIMD register. Aligned operations are usually faster. Application of aligned move operations to unaligned memory results in a hardware exception.

Operations provided by SIMD extensions vary significantly on different platforms, but usually all of the extensions provide some form of arithmetic operations on integers and floats, some element reordering operations, comparisons and mathematical functions. For more details on the functional classification please refer to Section 2.4.1.

### 2.3.1 CPUs

The primarily motivation to introduce SIMD extensions on CPUs was to accelerate multimedia-related tasks. That is why very often early SIMD instructions were referred as "multimedia extensions". Most of the modern CPUs nowadays are equipped with some form of SIMD instructions. Here are several examples: MVI (Alpha) [115], Altivec (IBM) [47], MAX (HP) [83], MMX/SSE/AVX (Intel) [60], VIS (SPARC) [132], NEON (ARM) [5], etc. All these architectures provide a set of vector registers and some form of floating point arithmetic, logical operations, comparisons and data movements.

The table in Fig. 2.2 shows the evolution of various SIMD instruction sets in time. From these figures we can see that the size of vector registers doubles every few years. Such a growth suggests that SIMD technology is unlikely to disappear in

| ISA extension name | Year | Bits      | First appeared       |

|--------------------|------|-----------|----------------------|

| MAX-1              | 1994 | 32  bits  | HP, PA-7100LC        |

| MAX-2              | 1996 | 64  bits  | HP, PA-8000          |

| MMX                | 1997 | 64  bits  | Intel, Pentium I     |

| ALTIVEC            | 1998 | 128  bits | Apple, IBM, Motorola |

| 3DNOW!             | 1998 | 64  bits  | AMD, K6              |

| SSE                | 1999 | 128  bits | Intel, Pentium III   |

| SSE2               | 2001 | 128  bits | Intel, Pentium IV    |

| SSE3               | 2004 | 128  bits | Intel, Pentium IV    |

| SSSE3              | 2006 | 128  bits | Intel, Xeon          |

| SSE4               | 2007 | 128  bits | Intel, Core 2        |

| AVX                | 2011 | 256 bits  | Intel, Sandy bridge  |

| AVX2               | 2013 | 256 bits  | Intel, Haswell       |

| MIC                | 2012 | 512 bits  | Intel, Xeon Phi      |

Figure 2.2: Length of a vector register

the near future, unless a very radical breakthrough in hardware happens. Also, there is still a large room for improvement. For instance, the latest vector supercomputer SX-ACE [91] from NEC is equipped with vector registers which can accommodate 256 doubles. That is an order of magnitude larger than what we have on standard CPUs. That suggests that speedups we can achieve today due to SIMD will get larger on the newer generations of hardware.

SIMD operations on the Xeon Phi accelerator are not very different from those that can be found on latest Intel CPUs. The important difference though is the long vector register (512 bits) and support for predicated execution of operations, i.e. normal operations like for example addition can get a mask that determines which of the elements in the register to add. Predication is very useful when expressing conditions in vector form.

### 2.3.2 Graphics Processing Units (GPUs)

Latest generations of Nvidia's GPUs introduce [98] SIMD instructions as part of their pseudo-assembly language specification. At first glance it seem to be controversial as GPUs according to Flynn's taxonomy are clearly SIMD processors. However, SIMD instructions provide much more fine-grain parallelism than the same code implemented in a usual GPU programming model — when a kernel is executed by a number of SIMT threads. Most importantly, for the diverging program flow, SIMD operations allow to avoid lock-step execution, which is the way SIMT threads evaluate a conditional statement.

The usefulness of having SIMD instructions on the GPUs is demonstrated for example in the work of Y. Liu et. al. [86] where authors demonstrate significant speedups of the protein sequence database search algorithm over existing GPU implementations. The main reason lies in gaining more data parallelism beyond the SIMT execution model on CUDA-enabled GPUs because of using n CUDA PTX SIMD video instructions.

Currently the set of supported SIMD operations is not very rich: PTX ISA v4.1 [98] defines integer addition and subtraction, average, absolute differences, minimum/maximum and masking. Most likely the capabilities of SIMD instructions on GPUs will get more and more advanced, which means that any results obtained for SIMD instructions on a CPU can be transferred to GPUs.

## 2.4 SIMD functionality

As it can be seen from Fig. 2.2 there exists a large number of different SIMD instruction sets available on the market. Despite being non-uniform in the way the code has to be expressed and exact operations they support, they all share common functionality. We are going to survey this functionality based on the analysis of instruction sets provided by three most widely used manufacturers. After that we will consider potential difficulties when integrating SIMD operations into programs.

### 2.4.1 Classes of SIMD instructions

We propose a macroscopic classification of the operations of the following instruction sets: Intel (MMX/SSE/AVX) [60], Altivec [47] and ARM's NEON [5]. The classification is concerned with the functionality of vector operations that a programmer can use in the code replacing scalar operations with vector ones. By joining the functionalities of individual architectures we get the following list.

**Data movement** defines instructions to load and store data from vector registers to memory and vice versa.

Scientific codes like stencil computations or image processing often require non-continuous memory access. Such an operation, when elements are being loaded/stored from/to non-continuous memory are usually referred as gather/scatter. Some of the latest architectures provide native support for scatter/gather operations, but it is limited and not very efficient.

One important data movement operation that is found on almost all (but not every) architecture is *broadcast* which assigns a scalar value to all the elements of a vector.

- **Basic arithmetic** defines arithmetic operations like addition, multiplication, etc. which usually work as  $a_i + b_i$ , where a and b are vector operands.

- Advanced arithmetic defines operations that involve more sophisticated patterns compared to basic arithmetics. As an example Intel SSSE3 introduces

horizontal operations like PHSUBW, PHSUBD which for two operands a and b compute  $[a_0 - a_1, a_2 - a_3, \dots b_0 - b_1, b_2 - b_3, \dots]$ . ARM NEON's VPADD, VPADAL instructions operate in a similar fashion, performing addition.

Another example of advanced arithmetic are MIN/MAX instructions that chose a minimum/maximum element of the given vector.

**Comparison operations** define the element-wise application of standard comparison operations like equal, less than, etc. The result is usually a vector of boolean values which indicates result of the comparison for every pair. Later such a result is commonly used in masking operations which select components either from the first or second operand according to the boolean vector. Such operations are essential for vectorising the code containing control-flow like:

for (i = ...)

if (a[i] > 3)

b[i] = 5;

else

b[i] = 6;

in which case it is being transformed into something similar to:

for  $(vec_i = ...)$  $vec_b[vec_i] = mask (vec_lt (vec_a[vec_i], [3,3,...]), [5,5,...], [6,6,...])$

where **mask** choses elements from the second operand at positions where the first operand is true and from the third operand at positions where first operand is false.

Finally, some of the architectures have instructions to set the flag that can trigger branching if all the elements in a boolean vector are true/false. For example Intel's PTEST instruction sets the Zero flag to the result of bitwise and of all vector components. Altivec defines *all* and *any* variants of comparison operations which are element-wise conjunctions and disjunctions of the vector elements accordingly.

- Mathematical operations defines the element-wise application of a mathematical operation like *sin*, *sqrt*, etc. Most of the mathematical instructions operate on a single or floating point vectors, however for the sake of classification, we do not fix the type of mathematical operations.

- **Logical operations** are element-wise applications of scalar logical operations like bitwise and, bitwise or, etc.

- **Shift operations** define element-wise shifts of vector components.

- **Conversion operations** define conversions between different data types. For example, a vector of integers can be converted to a vector of floats, or first two elements of a vector of four floats can be converted into a vector of two doubles.

- **Element reordering** define instructions that change the order of elements in a given vector. Those operations are very broad, and can vary from interleaving odd and even elements from two vectors to reversing elements to performing a general permutation of elements.

- **Operations on parts of the vector** operate not on all the elements of the vector but on some subset. For example, indexing operations and assigning an element of a vector are of that nature. Intel SSE defines a set of operations with a *-SS* postfix which operate on the low values of vectors only.

- **Complex operations** define operations that combine several actions in one. For example: multiply-add  $(a := a + (b \times c))$ , absolute difference (|a| - |b|), etc.

- **Application-specific instructions** define instructions that implements application-specific functions in hardware. For example Intel AVX introduces a set of AES<sup>3</sup>-specific instructions for faster cryptography.

Such a classification covers nearly all the instructions of the architectures we have considered. Please note that as SIMD instructions encode the expected type of the elements in SIMD registers, we have to be careful when we say that a certain functionality is present. It often happens that an architecture supports an operation on vectors of floats, but does not support the same operation on 8-bit integers. This is especially noticeable on Intel-based CPUs as SIMD extensions were introduced gradually, not only introducing functionally new operations, but extending the types that the existing operation can be applied to.

Some specific instructions like memory prefetching or data movement without polluting caches are left outside of this classification. Their functions do not reflect any logical operations that help to express parts of algorithms, but they are more of architecture-specific tricks to optimise data movement.

Most of the SIMD instructions in the proposed classification have standard scalar counterpart, i.e. their functionality can be directly mapped into several scalar instructions from the basic instruction set of a given architecture. However, there are exceptions from this rule, specifically we are talking about group of instructions for:

- saturated arithmetics<sup>4</sup>,

- half-floating point (16-bit floats) arithmetics, and

- estimated mathematical functions, for example estimated reciprocal a faster but less precise version of the expression 1/x

which all the three manufacturers support. The proposed classification covers the functionality that these instructions provide, but from a programmability perspective we believe that they deserve a special treatment.

$<sup>^{3}</sup>$ Advanced Encryption Standard (AES) is a specification for the encryption of data established by the National Institute of Standards and Technology (NIST) in 2001.

<sup>&</sup>lt;sup>4</sup>A standard arithmetic on integers, but in case the result of an operation overflows, either a minimum or maximum value of the integer type is returned.

### 2.4.2 Known difficulties

Programs that target SIMD architectures in replacing some scalar instructions with vector ones does not necessarily results in faster execution. One can construct a number of cases when SIMD implementations will run slower than its scalar analogues. The main reasons for that are as follows:

- Scatter/Gather Gathering data into SIMD registers and scattering it into the memory is tricky and can be inefficient. Some of the architectures do not provide any instructions to address this, those that provide them are not very efficient. This means that whenever operations include non-continuous access to memory, a programmer has to make choices on how to implement it.

- Alignment For sequential memory loads one has to be aware of alignment issues. Some of the architectures due to technical limitations with load/store operation require memory address to be aligned. This means that whenever one loads/stores non-aligned data, two vector loads/stores are required. That might be done via a special instruction, to avoid manual scaffolding, but the execution time will be still lower than the aligned counterpart. In order to tolerate that one would have to align the data in memory (if possible) or fallback to unaligned loads/stores in case alignment is unknown, like in the case when a function gets a pointer.

- Missing instructions Some instruction sets might not include operations that might be required in terms of an algorithm. For example shuffling or rotates. In that case one could try to emulate an operation using existing instructions, but the risk is that its performance would be so bad that all the achieved gains will be lost. Alternatively one could fall back on scalar mode, but again, instruction pipelining, and accessing vector elements might destroy all the vectorisation gains.

- **Conditions** When vectorising conditions, the usual technique is to execute both branches and then mask the result. This is inefficient from the power perspective as we compute vector elements which are going to be discarded. In case conditions are nested we will have to execute twice the number of operations than in the original program. To address this problem, the latest instruction sets introduce predication. This allows one to pass a mask to every vector instruction and avoid operations on the elements that will be discarded. If predication is not present, it has to be carefully emulated. This is tricky and might be inefficient.

- **Loops** In imperative languages like C or Fortran loops are the natural source of data parallelism. However, building a generic loop vectorisation framework is challenging, as such a framework has to perform non-trivial code analysis and capture pretty large context. Loops might contain conditions, control flow or

other loops. The iterations of the loop might have dependencies. The iteration space of the loop might be unknown at compile time.

## 2.5 Programming models

Programming SIMD architectures is a big challenge, as it requires to reformulate algorithms in a data-parallel style and to take into account all the above-mentioned difficulties. Programming SIMD architectures in a portable way is a double challenge, as the means of programming either target a limited number of instruction sets or have severe limitations on expressibility. Finding the right programming abstractions that will maximise program performance on the SIMD-capable architectures is an open problem. Performance characteristics of the instructions vary from architecture to architecture at the same time exactly those characteristics determine the way algorithms have to be expressed.

The existing programming models for SIMD architectures very often depend on the surrounding context. The way a programming model and a programming language target parallelism in general very much determine how one can program SIMD. To understand the SIMD choices better we are going to review them in the context of programming models and languages for general parallelism.

### 2.5.1 Programming languages overview

Almost all of the early programming languages happened to be imperative. One of the reasons for that is that most of the early computer architectures were based on the von Neumann model [141] which is imperative itself, and a lot of languages were developed by creating abstractions for the parts that were hard to read or long to write. The first such an abstraction was an assembly language which was just a symbolic representation of machine codes. Further, languages like Fortran [9], Algol [92], Cobol [117] started to appear, providing higher and higher levels of abstractions. As a consequence, the mapping from the language into hardware was not so obvious anymore, plus, when a level of abstraction reached a certain threshold the complexity of compilers increased dramatically. That in turn had an influence on the quality of the generated code.

The next non-trivial problem was automatic refactoring. Programming languages do evolve and introduce new features especially on the early stages of development. Sometimes it comes as a desire to abstract a certain hardware feature, like for example the ++ operator being a direct abstraction of an increment instruction; sometimes it can be a revisit of some earlier design decisions. However, such changes in programming languages impact existing codes, requiring them to be modified. Ideally, one would like to refactor the code automatically and to get new language features for free. Unfortunately, this is not a simple task, especially in the imperative setup. Realisation of this problem raised a number of proposals explaining how to make languages more analysable. Peter Landin in [80, 81] demonstrated how the semantics of Algol 60 can be formalised using Church's lambda calculus. Later in 1977 John Backus named his Turing award lecture [10] "Can Programming Be Liberated from the von Neumann Style?", where he proposed to use functional programming to reason about programs using what he calls an algebra of programs. It seems that the trend was to get rid of imperative programming style and use a functional style instead. One could claim that this is still valid today.

The main difficulty with such a language shift is the amount of code that exists and is actively used in day-to-day life. Large projects like OS kernels or compilers have accumulated millions of lines of code during several decades and they are still being actively developed. Rewriting them in a new language is a major undertaking, and as not all the imperative constructions can be easily mapped into declarative languages, automating this process is arbitrarily hard. Finally, before embarking on such a rewriting journey, one has to be absolutely sure that the new compilers will generate code at least as good as the existing one. Unfortunately, none of the existing functional languages can give such guarantees today.

A lot of mainstream programming languages today were originally designed for sequential hardware, therefore they do not provide any parallel constructs. When intending to target parallel hardware using such languages, there is a choice of how to express parallelism. Most commonly in practice the following three ways are being used:

- 1. To use low-level abstractions like inline assembly in the case of SIMD instructions or threading libraries in case of multicores. The problem with this approach is the lack of code portability — to support a new hardware a new version of the code has to be written.

- 2. Extending a language. The problem with language extensions lies in finding a compromise between genericity of extensions and tight control of the underlying hardware.

- 3. Recognising parallelism by means of program analysis. Although this is a very desirable solution, as we mentioned above, analysing imperative languages is a very challenging problem.

Further we are going to consider existing solutions to the parallel language conundrum as well as to the general SIMD portable programming problem.

### 2.5.2 Low-level approaches to SIMD programming

The standard way of programming SIMD directly is either by using assembly (if a language allows, it can be inline assembly), or to use compiler intrinsics. The latter is a compiler-defined functions that expand into specific assembly instructions. As we have mentioned earlier, such an approach is bound to produce non-portable code. At the same time, it allows to explore all the possible capabilities of the architecture, as the programming happens at the lowest possible level.

#### Library-based

To abstract things away, a number of projects propose tailor-made libraries to target SIMD instructions [142, 75, 41]. For example, M. Kretz et. al. describe a C++ library called Vc [75] and they demonstrate that the overheads of the library are negligible which means that it can be used as a replacement for intrinsics or assembly kernels. In despite of someone has to create and maintain a library, updating it whenever a new architecture appears etc., for performance reasons the level of abstraction that the library creates has to be eliminated by the underlying compiler. Guaranteeing such a behaviour is very difficult, but the performance penalty might get rather high.

#### Intrinsics to intrinsics mapping

To increase a portability of architecture-specific codes [152] presents a mapping from the ARM intrinsics to MMX/SSE intrinsics, allowing one to run applications created for ARM-tuned applications on Intel.

#### Virtual instruction sets

The HSA<sup>5</sup> foundation proposes [45] a design of a processor which integrates heterogeneous hardware, most importantly CPUs and GPUs, on the same bus and provides a unified programming model to target them. HSA introduces virtual memory address space which can be mapped into the main memory and the memory of GPUs. The virtual instruction set is kept ISA-agnostic, providing support for parallel sections of the algorithm. Virtual instructions are dispatched to concrete devices by the runtime system which is a part of the HSA programming model. One of such devices can be SIMD, although while the project is at the design phase and no actual hardware is built, for the time being it is difficult to evaluate the validity of such an approach in application to SIMD.

R. Bocchino et. al. [15] address the problem of portability of SIMD instructions by introducing a virtual instruction set specially designed for vector operations. The main design criteria is to provide an abstraction for various vector architectures and architecture classes. Architecture classes include sub-word SIMD like Intel SSE and PowerPC Altivec and streaming processors like RSVP [30]. The proposed virtual instruction set allows both arbitrary length and fixed vectors providing asynchronous load and store semantics for long vectors and introducing alignment attributes. The compilation scheme involves a compiler which can generate a portable vector code and a translator with full information about the target architecture and system configuration.

<sup>&</sup>lt;sup>5</sup>Heterogeneous System Architecture (HSA) foundation is a not-for-profit industry standards body focused on making it dramatically easier to program heterogeneous computing devices.

#### 2.5.3 Annotations

One of the most pragmatic and yet powerful approach to extending a programming language with extra functionality is to come up with a set of annotations on top of the existing syntax. OpenMP [102] has started out as a set of extensions for C and Fortran for multi-platform shared memory multiprocessing programming. OpenMP uses a fork-join multithreaded execution: it spawns a group of tasks at the beginning of a parallel section and waits until all the tasks are terminated at the end of the section. OpenMP provides a set of directives to orchestrate the process. A typical example is:

```

#pragma omp parallel for private(i) shared(x)

for (i = 0; i < N; i++)

x[i] = x[i] + 1;</pre>

```

The annotation on top of the for-loop informs the compiler that the loop should be executed in parallel, that the variable  $\mathbf{x}$  should be shared between the threads and that the variable  $\mathbf{i}$  is private for the individual threads. The variable  $\mathbf{i}$  is an iteration variable of the loop, so every thread would range over the slice of the iteration space. How exactly the iteration space is going to be divided between the threads depends on the implementation of OpenMP. However, the default schedulers can be controlled for every parallel section.

Comparing with manual approaches for multi-threaded execution, like for example when using pthreads [93], OpenMP is much simpler for a programmer and the resulting code is suitable for both single threaded and multi threaded executions. The annotations can be ignored by means of a compiler switch. The latest OpenMP standard (version 4.0) allows one to use the code on GPUs.

OpenMP 4.0 [103] and Cilk+ [62] introduce high-level constructs targeted at SIMD instructions. Cilk+ introduces a pragma called simd with the following description: "The pragma can be applied to a loop, to indicate the intention that the loop needs to be implemented using vector instructions." OpenMP 4.0 introduces an analogous prgama called **pragma omp for simd**. Both extensions introduce a way to annotate a function operating on scalar elements, which creates a version of the function where scalar operations are projected into corresponding SIMD operations, and as a result a function can be applied to SIMD arguments. Cilk+ calls this elemental functions, and OpenMP 4.0 — declare simd construct.

The limitations of the annotation-based approach are first of all that the annotations have to be inserted manually. That raises risks for introducing race conditions and synchronisation bugs which are really hard to find. OpenMP uses a threading model called fork-join model in which program execution branches off at designated points in the program and has to be joined at a subsequent point, resuming sequential execution. Such a high level threading abstraction does not allow one to fine-tune the parallel execution. Finally, a compiler has to support OpenMP which implies that various compilers may not produce equally performing code (time wise).

OpenACC [101] is another set of compiler directives for C and Fortran with a primary goal to offload computations to accelerators. A typical code looks like this:

This is a matrix multiply example. The annotations on top of the loops are very similar to what we have seen in the case of OpenMP. They indicate that the annotated loop should be executed in parallel and specify which variables are not shared. In reduction loops, as in the case of the inner loop that sums results into tmp variable, the annotation indicates the reduction operation and reduction variable. Also, we have to specify which data has to be transferred to an accelerator and which should be copied back to the host.

OpenCL [73] is another popular approach that allows to target CPUs and accelerators like GPUs. OpenCL positions itself as a standard for writing programs to be executed on heterogeneous systems. It is not directive-based, instead it views a computing system as consisting of compute devices which normally are CPUs and accelerators, and it defines a C-like language to create kernels that execute on compute devices. This approach still allows one to reuse existing programs written in C, but it requires one to introduce a lot of boilerplate code to establish communication with compute devices.

The C-like language for kernel programming defines abstractions to express SIMD operations. In case kernels are executed on a CPU, depending on the implementation of OpenCL, these operations may be mapped into SIMD extensions of the given processor. In case kernels are executed on GPUs, the abstractions may be mapped into SIMD instructions of a graphics card.

#### 2.5.4 Extensions of the existing languages

An alternative to using annotations is to introduce new constructs in the language. The main difference between the two approaches is that annotations can be easily ignored and the program would be still usable in terms of the original language, where extensions irrevocably change semantics of programs.

Languages like UPC [20], Coarray Fortran [94], HPF [56] follow this approach. UPC extends C99, Coarray Fortran extends Fortran 95/2003 and HPF extends Fortran 90. HPF (High Performance Fortran) uses a data parallel view of computations which allows one to spread a computation on a given array across several processors. HPF defines an implicit parallel statement such as FORALL and introduces a way to define side-effect-free procedures via the IMPLICIT keyword. Additionally HPF allows one to control how data is being distributed across processors by annotating data allocations. Finally it defines additional routines for message passing, in case parallelism does not fit into HPF model and a number of library routines.

UPC and Coarray Fortran are based on the PGAS [32] model. The main idea of PGAS (Partitioned Global Address Space) is to introduce locality awareness on top of message passing. PGAS presents distributed memory as a continuous address space. However, the address space is also logically partitioned between threads or processes which allows local computations, and at the same time all the memory is shared which allows SPMD style programming. Both UPC and CAF use source-tosource translation, producing the C or Fortran code appended with communication routines. The main difference between the languages is that UPC allows uniform access to any memory cell (potentially with some time overheads) when CAF is strict with respect to the boundaries of distributed arrays. In the case of the need to access remote memory a special syntax has to be used.

All the above mentioned examples did not target SIMD instructions as their primary goal. The main architectures in mind were multi-threaded machines or clusters. However, the presence of FORALL-like parallel constructions in the language allows a compiler to chose how to implement an operation. For example a compiler can chose to express it via SIMD instructions.

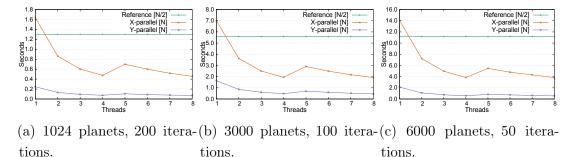

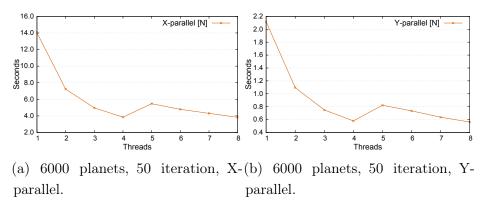

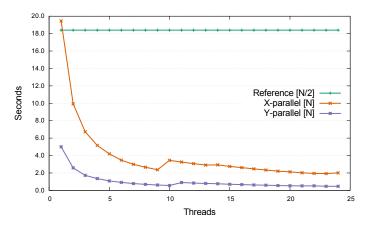

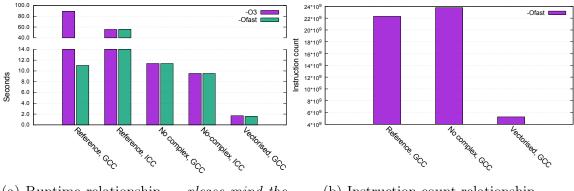

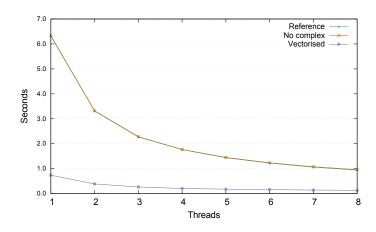

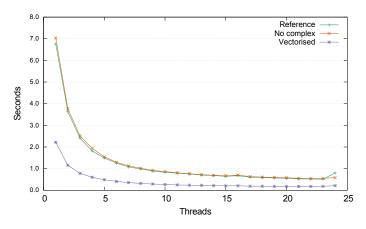

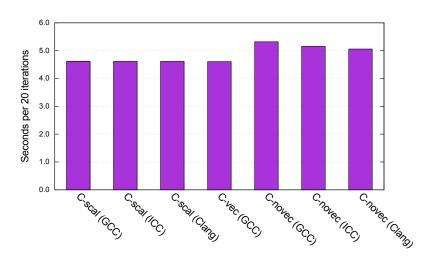

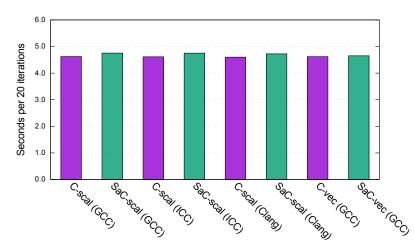

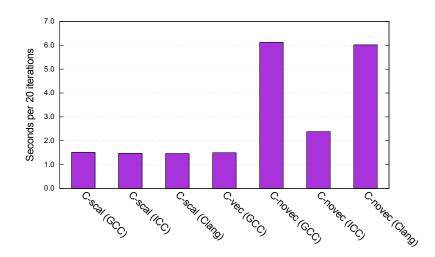

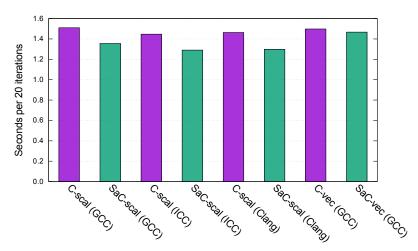

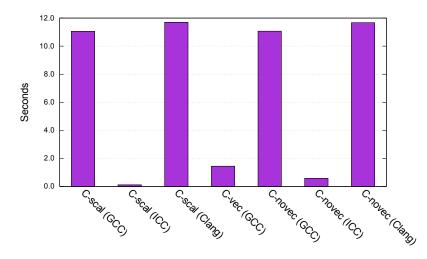

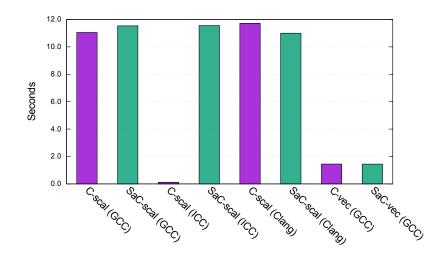

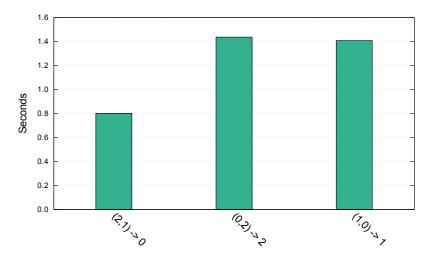

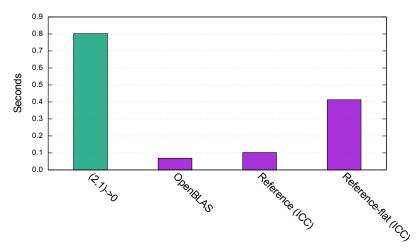

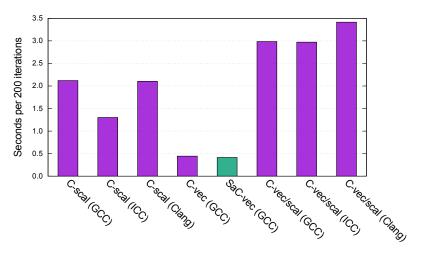

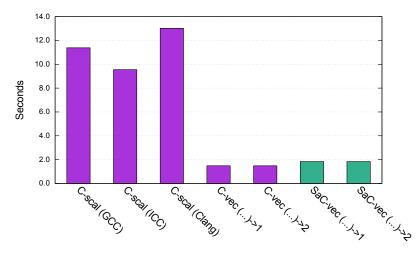

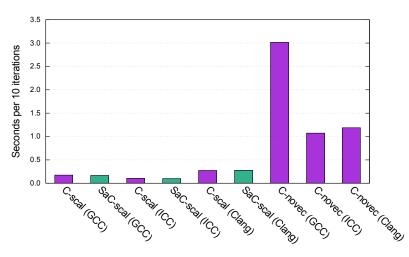

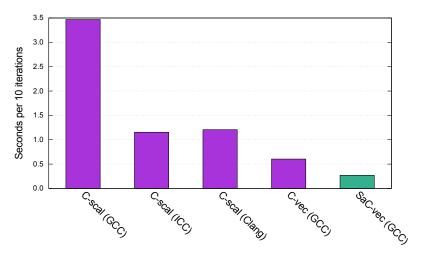

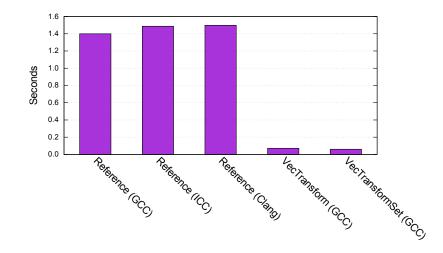

#### 2.5.5 Fully implicit parallelism