# Control of a Modular Multilevel Flying Capacitor Based STATCOM for Distribution Systems

Chigozie John Nwobu

Submitted in accordance with the requirements for the degree of Doctor of Philosophy

The University of Leeds School of Electronic and Electrical Engineering

August, 2016

The candidate confirms that the work submitted is his/her own, except where work which has formed part of jointly-authored publications has been included. The contribution of the candidate and the other authors to this work has been explicitly indicated below. The candidate confirms that appropriate credit has been given within the thesis where reference has been made to the work of others.

#### Publications:

The contribution of the candidate and other authors to this work has been explicitly indicated below.

- Nwobu, C.J.; Zhang, L., "Lifting wavelet transform and energy operator synchronization for a flying capacitor multi-level inverter based active power filter," in Power Electronics and Applications (EPE), 2013 15th European Conference on , vol., no., pp.1-10, 2-6 Sept. 2013

- Nwobu, C.J.; Efika, I.B.; Oghorada, O.J.K.; Zhang, L. "A modular multilevel flying capacitor converter-based STATCOM for reactive power control in distribution systems", Power Electronics and Applications (EPE'15 ECCE-Europe), 2015 17th European Conference on, page(s): 1 – 9

- Efika, I.B.; Nwobu, C.J.; Zhang, L., "Reactive power compensation by modular multilevel flying capacitor converter-based STATCOM using PS-PWM," in Power Electronics, Machines and Drives (PEMD 2014), 7th IET International Conference on , vol., no., pp.1-6, 8-10 April 2014

- 4) Nwobu, C.J.; Chong, B.V.P.; Zhang, L. "A novel phase locked loop scheme for grid voltage synchronisation using the energy operator", Power Electronics and Applications (EPE'15 ECCE-Europe), 2015 17th European Conference on, page(s): 1 10

Chapter 3 of the thesis comprises work forming part of the  $1^{st}$  publication . Chapters 2, 5 and 6 of the thesis are comprised of work forming part of the  $2^{nd}$  publication and 3rd publication. Chapter 4 comprises work forming part of the publication in the  $4^{th}$  publication. The entire works in Chapters 1-8 are attributable to the candidate under the supervision of Dr. Li Zhang. This copy has been supplied on the understanding that it is copyright material and that no quotation from the thesis may be published without proper acknowledgement.

### Assertion of moral rights (optional):

The right of Chigozie John Nwobu to be identified as Author of this work has been asserted by him in accordance with the Copyright, Designs and Patents Act 1988.

© 2016 The University of Leeds and Chigozie John Nwobu

## Acknowledgements

I would like to acknowledge the support given by my supervisor Dr. Li Zhang who showed utmost enthusiasm in the conduction of this research project. I appreciate her advice and understanding during the project. I would like to thank Dr. Ben Chong whose guidance and assistance was most beneficial in some aspects of this project. I would like to show gratitude to the previous PhD student Dr. Ikenna Bruce Efika who started this work for his support during and after his study. Special thanks to Edward Bray for assistance in some aspects of the rig build up.

To my friends and well-wishers, I couldn't have gone through the years of study without your motivation and words of encouragement. I am glad to let you all I know I made it at the end. A huge thank you most especially to Tolani who was there for me during difficult times. May God reward your efforts towards my life.

To my family, my brothers Chukwudi, Dr. Ifeanyi and Dr. Chineme, I want to say thank you for never doubting me and encouraging me to take on this PhD. You all have always fought for my education from birth and I am eternally grateful. To my parents, Dr. Mike Nwobu and Mrs. Felicia Nwobu thanks wouldn't be enough to show my appreciation. You funded my study for 8 years in UK and have catered for me financially. I pray we your children would continually make you proud and may God grant you your heart desires.

Most importantly to God Almighty, My Sovereign Father,

Chukwu Ebuka, Chukwu Ebuka, (You are Great) Sorom Tobe Ya, (Join me and Worship Him) Ma'm kowa nmeso oma gi oh, (If I talk about your goodness), Chi ga eji, chi ga abo (Night will come, and Day will break), Ma'm kowa ihe oma Ine meren m oh (If I talk about the all the good things you do), Chi ga eji, chi ga abo (Night will come, and Day will break), Asi n'aru mu buru so onu (If all my body was my mouth), Ozughi inye gi ekele ( It is not enough to praise you), Chi di nma (God is Good), Nare ekele (Take all the praise).

#### Abstract

Voltage fluctuation and power losses in the distribution line are problems in distribution networks. One method to mitigate these problems is by injecting reactive power into the network using a Static Synchronous Compensator (STATCOM). This can be used both for regulating the voltage and reducing the losses. A STATCOM is critically dependent on a grid synchronisation scheme that can accurately track the changes occurring in the grid phase and frequency. The Modular Multilevel Converter (MMC) is a promising topology for STATCOM applications because of its simple modular circuit structure that allows for higher voltage ratings, and conventionally uses a stack of sub-modules which are either two-level half or H-bridge converters.

As a novel alternative, the thesis investigates the practicality of a STATCOM based on a three-level flying capacitor (FC) converter. Two variants of this topology are presented; the FC Half-bridge and FC H-bridge. A comprehensive study is undertaken to compare these with the Half and H-bridge sub-module under STATCOM operation. Most importantly, an FC H-bridge-based STATCOM is investigated for reactive power compensation. The challenges of multilevel, multi-module PWM control schemes achieving good waveforms at low switching frequency, whilst maintaining module capacitor voltage balance, are thoroughly addressed. Simulation results validate the operation for both line voltage regulation and power factor correction. An experimental power system with an FC-based STATCOM rig is designed and built, and validates the simulation results for power factor correction. It demonstrates correct operation of a control scheme that includes a system for maintaining capacitor voltage balance.

Another new contribution is the investigation of a phase locking technique based on the Energy Operator (EO). The method, combining two different EO computations, is shown to achieve fast and accurate detection of frequency and phase angle when combined with an appropriate filter, and crucially operates well under unbalanced voltage conditions. The technique is compared with two other well-known phase locked loop (PLL) schemes, showing that it outperforms the others in terms of speed and accuracy. A hardware implementation of the EO-PLL validates the principle, showing the simplicity of the method.

# **Table of Contents**

| Acknowledgementsiv                                                            |

|-------------------------------------------------------------------------------|

| Abstractv                                                                     |

| Table of Contentsvi                                                           |

| List of Tables xiii                                                           |

| List of Figuresxv                                                             |

| List of Abbreviationsxxi                                                      |

| Chapter 1 Introduction1                                                       |

| 1.1 Background Literature1                                                    |

| 1.2 Flexible AC Transmission Systems                                          |

| 1.2.1 Thyristor Controlled Series Capacitor (TCSC)                            |

| 1.2.2 Static VAR Compensator (SVC)4                                           |

| 1.2.3 Static Synchronous Series Compensator (SSSC)5                           |

| 1.2.4 Static Synchronous Compensator (STATCOM)6                               |

| 1.2.5 Unified Power Flow Controller (UPFC)7                                   |

| 1.3 Multilevel Converter Topologies8                                          |

| 1.3.1 Neutral Point Clamped Converter8                                        |

| 1.3.2 Flying Capacitor Converter10                                            |

| 1.4 Modular Multilevel Converter Topologies                                   |

| 1.4.1 Classification of Modular Multilevel Converters (MMC) 13                |

| 1.4.2 Other MMC Sub-Module Configurations 15                                  |

| 1.4.2.1 Sub-Module Concepts15                                                 |

| 1.4.2.2 Other Circuit Structures                                              |

| 1.6 Grid Voltage Synchronisation Schemes 17                                   |

| 1.6.1 Open-Loop Schemes18                                                     |

| 1.6.2 Closed-Loop Schemes                                                     |

| 1.6.2.1 Classical SRF-PLL                                                     |

| 1.6.2.2 SRF-PLL with Filters                                                  |

| 1.6.2.3 SRF-PLL with Positive Sequence Extraction                             |

| 1.7 Aims, Objectives and Thesis Structure                                     |

| Chapter 2 Modular Multilevel Converter Sub-Module Assessment<br>for STATCOM25 |

| 2.1 Sub-Module Circuits Under Study                                           |

| 2.1.1 Devices and Components for Sub-Modules                                  |

| 2.1.2 Numbers of Sub-Modules Required                                | 27 |

|----------------------------------------------------------------------|----|

| 2.2 Guidelines for Sub-Module Assessment                             | 28 |

| 2.2.1 Footprint Assessment Guidelines                                | 28 |

| 2.2.2 Cost Assessment Guidelines                                     | 30 |

| 2.2.4 Control Assessment Guidelines                                  | 38 |

| 2.2.5 Topology Assessment Guidelines                                 | 38 |

| 2.3 Assessment of Different Sub-Module Concepts                      | 39 |

| 2.3.1 Half-Bridge Sub-Module                                         | 39 |

| 2.3.1.1 Footprint Assessment                                         | 39 |

| 2.3.1.2 Cost Assessment                                              | 40 |

| 2.3.1.3 Efficiency Assessment                                        | 40 |

| 2.3.1.4 Control Assessment                                           | 41 |

| 2.3.1.5 Topology Assessment                                          | 42 |

| 2.3.2 H-Bridge Sub-Module                                            | 42 |

| 2.3.2.1 Footprint Assessment                                         | 43 |

| 2.3.2.2 Cost Assessment                                              | 43 |

| 2.3.2.3 Efficiency Assessment                                        | 44 |

| 2.3.2.4 Control Assessment                                           | 44 |

| 2.3.2.5 Topology Assessment                                          | 45 |

| 2.3.3 FC-Half-Bridge Sub-Module                                      | 46 |

| 2.3.3.1 Footprint Assessment                                         | 47 |

| 2.3.3.2 Cost Assessment                                              | 47 |

| 2.3.3.3 Power Efficiency Assessment                                  | 48 |

| 2.3.3.4 Control Assessment                                           | 48 |

| 2.3.3.5 Topology Assessment                                          | 49 |

| 2.3.4 FC H-Bridge Sub-Module                                         | 50 |

| 2.3.4.1 Footprint Assessment                                         | 50 |

| 2.3.4.2 Cost Assessment                                              | 51 |

| 2.3.4.3 Efficiency Assessment                                        | 51 |

| 2.3.4.4 Control Assessment                                           | 52 |

| 2.3.4.5 Topology Assessment                                          | 53 |

| 2.4. Discussion and Comparison of Sub-Module Concepts for<br>STATCOM | 54 |

|                                                                      |    |

| 2.5. Summary<br>Chapter 3 Pulse Width Modulation Schemes for FC-MMC  |    |

| 3.1 Sine-Triangle Based PWM Modulation Schemes                       |    |

|                                                                      |    |

| 3.2 Design Considerations for an FC-MMC-Based STATCOM                                                                                                                                                   | 60                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 3.2.1 Structure of the FC-MMC                                                                                                                                                                           | 60                                                                   |

| 3.2.2 Total Harmonic Distortion (THD)                                                                                                                                                                   | 60                                                                   |

| 3.2.2.1 Analysis of THD for Bipolar Switching                                                                                                                                                           | 60                                                                   |

| 3.2.2.2 Analysis of THD for Unipolar Switching                                                                                                                                                          | 62                                                                   |

| 3.2.3 Natural Balancing Capability                                                                                                                                                                      | 64                                                                   |

| 3.2.4 Sub-Module Utilisation                                                                                                                                                                            | 65                                                                   |

| 3.2.5 Circuit and PWM Parameters Used for Simulation                                                                                                                                                    | 65                                                                   |

| 3.3. Phase Disposition PWM for FC-MMC                                                                                                                                                                   | 66                                                                   |

| 3.3.1 Total Harmonic Distortion (THD) Analysis                                                                                                                                                          | 67                                                                   |

| 3.3.2 Natural Voltage Balancing Capability                                                                                                                                                              | 69                                                                   |

| 3.3.3 Sub-Module Utilisation                                                                                                                                                                            | 70                                                                   |

| 3.4 Phase Shifting PWM for FC-MMC                                                                                                                                                                       | 70                                                                   |

| 3.4.1 Total Harmonic Distortion (THD) Analysis                                                                                                                                                          | 72                                                                   |

| 3.4.2 Natural Balancing Capability                                                                                                                                                                      | 74                                                                   |

| 3.4.3 Sub-Module Utilisation                                                                                                                                                                            | 74                                                                   |

| 3.5 Comparison of PD-PWM and PS-PWM Schemes                                                                                                                                                             | 75                                                                   |

| 3.6. Summary                                                                                                                                                                                            | 76                                                                   |

|                                                                                                                                                                                                         |                                                                      |

| Chapter 4 Synchronisation of Grid Connected Converters Using<br>the Energy Operator                                                                                                                     | 77                                                                   |

|                                                                                                                                                                                                         |                                                                      |

| the Energy Operator                                                                                                                                                                                     | 78                                                                   |

| the Energy Operator.4.1 Grid Synchronisation Based on Energy Operator                                                                                                                                   | 78<br>78                                                             |

| <ul> <li>the Energy Operator.</li> <li>4.1 Grid Synchronisation Based on Energy Operator</li> <li>4.1.1 Literature Review of the Energy Operator</li> </ul>                                             | 78<br>78<br>78                                                       |

| <ul> <li>the Energy Operator.</li> <li>4.1 Grid Synchronisation Based on Energy Operator</li> <li>4.1.1 Literature Review of the Energy Operator</li> <li>4.1.2 Principle of Energy Operator</li> </ul> | 78<br>78<br>78<br>80                                                 |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>78<br>80<br>80                                           |

| <ul> <li>the Energy Operator.</li> <li>4.1 Grid Synchronisation Based on Energy Operator</li></ul>                                                                                                      | 78<br>78<br>78<br>80<br>80<br>81                                     |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>78<br>80<br>80<br>81<br>82                               |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>80<br>80<br>81<br>82<br>82                               |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>80<br>80<br>81<br>82<br>82                               |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>80<br>80<br>81<br>82<br>82<br>83                         |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>78<br>80<br>80<br>81<br>82<br>82<br>83                   |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>78<br>80<br>80<br>81<br>82<br>82<br>83<br>84<br>85       |

| <ul> <li>the Energy Operator</li></ul>                                                                                                                                                                  | 78<br>78<br>78<br>80<br>80<br>81<br>82<br>82<br>83<br>83<br>85<br>85 |

| 4.2     | Energy Operator Phase Locked Loop (EO-PLL)                                |        |

|---------|---------------------------------------------------------------------------|--------|

|         | 4.2.1 Energy Operator PLL (EO-PLL) Algorithm                              |        |

|         | 4.2.2 Features of EO-PLL Scheme                                           | 91     |

|         | 4.2.3 Filtering Requirements                                              | 91     |

| 4.3     | Simulation Studies of EO-PLL Scheme                                       |        |

|         | 4.3.1Performance of EO-PLL with Balanced Voltage                          |        |

|         | 4.3.1.1Simulation Results                                                 |        |

|         | 4.3.2 Performance of EO-PLL with Unbalanced Voltage                       |        |

|         | 4.3.2.1 Simulation Results - Type B Fault                                 |        |

|         | 4.3.2.2 Simulation Results - Type C Fault                                 |        |

|         | 4.3.2.3 Computational Complexity                                          |        |

|         | 4.3.3 Performance of EO-PLL with Voltage Corrupted with<br>Harmonic Noise |        |

|         | 4.3.3.1 Simulation Results                                                |        |

| 4.4     | Experimental Validation of EO-PLL                                         | 101    |

|         | 4.4.1 Voltage Generation                                                  | 101    |

|         | 4.4.1.1 Filtering Requirements                                            | 103    |

|         | 4.4.2 Signal Processing                                                   | 104    |

|         | 4.4.3 Experimental Studies of EO-PLL Scheme                               | 106    |

|         | 4.4.3.1 Performance of EO-PLL with Balanced Volta                         | ge 106 |

|         | 4.4.3.2 Performance of EO-PLL with Unbalanced<br>Voltage                  | 108    |

| 4.5     | Conclusions                                                               | 110    |

| Chapter | 5 FC-MMC Based STATCOM                                                    | 111    |

| 5.1     | Power Flow Analysis                                                       | 112    |

|         | 5.1.1 PCC Voltage Regulation                                              | 113    |

|         | 5.1.2 Unity Power Factor Correction                                       | 115    |

| 5.2     | Power Rating of Converter                                                 | 116    |

|         | 5.2.1 DC Capacitor Voltage Rating                                         | 119    |

|         | 5.2.1.1 Energy Requirements of Sub-Module<br>Capacitors                   | 121    |

|         | 5.2.1.2 Converter Filter Design Consideration                             | 123    |

|         | 5.2.2 Case Study: Variations of DC-Bus Voltage Rating                     | 123    |

| 5.3     | Simulation Studies of an FC-MMC STATCOM                                   | 126    |

|         | 5.3.1 Power System Configuration                                          | 126    |

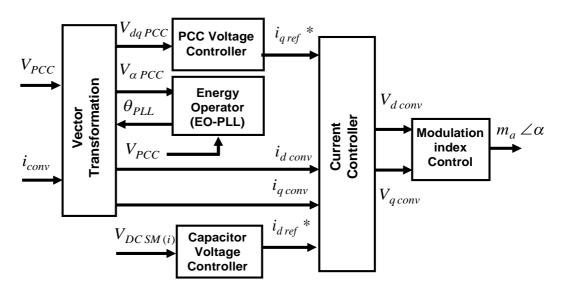

|         | 5.3.2 Control System Implementation                                       | 129    |

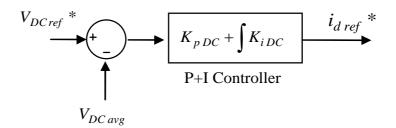

|         | 5.3.3 Sub-Module DC Voltage Control            | 130 |

|---------|------------------------------------------------|-----|

|         | 5.3.4 PCC Voltage Control                      | 131 |

|         | 5.3.5 Current Controller                       | 132 |

| 5.4 \$  | Simulation Results and Discussions             | 132 |

|         | 5.4.1 Regulation of PCC Voltage                | 132 |

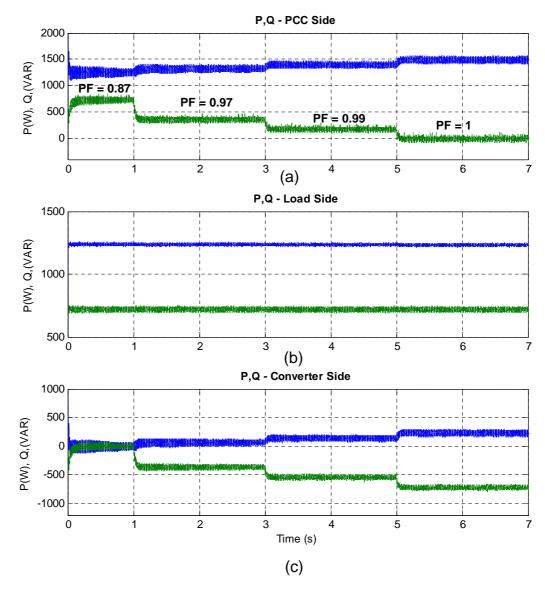

|         | 5.4.1.1 Responses of Active and Reactive Power | 133 |

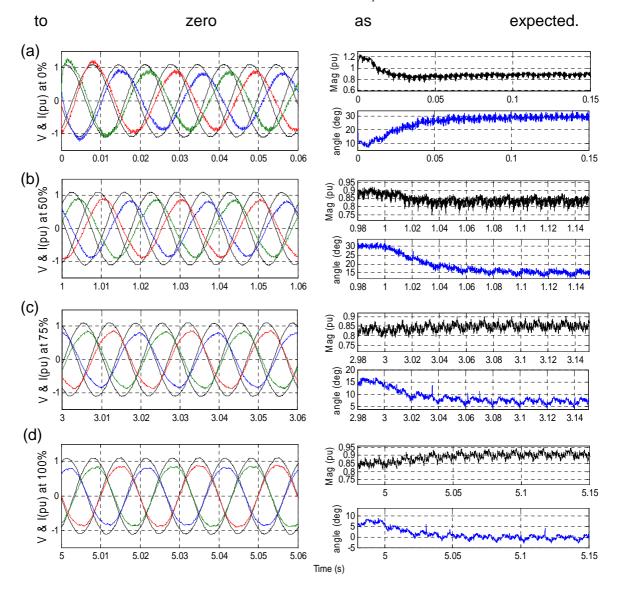

|         | 5.4.1.2 PCC Side Voltage and Current Responses | 134 |

|         | 5.4.1.3 Converter DC Capacitor Voltage         | 136 |

|         | 5.4.2Power Factor Correction Control           | 138 |

|         | 5.4.2.1 Active and Reactive Current Responses  | 138 |

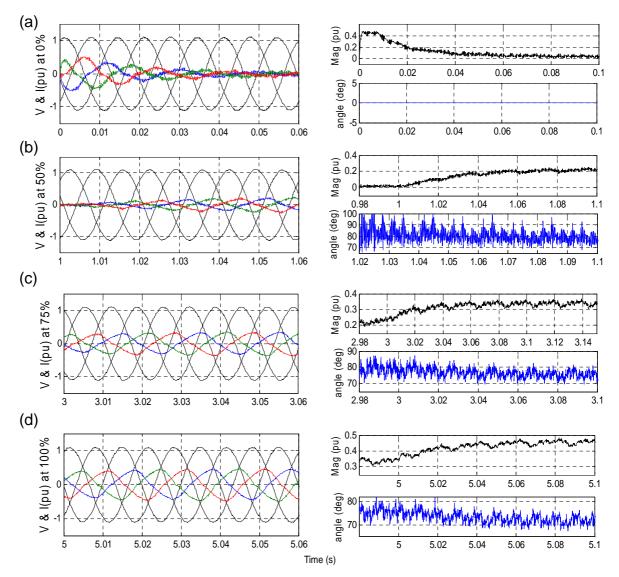

|         | 5.4.2.2 PCC Side Voltage and Current Responses | 139 |

|         | 5.4.2.3 Converter DC Capacitor Voltage         | 141 |

| 5.5     | Conclusions                                    | 143 |

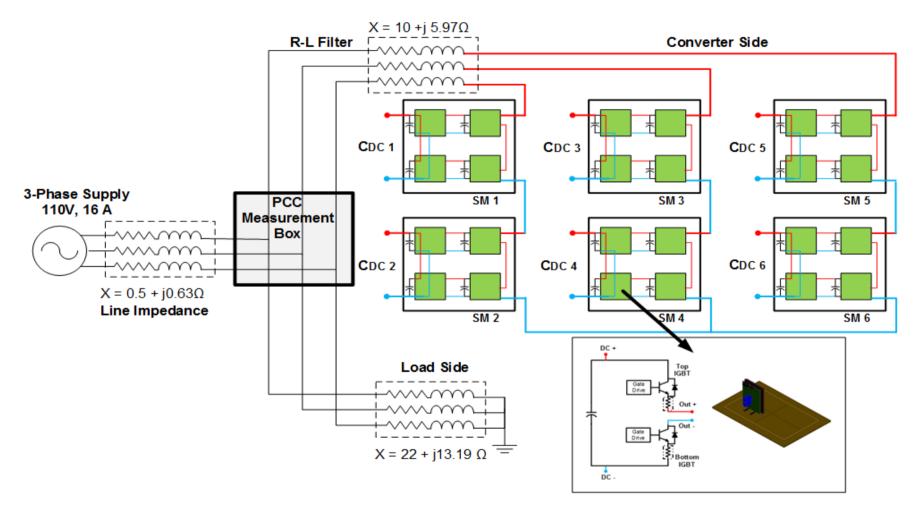

| Chapter | 6 Experimental System                          | 144 |

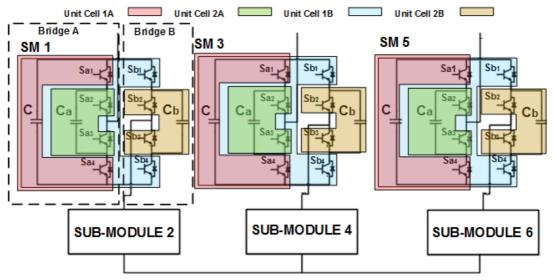

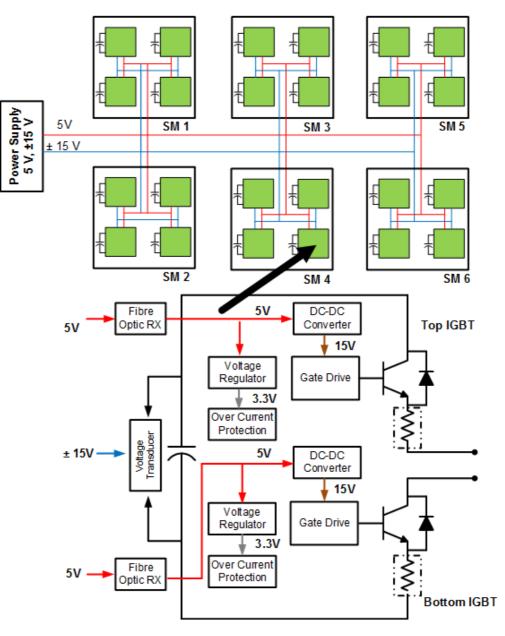

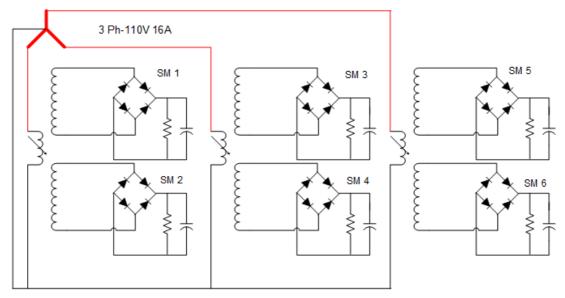

| 6.1     | The Structure of FC-MMC                        | 145 |

|         | 6.1.1 Power Circuit of Cell Card               | 150 |

|         | 6.1.2 Gate Drive Circuit                       | 153 |

|         | 6.1.3 Fibre Optic Transmitter/Receiver Circuit | 153 |

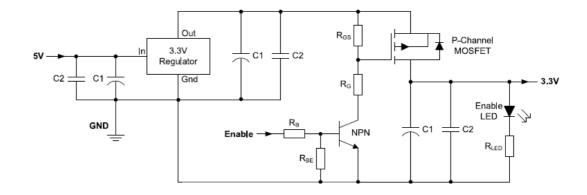

|         | 6.1.4 Power Supplies for Cell Cards            | 155 |

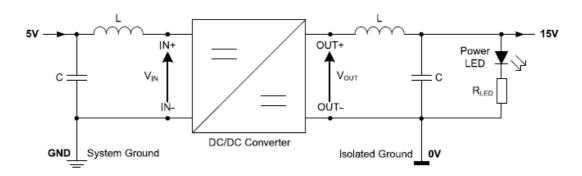

|         | 6.1.5 Isolated DC Power Supply                 | 157 |

|         | 6.1.6 Power Components                         | 158 |

|         | 6.1.7.1 Switching Device                       | 158 |

|         | 6.1.7.2 Capacitors                             | 159 |

| 6.2     | Data Acquisition Unit                          | 160 |

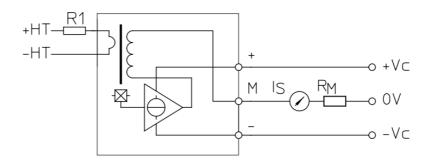

|         | 6.2.1 Voltage Measurement                      | 160 |

|         | 6.2.2 Current Measurement                      | 161 |

|         | 6.2.3Measurement PCC Box Layout                | 161 |

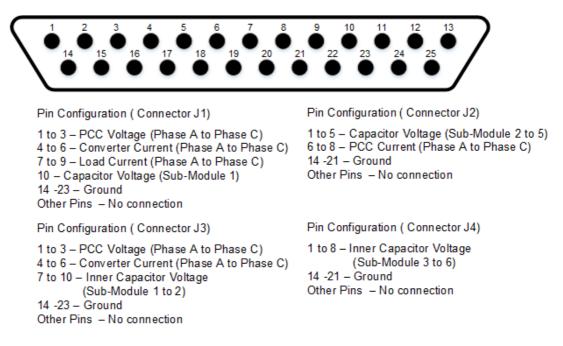

|         | 6.2.4.1 Pin layout Power Cell Card Feedback    | 166 |

|         | 6.2.4.2 Pin layout Breakout Connectors         | 166 |

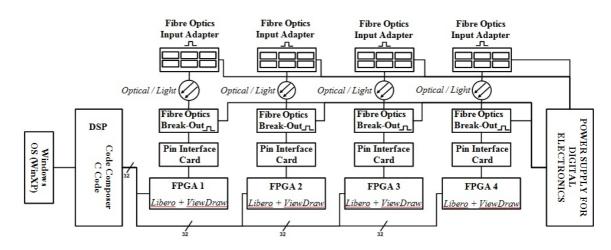

| 6.3     | Devices and Digital Control Unit               | 167 |

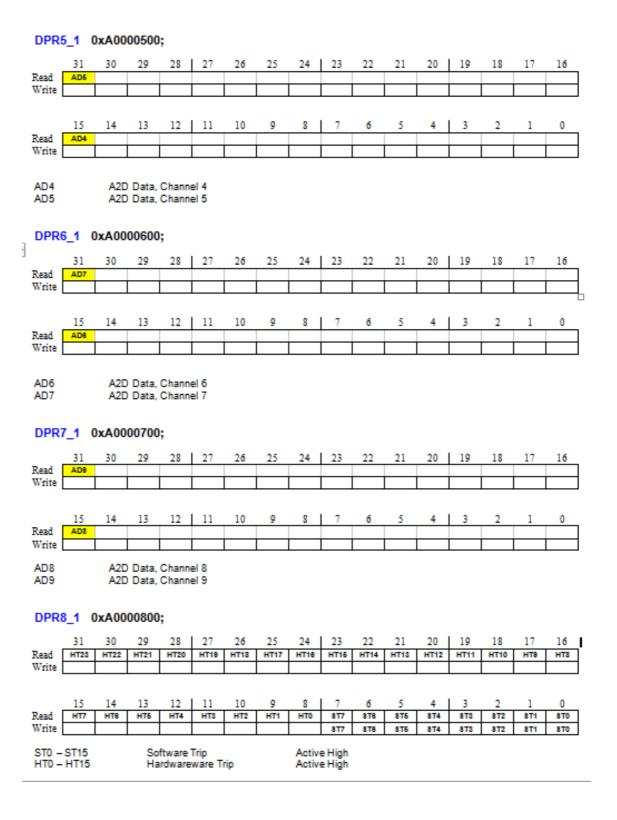

|         | 6.3.1 FPGA Cards                               | 168 |

|         | 6.3.1.1 Analogue to Digital Conversion         | 170 |

|         | 6.3.1.2 Interrupt Signal Generator             | 170 |

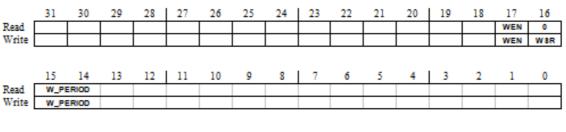

|         | 6.3.1.3 Modulation Unit                        | 171 |

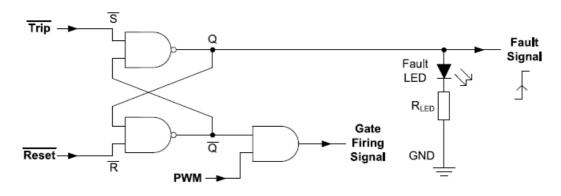

|         | 6.3.1.4 Fault Trip Unit                        | 173 |

| 6.3.2 Digital Signal Processor                           | 173 |

|----------------------------------------------------------|-----|

| 6.3.2.2 Calibration                                      | 174 |

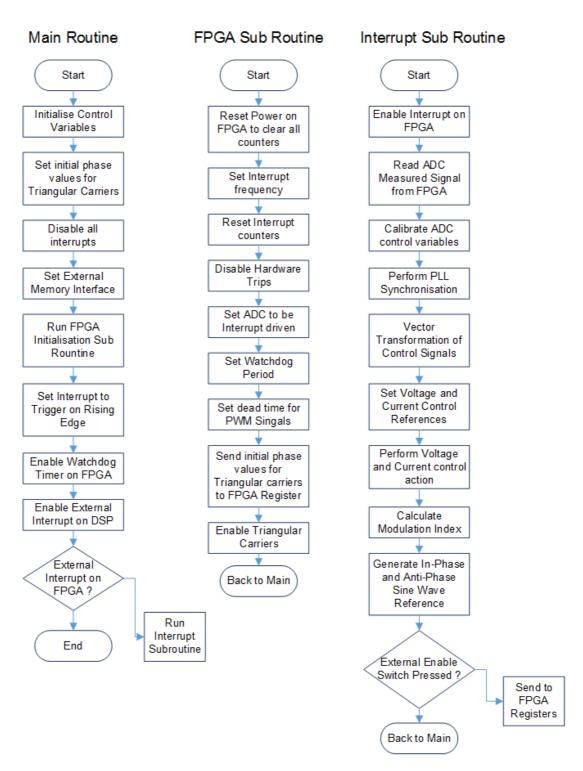

| 6.3.2.3 Program Overview                                 | 175 |

| 6.4 Conclusions                                          | 177 |

| Chapter 7 Experimental Validation                        | 178 |

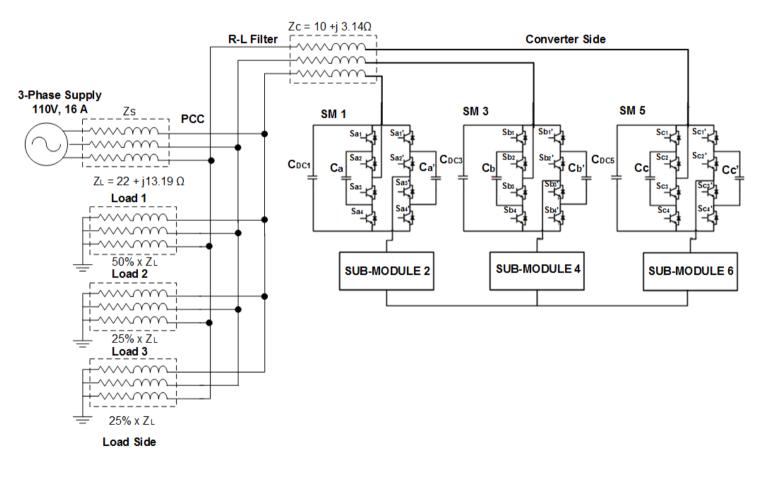

| 7.1 Power System Configuration                           | 178 |

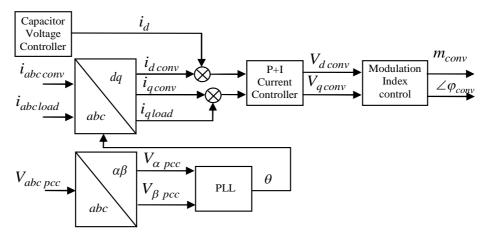

| 7.2 Control System Implementation                        | 182 |

| 7.2.1 Grid Synchronisation                               | 182 |

| 7.2.2 Discrete PI Control                                | 183 |

| 7.2.3 Capacitor Pre-Charge Control                       | 184 |

| 7.3 Results and Discussion                               | 185 |

| 7.3.1 Sub-module Voltages maintained by DC Power Supply. | 185 |

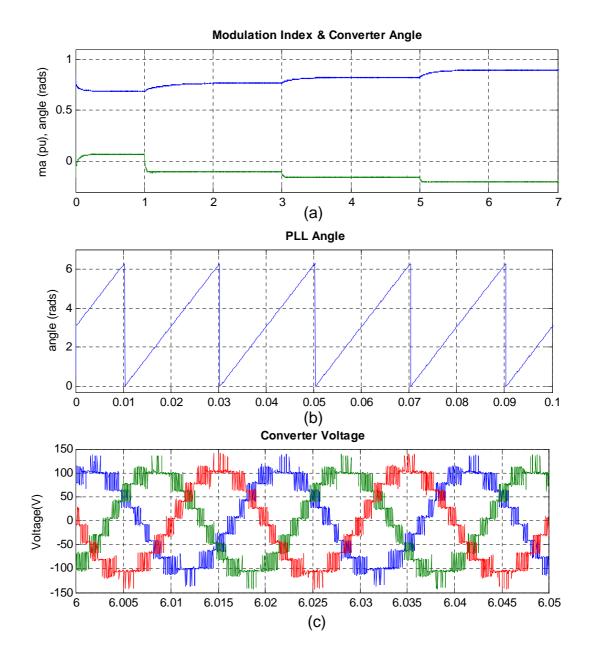

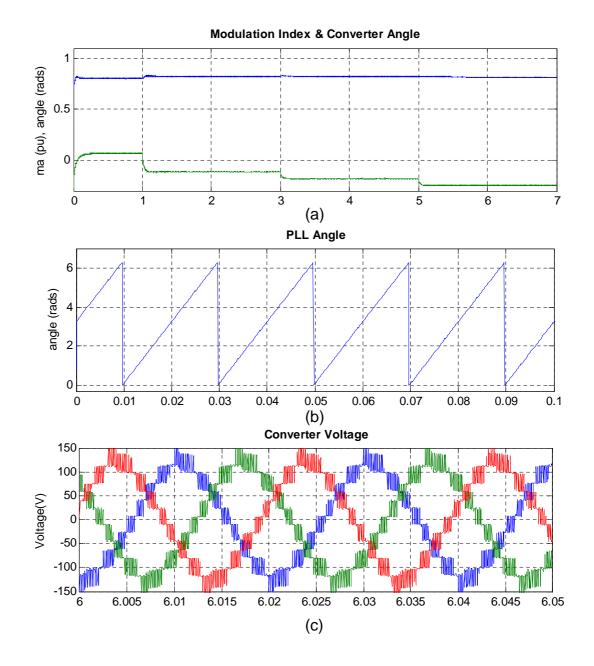

| 7.3.1.1 Vector Control Signals                           | 185 |

| 7.3.1.2 Active and Reactive Power                        | 188 |

| 7.3.1.3 PCC Side Waveforms                               | 189 |

| 7.3.1.4 Converter Side Waveforms                         | 190 |

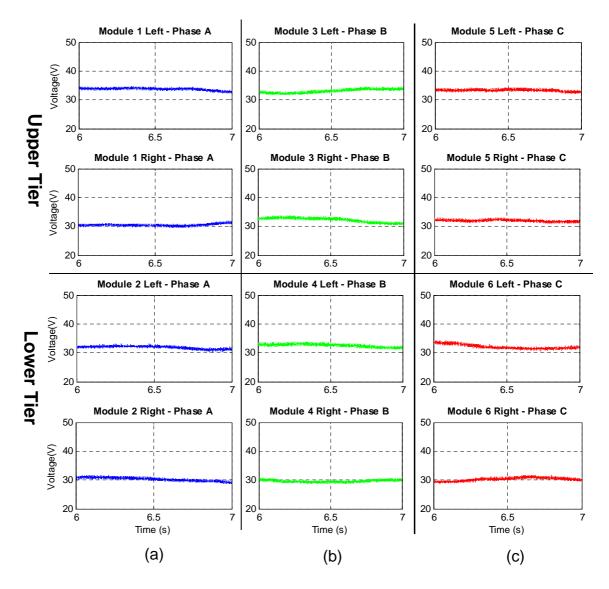

| 7.3.1.5 Capacitor Balancing                              | 193 |

| 7.3.2 Sub-module Voltages maintained by DC Voltage       |     |

| Control                                                  |     |

| 7.3.2.1 Vector Control Signals                           |     |

| 7.3.2.2 Active and Reactive Power                        |     |

| 7.3.2.3 PCC Side Waveforms                               |     |

| 7.3.2.4 Converter Side Waveforms                         | 200 |

| 7.3.2.5 Capacitor Balancing                              | 202 |

| 7.3 Comparison with Simulation Results                   | 205 |

| 7.4 Conclusions                                          |     |

| Chapter 8 Conclusions and Future Recommendations         |     |

| 8.1 Conclusions                                          | 207 |

| 8.2 Future Recommendations                               | 208 |

| List of References                                       | 210 |

| Appendix A                                               | 224 |

| A.1 Multilevel Converter Current Paths                   | 224 |

| A.2 Fortescue Theorem                                    | 225 |

| Appendix B                                               | 226 |

| B.1 Energy Operator Trigonometric Identities             | 226 |

| B.2 Principles of PLL Schemes Used for Comparison        | 227 |

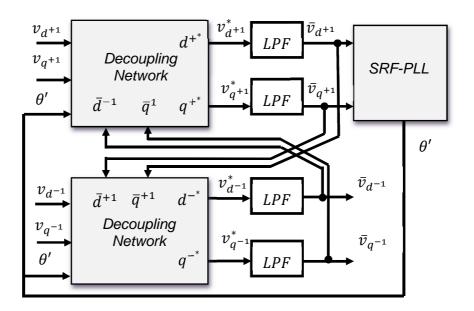

| B.2.1 Decoupled Double Synchronous Reference Frame<br>(DDSRF) | 227 |

|---------------------------------------------------------------|-----|

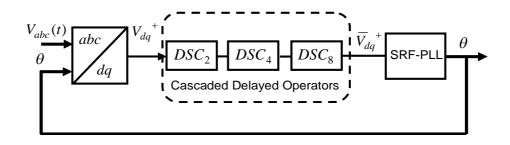

| B 2.2 Cascaded Delay Signal Cancellation (CDSC-PLL)           |     |

| B.3 C-Code for Energy Operator Experiments                    |     |

| B 3.1 C-Code for Voltage Generation                           | 231 |

| Appendix C Fundamental Power Relationships                    | 233 |

| C.1 Clarkes and Parks Transformation                          | 233 |

| C.2 Derivation of Decoupling Operator $(e^{j\theta})$         | 235 |

| C.3 Matlab Code for Case Study                                | 237 |

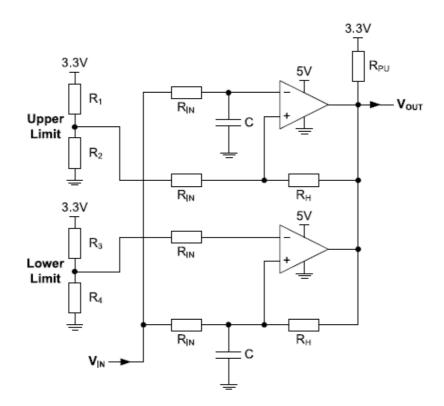

| Appendix D Current Protection Circuitry                       | 238 |

| D.1 Current Sensing Circuit                                   | 238 |

| D.2 Current Limiter Circuit                                   | 240 |

| Appendix E DSP and FPGA Register Allocation                   | 242 |

| Table 1.1: Three-level neutral point clamped inverter switching                                  | ~ |

|--------------------------------------------------------------------------------------------------|---|

| states1                                                                                          |   |

| Table 1.2: Five-level flying capacitor multilevel switching states1                              |   |

| Table 2.1: Devices for Sub-Module Assessment    2                                                |   |

| Table 2.2: Devices and Per-unitised sizes    3                                                   |   |

| Table 2.3: Price of Devices for One Sub-Module    3                                              |   |

| Table 2.4: Topology Score Based Guide                                                            | 8 |

| Table 2.5: Per-unit Width of a Half-bridge Sub-module         3                                  | 9 |

| Table 2.6: Half-Bridge Sub-Module Cost Assessment                                                | 0 |

| Table 2.7: Switch and Diode States for Rectifier and Inverter Mode         of Operations       4 | 1 |

| Table 2.8: Possible Ways to Charge and Discharge Capacitors 4                                    | 1 |

| Table 2.9: Topology Assessment of Half-Bridge Sub-Module 4                                       | 2 |

| Table 2.10: Per-unit Width of a H-bridge Sub-module 4                                            | 3 |

| Table 2.11:Half-Bridge Sub-Module Cost Assessment                                                | 3 |

| Table 2.12:Switch and Diode States for Rectifier and InverterMode of Operation                   | 4 |

| Table 2.13: Possible Ways to Charge and Discharge Capacitors 4                                   | 5 |

| Table 2.14: Topology assessment of the H-bridge sub-module 4                                     | 5 |

| Table 2.15: Per-unit Width of a FC Half-Bridge Sub-Module 4                                      | 7 |

| Table 2.16:Half-Bridge Sub-Module Cost Assessment                                                | 7 |

| Table 2.17:Switching and Diode States for Rectifier and Inverter         Mode of Operation       | 8 |

| Table 2.18: Possible Ways to Charge and Discharge Capacitors 4                                   | 9 |

| Table 2.19: Topology assessment of the FC Half-Bridge Sub-         Module                        |   |

| Table 2.20: Per-unit Width of a FC Full-bridge Sub-module                                        |   |

| Table 2.21:H-Bridge Sub-Module Cost Assessment                                                   |   |

| Table 2.22:Switching and Diode States for Rectifier and Inverter         Modes         5         |   |

| Table 2.23: Possible Ways to Charge and Discharge Capacitors                                     | 3 |

| Table 2.24: Topology assessment of the FC H-bridge Sub-Module 5                                  | 3 |

| Table 2.25: Comparison of Sub-Module Concepts based on a 20kV MMC STATCOM                        |   |

| Table 3.1 Parameters for FC-MMC Comparison                                                       |   |

| •                                                                                                |   |

| Table 3.2: Comparison of Modulation Techniques for FC-MMC                                                                             | . 75 |

|---------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 4.1: Complexity of the Schemes Based on Performance                                                                             | . 98 |

| Table 4.2: Compatibility Levels For Individual harmonic Voltages         in Low and Medium Voltage Networks Reproduced from IEC 6100- | 00   |

| 3-6                                                                                                                                   | . 99 |

| Table 5.1: Power System Parameters FC-MMC                                                                                             | 127  |

| Table 6.1: IGBT Characteristics                                                                                                       | 159  |

| Table 6.2: Capacitor Characteristics                                                                                                  | 159  |

| Table 7.1: Power System Characteristics                                                                                               | 179  |

# List of Figures

| Figure 1.1: Future Transmission and Distribution Grid System                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Thyristor Controlled Series Capacitor: (a) Thyristor<br>Controlled Reactor with fixed capacitor (b) Variable reactance<br>representation                      |

| Figure 1.3: Static VAR Compensator: (a) TCR with fixed capacitor 5                                                                                                        |

| Figure 1.4: Static Synchronous Series Compensator: (a)<br>Converter connected to network by series transformer (b)<br>Equivalent power circuit representation             |

| Figure 1.5: Static Synchronous Compensator: (a) Converter shunt<br>connected to the network (b) Equivalent power circuit<br>representation                                |

| Figure 1.6: Unified Power Flow Controller7                                                                                                                                |

| Figure 1.7: H-bridge Configuration of a Neutral Point Clamped<br>Converter                                                                                                |

| Figure 1.8: H-bridge configuration of a five-level Flying Capacitor<br>Multilevel Inverter                                                                                |

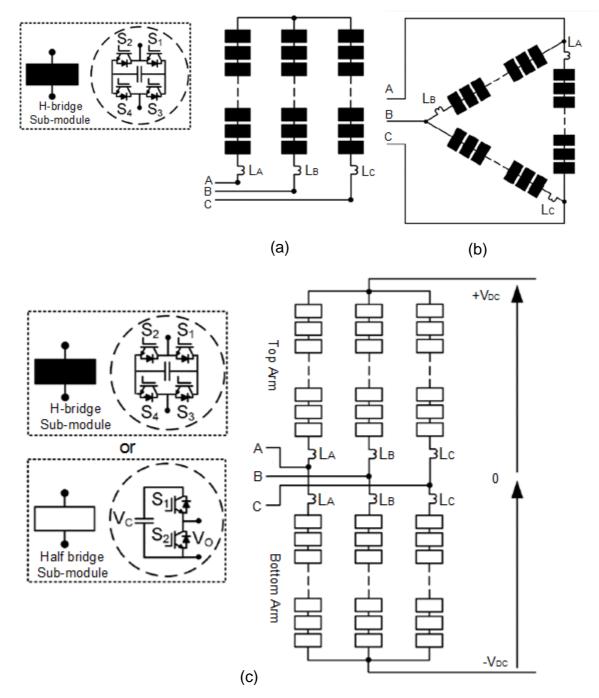

| Figure 1.9: Power Circuit Configuration (a) Single Star Bridge<br>Cells (b) Single Delta Bridge Cells (c) Double Star Chopper/Bridge<br>Cells                             |

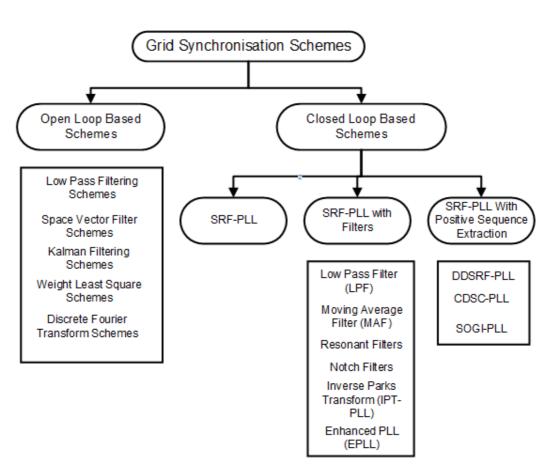

| Figure 1.10: Classification of Grid Synchronisation Schemes                                                                                                               |

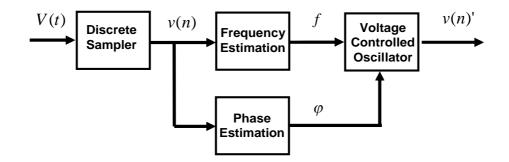

| Figure 1.11: Basic structure of an open loop synchronisation technique                                                                                                    |

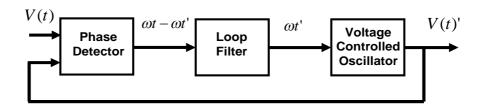

| Figure 1.12: Basic structure of a closed loop synchronisation technique                                                                                                   |

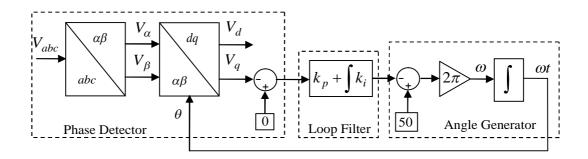

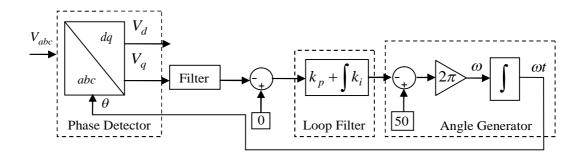

| Figure 1.13: Synchronous Reference Frame PLL (SRF-PLL)                                                                                                                    |

| Figure 1.14: Filter +SRF-PLL 22                                                                                                                                           |

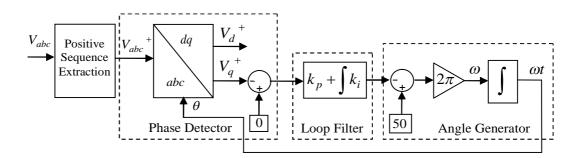

| Figure 1.15: Positive Sequence Extraction + (SRF-PLL)                                                                                                                     |

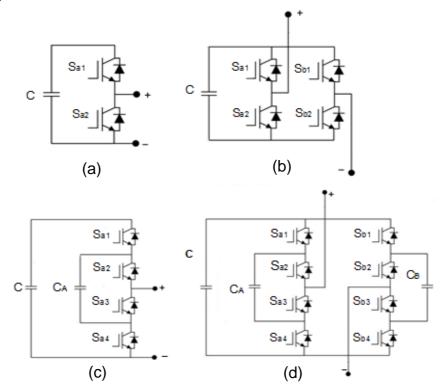

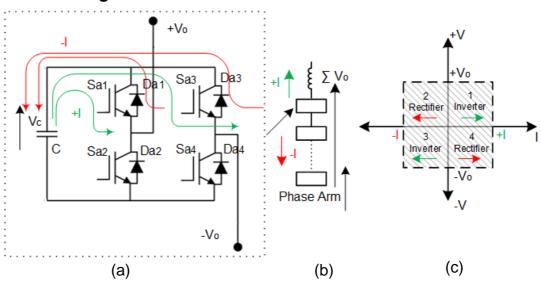

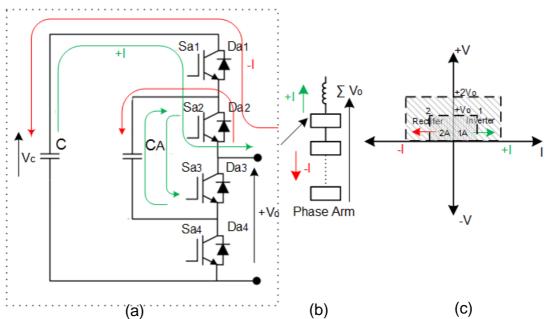

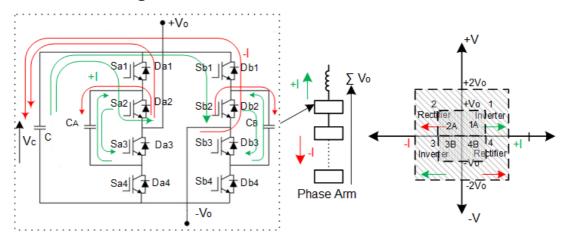

| Figure 2.1: MMC Sub-modules (a) Half-Bridge (b) H-bridge (c) FC<br>Half-bridge (d) FC H-bridge                                                                            |

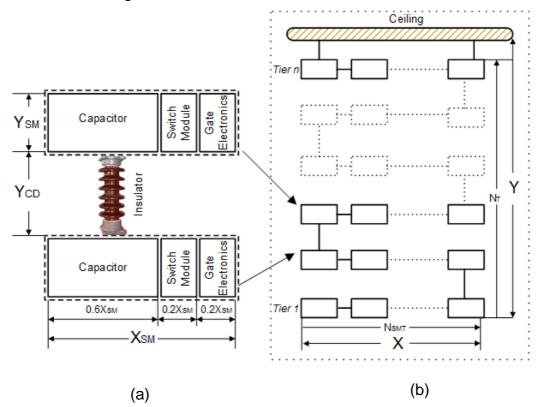

| Figure 2.2: Guideline for Footprint Assessment (a) Sub-module<br>Footprint with insulator (b) Platform Footprint with sub-modules 28                                      |

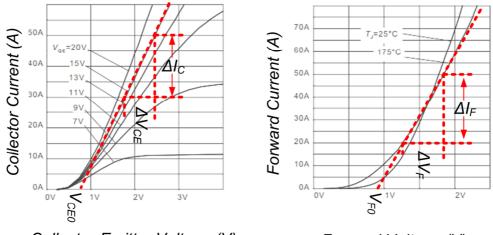

| Figure 2.3: Characteristics of the IGBT Collector-Emitter Voltage to current and Diode Forward Voltage to current                                                         |

| Figure 2.4: Characteristics of the IGBT current and switching energy losses [144]                                                                                         |

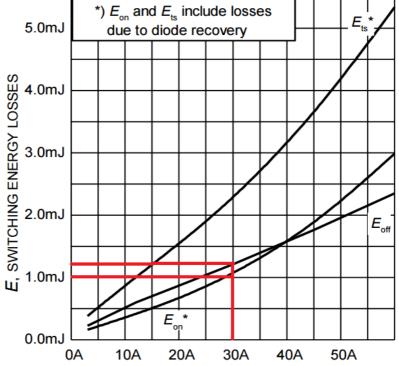

| Figure 2.5: Half-bridge Sub-module: (a) Power Circuit showing<br>Rectifier and Inverter Mode (b) Sub-module arrangement for one<br>phase (c) Two Quadrant operation modes |

| Figure 2.6:H-bridge Sub-module: (a) Power Circuit showing<br>Rectifier and Inverter Modes (b) Sub-module arrangement for one<br>phase (c) Four Quadrant operation modes        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.7: FC Half-bridge Sub-module: (a) Power Circuit showing<br>Rectifier and Inverter Modes (b) Sub-module arrangement for one<br>phase (c) I-V two Quadrant operations46 |

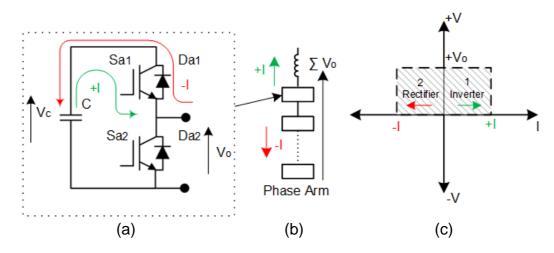

| Figure 2.8:FC H-bridge Sub-module: (a) Power Circuit showing<br>Rectifier and Inverter Mode (b) Sub-module arrangement for one<br>phase (c) I-V four Quadrant operations       |

| Figure 3.1: Circuit diagram of sub-modules in star configuration 60                                                                                                            |

| Figure 3.2: Bipolar Switching of Unit Cells61                                                                                                                                  |

| Figure 3.3: Total Harmonic Distortion (THD) for Bipolar Switching 62                                                                                                           |

| Figure 3.4: Unipolar Switching of Unit Cells                                                                                                                                   |

| Figure 3.5:Total Harmonic Distortion (THD) for Unipolar Switching 64                                                                                                           |

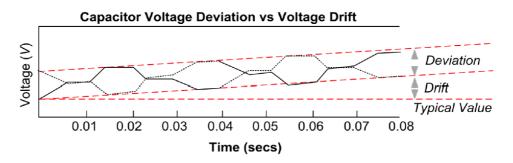

| Figure 3.6: Illustration of Capacitor Voltage Deviation and Voltage Drift                                                                                                      |

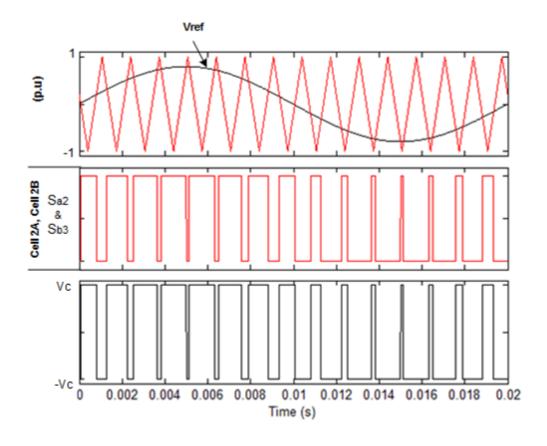

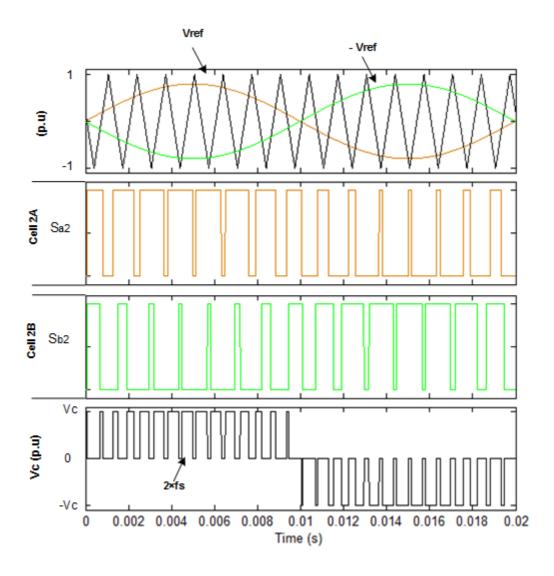

| Figure 3.7: Phase Disposition PWM applied to FC-MMC at $m_f = 1566$                                                                                                            |

| Figure 3.8: Phase Voltage of the FC-MMC under PD-PWM                                                                                                                           |

| Figure 3.9: Phase voltage spectrum & THD value for PD-PWM at $m_f = 15$                                                                                                        |

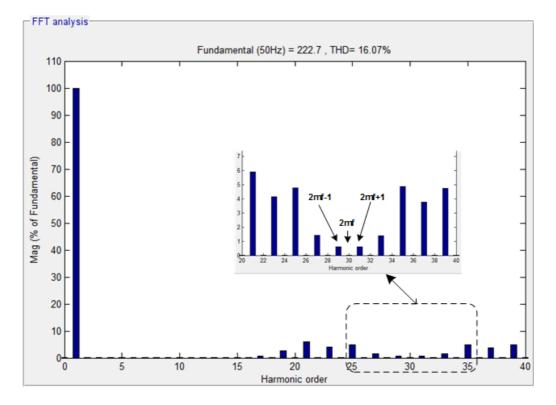

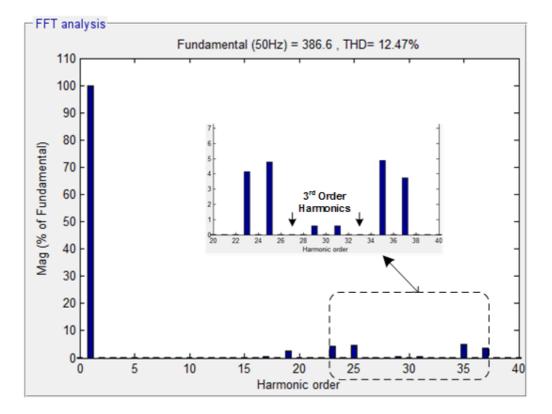

| Figure 3.10:Line Voltage Spectrum & THD value for PD-PWM at $m_f = 15$                                                                                                         |

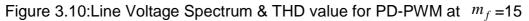

| Figure 3.11: PD-PWM Switching actions for One sub-module in a fundamental cycle                                                                                                |

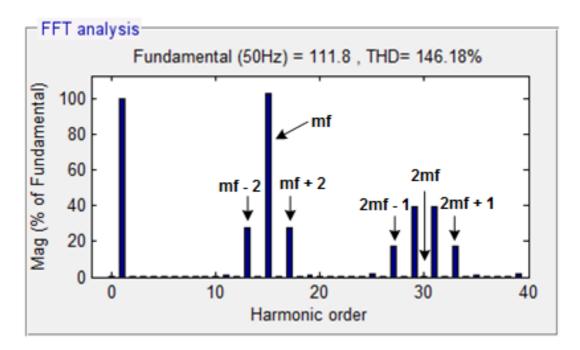

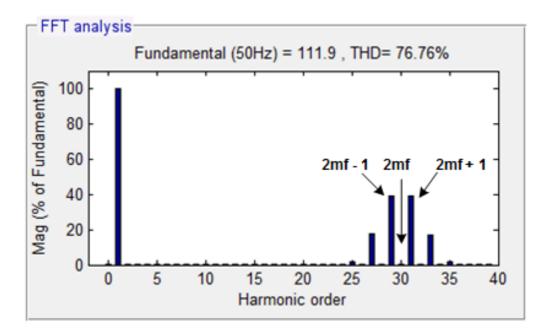

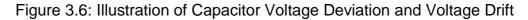

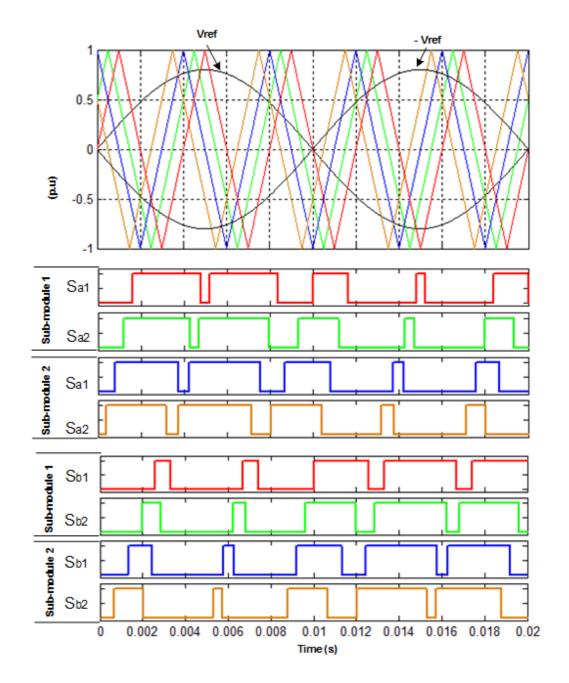

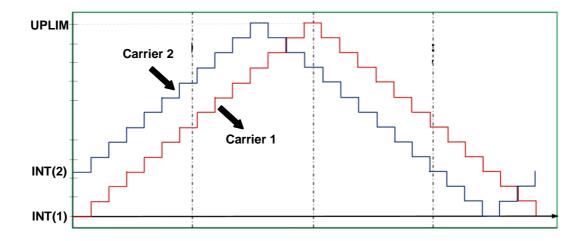

| Figure 3.12: Phase Disposition PWM applied to FC-MMC at $m_f = 5 \dots 71$                                                                                                     |

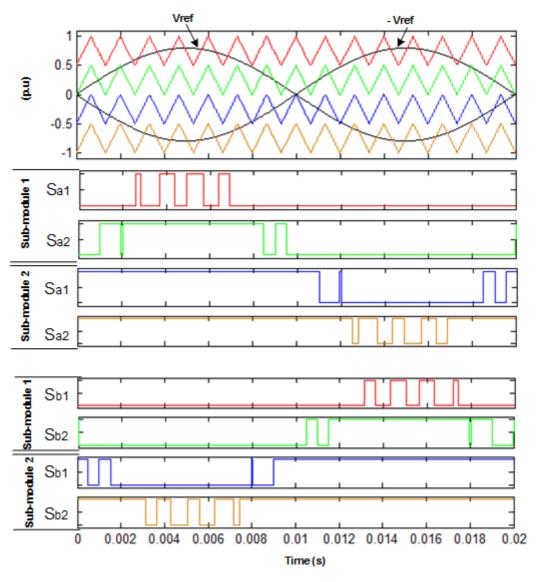

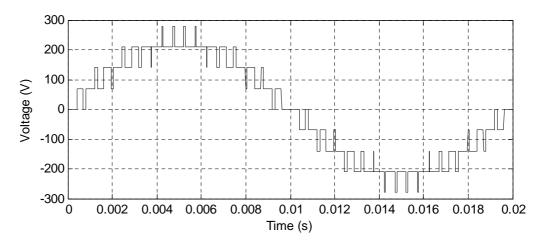

| Figure 3.13: Phase Voltage of the FC-MMC under PS-PWM                                                                                                                          |

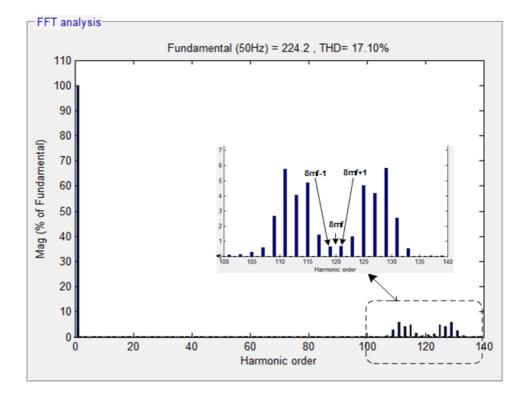

| Figure 3.14: Phase Voltage Spectrum & THD value for PS-PWM at $m_f = 15$                                                                                                       |

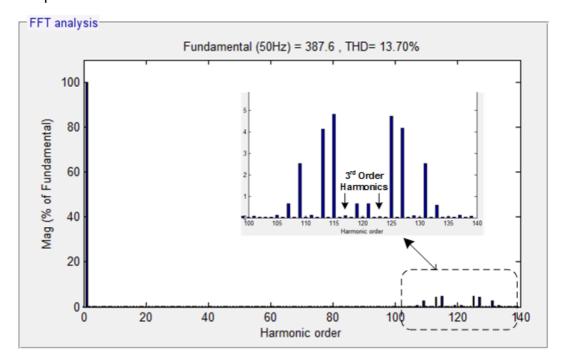

| Figure 3.15: Line Voltage Spectrum & THD for PS-PWM at $m_f$ =1573                                                                                                             |

| Figure 3.16: PS-PWM Switching actions in a fundamental cycle                                                                                                                   |

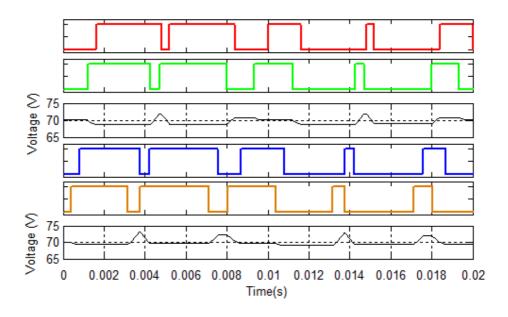

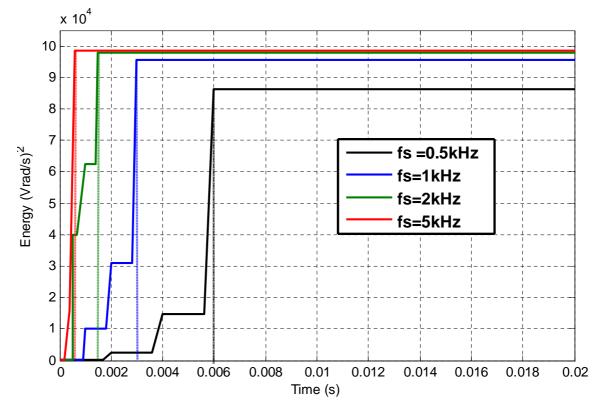

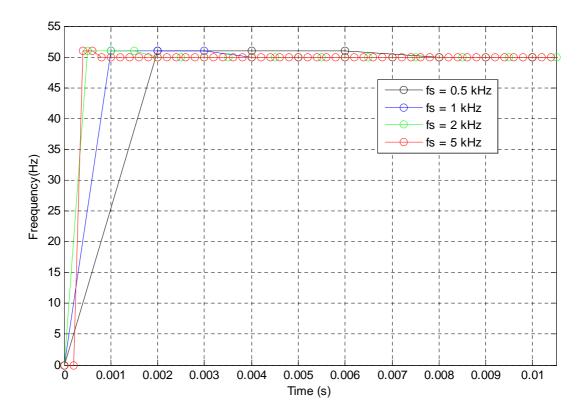

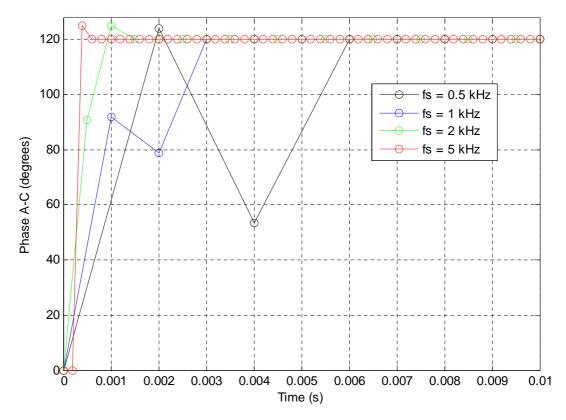

| Figure 4.1: Energy of voltage signal at different sampling frequencies                                                                                                         |

| Figure 4.2: Frequency estimates of voltage signal at different sampling frequencies                                                                                            |

| Figure 4.3: Phase angle estimation of a voltage signal at different sampling frequencies                                                                                       |

| Figure 4.4: Block Diagram of EO-PLL Implementation                                                                                                                             |

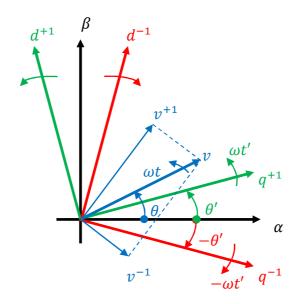

| Figure 4.5: Graphical Illustration of EO-PLL Under Unbalanced Voltages                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.6: Data processing stages with a DFT as a filter                                                                                                                                                      |

| Figure 4.7: EO-PLL Under Balanced Voltage Conditions                                                                                                                                                           |

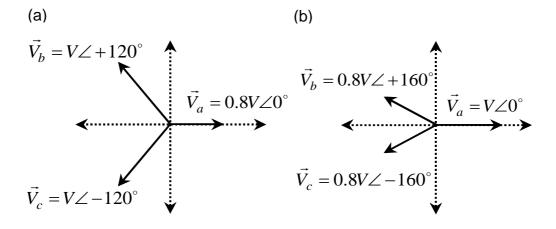

| Figure 4.8: (a) Single phase grid fault – Type B (b) Phase to phase grid fault -Type C                                                                                                                         |

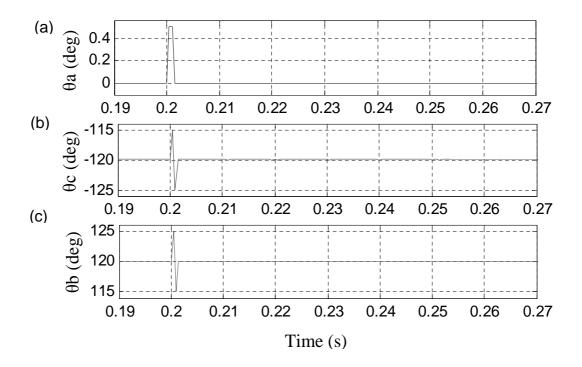

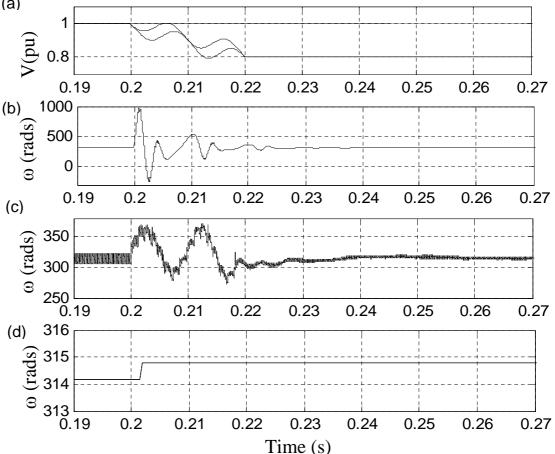

| Figure 4.9: Comparison of response times for frequency tracking<br>under type B fault (a) Peak Voltage (pu) (b) DDSRF-PLL, (c) CDSC-<br>PLL, (d) EO-PLL                                                        |

| Figure 4.10: EO-PLL Estimation of Phase Angles under type B<br>fault; (a) Phase A (degrees) (b) Phase C (degrees), (c) Phase B<br>(degrees)                                                                    |

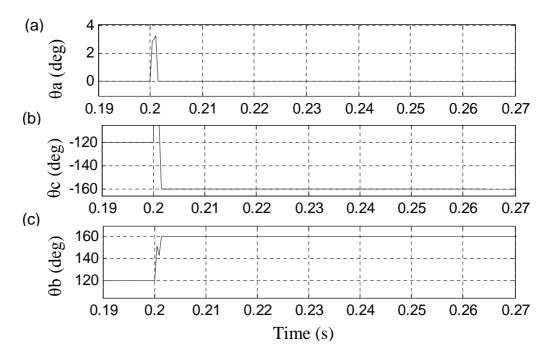

| Figure 4.11: Comparison of response times of schemes for<br>angular frequency tracking under type C fault (a) Peak Voltage<br>(pu) (b) DDSRF-PLL, (c) CDSC-PLL, (d) EO-PLL                                     |

| Figure 4.12: EO-PLL Estimation of Phase Angles under type C fault; (a) Phase A (degrees) (b) Phase C (degrees), (c) Phase B (degrees)                                                                          |

| Figure 4.13: (a) Voltage with harmonics, (b) Voltage after DFT, (c) frequency detection, (d) –(f) Phase detection (A,B,C)                                                                                      |

| Figure 4.14: EO-PLL hardware test circuit setup 101                                                                                                                                                            |

| Figure 4.15: Voltage Generation Program Flow Chart                                                                                                                                                             |

| Figure 4.16: Program Flow Chart for EO-PLL Scheme 105                                                                                                                                                          |

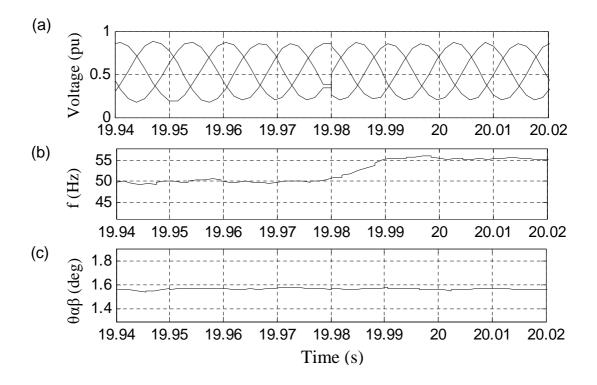

| Figure 4.17: Experimental EO-PLL tracking changes in frequency from 50-55 Hz: a) Generated 3-phase voltage, b) estimated frequency, c) estimated phase                                                         |

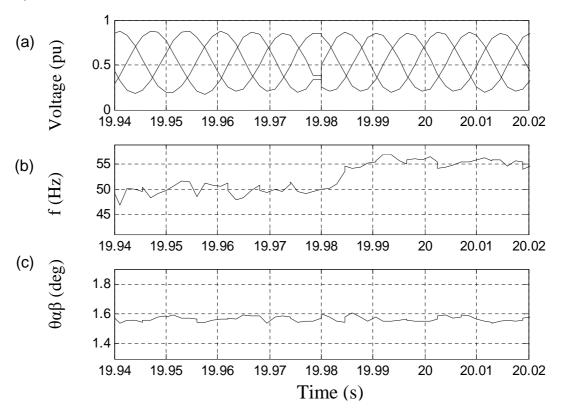

| Figure 4.18:Experimental EO-PLL tracking changes in frequency from 50-55 Hz with no pre-filtering : a) Generated 3-phase voltage, b) estimated frequency, c) estimated phase                                   |

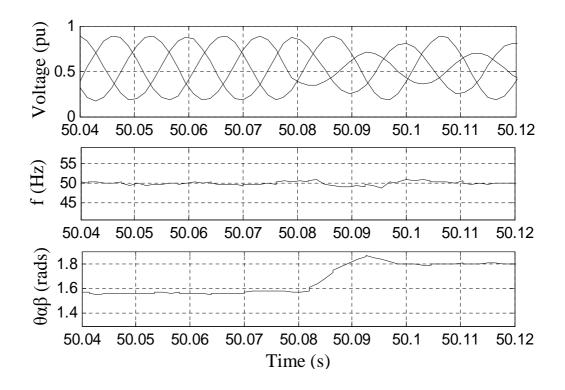

| Figure 4.19: Detected result for 50% and 80% reduction in phase-<br>B and phase-C respectively amplitude: a) Generated 3-phase<br>voltage, b) estimated frequency, c) estimated phase                          |

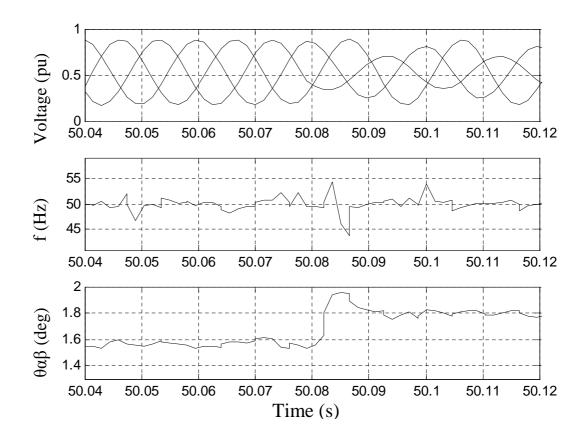

| Figure 4.20: Detected result for 50% and 80% reduction in phase-<br>B and phase-C respectively amplitude with no pre-filtering: a)<br>Generated 3-phase voltage, b) estimated frequency, c) estimated<br>phase |

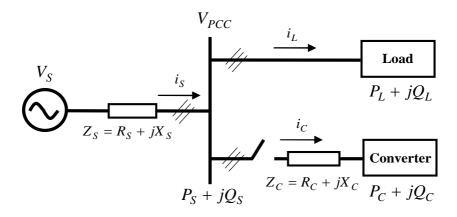

| Figure 5.1: Single Line Diagram of Power System 112                                                                                                                                                            |

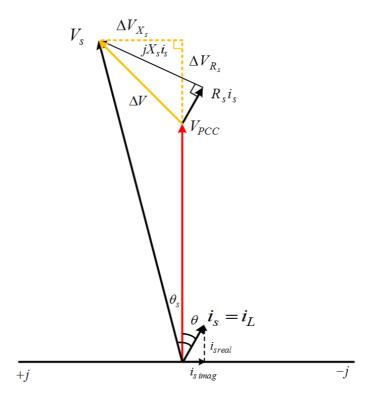

| Figure 5.2: Phasor Diagram between Grid Side and PCC 113                                                                                                                                                       |

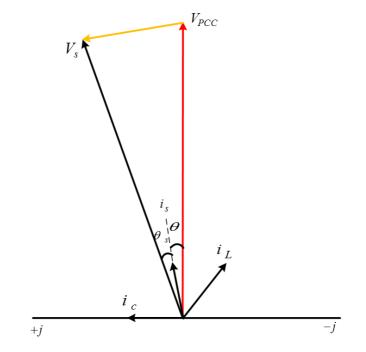

| Figure 5.3: Phasor Diagram showing $ V_S  =  V_{PCC} $ operation                                                                                                                                               |

| Figure 5.4: Phasor Diagram showing Unity Power Factor Operation                                                                                                                                                |

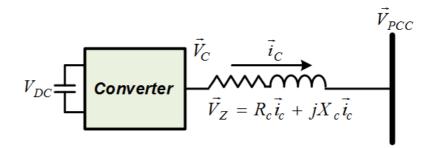

| Figure 5.5: Voltage-Current relationship between Converter and PCC                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.6: Phasor Diagram between Converter and PCC voltages & currents                                                                     |

| Figure 5.7: Simplified Phasor Diagram between Converter and PCC voltages                                                                     |

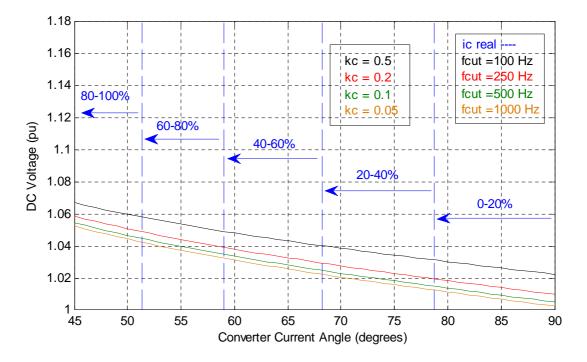

| Figure 5.8: Changes in Converter Current phase Angle Vs<br>Required DC Voltage when $k_f = 0.4$ for fc between 100Hz to<br>1kHz              |

| Figure 5.9: Changes in Converter's Current Angle Vs Required DC Voltage when $k_f = 0.1$ for fc 100Hz – 1kHz                                 |

| Figure 5.10: Simulation Power System Configuration                                                                                           |

| Figure 5.11: Block Diagram of Control Scheme                                                                                                 |

| Figure 5.12: Capacitor DC Voltage Controller                                                                                                 |

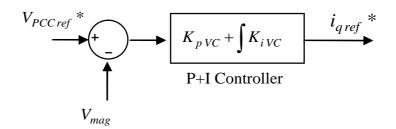

| Figure 5.13: PCC Voltage Controller131                                                                                                       |

| Figure 5.14: Current Controller 132                                                                                                          |

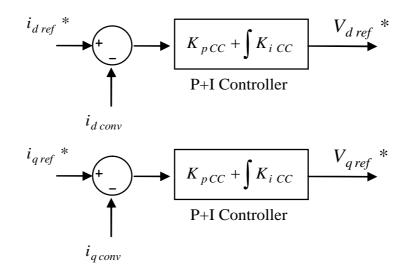

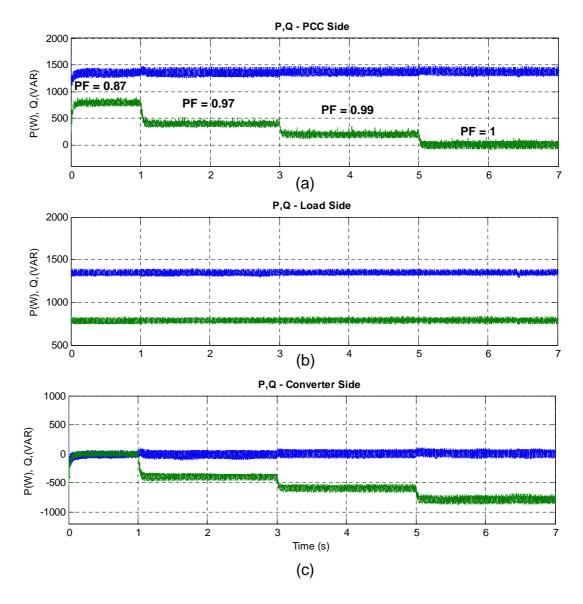

| Figure 5.15: Active and Reactive Power Responses, (a) PCC Side,<br>(b) Load Side, (c) Converter Side134                                      |

| Figure 5.16: (a) Three Phase Voltage and Current, (b) Voltage Magnitude and Current Magnitude, (c) Power Factor Angle                        |

| Figure 5.17: Converters Terminal Voltages135                                                                                                 |

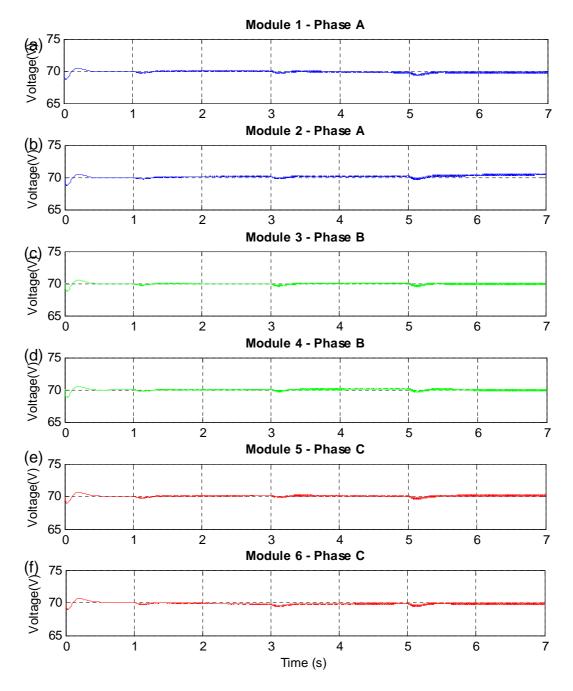

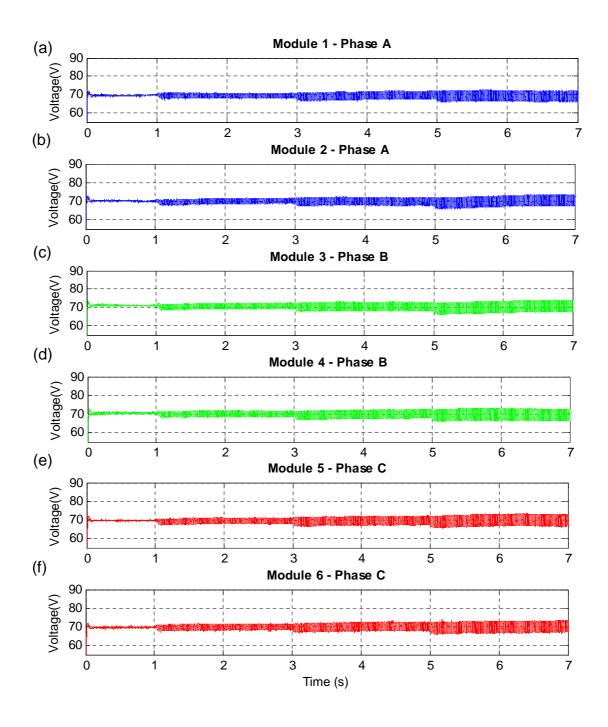

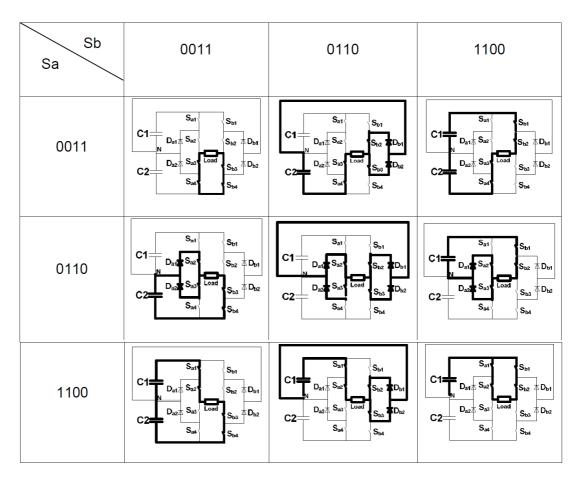

| Figure 5.18: Outer Capacitor Waveforms 136                                                                                                   |

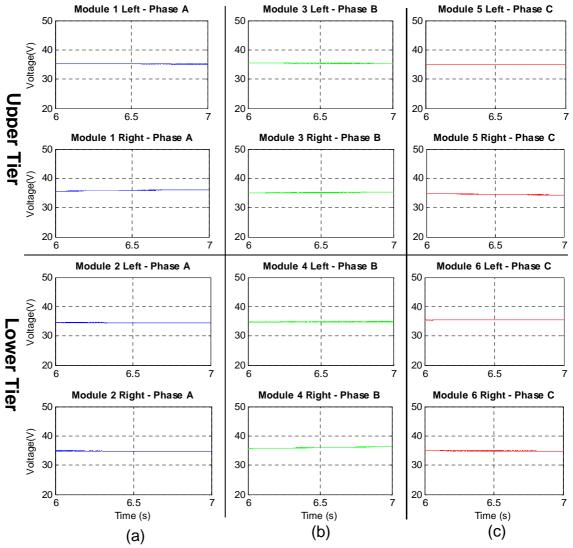

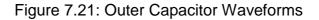

| Figure 5.19: Inner Capacitor Waveforms137                                                                                                    |

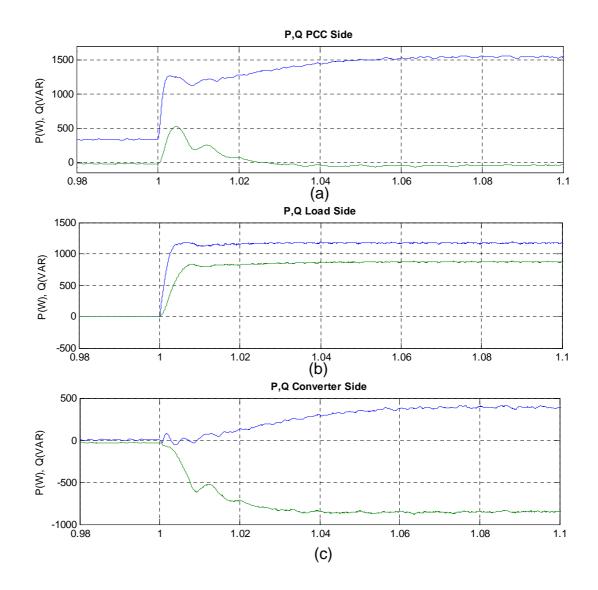

| Figure 5.20: d-q current responses under STATCOM Control (a)<br>PCC Side, (b) Load Side, (c) Converter Side                                  |

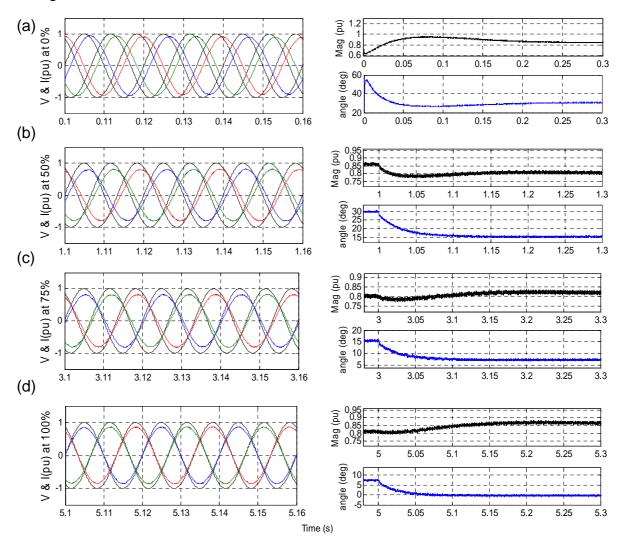

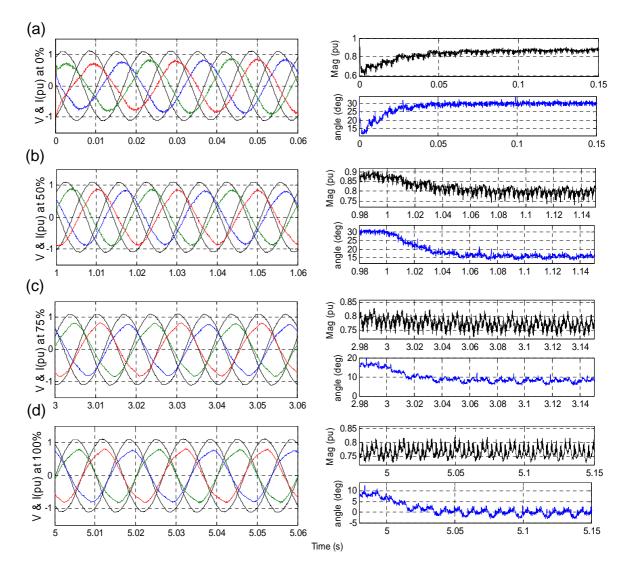

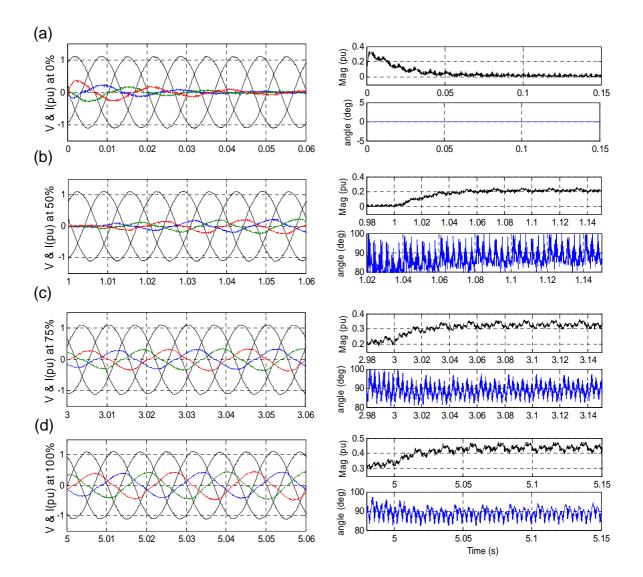

| Figure 5.21: Voltage, Current and Power Factor Angle, (a) no compensation, (b) 50% compensation, (c) 75% compensation, (d) 100% compensation |

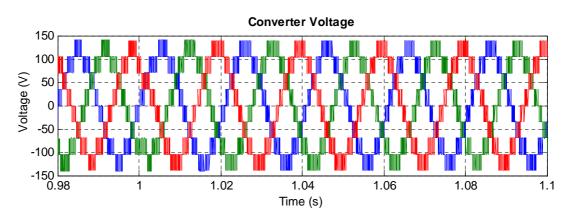

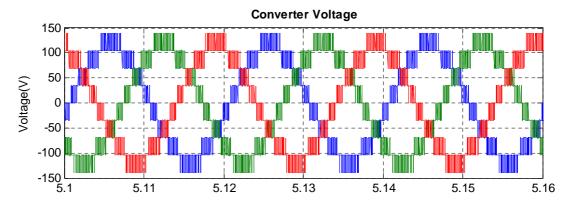

| Figure 5.22: Converters Terminal Voltages140                                                                                                 |

| Figure 5.23: Outer Capacitor Waveforms141                                                                                                    |

| Figure 5.24: Inner Capacitor Waveforms142                                                                                                    |

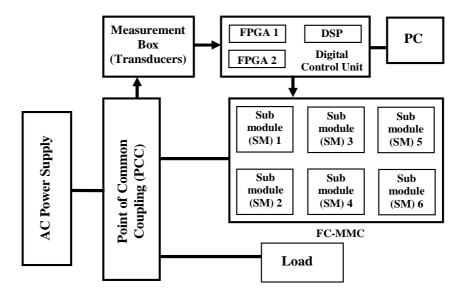

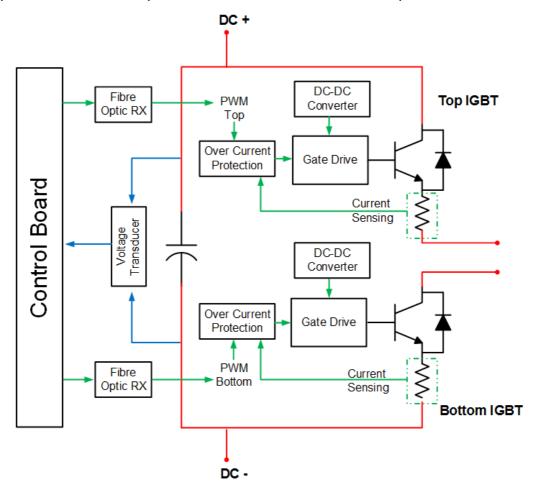

| Figure 6.1: Block Diagram of FC-MMC STATCOM                                                                                                  |

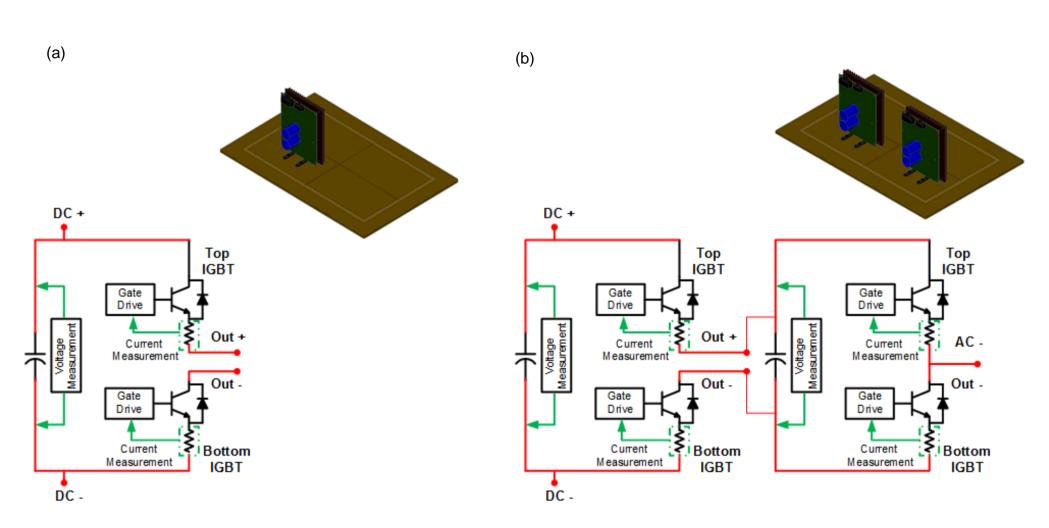

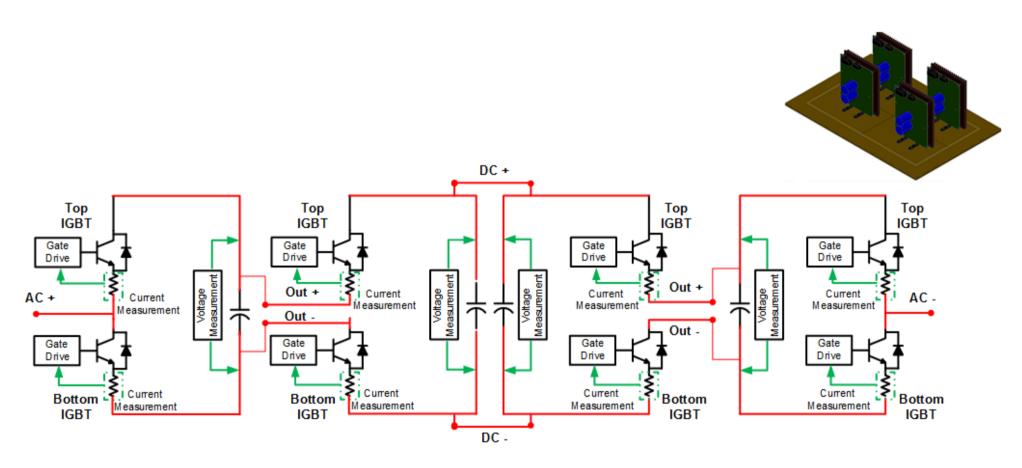

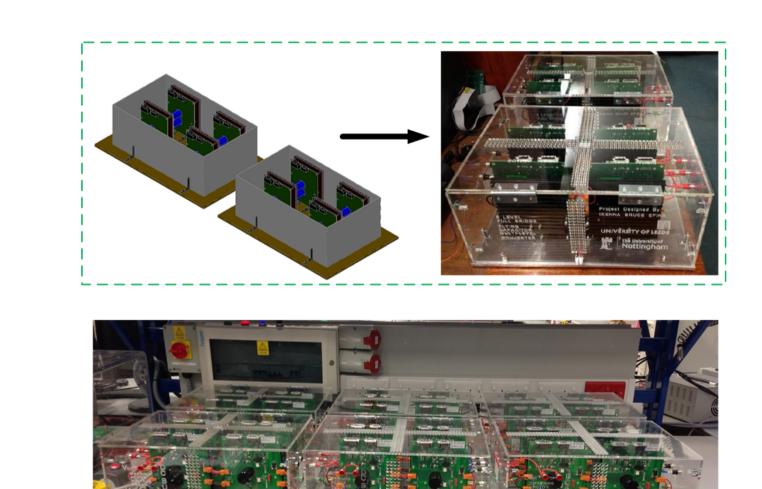

| Figure 6.2: (a) Unit Power Cell (Half-bridge), (b) 5-level Half-bridge<br>Flying Capacitor                                                   |

| Figure 6.3: 5-level Full bridge Flying Capacitor148                                                                                          |

| Figure 6.4: (a) Single Phase 5-level MMC-FC, (b) Three-Phase 5-<br>level MMC-FC149                                                           |

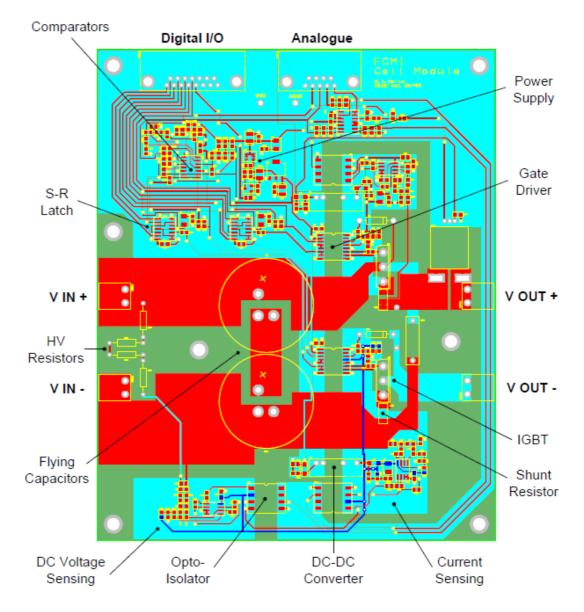

| Figure 6.5: Unit Power Cell Circuit Diagram150                                                                                               |

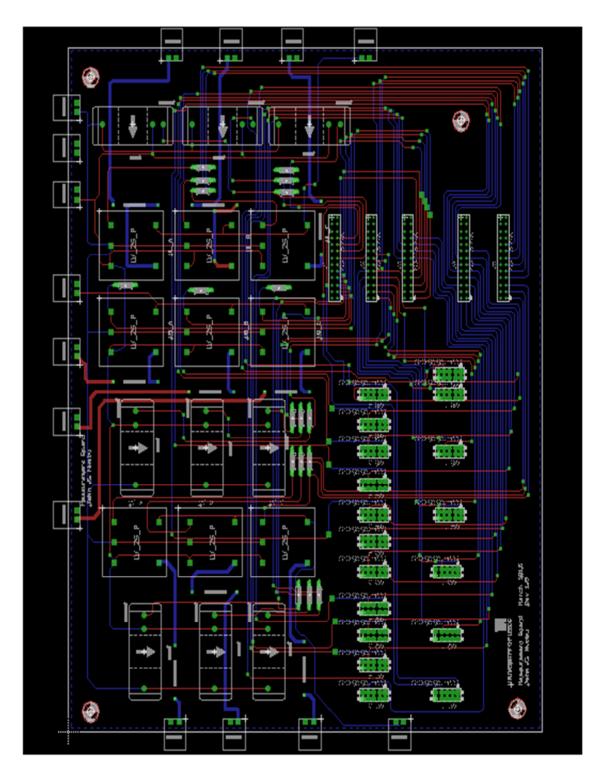

| Figure 6.6: Unit Power Cell Card PCB Design                                                                                                  |

| Figure 6.7: Manufactured PCB 152                                      |

|-----------------------------------------------------------------------|

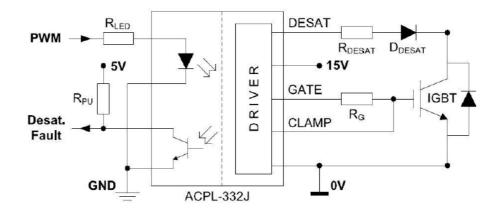

| Figure 6.8: Gate Drive Circuit153                                     |

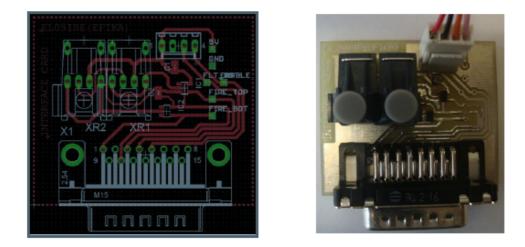

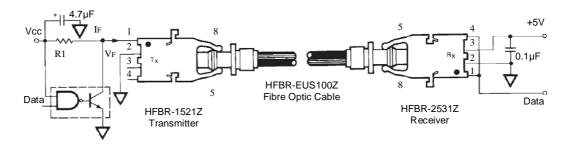

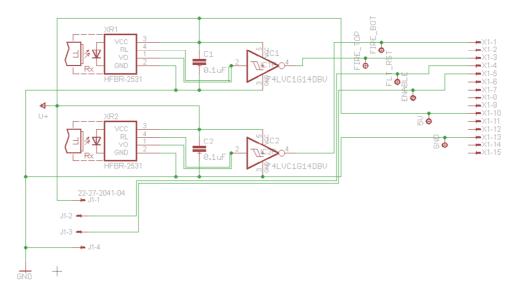

| Figure 6.9: Fibre Optic Receivers PCB Design 154                      |

| Figure 6.10: Fibre Optic Transmitter and Receiver Circuit Diagram 154 |

| Figure 6.11: Schematic for Fibre Optic Transmitter and Receiver 155   |

| Figure 6.12: Power Supply Layout156                                   |

| Figure 6.13: +3.3 V Switch Mode Power Supply 157                      |

| Figure 6.14: +15V Switch Mode Power Supply 157                        |

| Figure 6.15: Isolated DC Power Supply Circuit 157                     |

| Figure 6.16: Built Isolated DC Power Supply (One Phase) 158           |

| Figure 6.17: Voltage Transducer Circuit160                            |

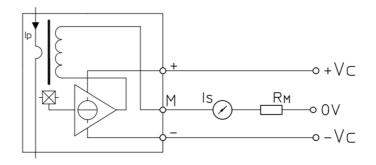

| Figure 6.18: Current Transducer Circuit161                            |

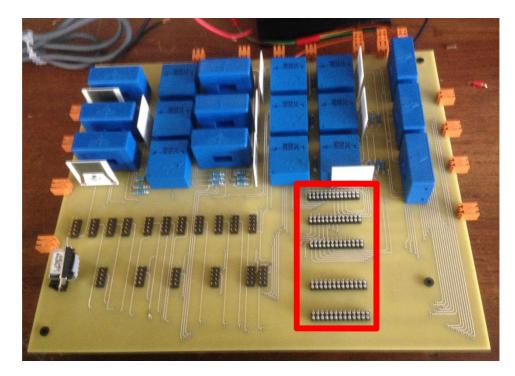

| Figure 6.19: Populated PCB of PCC Measurement Box 162                 |

| Figure 6.20: Built PCC Measurement Box163                             |

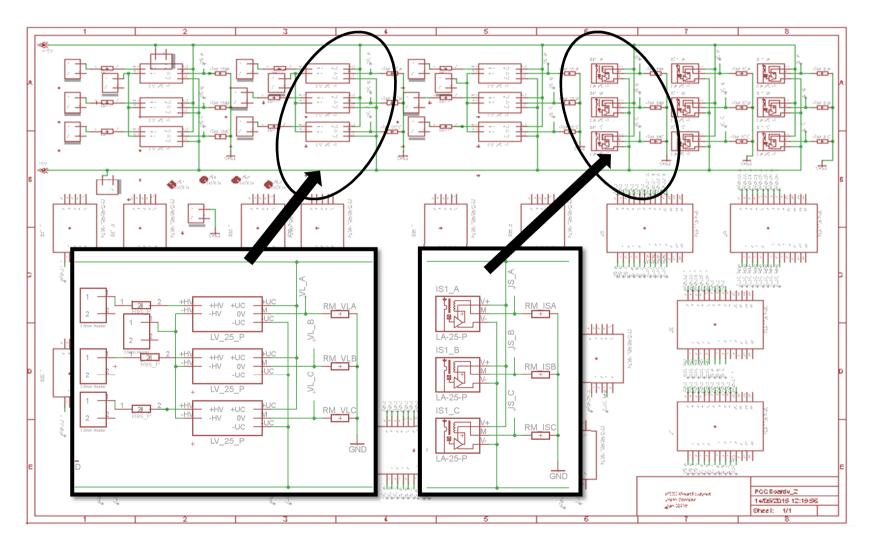

| Figure 6.21: Schematic for PCC Measurement Box 164                    |

| Figure 6.22: PCB Schematic for PCC Measurement Box                    |

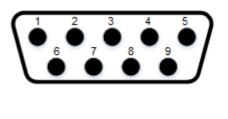

| Figure 6.23: Pin layout Feedback Signals166                           |

| Figure 6.24: Pin Layout for Breakout Connectors                       |

| Figure 6.25: Block Diagram Software Control Unit 168                  |

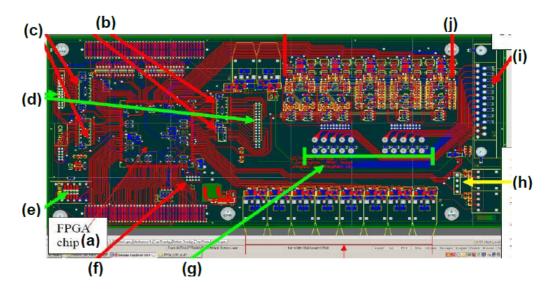

| Figure 6.26: Actel Pro Asic 3 FPGA Layout169                          |

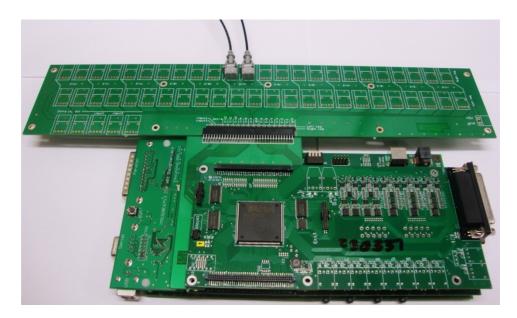

| Figure 6.27: FPGA with Fibre Optic Break Out Boards                   |

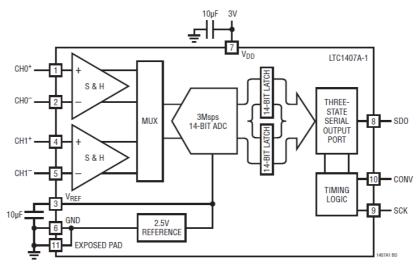

| Figure 6.28: Power Circuit of ADC Converters 170                      |

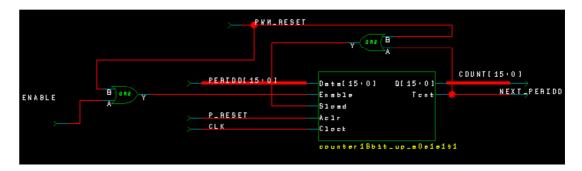

| Figure 6.29: 16-bit Interrupt Counter 171                             |

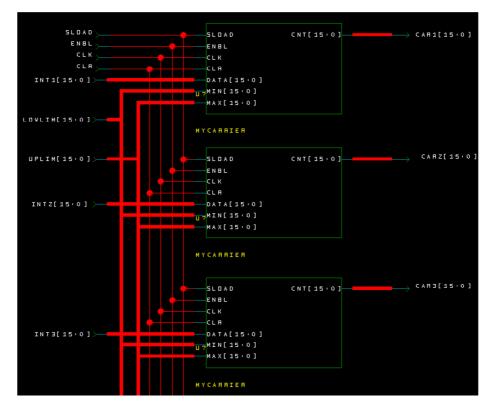

| Figure 6.30: Triangular Carrier Generation 172                        |

| Figure 6.31: Carrier Generation Unit in FPGA 172                      |

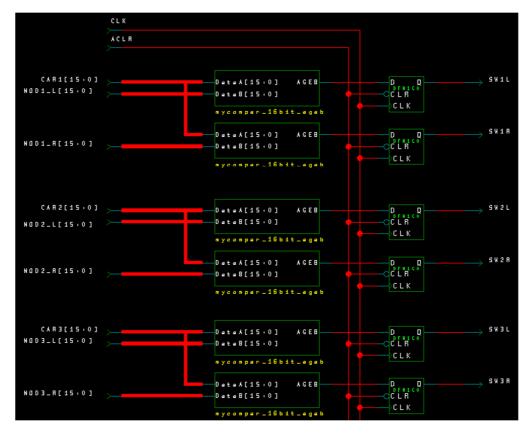

| Figure 6.32: Pulse Generation unit in FPGA 173                        |

| Figure 6.33: Texas Instrument TMS320C6713 DSP 174                     |

| Figure 6.34: Program Flow Chart for Main Routine and Sub Routine      |

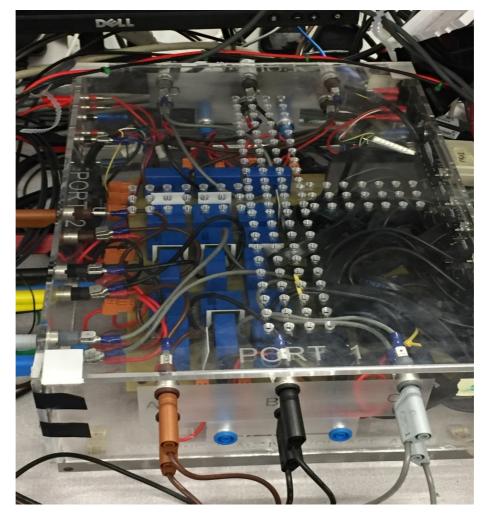

| Figure 7.1: Experimental Power System Configuration                   |

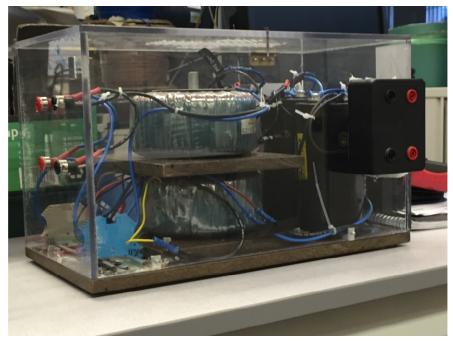

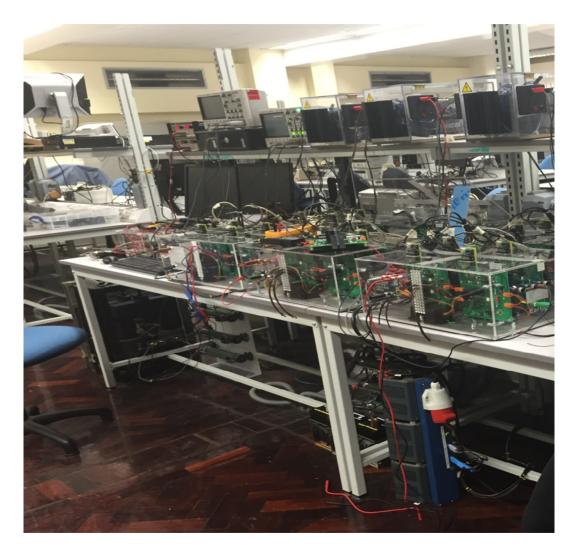

| Figure 7.2: Experimental Setup181                                     |

| Figure 7.3: Block Diagram of the Control System                       |

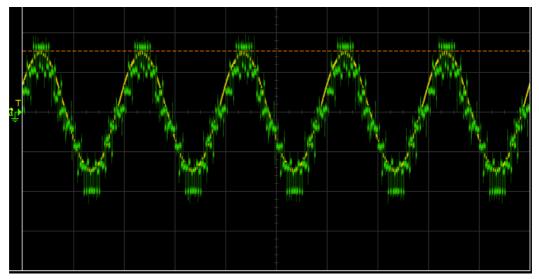

| Figure 7.4: Synchronised Voltage (One Phase) 183                      |

| Figure 7.5: Block Diagram P+I Controller                              |

| Figure 7.6: Block Diagram for Pre-Charge Control 185                  |

| Figure 7.7: d-q current responses under STATCOM Control (a)<br>PCC Side, (b) Load Side, (c) Converter Side                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.8: Response time of STATCOM current under each load condition Signals, (a) id current, (b) iq current                                  |

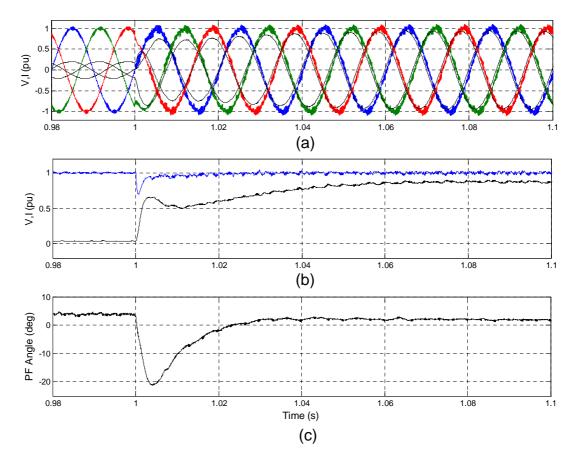

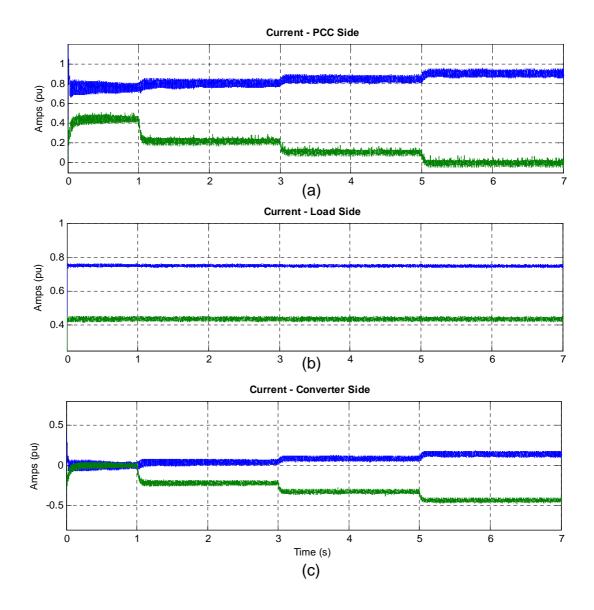

| Figure 7.9: Active and Reactive Power Responses, (a) PCC Side,<br>(b) Load Side, (c) Converter Side                                             |

| Figure 7.10: Voltage, Current and Power Factor Angle, (a) Zero compensation, (b) 50% compensation, (c) 75% compensation, (d) Full compensation  |

| Figure 7.11: Voltage, Current and Converter Angle, (a) Zero compensation, (b) 50% compensation, (c) 75% compensation, (d) Full compensation     |

| Figure 7.12: (a)Converter Modulation Index and Angle, (b) PLL<br>Angle, (c) Converter Voltages Full Compensation                                |

| Figure 7.13: Outer Capacitor Voltages 194                                                                                                       |

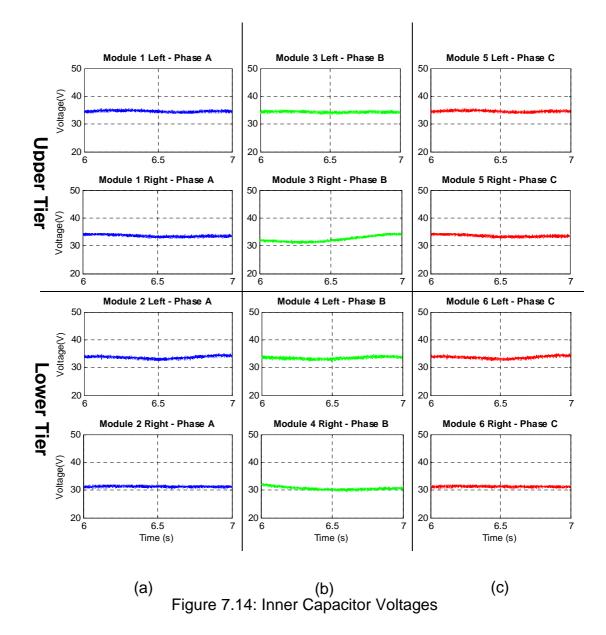

| Figure 7.14: Inner Capacitor Voltages 195                                                                                                       |

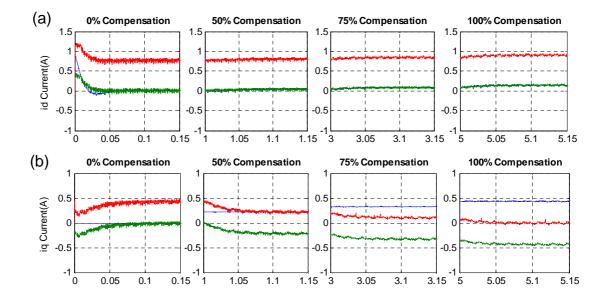

| Figure 7.15: d-q current control, (a) PCC Side, (b) Load Side, (c)<br>Converter Side                                                            |

| Figure 7.16: Response time of STATCOM current under each load condition Signals, (a) id current, (b) iq current, (a) id current, (b) iq current |

| Figure 7.17: Active and Reactive Power, (a) PCC Side, (b) Load Side, (c) Converter Side                                                         |

| Figure 7.18: Voltage, Current and Power Factor Angle, (a) Zero compensation, (b) 50% compensation, (c) 75% compensation, (d) Full compensation  |

| Figure 7.19: Voltage, Current and Converter Angle, (a) Zero compensation, (b) 50% compensation, (c) 75% compensation, (d) Full compensation     |

| Figure 7.20: (a)Converter Modulation Index and Angle, (b) PLL<br>Angle, (c) Converter Voltages Full Compensation                                |

| Figure 7.21: Outer Capacitor Waveforms 203                                                                                                      |

| Figure 7.22: Inner Capacitor Waveforms                                                                                                          |

# List of Abbreviations

| PCC      | Point of Common Coupling                             |

|----------|------------------------------------------------------|

| TCSC     | Thyristor Controlled Series Capacitor                |

| SVC      | Static VAR Compensator                               |

| SSSC     | Static Series Compensator                            |

| STATCOM  | Static Compensator                                   |

| UPFC     | Unified Power Flow Controller                        |

| UPQC     | Unified Power Quality Conditioner                    |

| PLL      | Phase Locked Loop                                    |

| DDSRF    | Decoupled Double Synchronisation Reference Frame PLL |

| CDSC-PLL | Cascaded Delay Signal Cancellation PLL               |

| EO-PLL   | Energy Operator PLL                                  |

| SRF-PLL  | Synchronisation Reference Frame PLL                  |

| NPC      | Neutral Point Clamped Converter                      |

| FC       | Flying Capacitor Converter                           |

| MMC      | Modular Multilevel Converter                         |

| FC-MMC   | Flying Capacitor Modular Multilevel Converter        |

| PS-PWM   | Phase-Shifting Pulse-Width Modulation                |

| PD-PWM   | Phase Deposition Pulse Width Modulation              |

| FACTS    | Flexible AC Transmission Systems                     |

| HVDC     | High Voltage DC Transmission                         |

| LCC HVDC | Line Commutated Converter HVDC                       |

# Chapter 1 Introduction

# 1.1 Background Literature

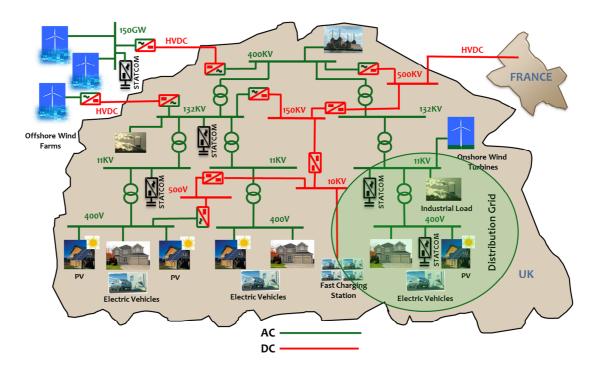

Sustainable and clean ways of generating electricity from renewable natural sources like solar and wind now exist in the distribution grid network. This offers solutions for increasing the total power generation capacity and reducing environmental impact. However, the integration of solar and wind power generators poses a challenge as the conventional distribution grid structure is designed to allow mainly unidirectional power flow. There is also now the requirement of integrating the AC grid with the DC networks with the growing need for charging of electrical vehicles. Concerns are arising over how ageing electrical infrastructures built decades ago will cope with these changes.

The establishment of a more efficient distribution grid network is an effective solution to meeting the challenges posed. This advanced network, with reinforced electrical power infrastructures and improved communications, will allow optimum management of electricity distribution to consumers. It has sparked global interest and increased investment in improving the efficiency of the electrical power infrastructure. However, the guidelines for achieving this are still being developed as they involve the integration of various key sectors like IT, power generation, and communications.

The overall objective is to develop an intelligent digitised energy network delivering electricity in an optimum way from generating sources to the consumers. This can be viewed in two ways

- The deployment of automated metering infrastructure that improves communication between energy suppliers and consumers, i.e. consumers can now also benefit from knowing how to optimise their energy usage and communicate effectively with energy suppliers.

- The deployment in the distribution system of automated devices that allow operation of distribution infrastructure with greater efficiency and flexibility.

In short, the two arms of this strategy are improving the power metering and data communication, and improving the control of power flow within the network.

Power electronic devices are the enabling technology in achieving control of the power flow and research is led by industry and academic experts on their application in power systems. The future grid network needs considerable research in power flow control using Flexible AC Transmission Systems (FACTS), such as the Static Compensator (STATCOM) for reactive power compensation, and High Voltage transfer using HVDC systems as illustrated below in Figure 1.1.

Figure 1.1: Future Transmission and Distribution Grid System

# **1.2 Flexible AC Transmission Systems**

Research on Flexible AC Transmission systems (FACTS) dates back as far as the 1960's [1] when a proposal was made for the improvement of transient stability of a power network with series connected switched capacitors. The definitions and concepts were published in later years (1988) by Hingorani [2] but still failed to be realisable due to the poor response of power electronic devices and control systems at that time. FACTS controllers are generally categorised into three eras: 1<sup>st</sup> generation: which includes shunt and series connected devices:

- Thyristor Controlled Series Capacitor (TCSC)

- Static VAR Compensator (SVC)

2<sup>nd</sup> generation: which also includes shunt and series connected devices:

- Static Synchronous Series Compensator (SSSC)

- Static Compensator (STATCOM)

3<sup>rd</sup> generation: which combines series-shunt compensation devices:

- Unified Power Flow Controller (UPFC)

- Unified Power Quality Controller (UPQC)

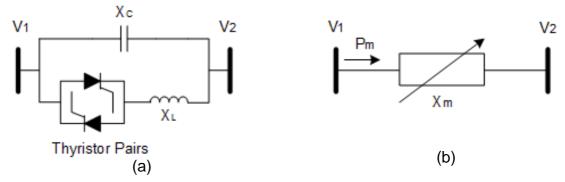

### 1.2.1 Thyristor Controlled Series Capacitor (TCSC)

The Thyristor Controlled Series Capacitor (TCSC) is a series compensation scheme that works by varying the effective reactance of the transmission line to regulate active power flow. Its circuit is a combination of thyristor controlled capacitors and reactors /inductors across two nodes of the transmission line as shown in Figure 1.2 (a). This forms the nonlinear reactance  $X_m$  which is connected in series with the transmission line as shown in Figure 1.2 (b). Provided the transmission line resistance is much far less than its reactance, the active power can be regulated by varying the reactance  $X_m$  according to equation (1.1).

$$P_m = \frac{\left|V_1\right| \left|V_2\right|}{X_m} \cdot \sin\left(\theta_1 - \theta_2\right) \tag{1.1}$$

where,  $\theta_1$  = angle of the voltage at bus  $V_1$  and  $\theta_2$  = angle of the voltage at bus  $V_2$ .

The Thyristor Controlled Series Capacitor (TCSC) has been available commercially since the early 1990's. The first such installation was the thyristor switched series capacitor version (TSSC) in a 345 kV transmission line at the Kanawa River Substation [3]. Subsequent early installations are recorded in the 230 kV transmission lines at Kayentta Substation [4] and at the Slatt substation [5]. TCSC product ranges are still available from some companies, e.g. Siemens and ABB [6, 7].

Figure 1.2: Thyristor Controlled Series Capacitor: (a) Thyristor Controlled Reactor with fixed capacitor (b) Variable reactance representation

#### 1.2.2 Static VAR Compensator (SVC)

The Static VAR Compensator (SVC) is a parallel connected equivalent of the TCSC and acts like a nonlinear shunt-connected variable reactance  $X_m$ . This generates or absorbs reactive power to enable voltage regulation across the line using either thyristor controlled capacitor banks (TSCs) or reactor banks (TCRs). The power circuit of an SVC with thyristor controlled reactors is as shown in Figure 1.3 (a). A nonlinear model representation is as shown in Figure 1.3 (b) where the reactance  $X_m$  is represented as equivalent susceptance  $B_m$ . Assuming the resistance across the line is negligible, the reactive power can be regulated by adjusting the susceptance  $B_m$  using equation (1.2).

$$Q_m = -\left|V_1\right|^2 B_m \tag{1.2}$$

This technology was introduced to improve the power quality in transmission lines. The first commercially available FACTS controllers for Static VAR Compensator (SVC) application to voltage control and stability improvement are dated as early as the late 1970's [8]. The major drawback is that it requires switching in of pre-calculated values of the capacitors and reactors. However, commercially available SVC's are still marketed by transmission grid equipment manufacturers like Siemens, GE Grid Solutions (Alstom) and ABB [9-11].

Figure 1.3: Static VAR Compensator: (a) TCR with fixed capacitor (b) Variable susceptance representation

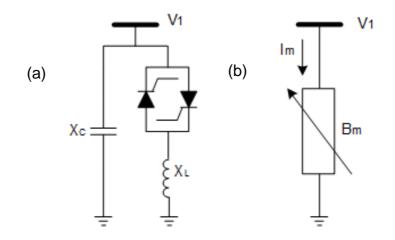

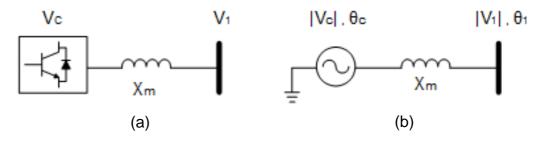

#### **1.2.3 Static Synchronous Series Compensator (SSSC)**

The second generation of FACTS controller replaced the thyristor - switched elements with power converters. The basic principle was the use of power converters coupled with reactive components to control the effective parameters of the transmission line. Similarly to first generation devices, the static series compensator (SSSC) would be series connected and be used to control the active power flow by varying the apparent impedance of the transmission line. However the SSSC provides additional functionality as it can provide also regulation of reactive power flow because of the converter's DC capacitor. Figure 1.4 (a)-(b) shows the power circuit configuration for the SSSC and its equivalent power circuit representation. The equivalent model can be represented as a series connected voltage source with variable magnitude  $V_C$  and phase angle  $\angle \theta_C$ . Adjusting the magnitude and phase angle regulates the active and reactive power flow across the line:

$$V_C = |V_C|(\cos\theta_C + j\sin\theta_C) \tag{1.3}$$

The Static Synchronous Series compensator (SSSC) is not as commonly used commercially as other FACTS devices. Most literature available for practical applications deals with laboratory scale investigations using various control schemes and methods [12-14]. Its commercial application is reported as part of the first early installation of a UPFC at the Inez Substation [8, 15] and more recently the KEPCO UPFC at Kangjin substation [16]. Transmission grid suppliers like ABB, Siemens and GE grid solutions at present do not have product ranges advertised on their websites.

Figure 1.4: Static Synchronous Series Compensator: (a) Converter connected to network by series transformer (b) Equivalent power circuit representation

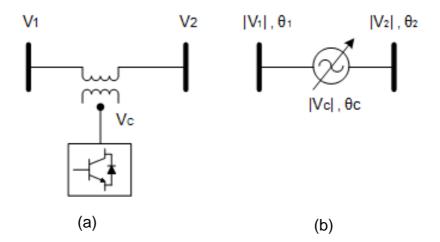

#### **1.2.4 Static Synchronous Compensator (STATCOM)**

The static synchronous compensator (STATCOM) is a shunt connected version of an SSSC. The shunt connected power circuit and its equivalent model are as shown in Figure 1.5 (a)-(b). This also regulates the active and reactive power flow across the line by controlling the magnitude and phase angle of the converter voltage. For an ideal STATCOM under reactive power operation with no active power loss, the reactive power is regulated based on equation (1.4).

$$Q_{m} = \frac{|V_{1}|^{2} - |V_{1}||V_{C}|}{X_{m}} \cdot \cos(\theta_{1} - \theta_{C})$$

(1.4)

The static synchronous compensator (STATCOM) is the most popularly used among the other FACTS controllers. Its first commercial application was for a 20 MVAR STATCOM using force-commutated thyristors by Kansai Electric Power Co. Inc. (KEPCO) and Mitsubishi Motors, inverters, in 1980 [17] . Following that, a 1 MVAR STATCOM using high power GTO inverters was developed by Westinghouse Electric Company [18]. Some other installations documented are the ±80 MVAR STATCOM in Japan (1991) [19]; the ±100 MVAR STATCOM at Sullivan substation (1996) [20]; the 8 MVA STATCOM at Rejsby Hede wind farm (1997) [21] and the ± 200 MVAR STATCOM at Marcy substation (2001) [22]. A general list of more recent installations by different companies up to the year 2015 is presented in [23].

The first of the modular multilevel cascaded converter (MMC) based STATCOMs was reported in early 2001 with a 175 MVAR STATCOM

developed by Alstom [24]. Some other known installations are three-level ±100 MVAR STATCOM and Talega substation (2002) [25], while ABB has also installed six of these MMC STATCOM controllers known as SVC Light in Sweden, Germany, France, Finland and USA [26, 27].

Figure 1.5: Static Synchronous Compensator: (a) Converter shunt connected to the network (b) Equivalent power circuit representation

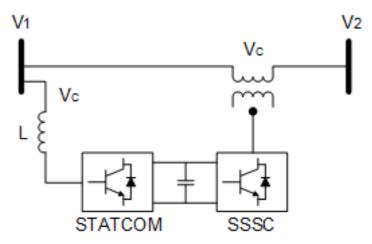

### 1.2.5 Unified Power Flow Controller (UPFC)

The Static Synchronous Series compensator (SSSC) proposed by L. Gyugyi [28] was later extended to the concept of the Unified Power Flow Controller (UPFC). This third generation of FACTS controllers is a combination of series and shunt connected second generation devices. The main concept is for simultaneous implementation of both series and shunt connected compensators. The shunt connected device regulates the reactive power flow on the line whilst maintaining the common DC bus capacitor voltage at to be a fixed value whilst the series connected device controls the active power flow in the transmission line. [29-34].

Figure 1.6: Unified Power Flow Controller

# **1.3 Multilevel Converter Topologies**

The introduction of multilevel converters replaced the conventional two-level converters used for early STATCOM applications. The concept dates back to the early 1970's with the design of the three-level converter [35, 36], and is based on building up multiple voltage levels by stacking extra switches in the converter structure either through clamping diodes, capacitors or cascading converters.

The stacked levels produce a fraction of the DC source voltage resulting in

(n) levels with  $\left(\frac{V_{DC}}{2(n-1)}\right)$  across it. The resulting waveform is emulated as multiple voltage levels of DC pulses, and, depending on the switching scheme, harmonics and losses are reduced; hence there are little or no filter requirements. The major advantage is the reduced voltage stress as the

total voltage is distributed across the switches. This results in lower power losses.

Multilevel converters have been studied extensively for STATCOM applications. Most popular are the Neutral Point Clamped (NPC) and the Flying capacitor (FC) converter. A review of the well-established standards for multilevel converters is presented in the literature [35, 37-46]. Currently, converters for STATCOM applications are commercially offered by a growing list of companies in the field [6, 7, 9, 10, 23, 27].

Although they are a well-established and proven technology, multilevel converters still present certain challenges such as improving the energy efficiency, power density, simplicity and cost [41]. Most multilevel converters like the NPC are used in medium voltage applications. Researchers in the past have addressed these issues and looked into possibilities of extending the technique for High voltage application [47-51].

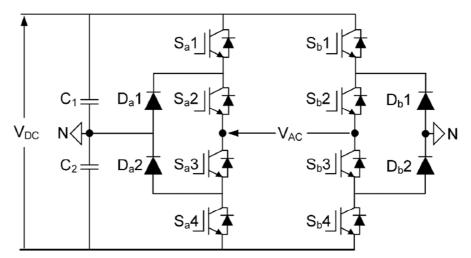

# **1.3.1 Neutral Point Clamped Converter**

The Neutral Point Clamped (NPC) Multi-level Converter was initially proposed by Nabae et al in 1981 [52]. It is also referred to as the diode clamped or multipoint clamped converter, as clamping diodes are used to clamp levels of switches to distinct voltage levels.

The Neutral point converter (NPC) belongs to the family of medium voltage high power converters (2.3 to 6.6 kV) and features medium to high voltage power devices. This makes it suitable for back-to back regenerative applications and it is more widely used in industry than the flying capacitor converter [41]. The 5-level NPC configuration is mostly used because of its

simple power circuit structure with a lower number of power devices and capacitors. Extending this to more levels is less attractive because there are higher and unevenly distributed losses across the power devices, most especially among the increased number of diodes. In addition, the DC link capacitor voltage becomes unbalanced under certain conventional modulation schemes which make is less feasible for higher power applications [53-55].

The five level configuration for the neutral point (NPC) converter, as shown in Figure 1.7, is capable of synthesizing five distinct voltage levels of 0,  $+V_{DC}/2$ ,  $-V_{DC}/2$ ,  $+V_{DC}$  and  $-V_{DC}$ .

Figure 1.7: H-bridge Configuration of a Neutral Point Clamped Converter

In the full bridge configuration each leg of the converter (i.e.  $S_{a1} - S_{a4}$ ,  $S_{b1} - S_{b4}$ ) are clamped together by two diodes ( $D_{a1}$ ,  $D_{a2}$ ;  $D_{b1}$ ,  $D_{b2}$ ) and this prevents the voltage in one level from surpassing the next level. The complementary switching pairs are  $S_1$ ,  $S_3$  and  $S_2$ ,  $S_4$  on each leg which are not operated at the same switching state to prevent short-circuiting the voltage supply. It is also important to note that  $S_1$  and  $S_4$  cannot be switched on at the same time to prevent over voltage. Table 1.1 shows the valid switching states during operation

|                 | Leg A S         | witches         |                 |                 | V <sub>AC</sub> |                 |          |                     |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|---------------------|

| S <sub>a1</sub> | S <sub>a2</sub> | S <sub>a3</sub> | S <sub>a4</sub> | S <sub>b1</sub> | S <sub>b2</sub> | S <sub>b3</sub> | $S_{b4}$ |                     |

| 1               | 1               | 0               | 0               | 0               | 0               | 1               | 1        | V <sub>DC</sub>     |

| 1               | 1               | 0               | 0               | 0               | 1               | 1               | 0        | +V <sub>DC</sub> /2 |

| 0               | 1               | 1               | 0               | 0               | 0               | 1               | 1        | +V <sub>DC</sub> /2 |

| 1               | 1               | 0               | 0               | 1               | 1               | 0               | 0        | 0                   |

| 0               | 1               | 1               | 0               | 0               | 1               | 1               | 0        | 0                   |

| 0               | 0               | 1               | 1               | 0               | 0               | 1               | 1        | 0                   |

| 0               | 1               | 1               | 0               | 1               | 1               | 0               | 0        | -V <sub>DC</sub> /2 |

| 0               | 0               | 1               | 1               | 0               | 1               | 1               | 0        | -V <sub>DC</sub> /2 |

| 0               | 0               | 1               | 1               | 1               | 1               | 0               | 0        | -V <sub>DC</sub>    |

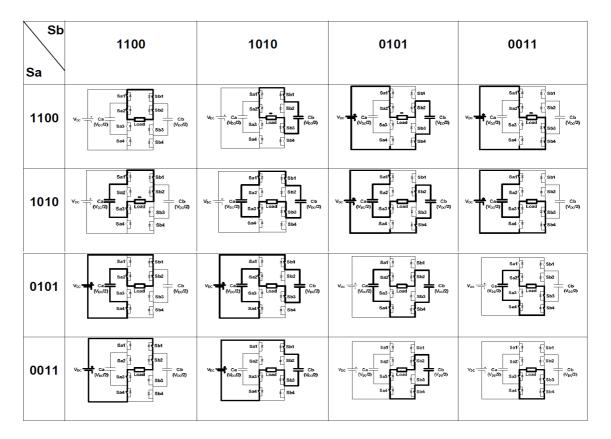

Table 1.1: Three-level neutral point clamped inverter switching states

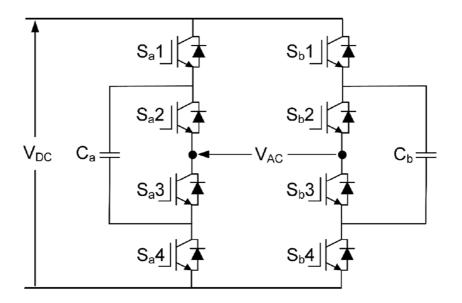

### **1.3.2 Flying Capacitor Converter**

The Flying Capacitor (FC) Multi-level Converter was developed by Meynard and Foch [40, 56] and, instead of diodes as in the neutral point clamped converter; it uses capacitors to clamp the switches to distinct voltage levels. The application of the FC converter is covered well in literature [37, 38, 57-59]. Although the FC is well established, it has been less applicable in industry because higher switching frequencies (>1200Hz) are required to keep its capacitors balanced, whereas high power applications require switching in the range of 500-700 Hz [41]. In addition, the higher number of capacitors compared to the NPC makes its power circuit bulky and more expensive. However compared to the NPC, this converter presents more redundant switching states in achieving the multilevel voltage steps.

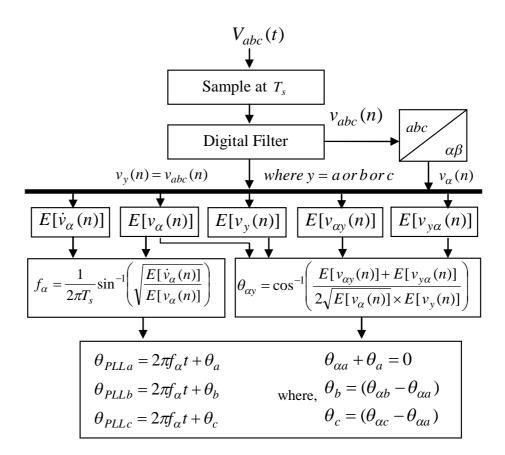

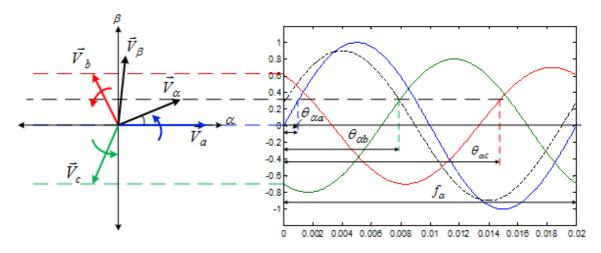

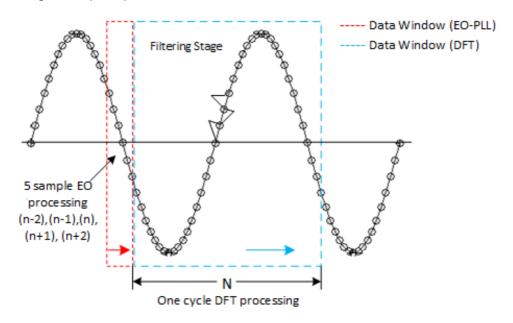

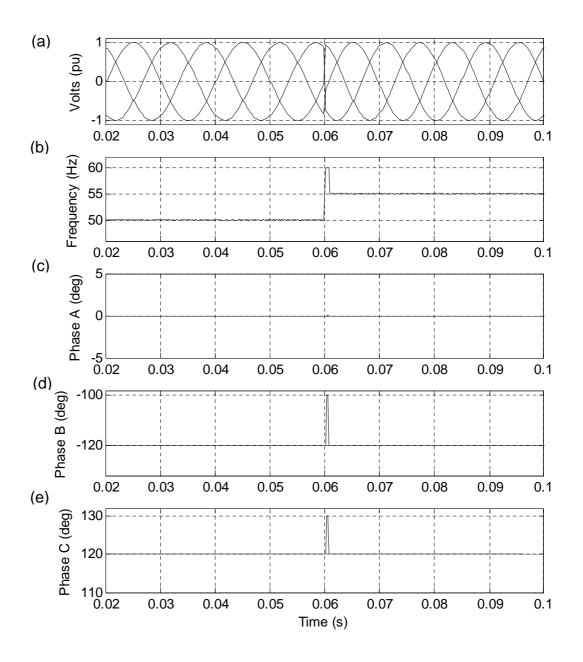

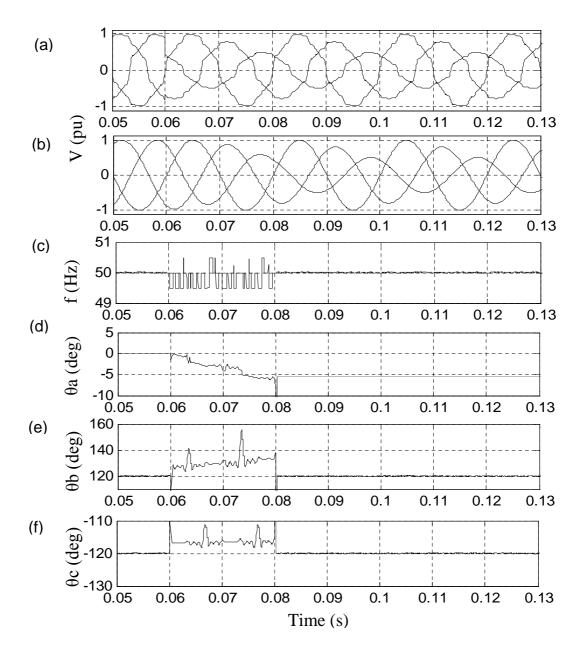

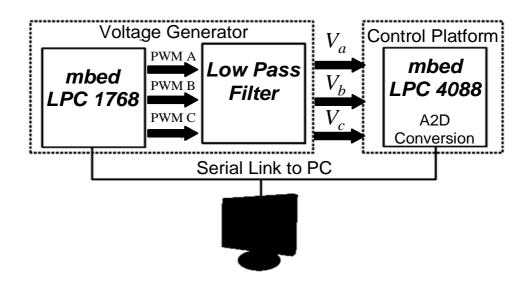

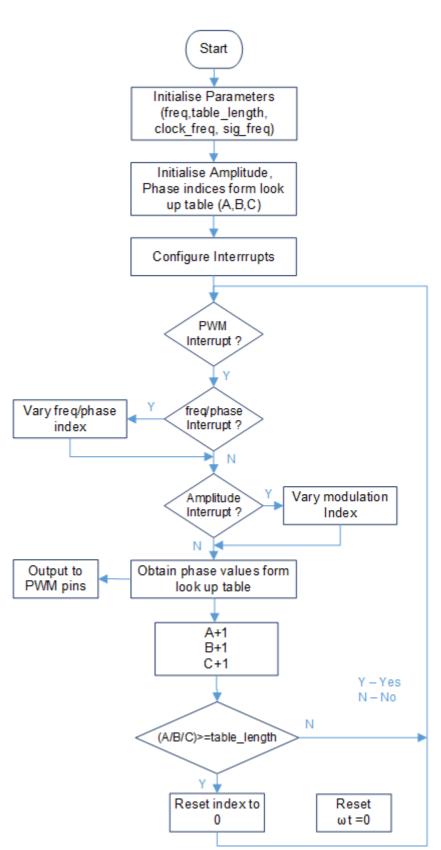

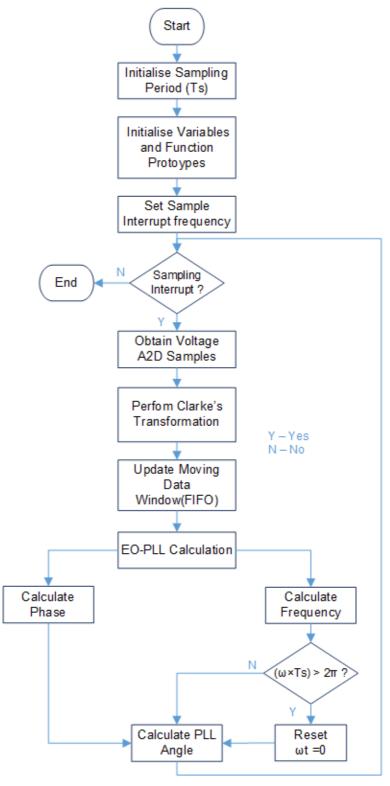

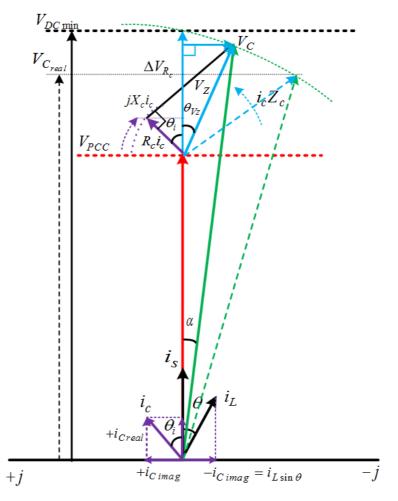

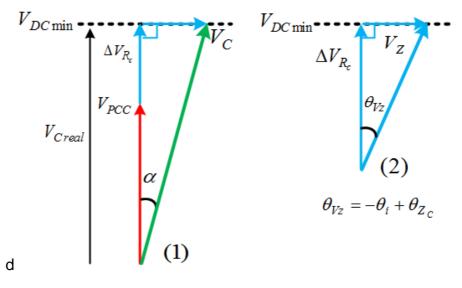

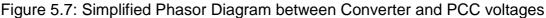

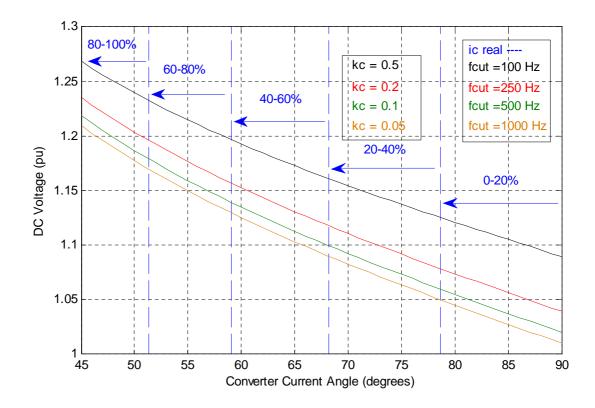

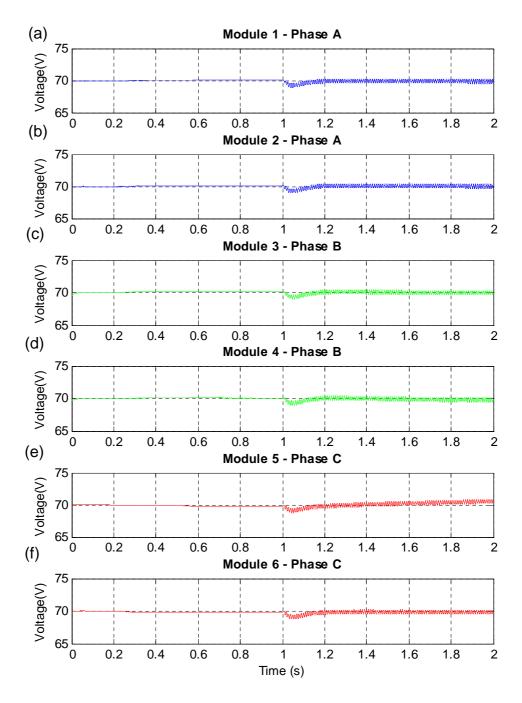

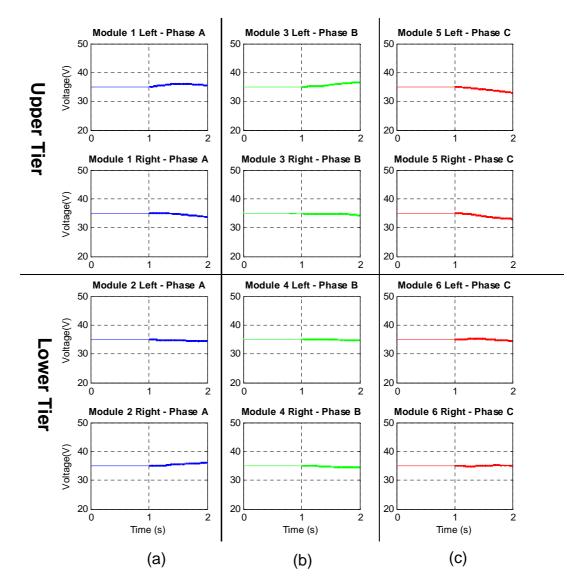

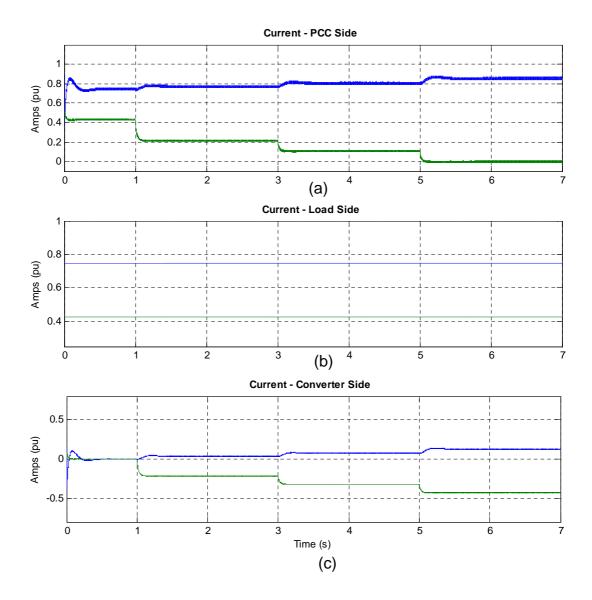

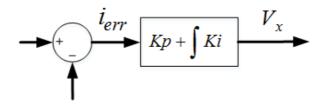

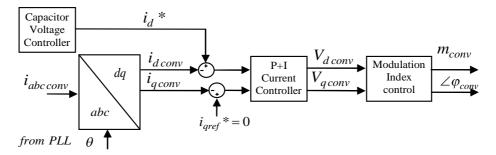

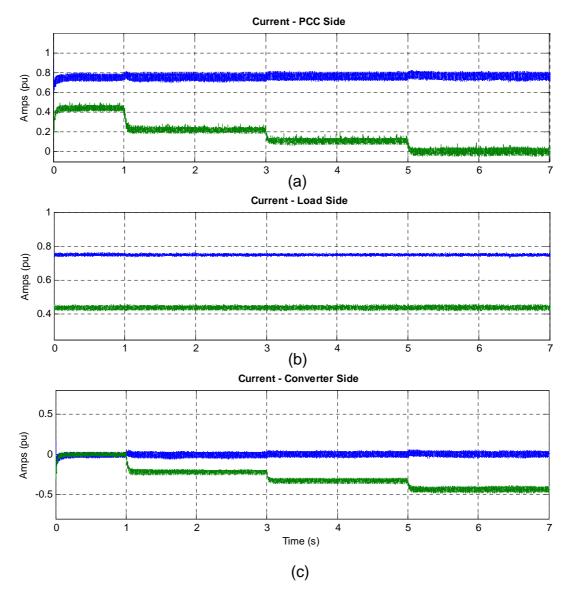

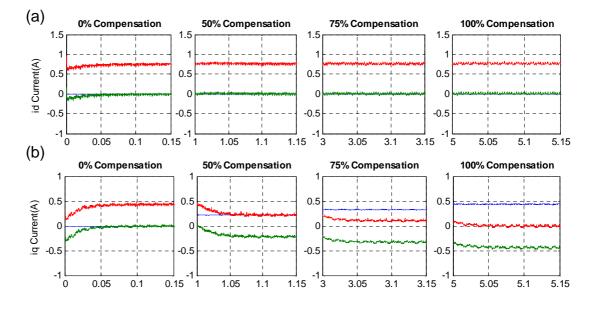

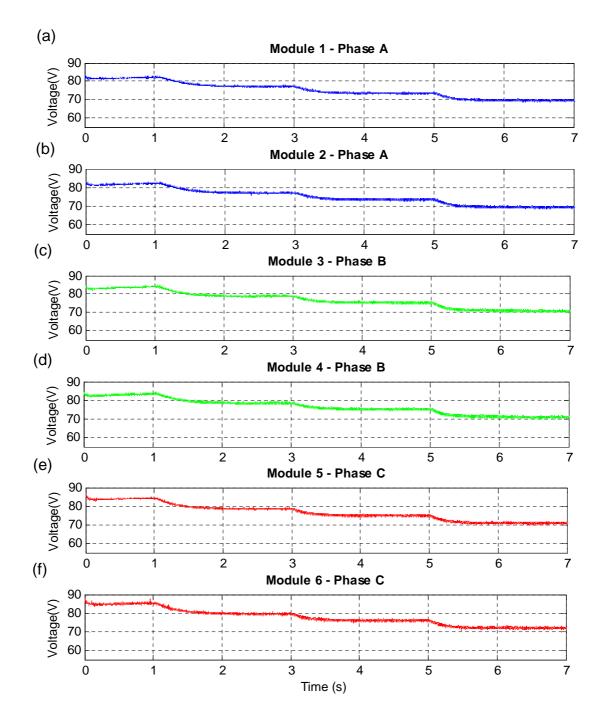

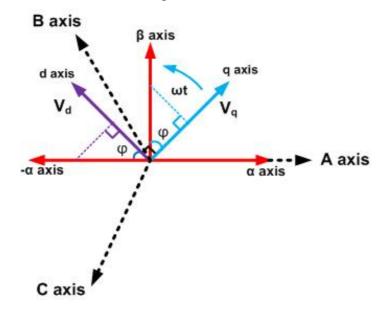

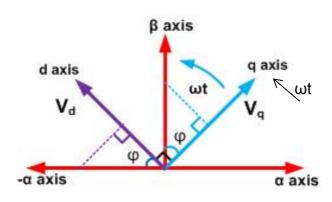

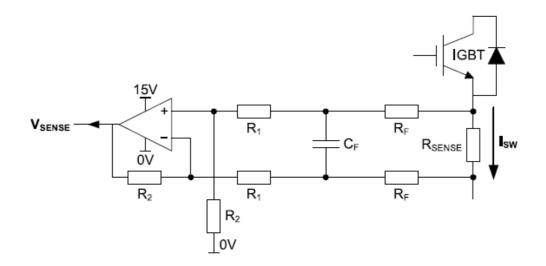

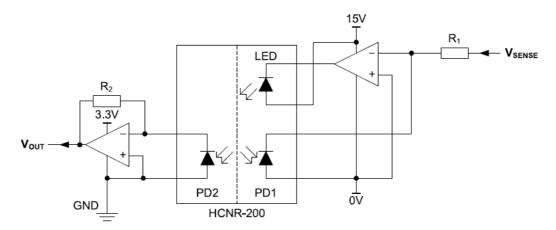

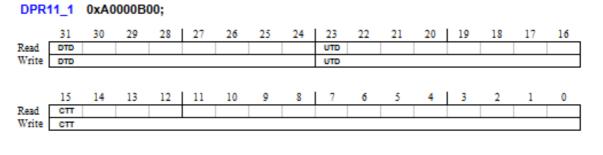

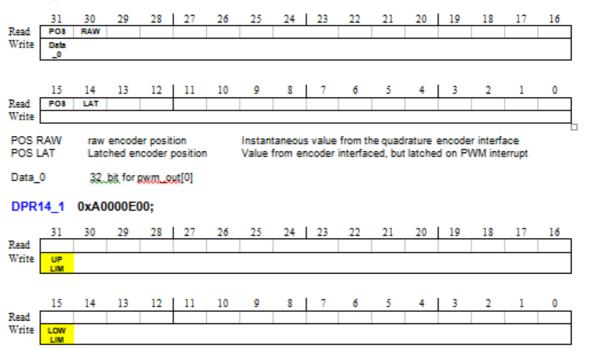

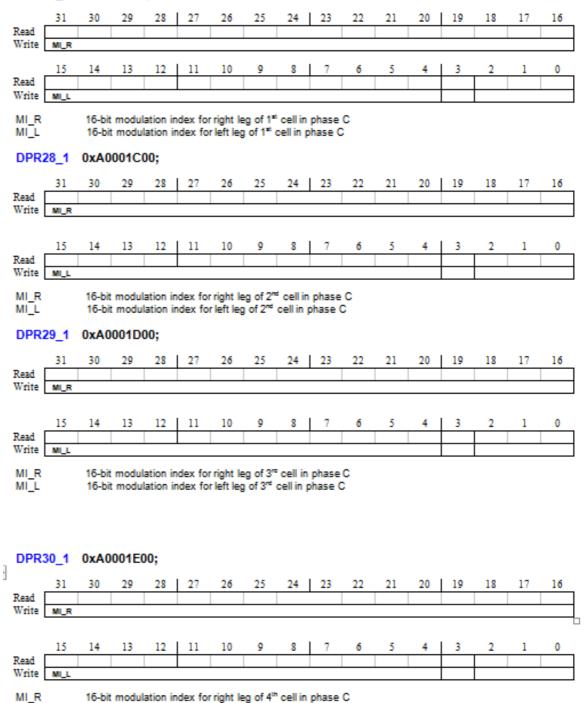

The five level configuration for the flying capacitor multi-level converter is as shown in Figure 1.8 and is capable of synthesizing five distinct voltage levels of 0,  $+V_{DC}/2 - V_{DC}/2 + V_{DC}$  and  $-V_{DC}$  at its output.