# New processing techniques for largearea electronics

**Minho Yoon**

A thesis presented for the degree of

Doctor of Philosophy

Department of Physics

Imperial College London

United Kingdom

August 2016

### ABSTRACT

Recent advancements in the semiconductor industry have been driven by the extreme downscaling of device dimensions enabled by innovative photolithography methods. However, such nano-scale patterning technologies are impractical for large-area electronics primarily due to extremely high cost and incompatibility with large-area processing. Therefore, alternative techniques that are simpler, more scalable and compatible with large-area manufacturing are required. This thesis explores the technological potential of two recently developed patterning techniques namely interlayer lithography (IL) and adhesion-lithography (a-Lith) for application in the field of large-area nano/electronics. The IL method relies on the use of a pre-patterned metal electrode that acts as the mask during back illumination of a photoresist layer followed by a conventional lift-off process step. On the other hand in the a-Lith approach, the surface energy of a patterned metal electrode is modified through the use of surface energy modifiers such as organic self-assembling monolayer (SAM). Following, a second metal is evaporated on the entire substrate. However, because of the present of the SAM, regions of metal-2 overlapping with metal-1 can easily be peeled off with the aid of a adhesive layer (e.g. sticky tape) leaving behind the two metal electrodes in close proximity to each other. Analysis of the resulting structures reveals that inter-electrode distances <20 nm can easily be achieved. The method was then used to develop innovative process protocols for the fabrication of functional self-aligned gate (SAG) transistor architectures. Best performing devices exhibited charge carrier mobility in the range of 0.5-1 cm2/Vs, high current on-off ratio ( $\sim 10^4$ ), negligible operating hysteresis and excellent switching speed. Using the same a-Lith process protocol, low-voltage organic ferroelectric tunnel junction memory devices were also developed by combining the metal-1/metal-2 nanogap electrodes with a ferroelectric copolymer deposited in-between them. Controllable ferroelectric tunnelling was observed enabling the devices' conductivity to be programmed using low biases and hence been used as a non-volatile memory cell. The alternative and highly scalable patterning methods described in this thesis may one day play a significant role on how largearea electronics of the future would be manufactured.

# **DECLARATION**

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work

I declare that contents of this thesis are my own work, and that contributions from other sources are appropriately acknowledged and referenced.

Minho Yoon

# ACKNOWLEDGEMENTS

Firstly I really appreciate my supervisor, Prof. Thomas, for taking me as a student and his kind and endless suggestions. Without his careful supervision, I cannot complete my research. Many thanks again. I would like to acknowledge Prof. Gerwin and Dr. Albert in Holst centre. They shared their vast experiences and wisdoms about the organic ferroelectric materials and analysing the carrier transport mechanisms. With their help, I can get some interesting results on ferroelectric tunnel junctions. Thanks also to Dr. Yong-Uk Lee. He gave me insights about current research trends. Based on his advices, I can catch up the trends and it was very useful for introducing my thesis. Thanks also to Prof. Jiyol Lee for sharing his experience on the ion-gel materials. When I did the first experiment about the materials, his advice was really helpful for me to get some results. Thanks also to Dr. Minsuk Oh for answering my questions about the oxide transistors. His reply was a very clear answer to my complex questions and helpful for me to setup the oxide semiconductors. Thanks also to our lab members for teaching me how to run the evaporator and other things. With their help, I can handle the machine without any troubles. Especially to Dr, Hendrik and Simon. I also appreciate Simon, Peach and Stefan for helping me to live in London. With their kindness, I can endure the stresses for living in London.

Finally, I really appreciate to my family and especially to my wife, Yunjung. I would never have finished this thing without your limitless patience, interest and encouragement. Many Thanks.

Minho Yoon

# **TABLE OF CONTENTS**

| 1. Introduction                                                                    | 13 |

|------------------------------------------------------------------------------------|----|

| 1.1. Motivation                                                                    | 13 |

| 1.2. Objectives and thesis layout                                                  | 15 |

| 2. Background                                                                      | 17 |

| 2.1. Lithography                                                                   | 17 |

| 2.2. Device physics of thin-film transistors                                       | 20 |

| 2.3. Ferroelectricity in solid-state materials                                     | 28 |

| 3. New processing techniques for large-area electronics                            | 33 |

| 3.1. Interlayer lithography                                                        | 33 |

| 3.2. Adhesion lithography                                                          | 40 |

| 3.3. Summary                                                                       | 49 |

| 4. Low operating voltage, self-aligned gate transistors                            | 50 |

| 4.1. Introduction                                                                  | 50 |

| 4.2. Solution-processed metal oxides semiconductors                                | 51 |

| 4.3. Dielectric materials for low-voltage operation                                | 60 |

| 4.4. Process architecture of self-aligned gate transistors by Adhesion Lithography | 73 |

| 4.5. Summary                                                                       | 79 |

| 5. Organic ferroelectric tunnel junction memory                                    | 80 |

| 5.1. Introduction                                                                  | 80 |

| 5.2. Charge transport in Ferroelectric tunnel junction memories                    | 81 |

| 5.3. Experimental Methods                                                          | 84 |

| 5.4. Results and Discussion                                                        | 86 |

| 5.5. Summary                                                                       | 95 |

| 6. Summary and Conclusions                                                         | 97 |

# Bibliography

# **LIST OF FIGURES**

| 1.1   | <ul><li>(a) Schematic illustration of potential applications of IoT.</li><li>(b) Concept of building blocks of IoT</li></ul>                                                                                                                                                                                                                          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2   | Global research programs on IoT 14                                                                                                                                                                                                                                                                                                                    |

| 2.1.1 | Schematic process diagrams of shadow mask lithography 17                                                                                                                                                                                                                                                                                              |

| 2.1.2 | Schematic diagrams of photolithography based on the negative photoresist 19                                                                                                                                                                                                                                                                           |

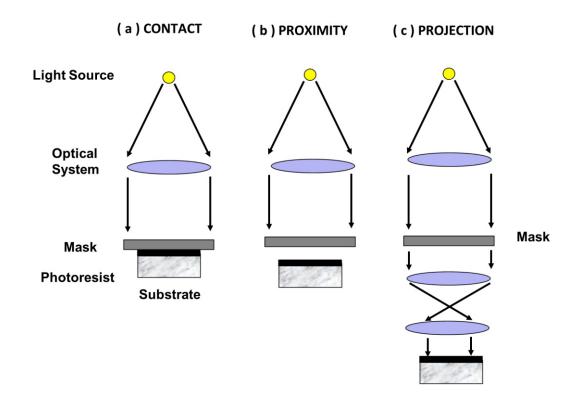

| 2.1.3 | Schematic diagrams of exposure systems.(a) Contact system. (b) Proximity system.<br>(c) Projection system                                                                                                                                                                                                                                             |

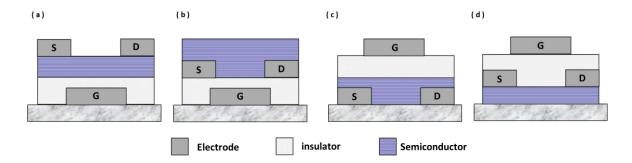

| 2.2.1 | Schematic representations of field-effect transistor architectures. (a) bottom-gate top-contact. (b) bottom-gate bottom-contact. (c) top-gate bottom-contact. (d) top-gate top-contact                                                                                                                                                                |

| 2.2.2 | Cross-sectional view of a bottom-gate top-contact staggered thin-film transistor22                                                                                                                                                                                                                                                                    |

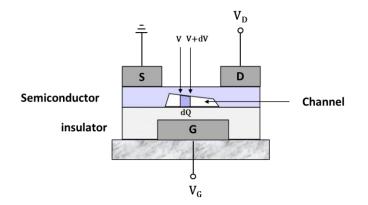

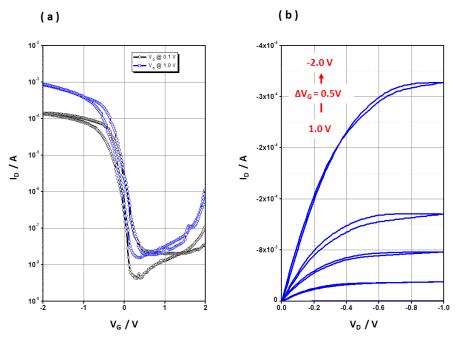

| 2.2.3 | (a) Linear ( $V_D = 0.1$ V) and saturated ( $V_D = 1.0$ V) transfer characteristics of a top-gate, top-contact TFT with channel width W =1000 µm and channel length L = 100 µm, fabricated with poly 3-hexylthiophene (P3HT) films on ion-gel dielectric.<br>(b) Output characteristics of the ion-gel gated poly 3-hexylthiophene (P3HT) transistor. |

| 2.2.5 | (a) Device Schematic illustration of a thin-film transistor. (b) Simplified small-<br>signal model of a thin-film transistor                                                                                                                                                                                                                          |

| 2.2.6 | Thin-film transistor schematic showing the parasitic overlaps between the various electrode terminals                                                                                                                                                                                                                                                 |

| 2.3.1 | (a) Chemical structure of the VDF monomer. (b) Crystal structures of P(VDF) 30                                                                                                                                                                                                                                                                        |

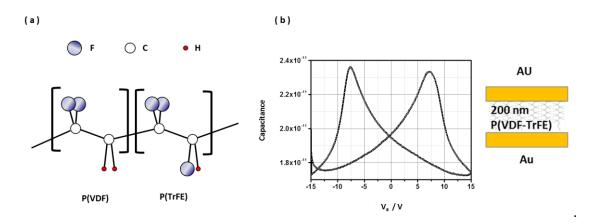

| 2.3.2 | (a) Schematic chemical structure of P(VDF-TrFE). (b) Typical hysteresis loop of 200-nm-thickness of organic ferroelectric materials, P(VDF-TrFE). Device structures was 200 nm thick P(VDF-TrFE) MIM Capacitors                                                                                                                                       |

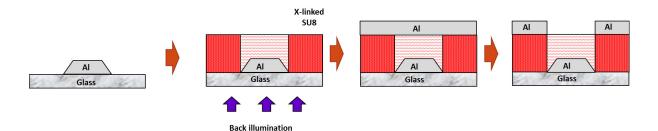

| 3.1.1 | Schematic representation of the IL process                                                                                                                                                                                                                                                                                                            |

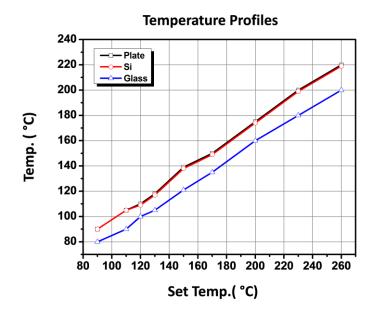

| 3.1.2 | Measured surface temperatures (black) versus hotplate set temperatures for a Si wafer (red) and a glass substrate (blue) from 90 °C to 260 °C                                                                                                                                                                                                         |

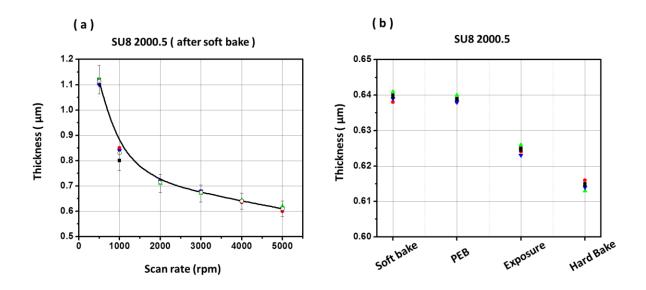

| 3.1.3 | (a) TPR curve of <i>SU-8</i> according to the spin rate from 500 rpm to 5000 rpm. (b) Thickness changes of spin-coated SU-8 during the post-processes                                                                                                                                                                                                 |

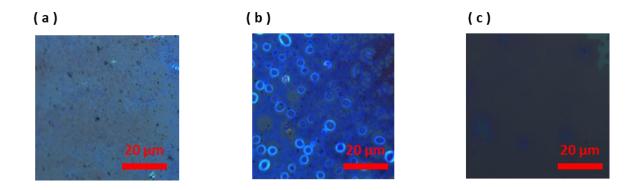

| 3.1.4 | Surface images of spin-casted <i>SU-8</i> at various PEB temperatures. (a) 95°C, 3 min.<br>(b) 115°C, 3 min. (c) 135°C, 3 min                                                                                                                                                                                                                         |

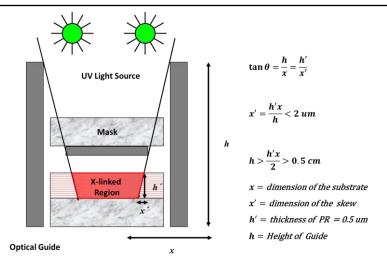

| 3.1.5 | Schematic illustration of the hand-made exposure system. From the geometrical considerations, guides of 2 cm height were installed on the system for enhancing the patterning resolution                                                                                                                                                              |

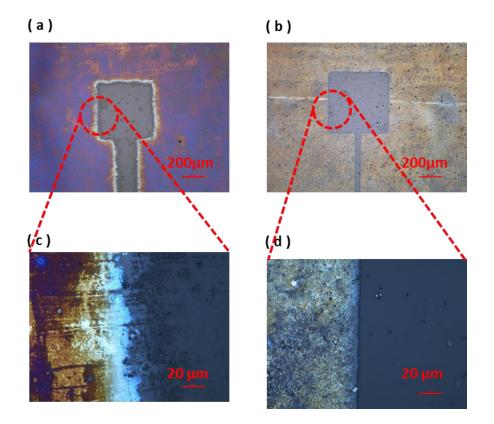

| 3.1.6 | Pattern images without guide at low (a) and high resolution (c), Pattern images with guide at low (b) and high resolution (d) for IL                                                                                                                                                                                                                  |

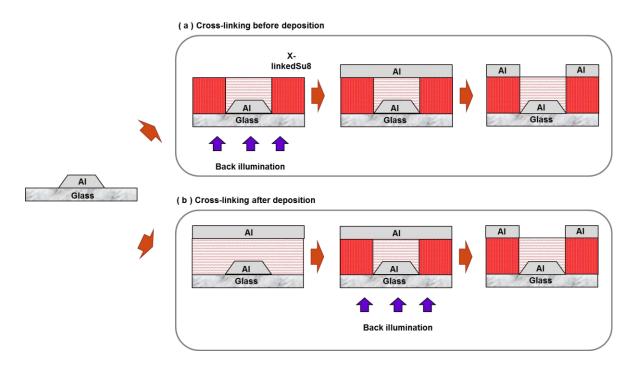

| 3.1.7 | Two possible process routes for IL. (a) Cross-linking before deposition. (b) Cross-                                                                                                                                                                                                                                                                   |

|        | linking after deposition                                                                                                                                                                                                                                                                                                                                                          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

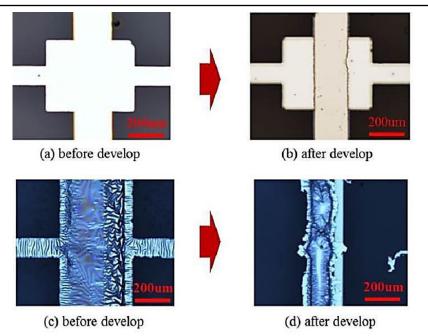

| 3.1.8  | Pattern images of the "deposition after cross linking" route. before (a) and after (b) develop. Pattern images of the "cross-linking after deposition" route before (c) and after (d) develop                                                                                                                                                                                     |

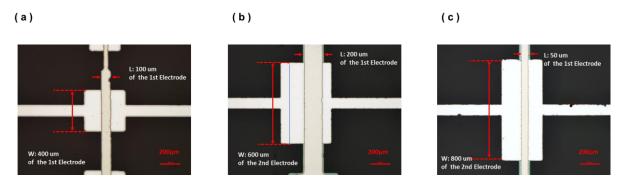

| 3.1.9  | Electrode patterns with different dimensions produced by IL. (a) $W/L = 400/100$ $\mu$ m. (b) $W/L = 600/200 \mu$ m. (c) (b) $W/L = 800/50 \mu$ m                                                                                                                                                                                                                                 |

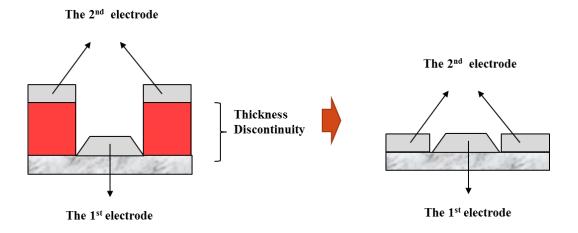

| 3.1.10 | Schematic demonstrating the fundamental limitation of IL, thickness discontinuity between electrodes                                                                                                                                                                                                                                                                              |

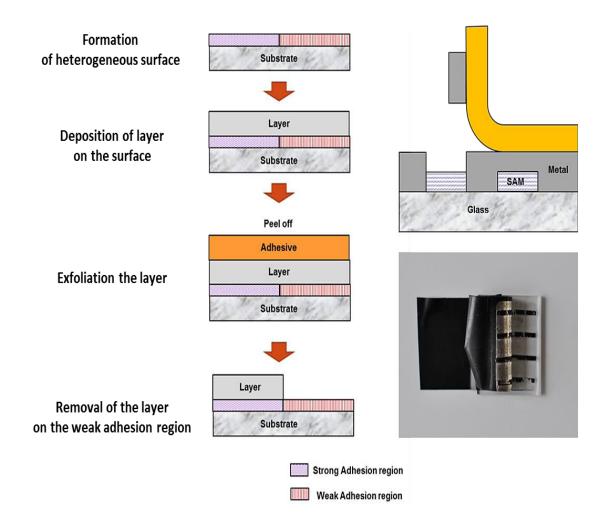

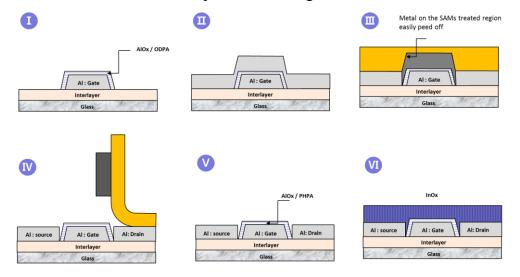

| 3.2.1  | Basic process flow chart of a-Lith                                                                                                                                                                                                                                                                                                                                                |

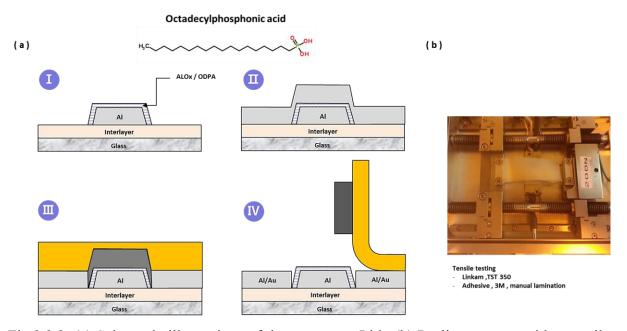

| 3.2.2  | (a) Schematic illustrations of the process, a-Lith. (b) Peeling process with a tensile tester, Linkam TST 350 43                                                                                                                                                                                                                                                                  |

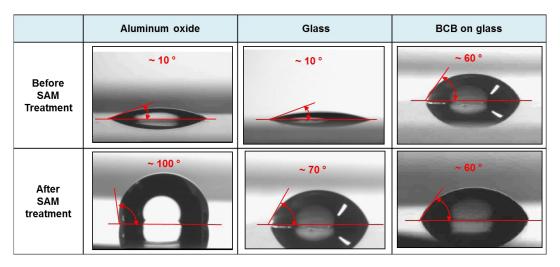

| 3.2.3  | D.I water contact angle measurement on various substrates                                                                                                                                                                                                                                                                                                                         |

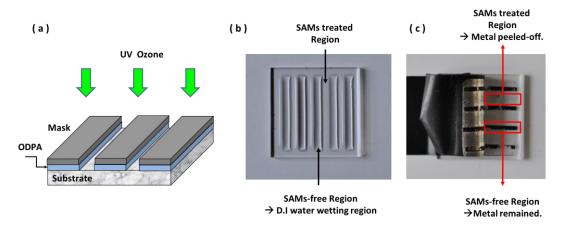

| 3.2.4  | (a) Removal of SAMs by UV-ozone treatment with a metal mask. (b) D.I water dropping test on the substrates. D.I water was spreading only on the SAM-free region. (c) Peeling test on glass. Metal on the SAMs treated region was peeled-off, while remained on the SAM-free region                                                                                                |

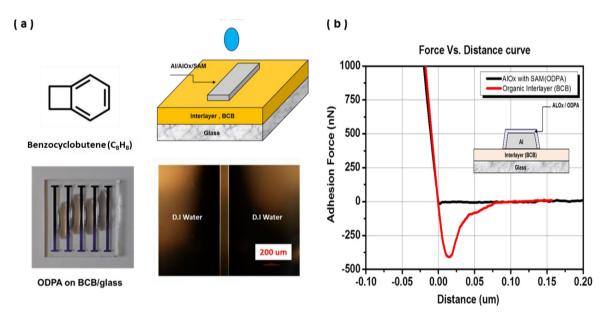

| 3.2.5  | (a) Selective SAM treatment on the BCB coated glass. (b) Force and distance curves of the SAM treat aluminum oxide and BCB coated glass                                                                                                                                                                                                                                           |

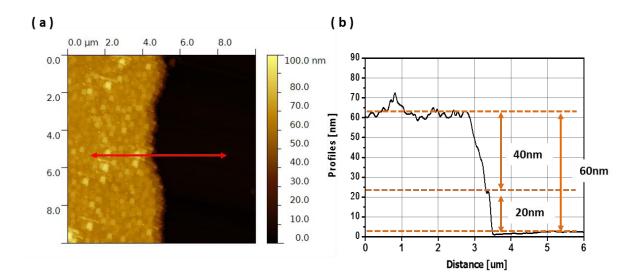

| 3.2.6  | Multilayer ODPA film. (a) AFM topography image. (b) Depth profiles of the line (red). Total measured thickness of the layers is 60 nm, where 40 nm for the deposited metal on the SAMs. Remaining 20 nm is due to the formation of ODPA multilayer structures. 46                                                                                                                 |

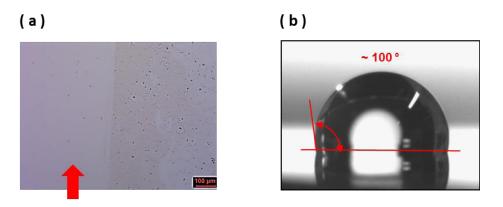

| 3.2.7  | (a) Optical image of ODPA SAMs by mechanical Exfoliation. (b) Contact angle of D.I water on the exfoliated region ( $\sim$ 100 °)                                                                                                                                                                                                                                                 |

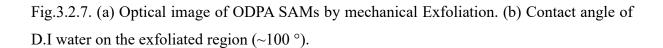

| 3.2.8  | <ul> <li>(a) Schematic illustration of the chemical bonding nature of multi-layered ODPA.</li> <li>(b) Formation of Monolayer of ODPA SAMs by mechanical exfoliation. During the exfoliation, the relatively week Van der Waals bonding between the multi-layered ODPA molecules was broken, hence only chemically bounded- monolayer ODPA remained on the surface. 48</li> </ul> |

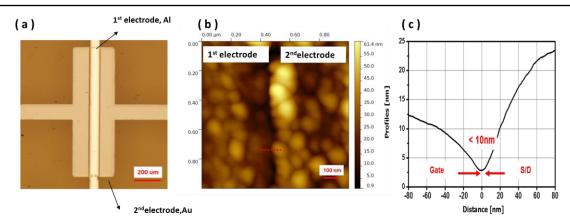

| 3.2.9  | (a) Optical image of the in-plane nanostructures. (b) Atomic force topography image of the gap between the 1st and 2nd electrodes. (c) The profiles of the gap and the values were sub 20 nm                                                                                                                                                                                      |

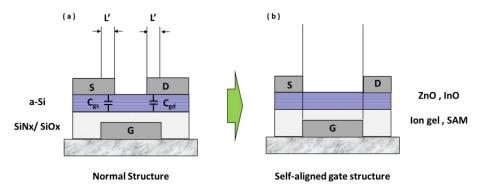

| 4.1.1  | Strategies for high performance and low-voltage thin-film transistors. (a) shows a conventional TFT structure while (b) an aligned gate TFT architecture where the parasitic capacitances due to electrode overlaps are minimized                                                                                                                                                 |

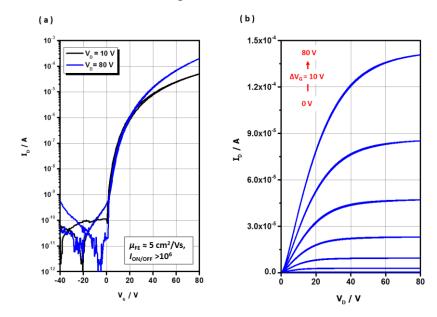

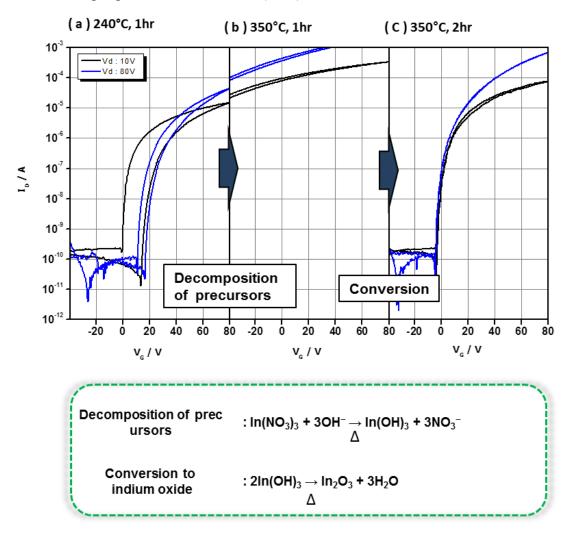

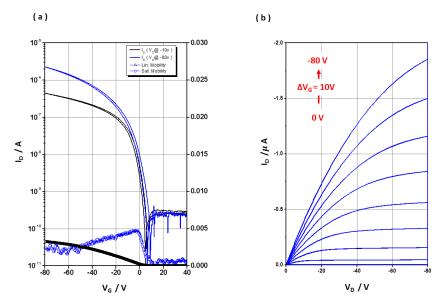

| 4.2.1  | Fig 4.2.1 (a) Linear ( $V_D = 10 \text{ V}$ ) and saturated ( $V_D = 80 \text{ V}$ ) transfer characteristics<br>of bottom-gate, top-contact TFTs with channel width W =1000 µm and channel<br>length L = 50 µm, fabricated with ZnO films on 200 nm-thick SiO <sub>2</sub> dielectric by<br>spin casting. (b) Output characteristics of the ZnO based TFT                        |

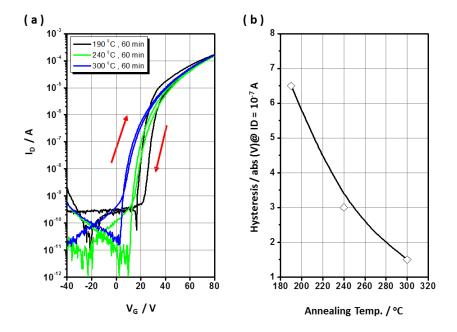

| 4.2.2  | Fig 4.2.2 (a) Saturated ( $V_D = 80$ V) transfer characteristics of bottom-gate, top-<br>contact TFTs with channel width W =1000 µm and channel length L = 50 µm,                                                                                                                                                                                                                 |

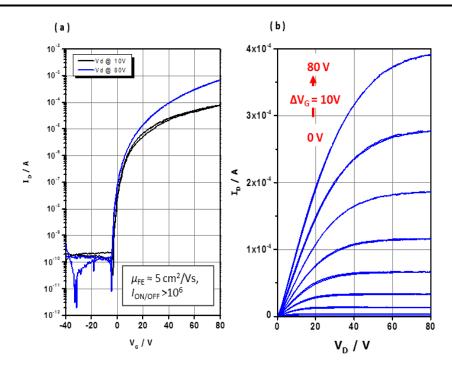

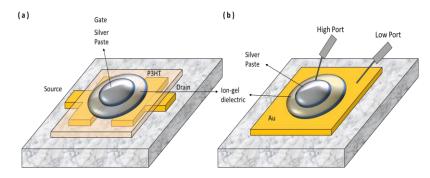

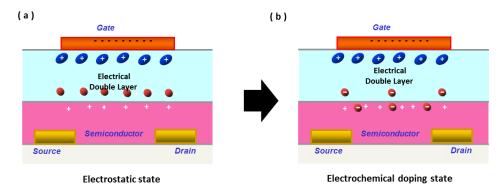

- 4.3.1 (a) Schematic diagrams of devices for measuring the performance characteristics of ion-gel gated transistors. (b) Illustration for the measurement for the values of the capacitance of the ion-gel dielectric.

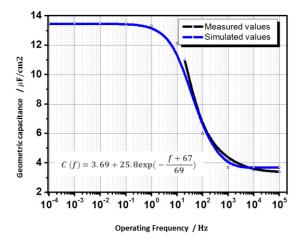

- 4.3.2 The frequent dependent geometric capacitance of an ion-gel dielectric material from 20 Hz to  $10^5$  Hz. Measured values were depicted in black line and simulated values were depicted in blue line. Inset: The fitting model according to the Debye relaxation model. 63

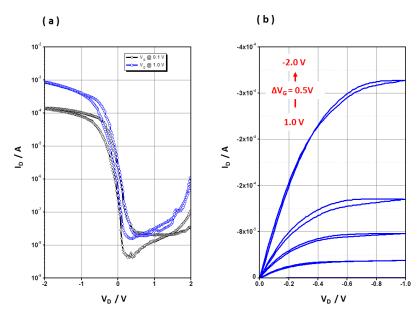

- 4.3.5 (a) Linear ( $V_D = 0.1 V$ ) and saturated ( $V_D = 1.0 V$ ) transfer characteristics of a top-gate, top-contact TFT with channel width W =1000 µm and channel length L = 100 µm, fabricated with P3HT films on ion-gel dielectric. (b) Output characteristics of the ion-gel gated P3HT transistor. 65

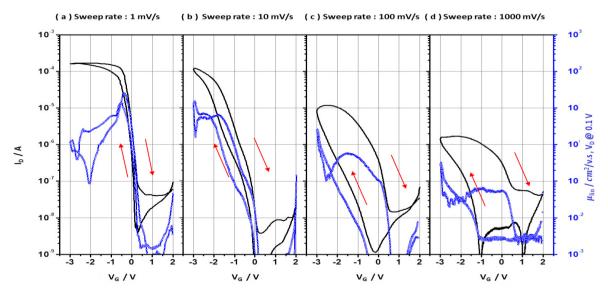

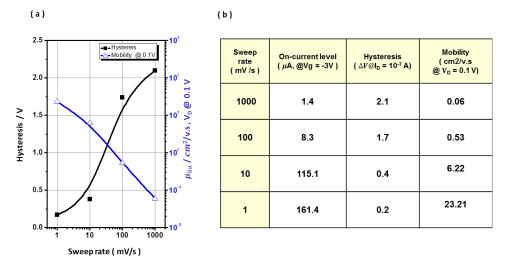

- 4.3.7 (a) Evolution of the operating hysteresis and hole mobility with gate voltage sweep rate measured for an ion-gel gated P3HT transistor. (b) Summary of key transistor parameters extracted from TFTs measured at different gate voltage sweep rates. 67

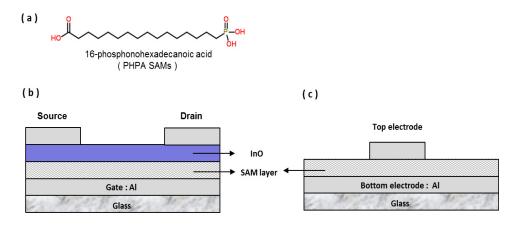

| 4.3.9  | (a) Chemical structure of 16-Phosphonohexadecanoic acid. (b) Schematic diagrams of devices for measuring the performance characteristics of the transistor on the |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | SAMs based dielectric. (c) Illustration for the measurement for the values of the                                                                                 |

|        | capacitance of the SAMs based dielectric                                                                                                                          |

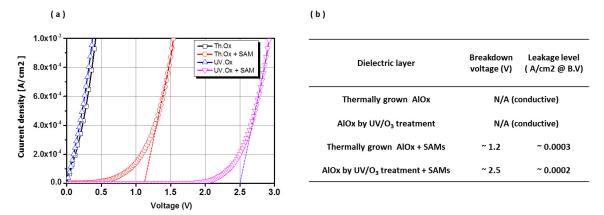

| 4.3.10 | (a) Current density versus applied bias and extraction of the break down voltage in                                                                               |

|        | devices based on differently processed alumina and alumina/SAM dielectric layers.                                                                                 |

|        | (b) Summary of the extracted device parameters                                                                                                                    |

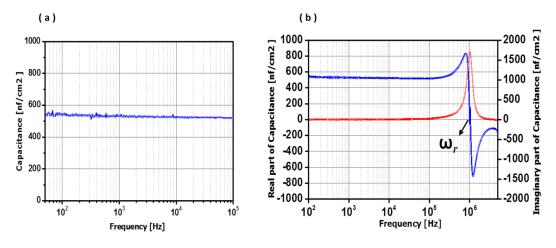

| 4.3.11 | Values of the geometric capacitance of the hybrid SAMs dielectric layer for                                                                                       |

|        | frequency signals. (a) Up to $10^5$ Hz. (b) Up to $10^7$ Hz. Resonance frequency of the                                                                           |

|        | hybrid SAMs dielectric layer, $\omega_r$ was near $10^6$ Hz, where the maximum operation                                                                          |

|        | frequency of the device with the hybrid SAMs dielectric can be determined by this                                                                                 |

|        | frequency                                                                                                                                                         |

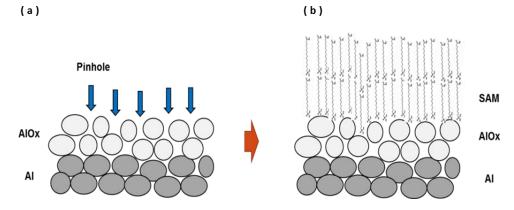

| 4.3.12 | Schematic illustration of the passivation process occurring on the native oxide by                                                                                |

|        | SAMs treatment. (a) Native aluminum oxide dielectric. (b) SAMs treated aluminum                                                                                   |

|        | oxide dielectric. A lot of density of pinhole and crevices could be passivated by the                                                                             |

|        | SAMs molecules. 70                                                                                                                                                |

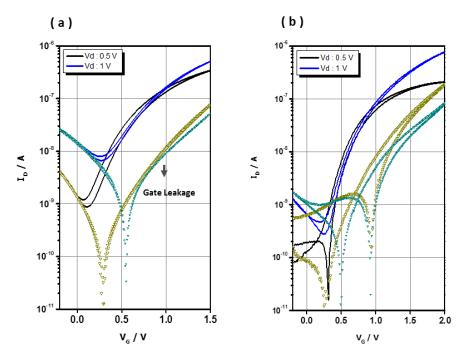

| 4.3.13 | Linear ( $V_D = 0.5 V$ ) and saturated ( $V_D = 1 V$ ) transfer characteristics of a bottom-                                                                      |

|        | gate, top-contact TFT with channel width W =1000 $\mu$ m and channel length L = 50                                                                                |

|        | $\mu$ m, fabricated with InO films. (a) On the thermally grown alumina prior to SAM                                                                               |

|        | functionalization. (b) On the UV ozone treated alumina prior to SAM                                                                                               |

|        | functionalization. 71                                                                                                                                             |

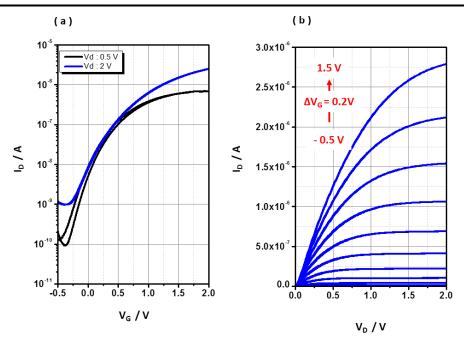

| 4.3.14 | (a) Linear ( $V_D = 0.5 V$ ) and saturated ( $V_D = 2.0 V$ ) transfer characteristics of a                                                                        |

|        | top-gate, top-contact TFT with channel width W =1000 $\mu$ m and channel length L =                                                                               |

|        | 50 $\mu$ m, fabricated with solution-processed indium oxide on the hybrid                                                                                         |

|        | alumina/SAM dielectric. (b) Output characteristics of the solution-processed indium                                                                               |

| 4 4 1  | oxide transistor. 72                                                                                                                                              |

| 4.4.1  | Schematic illustration of the process steps used to fabricate the SAGs TFTs by a-                                                                                 |

| 4 4 2  | Lith                                                                                                                                                              |

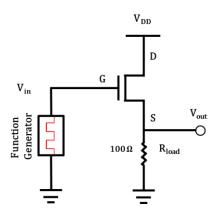

| 4.4.2  | Common-drain amplifier circuit configuration for measuring the operating speed of                                                                                 |

| 1 1 2  | the TFTs                                                                                                                                                          |

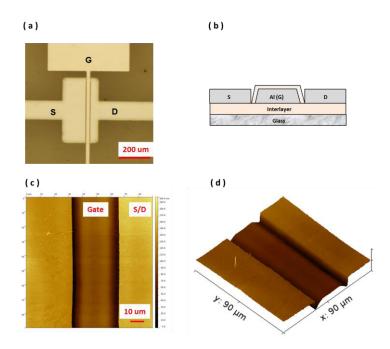

| 4.4.3  | Optical image of the SAG TFT structure. (b) Schematic cross-sectional view of the                                                                                 |

|        | illustration of the SAG TFT structure. (c) Two-dimensional AFM image of the self-                                                                                 |

|        | aligned gate sturcture. (d) Three-dimensional AFM image of the self-aligned gate sturcture. 75                                                                    |

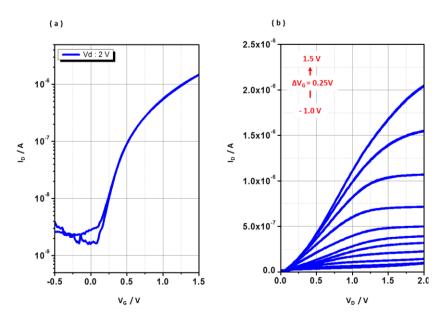

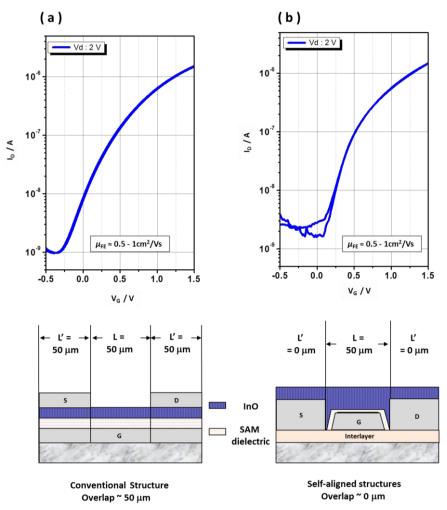

| 4.4.4  | (a) Saturated ( $V_D = 2.0$ V) transfer characteristics of the self-align bottom-gate,                                                                            |

| 4.4.4  | bottom-contact TFT with channel width W =1000 $\mu$ m and channel length L = 50                                                                                   |

|        | $\mu$ m, fabricated with solution-processed indium oxide on the hybrid alumina/SAM                                                                                |

|        | dielectric. (b) Output characteristics of the solution-processed indium oxide                                                                                     |

|        | transistor                                                                                                                                                        |

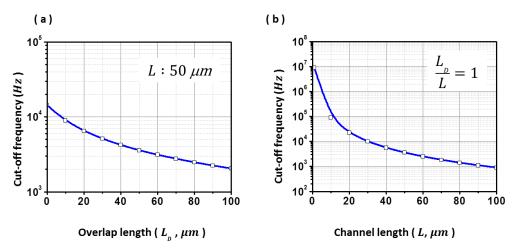

| 4.4.5  | (a) Simulation results of the values of the cutt-off frequency according to the                                                                                   |

|        | overlap length from 0 $\mu$ m to 100 $\mu$ m at the fixed channel length of 50 $\mu$ m. (a)                                                                       |

|        | Simulation results of the values of the cutt-off frequency according to the channel                                                                               |

|        | length from 0 $\mu$ m to 100 $\mu$ m at the fixed ratio of unity between the channel length                                                                       |

|        | rengen nom o pin to roo pin at the fixed fails of unity between the chamber felight                                                                               |

| 4.4.6 | Saturated ( $V_D = 2.0$ V) transfer characteristics of InO transistors with channel width W =1000 µm and channel length L = 50 µm. (a) A conventional structures                     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | with overlap length of 50 $\mu$ m. (b) A self-aligned gate structure with the ovelap length of close to 0 $\mu$ m                                                                    |

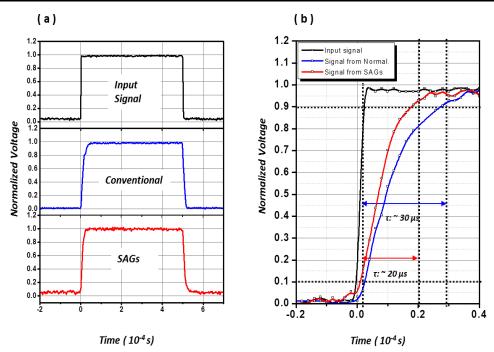

| 4.4.7 | Dynamic response of transistors. (a) One cycle of the input signal (black), the                                                                                                      |

|       | output signal of the conventional structures with overlap length of 50 $\mu$ m (blue) and the self-aligned gate structures with overlap length of 0 $\mu$ m (red). (c) Determination |

|       | of the rise time, required time for rising from 10 % to 90 % of the signal. The                                                                                                      |

|       | measured rise time of the SAG TFTs with the overlap length of 0 $\mu$ m was about 20                                                                                                 |

|       | μs (blue arrow), while that of a conventional TFT structure with a channel overlap                                                                                                   |

|       | length of 50 μm was 30 μs (red arrow)                                                                                                                                                |

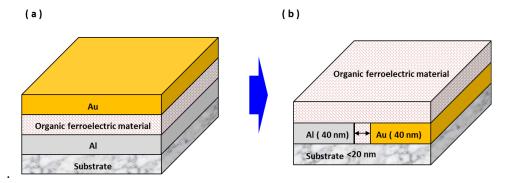

| 5.1   | Strategies for a low-voltage organic memory device by a-Lith. (a) Conventional vertical structure. (b)In-plane nanostructure. 81                                                     |

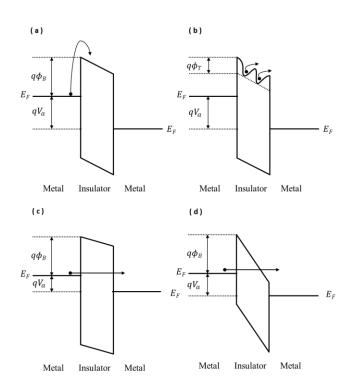

| 5.2   | Schematic illustrations of the charge-transport mechanisms though an insulator. (a)                                                                                                  |

|       | Schottky emission. (b) Poole-Frenkel emission. (c) Direct Tunneling. (d) Fowler–<br>Nordheim tunnelling                                                                              |

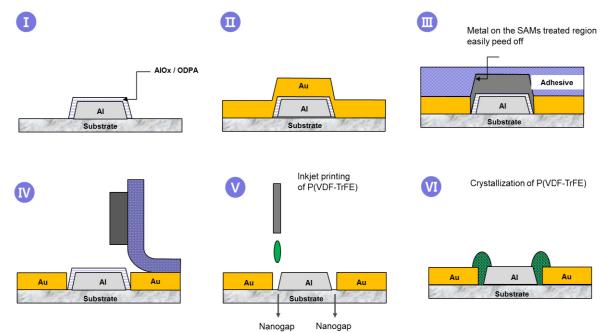

| 5.3   | Schematic of the process steps used to manufacture an organic ferroelectric tunnel                                                                                                   |

|       | juntion memory by a-Lith. Before inkjetting the P(VDF-TrFE) on to the nanogap,                                                                                                       |

|       | the SAM layer on the aluminium was removed by UV-Ozone treatment for 10                                                                                                              |

|       | minutes                                                                                                                                                                              |

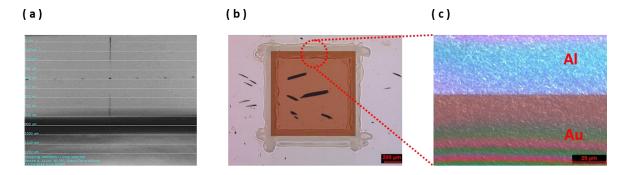

| 5.4   | Printed organic ferroelectric devices. (a) Printing image. (b) Low magnification                                                                                                     |

|       | non-polarized optical image of the whole device consisting of a square middle Al                                                                                                     |

|       | electrode surrounded by a global Au electrode. Scratches in the electrodes were                                                                                                      |

|       | from the electrical measurement. (c) Higher magnification polarized optical image of the neurogen region $O$ regards formulactric of $P(VDE TrEE)$ was printed in the                |

|       | of the nanogap region. Organic ferroelectric of P(VDF-TrFE) was printed in the nanogap region. The polarized image was yellowish in Au region. Birefringence of                      |

|       | the film in polarized mode was observed, which indicate the formation of crystal                                                                                                     |

|       | structure of P(VDF-TrFE) film                                                                                                                                                        |

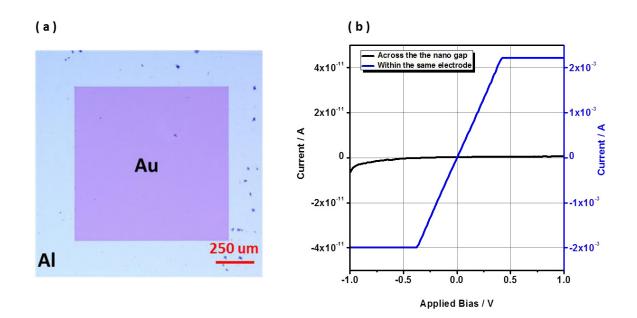

| 5.5   | (a) Optical image of the as-fabricated Al-Au nanogap. (b) I-V characteristics                                                                                                        |

|       | measured across the nanogap (black line) and in contact with the same electrode                                                                                                      |

|       | (i.e. both probes touching the same electrode)                                                                                                                                       |

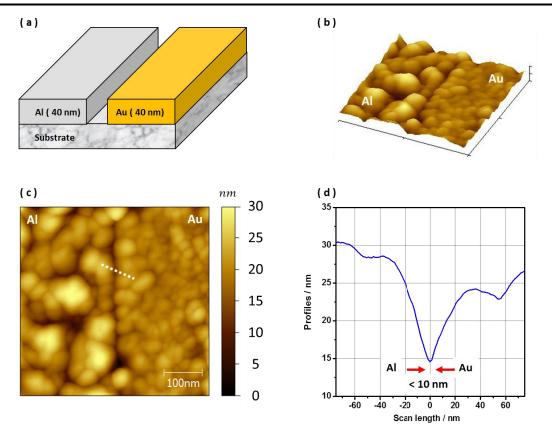

| 5.6   | (a) Schematic illustration of the in-plane nanogap structure. (b) 3-dimensional                                                                                                      |

|       | atomic force microscopy image of the in-plane nanogap structure. (c) 2-dimensional                                                                                                   |

|       | atomic force microscopy image of the in-plane nanogap structure. (d) The profiles                                                                                                    |

|       | of the gap and the value was sub 20 nm                                                                                                                                               |

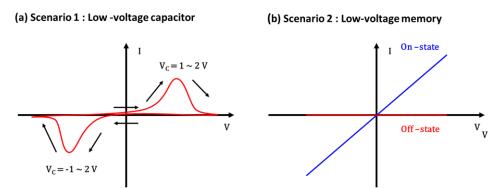

| 5.7   | Device estimations. (a) In-plane nano capacitors, Due to the sub 20 nm structure,                                                                                                    |

|       | the device could be operated in a low-voltage capacitors. Displacement current                                                                                                       |

|       | would be dominant, hence at the coercive voltage of $1 \sim 2$ V, the current density                                                                                                |

|       | would be maximized. (b) Tunnel-junction memory mode. If the charge carrier can                                                                                                       |

|       | be tunnelled into the nanogap of 20 nm, the device would show the high density of                                                                                                    |

|       | current and duality. There would be significant difference in the density of current                                                                                                 |

|      | between the on and off state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

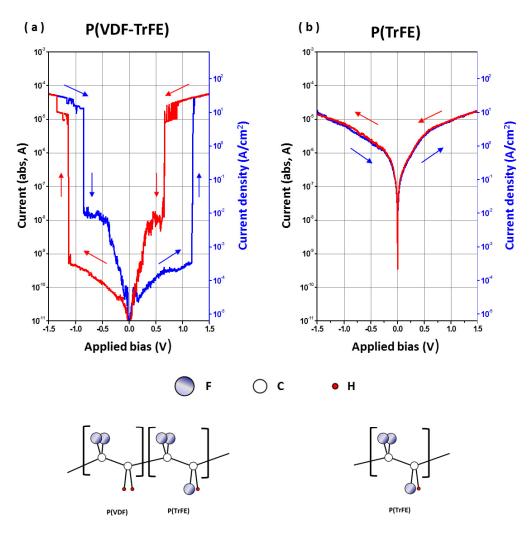

| 5.8  | Current-voltage characteristics of: (a) the ferroelectric P(VDF-TrFE) junction and (b) the non-ferroelectric (i.e. control) P(TrFE) device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

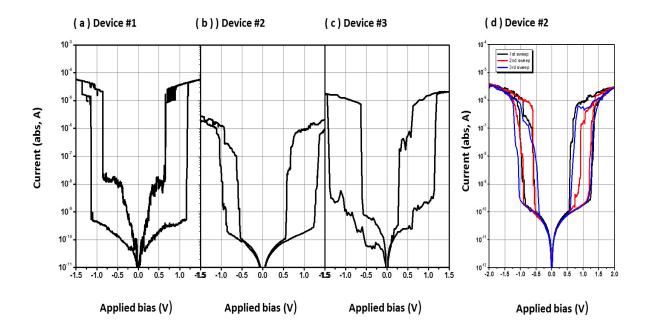

| 5.9  | (a,b,c) J-V characteristics of several different P(VDF-TrFE) tunnel junctions. (d)<br>Multiple J-V sweeps for device #2 demonstrating good operating stability 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

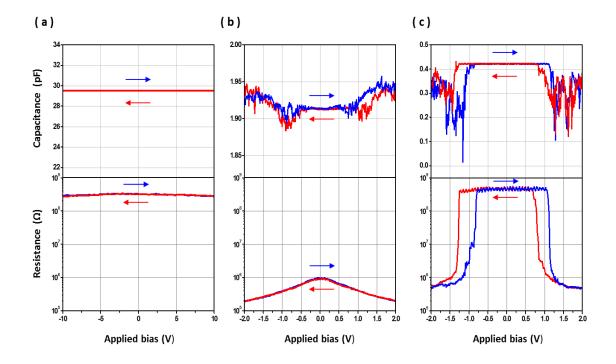

| 5.10 | Impedance analysis using parallel connected capacitance and resistance model for devices based on (a) SiNx, (b) P(TrFE), and (c) P(VDF-TrFE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

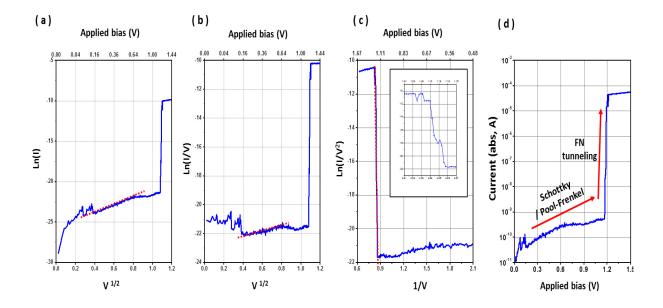

| 5.11 | Current-voltage analysis based on: (a) Schottky model, (b) Poole-Frenkel Model,<br>(c) Fowler–Nordheim tunnelling model. Inset: negative slope region above the<br>turning voltage of 1.1 V, well-matched with the Fowler–Nordheim tunnelling<br>model. (d) Charge transport mechanisms of the MFM junctions based on analysis of<br>the I-V characteristic of the device. 94                                                                                                                                                                                                                                                                                                                                                                                                                                    |

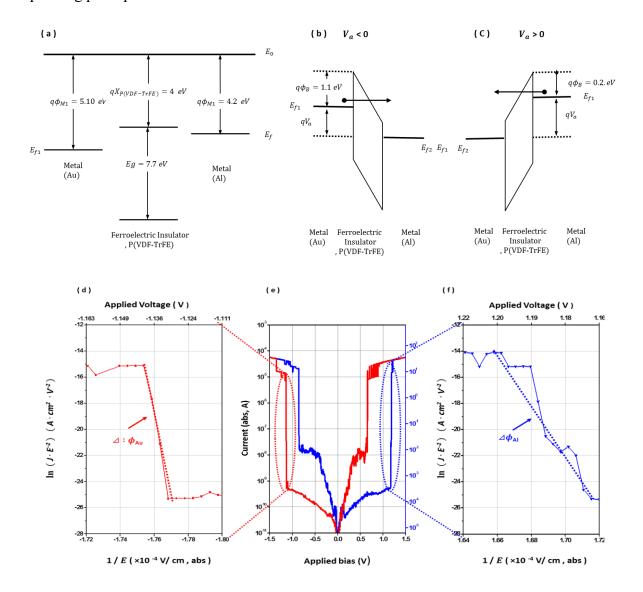

| 5.12 | (a) Energy band diagrams of the metal-ferroelectric-metal structure/materials before contact. (b, c) Estimated potential barriers for electron injection from Au and from Al to the ferroelectric material of 1.1 eV and 0.2 eV, respectively. (d, f) The characteristic slope measured using Fowler–Nordheim plot analysis of the MFM device under negative and positive bias. The slope of Au/Fe is higher than that of Al/Fe, which indicates that the analysis is in accordance to the assumed energy band picture. (e) Current-voltage characteristics of the ferroelectric P(VDF-TrFE) and (f) the corresponding Fowler–Nordheim plot                                                                                                                                                                      |

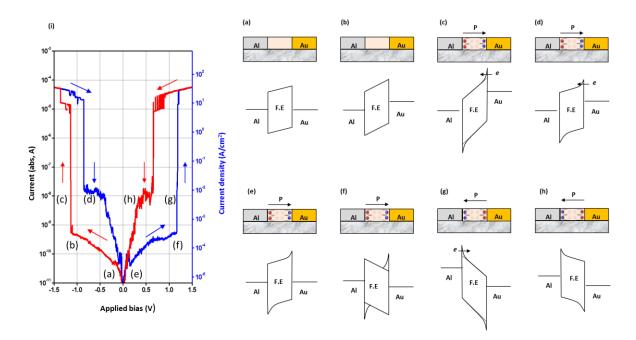

| 5.13 | Operation mechanism of organic ferroelectric tunnelling memory device at various<br>bias regions. (a) At equilibrium states. (b) Below the coercive voltage, current<br>transport is expected to be limited by the potential barrier between the Au and Fe.<br>(c) Above the coercive voltage, significant charge carrier density is transported via<br>the Fowler–Nordheim tunnelling. (d-e) Insufficient low bias region for Fowler–<br>Nordheim tunnelling. (f) The bias region for the antiparallel polarization vector to<br>the applied electric field. (g) The bias region for realignment of the polarization<br>vector to the applied electric field. Significant charge carrier density is re-<br>transported across the junction. (h) Insufficient low bias region for Fowler–<br>Nordheim tunnelling |

# **List of Tables**

| 2.1  | Representative ferroelectric materials and its properties          | 29 |

|------|--------------------------------------------------------------------|----|

| 2.2  | Research directions of organic memory devices based on P(VDF-TrFE) | 32 |

| 4.1  | Recent progresses of solution processed metal oxide semiconductors | 54 |

| 4.2  | Comparisons between zinc oxide and indium oxide transistors        | 60 |

| 5.1. | Summary of the charge-transport mechanisms though an insulator.    | 84 |

## **CHAPTER 1**

# Introduction

#### **1.1 Motivation**

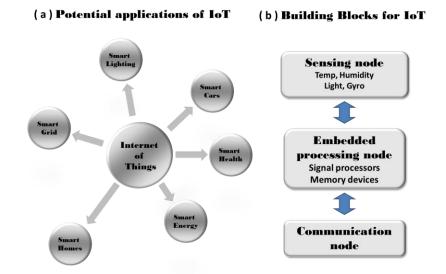

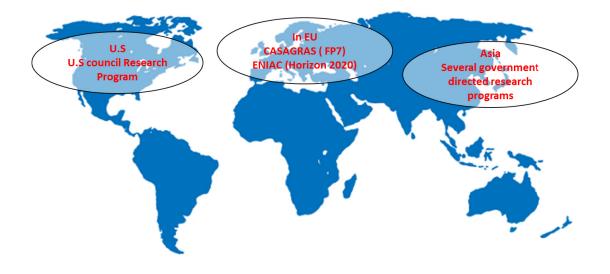

The "Internet of Things (IoT)" has been receiving increasing attention in recent years due to its huge potential for impacting our daily life in areas spanning from personal health, home appliances, communication and personal entertainment to transportation and energy.<sup>1,2</sup> The IoT is defined as "*A dynamic global network infrastructure with self-configuring capabilities based on standard and interoperable communication protocols where physical and virtual "things" have identities.*" by IoT European Research Cluster, IERC<sup>3</sup> (Figure 1.1). For this reason, significant research activities have been inspired across the world (Figure 1.2). For instance, within the European Union the IoT technology has been developed through programs such as Coordination and Support Action for Global RFID-related Activities and Standardization (CASAGRAS) under 7<sup>th</sup> Framework Program (FP7)<sup>4</sup>, and more recently within the nano electronic research program ENIAC under Horizon 2020<sup>5,6</sup>. In the United States, six main technologies related with IOT were selected and several research programs were financially supported by US research agencies.<sup>7</sup> Similarly, in Asia numerous government driven research programs have recently been initiatted.<sup>8,9</sup> These worldwide activities indicate the momentum IoT has created and hence reflecting its potential.

Fig.1.1. (a) Schematic illustration of potential applications of IoT.[1,2] (b) Concept of building blocks of IOT. [10]

#### **1. Introduction**

The building blocks of IoT are shown in Figure 1.1 and include several units: a sensing node for collecting the information from physical "things", an embedded processing node for processing the gathered information and transforming into the signal form of internet "things" and a communicating node for transmitting and receiving signals with central controlling units <sup>10,11</sup>.

#### World wide movements for "Internet of Things"

Fig.1.2. Global research programs on IoT. [4-9]

For realizing the IoT and successfully implementing it in our everyday life, a lowcost, energy-efficient embedded processing node is required with self-configuring capabilities.<sup>3</sup> Solution-processed semiconducting, insulating and conducting materials have been widely studied and proposed in the past few decades as possible building blocks for the manufacturing of such processing nodes. For example, numerous families of chemically stable organic semiconducting materials have been developed and their electrical performances has been improving steadily.<sup>12,13</sup> Metal oxides semiconducting materials such as zinc oxide, indium oxide and gallium oxide have also emerged with their electrical performances now in par with that of state-of-the-art low-temperature poly silicon transistors<sup>14,15</sup>. Similarly, complementary organics as well as inorganic insulating materials have also been developed and used in numerous large-area electronic applications.<sup>16-19</sup> Electrically conducting materials based on solution-processable metal nanowires and nanoparticle are also being developed as alternatives to conventional vacuum processed electrode materials.<sup>20-24</sup> As a result there is now a consensus that solution-processed materials

#### **1. Introduction**

poses a number of advantages over vacuum-processed systems in terms of manufacturing cost and could one day enable the much sought widespread adoption of electronic devices and sensors for realising the IoT.<sup>25,26</sup>

In the area of patterning techniques for the manufacturing of active opto/electronic devices, non-photolithographic based pattering methods such as nano-imprint lithography<sup>27,28</sup>, inkjet-printing<sup>29–31</sup> and gravure printing<sup>32–34</sup> appear to be the most favourable processes. However, numerous issues associated with these methods have been identified over the years. For example, although spatial resolution down to a few nanometre scales is indeed possible via nano-imprint lithography<sup>27</sup>, the cost for fabricating the master itself is very high while the durability of the master remains unproven. Similarly, in the case of inkjet printing, the resolution of the pattern is known to be limited typically in the order of 10 micrometre, while the uniformity of the printed layers suffers from unwanted effects such as coffee stain effect. Therefore, development of alternative patterning methods that are scalable, inexpensive and at the same time compatible with large-area electronics manufacturing, are urgently required.

#### 1.2 Objectives and thesis layout

The key motivation and aim of this study is the development of new processing methodologies and their implementation in large-area electronics and ultimately the IoT. In order to achieve this goal, a modified photo-lithographic patterning method namely Interlayer Lithography (IL) was firstly explored. After establishing the basic process steps of IL, other processing steps such as spin casting of the photoresist and light exposure conditions, were optimized for the manufacturing of reproducible metal patterns. Following, a nonphotolithographic method called Adhesion Lithography (a-Lith) was explored for the development of different metal patterns with unique features. These activities are summarized in Chapter 2. In Chapter 3, the new patterning processes were applied for the development of high performance solution-processed self-aligned gate (SAG) thin-film transistors (TFTs). Solution-processed metal oxides semiconductors, namely zinc oxide and indium oxides were combined with high capacitance (high-k) dielectric materials such as ion-gel dielectrics and hybrid metal oxide/self-assembled monolayer (SAM) dielectric system to produce low operating voltage TFTs. Fabrication of SAG TFT structure was also attempted via a-Lith in combination with various passive and active materials. Chapter 4 is the last experimental chapter and discusses the development of organic ferroelectric memory device using the pre-

#### **1. Introduction**

patterned metal electrode nanogap structures developed via a-Lith. Because of their unique nanogap electrode architecture, the devices are able to operate as non-volatile tunnel junction memories rather than conventional ferroelectric capacitors i.e. often seen in devices with nano-gaps >>10 nm. The measured current-voltage characteristics were analysed within the framework of various carrier transport mechanisms, and key conclusions were drawn. Finally, Chapter 5 provides a summary of the work and future outlook.

## **CHAPTER 2**

# Background

#### 2.1 Lithography

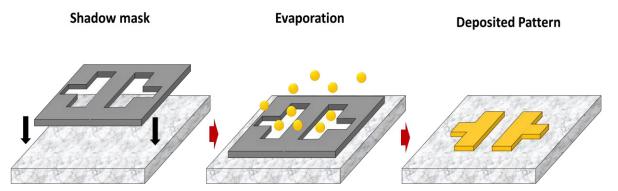

A variety of patterning methods have been developed within the microelectronics industry for the fabrication of electrode and device nano/microstructures. Among these methods shadow mask lithography is the simplest process. The latter relies on attaching the mask directly on the substrate and depositing the materials though the mask followed by removal of the mask from the substrate (Figure 2.1.1).<sup>38–40</sup> Although, shadow masking suffers from a lot of limitations such as low resolution, alignment inaccuracy and shadow effects, it is widely used in organic electronics because of its simplicity. Additionally, no solvents are involved during patterning, unlike photolithographic methods, hence avoiding issues related to the orthogonalilty of solvents used.<sup>41–43</sup>

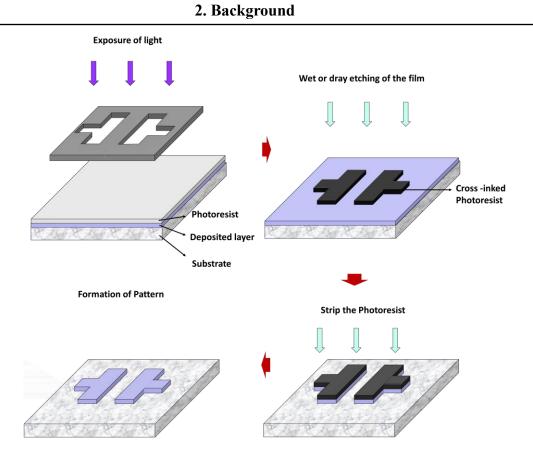

Compared to shadow mask, photolithography process consists of several steps.<sup>44–46</sup> Firstly, the pattern is transferred to light-sensitive materials called the *photoresist* (PR) by exposure to light. Next, the deposited layer is etched by wet or dry etching methods using the PR as a protective film. Finally, the residual PR is removed with a liquid resist stripper. The process is illustrated in Figure 2.1.2.

Fig.2.1.1. Schematic process diagrams of shadow mask lithography.

There are two kinds of photoresist; one is a positive-tone PR and the other a negative-tone PR. A photoresist is classed as a positive tone if it becomes more soluble to the developer liquid when exposed to light. Common positive-tone photoresists are based on mixtures of diazonaphthoquinone (DNQ) and novolac resin i.e. a phenol formaldehyde resin. On the other hand, if the photoresist is cross-linked by the exposure of light and becomes

insoluble to the developer, it is classed as a negative tone photoresist. In a negative tone photoresist, cross-linking agents in the PR are activated through exposure to light. The polymers are then cross-linked by a baking step, referred to as a post exposure bake (PEB). Hence, the PR becomes resistant to the developer and the patterned area is obtained. The process parameter of the PEB step such as temperature and time is crucial for the adhesion and resolution of a negative tone PR since the pattern is formed though the cross-linking process. A very common negative photoresist is the epoxy-based photoresist *SU-8*, from *Microchem* and this photoresist was used for IL here. <sup>47,48</sup>

In order to transfer the pattern to the PR layers, the layer is required to be exposed to suitable light. The basic principle of an exposure system is to focus the incoherent and uncollimated light from the source into a uniform and collimated beam on the substrate. Thus, the system is classified by the methods of focusing and irradiating. In the case of a contact system, which is the most primitive exposure system, one lens is used for focusing the light and the photo mask is attached to the substrate. During this step there is a probability of damaging the surface and the mask due to direct attachment of the two. Despite this risk however the contact method can deliver very high resolution patterning. A proximity system uses the same systems as a contact printing, but the mask does not make contact with the substrate. Because of this, the resolution limit of a proximity printing is not as high as the contact printing, so the method is often used for low resolution applications. A projection system system uses a multi lens system and is operated in scan and repeat mode. Such systems are widely used in large-area electronics manufacturing. Figure 2.1.3 shows schematics of the contact, proximity and projection systems.<sup>44</sup>

The minimum feature size, F, of a device produced by photoresists is dependent on the wave length used during exposure and expressed as:

$$F = 0.5 \quad \frac{\lambda}{NA} \tag{2.1}$$

where NA is the numerical aperture of the lens and  $\lambda$  is the wavelength of the light used. Thus higher definition patterns can be obtained by using light sources with shorter wavelength.

Fig.2.1.2. Schematic diagrams of photolithography based on the negative photoresist.

Fig.2.1.3. Schematic diagrams of exposure systems. (a) Contact system. (b) Proximity system.(c) Projection system.

#### 2.2 Device physics of thin-film transistors

A thin-film transistor (TFT) consists of three main components: a semiconductor, an insulator and three metal electrodes.<sup>77–80</sup> The semiconductor is isolated from the metal *gate* (G) electrode by the insulator. Two additional metal electrodes, namely *the source* (S) and *the drain* (D) are in contact with semiconductor. The distance between the S and D electrodes is the so-called channel length (L) while the length of the S-D electrodes defines the so-called channel width (W). Figure 2.2.1 shows several different TFT architectures according to the location of electrodes, an insulator and a semiconductor: (a) bottom-gate bottom-contact, (b) bottom-gate top-contact, (c) top-gate bottom-contact, and (d) top-gate/top-contact.<sup>79</sup> Despite the dramatic differences between the various TFT architectures, their operation is governed by exactly the same principles because charges accumulate at the semiconducting layer near the dielectric layer when biased thorough the gate electrode.

Fig.2.2.1. Schematic representations of field-effect transistor architectures. (a) bottom-gate top-contact. (b) bottom-gate bottom-contact. (c) top-gate bottom-contact. (d) top-gate top-contact.

The amount of charge will depend on the dielectric's properties and its geometry and the electrical potential applied. Under suitable conditions a conducting layer of mobile charge carriers, i.e. the conducting channel, is formed in the semiconductor/dielectric interface. Electrons or holes enter the channel from the source and leave at the drain if a voltage is applied also between the source and drain. In this way, the conductance of the channel (i.e. the amount of current) is modulated by the electric field applied at the gate terminal. The ability to modulate large currents through the application of electrostatic gate fields enables use of the TFT as low-power switches in numerous electronic applications.

The current equation for the TFT at low drain-source voltages,  $V_D$ ,  $(V_D \ll V_G - V_T)$  is described by the time-dependant model, often called *the charge-control model*.<sup>77–80</sup> The

threshold voltage,  $V_T$  is defined as the gate voltage at which current between the source and drain terminals starts to flow. The drain-source current  $I_D$  is represented by Equation 2.2, which is related to the total charge in the channel  $Q_N$  by the transit time  $T_{tr}$ . Assuming the current is dominated by a drift flow and the charge per unit area  $Q_n$  regarded as constant with the channel dimension WL, the transit time becomes the channel length divided by the drift velocity of the carriers. The drift velocity can be expressed as  $v_d = -\mu_n (V_D - V_S) / L = -\mu_n V_{DS} / L$ . Therefore, the drain current at low drain voltages, Equation 2.5, is obtained by substituting Equations 2.3 and 2.4 into Equation 2.2. As a result, for  $V_D \ll V_G - V_T$ , the drain current is expected to vary linearly with the drain-source voltage  $V_{DS}^{77}$ :

$$I_D = \frac{-Q_N}{T_{tr}} \tag{2.2}$$

$$T_{tr} = \frac{L^2}{\mu_n V_{DS}} \tag{2.3}$$

$$Q_N = Q_n WL = C_i \left[ V_G - V_T \right] WL$$

(2.4)

$$I_{D} = \mu_{n} C_{i} \frac{W}{L} [(V_{G} - V_{T}) V_{DS}]$$

(2.5)

However, if the drain voltage increases, the analysis becomes invalid since the charge per unit area  $Q_n$  is affected by the drain-source voltage and becomes variable. The square-law model based on the gradual-channel approximation considers this variability and describes the behaviour using a differential equation.<sup>77</sup> According to this approximation, the distribution of the induced charge,  $Q_n$ , can be expressed linearly with channel voltage  $V_C(y)$ [Equation 2.6]. Additionally, assuming that drain current only flows along the channel length direction and the channel length is longer than the depletion region at the drain, the incremental channel voltage,  $dV_C$ , can be expressed as the product of the drain-source current and incremental resistance dR [Equation 2.7].

$$Q_n = C_i \left[ V_G - V_T - (V_C - V_S) \right]$$

(2.6)

$$dV_C = I_D dR = -\frac{I_D dy}{W \mu_n Q_n(y)}$$

(2.7)

Then the drain current is obtained by integrating from the source to the drain where  $V_{DS}$  is equal to  $V_D$ -  $V_S$  [Equations of 2.8 and 2.9]:

$$I_{D} = \frac{-\mu_{n}W}{L} \int_{V_{s}}^{V_{D}} Q_{n}(V_{C}) dV_{C}$$

(2.8)

$$I_{D} = \mu_{n} C_{i} \frac{W}{L} \left[ \left( V_{G} - V_{T} \right) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

(2.9)

Equations 2.8 and 2.9 describe the evolution of channel current with drain voltage in the so-called linear regime. If the drain voltage  $V_{DS} > V_G - V_T$ , the induced charge becomes negative which is physically unreasonable. In that condition, the drain current starts to pinch off at the end of the channel, which means the end of channel is no longer at y = L but rather at y = L' (where L' is smaller than L). Thus the voltage at which  $Q_n \rightarrow 0$  is  $V_{DSAT} = V_G - V_T + V_S$  and the drain current is calculated by applying this relation of  $V_{DSAT}$  into the Equation 2.9 and expressed as:

$$I_{Dsat} = \mu_n C_i \; \frac{W}{2L} \quad (V_G - V_T)^2 \tag{2.10}$$

The drain current now becomes independent of the drain voltage, in other words it saturates. This condition, i.e.  $V_D \ge V_G - V_T$ , is known as the saturation regime.

Fig.2.2.2. Cross-sectional view of a bottom-gate, top-contact staggered thin-film transistor.

Typical transfer ( $I_D$  versus  $V_G$ ) and an output ( $I_D$  versus  $V_D$ ) curves measured for an ion-gel gated transistor is shown in Figure 2.2.3. Several important parameters can be extracted from these characteristics. From the transfer curve, the on/off ratio can be deduced by comparing the on and off currents and the hysteresis characteristics is also investigated by comparing the current loops between forward (off to on) and reverse (on to off) sweeps. In addition, the threshold voltages can be identified from the plot of  $\sqrt{I_D}$  versus  $V_G$ , which should be linear in the saturation regime. The equation is expressed simply by modifying Equation 2.11 and is given as:

$$\sqrt{I_{Dsat}} = \sqrt{\mu_n C_i \frac{W}{2L}} \quad (V_G - V_T) \tag{2.11}$$

The value of carrier mobility can also be deduced from both the linear and saturation regimes using Equations 2.5 and 2.10, respectively:

$$\mu_{LIN} = \frac{1}{C_i V_D} \frac{L}{W} \frac{\partial I_D}{\partial V_G}$$

(2.12)

$$\mu_{SAT} = \frac{2}{C_i} \frac{L}{W} \left( \frac{\partial \sqrt{I_D}}{\partial V_G} \right)^2$$

(2.13)

In general, the performance of the transistor is evaluated by the magnitude of the charge carrier mobility, the on/off channel current ratio, the threshold voltage (the closer to 0 V, the better) and the operating hysteresis (measured between forward and reverse  $V_G$  sweeps). Here, these values will also be used as the main figures of merit for investigating the performance characteristics of various TFTs developed.

Fig.2.2.3. (a) Linear ( $V_D = 0.1 \text{ V}$ ) and saturated ( $V_D = 1.0 \text{ V}$ ) transfer characteristics of a top-gate, top-contact TFT with channel width W =1000 µm and channel length L = 100 µm, fabricated with poly 3-hexylthiophene (P3HT) films on ion-gel dielectric. (b) Output characteristics of the ion-gel gated poly 3-hexylthiophene (P3HT) transistor.

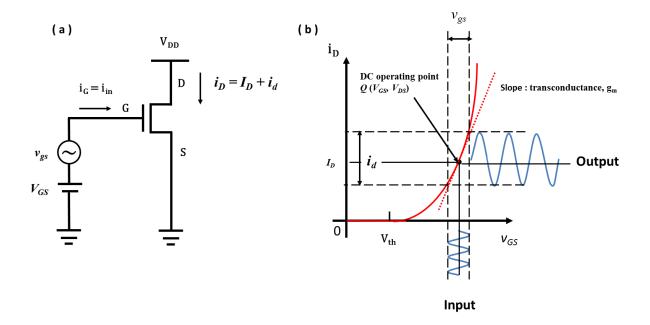

One of the most important figures of merits for any transistor technology is the *cut-off frequency*,  $f_T$ , of operation. This is because  $f_T$  determines the maximum switching speed that the unit device (i.e. the transistor) can be operated and used for designing the logic circuitry. In MOSFET technology,  $f_T$  is derived from the small-signal model of the device and experimentally determined by measuring the frequency at which the current-gain of the device decreases to one.<sup>77</sup> In this section, the small-signal model of a MOSFET was modified for a thin-film transistor and the cut-off frequency of the device is introduced. When a DC and a small-signal AC bias are applied to the transistor through the gate electrode, each voltage and current in the circuit has both a DC and small-signal component as illustrated in the Figure 2.2.4. Because the small-signal is considered to be a small perturbation, hence, non-linear components become linear, where superposition can be applied to determine the circuit response. On the basis of this assumption, the total gate-source voltage and total drain-source current can be written as:

$$v_{GS} = V_{GS} + v_{gs}, \ i_D = I_D + i_d \tag{2.14}$$

where small letters with large subscripts are total responses, large letters with large subscripts denote DC components and small letters with small subscripts represent the small-signal response.

Figure.2.2.4. (a) Schematic of the transistors and the various voltage and current components.(b) DC and small-signal AC components of the transistors.

The relationship of the increment in drain current  $(i_d)$  due to an increment in gatesource voltage  $(v_{gs})$  or drain-source voltage  $(v_{ds})$  can be obtained from the first terms of Taylor expansion of the total drain current around the DC operating point,  $Q(V_{GS}, V_{DS})$  and is expressed as:

$$i_D \left( V_{GS} + v_{gs}, V_{DS} + v_{ds} \right) = i_D \left( V_{GS}, V_{DS} \right) + \frac{\partial i_D}{\partial V_{GS}} \Big|_Q \left( v_{gs} \right) + \frac{\partial i_D}{\partial V_{DS}} \Big|_Q \left( v_{ds} \right)$$

(2.15)

where  $i_D(V_{GS}, V_{DS})$  becomes  $I_D(V_{GS}, V_{DS})$  because it is a DC component. Therefore, the small-signal response of circuit can be written as:

$$i_d \left( v_{gs}, v_{ds} \right) = \left. \frac{\partial i_D}{\partial V_{GS}} \right|_Q \left( v_{gs} \right) + \left. \frac{\partial i_D}{\partial V_{DS}} \right|_Q \left( v_{ds} \right) = g_m v_{gs} + g_0 v_{ds}$$

(2.16)

The first term in Equation 2.16, the small-signal current due to  $v_{gs}$ , is defined as the **transconductance**,  $g_m$  and the second term relating to  $v_{ds}$  as the output conductance,  $g_o (1/r_0)$ .

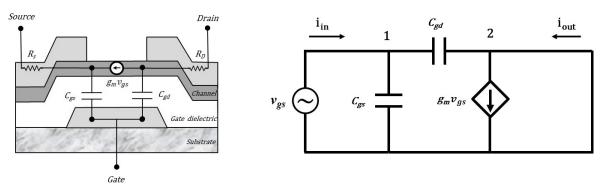

Figure.2.2.5.(a) Device Schematic illustration of a thin-film transistor. (b) Simplified small-signal model of a thin-film transistor.

As shown in the simplified small-signal model of a thin-film transistor in Figure 2.2.5, the input  $(i_{in})$  and output  $(i_{out})$  currents of the circuit can be extracted when considering the circuit at nodes 1 and 2 using:

node 1 :

$$i_{in} - v_{gs} j \omega C_{gs} - v_{gs} j \omega C_{gd} = 0 \rightarrow i_{in} = v_{gs} j \omega (C_{gs} + C_{gd})$$

(2.17 a)

node 2 :

$$i_{out}$$

-  $g_m v_{gs} + v_{gs} j \omega C_{gd} = 0 \rightarrow i_{out} = v_{gs} (g_m - j \omega C_{gd})$  (2.17 b)

where  $C_{gs}$  is the gate-source capacitance,  $C_{gd}$  is the gate-drain capacitance and  $\omega$  is the angular frequency. Then, the current gain  $(h_{21})$  and its magnitude can be written as:

$$h_{21} = \frac{i_{out}}{i_{in}} = \frac{g_m - j\omega C_{gd}}{j\omega (C_{gs} + C_{gd})}$$

(2.18 a)

$$|h_{21}| = \frac{\sqrt{g_m^2 + \omega^2 C_{gd}^2}}{\omega(C_{gs} + C_{gd})}$$

(2.18 b)

According to the operating frequency, the magnitude can be expressed in a simpler form as:

$$|h_{21}| \approx \frac{g_m}{\omega(C_{gs} + C_{gd})}$$

at low frequency ( $\omega \ll g_m / C_{gd}$ ) (2.19 a)

$$|h_{21}| \approx \frac{C_{gd}}{(C_{gs} + C_{gd})}$$

at high frequency ( $\omega \gg g_m / C_{gd}$ ) (2.19 b)

When the magnitude of  $h_{21}$  becomes unity, the frequency can be written as.

$$\frac{g_m}{\omega_T (C_{gs} + C_{gd})} = 1$$

(2.20 a)

$$\omega_T = 2\pi f_T = \frac{g_m}{(C_{gs} + C_{gd})}$$

(2.21 b)

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})}$$

(2.22 C)

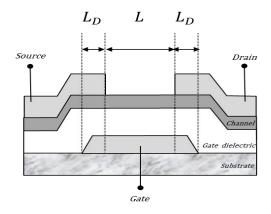

The higher the value of  $f_T$  is, the faster the thin film transistor can operate. Furthermore, the cut-off frequency can be physically interpreted when combined with the capacitances ( $C_{gs}$ ,  $C_{gd}$ ) and its transconductance. The capacitances contain not only intrinsic elements but also parasitic elements due to the overlap of the gate and the source and drain electrodes ( $L_D$ ) as shown in Figure 2.2.6. In the linear regime, the channel is considered to be uniform from the source and drain, so the  $C_{gs}$  and  $C_{gd}$  is a same value as  $1/2C_{ox}WL + C_{ox}WL_D$ . In the saturation regime, the channel starts to be pinched off near the drain electrode and it is not assumed to be uniform. Thus, the  $C_{gs}$  becomes approximately  $2/3C_{ox}WL + C_{ox}WL_D$ , while  $C_{gd}$  contains only the remaining parasitic capacitance component of  $C_{ox}WL_D$ . The transconductance is found by differentiating the drain current with respect to  $V_{GS}$  and it can be expressed as  $\mu_n C_{OX}(W/L)V_{DS}$  in the linear regime and  $\mu_n C_{OX}(W/L)(V_{gs} - V_{th})$  in the saturation regime, respectively. Therefore, the cut-off frequency in the linear and saturation regime can be written as:

$$f_T = \frac{\mu_n V_{DS}}{2\pi L^2 (1 + 2L_D/L)} \quad \text{linear regime}$$

(2.23 a)

$$f_T = \frac{3\,\mu_n(V_{gs} - V_{th})}{4\pi L^2\,(1 + 3L_D/L)} \quad \text{saturation regime}$$

(2.23 b)

From Equation 2.23 it is evident that  $f_T$  can be increased by: (i) reducing the channel length (L) of the transistor, (ii) reducing the electrode overlap length ( $L_D$ ), (iii) increasing the charge carrier mobility of the semiconductor. In the next section, significant effort was focused on minimizing  $L_D$  by fabricating self-aligned gate transistors developed via new-processing method, adhesion lithography.

Figur.2.2.6. Thin-film transistor schematic showing the parasitic overlaps between the various electrode terminals.

#### 2.3 Ferroelectricity in solid-state materials

In an isotropic dielectric material, the bound charge is slightly separated by an applied electric field, **E**. This partial charge separation induces a local electric dipole moment in the material, and the vector sum of these dipole moments per unit volume is defined as polarization, **P**. This polarization is dependent on the material property and can be expressed as:

$$\mathbf{P} = \varepsilon_0 \chi \boldsymbol{E} \tag{2.24}$$

where  $\varepsilon_0$  is the vacuum permittivity and  $\chi$  is the responsivity to an applied field, susceptibility. Then the total polarization can be expressed by combining the polarization of dielectric material with free space effect. This physical quantity is called as the electric displacement field, given by the equation:

$$\mathbf{D} = \varepsilon_0 \mathbf{E} + \mathbf{P} \tag{2.25}$$

However, there are specific dielectric materials that show spontaneous polarization due to the incongruity of crystal structure. In the crystal structure of barium titanate, for example, the centre of positive charge does not correspond with the centre of negative charge. This causes the dielectric material exhibits inherent, spontaneous polarization. This polarization can be switched by a specific applied electric field in the opposite direction, coercive field. This directed polarization is sustained even in the absence of an external electric field, yielding a hysteresis loop. This bistable and hysteric characteristic is called ferroelectricity<sup>120,121</sup>. When ferroelectric materials are heated above a certain temperature, ferroelectricity disappears. The temperature at which this phenomenon occurs is the so-called Curie temperature and is attributed to thermal disordering of the crystal structure.

Ferroelectricity has been found in numerous materials and includes inorganics such as  $SrBi_2Ta_2O_9$  (SBT),  $Pb[Zr_xTi_{1-x}]O_3$  (PZT) as well as organics such as ferroelectric nylons, a polyvinylidene fluoride, P(VDF) and P(VDF) based copolymers. Representative ferroelectric materials and its properties are summarized in the table 2.1. Among these materials, the organic ferroelectric material, P(VDF-TrFE) will be further discussed due to its relatively high ferroelectricity and the potential for cost processing from solution phase.

|                               | Inorganic Based NVM                                                                                                | Organic Based NVM             |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Technology<br>Readiness Level | Already in Market                                                                                                  | Close to Market               |

| Material                      | SrBi <sub>2</sub> Ta <sub>2</sub> O <sub>9</sub> (SBT), Pb[Zr <sub>x</sub> Ti <sub>1-x</sub> ]O <sub>3</sub> (PZT) | Ferroelectric nylons , P(VDF) |

| Energy Efficient              | Excellent                                                                                                          | Low                           |

| Ec ( MV/m)                    | < 5                                                                                                                | > 50                          |

| Process<br>Temperature        | <b>&gt; 900</b> °C                                                                                                 | < 150 °C                      |

| Cost                          | Moderate                                                                                                           | Ultra low-cost attainable     |

Table.2.1. Representative ferroelectric materials and its properties.

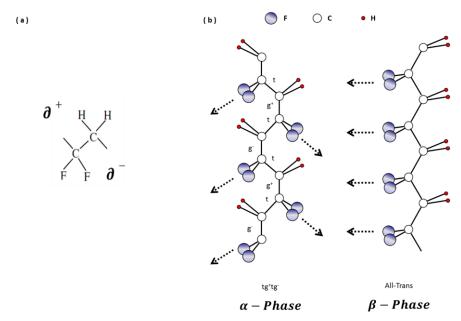

Polyvinylidene fluoride, P(VDF) is a linear fluorinated hydrocarbon polymer, based on the monomer CH<sub>2</sub>CF<sub>2</sub>. The dielectric properties of P(VDF) are significantly dependant on the molecular orientation of this monomer and its crystal structures<sup>122,123</sup>. The monomer itself shows polar characteristics because there is a difference in the electronegativity between the hydrogen and the fluorine atoms, which induces a dipole moment. During polymerization and crystallization, if the monomers are unaligned, the net polarization of the polymer becomes a neutralized state and there is no permanent electric dipole. This kind of P(VDF) such as transgauche TGT $\overline{G}$ ,  $\alpha$ -phase display paraelectricity. However, if the monomers are aligned such as the all-trans (TTTT)  $\beta$ -phase, the polymer crystal shows polar characteristics and this polarization can be switched according to the external electric field, hence manifested as ferroelectricity. The chemical structure of the monomer and the different crystal structures of P(VDF) are depicted in Figure 2.3.1.

The  $\beta$ -phase of P(VDF) is useful for applications such as a non-volatile memory devices and additional post-treatment is often required to obtain it. To this end, there are several methods one can employ to obtain the  $\beta$ -phase including: mechanical extension followed by electrical poling from the  $\alpha$ -phase, high pressure crystallization, ultra-fast cooling, addition of nucleating fillers such as BaTiO<sub>3</sub> and copolymerization with other

polymer such as trifluoroethylene, hexafluoropropene and chloride trifluoride ethylene <sup>124,122</sup>. Among these methods, the most well established method is copolymerization with trifluoroethylene, P(TrFE), resulting P(VDF-TrFE). The addition of the third fluoride in the TrFE enhances the  $\beta$ -phase formation due to a large steric hindrance. Additionally, the  $\beta$ -phase of P(VDF-TrFE) is easily processed directly from the solution states, thus P(VDF-TrFE) has been studied extensively.<sup>123,125</sup> Usually the molar ratios of VDF to TrFE are between 50:50 mol% and 80:20 mol%. A schematic chemical structure of P(VDF-TrFE), together with the ferroelectric behaviour of a capacitor under operation and its structure are illustrated in Figure 2.3.2.

Fig.2.3.1.(a) Chemical structure of the VDF monomer. (b) Crystal structures of P(VDF).

Fig.2.3.2.(a) Schematic chemical structure of P(VDF-TrFE). (b) Typical hysteresis loop of 200-nm-thickness of organic ferroelectric materials, P(VDF-TrFE). Device structures was 200 nm thick P(VDF-TrFE) MIM Capacitors.

One of main research directions in the field of P(VDF-TrFE) based memory capacitors is achieving low-voltage operation. When compared to inorganic ferroelectric materials and devices, organic ferroelectric devices require a relatively high operating voltage due to high coercive field (~ 50 MV/m). For example, the coercive field of  $Pb[Zr_xTi_{1-x}]O_3$ (PZT) is below 5 MV/m, which translates to an operating voltage of 1 V for a 200 nm-thick active layer. For an equivalent thickness P(VDF-TrFE) layer the operating voltage of the capacitor would have been 10 V i.e. five times higher. There have been numerous attempts to reduce the voltage operation of organic ferroelectric memories with relatively little success. The simplest way for achieving low-voltage operation is by decreasing the ferroelectric film thickness. Bune et al. showed that low voltage operation (< 1 V) was attainable with Langmuir-Blodgett (LB) deposited ultrathin film (~1 nm)<sup>119</sup>. Fujisaki et al. also reported that low-voltage operation with the film thickness of 65 nm by spin casting<sup>126</sup>. Kliem et al., however, experimentally figured out that the thinner the film is, the higher the coercive field becomes. This dependence was expressed in a power law given as  $Ec \sim d^{-\alpha}$ , where  $\alpha = 0.64$ and d is film thickness<sup>127</sup>. This dependency was attributed to the reduction in the crystallinity within the layer and the non-ferroelectric "dead" layer present on the aluminium electrodes. Naber et al. proposed that introducing of the organic conductive doped polymer PEDOT:PSS layer instead of aluminium suppressed this scaling effect and achieved an operation voltage of 5.2 V<sup>128</sup>. Recently, a noteworthy result was reported by Hu et al, which showed that low voltage operation of <0.8 V was achievable by confining the grain boundary of P(VDF-TrFE) films using nano imprint method (NIL)<sup>118</sup>.

An alternative approach for reducing the operating voltage of organic ferroelectric is by simplifying the device structure. Device layouts of 1 TFT with 1 Capacitor or 2 TFTs with 2 Capacitors is required when implementing the ferroelectric materials into memory devices<sup>125</sup>. However, if devices can be fabricated in a simpler form, may also provide significant advantages. For example, Asadi *el al.* developed non-volatile bistable resistive memory devices by blending P(VDF-TrFE) with semiconducting poly(3-hexylthiophene), P3HT<sup>129</sup>. Charge transport through the semiconducting phase could be controlled by external ferroelectric polarization of polymer. Similarly, Khan *el al.* reported that this blending method can be extended to n-type organic semiconductor, [6,6]-phenyl-C61-butyric acid methyl ester (PCBM)<sup>130</sup>. In addition, Breemen *el al.* developed similar organic blend system in a more controlled way by surface directed phase separation with patterned SAMs<sup>131</sup>. Moreover, the possibility of fabrication of array devices on plastic film in simpler forms of

1D or 1D1R was also demonstrated. These various research directions relevant to organic memory devices based on P(VDF-TrFE) are summarized in the Table 2.2.

|            | Low-voltage capacitors                                                    | Resistive memory                                                                                                                           |

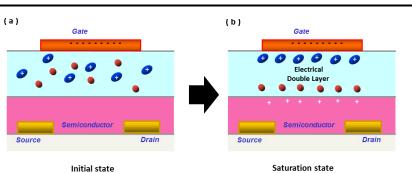

|------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|