## Development and Evaluation of Silicon Drift Chambers

bу

### John Anthony Ellison

.

#### A thesis submitted for the degree of Doctor of Philosophy of the University of London and Membership of the Diploma of Imperial College

February 1987

Imperial College London

#### ABSTRACT

This thesis presents results on silicon drift chambers, which are new detectors based on the idea of electrons drifting along a potential minimum in a fully depleted silicon wafer. Emphasis is placed on the following: (i) fabrication of the devices which was carried out at Micron Semiconductor Ltd., (ii) laboratory tests of the behaviour of the detectors, in particular their DC characteristics and their response to minimum ionising  $\beta$  particles and (iii) computer modelling of the potential distribution and motion of charge carriers within the detector.

#### ACKNOWLEDGEMENTS

I extend my thanks to all those people who have helped with my work over the last few years.

At Imperial College I would like to thank D.M. Websdale and S. Roe and particularly G. Hall for acting as my supervisor. I thank D.M. Binnie for allowing me to join the HEP group. I also acknowledge the efforts of the HEP electronics and mechanical workshops.

I thank S. Roe and G. Hall for performing the experimental measurements described in section 6.3.4 and particularly G. Hall who wrote and developed the computer simulation programs described in . chapter 6.

I gratefully acknowledge the part played in this project by A.D. Lucas and C.D. Wilburn and the staff of Micron Semiconductor Ltd., for allowing me the use of their facilities and for their efforts in producing some of the detectors used in this work.

I would also like to acknowledge the assistance of the Rutherford Appleton Laboratory Electron Beam Lithography Facility, especially J. Ayres and P. Sharp, in producing masks for detector fabrication.

I especially thank my parents for their continual love and support. Finally, loving thanks to Ann.

- 3 -

## CONTENTS

;

•

| ABSTRACT                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                             |

| <u>Chapter</u> page                                                                                                                                                                                                                                                                                          |

| I. INTRODUCTION                                                                                                                                                                                                                                                                                              |

| Applications of Semiconductor Detectors15Nuclear Physics15High Energy Physics16Other Uses of Silicon Detectors in High Energy Physics20Charge Coupled Devices20Silicon Detectors as Sampling Devices in Calorimeters21Silicon Photodiodes for Scintillator Readout21Present Status and Recent Developments22 |

| II. THEORY OF SILICON DETECTORS                                                                                                                                                                                                                                                                              |

| Band Theory of Solids27Conduction in Intrinsic and Extrinsic Silicon28The pn Junction32The Reverse Biased pn Junction37Contributions to the Leakage Current38Depletion Layer Capacitance43Silicon Microstrip Detectors45Silicon Drift Chambers47                                                             |

| III. FABRICATION TECHNIQUES FOR SILICON DETECTORS 55                                                                                                                                                                                                                                                         |

| Introduction                                                                                                                                                                                                                                                                                                 |

| Control of Oxide Charges                                                                                                                                                                                                                                                                                     |

- 4 -

| ιν.  | FABRICATION OF SILICON DRIFT CHAMBERS                                                                                                                                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Production of the Photolithographic Masks                                                                                                                                                                                                                                                                                                                                           |

|      | Photoprocessing of the $p^{\uparrow}$ Electrodes $\dots \dots \dots$                                                                                                                                                                                                                |

|      | Fabrication of the n Anode Strip85Annealing86Metallisation87Postmetallisation Annealing87Mounting and Wire Bonding88Detector Evaluation and Selection89                                                                                                                                                                                                                             |

| ۷.   | EXPERIMENTAL TESTS OF SILICON DRIFT CHAMBERS 91                                                                                                                                                                                                                                                                                                                                     |

|      | The Prototype Detectors91Results From the First Prototype SDCs92Leakage Currents93Capacitance Characteristics94Observation of Signals From β Particles101Pulse Heights and Noise103The Second Set of Prototype Detectors109Capacitance Measurements110Leakage Current and Noise114Observation of Drift Using a Collimated β Source115                                               |

| VI.  | ANALYSIS AND SIMULATION OF SILICON DRIFT<br>CHAMBERS                                                                                                                                                                                                                                                                                                                                |

|      | Introduction121Description of the Simulation Programs123Solution for Electrostatic Field and Potential123Electron Drift Paths125The Shape of the Output Signal126Results of the Simulations of SDCs128Modelling of the Output Signal132Effects of Diffusion of the Charge Cloud136Undulations in the Potential Minimum138Self-biasing of SDCs142Design of Silicon Drift Chambers147 |

| vii. | SUMMARY AND CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                             |

| REFE | RENCES                                                                                                                                                                                                                                                                                                                                                                              |

. .

# LIST OF TABLES

.

.

.

.

| Tab | ble                                                 |      |

|-----|-----------------------------------------------------|------|

|     |                                                     | bage |

| 1.  | Spatial resolutions of silicon microstrip detectors | . 24 |

| 2.  | Electrode dimensions and expected drift fields      | 148  |

# LIST OF FIGURES

•

# Figure

|      | pag                                                                   | <u>e</u> |

|------|-----------------------------------------------------------------------|----------|

| 1.   | Cross-section through a typical ion implanted detector 1              | 4        |

| 2.   | Energy level diagrams for solids                                      | 8        |

| 3.   | Intrinsic semiconductor at equilibrium                                | 0        |

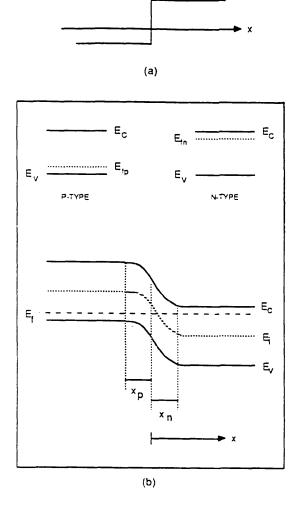

| 4.   | The step junction model                                               | 4        |

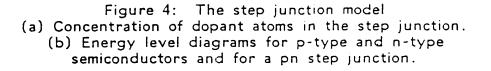

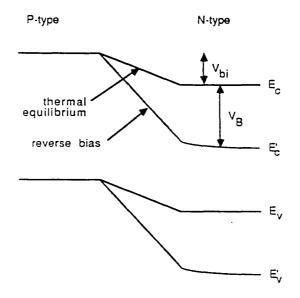

| 5.   | Properties of the step junction model                                 | 6        |

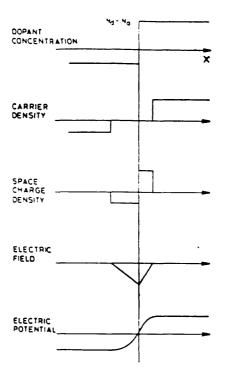

| 6.   | Energy level diagram for reverse bias                                 | 8        |

| 7.   | Band-bending due to oxide fixed charge 4                              | 1        |

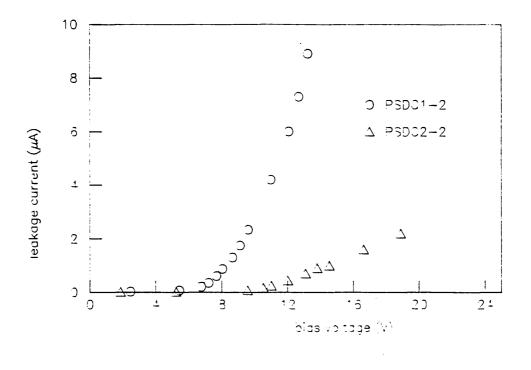

| 8.   | Leakage currents plotted against bias voltage 4                       | 3        |

| 9.   | Capacitance characteristics of detectors                              | 4        |

| .10. | Cross-section through a microstrip detector 4                         | 5        |

| 11.  | Electric field and potential in a microstrip detector 4               | 6        |

| 12.  | Depletion of a standard $p^{+}n$ junction detector 4                  | 8        |

| 13.  | Two standard $p^{+}n$ detectors in proximity $\ldots \ldots \ldots 4$ | 9        |

| 14.  | Depletion of a single n-type semiconductor                            | 0        |

| 15.  | Practical means of contacting the n-type silicon 5                    | 1        |

| 16.  | Potential of a fully depleted silicon wafer 5                         | 2        |

| 17.  | Practical realisation of a silicon drift chamber 5                    | 2        |

| 18.  | Potential within a silicon drift chamber                              | 4        |

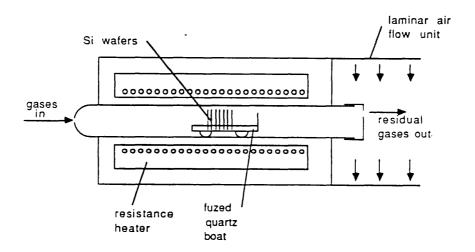

| 19.  | The oxidation furnace                                                 | 9        |

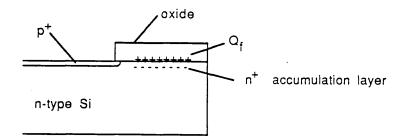

| 20.  | Effect of oxide fixed charge on a planar $p^{+}n$ detector 6          | 8        |

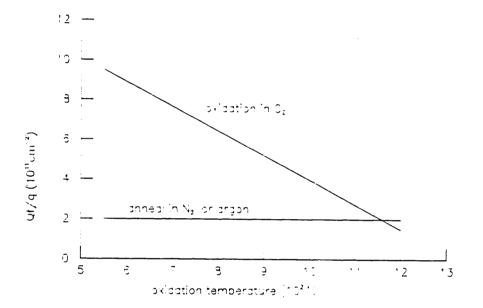

| 21.  | Oxide fixed charge density                                            | 9        |

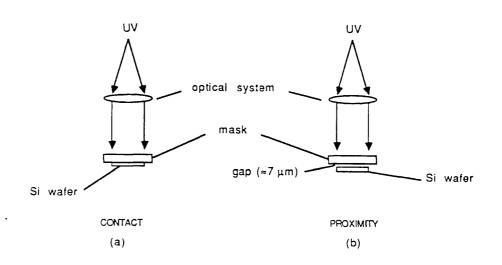

| : | 22. | Optical lithographic exposure techniques                                |

|---|-----|-------------------------------------------------------------------------|

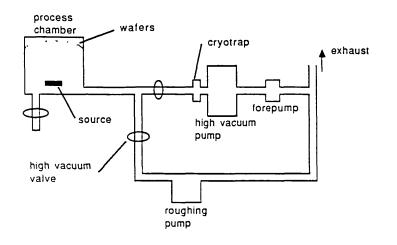

| : | 23. | Schematic representation of the high vacuum chamber 75                  |

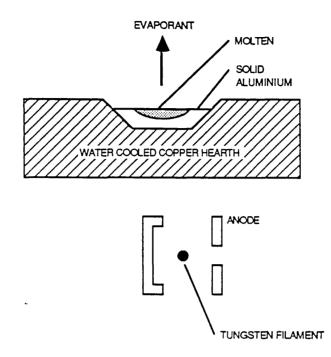

| : | 24. | The electron beam evaporation system                                    |

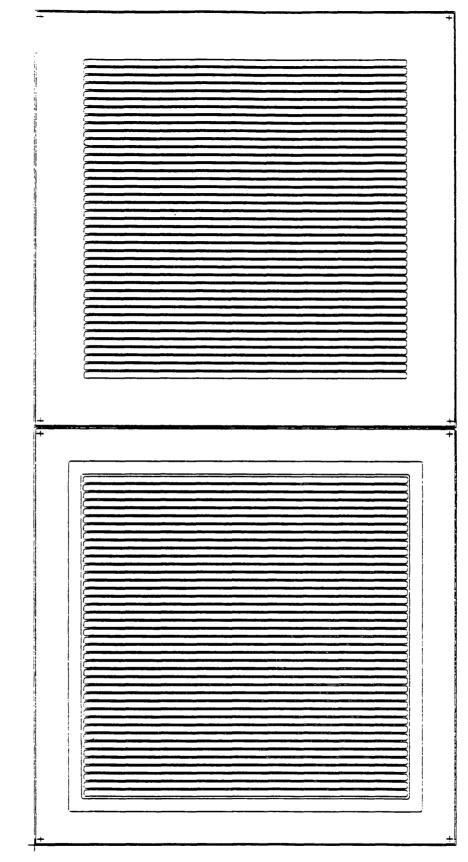

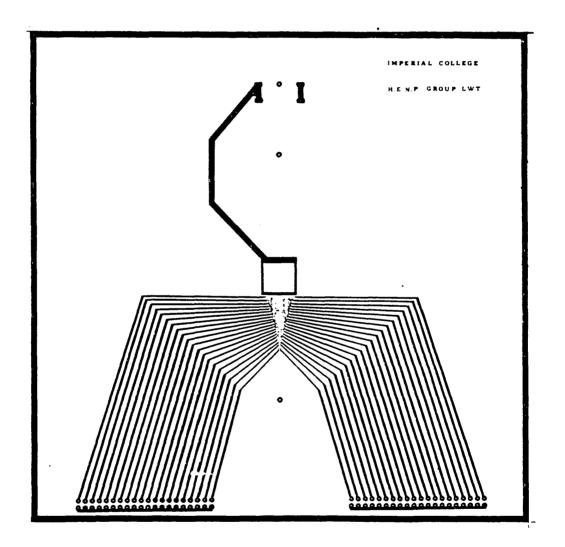

| : | 25. | Magnified diagram of a pair of SDCs                                     |

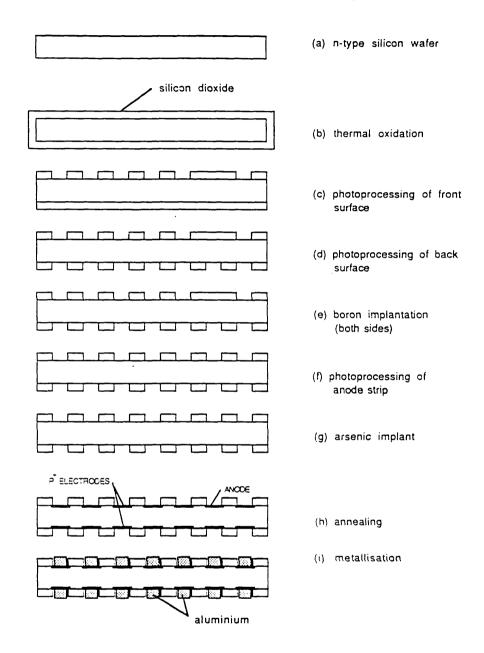

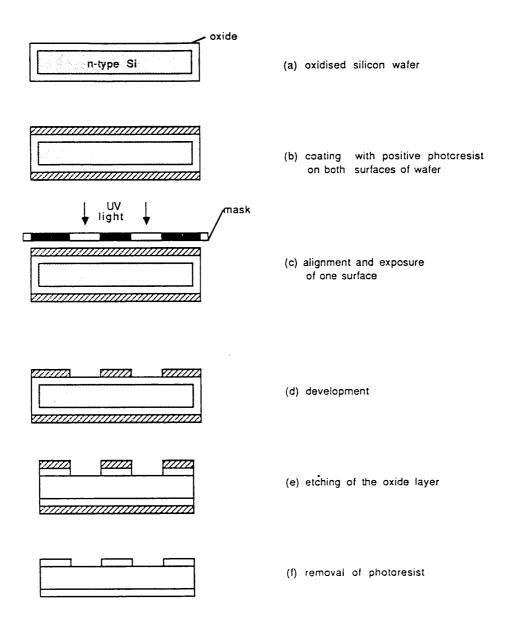

| · | 26. | Processing steps in the fabrication of the SDCs 81                      |

| : | 27. | Basic steps in the photolitography                                      |

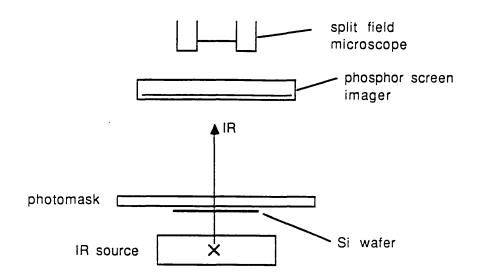

| : | 28. | The infra-red alignment system                                          |

| : | 29. | The fan out printed circuit board                                       |

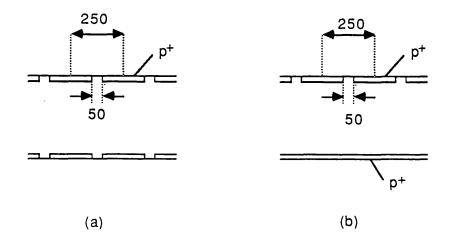

| : | 30. | Cross-sections of the SDC designs                                       |

| : | 31. | Leakage current of the single-area $p^+$ electrode $\ldots$ $\ldots$ 94 |

|   | 32. | Capacitance between all $p^+$ electrodes and the anode 95               |

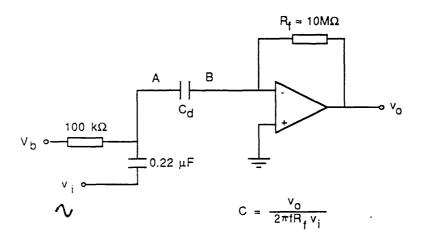

|   | 33. | Circuit used for capacitance measurements                               |

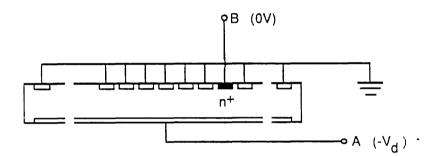

|   | 34. | Biasing arrangement for the CV measurements $\ldots$ $\ldots$ 97        |

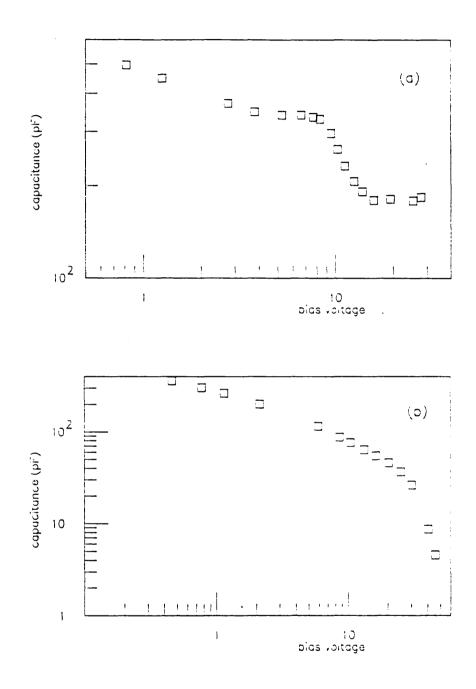

|   | 35. | Measurements of two capacitance characteristics                         |

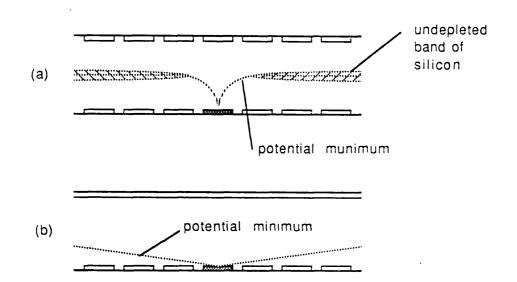

|   | 36. | Interpretation of the capacitance measurements                          |

|   | 37. | Biasing arrangement for CV measurement of figure 35 $\dots$ 100         |

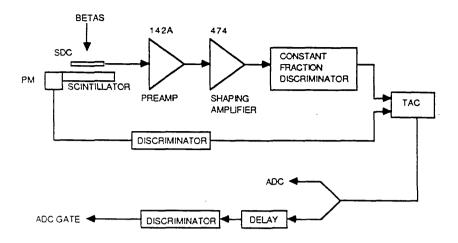

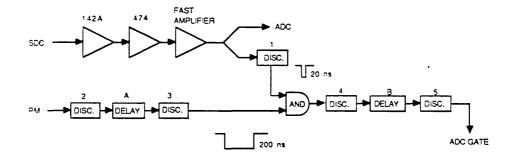

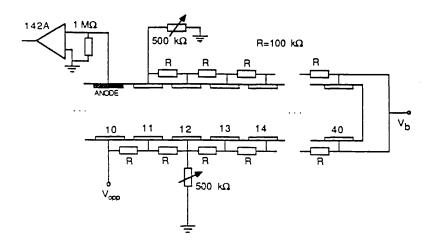

|   | 38. | Electronics chain used for timing measurements 102                      |

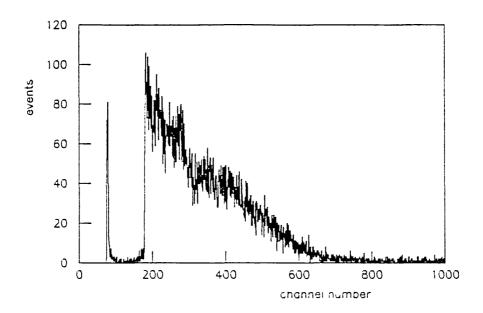

|   | 39. | Time spectrum of signals in the SDC                                     |

|   | 40. | Electronics chain used for pulse height measurements 103                |

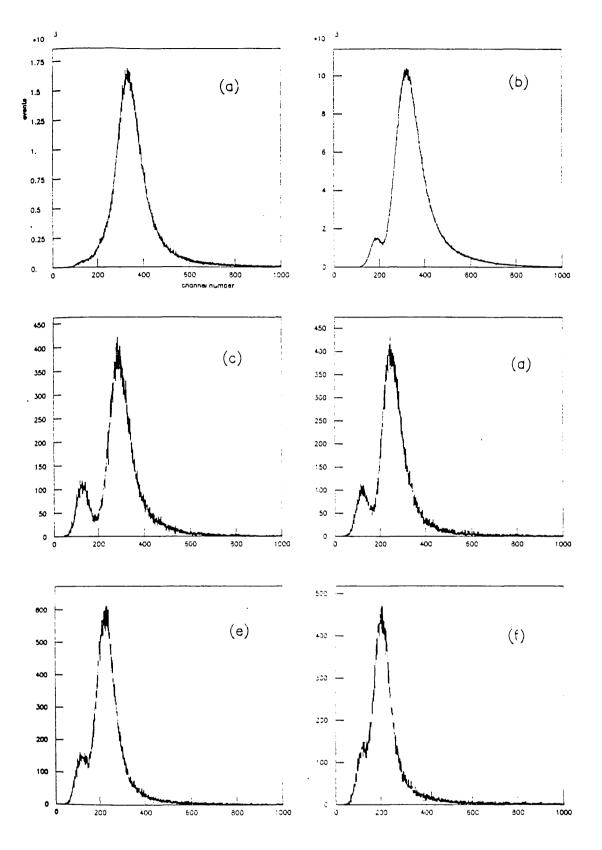

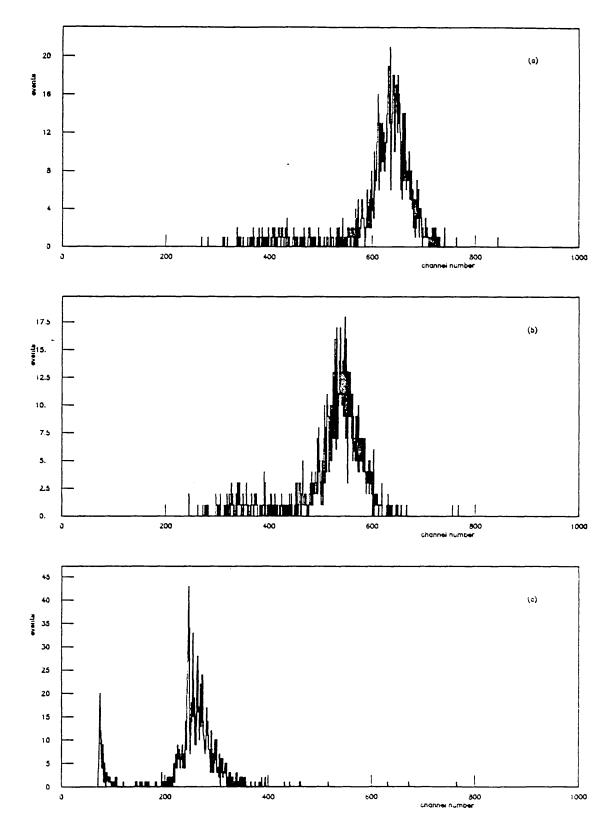

|   | 41. | Pulse height spectra for various time delays 105                        |

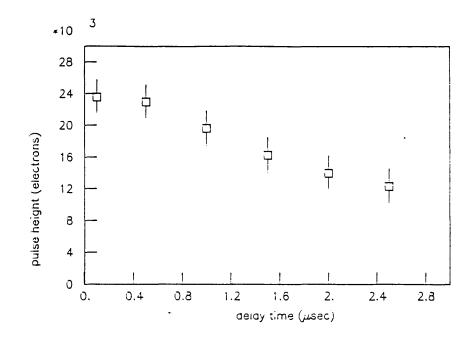

|   | 42. | Pulse height as a function of time delay                                |

|   | 43. | Undulations in the potential minimum                                    |

|   | 44. | Pockets of undepleted silicon within the detector 107                   |

|   | 45. | $Am^{241}$ & spectrum obtained with an SDC                              |

|   | 46. | Measurement of the capacitance characteristics                          |

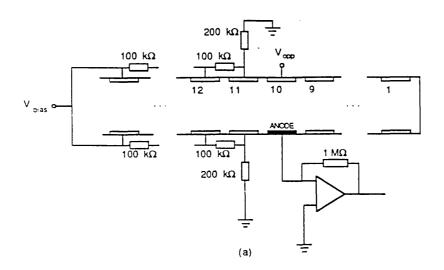

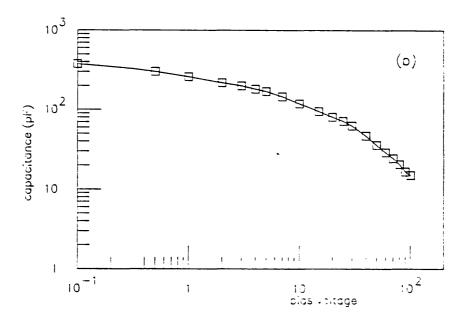

|   | 47. | CV characteristics of an SDC with applied drift field 113               |

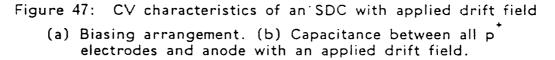

|   | 48. | Anode leakage current vs. bias voltage                                  |

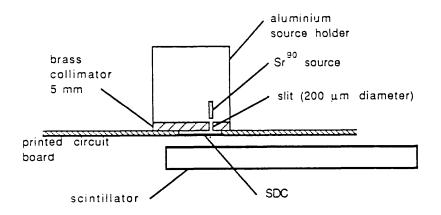

| 49. | Biasing arrangement for observation of drift action            | 116 |

|-----|----------------------------------------------------------------|-----|

| 50. | Experimental set up for observation of signals                 | 116 |

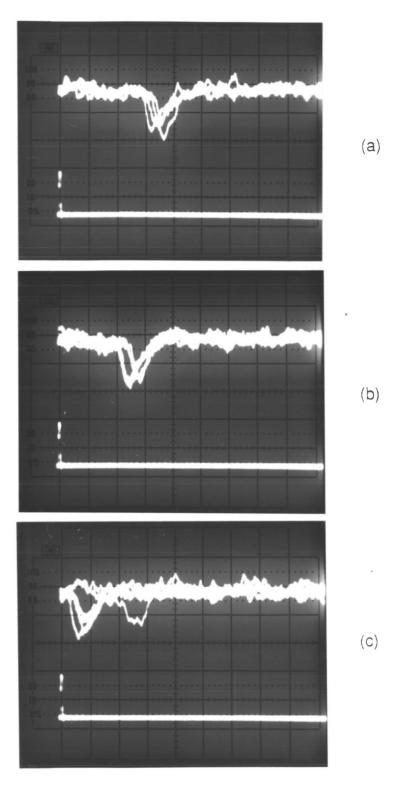

| 51. | Waveforms at the output of the shaping amplifier               | 118 |

| 52. | Time spectra of pulses in the SDC                              | 119 |

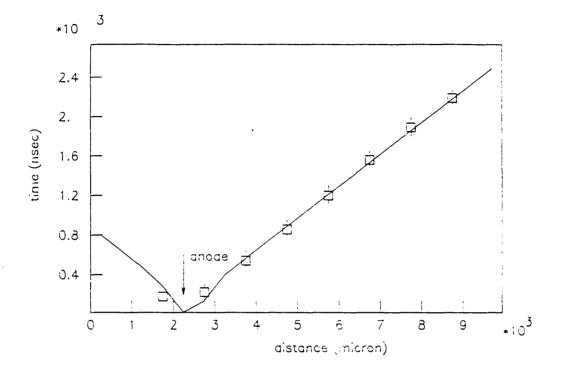

| 53. | Drift time as a function of drift distance                     | 120 |

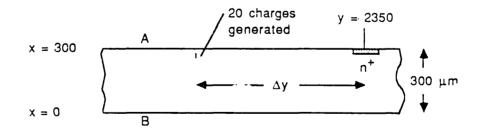

| 54. | Schematic representation of a silicon drift chamber            | 123 |

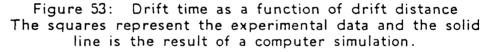

| 55. | Parameters used for the simulation of the SDC                  | 128 |

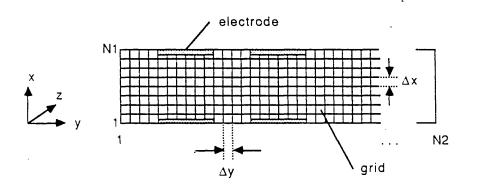

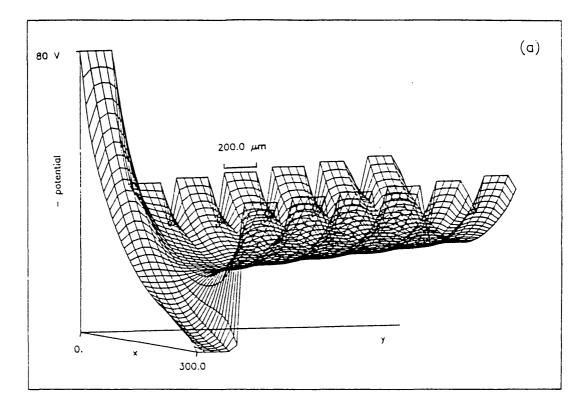

| 56. | Calculated potential distribution in the SDC                   | 130 |

| 57. | Drift paths of electrons in the SDC                            | 131 |

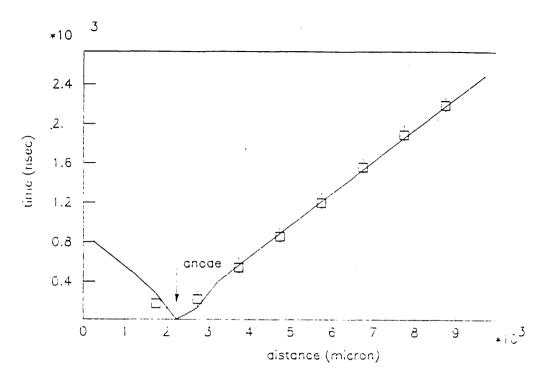

| 58. | Simulated distance-time relationship                           | 132 |

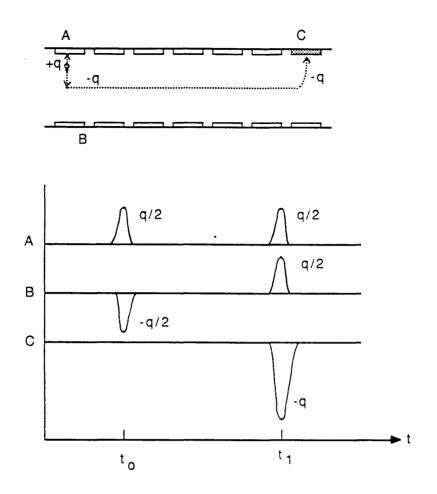

| 59. | Development of signals due to charge deposited in the SDC      | 134 |

| 60. | Generation of charge in the SDC                                | 134 |

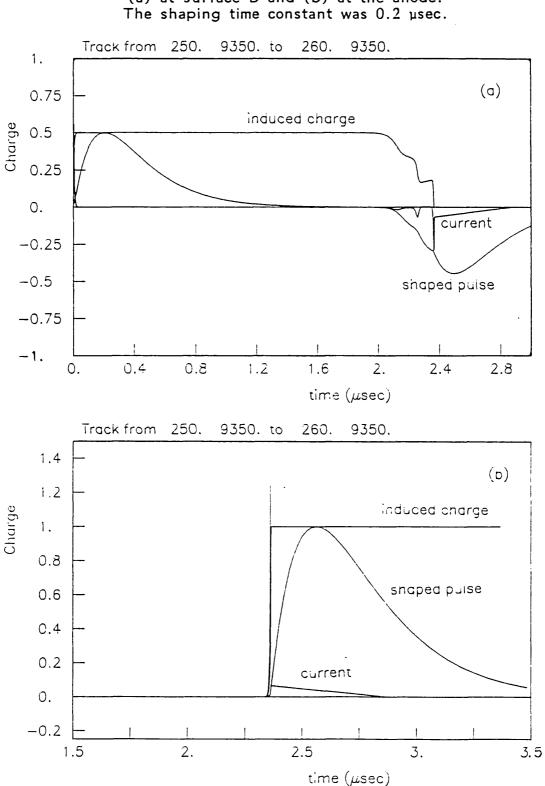

| 61. | Signals induced by charges for 7.0 mm drift distance           | 135 |

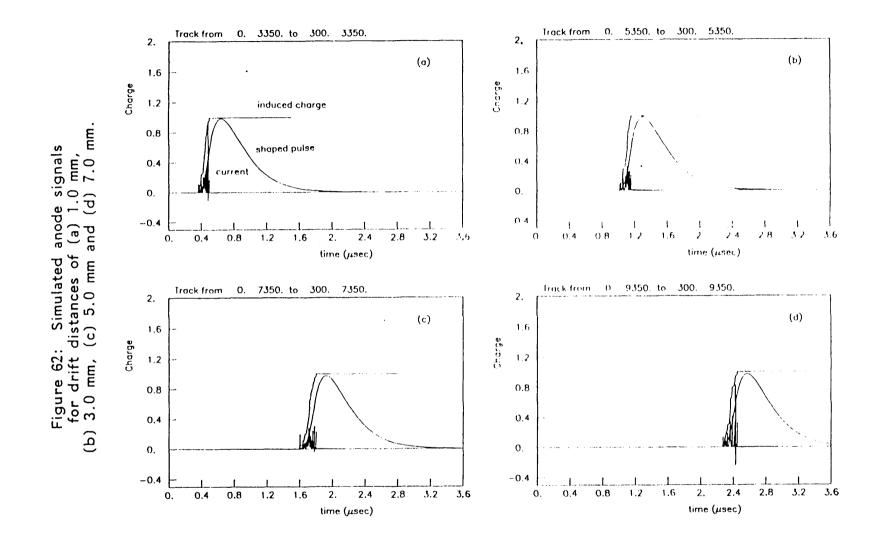

| 62. | Simulated anode signals                                        | 137 |

| 63. | Variation of the potential minimum                             | 139 |

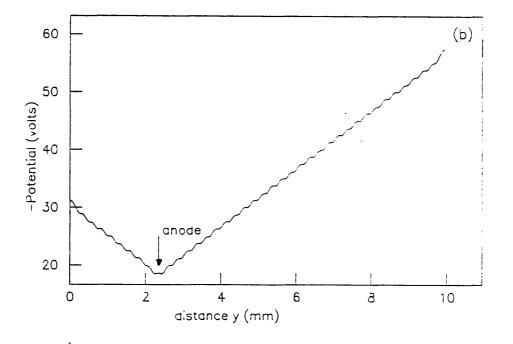

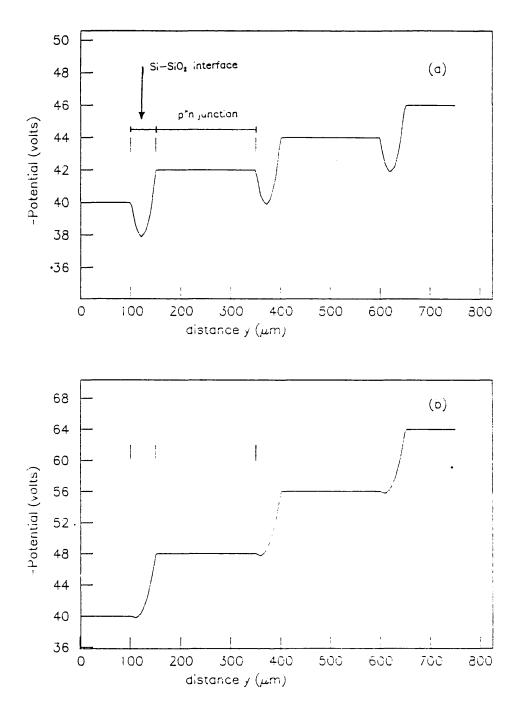

| 64. | Variation of the potential along the centre of the SDC $\ .$ . | 141 |

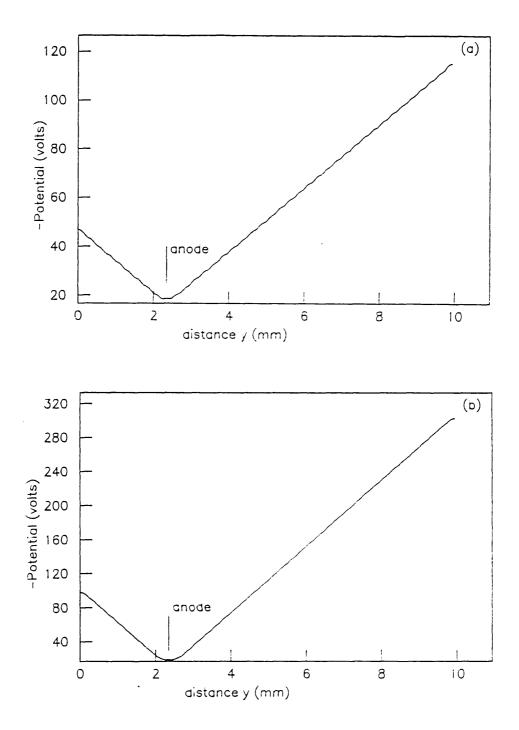

| 65. | Potential distribution along the surface of the SDC            | 144 |

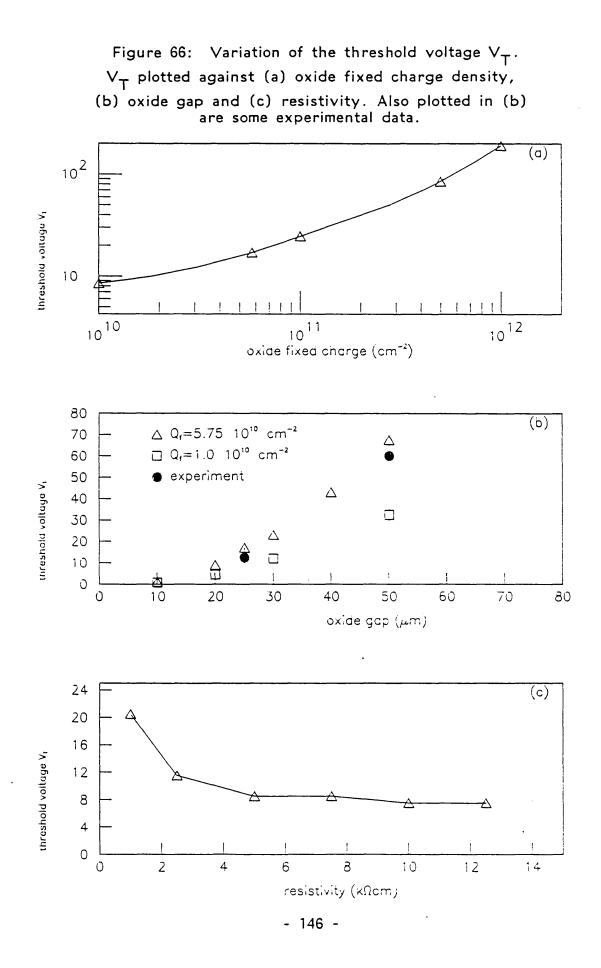

| 66. | Variation of the threshold voltage $V_T$                       | 146 |

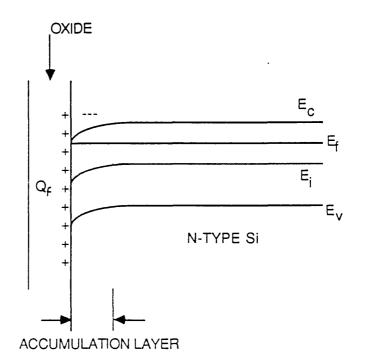

| 67. | Band-bending at the surface of an n-type semiconductor         | 147 |

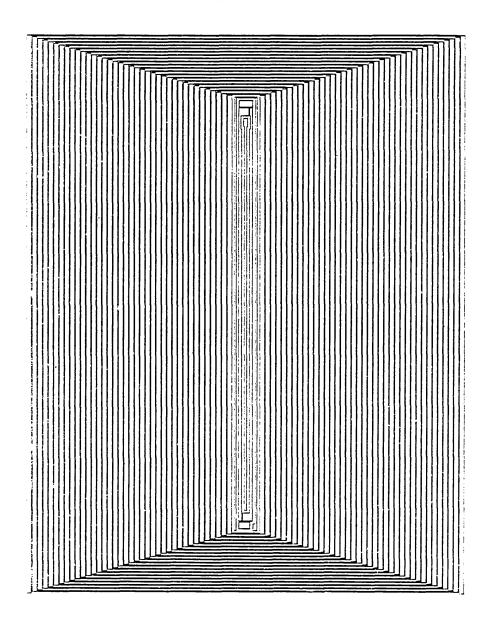

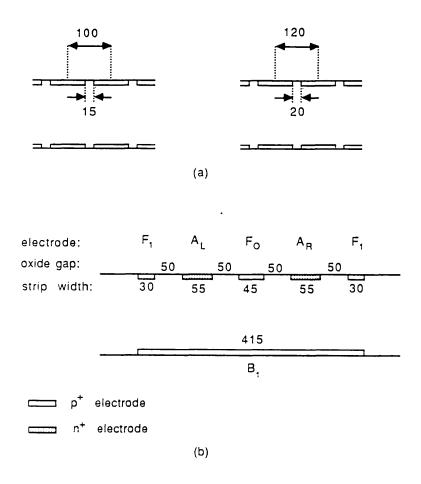

| 68. | Design of the front surface of the SDC                         | 149 |

| 69. | Cross-sectional view of the new SDC designs                    | 150 |

- 9 -

. •

.

.

.

#### Chapter I

#### INTRODUCTION

Silicon detectors have found widespread use in several branches of physics in the past and due to the recent advances in fabrication technology they are becoming increasingly more adaptable to many other uses. There are several desirable properties of silicon (and germanium) detectors which make them suitable for radiation detection applications. One obvious property is that silicon detectors are solid-state detectors and in some uses this is a great advantage. This means that for the detection of high energy particles the detector size can be kept small compared to an equivalent gas-filled detector because of the much higher density of silicon. Another great advantage of silicon as a detection medium is the relatively small amount of energy required to produce an electrical signal in the detector. The amount of energy needed to produce one elecron-hole pair in silicon is 3.62 eV. This can be compared to the energy required to produce one photoelectron in a plastic scintillator detector which is of the order of 1000 eV, or the energy needed to produce one electron-ion pair in a gas-filled detector which is approximately 30 eV. The fact that this energy is so low in silicon is a direct consequence of the fact that silicon is a semiconductor and therefore has a very narrow bandgap energy. This means that the number of carriers produced in a typical radiation interaction is much higher in silicon detectors and so means that the statistical fluctuation in the signal is very low.

Other advantages include the fast charge collection time (typically 20 nsec) and hence good timing characteristics and the compact size of the detector. The disadvantages of silicon detectors include their degradation due to radiation-induced damage and the limitation to small detection areas. All these points will be discussed in subsequent chapters.

In principle, one could construct a silicon detector by simply applying an electric field across a crystal of pure silicon. Then, radiation incident on the crystal would generate electron-hole pairs which would separate and be swept away to opposite contacts by the electric field. This would constitute a signal in the detector. However, in practice, the steady-state leakage currents observed in such a detector would be too high to allow detection of the incident particles or radiation. This leakage current can be reduced to desirable levels by using a crystal of silicon on which a diode is fabricated and, indeed, the diode has formed the basis of semiconductor detectors up to this day.

Because recent semiconductors utilise a pn junction, their fabrication technology has benefitted greatly from the microelectronics industry. One type of detector can be made using the diffusion process. A crystal of, say, n-type silicon is exposed to a gaseous dopant of p-type impurity (e.g. boron) in a diffusion furnace. This produces a thin region of p-type material near the surface and a pn junction is formed, typically 0.1-2.0 µm below the surface. The

- 11 -

opposite surface is treated similarly with an n-type dopant (e.g. phosphorus) to produce an ohmic contact. When a reverse bias voltage is applied (p-type negative with respect to n-type) to the detector a 'depletion region' (containing essentially no free charge carriers) extends from the p-type surface into the bulk of the detector. This depletion region, which increases in thickness as the bias voltage increases, constitutes the active volume of the detector. The limits on thickness are set by the breakdown voltage of the junction and is about 1-2 mm for high resistivity silicon.

A second type of detector is the surface barrier detector which is based on the rectifying junction produced when certian metals are in contact with a semiconductor. The physics of this structure was first described by Schottky's model of the metal-semiconductor contact [1]. Fabrication is achieved by first etching the surface and then evaporating a thin gold film onto this surface. The evaporation is usually carried out under conditions which promote slight oxidation of the surface. It has been shown that this oxide is important in the formation of the surface barrier. Surface barrier detectors have the advantage that they can be made with extremely thin dead windows but they are also particularly sensitive to surface contamination and damage which can dramatically degrade their performance.

Although these types of detectors were used for the detection of radiation it was realised that they suffered from several problems which limited the signal-to-noise ratio. A major problem is that such detectors are susceptible to changes in the surface conditions. The fact that the surface of a semiconductor can drastically affect the

- 12 -

properties of semiconductor devices will be discussed later, but, for example, the introduction of a large number of surface states by contamination or damage can lead to an increase in the leakage current of a silicon detector. Several methods were proposed to reduce this problem including hermetically sealed devices, edge protection using doped epoxies and the use of guard rings. However the most successful method and the one which is used in most modern detectors is oxide passivation in which the silicon surface is passivated by a thermally grown oxide. This is used in conjunction with the so-called planar technology in which the oxide also serves as a mask against impurities thereby defining the pattern of the detector junction diodes. All the detectors fabricated for this work were of this type and the impurity dopants were introduced into the silicon by ion implantation. In this method the oxide-masked silicon is exposed to a beam of monoenergetic ions produced by an accelerator which have a well defined range in the silicon. This method allows the control of both the concentration profile of impurities, by adjustment of the incident beam energy, and the total dose of implanted ions. After implantation the silicon wafers must be annealed at a moderate temperature which serves to electrically activate the dopant ions and to reduce the radiation damage caused by the incident ions. In general, because ion implantation is a moderately low temperature process, high minority carrier lifetimes can be achieved.

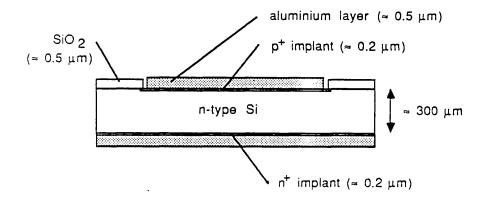

Figure 1 shows a schematic cross-section through a typical ion-implanted detector. The particular detector depicted has a single active area (i.e. the implanted area) but detectors are by no means

- 13 -

limited to this design - in reality almost any geometry is possible. The detector can be fabricated on a wafer of silicon of high resistivity (1-20 k $\Omega$ cm) which in this case is n-type silicon. The main features are the thermally-grown oxide which is usually between 0.5-1.0 µm thick and serves as an implantation mask and to passivate the surface, a thin layer of implanted p-type impurites forming the pn junction and a thin layer of implanted n-type impurites forming an ohmic contact on the back surface. Contacts are made via the thin layer (approximately 1.0 µm) of aluminium which covers some or all of the implanted areas on both surfaces.

Figure 1: Cross-section through a typical ion implanted detector

Also, associated with the oxide and oxide-silicon interface, are several types of charge centres which may influence the electrical characteristics of the detector if present in high concentrations. In most circumstances it is desirable to have low concentrations of oxide charges to achieve low leakage currents and high breakdown voltages

- 14 -

and this provides another important constraint on the manufacturing process.

#### 1.1 APPLICATIONS OF SEMICONDUCTOR DETECTORS

#### 1.1.1 Nuclear Physics

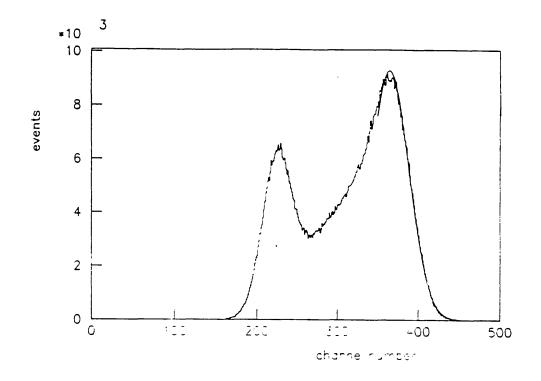

Silicon detectors are employed in nuclear physics for the spectroscopy of alpha particles, fission fragments and other heavy ions. Silicon surface barrier devices are excellent detectors of alpha particles. Their performance can be gauged by analysing the pulse height spectrum resulting when a source of monoenergetic alpha particles is incident on the detector. The most common source is alpha particles of energy 5.49 MeV emmited from  $Am^{241}$  and the pulse height spectrum has a full width at half maximum (FWHM) which is a measure of the energy resolution of the detector. This is true, of course, only if the broadening of the peak due to electronic noise is small compared to the inherent resolution of the detector itself. In practice, for  $Am^{241}$   $\alpha$  particles, this is the case and a typical value of the FWHM is about 20 keV although detectors are available with resolutions down to approximately 12 keV FWHM.

Silicon detectors are also suited to fission fragment spectroscopy (and heavy ion spectroscopy) although their response to such particles is more complicated. For heavily ionising fission fragments it is well established that a pulse height defect (PHD), or apparent loss of energy measured in the detector compared to the true energy, is observed. The pulse height for heavy ions is less than that observed for light ions (e.g.  $\alpha$ s) of the same energy and this PHD has been

- 15 -

attributed to three different phenomena: (i) the more heavily ionising ions deposit more of their energy in the insensitive entrance windows; (ii) the increased energy loss of the low velocity heavy ions due to nuclear collisions; and (iii) recombination of electron-hole pairs in the dense plasma created along the track of the heavily ionising particles. Measurements of the pulse height defect for surface barriers show that a value of 15 MeV for the defect is possible when fission fragments of average energy of about 80 MeV are used [2]. A further consideration is that radiation damage caused by prolonged exposure to heavy ions or fission fragments can result in rapid deterioration of the performance of the silicon detectors.

As well as energy measurements, silicon detectors are also widely used for particle identification via measurements of the specific energy loss dE/dx. In such applications the device is often called a 'dE-detector'. For this purpose a detector which is thin compared to the range of the incident particle is required and the thickness has to be made as uniform as possible. The superior energy resolution of silicon detectors is again an advantage in dE-detectors.

#### 1.1.2 High Energy Physics

In high energy physics (HEP), the discovery of charmed particles [3] in 1974 provided the impetus for a great effort towards the development of vertex detectors. Many of these charmed particles were found to have lifetimes in the region  $10^{-13}$  to  $10^{-12}$  sec so that they may travel ~ 1 mm from their production point in a HEP experiment before they decay. Charmed mesons were first observed

- 16 -

as effective mass peaks in e e annihilation experiments. However, fixed target experiments at Fermilab and at the CERN SPS were unable to detect the presence of the charmed particle resonances in their effective mass plots due to overwhelming combinatorial backgrounds. Meanwhile individual charm decays began to be observed by experiments using vertex detectors - nuclear emulsions or special purpose bubble chambers were used, resulting in events where secondary vertices ~ 100 µm from the interaction vertex were clearly seen.

Despite their high precision nuclear emulsions and bubble chambers have very limiting disadvantages such as their inability to provide an on-line trigger and problems with low data taking rates. This led to a concerted effort to develop silicon vertex detectors with the necessary spatial resolution and an excellent example of the use of such a detector is provided by the NA11 experiment at the CERN SPS. This group, a collaboration from Amsterdam, Bristol, CERN, Cracow, Max Planck Institute, Munich and the Rutherford Laboratory, (ACCMOR), has studied the hadronic production of charmed particles in a beryllium target. The experiment relied on a single-electron trigger to enrich the charm content of the data. This consisted of triggering on the semi-leptonic decay of one of the pair-produced charm particles, and also to see the hadronic decay of the other in their detectors.

- 17 -

However, even with this enriched charm sample, the data from NA11 only showed the  $D^{\pm}$  and  $D^{0}$  signals as small effects on large backgrounds.

The ACCMOR collaboration then decided to improve the experiment by adding a silicon vertex detector downstream of the beryllium target. Using this detector system, particles consistent with a displaced secondary vertex could be identified. The result was that most events (i.e. events in which all the particles emerged from the primary vertex) could be rejected and many tracks from the remaining events could also be rejected. With this method combinatorial background levels were drastically reduced which enabled the observation of clear charm signals with very little background. It also enabled measurements of the lifetimes of the charmed particles to be made.

The NA11 vertex detector consisted of six planes of silicon microstrip detectors, each detector having an active area of  $24\times36$ mm<sup>2</sup> with 1,200 parallel diode strips. The strip pitch was dictated by the typical average impact parameter which is of the order ct (where t is the particle lifetime), i.e. about 60-300 um. The strip pitch was 20 µm but to overcome fanout problems and to limit the amount of electronics, only 240 strips were read out from each plane. Capacitive charge division was used so that the readout strips could see signals from the passage of a particle between them, determined by the inter-strip and strip-to-substrate capacitances. This resulted in a precision on the impact parameter of typically 15 µm.

- 18 -

The NA11 experiment and other charm investigations such as the **NA14** charm photoproduction experiment have shown that semiconductor vertex detectors are very successful tools for the recognition of particles which give rise to a secondary vertex as in charm decay. In the past decade a succession of particles ( the  $\tau$ lepton and hadrons such as  $D, F, \Lambda_c, B, \ldots$ ) have been discovered which have lifetimes in the range 10<sup>-13</sup>-10<sup>-12</sup> sec. It is therefore foreseen that silicon vertex detectors will continue to find applications in high energy physics experiments of the future. One such application may be in the case of Z<sup>0</sup>-production at SLC or LEP. The Z° will decay via all kinematically allowed qq final states including the higher flavours. The subsequent heavy quark decays involve a large release of energy with many charged particles usually being produced and decays such as  $D \longrightarrow K\pi$  will be hidden in the combinatorial background. Silicon microstrips can be employed here to recognise the K and  $\pi$  tracks not coming from the primary vertex. Another possibility is the production of the Higgs boson which, as yet, has never been detected. A likely production mode is  $Z^{\circ} \longrightarrow H^{\circ} |_{}^{+} |_{}^{-}$ which would result in two jets due to the decay of the Higgs to bb or higher flavours. The large backgrounds caused by leptons from semi-leptonic decays of bottom and charm particles may well swamp the small number (~ 100) of Higgs events expected. Using a vertex detector these leptons could be identified as coming from a secondary vertex and therefore vetoed. In this way the prompt origin of each lepton can be identified providing a powerful method of background rejection.

# 1.2 OTHER USES OF SILICON DETECTORS IN HIGH ENERGY PHYSICS

#### 1.2.1 Charge Coupled Devices

Charge coupled devices (CCDs) were invented in 1970 at Bell Labs and have recently been adapted to charged particle detection in HEP. In general CCDs consist of a fine matrix of potential wells just below the surface of the silicon, typically 20  $\mu$ m × 20  $\mu$ m in area and approximately 10  $\mu$ m in depth. The potential wells, created by a series of metal-oxide-semiconductor (MOS) structures, are called pixels and the devices are fabricated such that charges from each pixel can be transfered to adjacent pixels and finally to a charge amplifier. The beauty of CCDs is that they measure space points since, unlike microstrip detectors, they provide two-dimensional readout. A group at the Rutherford Laboratory [4] has shown that for the detection of minimum ionising particles these devices can achieve

- detection efficiency of (98 ± 2)%

- two-dimensional spatial accuracy of 4.3  $\mu$ m × 6.1  $\mu$ m

- two-particle resolution of 40 µm in space.

Due to the thin depletion layer of these devices, the above performance is not degraded significantly if particles traverse the detector at non perpendicular incidence. However, the small depletion depth of approximately 10  $\mu$ m, yielding ~ 1000 charge carriers for minimum ionising particles, makes cooling of the devices and the front-end amplifier essential to achieve small leakage currents and low noise. Another disadvantage of CCDs is their relatively slow readout time of typically 50 msec.

- 20 -

1.2.2 Silicon Detectors as Sampling Devices in Calorimeters

The response of silicon detectors to charged particles is very well understood and the idea of using silicon as the active material for energy (and position) measurement in calorimeters has been recently proposed by Barbellini and Rancoita [5]. Silicon detectors could be well suited to this application since (i) they are compact due to high density and efficient conversion of deposited energy into charge carriers, (ii) they have no gain and are therefore very stable and (iii) they are insensitive to magnetic fields.

However, there are several unanswered questions, mainly concerned with the effects of radiation damage and the possible degradation of the energy resolution due to sampling fluctuations. In addition the feasibility of producing the large number of silicon detectors needed for a calorimeter in a typical HEP experiment at reasonable costs has not yet been proven.

#### 1.2.3 Silicon Photodiodes for Scintillator Readout

The basic structure of a silicon photodiode is similar to the structure of a standard silicon particle detector, the differences arising from the fact that photons in the visible and ultraviolet region are absorbed within a very shallow layer near the surface of the silicon. Compared to other light-sensitive detectors such as photomultipliers, they offer several advantages:

- high quantum efficiency over a wide spectral range

- insensitivity to magnetic fields

- compactness

- stability of the device since there is no intrinsic amplification

- 21 -

The recent interest in silicon photodiodes has led to the availability of photodiodes of up to several cm<sup>2</sup> in area and with leakage currents of only a few nA, manufactured using the oxide-passivated ion implantation technology. The important characteristics of a photodiode in most HEP applications are the quantum efficiency, the reverse bias (dark) leakage current and the capacitance. The best devices available at present achieve capacitances of approximately 80-100 pF for 100 µm depletion depth at reverse currents of below 1 nA/cm<sup>2</sup>. With amplifier shaping time constants of ~ 2  $\mu$ sec the equivalent noise charge is around  $\sigma$  ~ 400 electrons. Since in many situations the light yield from a minimum ionising particle is expected to be of the order of a few thousand photons, the use of silicon photodiodes for scintillator readout is clearly feasible and their performance has been studied experimentally by G.Hall et. al. [6].

#### 1.3 PRESENT STATUS AND RECENT DEVELOPMENTS

Silicon microstrip detectors are the most advanced high spatial resolution detectors which have been used by several groups [7] in HEP experiments. Microstrip detectors with parallel strips of diodes can be fabricated on 3-inch diameter silicon wafers resulting in an active area of up to 50×50 mm<sup>2</sup>. For a high spatial resolution it is desirable to make the strip pitch small. The minimum strip pitch which has been used so far is 20 µm and the spatial resolution of such a detector has been measured with minimum ionising particles [8]. The measured position resolution for normal incidence of a

- 22 -

single particle onto the detector was measured to be 3  $\mu$ m (this is close to the theoretical minimum of ~ 1  $\mu$ m arising from spatial fluctuation of the ionisation due to delta electrons). To achieve this precision it was necessary to readout every strip of the detector for the measurement. Thus, to achieve a precision of 3  $\mu$ m over an area of 50×50 mm<sup>2</sup>, for example, would require 2,500 channels of electronics. This can be a major disadvantage in many situations for several reasons. Firstly the physical volume of the electronics can become very large compared to the size of the detector. There are also other problems: the high cost of the large amount of electronics; fanout difficulties and the detector-to-preamplifier interconnections; and the problem of heat dissipation in the electronics.

In order to widen the range of applications of microstrip detectors it is therefore desirable to reduce the amount of electronics needed to read out these devices. One method which has been devised is to use capacitive charge division where only every n<sup>th</sup> strip is connected to readout electronics. Via the array of interstrip capacitances, the charge collection at intermediate strips induces charges on the readout strips which are inversely proportional to the distance between interpolation and readout strips. From this the position where a particle traversed the detector can be calculated. For uniform charge collection, the intermediate strips have to be kept at the same voltage as the readout strips. This can be realised by sputtering a strip of amorphous silicon over the detector. The resistance between adjacent strips is then > 1 M $\Omega$  which, combined with a low leakage current of ~ 1 nA, results in a uniform voltage on

- .23 -

each strip. Detectors with a 20  $\mu$ m pitch and readout pitches of 60, 120 and 240  $\mu$ m (i.e. n= 3, 6 and 12) using capacitive charge division have achieved resolutions given in table 1.

| n  | Readout pitch | Measured spatial resolution |

|----|---------------|-----------------------------|

| 3  | 60μm          | 4.5µm                       |

| 6  | 120μm         | 7.8µm                       |

| 12 | 240μm         | 20.0µm                      |

#### TABLE 1

Spatial resolutions of silicon microstrip detectors

with capacitive charge division read out.

Capacitive charge division has two main disadvantages: (a) The summed A pulse height measured by the two readout channels nearest to the passage of the particle depends on the position of the particle. This is due to the capacitive coupling of the interpolation strips to ground. The loss of pulse height means that (i) the detectors are not suited to pulse height measurements and (ii) the spatial resolution is worsened; (b) also due to capacitive coupling, charges are induced in the strips beyond the two readout strips nearest to the passage of the particle. This significantly worsens the two-particle resolution of the detector.

Future HEP experiments, for example at SLC, LEP and TEVATRON, will require silicon vertex detectors to have small pitch

- 24 -

and small readout pitch (<20 µm) and at the same time cover larger areas. Thus large numbers of readout electronics must be accomodated in relatively small areas in the vicinity of the detectors. With this in mind, there has been considerable effort in the past few years to achieve a high density of readout electronics for silicon detectors, or to reduce the amount of electronics required. There have been essentially two main developments in this area.

The first approach is the use of large scale integration (LSI) technology. Two projects are under way to develop an LSI readout chip incorporating (i) a low noise charge sensitive preamplifier and (ii) a multiplexer to switch many channels onto a single output line [9]. The first results have been obtained by the CERN-Hawaii University- Stanford University group using an LSI chip to readout a 25 µm pitch microstrip detector fabricated by Micron Semiconductor Ltd. The MICROPLEX chip has been developed for a high resolution microvertex detector for the DELPHI experiment at LEP and for a similar detector for MARK II at SLC. The chip contains 128 readout channels of charge sensitive preamplifiers with serial readout from all 128 channels controlled by a shift register. The chip is ~ 6 mm  $\times$  6 mm in size. With this chip, readout speeds of several MHz are possible and the results of experimental tests indicate that the electronic noise was  $\sigma \sim 1600$  electrons, comparable with the noise obtainable with conventional readout electronics on the same detector.

The second approach is the development of a new type of detector called the silicon drift chamber (SDC). The idea of the SDC was first proposed by E.Gatti and P.Rehak [10] and later demonstrated

- 25 -

by them and J.Walton. The SDC operates by collecting electrons at an anode after they have drifted up to several mm along a fully depleted detector so that a relatively large detection area can be read out by a single channel of electronics connected to the anode. The position of the generation of charge carriers in the detector by an incident ionising particle can then be deduced by the drift time of these charge carriers (electrons). Prototype SDCs have also been built by a Micron-Imperial College collaboration and tested at Imperial College and the results will be presented in subsequent chapters.

# Chapter II

#### THEORY OF SILICON DETECTORS

#### 2.1 BAND THEORY OF SOLIDS

In a solid the atoms are close enough together for the electric fields from one atom to interact with the electrons in another atom. As a consequence the energy levels merge into a series of bands in which the levels are so close together as to be essentially continuous. This concept, which is described by quantum mechanics, is vital in classifying materials into insulators, conductors or semiconductors.

As depicted in figure 2 (a), insulators are characterised by band gaps which are very large compared to kT at room temperature (approximately 0.025eV). For example silicon dioxide, which is a very important insulator in silicon device technology, has a band gap In such materials only the quantum states in the valence of 9eV. band are filled with electrons and therefore if an electric field is applied these electrons cannot increase their kinetic energy sufficiently and so no net current flows. Only if the field was excessively strong (around 107-108 V/cm), forcing electrons into the conduction band, would a net motion of electrons be allowed. In metals, figure 2 (b), the band gap is small, or the valence and conduction bands actually overlap, so that valence electrons are free to gain energy from very small applied fields because of the empty quantum states above the valence states.

- 27 -

In semiconductors, figure 2 (c), the band gap is sufficiently small that some electrons can have enough thermal energy imparted to them to be promoted to empty states in the conduction band. Semiconductors therefore have conductivities intermediate between metals and insulators.

conduction band Ę

(a)

εv Ec (b)

Ę E,

(C)

Figure 2: Energy level diagrams for solids (a) Insulator, (b) metal and (c) semiconductor.

#### 2.2 CONDUCTION IN INTRINSIC AND EXTRINSIC SILICON

In pure or intrinsic silicon the band gap is approximately 1.1 eV at room temperature which results in a very low conductivity. To estimate the concentration of electrons in the conduction band it is necessary to know the form of the Fermi-Dirac function which expresses the probability that a state of energy E is filled by an electron,

$$F(E) = \frac{1}{1 + e^{(E-E_f)/kT}}$$

(2.1)

- 28 -

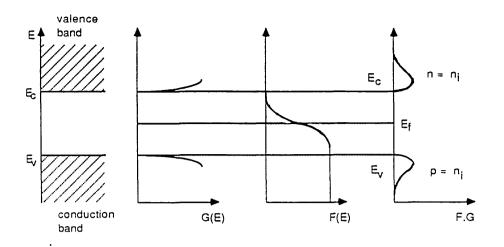

where  $E_f$  is called the Fermi level and is the energy level for which the occupation probability is 0.5. The concentration of electrons in the conduction band is given by F.G where G(E) is the density of states in the silicon. The empty states left in the valence band are called holes and these also act as charge carriers. This can be visualised as the movement of a hole or electron vacancy in response to an applied field due to the repopulation of states in the valence The concentration of holes in the valence band is given by band.  $(1-F)\times G$ . Figure 3 shows the form of F(E) and G(E) together with the resultant charge carrier distributions. In intrinsic silicon the Fermi level is approximately at the middle of the band gap and the concentrations of electrons and holes are roughly equal. Although the properties of intrinsic silicon can be described theoretically, in practice it is virtually impossible to produce and the electrical properties of real semiconductors are determined by the small levels of residual impurities. In silicon device fabrication it is therefore very important to be able to control the amount and type of impurity atoms in the silicon.

Extrinsic silicon is achieved by doping, that is the addition of controlled amounts of specific impurity atoms with the express purpose of increasing either the electron or hole concentration. For example, phosphorus has five valence electrons compared with four for silicon. When present in small concentrations the phosphorus atom will occupy a substitutional site within the silicon lattice resulting in an extra electron after all four covalent bonds have been formed. At room temperature most of the extra phosphorus electrons

- 29 -

Figure 3: Intrinsic semiconductor at equilibrium Schematic band diagram, density of states, Fermi-Dirac distribution and carrier concentrations.

are only lightly bound and are therefore available for conduction. This results in n-type extrinsic silicon. Conversely, boron has three valence electrons, leaving one vacant bond, easily filled by the movement of electrons. This is usually visualised as the inverse motion of the vacant bond or hole. This type of material with a high concentration of holes is called p-type.

For doped silicon an important quantity is the resistivity p which . depends on the concentrations of free electrons and holes and on their mobilities. These are a function of temperature and of impurity concentration. The resistivity is given by

$$\rho = \frac{1}{e (\mu_n n + \mu_p p)}$$

(2.2)

where e is the electron charge, n and p are the electron and hole concentrations and  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities

- 30 -

respectively. In the fabrication of silicon detectors, for reasons which will become obvious, it is usual practice to use silicon of very high resistivity. Crystals of resistivity of up to approximately 20 k $\Omega$ cm are commercially available [11], the upper limit being determined by the smallest doping concentrations which can be achieved. 20 k $\Omega$ cm p-type silicon, for example, requires a doping concentration of 5×10<sup>11</sup> acceptor atoms cm<sup>-3</sup>, which is equivalent to one acceptor atom in 10<sup>11</sup> in the silicon lattice. This presents a major challenge in both the crystal growing process and the subsequent steps in the fabrication of the detector.

The electron and hole concentrations in silicon, given by F.G and (1-F).G, can be calculated, yielding [12]

$$n = N_{c} e^{-(E_{c}-E_{f})/kT}$$

$$p = N_{v} e^{-(E_{f}-E_{v})/kT}$$

(2.3)

for the electron and hole concentrations respectively. Here,  $N_c$  and  $N_v$  are the effective density of states in the conduction band and valence band respectively,  $E_c$  and  $E_v$  are the electron (hole) energy at the conduction (valence) band edge respectively and  $E_f$  is the Fermi level. Alternatively, these equations can be written in terms of the intrinsic carrier concentration  $n_i$ ,

$$n = n_{i} \exp \left[ (E_{f} - E_{i})/kT \right]$$

$$p = n_{i} \exp \left[ (E_{i} - E_{f})/kT \right]$$

(2.4)

where  $E_i = \frac{1}{2}(E_c + E_v) + \frac{1}{2}kT \ln(N_v/N_c) - \frac{1}{2}(E_c + E_v)$  is the intrinsic Fermi level, which is very near to the middle of the band gap. This indicates that the deviation of a doped semiconductor from the

- 31 -

intrinsic material can be represented by the energy difference between the Fermi level and the intrinsic Fermi level. The above formulae become inaccurate when the semiconductor becomes degenerate (i.e. when the Fermi level comes close to the conduction or valence band edge to within  $\sim kT$ ).

It is evident that for a semiconductor in equilibrium the product of the concentrations of electrons and holes remains constant i.e.

np =

$$n_i^2 = N_c N_v e^{-E} G^{/kT}$$

(2.5)

where  $E_G = E_c - E_v$

#### 2.3 THE PN JUNCTION

In an n-type semiconductor the Fermi level is close to  $E_c$  and the electron concentration is much greater than the hole concentration. In this case the electrons are called the majority carriers and the holes are called the minority carriers. In p-type semiconductors the Fermi level is close to  $E_v$  and the hole concentration is much larger than the electron concentration. The structure formed when n-type material is in contact with p-type material is known as the pn junction and forms the basis of most silicon particle detectors.

Pn junctions can be characterised by the spatial distribution of the dopant concentration across the junction and in this section a simple model - the step junction model - is invoked to predict some of the properties of real pn junctions. The model assumes a step function form of the dopant concentration as shown in figure 4 (a). On contact of the n-type silicon with the p-type, the charge carrier

- 32 -

concentration difference between the two regions causes electrons to diffuse into the electron-free p-region and holes to diffuse into the hole-free n-region and recombine. This produces a region of fixed positively charged donor ions on the right of the junction and a region of fixed negatively charged acceptor ions on the left. The charge imbalance in turn produces an electric field, which eventually counteracts the diffusion so that in equilibrium the net flow of carriers is zero. Once this condition is reached the Fermi levels in the two materials become equal. The charged region near the junction which has been depleted of free charge carriers is called the depletion region or space-charge region.

The characteristics of the space-charge region can be calculated using the depletion approximation in which it is assumed that it consists entirely of the charge of the ionised donors and acceptors. The energy band diagram is shown in figure 4 (b) and it is useful to define the Fermi potential

$$\phi = -(E_f - E_j)/e \tag{2.6}$$

Thus  $\phi$  is positive for p-type material and negative for n-type material. From (2.4)

$$\phi_{n} = -(kT/e) \ln (N_{D}/n_{i})$$

$\phi_{p} = (kT/e) \ln (N_{A}/n_{i})$  (2.7)

The total potential variation across the junction is then

$$\phi_{\rm B} = \phi_{\rm p} - \phi_{\rm n} = (kT/e) \ln (N_{\rm D} N_{\rm A}/n_i^2)$$

(2.8)

This is called the built-in voltage of a pn junction.

- 33 -

N<sub>D</sub>- N<sub>A</sub>

The electric field E(x) and electric potential  $\phi(x)$  can be obtained by solving Poisson's equation

$$\frac{d^2 \phi}{dx^2} = -\rho(x)/\varepsilon_s$$

(2.9)

- 34 -

where p(x) is the charge density per unit volume,  $\varepsilon_s$  is the permittivity of silicon =  $\varepsilon_0 \varepsilon_r$ ,  $\varepsilon_0$  is the permittivity of free space and  $\varepsilon_r$  is the dielectric constant of silicon. With the charge density given by

$$\begin{aligned} \rho(x) &= + eN_D & \text{for } 0 \leq x \leq x_n \\ &= - eN_A & \text{for } -x_p \leq x \leq 0 \\ &= 0 & \text{in the bulk, i.e., } x < x_p \text{ and } x > x_n \end{aligned}$$

(2.10)

the solution for the field E(x) is

$$E(x) = -(eN_{D}/\epsilon_{s})(x_{n} - x) \quad \text{for } 0 \leq x \leq x_{n}$$

$$E(x) = -(eN_{A}/\epsilon_{s})(x + x_{p}) \quad \text{for } -x_{p} \leq x \leq 0 \quad (2.11)$$

The undepleted silicon on either side of the junction is field-free i.e. E(x) = 0. The form of E(x) is shown in figure 5 (d). For continuity of the field at x = 0 it is seen that

$$N_A x_p = N_D x_n \tag{2.12}$$

Thus, to obtain deep depletion regions in silicon detectors the dopant concentration of the substrate is made very low, i.e. high resistivity silicon is used. By integration of (2.11) the electric potential is obtained

$$\begin{split} \varphi(x) &= -\varphi_{n} - (eN_{D}/2\varepsilon_{s}) (x_{n} - x)^{2} \quad 0 \leq x \leq x_{n} \\ \varphi(x) &= -\varphi_{p} + (eN_{A}/2\varepsilon_{s}) (x + x_{p})^{2} \quad -x_{p} \leq x \leq 0 \end{split}$$

$$(2.13)$$

Imposing continuity of  $\phi(x)$  at x = 0 implies that the total depletion width is given by

$$d = x_n + x_p = \{(2\varepsilon_s/e) \phi_B [(1/N_A) + (1/N_D)]\}^{1/2}$$

(2.14)

- 35 -

Figure 5: Properties of the step junction model (a) Dopant concentration, (b) carrier density, (c) space charge density, (d) electric field and (e) electric potential.

For a pn junction fabricated on high resistivity n-type material  $N_D^{<<} N_A$  and so  $x_p \sim 0$ . In this case the depleted region extends into the n-type region of the detector and is given by

$$x_n \approx \{(2\epsilon_s/e) \phi_B (1/N_D)\}^{1/2}$$

(2.15)

The above results are summarised in figure 5.

## 2.4 THE REVERSE BIASED PN JUNCTION

With no external voltage applied, a silicon pn junction diode will function as a detector, but only with very poor performance. The built-in voltage  $\phi_B$  across the junction is small so that the electric field is not large enough to make the charge carriers move very rapidly. In addition, since the depletion region is very narrow, the active detection volume is small. Also the junction capacitance ( $\ll d^{-1}$ ) is high so the noise properties of such a detector when connected to the input stage of a preamplifier may be quite poor. For these reasons most pn junction detectors are used with an external voltage applied so that the junction becomes reversed biased.

The situation is then as shown in figure 6. The Fermi levels are displaced by an amount equal to the bias voltage. The n-bulk region is shifted downward by  $-V_{R}$ . The slope of the band edges in the depletion region has increased, reflecting the increase in electric field for reverse bias. Also there is an increase in potential difference across the junction - the applied voltage adds to the built-in voltage. This produces an increase in the barrier height for diffusion of majority carriers across the junction. Consequently the diffusion component of the current is reduced to less than its thermal equilibrium value. However, the drift current component of minority carriers down the potential hill remains approximately at its equilibrium value (small). Evidently there is a net current flowing within the diode, which is typically very small, referred to as the leakage current.

Figure 6: Energy level diagram for reverse bias at thermal equilibrium.

# 2.5 CONTRIBUTIONS TO THE LEAKAGE CURRENT

The reverse leakage current is the sum of several components which are all due to electron-hole (e-h) pairs generated somewhere in the semiconductor. Under equilibrium conditions electron-hole pairs are continually generated but they recombine giving rise to zero net current. Under reverse bias, e-h pairs, once generated, will be separated by the field and their probability of recombination is diminished. There are three main contributions to the leakage current:

(a) Generation within the depletion region - "generation current"

(b) Generation in the neutral regions - "diffusion current"

(c) Generation at surface states or conduction through surface channels at the edge of the device which I shall call the surface component of the current.

- 38 -

The generation of e-h pairs in the depletion region takes place via intermediate-level centres. These are energy states which have energy levels in the forbidden gap and are associated with impurities such as heavy metal ions and imperfections in the silicon lattice. Because the probability of transitions depends on the size of the step in energy, such states can increase the efficiency of the generation-recombination process, especially if the state is near the centre of the band gap [13].

The intermediate-level centres within the depletion region alternately emit electrons and holes and the rate of generation of e-h pairs is given by

$$U = - \frac{\sigma_p \sigma_n v_{th} N_t n_i}{\sigma_n e^{(E_t - E_i)/kT} + \sigma_p e^{(E_i - E_t)/kT}} \equiv -n_i/(2\tau_0)$$

(2.16)

where  $N_t$  is the density of bulk generation-recombination centres with energy  $E_t$ ,  $\sigma_n$  and  $\sigma_p$  are the electron and hole capture cross-sections respectively and  $v_{th}$  is the thermal velocity of carriers.  $\tau_o$  is defined as the minority carrier lifetime within a reverse biased depletion region and is given by

$$\tau_{o} = \frac{\sigma_{n} e^{(E_{t} - E_{i})/kT} + \sigma_{p} e^{(E_{i} - E_{t})/kT}}{2 \sigma_{p} \sigma_{n} v_{th} N_{t}}$$

(2.17)

From (2.16) it can be seen that only those centres whose energy level  $E_t$  is near the intrinsic Fermi level  $E_i$  contribute significantly to the generation rate. The generation current is given by  $I_a = q|U|dA$  or

$$I_{g} = (1/2) e (n_{j}/\tau_{0}) dA$$

(2.18)

- 39 -

where d is the depletion region width and A is the junction area.

A second contribution to the leakage current is due to the generation of minority carriers in the undepleted region (within a diffusion length of the depletion region boundary) which diffuse into the depletion region and are swept away by the electric field there. The magnitude of the diffusion current can be calculated by solving the diffusion equation [14] and is given by

$$I_{d} = q A n_{i}^{2} \{ [D_{n}/(N_{A}L_{n})] + [D_{p}/(N_{D}L_{p})] \}$$

(2.19)

where  $D_n$  and  $D_p$  are the diffusion coefficients for electrons and holes respectively and  $L_n$  and  $L_n$  are the corresponding diffusion lengths. Since silicon detectors are usually operated in the fully depleted mode the diffusion current is essentially zero and can be neglected. A further contribution to the total leakage current is the surface component. To understand this component of the leakage current it is necessary to understand the effects of charges in the Si-SiO, system and a summary is given in section 3.2.5 and reference [15]. The two most important types of charge are the fixed oxide charge  $Q_f$ , which is usually positive and located in the oxide within ~ 30 Å of the Si-SiO $_2$  interface, and the interface trapped charges Q $_{it}$  which have energy states in the forbidden gap and can interact electrically with the underlying silicon. The interface trapped charges act as intermediate centres for the generation process in much the same way as the bulk intermediate centres do. The surface leakage current arising from generation via the interface trapped charge can be calculated in a similar manner to the calculation of I and is given by [16]

$$s = (1/2) q A \pi \sigma v_{th} D_{it} kT n_{i}$$

(2.20)

- 40 -

where it was assumed that  $\sigma_n = \sigma_p = \sigma$ . Here  $D_{it}$  is the surface state density per unit area per electron-Volt near the midpoint of the bandgap. The physical origin of the interface trapped charge is not understood but it is assumed that these states result from either defects in the structure of the interface region, or from impurities in this region, or both. Since  $I_s$  can completely dominate the total leakage current if the surface state density is high, suitable steps have to be taken in the processing of the silicon to minimise  $D_{it}$ . The techniques used are described in chapters 3 and 4.

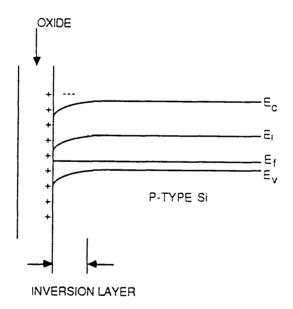

Another factor which influences the surface leakage current is the oxide fixed charge  $Q_f$ . The effect of oxide fixed charge present in oxidised p-type silicon is depicted in figure 7.

Figure 7: Band-bending due to oxide fixed charge at the surface of a p-type semiconductor.

The positive fixed charge  $Q_f$  must be compensated by an equal amount of negative charge within the bulk of the silicon, thus producing an inversion layer of electrons and causing the energy bands to bend downwards as shown. The charge values  $Q_f$  and  $Q_{it}$  determine how near the Fermi level at the silicon surface is to the midgap, where interface traps generate leakage current most efficiently. Thus for p-type silicon the band-bending resulting from the presence of fixed oxide charge causes the Fermi level to be closer to midgap resulting in an increased leakage current. For n-type silicon the opposite effect occurs.

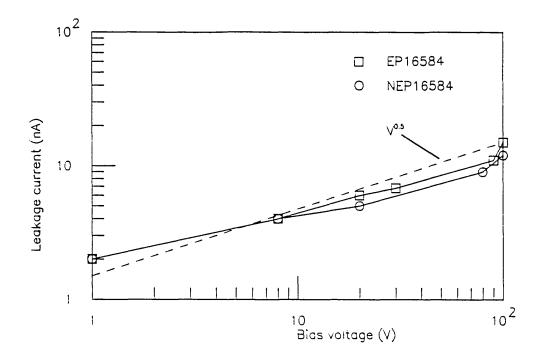

Figure 8 shows the results of measurements of the leakage current for two ion-implanted n-type detectors of nominal area 1 cm<sup>2</sup>. From this plot of leakage current versus reverse bias voltage it is evident that  $I_{leak}$  is approximately proportional to  $V^{\alpha}$  ( $\alpha$  = constant) but it does not follow exactly the  $V^{\frac{1}{2}}$  dependence expected if the generation current  $I_g$  is the dominant component. This shows that either the surface component  $I_s$  or the diffusion component  $I_d$  or both have some contribution to the total leakage current.

Figure 8: Leakage currents plotted against bias voltage for detectors EP-16584 and NEP-16584.

# 2.6 DEPLETION LAYER CAPACITANCE

A further important property of the reverse biased pn junction is its The capacitance per unit area is defined as  $C^{-1} = dV/dQ$ , capacitance. voltage where dV is incremental increase in the dQ charge is added. when a For the pn junction detector in reverse bias the capacitance is due to the depletion region and, for the step junction model, is given by [12]

$$C = \varepsilon_{\rm S}/d = \sqrt{\{\varepsilon_{\rm S}/[2\,\mu_{\rm n}\,\rho\,(\phi_{\rm B}+V)]\}} \approx \sqrt{\{\varepsilon_{\rm S}/(2\,\mu_{\rm n}\,\rho\,V)\}} \tag{2.21}$$

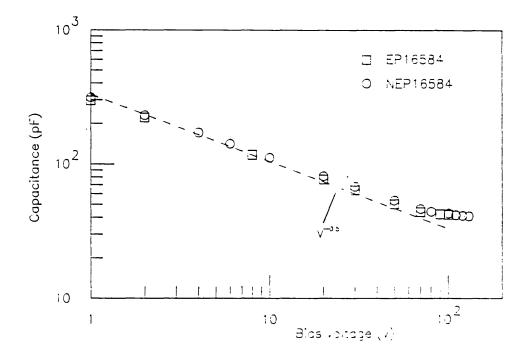

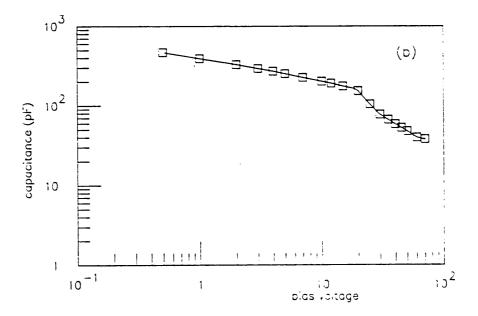

Figure 9 shows the results of the measurements of the capacitance for two detectors, EP-16584 and NEP-16584. As the depletion region width increases the capacitance falls and reaches a constant value at ~ 80-90V when the detector is fully depleted. The proportionality of the capacitance to  $V^{-0.46}$  is close to the theoretical value of  $V^{-\frac{1}{2}}$  indicating that the step junction model is valid in this case. If C is plotted against  $V^{-\frac{1}{2}}$  the slope of the line can be used to estimate the resistivity of the n-type silicon:

$$P \sim 3720 \ \Omega \text{cm}$$

(NEP-16584)

$P \sim 4100 \ \Omega \text{cm}$  (EP-16584)

.

Figure 9: Capacitance characteristics of detectors EP-16584 and NEP-16584.

## 2.7 SILICON MICROSTRIP DETECTORS

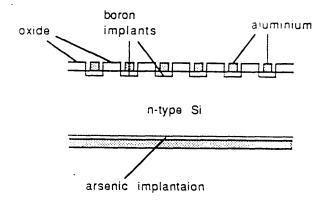

Figure 10 shows the structure of a typical silicon microstrip detector. It consists of a fully depleted crystal of silicon with one surface subdivided into parallel p<sup>T</sup>n diode strips with a pitch of typically The thickness of the detector depends on the particular 20-50 um. application but for the detection of minimum ionising particles a thickness of ~ 300 µm is suitable. Making the detector thinner results in a lower signal-to-noise ratio since the energy loss of the incident particle is less. A suitable reverse bias voltage is applied across the wafer which serves to deplete the detector and to provide a collection field. A fast charged particle passing through the detector produces e-h pairs which drift towards the electrodes under the influence of the electric field. The motion of the charge carriers induces the signal in an external amplifier connected between the n and p contacts.

Figure 10: Cross-section through a microstrip detector

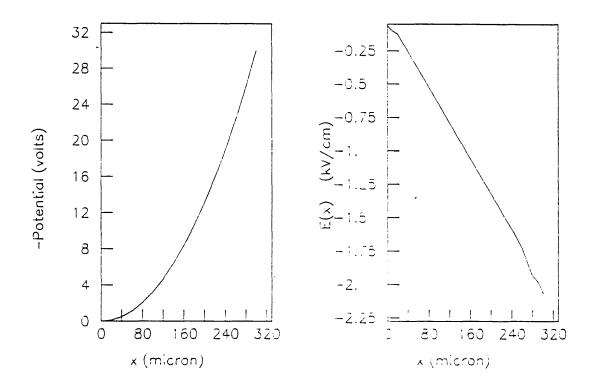

The form of the electric potential and electric field inside a silicon microstrip detector is shown in figure 11. These plots are based on the results of a computer simulation using the programs described in chapter 6. The simulation was done for a detector of thickness 300  $\mu$ m, strip pitch 50  $\mu$ m and resistivity 10 k $\Omega$ cm. The electric field varies linearly with the distance and the potential is parabolic as expected on the basis of the step junction model.

## 2.8 SILICON DRIFT CHAMBERS

The principle of the SDC was first described by E. Gatti and P. Rehak [10]. They were able to show that it is possible to fully deplete a thin, large area semiconductor wafer through a small contact somewhere at the edge of the wafer. After full depletion of the silicon wafer a second electric field can be superposed which serves to transport the charge carriers along the plane of the wafer to a collection electrode (the anode).

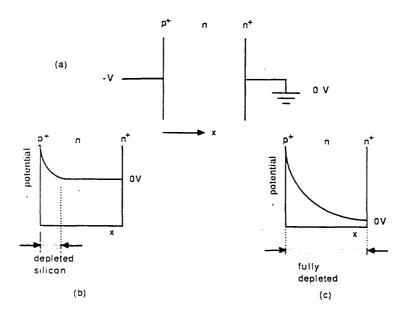

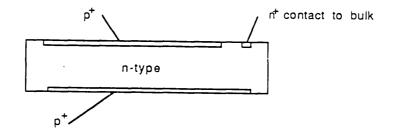

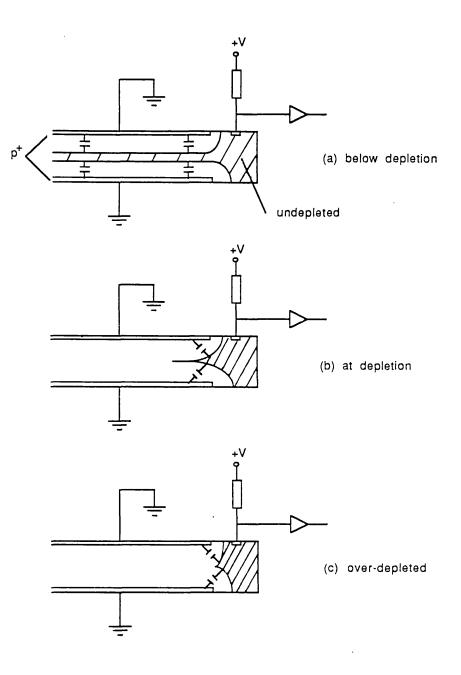

First consider the depletion of a standard n-type silicon detector. In figure 12 (a) the  $n^+$  contact is shown at zero volts while a negative potential -V is applied to the  $p^+$  contact. As the bias voltage is increased above 0 V the depletion region extends from the  $p^+$  contact into the bulk as shown in figure 12 (b). The form of the potential is given by the solution to Poisson's equation and is parabolic as shown. The remainder of the silicon near the  $n^+$  contact is a field-free undepleted region which acts as a conductor. Electrons and holes generated in the depletion region AB experience forces due to the electric field there, causing holes to be swept to the  $p^+$  contact and electrons to be carried to the undepleted region.

As the bias voltage is increased further the depletion region extends further towards the  $n^+$  contact and eventually the detector becomes fully depleted as shown in figure 12 (c). Neglecting the built-in voltage, the depletion condition is reached when the bias voltage reaches  $V_D$  where

$$V_{\rm D} = \frac{d^2}{2\epsilon\mu_{\rm D}\rho}$$

(2.22)

Figure 12: Depletion of a standard p n junction detector

Electron-hole pairs thermally generated in the detector are swept out of the depletion region by the action of the electric field - holes to the  $n^+$  contact and electrons to the  $p^+$  contact. Thus the fully depleted condition is stable.

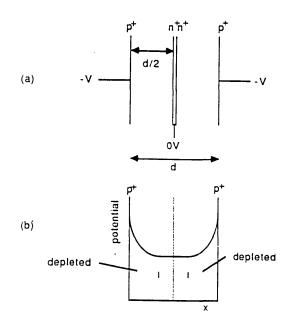

Now consider two n-type silicon detectors placed parallel to each other such that the two  $n^+$  electrodes are in contact as shown in figure 13 (a). If a small reverse bias is applied to both detectors, two depletion regions are formed at each  $p^+n$  junction extending into the silicon bulk with equal depths. The depletion regions and potential distribution are shown in figure 13 (b).

The formation of the depletion layers is a consequence of the reverse bias applied to the  $p^{+}n$  junctions. The fixed positive charge of the ionised donors in the depleted region is compensated by an

- 48 -

Figure 13: Two standard p<sup>\*</sup>n detectors in proximity (a) With n<sup>\*</sup> electrodes in contact. (b) Potential and depletion regions of the two detectors under reverse bias.

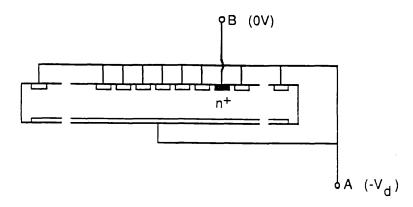

equal amount of negative charge sitting in the p<sup>\*</sup>n junctions. The n<sup>\*</sup>n contacts act only to conduct charge and do not play any role in the depletion mechanism. Thus the same situation can be realised using a single semiconductor wafer of twice the thickness with two p<sup>\*</sup>n junctions at opposite surfaces of the wafer, as shown in figure 14 (a). The depletion mechanism is the same as with the standard p<sup>\*</sup>n junction - as the bias voltage V is increased, the depletion region increases at the expense of the thickness of the undepleted conductive channel. The contact to the n-type silicon can be made at the edge of the wafer as shown in figure 13 (a), or more realistically via an n<sup>\*</sup> implant like that shown in figure 15.

Figure 14: Depletion of a single n-type semiconductor with  $p^{+}$  junctions on both sides.

As the bias voltage is increased further, the central undepleted conductive channel becomes narrower and eventually, at full depletion, it disappears. In this situation the detector becomes fully depleted and the bias voltage required is given by

$$V_{\rm D}' = \frac{(d/2)^2}{2 \epsilon \mu_{\rm D} \rho} = V_{\rm D}/4$$

(2.23)

- 50 -

Thus the voltage needed to fully deplete the wafer is equal to a quarter of the voltage required to fully deplete a standard  $p^{+}n$  diode detector of the same thickness and resistivity.

Figure 15: Practical means of contacting the n-type silicon via an  $n^+$  implant at one side of the detector.

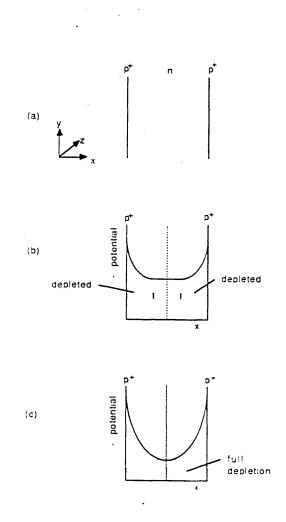

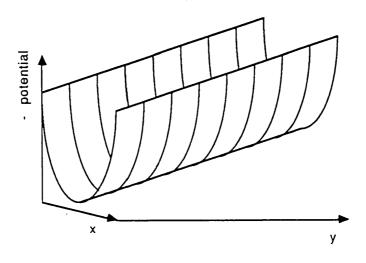

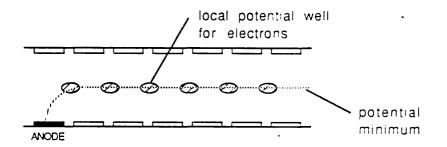

The important feature of the fully depleted condition is the existence of the potential minimum for electrons at the centre of the Since e-h pairs are continuously produced by thermal wafer. generation, this depletion state is evidently unstable because electrons would tend to accumulate at this potential minimum. The answer is to incline the potential as shown in figure 16 so that thermally generated electrons are continuously swept towards the n anode. Figure 16 also illustrates the principle of drift in SDCs. Electrons generated by the passage of an ionising particle in the detector are transported along the potential 'gutter' to the anode. The time delay between the passage of the particle and the signal at the anode is due to drift of electrons and can be used to measure the position of the incident particle.

- 51 -

Figure 16: Potential of a fully depleted silicon wafer when an additional constant field along the y-axis is applied.

Figure 17: Practical realisation of a silicon drift chamber

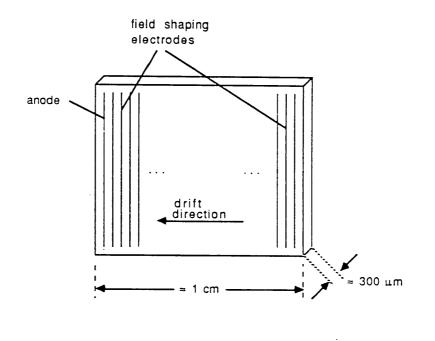

The arrangement used in an actual detector is shown in figure 17.

.

Both surfaces are subdivided into parallel p strips and on one surface the first strip (the anode) is an n<sup>+</sup> implant. A positive potential is applied to the anode to fully deplete the detector as described above and in addition a drift field is provided by superposing a potential of the form

$$\phi = - \mathbf{E} \cdot \mathbf{y} \tag{2.24}$$

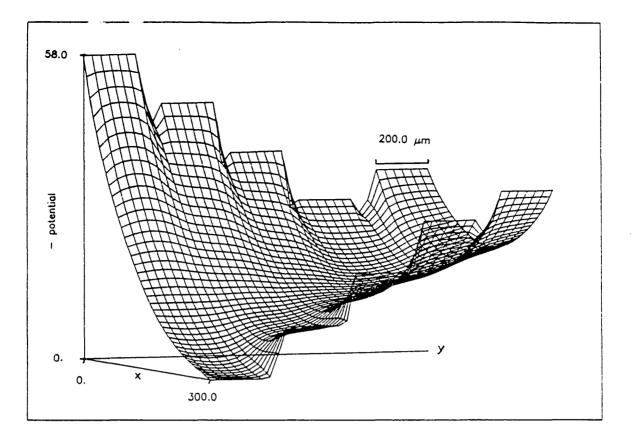

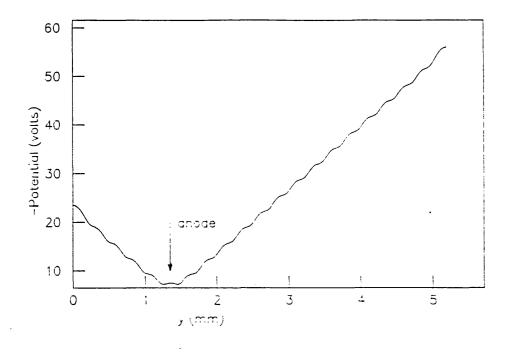

where E is the electric field. This is achieved in practice by linearly grading the potential on the strips, the potential becoming more positive towards the anode. In the anode region the potential minimum is shifted from the centre of the wafer to the anode surface so that electrons drifting along the detector are finally collected at the anode. The resultant potential distribution in the SDC in a region near the anode is shown in the plots of figure 18.

With an electrode pitch of 250  $\mu$ m and a voltage per strip of  $\Delta V = 5V$ , the drift field is 200 V/cm. The drift velocity is then  $v_d = -\mu_n E = 2.7 \ \mu$ m/nsec. Thus the drift field is small compared to typical internal fields induced by the depletion process allowing drift times which are measurably long. The position information is derived from the measurement of the electron drift time. When a fast charged particle traverses the detector the electrons generated drift along the detector in the potential gutter. During the transit time the signal charge is screened by the p<sup>+</sup> electrodes and the signal appears only when the electrons arrive close to the collecting anode.

The anode can be connected to a charge sensitive amplifier to read out the signal. The capacitance of the anode is very small and independent of the active area of the detector. Also, the single

- 53 -

Figure 18: Potential within a silicon drift chamber in a region close to the anode.

channel of electronics connected to the anode is used to read out a relatively large area of the detector thereby reducing the number of readout channels by a factor of ~ 100 compared with a microstrip silicon detector.

#### Chapter III

#### FABRICATION TECHNIQUES FOR SILICON DETECTORS

#### 3.1 INTRODUCTION

Silicon detectors fabricated by the planar process, using oxide passivation and ion implantation, were pioneered by J.Kemmer [17, ] 18]. The planar process is a well known fabrication technique and the technology has been highly developed for the manufacture of silicon devices and integrated circuits (ICs). However, the application of the planar process to silicon detector production is not a trivial step and has caused some difficulties. For IC fabrication, both n-type and p-type silicon are used, but the doping concentration is much higher and the lifetimes of minority carriers are some orders of magnitude lower. Silicon crystals of orientation <100> are generally used since they have the lowest surface state density.

For silicon detectors wafers of high resistivity and of <111> orientation must be used. To obtain low leakage currents special care during the processing must be exercised to ensure low charge densities in the Si-SiO<sub>2</sub> interface system and to avoid killing of the minority carrier lifetime during high temperature treatments. Using a suitable processing plan these aims can be achieved and this chapter describes some of the techniques used in the production of silicon detectors.

- 55 -

The growth of single crystals of silicon from high purity polysilicon represents the first significant step in the manufacture of a highly perfect semiconductor material. For detector grade silicon this is achieved by the floating zone (or float zone crucible-less) technique. In this process a polycrystalline rod of silicon is converted into a single crystal rod by traversing a molten zone of silicon from one end of the polycrystalline rod to the other with the initial zone being created in contact with a single crystal seed. Melting of the silicon to form a zone is achieved by induction heating.

Conversion of silicon ingots into polished wafers requires firstly slicing the crystal followed by etching and polishing. Slicing is performed with a diamond-edged saw blade leaving the surfaces of the resulting wafer damaged and contaminated in a region of typical depth This layer is removed by chemical etching and finally the 10 um. wafers are polished by a chemi-mechanical process to provide a specular smooth, surface where device features can be photoengraved.

## 3.2 OXIDATION OF SILICON

In silicon integrated circuit technology oxide layers provide surface passivation for a silicon device, act as a diffusion mask and ion implantation mask and also provide isolation of one device from another. These requirements have led to the development of a number of methods of oxidation. The most widely used ones are plasma anodisation [19, 20], chemical anodisation [21], vapour-phase

- 56 -

reaction [22] and thermal oxidation [23]. For silicon detectors low leakage currents are required and the oxide-silicon interface must have a minimum, stable density of oxide fixed charge and interface trapped charge (see section 3.2.5). The oxide must also be stable under fields normal to the oxide-air interface. The oxide that meets these requirements best is the thermally grown oxide. Thermal oxidation is therefore the predominant oxidation technique used in both silicon detector and IC fabrication.

### 3.2.1 Silicon Oxidation Model

The growth of oxide layers on silicon by thermal oxidation can be achieved in several ways. For oxidation in pure oxygen, producing 'dry oxides', the chemical reaction is

$Si(solid) \cdot O_2 \leftrightarrows SiO_2$  (solid)

For wet oxides, where the oxidation is carried out in a water vapour ambient, the reaction is

Si(solid) +  $2H_2O \Leftrightarrow SiO_2(solid) + 2H_2$

The basic process involves shared valence electrons between silicon and oxygen forming covalent bonds. During the oxidation the  $Si-SiO_2$ interface moves into the silicon and the amount of silicon used up can be calculated from the densities and molecular weights of silicon and silicon dioxide. For the growth of an oxide film of thickness d, a layer of silicon 0.45d thick is consumed.

It has been shown experimentally that oxidation of the silicon proceeds at the  $Si-SiO_2$  interface and that the oxidising species diffuses through the oxide layer and reacts at the  $Si-SiO_2$  interface.

- 57 -

Uncertainties exist, however, as evidenced by controversies in the literature as to whether charged or neutral species are transported through the oxide, and on the details of the reaction at the Si-SiO<sub>2</sub> interface. If a silicon sample is exposed to an oxidising ambient, the initial oxidation rate is fast since there are a great number of oxidant molecules available at the silicon suface. As the oxide layer grows the rate becomes limited by the fact that oxidant molecules must diffuse through the silicon dioxide layer. The oxide thickness at which diffusion of the oxidant becomes limiting is about 40 Angstroms for dry oxidation and 1000 angstroms for wet oxidation. The kinetics of the oxidation process are described mathematically by the model of Deal and Grove [24].

For oxides grown in steam the oxide layer is, in fact, SiO<sub>2</sub> containing a given amount of water molecules, the amount being dependent on the oxidation conditions. The amount of hydration of an oxide layer is important since it can determine how well a photoresist layer will adhere to it and can also affect the stability of the device. One advantage of wet oxides is that the time taken to grow an oxide of given thickness at a given temperature is much less than the time required in a pure dry oxygen ambient. However, in general, silicon detectors for HEP have employed dry oxidation because of the improved electrical properties obtained.

- 58 -

### 3.2.2 Practical Means of Oxidation