## MICROPROCESSOR-CONTROLLED INVERTER-FED SYNCHRONOUS MOTOR

by Nicholas Martin Mallinson, B.Sc.(Eng), A.C.G.I.

Volume One of Two Volumes

October 1983

A thesis submitted for the degree of Doctor of Philosophy of the University of London and for the Diploma of Membership of the Imperial College of Science and Technology

Department of Electrical Engineering Imperial College of Science and Technology London SW7 2AZ

### ABSTRACT

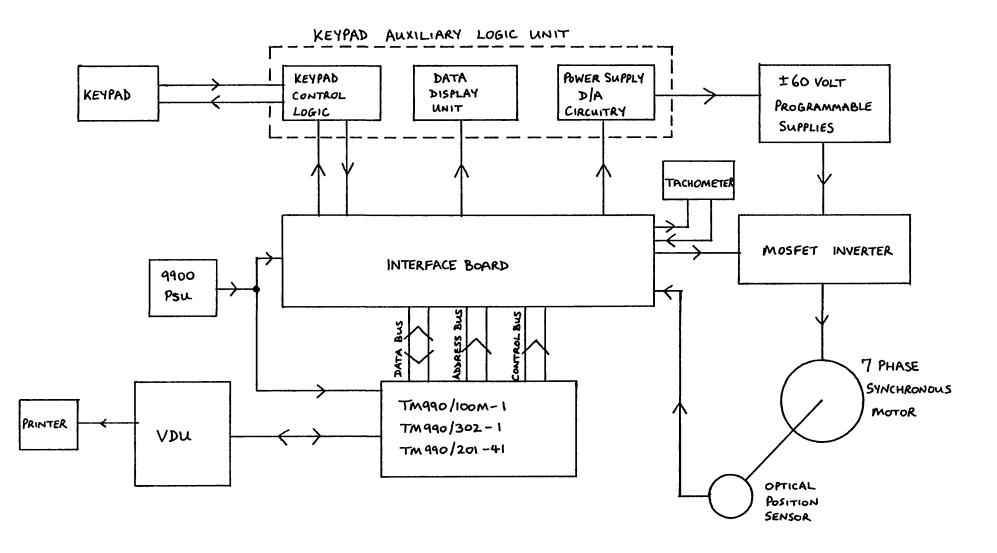

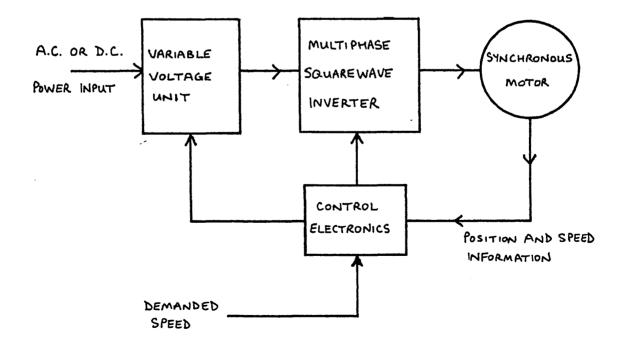

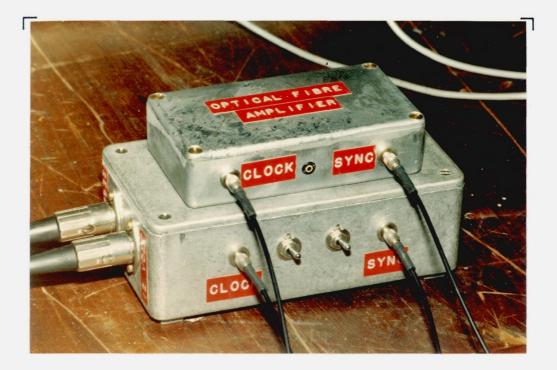

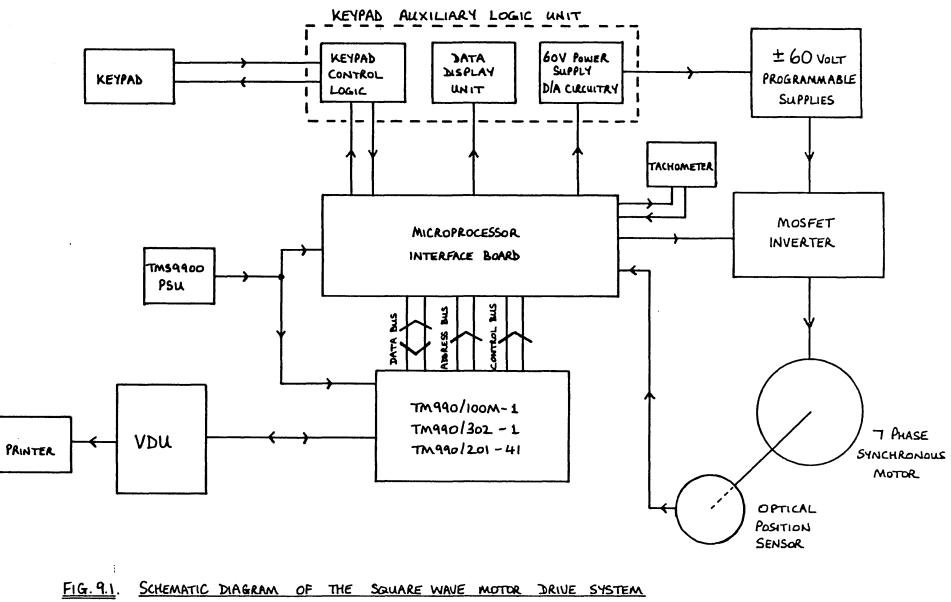

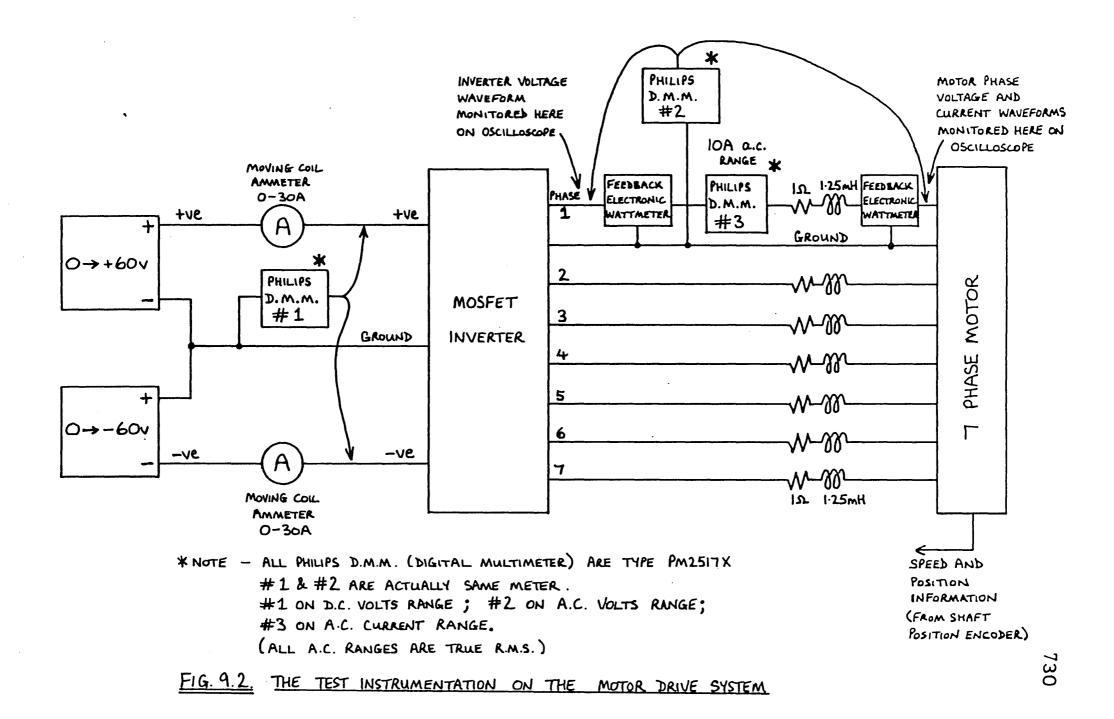

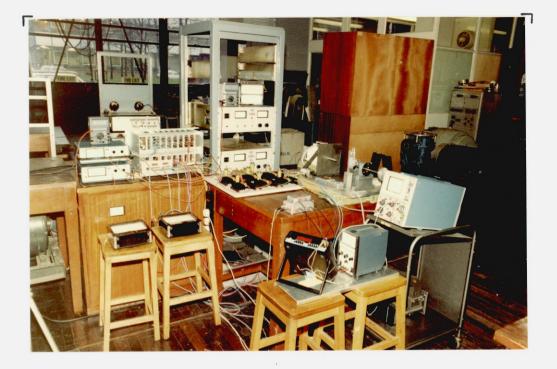

The thesis is concerned with a class of variable-speed motor drive system, in which a synchronous motor is operated in the autopiloted mode from a voltage-source inverter. A system comprising a permanent magnet squarewave synchronous motor, a transistor inverter, a microprocessor controller and an optical fibre shaftposition detector was designed, built and tested.

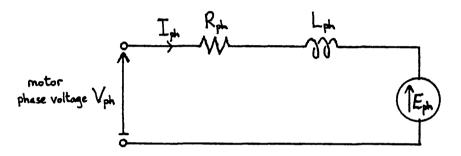

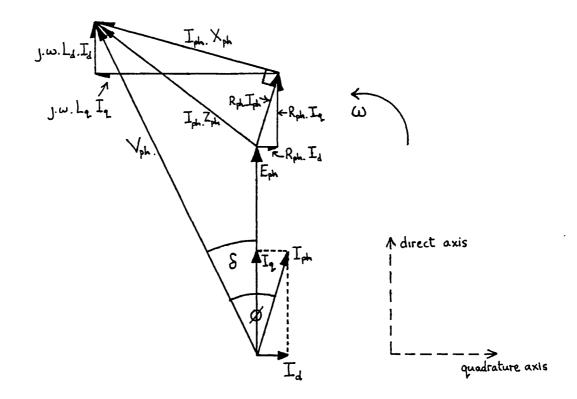

A simple sinusoidal analysis to predict the performance of a synchronous motor operated in voltage-forced mode is given. The experimental test equipment used to confirm the general nature of the predictions is described and the results presented. The logic circuits that the microprocessor later replaced are explained.

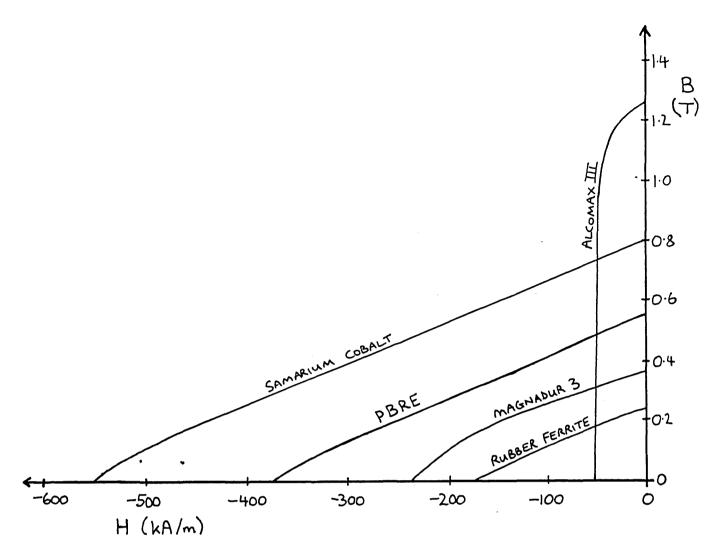

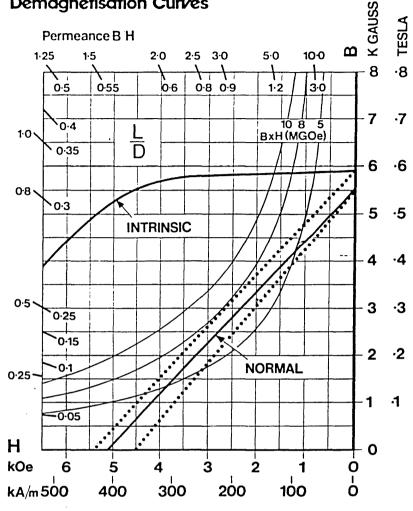

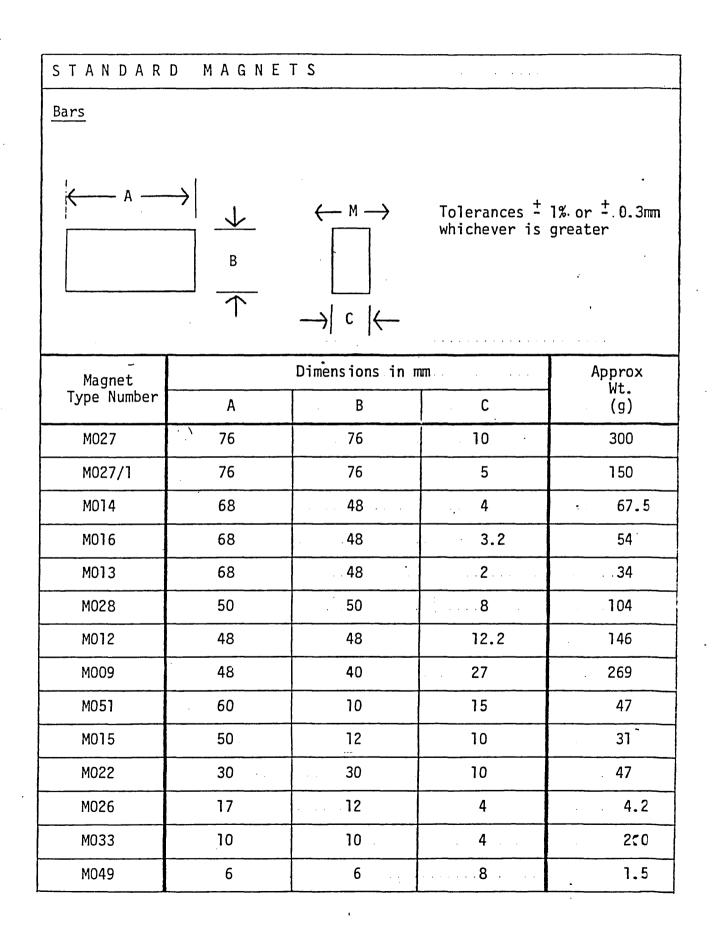

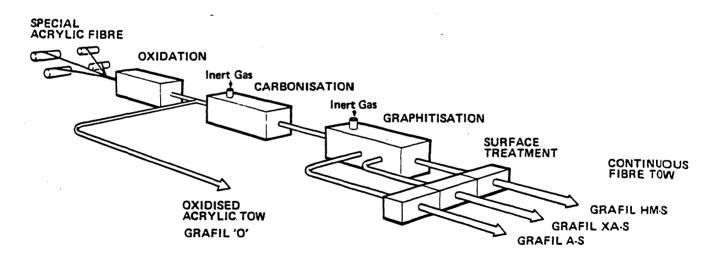

The motor design is unusual. The stator has seven phases and generates a quasi-square back-emf to match the inverter voltage waveform. A designed rotor speed of 30000 rpm results in a high power-to-weight ratio. The squarewave rotor flux is generated by polymer bonded samarium cobalt magnets encased in a carbon fibre cylinder.

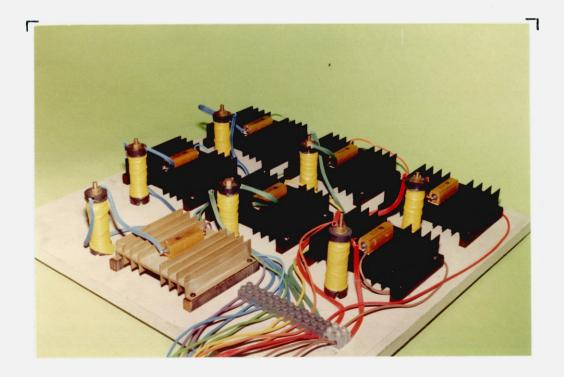

The inverter uses MOSFET transistors and the seven phases are independently controllable. The phase rating is  $\pm 60$  volts at 7 amperes giving a total continuous rating of 3kW at frequencies from d.c. to at least 1.5kHz.

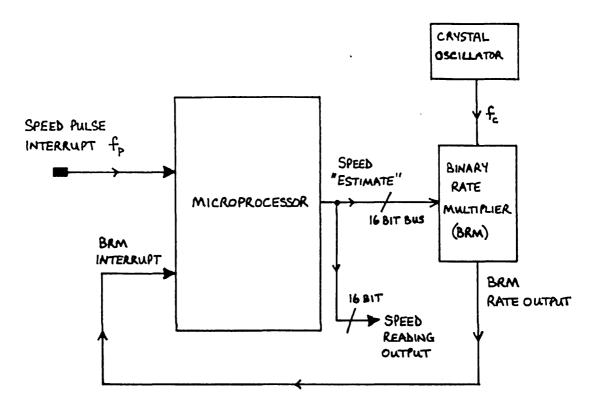

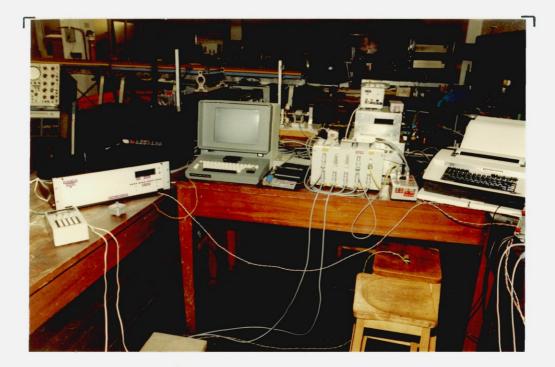

The controller uses the 16 bit Texas 9900 microprocessor to keep the motor synchronised. Software was developed to implement two synchronising strategies using either interrupts or a counter sampled by the microprocessor. Control commands are entered via a purpose built keypad. A digital tachometer was developed to provide speed data to the controller.

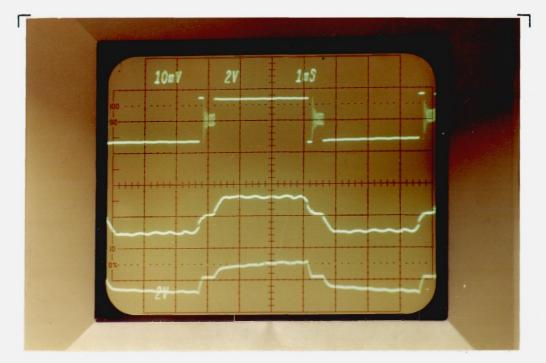

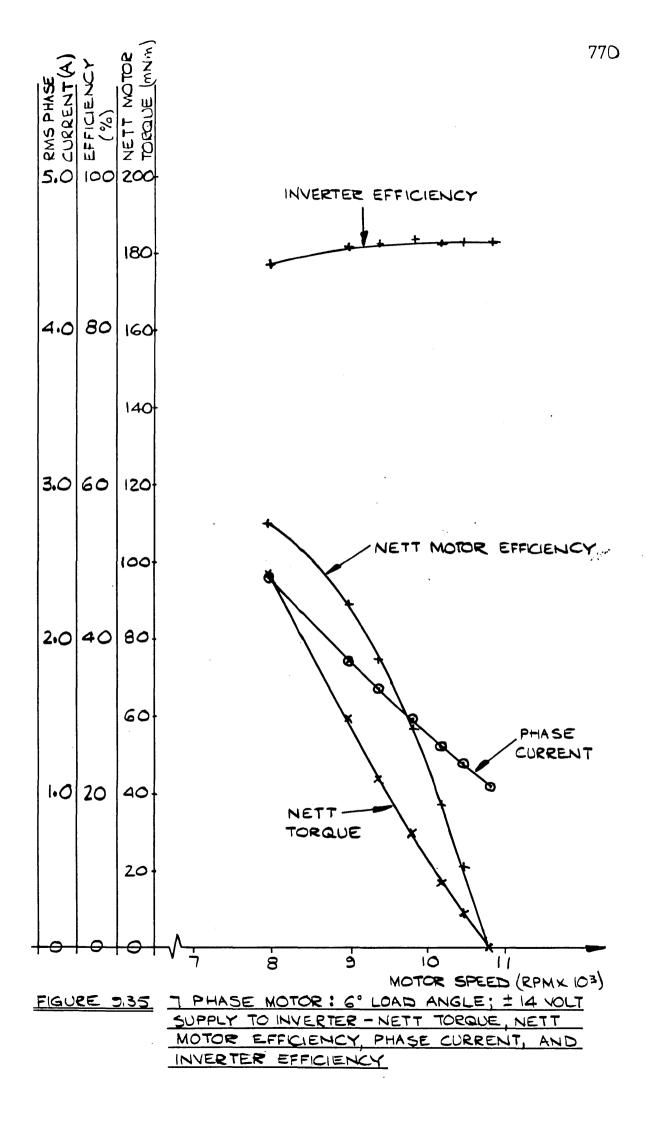

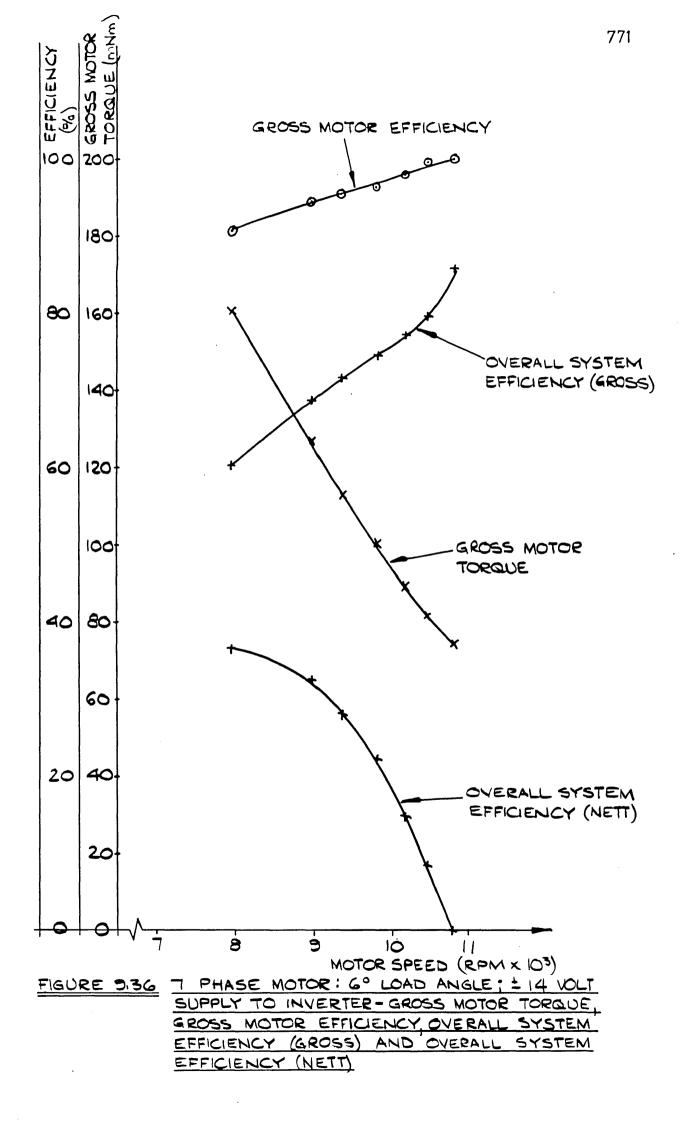

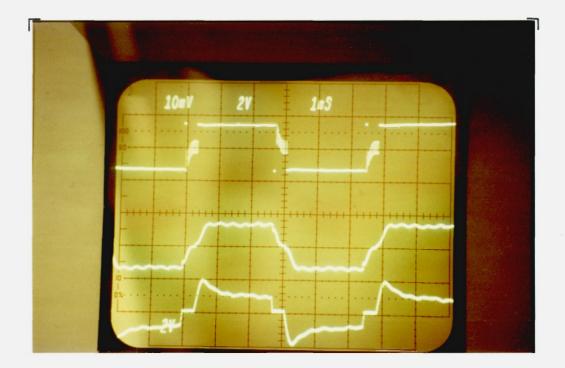

The system was tested under steady state conditions and the performance characteristics and waveforms are illustrated by experimental curves and photographs, and are compared with predictions.

It is concluded that most of the system's design features have potential for use on autopiloted synchronous motor drives of various rated powers, and in particular the performance of the square-wave motor is sufficiently promising to warrant further investigation. It is also concluded that a microprocessor can successfully replace hardwired logic in inverter controllers.

#### ACKNOWLEDGEMENTS

The author would like to express his gratitude to his supervisor, Dr. H.R. Bolton, for providing valuable guidance whilst not interfering excessively during the course of the work described in this thesis. Without doubt, the author would not have contemplated working for a Ph.D had Dr. Bolton not provided the opportunity to do so. The author was given great freedom to direct the work and Dr. Bolton deserves sincere thanks for this.

Thanks for financial support are due to the S.E.R.C. (formerly the S.R.C.) and to Dr. Bolton.

Several friends have been particularly helpful. Those who deserve special mention are: Malcolm Shute; Nigel McQuin; John Tasker; Dr. Clive Bryant; Dr. Somchai Chatratana; Dr. Robert Palmer. The author feels that without the assistance given by the above mentioned people, the project may not have reached such a successful conclusion.

The author would also like to acknowledge the manufacturing and technical assistance given to him by Mr. R.B. Owen, Mr. R. Moore, Dr. B. Williams, Dr. S. Williamson and Dr. D.A.G. Peddar during the project.

Finally, it must be stated that none of the work would have been possible without the continuous support, financial and otherwise, provided by the author's wife, Jennie. The low standard of rented accomodation in London is but one of the many sacrifices that she has endured during the course of the work. This thesis is a splendid demonstration of her newly acquired skill of typing.

Thank you Jennie.

# Volume One

|       |                     |                                                                                                                                | Page                    |

|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ABSTR | RACT                |                                                                                                                                | 2                       |

|       | WLEDGEME            | NTS                                                                                                                            | 3                       |

| LIST  | OF CONTE            | NTS                                                                                                                            | 4                       |

|       |                     |                                                                                                                                |                         |

| CHAPI | <u>TER 1</u> :      | INTRODUCTION                                                                                                                   | 16                      |

| CHAPI | <u>TER 2</u> :      | SINEWAVE ANALYSIS OF A VARIABLE<br>FREQUENCY VOLTAGE FORCED<br>AUTOPILOTED SYNCHRONOUS MOTOR                                   | 27                      |

| 2.1   | Introduc            | tion                                                                                                                           | 2 <b>7</b>              |

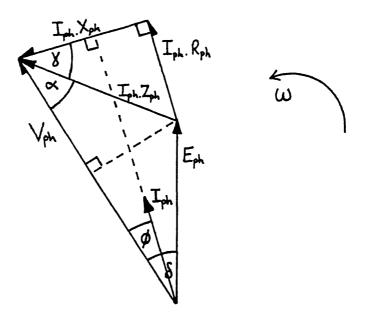

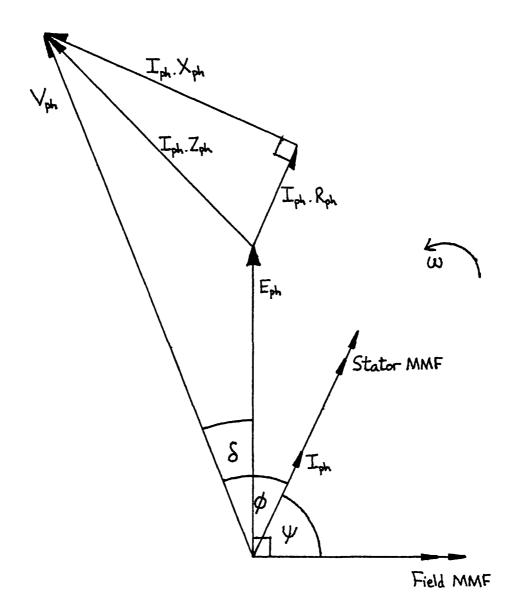

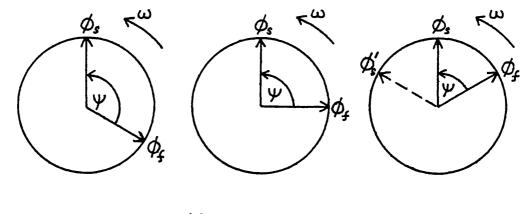

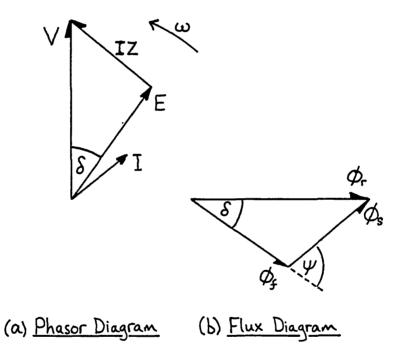

| 2.2   |                     | tate Performance Characteristics of<br>Forced Autopiloted Synchronous Motors                                                   | 2 <b>7</b>              |

|       | 2.2.1               | Survey of Simple Analysis Methods                                                                                              | 2 <b>7</b>              |

|       | 2.2.2               | Relationships Between Presented<br>Analysis and Previously Published<br>Analyses                                               | 29                      |

| 2.3   | The Sync            | hronous Motor Torque Equation                                                                                                  | 31                      |

|       | 2.3.1               | The Derivation of the Torque Equation<br>for a N Phase Salient Pole<br>Synchronous Motor Fed From a Voltage<br>Source Inverter | 31                      |

|       | 2.3.2               | Simplification of the Salient Pole<br>Torque Equation to the Cylindrical<br>Rotor Form                                         | 35                      |

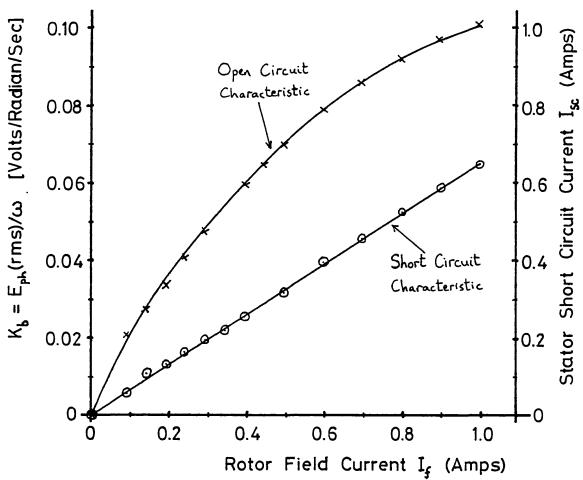

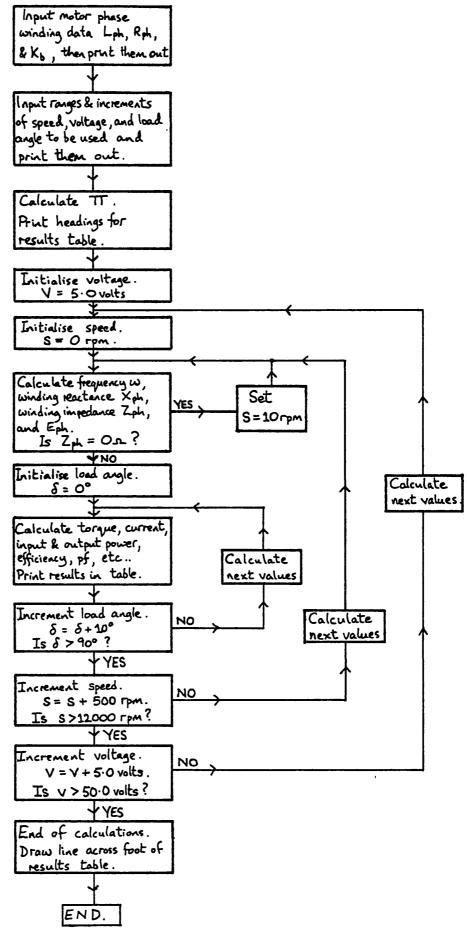

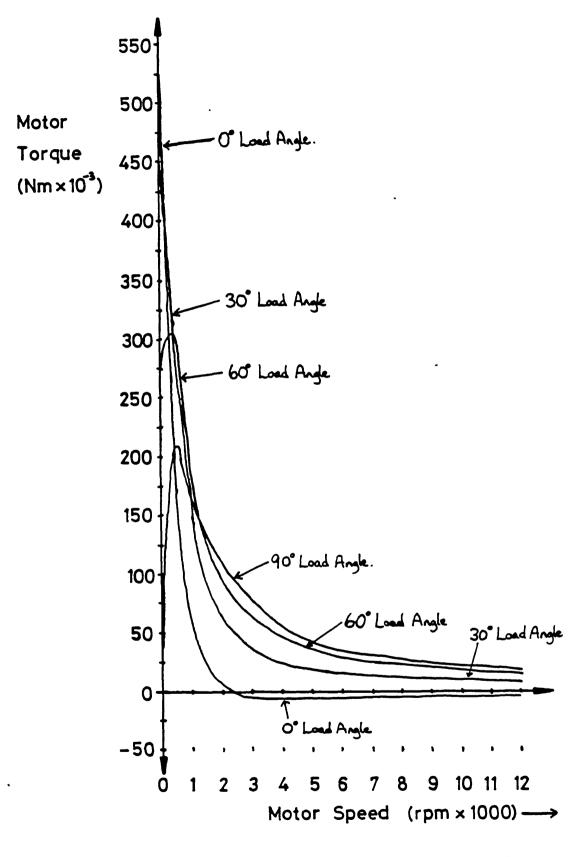

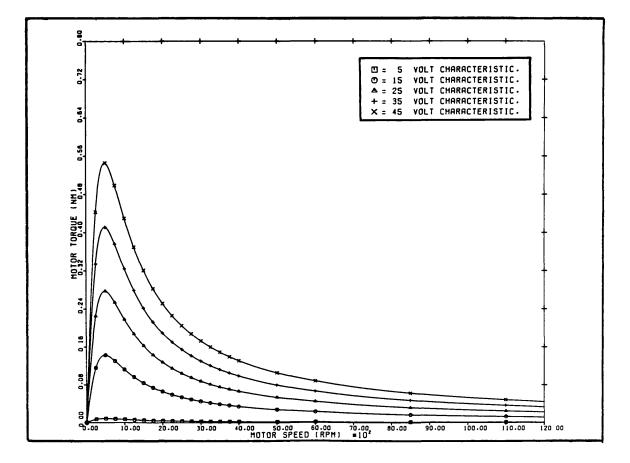

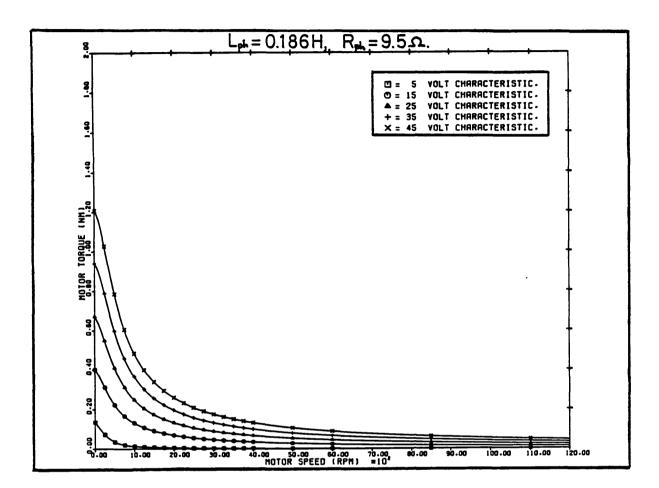

| 2.4   | Predicte<br>Machine | d Characteristics for the Magslip                                                                                              | 38                      |

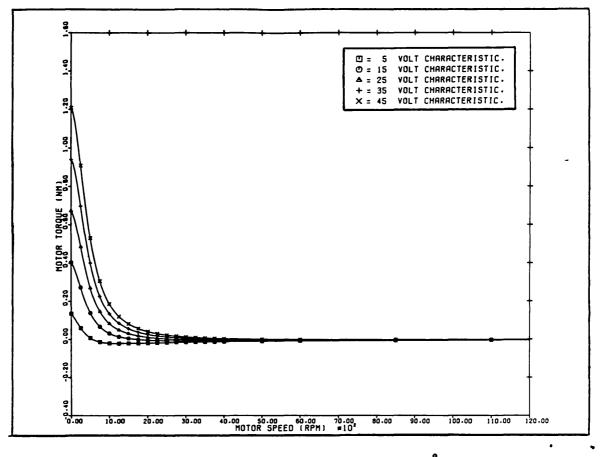

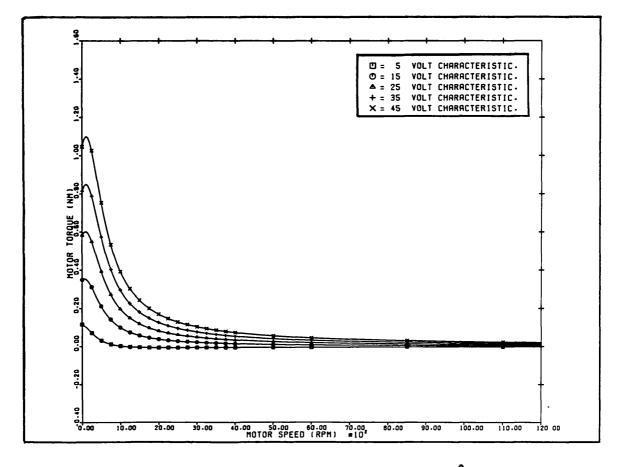

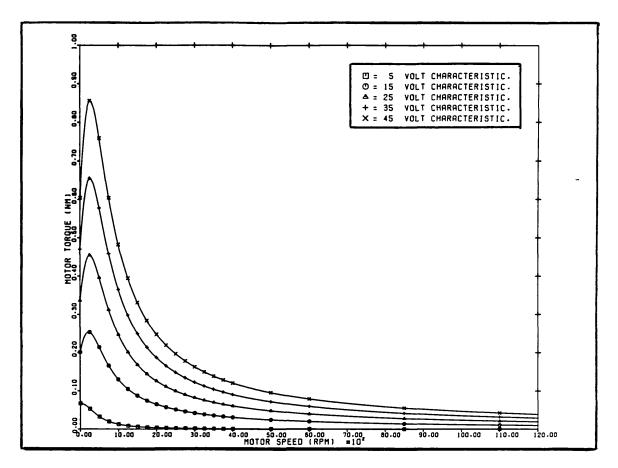

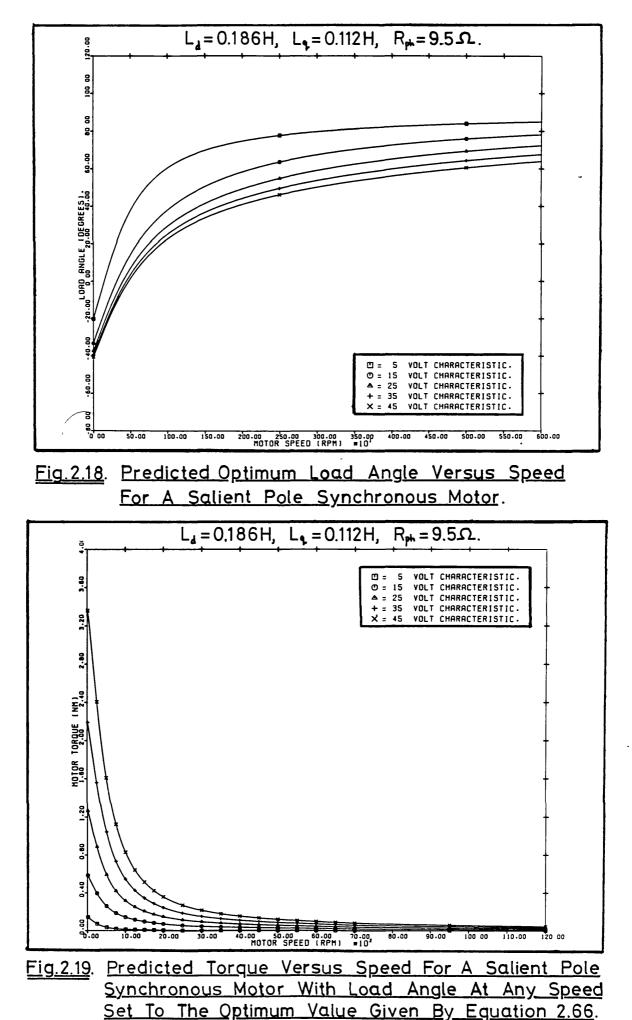

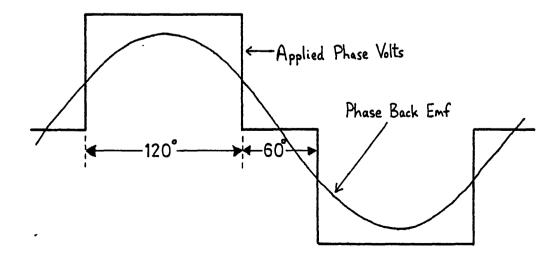

| 2.5   | The Opti<br>a Given | mum Load Angle for Maximum Torque at<br>Speed                                                                                  | 50                      |

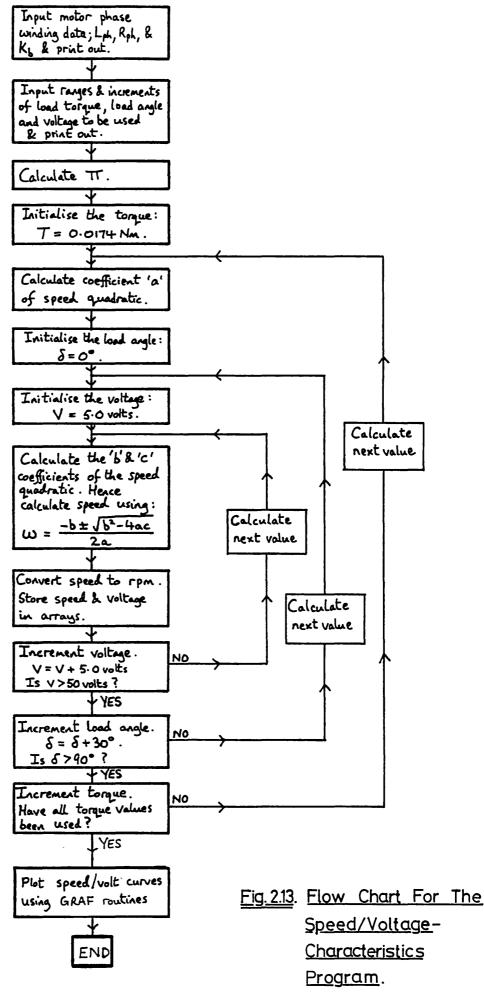

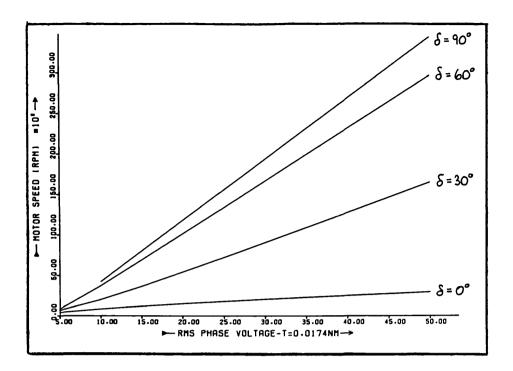

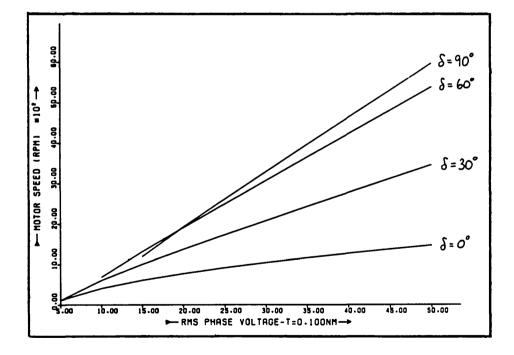

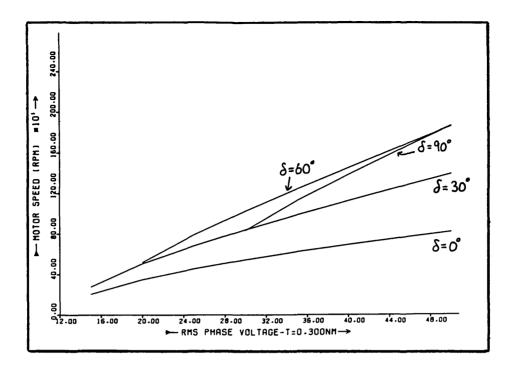

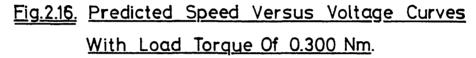

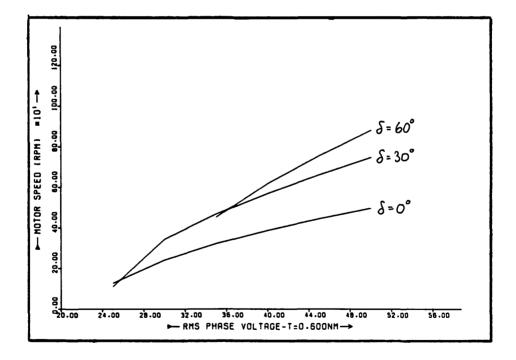

| 2.6   |                     | on of a Speed Versus Applied Stator<br>Characteristic                                                                          | 53                      |

| 2.7   |                     | ation of the Optimum Operating Load<br>or a Salient Pole Synchronous Motor                                                     | 58                      |

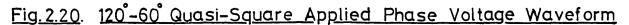

| 2.8   | Attempts            | at Square Wave Analysis                                                                                                        | 63                      |

| 2.9   | Synchron            | ous Motor or D.C. Motor?                                                                                                       | 69                      |

| 2.10  | Conclusi            | ons                                                                                                                            | <b>7</b> 0 <sup>°</sup> |

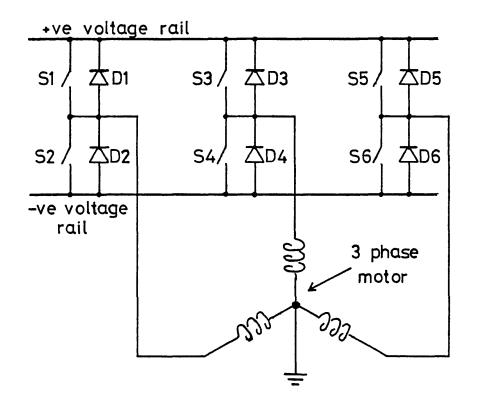

| CHAP  | TER 3:              | A 3 PHASE SINUSOIDAL SYNCHRONOUS<br>MOTOR DRIVEN BY A 3 PHASE QUASI-<br>SQUARE WAVE VOLTAGE SOURCE INVERTER                    | 71                      |

| 3.1   | Introduc            | tion                                                                                                                           | 71                      |

•

# Page

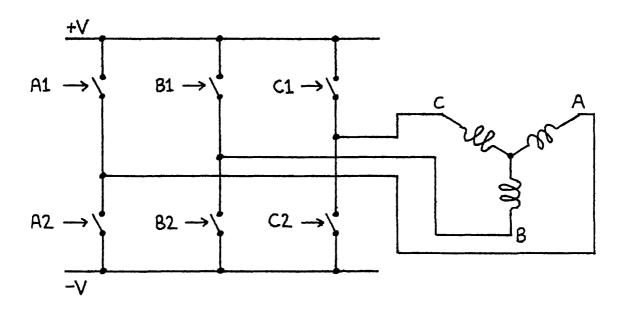

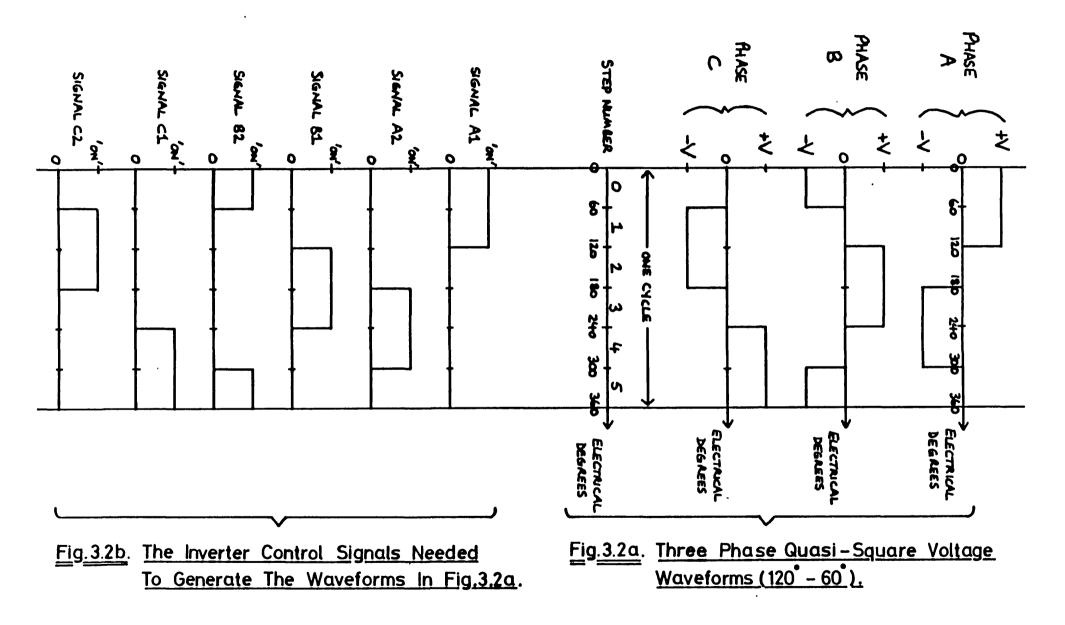

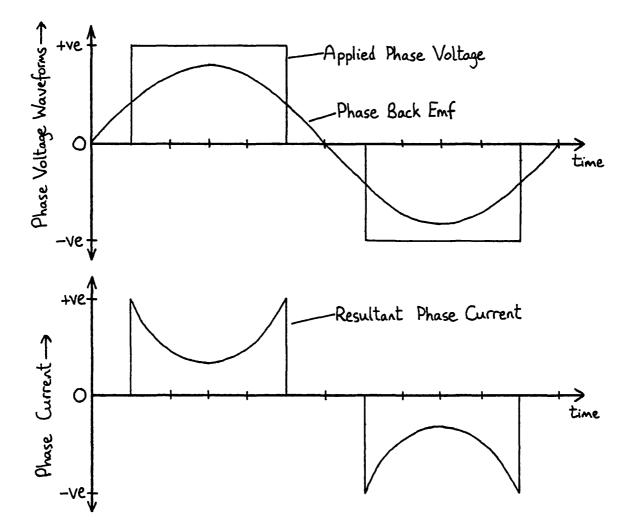

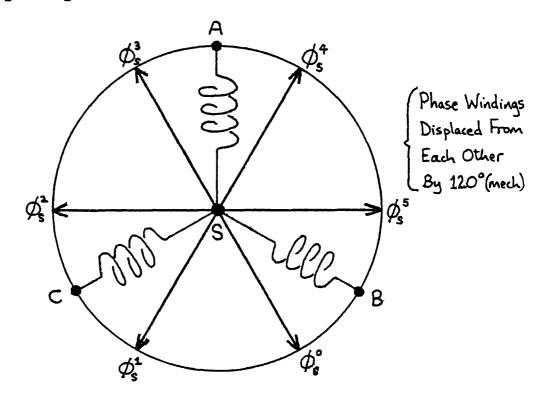

| 3.2 |                       |               | of a Sinusoidal Motor from a<br>Variable Frequency Voltage Source                                 | 71          |

|-----|-----------------------|---------------|---------------------------------------------------------------------------------------------------|-------------|

|     | 3.2.1                 |               | ods of Achieving Reverse<br>r Rotation                                                            | 80          |

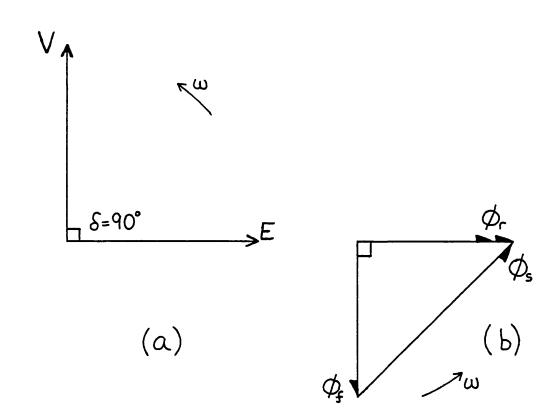

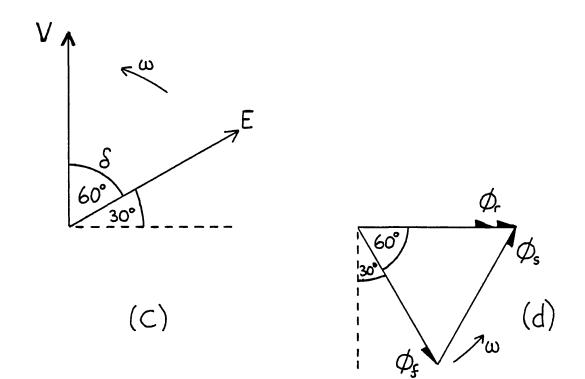

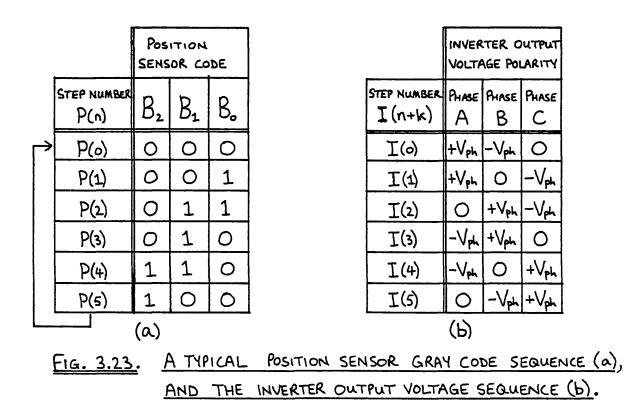

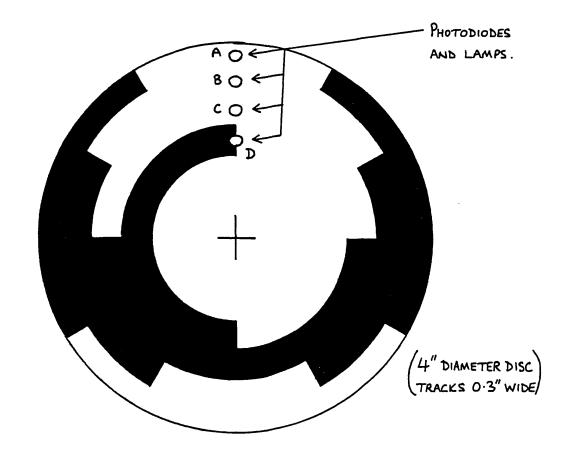

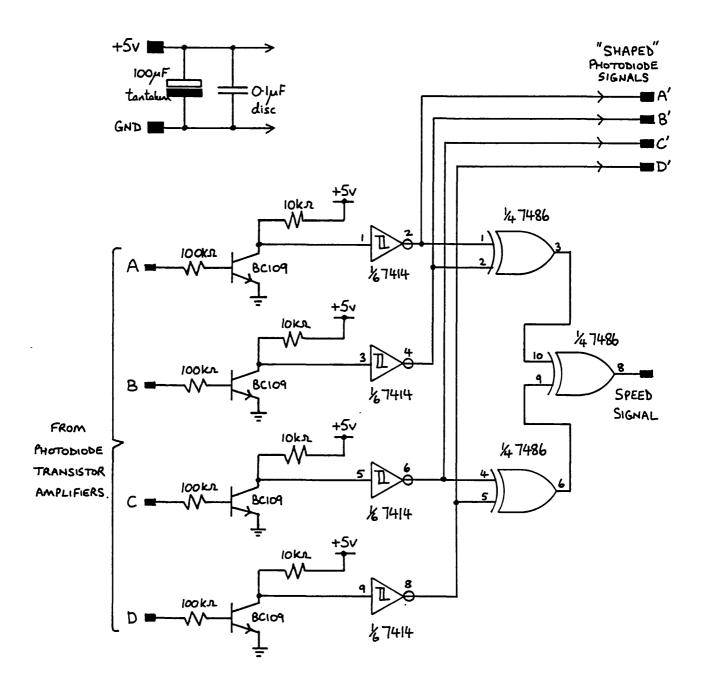

| 3.3 | Digital :<br>of Rotor |               | ion Sensors for the Detection<br>tion                                                             | 83          |

|     | 3.3.1                 | Avai          | lable Types of Position Sensors                                                                   | 86          |

|     | 3.3.2                 | Poss          | ible Arrangements of the Sensors                                                                  | 88          |

|     | 3.3.2.                |               | NOLOG (No Logic) Position<br>Sensor Systems                                                       | 89          |

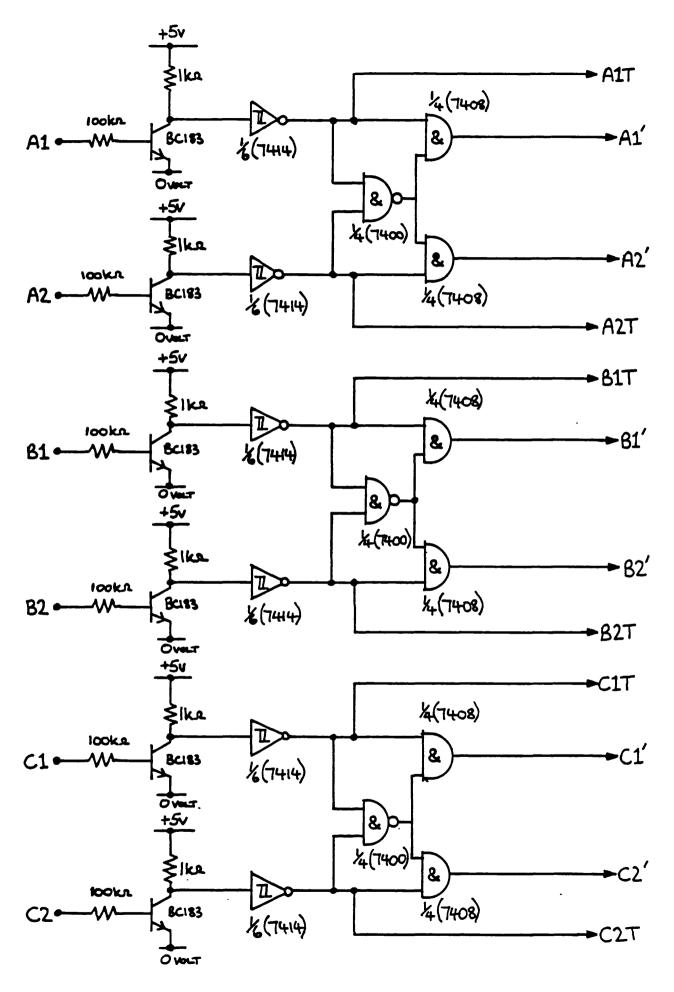

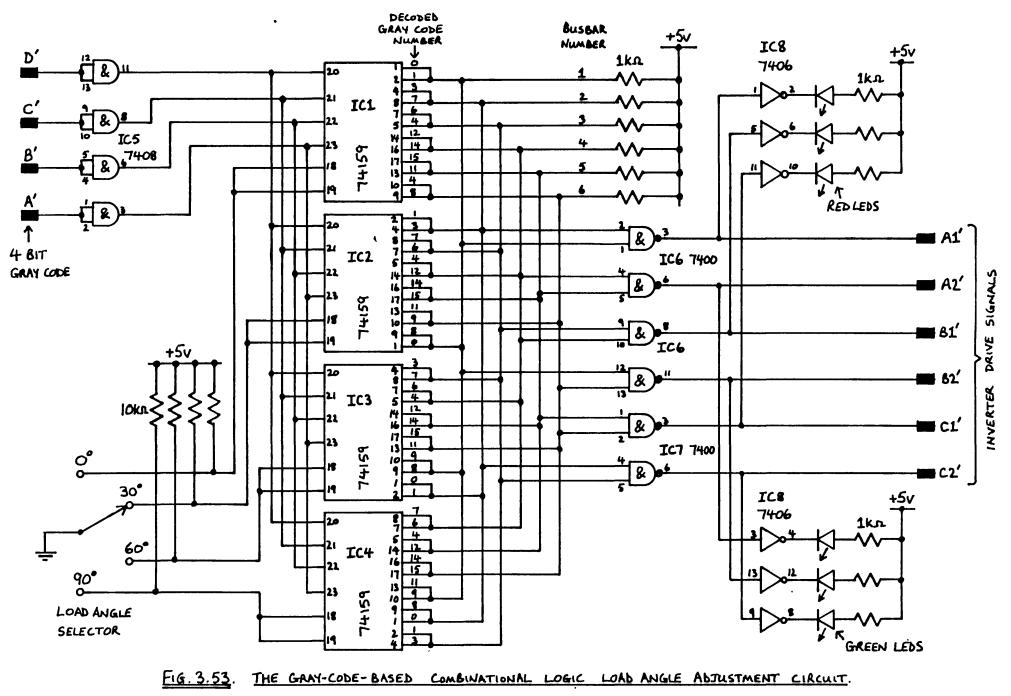

|     | 3.3.2.                |               | COMLOG (Combinational Logic)<br>Position Sensor Systems                                           | 91          |

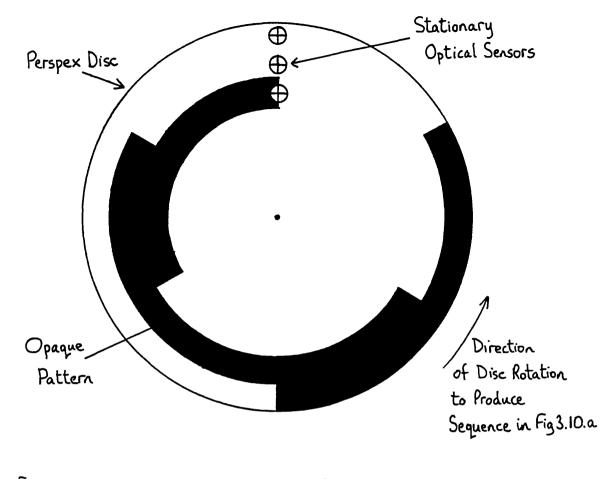

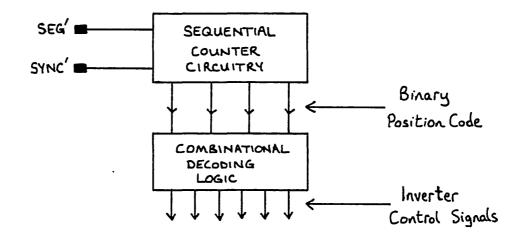

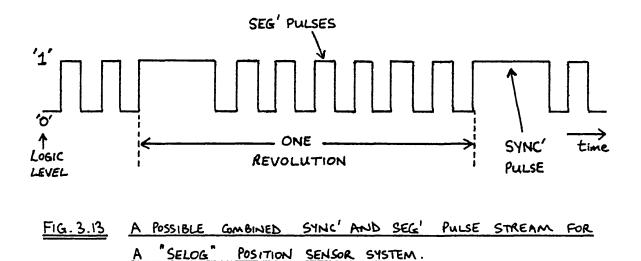

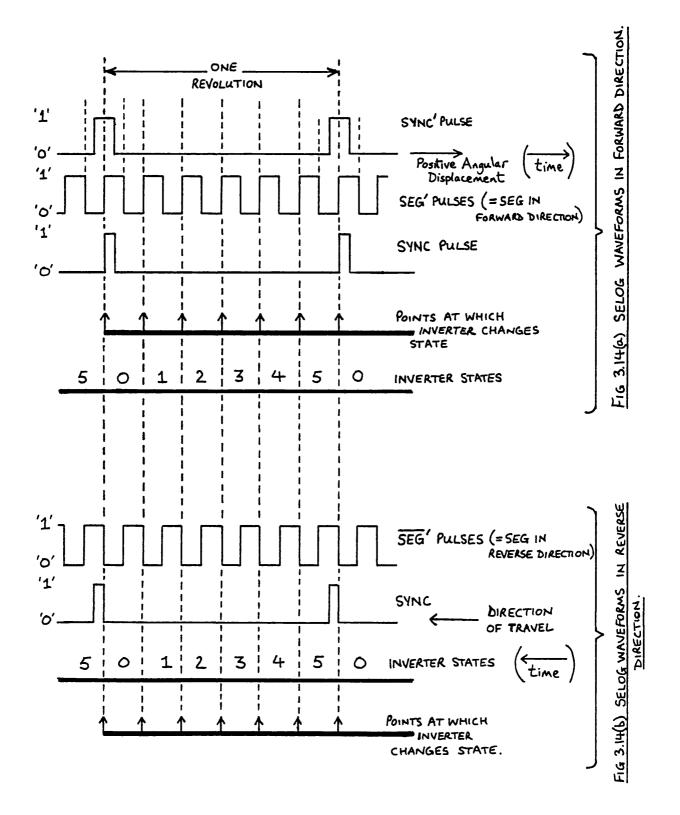

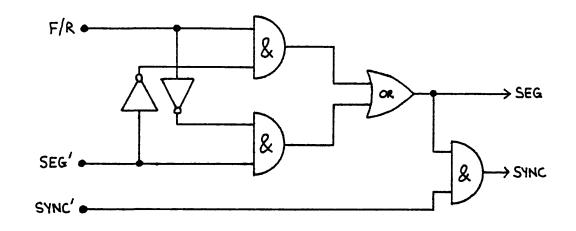

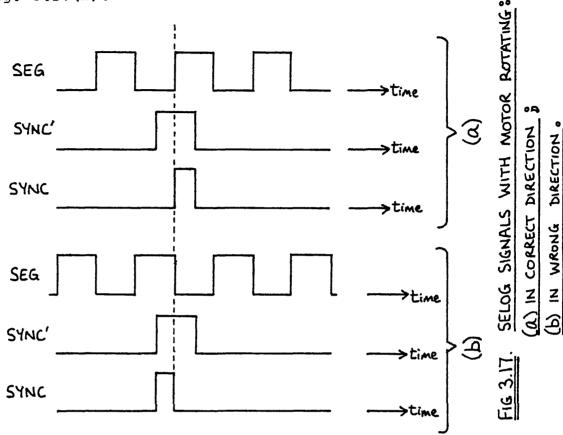

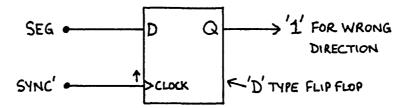

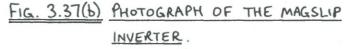

|     | 3.3.2.                | 5             | Basic Pulse Counting "Single Edge"<br>Sensing SELOG (Sequential Logic)<br>Position Sensor Systems | 95          |

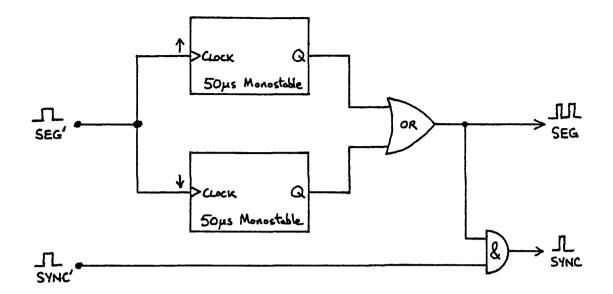

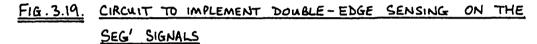

|     | 3.3.2.                |               | Improved-Resolution SELOG<br>Position Sensor System                                               | 107         |

|     | 3.3.2.                | (             | Brief Summary of the Pros and<br>Cons of NOLOG, COMLOG, and SELOG<br>Position Sensors             | 111         |

| 3.4 | Adjustme              | nt of         | Load Angle                                                                                        | 112         |

|     | 3.4.1                 | Time          | Delay Adjustment of Load Angle                                                                    | 113         |

|     | 3.4.2                 | Logi<br>Angle | cal Methods of Adjusting Load<br>e                                                                | 117         |

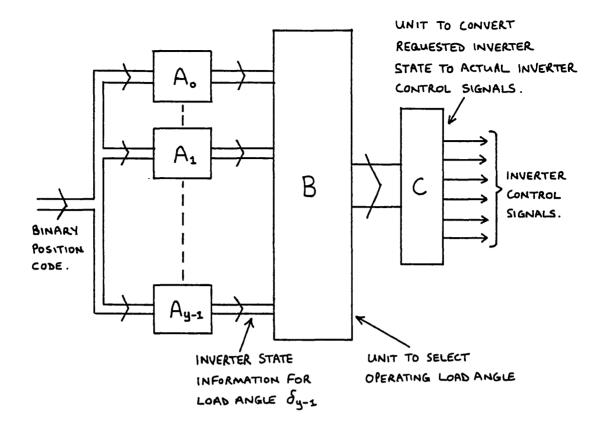

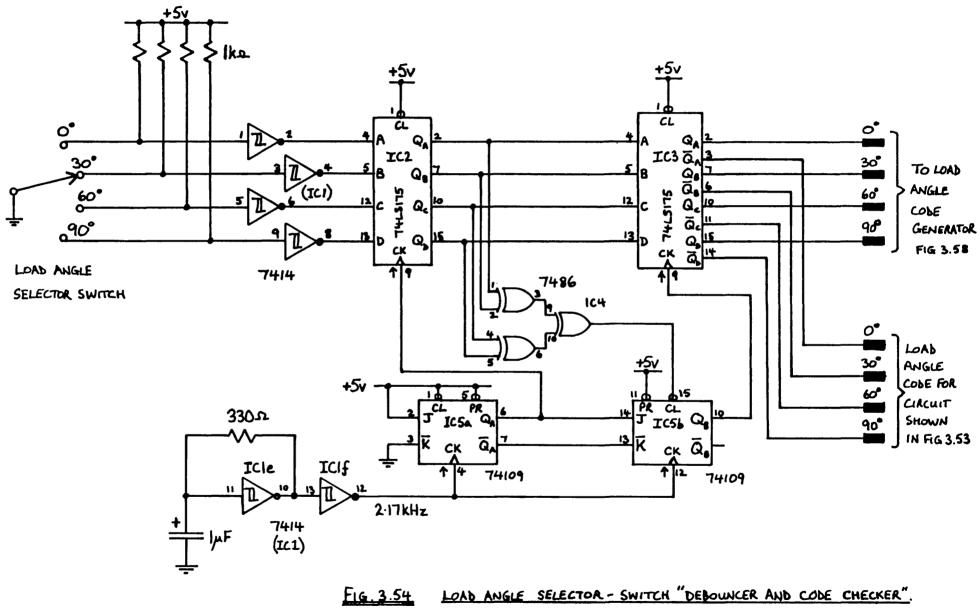

|     | 3.4.2.                |               | COMLOG - Based Load Angle<br>Adjustment Circuit                                                   | 123         |

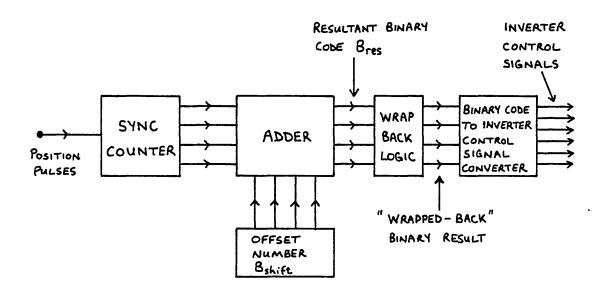

|     | 3.4.2.                |               | Discrete - Logic SELOG - Based<br>Load Angle Adjustment Circuit                                   | 125         |

|     | 3.4.2.                |               | Microprocessor - Based Load Angle<br>Adjustment Circuit                                           | 129         |

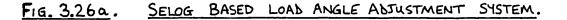

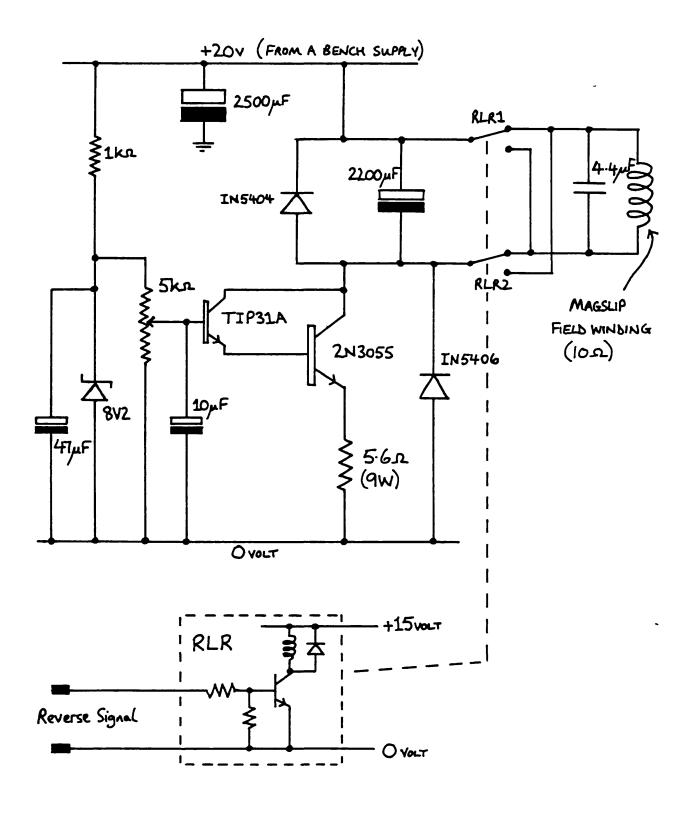

| 3.5 | Basic Ma              | gslip         | Motor Drive System                                                                                | 130         |

|     | 3.5.1                 | The l         | Magslip (Block D)                                                                                 | 131         |

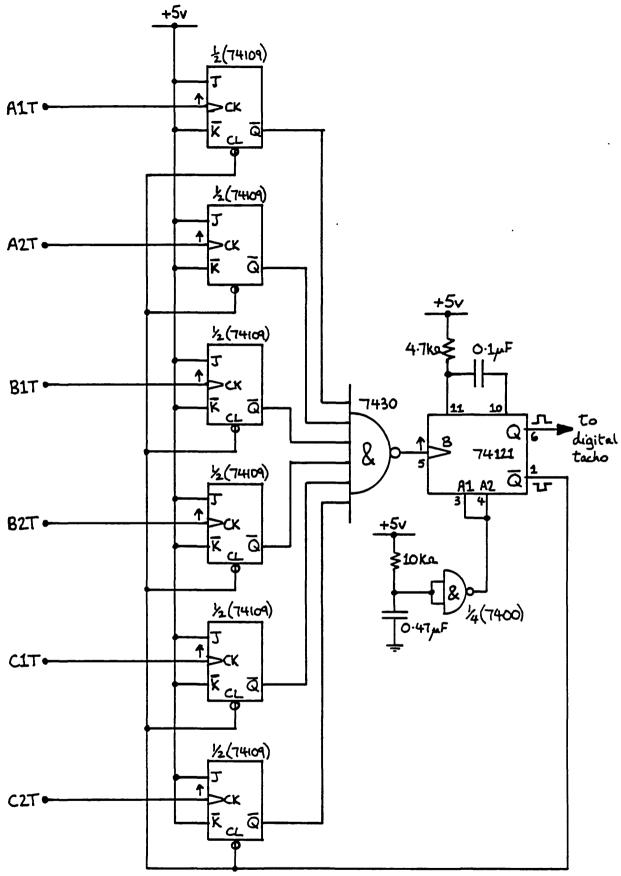

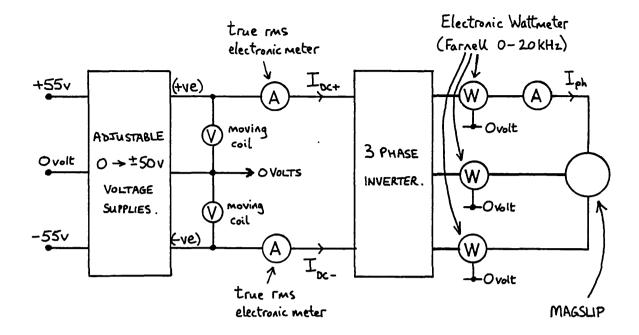

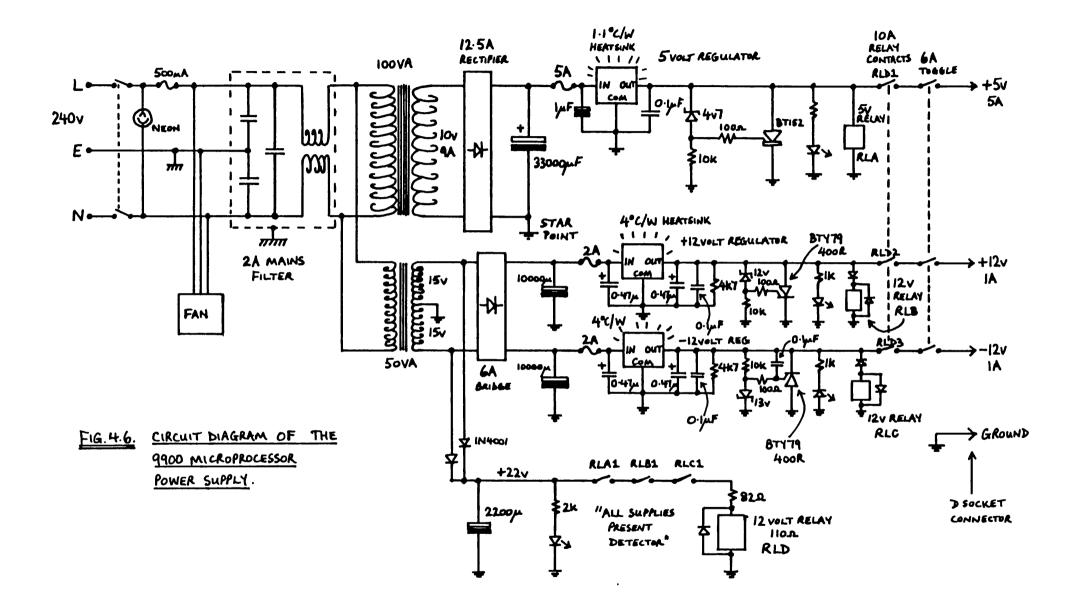

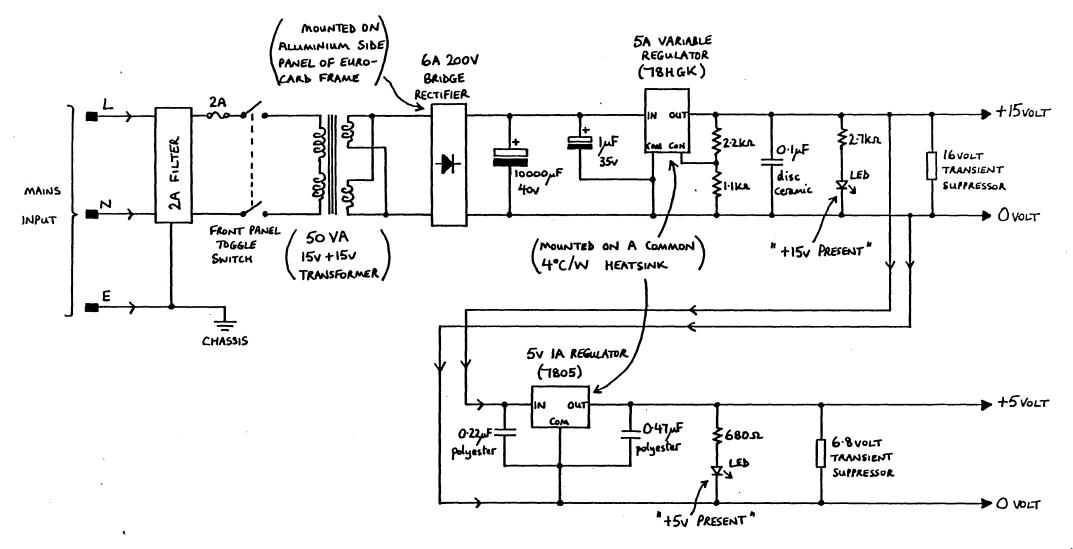

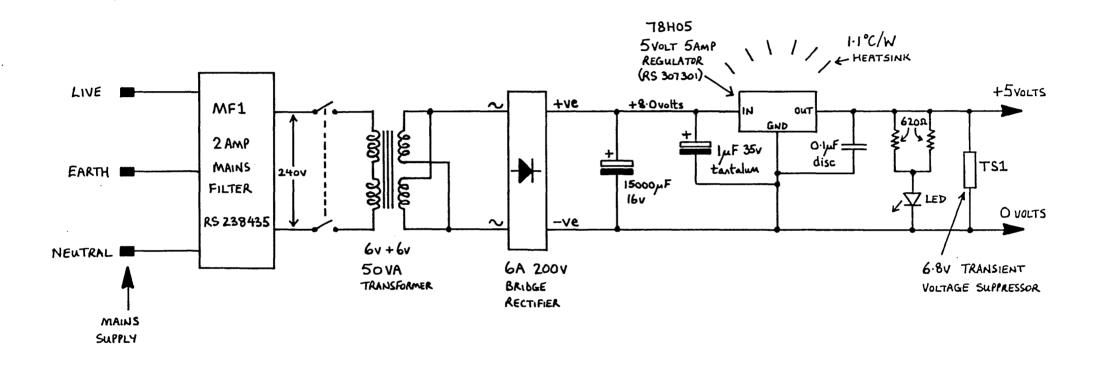

|     | 3.5.2                 |               | Regulated D.C. Power Supplies<br>ck A)                                                            | 132         |

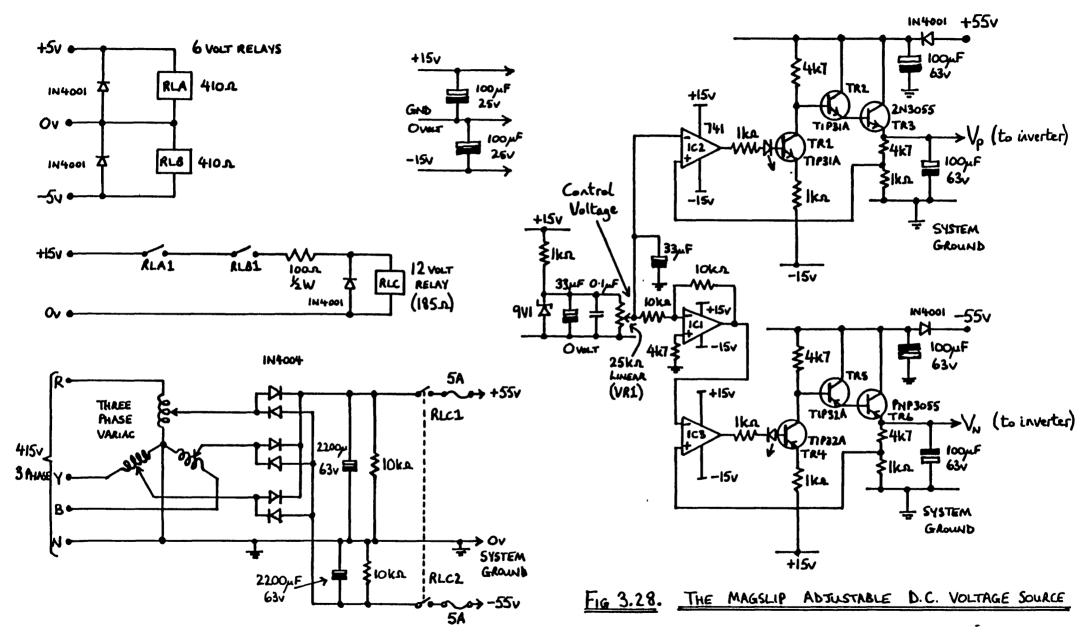

|     | 3.5.3                 |               | Adjustable D.C. Voltage Source<br>ck B)                                                           | 132         |

|     | 3.5.4                 | The s         | Shaft Position Sensor (Block E)                                                                   | 134         |

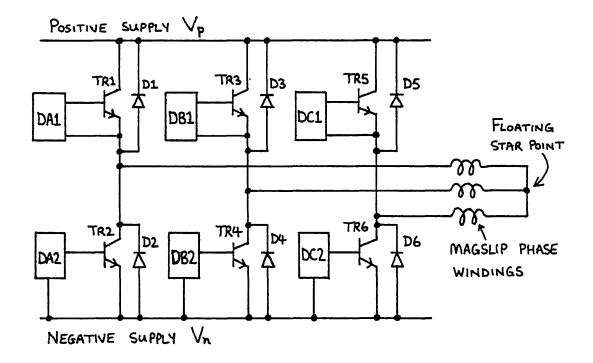

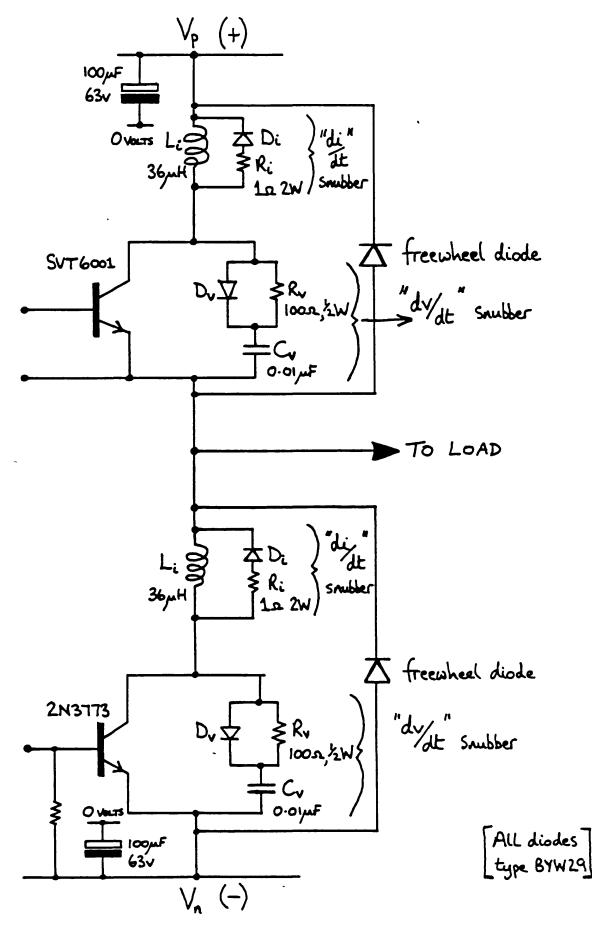

|     | 3.5.5                 |               | i Square Wave Voltage Source<br>rter (Block C)                                                    | 135         |

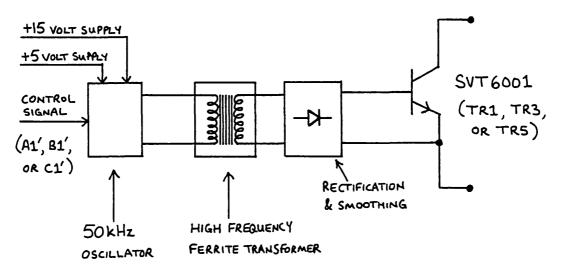

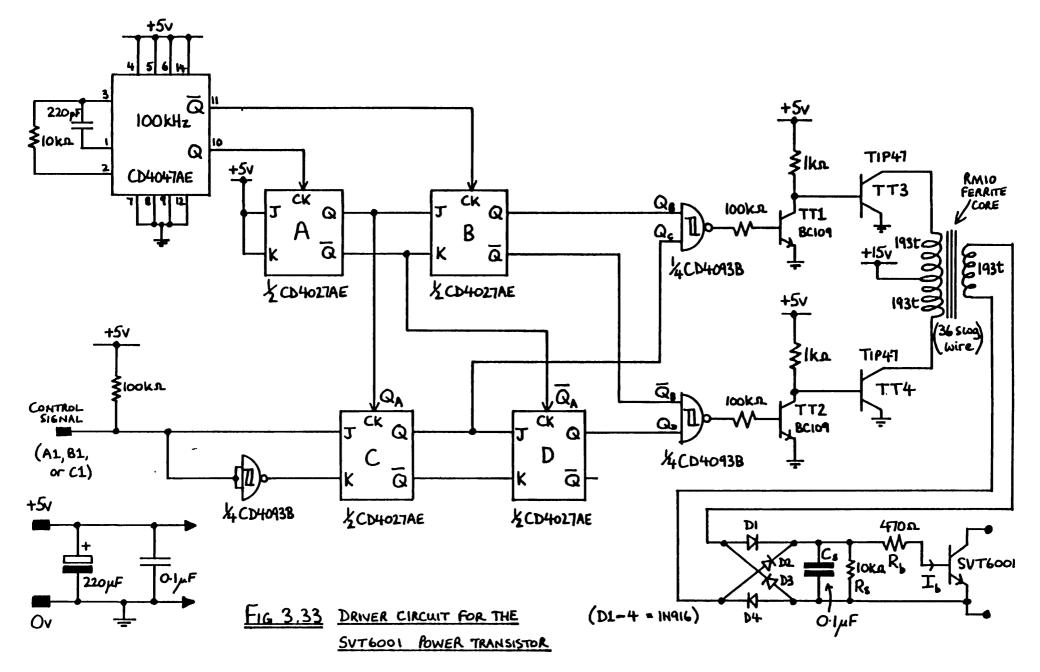

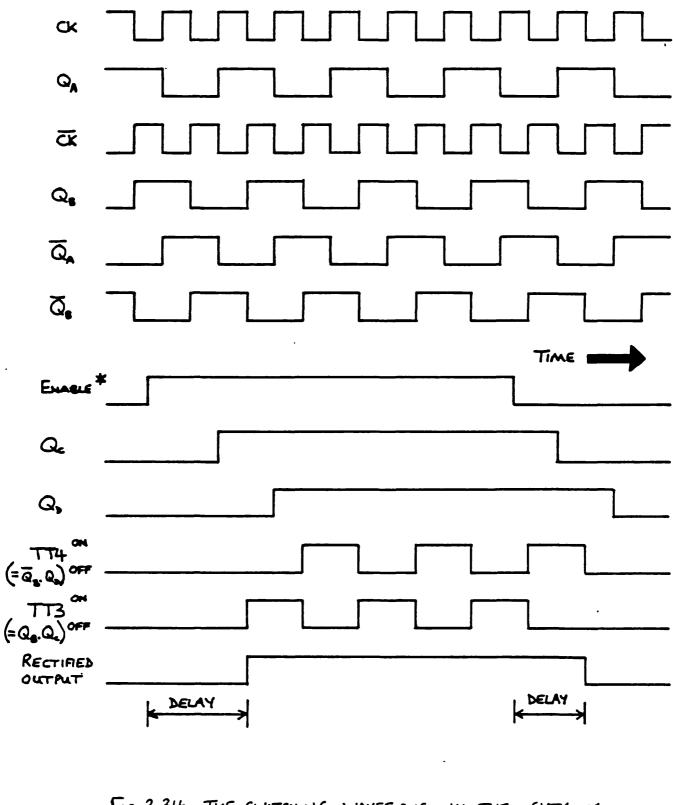

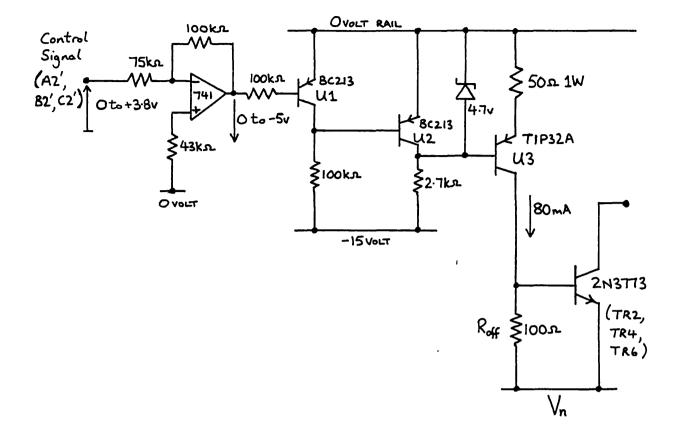

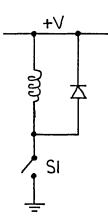

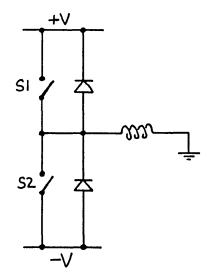

|     | 3.5.5.                |               | Positive Rail Transistor Driver<br>Circuit                                                        | 138         |

|     | 3.5.5.                |               | Negative Rail Transistor Driver<br>Circuit                                                        | <b>1</b> 42 |

|     | 3.5.5.                |               | Snubber Protection for the Power<br>Transistors                                                   | 144         |

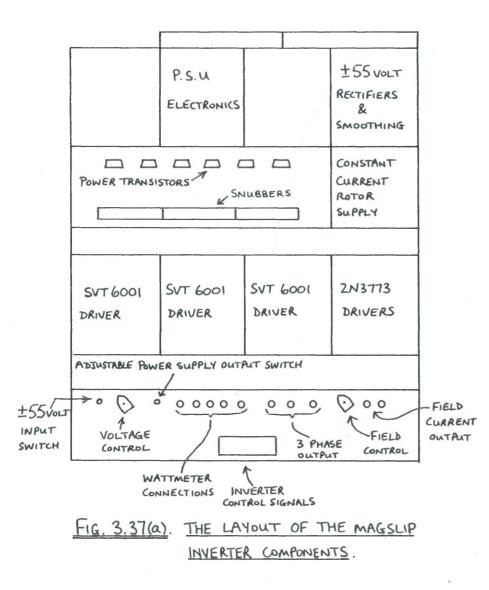

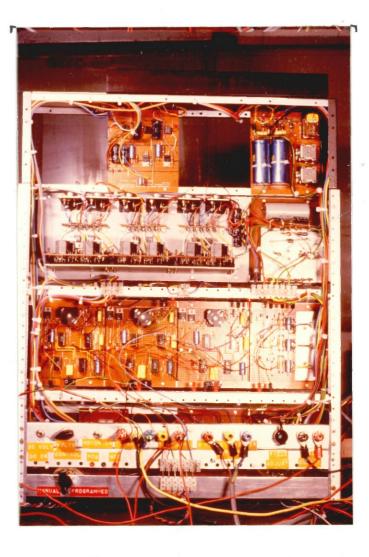

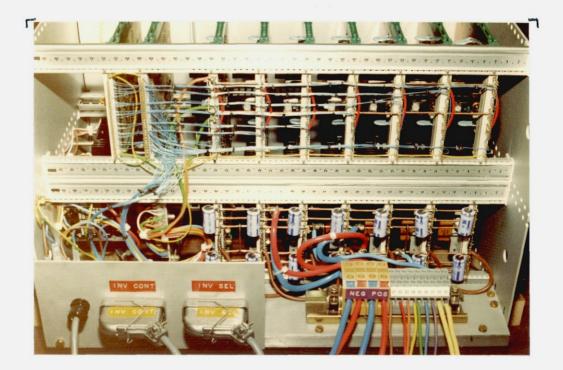

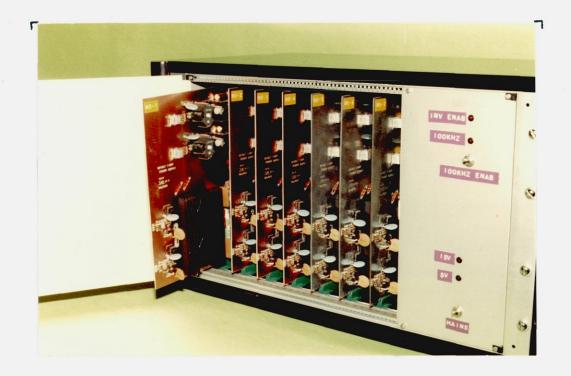

|     | 3.5.5.                | 4 :           | Inverter Assembly                                                                                 | 147         |

.

•

-

|      |                     |                                                                                            | Page        |

|------|---------------------|--------------------------------------------------------------------------------------------|-------------|

|      | 3.5.6               | Tachometer Signal Generator<br>(Block G)                                                   | 147         |

|      | 3.5.7               | Magslip Field Current Source<br>(Block H)                                                  | 150         |

|      | 3.5.8               | Operating Comments                                                                         | 150         |

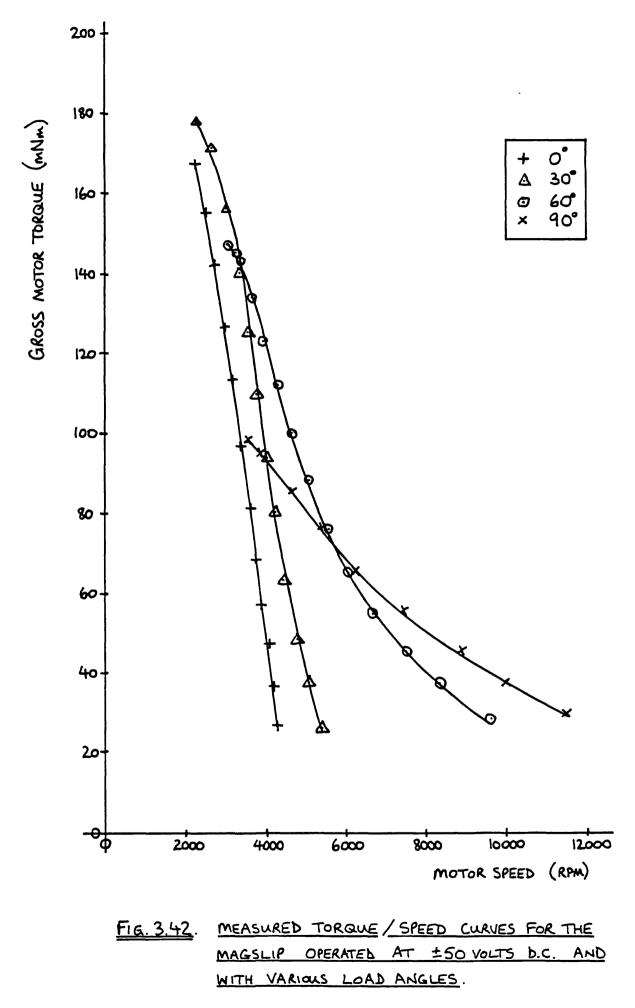

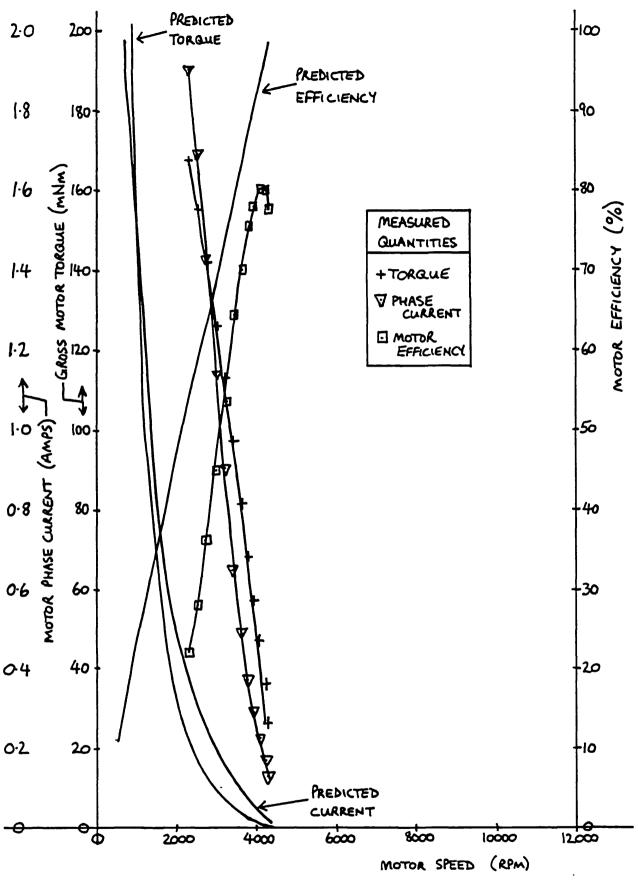

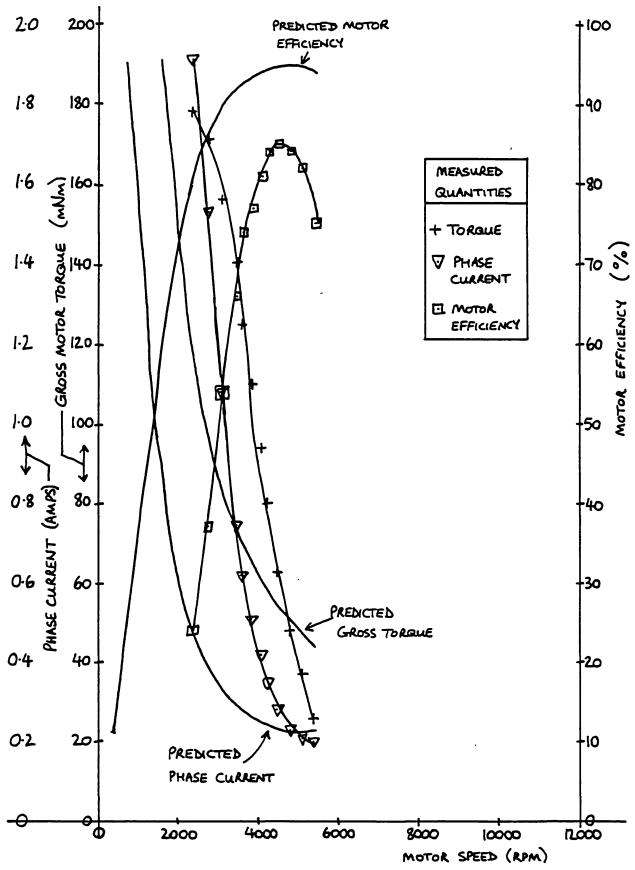

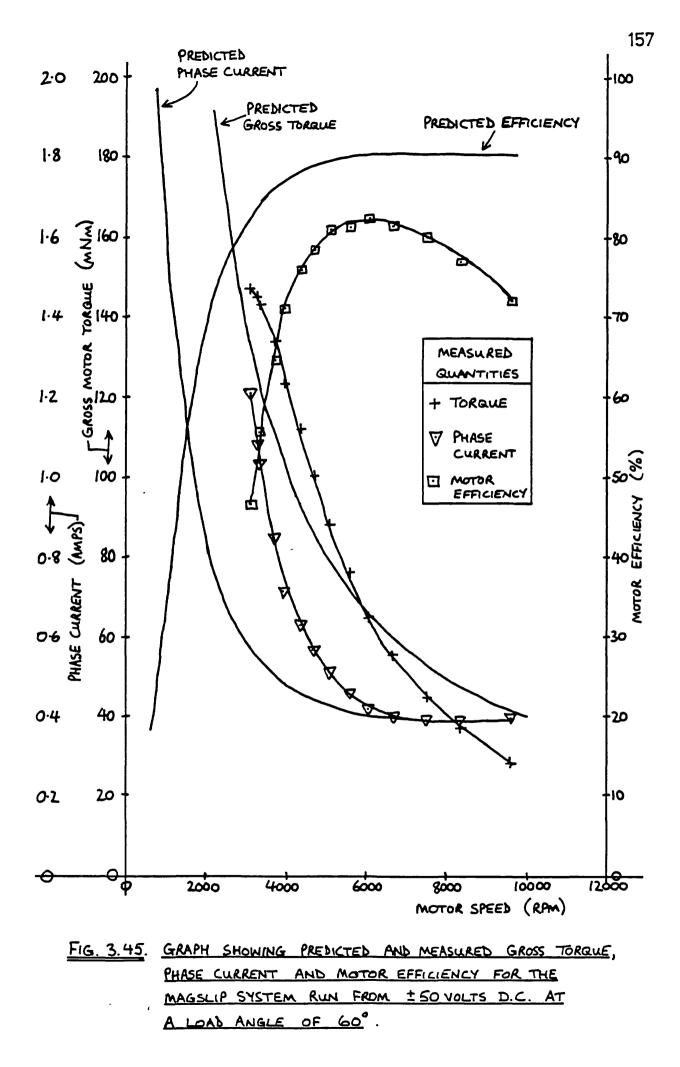

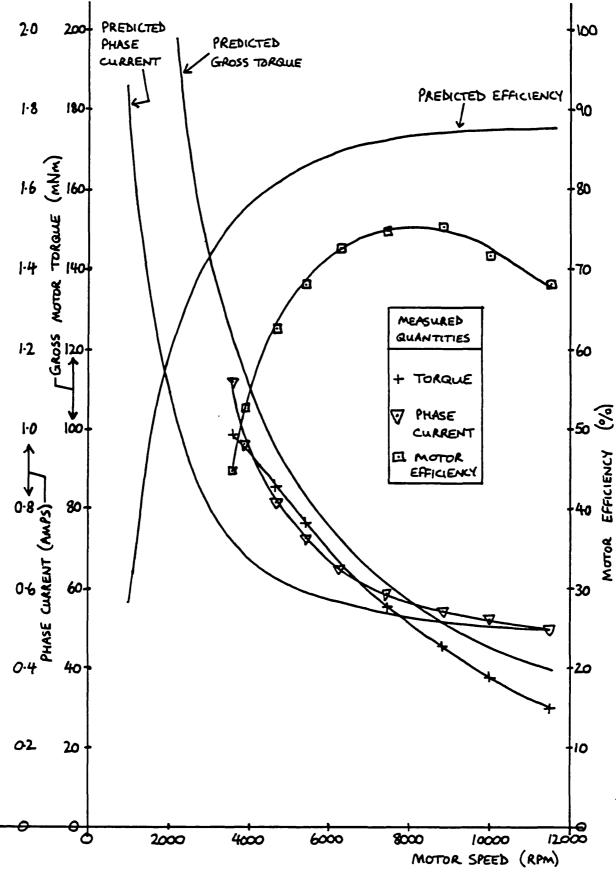

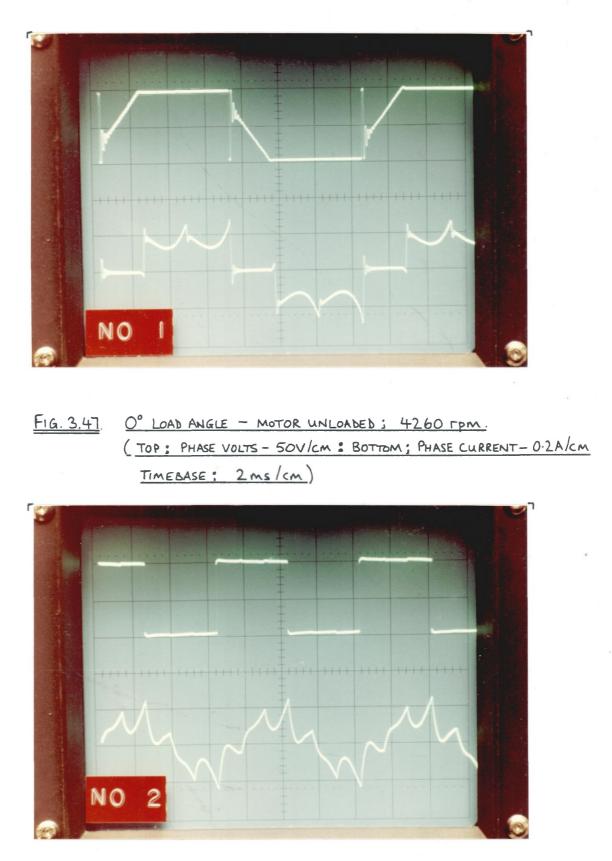

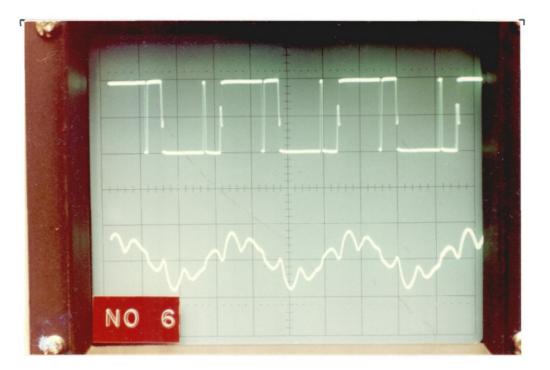

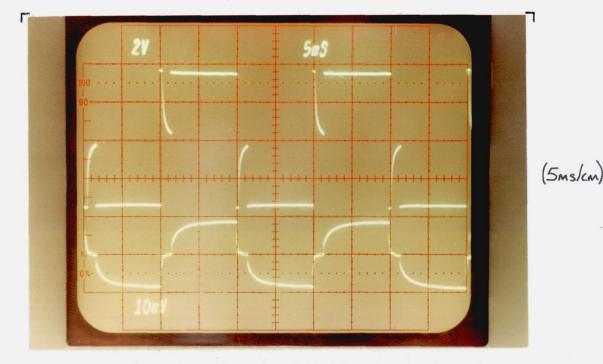

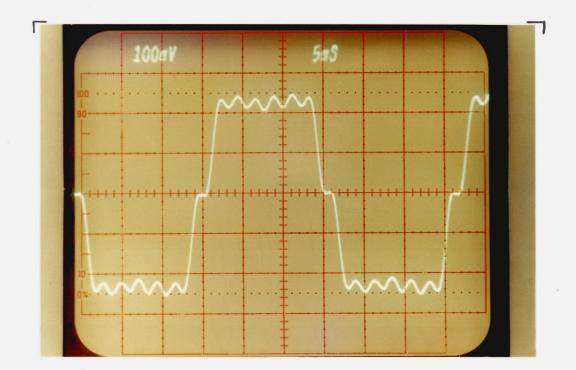

| 3.6  | Magslip             | Operating Characteristics                                                                  | 152         |

| 3.7  | Electron            | ic Load Angle Adjustment Circuits                                                          | 164         |

|      | 3.7.1               | 'COMLOG' Based System                                                                      | 164         |

|      | 3.7.2               | 'SELOG' Based System                                                                       | 168         |

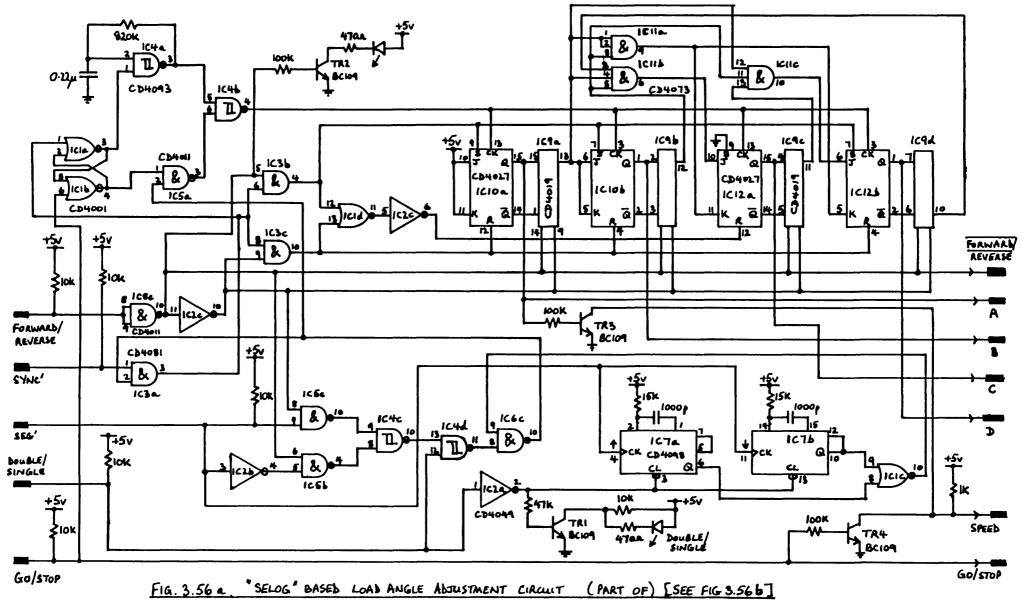

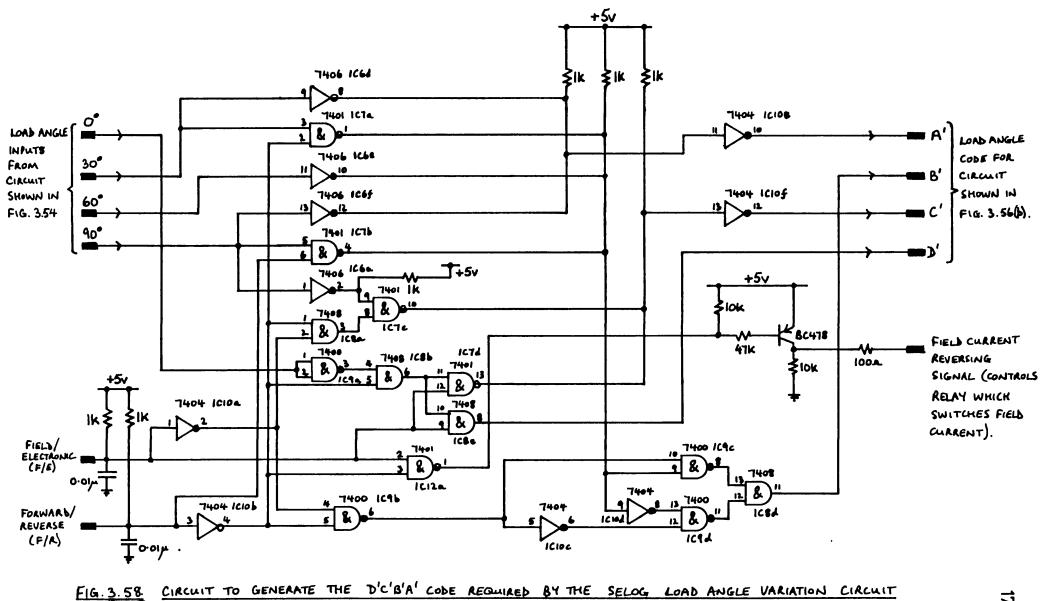

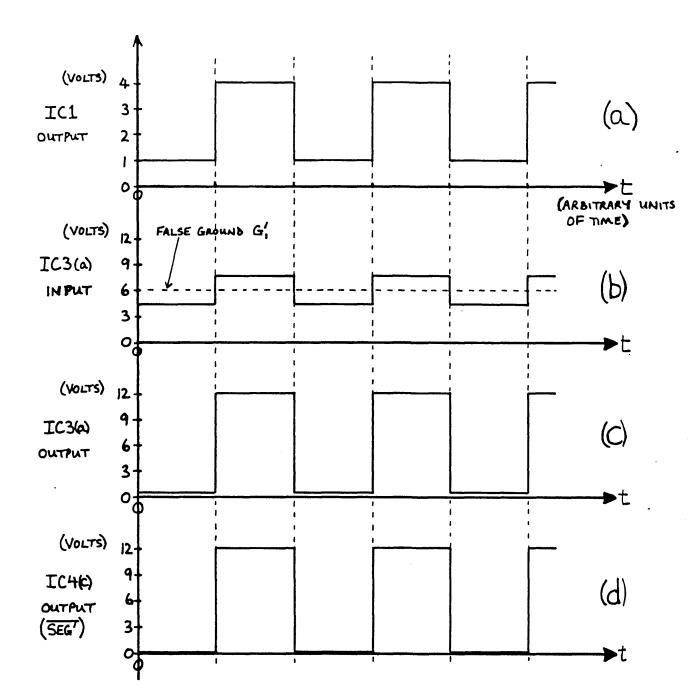

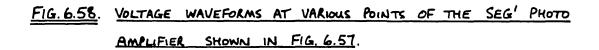

|      | 3.7.2.              | 1 SEG and SYNC Signal Generation<br>(fig. 3.56(a))                                         | 173         |

|      | 3.7.2.              | 2 Starting and Synchronising<br>Circuit (fig. 3.56(a))                                     | 174         |

|      | 3.7.2.              | 3 SEG Signal Counter Circuit<br>(fig. 3.56(a))                                             | 174         |

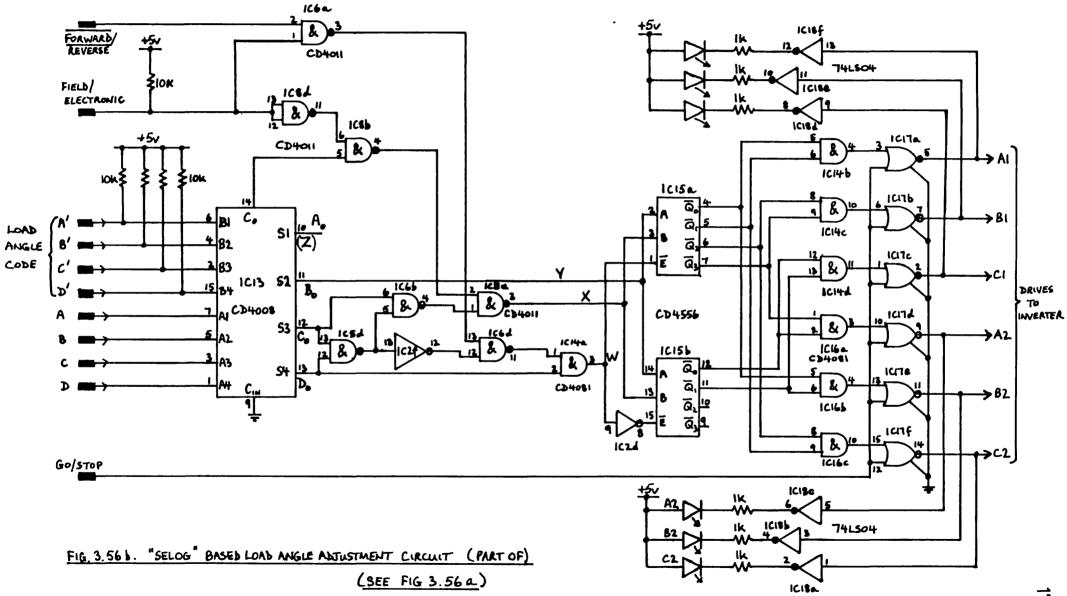

|      | 3.7.2.              | 4 Binary Position Code Adder<br>Circuit (fig. 3.56(b))                                     | 175         |

|      | 3.7.2.              | 5 Resultant Binary Code<br>Processing (fig. 3.56(b))                                       | 177         |

|      | 3.7.2.              | 6 Generation of Inverter Control<br>Signals (fig. 3.56(b))                                 | 177         |

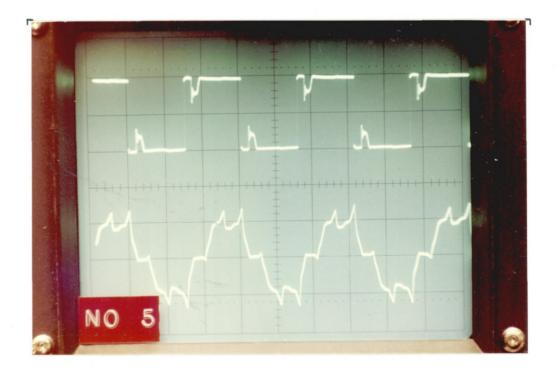

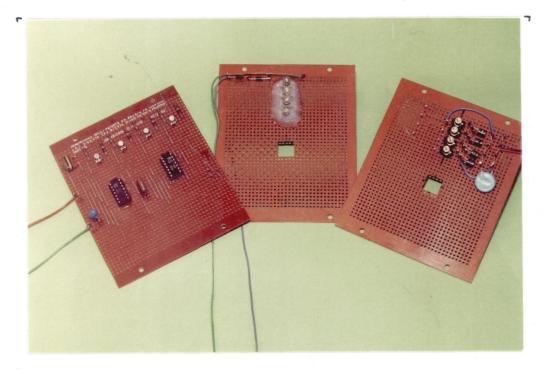

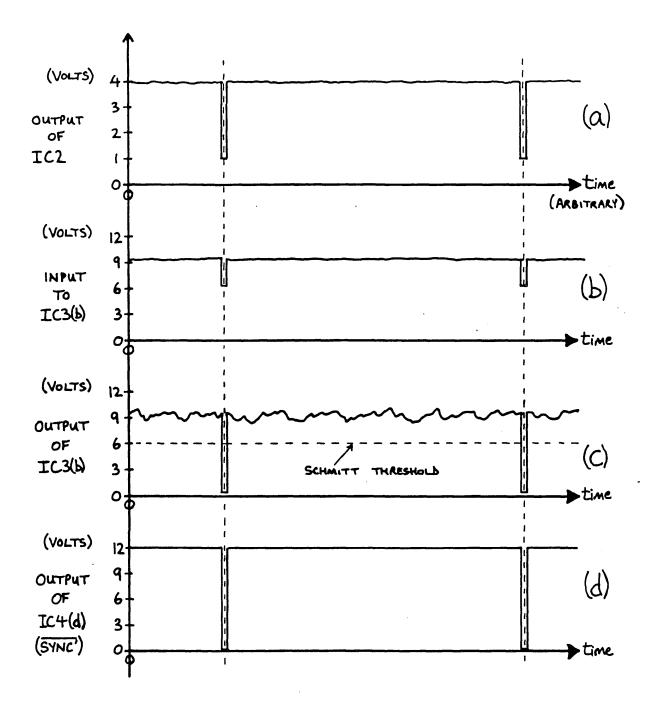

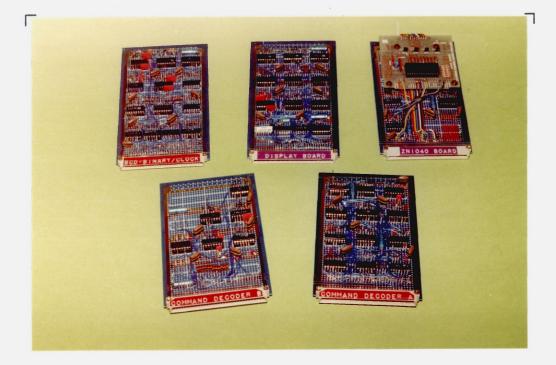

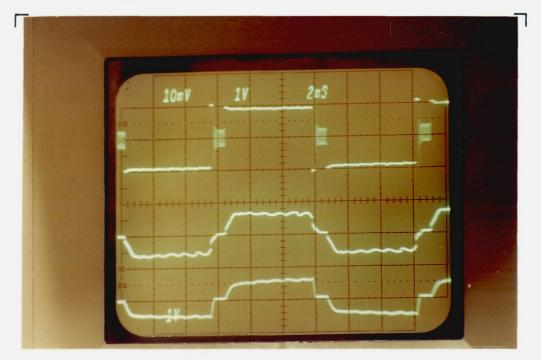

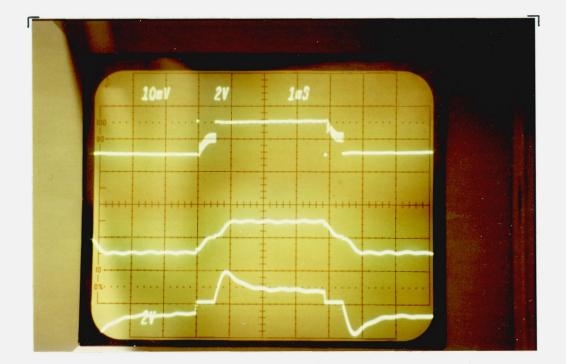

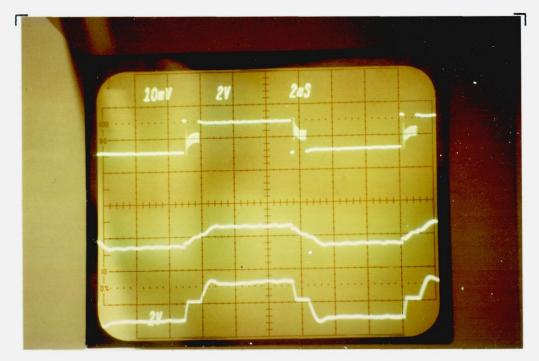

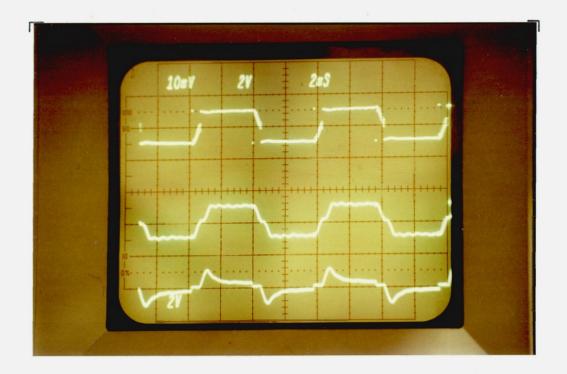

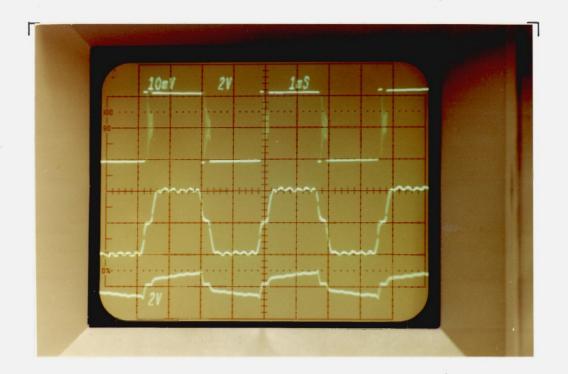

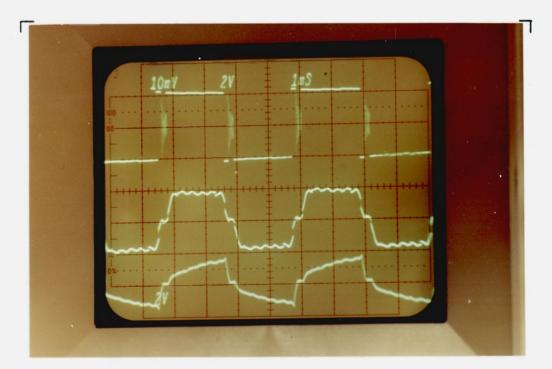

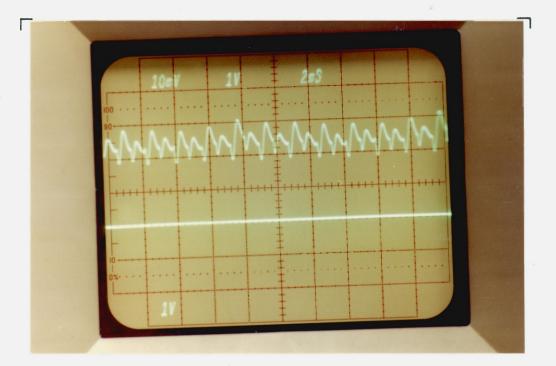

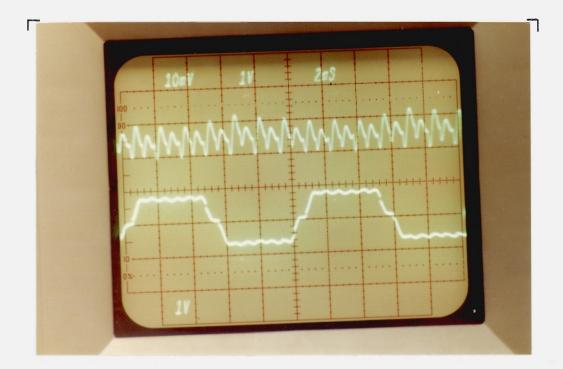

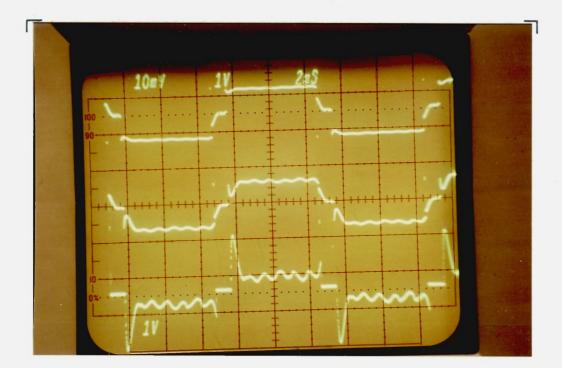

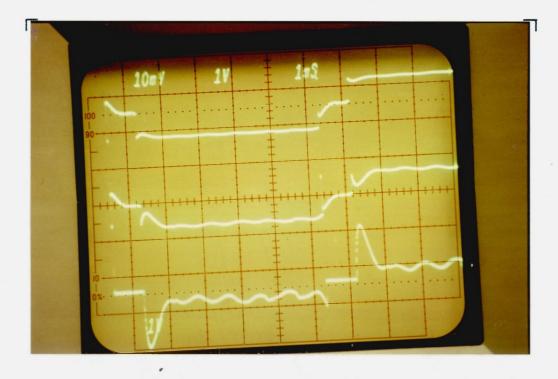

|      | 3.7.3               | Photographs of the Load Angle<br>Adjustment Electronics                                    | 179         |

| 3.8  | Conclusi            | ons                                                                                        | 179         |

| CHAP | TER 4:              | THE USE OF A TEXAS TMS9900<br>MICROPROCESSOR TO AUTOPILOT<br>HIGH SPEED SYNCHRONOUS MOTORS | 182         |

| 4.1  | Introduc            | ction                                                                                      | 182         |

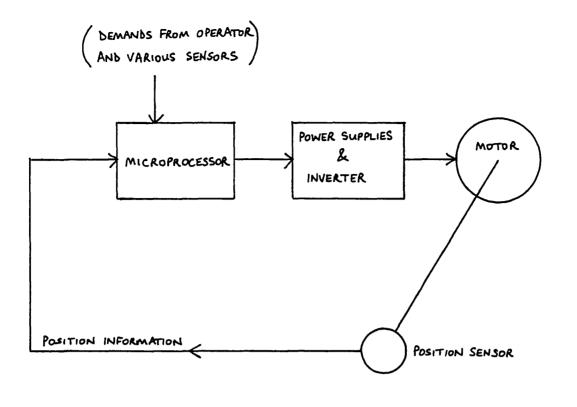

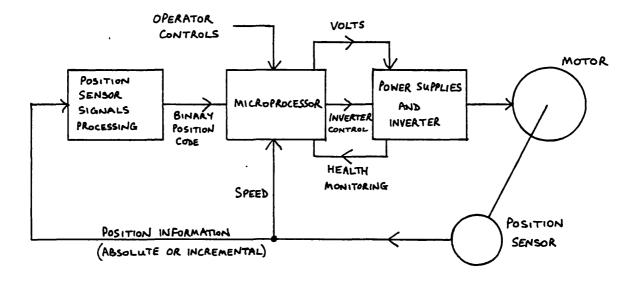

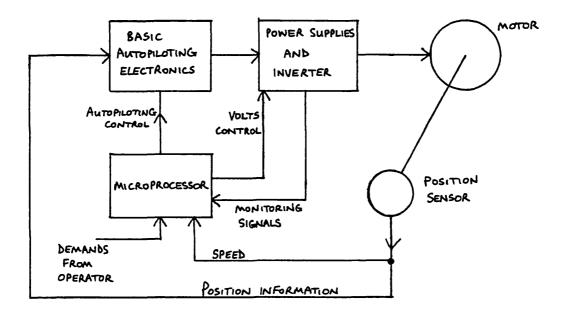

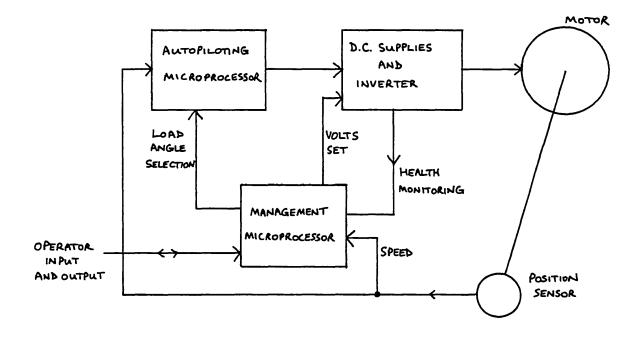

| 4.2  | The Use<br>Motor Sy | of Microprocessors in Autopiloted<br>stems                                                 | 183         |

| 4.3  |                     | to Consider in the Implementation of a<br>Decessor Autopiloted Synchronous Motor           | 192         |

| 4.4  |                     | ice of a Suitable Microprocessor for<br>n Speed "Square Wave" Synchronous<br>ystem         | <b>1</b> 94 |

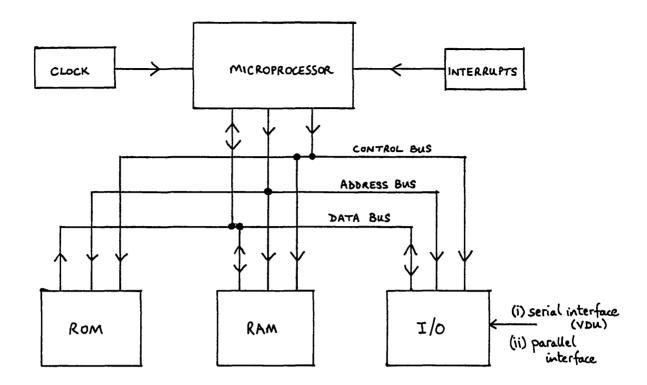

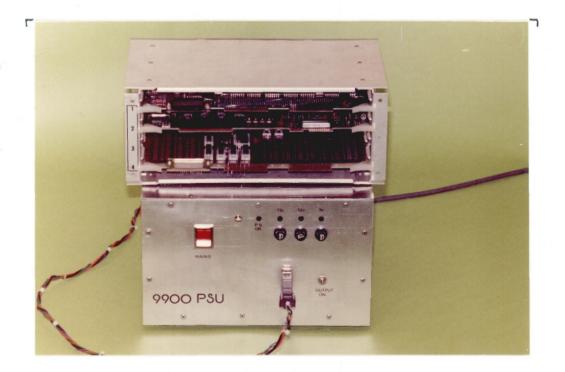

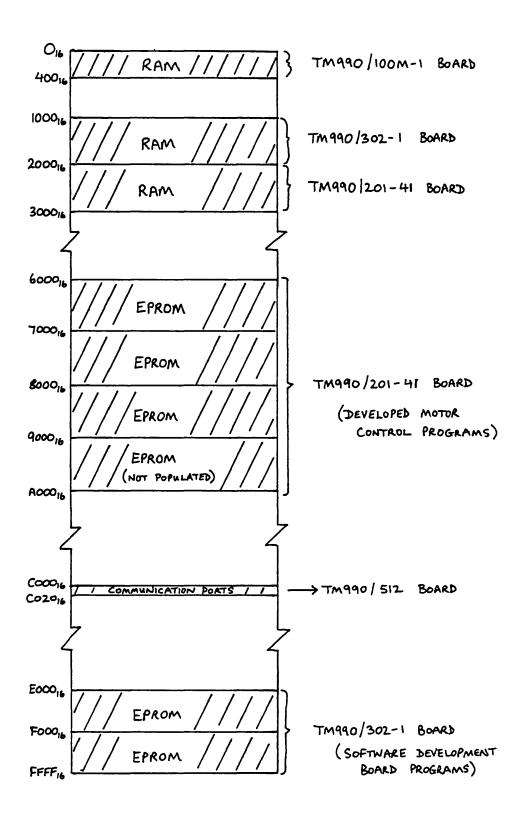

| 4.5  | The TMS9            | 9900 Microprocessor System                                                                 | 196         |

|      | 4.5.1               | The "Architecture" of the TMS9900<br>Microprocessor                                        | 196         |

|      | 4.5.2               | Basic Microprocessor System<br>Implementation                                              | 200         |

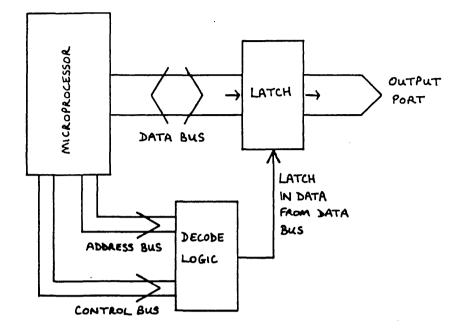

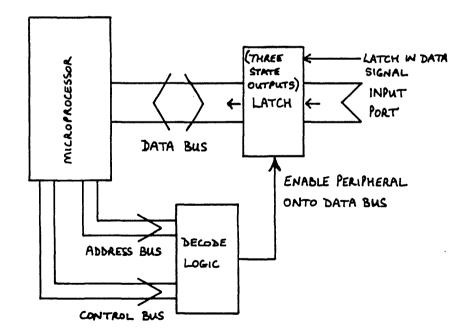

| 4.6  |                     | roprocessor System Interfacing Logic -<br>nterfacing Philosophy                            | 20 <b>7</b> |

| 4.7  | Practica            | al Implementation of System Interfacing                                                    | 220         |

|      |                     |                                                                                            |             |

,

•

6

Page

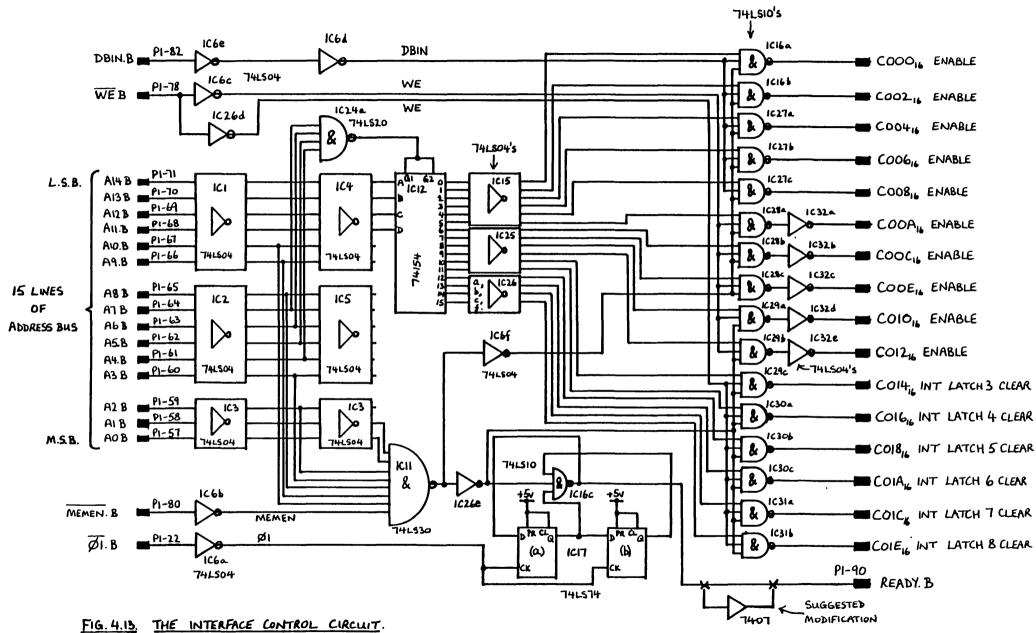

|         | Memory Mapped Interface Control<br>Circuit                                                                | 222              |

|---------|-----------------------------------------------------------------------------------------------------------|------------------|

|         | The Provision of all Remaining<br>I/O Requirements                                                        | 229              |

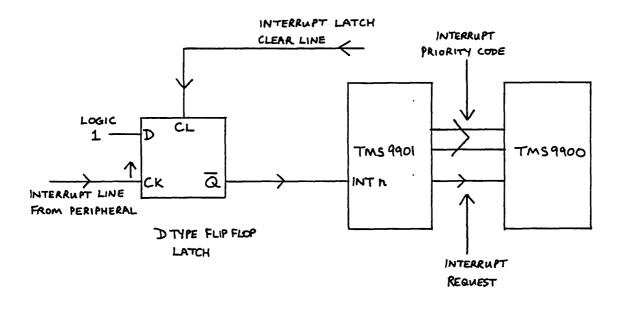

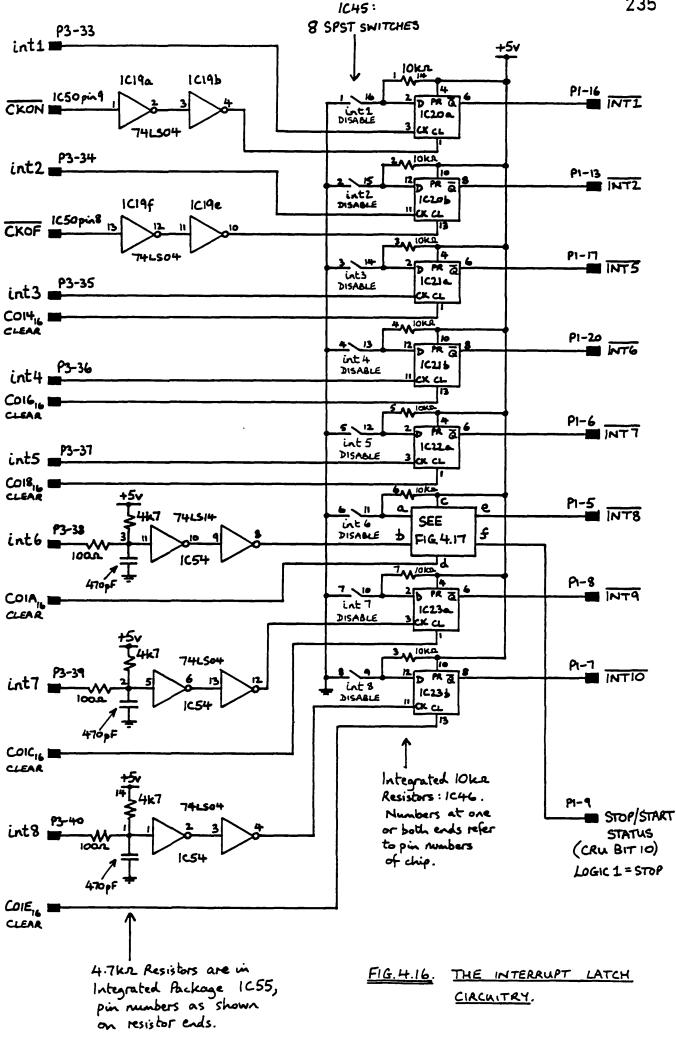

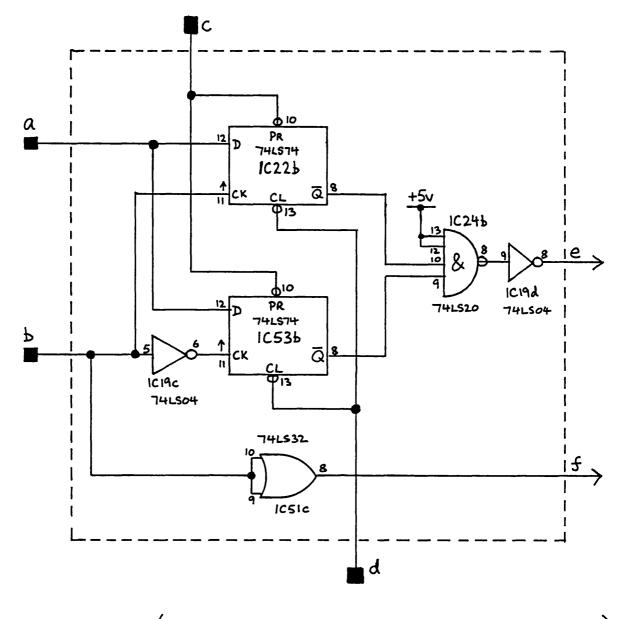

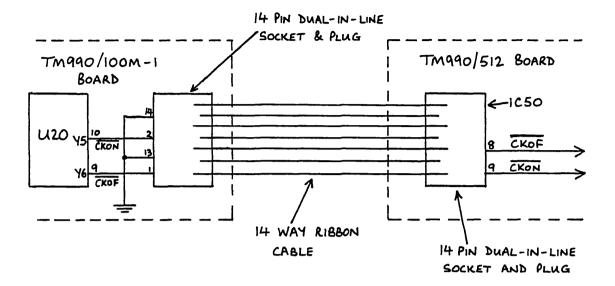

|         | The Interrupt Latch Circuitry and the<br>Associated TMS9900 Interrupt Prioritie                           | 23 <b>1</b><br>s |

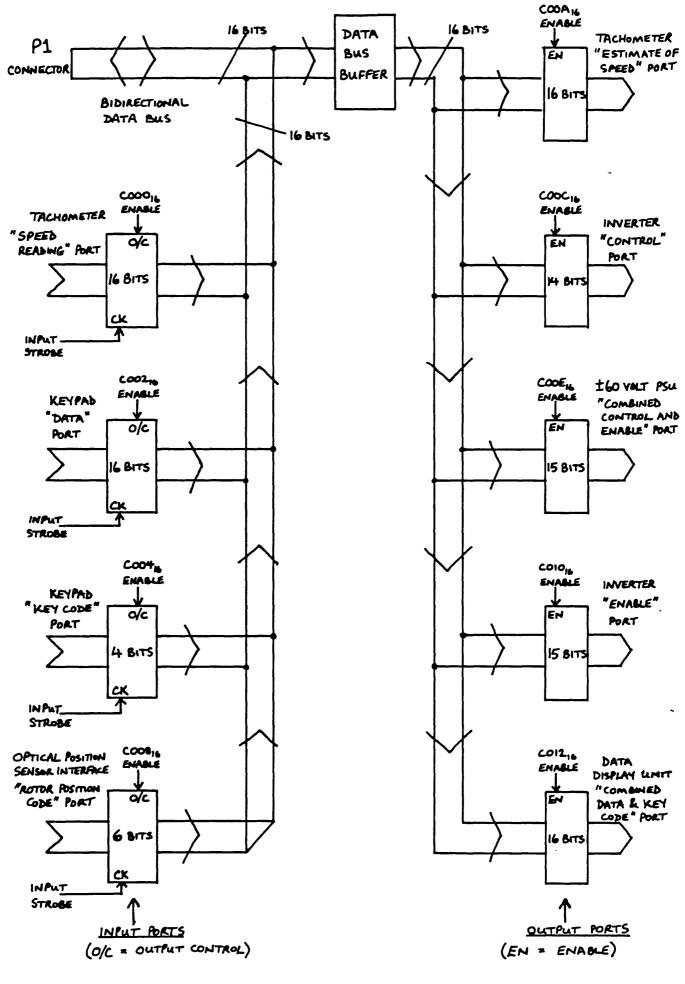

| 4.7.4   | The Input and Output Port Organisation                                                                    | 238              |

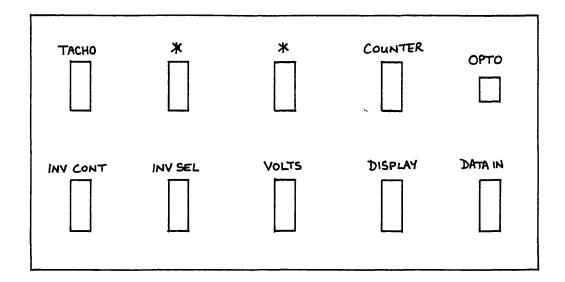

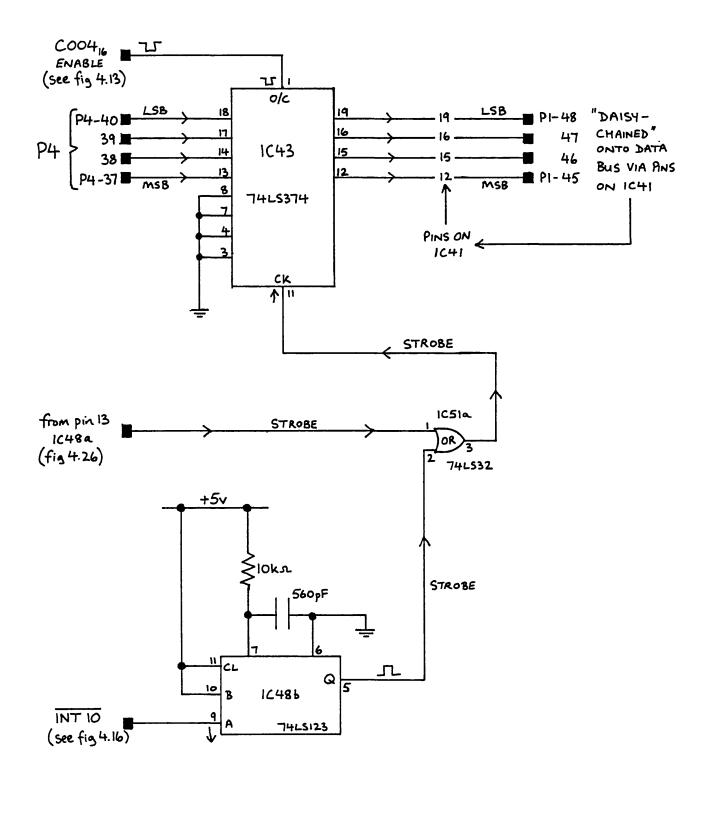

| 4.7.4.1 | Data Bus Output Buffer                                                                                    | 241              |

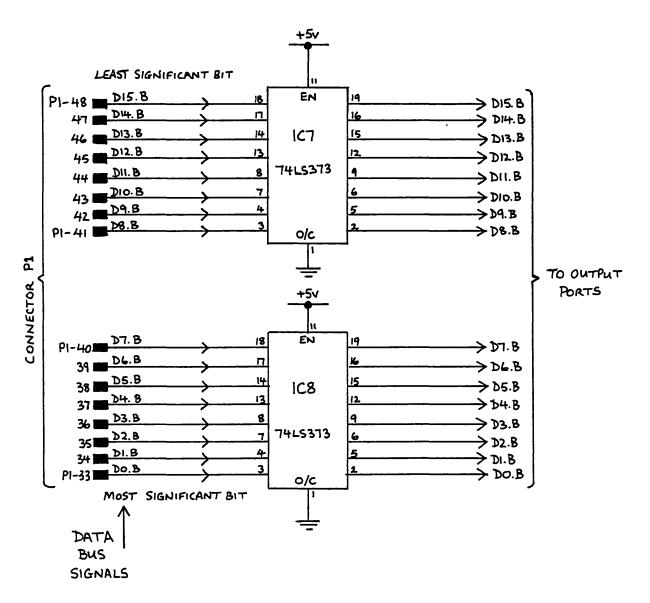

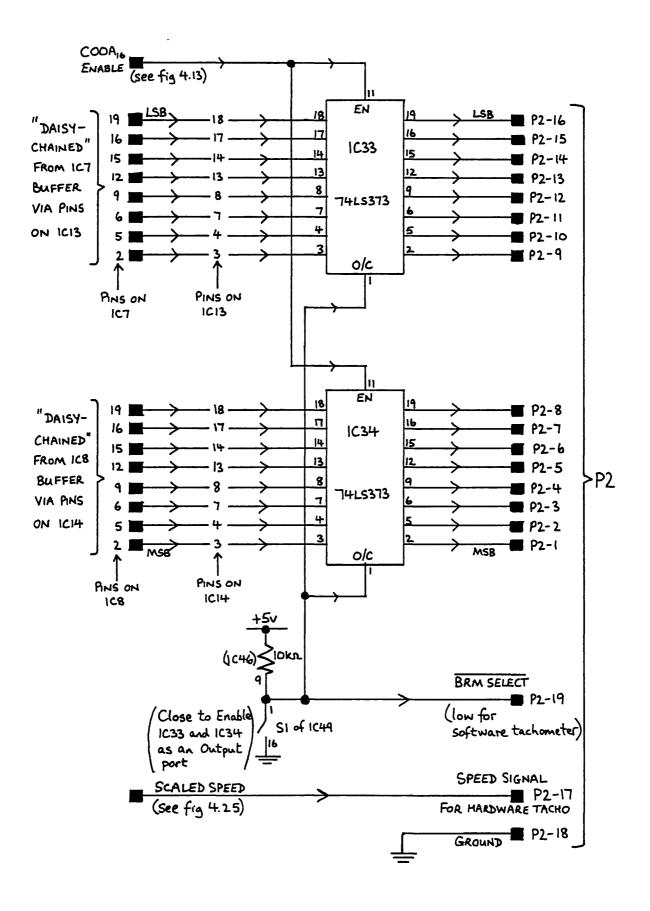

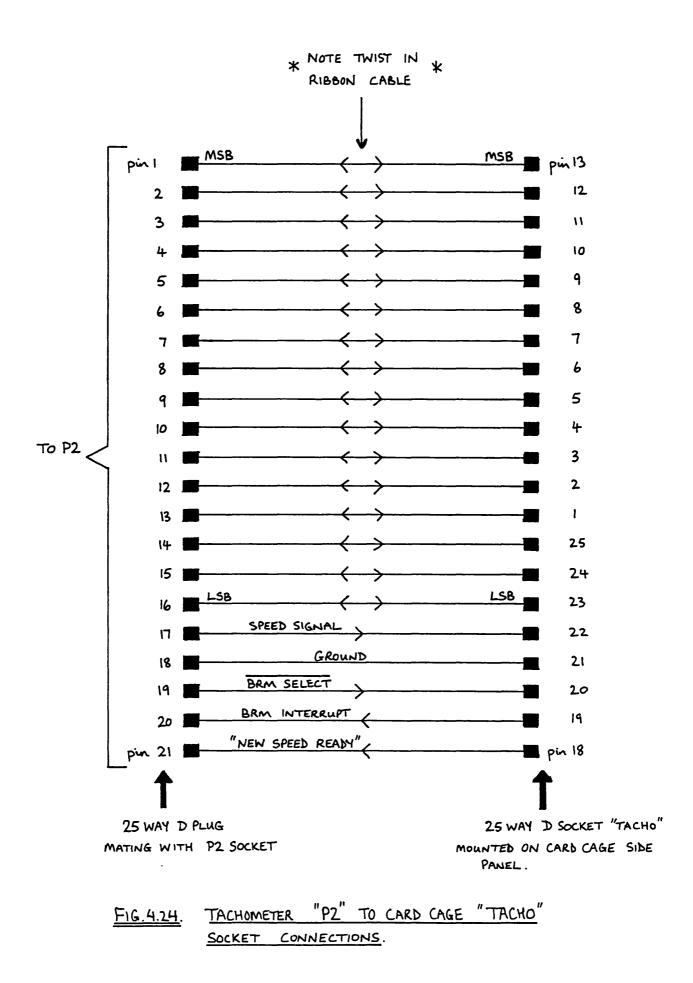

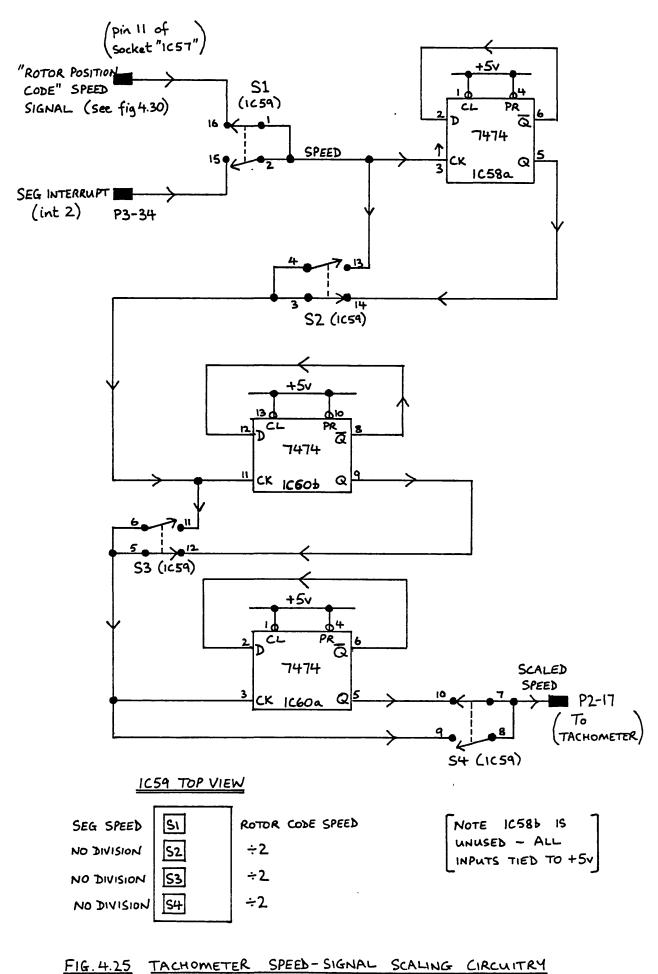

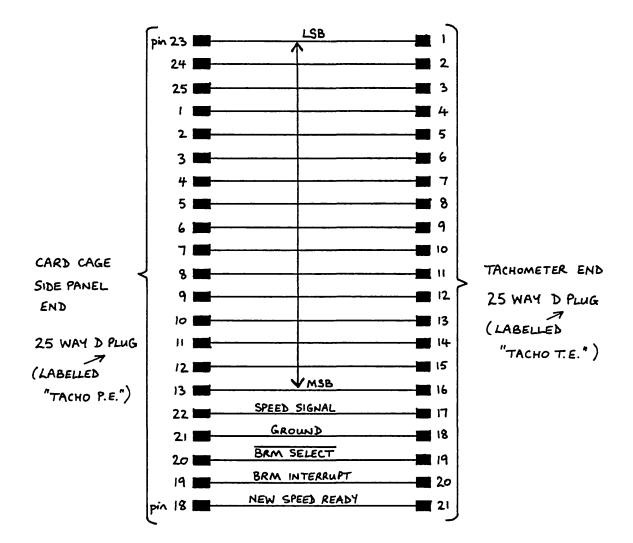

| 4.7.4.2 | The Tachometer Input and<br>Output Ports                                                                  | 242              |

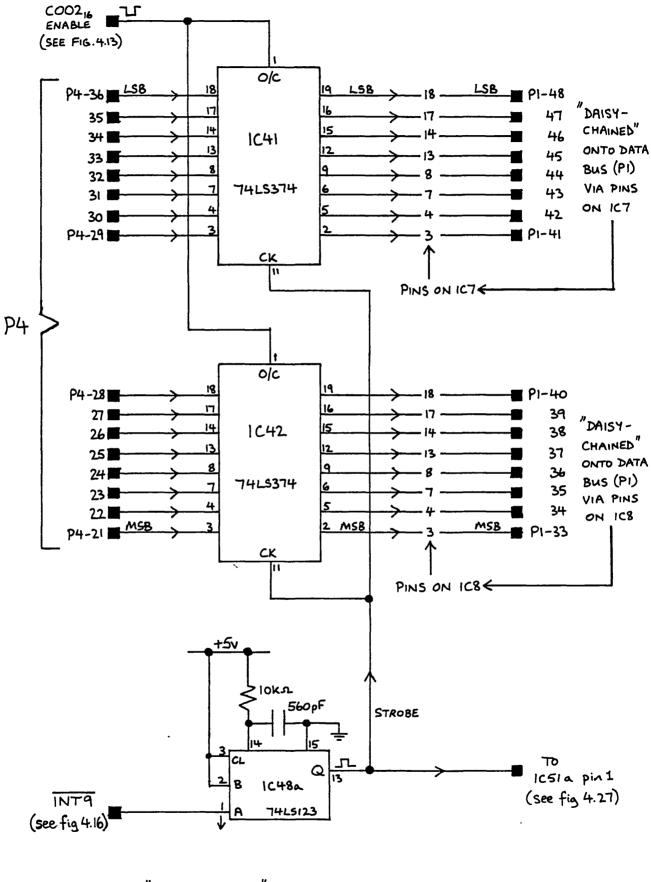

| 4.7.4.3 | The "Keypad Data" Input Port                                                                              | 24 <b>7</b>      |

| 4.7.4.4 | The Keypad "Key Code" Input Port                                                                          | 250              |

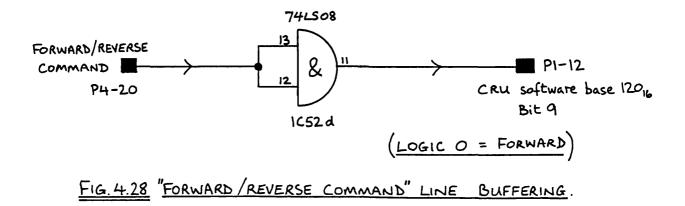

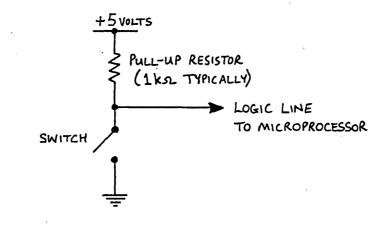

| 4.7.4.5 | The "Forward/Reverse Command"<br>Input Line                                                               | 250              |

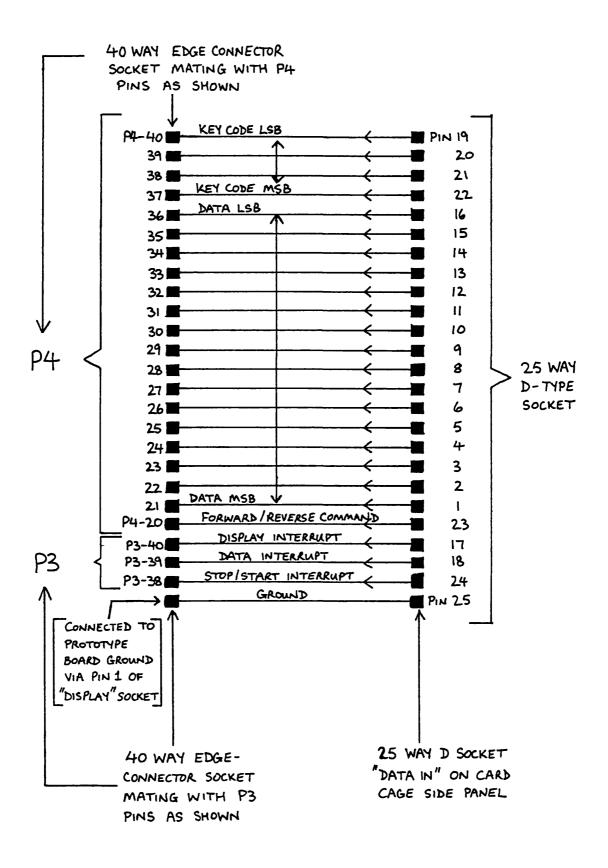

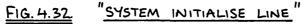

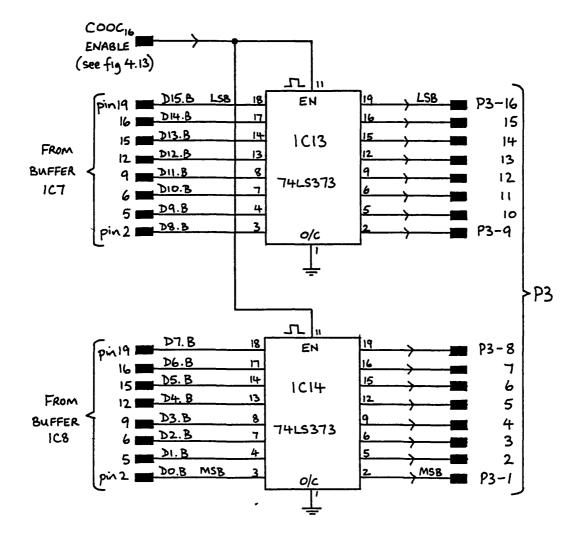

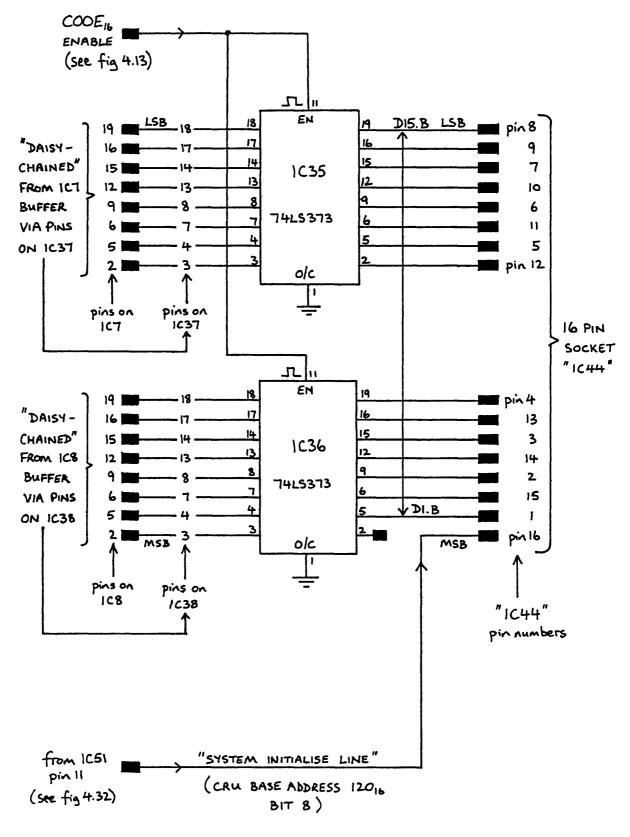

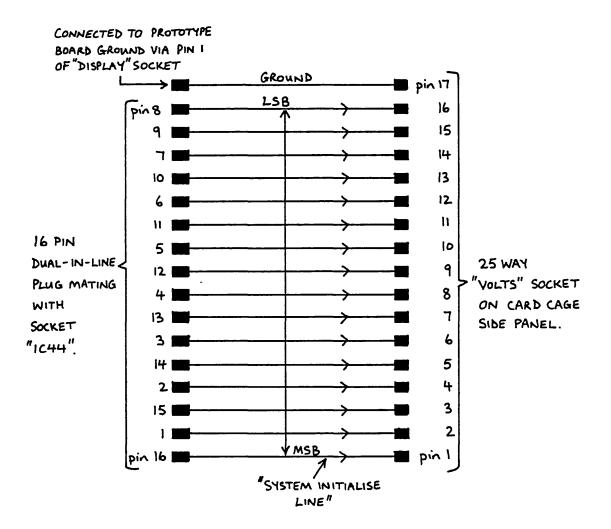

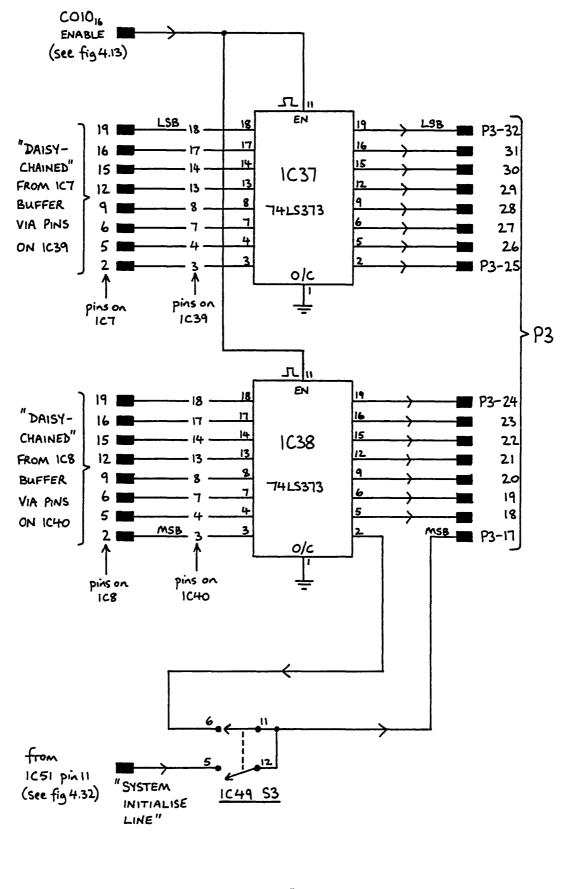

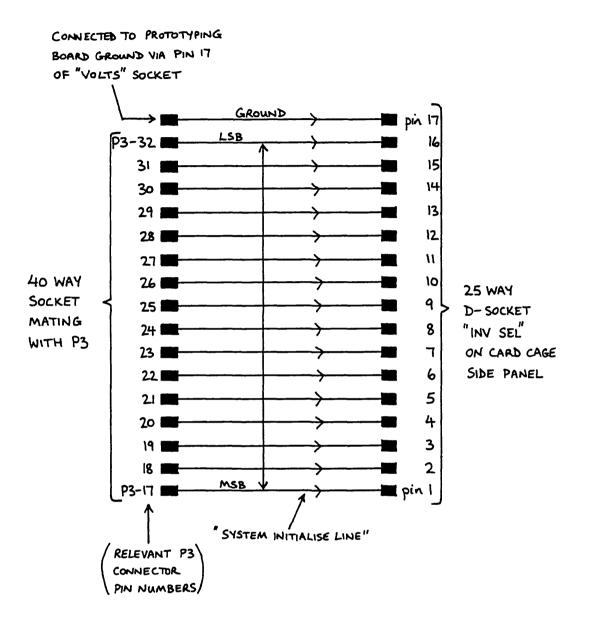

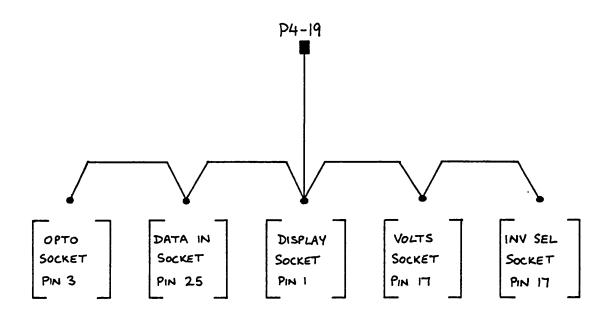

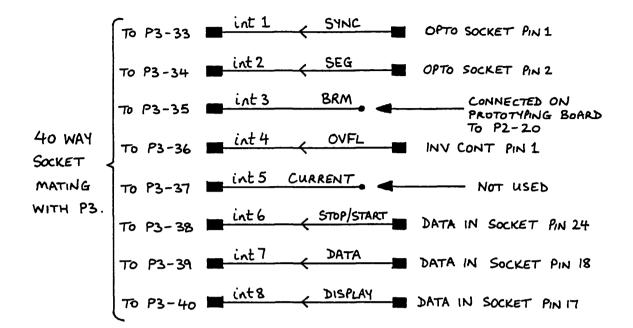

| 4.7.4.6 | Connections between the "DATA IN"<br>Card Cage Socket, and Prototyping<br>Board Edge-Connectors P3 and P4 | 25 <b>1</b>      |

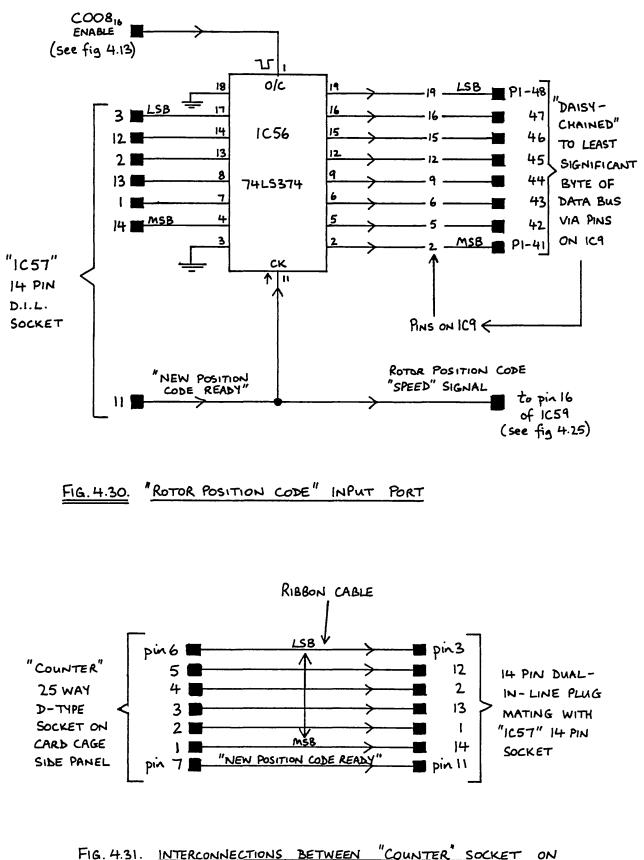

| 4.7.4.7 | The "Rotor Position Code" Input<br>Port                                                                   | 25 <b>1</b>      |

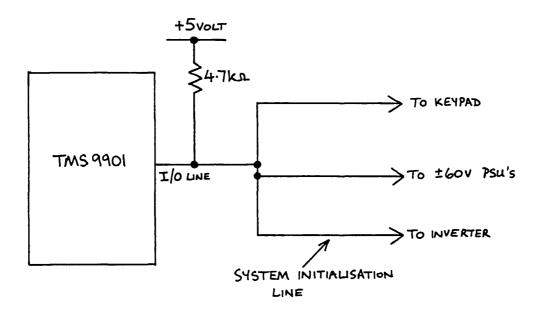

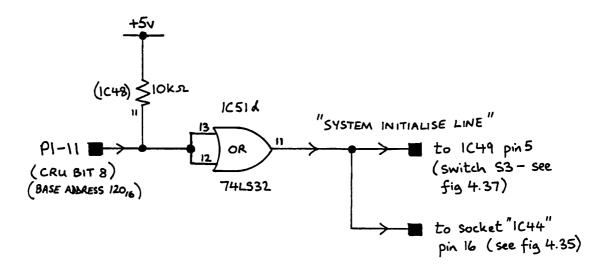

| 4.7.4.8 | The "System Initialise Line"                                                                              | 251              |

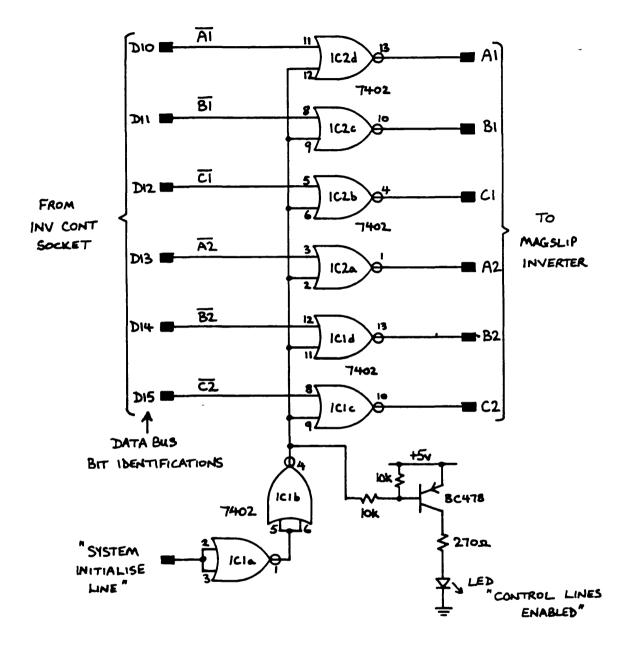

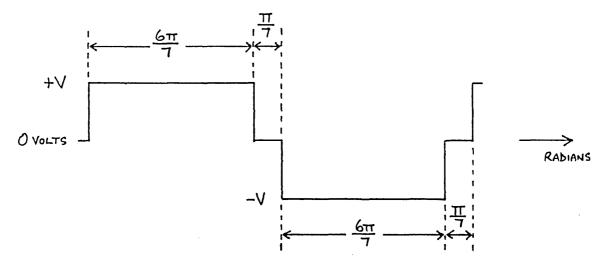

| 4.7.4.9 | The "Inverter Control" Output Port                                                                        | 251              |

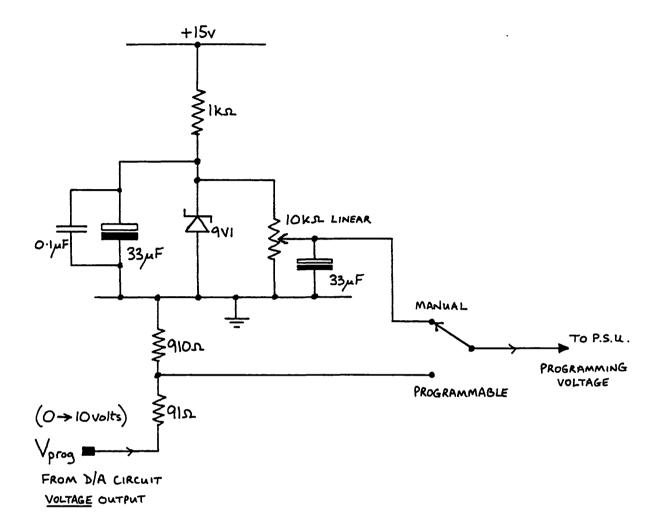

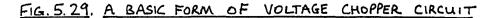

| 4.7.4.1 | 0 The ±60 volt Power Supply<br>"Combined Control and Enable" Port                                         | 255              |

| 4.7.4.1 | 1 The "Inverter Enable" Output Port                                                                       | 258              |

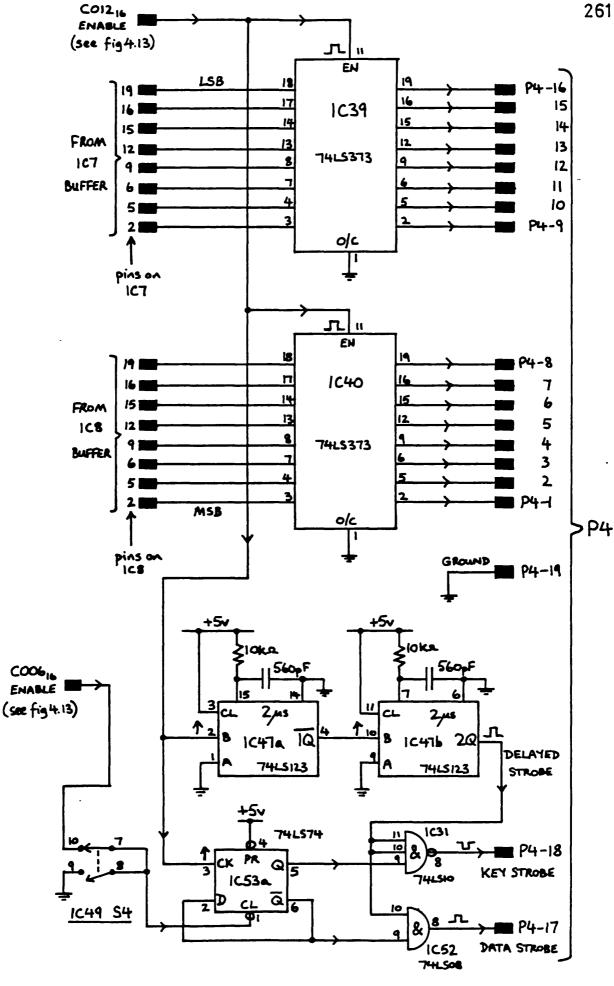

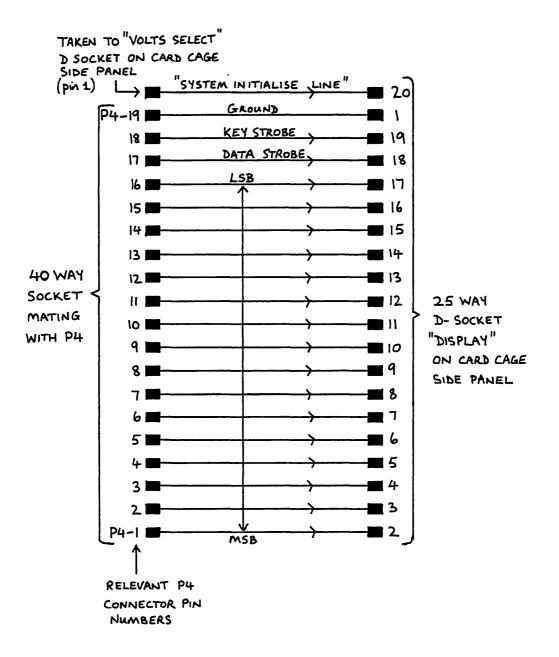

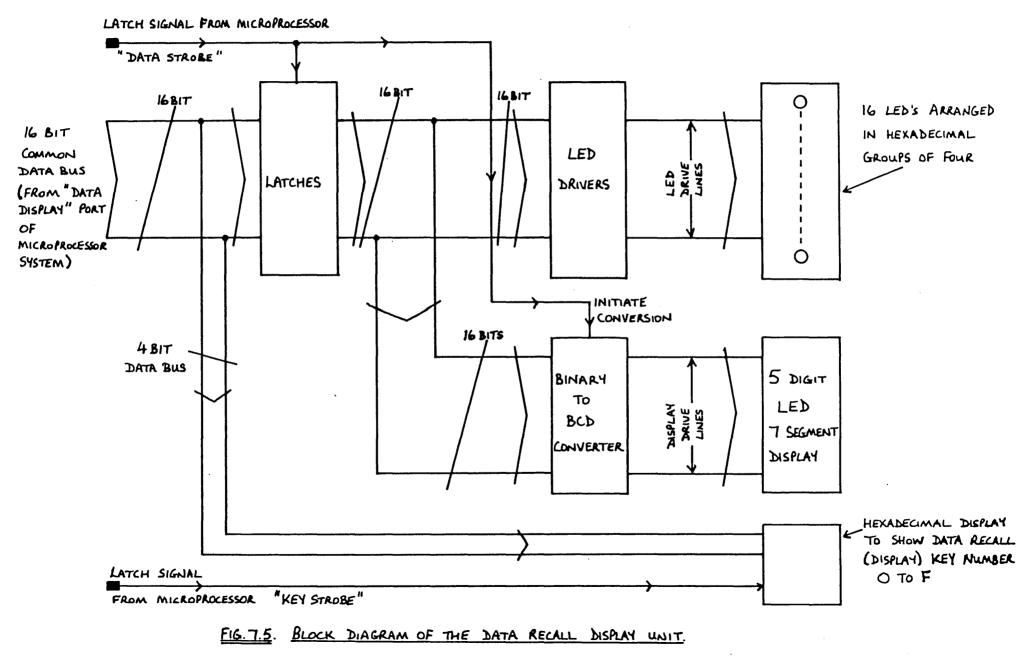

| 4.7.4.1 | 2 The "Data Display" Output Port                                                                          | 258              |

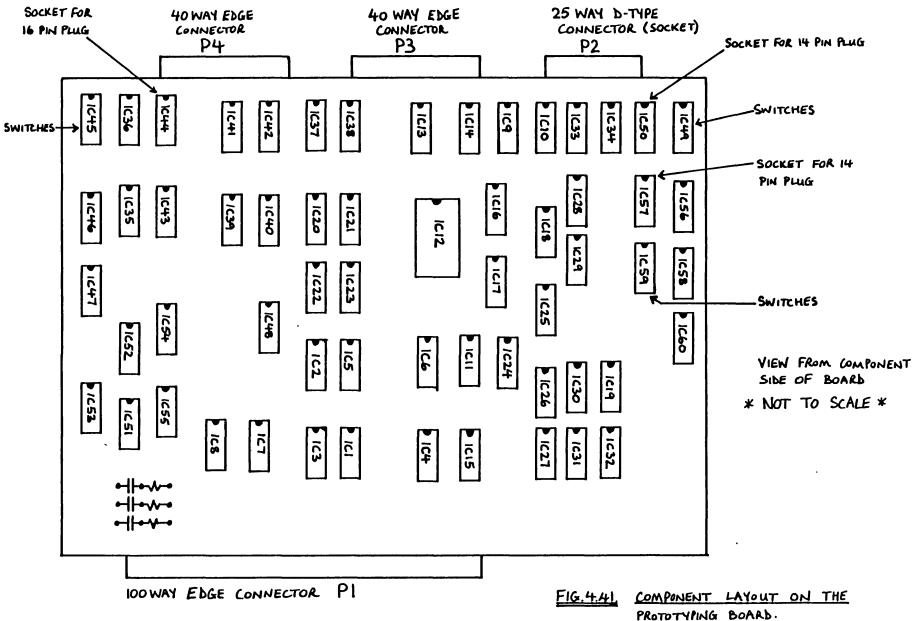

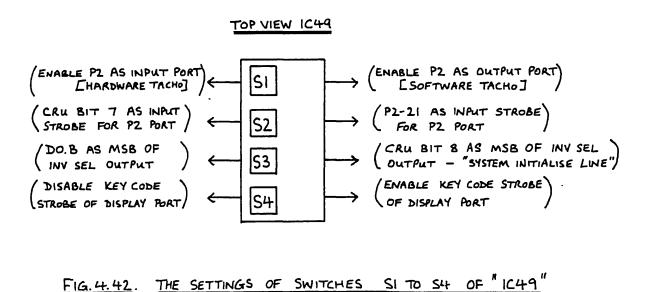

| 4.7.5   | Miscellaneous Details about the<br>Prototyping Board                                                      | 264              |

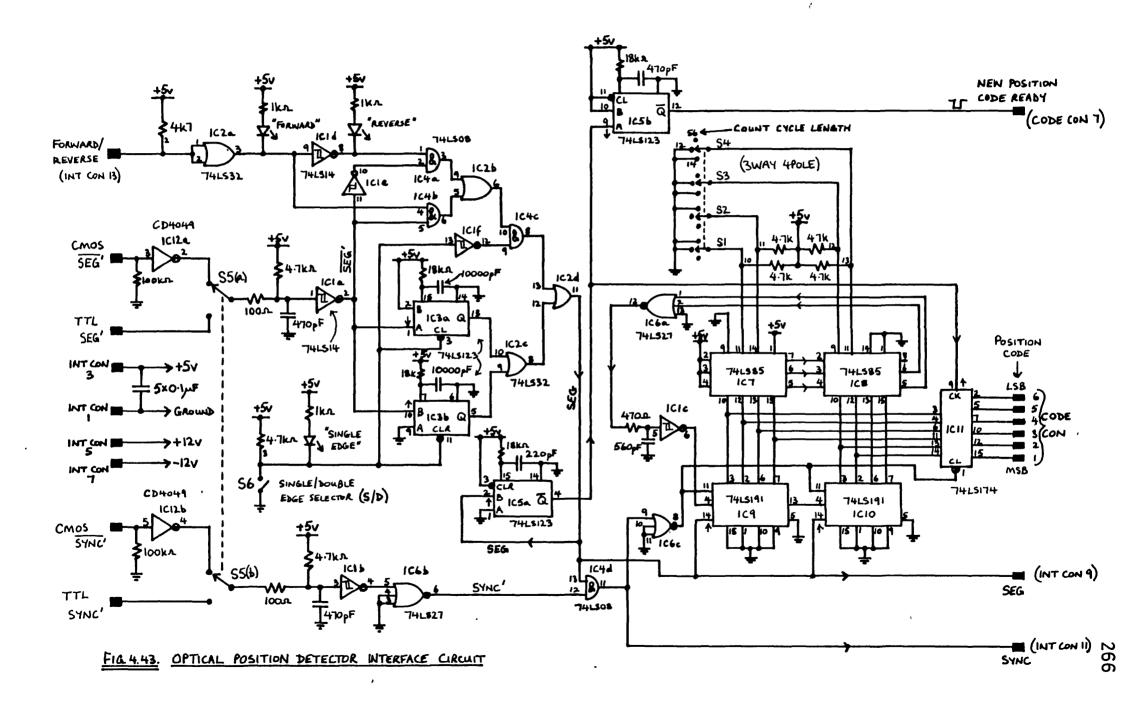

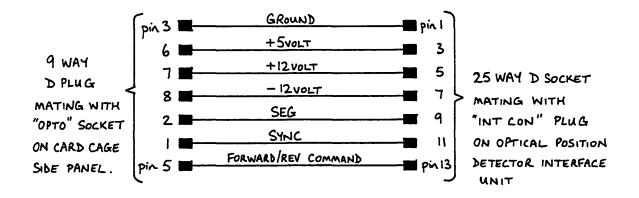

| 4.7.6   | The Optical Position Detector<br>Interface Unit                                                           | 265              |

| 4.7.7   | Miscellaneous Details Relating to the<br>Card Cage                                                        | 269              |

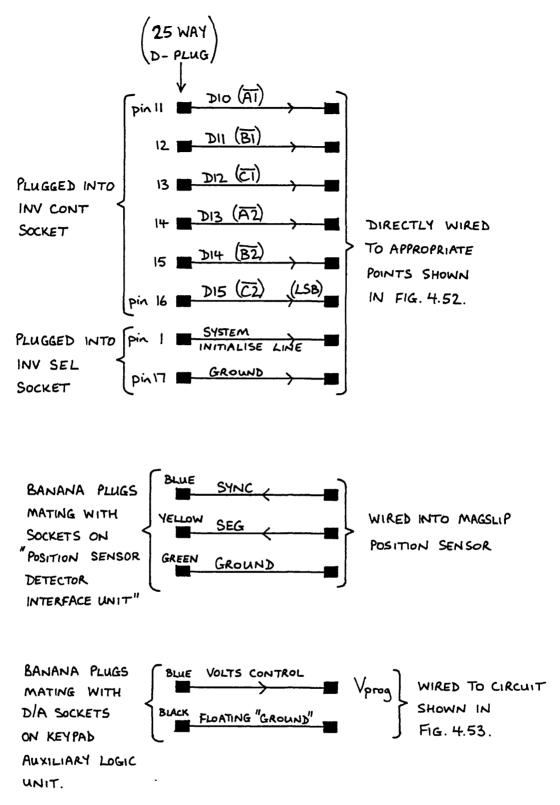

| 4.7.7.1 | Connections between the Card Cage<br>Side Panel Sockets and the System<br>Peripherals                     | 269              |

| 4.7.7.2 | Connections between Various<br>Sockets on the Card Cage Side<br>Panel                                     | 273              |

| 4.7.7.3 | Summary of Hardwired Interrupt<br>Connections                                                             | 274              |

| 4.7.7.4 | The "System Initialise Line"<br>Reset Button                                                              | 274              |

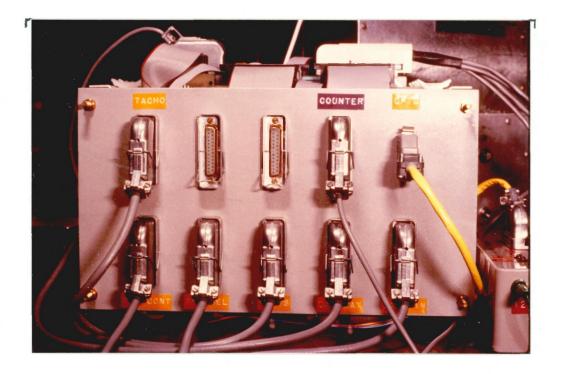

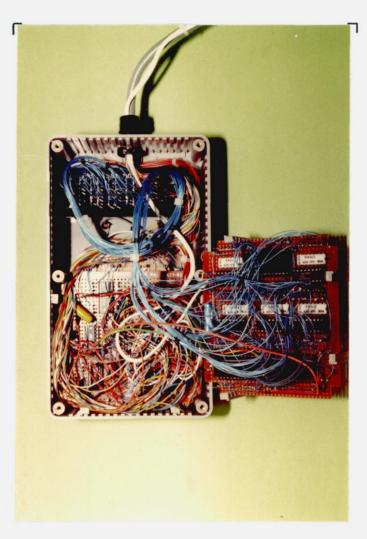

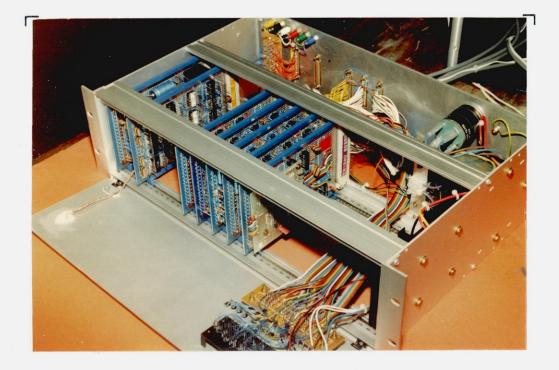

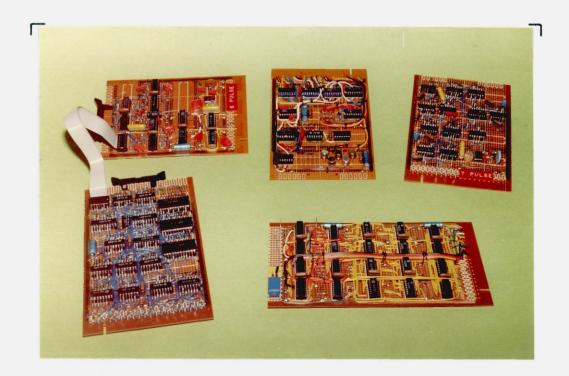

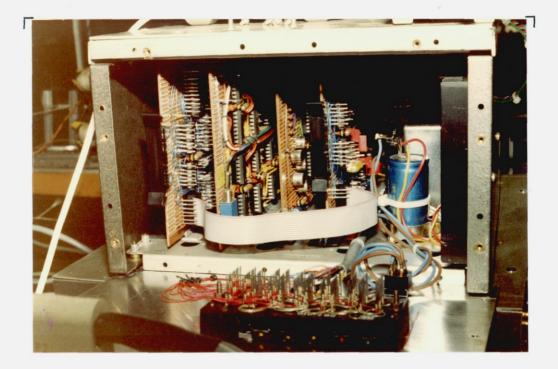

| 4.7.7.5 | 6 Card Cage Circuit Board<br>Photographs                                                                  | 276              |

| 4.7.8   | Extra Hardware Required to Interface<br>the Magslip System to the Microprocess                            | 276<br>sor       |

.

•

---

.

| Dago |  |

|------|--|

| Page |  |

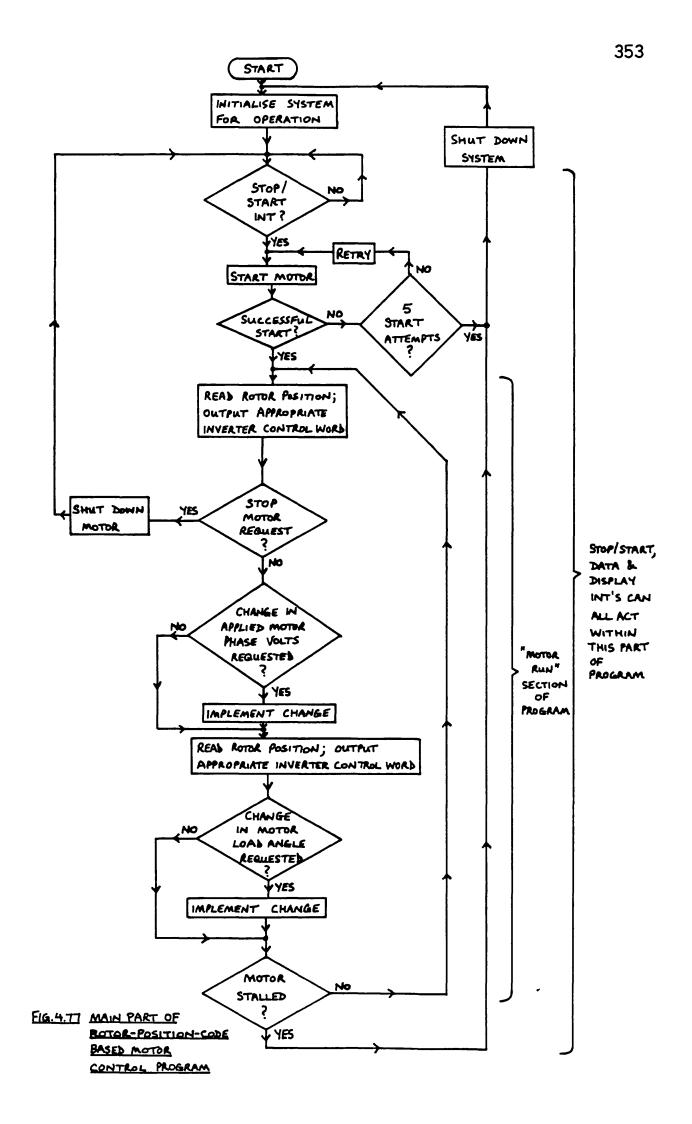

| 4.8 | Capable | ofC | ent of Microprocessor Programs<br>ontrolling a High Speed<br>Synchronous Motor System                                                               | 281         |

|-----|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|     | 4.8.1   |     | Basic System Tasks for the<br>roprocessor to Perform                                                                                                | 282         |

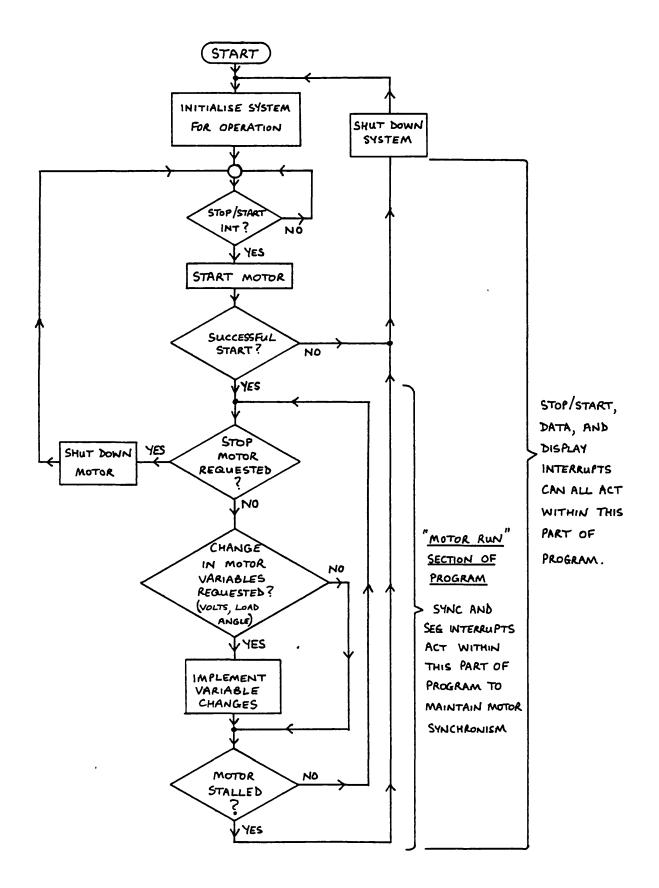

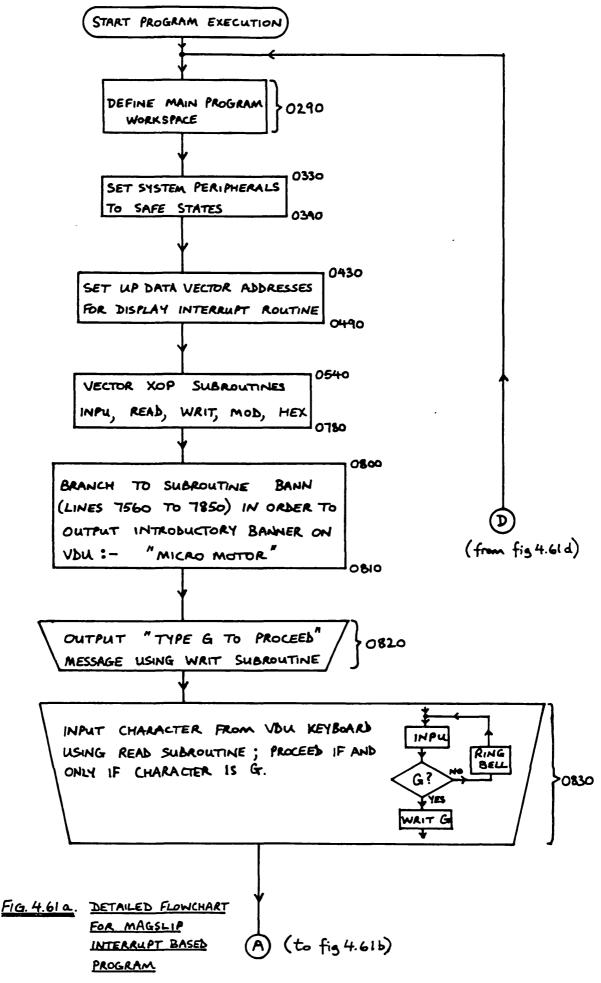

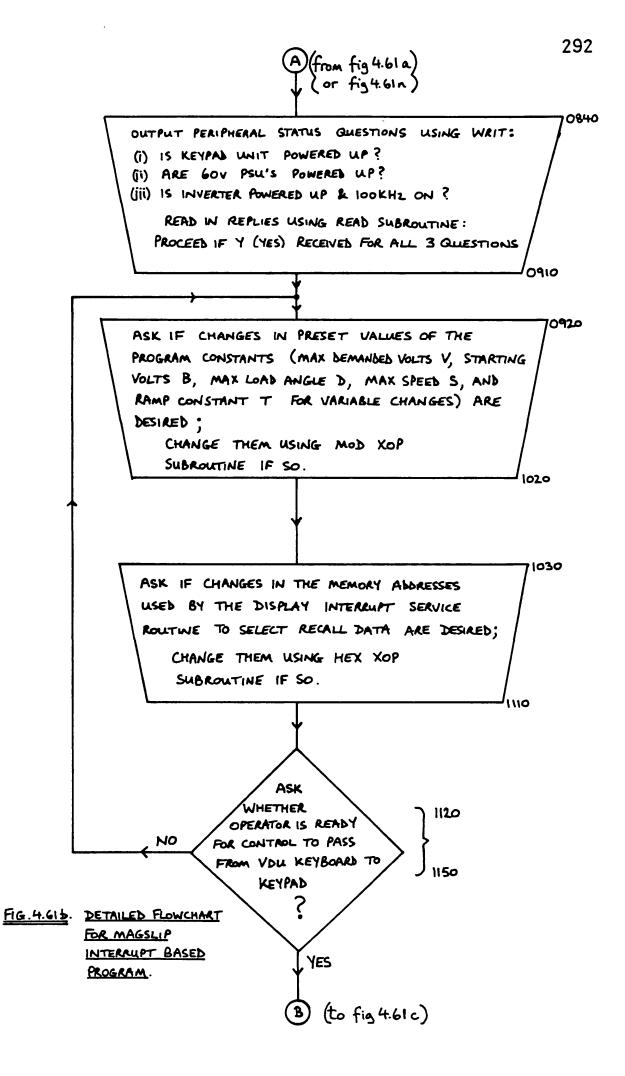

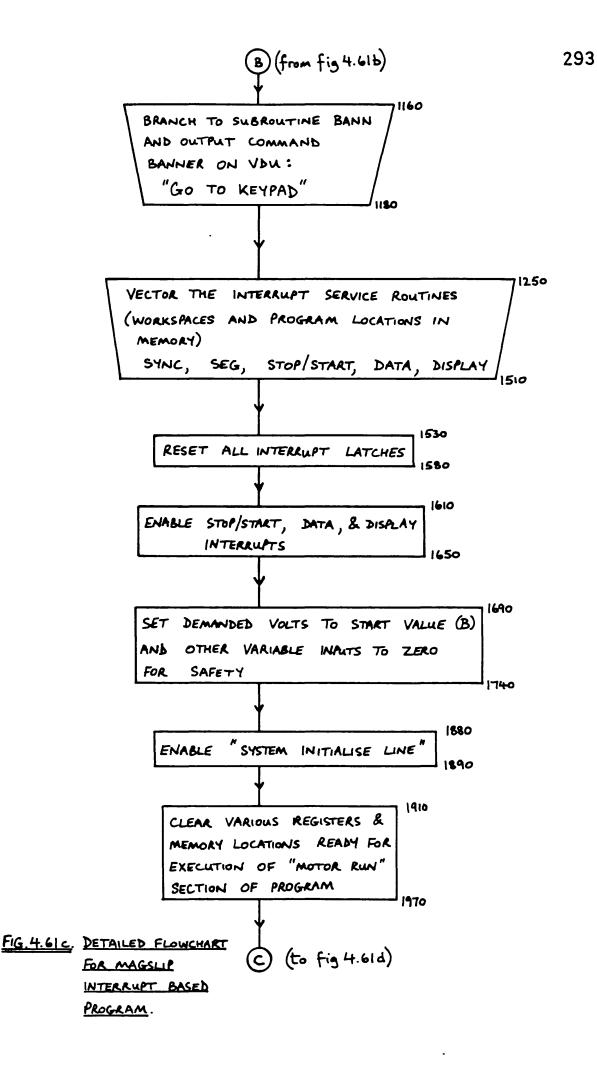

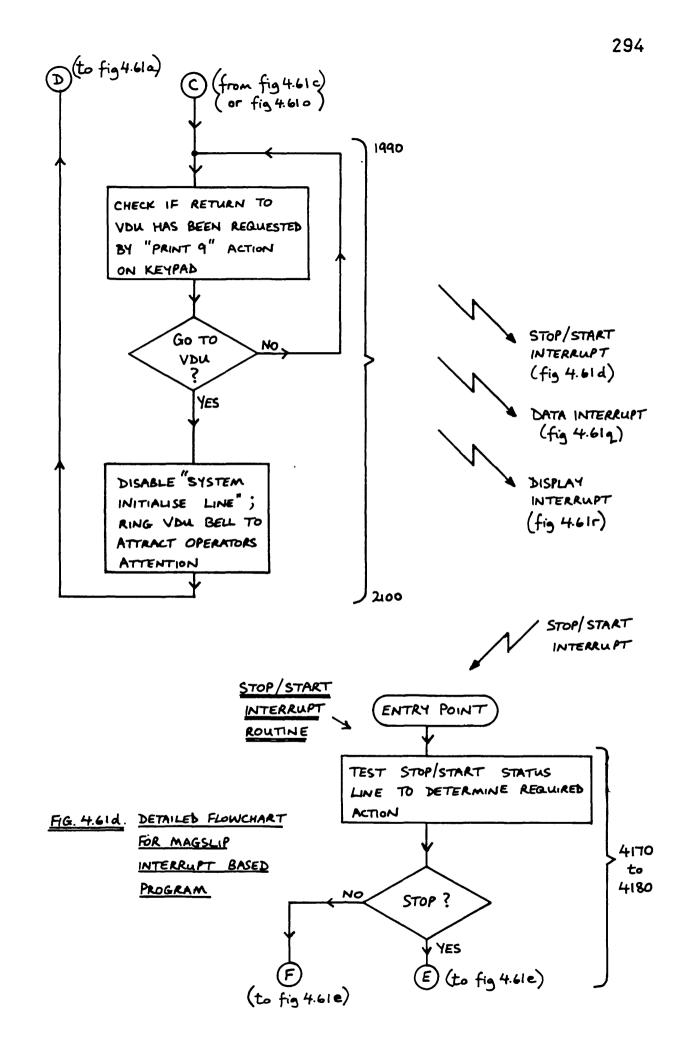

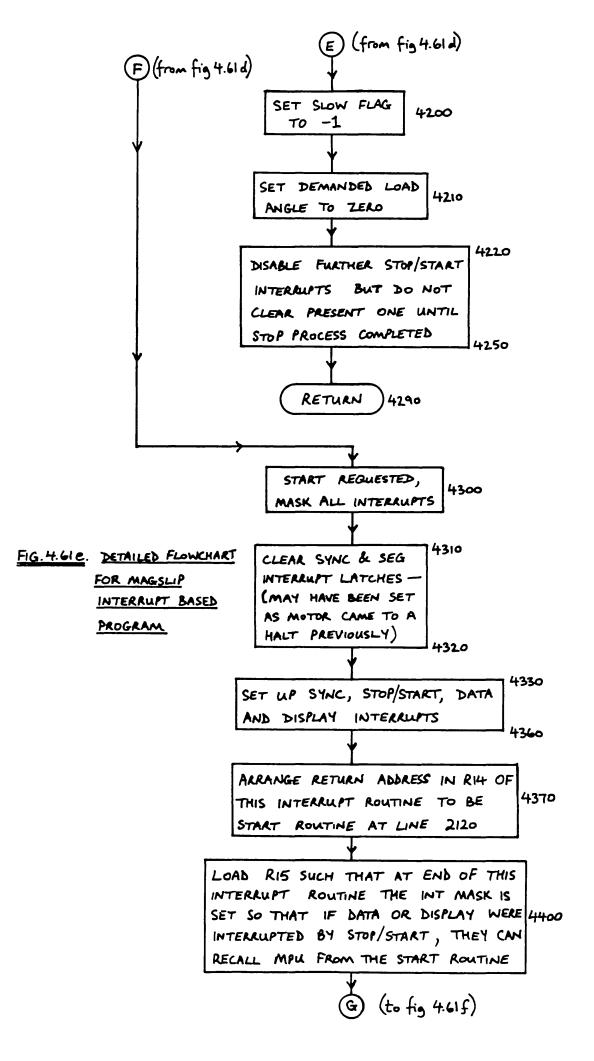

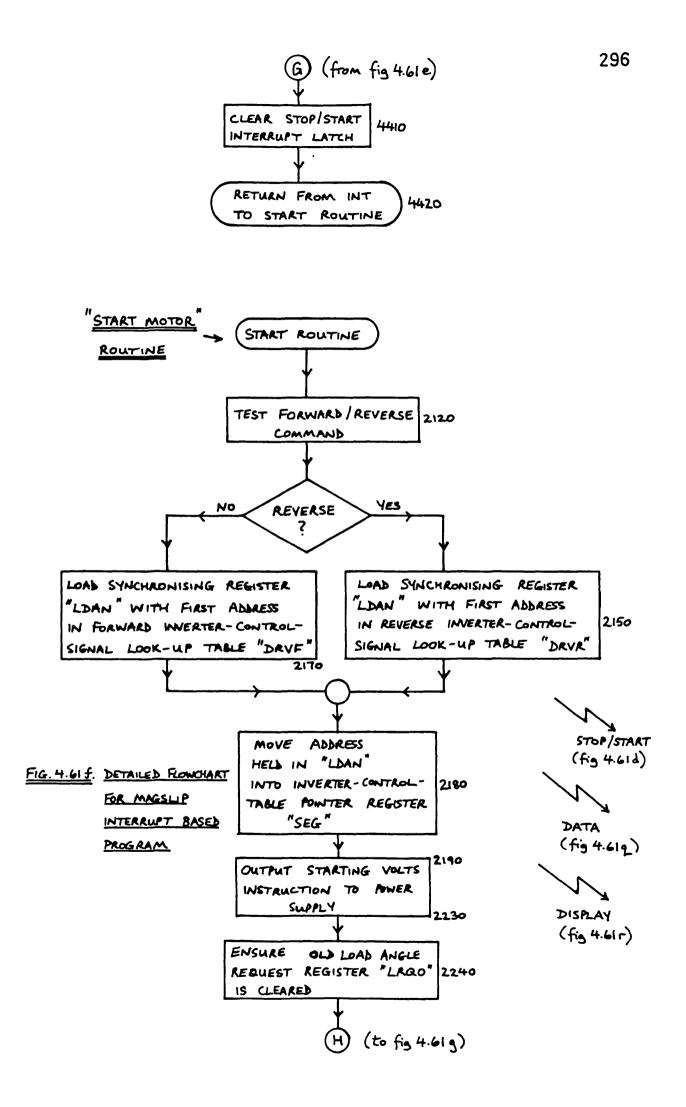

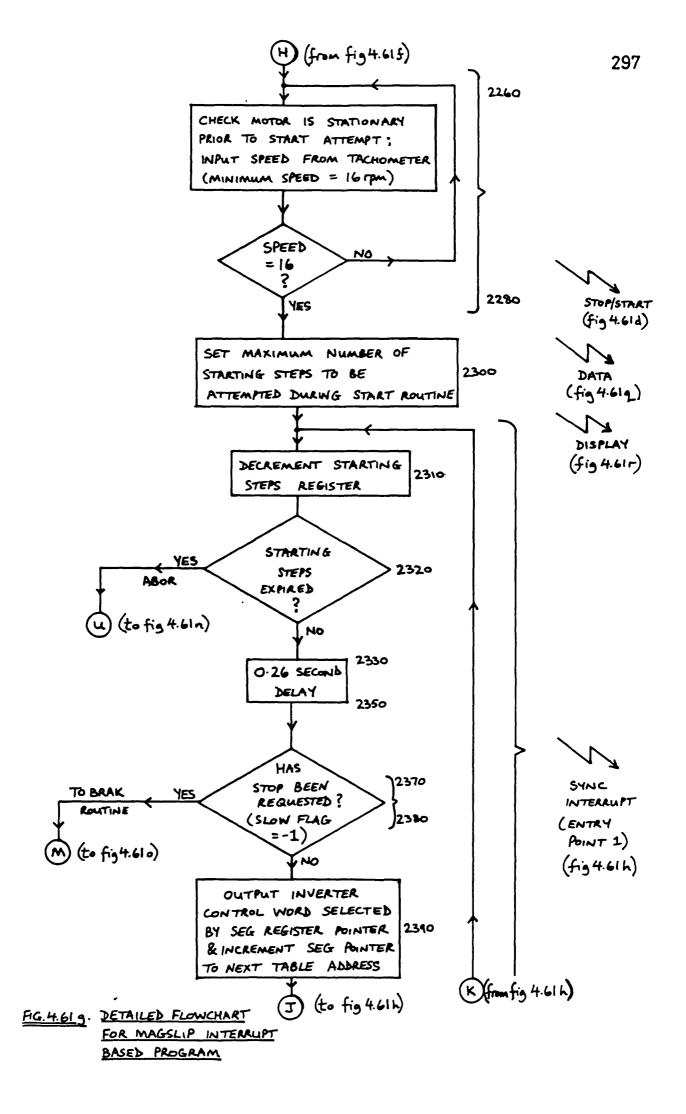

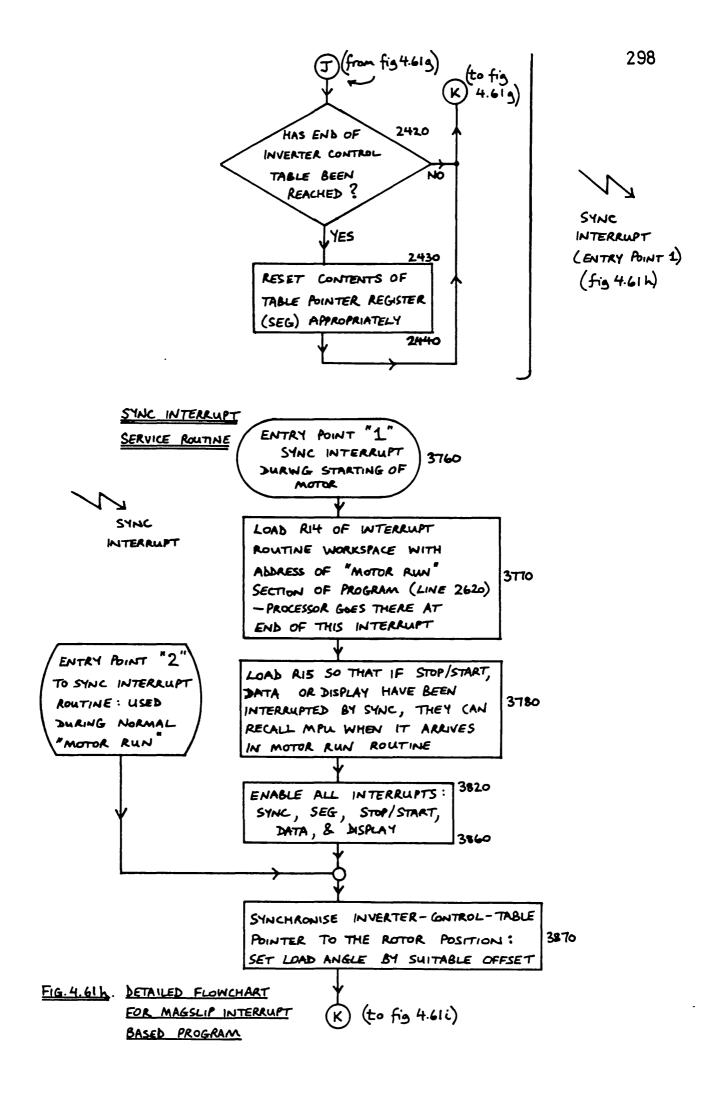

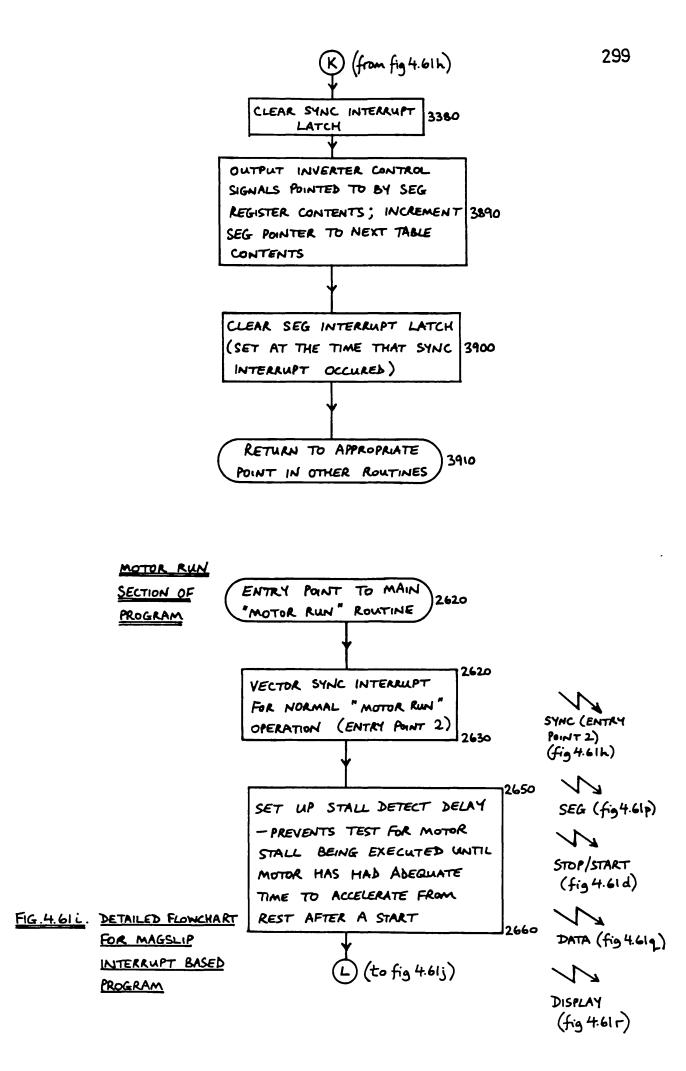

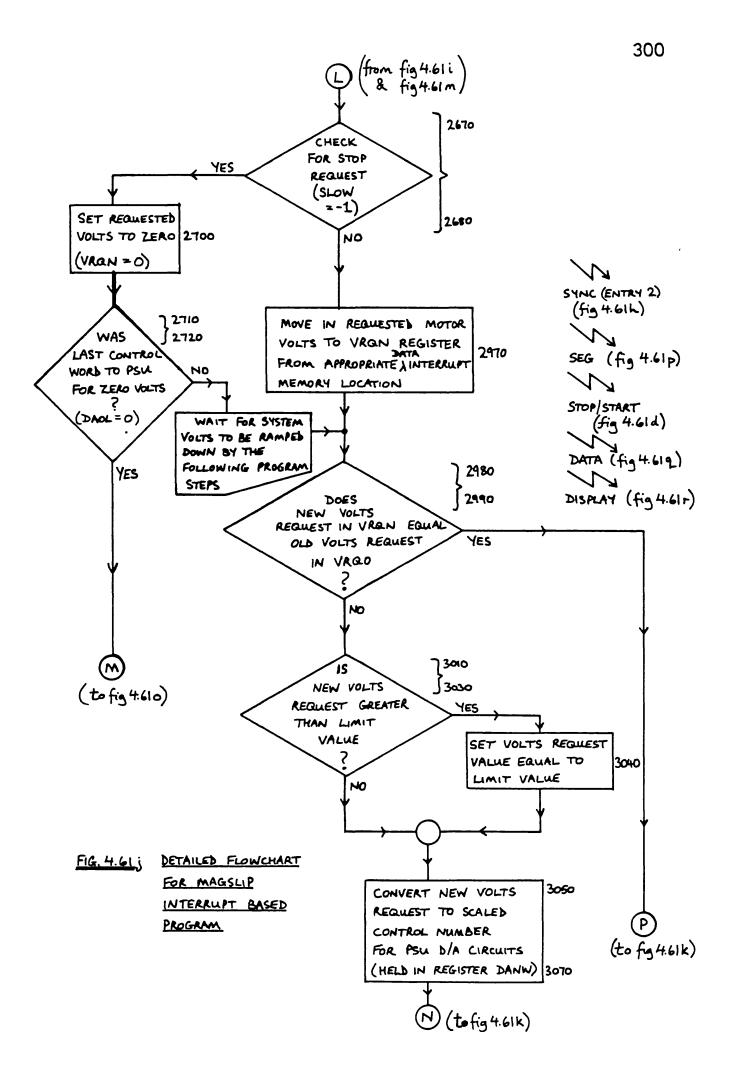

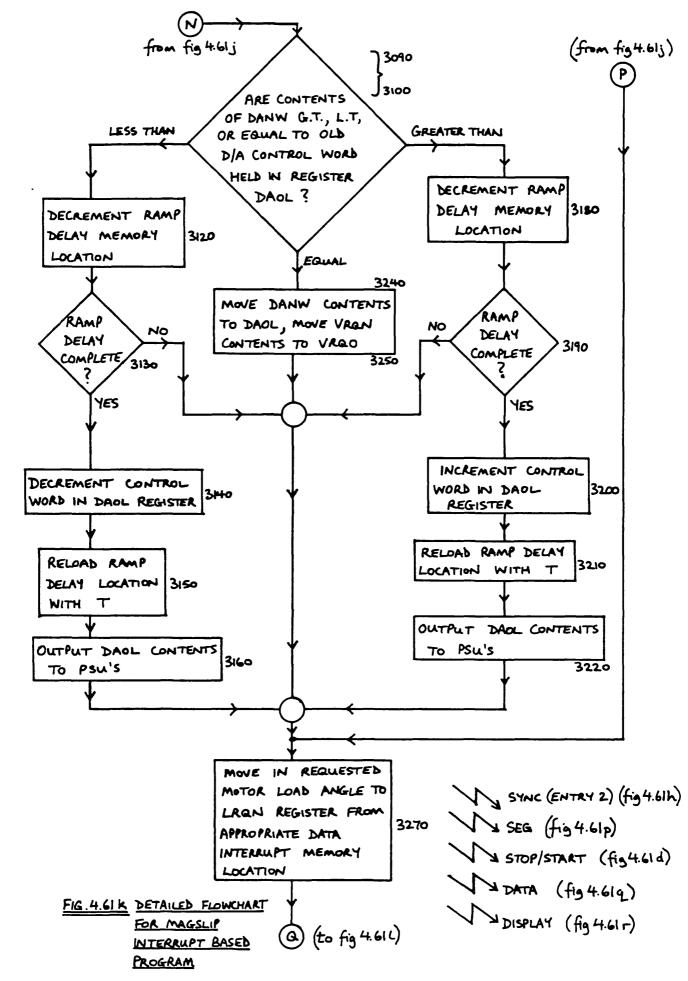

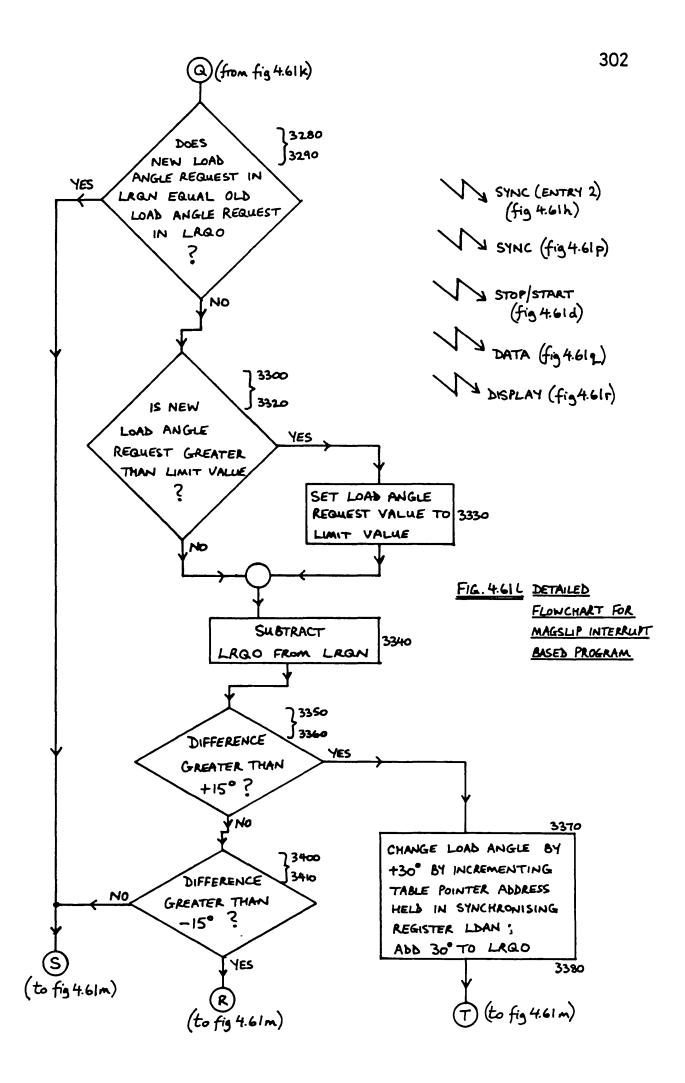

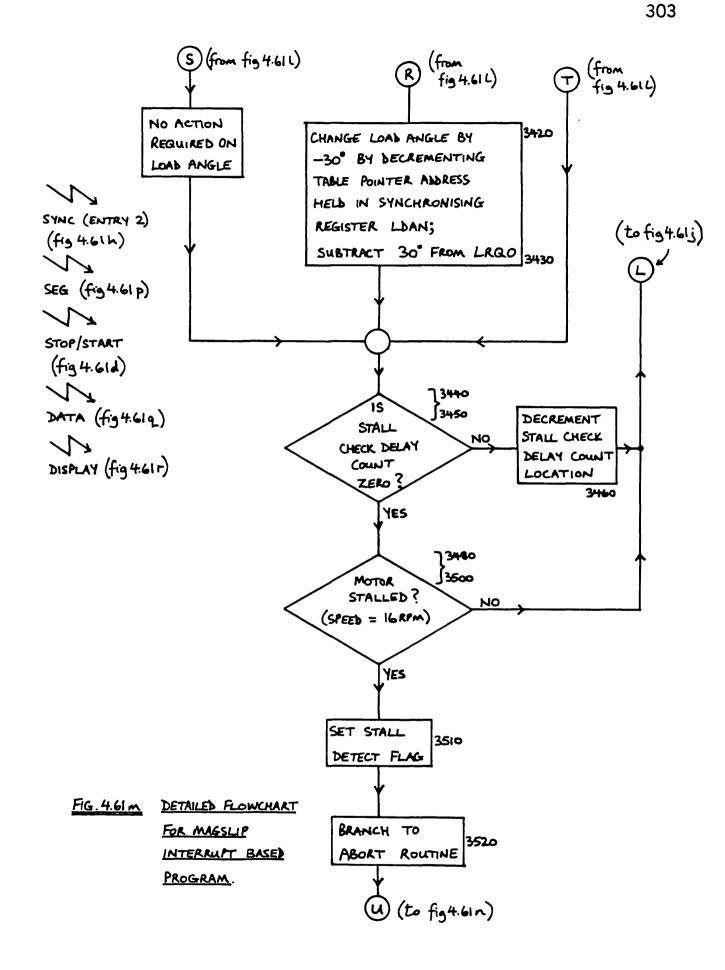

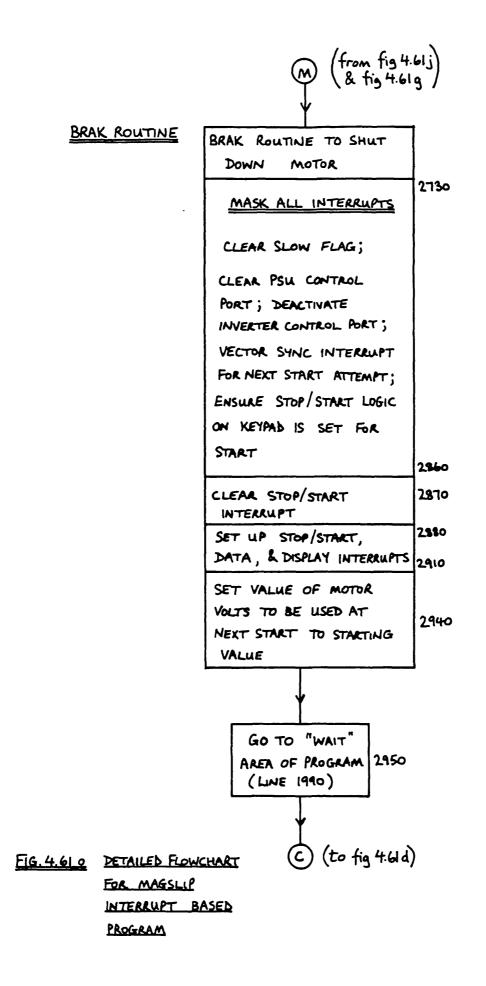

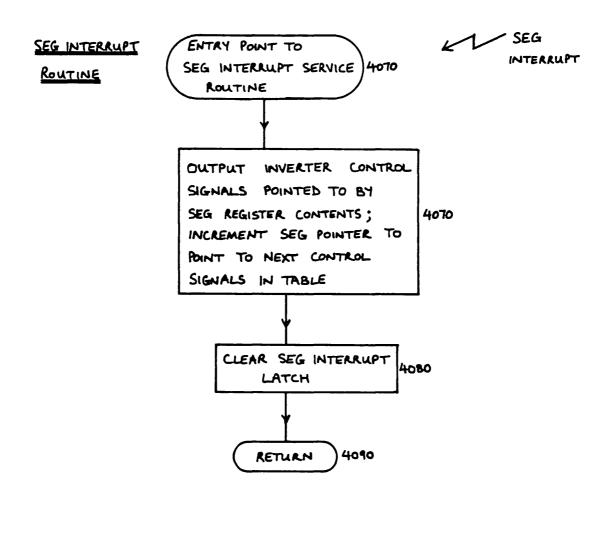

|     | 4.8.2   |     | errupt Based Autopiloting<br>gram Flowchart                                                                                                         | 284         |

|     | 4.8.3   |     | Magslip System Interrupt-Based<br>trol Program                                                                                                      | 284         |

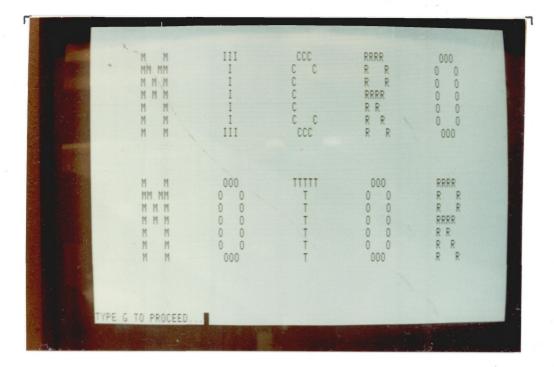

|     | 4.8.3.  | 1   | The Introductory Section of<br>the Program                                                                                                          | 309         |

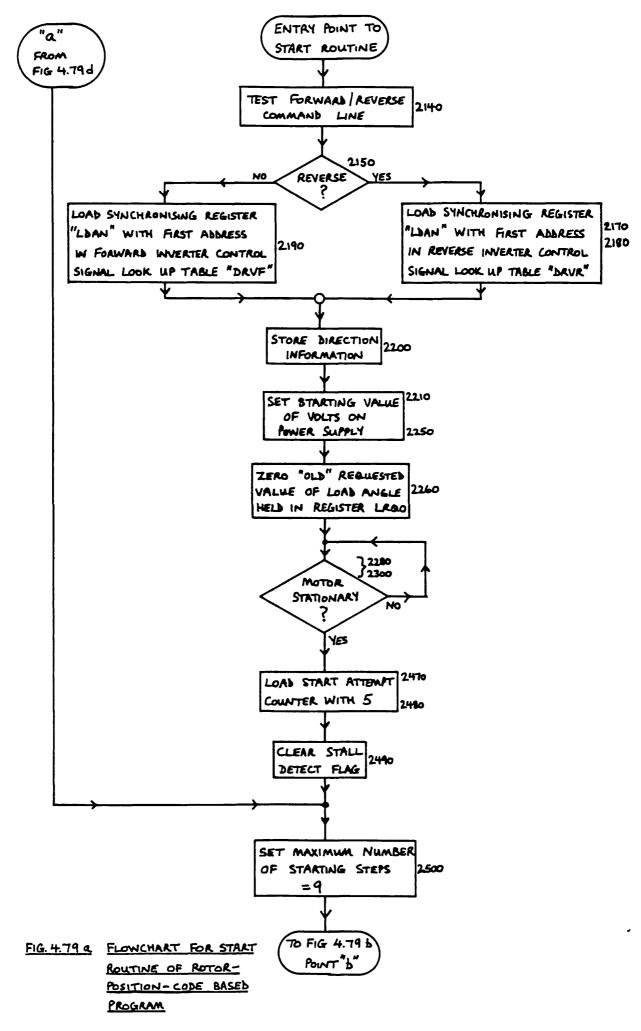

|     | 4.8.3.  | 2   | Start Routine of the Magslip                                                                                                                        | 315         |

|     | 4.8.3.  | 3   | Comments on the "Main Body"<br>of the Program                                                                                                       | 318         |

|     | 4.8.3.  | 4   | The TMS9900 Instructions Used on<br>the Memory Mapped I/O Ports                                                                                     | 320         |

|     | 4.8.3.  | 5   | The Chosen TMS9900 Instructions<br>for the Resetting of the "Memory<br>Mapped" Interrupt Latches                                                    | 321         |

|     | 4.8.3.  | 6   | The Relationship between the<br>Workspace of the "Main Body"<br>Routine and those of the SYNC,<br>SEG, and STOP/START Interrupt<br>Service Routines | 321         |

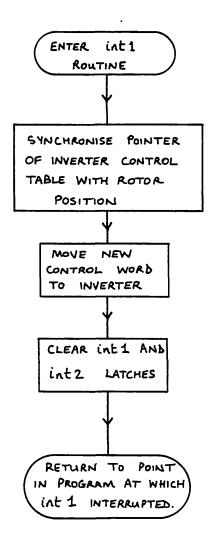

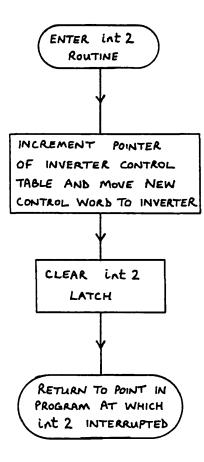

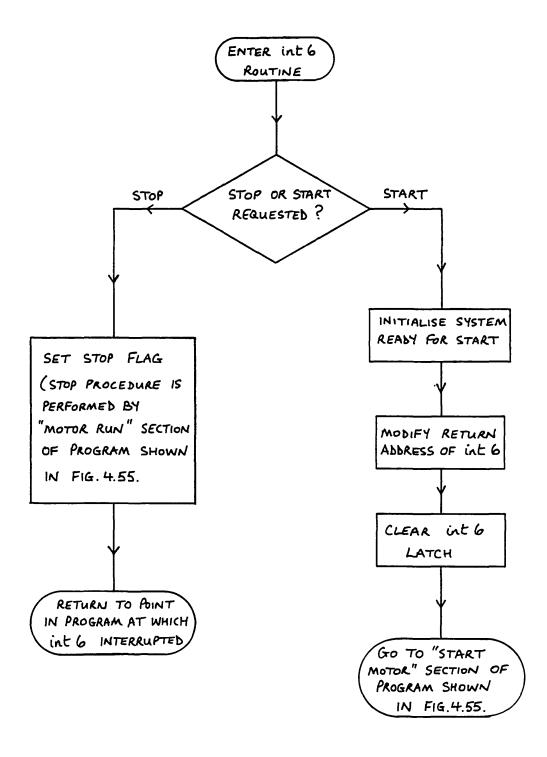

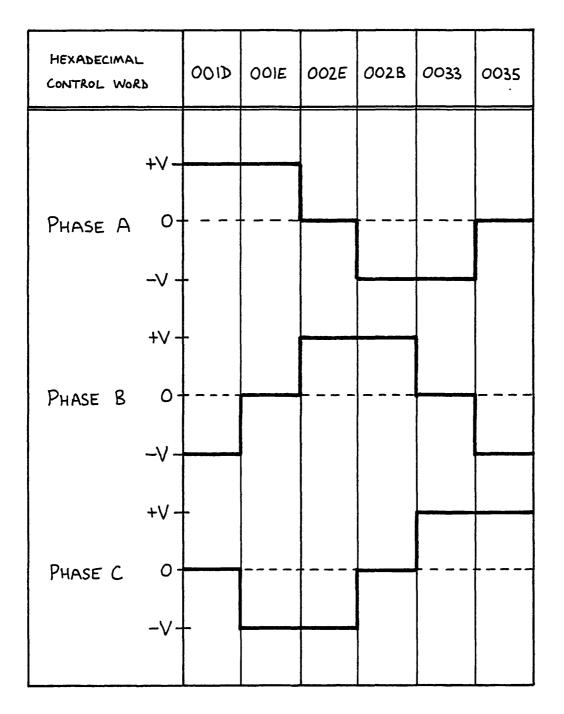

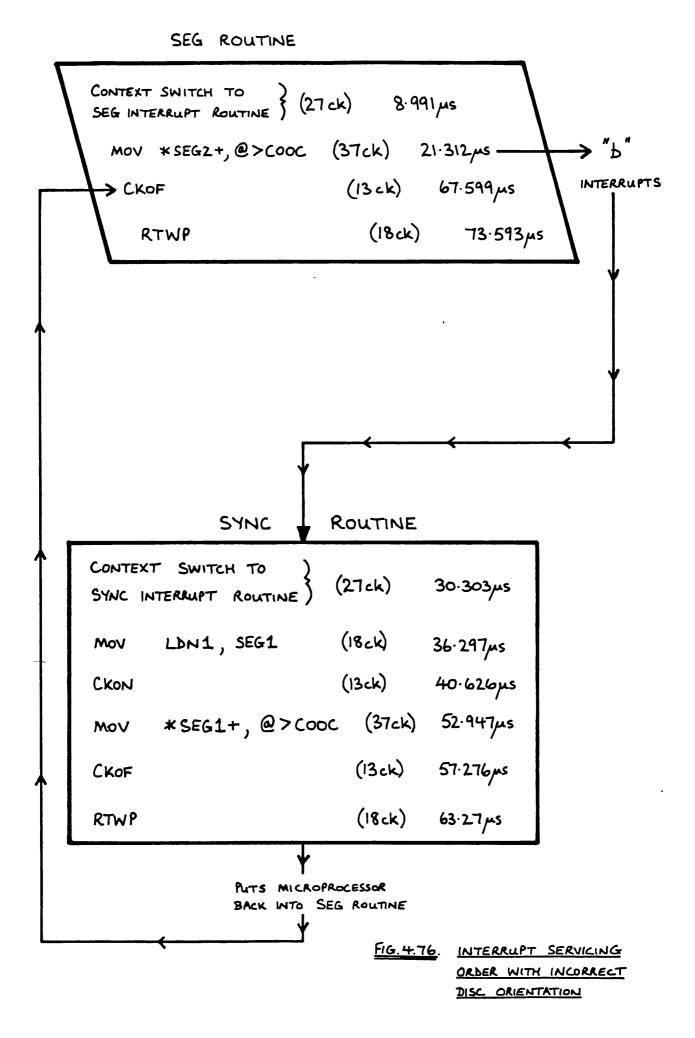

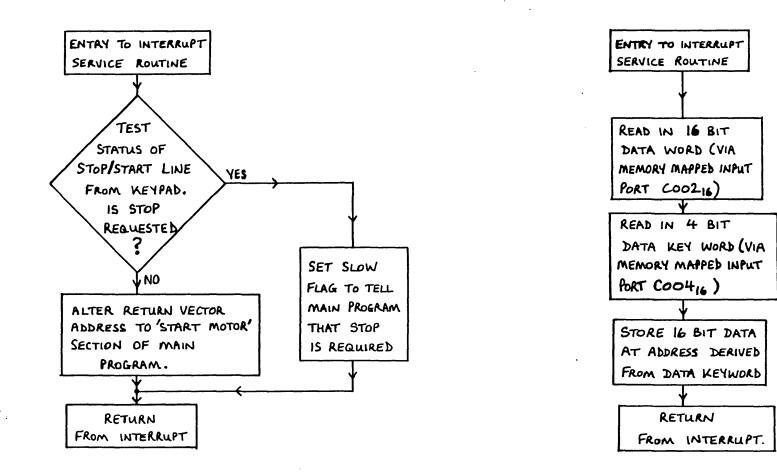

|     | 4.8.3.  | 7   | The Autopiloting Interrupt<br>Service Routines                                                                                                      | 322         |

|     | 4.8.3.  | 8   | Execution Time of the STOP/START<br>Interrupt Service Routine                                                                                       | 326         |

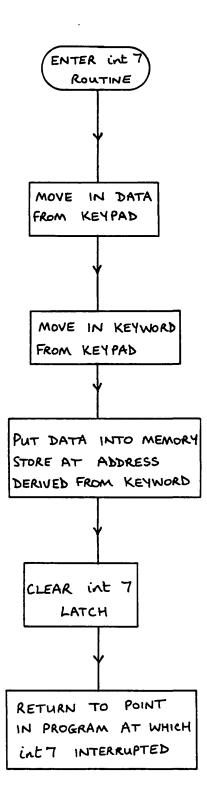

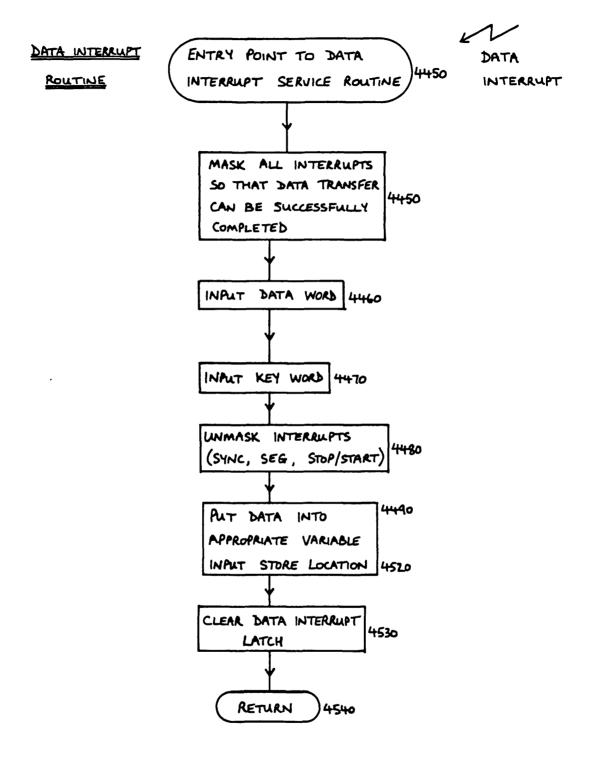

|     | 4.8.3.  | 9   | The DATA Interrupt Service<br>Routine                                                                                                               | 32 <b>7</b> |

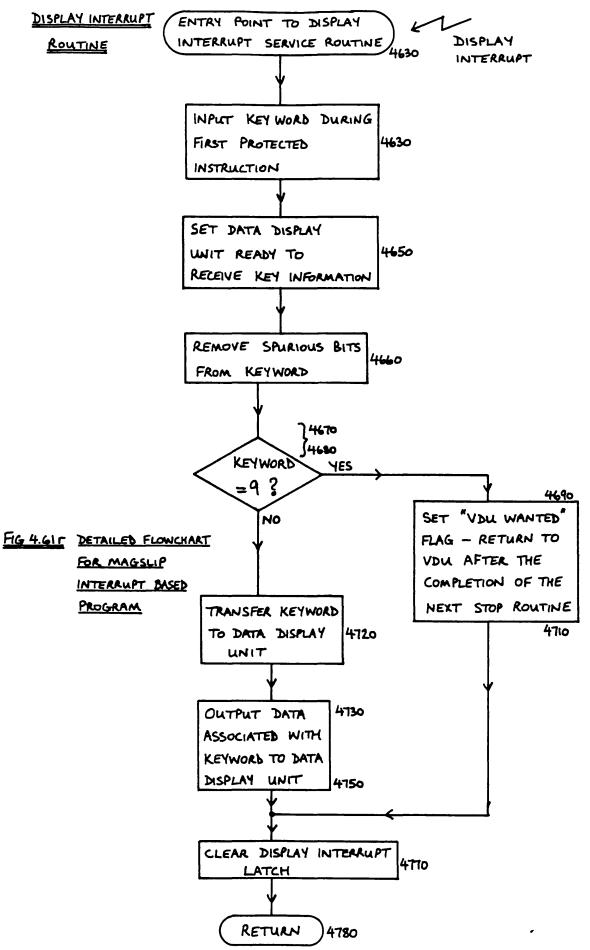

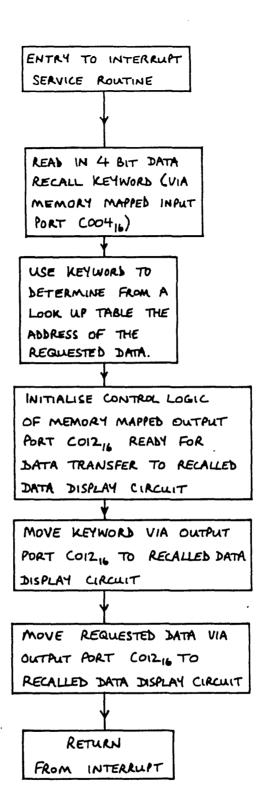

|     | 4.8.3.  | 10  | The DISPLAY Interrupt Service<br>Routine                                                                                                            | 328         |

|     | 4.8.3.  | 11  | Precautions to Ensure Correct<br>Interrupt Servicing                                                                                                | 330         |

|     | 4.8.3.  | 12  | Miscellaneous Errata in the<br>Magslip Program                                                                                                      | 331         |

|     | 4.8.4   |     | slip Interrupt Based Program<br>ration                                                                                                              | 332         |

|     | 4.8.5   |     | 7 Phase Motor Interrupt Based<br>trol Program                                                                                                       | 334         |

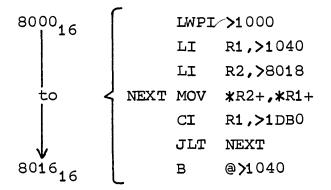

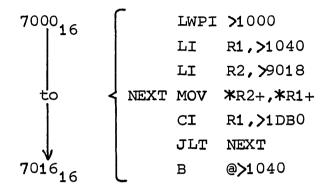

|     | 4.8.5.  | 1   | The 0 to ±60 volt Look-Up Table<br>for the Interrupt Based 7 Phase<br>Motor Program                                                                 | 335         |

|     | 4.8.5.  | 2   | The Inverter Control Look-Up<br>Tables for the Interrupt Based<br>7 Phase Motor Program                                                             | 335         |

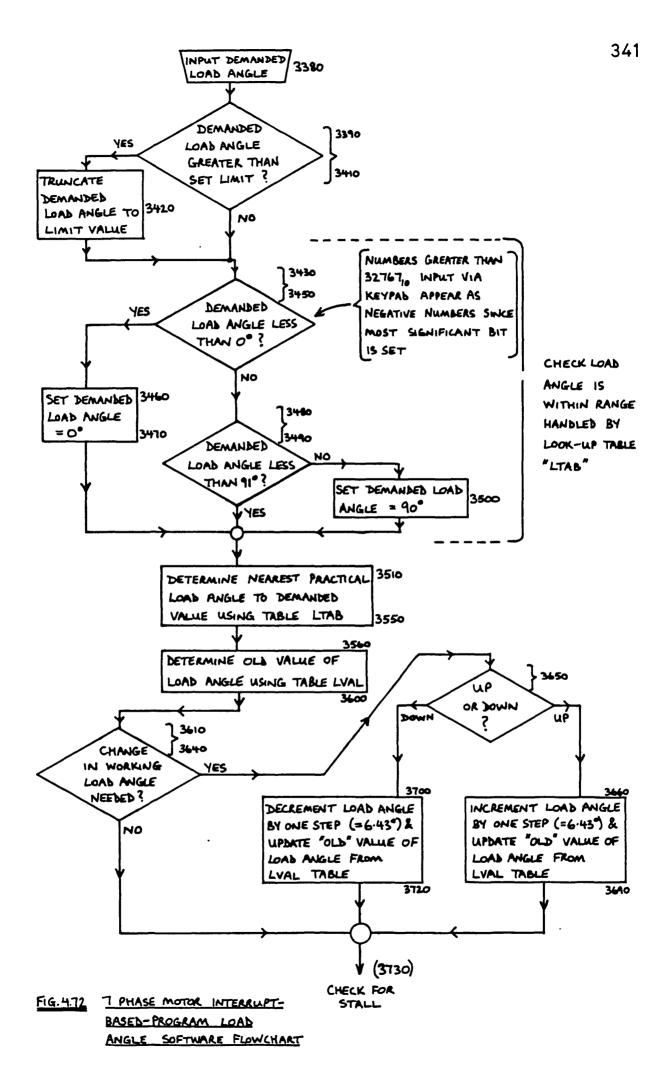

|     | 4.8.5.  | 3   | The Load Angle Selection Software                                                                                                                   | 339         |

,

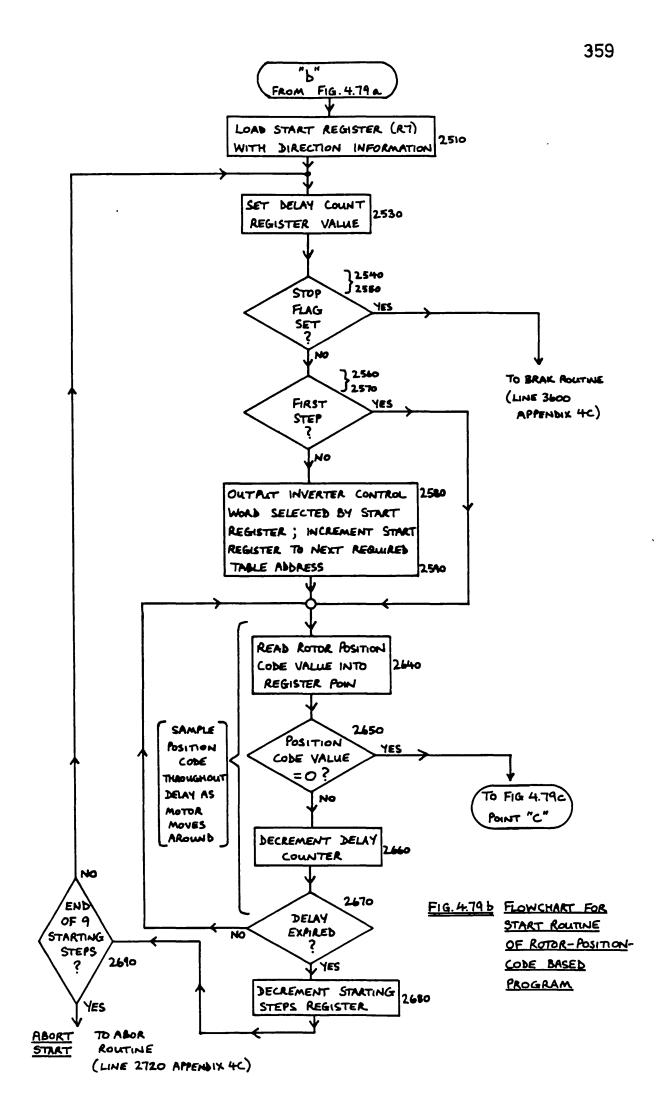

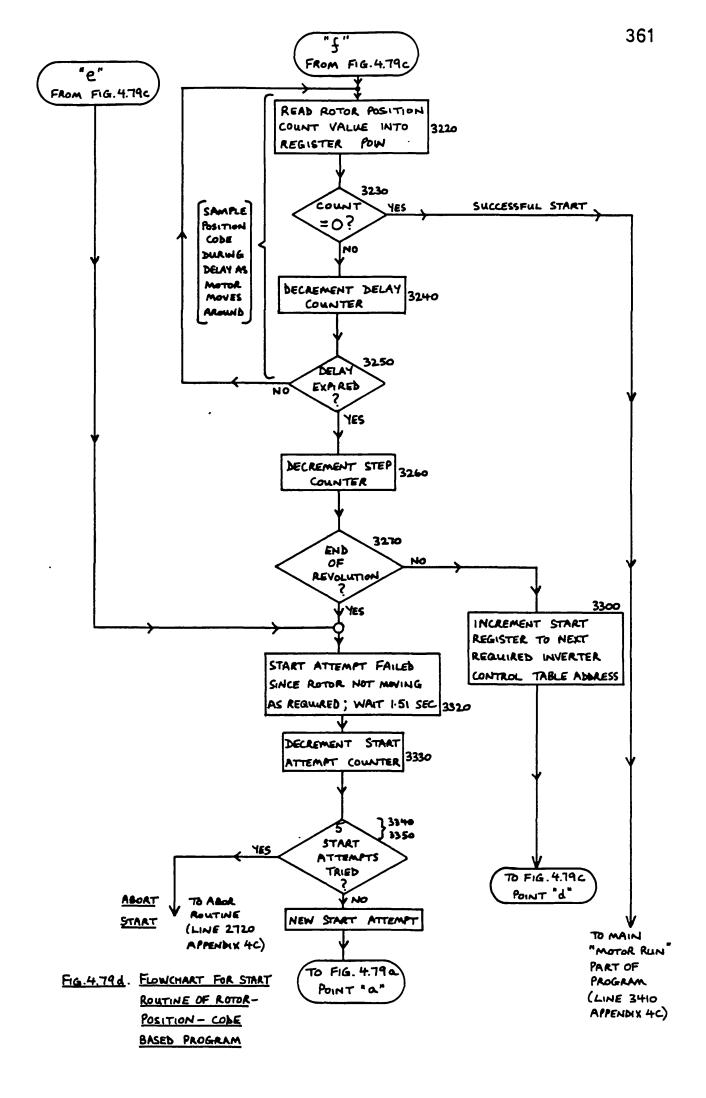

| Routine       4.8.6       7 Phase Motor Interrupt-Based-Program       343         4.8.7       Rotor-Position-Code Based Autopiloting       352         Program Flowchart for the Magslip       4.8.7       Rotor-Position-Code Based Autopiloting       354         4.8.7       Rotor-Position-Code Based Autopiloting       352       354         4.8.8       The Magslip System Rotor-Position-Code       354         4.8.8.1       Interrupts Used in the Rotor-<br>Position-Code Based Program       354         4.8.8.2       The Overlapped Workspaces in the<br>Rotor-Position-Code Based Program       354         4.8.8.1       Comments on the Rotor-Position-<br>Position-Code Register "POIN"       356         4.8.8.3       Comments on the Rotor-Position-<br>Position-Code Register "POIN"       364         4.8.8.4       The Starting Procedure for the<br>Rotor-Position-Code Based Program       367         4.8.8.5       The Rotor-Position Detection<br>Software for Autopiloted Operation       367         4.8.9       Magslip Rotor-Position-Code Based<br>Program Operation       368         4.9       Conclusions and Possible Programming Improvements       368         APPENDIX 2A:       Muirhead Magslip Data Sheet       374         APPENDIX 3A:       Magslip Inverter Snubber Design       383         APPENDIX 3A:       Source Listing Of The Magsli                                                                                |               |                                           | raye         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------|--------------|

| 0peration       4.8.7       Rotor-Position-Code Based Autopiloting<br>Program Flowchart for the Magslip       352         4.8.7       Rotor-Position-Code Based Autopiloting<br>Program Flowchart for the Magslip       354         4.8.8       The Magslip System Rotor-Position-Code<br>Position-Code Based Program       354         4.8.8.1       Interrupts Used in the Rotor-<br>Position-Code Based Program       354         4.8.8.2       The Overlapped Workspaces in the<br>Rotor-Position-Code Based Program       354         4.8.8.3       Comments on the Rotor-Position-<br>Code Input Port and the Rotor-<br>Position-Code Register "POIN"       364         4.8.8.3       Comments on the Rotor-Position-<br>Code Input Port and the Rotor-<br>Position-Code Based Program       364         4.8.8.5       The Rotor Position Detection<br>Software for Autopiloted Operation       364         4.8.8.5       The Rotor-Position-Code Based<br>Program Operation       367         4.9       Conclusions and Possible Programming Improvements       368         APPENDIX 2A:       Muirhead Magslip Data Sheet       374         APPENDIX 2B:       The Extraction of the Roots of a<br>Quartic Polynomial       376         APPENDIX 3A:       Magslip Inverter Snubber Design       383         APPENDIX 3B:       Transistor Data Sheet (2N3773)       391         APPENDIX 4A:       Source Listing Of The Magslip System<br>Interrupt-Based Control | 4.8.5.4       | 2                                         | 342          |

| Program Flowchart for the Magslip       354         Control Program       354         4.8.8.1       Interrupts Used in the Rotor-<br>Position-Code Based Program       354         4.8.8.1       Interrupts Used in the Rotor-<br>Position-Code Based Program       354         4.8.8.2       The Overlapped Workspaces in the<br>Rotor-Position-Code Based Program       354         4.8.8.2       The Overlapped Workspaces in the<br>Rotor-Position-Code Based Program       356         4.8.8.3       Comments on the Rotor-<br>Position-Code Register "POIN"       357         4.8.8.4       The Starting Procedure for the<br>Rotor-Position-Code Based Program       364         4.8.8.5       The Rotor Position Detection<br>Software for Autopiloted Operation       364         4.8.9       Magslip Rotor-Position-Code Based<br>Program Operation       367         4.9       Conclusions and Possible Programming Improvements       368         APPENDIX 2A:       Muirhead Magslip Data Sheet       376         APPENDIX 2B:       The Extraction of the Roots of a<br>Quartic Polynomial       376         APPENDIX 3A:       Magslip Inverter Snubber Design       383         APPENDIX 3B:       Transistor Data Sheet (SVT6000 series)       387         APPENDIX 3C:       Transistor Data Sheet (2N3773)       391         APPENDIX 4A:       Source Listing Of The Magslip Sy                                                                         | 4.8.6         |                                           | 343          |

| Control Program<br>4.8.8.1 Interrupts Used in the Rotor-<br>Position-Code Based Program<br>4.8.8.2 The Overlapped Workspaces in the<br>Rotor-Position-Code Based Program<br>4.8.8.3 Comments on the Rotor-Position-<br>Code Input Port and the Rotor-<br>Position-Code Register "POIN"<br>4.8.8.4 The Starting Procedure for the<br>Rotor-Position-Code Based Program<br>4.8.8.5 The Rotor Position Detection<br>Software for Autopiloted Operation<br>4.8.9 Magslip Rotor-Position-Code Based<br>Program Operation<br>4.9 Conclusions and Possible Programming Improvements 368<br><u>APPENDIX 2A</u> : Muirhead Magslip Data Sheet<br>374<br><u>APPENDIX 3A</u> : Magslip Inverter Snubber Design<br>383<br><u>APPENDIX 3B</u> : Transistor Data Sheet (SVT6000 series)<br>387<br><u>APPENDIX 3C</u> : Transistor Data Sheet (2N3773)<br>391<br><u>APPENDIX 4A</u> : Source Listing Of The Magslip System<br>Interrupt-Based Control Program<br><u>APPENDIX 4B</u> : Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program<br><u>APPENDIX 4C</u> : Source Listing Of The Magslip Rotor-<br>415                                                                                                                                                                                                                                                                                                                                                       | 4.8.7         |                                           | 352          |

| Position-Code Based Program       354         4.8.8.2       The Overlapped Workspaces in the<br>Rotor-Position-Code Based Program       354         4.8.8.3       Comments on the Rotor-Position-<br>Code Input Port and the Rotor-<br>Position-Code Register "POIN"       356         4.8.8.4       The Starting Procedure for the<br>Rotor-Position-Code Based Program       357         4.8.8.5       The Rotor Position Detection<br>Software for Autopiloted Operation       364         4.8.9       Magslip Rotor-Position-Code Based<br>Program Operation       367         4.9       Conclusions and Possible Programming Improvements       368         APPENDIX 2A:       Muirhead Magslip Data Sheet       374         APPENDIX 2B:       The Extraction of the Roots of a<br>Quartic Polynomial       376         APPENDIX 3A:       Magslip Inverter Snubber Design       383         APPENDIX 3B:       Transistor Data Sheet (SVT6000 series)       387         APPENDIX 3C:       Transistor Data Sheet (2N3773)       391         APPENDIX 4A:       Source Listing Of The Magslip System<br>Interrupt-Based Control Program       395         APPENDIX 4E:       Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program       405                                                                                                                                                                                                     | 4.8.8         |                                           | 354          |

| Rotor-Position-Code Based Program         4.8.8.3       Comments on the Rotor-Position-<br>Code Input Port and the Rotor-<br>Position-Code Register "POIN"       356         4.8.8.4       The Starting Procedure for the<br>Rotor-Position-Code Based Program       357         4.8.8.5       The Rotor Position Detection<br>Software for Autopiloted Operation       364         4.8.9       Magslip Rotor-Position-Code Based<br>Program Operation       367         4.9       Conclusions and Possible Programming Improvements       368 <u>APPENDIX 2A</u> :       Muirhead Magslip Data Sheet       374 <u>APPENDIX 2B</u> :       The Extraction of the Roots of a<br>Quartic Polynomial       363 <u>APPENDIX 3A</u> :       Magslip Inverter Snubber Design       383 <u>APPENDIX 3B</u> :       Transistor Data Sheet (2N3773)       391 <u>APPENDIX 4A</u> :       Source Listing Of The Magslip System<br>Interrupt-Based Control Program       395 <u>APPENDIX 4B</u> :       Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program       405 <u>APPENDIX 4B</u> :       Source Listing Of The Magslip Rotor-       415                                                                                                                                                                                                                                                                                                                 | 4.8.8.1       | <b>▲</b>                                  | 354          |

| Code Input Port and the Rotor-<br>Position-Code Register "POIN"4.8.8.4The Starting Procedure for the<br>Rotor-Position-Code Based Program3574.8.8.5The Rotor Position Detection<br>Software for Autopiloted Operation3644.8.9Magslip Rotor-Position-Code Based<br>Program Operation3674.9Conclusions and Possible Programming Improvements368APPENDIX 2A:Muirhead Magslip Data Sheet374APPENDIX 2B:The Extraction of the Roots of a<br>Quartic Polynomial376APPENDIX 3A:Magslip Inverter Snubber Design383APPENDIX 3B:Transistor Data Sheet (SVT6000 series)387APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System<br>Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.8.8.2       |                                           | 354          |

| Rotor-Position-Code Based Program4.8.8.5The Rotor Position Detection<br>Software for Autopiloted Operation3644.8.9Magslip Rotor-Position-Code Based<br>Program Operation3674.9Conclusions and Possible Programming Improvements368 <u>APPENDIX 2A</u> :Muirhead Magslip Data Sheet374 <u>APPENDIX 2B</u> :The Extraction of the Roots of a<br>Quartic Polynomial376 <u>APPENDIX 3A</u> :Magslip Inverter Snubber Design383 <u>APPENDIX 3E</u> :Transistor Data Sheet (SVT6000 series)387 <u>APPENDIX 3C</u> :Transistor Data Sheet (2N3773)391 <u>APPENDIX 4A</u> :Source Listing Of The Magslip System<br>Motor Interrupt-Based Control Program395 <u>APPENDIX 4B</u> :Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405 <u>APPENDIX 4C</u> :Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.8.8.3       | Code Input Port and the Rotor-            | 356          |

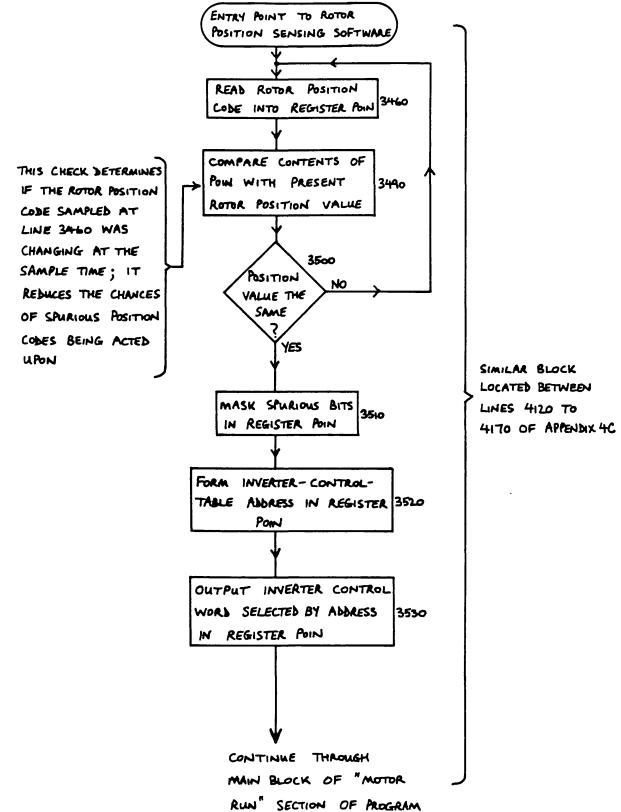

| Software for Autopiloted Operation4.8.9Magslip Rotor-Position-Code Based367Program Operation9Conclusions and Possible Programming Improvements368APPENDIX 2A:Muirhead Magslip Data Sheet374APPENDIX 2B:The Extraction of the Roots of a<br>Quartic Polynomial376APPENDIX 3A:Magslip Inverter Snubber Design383APPENDIX 3B:Transistor Data Sheet (SVT6000 series)387APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System<br>Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.8.8.4       |                                           | 35 <b>7</b>  |

| Program Operation         4.9 Conclusions and Possible Programming Improvements 368 <u>APPENDIX 2A</u> :       Muirhead Magslip Data Sheet       374 <u>APPENDIX 2B</u> :       The Extraction of the Roots of a Quartic Polynomial       376 <u>APPENDIX 3B</u> :       The Extraction of the Roots of a Quartic Polynomial       383 <u>APPENDIX 3A</u> :       Magslip Inverter Snubber Design       383 <u>APPENDIX 3B</u> :       Transistor Data Sheet (SVT6000 series)       387 <u>APPENDIX 3C</u> :       Transistor Data Sheet (2N3773)       391 <u>APPENDIX 4A</u> :       Source Listing Of The Magslip System Interrupt-Based Control Program       395 <u>APPENDIX 4B</u> :       Source Listing Of The Seven Phase Motor Interrupt-Based Control Program       405 <u>APPENDIX 4C</u> :       Source Listing Of The Magslip Rotor-       415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.8.8.5       |                                           | 364          |

| APPENDIX 2A:Muirhead Magslip Data Sheet374APPENDIX 2B:The Extraction of the Roots of a<br>Quartic Polynomial376APPENDIX 3A:Magslip Inverter Snubber Design383APPENDIX 3B:Transistor Data Sheet (SVT6000 series)387APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System<br>Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.8.9         |                                           | 36 <b>7</b>  |

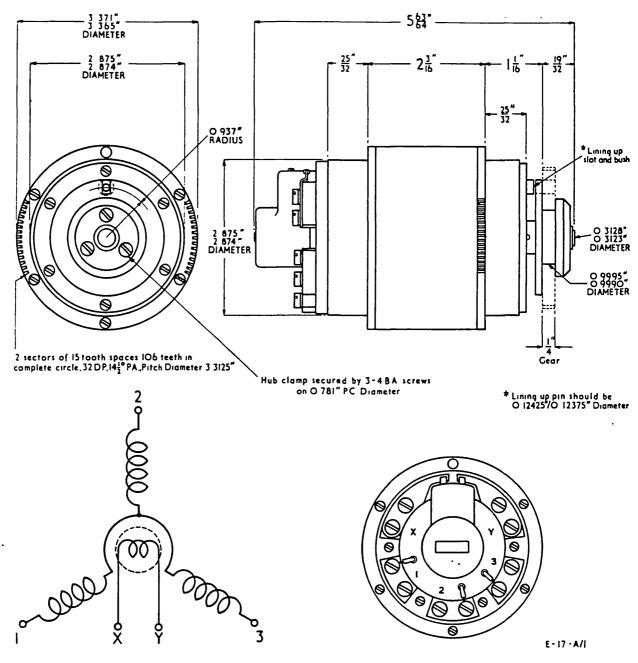

| APPENDIX 2B:The Extraction of the Roots of a<br>Quartic Polynomial376APPENDIX 3A:Magslip Inverter Snubber Design383APPENDIX 3B:Transistor Data Sheet (SVT6000 series)387APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System<br>Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.9 Conclusio | ons and Possible Programming Improvements | 368          |

| Quartic PolynomialAPPENDIX 3A:Magslip Inverter Snubber Design383APPENDIX 3B:Transistor Data Sheet (SVT6000 series)387APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System395Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | APPENDIX 2A:  | Muirhead Magslip Data Sheet               | 374          |

| APPENDIX 3B:Transistor Data Sheet (SVT6000 series)387APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System395Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | APPENDIX 28:  |                                           | 3 <b>7</b> 6 |

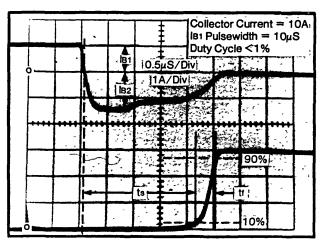

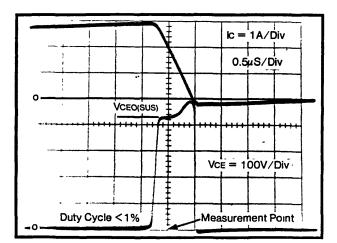

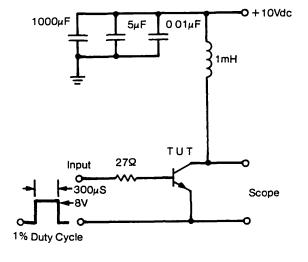

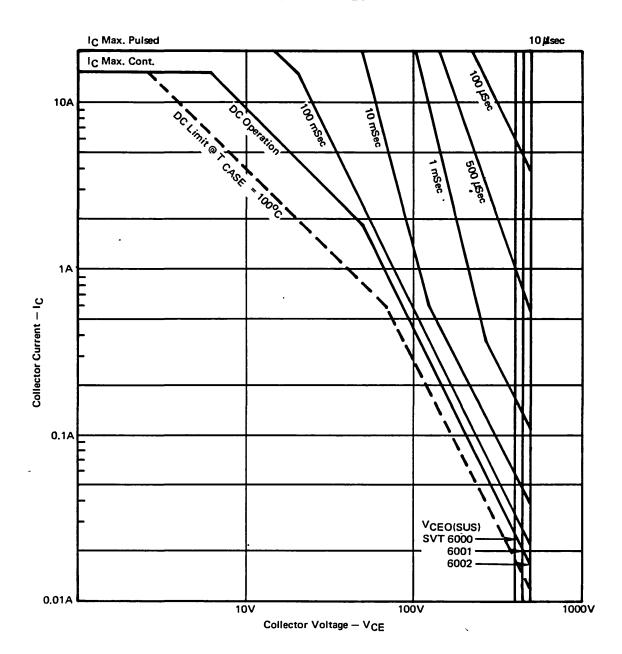

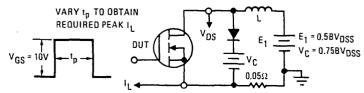

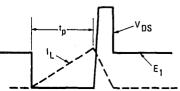

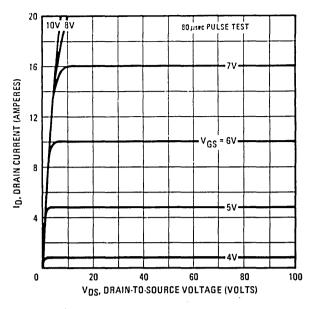

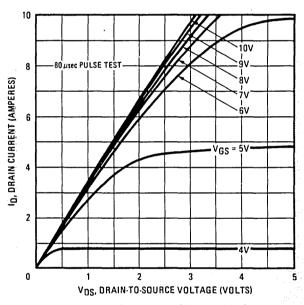

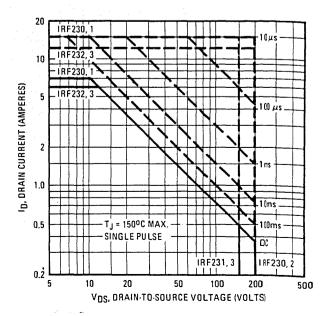

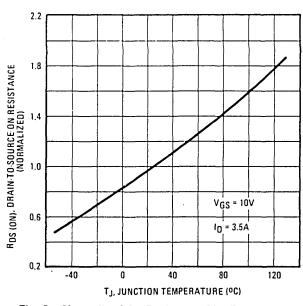

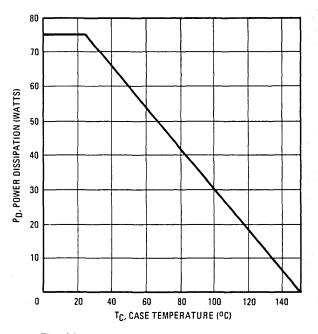

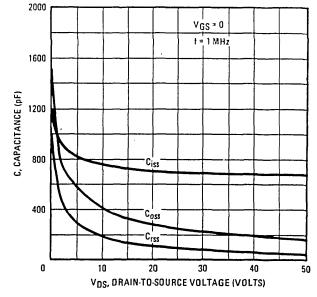

| APPENDIX 3C:Transistor Data Sheet (2N3773)391APPENDIX 4A:Source Listing Of The Magslip System395Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | APPENDIX 3A:  | Magslip Inverter Snubber Design           | 383          |

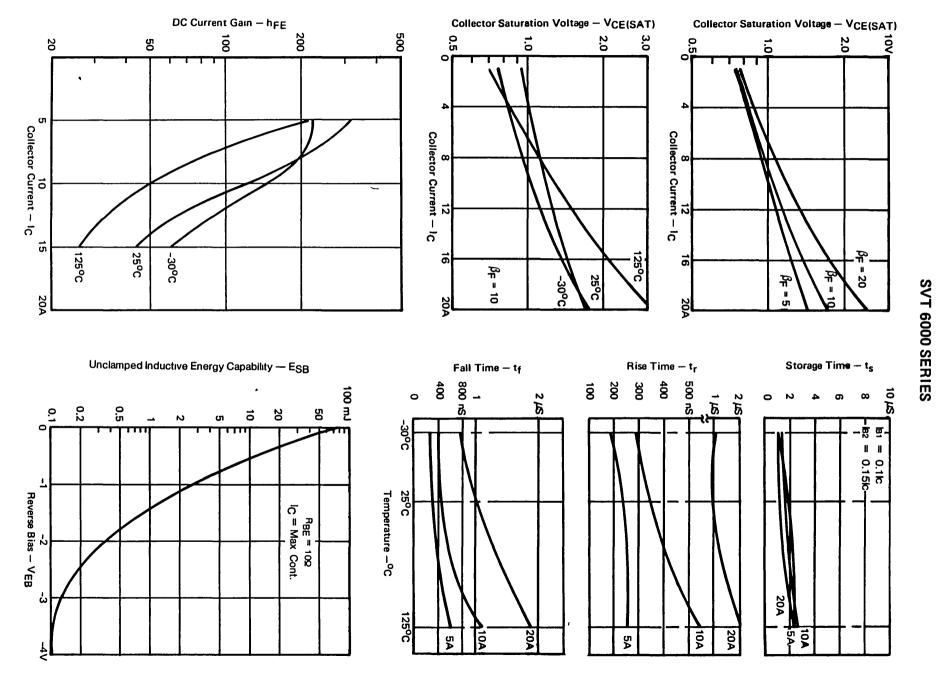

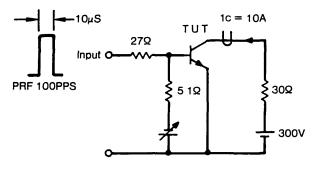

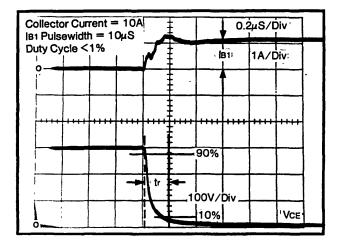

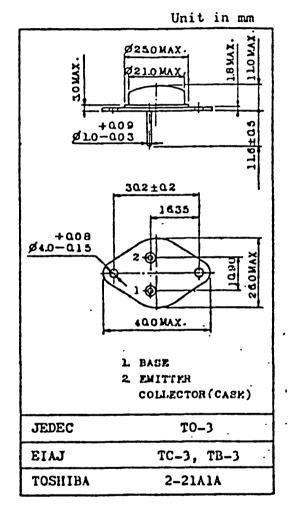

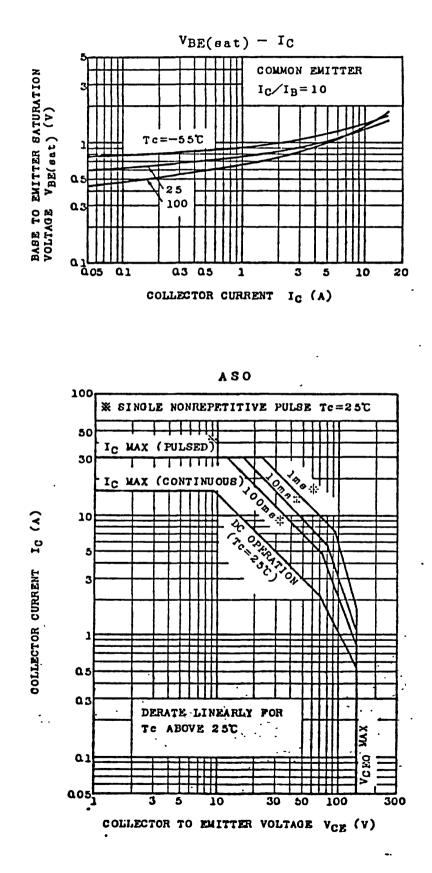

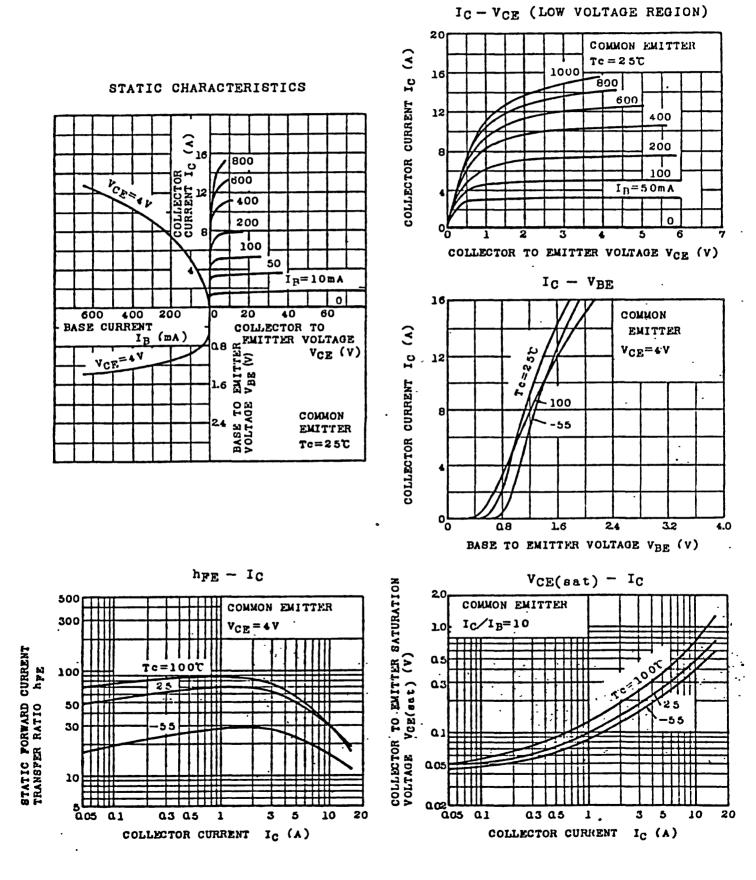

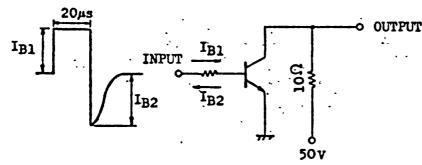

| APPENDIX 4A:Source Listing Of The Magslip System395Interrupt-Based Control Program395APPENDIX 4B:Source Listing Of The Seven Phase<br>Motor Interrupt-Based Control Program405APPENDIX 4C:Source Listing Of The Magslip Rotor-415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | APPENDIX 3B:  | Transistor Data Sheet (SVT6000 series)    | 38 <b>7</b>  |

| APPENDIX 4B:       Source Listing Of The Seven Phase       405         Motor Interrupt-Based Control Program       405         APPENDIX 4C:       Source Listing Of The Magslip Rotor-       415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | APPENDIX 3C:  | Transistor Data Sheet (2N3773)            | 391          |

| Motor Interrupt-Based Control Program<br>APPENDIX 4C: Source Listing Of The Magslip Rotor- 415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | APPENDIX 4A:  |                                           | 395          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | APPENDIX 4B:  |                                           | 405          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | APPENDIX 4C:  |                                           | 4 <b>1</b> 5 |

REFERENCES IN VOLUME ONE

-

.

425

•

|             |                        |      |                                                                               | Page         |

|-------------|------------------------|------|-------------------------------------------------------------------------------|--------------|

| CHAPT       | <u>TER 5</u> :         | THE  | SEVEN PHASE MOSFET INVERTER                                                   | 434          |

| 5.1         | Introduct              | ion  |                                                                               | 434          |

| 5.2         | Review of              | Pos  | sible Inverter Types                                                          | 434          |

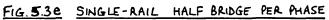

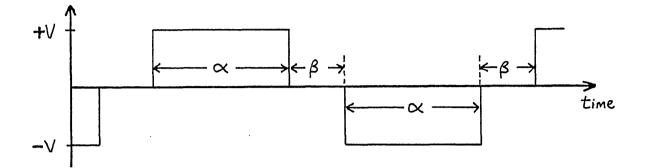

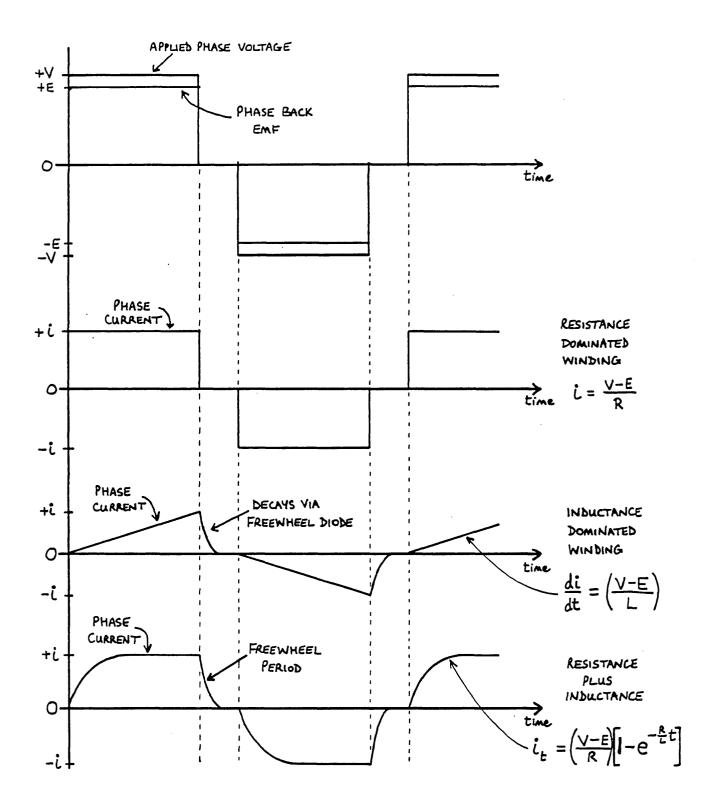

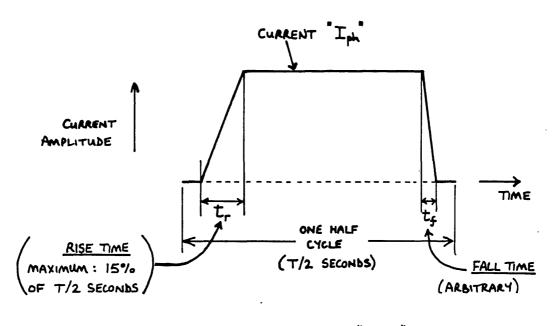

|             | 5.2.1                  | Wave | eform Shape                                                                   | 435          |

|             | 5.2.1.1                |      | Sinusoidal Waveform Inverter                                                  | 435          |

|             | 5.2.1.2                |      | Quasi-Square Waveform Inverter                                                | 435          |

|             | 5.2.1.3                |      | Complex Waveform Inverter                                                     | 436          |

|             | 5.2.2                  | Wave | eform Generation                                                              | 436          |

|             | 5.2.2.1                |      | Linear Mode Inverter                                                          | 436          |

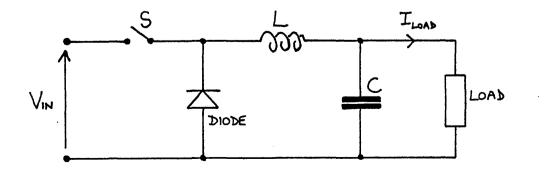

|             | 5.2.2.2                |      | Switching Mode Inverter                                                       | 43 <b>7</b>  |

|             | 5.2.3                  | Inve | erter Output Controlled Quantity                                              | 438          |

|             | 5.2.3.1                |      | Voltage Source Inverter                                                       | 438          |

|             | 5.2.3.2                |      | Current Source Inverter                                                       | 439          |

|             |                        |      | lished Literature on Various<br>ects of Inverters                             | 440          |

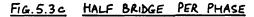

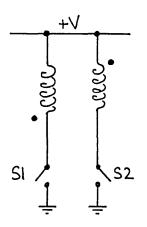

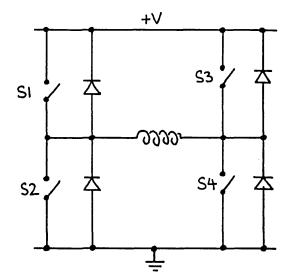

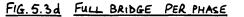

| 5.3         | The Chose              | n Ir | nverter Type                                                                  | 440          |

| 5.4         | The Choic<br>in the In |      | E Semiconductor Switch for Use<br>Cer                                         | 443          |

|             | 5.4.1                  | Thyı | ristor Characteristics                                                        | 444          |

|             | 5.4.2                  | Bipo | olar Transistor Characteristics                                               | 445          |

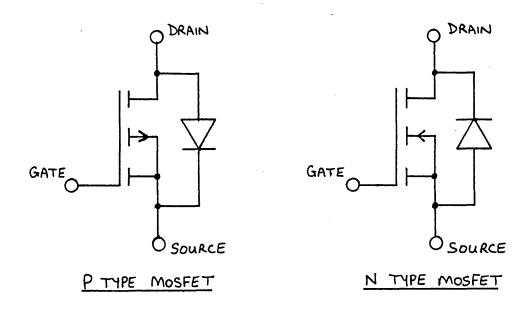

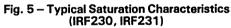

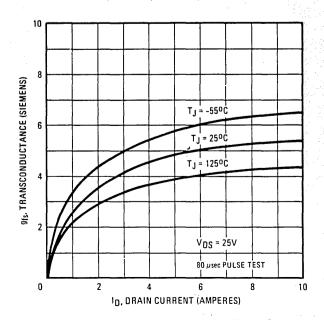

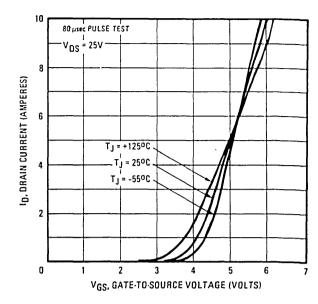

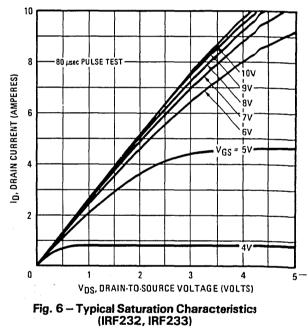

|             | 5.4.3                  | The  | MOSFET Transistor                                                             | 44 <b>7</b>  |

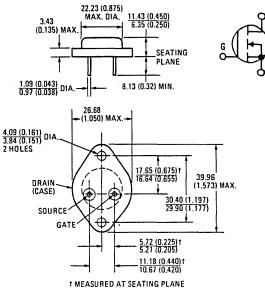

|             | 5.4.4                  | The  | Chosen Inverter Switching Device                                              | 450          |

| 5.5         | The Inver              | ter  | Design                                                                        | 456          |

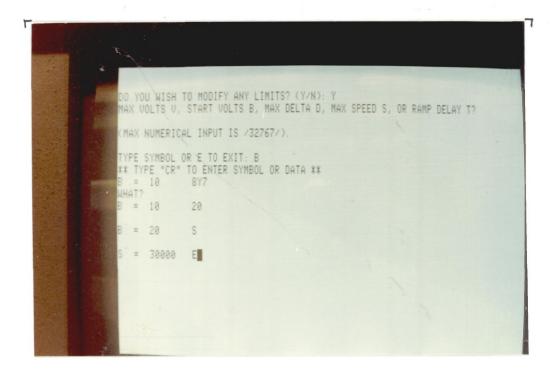

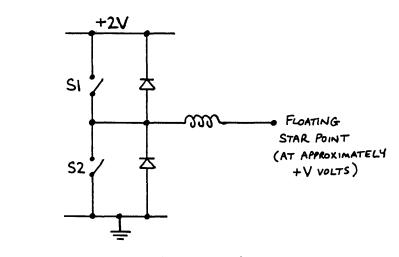

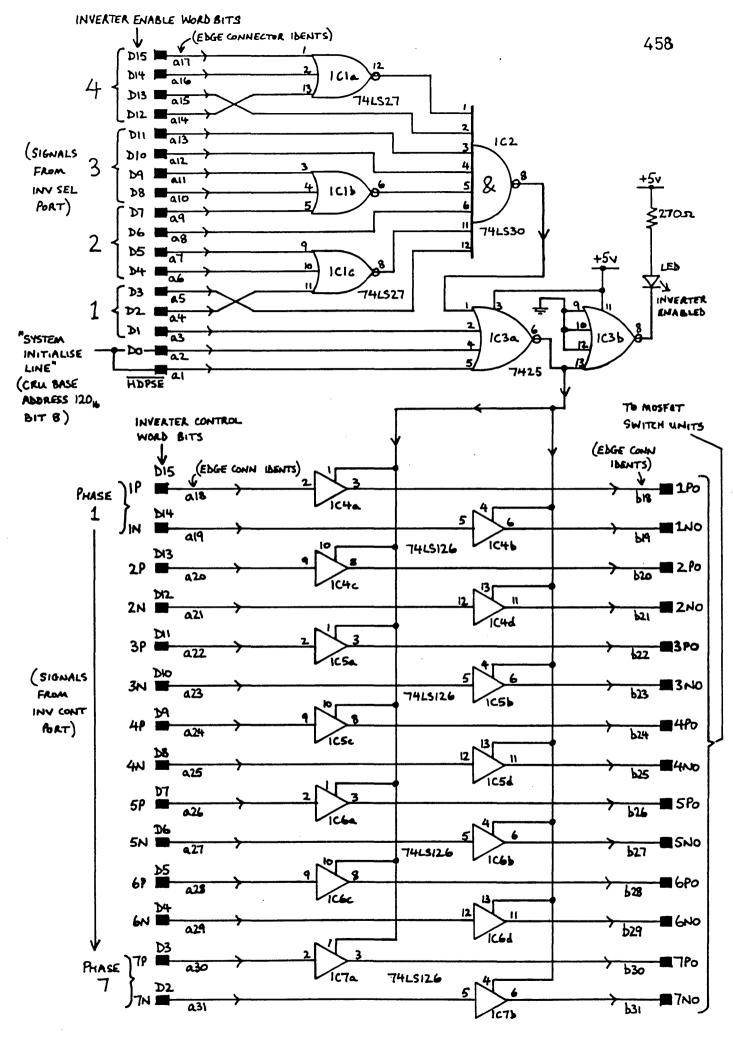

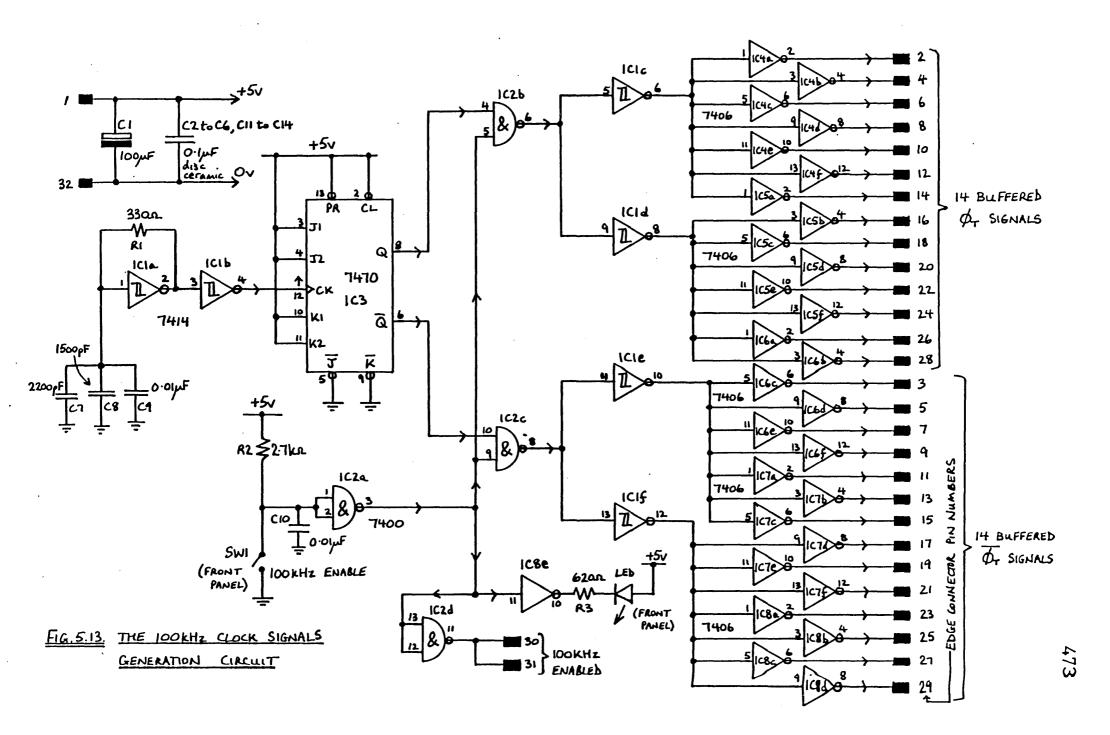

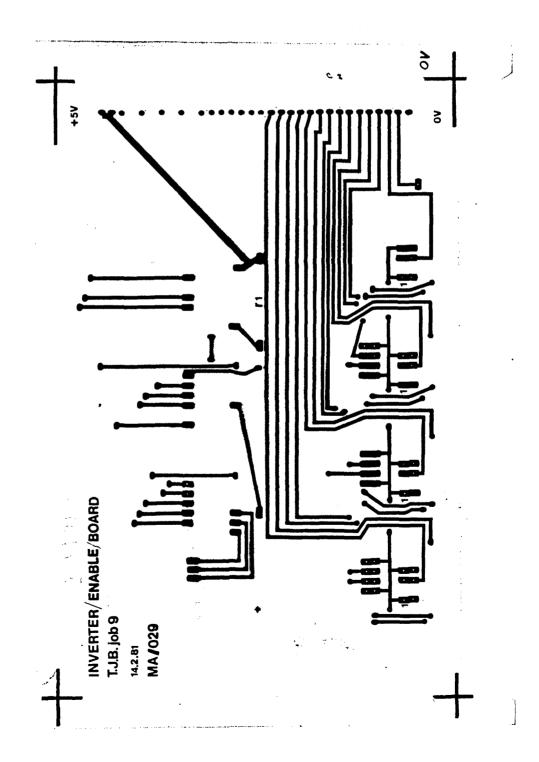

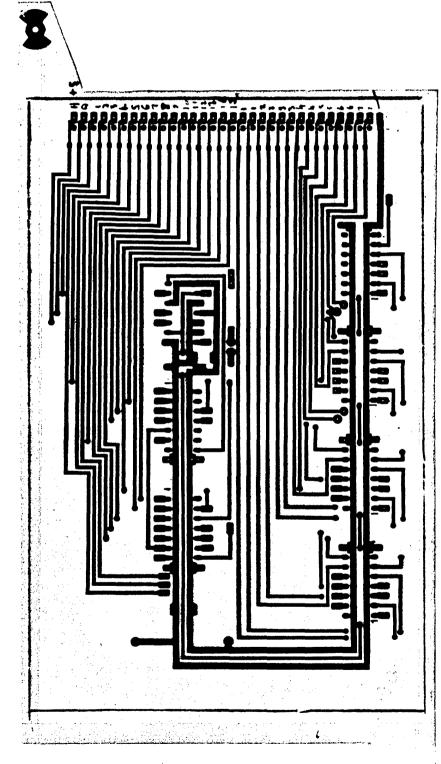

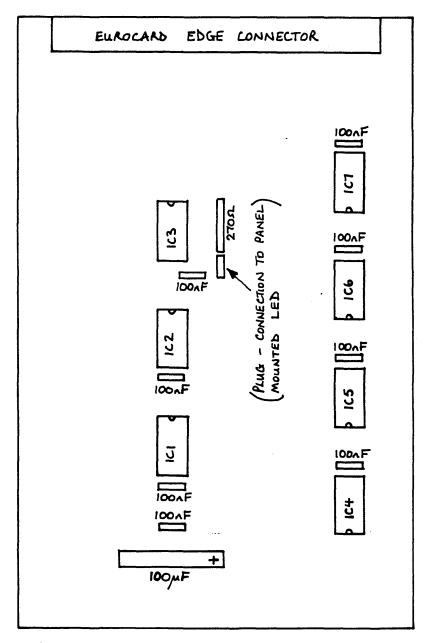

|             | 5.5.1                  | The  | Inverter Control Logic                                                        | 45 <b>7</b>  |

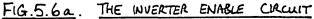

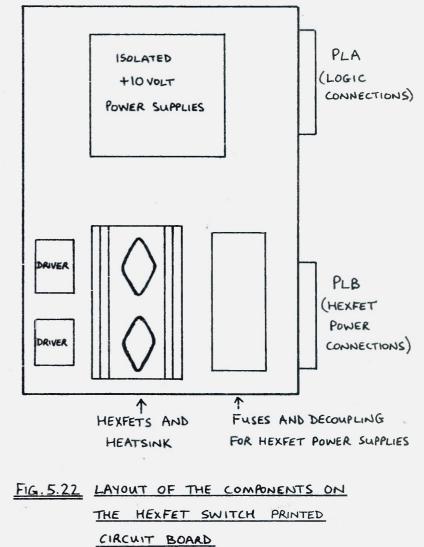

|             | 5.5.2                  | The  | Hexfet Switch Unit                                                            | 460          |

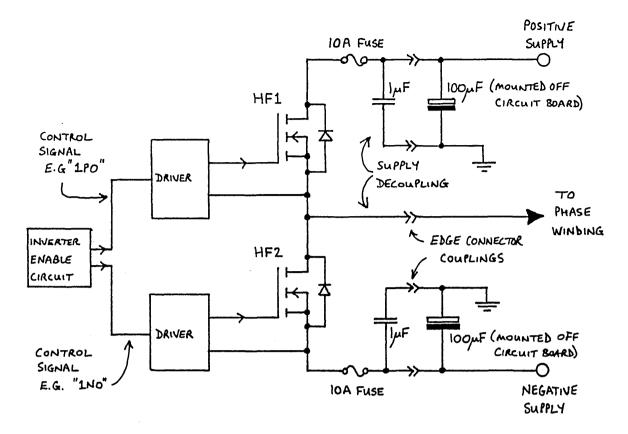

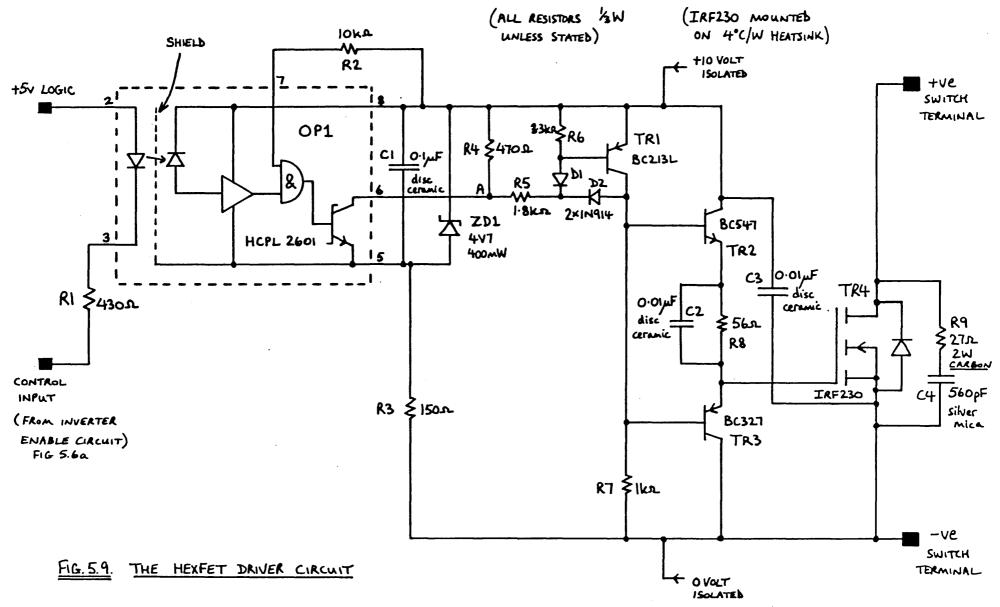

|             | 5.5.2.1                |      | Hexfet Driver Circuit Design                                                  | 463          |

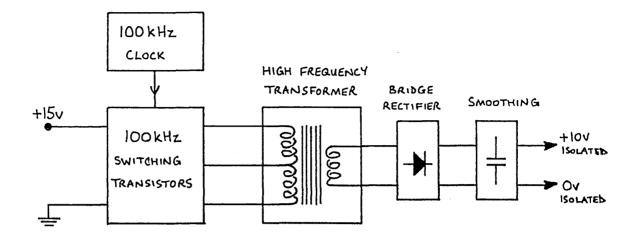

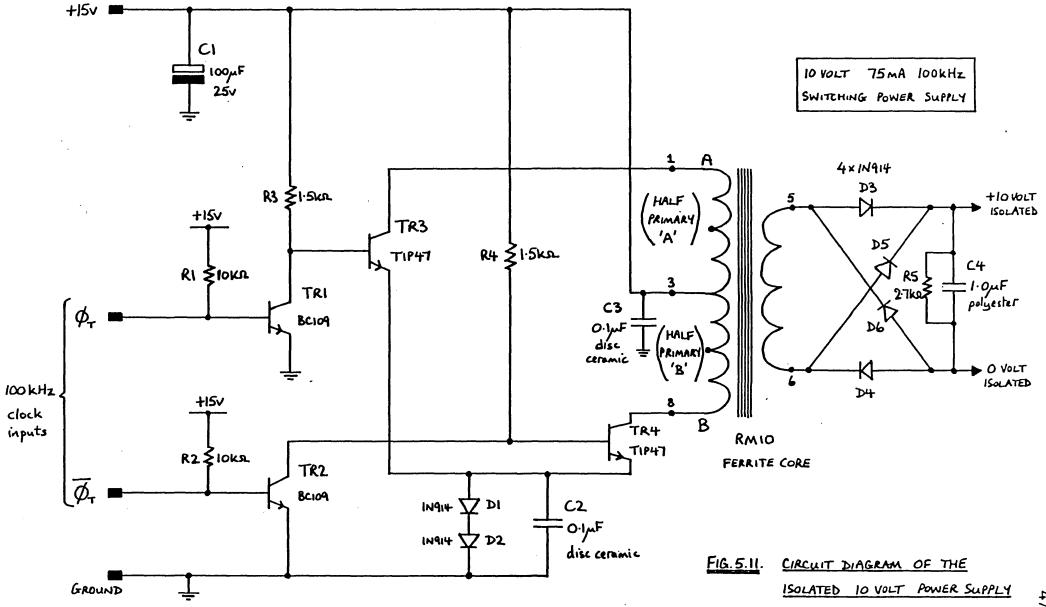

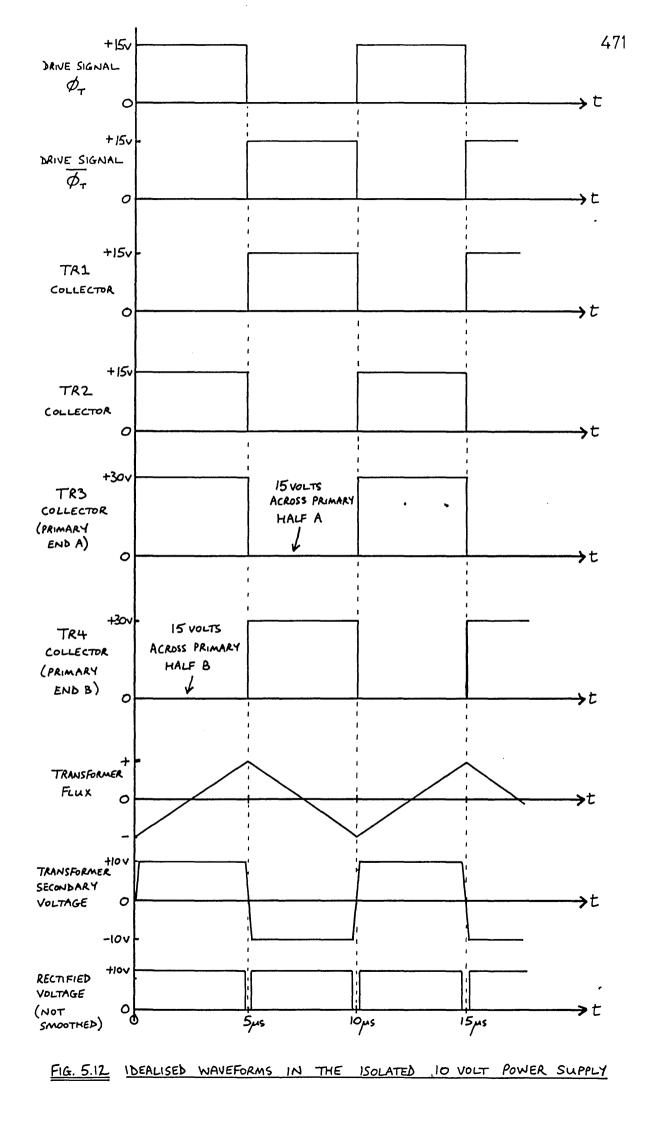

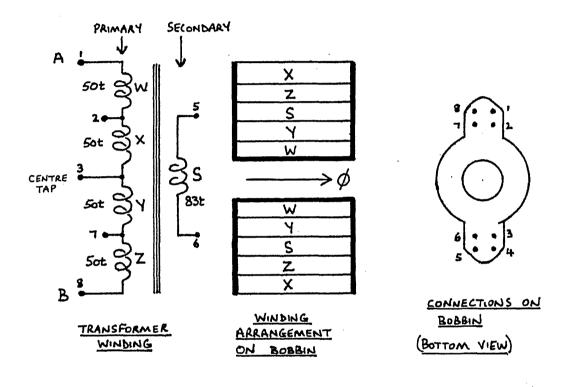

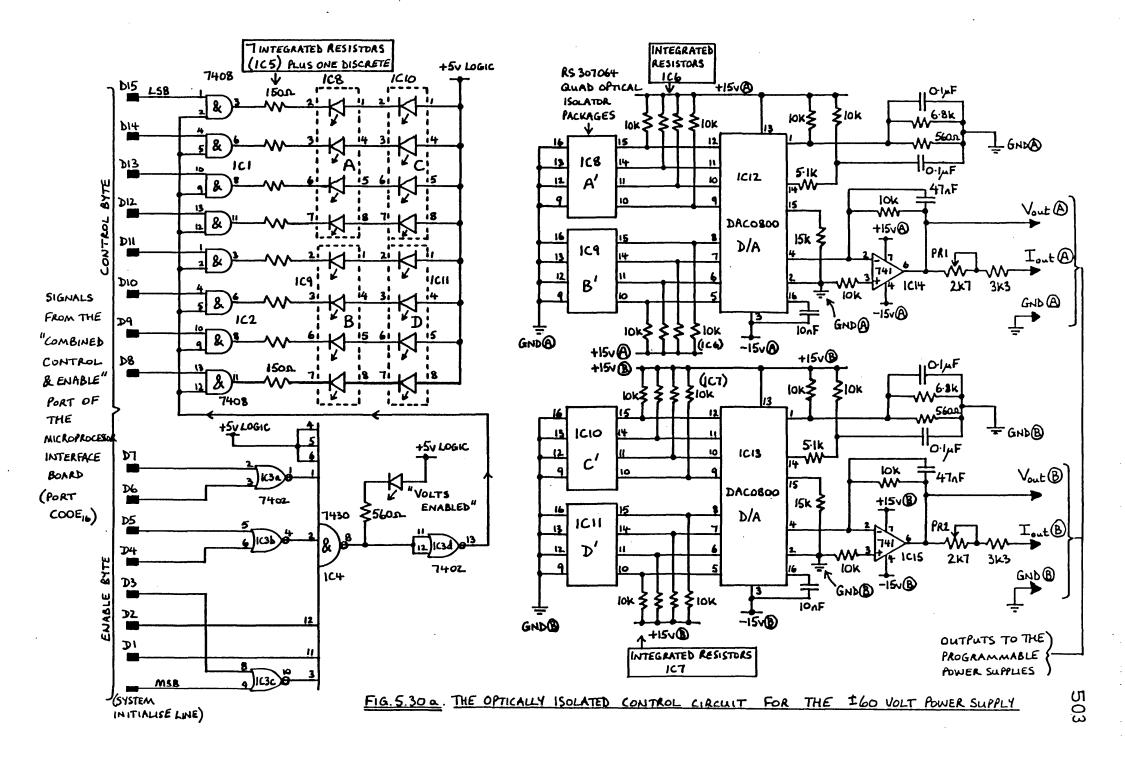

|             | 5.5.2.2                | 2    | The Floating Power Supplies for the Hexfet Driver Circuit                     | . 468        |

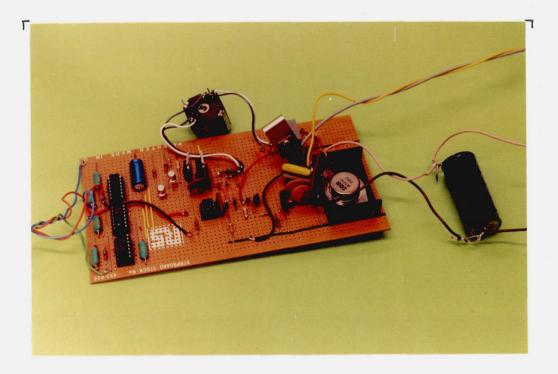

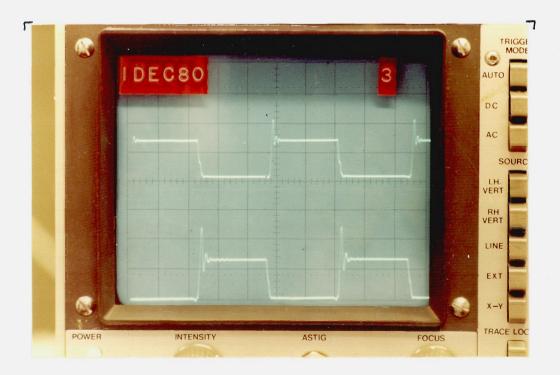

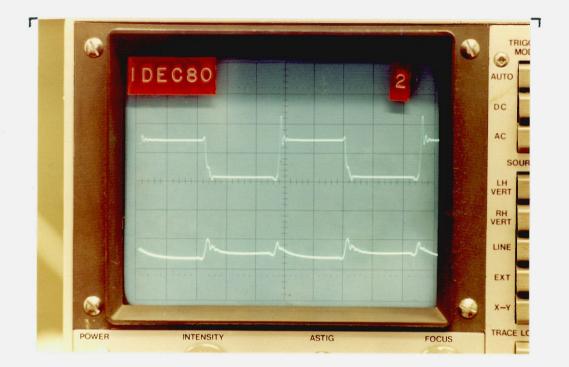

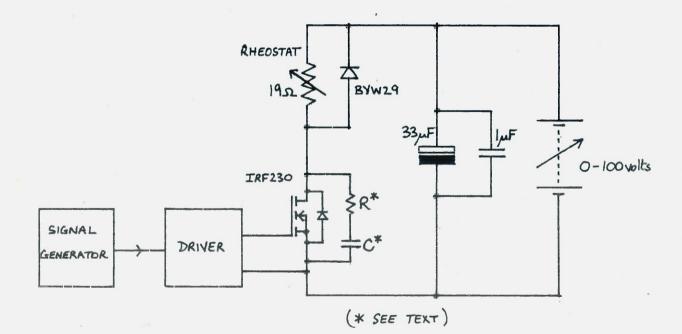

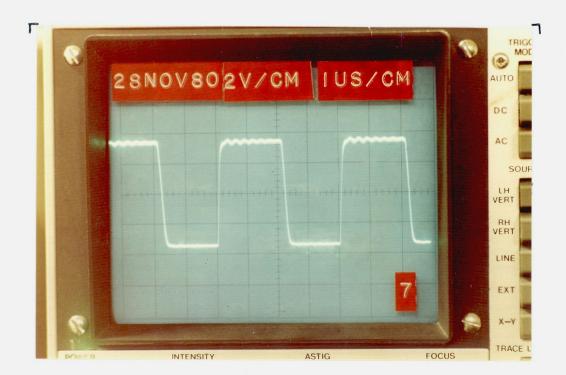

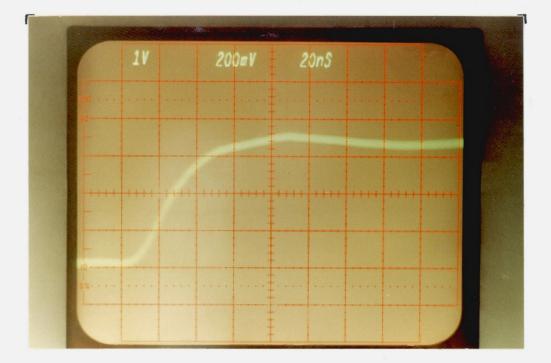

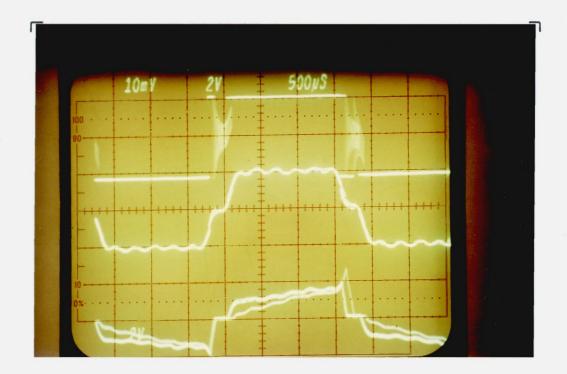

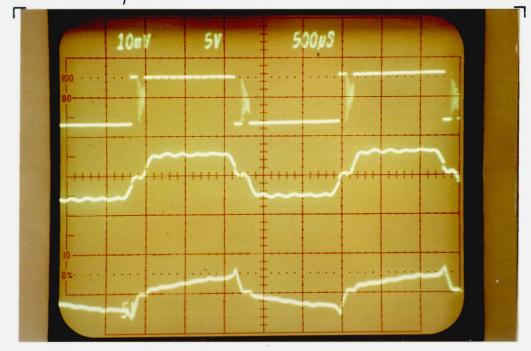

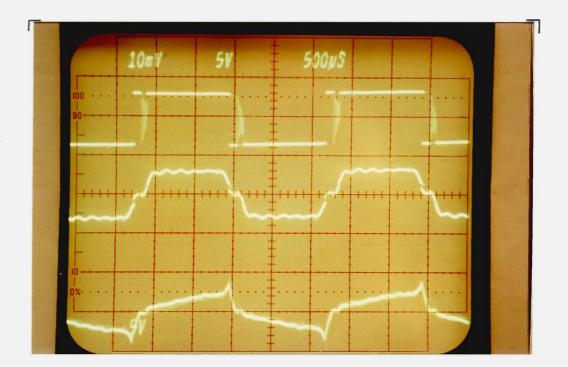

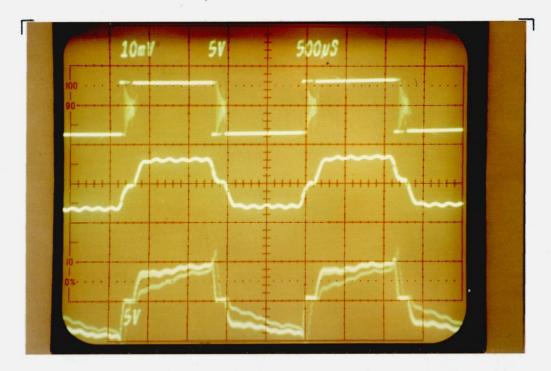

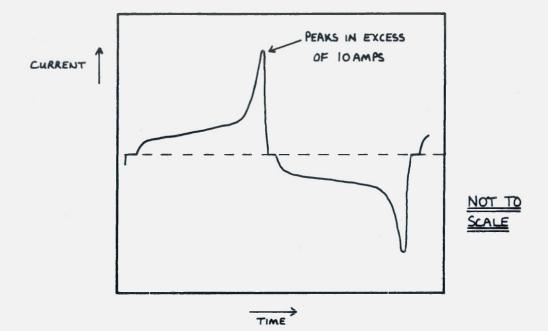

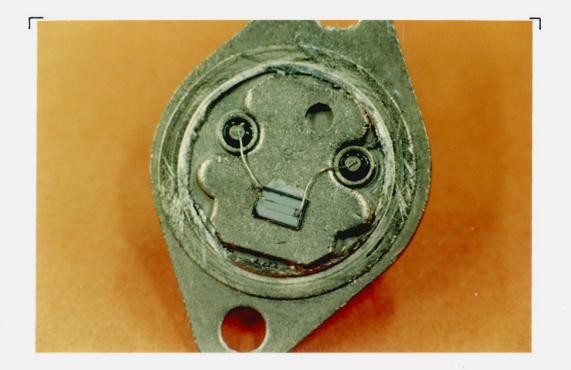

|             | 5.5.2.3                | }    | The Testing of the Prototype<br>Switch Unit                                   | 4 <b>7</b> 8 |

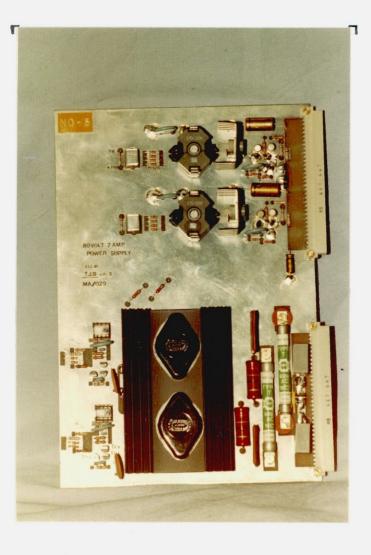

|             | 5.5.2.4                |      | The Design of the Printed Circuit<br>Boards for the Hexfet Switch<br>Circuits | 483          |

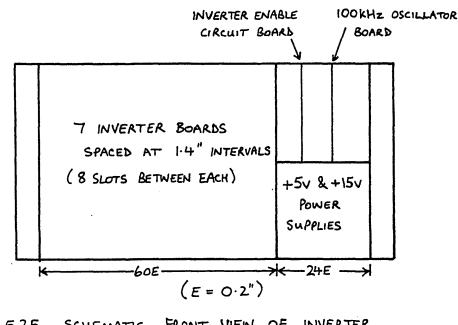

|             | 5.5.3                  |      | Inverter Assembly and Initial<br>ting                                         | 494          |

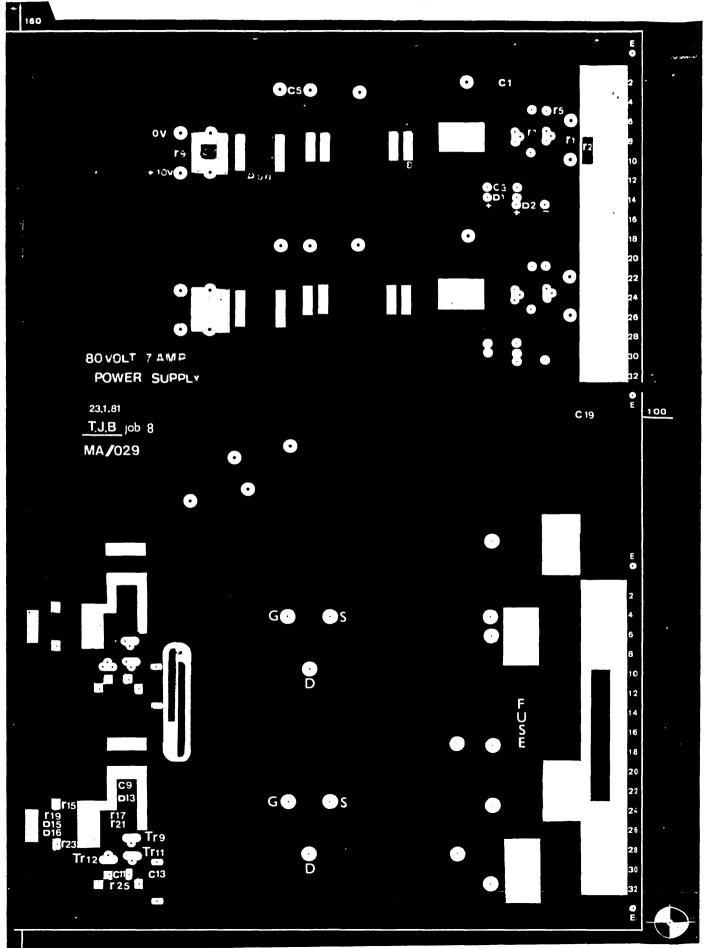

| 5.6         | The Varia              | ble  | D.C. Inverter Voltage Supplies                                                | 500          |

| 5 <b>.7</b> | Precautic              | mar  | y Current Limit Components                                                    | 508          |

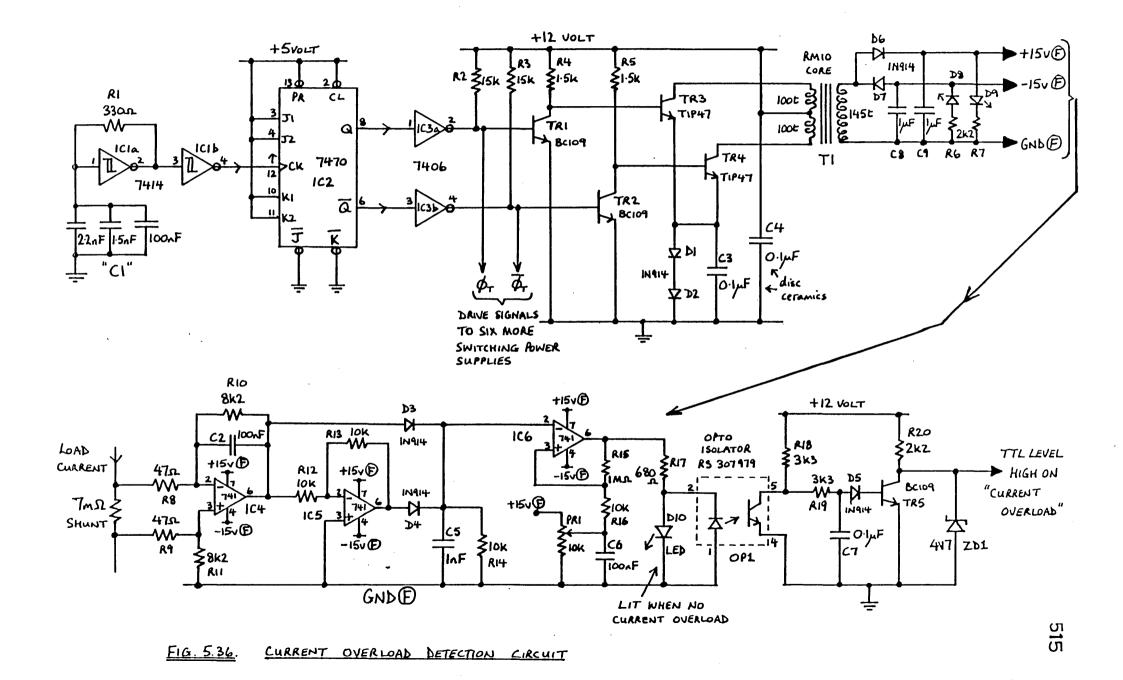

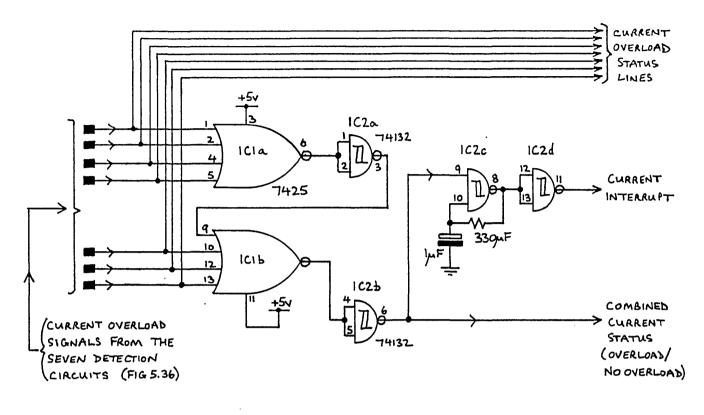

| 5.8         | Current I              | eve. | l Detection                                                                   | 512          |

| 5.9         | Conclusio              | ons  |                                                                               | 5 <b>1</b> 6 |

,

-

|--|

Page

| CHAPTER 6: |                                                                                    | THE DESIGN AND CONSTRUCTION OF A<br>"SQUARE WAVE" SYNCHRONOUS MOTOR<br>AND ITS ASSOCIATED POSITION SENSOR | 518          |

|------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------|

| 6.1        | Introduc                                                                           | tion                                                                                                      | 518          |

| 6.2        | Initial D                                                                          | Motor Design Decisions                                                                                    | 519          |

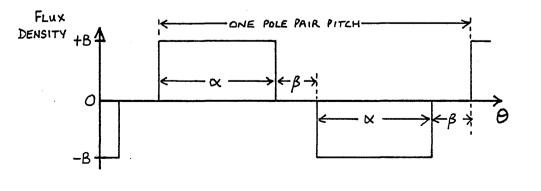

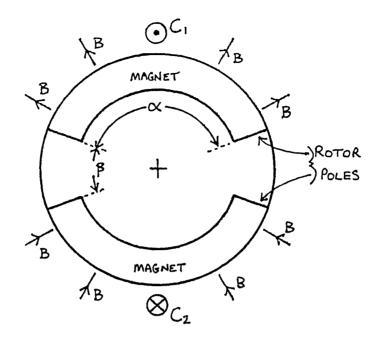

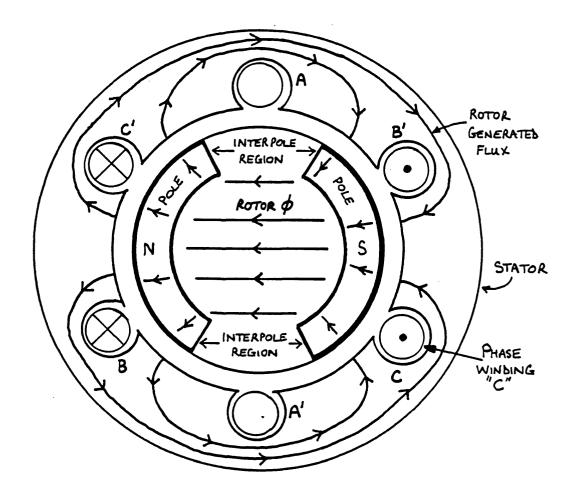

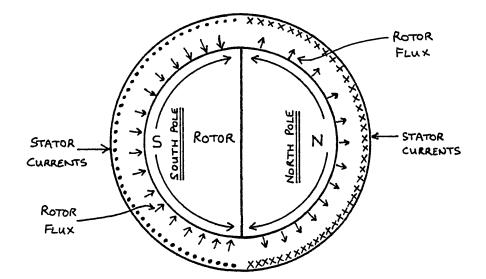

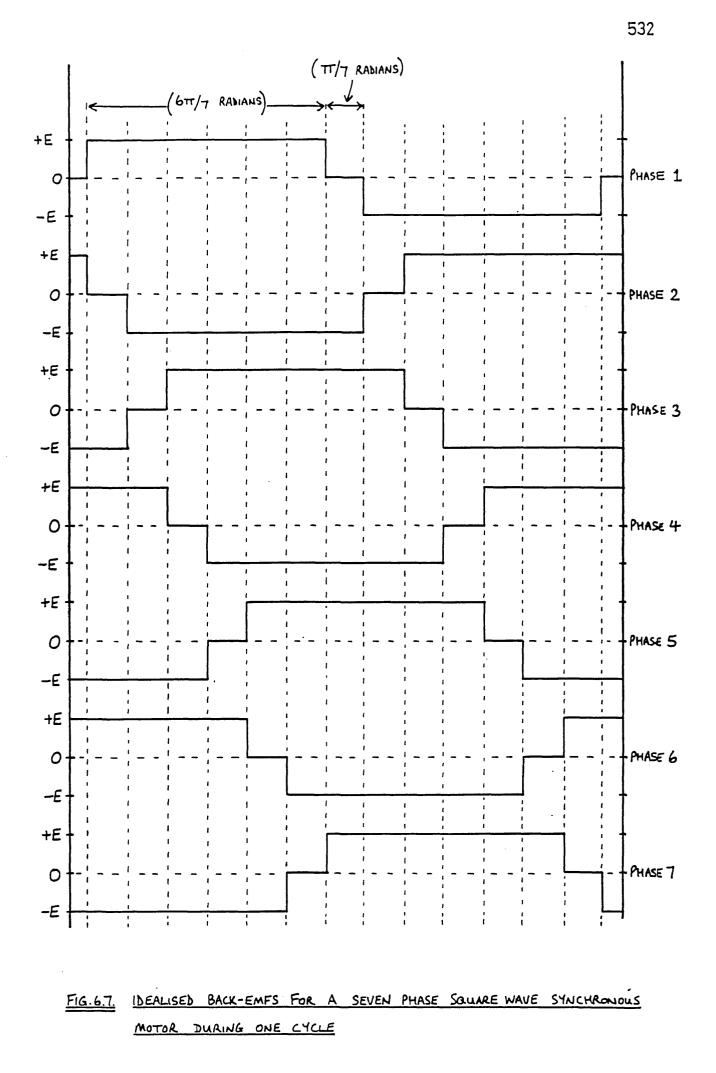

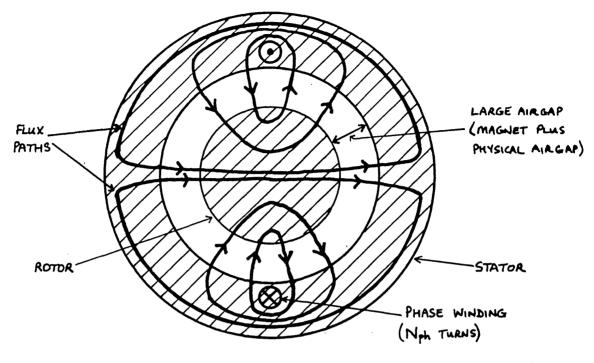

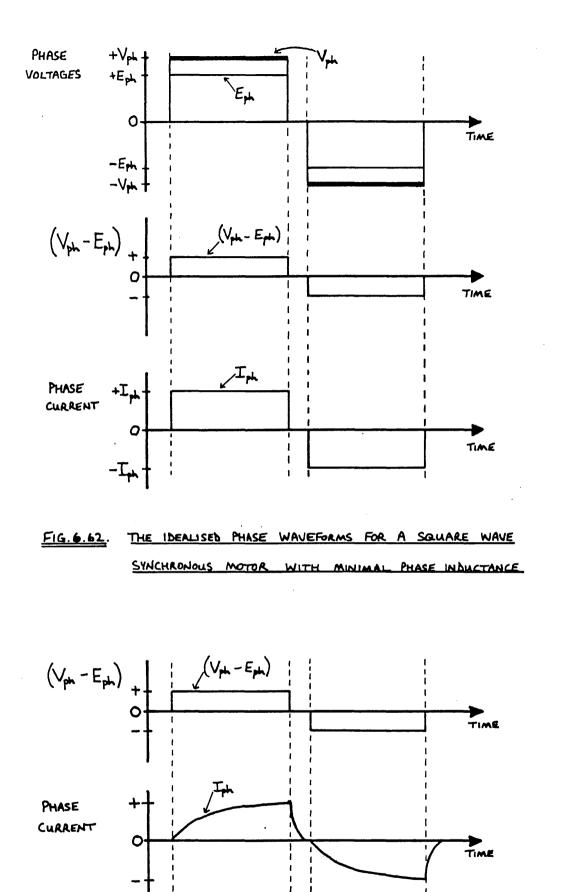

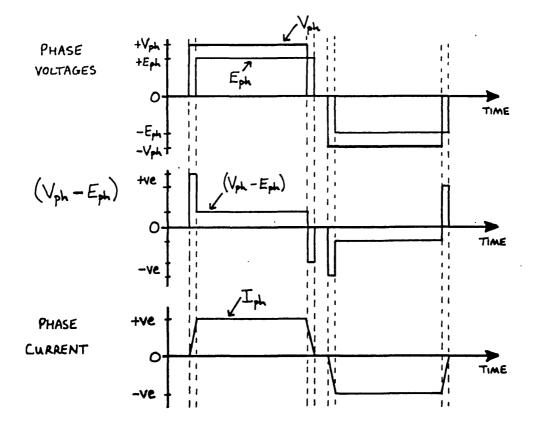

| 6.3        | The Basic Requirements For and the Operation<br>Of a Square Wave Synchronous Motor |                                                                                                           |              |

| 6.4        | Choice of                                                                          | f the Number of Phases                                                                                    | 530          |

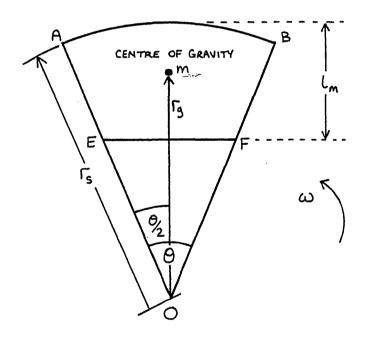

| 6.5        | The Desi                                                                           | gn of the Rotor                                                                                           | 533          |

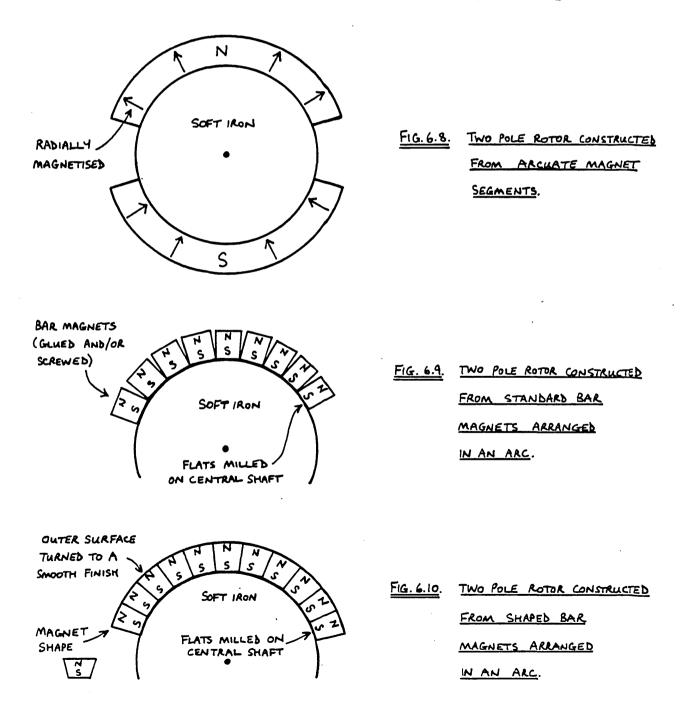

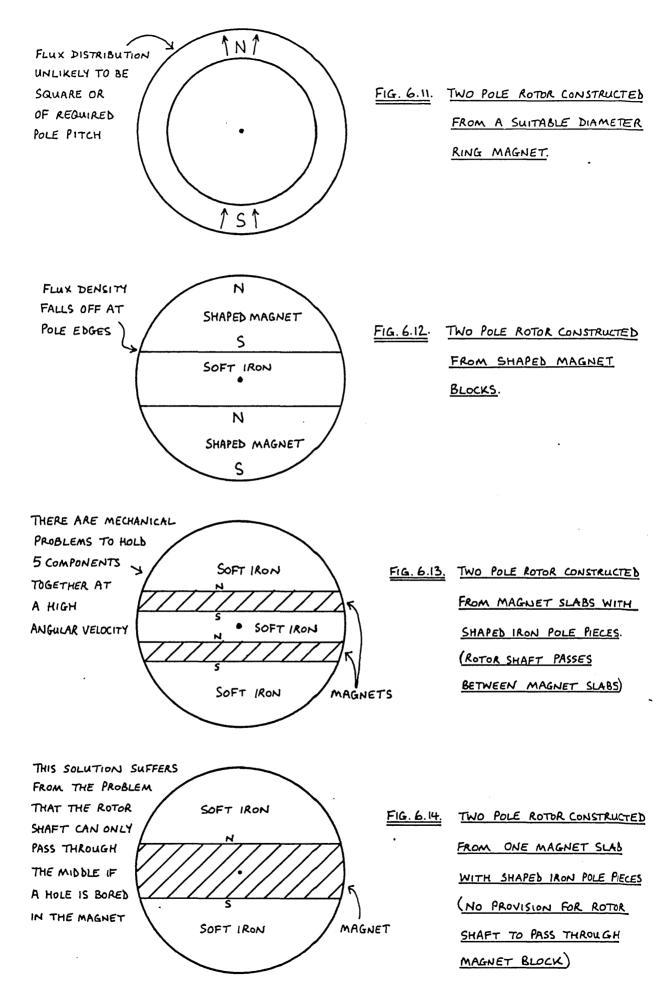

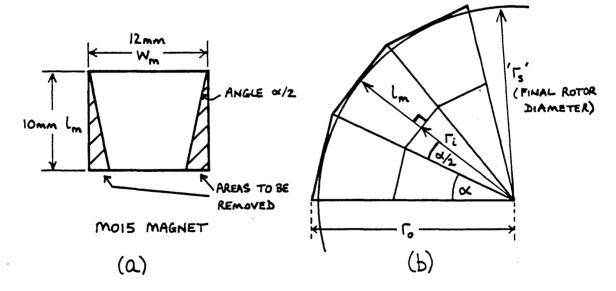

|            | 6.5.1                                                                              | Rotor Magnet Configurations                                                                               | 534          |

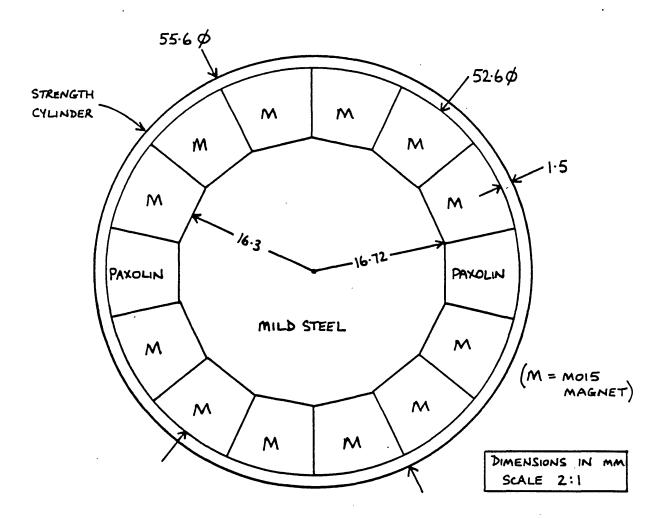

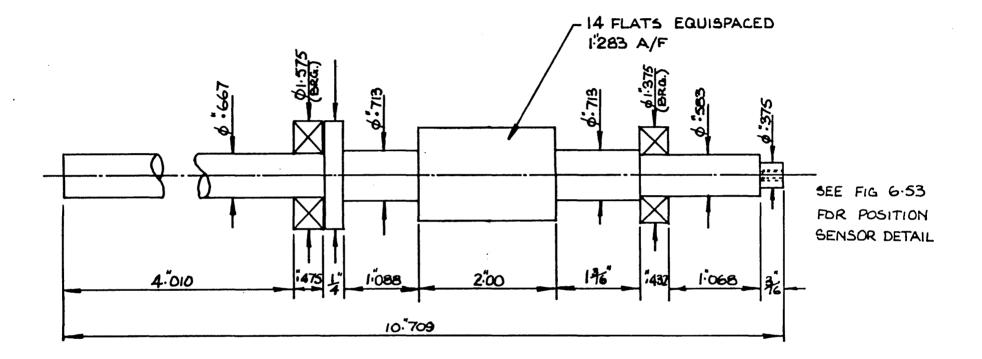

|            | 6.5.2                                                                              | Final Dimensions of Rotor                                                                                 | 539          |

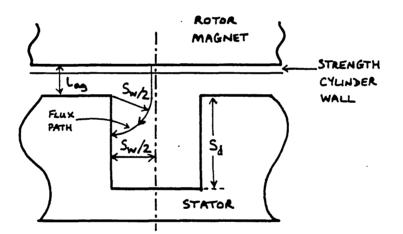

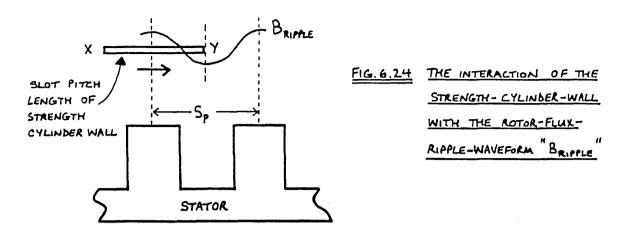

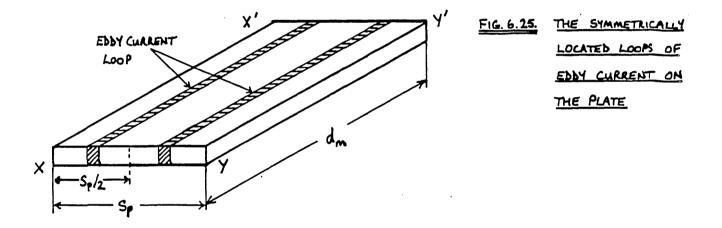

|            | 6.5.3                                                                              | Choice of a Suitable Strength<br>Cylinder for the Rotor                                                   | 545          |

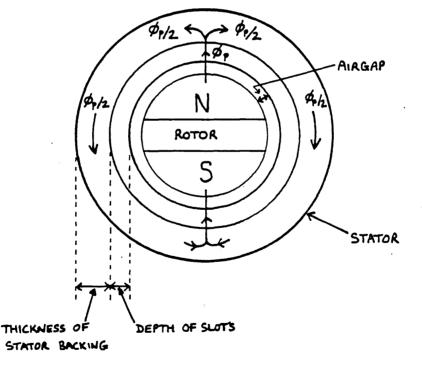

| 6.6        | The Desi                                                                           | gn of the Stator                                                                                          | 55 <b>7</b>  |

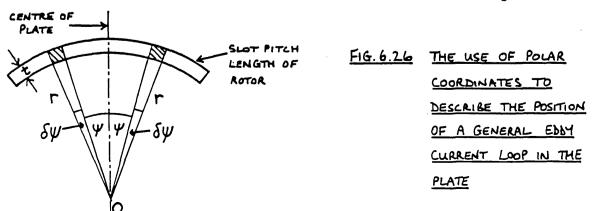

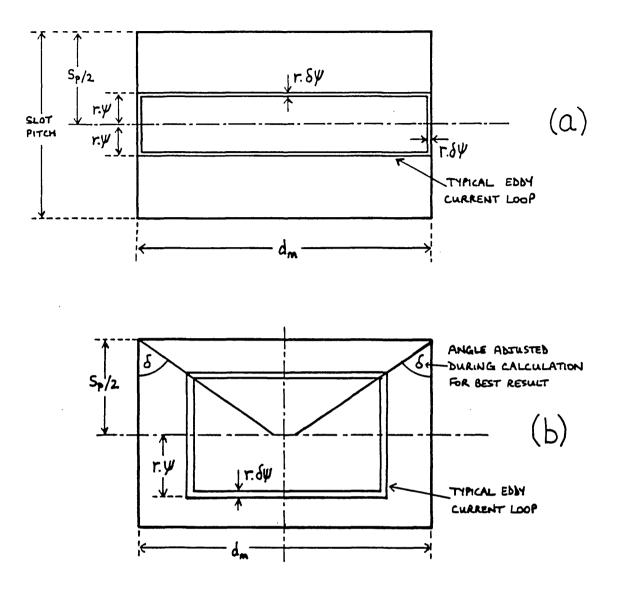

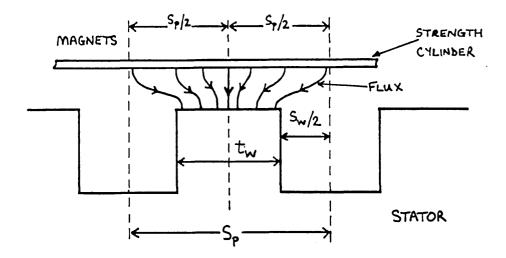

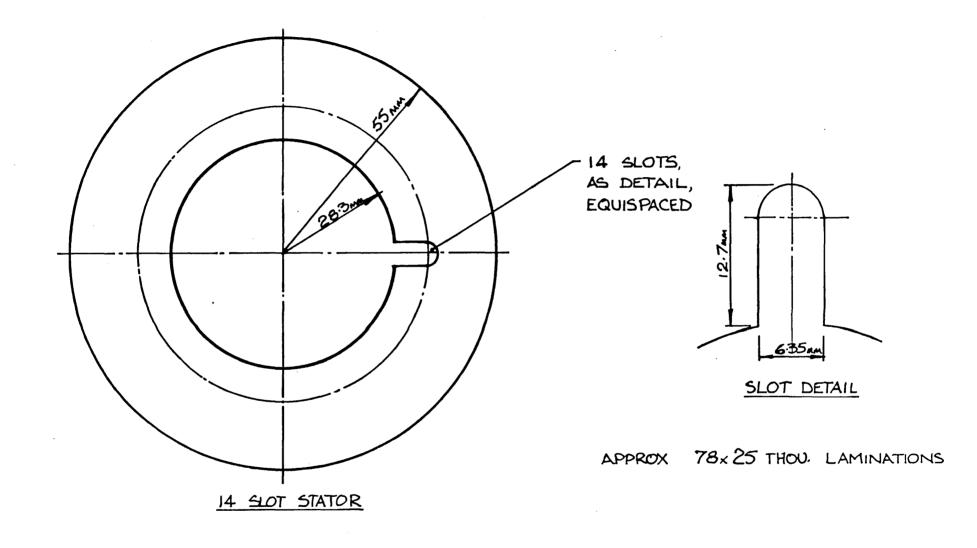

|            | 6.6.1                                                                              | Slot Pitch                                                                                                | 55 <b>7</b>  |

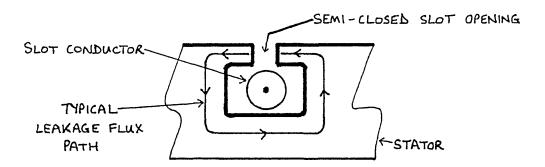

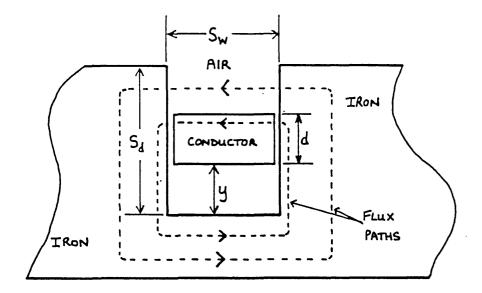

|            | 6.6.2                                                                              | Tooth and Slot Widths                                                                                     | 55 <b>7</b>  |

|            | 6.6.3                                                                              | The Slot Depth                                                                                            | 56 <b>1</b>  |

|            | 6.6.4                                                                              | The Stator Axial Length, l                                                                                | 565          |

|            | 6.6.5                                                                              | The Thickness of the<br>Stator Backing Iron, S <sub>h</sub>                                               | 565          |

|            | 6.6.6                                                                              | The Thickness of the<br>Stator Laminations                                                                | 56 <b>7</b>  |

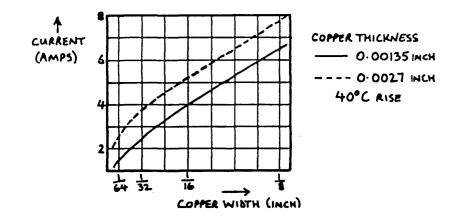

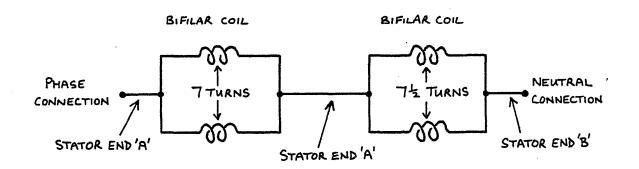

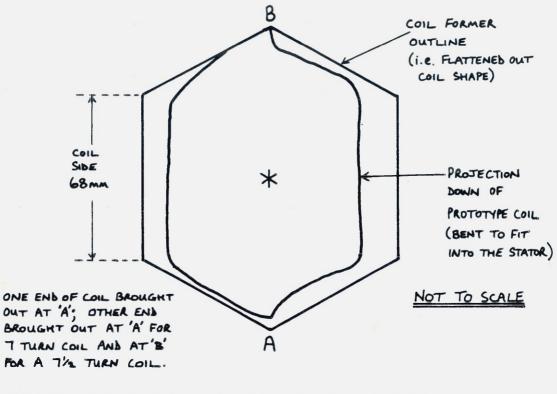

|            | 6 <b>.</b> 6 <b>.7</b>                                                             | The Number of Turns per Phase, N <sub>ph</sub> ,<br>and the Minimum Wire Diameter                         | 56 <b>7</b>  |

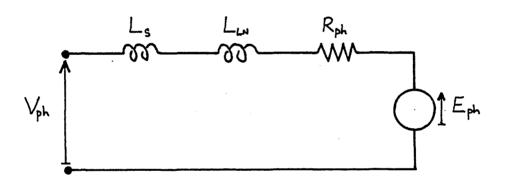

|            | 6.6.8                                                                              | Calculation of the Resistance and<br>Self Inductance of a Typical<br>Phase Winding                        | 5 <b>7</b> 0 |

|            | 6.6.9                                                                              | Stator Copper Loss                                                                                        | 572          |

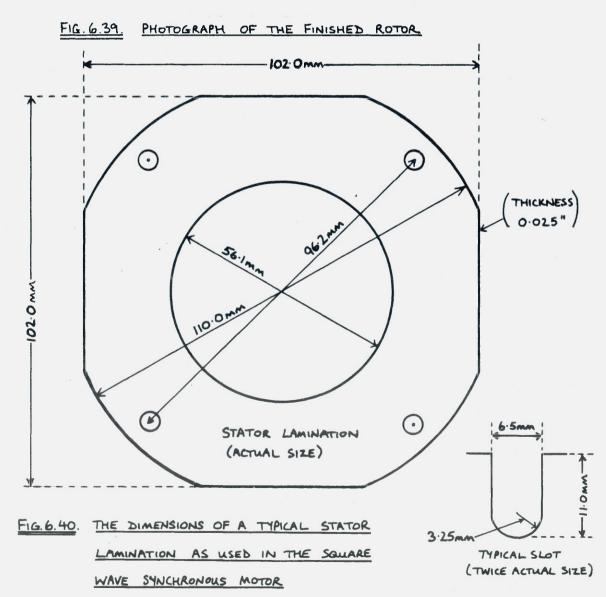

|            | 6.6.10                                                                             | Final Proposed Stator Lamination<br>Cross Section                                                         | 5 <b>7</b> 3 |

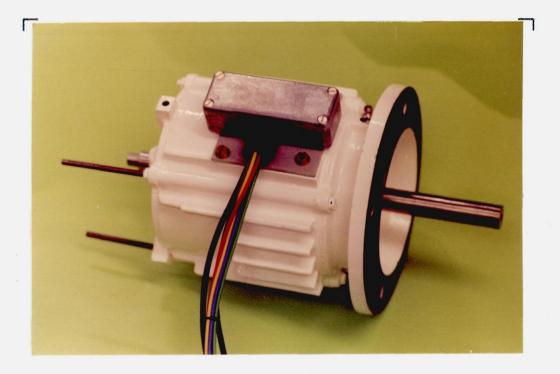

| 6.7        | Construc                                                                           | tional Details of the Motor                                                                               | 5 <b>7</b> 3 |

|            | 6.7.1                                                                              | The Rotor Construction                                                                                    | 5 <b>7</b> 3 |

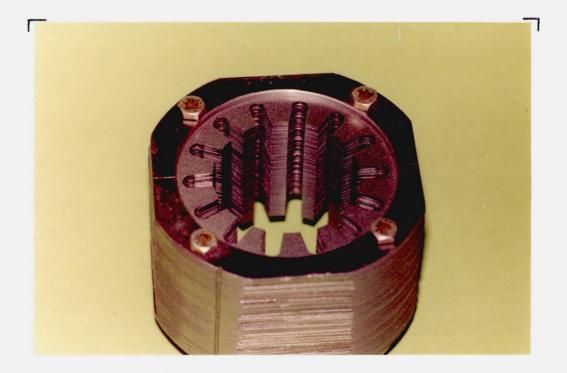

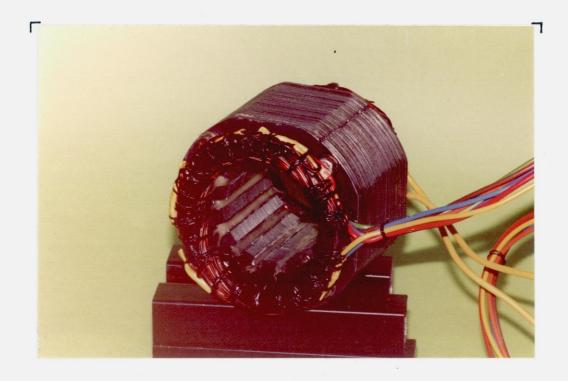

|            | 6.7.2                                                                              | The Stator Construction                                                                                   | 5 <b>7</b> 8 |

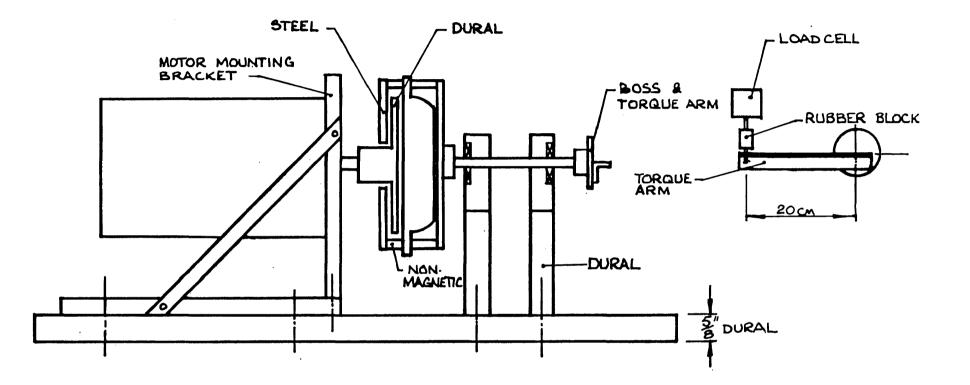

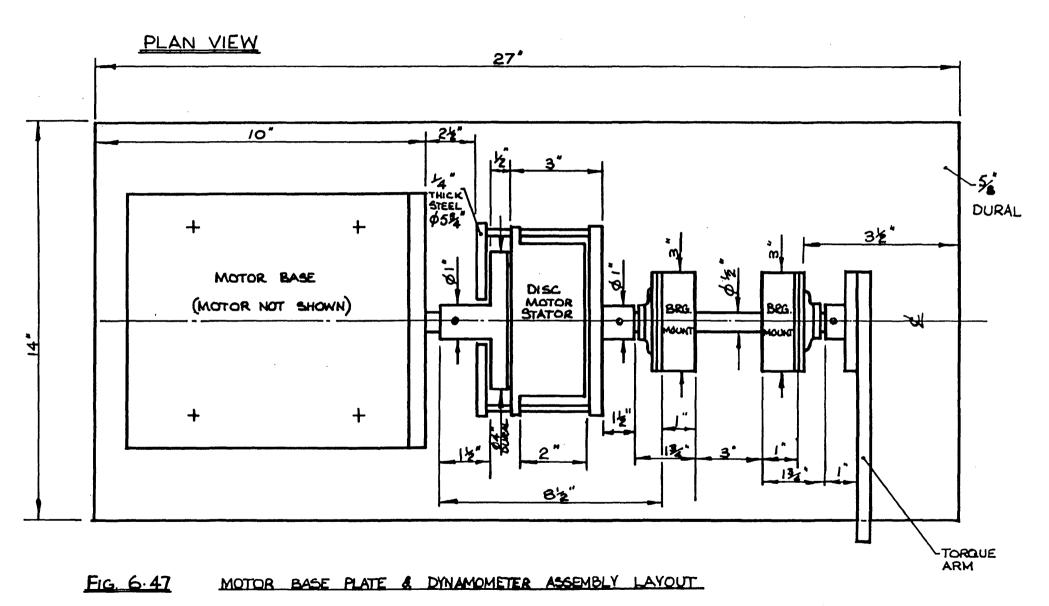

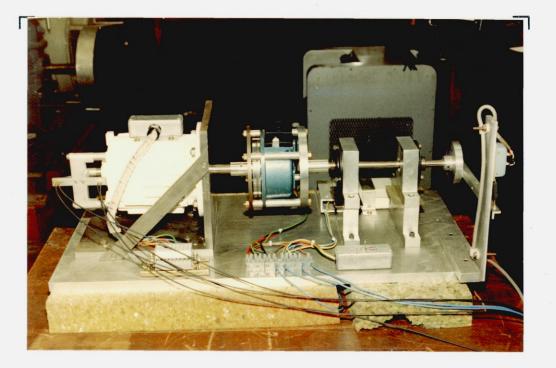

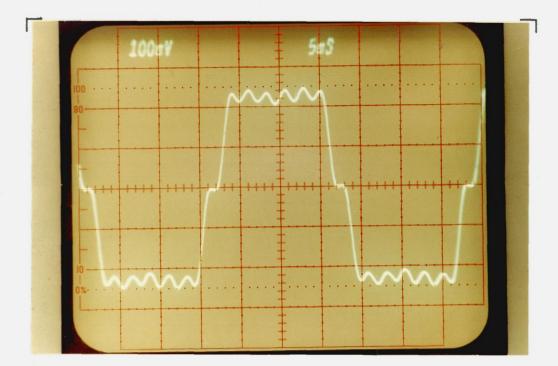

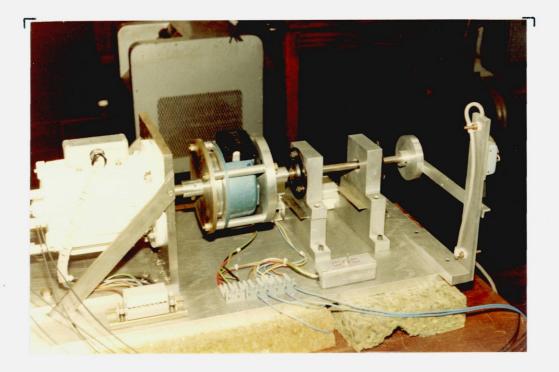

| 6.8        | Motor Te                                                                           | st Rig                                                                                                    | 583          |

| 6.9        | Motor Pa                                                                           | rameter Checks                                                                                            | 58 <b>7</b>  |

|            | 6.9.1                                                                              | Phase Winding Resistance and<br>Inductance                                                                | 58 <b>7</b>  |

|            | 6.9.2                                                                              | Motor Cogging Torque                                                                                      | 588          |

|            | 6.9.3                                                                              | Rotor Airgap Flux Density                                                                                 | 588          |

|            | 6.9.4                                                                              | Summary of Motor Parameters                                                                               | 59 <b>1</b>  |

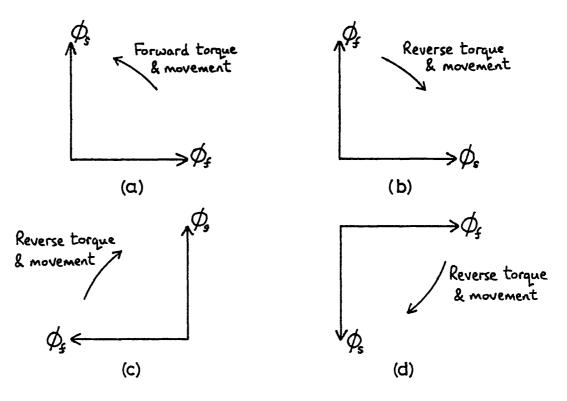

| 6.10       | Rotor Po                                                                           | sition Sensor Unit                                                                                        | 592          |

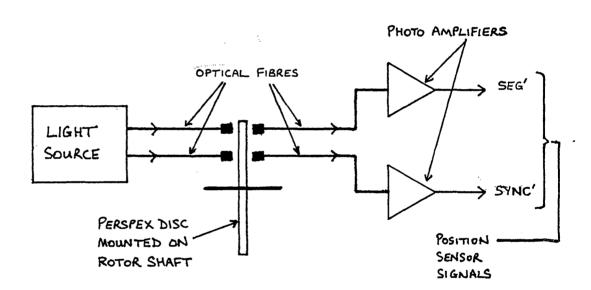

|            | 6.10.1                                                                             | The Basic System                                                                                          | 592          |

•

.

-

| Page |

|------|

|      |

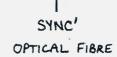

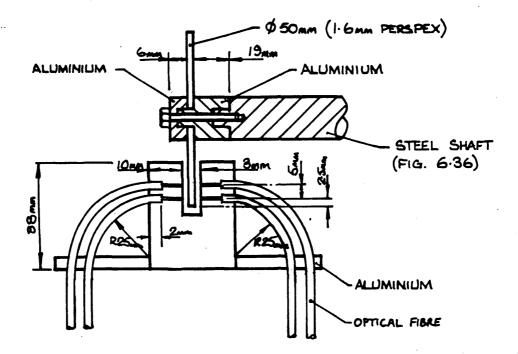

|      | 6.10.2                                                                                               | Practical Details of the Position<br>Sensor System                                              | 595          |

|------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------|

|      | 6.10.2                                                                                               | .1 The Optical Fibre                                                                            | 595          |

|      | 6.10.2                                                                                               | .2 The Light Source                                                                             | 595          |

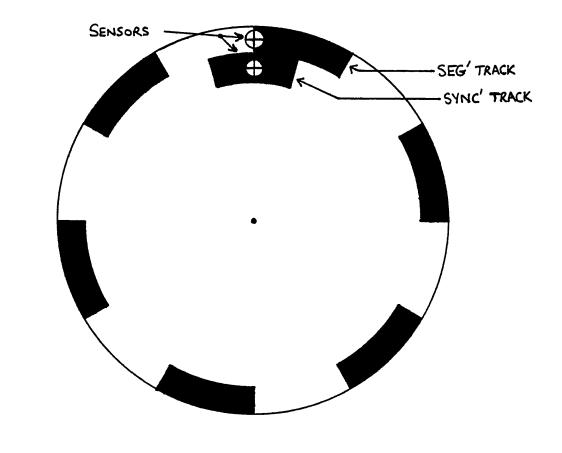

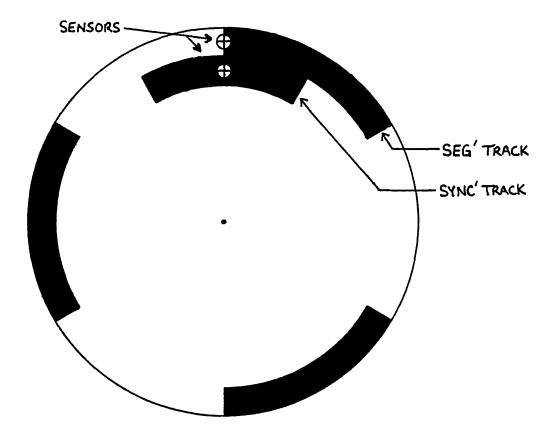

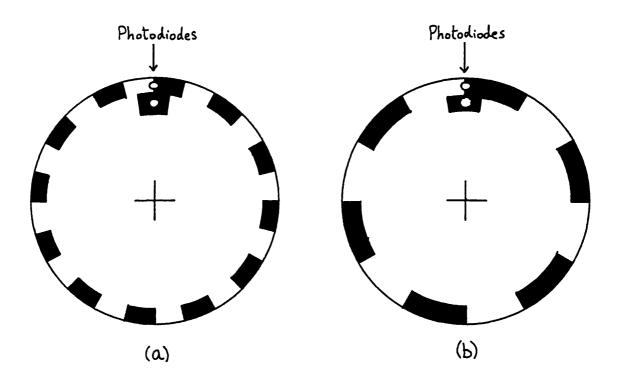

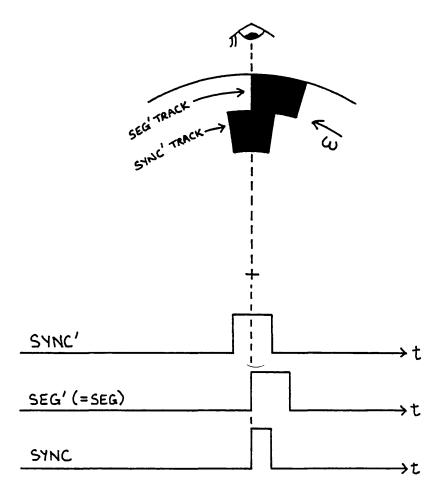

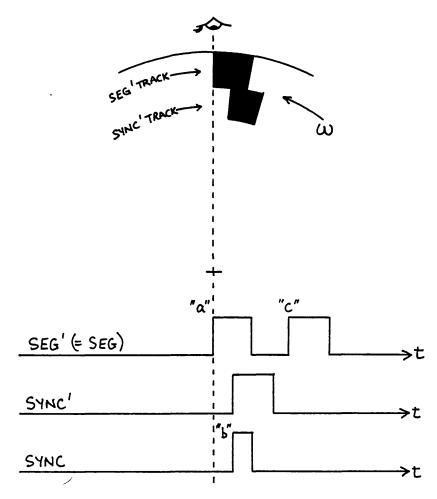

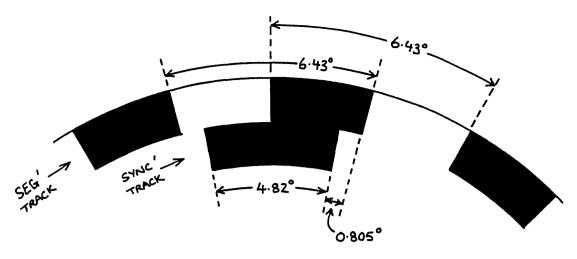

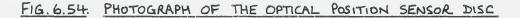

|      | 6.10.2                                                                                               | .3 The Perspex Disc and SEG'/SYNC'<br>Pattern                                                   | 596<br>-     |

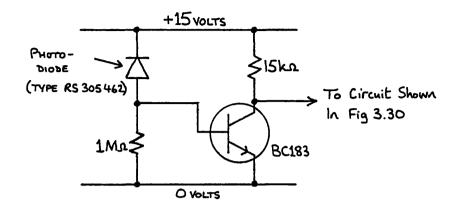

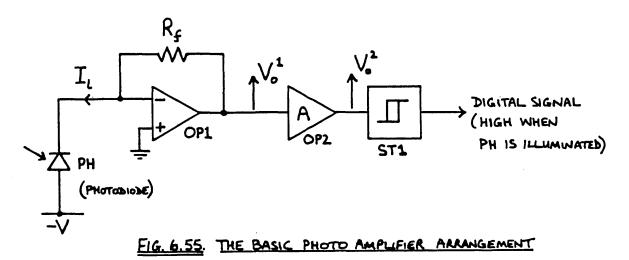

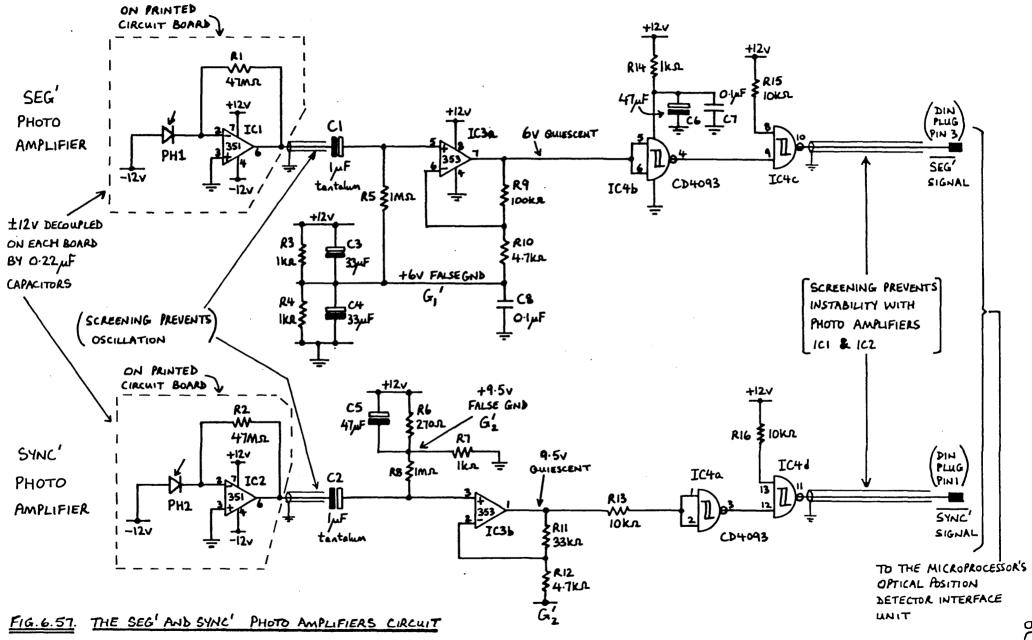

|      | 6.10.2                                                                                               | .4 The Photo Amplifiers                                                                         | 599          |

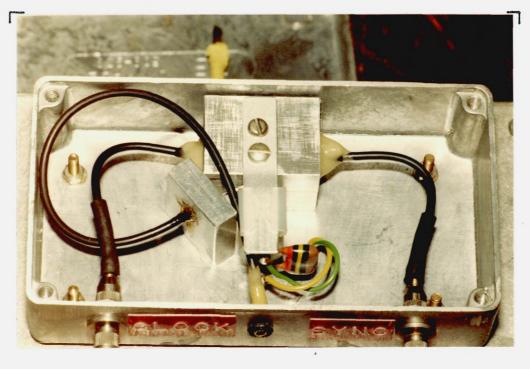

|      | 6.10.2                                                                                               | .5 Final Assembly of Photo<br>Amplifier/Light Source Unit                                       | 608          |

|      | 6.10.2                                                                                               | .6 The Number of SEG' Pulses per<br>Revolution and Aspects of<br>System Operation               | 608          |

| 6.11 | Conclusi                                                                                             | ons                                                                                             | 615          |

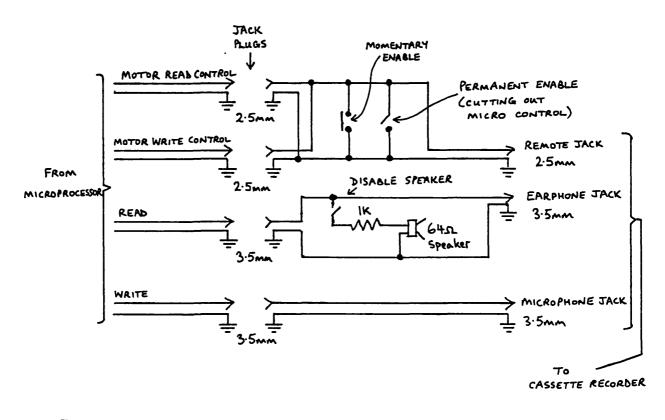

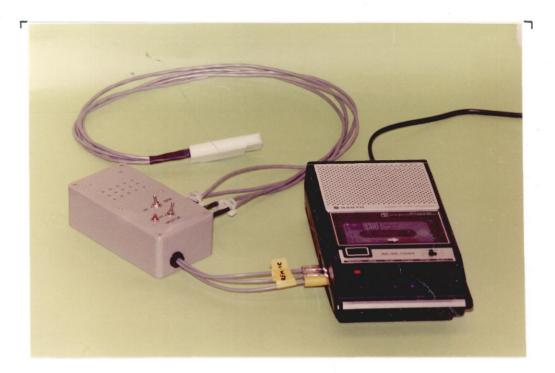

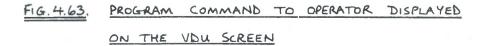

| CHAP | <u>TER 7</u> :                                                                                       | COMMUNICATION WITH A MICROPROCESSOR<br>EXECUTING A REAL TIME PROGRAM                            | 616          |

| 7.1  | Introduc                                                                                             | tion                                                                                            | 6 <b>1</b> 6 |

| 7.2  | Possible                                                                                             | Data Terminal Strategies                                                                        | 6 <b>1</b> 9 |

|      | 7.2.1                                                                                                | VDU or Similar Keyboard/Printer Unit                                                            | 619          |

|      | 7.2.2                                                                                                | Special Purpose Unifunctional Data<br>Peripherals                                               | 623          |

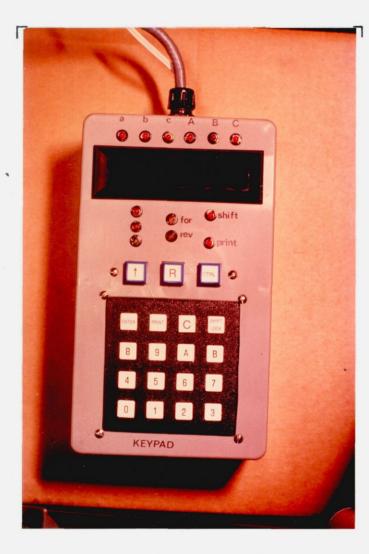

|      | 7.2.3                                                                                                | Multipurpose Keypad                                                                             | 628          |

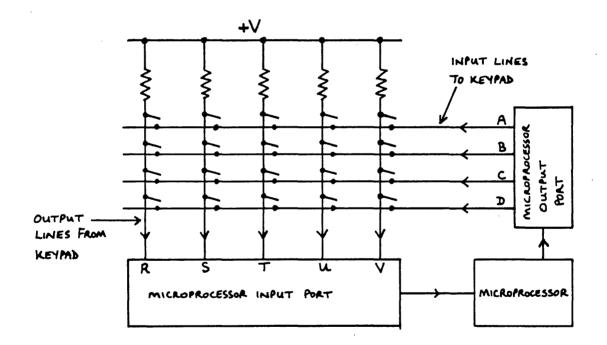

| 7.3  | Possible                                                                                             | Keypad Circuit Strategies                                                                       | 630          |

|      | 7.3.1                                                                                                | Hardwired Logic Circuitry                                                                       | 630          |

|      | 7.3.2                                                                                                | Keypad Controlled by the Main<br>System Microprocessor                                          | 631          |

|      | 7.3.3                                                                                                | Keypad Controlled by a<br>Dedicated Microprocessor                                              | 632          |

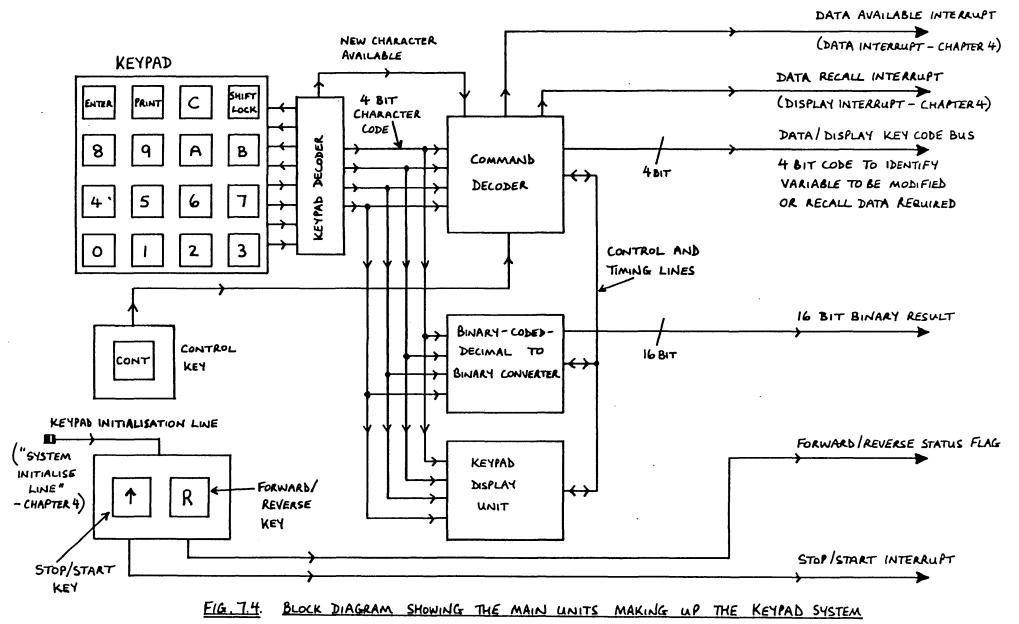

| 7.4  | The Necessary and Sufficient Functions<br>Required to Enable a Keypad to Control<br>the Motor System |                                                                                                 | 633          |

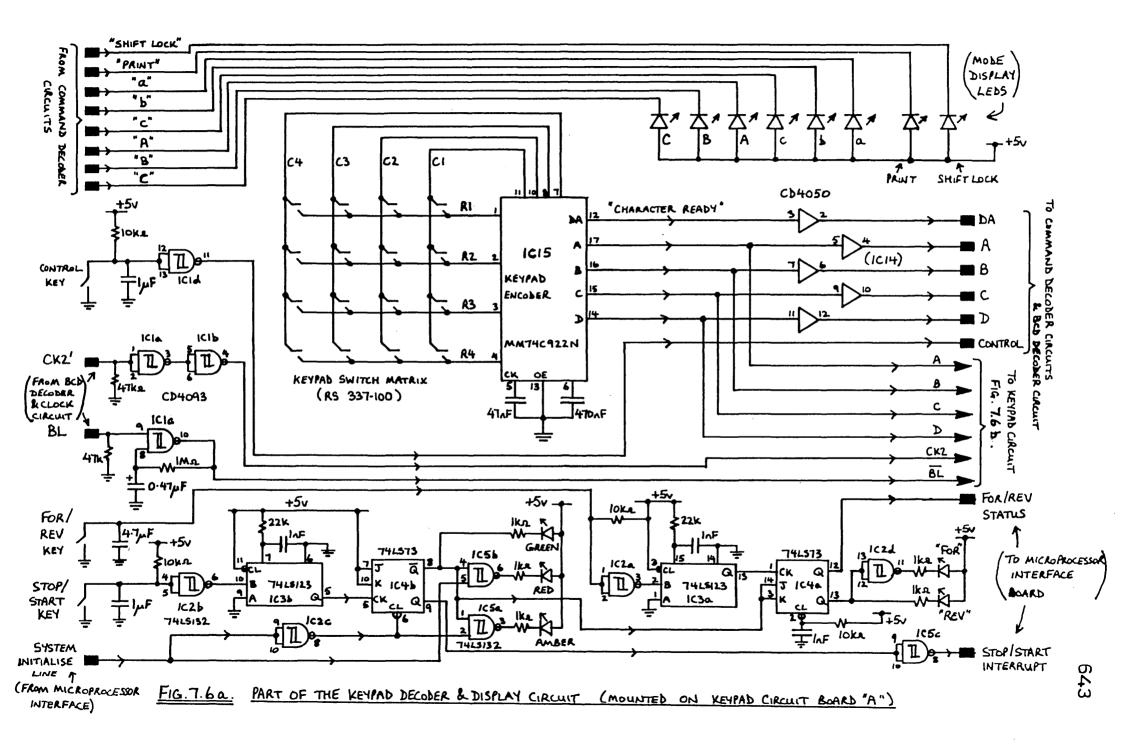

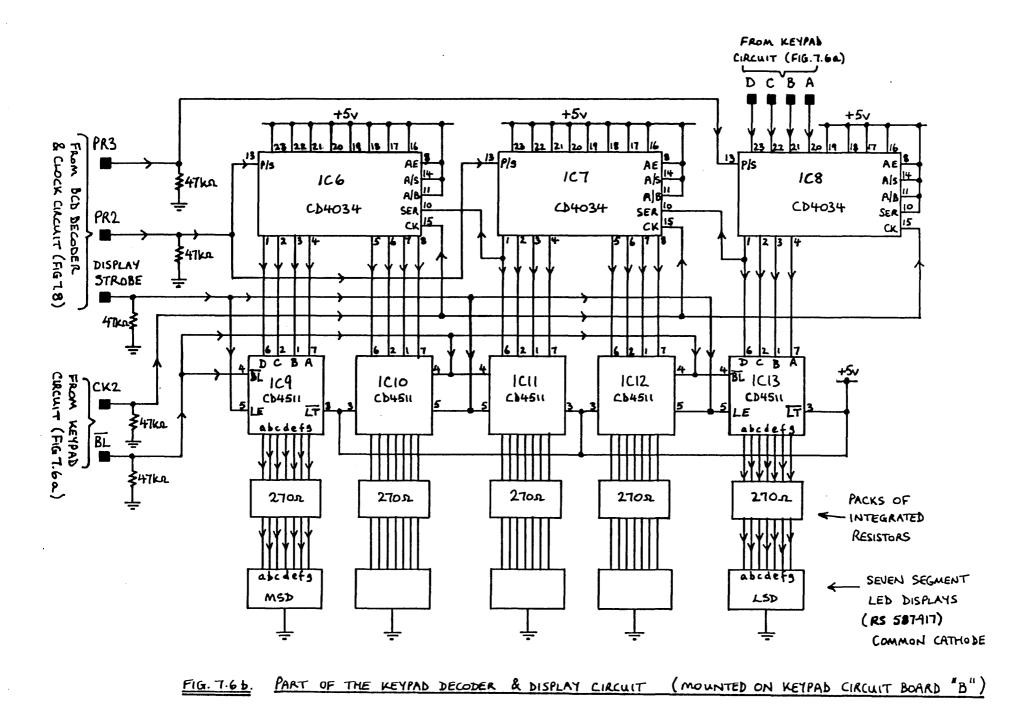

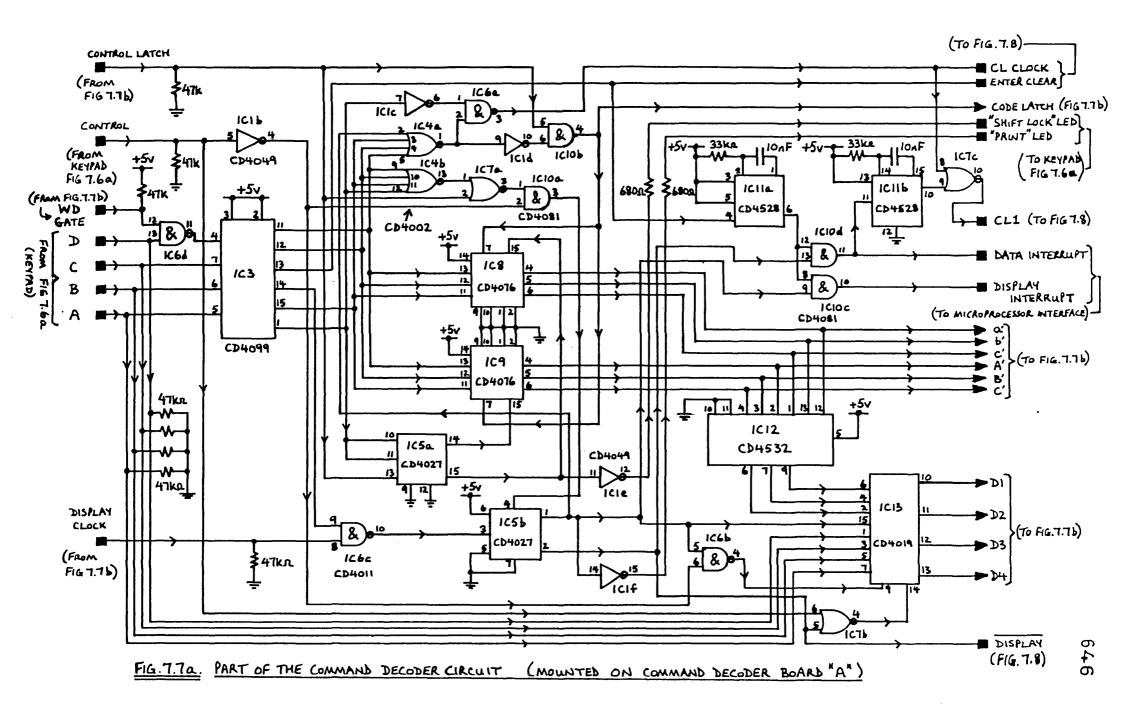

| 7.5  | Keypad C                                                                                             | ircuit Design                                                                                   | 634          |

|      | 7.5.1                                                                                                | Practical Considerations Relevant to<br>the Design and Construction of<br>the Unit              | 635          |

|      | 7.5.2                                                                                                | Choice of Components                                                                            | 635          |

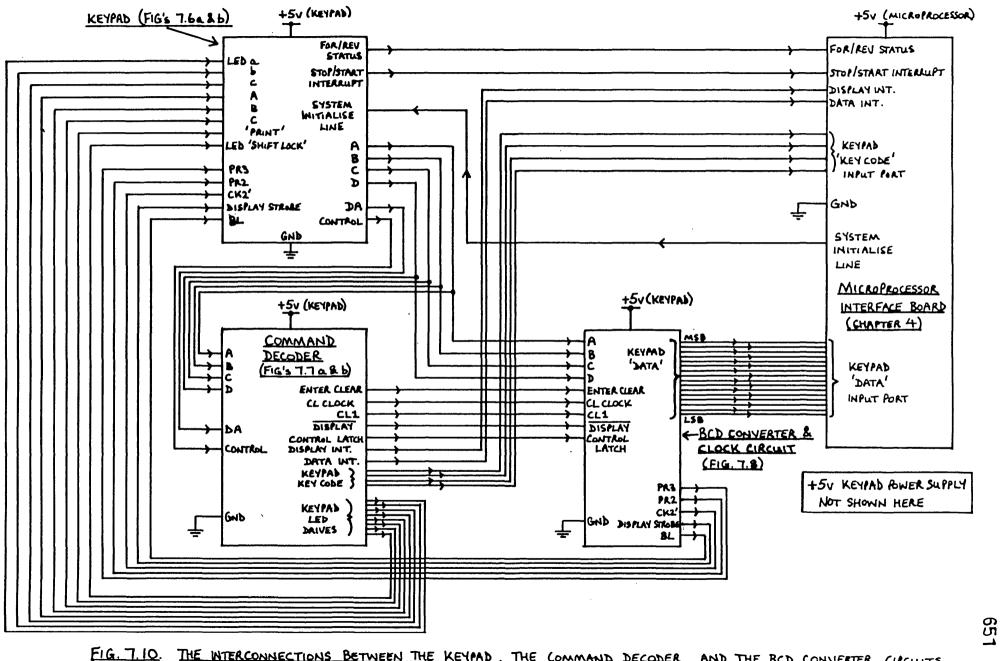

|      | 7.5.3                                                                                                | Signal Lines Required Between the Two<br>Keypad Units and the Microprocessor<br>Interface Board | 636          |

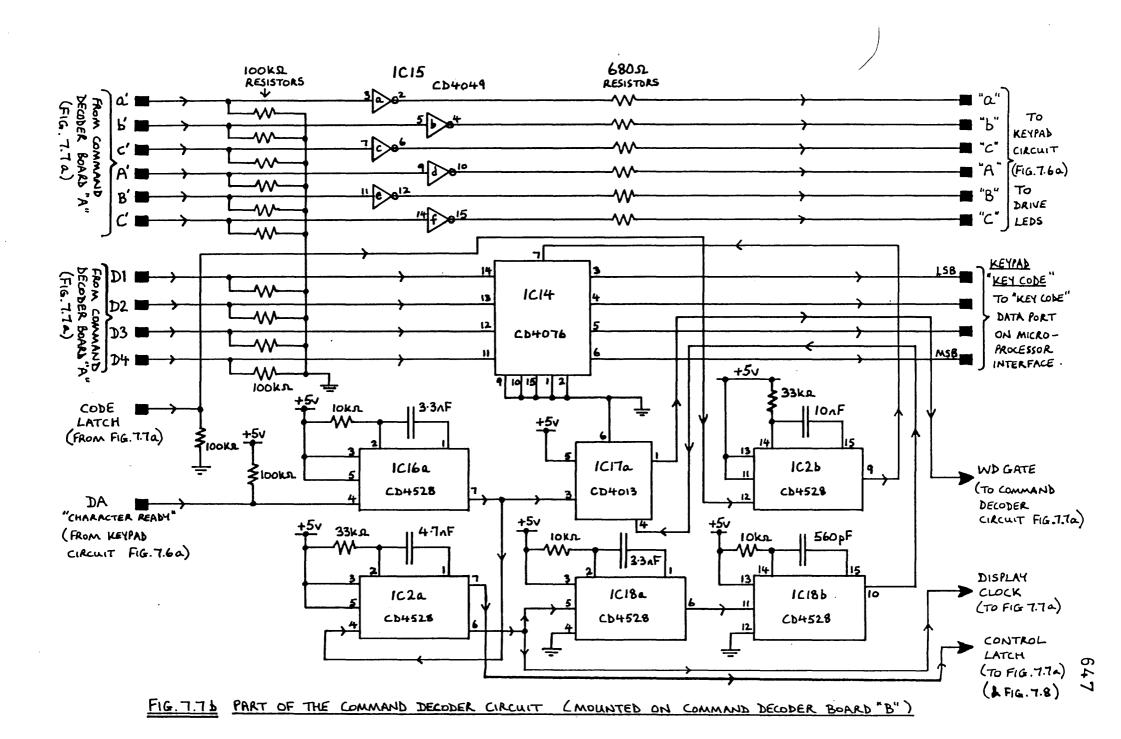

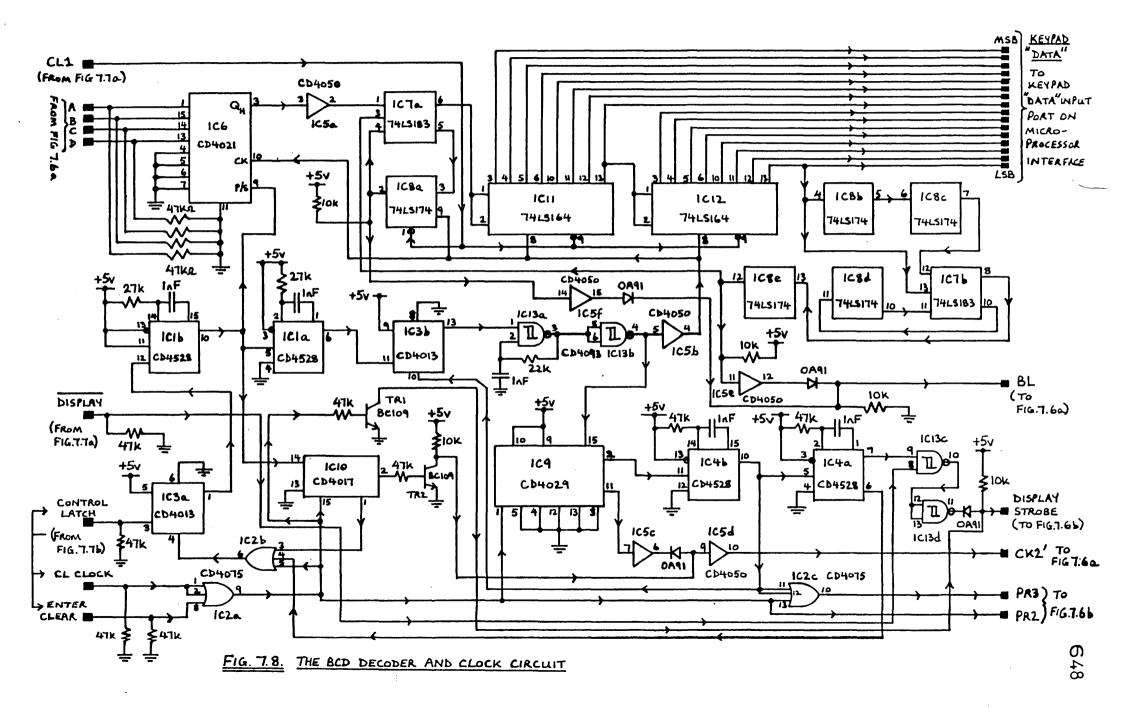

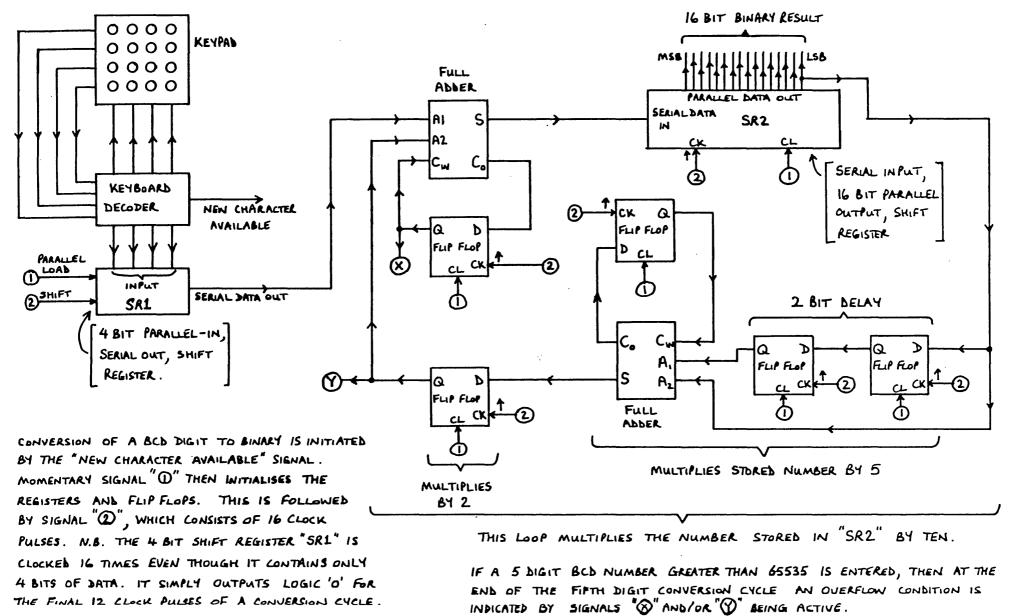

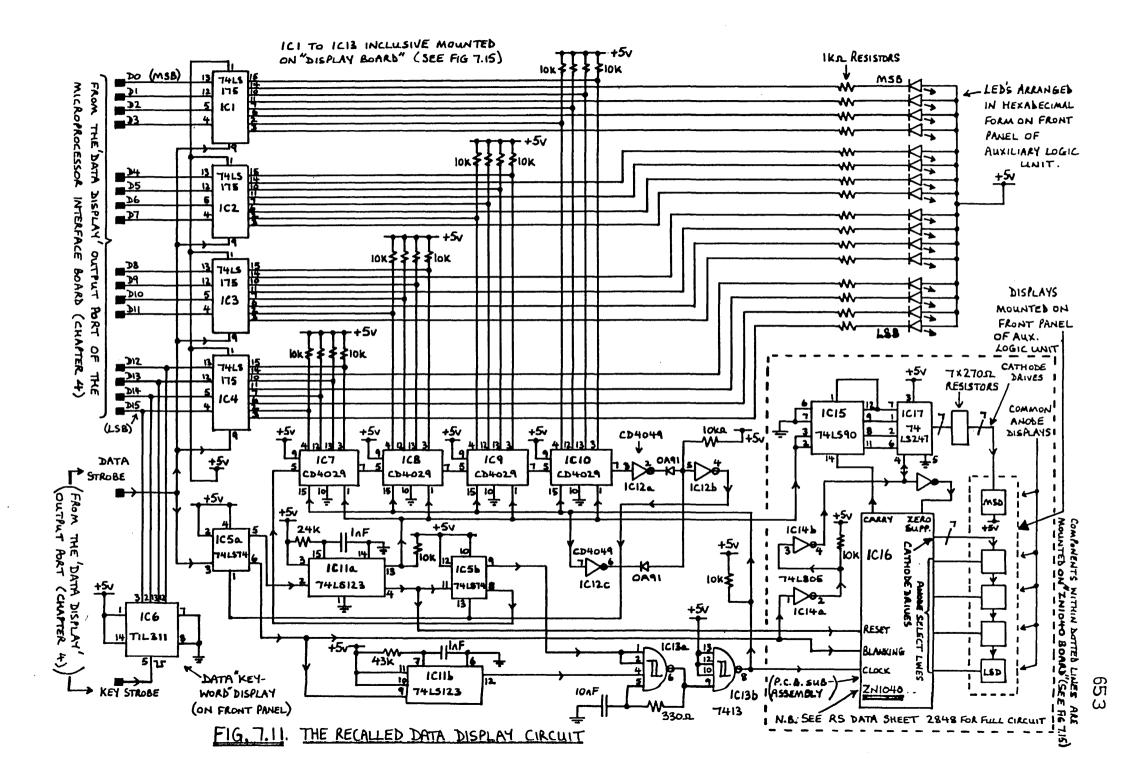

|      | 7.5.4                                                                                                | Circuit Description and Diagrams                                                                | 63 <b>7</b>  |

| 7.6  | Software                                                                                             | Required to Service the Keypad Unit                                                             | 655          |

| 7.7  | Operatio                                                                                             | nal Problems                                                                                    | 655          |

| 7.8  | Conclusi                                                                                             | ons                                                                                             | 660          |

•

-

Page

|      |                                                               |                                                                                        | raye         |

|------|---------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------|

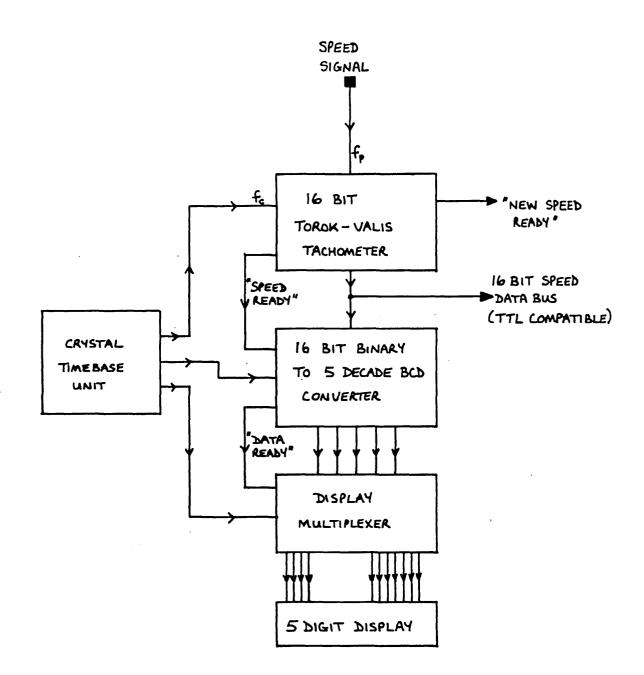

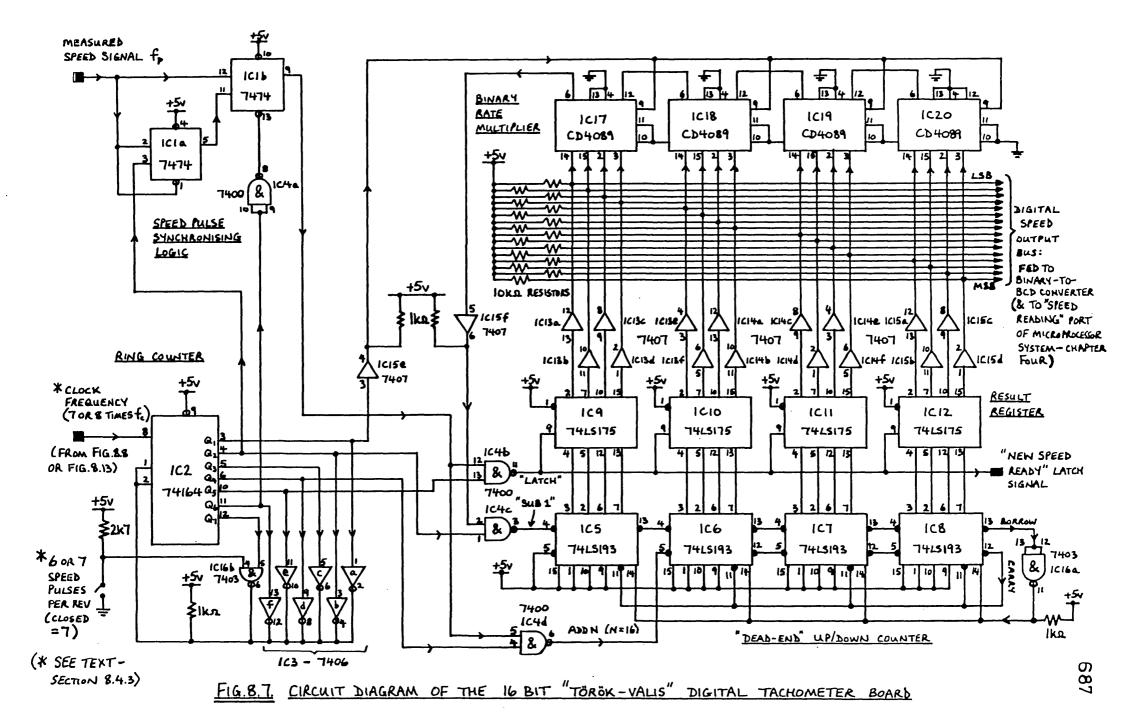

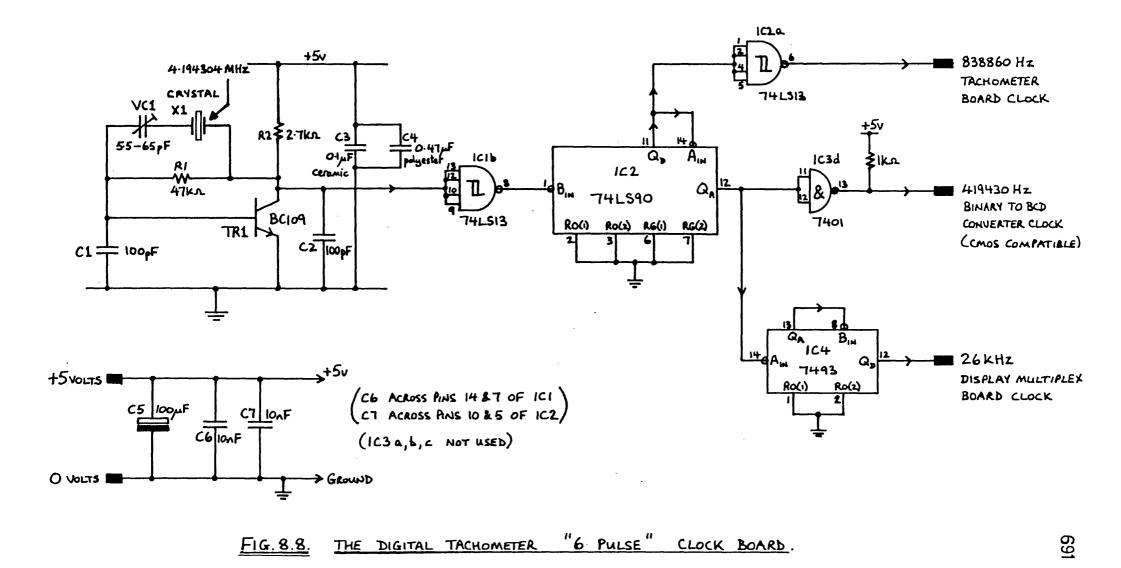

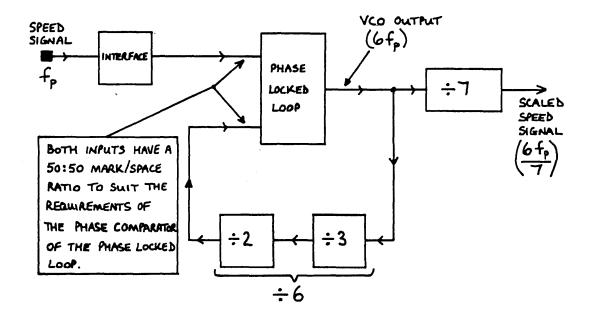

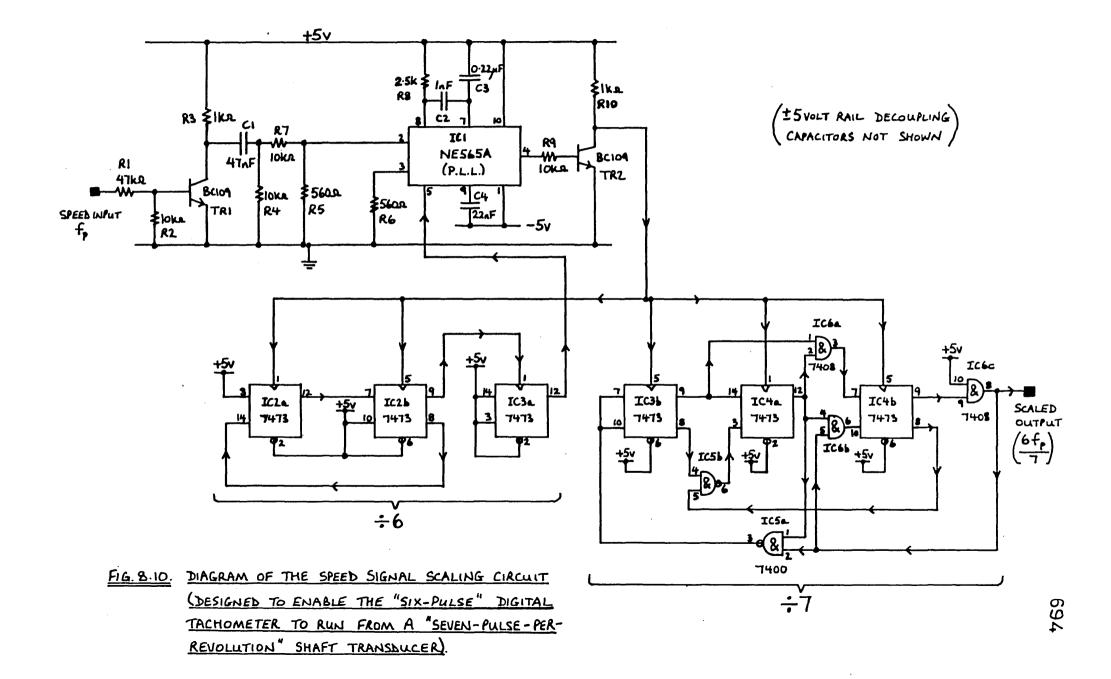

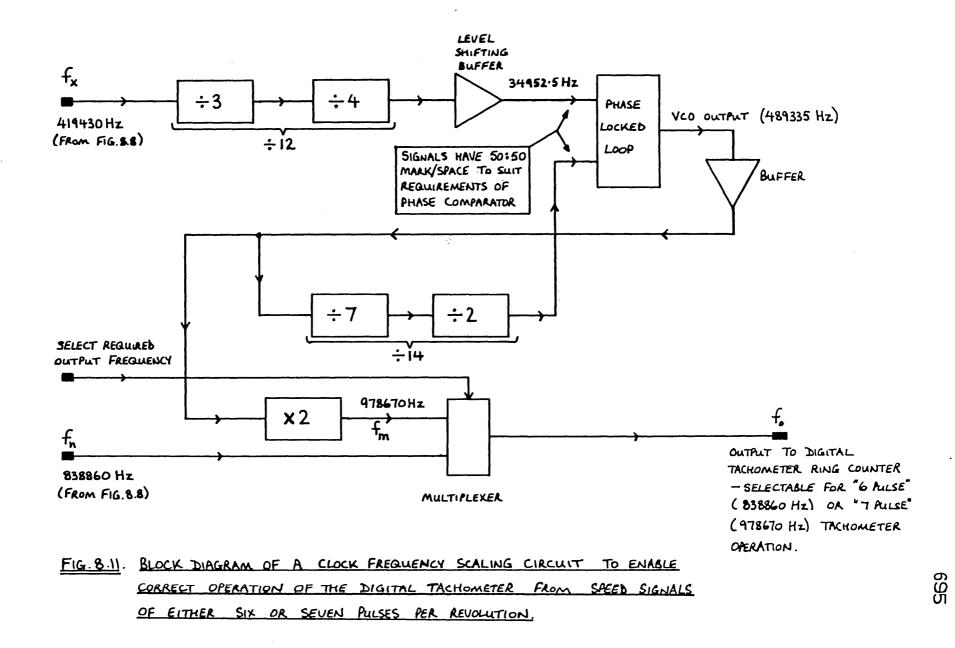

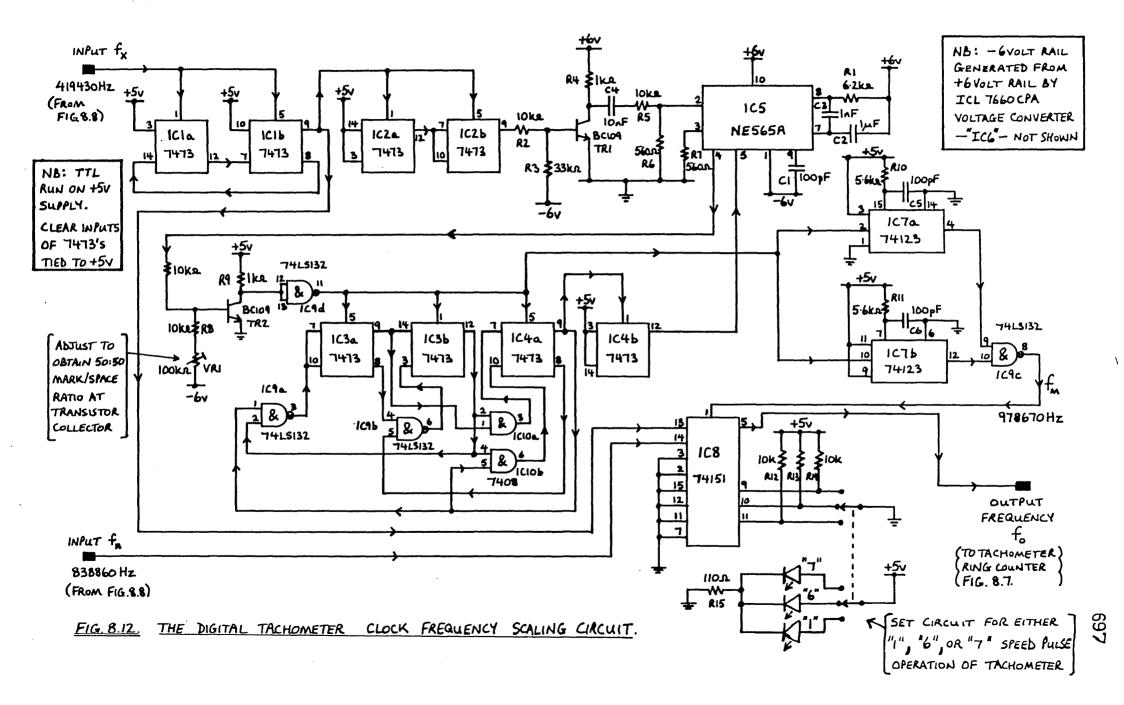

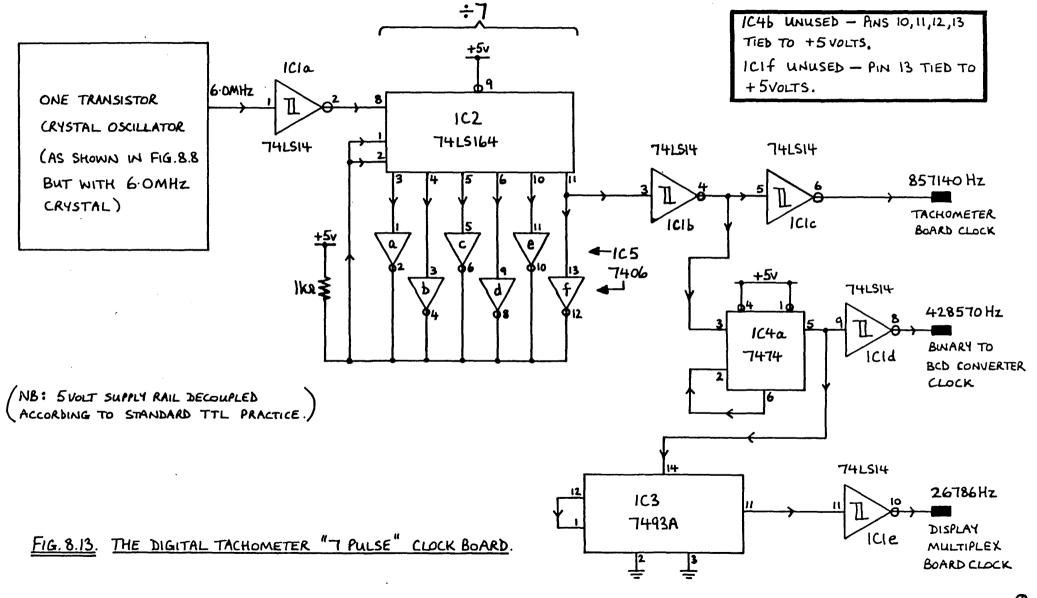

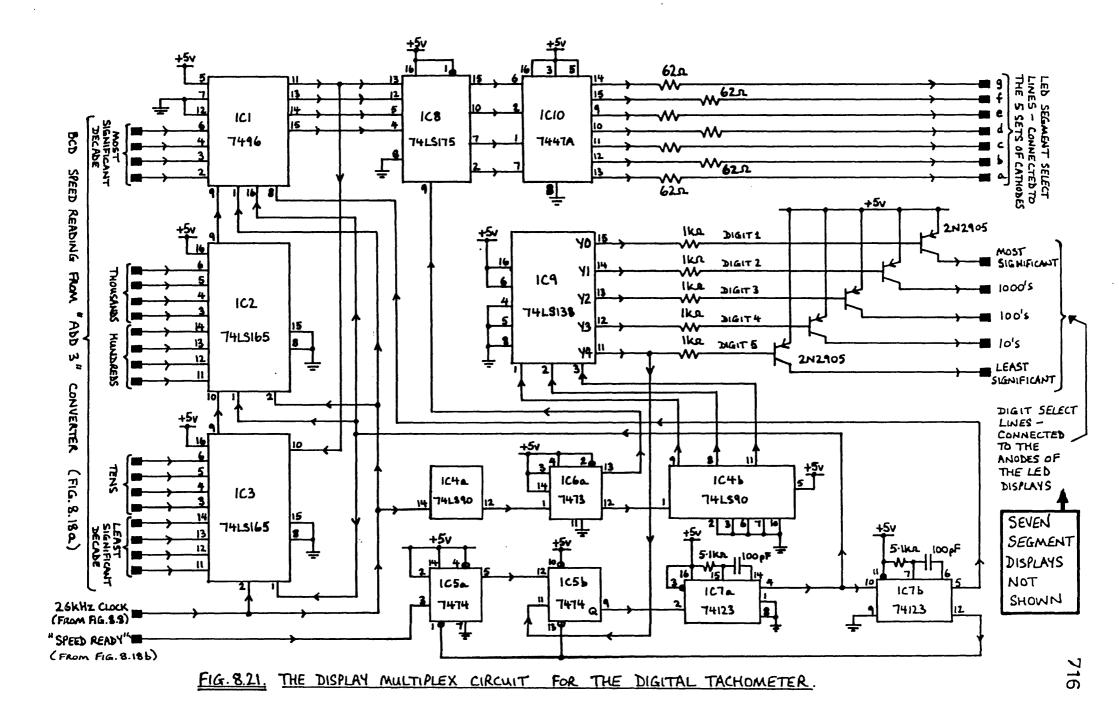

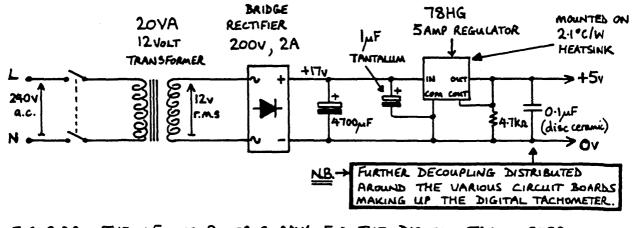

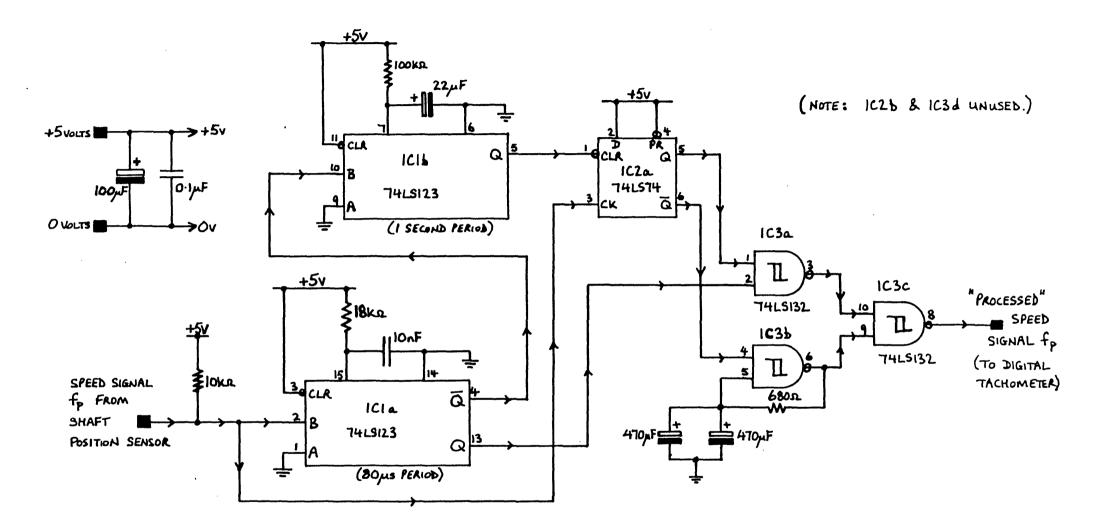

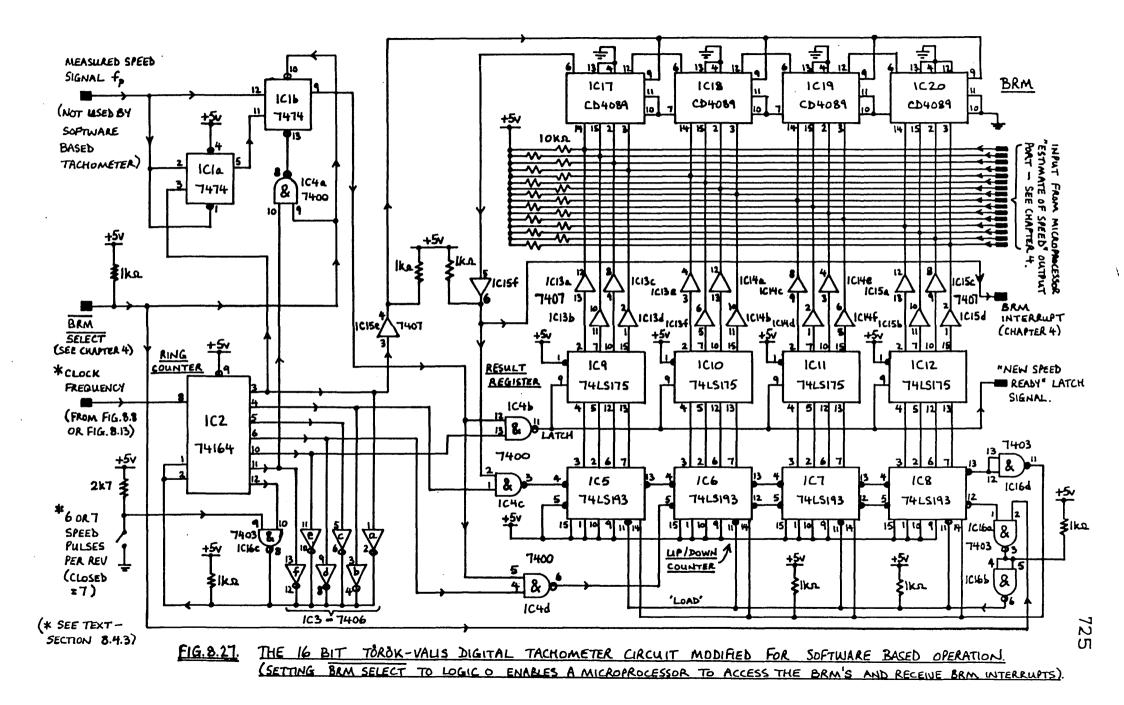

| CHAP | TER 8:                                                        | DESIGN AND DEVELOPMENT OF A HIGH<br>RESOLUTION DIGITAL TACHOMETER                      | 66 <b>1</b>  |

| 8.1  | Introduction                                                  |                                                                                        |              |

| 8.2  | Requirements for a Tachometer Used in a<br>Motor Drive System |                                                                                        |              |

| 8.3  | _                                                             |                                                                                        |              |

|      | 8.3.1                                                         | Analogue Tachometer Circuits                                                           | 663          |

|      | 8.3.1                                                         | 1 Tachogenerators                                                                      | 663          |

|      | 8.3.1                                                         | 2 Charge Pump Frequency to<br>Voltage Converters                                       | 664          |

|      | 8.3.1.                                                        | .3 Phase-Locked Loops                                                                  | 665          |

|      | 8.3.2                                                         | Digital Tachometer Circuits                                                            | 665          |

|      | 8.3.2                                                         | 1 Pulse Counting Over<br>a Fixed Timebase                                              | 666          |

|      | 8.3.2                                                         | 2 Period Timing Between<br>Two Pulses                                                  | 667          |

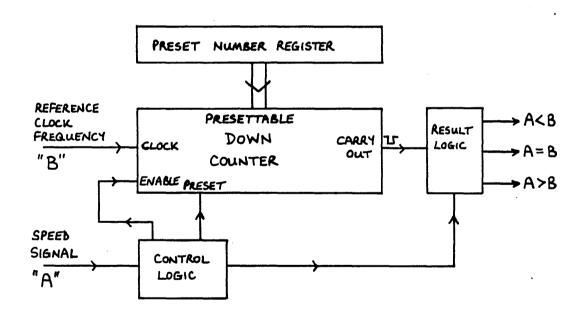

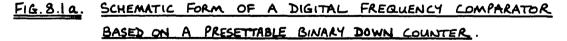

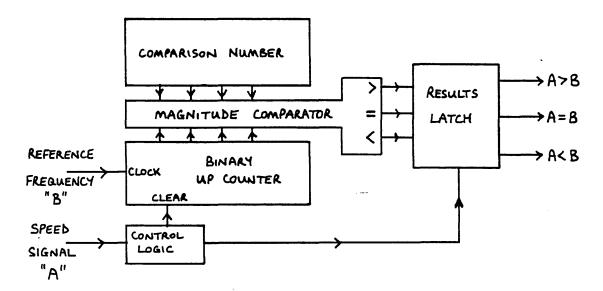

|      | 8.3.2                                                         | .3 Digital Frequency Comparators                                                       | 668          |

|      | 8.3.3                                                         | Hybrid Tachometer Circuits                                                             | 6 <b>77</b>  |

| 8.4  | The Chos                                                      | sen Tachometer System                                                                  | 677          |

|      | 8.4.1                                                         | Basic Design Decisions                                                                 | 6 <b>7</b> 8 |

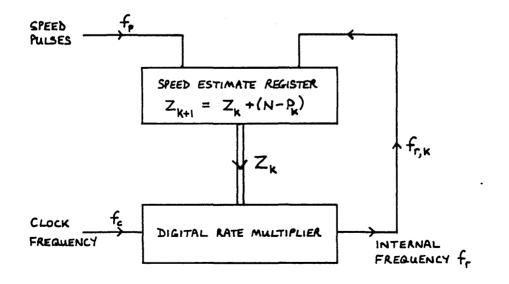

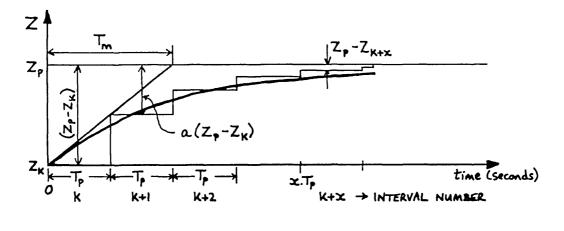

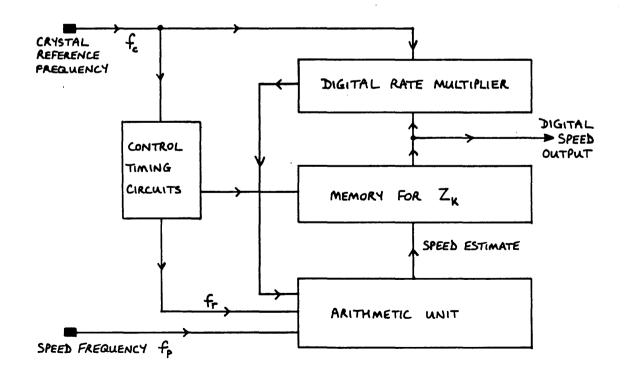

|      | 8.4.2                                                         | The Hardware Torok-Valis Tachometer<br>Circuit                                         | 686          |

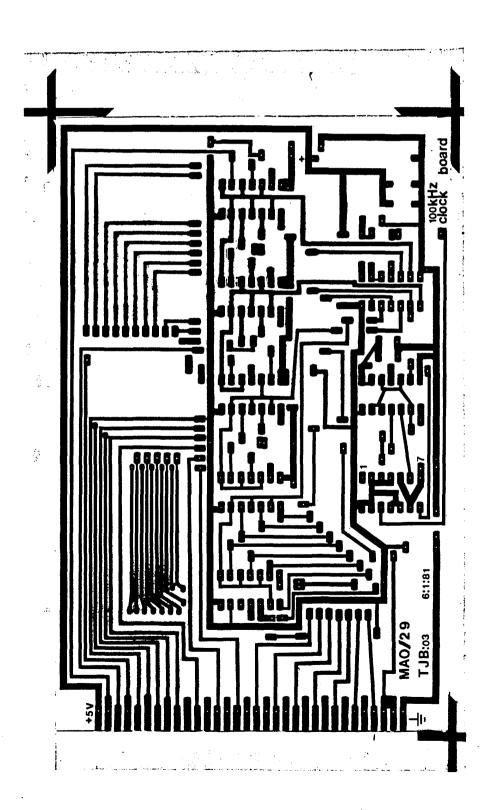

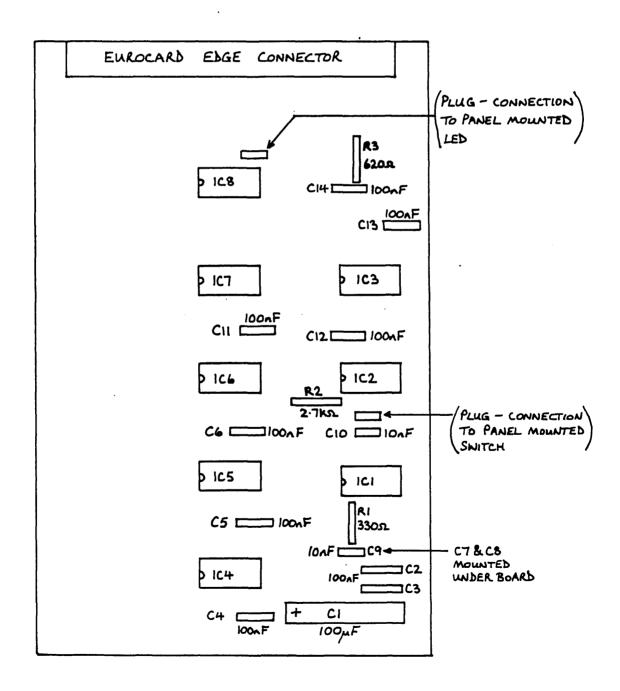

|      | 8.4.3                                                         | The Crystal-Locked Reference<br>Frequency Oscillators                                  | 689          |

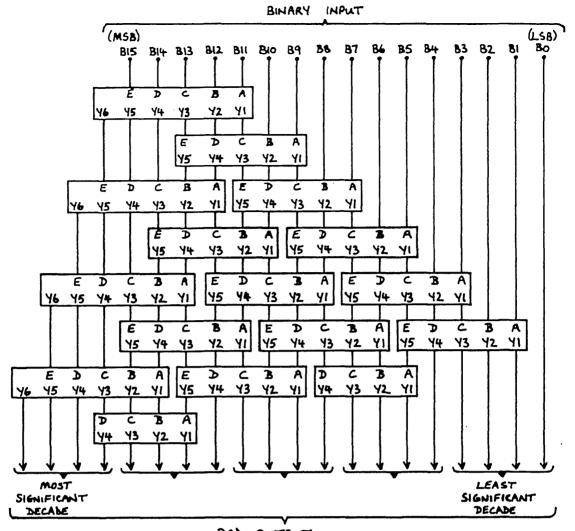

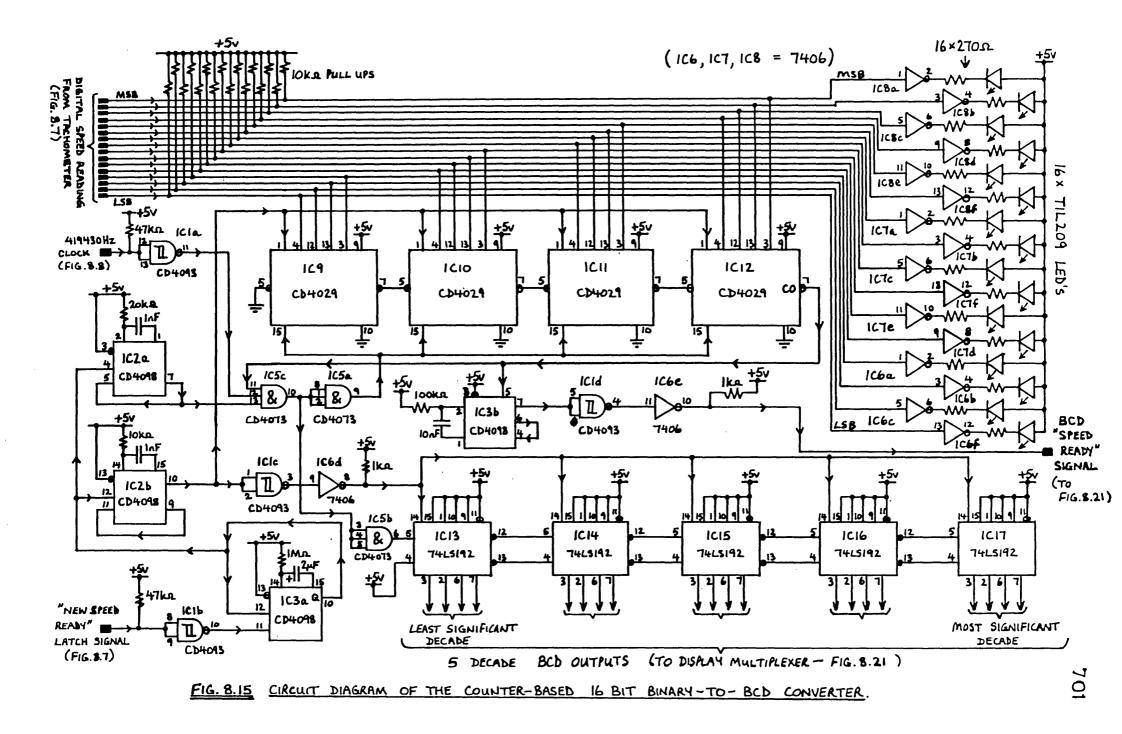

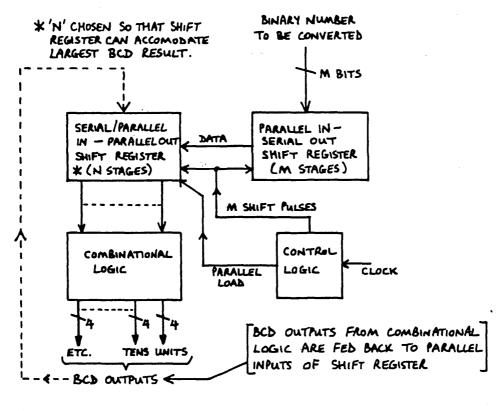

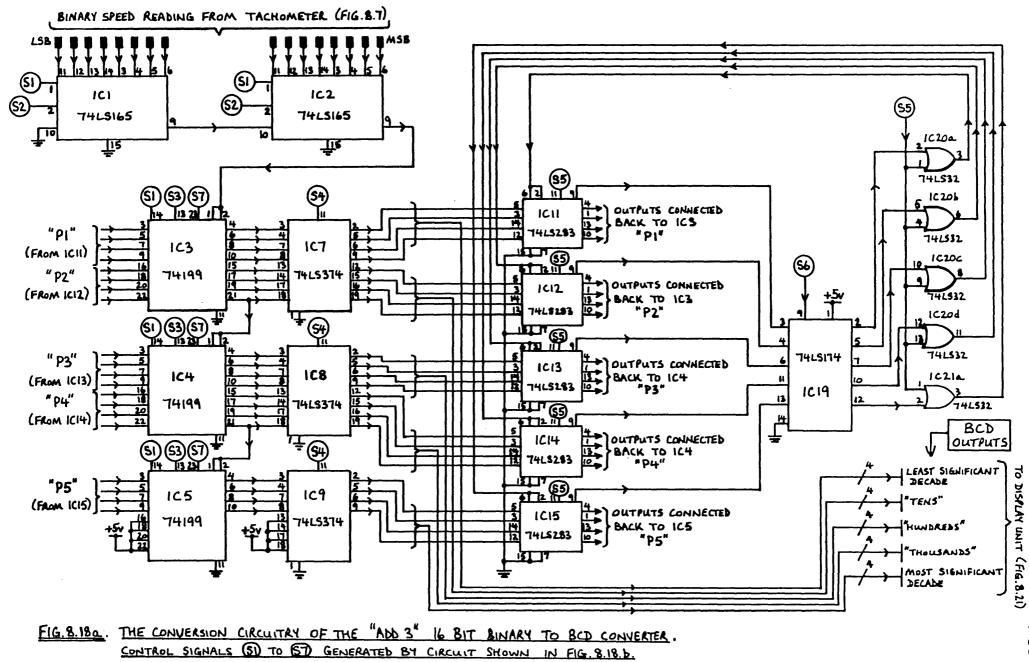

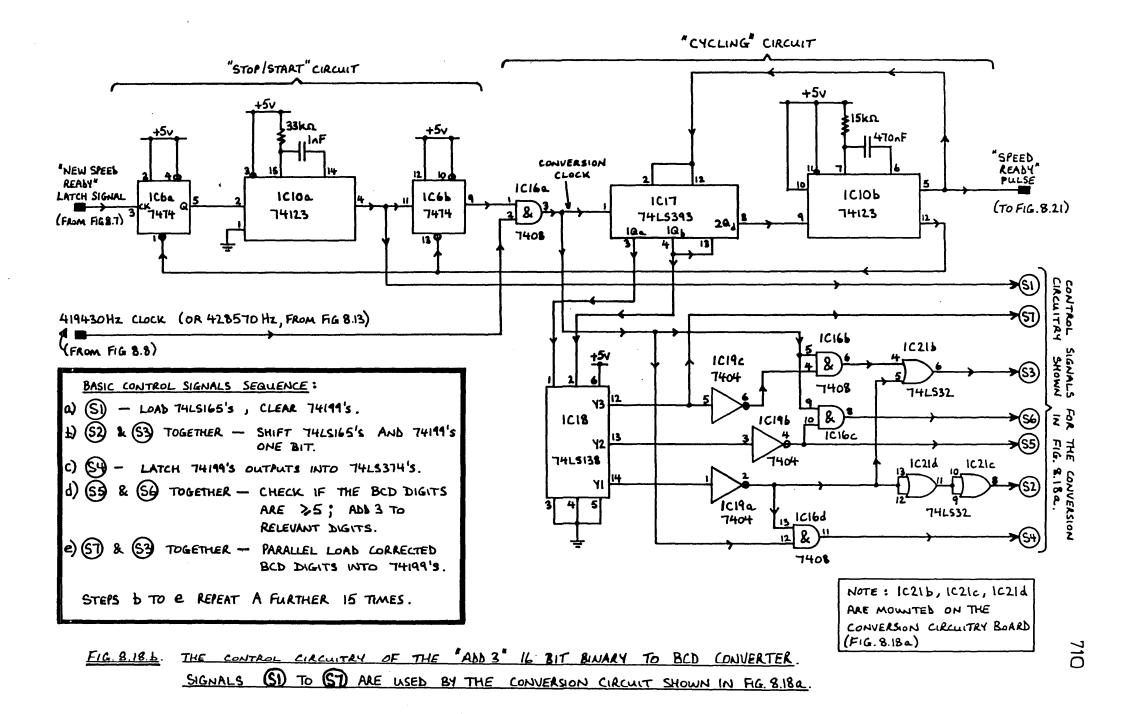

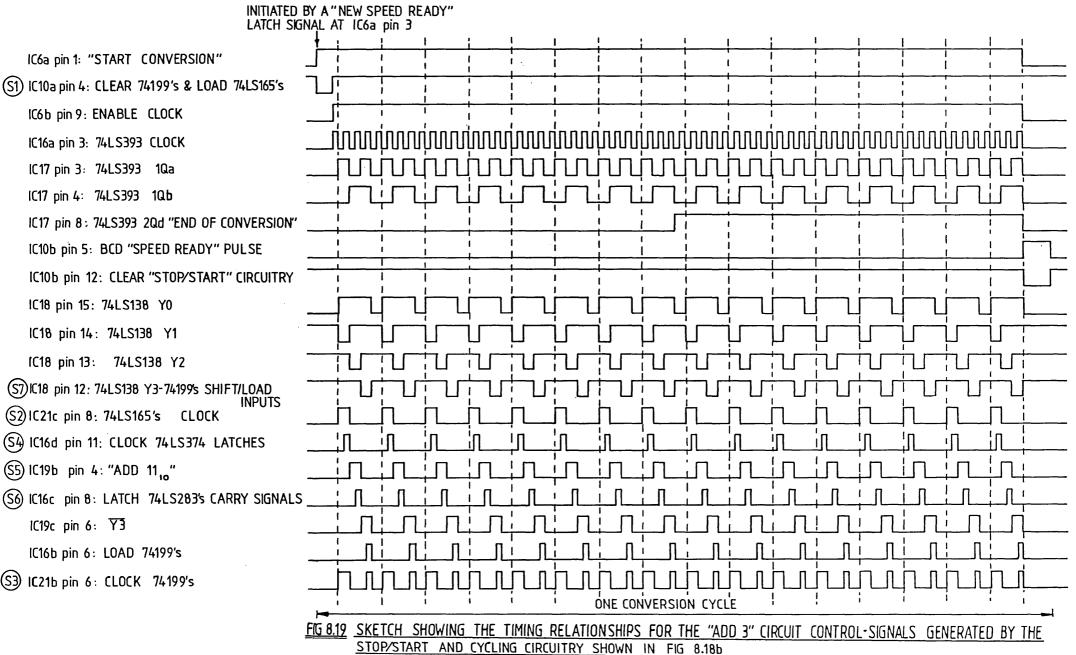

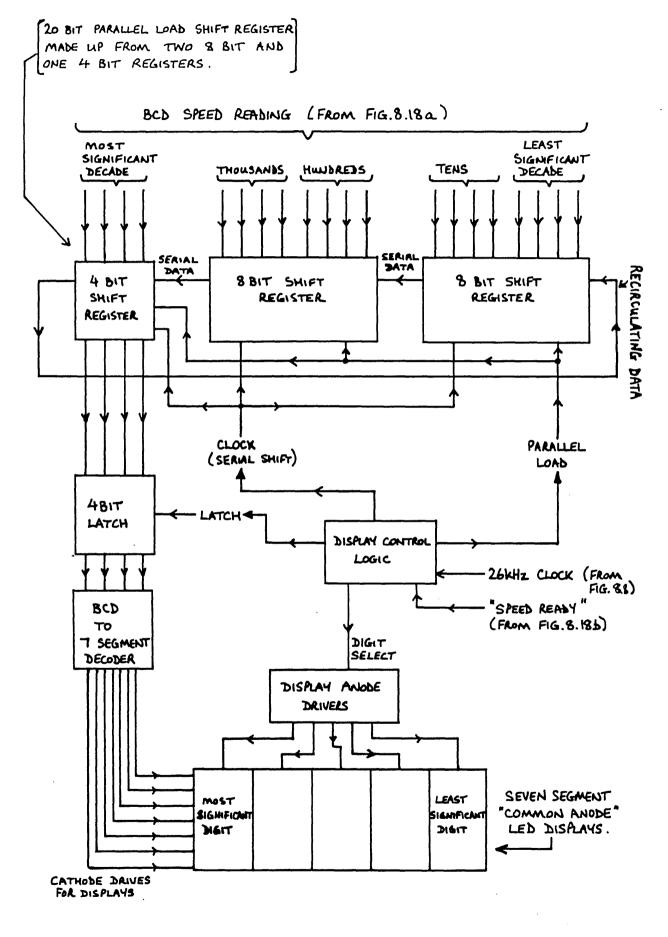

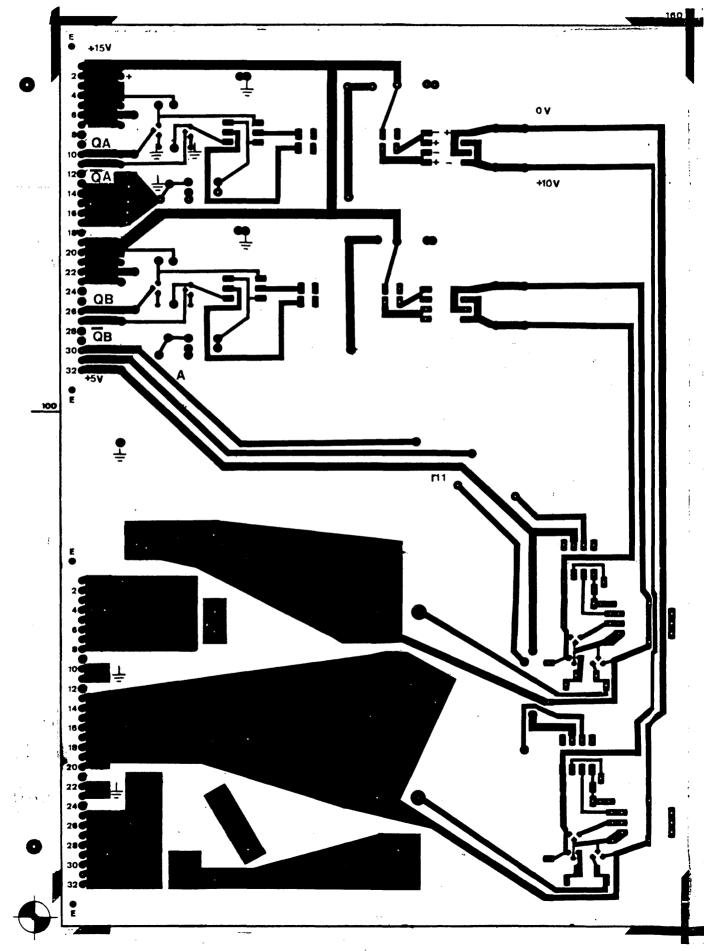

|      | 8.4.4                                                         | The Binary to BCD Converter Circuit                                                    | 699          |