# ALGORITHMS FOR THE STATISTICAL DESIGN OF ELECTRICAL CIRCUITS

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING, THE UNIVERSITY OF LONDON.

ΒY

RANDEEP SINGH SOIN

DEPARTMENT OF ELECTRICAL ENGINEERING IMPERIAL COLLEGE OF SCIENCE AND TECHNOLOGY EXHIBITION ROAD, LONDON, S.W.7.

FEBRUARY, 1980.

ABSTRACT

The research reported in this thesis is concerned with algorithms for designing for statistical variations in the performance of manufactured circuits. The variation in performance is a consequence of variations in component parameter values which in turn result from uncertainties in the process of manufacture of these components or to their dependence on environmental effects such as temperature.

The research contribution can be seen to comprise three distinct elements: (a) A review of the general field of statistical design (chapter 1) and an assessment of existing techniques and algorithms, including a clear problem formulation and classification (chapter 2). (b) A practical investigation of some of the techniques reviewed and the proposal, implementation and general investigation of new algorithms to extend the range of problems addressed (chapter 3,4 and 5) and (c) the identification of areas of further research (chapters 2 and 6).

The thesis commences with an overview of the general field of statistical design, followed by a critical review of existing algorithms and techniques addressed to some particular statistical design problems (namely tolerance assignment and design centering). The next three chapters present contributions of new algorithms and techniques. In chapter three we discuss branch and bound methods of discrete optimization, applied to the tolerance assignment and design centering problems. A geometrically based feasibility testing procedure, INDENTATION, is described and demonstrated for a particular circuit example. In chapter four iterative Monte Carlo based design centering methods are described and demonstrated for circuit examples involving up to 43 variable components. Special sampling schemes for reducing overall computational effort are discussed and compared. In chapter five, iterative Monte Carlo based tolerance assignment methods are considered. Results of a practical investigation of an existing method, TOLERATE, are presented and its shortcomings are demonstrated. A new method, PERTOL, which overcomes some of these shortcomings is proposed and demonstrated for practical circuit examples. Finally, in chapter six an assessment of existing techniques (including those reported in this thesis) is made and areas of further research identified.

.

## To my Mother and Father

٠.,

2

.

.

ਪੜ੍ਹਿ ਪੜਿ ਗਡੀ ਲਦੀ ਅਹਿ। ਪੜ੍ਹਿ ਪੜ੍ਹਿ ਭਰੀਆਰਿ ਸਾਮ। ਪੜ੍ਹਿ ਪੜਿ ਬੇੜੀ ਪਾਈਐ।ਪੜ੍ਹਿ ਪੜ੍ਹਿ ਗਡੀ ਅਹਿ ਖਾਤ। ਪੜੀ ਅਹਿ ਜੇਤੇ ਬਰਸ ਬਰਸ। ਪੜੀ ਆਹਿ ਜੇਤੇ ਸਾਸ। ਪੜੀ ਆਹਿ ਜੇਤੇ ਆਰਜਾ। ਪੜਿਆਹਿ ਜੇਤੇ ਸਾਸ। ਨਾਨਕ ਲੇਬੋ ਇਕ ਗਲ। ਹੋਰੁ ਹਉਂ ਸੇ ਬਖਣਾ ਬਾਖਾ।

> A man may load carts with books; he may load men with books to take with him;

Books may be put on boats; pits may be filled with them.

A man may read books for months; he may read them for years;

He may read them for life; he may read them while he hath breath -

Nanak, only one word, God's name, would be of account; all else would be the senseless discussion of pride.

Guru Nanak

#### ACKNOWLEDGEMENTS

I am greatly priviledged to have had Dr Robert Spence as my supervisor. I wish to take this opportunity of expressing deep gratitude for his guidance and encouragement throughout the course of my research work.

I also wish to express a special thanks to my friend and colleague Dr Kirpal Tahim for much valued criticism and encouragement.

I am grateful to Mr Robert Tung, Dr David Agnew, Mr Paul Rankin, Mr Kenneth Moulding, and to numerous colleagues and friends in the communications section for many stimulating discussions.

I am also very grateful to Mr Hugh Koanantakool for assistance in the preparation of this thesis.

A very special thanks is due to my beloved sister, Bholan Dhot, for persevering with the typing of this thesis over its protracted period of preparation.

The research reported in this thesis was carried out while I was the recipient of a research studentship of the U.K. Science Research Council and later of a bursary sponsored by the Submarine Systems Division of the Standard Telephone and Cables Company. The financial assistance of both organisations is gratefully acknowledged.

## CONTENTS

| TITLE | PAGE.   |                                                                 | 1  |

|-------|---------|-----------------------------------------------------------------|----|

| ABSTR | ACT.    |                                                                 | 2  |

| ACKNO | WLEDGEN | MENTS.                                                          | 3  |

| CONTE | NTS.    |                                                                 | 4  |

| LIST  | OF FIGU | JRES.                                                           | 9  |

| LIST  | OF TABI | LES.                                                            | 15 |

| STATE | MENT OF | F ORIGINALITY.                                                  | 17 |

| СНАРТ | 'ER 1 - | STATISTICAL CIRCUIT DESIGN - THE SCENARIO.                      | 19 |

| 1.1   | Introdu | action.                                                         | 20 |

| 1.2   | Notatio | on and terminology.                                             | 24 |

| 1.3   | Statist | tical analysis.                                                 | 27 |

|       | 1.3.1   | Monte Carlo analysis.                                           | 29 |

|       | 1.3.2   | The method of moments.                                          | 32 |

| 1.4   | Paramet | ter value distributions.                                        | 37 |

|       | 1.4.1   | Discrete components.                                            | 37 |

|       | 1.4.2   | Integrated circuits components.                                 | 39 |

| 1.5   | Statist | tical circuit design - some scenarios.                          | 40 |

|       | 1.5.1   | Tolerance assignment and design centering.                      | 41 |

|       | 1.5.2   | Choice of performance specifications.                           | 43 |

|       |         | (a) Specification sensitivity.                                  | 43 |

|       |         | (b) System specification.                                       | 44 |

|       | 1.5.3   | Specification of manufacturing tests.                           | 46 |

|       |         | (a) Go-no go testing.                                           | 46 |

|       |         | (b) Accounting for environmental effects<br>in factory testing. | 47 |

|       |         | (c) Selection of testing accuracy.                              | 47 |

| 1.6   | Summary |                                                                 | 48 |

4

PAGE

|      | · · ·                                                                                       | PAGE |

|------|---------------------------------------------------------------------------------------------|------|

| СНАР | TER 2 - ALGORITHMS FOR TOLERANCE ASSIGNMENT<br>AND DESIGN CENTERING - A CRITICAL<br>REVIEW. | 60   |

| 2.1  | Introduction.                                                                               | 61   |

| 2.2  | Cost models.                                                                                | 63   |

|      | 2.2.1 Component cost functions.                                                             | 63   |

|      | 2.2.2 The unit cost function.                                                               | 64   |

| 2.3  | Problem formulations.                                                                       | 66   |

|      | 2.3.1 Problem Pl: Composite tolerance assignment<br>and design centering.                   | 66   |

|      | 2.3.2 Problem P2: Worst case tolerance assignment and design centering.                     | 67   |

|      | 2.3.3 Problem P3: Worst case tolerance assignment.                                          | 68   |

|      | 2.3.4 Problem P4: Statistical tolerance assignment and design centering.                    | 68   |

|      | 2.3.5 Problem P5: Statistical tolerance assignment.                                         | 69   |

|      | 2.3.6 Problem P6: Design centering (Yield maximization).                                    | 69   |

|      | 2.3.7 Problem P7: Tolerance assignment, design centering, and tuning.                       | 69   |

| 2.4  | The review.                                                                                 | 71   |

|      | 2.4.1 Methods based on geometrical characterization.                                        | 71   |

|      | 2.4.2 Methods based on non-linear programming.                                              | 73   |

|      | (a) Worst case formulation.                                                                 | 74   |

|      | (b) Statistical formulation.                                                                | 76   |

|      | 2.4.3 Methods based on Monte Carlo analysis.                                                | 79   |

|      | 2.4.4 Discrete methods.                                                                     | 81   |

| 2.5  | Summary and conclusions.                                                                    | 82   |

ź

| CHAP | TER 3 - DISCRETE OPTIMIZATION METHODS FOR WORST<br>CASE TOLERANCE ASSIGNMENT AND DESIGN<br>CENTERING. | 101         |

|------|-------------------------------------------------------------------------------------------------------|-------------|

| 3.1  | Introduction.                                                                                         | 102         |

| 3.2  | Notation.                                                                                             | 103         |

| 3.3  | Branch and bound methods.                                                                             | 105         |

|      | 3.3.1 General structure.                                                                              | 106         |

|      | 3.3.2 Procedures for selecting tolerance solutions for feasibility testing.                           | 107         |

|      | 3.3.3 Considerations for eliminating non-<br>feasible and non-optimal solutions.                      | 109         |

|      | 3.3.4 Feasibility testing procedure.                                                                  | 111         |

|      | (a) Monte Carlo analysis.                                                                             | 111         |

|      | (b) Vertex analysis.                                                                                  | 113         |

|      | (c) Pairwise constraints.                                                                             | 114         |

|      | (d) Indentation.                                                                                      | <b>1</b> 16 |

| 3.4  | Circuit example and results.                                                                          | 120         |

| 3.5  | Summary.                                                                                              | 122         |

| СНАР | TER 4 - ITERATIVE MONTE CARLO BASED METHODS FOR<br>DESIGN CENTERING.                                  | 137         |

| 4.1  | Introduction.                                                                                         | 138         |

| 4.2  | Problem formulation and geometrical interpretation.                                                   | 139         |

| 4.3  | Optimization methods for yield maximization -<br>some general comments.                               | 142         |

| 4.4  | Direct search methods.                                                                                | 144         |

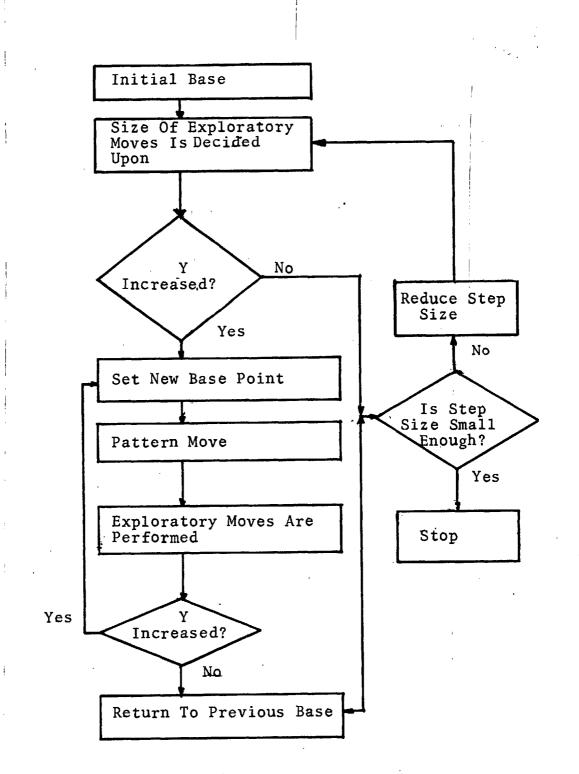

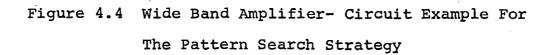

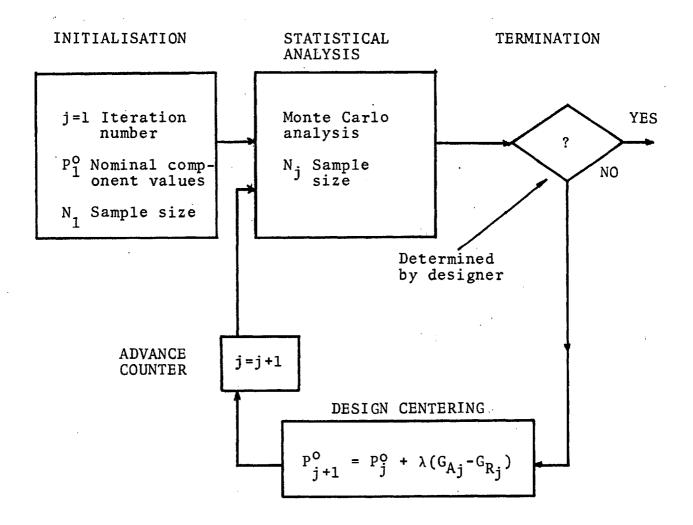

|      | 4.4.1 The pattern search method.                                                                      | 145         |

|      | 4.4.2 The statistical exploration method.                                                             | 148         |

|      | (a) Choice of search direction.                                                                       | 149         |

|      | (b) Choice of step size.                                                                              | 150         |

|      | (c) Choice of sample size.                                                                            | 154         |

|      | (d) The correlated sampling scheme.                                                                   | 156         |

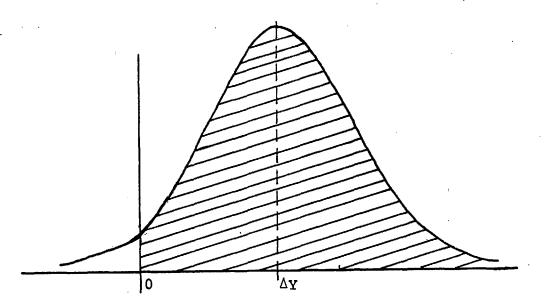

|      | (e) The common points scheme                                                                          | 160         |

•

6

PAGE

PAGE (f) Some algorithms. 168 (i) Algorithm 4.1 - correlated sampling 169 scheme. (ii) Algorithm 4.2 - common points scheme. 170 (g) Circuit examples and results. 172 (i) Passive high pass filter. 172 (ii) A high frequency amplifier. 178 (iii) A transversal filter. 179 4.5 Summary and conclusions. 181 CHAPTER 5 - ITERATIVE MONTE CARLO BASED METHODS FOR 224 TOLERANCE ASSIGNMENT Introduction. 5.1 225 5.2 Problem Formulation. 226 5.3 The TOLERATE method. 229 5.3.1 An Overview. 229 5.3.2 The tolerance assignment criterion. 231 (a) Implications on yield. 231 (b) Some practical considerations. 235 Yield sensitivity. 5.3.3 237 Summary. 5.3.4 240 The PERTOL method. 5.4 241 5.4.1 The PERTOL criterion 242 The practical algorithm. (a) 242 Implications on yield. (b) 244 5.4.2. Results. 247 5.5 Summary and conclusions. 248

| СНАРТ | 'ER 6 -                             | SUMMARY AND SUGGESTIONS FOR FURTHER RESEARCH                                                                  | 289 |  |  |

|-------|-------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|--|--|

| 6.1   | Introdu                             | action.                                                                                                       | 290 |  |  |

| 6.2   | Summary                             | of the thesis and conclusions.                                                                                | 290 |  |  |

| 6.3   | 3 Suggestions for further research. |                                                                                                               |     |  |  |

|       | 6.3.1                               | Extensions to techniques developed in the thesis                                                              | 299 |  |  |

|       | 6.3.2                               | Extension of the Monte Carlo based design<br>approach to other problems in the field<br>of statistical design | 306 |  |  |

References

8

PAGE

## LIST OF FIGURES

I

| Fig. | 1.1  | A general circuit representation.                                                                                                | 50 |

|------|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. | 1.2  | An illustration of some notation.                                                                                                | 51 |

| Fig. | 1.3  | Monte Carlo analysis - a general<br>flow chart.                                                                                  | 52 |

| Fig. | 1.4  | Typical set of Monte Carlo samples<br>(points) generated by a pseudo-<br>random process.                                         | 53 |

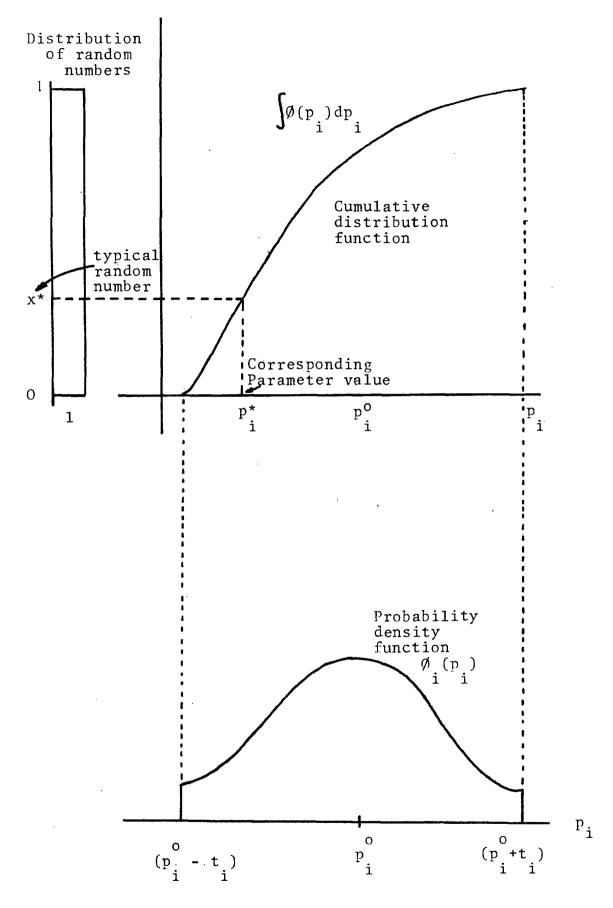

| Fig. | 1.5  | Illustrating a method for generating<br>component parameter values from<br>random numbers distributed in the<br>interval 0 to 1. | 54 |

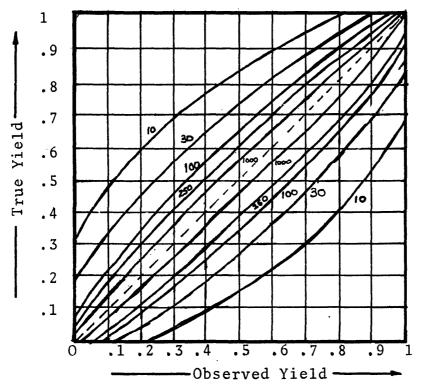

| Fig. | 1.6  | The relationship between the number<br>of samples and the accuracy of the<br>yield estimate, in Monte Carlo<br>analysis.         | 55 |

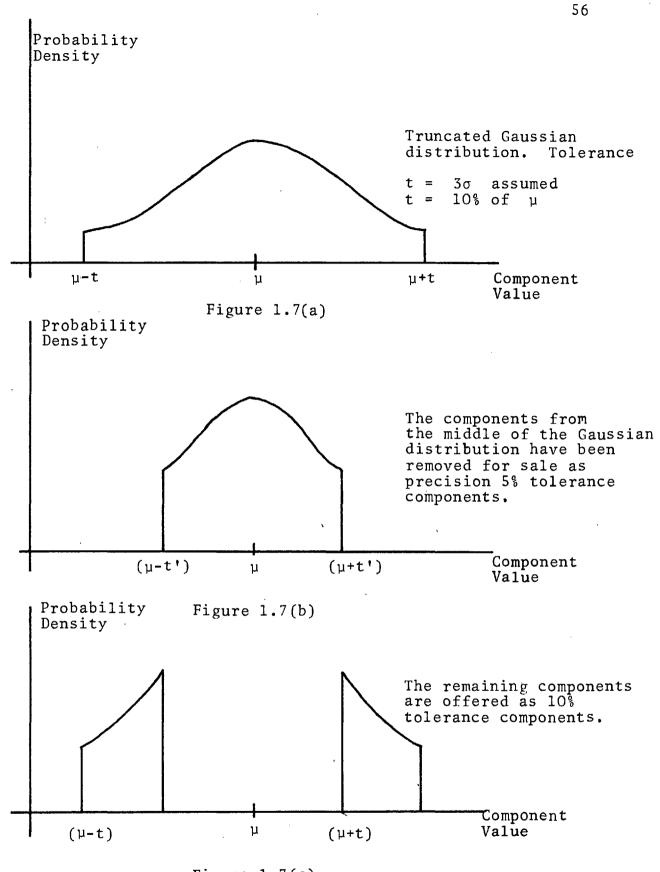

| Fig. | 1.7  | Typical probability density functions encountered with discrete components.                                                      | 56 |

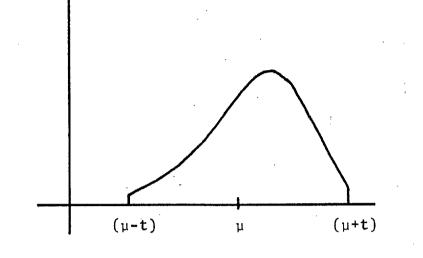

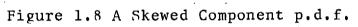

| Fig. | 1.8  | A skewed component p.d.f.                                                                                                        | 57 |

| Fig. | 1.9  | Illustration of the terms-design center and tolerance.                                                                           | 57 |

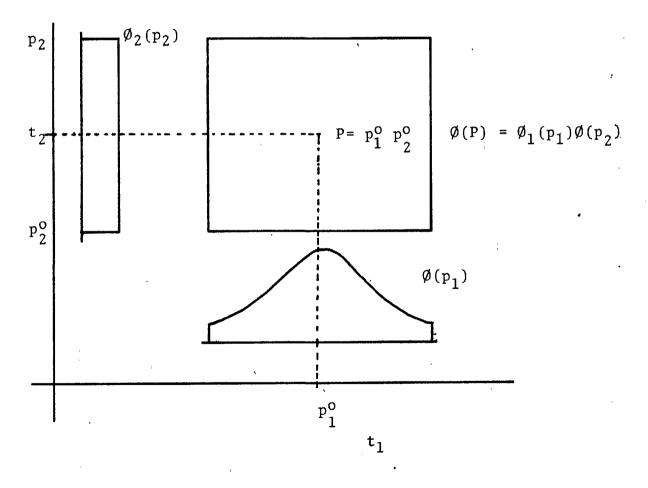

| Fig. | 1.10 | Geometrical interpretation of design centering and tolerance assignment.                                                         | 58 |

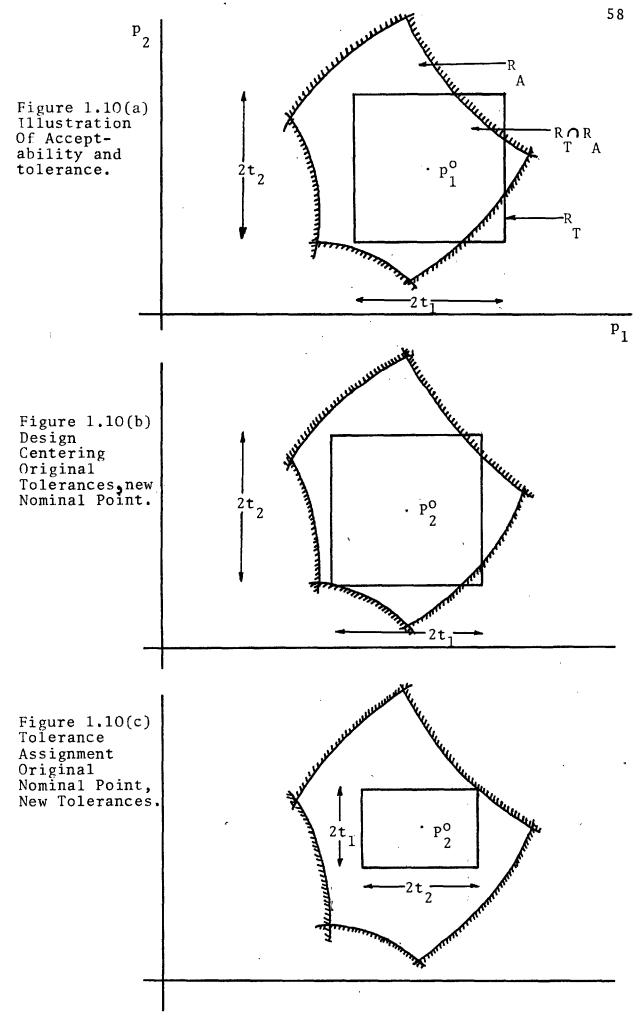

| Fig. | 1.11 | Illustrating the application of<br>statistical design to the problem<br>of selecting testing accuracy.                           | 59 |

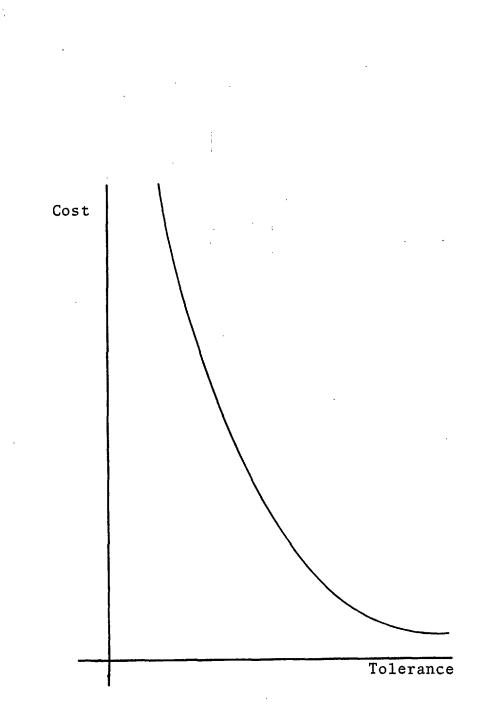

| Fig. | 2.1  | A typical cost-versus-tolerance relationship.                                                                                    | 87 |

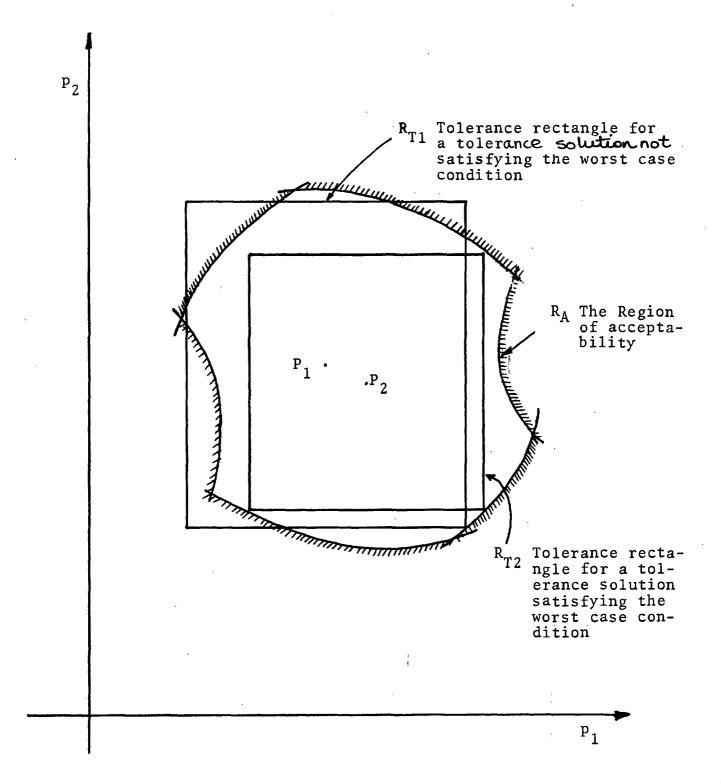

| Fig. |      | Geometrical illustration of the worst<br>case tolerance assignment and design<br>centering problem.                              | 88 |

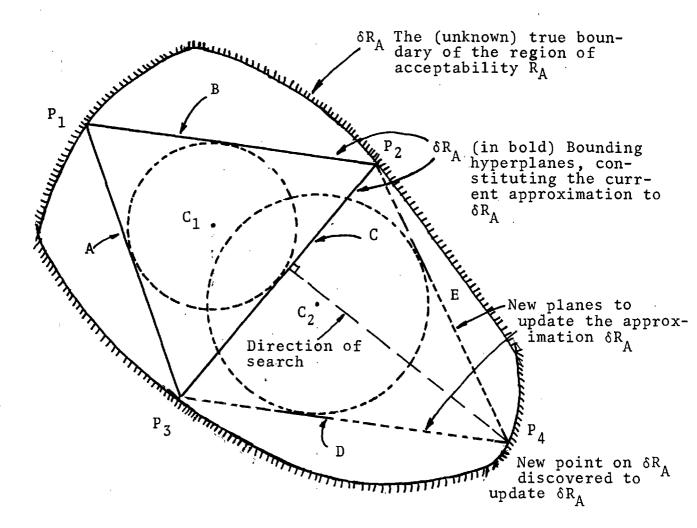

| Fig. | 2.3  | An illustration of the (face based)<br>simplicial approximation method<br>of design centering.                                   | 89 |

|      |      |                                                                                                                                  |    |

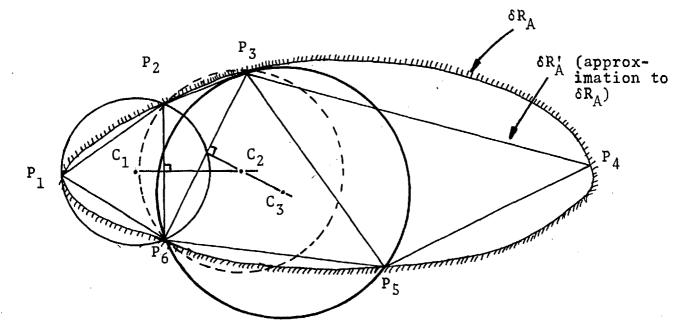

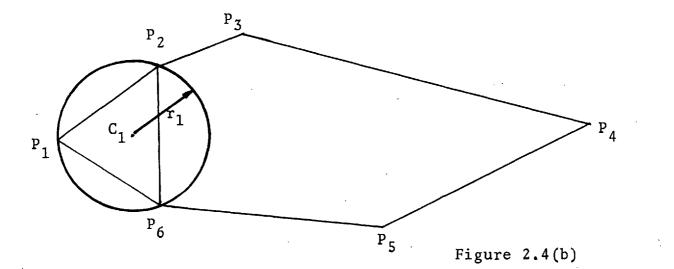

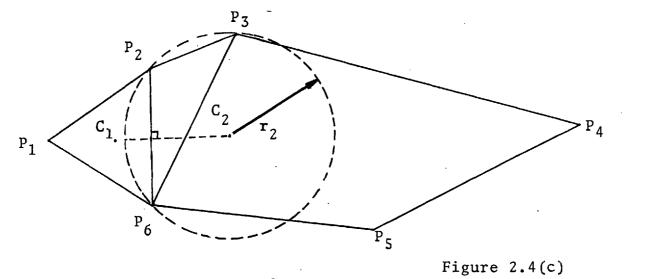

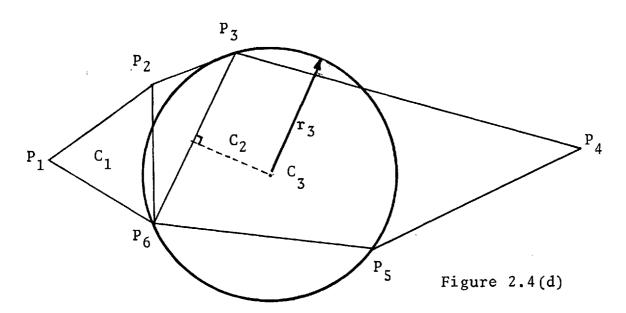

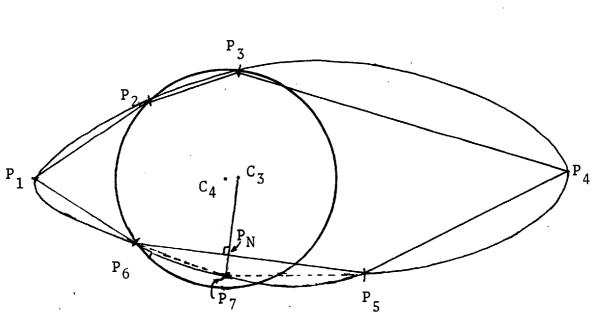

Fig. 2.4 The point basis method of design 90 centering.

.

PAGE

.

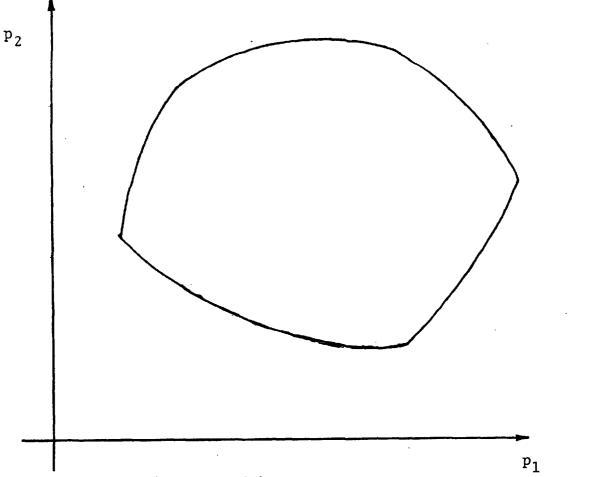

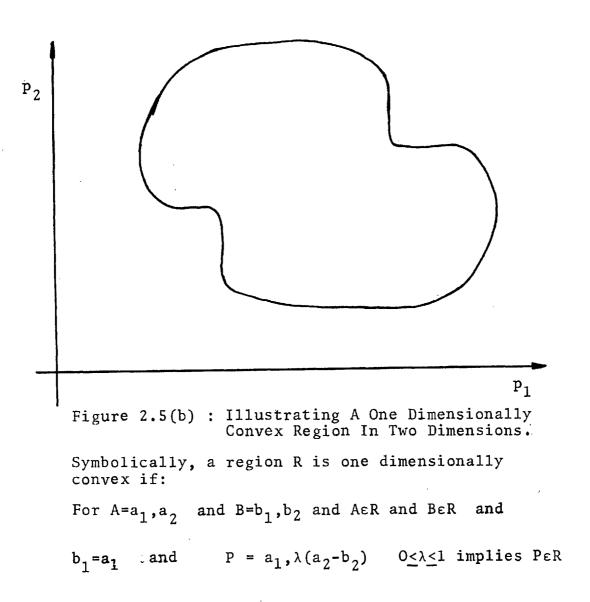

| Fig. | 2.5  | An illustration of one-dimensional convexity.                                                                                                                                                                   | 93  |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

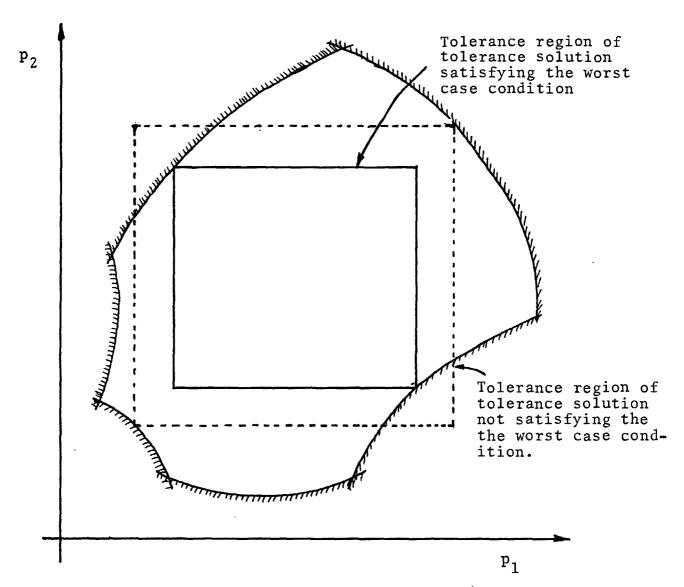

| Fig. | 2.6  | Illustrating the overdesign inherent in worst case tolerance solutions.                                                                                                                                         | 95  |

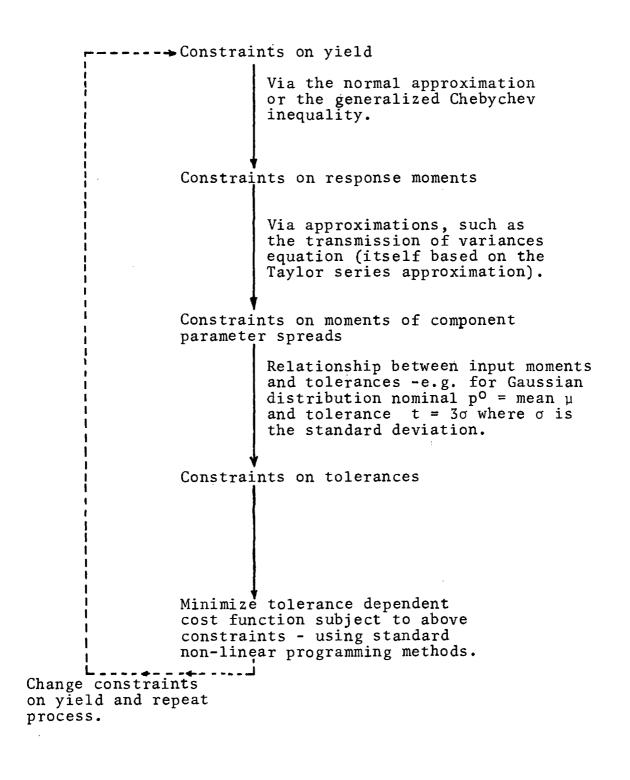

| Fig. | 2.7  | An illustration of the structure<br>of statistical, non-linear programming<br>based methods for tolerance assignment.                                                                                           | 96  |

| Fig. | 2.8  | A yield estimation procedure based on linear approximations of the boundary of the intersection of the regions $R_A$ and $R_T$ .                                                                                | 97  |

| Fig. | 2.9  | The TOLERATE method of tolerance assignment.                                                                                                                                                                    | 98  |

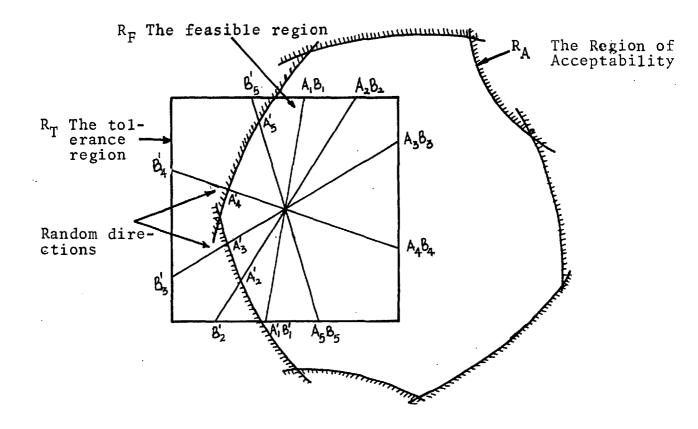

| Fig. | 2.10 | The radial exploration method of obtaining an indication of yield.                                                                                                                                              | 99  |

| Fig. | 2.11 | The radial exploration method of design centering.                                                                                                                                                              | 100 |

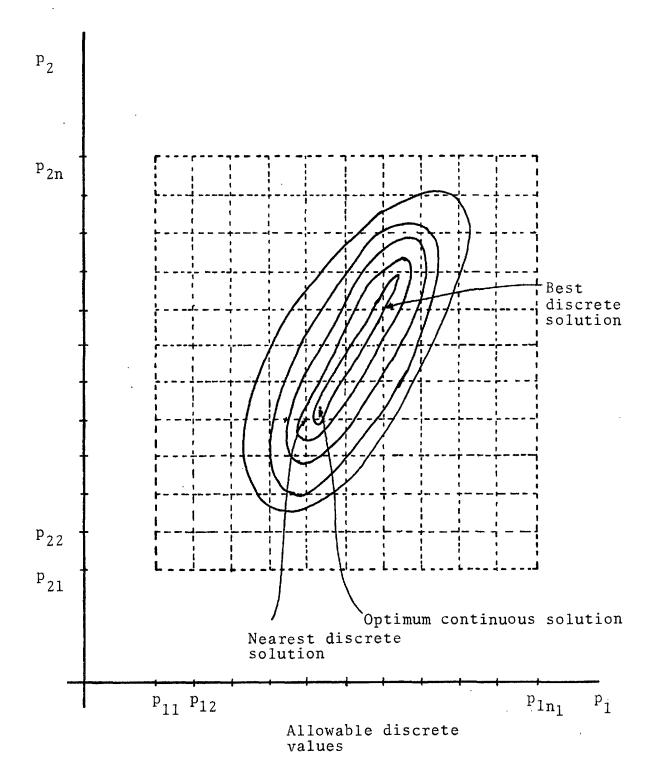

| Fig. | 3.1  | Contours for a hypothetical objective<br>function showing that in general the<br>discrete solution nearest to the<br>continuous optimum solution is not<br>necessarily the best available discrete<br>solution. | 123 |

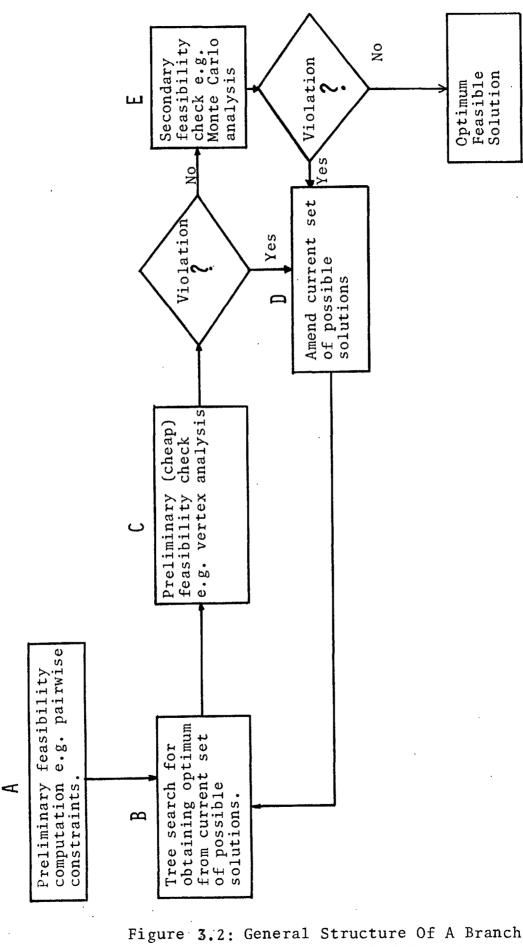

| Fig. | 3.2  | General structure of a branch and<br>bound method for discrete worst case<br>tolerance assignment.                                                                                                              | 124 |

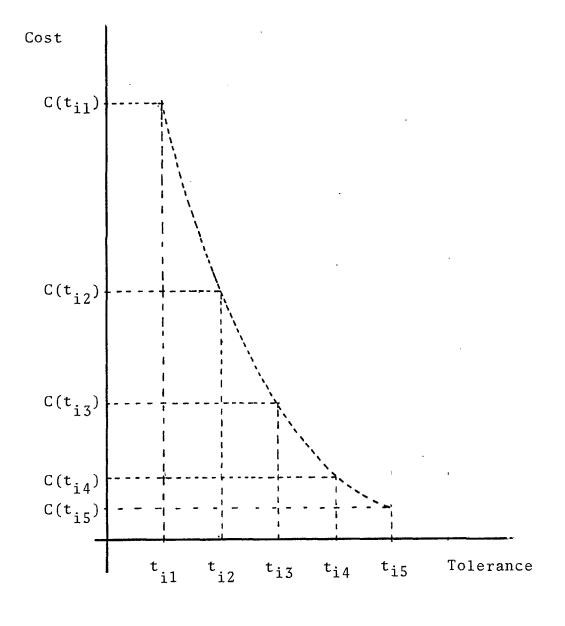

| Fig. | 3.3  | Typical discrete cost versus tolerance relationship.                                                                                                                                                            | 125 |

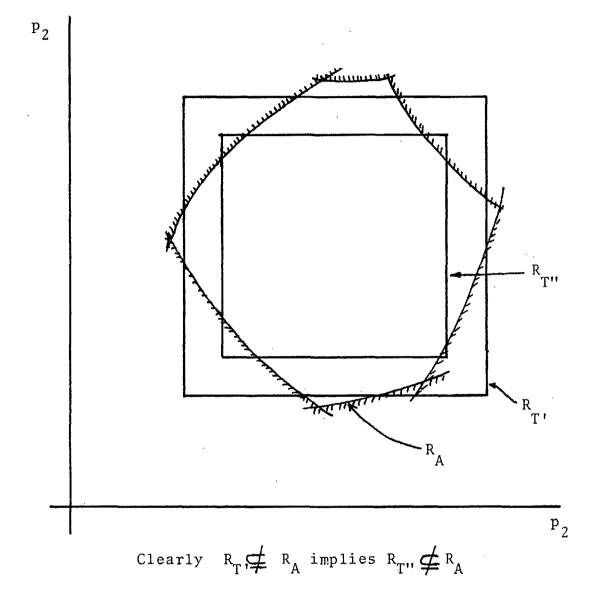

| Fig. | 3.4  | Illustrating the basis for eliminating<br>certain non-feasible solutions in the<br>branch and bound methods for worst case<br>tolerance assignment.                                                             | 126 |

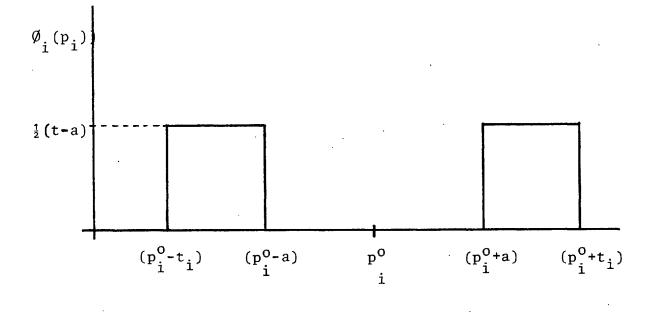

| Fig. | 3.5  | Bimodal distribution used in Monte Carlo 'feasibility testing.                                                                                                                                                  | 127 |

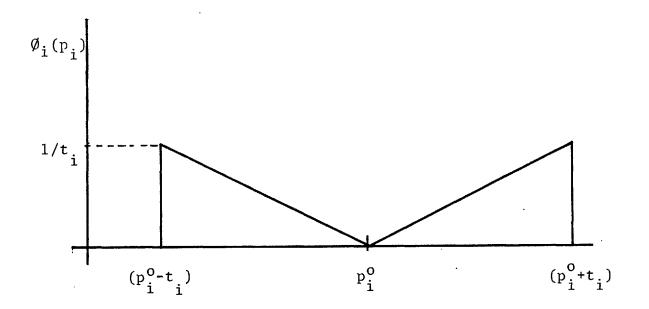

| Fig. | 3.6  | Double triangular distribution used in<br>Monte Carlo feasibility testing.                                                                                                                                      | 127 |

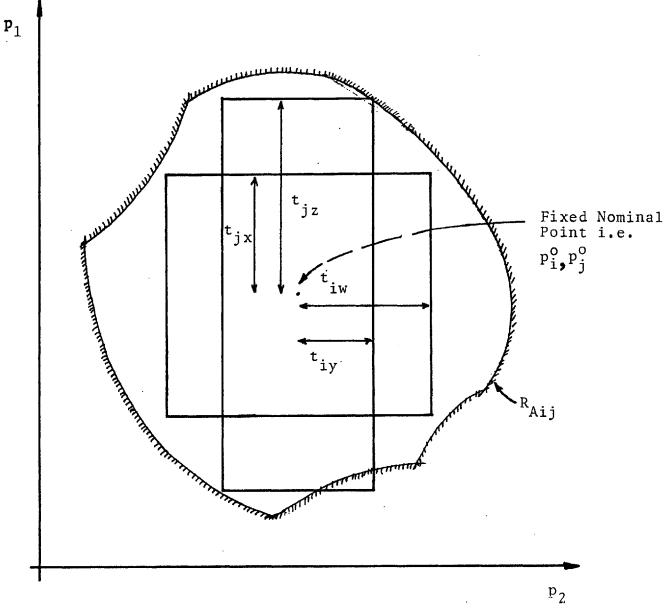

| Fig. | 3.7  | An illustration of pairwise feasibility.                                                                                                                                                                        | 128 |

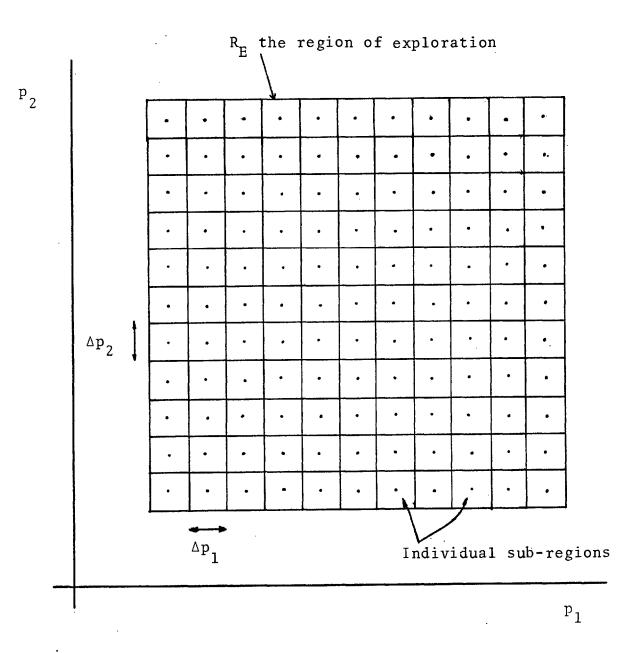

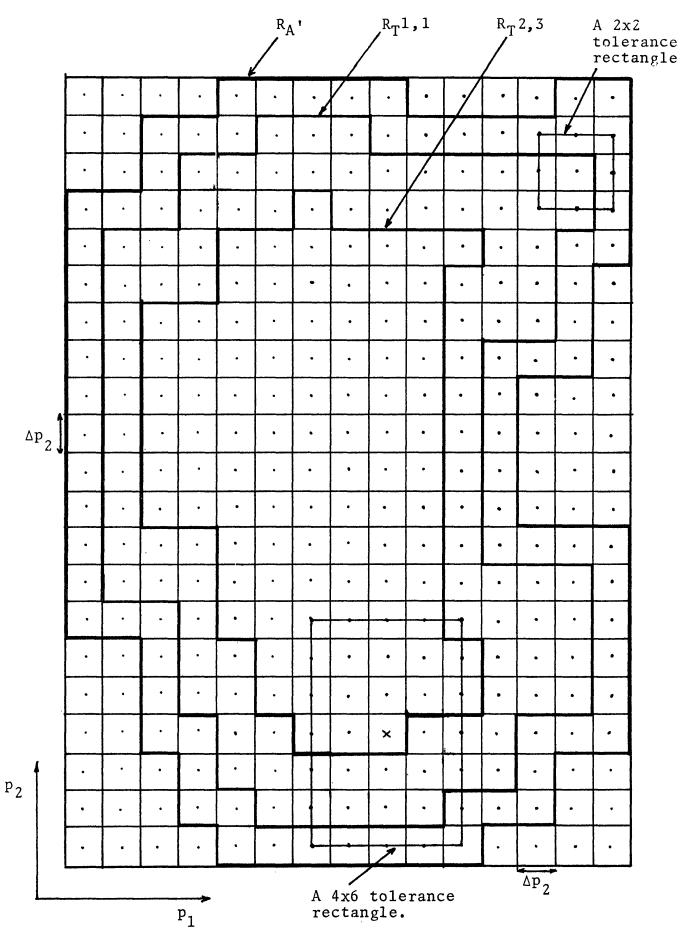

| Fig. | 3.8  | Illustrating regionalization for a two<br>dimensional example.                                                                                                                                                  | 129 |

|      |      | ·                                                                                                                      | PAGE |

|------|------|------------------------------------------------------------------------------------------------------------------------|------|

| Fig. | 3.9  | A discrete representation of the region of acceptability.                                                              | 130  |

| Fig. | 3.10 | Illustrating the basis of the indentation method.                                                                      | 131  |

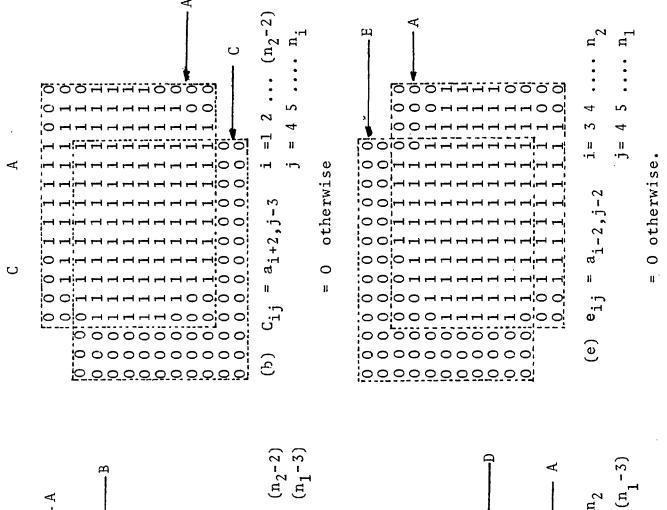

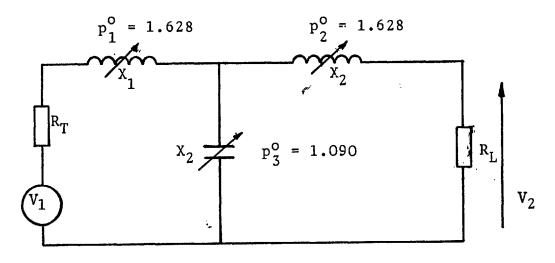

| Fig. | 3.11 | Representing the region of exploration as a matrix of logical elements.                                                | 132  |

| Fig. | 3.12 | Illustrating partial indentation.                                                                                      | 133  |

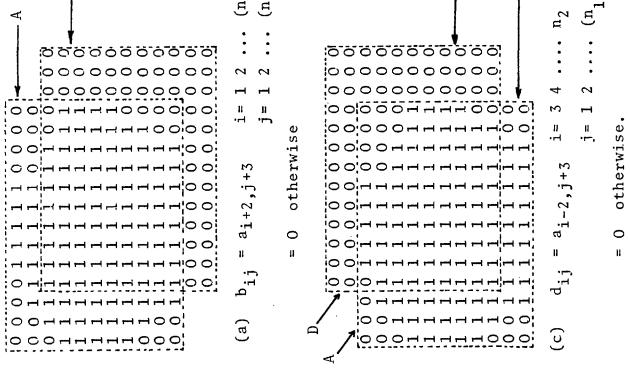

| Fig. | 3.13 | A low pass filter example.                                                                                             | 135  |

| Fig. | 3.14 | Performance requirements for the low pass filter example.                                                              | 135  |

| Fig. | 3.15 | The region of acceptability of the<br>low pass filter represented as a<br>3-dimensional matrix of logical<br>elements. | 136  |

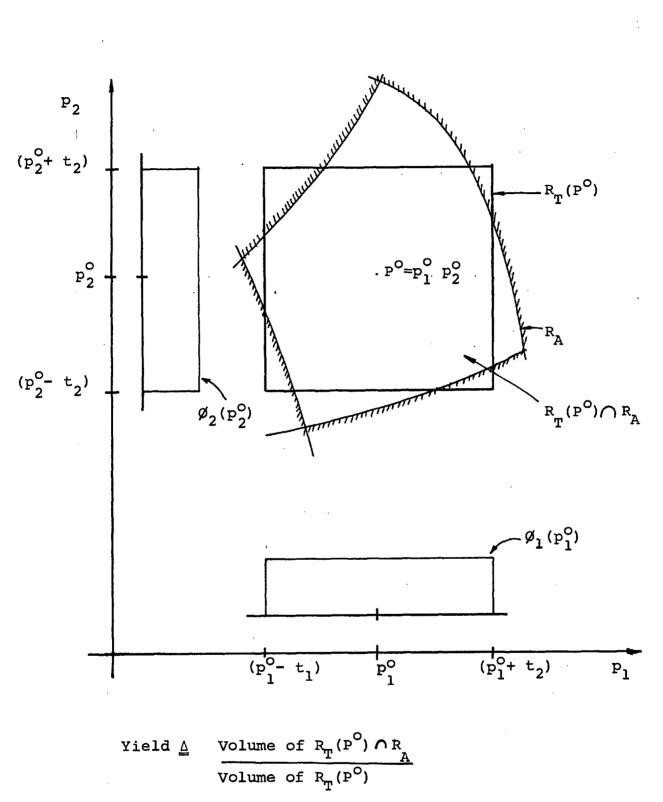

| Fig. | 4.1  | A geometrical interpretation of yield.                                                                                 | 196  |

| Fig. | 4.2. | A general flow chart for the Pattern<br>Search method.                                                                 | 197  |

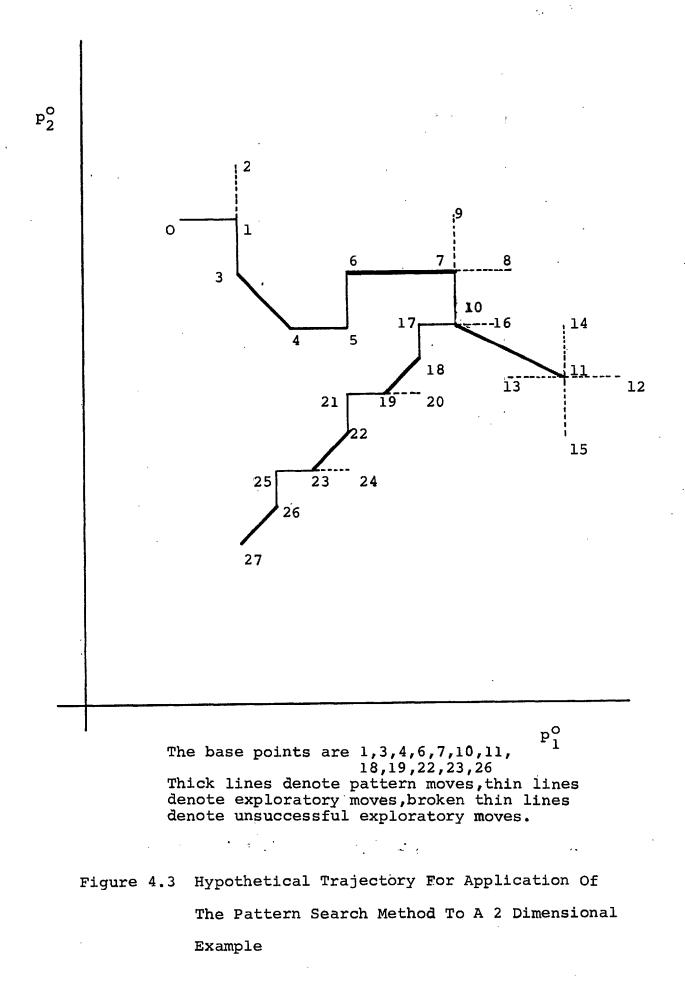

| Fig. | 4.3  | Hypothetical trajectory for application<br>of the pattern search method to a<br>2-dimensional example.                 | 198  |

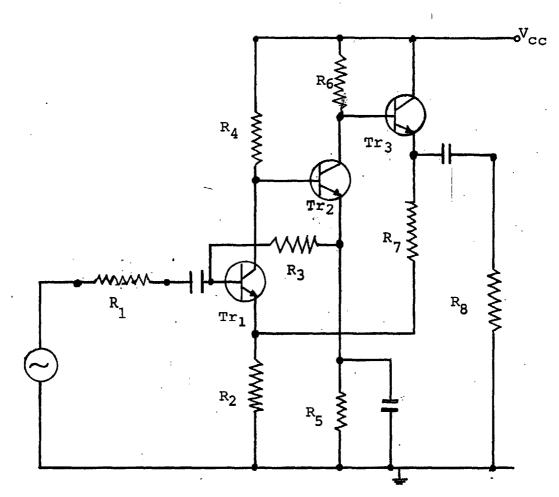

| Fig. | 4.4  | Wide band amplifier circuit example for the pattern search strategy.                                                   | 199  |

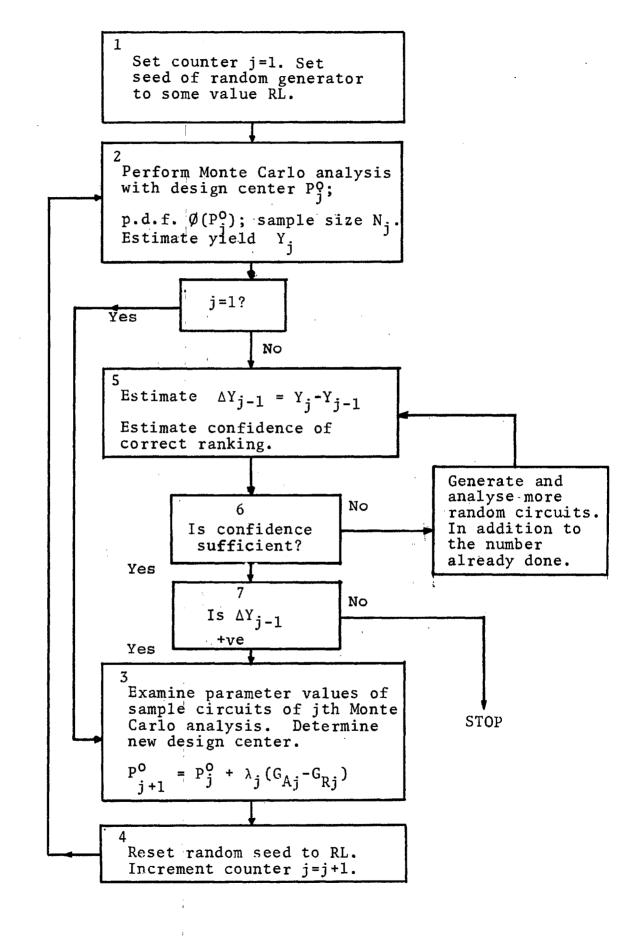

| Fig. | 4.5  | General flow chart for the statistical exploration method.                                                             | 200  |

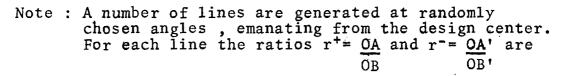

| Fig. |      | A geometrical representation of the<br>relationship between successive iterates<br>in design centering.                | 201  |

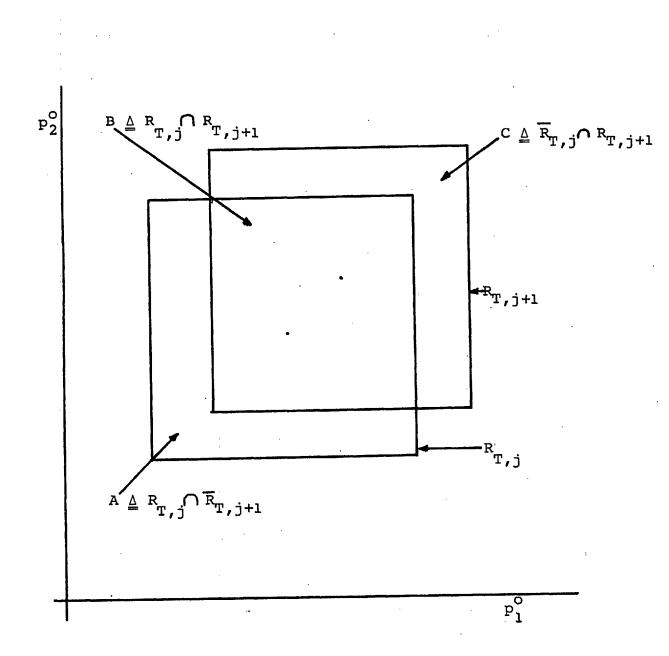

| Fig. | 4.7  | Illustrating some additional notation.                                                                                 | 202  |

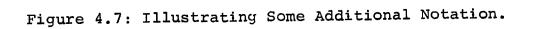

| Fig. | 4.8  | Sampling distribution of the yield estimate.                                                                           | 203  |

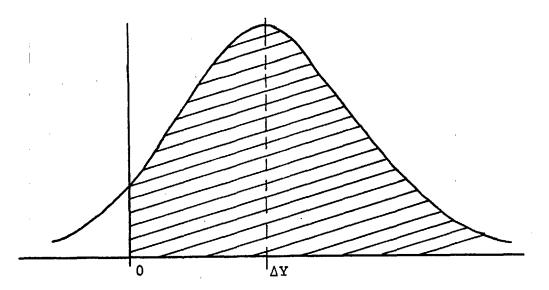

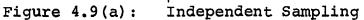

| Fig. | 4.9  | Sampling distributions for estimating yield difference.                                                                | 204  |

| Fig. | 4.10 | Illustrating the relationship between p.d.f.'s of successive iterates.                                                 | 205  |

| Fig | g. 4.11 | Illustrating the relationship between<br>corresponding sample points for<br>successive tolerance regions when the<br>correlated sampling scheme is employed. | 206 |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig | 4.12    | Illustrating notation for the distri-<br>bution of sample points in the common<br>points scheme.                                                             | 207 |

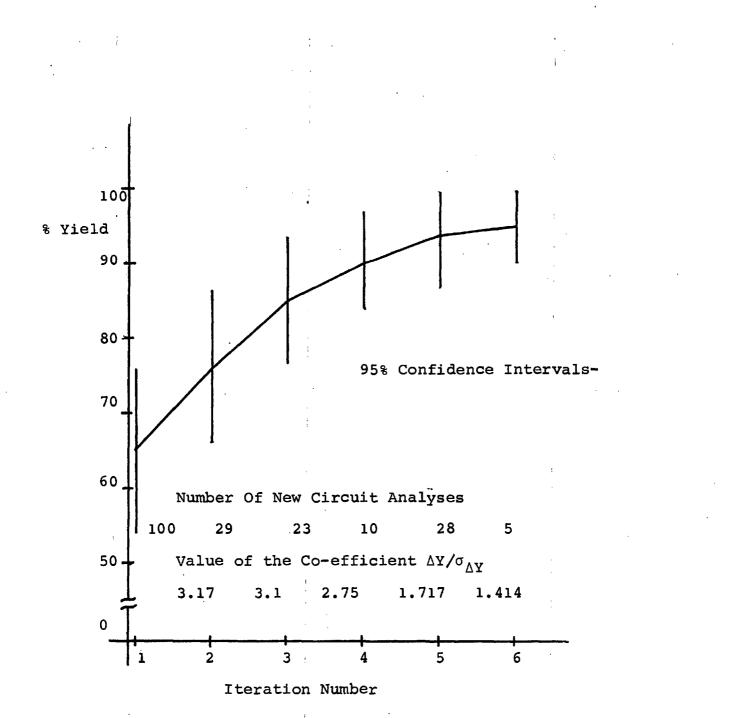

| Fig | 4.13    | Yield trajectory for a high pass filter<br>example; demonstrating the effective-<br>ness of the common points scheme.                                        | 208 |

| Fig | . 4.14  | Flow chart for a statistical explo-<br>ration - design centering algorithm<br>employing the correlated sampling<br>scheme.                                   | 209 |

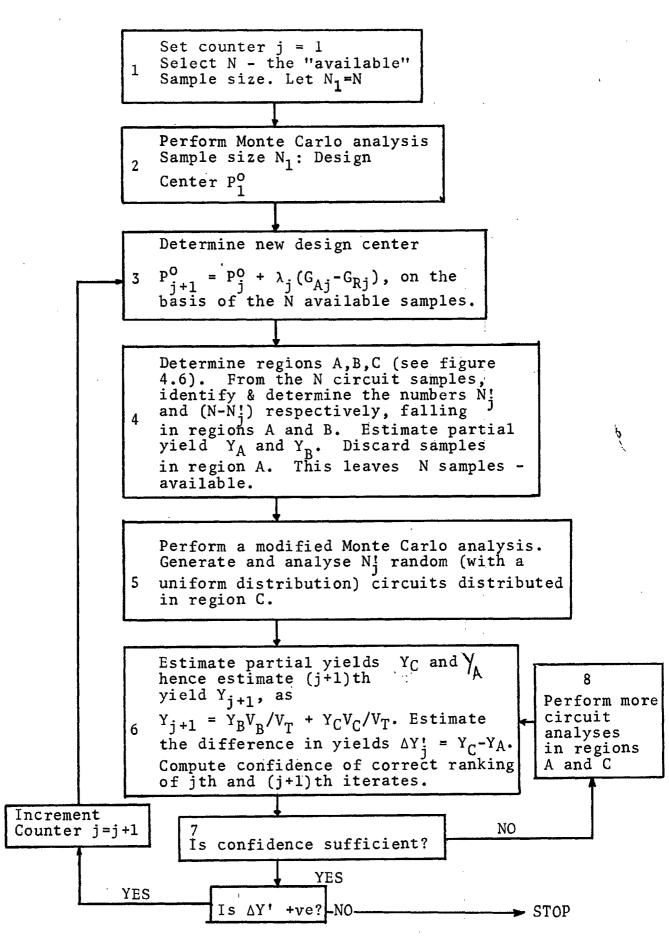

| Fig | . 4.15  | Flow chart for a statistical exploration-<br>design centering algorithm employing<br>the common points scheme.                                               | 210 |

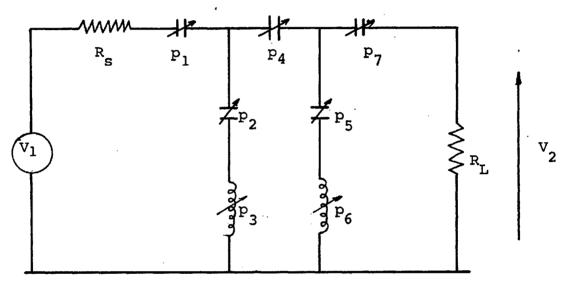

| Fig | . 4.16  | Circuit diagram of the passive high pass<br>filter.                                                                                                          | 211 |

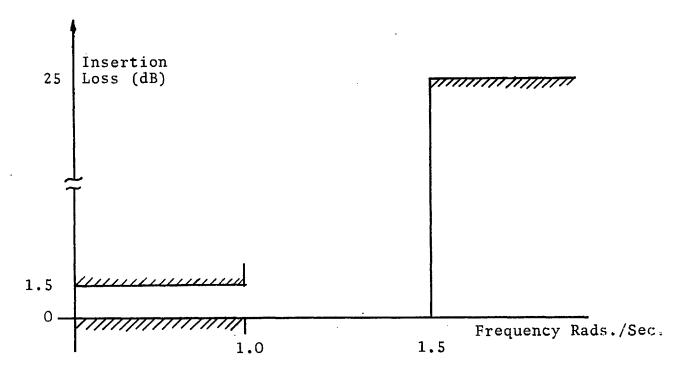

| Fig | . 4.17  | Performance requirements for the high pass filter.                                                                                                           | 212 |

| Fig | . 4.18  | Yield trajectory for the high pass<br>filter assuming 5% tolerances<br>and uniform distributions.                                                            | 213 |

| Fig | . 4.19  | Yield trajectory for the high pass<br>filter assuming 15% tolerances<br>and uniform distributions.                                                           | 214 |

| Fig | . 4.20  | Yield trajectories for the high pass<br>filter assuming 10% tolerances and<br>uniform and Gaussian distributions.                                            | 215 |

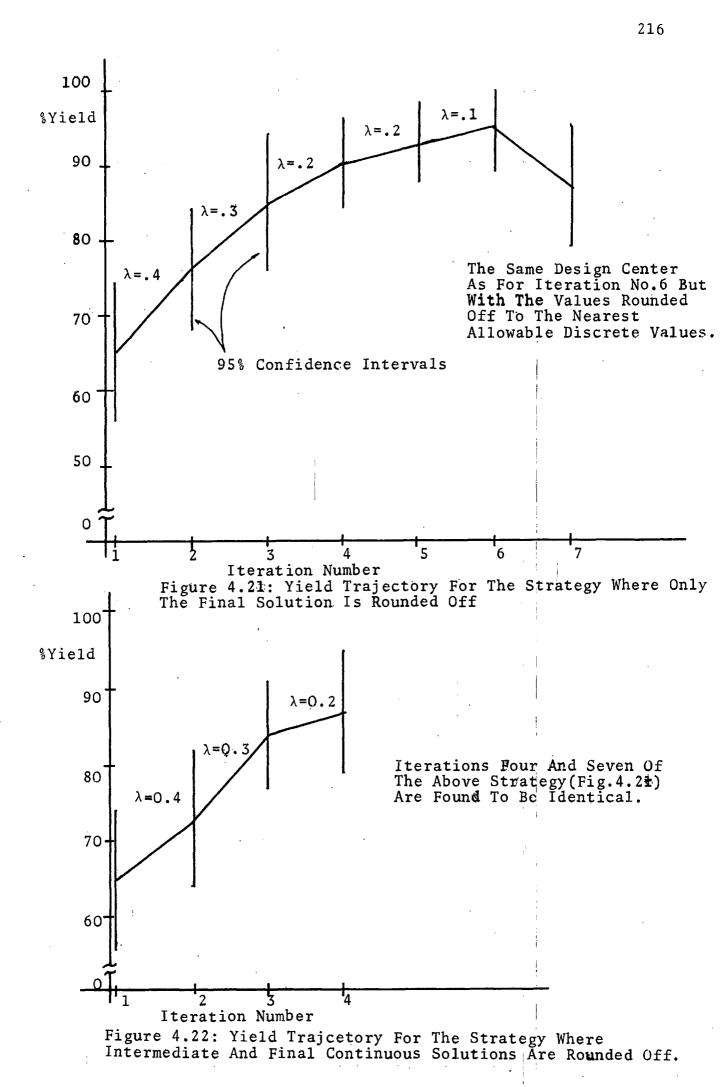

| Fig | . 4.21  | Yield trajectory for the strategy<br>where only the final continuous<br>solution is rounded off.                                                             | 216 |

| Fig | 4.22    | Yield trajectory for the strategy<br>where intermediate and final<br>continuous solutions are rounded<br>off.                                                | 216 |

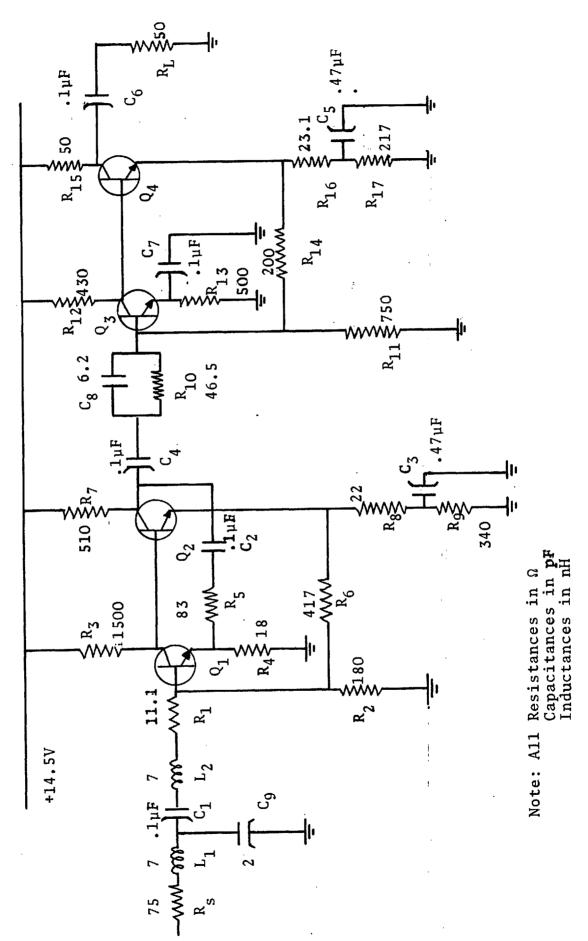

| Fig | . 4.23  | Circuit diagram of the high frequency<br>amplifier example, including the d.c.<br>biasing components.                                                        | 217 |

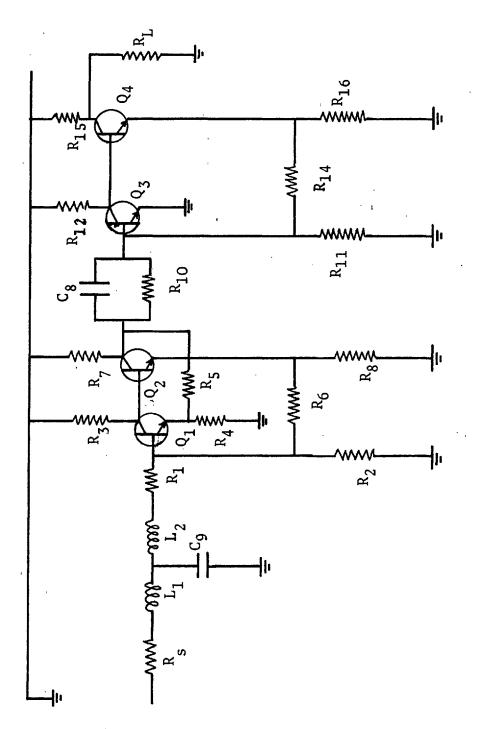

| Fig | . 4.24  | Circuit diagram of the a.c. equivalent of the high frequency amplifier.                                                                                      | 218 |

۰. ۱

i

•

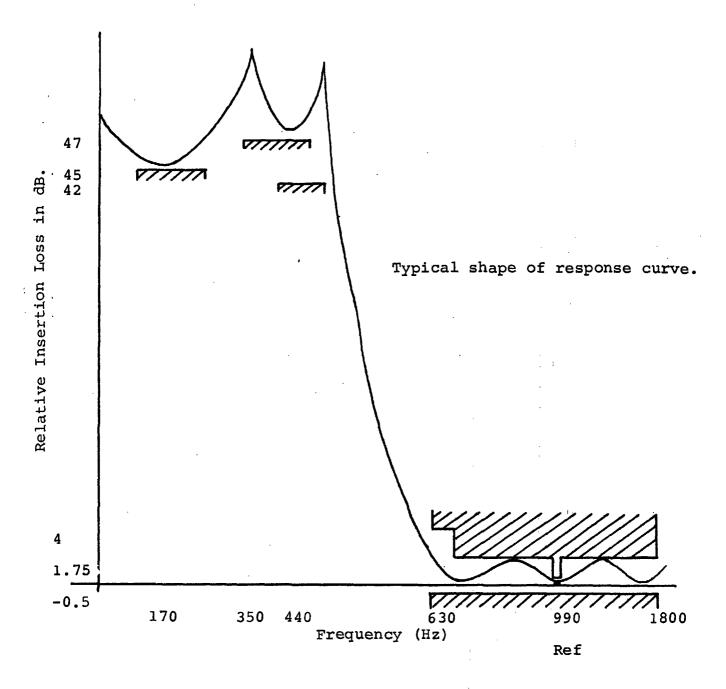

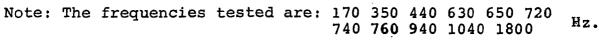

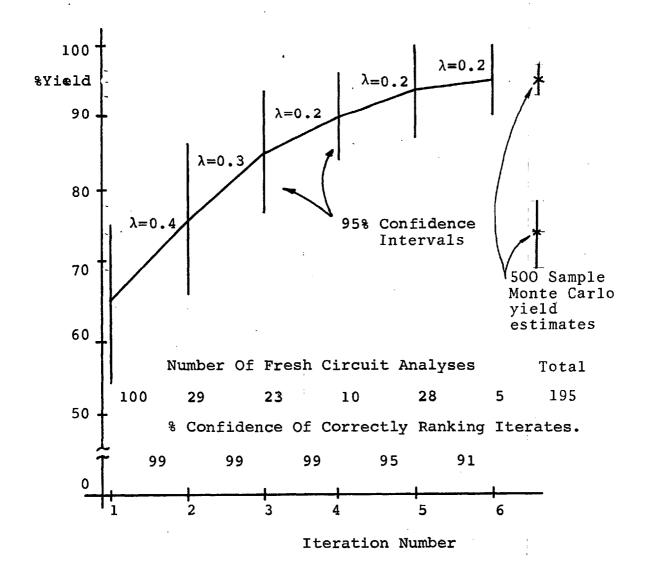

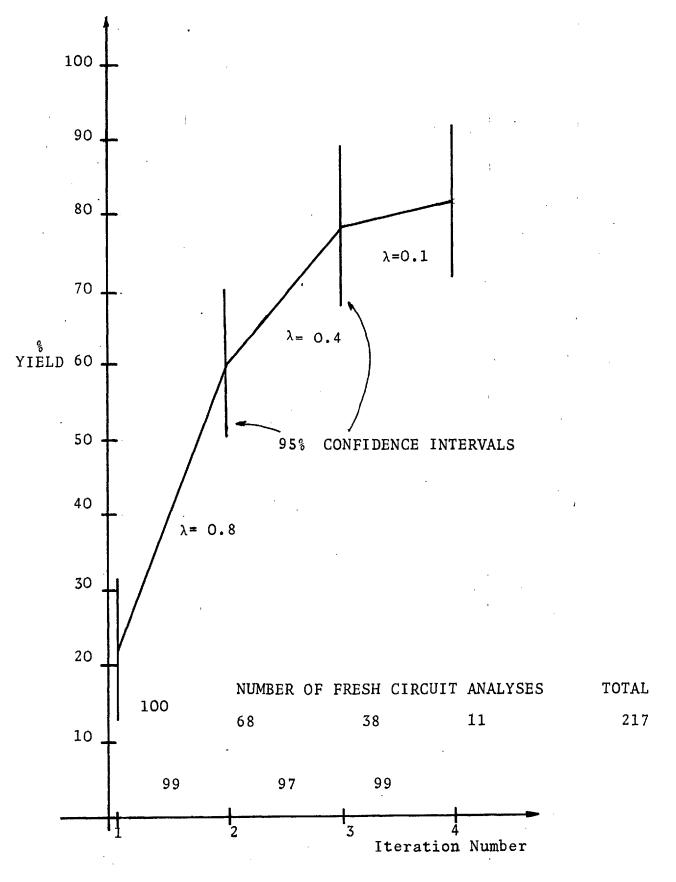

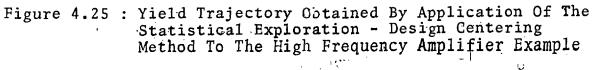

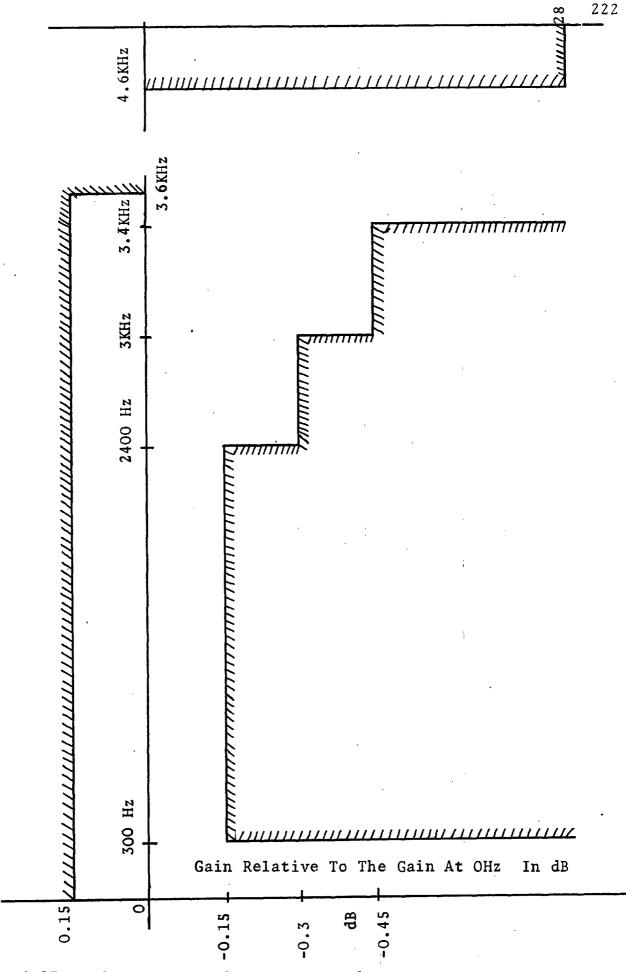

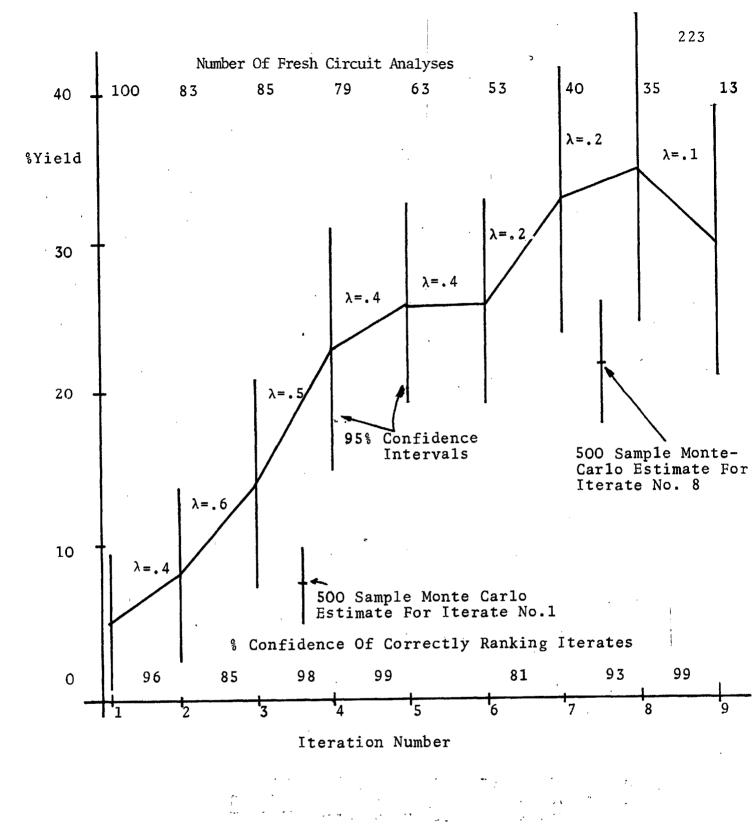

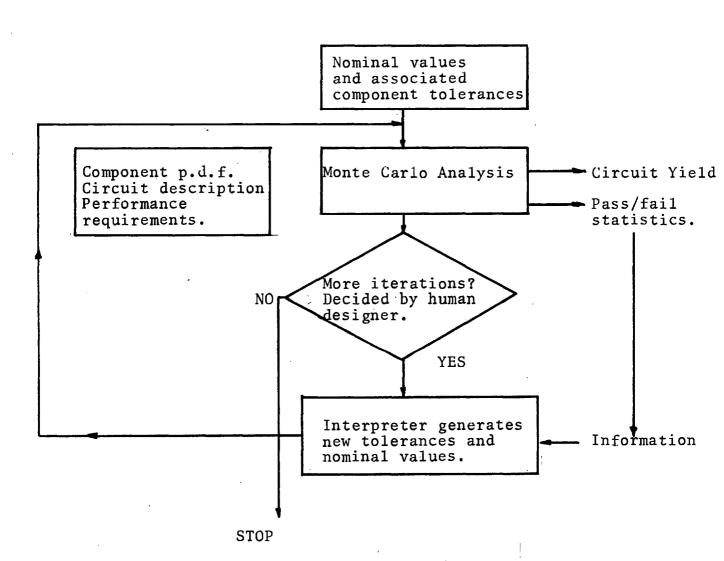

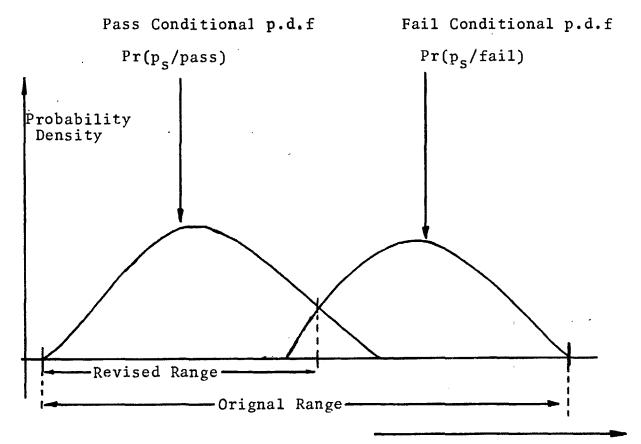

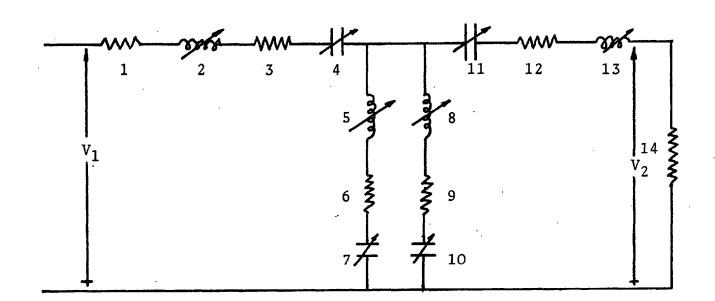

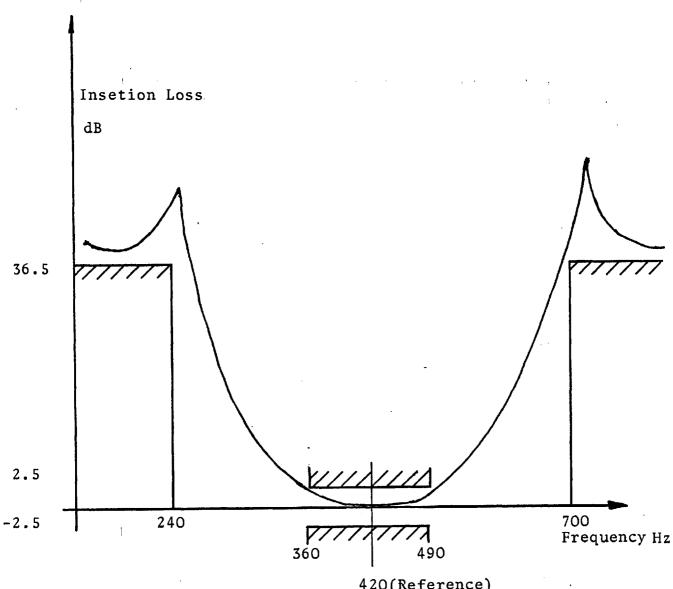

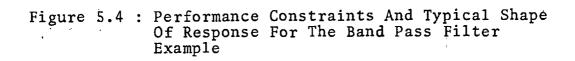

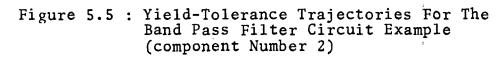

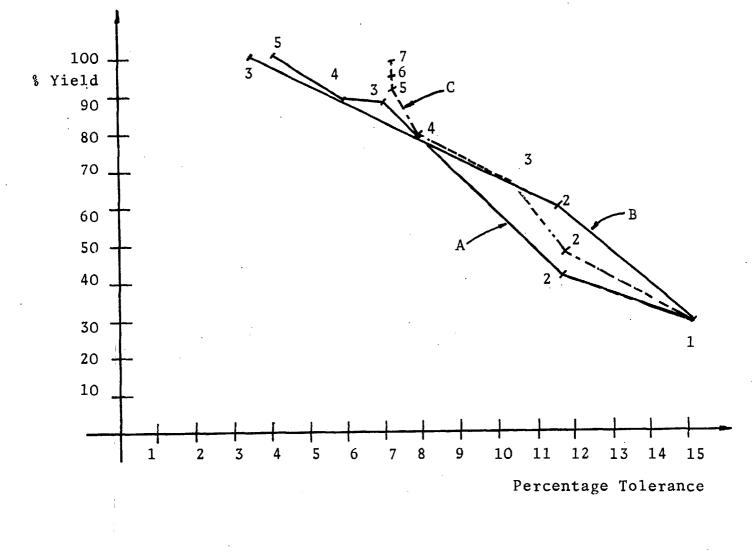

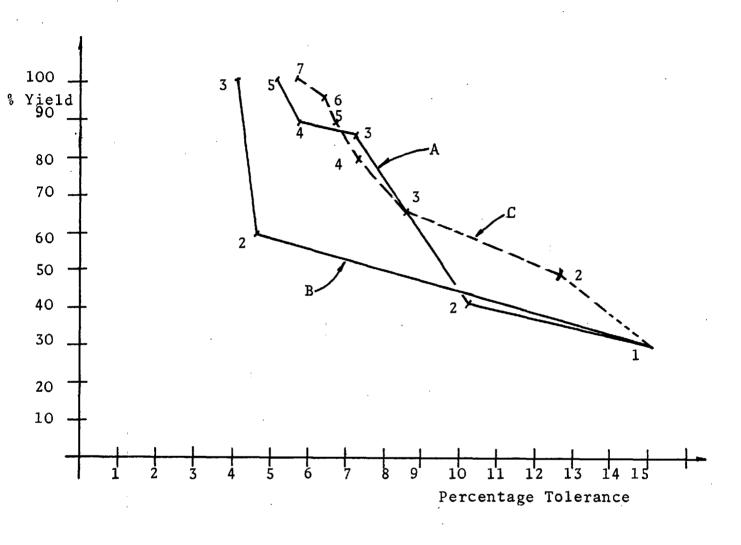

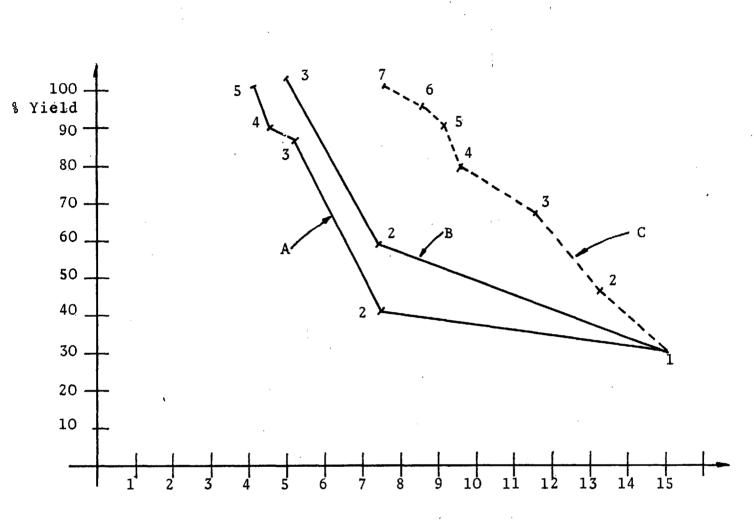

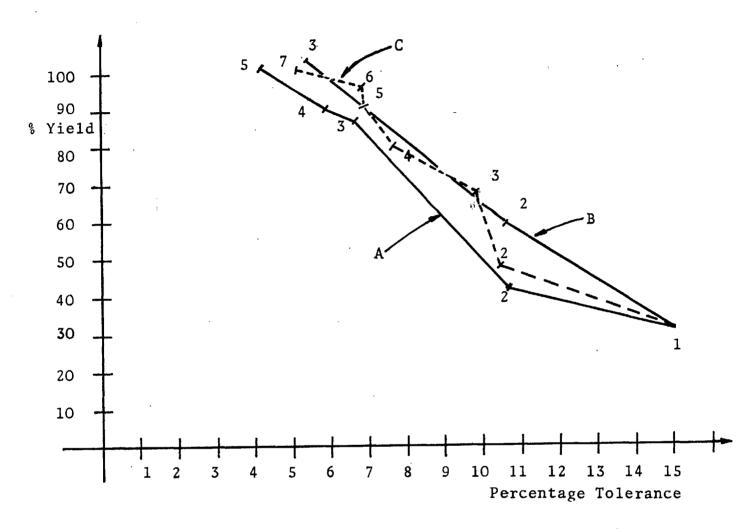

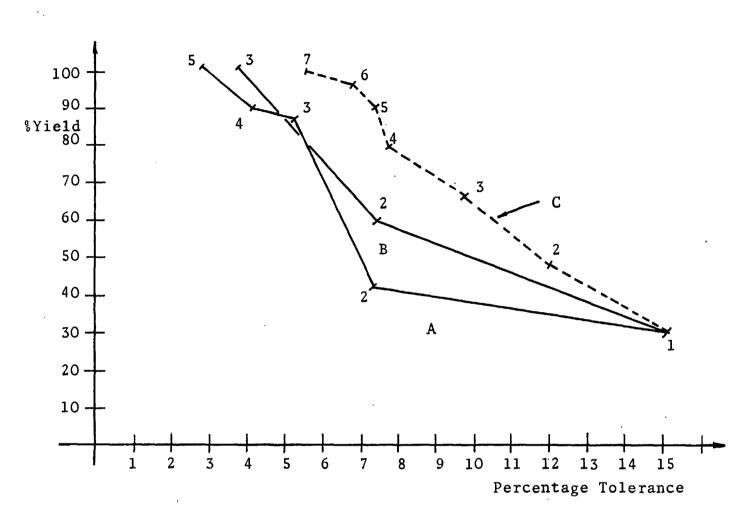

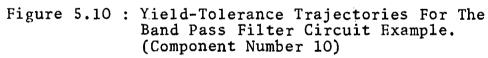

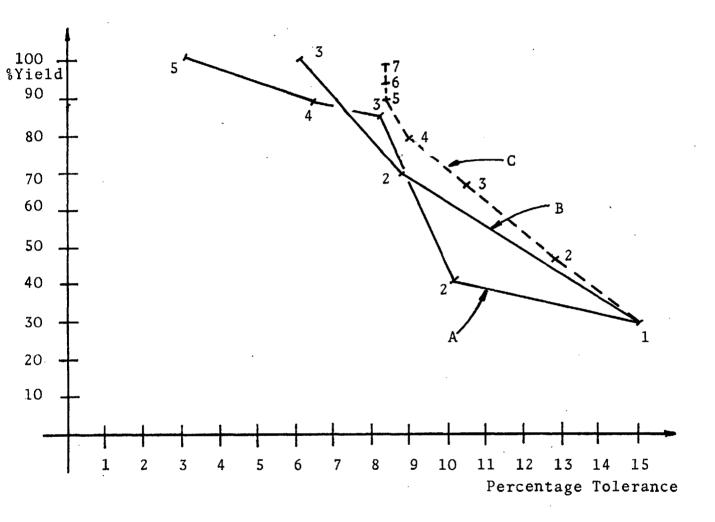

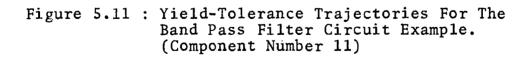

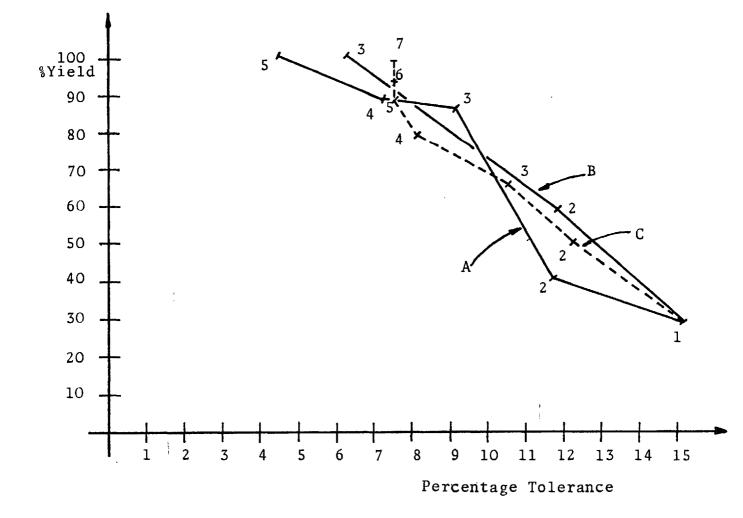

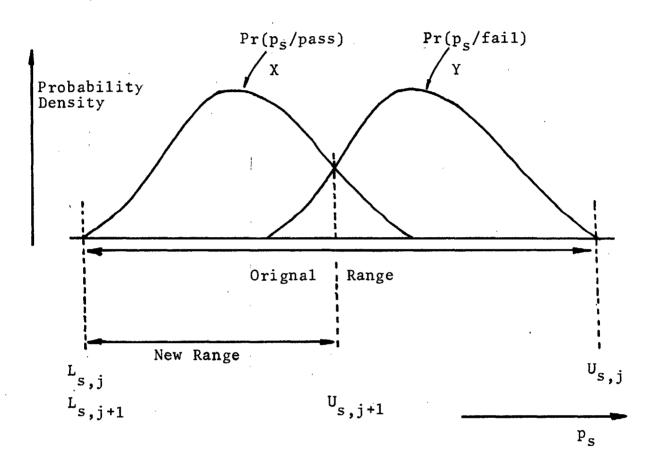

220 Fig. 4.25 Yield trajectory obtained by application of the statistical exploration-design centering method to the high frequency. amplifier example. Fig. 4.26 A general structure for a transversal 221 filter. Fig. 4.27 Performance requirements for the transversal filter example. 222 Fig. 4.28 Yield trajectory obtained by application 223 of the statistical exploration design centering method to the 43 variable transversal filter. A general flow chart for the TOLERATE And 254 Fig. 5.1 PERTOL methods of tolerance assignment. Fig. 5.2 The TOLERATE tolerance assignment criterion, 255 showing the original and revised ranges; assuming  $\lambda = 1$ . Circuit diagram of the band pass filter exa Fig. 5.3 256 example. Performance constraints and typical shape Fig. 5.4 257 of response for the band pass filter example. Yield tolerance trajectories for the band Fig. 5.5 258 pass filter circuit example (component number 2). Yield tolerance trajectories for the band Fig. 5.6 259 pass filter circuit example ( component number 4). 11 11 11 (Component number 5). Fig. 5.7 260 11 11 11 7). Fig. 5.8 11 ( 261 11 11 11 11 8). ( Fig. 5.9 262 11 11 11 \*\* Fig. 5.10 ( 10). 263 11 11 ſ 11 11 11). Fig. 5.11 264 11 11 11 11 13). Fig. 5.12 ( 265 Fig. 5.13 An illustration of expression 5.13. 266

PAGE

ŧ.

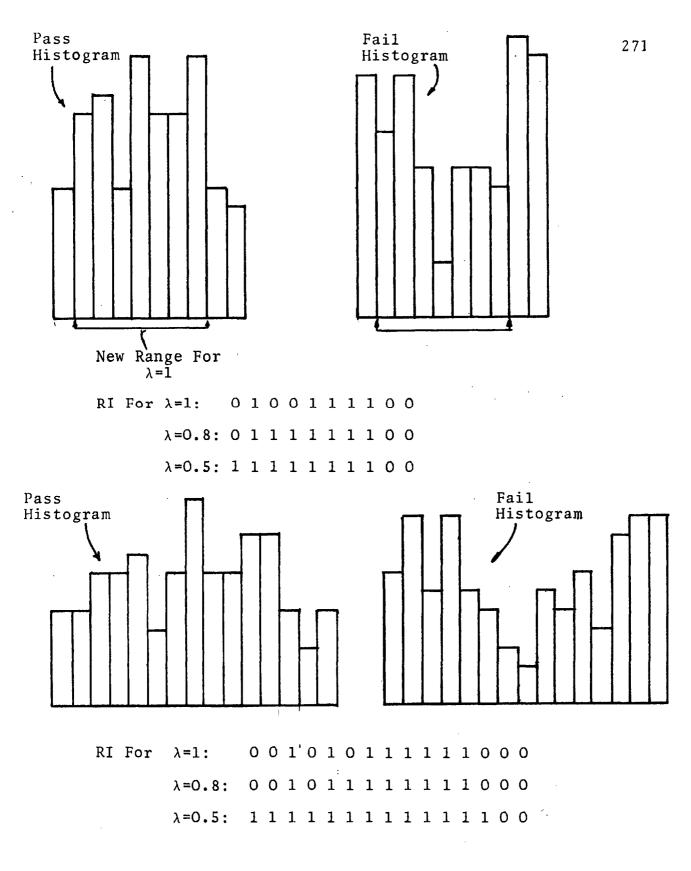

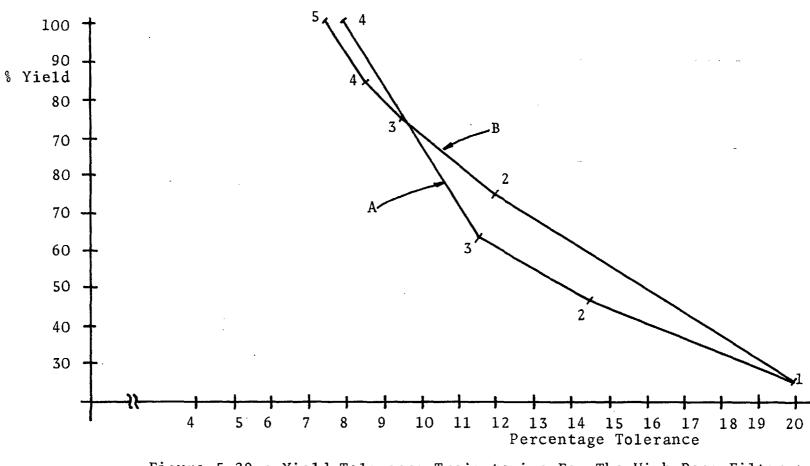

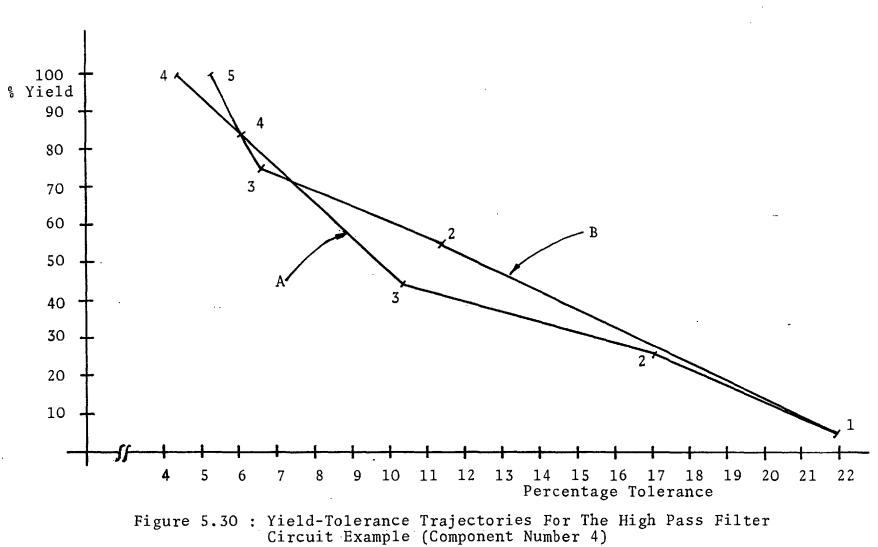

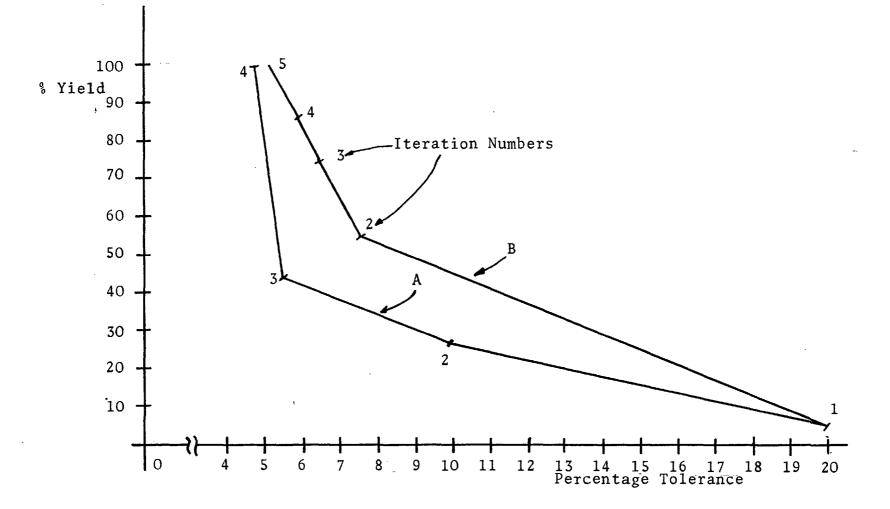

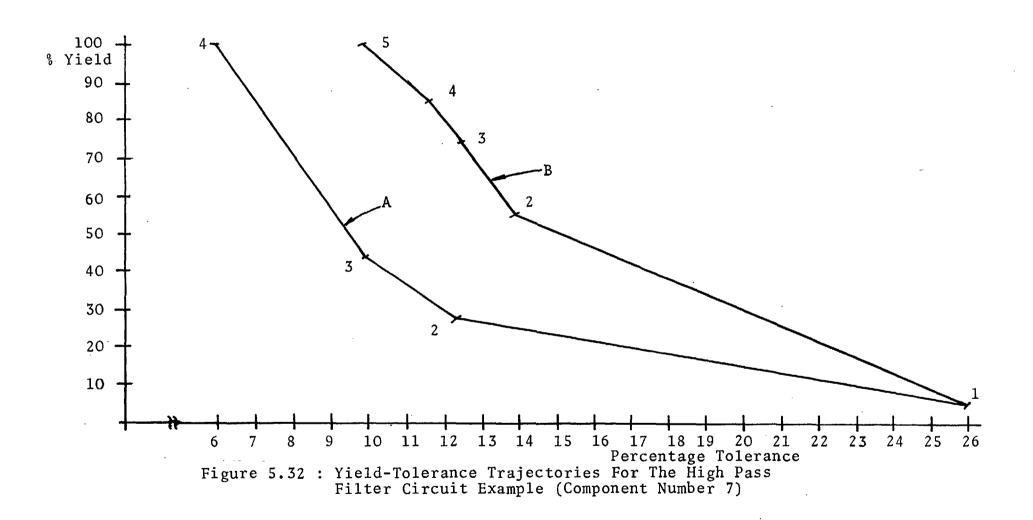

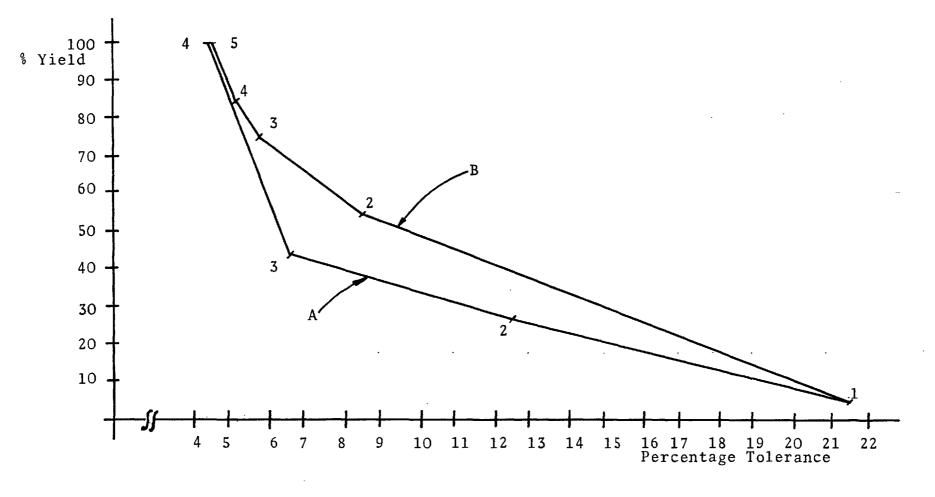

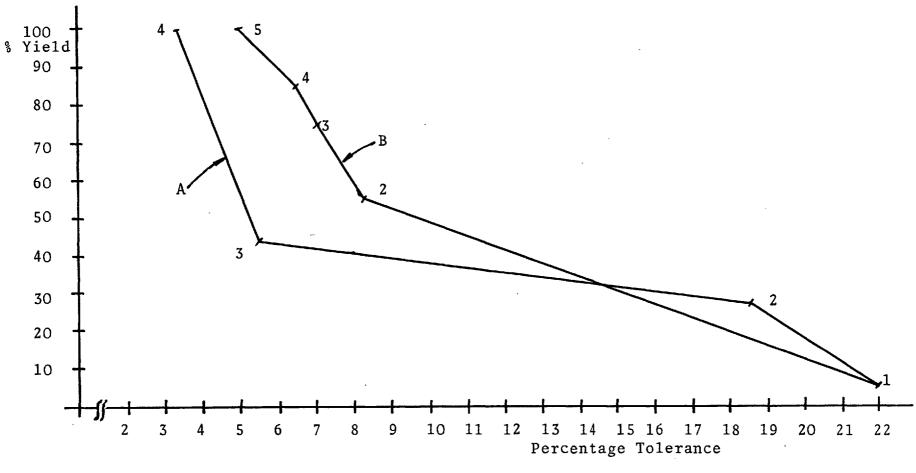

| Fig. | 5.14  | Diagram sho<br>of the high<br>(Component | pass            | filter             |                   |                 |                  | 269 |

|------|-------|------------------------------------------|-----------------|--------------------|-------------------|-----------------|------------------|-----|

| Fig. | 5.15  | **                                       | tt -            | 17 11              | (Compor           | nent 1          | Number 3).       | 270 |

| Fig. | 5.16  | 11                                       | 11              | 11 11              | ( "               |                 | " 4).            | 271 |

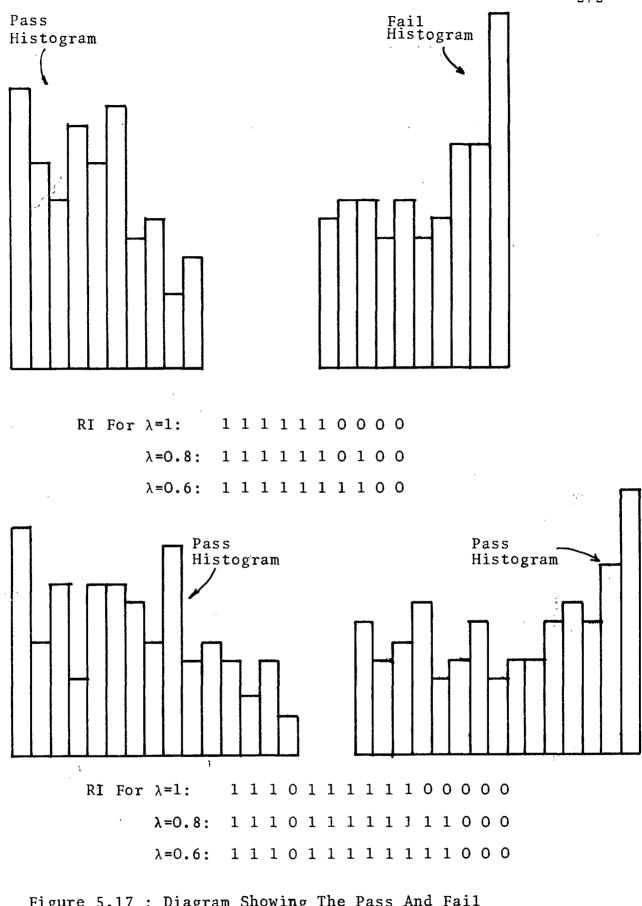

| Fig. | 5.17  | **                                       | 11              | ** **              | ("                |                 | " 6).            | 272 |

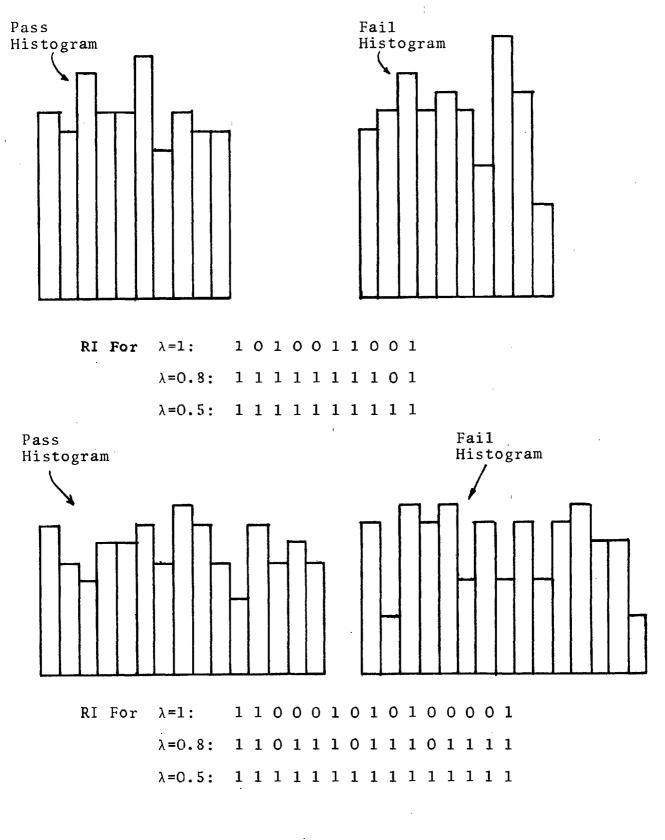

| Fig. | 5.18  | 11                                       | 11              | 11 11              | ( "               |                 | " 7).            | 273 |

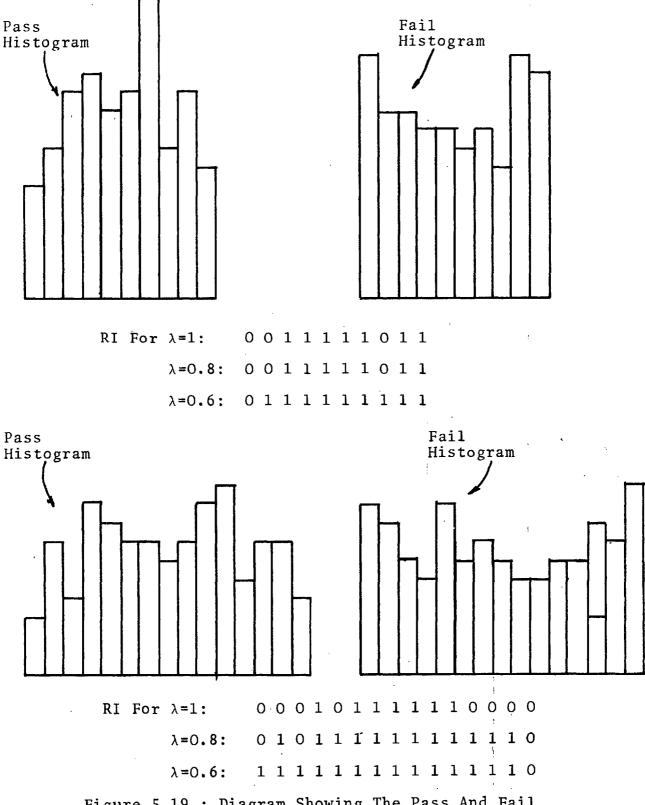

| Fig. | 5.19  | H.                                       | **              | 11 11              | ( "               |                 | " 8).            | 274 |

| Fig. | 5.20  | **                                       | **              | ** **              | ("                |                 | " 10).           | 275 |

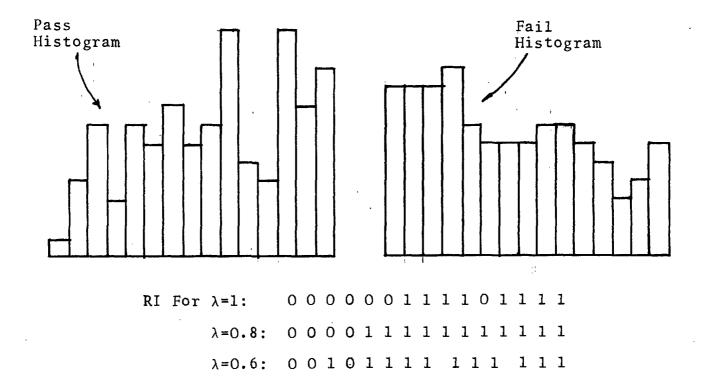

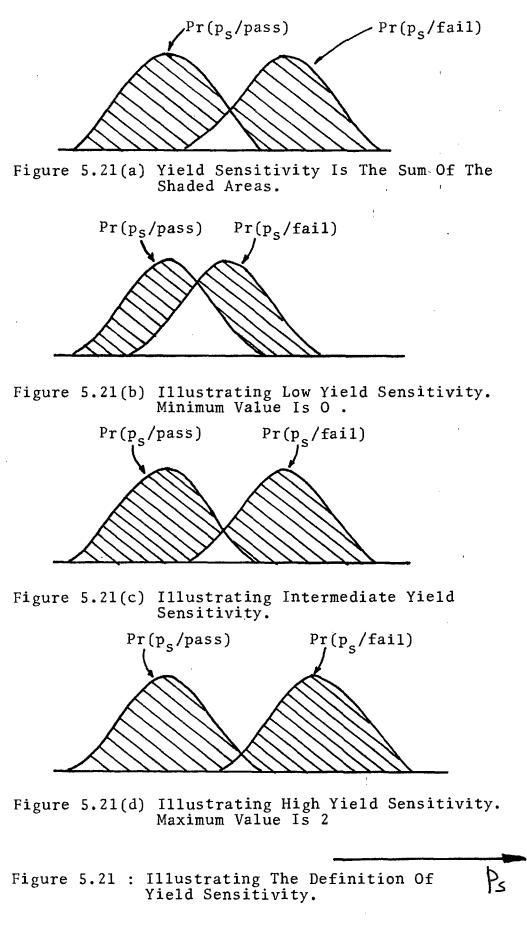

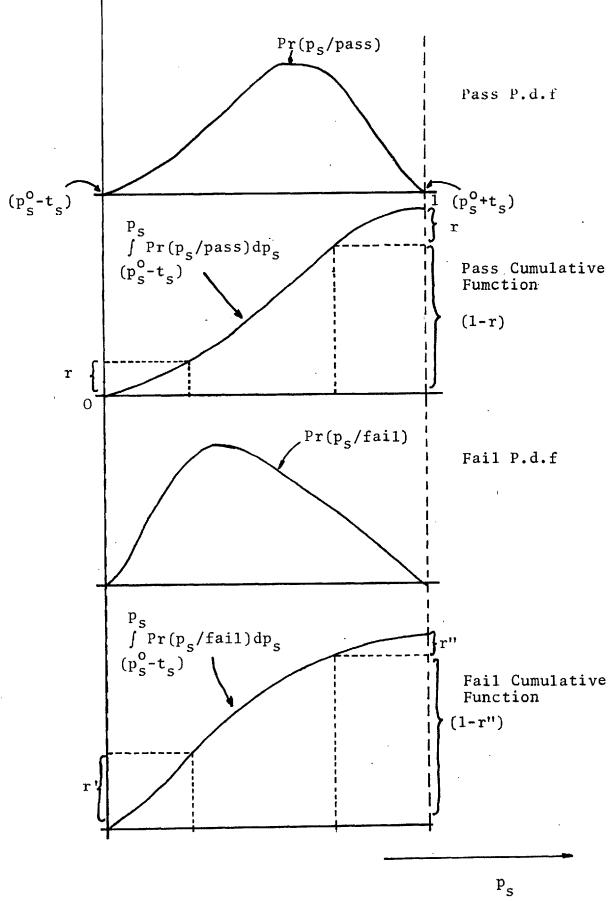

| Fig. | 5.21  | Illustratin                              | g the           | definit            | ion of            | yiel            | d sensitivity.   | 276 |

| Fig. | 5.22  | Illustratin<br>assignment.               |                 | PERTOL             | criter            | ion fo          | or tolerance     | 277 |

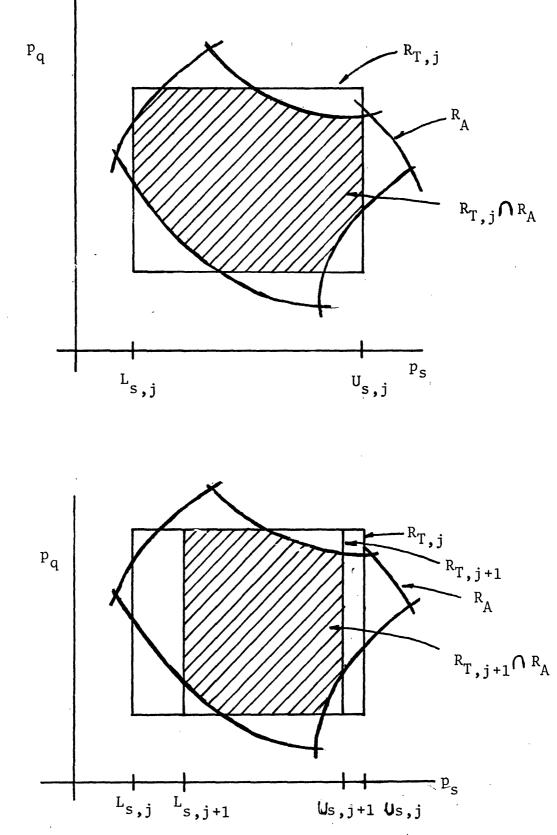

| Fig. | 5.23. | Illustratin                              | g some          | termin             | ology.            |                 |                  | 278 |

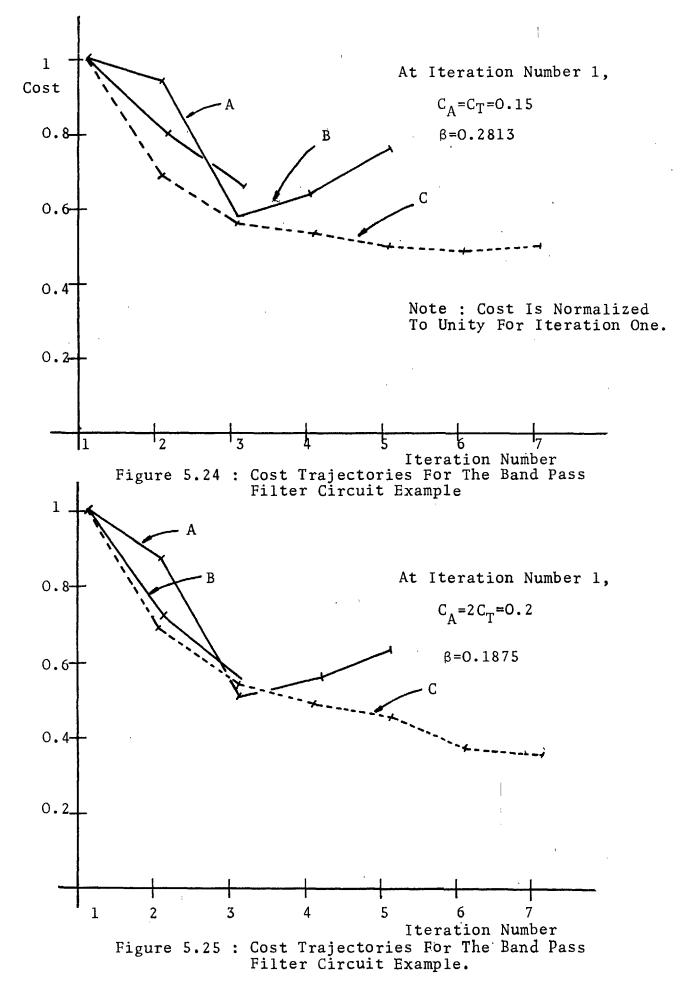

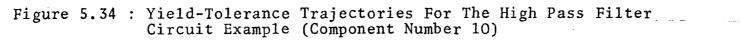

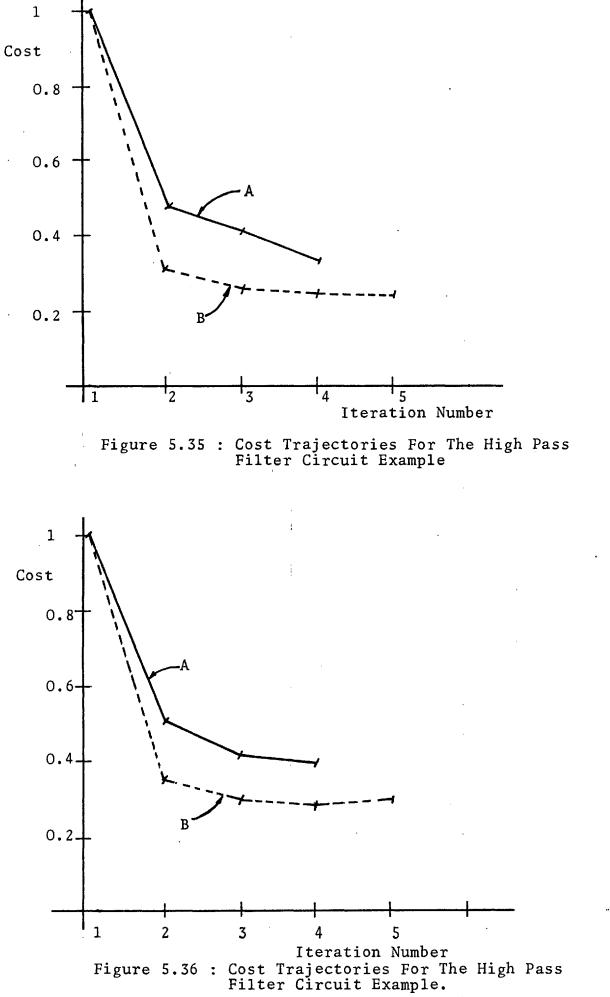

| Fig. | 5.24  | Cost trajec<br>circuit exa               |                 | for th             | e band            | pass            | filter           | 279 |

| Fig. | 5.25  | 11 11                                    | **              | 11                 | **                | 17              | **               | 279 |

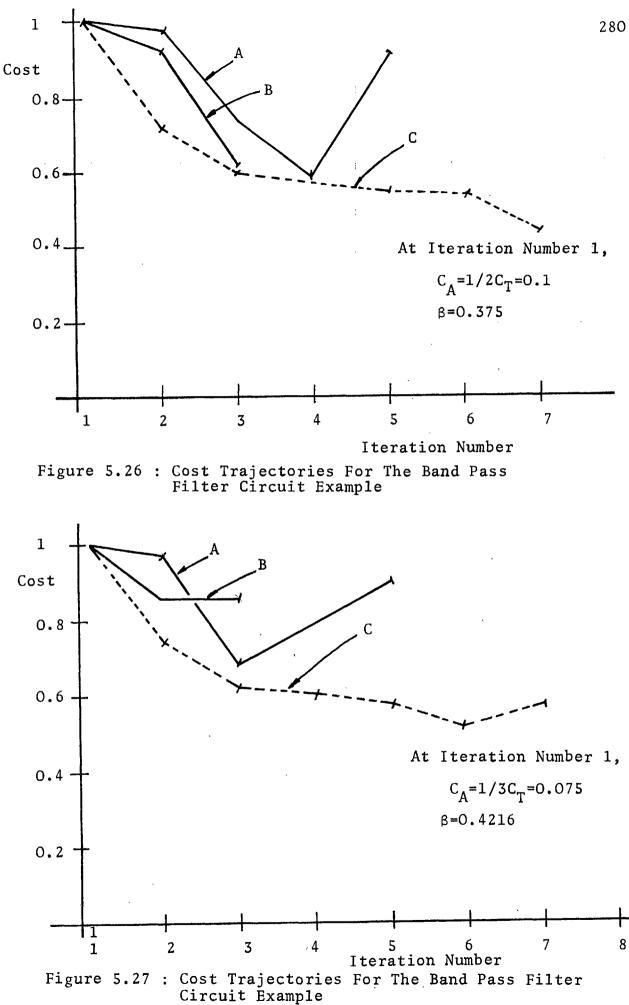

| Fig. | 5.26  | ** **                                    | 11              | 11                 | <b>11</b>         | 11              |                  | 280 |

| Fig. | 5.27  | 11 11                                    | 11              | ŤŤ                 | **                | **              | **               | 280 |

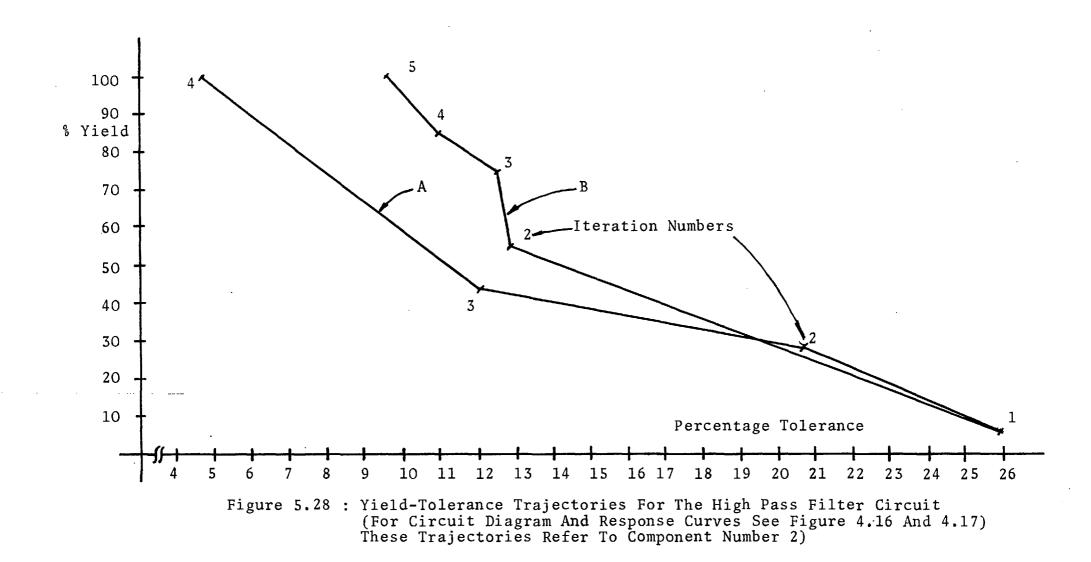

| Fig. | 5.28  | Yield toler<br>pass filter               | ance t<br>circu | rajecto<br>it (Com | ries fo<br>ponent | or the<br>Numbe | e high<br>er 2). | 281 |

| Fig. | 5.29  | ** **                                    | 11              | "(                 | 11                | **              | 3).              | 282 |

| Fig. | 5.30  | 11 11                                    | **              | "(                 | 11                | **              | 4).              | 283 |

| Fig. | 5.31  | 11 11                                    | 11              | "(                 | **                | **              | 6).              | 284 |

| Fig. | 5.32  | 17 11                                    | 11              | "(                 | 11                | 11              | 7).              | 285 |

| Fig. | 5.33  | 11 II                                    | 11              | "(                 | 11                | 11              | 8).              | 286 |

| Fig. | 5.34  | tt . ft                                  | **              | "(                 | **                | 11              | 10).             | 287 |

| Fig. | 5.35  | Cost trajec<br>circuit exa               |                 | for th             | e high            | pass            | filter           | 288 |

| Fig. | 5.36  | 17 71                                    | **              | **                 | 11                | **              |                  | 288 |

| Fig. | 6.1   | Diagram sho<br>correspondi               |                 |                    |                   |                 |                  | 310 |

Diagram showing the relationship between corresponding points of successive iterates.

.

PAGE

LIST OF. TABLES

|                |             |                                                                                                                                                                                                                                          | PAGE |

|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table          | 1 <b>.1</b> | Typical tolerances and temperature<br>coefficients of component parameters<br>in integrated circuits.                                                                                                                                    | 49   |

| Table          | 2.1         | A summary of the main contributions<br>in the field of tolerance assignment and<br>design centering.                                                                                                                                     | 86   |

| Tab <b>le</b>  | 4.1         | Performance constraints for the wide-<br>band amplifier circuit example.                                                                                                                                                                 | 186  |

| Table          | 4.2         | Summary of results of the application<br>of the Pattern search strategy for<br>the wide band amplifier circuit example.                                                                                                                  | 187  |

| T <b>abl</b> e | 4.3         | Summary of a set of results demonstrating<br>the efficacy of the common points scheme<br>and a comparison with the correlated<br>sampling scheme.                                                                                        | 188  |

| Table          | 4.4         | Component values for the various iterations<br>of the statistical exploration - design<br>centering run summarised in figure 4.18.                                                                                                       | 189  |

| Table          | 4.5         | Component values for the various iterations<br>of the statistical exploration design-<br>centering run summarised in figure 4.19.                                                                                                        | 190  |

| Table          | 4.6         | Component values for the various iterations<br>of the statistical exploration design<br>centering run summarised in figure 4.20.                                                                                                         | 191  |

| Table          | 4.7         | Component values for the various iterations<br>of the statistical exploration - design<br>centering run summarised in figure 4.22.                                                                                                       | 192  |

| Table          | 4.8         | Gain specifications, component nominal<br>values, and tolerances for the high<br>frequency amplifier cricuit example.                                                                                                                    | 193  |

| Table          | 4.9         | A summary of typical results for six<br>circuit examples showing that the number<br>of iterations performed (until no further/<br>in yield accrue), using the statistical<br>exploration method is independent of<br>the dimensionality. | 195  |

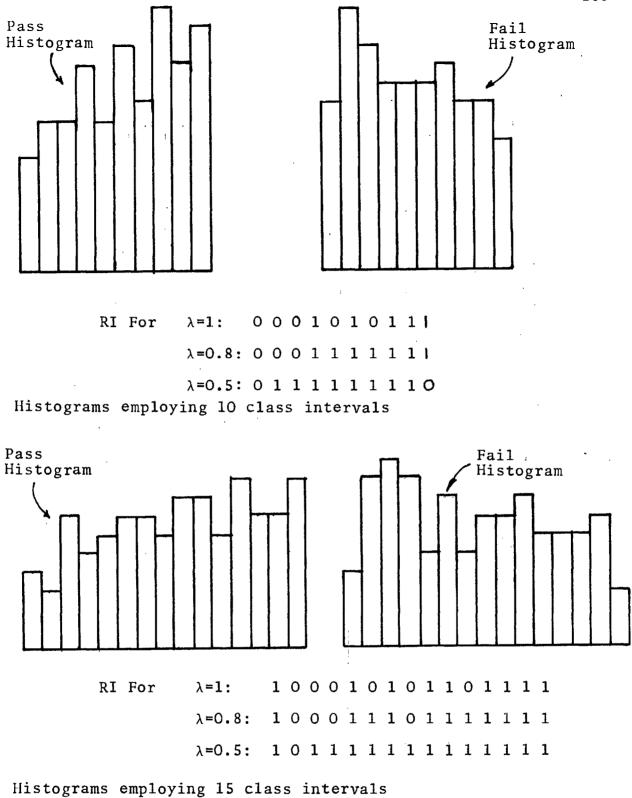

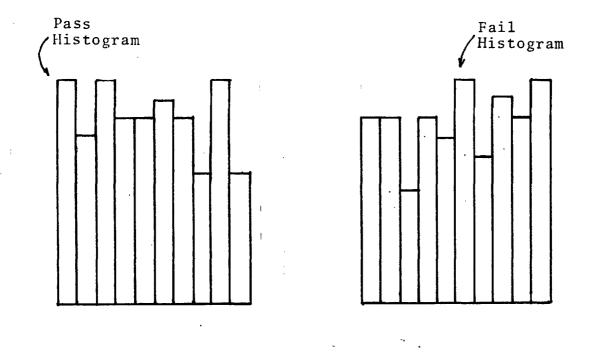

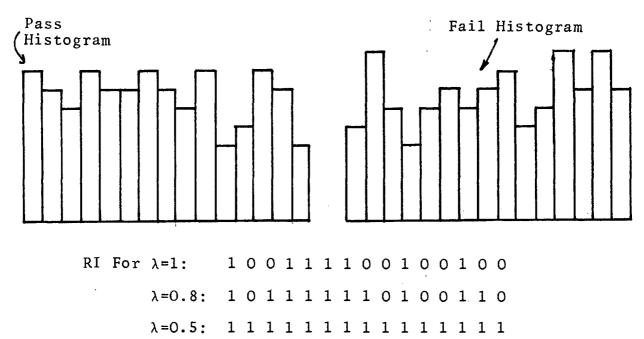

| Table          | 5.1         | Table showing the variation with number<br>of class intervals, of the estimated<br>yield sensitivity and sensitivity<br>ranking of individual components for<br>a low yield.                                                             | 251  |

•

.

15

Х

- Table 5.2 Table showing the variation with number 252 of class intervals, of the estimated yield sensitivity and sensitivity ranking of individual components for an intermediate yield value.

- Table 5.3 Table showing the variation with number 253 of class intervals, of the estimated yield sensitivity and sensitivity ranking of individual components for a high yield.

#### STATEMENT OF ORIGINALITY

1

As far as the author is aware, the opinions and techniques presented in this thesis are his own unless otherwise acknowledged by making specific reference. The main contributions are deemed to be the following:

1. The proposal and implementation of an iterative, small sample, Monte Carlo based, statistical method (called MYOSE) for design centering, and its verification for practical circuit examples (chapter 4). This includes the proposal of specific criteria for choosing a direction of search and step size (to move the design centre to improve yield) based on results obtained in Monte Carlo analysis.

In addition, in the case where only certain discrete values for the design centers may be available, the demonstration of the efficacy of a procedure for rounding of the optimum continuous solution to the nearest discrete solutions.

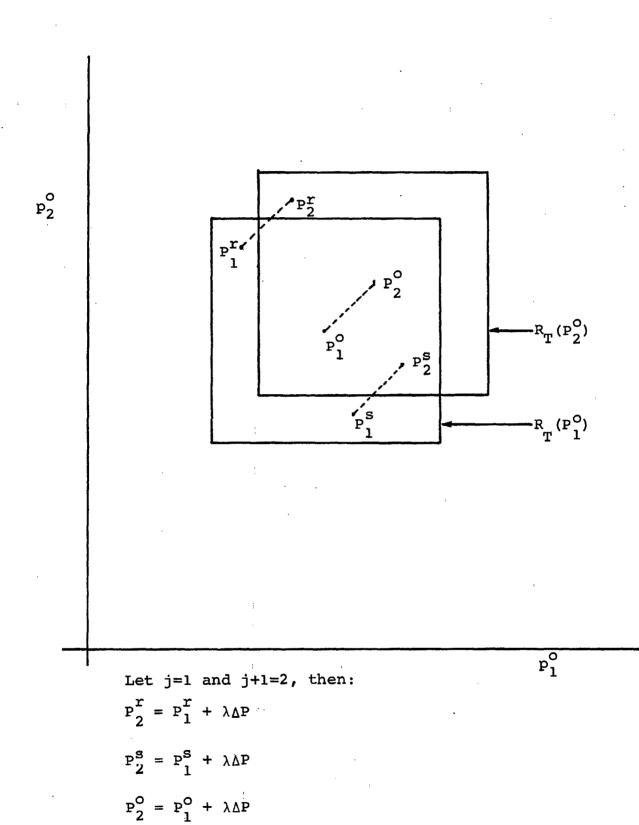

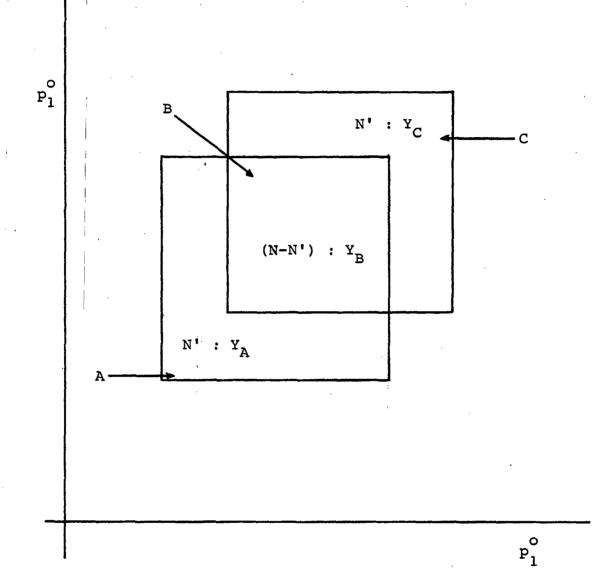

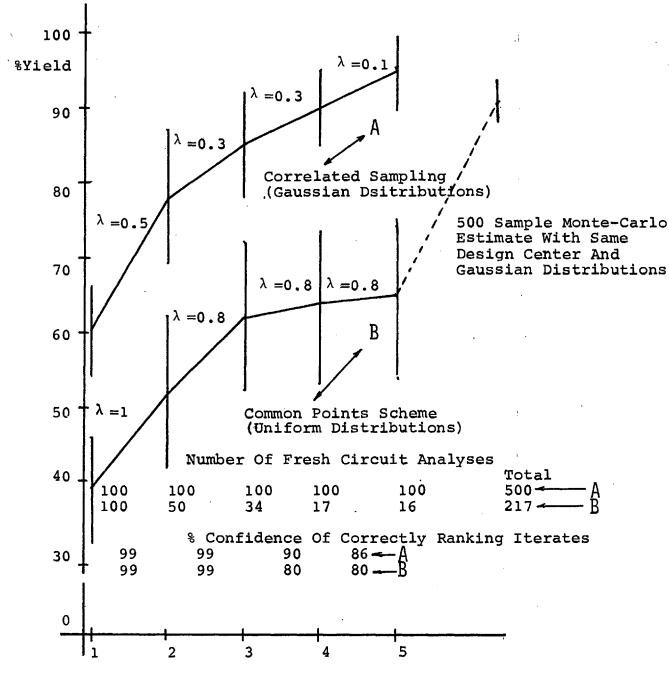

2. The proposal and incorporation in MYOSE (chapter 4) of a special sampling scheme (called the common points scheme) to reduce computational cost by re-employing both for design centering and yield estimation, at current iterations, circuit analyses performed at previous iterations. In addition the demonstration of the added efficiency of this sampling scheme for purposes of ranking yield estimates when their confidence intervals overlap, and a practical comparison of the common points scheme with a standard sampling scheme, called correlated sampling /1/.

3. A practical assessment of an existing Monte Carlo based, statistical method of tolerance assignment, TOLERATE /2/ (chapter 5). The proposal and implementation of a more effective technique, called PERTOL. This includes the proposal of specific criteria for choosing nominals and tolerances on the basis of results obtained in Monte Carlo analysis. In addition a practical comparison of the two methods when applied to particular circuit examples.

4. The proposal and implementation of a geometrical technique (called INDENTATION) for testing the worst case feasibility (i.e. 100% yield) of tolerance solutions; as part of a general branch and bound method /4/ for tolerance assignment and design centering for the situations where only discrete values of tolerances and nominals may be available (chapter 3). This includes a demonstration of the applicability of the method for a particular circuit example.

5. A critical review and classification of existing methods for tolerance assignment and design centering.(chapter 2).

6. A review of specific problems and techniques in the general field of statistical circuit design. (chapter 1).

7. An identification of the outstanding problems in the field of statistical design of electrical circuits, and proposals for future research in this area in the light of the contributions in this thesis. (chapter 6).

### CHAPTER 1 - STATISTICAL CIRCUIT DESIGN - THE SCENARIO

- 1.1 Introduction.

- 1.2 Notation and terminology.

- 1.3 Statistical analysis.

- 1.3.1 Monte Carlo analysis.

- 1.3.2 The method of moments.

- 1.4 Parameter value distributions.

1.4.1 Discrete components.

1.4.2 Integrated circuits components.

- 1.5 Statistical circuit design some scenarios.

- 1.5.1 Tolerance assignment and design centering.

- 1.5.2 Choice of performance specifications.

- (a) Specification sensitivity.

- (b) System specification.

1.5.3 Specification of manufacturing tests.

- (a) Go-no Go testing.

- (b) Accounting for environmantal effects in factory testing.

- (c) Selection of testing accuracy.

- 1.6 Summary.

#### CHAPTER 1

#### STATISTICAL CIRCUIT DESIGN - THE SCENARIO

#### 1.1 INTRODUCTION

The increasing degree of reliance placed on computer aids by circuit and systems designers may be traced to two broad trends. Firstly, the availability in increasing volume of progressively cheaper and more powerful computing facilities. Concomitant with this trend has been the discovery and development of numerous algorithms and programs  $/5/^{\alpha}$ addressed to the solution of various problems in the design and manufacture of electrical circuits and systems. Secondly, there has been a proliferation in the range and complexity of available devices and circuits, such as integrated circuits. For these, some of the traditional methods of approximate modelling and laboratory simulation and experimentation (e.g. breadboarding) are inadequate.

Three broad areas of engineering activity for which computer aids are available may be discerned. Firstly, in circuit design, where the principal aids are circuit simulators. These comprise facilities for describing to the computer program, the topology of the circuit, the component types and their parameter values. The program employs appropriate mathematical models of the electrical behaviour of the relevant components, and facilitates numerical simulation to study and change the circuit

$<sup>^{\</sup>alpha}$ An extensive review of available circuit analysis packages is reported by Bowers and Zobriest et al /6/.

to improve its performance. Secondly, computer aids are essential in the area of component layout, the routing of interconnections, the drafting of artwork for photolithographic processes etc, in the manufacture of many types of electrical circuits, especially integrated circuits /7/. Thirdly, with the increased complexity of performance of circuits and systems, and for greater cost effectiveness, computer aids are increasingly being brought to the factory floor to aid activities such as testing, verifying performance and detecting faults in manufactured circuits and systems /8/.

Therefore in some specific areas of application, computers help perform traditional design tasks more efficiently, and in others design activities are introduced which could only be performed crudely and with a large degree of approximation . if at all by non computer aided methods. One such area of application in the field of circuit design, is statistical design. The most common application of computers in circuit design is in performing analyses of circuit behaviour to compute various responses such as voltages, currents, power gains, time delays, sensitivities etc. This information is then used either manually by the designer, or automatically by the computer program, to make adjustments to the proposed circuit, to improve its performance with respect to appropriate criteria. Here the designer is experimenting with the nominal circuit. However, when a circuit is to be manufactured in large numbers, the designer must analyse and design for statistical spreads in the performance of nominally identical circuits, arising from statistical

spreads encountered in values of the parameters of their constituent components. This latter design activity is called statistical design.

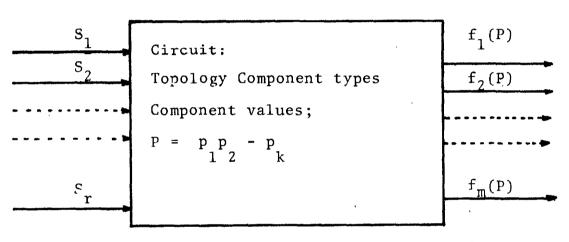

For illustration consider the representation of figure 1.1. For a particular set of stimuli  $S = S_1 \dots S_r$ , the circuit responses  $f_1 f_2 \dots f_m$  are functions of the component parameters  $P = p_1 p_2 \dots p_k$ , i.e.  $f_j = f_j (p_1 \dots p_k);$ j=1 .... m. For example, for a frequency selective circuit, the parameters may be values of the resistances, capacitances and inductances, while the  $f_i$  (.) may be responses such as insertion loss, group delay etc, at a number of frequencies. Uncertainty is associated with the values of the component parameters and thus the values of the response functions, in the following sense. If a number of nominally identical circuits are to be manufactured (assembled or fabricated) from their constituent components, then variations in the processes of manufacture of the components cause the values of their parameters to be statistically distributed. Consequently, the response values of the manufactured circuits also display variation from one circuit sample to another. In addition the response of a particular circuit whose component parameters have particular values  $p_1 * p_2 * \dots p_k *$  at the time of manufacture, will experience a non-deterministic drift in response, as a result of drift in the values of these component parameters due to factors such as fluctuations in the environmental conditions of service (e.g. temperature or humidity) or component ageing.

The spread in performance may be such that some of the manufactured circuits fail to meet the required limits on response values specified by the customer. Therefore, yield<sup> $\alpha$ </sup>,<sup> $\beta$ </sup> will be less than 1 (100%). The failing circuits need then be discarded or repaired, hence incurring additional The extent of spread of response may be reduced and cost. hence the yield increased by employing more precise (i.e. subject to a smaller extent of spread) components. However. precise components are more expensive. Therefore, the circuit designer may seek a compromise between yield and precision (generally called tolerance) of component parameters to minimize overall cost. This particular design problem is called tolerance assignment. On the other hand yield may be increased by re-assigning the nominal values of the component parameters, while their tolerances remain fixed. This latter procedure is called design centering. In the general case a combined procedure for reassigning both tolerances and nominals will lead to the design of the most cost effective circuits.

Numerous algorithms have been proposed for various formulations of the design centering and tolerance assignment problems. The work reported in this thesis is addressed to a critical

<sup>&</sup>lt;sup>Q</sup>Yield is that proportion of manufactured circuits whose response meets the limits specified by the customer. Yield will be formally defined in section 1.2.

<sup>&</sup>lt;sup>β</sup>From the point of view of yield, we shall only consider circuits which are assumed to be free from gross errors, such as wiring faults, mask misalignment, crystal defects etc.

survey of the nature and limitations of existing methods, and the proposal and investigation of new and improved methods. In chapter two several formulations of these design problems are presented, together with a classification and critical review of proposed solution techniques. The next three chapters then report the proposal, implementation and general investigation of a number of new algorithms. Finally, in chapter six, we outline areas of future research in this field.

The aims of this chapter are two fold. Firstly, we introduce a consistent terminology and notation to be then used throughout this thesis. In addition the expected parameter distributions and methods of statistical analysis are briefly reviewed. Secondly, we note that tolerance assignment and design centering are particular instances of statistical design problems. Therefore the latter half of this chapter discusses various scenarios to illustrate the wider scope of statistical design.

#### 1.2 NOTATION AND TERMINOLOGY

Let  $p \triangleq p_1 p_2 \dots p_K$  be a general set of values for the component parameters of the circuit in question. P can be thought of as a point in a K-dimensional space (called the input space). The variability of P can be represented by a K-dimensional probability density function (p.d.f.), denoted by  $\phi(P)$ . Therefore the following equation holds:

$$\int_{-\infty}^{\infty} \cdots \int_{-\infty}^{\infty} \phi(\mathbf{P}) \, d\mathbf{p}_1 \cdots d\mathbf{p}_K = 1 \qquad 1.1$$

In practice the range of variation of the individual parameters

will be truncated i.e.

$$\emptyset(\mathbf{P}) = 0 \text{ for } \underline{\mathbf{p}}_j \leq \underline{\mathbf{p}}_j \leq \overline{\mathbf{p}}_j \quad j=1 \dots K \qquad 1.2$$

Where  $\underline{p}_j$  and  $\overline{p}_j$  are constants, respectively termed the lower limit and the upper limit of variation of the jth parameter. Also consider the vector of tolerances

$$T \triangleq t_1 t_2 \dots t_K$$

where  $t_i = (\overline{p}_i - \underline{p}_i)/2$  i=1 .... K

and the vector of nominal values:

$P^{o} \triangleq p_{1}^{o} \cdots p_{K}^{o}$  where,  $p_{i}^{o} = (\overline{p}_{i} + \underline{p}_{i})/2$

Equation 1.1 may then be rewritten as

$$p_{K}^{o} + t_{K} \qquad p_{i}^{o} + t_{1}$$

$$\int \cdots \int \qquad \oint (P) dp_{1} dp_{2} dp_{K} \approx 1 \quad 1.3$$

$$p_{K}^{o} - t_{K} \qquad p_{i}^{o} - t_{1}$$

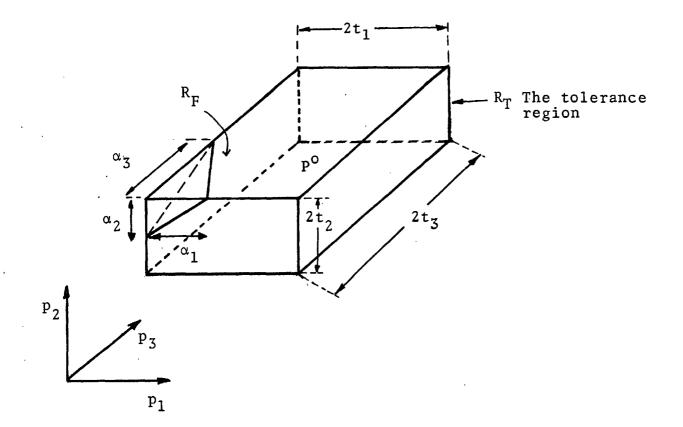

Relation (1.2) defines a region in the input space, called the tolerance region, and denoted  $R_{_{T}}$ , such that

$$P \in R_{m} \text{ if } \emptyset(P) > 0 \qquad 1.4$$

Clearly  $R_T$  is a hyper rectangle, with center  $P^0$  and sides of length  $2t_i$ , i=1 .... K. A geometrical representation is given in figure 1.2. Also we denote by  $f_i(P)$ , i=1 ... m the response functions of the circuit. The variability of these responses may be modelled in terms of another joint probability density function, which is denoted as  $\Omega(f_1f_2 \dots f_m)$ . In addition we denote by  $\Omega_i(f_i)$  the particular p.d.f. of the ith performance function. The problems of statistical analysis involve computation of various parameters of the function  $\Omega(.)$ . For example the customer for whom the circuit is manufactured may require its response to be constrained such that

$$\underline{f}_{i} \leq f_{i} \quad (P) \leq \overline{f}_{i} \quad i=1 \dots m \qquad 1.5$$

where  $\underline{f}_i$  and  $\overline{f}_i$  are constants. The proportion of manufactured circuits which meet condition 1.5 is termed the production yield, and may be written as the multi-dimensional integral

Yield =

$$\begin{cases} \mathbf{f}_{m} & \mathbf{f}_{1} \\ \int \cdots & \int \Omega(\mathbf{f}_{1} & \cdots & \mathbf{f}_{m}) d\mathbf{f}_{1} & \cdots & d\mathbf{f}_{m} \\ \mathbf{f}_{m} & \mathbf{f}_{1} \end{cases}$$

1.6

Alternately we may define a testing function g(P) reflecting the acceptance or rejection of a circuit, such that g(P) = 1 if  $\underline{f_i} \leq f_i$   $(P) \leq \overline{f_i}$   $i = 1 \dots m$  1.7 and = 0 otherwise.

Yield is then the following expectation.

Yield =  $\langle g(P) \rangle = \int \dots \int g(P) \phi(P) dP_1 \dots dP_K$  1.8  $p_K^o - t_K p_1^o - t_K$

Relation (1.7) allows definition of another region in the input space, the region of acceptability,  $R_A$ , such that

$$P \in R_A$$

if  $g(P) = 1$  1.9

Clearly  $R_A$  represents all those combinations of component values which result in acceptable circuits. With the definition of the tolerance region  $R_T$  and the region of

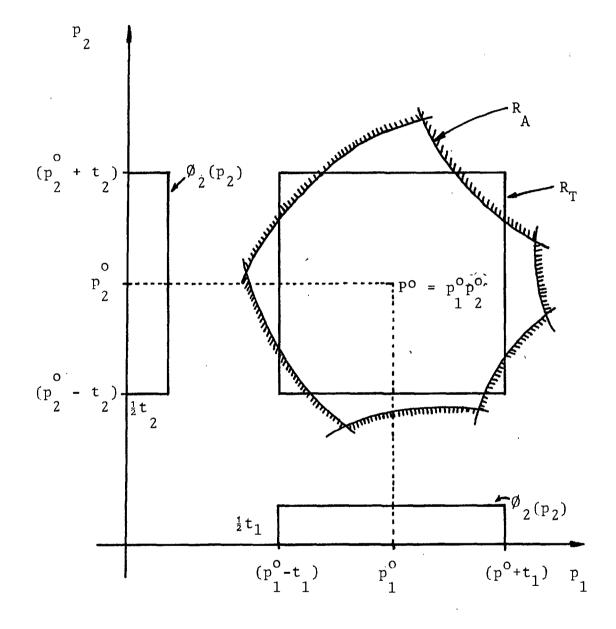

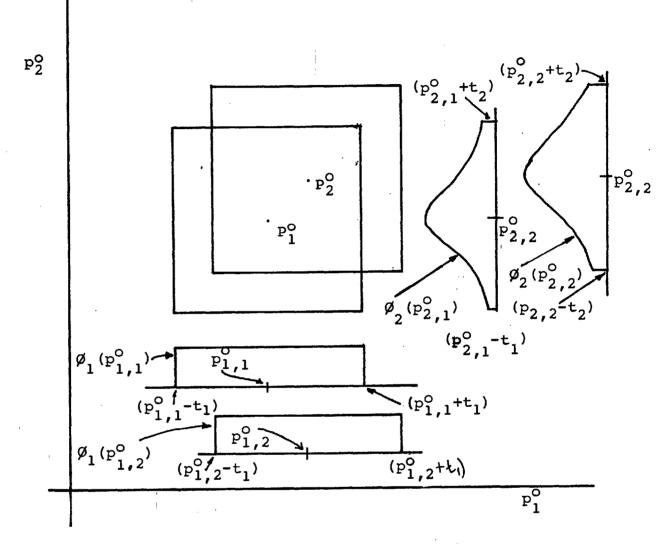

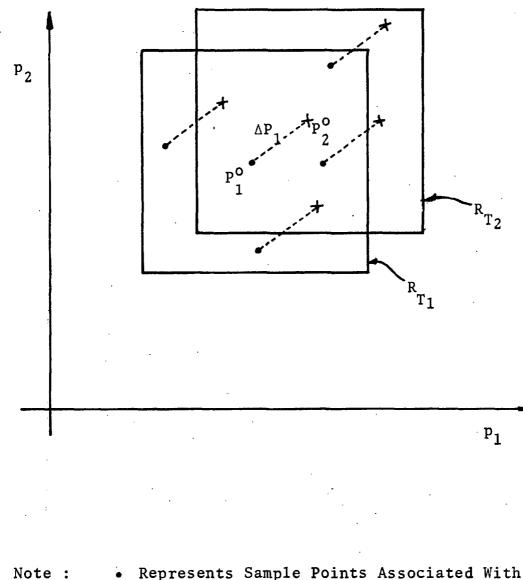

acceptability  $R_A$  it is useful to consider a geometrical interpretation of yield, as represented in figure 1.2. Here we consider a 2 dimensional example (K=2), with nominal  $P^0 = p_1^0$ ,  $p_2^0$  and tolerances  $T = t_1$ ,  $t_2$ . Initially we assume that the p.d.f.  $\emptyset(P)$  is bivariate uniform and the parameters are statistically independent /9, chapter 5/, i.e.  $\emptyset(P) = \emptyset_1(p_1) \cdot \emptyset_2(p_2)$

and

$$\emptyset_{1}(p_{1}) \begin{cases} = \frac{1}{2t_{1}} & \text{for } (p_{1}^{o} - t_{1}) \le p_{1} \le (p_{1}^{o} + t_{1}) \\ = 0 & \text{otherwise} \end{cases}$$

1.10

and

$$\phi_2(p_2) \begin{cases} = \frac{1}{2t_2} \text{ for } (p_2^{\circ} - t_2) \leq p_2 \leq (p_2^{\circ} + t_2) \\ = 0 \text{ otherwise} \end{cases}$$

Then, yield is the ratio of the areas (in the general case volumes) of the regions  $(R_T \cap R_A)$  and  $R_T$ . That is;

Yield =

$$V(R_T n_A) / V(R_T)$$

. 1.11

Where V(.) indicates volume. For the more general case the parameter values may be statistically dependent (correlated) and the individual probability density functions may be other than uniform. In that case the function  $\emptyset(.)$  may be taken to represent a weighting of the points of  $R_T$ . Hence the volumes in expression 1.11 should now be interpreted as weighted volumes.

### 1.3 STATISTICAL ANALYSIS

Statistical analysis involves computation of various parameters of the output probability density function  $\Omega(.)$ .

For example, for a particular set of nominal values, tolerances and input p.d.f., it is very important to estimate the expected production yield. For the present discussion, it is assumed; (i) that for a set of values P\* for the K parameters of the circuit in question, it is possible to evaluate the m response functions, and (ii) the form of the input probability density function is known. In practice the first assumption is true for most circuits of interest, although evaluation of circuit responses may involve considerable computational expense. However, the statistical distribution of component parameters is not generally known. In some situations, namely discrete components, a simple choice (such as Uniform or Gaussian p.d.f.) may suffice. However, for integrated circuits, the function  $\emptyset(.)$  may be very complex. The question of suitable choice for  $\phi(.)$  is discussed later.

A thorough review of different methods of statistical analysis is reported by Tahim /10/. We shall re-iterate the main features of two methods, namely, Monte Carlo analysis and the method of moments. These are emphasised here because of their importance as integral parts of certain statistical design methods, to be discussed in this thesis. Monte Carlo analysis is a direct and general method, applicable to all circuit problems. However, it is computationally very expensive and may be prohibitively so in many cases. On the other hand the method of moments, although computationally cheaper, involves considerable approximation. However, the approximations may not hold in all situations. Nevertheless, the method of moments is useful in several statistical design methods.

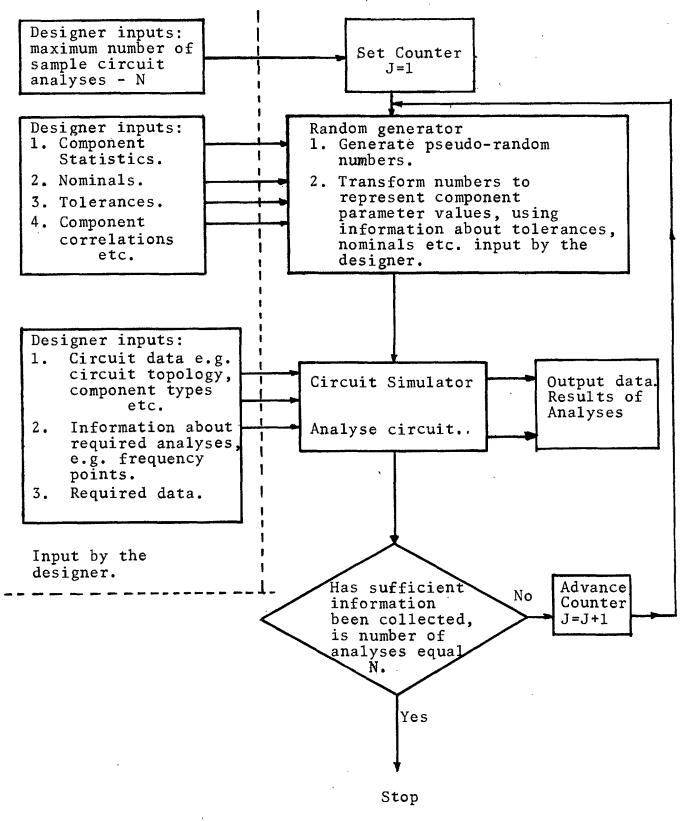

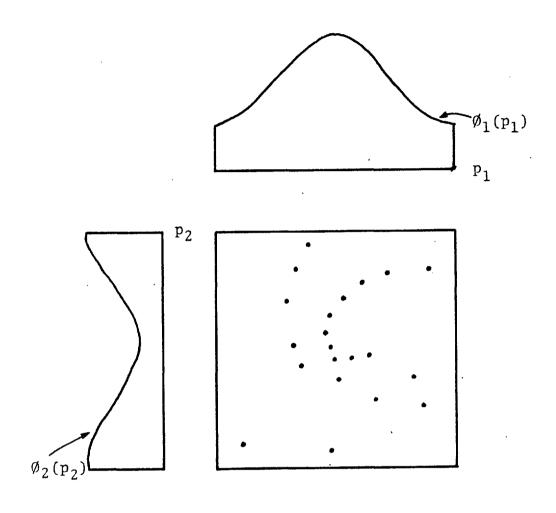

#### 1.3.1 MONTE CARLO ANALYSIS

In this method, illustrated in figure 1.3, a number N:  $P_1 P_2 \dots P_N$ , of sets of sample circuit values are generated. These values are obtained by suitably transforming pseudo random numbers, so that they are distributed according to the relevant p.d.f.  $\emptyset(.)$ . This is illustrated for a two dimensional example in figure 1.4. The sample circuits are analysed and a representation of the performance distribution is obtained. To illustrate its salient features, the use of the method for estimating yield is discussed here.

The Monte Carlo method simulates the process which takes place in a circuit production run. Circuits are assembled using components randomly picked from particular bins $^{\alpha}$ . In the equivalent computer exercise, random numbers are generated with a uniform distribution, in the interval 0 to 1 and are then transformed (this is illustrated for one component in figure 1.5) to satisfy the required p.d.f. Each set of component parameter values, representing a manufactured circuit, is analysed and the corresponding values of the performance functions are obtained. Each analysed circuit is assigned to one of two mutually exclusive classes namely acceptable and reject. An acceptable circuit is one which meets all performance requirements such as relation 1.5. A reject circuit is one which fails at least one requirement. The process is repeated a number of times and yield is estimated as follows.

$<sup>^{\</sup>alpha}$ Although for integrated circuits, individual components may not be handled, the analogy still holds.

If, of N analysed circuits NA are found to be acceptable then  $\tilde{Y} = NA/N$  is an unbiased estimate<sup> $\alpha$ </sup> of the true yield Y.  $\tilde{Y}$  is a random variable, since if the experiment were to be repeated with a different set of N sample circuits, a different value would be obtained for  $\tilde{Y}$ . It is appropriate to consider the accuracy of the estimate  $\tilde{Y}$ , and its dependence on the number of circuits analysed. Specifically, it is required to construct confidence intervals, so that we can make statements like

$$(\tilde{Y}-C) < Y < (\tilde{Y}+C)$$

1.12

with a particular degree of confidence. Here, C denotes some constant called the confidence interval.

Each circuit analysis and test for compliance with performance requirements may be taken to be a Bernoulli<sup> $\beta$ </sup> trial. If the probability that a circuit with randomly selected component values is acceptable, is Y, then the probability of exactly NA acceptable circuits in N trials is

$$F(NA) = \frac{N!}{(N-NA)! NA!} Y^{NA} (1-Y)^{N-NA}$$

1.13

The function F(NA) is a Binomial probability density function (p.d.f.) with mean and variance given by:

$\mu = NY$

1.14

$^{\alpha}$ In statistics an unbiased estimator is a random variable, whose expected value is the parameter being estimated. An unbiased estimate is an estimate provided by such an estimator. /9, chapter 7, page 230).

<sup> $\beta$ </sup>A Bernoulli trial is a random experiment which can only have one of two outcomes, e.g. the tossing of a coin.

$$\sigma^2 = NY(1-Y)$$

1.15

When N is reasonably large, the Binomial distribution may be approximated by a Gaussian distribution. Therefore, the p.d.f. of the random variable  $\tilde{Y}$  may be written as

$$F(\widetilde{Y}) = \frac{1}{\sigma_{\widetilde{Y}}\sqrt{2\pi}} \quad \exp - \frac{1}{2} \quad \frac{(\widetilde{Y} - \mu_{Y})^{2}}{\sigma_{\widetilde{Y}}^{2}} \qquad 1.16$$

where the mean  $\mu_{Y}$  and variance  $\sigma_{Y}^{2}$  are given by:

$\mu_{\rm Y} = {\rm Y} \qquad \qquad 1.17$

and

and

$$\sigma_{\widetilde{Y}}^2 = \frac{\widetilde{Y}(1-\widetilde{Y})}{N}$$

1.18

Thence the confidence interval for the Yield estimate Y can be constructed as follows. The probability of  $\tilde{Y}$  falling in the interval  $(\tilde{Y} - \varepsilon \sigma_Y)$  to  $(\tilde{Y} + \varepsilon \sigma_Y)$  is the integral

$$\widetilde{Y} + \varepsilon \sigma_{\widetilde{Y}}$$

$\int F(\widetilde{Y}) dY$  1.19

$\widetilde{Y} - \varepsilon \sigma_{\widetilde{Y}}$

$$= \frac{1}{\sqrt{2\pi}} \int_{-\epsilon}^{\epsilon} \exp \frac{-x^2}{2} dx \qquad 1.20$$

where  $x = \frac{\tilde{Y}-Y}{\sigma_{\tilde{Y}}}$  and  $\varepsilon$  is a constant.

The function F(.) is now Gaussian. The most commonly used value for  $\varepsilon$  is 2, leading to a probability of 0.95 that the true value of yield is between the limits  $(\tilde{Y}-2\alpha)$  and  $(\tilde{Y}+2\alpha)$ .

Clearly Monte Carlo analysis is a very general procedure and can accomodate any type of circuit (linear, non-linear etc) and any number and type of circuit response. However, the

repetitive analysis of sample circuits is computationally expensive. The total cost of a Monte Carlo analysis is roughly proportional to N, the number of sample circuits analysed. However, as embodied in equation 1.18 the accuracy of the resulting estimates is proportional to the inverse of the square root (i.e.  $1/\sqrt{N}$ ) of the number of analyses. Therefore to double the accuracy, N has to be increased four fold. For different values of yield, the dependence of the confidence interval on the sample size, is depicted in figure 1.6. The corresponding confidence level is 95% i.e. the probability of bracketing the true yield, in the appropriate confidence intervals is 0.95.

#### 1.3.2 THE METHOD OF MOMENTS

Whereas in the Monte Carlo method an empirical characterization of the output p.d.f.  $\Omega(.)$  is constructed, here we consider approximation to  $\Omega(.)$  constructed from a knowledge of the moments of the input p.d.f.  $\emptyset(.)$  and an approximation of the performance function in terms of the input parameters.

Each of the performance functions  $f_i(p_i)$ ; i=1 .... m, may be expanded in Taylor series /11, Sec.4.10 / to give analytic expressions for these functions in the vicinity of the nominal point P<sup>0</sup>. i.e.

$$f_{i}(p_{1} \dots p_{K}) = f_{i}(P^{0}) + \sum_{r=1}^{K} \frac{\partial f_{i}}{\partial p_{r}} \Delta p_{r} + \sum_{r=1}^{K} \sum_{s=1}^{K} \Delta p_{r} \frac{\partial^{2} f_{i}}{\partial p_{r} \partial p_{s}} \Delta p_{s} + \dots 1.21$$

where the  $\Delta p_{i}$  are deviations from the nominal values,

i.e.  $\Delta p_{i} = p_{i} - p_{i}^{0}$ .

Neglecting second and higher order terms in 1.21, we get 1.22

$$f_i(p_1 \dots p_K) = f_i(p^o) + \sum_{r=1}^K \frac{\partial f_i}{\partial p_r} \Delta p_r$$

1.22

We may then easily obtain the following expression relating the variances  $\sigma^2$ ; i=1 ... K, of the input parameters to  $p_i$ the variances  $\sigma^2_j$ ; j=1 ... m of the performance functions, as:  $f_j$

$$\sigma_{\mathbf{f}_{j}}^{2} = \sum_{i=1}^{K} \frac{\partial \mathbf{f}_{j}}{\partial p_{i}} \sigma_{p_{i}}^{2} + 2 \sum_{r=1}^{K} \sum_{s=1}^{K} \frac{\partial \mathbf{f}_{j}}{\partial p_{r}} \frac{\partial \mathbf{f}_{j}}{\partial p_{s}} \operatorname{COV}(p_{r}, p_{s}) \dots 1.23$$

Where  $COV(p_r, p_s)$  is the covariance between parameters  $p_r$  and  $p_s$ . Further the mean value of  $f_i$ , will clearly be  $f_i(p^0)$ . Expressions equivalent to 1.23 may be obtained for all m performance function /3, chapter 3/.

According to the central limit theorem /9, chapter 5/, the joint probability density function of the performance functions will be approximately m-variate Gaussian if several conditions are met /13, chapter 2-3/. These are; (a) the number of component parameters are large, (b) the variances of a few parameters are not much greater than those of all the others, (c) the individual parameter p.d.f.'s are symmetrical about the nominal values. The diagonal elements of the variance-covariance<sup> $\alpha$ </sup> matrix of  $\Omega(.)$  are given by expressions such as 1.20. Similar expressions may

<sup>&</sup>lt;sup> $\alpha$ </sup>For an m dimensional random variable, the variancecovariance matrix is an (m by m) symmetrical matrix. The elements s<sub>ij</sub> - i = 1 .... m, j = 1 .... m; are the covariances between component i and j of the random variable.

be obtained relating the covariances of different performance functions to the variances and covariances of the input p.d.fs. These form the non-diagonal elements of the variance covariance matrix of  $\Omega(.)$

Even such an approximation to  $\Omega(.)$  as a multivariate Gaussian p.d.f., presents formidable computational problems for obtaining yield, since it involves the evaluation of an m dimensional integral, where m may be large.

However, the Normal (Gaussian) approximation can effectively be used to derive bounds on the true value of yield. We first consider the notion of "partial yield". In all there will be m partial yields,  $Y_i$ ; i=1 ... m, where  $Y_i$  is the probability that a correctly manufactured circuit will meet the ith, performance requirement, i.e.

$$f_i = Probability (\underline{f}_i < f_i(P) < \overline{f}_i)$$

or the integral :

$$Y_{i} = \int_{f_{i}} \Omega_{i}(f_{i}) df_{i}$$

1.24

If all the performance functions were independent, i.e.  $\Omega(.)$  was the product

$$\Omega = \prod_{i=1}^{m} \Omega_{i} \qquad 1.25$$

then the overall yield Y, would be the product

$$Y = \prod_{i=1}^{m} Y_i$$

1.26

In practice 1.25 does not often hold, and 1.26 is replaced by the inequality 1.27.

$$Y > \prod_{i=1}^{m} Y_{i}$$

1.27

Hence, 1.27 provides a lower bound on the yield.

Evaluation of the  $Y_i$ , involves single dimensional integrations (expression 1.24). These may be easily performed, since the  $\Omega_i$  are assumed Gaussian with means and variances calculated from expressions such as 1.23. Tighter bounds on yield may be obtained as follows. Now the probability of occurrence of a reject circuit is the joint probability of occurrence of failure to meet at least one of the m performance requirements. Consider the following additional notation: Let  $x_j$  denote the condition that the jth performance requirements is met, i.e.

$$\underline{\mathbf{f}}_{j} \leq \mathbf{f}_{j}(\mathbf{P}) \leq \overline{\mathbf{f}}_{j}$$

1.28

and  $\overline{x}_j$  that the condition is not met. Then clearly  $Y_i = Pr(x_i)$ , where  $P_r(.)$  denotes probability.

Therefore we may write:

$$(1-Y) = P_r(\bar{x}_1 + \bar{x}_2 + \dots \bar{x}_m)$$

1.29

From elementary probability theory /9, chapter 2/, 1.29 may be rewritten as:  $(1-Y) = \{P_r(\overline{x}_1) + P_r(\overline{x}_2) + \dots + P_r(\overline{x}_m)\} +$  $\{Pr(\overline{x}_1\overline{x}_2) + Pr(\overline{x}_1\overline{x}_3) + \dots + Pr(\overline{x}_i\overline{x}_j) + Pr(\overline{x}_{m-1}, \overline{x}_m)\} + \dots + i \neq j$  $+ (-1) Pr(\overline{x}_1\overline{x}_2, \dots, \overline{x}_m) \qquad 1.30$  If we replace  $Pr(\overline{x}_i)$ ,  $Pr(\overline{x}_{ij})$  etc as follows.

$W_{j} = Pr(\overline{x}_{j})$   $W_{ij} = Pr(\overline{x}_{i}\overline{x}_{j})$ and  $W_{ijk} = Pr(\overline{x}_{i}\overline{x}_{j}\overline{x}_{k})$

Then (1.30) may be rewritten as

$$(1-Y) = \sum_{j=1}^{m} W_{j} + \sum_{j=1}^{m-1} \sum_{k=j+1}^{m} W_{jk} - \sum_{j=1}^{m-2} \sum_{k=j+1}^{m-1} W_{jk\ell} + \dots 1.31$$

Returning to equation 1.30, we note that the right hand side is the sum of  $(2^{m}-1)$  bracketed addends of non increasing numerical value with alternating signs. According to the Benferoni inequality procedure /3, chapter 3/, if we truncate the right hand side of 1.30, and use only the first K bracketed addends, then the value of the left hand side will be bounded by the first (K-1) and the first K addends. We may use this to obtain closer bounds on yield than 1.27. Equation 1.31 shows three addends. Thus the following bound on yield is obtained:

$$1 - \sum_{j=1}^{m} W_{j} + \sum_{j=1}^{m-1} \sum_{k=j+1}^{m} W_{jk} - \sum_{j=1}^{m-2} \sum_{k=j+1}^{m-1} M_{kk} \le Y \le 1 - \sum_{j=1}^{m} W_{j} + \sum_{j=1}^{m-1} \sum_{k=j+1}^{m} W_{jk}$$

$$1 - \sum_{j=1}^{m} W_{j} + \sum_{j=1}^{m-1} \sum_{k=j+1}^{m} W_{jk}$$

$$1.32$$

Clearly,  $Y_i = 1 - W_i$  etc. Hence evaluation of the  $W_i$ , the  $W_{ij}$  and the  $W_{ijk}$ , involve the integration of univariate, multivariate and trivariate

Gaussian probability density functions respectively e.g.

$$W_{ijk} = \int_{i}^{f_{i}} \int_{j}^{f_{j}} \int_{k}^{f_{k}} \Omega_{i} \Omega_{j} \Omega_{k} df_{i} df_{j} df_{k} etc.$$

The procedure for obtaining yield bounds, outlined above is computationally cheaper than Monte Carlo analysis. However, it relies on several series of approximations and assumptions and is therefore less general and less reliable.

## 1.4 PARAMETER VALUE DISTRIBUTIONS

To perform effective statistical analysis, it is necessary to have knowledge of the statistical distributions of the component parameter values. Distinct differences exist in the distributions encountered in the parameters of components in discrete circuits and those in integrated circuits.

#### 1.4.1 DISCRETE COMPONENTS

For discrete passive elements, i.e. resistors, capacitors, and inductors, it is adequate to determine the nominal values and form of the individual parameter p.d.f. The parameters of the various components in a circuit will be statistically independent. Therefore, the K dimensional joint p.d.f.  $\emptyset(.)$ , may be written as the product of the individual parameter p.d.fs. i.e.

$$\emptyset(P) = \prod_{i=1}^{K} \emptyset_{i}(P_{i})$$

1.33

The component manufacturer may impose tolerance limits on a batch of components by removing out of tolerance components. It is therefore convenient to write 1.33 as

$$\emptyset(P, P^{0}, T) = \prod_{i=1}^{K} \emptyset_{i}(p_{i}^{0}, t_{i}^{0}, p)$$

1.34

where as before  $P^{O}$  and T are respectively, the nominal value and tolerance vectors. Further we expect

$$\emptyset_{i}(p_{i},p_{i}^{0},t_{i}) = 0$$

for  $(p_{i}^{0}-t_{i}) > p_{i}$  1.35

or  $(p_{i}^{0}+t_{i}) < p_{i}$

The form of the p.d.f. for most manufactured components is found to be Gaussian (figure 1.7a), when they leave the production line /12, chapter 6/. This is especially the case if a manufacturer mixes nominally identical components from batches produced at different times. Manufacturers often select components from the middle of the distribution to sell as precision components. Therefore for particulr nominals and tolerances, the distributions encountered by the component purchaser may be of the form shown in figure 1.7b, and 1.7c. For some types of components, e.g. thin film resistors, the probability density function is often found to be markedly skewed, as shown in figure 1.8.

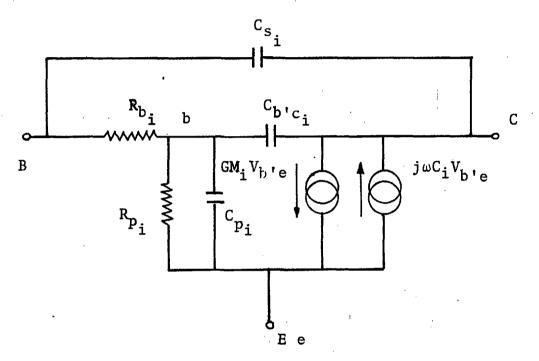

For purposes of circuit analysis discrete active circuits are represented by equivalent circuits. For example, the hybrid I model, which is applicable when the transistor is used in linear a.c. applications. The different parameters of the equivalent circuit will then be inter-related and their statistical distributions correlated. The interrelations and correlations may be characterized from a knowledge of the physics of the device or more commonly from measurements made on a representative number of sample components.

## 1.4.2 INTEGRATED CIRCUIT COMPONENTS

The values of the parameters of the components of an integrated circuit are determined by the physical properties (e.g. material properties such as mobility, doping levels, diffusion constants etc) of the material of which the component is made and the geometrical dimensions of its layers. In general parameter tolerances in integrated circuits are larger than those encountered in discrete components, and there are distinct differences in the forms of the distributions encountered. For example, the values of the resistances depend upon sheet resistivity. Uncertainty in the manufacturing processes results in a tolerance of a few percent, on the value of the sheet resistivity from slice to slice. However, the variation of resistivity in circuits on one slice will be very small. Further this variation will be very gradual over the slice. Therefore although large tolerances may be associated with individual resistors, the statistical distribution of values of resistors in close proximity on single chips, will be correlated, thus reducing the overall tolerance effect. Therefore the designer of integrated circuits may exploit this fact by designing circuits whose performance depends upon ratios of resistances. Similarly the parameters of other components, such as the  $\beta$ values of transistors, will be correlated, especially when they are in close proximity. Such correlations must be characterized and taken into account when performing statistical analysis of integrated circuits.

Tolerances in the lateral dimensions of integrated components also cause considerable variation in parameter values. Inaccuracies may result from errors in layout or cutting of master drawings and in the photographic reduction processes. Further, inaccuracies may occur in positioning masks with respect to previous patterns. In general, such surface dimension tolerances will tend to increase towards the edge of a circuit. The uncertainty in the definition of the edges may be reduced by making the sizes of the components larger.

Generally the p.d.fs encountered in integrated circuits will be continuous and for many parameters will approach a Gaussian form. However, for several important situations, the distributions will be skewed. For example a major source of error in a resistor will be its path width, and the chance of it being too narrow would be about twice the chance of it being too wide. Also the value of resistance for a particular length and depth is inversely proportional to the width. Therefore a  $\pm$  50% tolerance in width would result in a tolerance on resistance values from +100% to -33% with a marked skew towards the higher resistance values.

To summarize this discussion, typical tolerances of integrated circuit components are given in table 1.1 /12, chapter 6/.

## 1.5 STATISTICAL DESIGN - SOME SCENARIOS

Although in this thesis we are largely concerned with algorithms for tolerance assignment and design centering, many

other instances of statistical design problems may be identified. Therefore in this section we briefly examine some design scenarios. We commence however, with some comments on our specific problem (i.e. tolerance assignment) and introduce geometrical interpretations which will be useful for further exposition.

#### 1.5.1 TOLERANCE ASSIGNMENT AND DESIGN CENTERING

For discrete components, the parameter p.d.fs will be centered about the nominal value and be truncated at the tolerance limits. The region of variation in the input space may then be represented by a rectangle centered  $\alpha$ about the nominal value (design center) with sides of length 2t;, where the t; are the relevant tolerances. We illustrate this for a 2-dimensional case (K=2) in figure 1.9. Also which in this case are taken to shown are the two p.d.fs be, truncated Gaussian and uniform, for parameters p<sub>1</sub> and respectively. The region of acceptability, (defined  $\mathbf{p}_2$ in equation 1.9) is a mapping in the input space of the performance specifications defined in the output space. Consider figure 1.10(a) where both the tolerance region  $R_T$ and the region of acceptability  $R_{\Lambda}$  are represented. Initially, assume both parameters to be uniformly distributed. Then yield will be the ratio of the volume (area for K=2) of region  $(R_T \cap R_A)$  to the volume of region  $R_T$ . In the illustration of figure 1.10(a) this ratio is less than unity.

$<sup>^{\</sup>alpha}$ In the case of skewed p.d.f., the nominal value may by definition be taken to be the mid point between the tolerance limits.

To increase the yield the designer may keep the size of the

tolerance region fixed and increase the overlap between the two regions. This may be achieved by choosing the nominal values such that the tolerance region is more centrally placed inside the region of acceptability as illustrated in figure1.10(b). Hence, this process is called design centering. Alternately the designer may accept the nominal value and decrease tolerances, and therefore reduce the size of the tolerance region. This latter procedure is called tolerance assignment. Figures1.10(b) and 1.10(c) illustrate application of these two alternatives to the situation of figure 1.10(a). Tignter tolerances imply better grade and therefore more expensive components. Therefore, the designer may invoke a combination of both procedures to obtain a suitable trade-off between component costs and the cost of discarding or repairing failed circuits.

For the situation where all the parameters are not independent and uniformly distributed, the relevant p.d.f.  $\emptyset(P)$  will define a weighting of every point in  $R_T$ . The yield will then be a ratio of weighted volumes. A similar geometrical interpretation of tolerance assignment and design centering may also be considered in this situation.

In the manufacture of integrated circuits, individual components cannot be sorted and therefore tolerances cannot be placed upon individual parameters. For many parameters, tolerances determined by the manufacturing process have to be accepted and the designer may then attempt to maximize yield by re-assigning nominal values. However, for other components, for example resistors, tolerances on parameter values are determined by the chip area occupied by the component. The larger the area, the smaller the tolerance. However, larger component sizes increase the overall area occupied by the circuit. This increases the cost of processing the circuit and may result in a greater incidence of catastrophic faults. Here again a higher cost is associated with tighter tolerances. Therefore both tolerance assignment and design centering procedures are of relevance to integrated circuits.

#### 1.5.2 CHOICE OF PERFORMANCE SPECIFICATIONS

## (a) Specification Sensitivity

In the discussion so far it has been assumed that the specifications on performance (expression 1.7) are invariant and the engineer has to design for component value statistical spreads with respect to these specifications. However, the designer may find response spreads are such that even after tolerance assignment and design centering, the resulting circuits are still too expensive to manufacture. The designer may then explore the effect on yield of altering various specifications to consider possible trade-offs between different specifications. It may be possible to offer to the customer, circuits which are appreciably cheaper, but have specifications more commensurate with performance spreads achievable with available component spreads. The performance requirements are often somewhat arbitrary and there is usually the possibility of suitable trade-off of different specifications.

The sensitivity of yield to different performance specifications may be explored using Monte Carlo analysis. Associated with each of the N sample circuits is a number m of values for the performance functions. Overall yield is estimated as the proportion of the N analysed circuits which simultaneously meet all performance specifications. Similarly the partial yields (introduced in section 1.3.2) for each performance may be estimated as the fraction which meets that particular performance specification. The effect of relaxing or tightening specifications may then be explored by changing performance specifications and recalculating overall and partial yields.

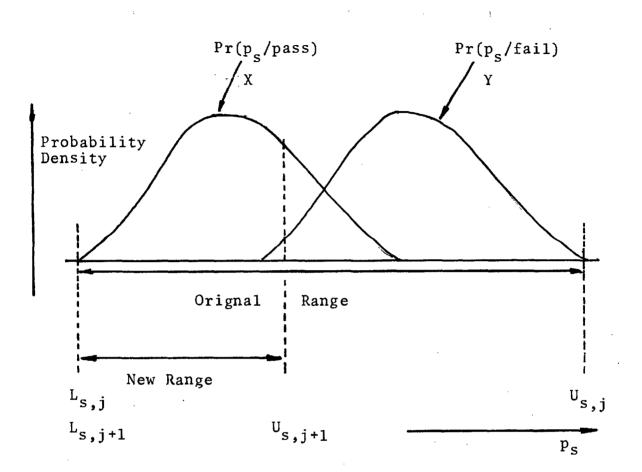

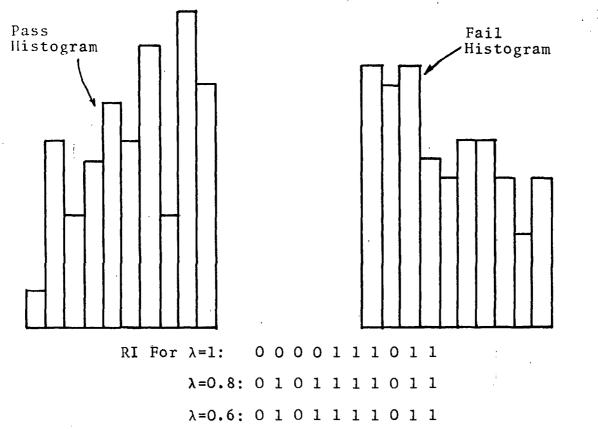

### (b) System Specification