# SLOW STATES

## ΙN

# THIN FILM TRANSISTORS

by

Steven Whitney Wright, B.Sc., A.R.C.S.

A Thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy of the University of London, and for the Diploma of Imperial College.

Department of Electrical Engineering Imperial College of Science and Technology September, 1978

#### SLOW STATES IN THIN FILM TRANSISTORS

by

#### S. W. WRIGHT

#### ABSTRACT

Slow state instability effects have been investigated in thin film field effect transistors in which the insulator was radio-frequency sputtered silicon dioxide and the semiconductor evaporated cadmium selenide. Capacitance-voltage, mobility, thermopower and resistivity measurements have been performed on the polycrystalline semiconductor film of the transistor, and the results obtained interpreted in terms of the effects of trapping states at grain boundaries in the material.

The degree of slow state instability in the devices has been measured as a function of gate field, and the effects of annealing treatments examined. The time decay characteristics of the process have been observed and shown to fit a direct tunneling model for charge transfer across the semiconductor-insulator interface to insulator trapping states. The capture cross-section and volume density of the insulator trapping states responsible for the instability have been determined.

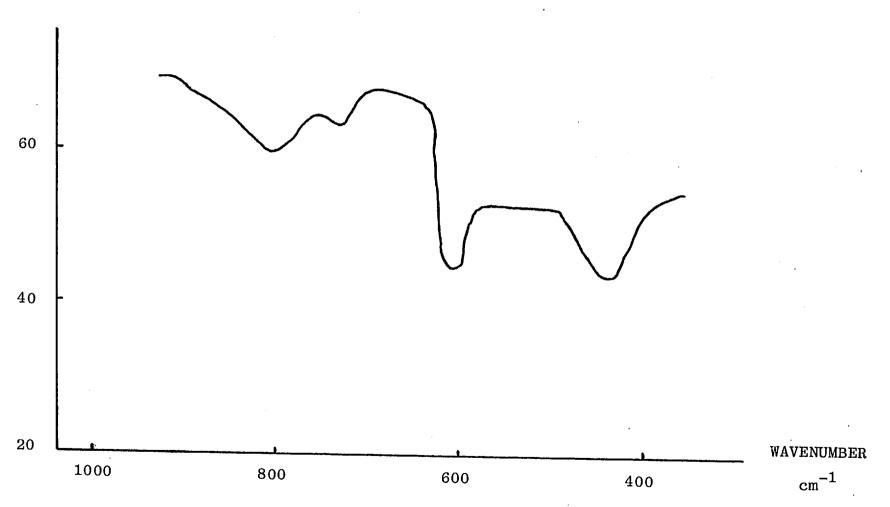

The low frequency noise behaviour of the devices has been examined, and the results related to the trapping behaviour. Also, the infra-red absorption spectra of the insulator film has been examined and certain conclusions as to the structure and composition of the material have been drawn. Identification of the state responsible for the slow trapping with electrically active oxygen vacancies in the insulator has been made.

#### ACKNOWLEDGEMENTS

My supervisor for the work described herein was Prof. J.C. Anderson, D.Sc., Professor of Electrical Materials at Imperial College, and I should like to express my gratitude for all his help, encouragement and guidance so freely offered.

I must also thank Dr. M.J. Lee for supplying the devices used in this work, and also for the advice and assistance he has profferred. Thanks should also be expressed to all my colleagues in the Materials Section for much stimulating advice and discussion.

I am most grateful to my mother, Mrs. Phyllis Wright, for undertaking the arduous task of typing the manuscript, and assisting in its production, and for her continual encouragement during the time I have been performing this work.

Finally, I acknowledge with gratitude the financial support of the Science Research Council and Marconi Radar Systems, Leicester, which has made it possible for me to undertake this work.

## INDEX

## Page No.

.

| CHAPT | TER 1 INTRODUCTION                               |    |

|-------|--------------------------------------------------|----|

| 1.1   | THE SILICON MOSFET                               | 1  |

| 1.2   | THE THIN FILM TRANSISTOR                         | 2  |

| 1.3   | COMPARISON BETWEEN MOSFET AND TFT                | 3  |

| 1.4   | INSULATOR INVESTIGATION IN MOSFETS               | 4  |

|       | 1.4.1 Effects of Silicon Dioxide on              |    |

|       | MOSFET Performance                               | 5  |

|       | 1.4.2 Control of Silicon Dioxide Properties      | 7  |

| 1.5   | INSULATOR INVESTIGATION IN THIN FILM TRANSISTORS | 9  |

| 1.6   | ORGANISATION OF THESIS                           | 13 |

|       | REFERENCES                                       | 15 |

## CHAPTER 2 THE TFT

. -

•

| 2.1 | INTRODUCTION TO THE TFT                 | 16 |

|-----|-----------------------------------------|----|

| 2.2 | STRUCTURE AND MANUFACTURE OF TFTS       | 17 |

| 2.3 | OPERATION OF THE TFT                    | 19 |

|     | 2.3.1 Simplified Analysis               | 24 |

|     | 2.3.2 The Threshold Voltage             | 25 |

| 2.4 | MANUFACTURE OF EXPERIMENTAL TFTs        | 30 |

|     | 2.4.1 Manufacture of TFTs               | 31 |

|     | 2.4.2 Annealing                         | 32 |

| 2.5 | DESCRIPTION OF DEVICES ON SUBSTRATE     | 33 |

| 2.6 | MEASUREMENT OF SEMICONDUCTOR PROPERTIES | 38 |

|     | 2.6.1 Measurements and Results          | 39 |

|     | 2.6.2 Discussion of Results             | 44 |

|     | REFERENCES                              | 53 |

| <u>CHAP1</u> | TER 3 SLOW STATE DENSITY MEASUREMENTS          | Page No. |

|--------------|------------------------------------------------|----------|

| 3.1          | INTRODUCTION                                   | 55       |

| 3.2          | EFFECT OF TRAPPING                             | 55       |

| 3.3          | MEASUREMENT OF SLOW-STATE DENSITY              | 56       |

|              | 3.3.1 Experimental Method                      | 56       |

|              | 3.3.2 Display of Results                       | 60       |

|              | 3.3.3 Calculation of Trap Density              | 60       |

| 3.4          | RESULTS OF SLOW-STATE MEASUREMENTS             | 62       |

|              | 3.4.1 Initial Slow-State Results               | 63       |

|              | 3.4.2 Reproducibility & Repeatability of Resul | lts 65   |

|              | 3.4.3 Effect of Deposition Conditions          | 72       |

|              | 3.4.4 Annealing of Slow-States                 | 77       |

| 3.5          | DISCUSSION                                     | 85       |

|              | REFERENCES                                     | 88       |

|              |                                                |          |

## CHAPTER 4 TRAP CAPTURE CROSS-SECTION MEASUREMENT

| 4.1 | INTRODUCTION |                                         |     |

|-----|--------------|-----------------------------------------|-----|

| 4.2 | TRAPPIN      | G KINETICS                              | 90  |

| 4.3 | EXPERIM      | ENTAL DETAILS                           | 90  |

|     | 4.3.1        | Measurement of Threshold Voltage Change | 91  |

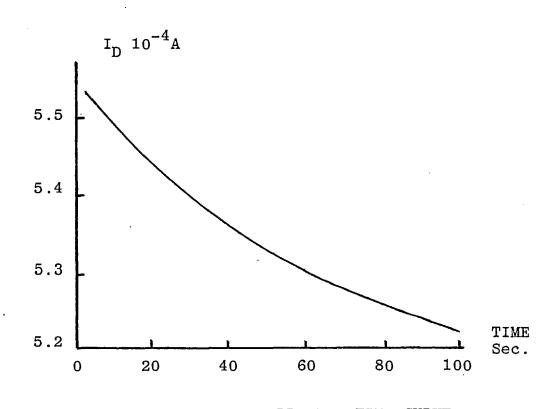

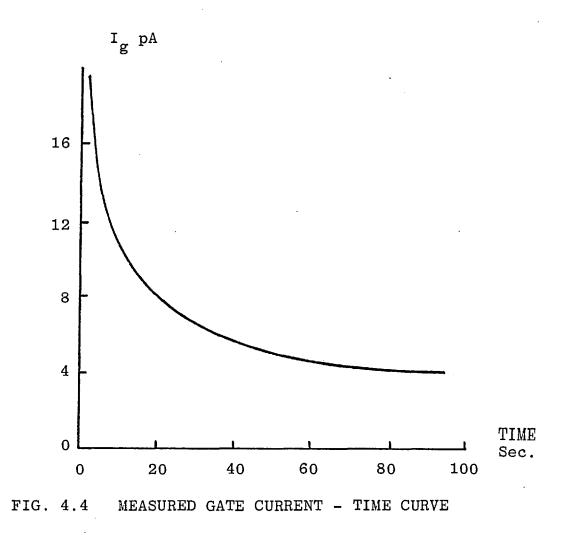

|     | 4.3.2        | Measurement of Gate Current             | 92  |

|     | 4.3.3        | Measurement System                      | 92  |

| 4.4 | THEORY       |                                         | 95  |

|     | 4.4.1        | Limitations in the Analysis Methods     | 96  |

|     | 4.4.2        | Mathematical Treatment                  | 97  |

|     | 4.4.3        | Special Case of Low Trapping Efficiency | 103 |

| 4.5 | RESULTS      | OF THE EXPERIMENT                       | 104 |

|     | 4.5.1        | Data Reduction                          | 104 |

|     | 4.5.2        | Calculations on Reduced Data            | 110 |

|     | 4.5.3        | Results                                 | 112 |

|     | 4.5.4        | Discussion of Results                   | 114 |

|     | REFEREN      | CES                                     | 118 |

Page No.

## CHAPTER 5 ADDITIONAL MEASUREMENTS

| 5.1 | INTRODU | UCTION                               | 119 |

|-----|---------|--------------------------------------|-----|

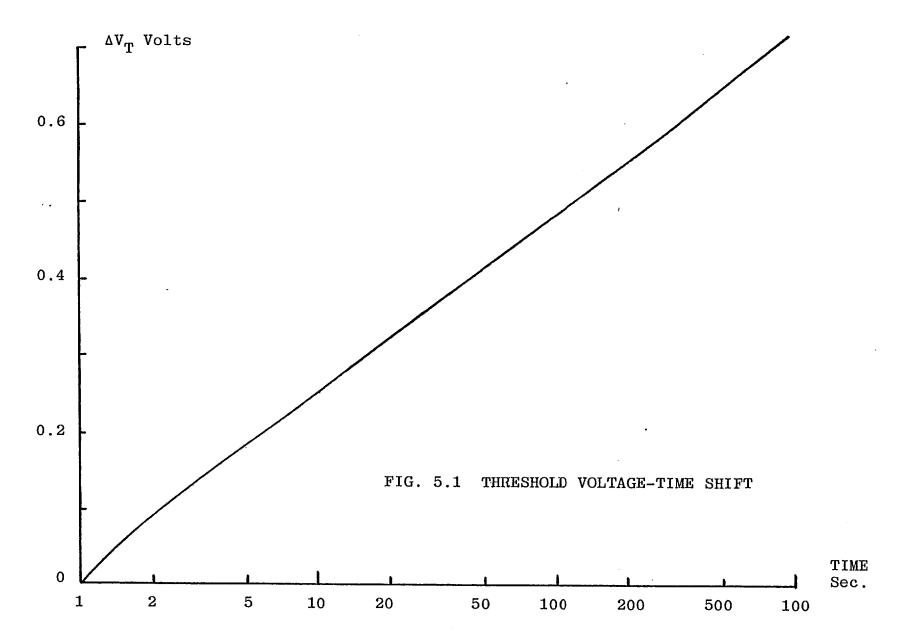

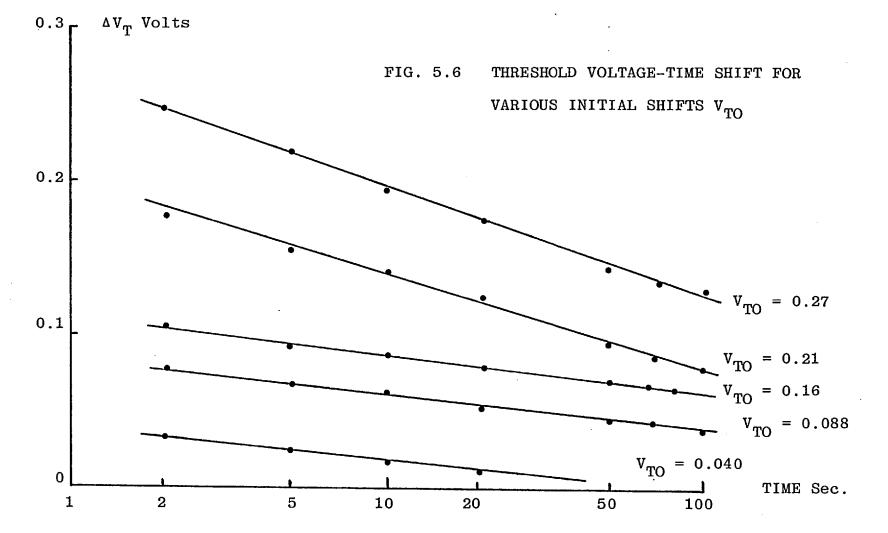

| 5.2 | THRESHO | OLD VOLTAGE TIME-DEPENDENCE          | 119 |

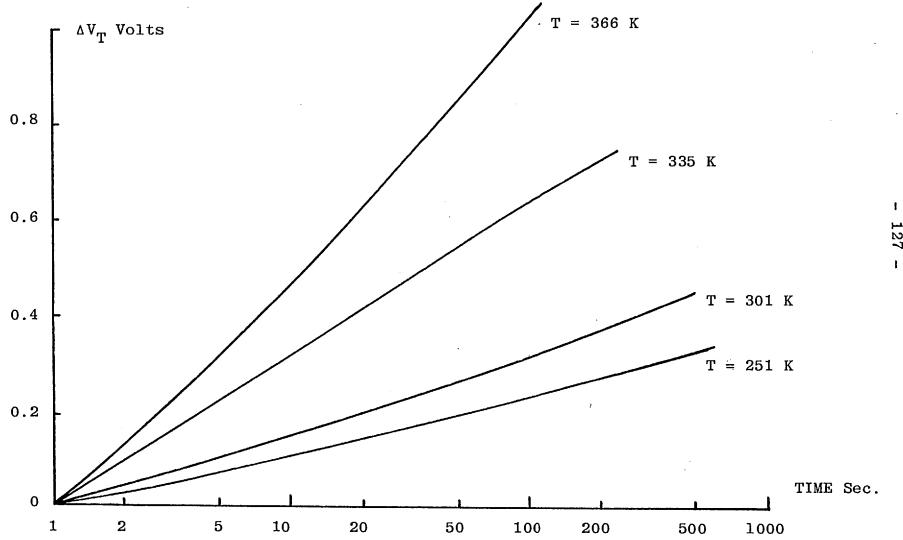

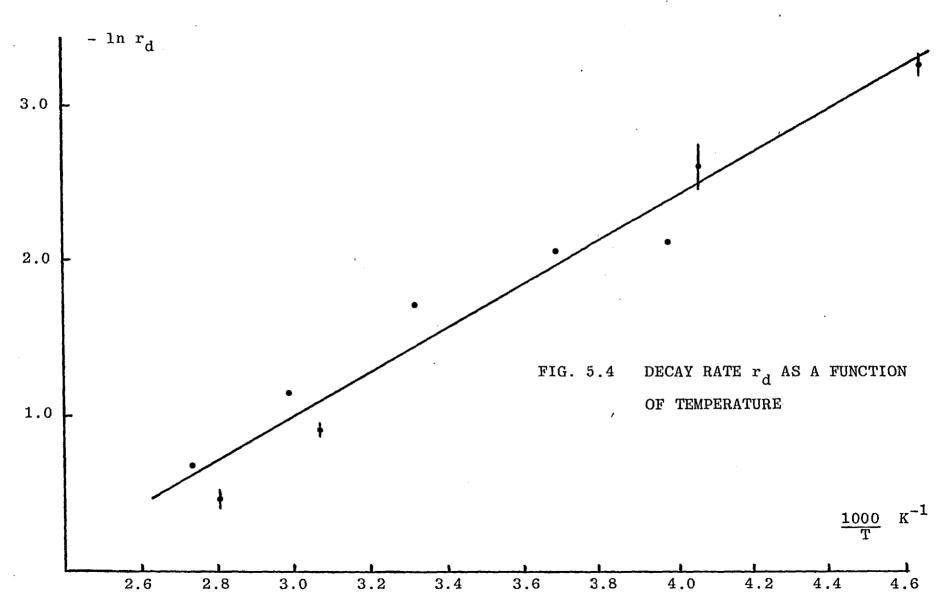

|     | 5.2.1   | Measurements and Results             | 122 |

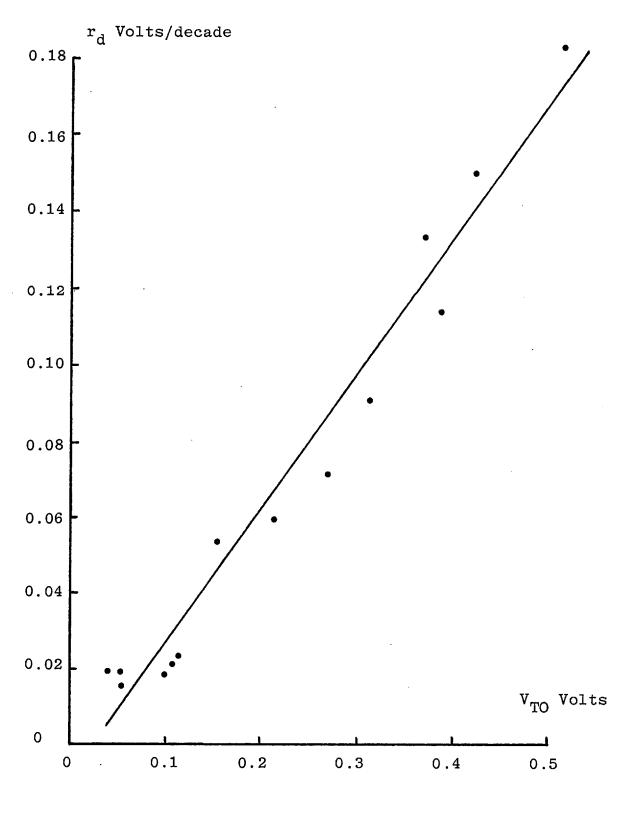

|     | 5.2.2   | Further Measurements                 | 130 |

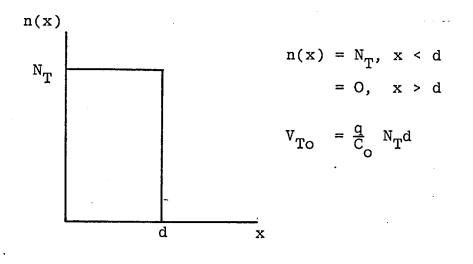

|     | 5.2.3   | Analysis of Experiment               | 136 |

|     | 5.2.4   | Analysis of Results                  | 140 |

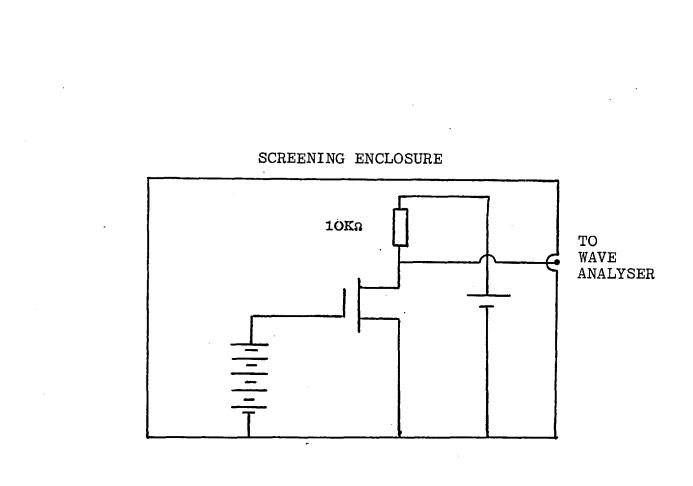

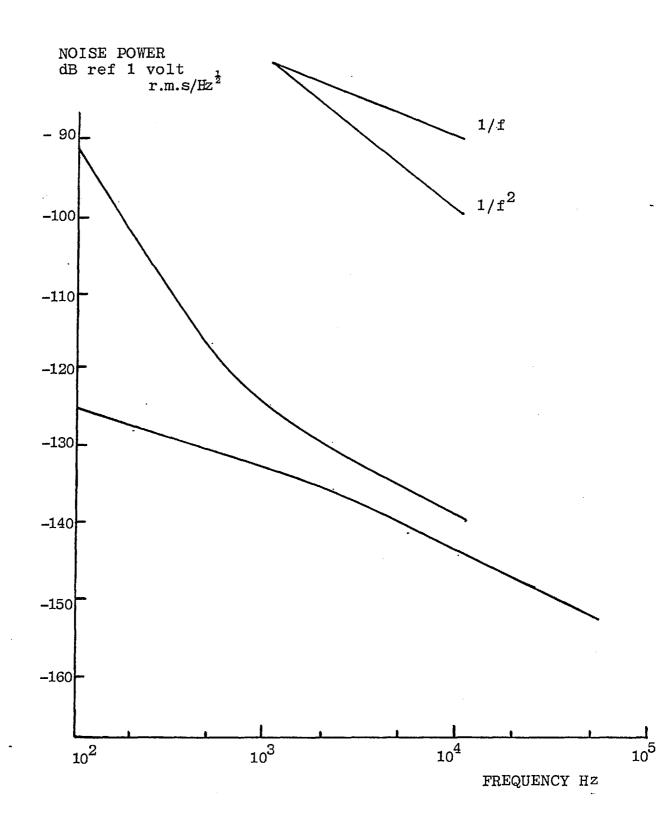

| 5.3 | NOISE 1 | IN THIN FILM TRANSISTORS             | 144 |

|     | 5.3.1   | Measurement of Noise Power           | 145 |

|     | 5.3.2   | Discussion                           | 149 |

|     | 5.3.3   | Relationship between Noise and       |     |

|     |         | Time Dependence                      | 151 |

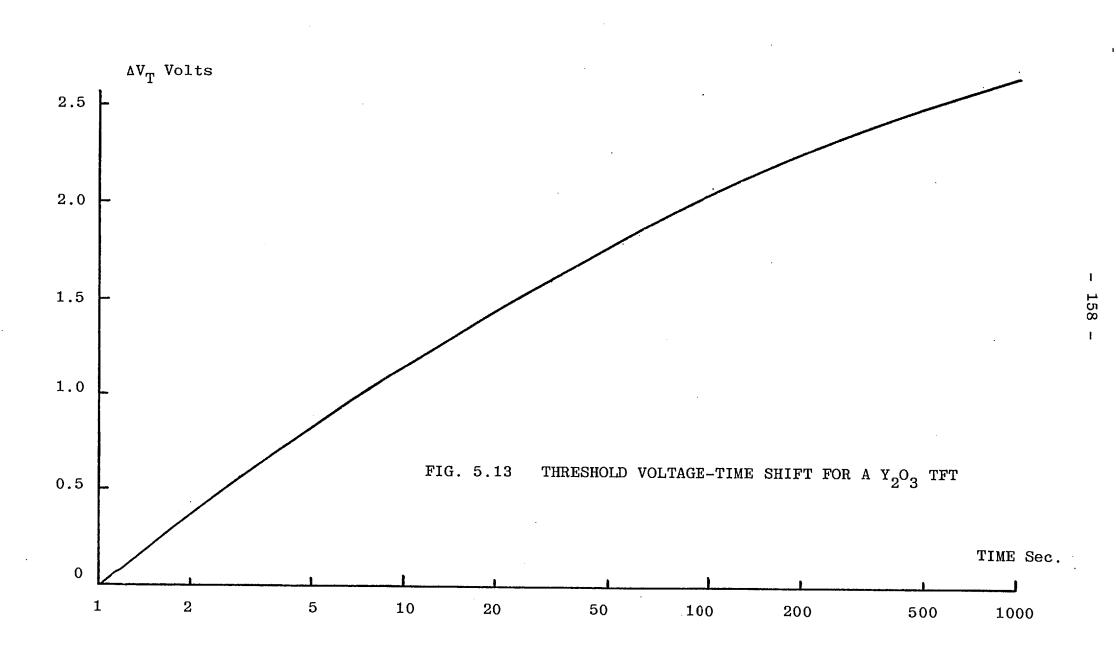

| 5.4 | EXPERIM | MENTS WITH ALTERNATIVE INSULATOR     | 154 |

|     | 5.4.1   | Measurement of Trap Cross-Section    | 155 |

|     | 5.4.2   | Threshold Voltage Time-Dependence    | 157 |

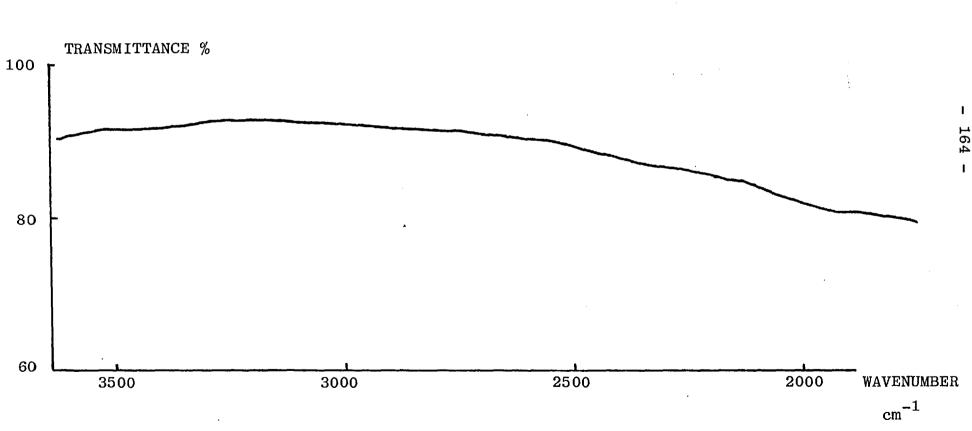

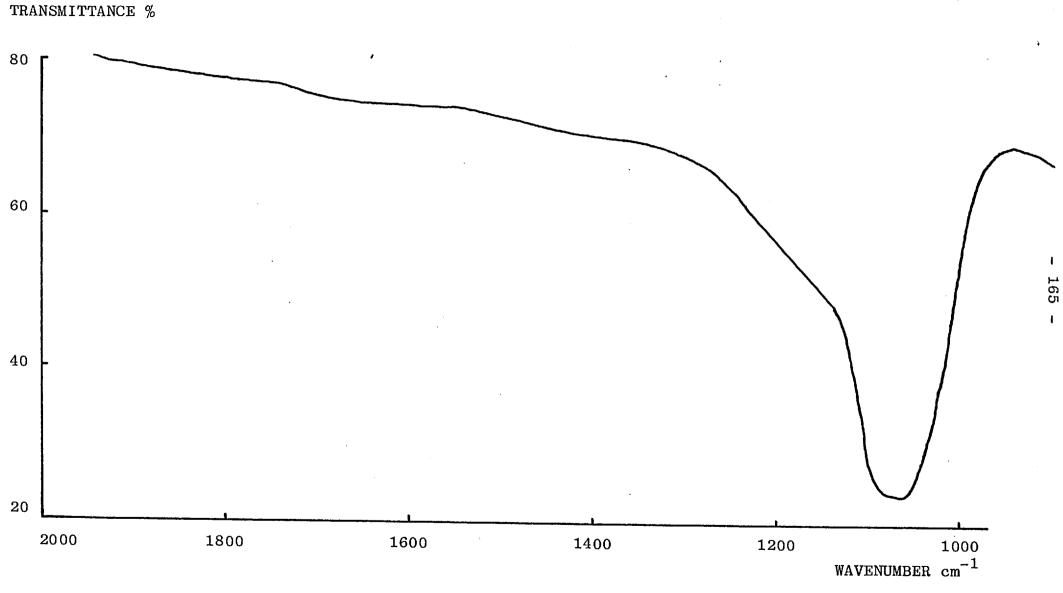

| 5.5 | INFRA-F | RED ABSORPTION ANALYSIS OF DIELECTIC | 159 |

|     | 5.5.1   | Experimental Method                  | 162 |

|     | 5.5.2   | Discussion                           | 167 |

|     | REFEREN | ICES                                 | 171 |

|     |         |                                      |     |

| CHAPTER | 6 | DISCUSSION | AND         | CONCLUSIONS |

|---------|---|------------|-------------|-------------|

|         | 0 | DIDCODDICH | <b>DIND</b> | CONCLORIO   |

1 7 9

| 6.1 | INTRODUCTION       | 173 |

|-----|--------------------|-----|

| 6.2 | STRUCTURAL DEFECTS | 174 |

| 6.3 | IMPURITY DEFECTS   | 176 |

| 6.4 | DISCUSSION         | 178 |

| 6.5 | CONCLUSIONS        | 185 |

|     | REFERENCES         | 188 |

#### CHAPTER 1 INTRODUCTION

This thesis reports an investigation of the electrical properties of a thin sputtered insulator film which are of relevance to its use in thin film field effect devices, otherwise called thin film transistors (TFTs). In this chapter the thin film transistor will be introduced, after briefly mentioning the more familiar silicon-based equivalent device, the MOSFET. The similarities and differences between the two types of device will be discussed together with their different areas of application. Previous work on the electrical properties of insulators and the semiconductor-insulator interface is briefly described and the approach followed in the present experiments is explained. Finally, the organisation and layout of this thesis will be described.

#### 1.1 THE SILICON MOSFET

The metal-oxide-semiconductor field effect transistor (MOSFET) has been known, in principle, for fifty years, and during the last twenty years MOSFETS built on a substrate of single crystal silicon have attained great technological and commercial importance. The technology has now advanced to the point where tens of thousands of transistors can be manufactured on a piece of silicon a few millimetres square, and interconnected to form, for example, the major part of a small computer system.

Because of the commercial importance of this technology a vast amount of effort has been applied to both the fundamental science and practical technology of every aspect of these devices. Fundamental to their manufacture is the technique of the thermal oxidation of the surface of a silicon crystal, the resulting silicon dioxide serving as the insulator in a MOSFET. The electrical properties of the bulk of this insulator material, and its interface with the silicon are crucial to the performance and long term stability of the devices. A variety of processing methods have been determined to produce suitable electrical and physical characteristics for successful device operation.

#### 1.2 THE THIN FILM TRANSISTOR

As originally conceived, the field effect transistor was to be made in thin film form, its active layers consisting of evaporated metal, semiconductor and insulator films. In the 1950s the great advances in silicon technology overshadowed that of thin films, and the thin film transistor has not as yet been developed to the point where it has found commercial application. Development work on these devices still continues however.

The thin film transistor consists of thin layers of material deposited generally by evaporation or sputtering in a vacuum system, in patterns delineated by thin metal aperture masks. A sequence of some half-dozen depositions is necessary to produce a completed transistor and, in the same way as for the MOSFET, a number of thin film transistors can be connected up by a final interconnection pattern to form a complete circuit.

The transistors under investigation were made with evaporated semiconductor and conductor layers, and a sputtered insulator film. The structure and deposition of the devices will be described in detail in a subsequent chapter.

- 2 -

1.3 COMPARISON BETWEEN MOSFET AND TFT

The MOSFET and the TFT are basically similar in that they both work by modulating the conductivity of a semiconductor by means of an electric field applied by a control electrode (the gate). There are considerable differences however, because the semiconductor has a different form in each of the two devices. In the MOSFET, where the semiconductor is a single crystal, the conduction process is well understood theoretically, and excellent agreement between theory and experiment is found.

In the TFT on the other hand the semiconductor consists of a thin polycrystalline film. The conduction process in these films is dominated by the effects of the boundary regions between the grains. The grain boundaries disrupt the crystal lattice of the semiconductor, interrupting the flow of charge carriers. The transport process in the material is in fact very complicated and not yet fully understood. The conduction of the TFT is controlled by a complicated interaction between the semiconductor surface, the grain boundaries and the gate field.<sup>(1)</sup>

As stated previously, MOSFETS have found important uses in many applications but there are certain limitations which prevent their use for some purposes. Some of these limitations do not apply to the TFT, which opens up new areas of application.

Silicon single crystal wafers are limited to a few inches in diameter which for electronic devices is ample. For some devices however, for example, display devices which have to interact with human beings, this is rather

- 3 -

small. One projected area of application of TFTs is in the manufacture of display devices (e.g. the "flat TV screen"). Here it would be necessary to deposit thin film transistors over the complete area of the display, and connect them up to form a circuit. Since the device is to be viewed, it has to be large, and depositing TFTs on a large substrate is perfectly possible.

MOSFETS, on the other hand, can be packed extremely densely onto the silicon wafer, but to make large silicon crystals is prohibitively expensive. There is a dividing line therefore between small, very densely packed, circuitry for which silicon MOSFET technology is eminently suitable, and large area devices of moderate density for which thin film techniques are perhaps more suitable.

In recent years, experimental display panels have been fabricated<sup>(2)</sup> involving many thousands of thin film transistors deposited over an area of many square inches, and extension of the principle to very much larger arrays would appear to be feasible.

#### 1.4 INSULATOR INVESTIGATION IN MOSFETS

The thermal silicon dioxide of the MOSFET, and its interface with the silicon surface, have been intensively studied during the past 20 years. The volume of literature generated is so great that a complete survey is not possible. Many reviews of the subject have been made, and the reader is referred to two recent such by Williams<sup>(3)</sup> and Nicollian<sup>(4)</sup>.

The conditions under which the silicon surface is oxidised, and subsequent annealing of the device, are

- 4 -

crucial to the fabrication of material with good electrical characteristics. The electrical behaviour of the interface is closely connected with the stoichiometry of the silicon dioxide. The highly stable characteristics of the siliconsilicon dioxide interface are due to the very close degree of control of the material composition which is obtainable by the thermal oxidation technique.

The charge centres in the insulator and at the semiconductor-insulator interface can be divided into two broad groups - fixed charge centres, and those which are capable of trapping and localising charge. The fixed charge centres are those whose occupancy does not change under the influence of the gate electric field, while the latter group of states do so change their occupancy. These states are located close to or at the interface, where they can exchange charge with the semiconductor with varying degrees of probability. It is these states which tend to change the characteristics of the transistor when in operation.

#### 1.4.1 Effects of Silicon Dioxide on MOSFET Performance

Early MOSFET devices were very prone to drift of their characteristics on varying timescales - from seconds to hours. It was discovered that much of the instability was caused by charge movement in the insulator material caused by the operational gate field, movement of charge initially "built-in" to the insulators, and charge injected into the insulator across the semiconductor-insulator interface. Technological processing steps have been found which reduces such effects to a level sufficient for the operation of the devices, and considerable theoretical

- 5 -

understanding of the underlying physical process has been achieved.

Among the main causes of variation of MOSFET characteristics were found to be charged ion drift in the insulator, and trapping (localisation) of charge in defect states in the insulator material and at the interface.

The transistor characteristic which is of most importance, and is also easily measurable, is the threshold voltage. This is the voltage which must be applied to the gate of a MOSFET to initiate conduction in the semiconductor. The effect of processes described above is to cause short or long term changes of this parameter to varying extents. These changes can drastically upset the operation of circuits incorporating MOSFETs and even cause them to cease working.

The simplest way of measuring the changes of threshold voltage is by examining the capacitance-voltage characteristics of an MOS capacitor<sup>(5)</sup>. This method has the advantage that it is not necessary to fabricate a complete MOSFET, which requires source and drain diffusion steps, but the experiment can be simply performed on the oxidised silicon slice with a metal gate deposited on top.

The threshold voltage is perhaps the most important, but not the only, parameter of the MOSFET which is influenced by charge trapping. Among others so influenced are the transconductance (gain) of the device, the low frequency noise behaviour and the drain and source junction breakdown voltages. The effect on the transconductance is caused by variation of electron or hole mobility in the conducting channel region between source and drain, caused

- 6 -

by the non-uniform potential of the charge localised in states close to the interface. The regular periodicity of the crystal lattice is disturbed by the random component of the potential, so scattering carriers out of the single crystal Bloch wave functions, and reducing their mobility, in much the same way as for impurity scattering. When the occupancy of the centres is changed by the gate field, the mobility changes correspondingly.

Noise, that is, random fluctuations of the current flow in the transistor, is caused by, among other mechanisms, the random capture and re-emission of charges by trapping states. In the process, the phase information carried by the electron or hole is lost, resulting in the production of random noise. Trapping centres have a wide spread of time constants, so the noise spectrum covers a correspondingly wide frequency range.

The junction breakdown voltages are changed by trap occupancy because the field due to charged trapping centres causes accumulation or depletion regions to form in addition to those caused by the field across the reverse biased electrode-substrate p-n junction.

#### 1.4.2 Control of Silicon Dioxide Properties

The aim of controlling the processing conditions of MOSFET devices is to reduce the density of both fixed charge states and interface states to a sufficiently low level that the device characteristics are not adversely affected by them. The means for achieving this end is control of the oxidation process (temperature, time, gaseous ambient) and post-oxidation annealing treatments.

- 7 -

To reduce interface state densities either a low  $(350^{\circ}C)$  or high  $(1000^{\circ}C)$  temperature anneal is used, the former after an aluminium layer has been deposited to the gates of the MOSFETs. In the low temperature anneal, it is thought that atomic hydrogen, formed by the reaction of water in the oxide with the aluminium, chemically reacts with the interface states to annihilate them. In the high temperature anneal direct thermal reduction of the centres occurs.

Fixed charge density is affected considerably by the conditions of oxidation, it being generally found that a high oxidation temperature (1200<sup>O</sup>C) in dry oxygen results in the lowest density of fixed charge in the oxide.

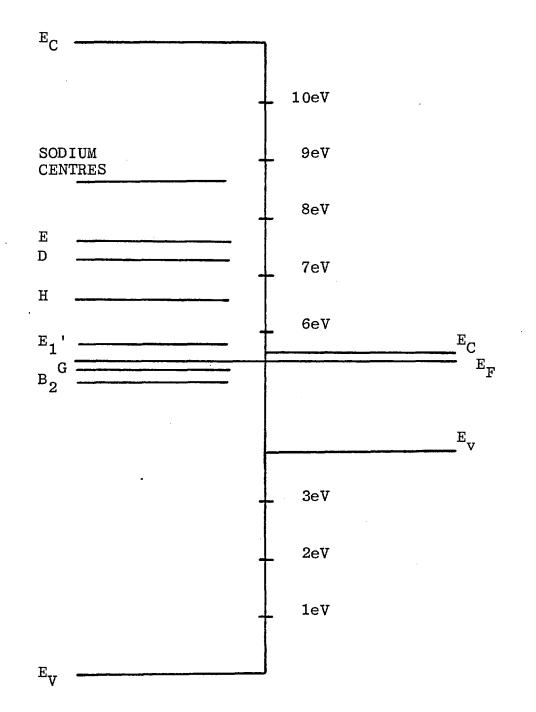

Effects similar to those of trapping state charging are caused by drift of mobile charged ions, principally sodium, in the insulator material under the influence of the gate field. Sodium is the most troublesome both because it has a high mobility in silica and because it is a very common environmental contaminant. The only solution to this problem is scrupulous cleanliness during manufacture of the devices, almost surgically-clean conditions being necessary. The reason for this will be obvious when it is realised that the airborne bacteria on the surface of a silicon wafer can supply sufficient sodium to cause considerable instability in the device. It has also been found that a thin layer of phosphosilicate glass on the surface of the oxidised silicon wafer can act as a "getter", immobilising any sodium present.

The actual physical nature of the trapping centres in

- 8 -

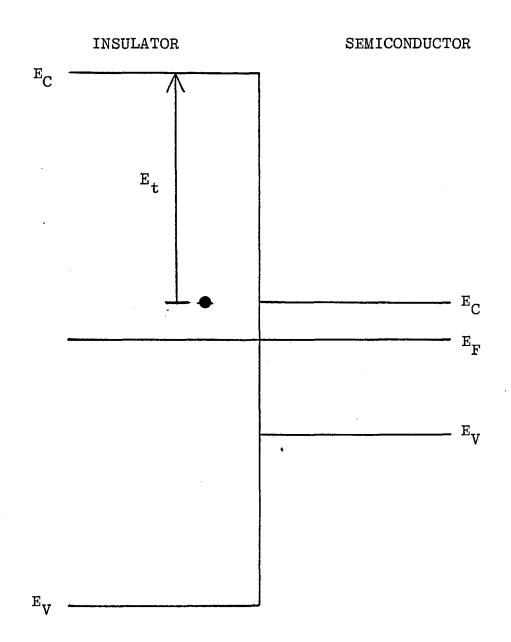

the oxide and in the interface has not been discussed yet. Various defects and impurities in the silicon dioxide have been identified as being such trapping states. Amongst these are oxygen and silicon oxygen vacancies in the insulator<sup>(6)</sup>, broken and strained interatomic bonds in the material<sup>(7)</sup>, and impurity atoms and ions, such as sodium<sup>(8)</sup> and tungsten<sup>(9)</sup>. Identification of electrically active trapping states with optically active centres which appear upon irradiation of SiO<sub>2</sub> has been made<sup>(10)</sup>. The physical nature of defect states will be discussed further subsequently.

### 1.5 INSULATOR INVESTIGATION IN THIN FILM TRANSISTORS

In this section the basic philosophy of insulator investigation in thin film devices is discussed, corresponding to the preceding section on single crystal silicon thermal oxide investigations.

Thin film transistors have long been known to suffer from short and long term changes in their characteristics. Such changes are analagous to the processes which occurred in silicon before it was learned how to control the oxidation process sufficiently precisely, and indeed similar causes have been established to be the root cause of these changes.

There are of course considerable differences between silicon MOSFETs and TFTs. In the former an interface between semiconductor and insulator is formed in the bulk of the material, under carefully controlled conditions, both the semiconductor and insulator materials being virtually defect free. In thin film devices, on the other

- 9 -

hand, two amorphous or polycrystalline materials are placed together one on top of the other. At the interfaces between the materials, and between grains, there exists a large population of localised states of the "Tamm" or "Schockley" type. Additionally there are defect states of various origins in the semiconductor and insulator.

The long term drift of characteristics which occurs in thin film transistors - the slow state drift - has been connected with the existence of trapping states in the insulator which capture and localise charges<sup>(11)</sup> (12). These localised charges reduce the effective electric field strength at the semiconductor-insulator interface. One way of looking at this is to say that a proportion of the electric field lines from the gate are terminated by the trapped charges, alternatively the trapped charge can be considered as setting up an opposing field to the gate field. The very long time constants associated with the slow trapping effects are due to trapping states with a very low probability of capturing charge. Localised states in the insulator material are the only states which have a sufficient spread of time constants.

There also exist in thin film devices many localised states in the semiconductor material and at the interface. These states are in close communication with the charge carriers of the semiconductor, and will therefore capture and release charge much more rapidly. The effect of these states is to immobilise a proportion of the charge induced in the semiconductor by the gate field, thereby reducing the degree of modulation attainable by the gate - that is,

- 10 -

the transconductance. The gain of thin film devices would therefore always be less than that of single-crystal devices, because of the grain boundary trapping states. In fact, however, the situation is not so simple, because the potential barriers between the grains are also modulated by the gate field, so altering the charge carrier mobility. It is found that the overall transconductance of thin film transistors can therefore be as great as, or even greater than, that of the single crystal device<sup>(1)</sup>.

The investigation of insulator charge-trapping properties in thin film devices broadly parallels that of the thermal SiO<sub>2</sub> in silicon technology. There exist fixed charges, which determines the threshold voltage, and trapping states which capture and release charge. The fastest responding of these are considered to be located at the interface, while similar states located in the insulator bulk will have longer response times and cause the slow state effects.

The distinction is essentially arbitrary between "slow" and "fixed" charge states, although there certainly exists truly fixed charge. Depending on the timescale of a particular measurement, some states will appear as fixed charge which under other conditions are charged or discharged. This will be seen in some of the experiments to be described, where insulator states are initially charged, that is, their occupancy is changed. A quick measurement of the device threshold voltage is then made, during which the same states appear as fixed charge. Their occupancy level can then be altered and the measurement repeated.

- 11 -

The method of deposition of the insulator material determines to a considerable degree the properties of the charge trapping centres in the material. In the present work, the materials under investigation are deposited by radio-frequency sputtering. The conditions under which this deposition occurs correspond to the oxidation conditions in silicon technology.

As in silicon technology, annealing in various ways affects the trapping state properties. In this matter however there is an additional difficulty. The evaporated polycrystalline semiconductor material is not in an equilibrium state, unlike a single crystal, and annealing at even moderate temperatures can have drastic effects on the semiconductor film. Indeed, annealing of the semiconductor to obtain the required properties, such as grain size, is frequently essential. This means that it is not possible to determine treatments to produce optimum insulator properties, as in the case of silicon technology - rather, the semiconductor and insulator must be considered as a whole. There exists considerably less freedom therefore in postmanufacture annealing treatments which may be used.

The measurements carried out to examine the insulator trapping properties are similar to those described in the previous section. The most important characteristic measured is the threshold voltage of thin film transistors, which provides information on the quantity and physical location of charge trapped in the insulator film. By further measurements it is possible to determine certain other characteristics of the trapping states.

- 12 -

#### 1.6 ORGANISATION OF THESIS

The contents of this thesis are arranged as follows. Following this introduction, Chapter 2 describes the thin film transistors used in this work in greater detail and the method of making the devices. The measurements performed in order to determine the semiconductor properties for later use are related in the same chapter, together with the results obtained therefrom.

The next chapter, Chapter 3, contains a description of the first measurements made of the slow state instability in these thin film transistors. The results of these experiments are described and discussed.

Chapter 4 contains an account of measurements performed in order to determine the capture cross-section of the trapping states which cause the slow threshold voltage drift in these devices. Having obtained these results some discussion is given of the possible identities for the trapping states in the insulator.

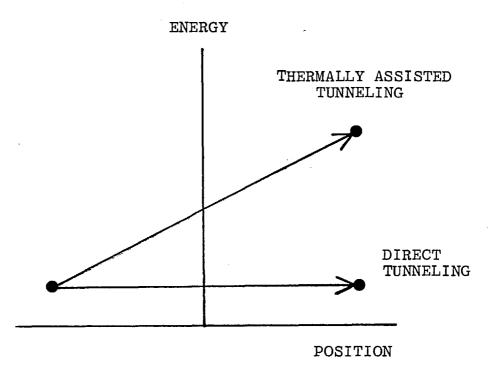

The final experimental chapter is Chapter 5, and consists of a description of experiments and results of four separate phenomena. First, and most important of these, are measurements of the time response of the trapping states when filling with and emptying of charge. From the results of these measurements a charge capture mechanism for the trapping states is determined.

The next section of this chapter contains the results of low frequency noise measurements made on the TFTs. The data obtained from these measurements is then related to that of the previous section.

- 13 -

Following this, the results of some measurements obtained on thin film transistors manufactured using a different insulator material are presented; the material chosen for this was yttrium oxide  $(Y_2O_3)$ .

Finally in this chapter are the results of measurements of the infra-red absorption spectra of the silicon dioxide insulator material, from which can be drawn certain conclusions regarding the material's structure.

#### REFERENCES - CHAPTER 1

- (1) J.C. Anderson, Thin Solid Films <u>38</u> 151 (1976)

- (2) T.P. Brody, F.C. Luo, Z.P. Szepesi and D.H. Davies,

IEEE <u>ED-22</u> 739 (1975)

- (3) R. Williams, J. Vac. Sci. Tech. 14 1106 (1977)

- (4) E.H. Nicollian, J. Vac. Sci. Tech. <u>14</u> 1112 (1977)

- (5) K.H. Zaininger and F.P. Heiman, Solid State Tech.13 No.5 p 49; No.6 p 46 (1970)

- (6) F.M. Fowkes and D.W. Hess, Appl. Phys. Lett. <u>22</u> 377 (1973)

- (7) T.P. Ma, G. Scoggan and R. Leone, Appl. Phys. Lett.

<u>27</u> 61 (1975)

- (8) F.M. Fowkes and T.E. Burgess, Surface Sci. <u>13</u>

184 (1969)

- (9) D.R. Young, D.J. DiMaria and N.A. BojarczukJ. Appl. Phys. 48 3425 (1977)

- (10) T.W. Hickmott, J. Appl. Phys. <u>48</u> 723 (1977)

- (11) H. Ishii and K. Yamada, Solid State Electron <u>10</u>

1201 (1967)

- (12) H. Sewell, PhD Thesis London University (1974)

- 15 -

#### CHAPTER 2 THE THIN FILM TRANSISTOR

#### 2.1 INTRODUCTION

The thin film transistor is a field effect transistor, that is to say, it works by modulation of the conductivity of a thin semiconductor film by the application of a capacitatively coupled transverse electric field. This field is applied by a gate electrode insulated from the semiconductor by a thin dielectric film, and the semiconductor is provided with two non rectifying contacts, the source and drain.

The thin film transistor was invented in 1926 and patented by Lilienfeld. The idea appears then to have been forgotten for many years.

With the greatly increased interest in semiconductors some years later, the field effect was revived as a means of examining the surface properties of semiconductors. In 1948, Bardeen and Brattain<sup>(1)</sup> measured the field effect in a germanium crystal, using as insulator a thin mica sheet. The degree of field effect modulation was found, however, to be only about one-tenth of that predicted from theory.

This discrepancy was attributed to the existence of trapping states on the surface of the crystal, which reduced the modulation by trapping and immobilising most of the charge carriers induced by the field plate voltage. The existence of such trapping states due to the interruption of the crystal periodicity at the crystal surface had been predicted previously on theoretical grounds by Tamm<sup>(2)</sup> and Shockley<sup>(3)</sup>. They may be thought of as being the

#### - 16 -

"dangling bonds" (unsatisfied valency bonds) left at the surface of the crystal.

Obviously, to produce a useful field effect device it is necessary to make a semiconductor-insulator interface with very few surface states. One method of doing so was discovered by Atalla et al<sup>(4)</sup> who found that the interface between silicon and thermally produced silicon dioxide has a very low trapping state density. This discovery was the key to the production of a workable field effect device on silicon.

Such a M-O-S (metal-oxide-semiconductor) device was produced by Hofstein and Heiman<sup>(5)</sup> on single-crystal silicon in 1962. At about the same time, the first thin film transistor (TFT) was produced by Weimer<sup>(6)</sup>. This used an evaporated polycrystalline semiconductor layer and an evaporated insulating layer, both about 1000 Å thick. Many semiconductor-insulator material combinations have since been found suitable for the manufacture of TFTs.

#### 2.2 STRUCTURE & MANUFACTURE OF TFTs

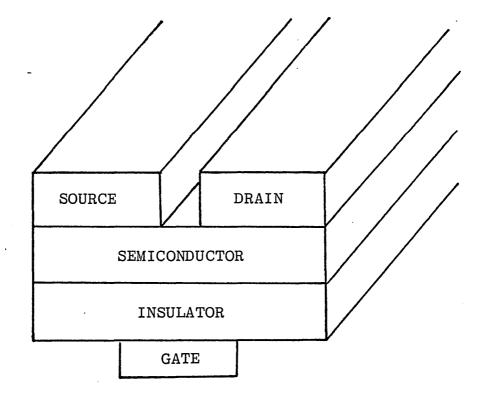

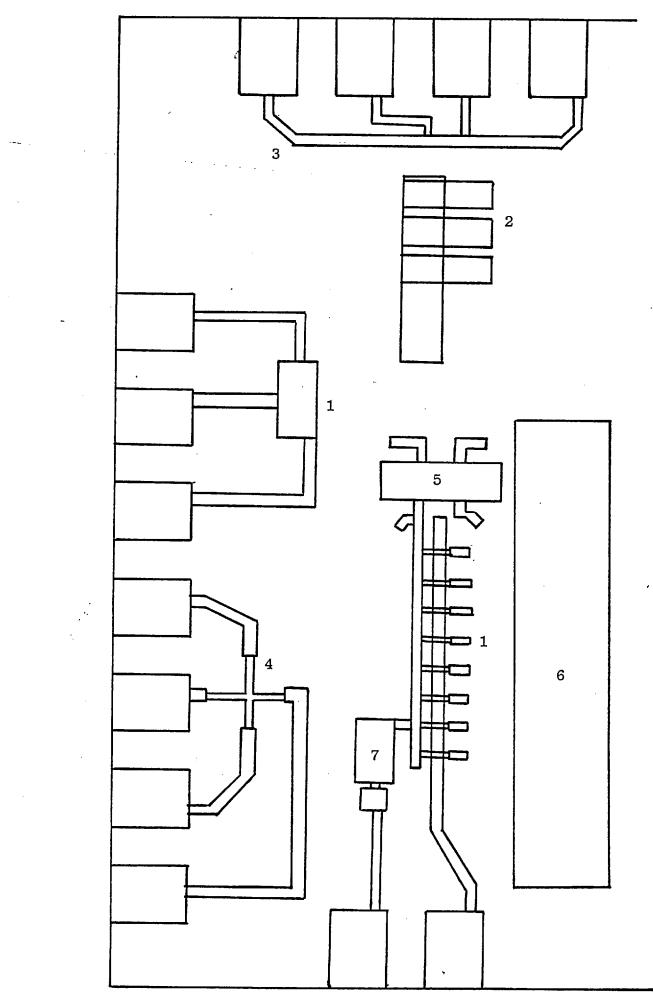

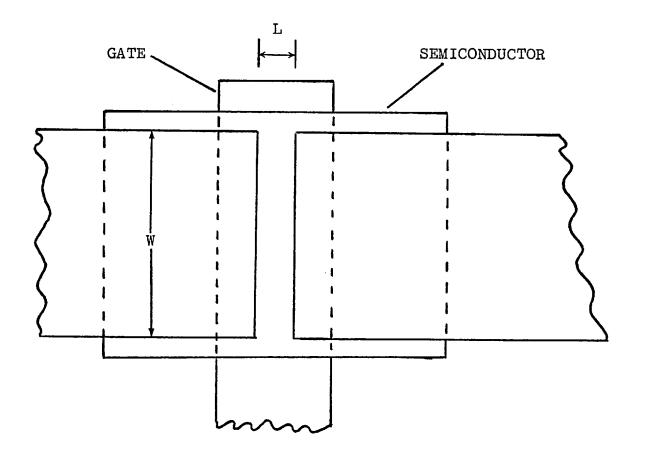

A TFT consists of a thin film of semiconductor material, provided with two closely spaced non-rectifying contacts, named the source and drain. Overlying the semiconductor is an insulator film, which separates the third electrode, the gate, from the semiconductor. The gate is a thin strip of metal placed opposite to the gap between source and drain. Fig. 2.1 is a generalised representation of the device.

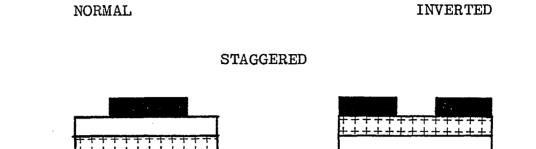

There are several ways of arranging these component parts of the device, and the four basic arrangements have been described by Weimer<sup>(7)</sup> as staggered or co-planar

- 17 -

# FIG. 2.1 STRUCTURE OF A TFT (not to scale)

electrode, inverted or non-inverted structures. These four arrangements are shown in Fig. 2.2. There are advantages and disadvantages to each configuration, the choice of which to use being governed by material properties and fabrication methods.

The early TFTs were made with all the layers being thermally evaporated, using cadmium sulphide or selenide as the semiconductor, silicon monoxide as the insulator and gold or aluminium as the metal electrodes. Certain disadvantages of evaporated insulator layers, due to the difficulty of controlling the process so as to get a stoichiometric insulator film, led to the use of anodised or r.f. sputtered dielectric materials, since both of these methods enable better control of the insulator properties to be obtained. With modern electron-beam evaporation sources, however, satisfactory insulator layers can now be produced by evaporation of oxide dielectrics.

#### 2.3 OPERATION OF THE TFT

From the description of the TFT it will be realised that it is a parallel-plate capacitor, one of the plates being a metal and one a semiconductor. If charge is placed on the metal plate by changing its potential an equal charge, opposite in sign, is induced in the semiconductor. The charge in the semiconductor forms a space charge layer which penetrates a certain distance into the depth of the semiconductor because of its low charge carrier concentration. Charge in the semiconductor is mobile, so the conductivity of the semiconductor is thereby altered.

- 19 -

FIG. 2.2 DIAGRAMMATIC REPRESENTATION OF TFT STRUCTURES

In operation, a voltage is applied between the source and drain terminals and a drain current flows, modulated by the voltage applied between the gate and source terminals.

Overall, then, a change in gate voltage induces free carriers into the semiconductor which modulate the current flowing from drain to source of the device. If the induced carriers have the same sign as those initially present in the semiconductor an accumulation region is formed and the drain current increases; conversely, charges of opposite sign, induced by a gate voltage of reverse polarity form a depletion region and reduce the drain current.

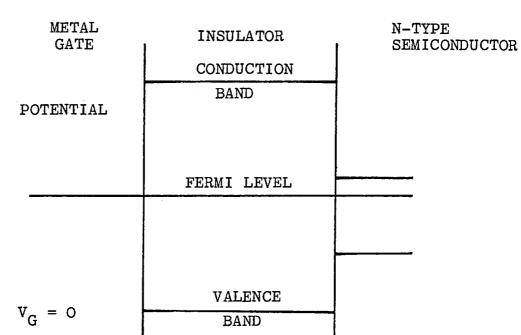

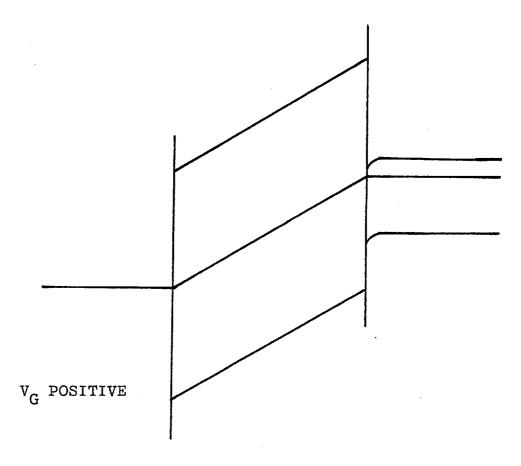

The process may be represented on energy level diagram which shows how the electrical potential changes throughout a system such as a TFT, or alternatively by a diagram showing the charge density in the various regions of the device. These are shown in Figs. 2.3a and 2.3b respectively. The device shown here has an n-type semiconductor (electrons are the majority carriers) which means that it requires a positive gate voltage to increase the drain current, and a negative voltage to reduce it. The effects of trapped charge at the semiconductor/insulator interface are, at this stage, neglected.

The relationship between drain current and gate-source voltage will now be obtained under the simplifying assumption that the drain-source voltage is small, that is, very much less than the gate-source voltage. This restriction ensures that the voltage across the dielectric is essentially constant over the whole area of the device. This in turn means that the charge induced by the gate is uniform over the surface of the semiconductor.

- 21 -

## FIG. 2.3a TFT ENERGY LEVEL DIAGRAM

## FIG. 2.3b TFT CHARGE DENSITY DIAGRAMS

- 23 -

#### 2.3.1 Simplified Analysis

The starting point in the analysis is the definition of drain current  $\mathbf{I}_{\mathrm{D}}$

$$I_{D} = \bigvee_{O} \int_{O}^{d} J(x) dx$$

J(x) - current density in semiconductor

x - distance into depth of semiconductor

W - width of device

d - thickness of semiconductor film

Ohm's Law states:

$$J(x) = \sigma(x) F$$

$\sigma(x)$  - conductivity

F - electric field between source and drain. The conductivity is given by

$\sigma(x) = n(x) q \mu$

n(x) - charge carrier density/unit volume

$\mu$  - carrier mobility

q - electronic charge

Taking these equations together

$$I_{D} = W F \mu q \int_{O}^{d} n(x) dx$$

The last term is the integral of the distribution of charge carriers through the depth of the semiconductor - that is, it is the area density of charge carriers.

Because the device is a capacitor, the charge

- 25 -

transferred to the semiconductor by a gate voltage  $V_{G}$  is:

$$Q_{G} = C_{O} V_{G} = q \int_{O}^{d} n(x) dx$$

substituting for the integral in the previous equation therefore:

$$I_{D} = W F \mu C_{O} V_{G}$$

the source-drain field F is equal to the drain potential  $V_{\rm D}$  divided by the source-drain spacing L, and so the final equation is:

$$I_{D} = \frac{W}{L} \mu C_{O} V_{D} V_{G}$$

or in terms of conductance:

$$G_{SD} = \frac{W}{L} \mu C_{O} V_{G}$$

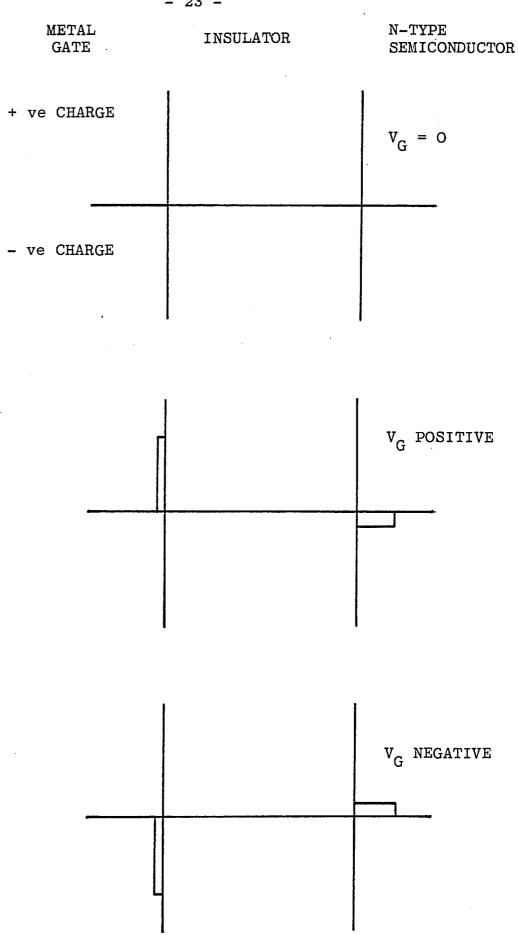

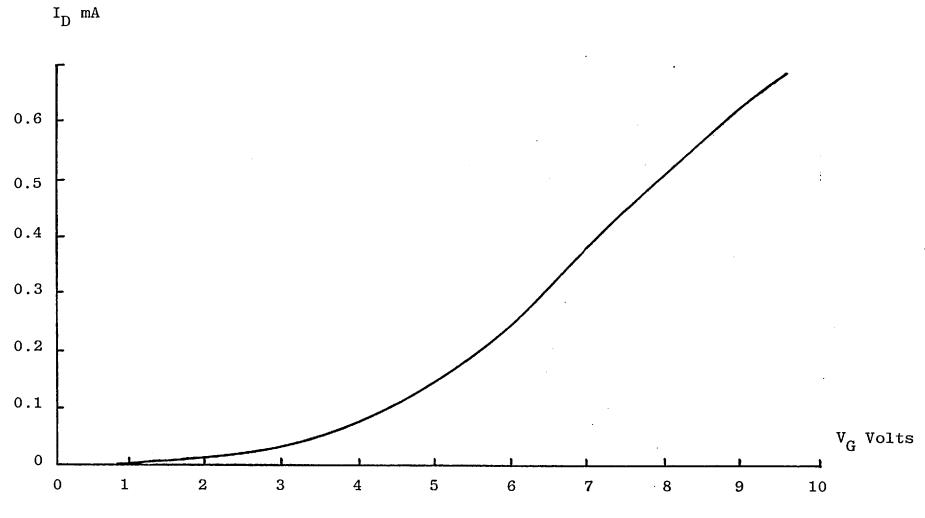

This simple analysis predicts therefore that the conductance of the device is a linear function of gate voltage. This is found in fact to be the case. In Fig. 2.4 conductance is plotted as a function of gate voltage for a TFT of the type used in this work. A straight line relationship is indeed observed, except at low gate voltages where the assumption of a uniform electric field across the insulator is not correct (because of the effect of the drain voltage).

#### 2.3.2 The Threshold Voltage

It will be observed from Fig. 2.4 that the linear portion of the curve does not pass through the origin but rather a certain gate voltage is required to initiate conduction. This voltage is called the threshold voltage and is a very important parameter of a TFT. The threshold voltage is caused by the presence of fixed electric charge

FIG. 2.4 TFT CONDUCTANCE - GATE VOLTAGE CHARACTERISTICS

in the insulator or at the insulator/semiconductor interface, incorporated at the time of manufacture. This charge induces a corresponding charge in the semiconductor which, if opposite in sign to the majority carriers forms a depletion region.

Before the carrier concentration can be increased and conduction occur this depletion must be cancelled out. The threshold voltage supplies the necessary amount of charge to do this.

The relation between the charge in the insulator, the charge in the semiconductor and the threshold voltage was derived by Snow et  $al^{(8)}$  and will be briefly reviewed at this point.

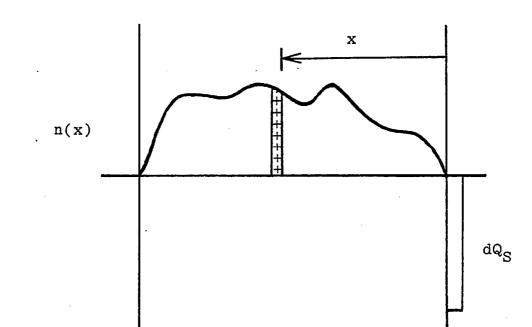

Consider an arbitrary distribution of charge carriers varying throughout the depth of the insulator, as in Fig.2.5 The shaded region of charge, width dx and distance x from the semiconductor induces a charge in the semiconductor

$$dQ_{s} = -\left(\frac{x_{o} - x}{x_{o}}\right)^{q} t^{(x)} dx$$

where  $n_t(x)$  is the volume density of charge carriers; this result follows immediately from Gauss's Law. The total charge induced in the semiconductor is obtained by integrating:

$$Q_{s} = -\frac{q}{x_{o}} \int_{0}^{x} (x_{o} - x) n_{t}(x) dx$$

The gate voltage which would cause this quantity of charge in the semiconductor is:

$$V = - \frac{Q_s}{C_o}$$

- 28 -

.

Where  $C_0$  is the insulator capacitance/unit area Therefore the threshold voltage corresponding to the insulator charge is:

$$V_{t} = \frac{q}{C_{o}x_{o}} \int_{0}^{x_{o}} (x_{o} - x) n(x) dx \qquad (21)$$

This expression may alternatively be expressed in the form:

$$V_t = \frac{q}{C_o} \left(1 - \frac{\overline{x}}{\overline{x}_o}\right) \int_0^{x_o} n(x) dx$$

Where  $\bar{\mathbf{x}}$  is the centroid of the charge distribution.

It is found that the threshold voltage of thin film transistors varies on a time scale of seconds to hours. This effect, often called slow state drift, is deleterious to the performance of circuits using TFTs because the operating conditons of the circuit will be upset, possibly causing the circuit to cease working. For this reason it is important that means of reducing these effects be found. Similar problems were encountered in the early days of silicon field effect transistor manufacture. The key to the problem was found to be the achievement of an insulatorsemiconductor interface virtually free of defects. This was found to be possible by the thermal oxidation of singlecrystal silicon.

Various mechanisms were found to be responsible for the drifts in threshold voltage which afflicted silicon devices and it is very likely that similar processes occur in TFTs. One of the mechanisms found to occur was movement of charged ionic species, principally sodium, in the insulator material under the influence of the gate field<sup>(8)</sup>. Another was trapping of carriers from the semiconductor at sites inside the insulator material, carriers interacting with traps by quantum mechanical tunneling<sup>(9)</sup>. Hot electron injection from the semi-conductor into the insulator can also give rise to trapped charge<sup>(10)</sup>.

The factor common to all the possible mechanisms is that a slow change occurs in the distribution of charge in the insulator causing a change of threshold voltage in the way previously explained.

Apart from the practical purpose of improving the TFT, the device is also a sensitive means of examining charge transport phenomena in thin insulator layers, which is both a theoretically and technologically interesting subject.

#### 2.4 MANUFACTURE OF EXPERIMENTAL TFTs

In this section the method of manufacture of the thin film transistors is described. The structure and function of the devices made are explained. A set of measurements of certain properties of the semiconductor and insulator layers is described, and the results presented.

The devices used throughout this work were made in the Thin Film Laboratory at Imperial College as part of a continuing programme of thin film transistor development, under the direction of Dr. M.J. Lee and were made available by him for this work.

- 30 -

## 2.4.1 Manufacture of Thin Film Transistors

The TFTs used in this work were of the inverted, staggered structure (Fig.2.4). They were made on a substrate of Corning 7059 glass cleaned by vapour degreasing in isopropyl-alcohol. A layer of silicon dioxide was first sputtered on to the substrate to form a clean smooth surface for deposition of subsequent layers. The aluminium gate was then evaporated to a thickness of 0.1 micron. Following the gate the dielectric was deposited by sputtering.

The material used for the transistor dielectric layer was silicon dioxide. The material was r.f. sputtered in a 95% argon-5% oxygen gas mixture at a pressure of 1 micron and a sputtering rate of 0.1 microns per hour from a fused silica target. This process gives a smooth pinhole-free high quality dielectric layer. The insulator thickness was 0.1 micron.

Following a cooling down period, the semiconductor layer was evaporated. The material used was high purity Cadmium Selenide in powder form, evaporated from a resistance heated silica boat at a rate of 0.025 microns per minute. The semiconductor thickness generally used was 0.12 microns. Cadmium selenide is an n-type semiconductor when made, no deliberate doping being necessary.

The final two depositions are an evaporated chromium layer to form an ohmic contact with the cadmium selenide, and an evaporated aluminium layer to interconnect the devices on the slide.

For each evaporation control of thickness and deposition rate was by a quartz crystal ratemeter (Edwards

#### - 31 -

Speedivac FTM1), calibrated by film thickness measurements by a Talysurf stylus instrument. The thickness of the sputtered layers was measured in the same way and was constant for a constant sputtering power and time. The substrate was unheated during the deposition process.

Each deposition was done through a different mask so as to form the required pattern. Between depositions the substrate holder was moved to the next mask at the appropriate deposition station. The whole process was completed in a single pump down of the vacuum system. The manufacturing process has been described in detail elsewhere<sup>(11)</sup>, (12).

## 2.4.2 Annealing

As evaporated the thin film transistors perform very poorly, little modulation being possible. To produce devices with good characteristics it is necessary to anneal them. The standard anneal used was one of 1½ hours at 380°C in a flowing dry nitrogen ambient. Some devices were annealed under different conditions to determine the effects on device performance.

The annealing process is known to cause a considerable increase in the mean crystallite size of the semiconductor  $film^{(13)}$  and therefore a decrease in the area of the grain boundary of the material. The grain boundary region is similar to the surface region of the semiconductor in that it is disordered and contains many trapping states. The grain growth on annealing will reduce the density of trapping states at grain boundaries, so increasing the fraction of the charge that is mobile.

- 32 -

It is found that annealing greatly increases the resistivity of the semiconductor, which is thought to be due to a reduction in bulk crystallite carrier density as a consequence of diffusion of impurities and defects during the anneal<sup>(13)</sup>.

## 2.5 DESCRIPTION OF DEVICES ON SUBSTRATE

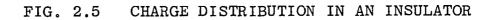

The layout of the devices on one half of the substrate is shown in Fig. 2.6, and the construction of a thin film transistor in Fig. 2.7. The channel length L and width W are marked on the drawing. The layout of the slide was symmetrical about the centre line in order to provide two halves prepared identically for certain experiments on post-deposition treatments, one half being used as a control.

The devices deposited on each half of the slide are as follows (the numbering refers to the designations on Fig. 2.6):

i. 9 thin film transistors, 8 small and 1 large

ii. 3 Al-SiO<sub>2</sub>Al metal-insulator-metal capacitors.

iii. Semiconductor bar for resistivity measurement.

iv. Semiconductor sample for Hall effect measurement.

v. Device for measurement of carrier mobility.

vi. A semiconductor slab for thermopower measurement.

vii. A metal-insulator-semiconductor structure (MIS).

for capacitance vs voltage measurements.

A brief description of each of these structures will now be given and the measurements done with each explained.

FIG. 2.6 LAYOUT OF SLIDE

- 34 -

FIG. 2.7 A THIN FILM TRANSISTOR

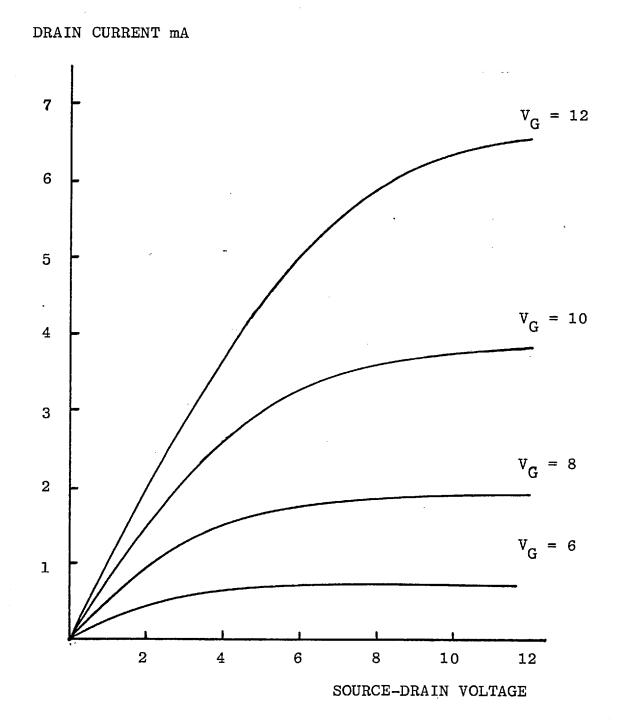

i. Thin Film Transistors - Apart from the individual experiments described subsequently, the drain current vs gate and drain voltage characteristics were measured on a curve tracer (Tektronix Type 575). A typical characteristic is shown in Fig. 2.8.

ii. M-I-M Capacitors - These devices were used to check the quality of the insulator layer on each slide, and to measure the insulator capacitance per unit area for subsequent use in analysing experimental results.

iii. Resistivity Measurement - This is a conventional four point measurement of the resistivity of the semiconductor film.

iv. Hall Effect - This measurement proved impossible because of the very high resistivity of the annealed cadmium selenide film. The measurement is however possible on unannealed films.

v. Carrier Mobility - The carrier mobility in the annealed semiconductor film was measured by a method due to Van Heek<sup>(14)</sup>. This is a modification of the usual Hall effect experiment to enable measurements to be done on very high resistivity semiconductor films.

vi. Thermoelectric (Seebeck) Effect - This is simply a rectangular area of cadmium selenide film to which contact may be made by hot and cold probes, between which a thermoelectric potential is developed. From this result the charge carrier density in the film may be calculated.

FIG. 2.8 TFT CHARACTERISTICS

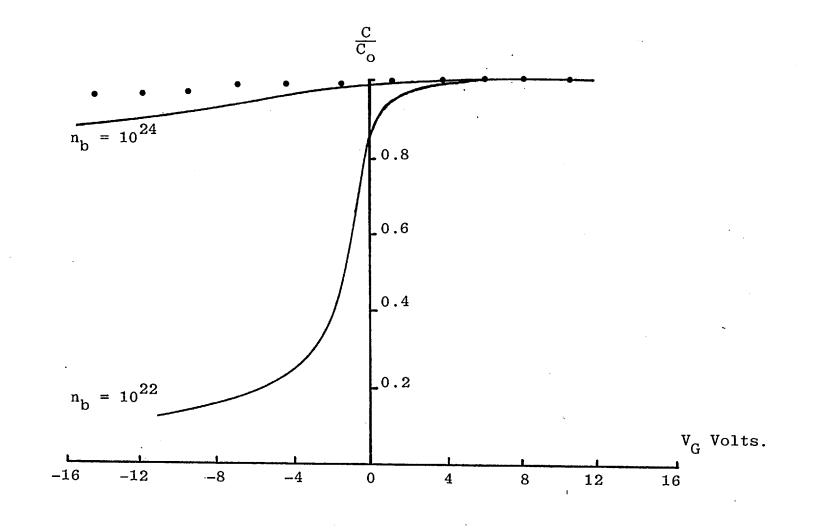

vii. Metal-insulator Semiconductor Device -This structure is used to measure the variation of spacecharge capacitance with field plate voltage, which is a well tried technique for determining the semiconductor doping density<sup>(15)</sup>.

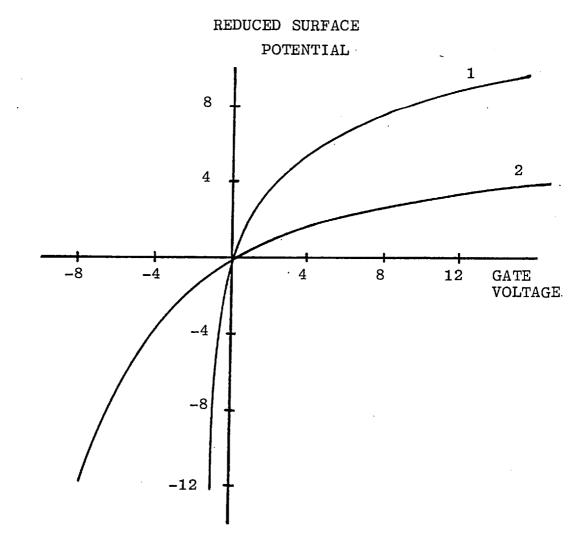

#### 2.6 MEASUREMENTS OF SEMICONDUCTOR PROPERTIES

This section describes the results of measurements made on the evaporated, annealed, cadmium selenide semiconductor which is the current-carrying layer in the completed thin film transistor. These measurements were done for the following reason. The original measurements of the trap density in the insulator of a TFT, described by Anderson, (16) used certain properties of the semiconductor in the interpretation of the results. Specifically, the variation of energy of the conduction-band edge at the semiconductor-insulator interface with gate field was This is a straightforward calculation (see for required. example Many, Goldstein and Grover $^{(17)}$  or Frankl $^{(18)}$ ). To carry out the calculation it is necessary to know the free carrier density in the bulk of the semiconductor. It was in order to measure this quantity accurately in the semiconductor films of the present devices that these measurements were made.

Evaporated semiconductor films such as these are of course polycrystalline, whereas the mathematical treatment used in the calculations was derived under the assumption of a single crystal material. It was at first thought that errors due to this difference would not be too severe; this was however found not to be the case.

- 38 -

### 2.6.1 Measurements and Results

The measurements performed using the different structures deposited on the substrate have been listed in Section 2.5. The measurements and their results will now be described in greater detail.

A well tried method of determining the bulk free carrier density is by measurement of the variation of space charge capacitance with applied gate voltage of a metalinsulator-semiconductor three layer structure. By a simple analysis it is possible to deduce the value of the carrier density in the semiconductor. The methods have been described in detail, and the necessary equations are given in graphical form, by Zaininger and Heiman<sup>(15)</sup>. A high carrier density results in a small variation of capacitance with gate voltage.

A measured capacitance-voltage curve is shown in Fig. 2.9. Also plotted are theoretical curves for different values of carrier density. The experimentally measured curve is seen to exhibit very little variation of capacitance, indicating a high carrier density in the cadmium selenide film. A full analysis of the experimental data shows that the semiconductor carrier density is greater than  $10^{24}$ m<sup>-3</sup>, which would mean that the semiconductor is degenerate.

A further means of determining the density of carriers in the semiconductor is to measure the thermoelectric power, or Seebeck co-efficient. The Seebeck effect is the phenomenon whereby a thermal gradient maintained in a semiconductor causes the appearance of an electric field. The

## FIG. 2.9 CAPACITANCE-VOLTAGE CURVES

- 40 -

effect is due to the increased thermal energy of the charge carriers in the material at the higher temperature compared to those at the lower. Some of the higher energy carriers drift along the thermal gradient, the concentration gradient of charge thereby produced setting up a counteracting electric field.

The measurement was carried out by fixing two thermocouples to the ends of a sample of semiconductor on the substrate, with a heated block being clamped to one end. A temperature difference is then set up across the sample and measured with the thermocouples. The potential difference set up across the sample is also measured using the thermocouple wires, a correction being made for the Seebeck effect in the thermocouple wire. The quotient of the two quantities, temperature drop and potential difference, is the Seebeck coefficient.

The Seebeck coefficient  $Q_s$  is related to the bulk carrier density  $n_b$  and the conduction band density of states  $N_c$  by the formula:

$$Q_{\rm s} = -\frac{k}{q} \left[ \ln \frac{N_{\rm c}}{n_{\rm b}} + \epsilon \right]$$

k is Boltzmann's constant, q the electronic charge and  $\epsilon$ a parameter which depends on the scattering process in the semiconductor, having a value in the range zero to two. Lacking any better knowledge, the value of  $\epsilon$  is taken as one. For cadmium selenide the value of N<sub>c</sub> is  $1.17 \times 10^{24} m^{-3}$ .

The Seebeck coefficient was measured on many samples. In all cases the observed values were in the range 0.5 -1.0mV/K. Using the equation above, these values correspond

- 41 -

to carrier densities in the range 3 x  $10^{19} - 10^{22} \text{m}^{-3}$ .

It will be noticed that these values are very different from those obtained from the C-V measurement.

It is clear that all is not well with these results. A further pair of measurements was made in an attempt to clarify the situation.

The first of these is measurement of the resistivity of the semiconductor film. This was done with a standard four point measurement using the structure deposited for this purpose on the substrate. The current in the sample was supplied by a dry battery, the voltage across the second pair of contacts being measured with a Keithley 616 electrometer. Because of the sample resistance, the high input impedance of the electrometer was essential.

The majority of the samples measured were found to have a resistivity in the range  $10^2 - 10^3$  ohm metre. The conductivity (reciprocal of resistivity) is the product of the carrier density, the carrier mobility and the charge on the electron. From the resistivity the product of carrier density and mobility may therefore be found, and for the range of values measured is of order  $10^{21}-10^{22}$ (S.I. units).

It is necessary to measure the carrier mobility in order to obtain the carrier density. The usual way would be to utilise the Hall effect in conjunction with a measurement of resistivity, to obtain both mobility and density of charge carriers separately. The annealed cadmium selenide is however of such a high resistivity that the current density that can be achieved with reasonable voltages is very small. Consequently the Hall voltage to be expected is also small. It was found in practice that the Hall voltage was immeasurably small, being far below the system noise level.

One way around this problem is to use a more sensitive but more complicated method, the A.C. Hall effect. This allows detection of very much smallerHall voltages which would be noise-dominated in a conventional D.C. measurement. This approach was considered and indeed some preliminary experiments performed, but was abandoned in favour of a modified method, due to van Heek<sup>(14)</sup> which allows the measurement of mobility in high resistivity materials. The modification consists essentially of transforming the circuit so that currents rather than voltages are measured, currents being much easier to measure in a high impedance circuit than voltages. The method of measurement is described in the paper by van Heek to which the reader is referred for further details.

Using this method the mobility of the charge carriers in the semiconductor films has been measured on many samples. The values of mobility found have generally been in the range  $10^{-3}-10^{-2}m^2/V$  sec. Taken with the results of the resistivity measurements, these figures give a range of values for the carrier density of  $10^{18}-10^{20}m^{-3}$ .

Several different measurements of the carrier density in thin semiconductor films have been described, and the results obtained from each given. The reason for the concentration on charge carrier density in these experiments and discussions is that it is the fundamental quantity in

- 43 -

any calculations based on the properties of a semiconductor. A considerable variation in the values of carrier density has been found, and in the next section the reasons for this and the consequences will be discussed.

### 2.6.2 Discussion of Results

To sum up the results of the experiments described in the preceding section, measurements of the semiconductor free carrier density were made by various methods. The results of these measurements were not consistent with one another, the C-V method giving a carrier density of approximately  $10^{24} \text{m}^{-3}$ , with the other methods giving results in the range  $10^{18} - 10^{22} \text{m}^{-3}$ . For single crystal semiconductor samples the results would be expected to be in good agreement with one another, so these inconsistencies are an indication that the single crystal semiconductor ideas and analysis are not applicable to evaporated thin films. This means that the calculation of the position in the energy gap of the semiconductor conduction band edge with gate field cannot be expected to give usable results, since a treatment assuming single crystal behaviour was used.

This in turn means that the interpretation of experiments on the trapping process in thin film transistors, which uses such calculations, will not be justified. Consequently the type of trap density measurements at first performed were abandoned, and an alternative method of obtaining the trap density sought. An attempt was made nevertheless, to interpret the results of the semiconductor measurements.

- 44 -

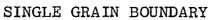

Evaporated semiconductor films are polycrystalline, that is, they consist of many individual grains, the regions of contact between the grains constituting the grain boundary region. The properties of the grain boundaries are vastly different from those of the bulk, central region of the crystallites, so it is in these grain boundaries that the reasons for the behaviour of the material must be sought.

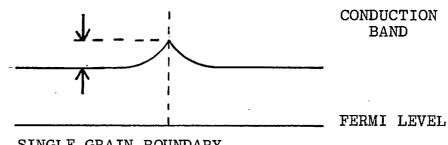

At the grain boundary, just as at the free surface of a semiconductor, their exists a high density of trapping states. Many of the charge carriers near the surface of the crystallite will become trapped at these sites, and a depletion space-charge region will be set up, extending back from the surface into the bulk of the crystallite. At each grain boundary there will be two such depletion regions, one in the crystallite on each site of the boundary. When drawn on an energy level diagram, the situation at a grain boundary is as shown in Fig. 2.10a.

A polycrystalline film consists of many such regions as in Fig. 2.10b. The conduction process and the modulation of conductivity by a gate field in such a material have been examined by Anderson<sup>(19)</sup>. The discussion of these processes which follows is based on this work. Following this, a possible explanation of the results of the measurements made is given.;

For conduction to occur in such a semiconductor film, charge carriers must travel through the material, traversing many such double-depletion regions in so doing. The intergranular depletion regions are energy barriers to the carriers in the semiconductor, and impede their progress

- 45 -

FIG.2.10 GRAIN BOUNDARY ENERGY BARRIERS

drastically. The result is that the carrier mobility in the polycrystalline film is much reduced from that found in a single crystal material.

For current flow in the material an electric field must be present. The field will increase the barrier height on one side of the boundary and reduce it on the other. The effects of many such barriers must be summed to fully understand the conduction process.

When a transverse electric field is applied, as in the thin film transistor, to modulate the current flowing, the situation becomes more complicated. Such a field deposits additional charge into the semiconductor. In single crystal material, the whole of this charge is mobile and so enhances the conductivity of the semiconductor. In the polycrystalline film, several processes occur.

The first is that some of the charges may be immobilised by trapping at the semiconductor-insulator interface (this also happens in a single crystal). Secondly, some of the charge will be immobilised in the traps at the grain boundaries. Being immobile, this charge does not contribute to the conductivity of the material. The remainder of the induced charge is free and so enhances the semiconductor conductance.

The extra charge trapped at the grain boundary is not only immobile, it also alters the charge distribution in the space charge region. In other words, the barrier height between crystallites is altered by the fraction of the induced charge that is trapped. The degree to which the motion of the carriers is impeded by the barriers is therefore altered, that is, the mobility is changed. This of course, changes the conductivity.

There are therefore two ways in which the conductivity of a polycrystalline semiconductor film is modulated; the usual modulation of carrier density and a modulation of mobility by variation of the height of the intergranular barriers. It will be realised therefore that the process is much more complex than for a single crystal material, and that to interpret the results of trapping experiments on the basis of the present understanding would be unjustified.

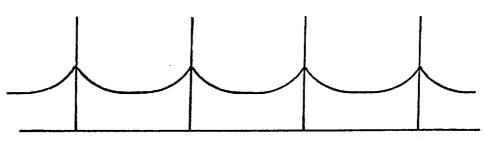

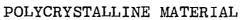

A possible explanation of the variations in the results of the different measurements of carrier concentration is suggested by these ideas. It will be recalled that the measurement by the C-V method resulted in a much higher value than either the resistivity or thermopower measurements. A fundamental difference between the C-V measurement and the others is that, with respect to the grain boundaries, the former is a 'parallel' measurement while the latter are 'series' measurements. The meanings of these terms are explained below with reference to Fig. 2.11.

Since the semiconductor is in the form of a thin film the number of crystallites down through its thickness is very much smaller than the number along the length of the film. In fact, it is often the case that the grain size in such films is approximately equal to the film thickness, so that there are then no grain boundaries through the depth of the film.

- 48 -

## FIG. 2.11 SERIES AND PARALLEL CURRENT FLOW

In the C-V measurement, where the capacitance is measured between the semiconductor and the gate electrode, the current flow is perpendicular to the plane of the film. parallel to the grain boundaries and so no current flows across the grain boundaries. The semiconductor with grain boundaries can be considered as two capacitors in parallel, one consisting of bulk semiconductor and the other of the grain boundary depletion regions. The capacitance of two capacitors in parallel is their sum, which means that the greater capacitance dominates the measurement. In the case of the semiconductor the higher capacitance is associated with the higher carrier density, which means the bulk material rather than the depletion regions. The value of carrier density obtained is therefore that of the bulk region of thecrystallites.

In the measurements of resistivity and thermopower on the other hand, current or charge flow is in the plane of the semiconductor film, and carriers have to cross the intergrain energy barriers. In these cases the semiconductor can be regarded as a series circuit of two components, one for the semiconductor bulk and one for the depletion regions. In the case of the resistivity measurement the components are resistances, and for the Seebeck measurement they are voltage sources. When measuring a series circuit of either resistances or voltage sources, the result is the sum of the individual components. Therefore, the larger component dominates.

In the case of the resistivity, this means the most resistive material, which is the depletion region. This

- 50 -

means that the carrier density value obtained is that in the depletion region, which is much less than that in the bulk.

In the case of the thermopower measurement, the material with the highest thermopower is again the depletion region, because of the inverse relationship between thermopower and carrier density. Consequently the carrier density measured will again be that of the depletion region.

This discussion has necessarily been entirely qualitative; to analyse properly the results of the experiments using these concepts it is necessary to consider mathematically the way in which the contributions of the different regions in the semiconductor sum to give the overall effect. This has been investigated by Anderson.

If the values of carrier density of  $10^{24} \text{m}^{-3}$  and  $18^{18} \text{-} 10^{22} \text{m}^{-3}$  are taken as being the carrier densities in the bulk and at the top of the barrier respectively, it is possible to estimate the barrier height. The carrier density at the top of the barrier n<sub>g</sub> and in the bulk n<sub>b</sub> are related by

$$n_g = n_b \exp\left(-\frac{E_b}{kt}\right)$$

where  $E_b$  is the barrier height (Fig. 2.10). For the carrier density values given above, the corresponding range of barrier heights is 0.12 - 0.35 eV.

Values quoted in the literature for barrier heights are generally considerably less than this. Barna et al<sup>(20)</sup> measured barrier heights of 0.01 - 0.025 eV in evaporated amorphous germanium films. Okuyama<sup>(21)</sup>, working with tellurium films, found barrier heights between 0.009 and

- 51 -

0.035 eV. Anderson<sup>(22)</sup>, in measurements on CdSe thin film transistors of the type used in the present work, calculated a barrier height of 0.15 - 0.2 eV, which is in reasonable agreement with the value obtained above.

In conclusion, the properties of the evaporated semiconductor are still not completely understood, and a considerable amount of work remains to be done.

#### **REFERENCES – CHAPTER 2**

- (1) W. Shockley and G.L. Pearson, Phys. Rev. <u>74</u> 232 (1948)

- (2) I. Tamm, Physick. Z. Sowjetunion 1 733 (1932)

- (3) W. Shockley, Phys. Rev. 56 317 (1939)

- M.M. Atalla, E. Tannenbaum and E.J. Scheibner,

Bell. Syst. Tech. J. 38 749 (1959)

- (5) S.R. Hofstein and F.P. Heiman, Proc. I.E.E.E. <u>51</u> 1190 (1962)

- P.K. Weimer, in "Physics of Thin Films" Vol. 2

Eds. G. Hass & R.E. Thun, Academic Press,

London, (1964)

- P.K. Weimer, Thin Film Field Effect Transistors, in

"Field Effect Transistors", Eds. J.T. Wallmark &

H. Johnson, Prentice-Hall, Englewood Cliffs N.J.

(1966)

- (8) E.H. Snow, A.S. Grove, B.E. Deal and C.T. Sah,

J. Appl. Phys. 36 1664 (1965)

- (9) F.P. Heiman and G. Warfield, I.E.E.E. <u>ED-12</u> 167 (1965)

- (10) T.H. Ning, C.M. Osburn and H.N. Yu, J. Appl. Phys. <u>48</u> 286 (1977)

- (11) M.J. Lee, Proc. 7th Int. Vac. Congr. 1979 (Vienna 1977)

- (12) J.H. Fisher, M. Phil. Thesis, London University, (1973)

- (13) K.H. Norian, Thin Solid Films 47 195 (1977)

- (14) H.F. Van Heek, Solid State Electronics <u>10</u> 268 (1967)

- (15) K.H. Zaininger and F.P. Heiman, Solid State Technology 13 No.5 p 49; No.6 p 46 (1970)

- (16) J.C. Anderson, Phil. Mag. 30 839 (1974)

- (17) A. Many, Y. Goldstein and N.B. Grover,

"Semiconductor Surfaces", North Holland,

Amsterdam (1965)

- (18) D.R. Frankl, "Electrical Properties of Semiconductor Surfaces", Pergamon Press (1967)

- (19) J. C. Anderson, Thin Solid Films 37 127 (1976)

- (20) A. Barna, P.B. Barna, Z. Bodo, J.F. Pocza,

I. Pozsgai and G. Radnoczi, Thin Solid Films

23 49 (1974)

- (21) K. Okuyama, Thin Solid Films 33 165 (1976)

- (22) J.C. Anderson, Private Communication

## CHAPTER 3 SLOW STATE DENSITY MEASUREMENTS

## 3.1 INTRODUCTION

In this chapter are described the measurements made of the density of slow trapping states in the insulator of thin film transistors. Originally the results of these experiments were used to calculate the actual density of trapping states and their distribution in energy. For the reasons explained in the previous chapter this technique cannot be relied on, but the method used will be briefly described for the sake of completeness.

The first measurements of slow state density reported here were done using transistors of the type used by Anderson in the original slow trapping measurements<sup>(1)</sup>. The bulk of the present work however was done on the later generation of thin film transistors which were described in the previous chapter. The effects of changes in the fabrication conditions and annealing treatments on the slow trapping state density were investigated.

#### 3.2 EFFECT OF TRAPPING

As was shown in Section 2.3.2 of the previous chapter, charge trapping in the insulator of a TFT has the effect of altering the threshold voltage. This is the slow state trapping - slow in this context meaning that the time scale on which the trapping occurs is seconds or minutes.

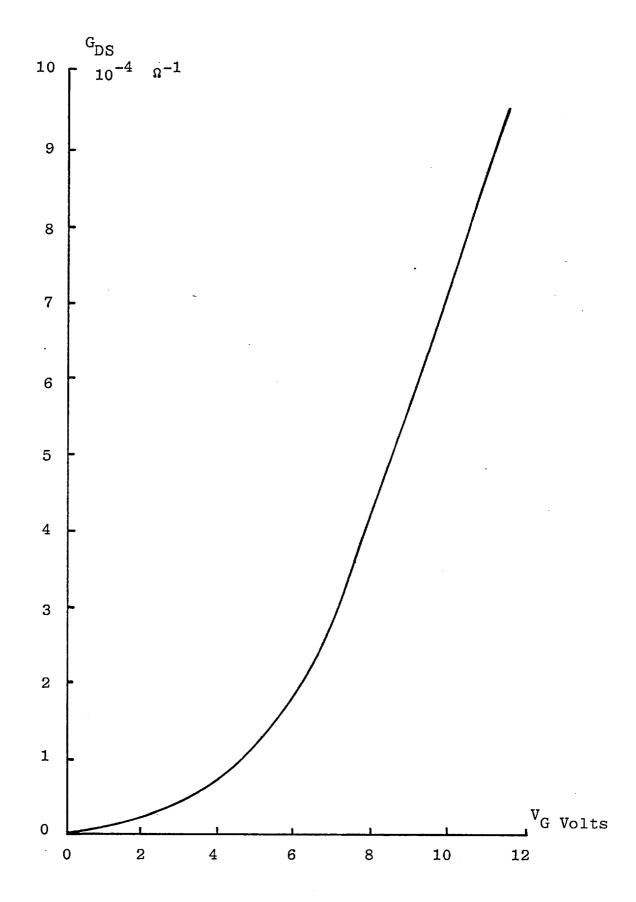

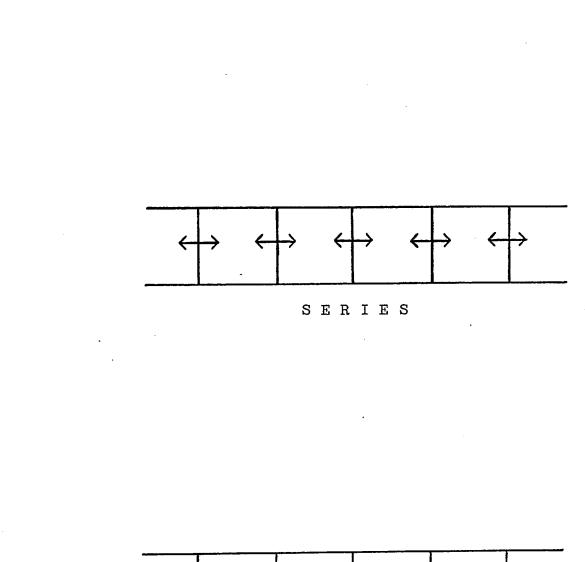

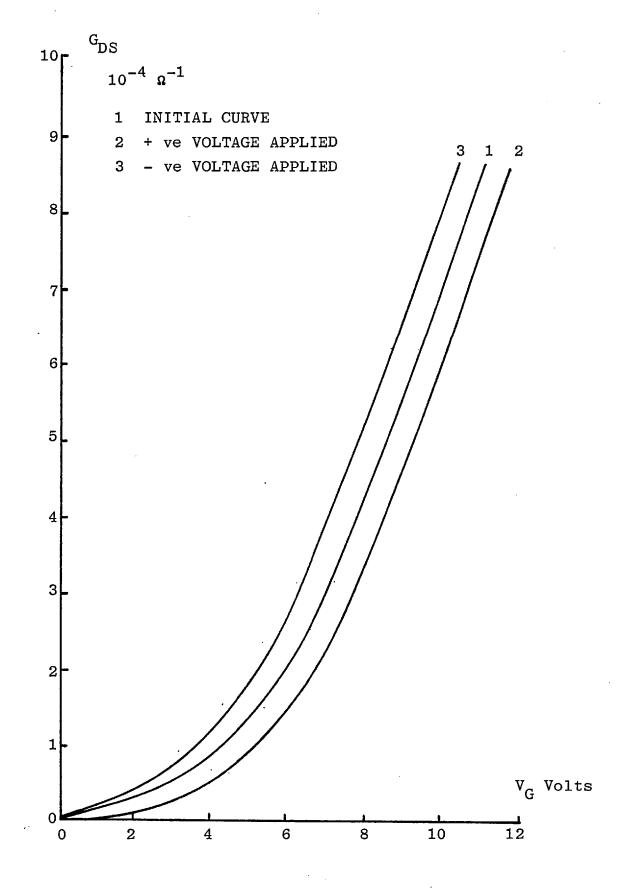

The direction of shift of threshold voltage is that a positive gate voltage causes the threshold voltage to shift to a greater positive voltage, while a negative gate voltage reverses the process, causing a shift towards negative values. This is illustrated in Fig. 3.1 in which the source-drain conductance G<sub>sd</sub> is plotted against gate voltage after three different gate voltages had been applied; zero, a positive and a negative voltage.

A threshold voltage shift in this direction indicates, for a device with an n-type semiconductor, that electrons are being trapped in the insulator when the gate voltage is positive and detrapped with a negative applied gate voltage.

## 3.3 MEASUREMENT OF SLOW-STATE DENSITY

In this section the way in which the slow state density is measured is explained. By density of slow trapping states is meant the area density of charges lost from the semiconductor. This is not a fixed density of trapping states which are filled before trapping ceases (the trapping has been observed to continue for at least 10 hours and was still continuing) so the number of trapped charges is measured in a certain fixed time.

The density of charge trapped is found by measuring the change in the threshold voltage of the TFT in the measurement time.

## 3.3.1 Experimental Method

There are two possible ways of measuring the change in threshold voltage, either gate voltage or source-drain conductance being maintained constant and the variation of the other quantity observed. In the former method as trapping occurs the conductance of the device falls. This change is measured and converted into a corresponding threshold voltage change by the use of the slope of the

- 56 -

FIG. 3.1 EFFECT OF SLOW STATE DRIFT ON TFT CHARACTERISTICS

conductance-voltage graph. The alternative method is to adjust the gate voltage so as to maintain a constant conductance, the change in voltage necessary to achieve this being the threshold voltage shift. The latter method was used for these measurements. The measurement was carried out at different gate voltages, so enabling a plot of the variation of the density of trapped charge with gate voltage to be drawn.

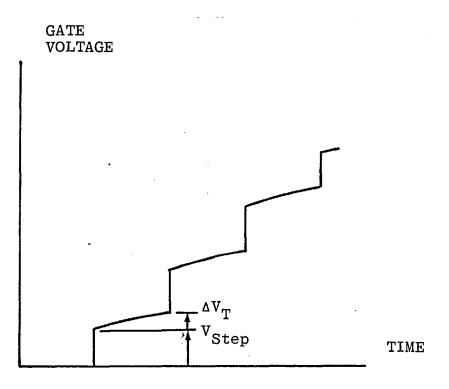

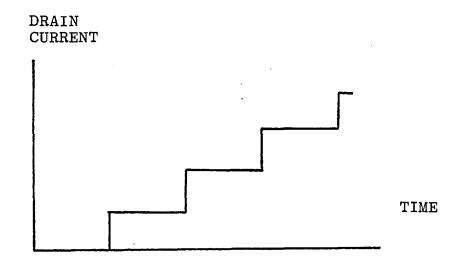

The experiment consisted of applying a certain increment in gate voltage,  $V_{step}$ , to the device and noting the drain current thereby caused to flow. The effect of trapping is to cause the drain current to reduce slowly following application of the gate voltage. The fall in drain current is counteracted by increasing the gate voltage as necessary to maintain the drain current at its initial value. The process of replacing the trapped charge in this way is continued for a fixed time, five minutes in these experiments. The change in gate voltage over this time is the threshold voltage shift caused by the trapping process. The gate voltage is then incremented by another step, the new drain current noted and the procedure repeated. The process is illustrated in Fig. 3.2 which shows the manner in which the gate voltage is varied with time.

In these experiments the initial gate voltage was zero and the maximum approximately twenty volts, this being the full range over which the transistors would be used. Measurements with negative gate voltages are not possible because the drain current is too small to be measured reliably. The uses made of the experimental data are detailed in the following sections.

- 58 -

# FIG. 3.2 GATE VOLTAGE-TIME SEQUENCE FOR SLOW STATE MEASUREMENT

- 59 -

## 3.3.2 Display of Results

The raw results of the experiment are measurements of the change in threshold voltage  $\Delta V_T$  and the corresponding gate voltage increment  $V_{step}$ . The first of these has supplied charge to be trapped in the trapping states, while the second has supplied charge to the semiconductor which is untrapped and supports conduction through the device.

The change in threshold voltage is converted into a change in trapped charge density by the usual equation:

$$\Delta n = C_0 \Delta V_T / q$$

$C_{o}$  being the insulator capacitance.

Each threshold voltage is converted into a density of trapping states in this way. This quantity is then normalised by division by the appropriate gate voltage increment  $V_{step}$ . This is then the area density of trapped charges per unit gate voltage, and is called the slow state density  $n_{ee}$ .

$$n_{ss} = \frac{C_o}{q} \frac{\Delta V_T}{V_{step}}$$

This is plotted as a function of the total active gate voltage. By this term is meant the gate voltage which has gone into supplying untrapped charge. This is simply the sum of the voltage increments  $V_{step}$ . Finally this is expressed in terms of insulator electric field to remove the dependence on insulator thickness.

## 3.3.3 Calculation of Trap Density

The initial reason for instituting these measurements was to use the results for the calculation of the density and distribution in energy of traps in the insulator. From the measurement the area density per gate volt is obtained, and is to be converted into the volume density per electron volt (eV). To do this it is necessary to know the relationship between gate voltage and semiconductor surface potential, and the depth in the insulator to which traps are filled. The former is a standard semiconductor calculation and the latter was calculated assuming that charge reaches the insulator traps by a tunneling process.

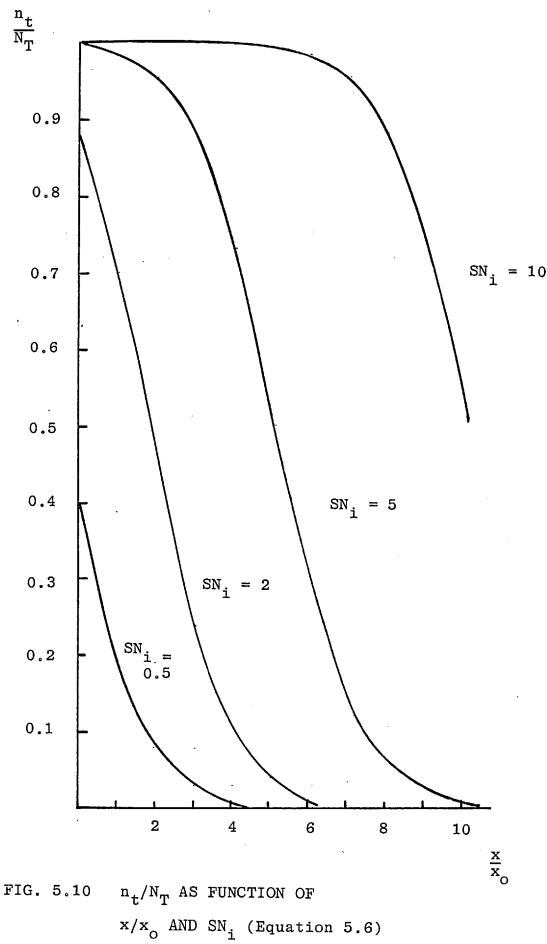

The mathematical treatment necessary to derive the relation between trap density and charge trapped in a certain time is fairly lengthy and so will not be given here. The basis of the theory is given in the paper by Anderson already cited, and the final result only will be given here. The equation which relates  $n_{ss}$  to the trap distribution in energy  $K(E_t)$  is:

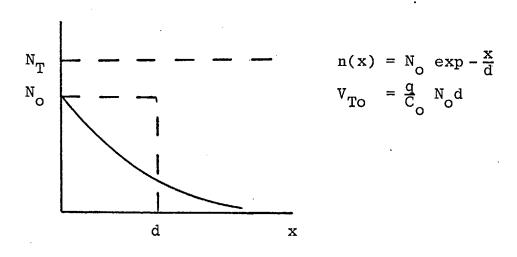

$$n_{ss} = K(E_t) \left[ \frac{x_m^2}{2x_o} + \frac{\Delta V_s}{\overline{V}_{step}} L_t \left\{ 1 - \exp\left(-\frac{x_m}{L_t}\right) \right\} \right]$$

$$x_m = \frac{1}{2\overline{K}_o} \ln (n_s \,\overline{\overline{v}} \, S \, t)$$

where

$$L_{t}^{2} = \frac{\varepsilon_{i}\varepsilon_{o}kT}{q^{2}K(E_{t})} \Delta V_{s}$$

$$K_{o}^{2} = \frac{2m^{*}}{h^{2}} (\Psi - E)$$

and

where  $\Psi$  is the height of the energy barrier between semiconductor and insulator, and E the kinetic energy of the electrons in the semiconductor.  $K_0$  is the wave-function decay constant, and is a characteristic length describing the electron wave-function in the insulator.  $K_0$  has a

- 61 -

slight dependence on gate field, through the variation in the energy barrier. This is sufficiently small as to be negligible.

in these equations is the insulator thickness, and x  $\mathbf{x}_{\mathrm{m}}$  is the maximum depth to which charge has been trapped in the time t. It is seen that it has a logarithmic dependence on time - this is a characteristic of the tunnelling process used in this model of the trapping. L<sub>+</sub> is a characteristic length related to the trapped charge distribution in the insulator,  $K(E_t)$  the trapping state density as a function of energy and  $\Delta V_s$  the change in semiconductor surface potential caused by the gate voltage increment  $K_{o}$  is the wave function decay constant for electrons V<sub>step</sub>. tunnelling into the insulator,  $n_s$  is the semiconductor surface charge carrier density, and  $\bar{v}$  the mean thermal velocity of the carriers in the insulator. The remaining symbols have their usual meanings.

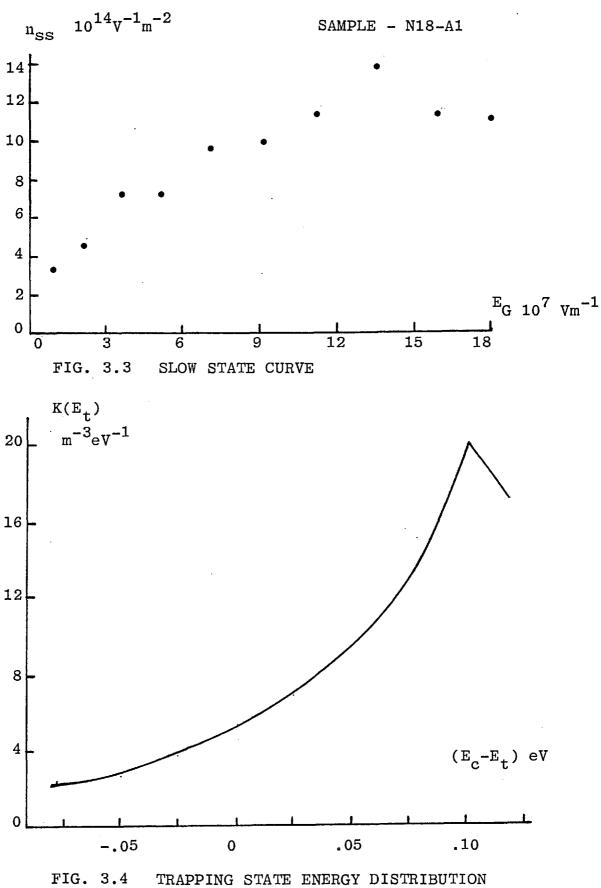

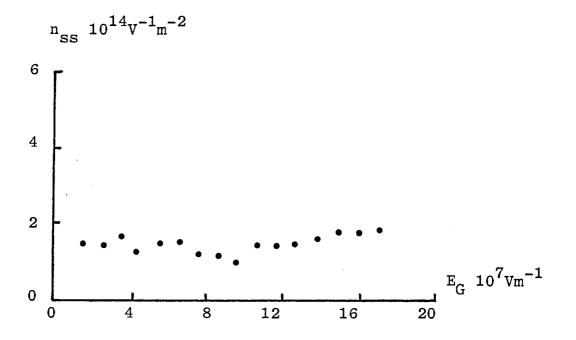

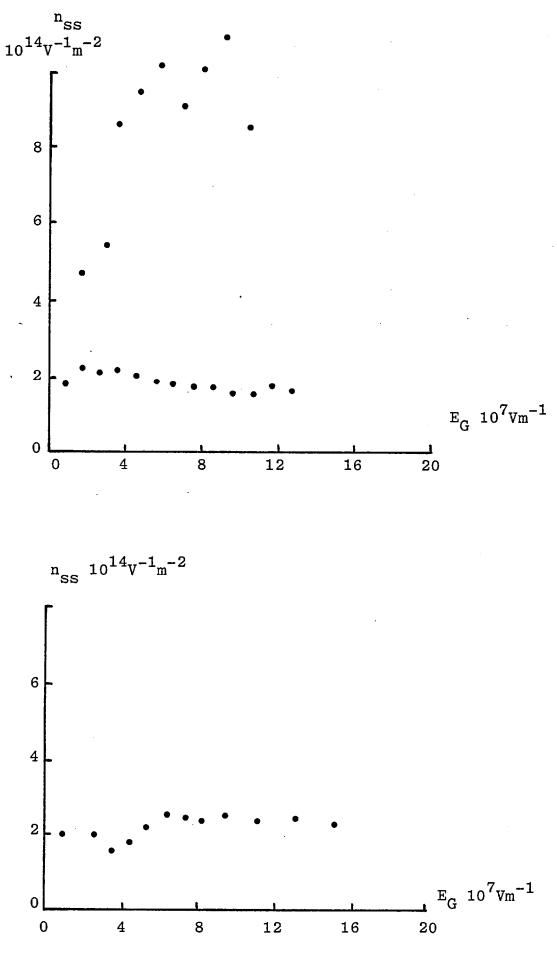

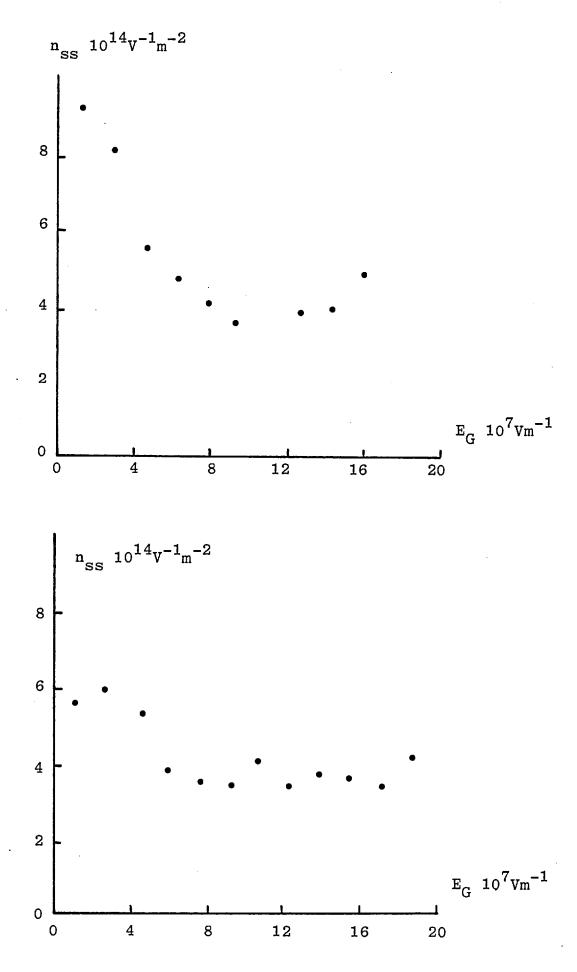

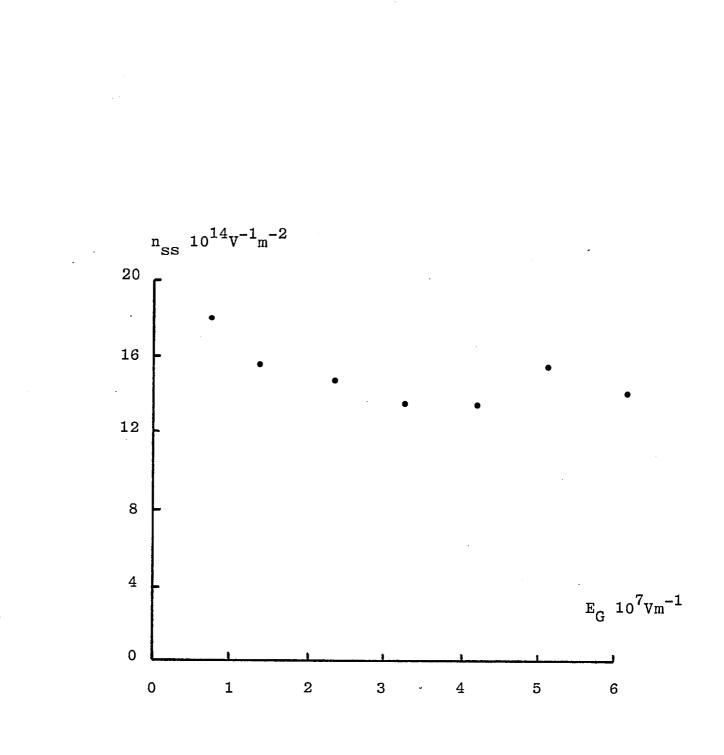

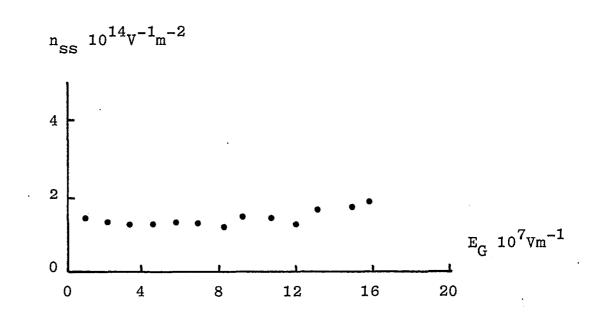

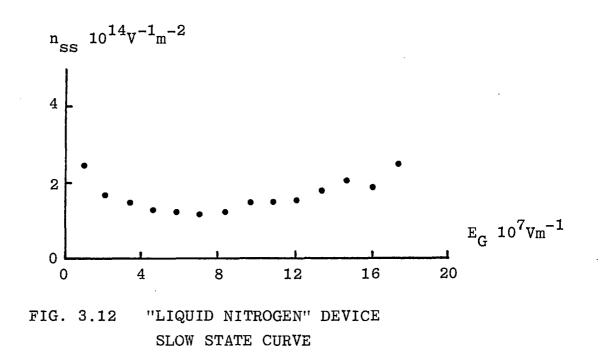

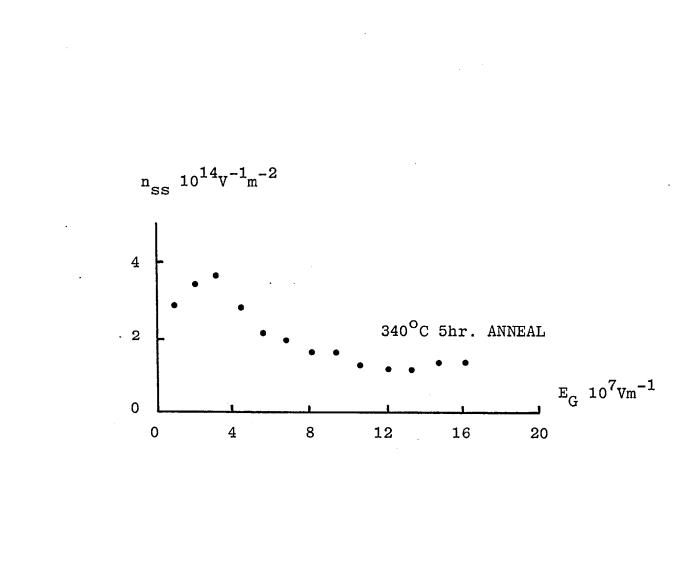

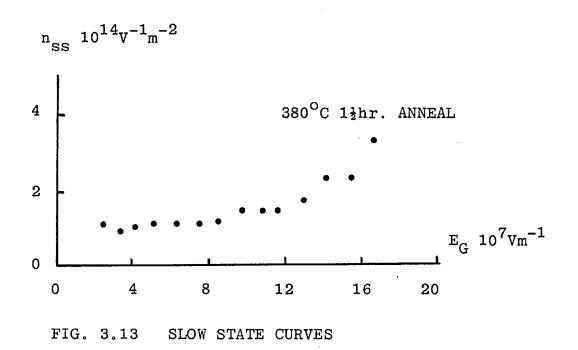

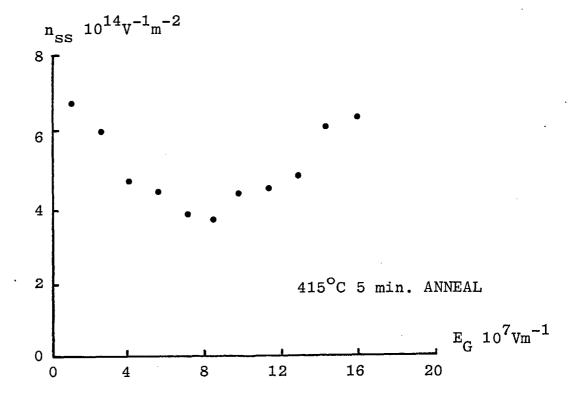

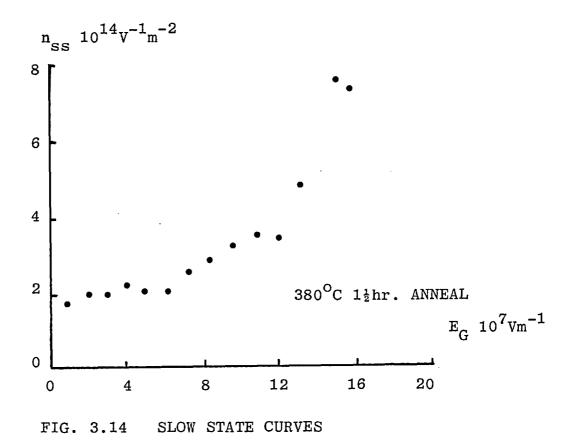

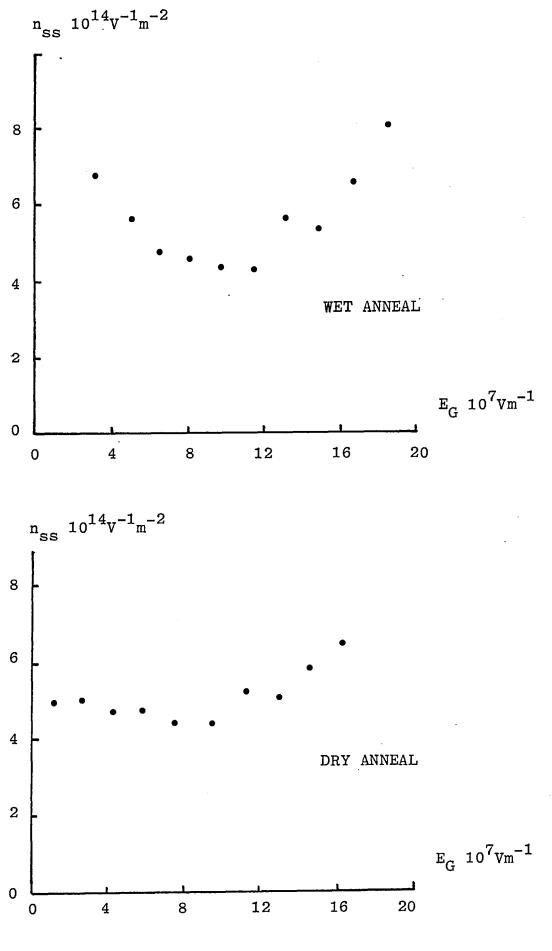

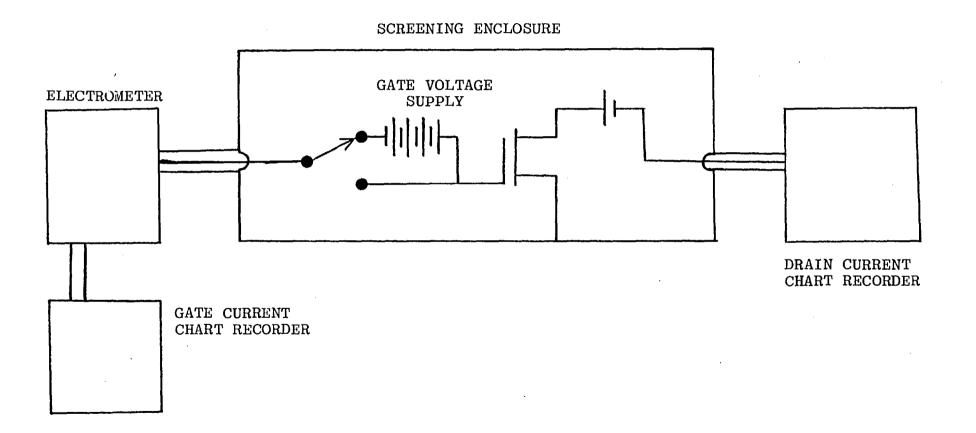

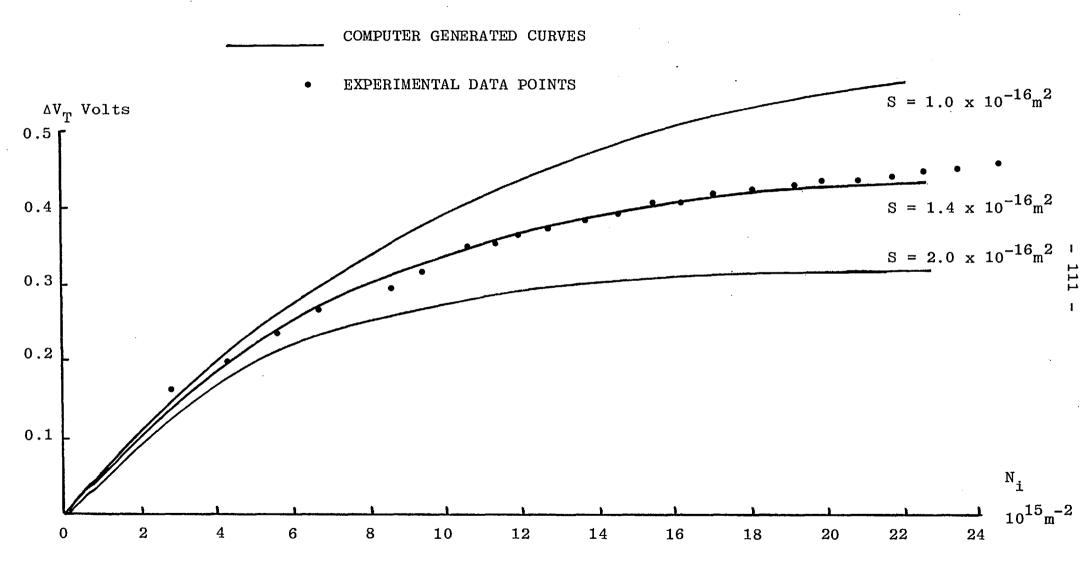

## 3.4 RESULTS OF SLOW STATE MEASUREMENTS