# IMPERIAL COLLEGE LONDON DEPARTMENT OF COMPUTING

## Automated Optimization of Reconfigurable Designs

Maciej Kurek

Submitted in part fulfillment of the requirements for the degree of Doctor of Philosophy in Computing of the Imperial College London and the Diploma of Imperial College London, September 2015

### Declaration of Originality

The work presented in this thesis is the result of my own original research. Wherever possible, references to the literature are provided and collaborative work is acknowledged.

### Copyright Declaration

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

#### Abstract

Currently, the optimization of reconfigurable design parameters is typically done manually and often involves substantial amount effort. The main focus of this thesis is to reduce this effort. The designer can focus on the implementation and design correctness, leaving the tools to carry out optimization. To address this, this thesis makes three main contributions.

First, we present initial investigation of reconfigurable design optimization with the Machine Learning Optimizer (MLO) algorithm. The algorithm is based on surrogate model technology and particle swarm optimization. By using surrogate models the long hardware generation time is mitigated and automatic optimization is possible. For the first time, to the best of our knowledge, we show how those models can both predict when hardware generation will fail and how well will the design perform.

Second, we introduce a new algorithm called Automatic Reconfigurable Design Efficient Global Optimization (ARDEGO), which is based on the Efficient Global Optimization (EGO) algorithm. Compared to MLO, it supports parallelism and uses a simpler optimization loop. As the ARDEGO algorithm uses multiple optimization compute nodes, its optimization speed is greatly improved relative to MLO. Hardware generation time is random in nature, two similar configurations can take vastly different amount of time to generate making parallelization complicated. The novelty is efficient use of the optimization compute nodes achieved through extension of the asynchronous parallel EGO algorithm to constrained problems.

Third, we show how results of design synthesis and benchmarking can be reused when a design is ported to a different platform or when its code is revised. This is achieved through the new Auto-Transfer algorithm. A methodology to make the best use of available synthesis and benchmarking results is a novel contribution to design automation of reconfigurable systems.

#### Acknowledgements

The first person I would like to thank is my supervisor Professor Wayne Luk. He has been a mentor and a friend to me since the final year of my undergraduate studies. I am most grateful for the trust and freedom he granted me. He always encouraged me to work on things I believe in, which others would consider risky or unconventional.

Special thanks to Tobias Becker, Sanjay Bilakhia, Thomas Chau, Giulia Ferretti, Xinyu Niu, Timothy Todman and Robert Wolstenholme for the help and advise they offered. The biggest challenge I faced during my research was to bring together the Bayesian optimization and reconfigurable computing worlds. All of them have helped me on numerous occasions by discussing my work, reviewing my papers and providing suggestions on how to better explain different aspects of work.

Special thanks to Stephen Weston. I have worked with Stephen during my internship at JPMorgan Chase during my first year of the PhD program, as well as at Maxeler Technologies during my write up period. Skills I learned during that time proved to be invaluable during my work on this Thesis. Furthermore, I would like to thank Steve Hutt and Florian Widmann, both of whom were my managers while working at Maxeler Technologies during my write up period. In particular, Steve has helped me develop a better, more thorough and precise approach to work.

I would like to thank Marc Deisenroth for his feedback on my late stage report and the help he has offered afterwards. He has been of great help in structuring the thesis and making the Bayesian Optimization components more approachable. His questions provided invaluable feedback.

Lastly, I would like to thank everyone in the Department of Computing at Imperial College London. That includes James Arram, Brahim Betkaoui, Pavel Burovskiy, Bridgette Cooper, Kit Cheung, Gabriel De Figueiredo Coutinho, Stewart Denholm, Paul Grigoras, Ce Guo, Liucheng Guo, Eddie Hung, Gordon Inggs, Qiwei Jin, Adrien Le Masle, Nicholas Ng, Shengjia Shao, David Thomas, Anson Tse, Shulin Yan, Jinzhe Yang. Hopefully I was not too much of an annoyance building countless numbers of bitstreams and constantly occupying our CAD machines.

### Dedications

To my parents,

For teaching me the value of hard work and all the support you have given me throughout all of those years, even if at times I did not seem as grateful as I should.

#### **Publications**

- M. Kurek and W. Luk, "Parametric Reconfigurable Designs with Machine Learning Optimizer", *International Conference on Field-Programmable Technology (FPT)*, 2012.

- M. Kurek, T. Becker and W. Luk, "Parametric Optimization of Reconfigurable Designs Using Machine Learning", International Symposium on Applied Reconfigurable Computing (ARC), 2013.

- M. Kurek, T. Liu and W. Luk, "Multi-objective Self-optimization of Reconfigurable Designs with Machine Learning", *Self-Awareness in Reconfigurable Computing Systems (SRCS)*, 2013.

- M. Kurek, T. Becker, T.C.P. Chau and W. Luk, "Automating Optimization of Reconfigurable Designs", *International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, 2014.

- T.C.P. Chau, M. Kurek, James S. Targett, J. Humphrey, G. Skouroupathis, A. Eele, J. Maciejowski, B. Cope, K. Cobden, P. Leong, P. Y.K. Cheung and W. Luk, "SMCGen: Generating Reconfigurable Design for Sequential Monte Carlo Applications", *International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, 2014.

# Contents

| 1 | Intr | oducti | ion                                                  | 33   |

|---|------|--------|------------------------------------------------------|------|

|   | 1.1  | Motiv  | ation                                                | 33   |

|   | 1.2  | Contri | ibutions                                             | 39   |

|   | 1.3  | Overv  | riew of the Thesis                                   | . 41 |

| 2 | Bac  | kgroui | nd                                                   | 43   |

|   | 2.1  | Recon  | afigurable Designs                                   | 43   |

|   |      | 2.1.1  | Applications of FPGAs                                | 46   |

|   |      | 2.1.2  | Reconfigurable designs as computation devices        | 47   |

|   | 2.2  | Design | n Development                                        | 48   |

|   |      | 2.2.1  | Design Development and Optimization Approaches       | 49   |

|   |      | 2.2.2  | Reconfigurable Design Optimization Problem Statement | 52   |

|   |      | 2.2.3  | Parameter Space                                      | 56   |

|   |      | 2.2.4  | Fitness Function and Constraints                     | 58   |

|   |      | 2.2.5  | Optimization Challenges                              | 59   |

|   | 2.3  | Mathe  | ematical optimization                                | 61   |

|   | 2.4  | Machi  | ine Learning                                         | 64   |

|   |      | 2.4.1  | Supervised Learning                                  | 64   |

|   | 2.5  | Surrog | gate Models for Experimental Design                  | 77   |

|   |      | 2.5.1  | Metaheuristics and Surrogate Models                  | 80   |

|   |      | 2.5.2  | Bayesian Optimization                                | . 81 |

|   | 2.6  | Concl  | usion                                                | 89   |

| 3 | Des  | ign by | Particle Swarm Optimization                          | 91   |

|   | 3.1  | MLO    | Optimization Approach                                | 93   |

|   | 3.2  | MLO    | Algorithm                                            | 94   |

|   |      | 3.2.1  | Latin Hypercube Sampling                             | 96   |

CONTENTS CONTENTS

|   |     | 3.2.2  | GP and SVM Training                            |

|---|-----|--------|------------------------------------------------|

|   |     | 3.2.3  | Particle Motion                                |

|   |     | 3.2.4  | Evaluate Best or Infill                        |

|   |     | 3.2.5  | Termination                                    |

|   | 3.3 | Evalua | ation                                          |

|   |     | 3.3.1  | Implementation                                 |

|   |     | 3.3.2  | Quadrature-based Financial Design              |

|   |     | 3.3.3  | Real-time Proximity Query (PQ) Design          |

|   |     | 3.3.4  | Stochastic Volatility Design                   |

|   |     | 3.3.5  | Robot Localization                             |

|   | 3.4 | Discus | sion                                           |

|   |     | 3.4.1  | Results                                        |

|   |     | 3.4.2  | Usability                                      |

|   | 3.5 | Conclu | ısion                                          |

| 4 | Dog | : b    | Efficient Global Optimization 127              |

| 4 | 4.1 | · ·    | Efficient Global Optimization 127 em Statement |

|   | 4.1 |        | GGO Approach                                   |

|   | 4.3 |        | GGO Algorithm                                  |

|   | 1.0 | 4.3.1  | Adaptive Sampling                              |

|   |     | 4.3.2  | GP and SVM Training                            |

|   |     | 4.3.3  | Infill                                         |

|   |     | 4.3.4  | Termination                                    |

|   | 4.4 |        | utational Complexity                           |

|   | 1.1 | 4.4.1  | Adaptive Sampling                              |

|   |     | 4.4.2  | Infill                                         |

|   |     | 4.4.3  | Dominant Components                            |

|   | 4.5 |        | ation                                          |

|   |     | 4.5.1  | Implementation                                 |

|   |     | 4.5.2  | Quadrature-based Financial Design              |

|   |     | 4.5.3  | Real-time Proximity Query Design               |

|   |     | 4.5.4  | Reverse Time Migration Design                  |

|   | 4.6 | Hardw  | vare Acceleration                              |

|   | 4.7 |        | sion                                           |

|   |     | 4.7.1  | Results                                        |

CONTENTS CONTENTS

|   |     | 4.7.2 Usabili | ty              |            |           |       |       |      |     |      |      |       | 158   |

|---|-----|---------------|-----------------|------------|-----------|-------|-------|------|-----|------|------|-------|-------|

|   | 4.8 | Conclusion    |                 |            |           |       |       |      |     |      |      |       | 159   |

| 5 | Des | ign and Know  | vledge Trans    | fer        |           |       |       |      |     |      |      |       | 161   |

|   | 5.1 | Problem State | ment            |            |           |       |       |      |     |      |      |       | 163   |

|   | 5.2 | Auto-Transfer | Approach        |            |           |       |       |      |     |      |      |       | 165   |

|   | 5.3 | Auto-Transfer | Algorithm       |            |           |       |       |      |     |      |      |       | 167   |

|   |     | 5.3.1 Knowle  | edge Transfer . |            |           |       |       |      |     |      |      |       | 169   |

|   | 5.4 | Evaluation    |                 |            |           |       |       |      |     |      |      |       | 174   |

|   |     | 5.4.1 Implen  | nentation       |            |           |       |       |      |     |      |      |       | 175   |

|   |     | 5.4.2 Cross-p | olatform, Quad  | drature-ba | ased Fi   | nanci | al .  |      |     |      |      |       | 177   |

|   |     | 5.4.3 Cross-j | olatform, Reve  | rse Time   | Migra     | tion  |       |      |     |      |      |       | 180   |

|   |     | 5.4.4 Related | l Designs, Sto  | chastic Vo | olatility | Desi  | gn ai | nd R | obo | t Lo | cali | zatic | n 181 |

|   | 5.5 | Discussion    |                 |            |           |       |       |      |     |      |      |       | 185   |

|   |     | 5.5.1 Results | 3               |            |           |       |       |      |     |      |      |       | 185   |

|   |     | 5.5.2 Usabili | ty              |            |           |       |       |      |     |      |      |       | 186   |

|   | 5.6 | Conclusion    |                 |            |           |       |       |      |     |      |      |       | 187   |

| 6 | Con | clusion and I | uture Work      |            |           |       |       |      |     |      |      |       | 189   |

|   | 6.1 | Summary of A  | chievements     |            |           |       |       |      |     |      |      |       | 189   |

|   | 6.2 | Future Work . |                 |            |           |       |       |      |     |      |      |       | . 191 |

|   |     | 6.2.1 Revisio | on of ARDEGO    | O          |           |       |       |      |     |      |      |       | . 191 |

|   |     | 6.2.2 Knowle  | edge Transfer . |            |           |       |       |      |     |      |      |       | 194   |

|   |     |               |                 |            |           |       |       |      |     |      |      |       |       |

CONTENTS CONTENTS

## Acronyms

ACO Ant Colony Optimization. 65

ALU Arithmetic Logical Unit. 48

ANN Artificial Neural Network. 67

API Application Programming Interface. 51, 52, 111, 195

**ARD** Automatic Relevance Determination. 76, 103, 112, 115, 119, 121, 122, 125–127, 140

**ARDEGO** Automatic Reconfigurable Design Efficient Global Optimization. 7, 32, 33, 35, 36, 44, 45, 129–131, 134–138, 141, 143–145, 148–158, 162–167, 172, 174, 175, 181, 184, 192, 193, 196, 197, 199

**ASIC** Application Specific Integrated Circuits. 35, 38, 47–50

**BRAM** Block RAM. 34, 48, 159, 190, 191, 199

**CAD** Computer Aided Design. 40, 41, 54, 80, 81, 130, 165

CAM Content Addressable Memory. 48

CPLD Complex Programmable Logic Device. 38, 48

**CPU** Central Processing Unit. 43, 50, 51, 151, 161, 181

**DSU** Debug Support Unit. 48

**EGO** Efficient Global Optimization. 7, 29, 32, 45, 85–88, 90, 91, 130, 136–138, 142, 143, 145, 196, 197

EI Expected Improvement. 85, 86, 89–91, 99, 137, 142–147, 150, 157, 192, 197

Acronyms Acronyms

FIR Finite Impulse Response. 39, 42

**FPGA** Field Programmable Gate Array. 27, 28, 35, 37–39, 43, 47–52, 55, 57–60, 62, 64, 65, 91, 93, 94, 109–111, 126, 129, 148, 149, 153, 158–163, 177, 181–184, 186, 187

**GA** Genetic Algorithm. 65

GbSA Galaxy-based Search Algorithm. 65

**GP** Gaussian Process. 28, 29, 34, 73–79, 82–85, 89, 90, 94, 98–100, 102, 103, 105, 109, 111, 124, 135–137, 139, 140, 142, 143, 145–147, 151, 162, 163, 174, 181, 197, 199

GP-UCB Gaussian Process – Upper Confidence Bound. 84, 90, 198

**GPU** Graphic Processing Unit. 52

HDL Hardware Description Language. 27, 38, 49, 52

**HLL** Higher Level Language. 38, 51, 52

**HLS** High Level Synthesis. 52, 195

**HPC** High Performance Computing. 50

**HSM** Hybrid Surrogate Model. 83

IP Intellectual Property. 49

**IWDP** Intelligent Water Drops. 65

**LUT** Lookup Table. 34, 48, 49, 110, 149, 176, 182, 190, 191

**MLO** Machine Learning Optimizer. 7, 29–31, 35, 44, 45, 93–95, 97, 98, 100–102, 104, 105, 107–112, 115, 118–120, 122, 124–126, 129, 135, 148, 150, 152, 153, 155–157, 162, 163, 195–197, 199

MOMLO Multiobjective Machine Learning Optimizer. 34, 199, 200

MPI Most Probable Improvement. 90

PAR Place and Route. 31, 39, 58, 61–63, 110, 117, 130, 155, 163, 182, 190, 201

Acronyms Acronyms

- **PES** Predictive Entropy Search. 90

- **PQ** Proximity Query. 28, 31, 32, 34, 39, 57, 58, 95, 109, 110, 117, 118, 131, 148, 149, 153, 155, 163, 182, 198, 200

- **PSO** Particle Swarm Optimization. 30, 65, 83, 93, 97–100, 104–107, 109, 124, 136, 143, 144, 147, 148

- **RBF** Radial Basis Function. 83

- **RTM** Reverse Time Migration. 32, 34, 131, 148, 149, 156, 157, 162–164, 167, 181, 182, 186, 187, 192

- RVM Relevance Vector Machine. 100, 137, 143, 199

- SA Simulated Annealing. 65

- **SMC** Sequential Monte Carlo. 95, 119, 181, 187, 188

- **SVM** Support Vector Machine. 28, 66, 69–72, 79, 82, 91, 97–100, 102, 103, 107, 109, 111, 112, 117, 136, 137, 139, 140, 142, 143, 146, 147, 151, 155, 162, 163, 181, 198, 201

Acronyms Acronyms

# List of Figures

| 1.1 | Some of many possible Field Programmable Gate Array (FPGA) boards:            |    |

|-----|-------------------------------------------------------------------------------|----|

|     | XMC-FPGA05D XMC/PM and PMC-FPGA05 with Xilinx Virtex-5 FP-                    |    |

|     | GAs from Curtiss Wright [1] and a Nallatech 395 with Atera Stratix V          |    |

|     | FPGA [2]                                                                      | 34 |

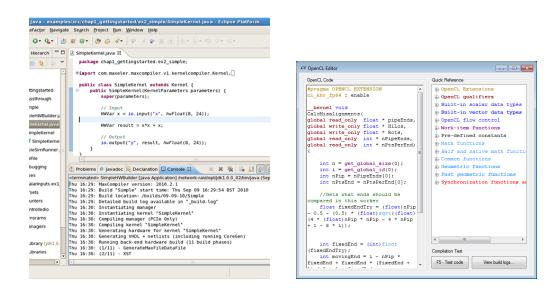

| 1.2 | Some of many available Hardware Description Language (HDL)s and their         |    |

|     | infrastracture: Maxeler MaxJ with MaxIDE [3] and OpenCL [4] with              |    |

|     | OpenCL Editor [5]                                                             | 35 |

| 1.3 | A sample script used for exhaustive search over a range of design parameters. |    |

|     | The code generates hardware configuration, builds the design and executes     |    |

|     | a benchmark. Finally the results are analyzed                                 | 36 |

| 1.4 | Automated parameter optimization algorithm. It takes as input the hard-       |    |

|     | ware generation scripts along with the parameter space definition             | 37 |

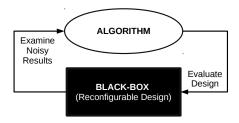

| 1.5 | Optimization of reconfigurable designs as a black-box optimizaton problem.    | 37 |

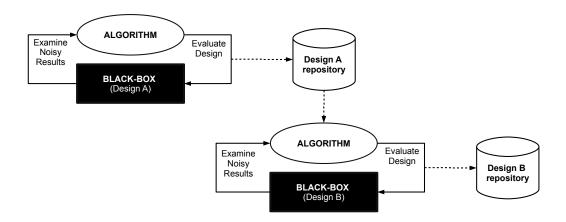

| 1.6 | Automated parameter optimization extended with a design optimization          |    |

|     | repository. Extra information can improve both the speed and accuracy of      |    |

|     | the optimization                                                              | 39 |

| 1.7 | Knowledge transfer in black-box optimization of reconfigurable designs        | 40 |

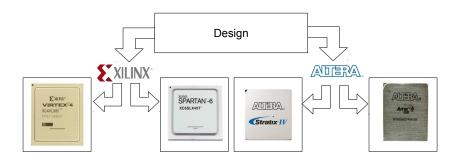

| 2.1 | FPGA design and a small subset of available platforms. Courtesy of Altera     |    |

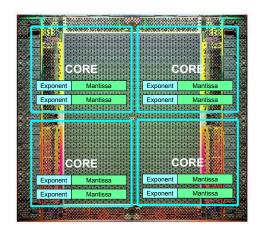

|     | Corporation [6] and Xilinx, Inc. [7]                                          | 44 |

| 2.2 | Two configuration of a reconfigurable design. One configured with 4 cores     |    |

|     | and narrower numerical implementation, one with two cores and wider           |    |

|     | numerical representation                                                      | 46 |

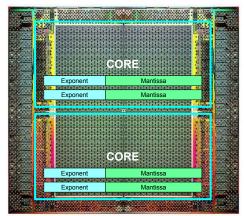

| 2.3 | FPGA Heterogeneous System. Courtesy of Intel Corporation [8], Samsung         |    |

|     | Electronics Co., Ltd [9] and Xilinx, Inc. [7]                                 | 47 |

| 2.4 | Simple loop suitable for FPGA based heterogeneous system                      | 48 |

| 2.5 | Two loop code                                                                 | 49 |

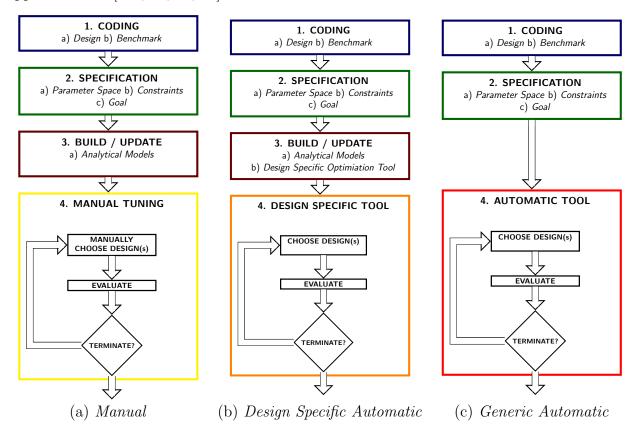

| 2.6  | Different optimization approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

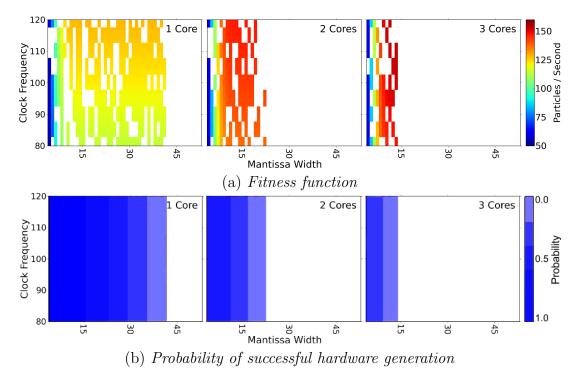

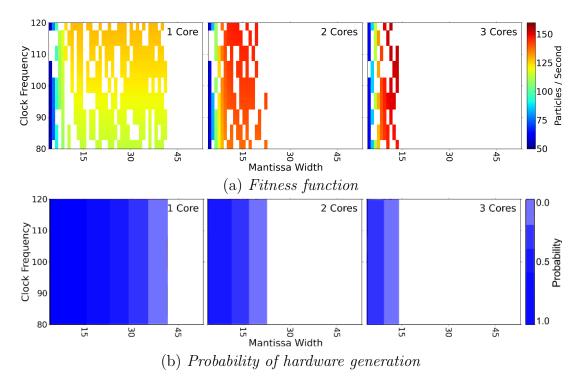

| 2.7  | Proximity Query (PQ) design throughput fitness function [46] (a) and probability of successful hardware generation visualization (b). Image (a) is based on real hardware generation, the design was implemented for Maxeler MPC-X1000 system with a Xilinx Virtex-6 XC6VSX475T FPGA. White patches represent unsuccessful hardware generation. In (b) green line marks the boundary between the valid and invalid region, white area is the invalid region. The probability figure is for demonstration purpose only, the numbers do not demonstrate the actual chance of successful hardware generation | 55 |

| 2.8  | Categorical parameter. Courtesy of Altera Corporation [6] and Xilinx, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56 |

| 2.9  | Continuous parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56 |

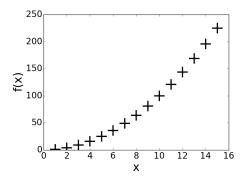

| 2.10 | Uniformly discrete parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57 |

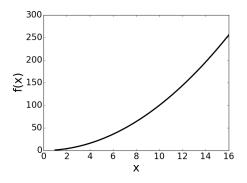

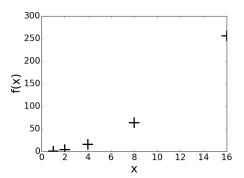

| 2.11 | Non-uniformly discrete parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57 |

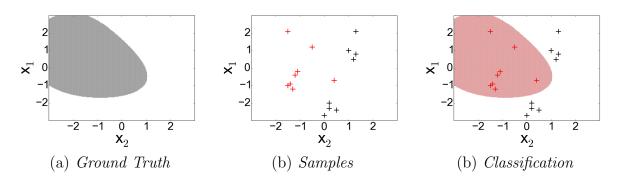

| 2.12 | Classification example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

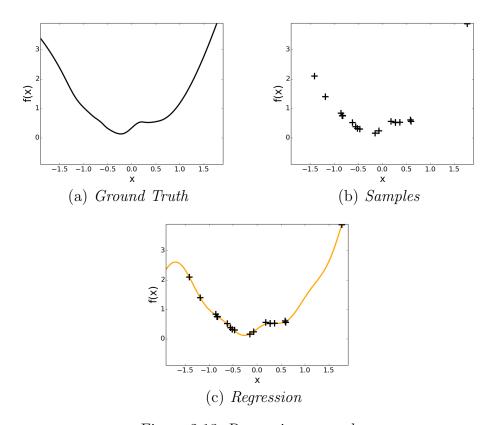

| 2.13 | Regression example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65 |

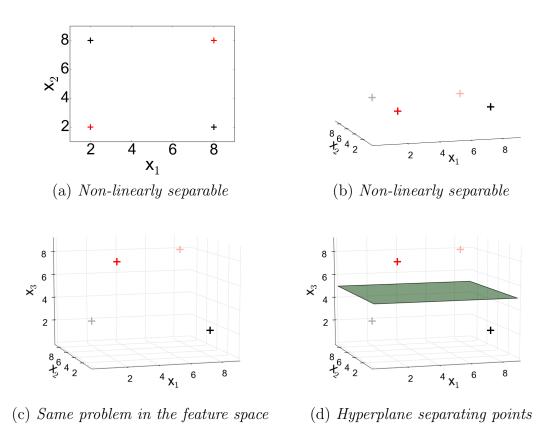

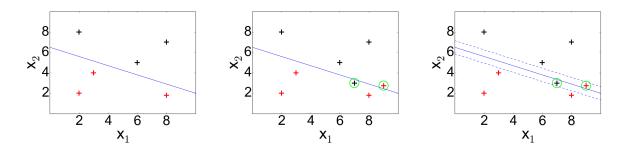

| 2.14 | Feature space mapping and Support Vector Machine (SVM) classification. The two sets of points presented in (a) and (b) are not linearly seperable. Yet, when the problem is brought into a 3 dimensional feature space (c), the solution becomes apparent (d) and a maximum margin hyperplane is constructed                                                                                                                                                                                                                                                                                              | 67 |

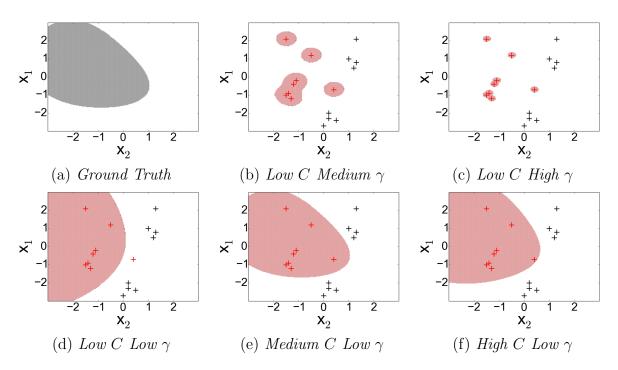

| 2.15 | Two class SVM classification using different values of $C$ and $\gamma$ hyperparameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

| 2.16 | Soft margin SVM classification. A hard margin classification is shown in (a), where a linear decision boundary is counctructed in the feature space to seperate two classes. In (b), new examples are added and the problem is no longer linearly seperable. To take into account the noisy examples, or fact that the classes are not linearly seperable in the feature space, a soft margin is introduced. In (c) this is represented by the two blue lines, where the SVM classifier is trained to allow for certain degree of misclassification.                                                      | 70 |

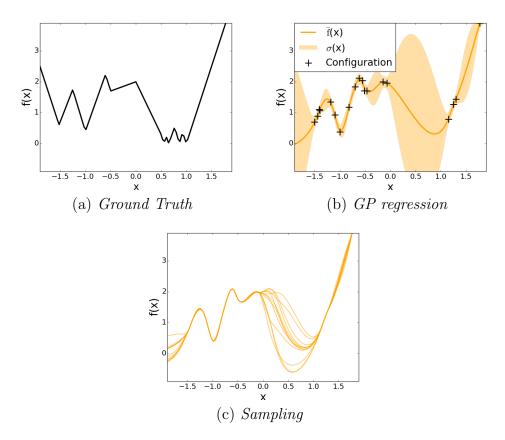

| 2.17 | Gaussian Process (GP) regression. A number of samples are drawn from the GP regression (b) and plotted in (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72 |

|      | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

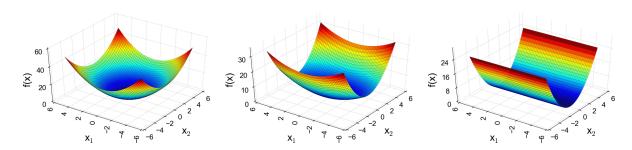

| 2.18 | Anisotropic and isotropic functions. The image (a) represents a quadratic function in two dimensions: $f(\mathbf{x}) = x_1^2 + x_2^2$ . This is an isotropic function, with equal impact of either of the dimensions. A different quadratic function is presented in (b), the function is anisotropic as the parameter $x_1$ has smaller impact on the function value than $x_2$ . In (c) the situation is put to                            |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the extreme and the function solely depends on $x_2$                                                                                                                                                                                                                                                                                                                                                                                         | 73 |

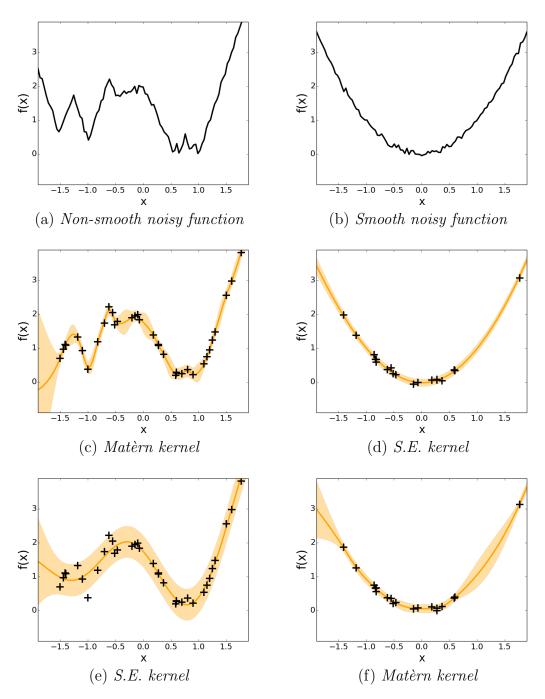

| 2.19 | GP regressions of non-smooth and a smooth function using Matèrn and squared exponential kernel functions. Figures (c) and (d) better modeled functions than (e) and (f), with clearly larger predicted process variance.                                                                                                                                                                                                                     | 75 |

| 2.20 | Cross-validation                                                                                                                                                                                                                                                                                                                                                                                                                             | 77 |

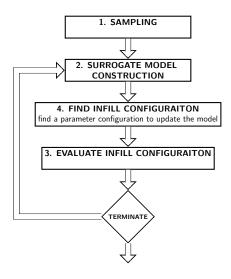

|      | Surrogate Model Optimization                                                                                                                                                                                                                                                                                                                                                                                                                 | 78 |

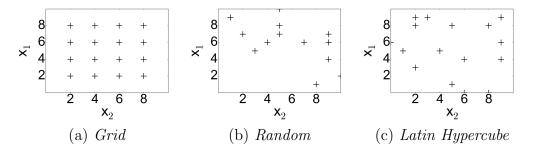

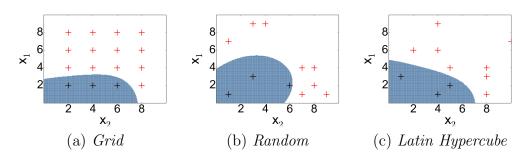

|      | Examples of sampling plans                                                                                                                                                                                                                                                                                                                                                                                                                   | 79 |

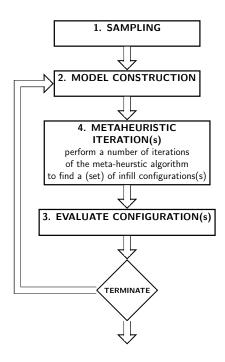

|      | Meteahueristic Optimization and Surrogate Model                                                                                                                                                                                                                                                                                                                                                                                              | 80 |

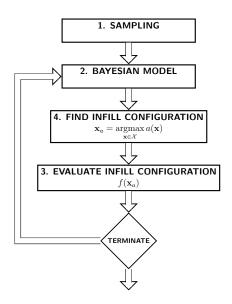

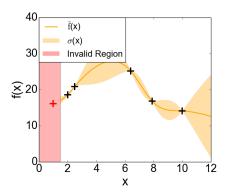

|      | Bayesian Optimization                                                                                                                                                                                                                                                                                                                                                                                                                        | 82 |

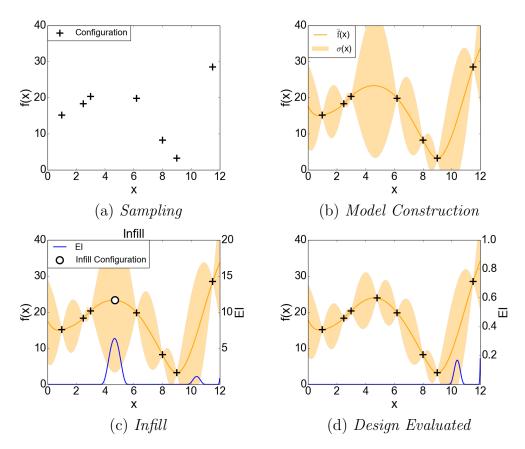

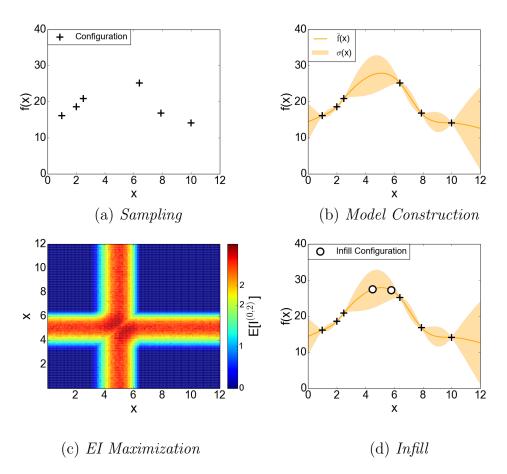

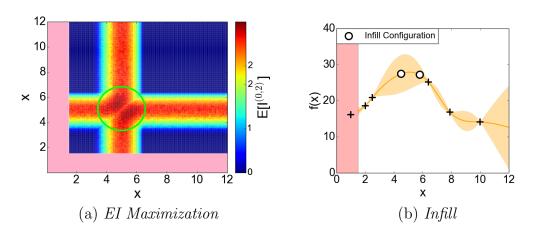

| 2.25 | EGO optimization. The algorithm starts with sampling after which it moves into the infill stage. First, the surrogate model is constructed and then used to calculate $E[I(\mathbf{x})]$ . The configuration chosen for infill is the one offering the highest $E[I(\mathbf{x})]$ . After configuration evaluation, the surrogate model is updated and the process continuous                                                                | 83 |

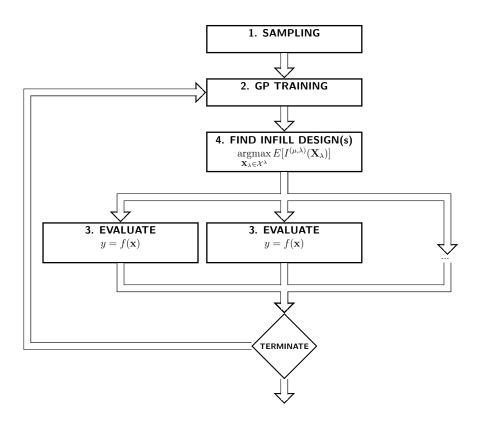

| 2.26 | Asynchronous Parallel EGO Algorithm                                                                                                                                                                                                                                                                                                                                                                                                          | 84 |

| 2.27 | Parallel EGO iteration with two worker nodes, the algorithm starts with sampling. Afterwards it moves into the infill stage. At first the surrogate model is constructed, with one configuration being evaluated. With one worker node free the current surrogate model is used to search for infill configuration by examining $E[I(\mathbf{x})]$ . When a configuration is evaluated, the surrogate model is updated and new search begins | 85 |

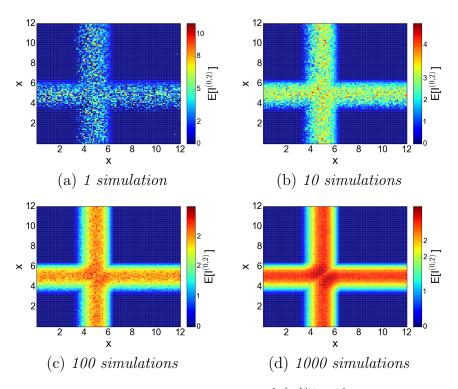

| 2.28 | $E[I^{(\mu,\lambda)}(\mathbf{X}_{\lambda})]$ estimation, as presented in [65] defined for a GP with a zero mean prior function                                                                                                                                                                                                                                                                                                               | 86 |

| 2.29 | Varying number of simulatuions in $E[I^{(\mu,\lambda)}(\mathbf{X}_{\lambda})]$ estimation. Although the ridge representing promising configurations is clearly visibile regardless of the number of simulations, the peak shown in image (d) can be difficult to                                                                                                                                                                             |    |

|      | localize. Note the symmetry                                                                                                                                                                                                                                                                                                                                                                                                                  | 87 |

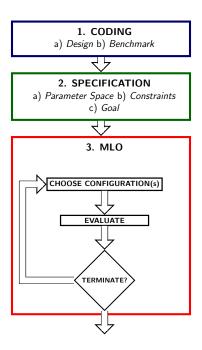

| 3.1  | MLO optimization approach                                                                                                                                                                                                                                                                                                                                                                                                                    | 94 |

| 3.2  | The input includes the parameter space specification, and scripts used to                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

|      | generate and benchmark bitstreams                                                                                  | 95  |

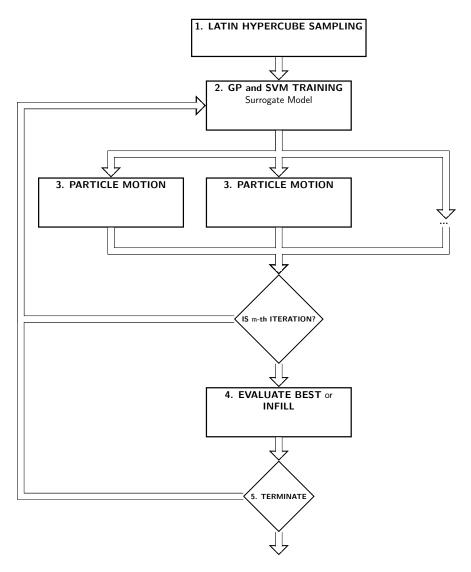

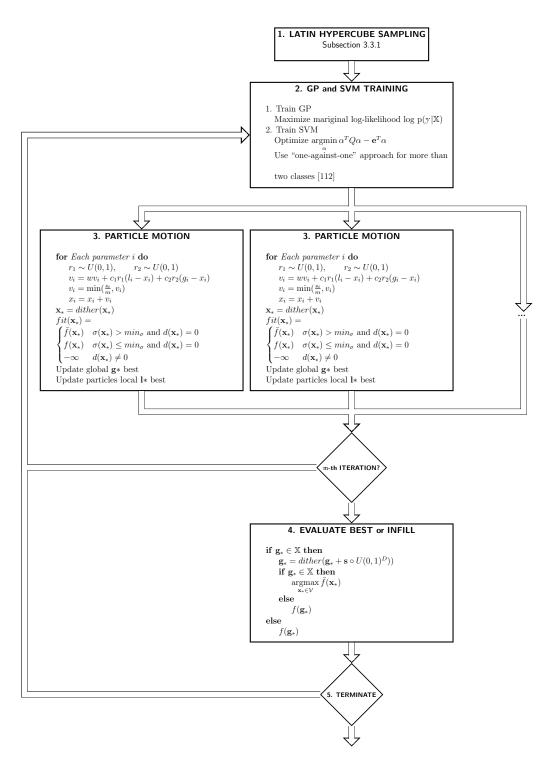

| 3.3  | MLO Algorithm overview                                                                                             | 97  |

| 3.4  | MLO iteration, the algorithm starts with Latin hypercube sampling                                                  | 98  |

| 3.5  | The procedure for Latin hypercube sampling on a discrete space                                                     | 98  |

| 3.6  | Mariginal likelihood calculation for Gaussian process regression [124]                                             | 99  |

| 3.7  | Prediction of mean $\bar{f}(\mathbf{x}_*)$ and of the variance $\text{Var}[\bar{f}(\mathbf{x}_*)]$ of the estimate |     |

|      | using Gaussian process regression [124]. The matrix $L$ and vector ${\bf v}$ are                                   |     |

|      | computed during model training. The vector $\mathbf{k}_*^+$ is the vector of covariances                           |     |

|      | between the configuration and training set $k(X^+, \mathbf{x}_*)$                                                  | 99  |

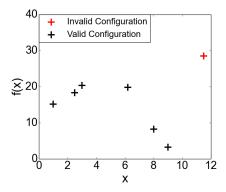

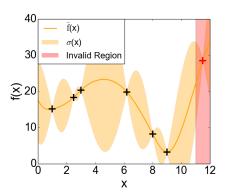

| 3.8  | MLO surrogate model                                                                                                | 100 |

| 3.9  | When calculating particle motion, depending on the uncertaintity prediction                                        |     |

|      | $\sigma(\mathbf{x}_*)$ , a particle either evaluates a configuration $f(\mathbf{x}_*)$ or uses the models          |     |

|      | fitness prediction. In (a) the highlighted particle exceeded the $min_{\sigma}$ ,                                  |     |

|      | subsequently the configuration was evaluated. In (b) the particles move                                            |     |

|      | towards promising eareas                                                                                           | 102 |

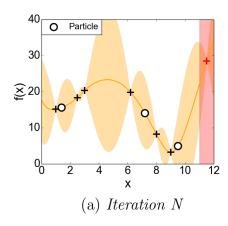

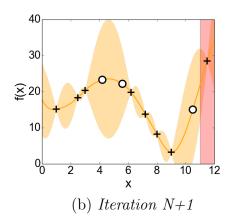

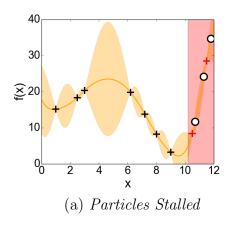

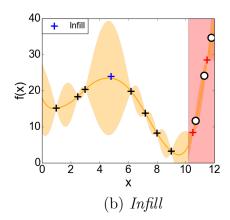

| 3.10 | In (a) all of the particles their local best found so far positions $\mathbf{l}_*$ reside                          |     |

|      | in the invalid region. The Particle Swarm Optimization (PSO) equations                                             |     |

|      | break. The infill (b) evaluates a configuration with highest mean across the                                       |     |

|      | parameter space, and subsequently updates the global found so far position                                         |     |

|      | $\mathbf{g}_*$ . The particle dynamics restarts                                                                    | 103 |

|      | MLO Algorithm with detailed data flow                                                                              | 104 |

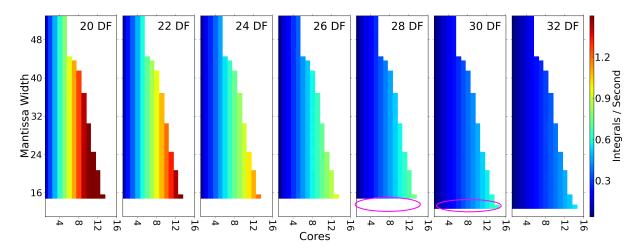

| 3.12 | Visualization of a subset of the parameter space for the throughput bench-                                         |     |

|      | mark of the Quadrature-based Financial design when $\epsilon_{rms} = 0.1$ . Area                                   |     |

|      | affected by decreasing $d_f$ is highlighted                                                                        | 108 |

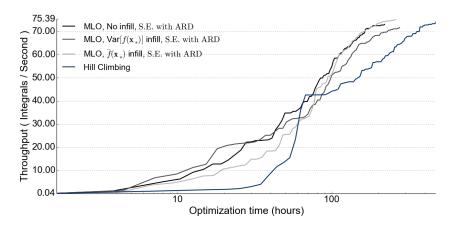

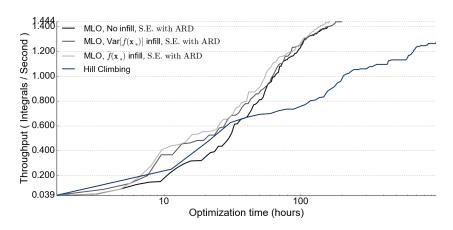

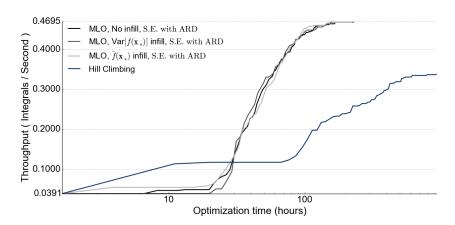

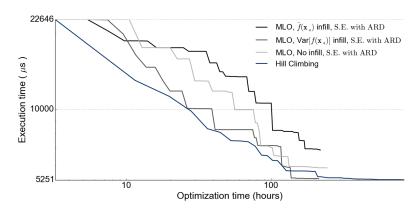

| 3.13 | Optimization of the Quadrature-based Financial design throughput bench-                                            |     |

|      | mark $\epsilon_{rms} = 0.1$ using different infill functions                                                       | 109 |

| 3.14 | Optimization of the Quadrature-based Financial design throughput bench-                                            |     |

|      | mark $\epsilon_{rms} = 0.01$ using different infill functions                                                      | 110 |

| 3.15 | Optimization of the Quadrature-based Financial design throughput bench-                                            |     |

|      | mark $\epsilon_{rms} = 0.001$ using different infill functions                                                     | 110 |

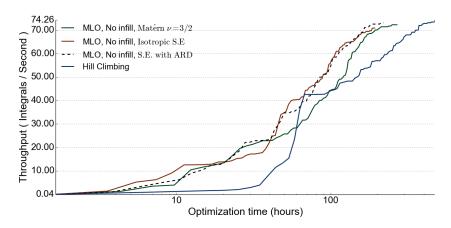

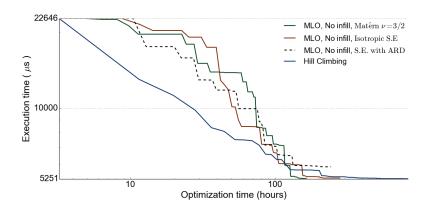

| 3.16 | Optimization of the Quadrature-based Financial design throughput bench-                                            |     |

|      | mark $\epsilon_{rms} = 0.1$ using different kernel functions                                                       | 110 |

| 3.17 | Optimization of the Quadrature-based Financial design throughput bench-                                            |     |

|      | mark $\epsilon_{rms} = 0.01$ using different kernel functions                                                      | 111 |

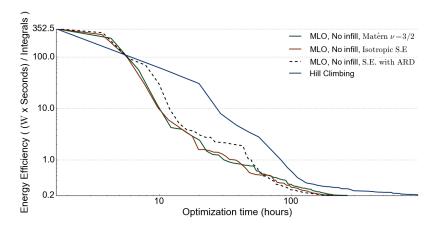

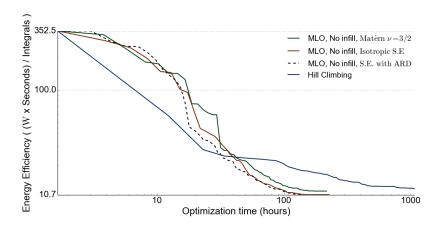

| 3.18 | Optimization of the Quadrature-based Financial design throughput bench-              |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | mark $\epsilon_{rms} = 0.001$ using different kernel functions                       | 111 |

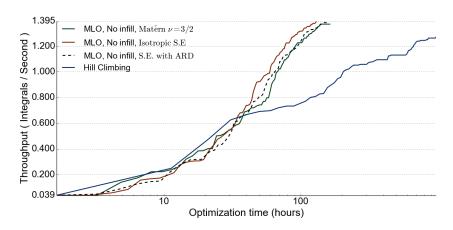

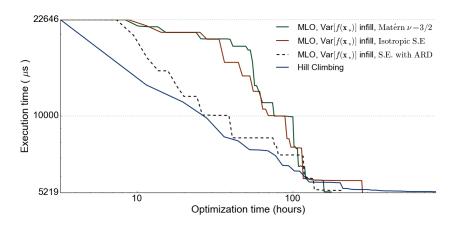

| 3.19 | Optimization of the Quadrature-based Financial design energy benchmark               |     |

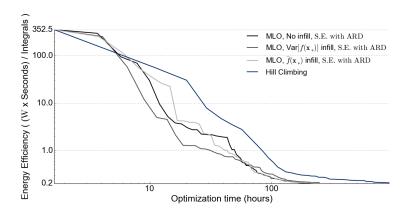

|      | $\epsilon_{rms}=0.1$ using different infill functions                                | 112 |

| 3.20 | Optimization of the Quadrature-based Financial design energy benchmark               |     |

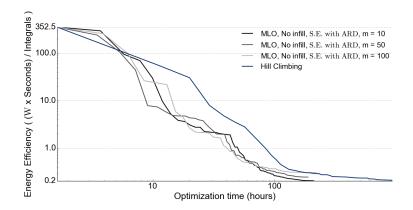

|      | $\epsilon_{rms} = 0.1$ using different $\mathfrak{m}$ values                         | 112 |

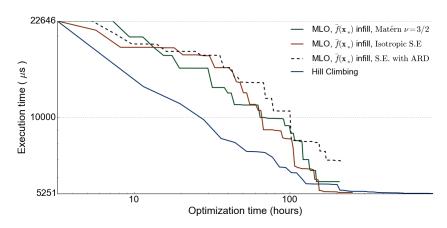

| 3.21 | Optimization of the Quadrature-based Financial design throughput bench-              |     |

|      | mark $\epsilon_{rms} = 0.1$ using different kernel functions                         | 112 |

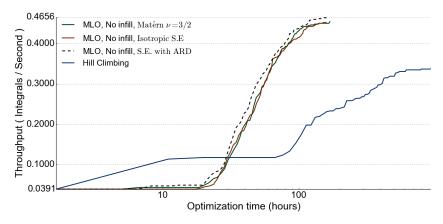

| 3.22 | Optimization of the Quadrature-based Financial design throughput bench-              |     |

|      | mark $\epsilon_{rms} = 0.01$ using different kernel functions                        | 113 |

| 3.23 | Optimization of the Quadrature-based Financial design throughput bench-              |     |

|      | mark $\epsilon_{rms} = 0.001$ using different kernel functions                       | 113 |

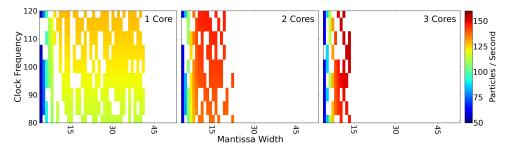

| 3.24 | PQ design throughput fitness function visualization [46]. There is a clear           |     |

|      | trend where with increased number of cores smaller number of designs                 |     |

|      | become available due to resource constraints. Random patches represented             |     |

|      | by blank of invalid area are the result of timing and Place and Route (PAR)          |     |

|      | issues                                                                               | 114 |

| 3.25 | Optimization of the PQ design using different infill functions. MLO configu-         |     |

|      | ration is the anistropic squared exponential kernel function and $min_{\sigma}=0.01$ | 115 |

| 3.26 | Optimization of the PQ design using different kernel functions. MLO                  |     |

|      | configuration is no infill and $min_{\sigma} = 0.01$                                 | 115 |

| 3.27 | Visualization of the stochastic volatility design with a single core. The left       |     |

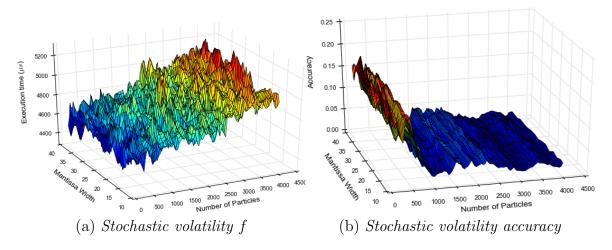

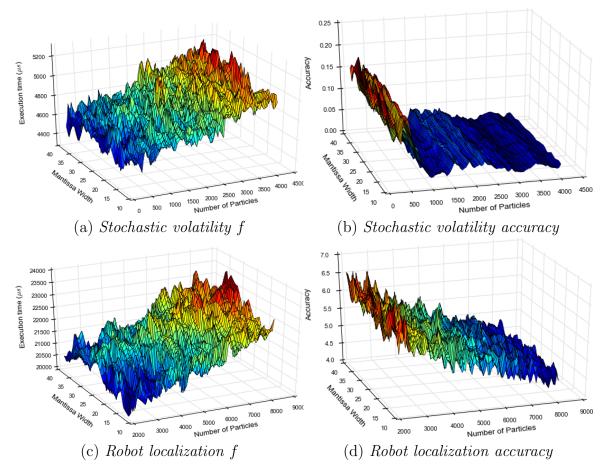

|      | image shows the execution time, while the right image shows the accuracy. $$         | 116 |

| 3.28 | Optimization of the stochastic volatility execution time benchmark using             |     |

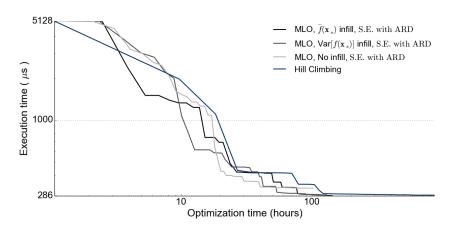

|      | different infill functions                                                           | 117 |

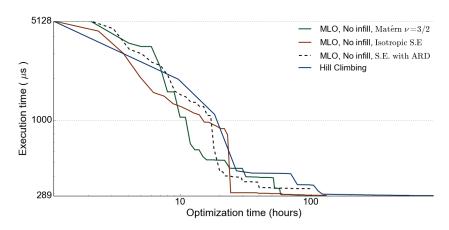

| 3.29 | Optimization of the stochastic volatility execution time benchmark using             |     |

|      | different kernel functions                                                           | 118 |

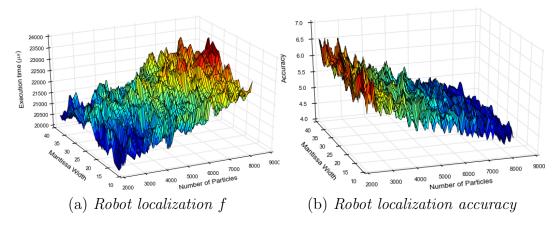

| 3.30 | Visualization of the robot localization design for a single core. The left           |     |

|      | image shows the execution time, while the right image shows the accuracy.            | 119 |

| 3.31 | Optimization of the robot localization execution time benchmark using                |     |

|      | different infill functions                                                           | 120 |

| 3.32 | Optimization of the robot localization execution time benchmark using                |     |

|      | different kernel functions                                                           | 120 |

| 3.33 | Optimization of the robot localization execution time benchmark using                |     |

|      | different kernel functions and variance infill function                              | 120 |

| 3.34 | Optimization of the robot localization execution time benchmark using different kernel functions and mean infill function                                  | 191   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ากร  |                                                                                                                                                            | 141   |

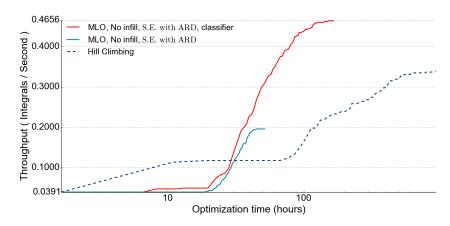

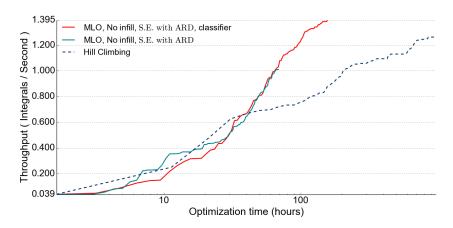

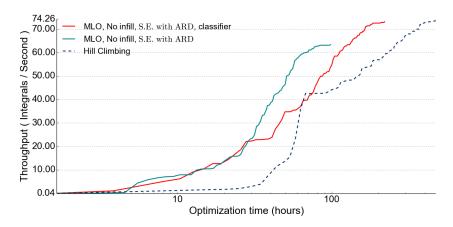

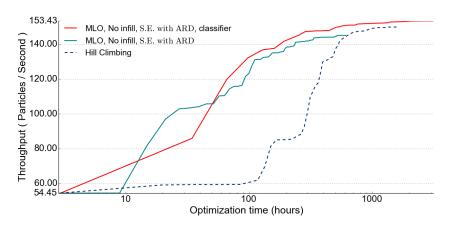

| 3.33 | Optimization of the Quadrature-based Financial design throughput benchmark $\epsilon_{rms} = 0.001$ with and without a classifier                          | 122   |

| 3 36 | Optimization of the Quadrature-based Financial design throughput bench-                                                                                    |       |

| 0.00 | mark $\epsilon_{rms} = 0.01$ with and without a classifier                                                                                                 | 122   |

| 3 37 | Optimization of the Quadrature-based Financial design throughput bench-                                                                                    |       |

| 5.51 | mark $\epsilon_{rms} = 0.1$ with and without a classifier                                                                                                  | 122   |

| 3.38 | Optimization of the PQ design with and without a classifier                                                                                                | 123   |

| 0.00 |                                                                                                                                                            |       |

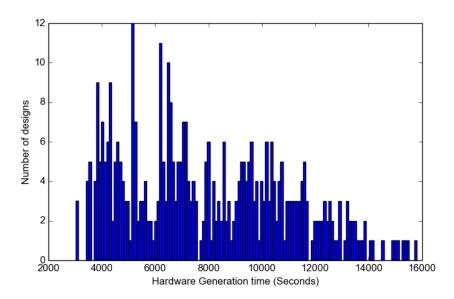

| 4.1  | Histogram of hardware generation time for the quadrature design [155]                                                                                      |       |

|      | implemented using MaxJ for the Maxeler MPC-X1000 system with a Xilinx                                                                                      |       |

|      | Virtex-6 XC6VSX475T                                                                                                                                        | 130   |

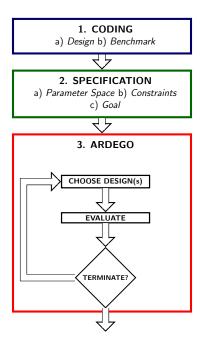

| 4.2  | ARDEGO optimization approach                                                                                                                               | 131   |

| 4.3  | The input includes the parameter space specification, and scripts used to                                                                                  |       |

|      | generate and benchmark bitstreams                                                                                                                          | 132   |

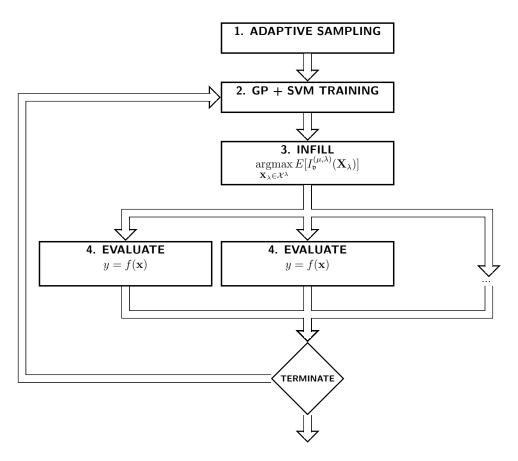

| 4.4  | ARDEGO, inspired by parallel EGO [75]                                                                                                                      | 133   |

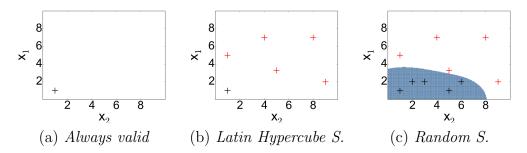

| 4.5  | Adaptive sampling plan, blue area indicates $V$                                                                                                            | 135   |

| 4.6  | Three alternative sampling plans                                                                                                                           | 135   |

| 4.7  | Mariginal likelihood calculation for Gaussian process regression [124]. $$ .                                                                               | 136   |

| 4.8  | Prediction of mean $\bar{f}(\mathbf{x}_*)$ and of the variance $\text{Var}[\bar{f}(\mathbf{x}_*)]$ of the estimate                                         |       |

|      | using Gaussian process regression [124]. The matrix $L$ and vector ${\bf v}$ are                                                                           |       |

|      | computed during model training. The vector $\mathbf{k}_*^+$ is the vector of covariances                                                                   |       |

|      | between the configuration and training set $k(X^+, \mathbf{x}_*)$                                                                                          | 136   |

| 4.9  | ARDEGO surrogate model                                                                                                                                     | 137   |

| 4.10 | ARDEGO search for infill using $E[I_{\mathfrak{v}}^{(\mu,\lambda)}]$ when two worker nodes are free.                                                       | 140   |

| 4.11 | $E_{MC}[I_{\mathfrak{v}}^{(\mu,\lambda)}(\mathbf{X}_{\lambda})],$ dervied from [65]. The set $\mathbf{X}_{\mathfrak{v}}$ is the set $\mathbf{X}$ excluding |       |

|      | configurations predicted to be invalid. $\Sigma_{\mathfrak{v}}$ is the covariance matrix of $\mathbf{Y}^{\mu}_{\mathfrak{v}}$                              |       |

|      | and $\mathbf{Y}^{\lambda}$                                                                                                                                 | 140   |

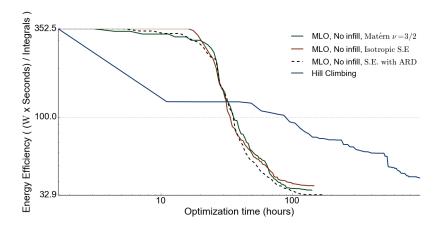

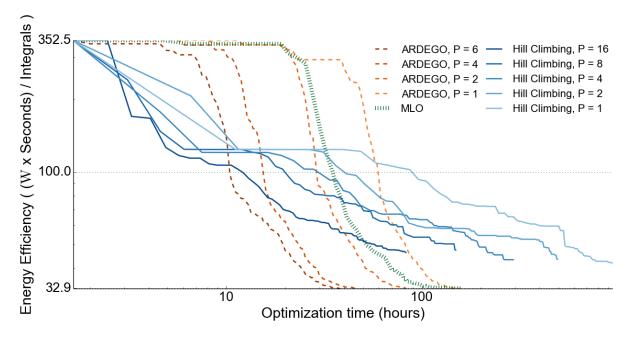

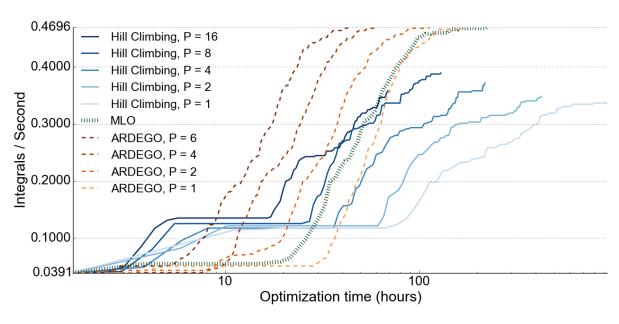

| 4.12 | Optimization of the quadrature-based financial design energy efficiency                                                                                    |       |

|      | benchmark                                                                                                                                                  | 148   |

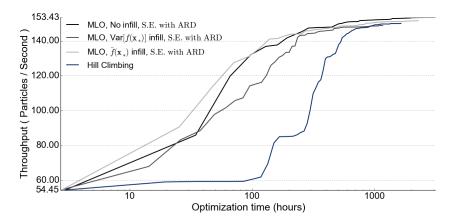

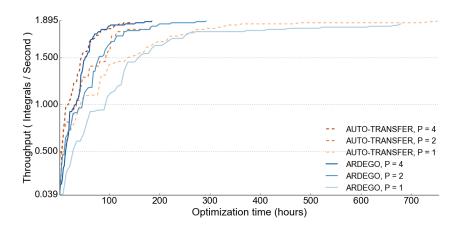

| 4.13 | Optimization of the quadrature-based financial design throughput benchmark                                                                                 | .149  |

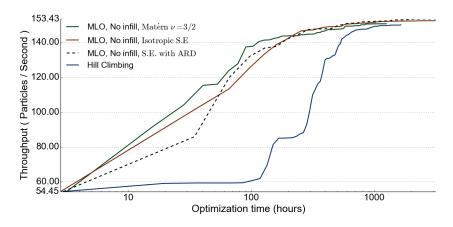

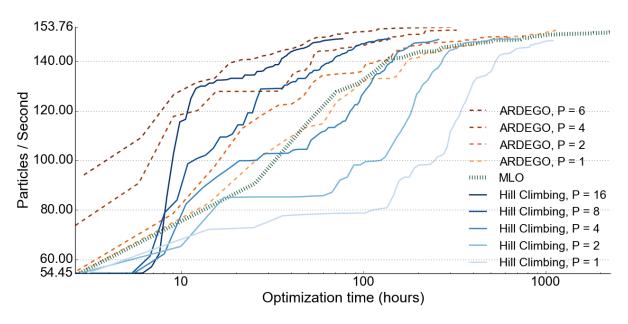

| 4.14 | Optimization of the PQ design throughput                                                                                                                   | 150   |

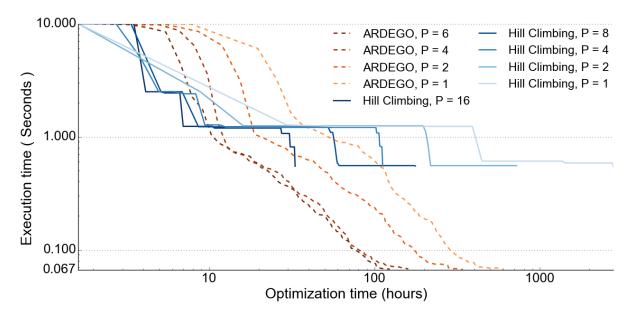

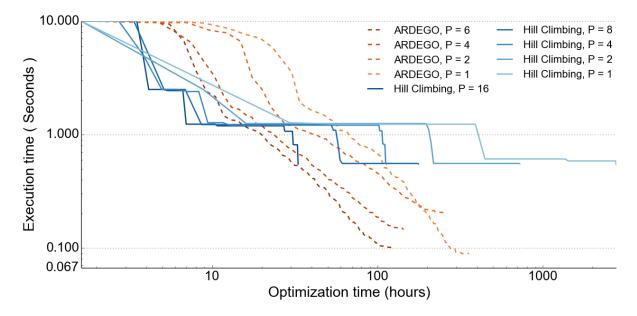

| 4.15 | Optimization of the Reverse Time Migration (RTM) design execution time.                                                                                    | 151   |

| 4.16 | Optimization of the RTM design execution time, Latin hypercube sampling                                                                                    | 3.152 |

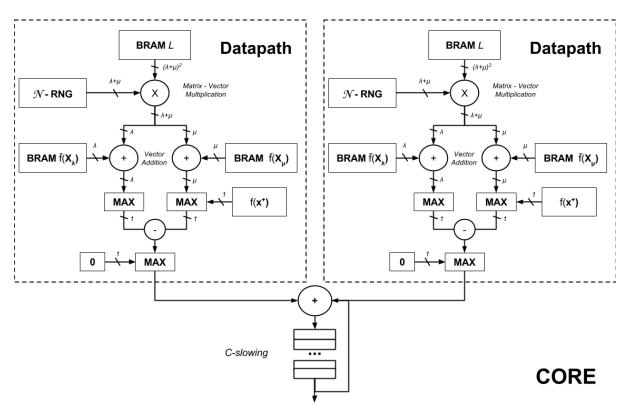

| 4.17 | A circuit used for acceleration of the $E[I^{(\mu,\lambda)}(\mathbf{X}_{\lambda})]$ and $E[I^{(\mu,\lambda)}_{\mathfrak{v}}(\mathbf{X}_{\lambda})]$ functions. The connectors widths represent the number of double or floating                                                                                                                                                                                                                               |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | point numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 154 |

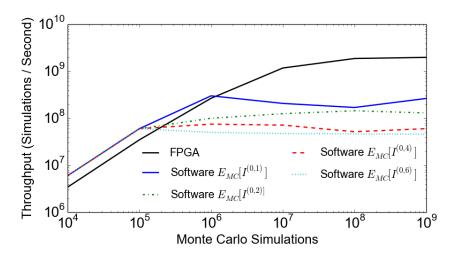

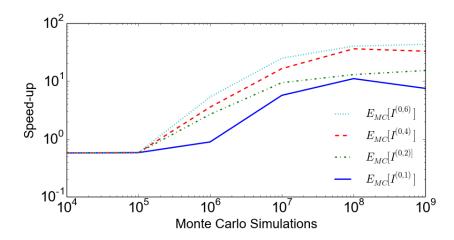

| 4.18 | Throughput of unoptimized hardware and multi-core software implementations of $E_{MC}[I^{(\mu,\lambda)}]$                                                                                                                                                                                                                                                                                                                                                     | 155 |

| 4.19 | Speed-up of the hardware vs. the software solution with increasing number of Monte Carlo simulations                                                                                                                                                                                                                                                                                                                                                          | 156 |

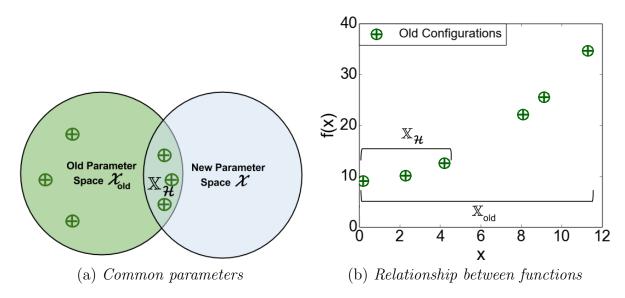

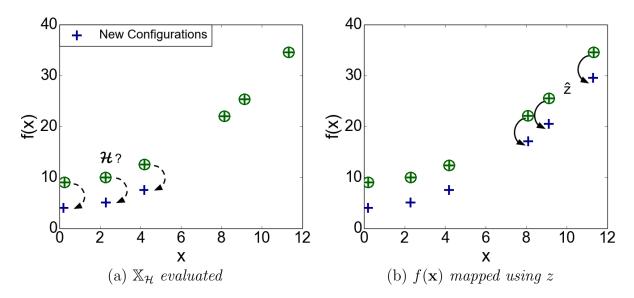

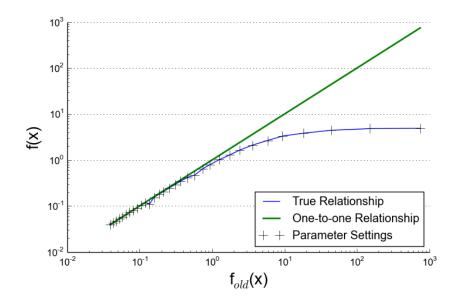

| 5.1  | In (a) six parameter settings are in the old design respository. The set $\mathbb{X}_{\mathcal{H}} \in \mathbb{X}_{old}$ consists of three out of six of those configurations. The three configurations can be evaluated for the new design and used to verify the relationship between the two designs                                                                                                                                                       | 163 |

| 5.2  | To transfer the old parameter settings, there needs to be a set of parameters $\mathbb{X}_{\mathcal{H}}$ , which can be used to verify the hypothesis that there is a relationship between the designs. In this case the set consists of parameter settings $\mathbf{x}_1$ to $\mathbf{x}_3$ . Those parameter settings allow to identify the relationship between the old and the new design. This is later used for more accurate modeling and optimization | 164 |

| 5.3  | Knowledge transfer optimization approach, extended to accomodate old                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | designs                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 165 |

| 5.4  | Moving to a new platform [6]                                                                                                                                                                                                                                                                                                                                                                                                                                  | 166 |

| 5.5  | Related designs                                                                                                                                                                                                                                                                                                                                                                                                                                               | 166 |

| 5.6  | The algorithm input is extended with a design database. The design database stores results of previous optimizations, allowing ARDEGO algorithm to transfer knowledge. This can improve both the speed and accuracy                                                                                                                                                                                                                                           |     |

|      | of the optimization                                                                                                                                                                                                                                                                                                                                                                                                                                           | 167 |

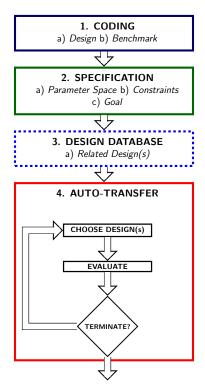

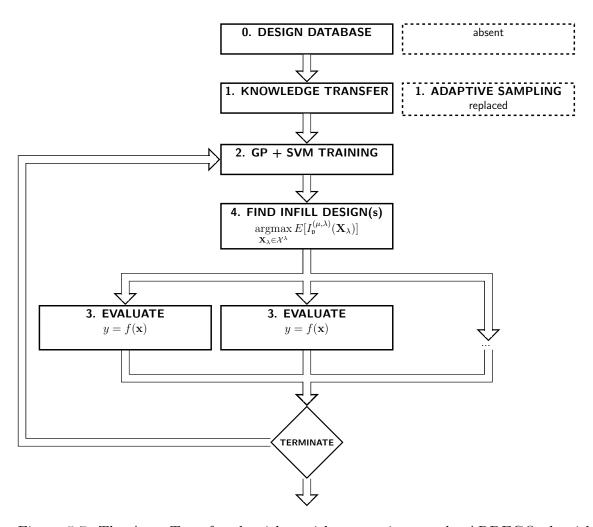

| 5.7  | The Auto-Transfer algorithm with comparison to the ARDEGO algorithm.                                                                                                                                                                                                                                                                                                                                                                                          | 168 |

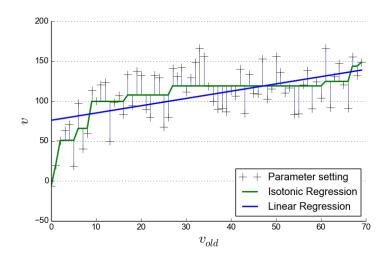

| 5.8  | Linear and Isotonic regression [115]                                                                                                                                                                                                                                                                                                                                                                                                                          | 172 |

| 5.9  | The knowledge transfer step                                                                                                                                                                                                                                                                                                                                                                                                                                   | 174 |

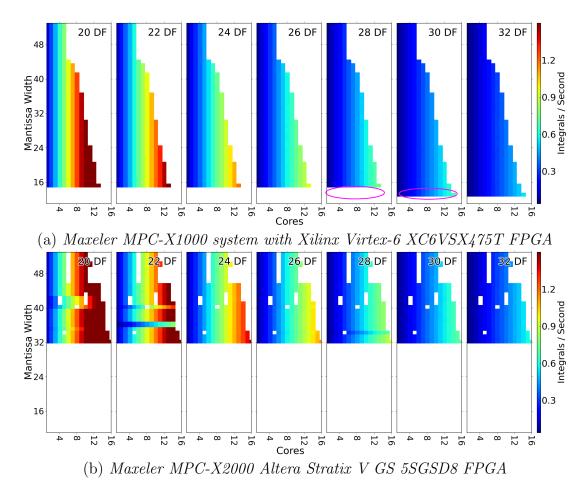

| 5.10 | Visualization of a subset of the parameter space for the throughput benchmark $\epsilon_{rms} = 0.1$ of the quadrature-based financial design implemented on                                                                                                                                                                                                                                                                                                  |     |

|      | two different platforms                                                                                                                                                                                                                                                                                                                                                                                                                                       | 177 |

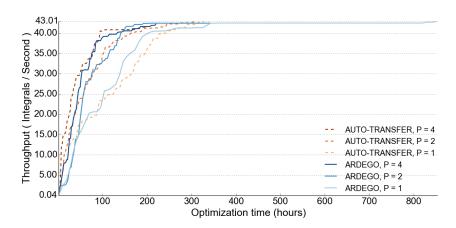

| 5.11 | Optimization of the quadrature-based financial design throughput benchmark for $\epsilon_{rms} = 0.1$ using knowledge transfer                                                                                                                                                                                                                                                                                                                                | 178 |

| 5.12 | Optimization of the quadrature-based financial design throughput bench-         |       |

|------|---------------------------------------------------------------------------------|-------|

|      | mark for $\epsilon_{rms} = 0.01$ using knowledge transfer                       | 178   |

| 5.13 | Optimization of the quadrature-based financial design throughput bench-         |       |

|      | mark for $\epsilon_{rms} = 0.001$ using knowledge transfer                      | 178   |

| 5.14 | Relationship between performance of a single core design for the quadrature     |       |

|      | design implemented on the MPC-X1000 and MPC-X2000 platforms. Note               |       |

|      | the log-scale. The throughput for MPC-X2000 improves little for low $d_{\it f}$ |       |

|      | values, as the problem becomes communcation bound instead of compute            |       |

|      | bound. This is less of an issue in the case of MPC-X1000                        | 179   |

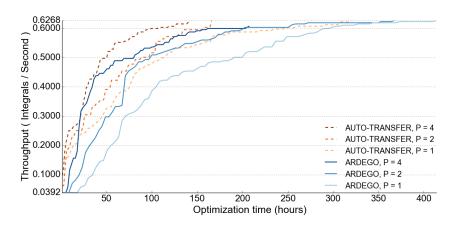

| 5.15 | Optimization of the RTM design execution time for MPC-X2000, using $$           |       |

|      | knowledge resue                                                                 | . 181 |

| 5.16 | Stochastic volatlity and robot localization designs                             | 182   |

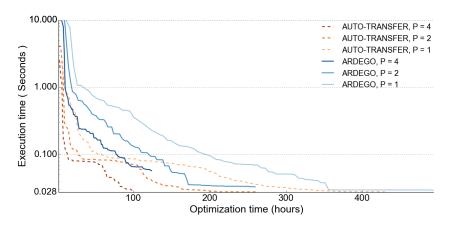

| 5.17 | Optimization of robot localization design using knowledge transferd from        |       |

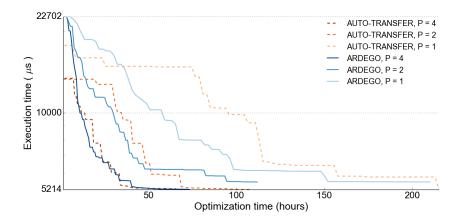

|      | the optimization of the stochastic volatility design                            | 183   |

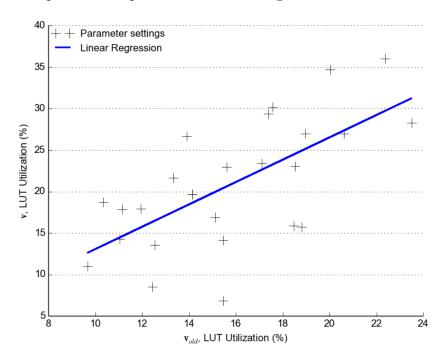

| 5.18 | Comparison of different parameter setting Lookup Table (LUT) utilization        |       |

|      | of the robot and stochastic volatility design. Stochastic volatility is the old |       |

|      | design                                                                          | 184   |

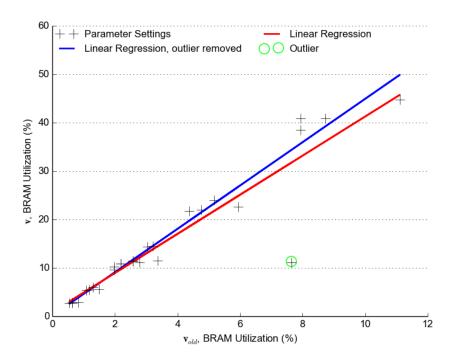

| 5.19 | Comparison of different parameter setting Block RAM (BRAM) utilization          |       |

|      | of the robot and stochastic volatility design. Stochastic volatility is the old |       |

|      | design                                                                          | 185   |

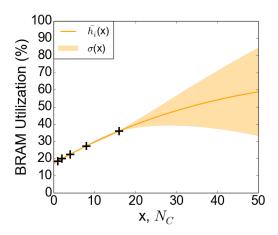

| 6.1  | GP prediction of BRAM utilization for the stochatic volatility design           | 193   |

| 6.2  | PQ design throughput fitness function [46] and probability of successful        |       |

|      | hardware generation visualization                                               | 194   |

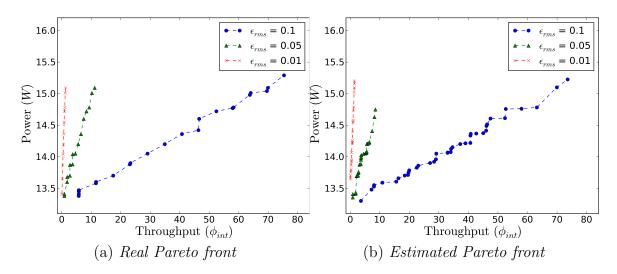

| 6.3  | Real and approximated Pareto fronts found with the Multiobjective Machine       |       |

|      | Learning Optimizer (MOMLO) algorithm [90]                                       | 195   |

|      |                                                                                 |       |

# List of Tables

| 1.1 | The three major challenges with optimization of reconfigurable designs                                                                                                                                                                   | . 41 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 | FPGA and Application Specific Integrated Circuits (ASIC) comparison                                                                                                                                                                      |      |

|     | $[10, 49, 82, 87, 138] \dots \dots$                                                                                                | 44   |

| 2.2 | Summary of the most commonly encountered parameters                                                                                                                                                                                      | 58   |

| 2.3 | Examples of fitness function constraints                                                                                                                                                                                                 | 58   |

| 2.4 | Summary of the three major challenges with optimization of reconfigurable                                                                                                                                                                |      |

|     | designs                                                                                                                                                                                                                                  | 60   |

| 2.5 | Mathematical Optimization Summary                                                                                                                                                                                                        | 63   |

| 3.1 | MLO test designs overview.                                                                                                                                                                                                               | 106  |

| 3.2 | The average optimization time in hours and the percentage of the average                                                                                                                                                                 |      |

|     | performance of the optimal configuration of different designs. The hill                                                                                                                                                                  |      |

|     | climbing algorithm and three different configuration of the MLO algorithm                                                                                                                                                                |      |

|     | are compared. The global optimum was found using exhaustive search                                                                                                                                                                       | 124  |

| 4.1 | ARDEGO test designs overview                                                                                                                                                                                                             | 145  |

| 4.2 | The average optimization time in hours and the percentage of the average performance of the optimal configuration of different designs. ARDEGO is compared with various algorithms. The global optimum was found using exhaustive search | 146  |

| F 1 |                                                                                                                                                                                                                                          | 110  |

| 5.1 | An example of a design repository $\mathbb{X}_{old}$ of a design configurable with $m_w$                                                                                                                                                 |      |

|     | mantissa width of floating point numerical operators and the number of cores <i>cores</i> . A total of 8 parameter settings were evaluated                                                                                               | 170  |

| 5.2 | An example $X_{\mathcal{H}}$ for the design presented in Table 5.1 and a related design.                                                                                                                                                 |      |

|     | There is a clear difference in performance                                                                                                                                                                                               | 170  |

LIST OF TABLES

LIST OF TABLES

| 5.3 | Correlations calculated for the set $X_{\mathcal{H}}$ presented in Table 5.1 and Table 5.2.         |     |

|-----|-----------------------------------------------------------------------------------------------------|-----|

|     | With $alpha = 0.05\%$ the $\mathcal{H}_l$ is rejected for the latency, although the $\mathcal{H}_m$ |     |

|     | holds. For mapping of the LUTs, both hypothesis are rejected                                        | 171 |

| 5.4 | The table presents training set created using knowledge transfer step for                           |     |

|     | the designs presented in Table 5.1 and Table 5.2. Blue rows represent                               |     |

|     | transferred data                                                                                    | 173 |

| 5.5 | knowledge transfer test designs overview                                                            | 176 |

| 5.6 | The average optimization time in hours and the percentage of the average                            |     |

|     | performance of the optimal configuration of different designs. ARDEGO                               |     |

|     | without and with knowledge transfer is compared. The global optimum                                 |     |

|     | was found using exhaustive search                                                                   | 186 |

| 6.1 | The three major challenges with optimization of reconfigurable designs                              | 190 |

## Chapter 1

### Introduction

### 1.1 Motivation

The history of computing dates back to the ancient analog computers used for astronomical calculations. Yet, it was only within the last 100 years that many major advancements in physics, chemistry and mathematics allowed for the creation of modern digital computers. One of the major milestones was the development of general-purpose programming languages like C or Fortran in the 1960s-1970s. They offered a layer of abstraction from the underlying hardware allowing for faster software development and thus massively increased complexity of the programs. In particular, development of JAVA in the 1990s went as far as automating memory management [11]. Languages like Ruby or Python went even further, they were designed to allow the programmer to express complex functionality in just a few lines of code. The process of hardware abstraction in software design became so advanced, that currently many programmers have little to no understanding of the underlying computer architecture. The job of machine code generation has been offset to compilers. In the meantime, although not as widely acknowledged, the process of hardware design was also changing. Especially interesting was the development of reconfigurable hardware and logic synthesizers.

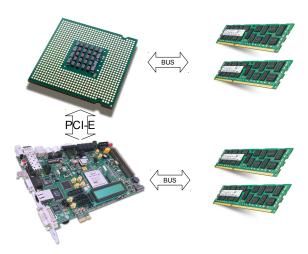

The initial idea of reconfigurable hardware is widely agreed to first appear in the 1960s [61]. It started gaining popularity in the 1990s with the increased availability of new FPGAs devices. Initially those devices could not compete with Application Specific Integrated Circuits (ASIC) both due to the performance and cost issues. However, in the early 2000s they became commercially viable due to the creation of better supporting software. Their main advantage over ASIC was lower up front development cost. When compared to Central Processing Units (CPUs) they offered better power utilization and

Figure 1.1: Some of many possible Field Programmable Gate Array (FPGA) boards: XMC-FPGA05D XMC/PM and PMC-FPGA05 with Xilinx Virtex-5 FPGAs from Curtiss Wright [1] and a Nallatech 395 with Atera Stratix V FPGA [2].

often orders of magnitude of speed-up.

While the technology has advanced, the reconfigurable hardware industry still faces a number of challenges. The spatial programming model used in FPGAs is very different from the widely understood temporal software programming model. Extracting spatial features from a temporal application written in C or Fortran and translating it to Hardware Description Language (HDL) consumes a large amount of engineering hours, often making FPGA accelerators economically infeasible. A number of ideas on automating the design process have been presented by various researchers, and some have been verified: new Higher Level Language (HLL), extensions of the existing languages or language specific accelerator libraries. In recent years the FPGA industry has been looking for the holy grail — an approach that would allow users to automatically and efficiently map HLL onto reconfigurable heterogeneous platforms. Such an approach would allow user to concentrate on developing an optimal algorithm, leaving most of the implementation to the system.

We are interested in providing domain experts like scientists and engineers with the power of reconfigurable computing while hiding the complexity of the application development. This scope being very broad, we focus on automatic optimization of reconfigurable design parameters. A good example of such a design is the Finite Impulse Response (FIR) filter

$$f(\mathbf{x}) = \sum_{i=0}^{q} \mathbb{b}_i \times \mathbf{x}_{q-i}$$

(1.1)

with a batch of q elements  $\mathbf{x} = \{x_i\}_{i=1}^q$ , where  $x_i \in \mathbb{R}$ , being processed using q coefficients  $b_i \in \mathbb{R}$  at every time step. Ideally multiple filters should be implemented in parallel, and the numerical representation of real numbers has to be specified. The design multiplication

Figure 1.2: Some of many available HDLs and their infrastracture: Maxeler MaxJ with MaxIDE [3] and OpenCL [4] with OpenCL Editor [5].

operators can be implemented using custom arithmetic, offering a trade-off between accuracy and throughput. The lower the operator precision, the more coefficients can be implemented. Alternatively, lower precision operators allow for more FIR filters on a single FPGA chip. The goal of optimization is to find the design offering the highest throughput for a specified accuracy. The optimization also includes design clock frequency, making design generation noisy due to potential timing issues. Depending on the parameter configuration, the design has a smaller or larger probability of hardware generation failure. For example, the real-time Proximity Query (PQ) design [46] suffers both from Place and Route (PAR) and timing problems and as a result hardware generation often fails. Looking back at the FIR design, it involves a lot of data streaming onto the FPGA. It is possible that the computation throughput is going to be limited by the connecting bus. Despite FIR being a very simple design, the above mentioned properties make optimization challenging. An exhaustive approach could use a script such as the one presented in Figure 1.3 to explore the parameter space.

Generally optimization of designs requires the designer to analyze the design, create models and benchmarks, and subsequently use them to optimize the design for throughput, power consumption or some other performance metric. This is a time consuming process even for an experienced designer, often lasting a number of days. There are multiple other examples of similar problems, such as optimization of multi-FPGA systems [71]. The level of parallelism can have non-obvious impact on the performance of run-time

```

# clock frequency

1

2

freq = 100

# iterate over the unrolling factor

3

for p in [1, 2, 4, 8] :

4

# iterate over width of the exponent

5

for wE in range (8, 11):

6

# iterate over width of the mantissa

7

8

for wM in range (11, 53):

9

# generate directories and hardware configuration file

10

buildConfig(p, freq, wE, wM)

# build hardware using the generated configuration

11

os.system ("Make_hw")

12

13

# run the generated hardware

os.system("Make_run")

14

15

# analyze results

16

results = analyze()

```

Figure 1.3: A sample script used for exhaustive search over a range of design parameters. The code generates hardware configuration, builds the design and executes a benchmark. Finally the results are analyzed.

reconfigurable designs [30]. The design throughput [46] is highly dependent on the numerical representation. It influences resource utilization and therefore the level of parallelism. Optimization of coefficients of constant multipliers can also yield improvement [76]. Balancing data-reuse and loop-level parallelism for hardware generation requires complicated frameworks [94]. Determining optimal stencil configuration is known to be a difficult problem [109]. Although authors present tools and models which allow for efficient optimization of specific designs, they have to be updated for new designs. The high manual effort and low re-usability of the tools make those approaches highly inefficient in terms of designer's productivity. Automation of tools and their generality are highly desired for increased productivity.

There were few attempts in the past to create generic automatic optimization tools for reconfigurable designs. The are two main obstacles in the engineering and application of those tools. The first obstacle is the massive design parameter spaces which possibly span out into thousands of designs. The second obstacle is the long design evaluation time, taking multiple hours to generate hardware and execute benchmarks. A prior attempt used surrogate modeling to speed-up expensive design evaluations [117]. Fitness Inheritance was used to decrease the number of design evaluations and hence speed-up optimization. In [100] authors present a design and Computer Aided Design (CAD) tool parameter tuning approach. Equally to the design parameters, proper selection of those CAD tool

```

# parameter space definition

1

2

parameters = {"freq_min" : 100,

3

"freq_{\text{max}}": 100,

p_{\min} = 1

4

"p_max"

5

: 10,

6

7

}

8

9

# Build bitstreams and run benchmarks, the fitness function

10

def buildHardwareRunBenchmark():

11

# execute bitstream generation

os.system ("Make_hw")

12

13

# execute benchmark and / or analyze bitstream

return os.system("Make_run")

14

15

\# supply the parameter definition and scripts to the optimization algorithm

16

17