# ASSESSMENT OF HVDC TECHNOLOGIES FOR AN OFFSHORE MTDC GRID

CAITRÍONA EVELYN SHERIDAN

Thesis submitted for the degree of

**Doctor of Philosophy**

Imperial College London

Control and Power Research Group Department of Electrical and Electronic Engineering Imperial College London October 2015

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

## Abstract

This thesis examines various HVDC converter technologies that could be used in offshore Multi-Terminal DC (MTDC) grids. MTDC grids rely on AC/DC converters to interface with AC systems and also for control services. Two AC/DC topologies were compared, the half-bridge Modular Multi-level Converter (MMC) and the Alternate Arm Converter (AAC). As new DC system voltages emerge the DC/DC converter could be an enabling technology for interconnection and future MTDC networks. As yet there is no consensus on DC/DC converter topology and a critical comparison of several potential designs was conducted. An MMC based DC/DC converter had distinct advantages compared with other designs. Several average value converter models of the converters were developed to allow efficient simulation of MTDC networks, while maintaining a high level of accuracy of the converter characteristics. These models were verified with full switching models for steady state and fault conditions. Two offshore MTDC networks were studied; a four-terminal network, and a MTDC network. The four-terminal network used a normally open point to connect two existing point-to-point links, allowing reconfiguration in the event of a DC fault. The MTDC network uses a DC/DC converter to interconnect a bipole HVDC link with the previously studied four-terminal network. Several simulation studies show how new converters can improve the operation of a MTDC and provide additional capabilities such as DC fault blocking.

## **Declaration of Originality**

I, hereby declare that this thesis is the result of my own work, and that any ideas or quotations from the work of others, published or otherwise, are appropriately referenced. This work presented in this thesis was carried out from January 2012 to October 2015 under the supervision of Prof. Tim C. Green at Imperial College London.

> Caitríona Evelyn Sheridan Imperial College London October 2015

## Acknowledgments

I want to thank my supervisor, Professor Tim Green, who provided me with guidance and great support throughout the duration of my PhD. He always reassured me on my research and ideas, and instilled confidence in me, even when I lost my voice.

I am grateful to Arup and National Grid who provided me with financial support for my PhD. I would like to thank Dr Paul Coventry and Kamal Siriwardhana for their input and feedback throughout the PhD. I am ever grateful to Kamal, as without him I would never have had such an opportunity.

I wish to express my sincere gratitude to Dr Michaël Merlin. He provided me with assertive support and advice throughout my PhD, both academically and as a friend. Without his positivity and encouragement I would never have come so far.

I am grateful to all those who have had the pleasure (torment!) of educating me, particularly in Wilson's Hospital School and UCC. I would like to thank David Grubb, Michael Finnegan, Rosemary and Gerry Eager for all their encouragement during secondary school. My deepest thanks to Joe Weafer to helping me find my way, may you always rest in peace. At UCC I had the pleasure of being taught by many fantastic academics, I would particularly like to thank Dr Mike Egan and Dr Bill Wright for their support towards pursuing this PhD.

I have made several new, and life long, friends as a result of studying at Imperial College. My thanks goes to Claudia, Thulasi, Kamu, Tom, Adrià, and Yousef, my office friends from Level 11, and to Paul, Phil, Jeff, Mark, Geraint, Nathaniel, and Richard, my friends from the Smart Energy Lab. A special mention to Phil and Claudia who have been great friends. You have all made my PhD more enjoyable and provided great support when it was needed.

Several school friends have also made the journey to London, some to live and some to visit. To Wilsonians Paula, Michelle, and Danielle, thank you for your kindness and humor, and making sure I keep my feet on the ground.

To my dear parents, Tony and Margaret, who have provided continued support and encouragement throughout my academic endeavours, I want to express my heartfelt gratitude for everything you have done for me. Even with the challenge of my studying across the Irish Sea, your love and kindness was always felt. I also wish to thank my family in Kent, who supported me when I arrived off the boat. Particularly Kevin, who provided me with a home away from home making the transition into the UK easier.

Finally, I want to express my deepest gratitude to Alwyn for being wonderfully supportive and loving regardless of the situation or mood.

## Contents

| Ał  | ostrac | ct in the second s | 5  |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| De  | eclara | tion of Originality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7  |

| Ac  | know   | ledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9  |

| Co  | onten  | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11 |

| Lis | st of  | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 |

| Lis | st of  | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19 |

| No  | omen   | clature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

| 1.  | Intro  | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

|     | 1.1.   | Offshore Transmission Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25 |

|     |        | 1.1.1. AC versus DC Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 |

|     | 1.2.   | Multi-Terminal DC Grids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 |

|     |        | 1.2.1. Technical Challenges for MTDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

|     | 1.3.   | HVDC Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |

|     |        | 1.3.1. Current Source Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34 |

|     |        | 1.3.2. Voltage Source Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36 |

|     | 1.4.   | Research Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

|    | 1.5. | Thesis  | Outline                                                                                     | 42  |

|----|------|---------|---------------------------------------------------------------------------------------------|-----|

| 2. | AC/  | DC Co   | nverters                                                                                    | 45  |

|    | 2.1. | Introdu | uction                                                                                      | 45  |

|    | 2.2. | Modula  | ar Multilevel Converter                                                                     | 45  |

|    |      | 2.2.1.  | Energy Balancing in the MMC                                                                 | 50  |

|    |      | 2.2.2.  | DC Fault Blocking Solutions                                                                 | 56  |

|    | 2.3. | Alterna | ate Arm Converter                                                                           | 59  |

|    |      | 2.3.1.  | Energy Balancing in the AAC                                                                 | 61  |

|    |      | 2.3.2.  | Extended Overlap AAC                                                                        | 63  |

|    | 2.4. | Compa   | arison of the MMC and AAC                                                                   | 64  |

|    |      | 2.4.1.  | Analytical Comparison                                                                       | 65  |

|    | 2.5. | Summa   | ary                                                                                         | 69  |

| 3. | DC/  | DC Co   | nverters                                                                                    | 71  |

|    | 3.1. | Introdu | uction                                                                                      | 71  |

|    | 3.2. | Backgr  | ound                                                                                        | 72  |

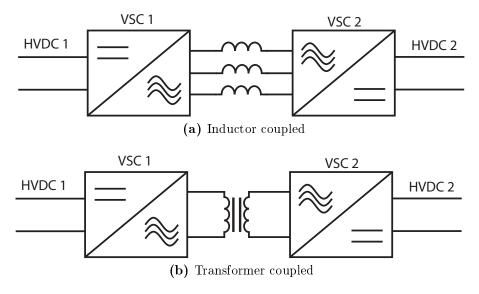

|    |      | 3.2.1.  | Front-to-Front Converter                                                                    | 72  |

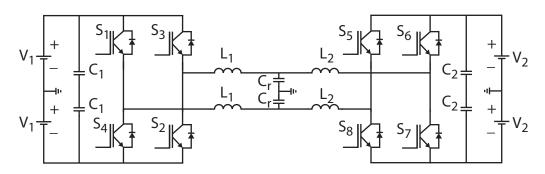

|    |      | 3.2.2.  | HVDC Auto Transformer                                                                       | 74  |

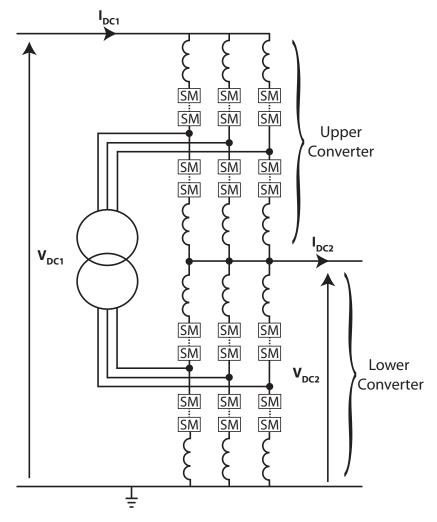

|    |      | 3.2.3.  | Modular Multilevel DC/DC Converter                                                          | 77  |

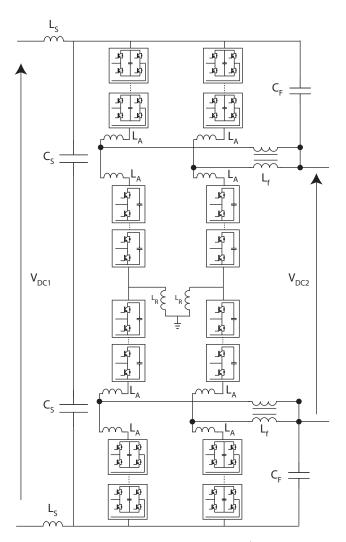

|    |      | 3.2.4.  | LCL DC/DC Converter                                                                         | 78  |

|    | 3.3. | Resona  | ant DC/DC Converter                                                                         | 80  |

|    |      | 3.3.1.  | Principle of Operation                                                                      | 80  |

|    |      | 3.3.2.  | Bidirectional Resonant DC/DC Converter                                                      | 85  |

|    | 3.4. | Alterna | ate Discontinuous Mode Operation                                                            | 91  |

|    |      | 3.4.1.  | ADM Simulations                                                                             | 99  |

|    | 3.5. | Compa   | arison of DC/DC Converters $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 103 |

|    | 3.6. | Summa   | ary                                                                                         | 107 |

| 4. | Ave  | rage M  | lodels of AC/DC Converters                                                  | 109   |

|----|------|---------|-----------------------------------------------------------------------------|-------|

|    | 4.1. | Backg   | round                                                                       | . 109 |

|    |      | 4.1.1.  | Average Value Models of the MMC                                             | . 112 |

|    | 4.2. | Chose   | n AVM Methodology                                                           | . 115 |

|    |      | 4.2.1.  | Voltage Limitation of the Voltage Sources                                   | . 118 |

|    |      | 4.2.2.  | Modified AVM                                                                | . 119 |

|    | 4.3. | Verific | ation of the AVM                                                            | . 121 |

|    |      | 4.3.1.  | Converter Simulations                                                       | . 121 |

|    |      | 4.3.2.  | System Simulations                                                          | . 126 |

|    | 4.4. | AVM     | of the Alternate Arm Converter                                              | . 131 |

|    |      | 4.4.1.  | Converter Simulations                                                       | . 132 |

|    |      | 4.4.2.  | System Simulations                                                          | . 136 |

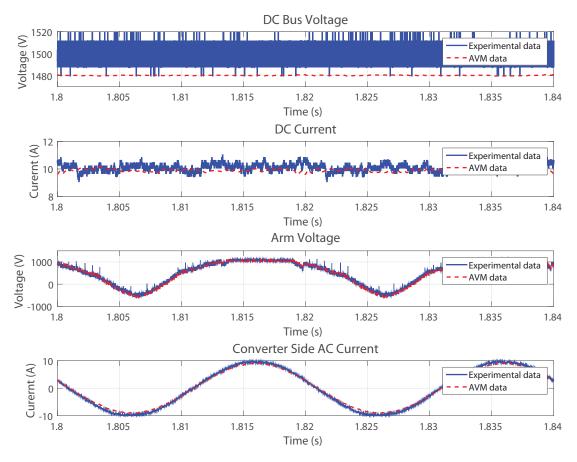

|    | 4.5. | Hardw   | vare Verification of the AAC AVM                                            | . 140 |

|    |      | 4.5.1.  | Lab Converter Description                                                   | . 140 |

|    |      | 4.5.2.  | Comparison of Results                                                       | . 141 |

|    | 4.6. | Summ    | ary                                                                         | . 142 |

| 5. | Offs | hore N  | 1TDC Networks                                                               | 145   |

|    | 5.1. | Introd  | uction                                                                      | . 145 |

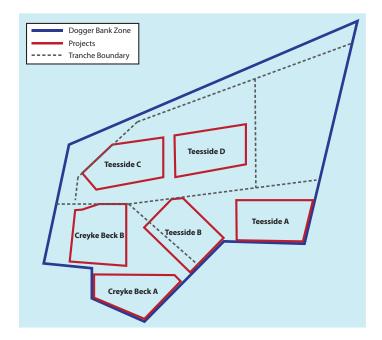

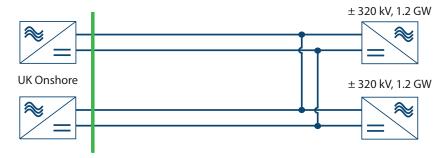

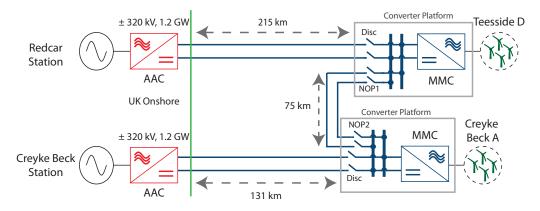

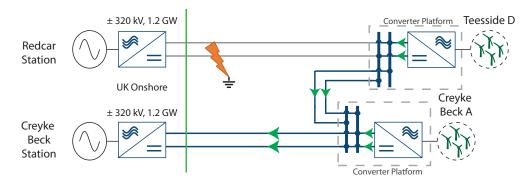

|    | 5.2. | Four 7  | Ferminal Network Study                                                      | . 146 |

|    |      | 5.2.1.  | Study Description                                                           | . 148 |

|    |      | 5.2.2.  | Cost Benefit Case for the Interconnecting Link                              | . 150 |

|    |      | 5.2.3.  | Simulation                                                                  | . 154 |

|    | 5.3. | MTDO    | C Network Studies                                                           | . 159 |

|    |      | 5.3.1.  | Offshore Interconnections                                                   | . 159 |

|    |      | 5.3.2.  | AVM of a DC/DC converter $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 161 |

|    |      | 5.3.3.  | Normal Operation Simulations                                                | . 164 |

|    |      |         |                                                                             |       |

|      | 5.3.4. DC Fault Scenarios                | . 166 |

|------|------------------------------------------|-------|

|      | .4. Summary                              | . 174 |

| 6.   | Conclusion                               | 175   |

|      | .1. General Conclusion                   | . 175 |

|      | .2. Contributions from the Author        | . 180 |

|      | .3. Future Work                          | . 183 |

| Bib  | ography                                  | 185   |

| Арр  | endices                                  | 203   |

| Α.   | Current Derivations for ADM              | 203   |

| В.   | OC/DC Converter Comparison Data          | 205   |

|      | 3.1. Front-to-Front Converter            | . 205 |

|      | 9.2. HVDC Auto Transformer               | . 206 |

|      | 3.3. DC MMC                              | . 206 |

| :    | 3.4. LCL Converter                       | . 207 |

|      | 5.5. Resonant Converter                  | . 207 |

|      | 6.6. LCL Converter Capacitor Calculation | . 207 |

| С.   | VM Accuracy and Computation Data         | 211   |

|      | 2.1. Half-Bridge MMC AVM                 | . 211 |

|      | 2.2. Alternate Arm Converter AVM         | . 212 |

| D. ' | Vind Energy Calculations                 | 213   |

# **List of Figures**

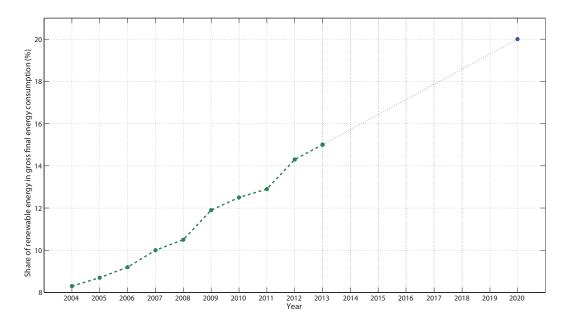

| 1.1.  | Share of renewable energy in gross final energy consumption $[9]$ | 24 |

|-------|-------------------------------------------------------------------|----|

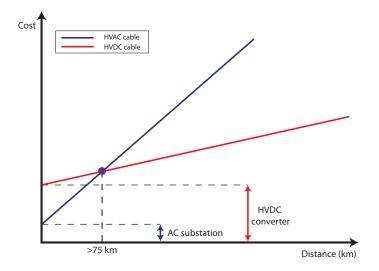

| 1.2.  | Distance versus cost for HVAC and HVDC cables                     | 26 |

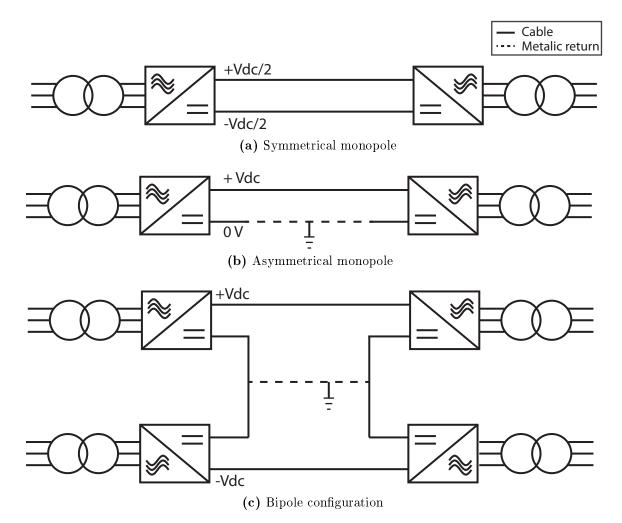

| 1.3.  | HVDC link configurations                                          | 28 |

| 1.4.  | ABB hybrid DC circuit breaker                                     | 31 |

| 1.5.  | European supergrid proposals                                      | 32 |

| 1.6.  | Six pulse CSC with thyristors                                     | 34 |

| 1.7.  | Two-level VSC                                                     | 37 |

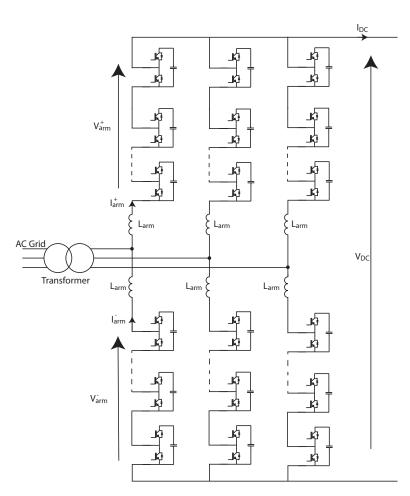

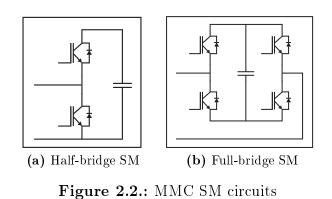

| 2.1.  | Half-bridge MMC                                                   | 46 |

| 2.2.  | MMC SM circuits                                                   | 47 |

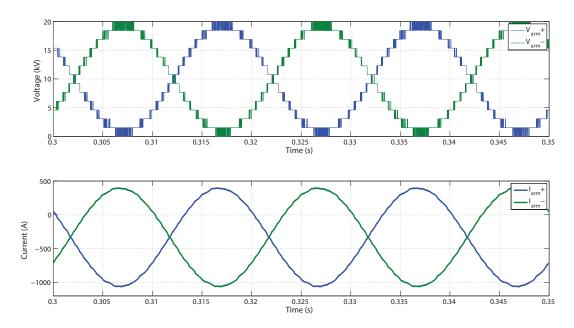

| 2.3.  | Example MMC arm voltage and current waveforms                     | 48 |

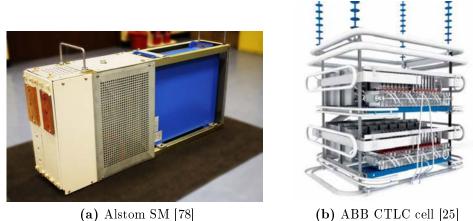

| 2.4.  | Pictures of SM designs from Alstom and ABB from                   | 50 |

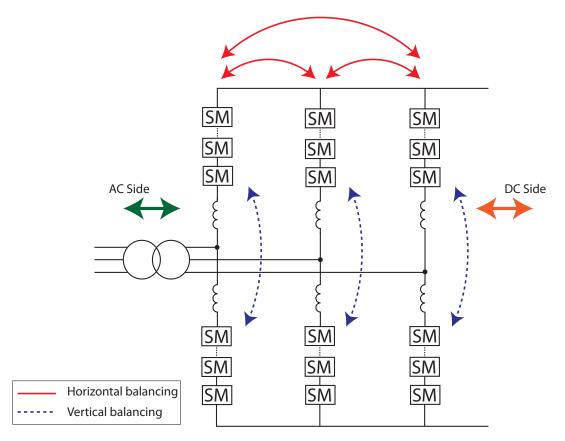

| 2.5.  | MMC energy balancing                                              | 51 |

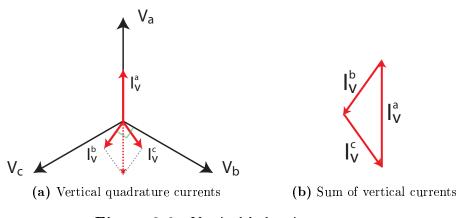

| 2.6.  | Vertical balancing currents                                       | 56 |

| 2.7.  | Double clamp submodule                                            | 57 |

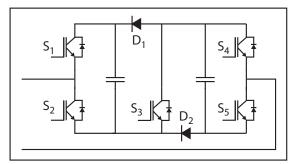

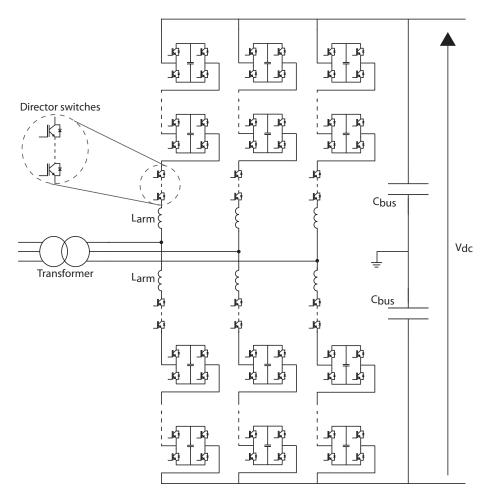

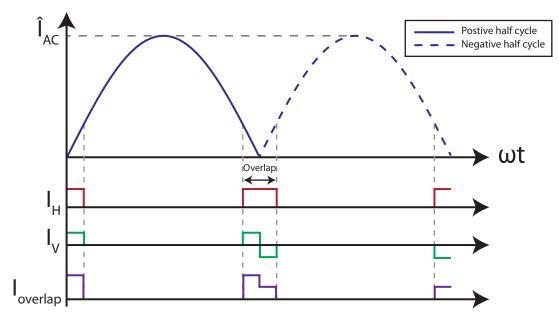

| 2.8.  | AAC circuit diagram                                               | 60 |

| 2.9.  | Balancing currents in the AAC                                     | 63 |

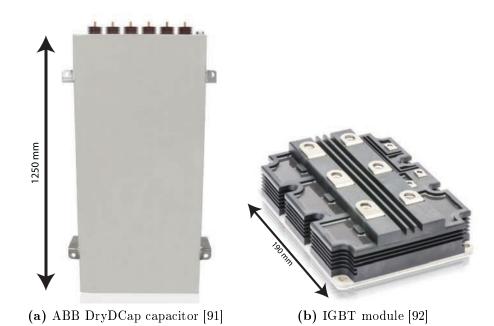

| 2.10. | SM electrical components                                          | 68 |

| 3.1.  | Front-to-front DC/DC converter                                    | 73 |

| 3.2.                                                                                                                       | HVDC auto transformer                                                                               | •   |          | •                | •           | •           | 76                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|----------|------------------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 3.3.                                                                                                                       | Modular multilevel DC/DC converter $\dots \dots \dots \dots$                                        | •   |          | •                | •           |             | 77                                                                                                                              |

| 3.4.                                                                                                                       | LCL DC/DC converter $\dots \dots \dots$ | •   |          | •                |             |             | 79                                                                                                                              |

| 3.5.                                                                                                                       | Unidirectional resonant DC/DC converter $\ldots \ldots \ldots$                                      | •   |          |                  | •           |             | 80                                                                                                                              |

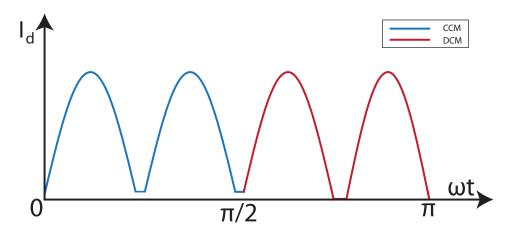

| 3.6.                                                                                                                       | Waveforms for CCM and DCM                                                                           | •   |          |                  | •           | •           | 81                                                                                                                              |

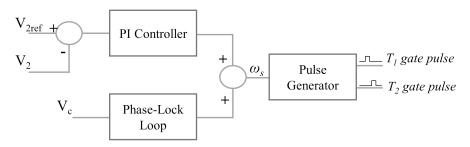

| 3.7.                                                                                                                       | Resonant converter control structure                                                                | •   |          |                  | •           | •           | 83                                                                                                                              |

| 3.8.                                                                                                                       | Resonant converter waveforms                                                                        | •   |          |                  | •           | •           | 84                                                                                                                              |

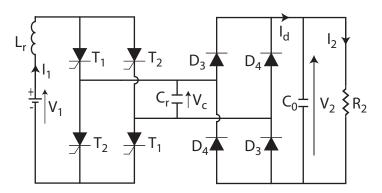

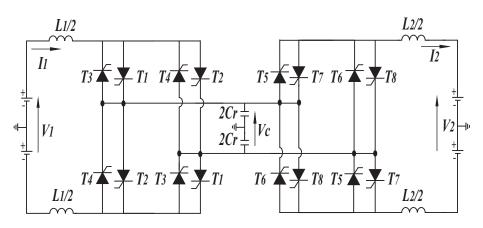

| 3.9.                                                                                                                       | Bidirectional resonant DC/DC converter $\ . \ . \ . \ . \ .$                                        | •   |          |                  | •           | •           | 85                                                                                                                              |

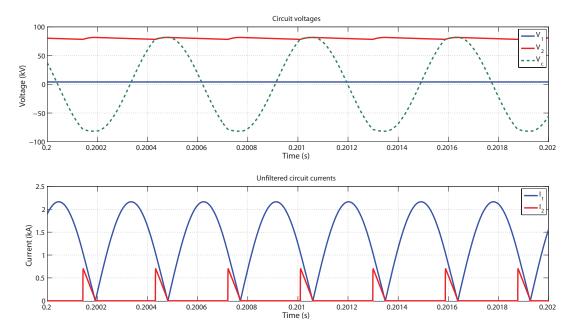

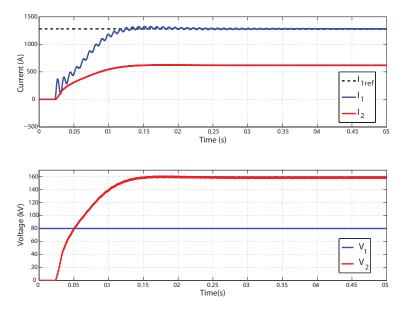

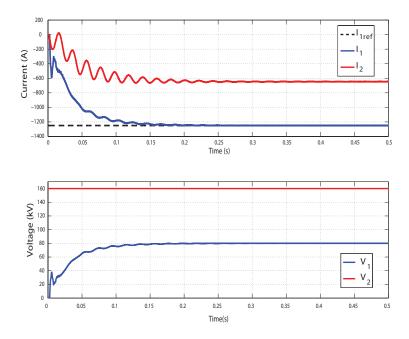

| 3.10.                                                                                                                      | Step-up converter waveforms                                                                         | •   |          | •                | •           |             | 88                                                                                                                              |

| 3.11.                                                                                                                      | Step-down converter waveforms                                                                       | •   |          |                  | •           | •           | 88                                                                                                                              |

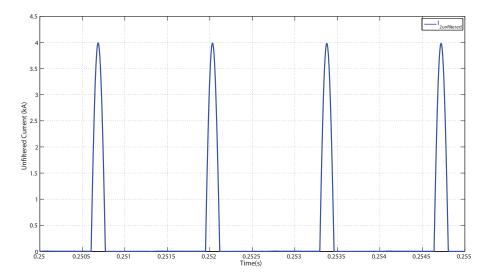

| 3.12.                                                                                                                      | Shape of unfiltered current waveform through thyristor valve                                        | ,   |          |                  | •           | •           | 89                                                                                                                              |

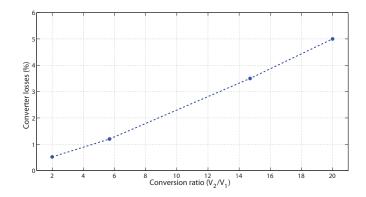

| 3.13.                                                                                                                      | Conversion ratio versus relative power losses [104, 109, 106]                                       |     |          |                  | •           | •           | 90                                                                                                                              |

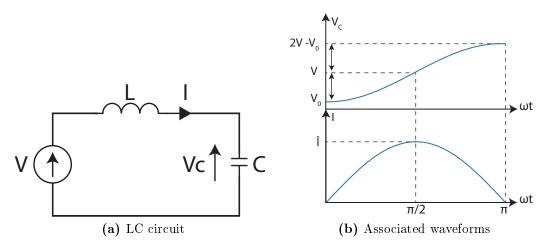

| 3.14.                                                                                                                      | Simple LC circuit and waveforms                                                                     | •   |          | •                | •           |             | 92                                                                                                                              |

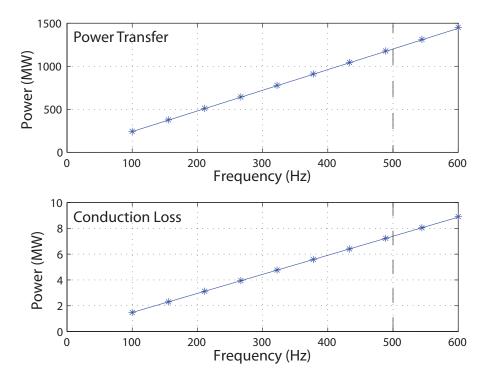

| 3.15.                                                                                                                      | Relationship between power transfer and conduction loss with                                        | l S | wi       | tc               | h-          |             |                                                                                                                                 |

|                                                                                                                            |                                                                                                     |     |          |                  |             |             |                                                                                                                                 |

|                                                                                                                            | ing frequency for Case C $\ldots$                                                                   | •   |          | •                | •           |             | 101                                                                                                                             |

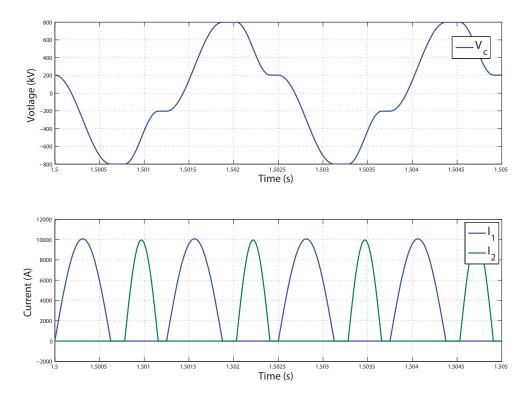

| 3.16.                                                                                                                      | ing frequency for Case C                                                                            |     |          |                  |             |             |                                                                                                                                 |

|                                                                                                                            |                                                                                                     | •   |          |                  |             |             | 102                                                                                                                             |

| 4.1.                                                                                                                       | Voltage and current waveforms for Case C $\ldots$                                                   | •   | •••      |                  |             | •           | 102<br>110                                                                                                                      |

| 4.1.<br>4.2.                                                                                                               | Voltage and current waveforms for Case C                                                            | •   | <br>     | •                | •           | •           | 102<br>110<br>112                                                                                                               |

| 4.1.<br>4.2.                                                                                                               | Voltage and current waveforms for Case C                                                            | •   | <br>     | •                | •           | ·<br>·      | 102<br>110<br>112<br>115                                                                                                        |

| <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                                                           | Voltage and current waveforms for Case C                                                            | •   | <br><br> | •                | ·<br>·      | ·<br>·      | 102<br>110<br>112<br>115<br>116                                                                                                 |

| <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li><li>4.4.</li></ul>                                                              | Voltage and current waveforms for Case C                                                            | •   | <br><br> | •                | ·<br>·<br>· |             | 102<br>110<br>112<br>115<br>116<br>119                                                                                          |

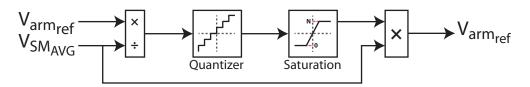

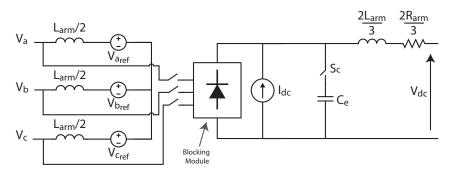

| <ol> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> </ol>                                           | Voltage and current waveforms for Case C                                                            | •   | · · ·    | •                | · · · · ·   | ·<br>·<br>· | 102<br>110<br>112<br>115<br>116<br>119<br>120                                                                                   |

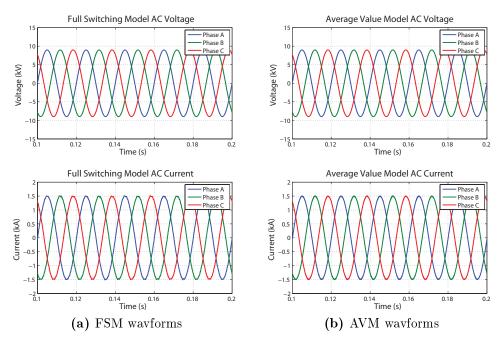

| <ol> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> </ol>               | Voltage and current waveforms for Case C                                                            | •   | · · ·    |                  | · · · · · · | · · · · · · | 102<br>110<br>112<br>115<br>116<br>119<br>120<br>122                                                                            |

| <ol> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>4.8.</li> </ol> | Voltage and current waveforms for Case C                                                            | •   | · · ·    | ·<br>·<br>·<br>· | · · · · · · | ·<br>·<br>· | <ol> <li>102</li> <li>110</li> <li>112</li> <li>115</li> <li>116</li> <li>119</li> <li>120</li> <li>122</li> <li>122</li> </ol> |

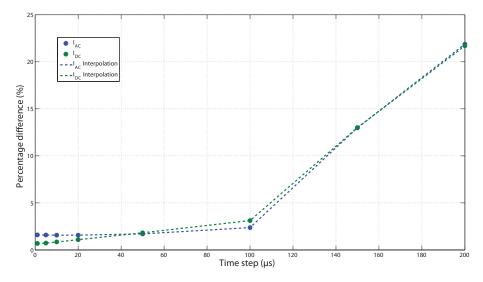

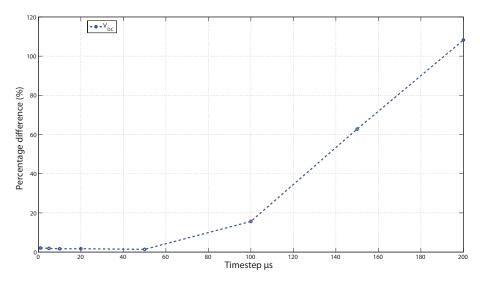

| 4.11. DC voltage percentage difference                                      | . 125 |

|-----------------------------------------------------------------------------|-------|

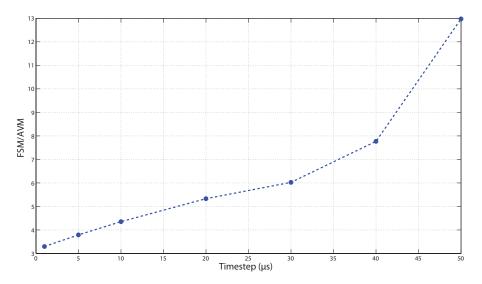

| 4.12. Computation time versus time step                                     | . 125 |

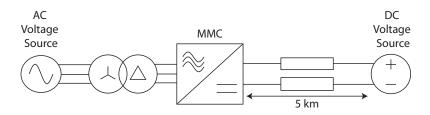

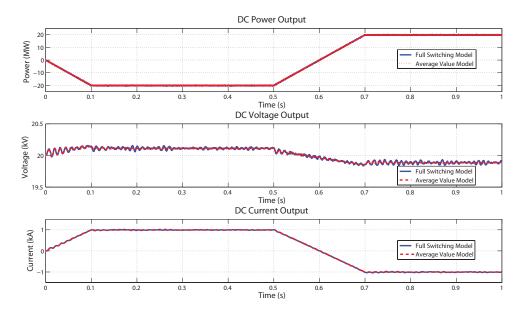

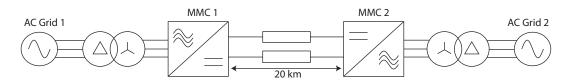

| 4.13. Point-to-point HVDC link                                              | . 126 |

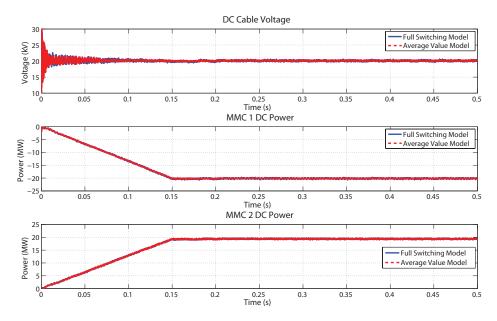

| 4.14. MMC point-to-point normal operating conditions                        | . 127 |

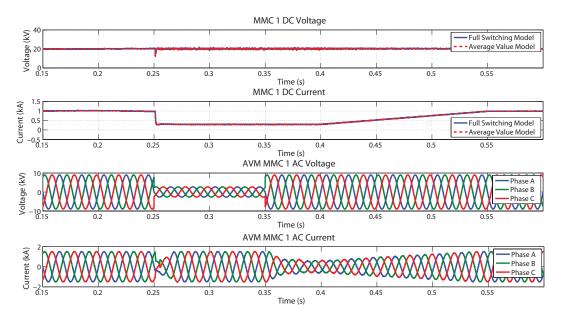

| 4.15. Three-phase AC fault MMC response                                     | . 128 |

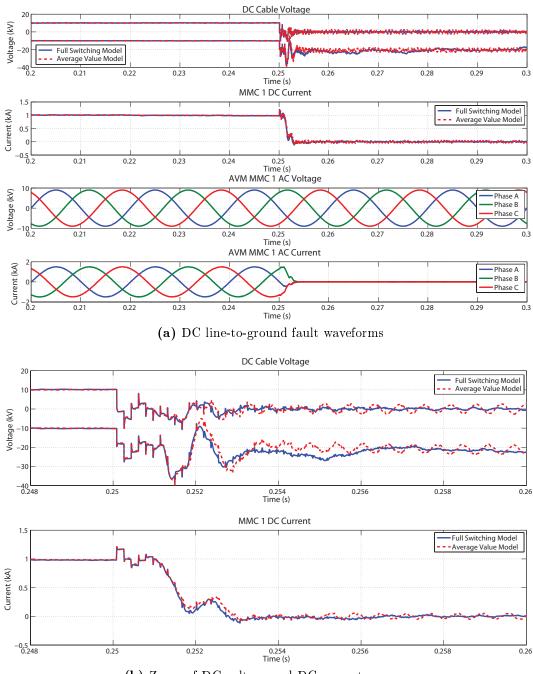

| 4.16. DC line to ground fault results                                       | . 129 |

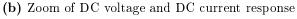

| 4.17. Circuit diagram of the AVM of the AAC                                 | . 131 |

| 4.18. Voltage control limit block diagram for the AAC                       | . 132 |

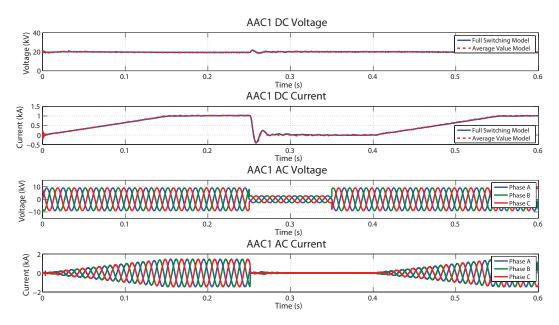

| 4.19. AAC DC converter waveforms                                            | . 133 |

| 4.20. AAC AC converter waveforms                                            | . 134 |

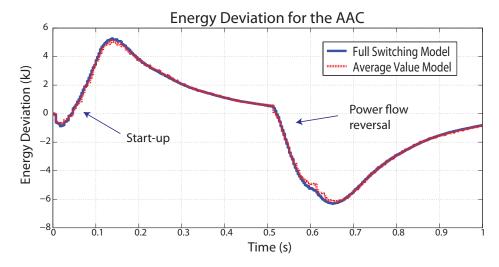

| 4.21. AAC energy deviation waveform                                         | . 134 |

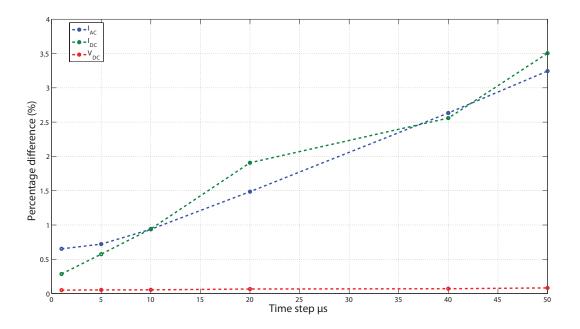

| 4.22. AAC current percentage difference plot                                | . 135 |

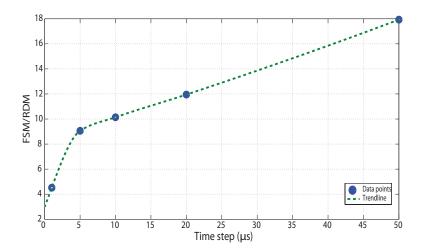

| 4.23. AAC computation speed gain versus time step                           | . 136 |

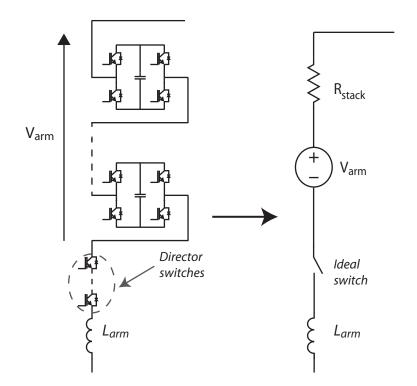

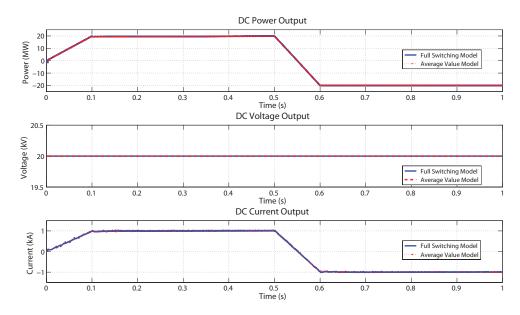

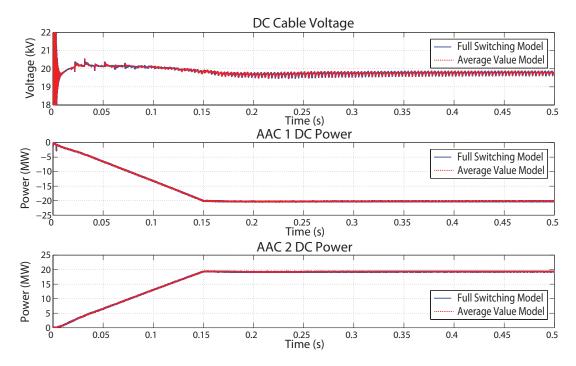

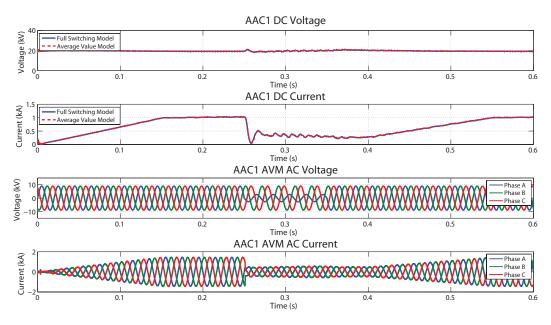

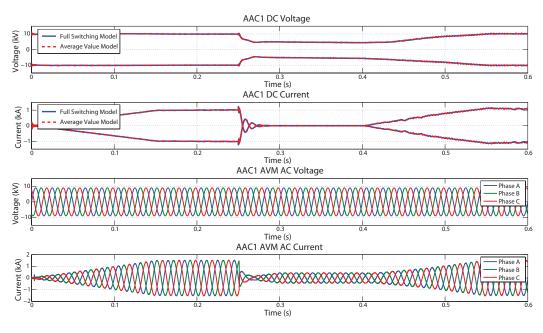

| 4.24. Voltage and power waveforms for normal operating conditions $\ . \ .$ | . 137 |

| 4.25. Three-phase AC fault                                                  | . 138 |

| 4.26. Single-phase-to-ground AC fault                                       | . 138 |

| 4.27. DC line to ground fault                                               | . 139 |

| 4.28. Comparison of experimental and AVM data                               | . 141 |

| 5.1. Dogger Bank tranches adapted from [120]                                | . 145 |

| 5.2. Four terminal network                                                  | . 147 |

| 5.3. Four terminal case study system                                        | . 149 |

| 5.4. Power routing after a fault on the Redcar - Teesside link              | . 153 |

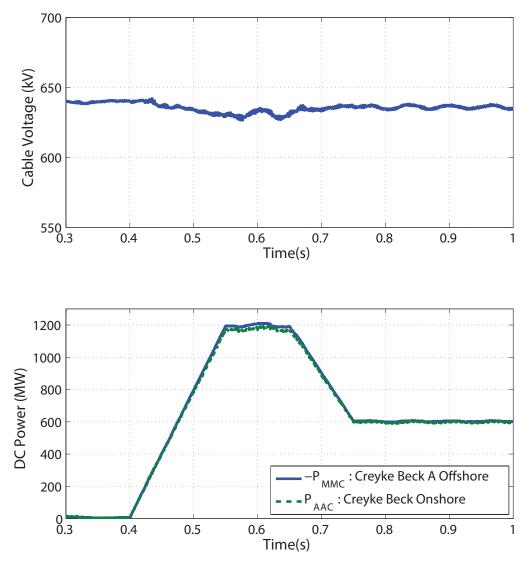

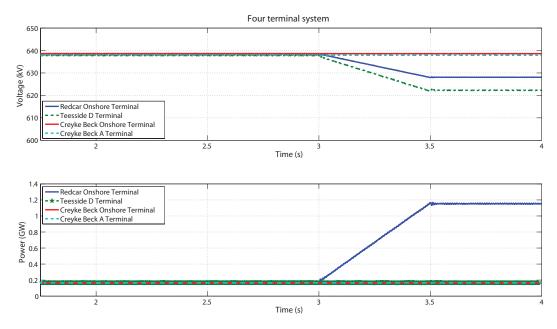

| 5.5. Power transfer on Cryeke Beck link                                     | . 155 |

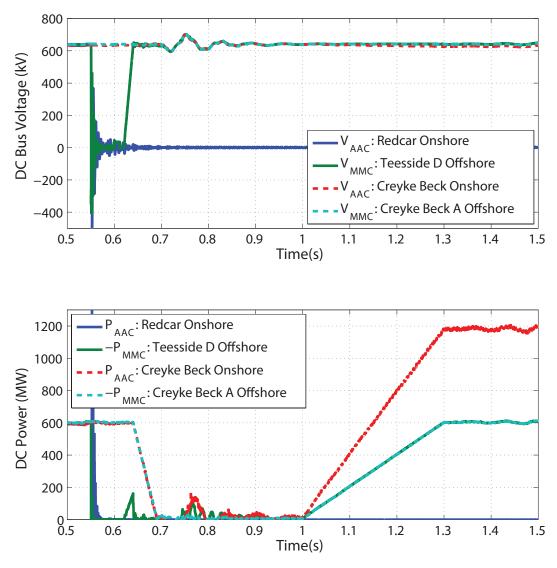

| 5.6. DC line-to-line fault simulation sceanrio                              | . 156 |

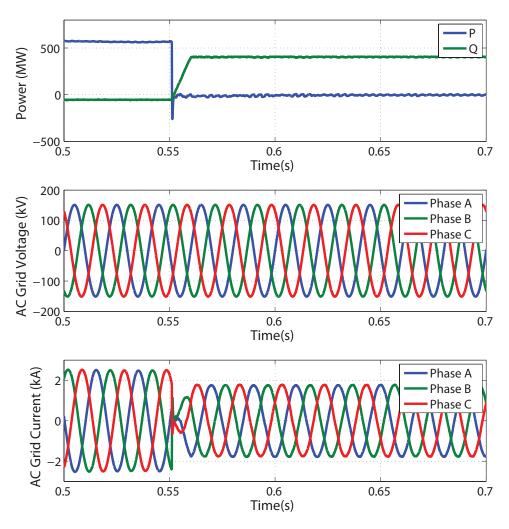

| 5.7. STATCOM operation of the AAC at Redcar station                         | . 158 |

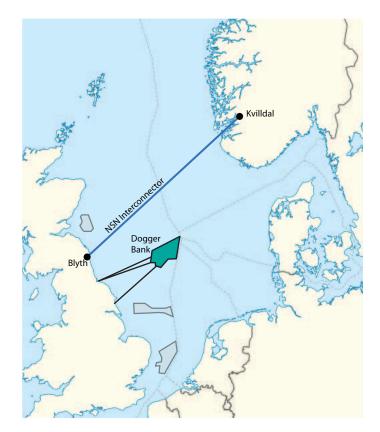

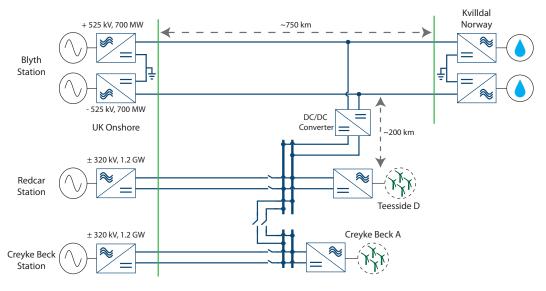

| 5.8. North Sea offshore wind and NSN link                                   | . 160 |

| 5.9.  | Case study system                                                           |

|-------|-----------------------------------------------------------------------------|

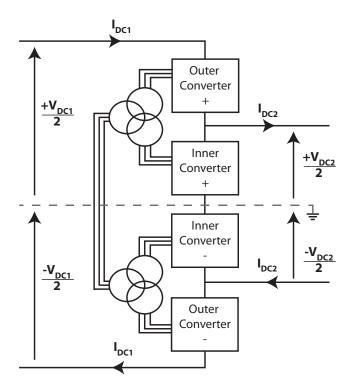

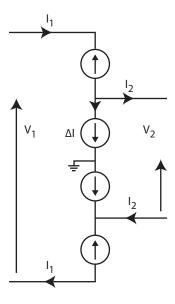

| 5.10. | HVDC auto transformer converter for interconnection of bipolar and          |

|       | monopolar HVDC                                                              |

| 5.11. | AVM of the HVDC auto transformer converter                                  |

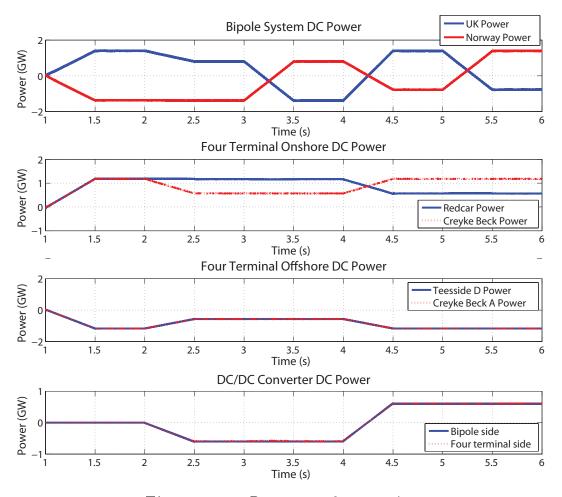

| 5.12. | Power transfer scenarios                                                    |

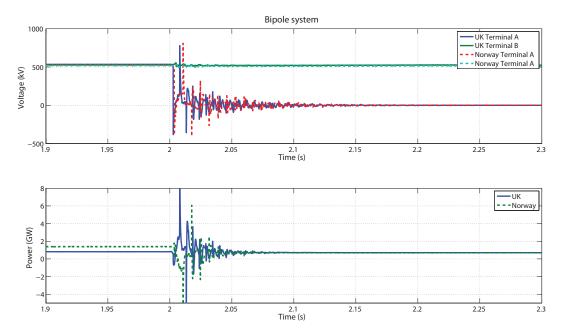

| 5.13. | Bipole voltage at each converter and total power at each terminal for       |

|       | scenario 1                                                                  |

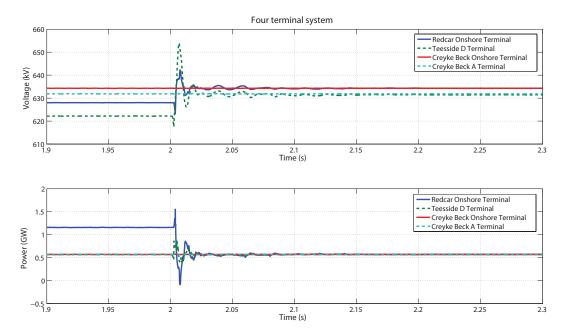

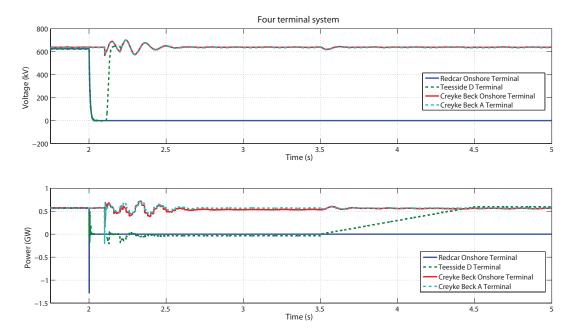

| 5.14. | Four terminal voltage and power at converter terminals for scenario 1 167   |

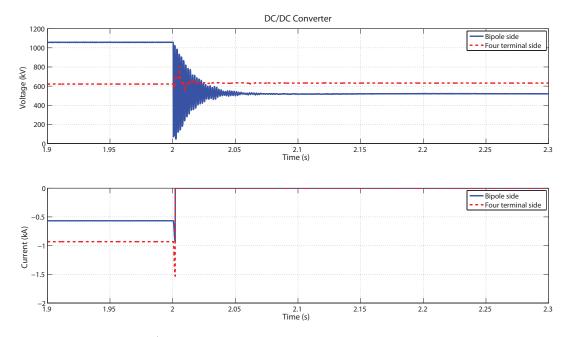

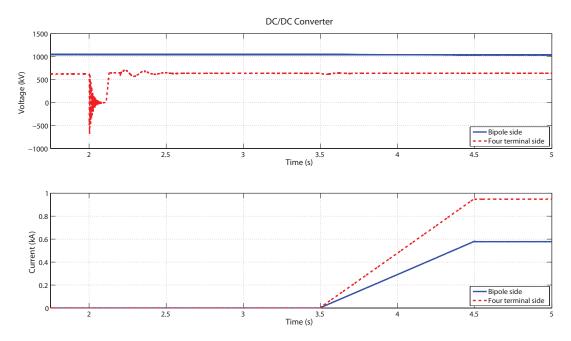

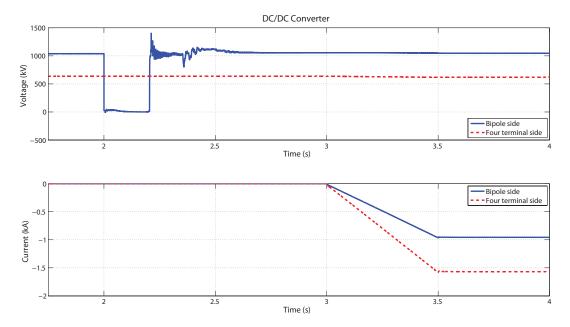

| 5.15. | $\rm DC/\rm DC$ converter terminal voltage and current for scenario $1$ 168 |

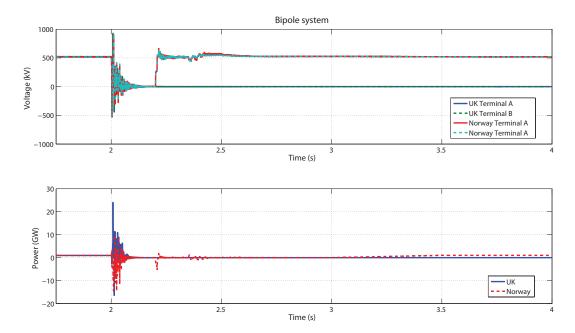

| 5.16. | Bipole voltages at each converter and power at each terminal for            |

|       | scenario 2                                                                  |

| 5.17. | Four terminal voltage and power at each converter terminal for sce-         |

|       | nario 2                                                                     |

| 5.18. | DC/DC converter voltage and current for scenario $2$ $\ldots$               |

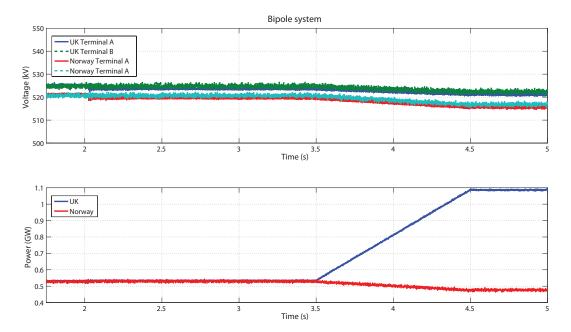

| 5.19. | Bipole voltage at each converter and total power at each terminal for       |

|       | scenario 3                                                                  |

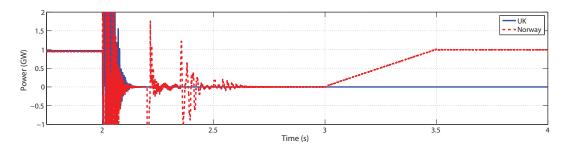

| 5.20. | Zoom in of terminal power of bipole network                                 |

| 5.21. | Four terminal voltage and power at converter terminals for scenario $3$ 172 |

| 5.22. | DC/DC converter terminal voltage and current for scenario $3$ 173           |

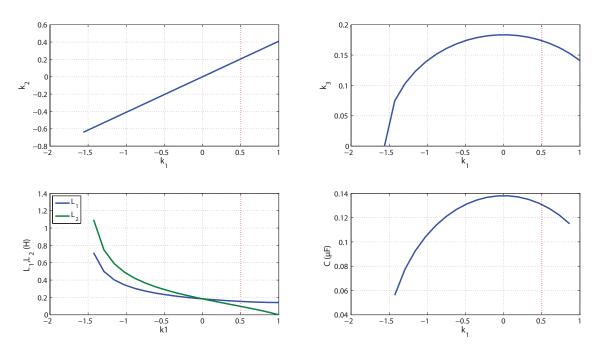

| B.1.  | Plots showing parameter values for varying $k_1$                            |

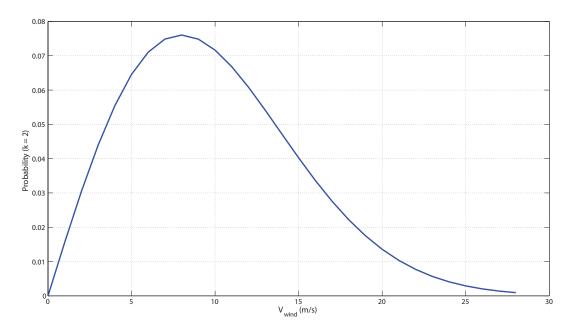

| D.1.  | Probability versus wind speed                                               |

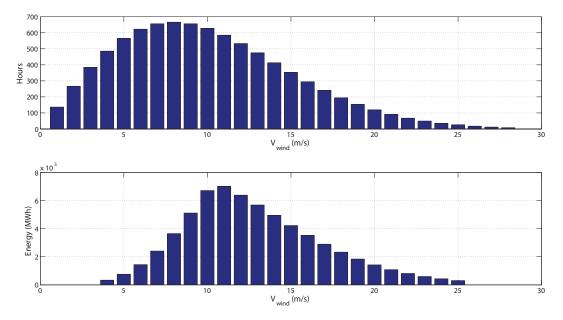

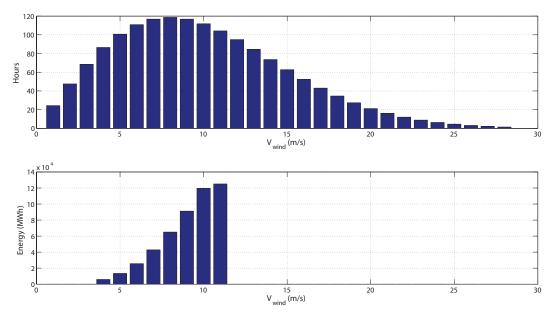

| D.2.  | 1 year case of hours and energy per wind speed                              |

| D.3.  | MTTR case of hours and energy per wind speed                                |

# List of Tables

| 1.1.  | European carbon reduction targets<br>The European Commission $[7,8]~$ .                                                                          | 24  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1.  | MMC topology comparison [85]                                                                                                                     | 58  |

| 2.2.  | Comparison of the MMC and AAC                                                                                                                    | 65  |

| 2.3.  | Scenario parameters                                                                                                                              | 66  |

| 2.4.  | Number of SMs and IGBTs                                                                                                                          | 67  |

| 2.5.  | Capacitor volume estimate                                                                                                                        | 68  |

| 2.6.  | SM volume estimate                                                                                                                               | 69  |

| 3.1.  | Voltage conversion ratio [93]                                                                                                                    | 71  |

| 3.2.  | Phase control thyristor parameters of ABB 5STP 21H4240 $\ldots$ .                                                                                | 86  |

| 3.3.  | 100 MW resonant DC/DC converter parameters                                                                                                       | 87  |

| 3.4.  | Thy<br>ristor conduction losses for 100 MW converter $\ldots \ldots \ldots$                                                                      | 89  |

| 3.5.  | Thyristor data                                                                                                                                   | 99  |

| 3.6.  | Simulation scenarios parameters                                                                                                                  | 100 |

| 3.7.  | Power transfer and conduction loss results                                                                                                       | 101 |

| 3.8.  | Comparison parameters                                                                                                                            | 103 |

| 3.9.  | Comparison results                                                                                                                               | 104 |

| 3.10. | . Capacitor energy storage comparison                                                                                                            | 105 |

| 3.11. | $DC/DC$ converter comparison $\dots \dots \dots$ | 105 |

| 4.1.                                                                                                                                     | Summary of simulation models for simulating MMCs $\ldots \ldots \ldots \ldots \ldots 110$                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2.                                                                                                                                     | MMC model parameters                                                                                                                                                                                                                                       |

| 4.3.                                                                                                                                     | Cable parameters                                                                                                                                                                                                                                           |

| 4.4.                                                                                                                                     | Computation and accuracy comparison for system simulation 130                                                                                                                                                                                              |

| 4.5.                                                                                                                                     | AAC model parameters                                                                                                                                                                                                                                       |

| 4.6.                                                                                                                                     | Accuracy and computation time difference data                                                                                                                                                                                                              |

| 4.7.                                                                                                                                     | Hardware converter specifications                                                                                                                                                                                                                          |

| 5.1.                                                                                                                                     | Interconnecting link cost estimate                                                                                                                                                                                                                         |

| 5.2.                                                                                                                                     | Availability data                                                                                                                                                                                                                                          |

| 5.3.                                                                                                                                     | Cost data for the four terminal network over a 25 year lifetime 153                                                                                                                                                                                        |

| 5.4.                                                                                                                                     | Four terminal case study data                                                                                                                                                                                                                              |

| 5.5.                                                                                                                                     | Switching sequence post fault                                                                                                                                                                                                                              |

|                                                                                                                                          |                                                                                                                                                                                                                                                            |

| B.1.                                                                                                                                     | No DC fault blocking front-to-front converter data                                                                                                                                                                                                         |

|                                                                                                                                          | No DC fault blocking front-to-front converter data                                                                                                                                                                                                         |

| B.2.                                                                                                                                     |                                                                                                                                                                                                                                                            |

| В.2.<br>В.3.                                                                                                                             | DC fault blocking front-to-front converter data                                                                                                                                                                                                            |

| B.2.<br>B.3.<br>B.4.                                                                                                                     | DC fault blocking front-to-front converter data                                                                                                                                                                                                            |

| B.2.<br>B.3.<br>B.4.<br>B.5.                                                                                                             | DC fault blocking front-to-front converter data                                                                                                                                                                                                            |

| <ul><li>B.2.</li><li>B.3.</li><li>B.4.</li><li>B.5.</li><li>B.6.</li></ul>                                                               | DC fault blocking front-to-front converter data206HVDC auto transformer data206DC MMC data206LCL converter data207                                                                                                                                         |

| <ul><li>B.2.</li><li>B.3.</li><li>B.4.</li><li>B.5.</li><li>B.6.</li><li>B.7.</li></ul>                                                  | DC fault blocking front-to-front converter data206HVDC auto transformer data206DC MMC data206LCL converter data207Resonant converter data207                                                                                                               |

| <ul> <li>B.2.</li> <li>B.3.</li> <li>B.4.</li> <li>B.5.</li> <li>B.6.</li> <li>B.7.</li> <li>C.1.</li> </ul>                             | DC fault blocking front-to-front converter data                                                                                                                                                                                                            |

| <ul> <li>B.2.</li> <li>B.3.</li> <li>B.4.</li> <li>B.5.</li> <li>B.6.</li> <li>B.7.</li> <li>C.1.</li> <li>C.2.</li> </ul>               | DC fault blocking front-to-front converter data206HVDC auto transformer data206DC MMC data206LCL converter data207Resonant converter data207Passive component values for LCL DC/DC converter209Percentage difference data211                               |

| <ul> <li>B.2.</li> <li>B.3.</li> <li>B.4.</li> <li>B.5.</li> <li>B.6.</li> <li>B.7.</li> <li>C.1.</li> <li>C.2.</li> <li>C.3.</li> </ul> | DC fault blocking front-to-front converter data206HVDC auto transformer data206DC MMC data206LCL converter data207Resonant converter data207Passive component values for LCL DC/DC converter209Percentage difference data211Computation time comparison211 |

# Nomenclature

| AAC                  | Alternate Arm Converter                                           |

|----------------------|-------------------------------------------------------------------|

| ADM                  | Alternate Discontinuous Mode                                      |

| AVM                  | Average Value Model                                               |

| ВМ                   | Blocking Module                                                   |

| $\operatorname{CCM}$ | Continuous Conduction Mode                                        |

| $\operatorname{CSC}$ | Current Source Converter                                          |

| CTLC                 | Cascases Two-Level Converter                                      |

| DCM                  | Discontinuous Conduction Mode                                     |

| EENS                 | Expected Energy Not Supplied                                      |

| EES                  | Expected Energy Supplied                                          |

| ENTSO-E              | European Network of Transmission System Operators for Electricity |

| FB                   | Full-Bridge                                                       |

| FSM                  | Full Switching Model                                              |

| HB                   | Half-Bridge                                                       |

- HVAC High Voltage Alternating Current

- HVDC High Voltage Direct Current

- IGBT Insulated Gate Bipolat Transistor

- LCoE Levelised Cost of Energy

- MAVM Modified Average Value Model

- MMC Modular Multilevel Converter

- MTBF Mean Time Between Failure

- MTDC Multi-Terminal DC

- MTTR Mean Time To Repair

- MWh Megawatt Hour

- NOP Normally Open Point

- PI Proportional Integral

- PWM Pulse Width Modulation

- RES Renewable Energy Source

- rms Root Mean Square

- SHE Selective Harmonic Elimination

- THD Total Harmonic Distortion

- VSC Voltage Source Converter

- XLPE Cross-Linked Polyethylene

## 1. Introduction

This thesis will describe work on particular aspects of offshore transmission networks aimed at increasing renewable energy penetration as part of a response to climate change. It is widely accepted that the increase in greenhouse gases since the preindustrial era (1861-1890) has contributed significantly to global climate change [1]. Climate change has had direct impact on humans and natural systems across the world. Therefore, it is essential to mitigate against further dangerous increases in the temperature of the climate system caused by greenhouse gas emissions [2]. It is believed that limiting the global mean temperature rise to 2°C above pre-industrial times could avoid many irreversible climate system changes [3]. The Kyoto Protocol calls for the reduction in six greenhouse gases including the main contributor  $CO_2$ [4, 1].

A significant producer of  $CO_2$  is the use of fossil fuels to power homes and industry [1]. Thus a key step in preventing further climate change is to decarbonise the energy sector. This decarbonisation can be achieved by using carbon neutral fuel sources, such as Renewable Energy Sources (RES), and by safeguarding forests [1, 5]. The leading RES is bioenergy, followed by hydropower and wind generation [5]. At present 5.3% of global power generation comes from RES [6].

The European Commission has put regulatory framework in place to reduce carbon emissions and increase the use of RES for its member states. The targets for 2020 and 2030 are given in Table 1.1.

| Measure                                         | EU 2020 | EU 2030 |

|-------------------------------------------------|---------|---------|

| Reduce greenhouse gases compared to 1990 levels | 20%     | 40%     |

| Increase share of renewable energy sources      | 20%     | 27%     |

| Increase energy efficiency <sup>1</sup>         | 20%     | 27%     |

Table 1.1.: European carbon reduction targets The European Commission [7, 8]

The 2020 targets were launched in 2010 to create conditions for sustainable economic growth and Figure 1.1 shows the increase of RES into the EU energy system since 2004.

Figure 1.1.: Share of renewable energy in gross final energy consumption [9]

These European targets have specific implications for the UK energy system, namely a target of 15 % of all energy used is to come from RES by 2020, this includes electricity, heat and transport [10]. This target translates to 30% of electricity generation to come from RES [11]. Toward the end of 2014 the penetration of renewable generation in to the UK electricity system was 17.8% [11]. Offshore wind generation is likely to be a large contributor to meeting the renewable targets for the UK, with more than 33 GW of potential capacity identified in UK waters [12]. Offshore wind has the advantages of a higher energy output and less constraints from public planning issues when compared to onshore wind generation [13]. However, building wind generation offshore has a high capital requirement, and in 2012 the Round 3 developments had a levelised cost of energy (LCoE) of £134 per megawatt hour (MWh) which was 1.6 times greater than the cost of gas generation [14]. The estimated LCoE at the end of 2014 was 121 £/MWh, and the cost is mainly being driven down by the use of larger wind turbines [15].

### 1.1. Offshore Transmission Networks

### 1.1.1. AC versus DC Transmission

Traditionally High Voltage AC (HVAC) has been used to transmit large amount of electrical energy. This is due to the key elements required for AC transmission being available from the beginning of the 20th century [16]. The transformer enables easy conversion to higher voltages which enables efficient transport of energy over long distances, and the AC circuit breaker can interrupt AC faults effectively [17].

In recent years High Voltage DC (HVDC) has become increasingly popular for bulk power transmission over great distances. This is due to advancement in semiconductor devices and to several advantages that HVDC has over traditional HVAC transmission. The first being that HVDC is not limited in the distance it can transfer power, Figure 1.2 shows the cost each transmission technology as the distance is increased for cable technology.

Figure 1.2.: Distance versus cost for HVAC and HVDC cables

There is an initial setup cost associated with HVDC due the necessity of an AC/DC converter, at each end of the link, and for short cable distances HVAC is the more economic solution. For longer cables, HVAC has a limited power transfer due to the high capacitance of the cable. As the cable is a closed conductor, this causes increased capacitance and thus an increased capacitive charging current [18]. For cable lengths greater than approximately 75 km, additional reactive power compensation is necessary to charge the cable which makes the option uneconomical [18]. Alternatively HVDC transmission can be used as the cables only require charging once and it does not suffer reactive losses [19]. For overhead lines HVAC is the economic choice up to approximately 500 km [20].

HVDC can also carry more power for a given conductor and insulator size than an equivalent HVAC conductor [21]. A single DC circuit requires a minimum of two conductors, compared to traditional AC transmission which requires three. This results in HVDC transmission requiring a smaller right of way when compared with HVAC [22]. Another advantage of HVDC is that can be used to connect asynchronous AC systems [21]. This can be done using back-to-back links, where two AC/DC converters are placed in the same station. Each AC/DC converter can adapt to the voltage and frequency of the AC system it is connected to [23]. This also means that the HVDC link can act as a firewall between the two connected AC systems, meaning that a disturbance on one AC grid is not seen on the other [24].

Given the great distance many of the Round 3 wind generation developments are from the UK shore, it is likely that many developments will be connected using HVDC transmission. Additionally any interconnectors with Europe may require HVDC as the asynchronous AC systems cannot be directly connected easily using HVAC, and many of the connections would be made using submarine cables.

HVDC link configurations can vary depending on the application. Some of the different configurations are shown in Figure 1.3. The symmetric monopole has no ground current and thus the converter transformers are not exposed to DC stresses. This arrangement requires two cables rated for half the DC voltage each [25]. The asymmetrical monopole requires one cable rated for the full DC voltage and can use a metallic return which requires less insulation, making it less expensive than the symmetric monopole scheme as only one fully rated cable is required. However the converter transformers must be designed to cope with DC stresses, as there is a DC voltage offset due to the asymmetric configuration of the converter. This configuration also enables expansion to a bipole system allowing an increase of power transfer capability at a later date. The monopole solutions are the least expensive option as they require only one converter per terminal [26]. The bipole system has two converters, at half the power rating, at each terminal and the system has the advantage of being able to operate at 50% power in the event of a fault on one of the cables or one of the converters. This arrangement also requires that the transformers

be able to handle DC voltage stress [25].

Figure 1.3.: HVDC link configurations

### 1.2. Multi-Terminal DC Grids

As more point-to-point HVDC links are completed, either between the UK and offshore generation or between the UK and other countries, it may become desirable to connect adjacent links to create a Multi-Terminal DC (MTDC) grid. A MTDC network is one that has three or more terminals. An offshore MTDC network in the North Sea could act as a precursor to a European Super Grid [27]. A pan-European grid could bring several advantages [28, 29]:

- Improved security of supply through international interconnection

- Balancing intermittent renewable energy sources over a wider area

- Decarbonisation of the electricity network through increased renewable energy penetration

- Increased energy trading within Europe

- Reduce congestion in existing AC transmission systems

- Reduced dependency on imports of fossil fuels

Despite these advantages there are a number of challenges to realising this grid. The main challenges are regulatory, economic, and technical. At present there are no grid codes in place for MTDC networks. A grid code would specify standards for voltage and power rating, and would detail regulation for interconnecting adjacent HVDC systems [28]. Such a grid code would complement the agreement made between the European countries which signed the North Sea Countries' Offshore Grid Initiative Memorandum of Understanding [30]. This memorandum outlines that the signatory countries are to cooperate to find common solutions to the development of an offshore grid in the North Sea [30]. The European Network of Transmission

System Operators for Electricity (ENTSO-E) has developed a draft network code for HVDC connections and DC connected generation, the document does not explicitly outline any regulation for MTDC networks [31]. The ENTSO-E draft does outline framework for HVDC links between different TSOs but it does not provide recommendations for standard DC voltages or maximum DC power ratings. Cigré working group B4.56 are currently working on guidelines for grid codes for MTDC grids, which includes guidelines for technical specifications such as DC voltage range and functional requirements for future extensions [32].

A significant amount of capital investment is necessary to create a pan European grid and it is likely to come from several investors and governments, rather than a single investor. The investment required for power transmission infrastructure is estimated to be in the range of C114-184 billion up to 2030 [33]. By coordinating and creating an offshore grid, rather than using solely point-to-point links, significant investment savings could be made [29].

### 1.2.1. Technical Challenges for MTDC

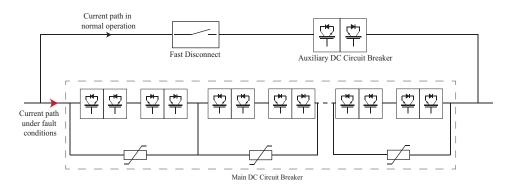

There are also technical barriers to a MTDC grid including difficulties in protection of DC networks and voltage conversion. A DC grid has low impedance through absence of impedance, which results in low losses, but in the event of a short circuit the low impedance of the network means that the fault current rises quickly and spreads rapidly through the network [34]. To break this fault current it must be forced to zero, as there is no natural zero crossing as in the AC system. Thus a DC circuit breaker must force the fault current to zero, dissipate the energy from the system, and do so quickly [34]. The speed at which a DC breaker opens is dependent on its topology. Electromechanical DC breakers, which use high speed mechanical switches, can operate at high voltages but take some time to open, in the region of 100 ms [35]. Solid-state DC circuit breakers, using semiconductor devices, can achieve fast opening times, in the order of microseconds. The cost of such a DC circuit breaker is high, and it has higher operational losses than a electromechanical breaker. At present there are no DC circuit breakers commercially available but manufacturers are developing prototypes. The most promising design prototypes are hybrid breakers which use a combination of a high speed mechanical switch, to maintain low power losses, and fast power electronic switches to achieve fast opening times. The ABB hybrid DC circuit breaker is shown in Figure 1.4 [36].

Figure 1.4.: ABB hybrid DC circuit breaker

The largest prototype to date is the State Grid Research Institute DC circuit breaker which operates at 200 kV and is capable of interrupting fault current of 15 kA within 3 ms [37].

As of yet there are no standardised DC voltage levels and as cable ratings increase it is likely that newly commissioned projects will use the latest technology, meaning adjacent HVDC projects may not operate at the same voltage level [38]. Connecting projects operating at different voltages requires a voltage conversion stage. This is achieved using a DC/DC converter which are described further in Chapter 3. How a European Supergrid might look, both technically and geographically, is still unclear. There are many proposals about how this supergrid might look, and some are shown in Figure 1.5.

(a) Friends of the Supergrid [39]

(b) European Wind Energy Association

(c) DNV GL vision [40]

Figure 1.5.: European supergrid proposals

Many of the proposals have the same traits, they show significant interconnection between European countries, and that the UK offshore developments play a big role in developing a MTDC network. An additional common feature is that several HVDC links connect at a single point, or node. This node could be a single platform or it could spread across a large geographical area. It is not yet known for certain how these nodes will be built.

There are two broad approaches that can be made to create this node, the use of either AC or DC technology. An AC node would make use of readily available and well known equipment, however the distance that AC submarine cables can travel is limited. An AC hub could be used within a wind farm development to allow a common connection point for several adjacent wind farms [41]. The clustering of nearby wind farms into AC hubs could also save a large amount of investment [42].

The alternative is to use DC technology to create this node. The Belgian transmission system operator, Elia, proposes an international HVDC platform in the North Sea that could enable energy trading between countries connected to that platform [43]. A benefit of using DC to create these offshore nodes that DC/DC converter could potentially be more compact than AC transformers, as medium frequency transformers can be used within the DC/DC converter, reducing platform size [44]. Additionally DC cables are more economical for cable applications and have lower losses than equivalent AC cables [45].

### **1.3. HVDC Converters**

In order to convert from AC to DC, a power electronic converter is required at each terminal. There are two HVDC converter types, Current Source Converters (CSC) and Voltage Source Converters (VSC).

#### 1.3.1. Current Source Converter

The first commercial CSC was the Gotland 1 project by ABB, built in Sweden in 1954 and was operated at 200 kV and 20 MW [46]. The converters in this project used mercury arc valves, however this technology suffers from several problems, including limited voltage ratings, a limit on the rate of change of load, and high maintenance costs [47]. Modern CSCs use thyristor valves, and the first thyristor based converter was the Eel River Scheme in Canada in 1972 [46]. Voltages of up to 1,100 kV are now available with power transfer capability of up to 10 GW [48]. Today the largest CSC project commissioned is the Jinping - Sunan project in China, which is rated for 7.2 GW at  $\pm$  800 kV [49]. A simplified circuit diagram of the thyristor valve based CSC is shown in Figure 1.6.

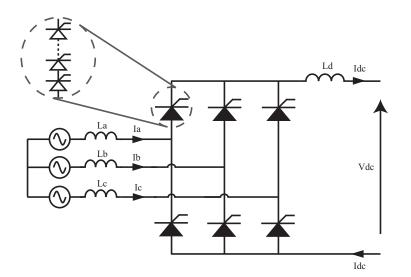

Figure 1.6.: Six pulse CSC with thyristors

The circuit is laid out as a three-bridge rectifier, and each thyristor in Figure 1.6 represents a value of series connected devices. The firing angle of the thyristors determines whether the converter is inverting or rectifying [50]. The power flow control is achieved by varying the current and maintaining a constant voltage magnitude. In order to change the direction of the power flow the DC voltage polarity

is reversed and the current is unidirectional [46]. The number of series thyristor devices required is proportional to the value of the DC bus voltage. The advantage of using thyristors is that they are very robust and have high voltage and current ratings, which enable bulk power transfer. Typical phase control thyristors, which are used for HVDC applications, are available with ratings up to 8.5 kV and 3.6 kA [51]. The converter has low power losses in the region of 0.7 % [52]. The power losses of the converter are an important factor and are optimised to be low in order to reduce the cost of losses over the lifetime of the converter [50].

The CSC has a significant reactive power load, this is due to the converter operating with a delay due to the firing angle of the thyristor which results in the current lagging the voltage [50]. This requires reactive power compensation, which comes mainly from AC harmonic filters [26]. In order to ensure that operates correctly it is necessary to connect both terminals to strong AC networks [21]. The filtering requirement is a major factor in the footprint of the converter, and can be as much as 75 % of the total footprint of the converter station [26].

#### **CSC** for MTDC Grids

The use of CSC in MTDC is limited as it is difficult to change the direction of power flow in a CSC based MTDC network. This is due to the power flow reversal being achieved by changing the voltage polarity. Thus special DC side switching arrangements must be put in place to allow the direction of power to change at one terminal while the same power direction is maintained on the other terminals [26]. Despite this difficulty the first MTDC schemes were developed using CSCs. The first MTDC scheme is the world was the SACOI project, which is still used to exchange energy with the Italian mainland with the islands of Sardinia and Corsica. The original scheme consisted of two terminals and was upgraded to three terminals in 1988 to add the connection to Corsica [53]. Another existing CSC MTDC scheme is the Québec - New England project commissioned in the early 1990's, and it was used to connect remote hydro generation in Québec to load centres in Montreal and Boston [54].

#### 1.3.2. Voltage Source Converter

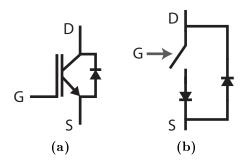

The VSC is becoming increasingly popular for HVDC applications. The first HVDC VSCs were introduced in 1997 by ABB and the first converters were installed in Sweden in a demonstrator project [55]. The demonstrator was a 3 MW,  $\pm$  10 kV converter with 10 km of overhead DC lines. Today the largest VSC commissioned is the INELFE bipole link connecting the French and Spanish transmission systems, which enables the transfer of 2000 MW at  $\pm$  320 kV between the two systems [56]. The semiconductor device used for HVDC VSCs is the Insulated Gate Bipolar Transistor (IGBT). The IGBTs can be controlled to turn off as well as on which means the VSC can provide flexible and independent control of real and reactive power [26]. This ability allows the VSC to connect to small or weak AC systems, making it the preferred technology for connecting intermittent remote generation such as wind generation [25]. The IGBT is limited in current and voltage ratings and more devices are required in the circuit when compared with the thyristor based CSC devices. However ratings are starting to become comparable to thyristors with the latest generation of IGBTs rated for 4.5 kV and 2 kA [57]. The first generation of VSC, the two-level converter is shown in Figure 1.7a.

Figure 1.7.: Two-level VSC

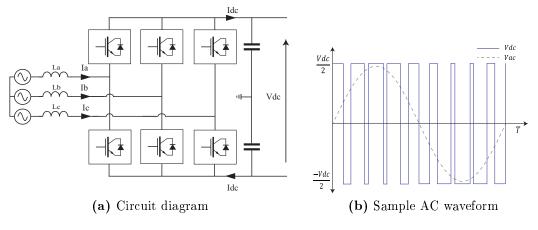

The converter works by holding a constant DC voltage and the power flow is controlled by changing the value of the DC current. The power flow is reversed by changing the polarity of the current. A DC bus capacitor is required on the DC terminals of the converter to stabilise the DC voltage and to absorb the harmonic switching content [58]. In the two-level VSC the AC waveform is generated by switching between the positive and negative DC voltage. Pulse Width Modulation (PWM) is used to improve the shape of the AC waveform, as shown in Figure 1.7b. PWM uses high switching frequencies which increases the switching losses of the converter and filtering is needed to remove the switching content from the AC waveforms [59]. Filtering increases the losses and the volume of the converter, however the filtering requirement is lower than the CSC as VSCs do not require reactive power compensation [60]. The power loss figure for the first generation of two-level VSCs was approximately 3 % [25].

In order to reach the high voltages required for HVDC the two-level converter can have hundreds of IGBTs connected in series to block the DC voltage. It is a challenge to switch all of the series connected devices simultaneously. If one devices turns off prior to the other devices it will not be able to block the full DC bus voltage and will fail [58]. The precautions to prevent this become increasingly burdensome and leads to a restriction in the DC voltage that can be achieved with this design and subsequently limits the power transfer capability of the converter.