## Imperial College London Department of Electrical and Electronic Engineering

## Design of Approximate Overclocked Datapath

Kan Shi

Supervised by George A. Constantinides

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy of Imperial College London and the Diploma of Imperial College London

#### Abstract

Embedded applications can often demand stringent latency requirements. While high degrees of parallelism within custom FPGA-based accelerators may help to some extent, it may also be necessary to limit the precision used in the datapath to boost the operating frequency of the implementation. However, by reducing the precision, the engineer introduces quantisation error into the design.

In this thesis, we describe an alternative circuit design methodology when considering trade-offs between accuracy, performance and silicon area. We compare two different approaches that could trade accuracy for performance. One is the traditional approach where the precision used in the datapath is limited to meet a target latency. The other is a proposed new approach which simply allows the datapath to operate without timing closure. We demonstrate analytically and experimentally that for many applications it would be preferable to simply overclock the design and accept that timing violations may arise. Since the errors introduced by timing violations occur rarely, they will cause less noise than quantisation errors.

Furthermore, we show that conventional forms of computer arithmetic do not fail gracefully when pushed beyond the deterministic clocking region. In this thesis we take a fresh look at Online Arithmetic, originally proposed for digit serial operation, and synthesize unrolled digit parallel online arithmetic operators to allow for graceful degradation. We quantify the impact of timing violations on key arithmetic primitives, and show that substantial performance benefits can be obtained in comparison to binary arithmetic. Since timing errors are caused by long carry chains, these result in errors in least significant digits with online arithmetic, causing less impact than conventional implementations.

#### Acknowledgements

Upon the finish of this thesis, I would like to offer my sincere gratitude to all the people who helped and encouraged me throughout the course of my PhD.

Firstly I would like to thank my supervisor George Constantinides for his remarkable vision in academic research and brilliant supervision of my PhD, without whom this thesis would not have been possible. He has shared his knowledge and ideas, been patient and constructive to my thoughts, and more importantly, nurtured my confidence in my early research career.

I must thank all my colleagues in CAS and all my friends at Imperial. Special thanks are made to David Boland for all his genuine assistances since the first day when I joined CAS. It is truly a great pleasure to work with him. His incredible talents and enthusiasm towards work and life keep motiving me to become a better person. I also would like to thank my awesome friends Huafeng Liu, Shuo Yang and Lan Sun, for consistently making me feel as warm as home in London.

Last of all I sincerely thank my parents Jianhua Shi and Xiaoman Ni, my parents in law Wei Zhang and Shaoxia Yuan, and my wife Xiaozhe Zhang, for their endless love, wisdom and support in my life. Finally to my beloved grandfather Quan Ni, this thesis is for you.

### **Copyright Declaration**

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

# Contents

| A            | bstra | ct      |                                                 | i  |

|--------------|-------|---------|-------------------------------------------------|----|

| $\mathbf{A}$ | ckno  | wledge  | ments                                           | ii |

| C            | opyri | ight De | eclaration                                      | ii |

| 1            | Intr  | oducti  | on                                              | 1  |

|              | 1.1   | Thesis  | Organization                                    | 4  |

|              | 1.2   | Staten  | nent of Originality                             | 5  |

|              | 1.3   | Public  | ations                                          | 6  |

| <b>2</b>     | Bac   | kgrou   | ıd                                              | 8  |

|              | 2.1   | Introd  | uction                                          | 8  |

|              | 2.2   | Word-   | Length Optimisation                             | 9  |

|              | 2.3   | Appro   | ximate Computing                                | 11 |

|              |       | 2.3.1   | Better Than Worst-Case Design                   | 13 |

|              |       | 2.3.2   | Unreliable Computing with Unreliable Components | 16 |

|              |       | 2.3.3   | Summary                                         | 19 |

|   | 2.4 | Online  | Arithmetic                                        | 20 |

|---|-----|---------|---------------------------------------------------|----|

|   |     | 2.4.1   | Redundant Number System                           | 21 |

|   |     | 2.4.2   | Digit-Serial Arithmetic                           | 24 |

|   |     | 2.4.3   | Theoretical Background of Online Arithmetic       | 25 |

|   |     | 2.4.4   | Advantages and Disadvantages of Online Arithmetic | 27 |

|   |     | 2.4.5   | Current Research                                  | 29 |

|   |     | 2.4.6   | Summary                                           | 33 |

| 3 | Ove | rclocke | ed Datapath with Conventional Arithmetic          | 35 |

|   | 3.1 | Introd  | uction                                            | 35 |

|   | 3.2 | Ripple  | Carry Adder                                       | 36 |

|   |     | 3.2.1   | Adder Structures in FPGAs                         | 37 |

|   |     | 3.2.2   | Probabilistic Model of Truncation Error           | 39 |

|   |     | 3.2.3   | Generation of Overclocking Error                  | 40 |

|   |     | 3.2.4   | Absolute Value of Overclocking Error              | 42 |

|   |     | 3.2.5   | Probability of Overclocking Error                 | 43 |

|   |     | 3.2.6   | Expectation of Overclocking Error                 | 44 |

|   |     | 3.2.7   | Comparison between Two Design Scenarios           | 45 |

|   | 3.3 | Carry   | Select Adder                                      | 46 |

|   |     | 3.3.1   | Timing Models for Carry Select Adder              | 47 |

|   |     | 3.3.2   | Accuracy Benefits and Area Overhead in CSA        | 49 |

|   | 3.4 | Choosi  | ing the Optimum Adder Structure                   | 51 |

|     | 3.4.1  | Determination of the Optimum Adder Structure for Given Fre- |    |

|-----|--------|-------------------------------------------------------------|----|

|     |        | quency Requirements                                         | 52 |

|     | 3.4.2  | Determination of the Optimum Adder Structure for Given Ac-  |    |

|     |        | curacy Requirements                                         | 54 |

|     | 3.4.3  | Design Guidance                                             | 56 |

| 3.5 | Const  | ant Coefficient Multiplier                                  | 56 |

|     | 3.5.1  | Probabilistic Model of Truncation Error                     | 57 |

|     | 3.5.2  | Absolute Value of Overclocking Error                        | 58 |

|     | 3.5.3  | Probability of Overclocking Error                           | 58 |

|     | 3.5.4  | Expectation of Overclocking Error                           | 59 |

|     | 3.5.5  | CCM with Multiple RCAs and Shifters                         | 60 |

| 3.6 | Case S | Study: FIR Filter                                           | 60 |

|     | 3.6.1  | Experimental Setup and Model Verification                   | 60 |

|     | 3.6.2  | Error Expectation                                           | 62 |

|     | 3.6.3  | Signal-to-Noise Ratio                                       | 63 |

| 3.7 | Test F | Platform on An FPGA                                         | 64 |

|     | 3.7.1  | Experimental Setup                                          | 65 |

|     | 3.7.2  | Benchmark Circuits                                          | 67 |

|     | 3.7.3  | Correcting for Conservative Timing Margin                   | 68 |

|     | 3.7.4  | Computing Model Parameters                                  | 69 |

| 3.8 | Result | s from FPGA Measurements                                    | 70 |

|     | 3.8.1  | Case study: FIR Filter                                      | 70 |

|     | 3.8.2  | Potential Benefits in Datapath Design                       | 73 |

|   |     | 3.8.3   | Area Overhead of Our Approach                             | 75  |

|---|-----|---------|-----------------------------------------------------------|-----|

|   | 3.9 | Concl   | usion and Discussion                                      | 77  |

| 4 | Ove | erclock | ing Datapath with Online Arithmetic                       | 79  |

|   | 4.1 | Introd  | luction                                                   | 79  |

|   | 4.2 | Backg   | round                                                     | 81  |

|   |     | 4.2.1   | Binary Online Addition                                    | 81  |

|   |     | 4.2.2   | Binary Online Multiplication                              | 81  |

|   | 4.3 | Proba   | bilistic Model of Overclocking Error                      | 85  |

|   |     | 4.3.1   | Probability of Timing Violations                          | 86  |

|   |     | 4.3.2   | Magnitude of Overclocking Error                           | 90  |

|   |     | 4.3.3   | Expectation of Overclocking Error                         | 90  |

|   | 4.4 | Case S  | Study: Image Filter                                       | 94  |

|   |     | 4.4.1   | Experimental Setup                                        | 94  |

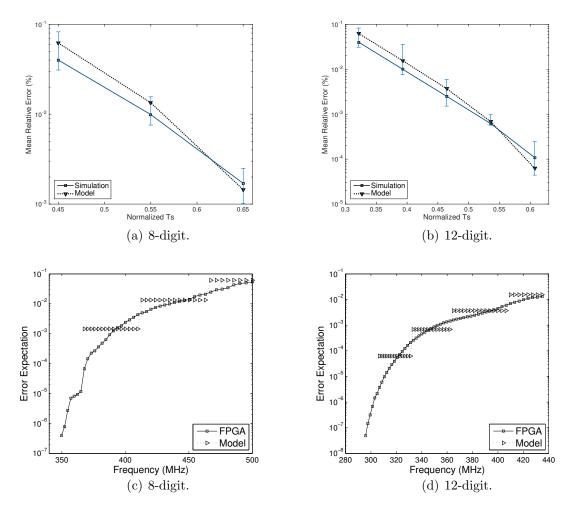

|   |     | 4.4.2   | The Impact of Overclocking                                | 95  |

|   |     | 4.4.3   | Potential Benefits in Circuit Design                      | 97  |

|   |     | 4.4.4   | Area Overhead of The Proposed Approach                    | 99  |

|   | 4.5 | Conclu  | usion                                                     | 100 |

|   | ъœ  | • • •   |                                                           | 101 |

| 5 | Eff | cient F | <b>FPGA Implementation of Online Arithmetic Operators</b> | 101 |

|   | 5.1 | Introd  | luction                                                   | 101 |

|   | 5.2 | Digit   | Parallel Online Adder for FPGAs                           | 104 |

|   |     | 5.2.1   | Related Work                                              | 104 |

|    |       | 5.2.2   | Proposed Mapping Method                           | 106 |

|----|-------|---------|---------------------------------------------------|-----|

|    |       | 5.2.3   | Performance Analysis                              | 108 |

|    | 5.3   | Design  | n Trade-off Evaluation for Different Adders       | 111 |

|    |       | 5.3.1   | Accuracy, Latency and Area Trade-offs for Adders  | 113 |

|    |       | 5.3.2   | Evaluation of Optimum Adder Structure             | 115 |

|    | 5.4   | Digit I | Parallel Online Multiplier for FPGAs              | 121 |

|    |       | 5.4.1   | Digit Parallel Online Multiplication Algorithm    | 121 |

|    |       | 5.4.2   | FPGA Implementation                               | 123 |

|    |       | 5.4.3   | Structure Optimisation for Half Precision Results | 125 |

|    |       | 5.4.4   | Performance Analysis                              | 127 |

|    | 5.5   | Result  | s from FPGA Measurements                          | 131 |

|    |       | 5.5.1   | DSP Benchmark Circuits                            | 131 |

|    |       | 5.5.2   | Taylor Expansion                                  | 136 |

|    | 5.6   | Conclu  | sion                                              | 141 |

| 6  | Con   | clusio  | n                                                 | 142 |

|    | 6.1   | Summ    | ary of Contributions                              | 142 |

|    | 6.2   | Future  | e Work                                            | 145 |

|    | 6.3   | Final l | Remarks                                           | 148 |

| Bi | bliog | raphy   |                                                   | 148 |

# List of Tables

| 2.1 | Two Possible Coding Metric for Signed-Digit Number.                   | 23 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Rated Frequencies of Example Designs                                  | 26 |

| 2.3 | Comparison of different forms of arithmetic in terms of time and area |    |

|     | complexity.                                                           | 28 |

| 3.1 | Ratio of Error Expectation: Traditional Over New                      | 62 |

| 3.2 | Difference of SNR (dB): New Over Traditional                          | 64 |

| 3.3 | Rated Frequencies of Example Designs                                  | 67 |

| 3.4 | Relative Reduction of MRE $(\%)$ in Overclocking Scenario for Various |    |

|     | Normalised Frequencies Based on $(3.40)$ for Two Types of Input Data: |    |

|     | Uniform Data (Uni) and Real Image Data from Lena (Lena)               | 74 |

| 3.5 | Frequency Speedups (%) in Overclocking Scenario Under Various Error   |    |

|     | Budgets for Two Types of Input Data: Uniform Data (Uni) and Real      |    |

|     | Image Data from Lena (Lena)                                           | 75 |

| 3.6 | Area Overhead of Our Approach with respect to Various Frequency       |    |

|     | Requirements                                                          | 76 |

| 3.7 | Area Overhead of Our Approach with respect to Given Error Budgets.    | 76 |

| 4.1  | Relative Reduction of MRE with Online Arithmetic for Various Nor-          |

|------|----------------------------------------------------------------------------|

|      | malised Frequencies                                                        |

| 4.2  | Improvement of SNR (dB) with Online Arithmetic for Various Nor-            |

|      | malised Frequencies, Calculated Using (4.13)                               |

| 4.3  | Relative Improvement in Frequency with Online Arithmetic for Various       |

|      | Error Budgets                                                              |

| 4.4  | Area Comparison between Designs with Two Types of Computer Arith-          |

|      | metic                                                                      |

| 5.1  | Rated Frequencies of Example Designs with Traditional Arithmetic and       |

|      | Online Arithmetic                                                          |

| 5.2  | Relative Reduction of MRE of FIR Filter with Online Arithmetic 133         |

| 5.3  | Relative Reduction of MRE of Sobel Edge Detector with Online Arith-        |

|      | metic                                                                      |

| 5.4  | Relative Reduction of MRE of IIR Filter with Online Arithmetic 133 $$      |

| 5.5  | Relative Reduction of MRE of Butterworth Filter with Online Arithmetic.133 |

| 5.6  | Relative Reduction of MRE of DCT with Online Arithmetic 134                |

| 5.7  | Geometric Mean of Relative Reduction of MRE of All Designs with            |

|      | Online Arithmetic.                                                         |

| 5.8  | Frequency Speed-ups of FIR Filter with Online Arithmetic                   |

| 5.9  | Frequency Speed-ups of Sobel Edge Detector with Online Arithmetic $135$    |

| 5.10 | Frequency Speed-ups of IIR Filter with Online Arithmetic                   |

| 5.11 | Frequency Speed-ups of Butterworth Filter with Online Arithmetic 135 $$    |

| 5.12 | Frequency Speed-ups of DCT with Online Arithmetic                          |

| 5.13 | Geometric Mean of Frequency Speed-ups of All Designs with Online |     |

|------|------------------------------------------------------------------|-----|

|      | Arithmetic.                                                      | 136 |

| 5.14 | Frequency Speed-ups of Design with Full Precision Results        | 138 |

| 5.15 | Frequency Speed-ups of Design with Half Precision Results        | 140 |

# List of Figures

| 2.1 | Better Than Worst-Case Design Concept, from [6]                          | 14 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Structure of Razor Logic from $[7, 35]$ . (a) the Razor flip-flop. It is |    |

|     | utilised to detect timing errors. (b) the pipeline recovery mechanism    | 15 |

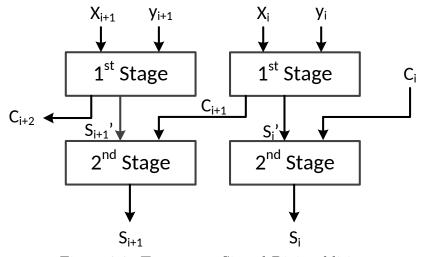

| 2.3 | Two stages Signed-Digit addition.                                        | 24 |

| 2.4 | Dataflow in digit-serial Online Arithmetic.                              | 26 |

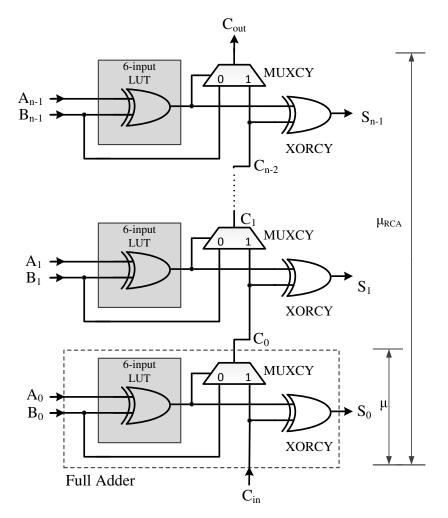

| 3.1 | An <i>n</i> -bit ripple carry adder in Xilinx Virtex-6 FPGA              | 38 |

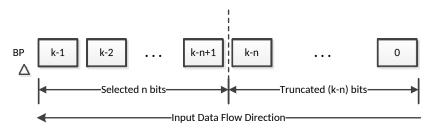

| 3.2 | Generation of Truncation Error                                           | 39 |

| 3.3 | An example of the generation of overclocking error                       | 40 |

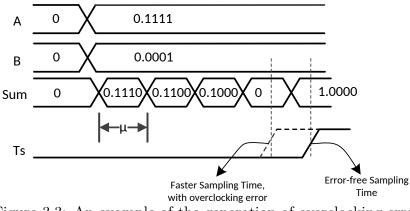

| 3.4 | The structure of CSA.                                                    | 47 |

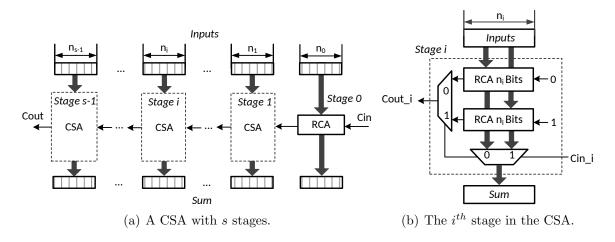

| 3.5 | The modelled value and experimental results of the maximum word-         |    |

|     | length of RCA and CSA with respect to various frequency requirements.    | 50 |

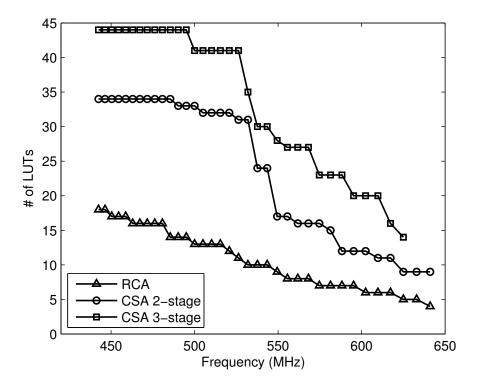

| 3.6 | Usage of LUTs for an RCA and a CSA with two stages and three stages      |    |

|     | with respect to various frequency requirements                           | 51 |

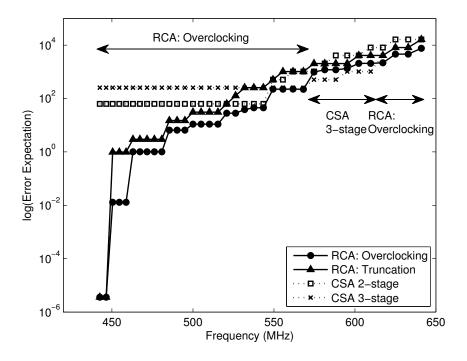

| 3.7 | A comparison between two design scenarios when the number of avail-      |    |

|     | able LUTs is 25. The RCA and CSA are investigated in the conventional    |    |

|     | scenario, while the RCA is explored in the overclocking scenario         | 53 |

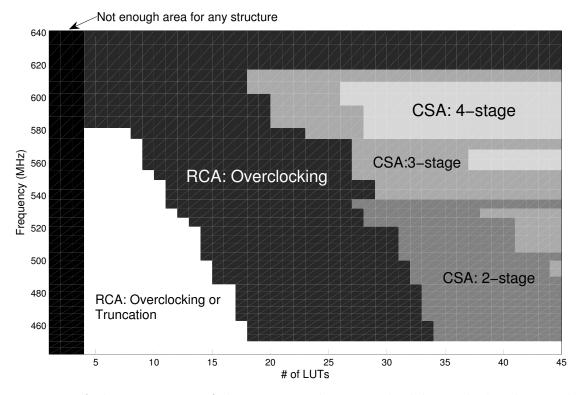

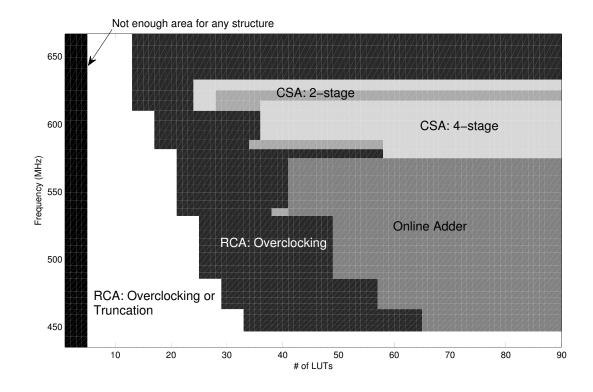

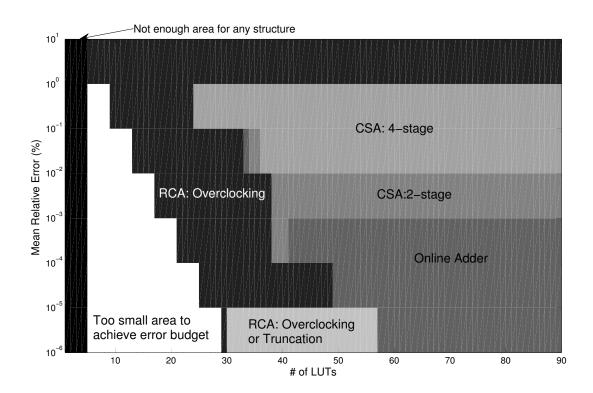

| 3.8  | A demonstration of the optimum design methodology which achieves           |    |

|------|----------------------------------------------------------------------------|----|

|      | the minimum error at outputs with respect to a variety of frequency        |    |

|      | and area constraints.                                                      | 54 |

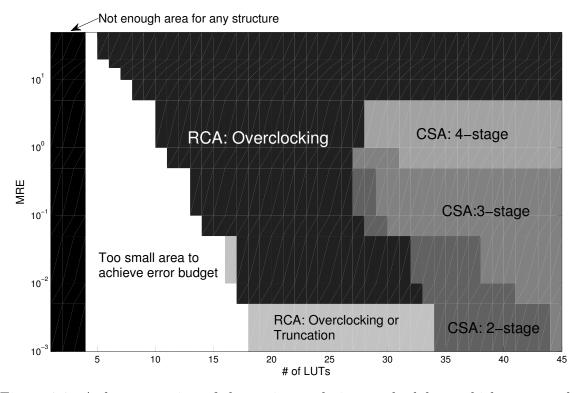

| 3.9  | A demonstration of the optimum design methodology which runs at            |    |

|      | the fastest frequency with respect to a variety of accuracy and area       |    |

|      | constraints.                                                               | 55 |

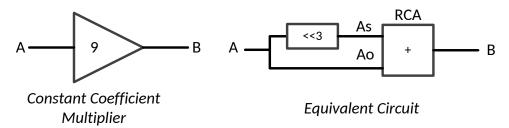

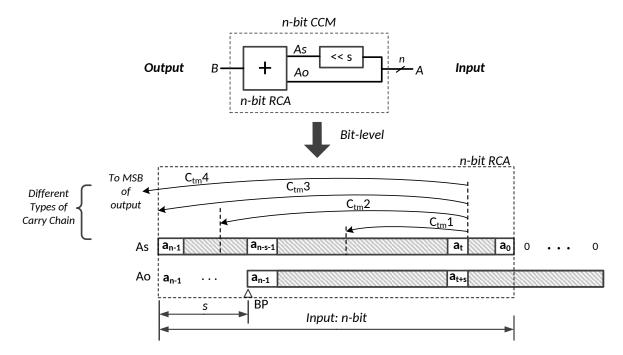

| 3.10 | Constant coefficient multiplier: symbol and equivalent circuit. $\ldots$ . | 56 |

| 3.11 | Four possible carry chain types in a constant coefficient multiplier with  |    |

|      | n-bit inputs. The notion $s$ denotes the shifted bits and $BP$ denotes the |    |

|      | binary point.                                                              | 57 |

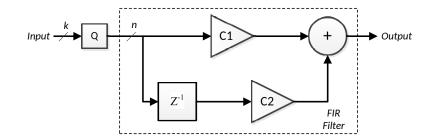

| 3.12 | A simple FIR filter                                                        | 61 |

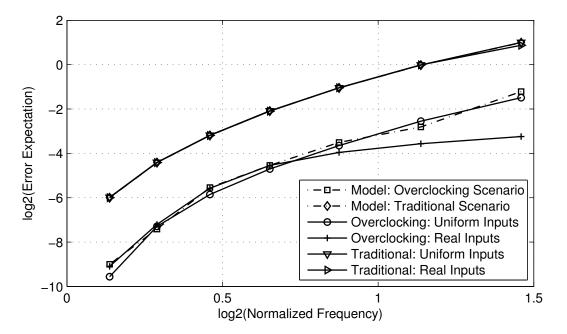

| 3.13 | Verification of proposed models under timing assumptions                   | 62 |

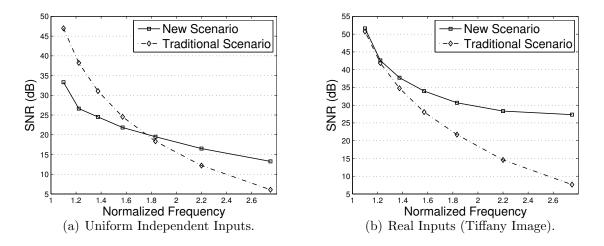

| 3.14 | Comparison between overclocking scenario and traditional scenario in       |    |

|      | terms of SNR                                                               | 64 |

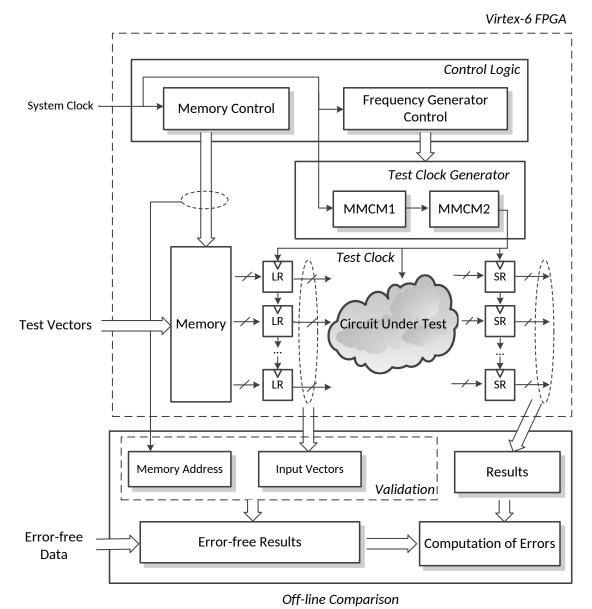

| 3.15 | Test framework, which is composed of a measurement architecture (the       |    |

|      | top dotted box) on an FPGA and an off-line comparator using software.      |    |

|      | The error-free data are obtained by either pre-computation or initial run  |    |

|      | with rated frequencies                                                     | 66 |

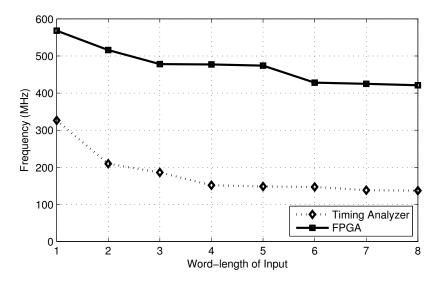

| 3.16 | The maximum operating frequencies for different input word-lengths of      |    |

|      | an FIR filter. The dotted line depicts the rated frequency reported by     |    |

|      | the timing analysis tool from Xilinx ISE 14.1. The solid line is obtained  |    |

|      | through FPGA tests using our platform.                                     | 69 |

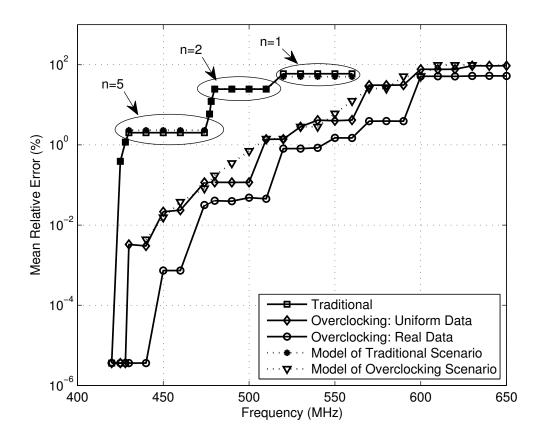

| 3.17       | A demonstration of two design perspectives with a $5^{th}$ order FIR filter,                                        |          |

|------------|---------------------------------------------------------------------------------------------------------------------|----------|

|            | which is implemented on Virtex-6 FPGA. The modelled values of both                                                  |          |

|            | overclocking errors and truncation errors are presented as dotted lines.                                            |          |

|            | The actual FPGA measurements are depicted using solid lines. Two                                                    |          |

|            | types of inputs are employed in the overclocking scenario: the uniformly                                            |          |

|            | distributed data and the real image data from Lena                                                                  | 71       |

| 3.18       | Output images of the FIR filter for both overclocking scenario (top row)                                            |          |

|            | and traditional scenario (bottom row) when operating frequencies are                                                |          |

|            | $425\mathrm{MHz},450\mathrm{MHz},480\mathrm{MHz}$ and $520\mathrm{MHz},\mathrm{respectively}$ (from left to right). | 72       |

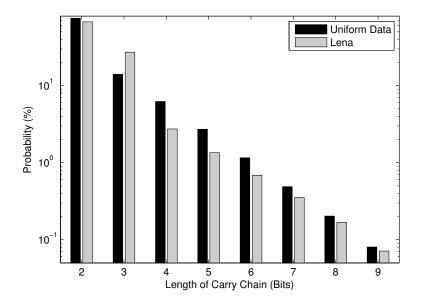

| 3.19       | Probability distribution of different length of carry chains in a 8-bit                                             |          |

|            | RCA. For the uniform data, two inputs of RCA are randomly sampled                                                   |          |

|            | from a uniform distribution. For the image data Lena, one input of                                                  |          |

|            | RCA uses the original data and the other uses the delayed original data                                             |          |

|            | for several clock cycles                                                                                            | 73       |

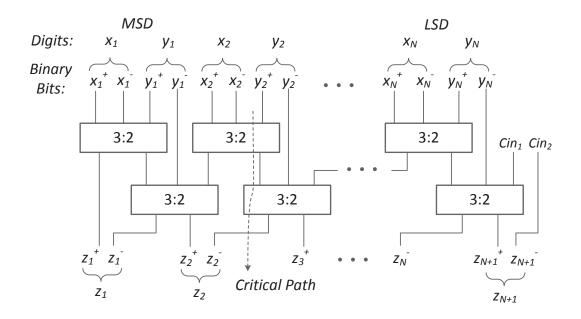

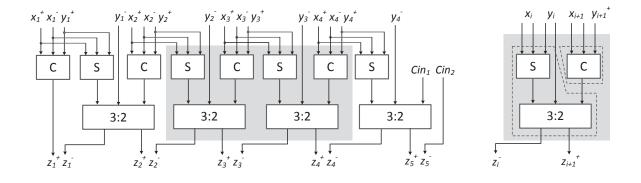

| 4.1        | An $N$ -digit binary digit-parallel online adder. Both inputs and outputs                                           |          |

|            | are represented using SD representation. "3:2" denotes a 3:2 compressor.                                            | 82       |

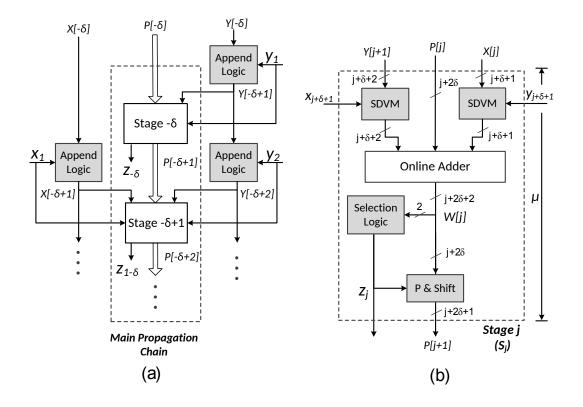

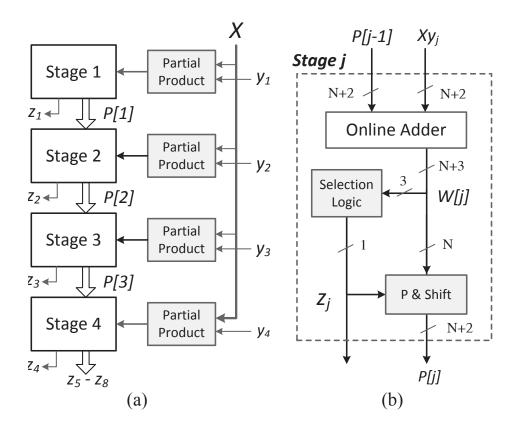

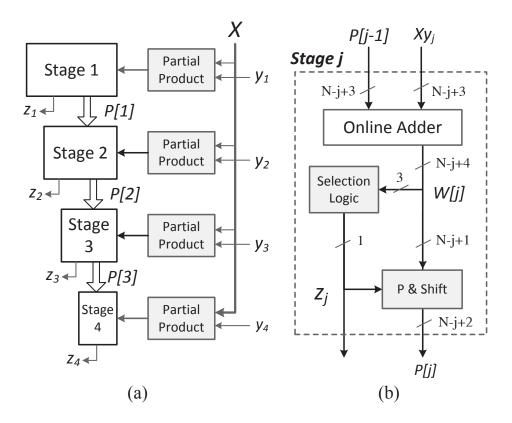

| 4.2        | (a) A digit-parallel implementation of the online multiplication algo-                                              |          |

|            |                                                                                                                     |          |

|            | rithm (b) Structure of one stage of online multiplier, the maximum                                                  |          |

|            | rithm (b) Structure of one stage of online multiplier, the maximum digit widths of signals are labelled.            | 84       |

| 4.3        |                                                                                                                     | 84       |

| 4.3        | digit widths of signals are labelled.                                                                               | 84       |

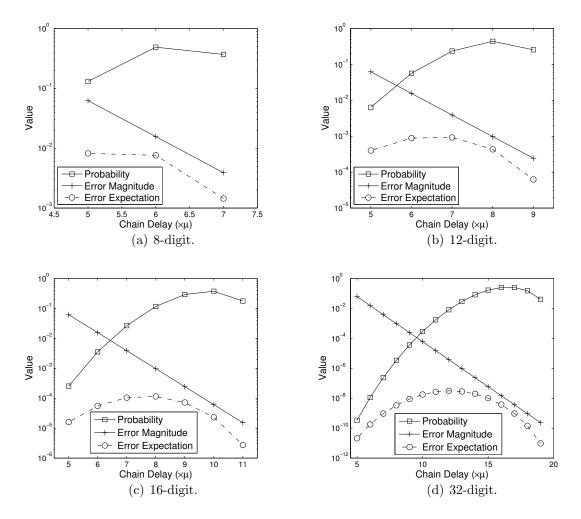

| 4.3        | digit widths of signals are labelled                                                                                | 84<br>92 |

| 4.3<br>4.4 | digit widths of signals are labelled                                                                                |          |

|            | digit widths of signals are labelled                                                                                |          |

|            | digit widths of signals are labelled                                                                                |          |

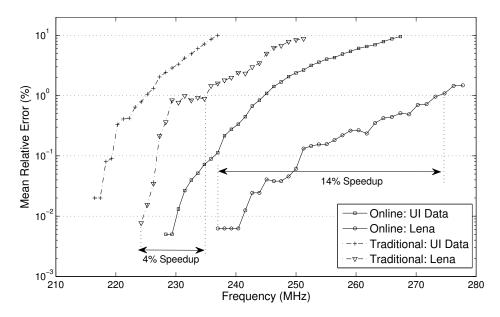

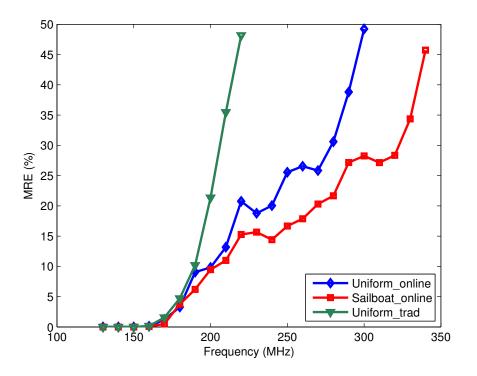

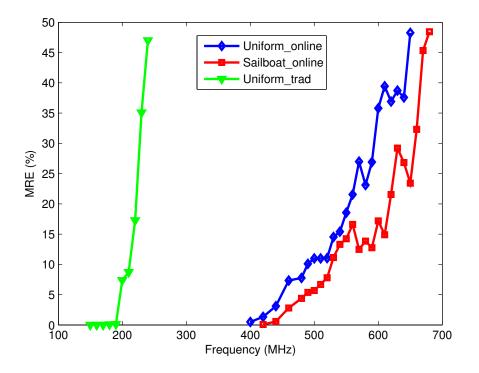

| 4.5 | Overclocking error in an image filter with two types of computer arith-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | metic: online arithmetic and standard binary arithmetic, of which the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | rated frequencies are 148.3MHz and 168.7MHz, respectively, according                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | to the timing analysis tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

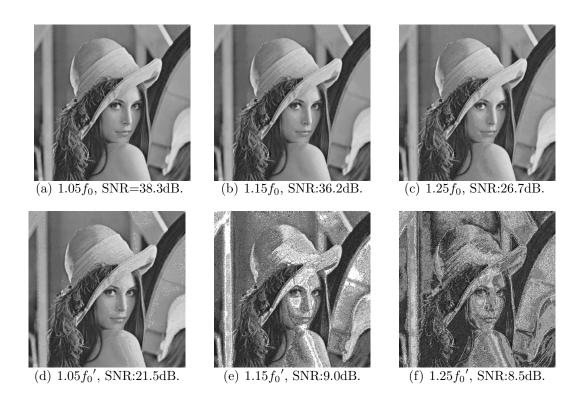

| 4.6 | Output images of image filter using online arithmetic (top row) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | traditional arithmetic (bottom row)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

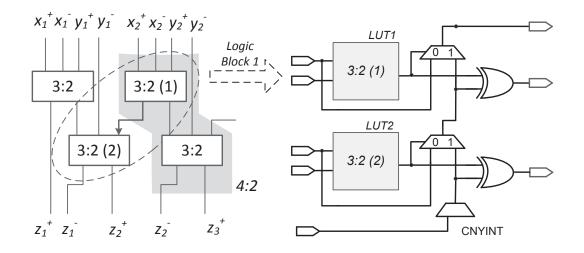

| 5.1 | Map the online adder onto Spartan FPGAs using the fast-carry re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | sources. The grey background highlights the 4:2 compressor. Dotted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | circle indicates the logic block (LB) which can be mapped to the FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | using the carry resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

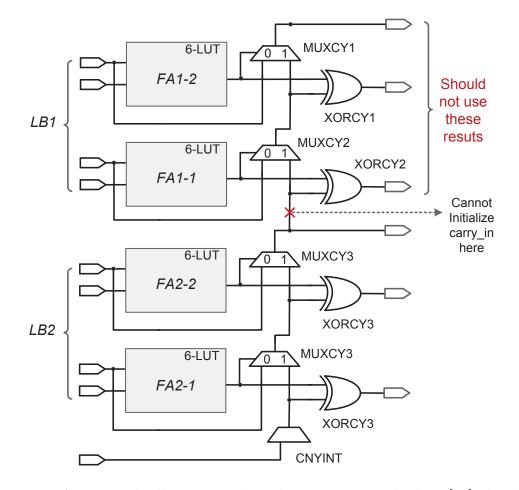

| 5.2 | An example illustrating that the mapping method in [63] should not be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | directly applied on a Virtex-6 FPGA, because the carry input of LB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | cannot be explicitly initialised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3 | cannot be explicitly initialised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.3 | Alternative structure of online adder. Left: 4-digit online adder. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.3 | Alternative structure of online adder. Left: 4-digit online adder. The shaded part refers to the two logic blocks (LBs) that can be mapped                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.3 | Alternative structure of online adder. Left: 4-digit online adder. The shaded part refers to the two logic blocks (LBs) that can be mapped onto one slice. Right: one LB. The dotted boxes outline the logic that can be mapped onto each LUT and the corresponding fast carry logic. 107                                                                                                                                                                                                                                                               |

|     | Alternative structure of online adder. Left: 4-digit online adder. The shaded part refers to the two logic blocks (LBs) that can be mapped onto one slice. Right: one LB. The dotted boxes outline the logic that can be mapped onto each LUT and the corresponding fast carry logic. 107                                                                                                                                                                                                                                                               |

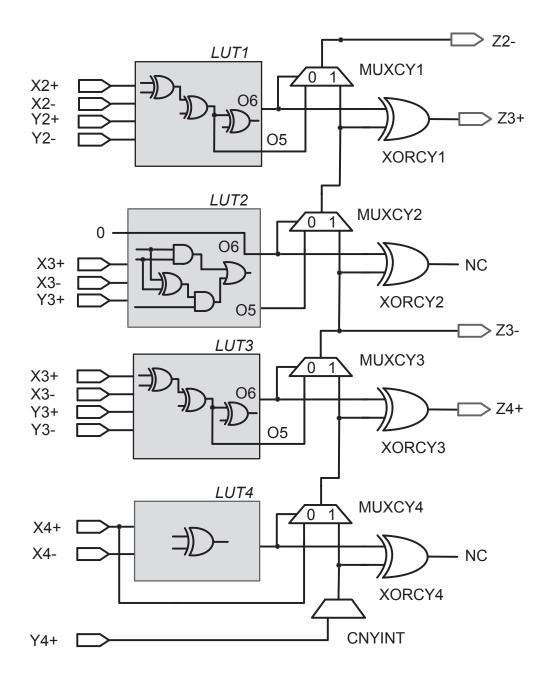

|     | Alternative structure of online adder. Left: 4-digit online adder. The<br>shaded part refers to the two logic blocks (LBs) that can be mapped<br>onto one slice. Right: one LB. The dotted boxes outline the logic that<br>can be mapped onto each LUT and the corresponding fast carry logic. 107<br>Implementation of two logic blocks (LBs) in one FPGA slice which                                                                                                                                                                                  |

| 5.4 | Alternative structure of online adder. Left: 4-digit online adder. The shaded part refers to the two logic blocks (LBs) that can be mapped onto one slice. Right: one LB. The dotted boxes outline the logic that can be mapped onto each LUT and the corresponding fast carry logic. 107 Implementation of two logic blocks (LBs) in one FPGA slice which contains four 6-LUTs. NC stands for "Not Care" 109                                                                                                                                           |

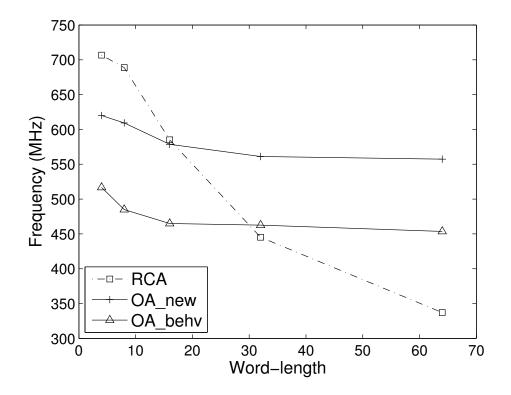

| 5.4 | Alternative structure of online adder. Left: 4-digit online adder. The shaded part refers to the two logic blocks (LBs) that can be mapped onto one slice. Right: one LB. The dotted boxes outline the logic that can be mapped onto each LUT and the corresponding fast carry logic. 107 Implementation of two logic blocks (LBs) in one FPGA slice which contains four 6-LUTs. NC stands for "Not Care" 109 Rated frequencies of RCA and online adder with different implementation.                                                                  |

| 5.4 | Alternative structure of online adder. Left: 4-digit online adder. The shaded part refers to the two logic blocks (LBs) that can be mapped onto one slice. Right: one LB. The dotted boxes outline the logic that can be mapped onto each LUT and the corresponding fast carry logic. 107<br>Implementation of two logic blocks (LBs) in one FPGA slice which contains four 6-LUTs. NC stands for "Not Care" 109<br>Rated frequencies of RCA and online adder with different implementation methods. The results are obtained from post place-and-route |

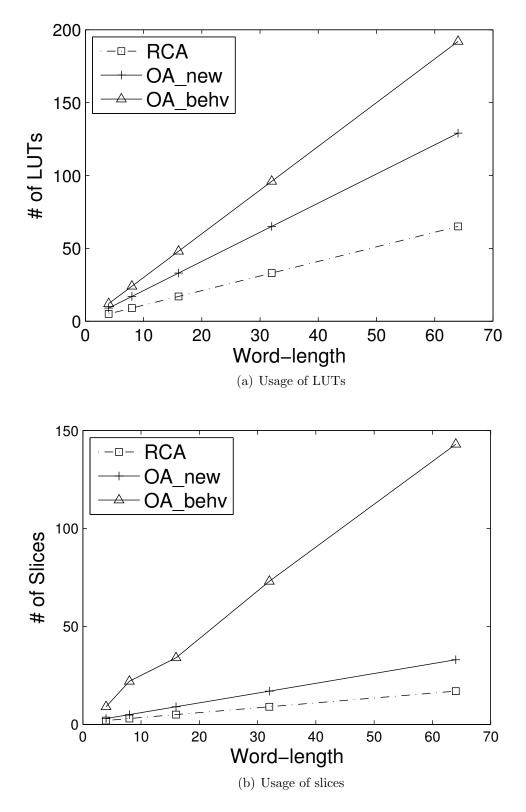

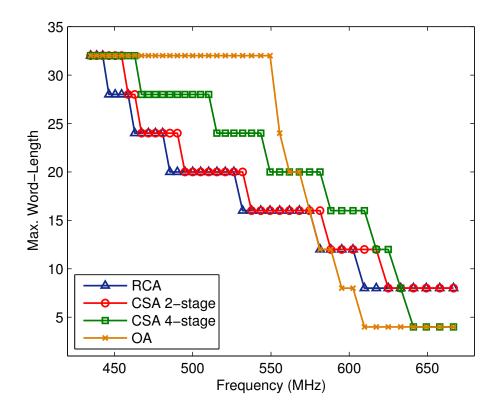

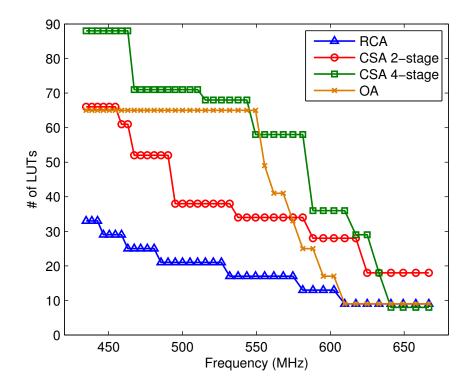

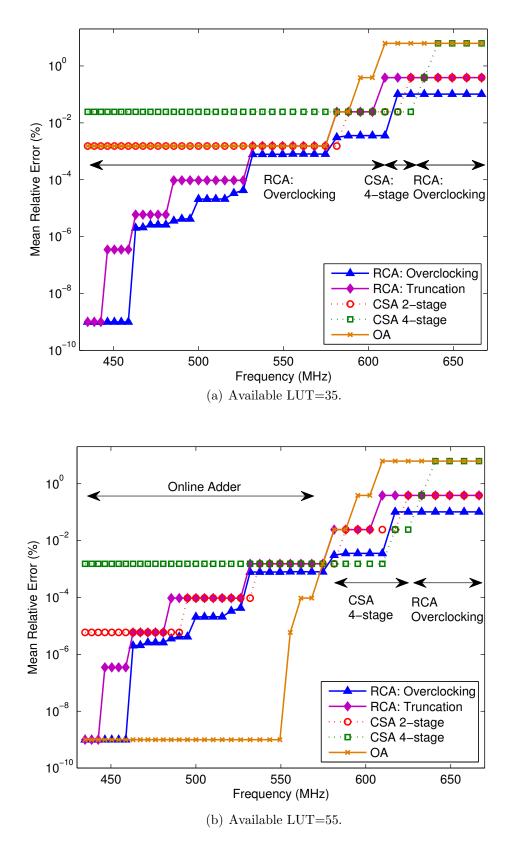

| 5.7  | The maximum word-lengths of different adder structures with respect            |     |

|------|--------------------------------------------------------------------------------|-----|

|      | to a variety of frequency requirements                                         | 13  |

| 5.8  | Area consumption with respect to a variety of frequencies of different         |     |

|      | adder structures                                                               | 114 |

| 5.9  | Two examples of comparisons between different design scenarios and             |     |

|      | adder implementations with limited area budget. Design scenario with           |     |

|      | minimum error is labelled                                                      | 117 |

| 5.10 | Mapping of the optimum design metric of adders, which achieves mini-           |     |

|      | mum error with respect to a variety of frequency and area constraints 1        | 118 |

| 5.11 | Mapping of optimum design metric of adders, which achieves highest             |     |

|      | frequency with respect to a variety of accuracy and area constraints $1$       | 120 |

| 5.12 | (a) Structure of a 4-digit online multiplier using the proposed algorithm.     |     |

|      | (b) Structure of Stage $j$ . The word-length of all signals are labelled in    |     |

|      | terms of the number of digits. ${\cal N}$ denotes the word-length of the input |     |

|      | signals                                                                        | 124 |

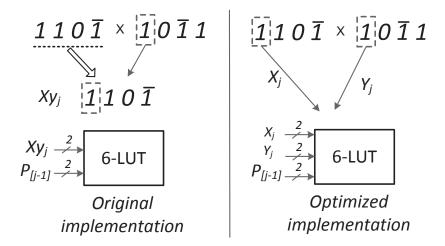

| 5.13 | Left: Direct implementation with extra logic to generate partial prod-         |     |

|      | ucts. Right: Combining the logic blocks that generate partial products         |     |

|      | into the Online Adder by fully utilizing all the inputs of the 6-LUTs 1        | 125 |

| 5.14 | (a) Modified structure of a 4-digit online multiplier which only generates     |     |

|      | the most significant 4-digit result. (b) Structure of Stage $j$ , with the     |     |

|      | word-lengths of all internal signals labelled                                  | 126 |

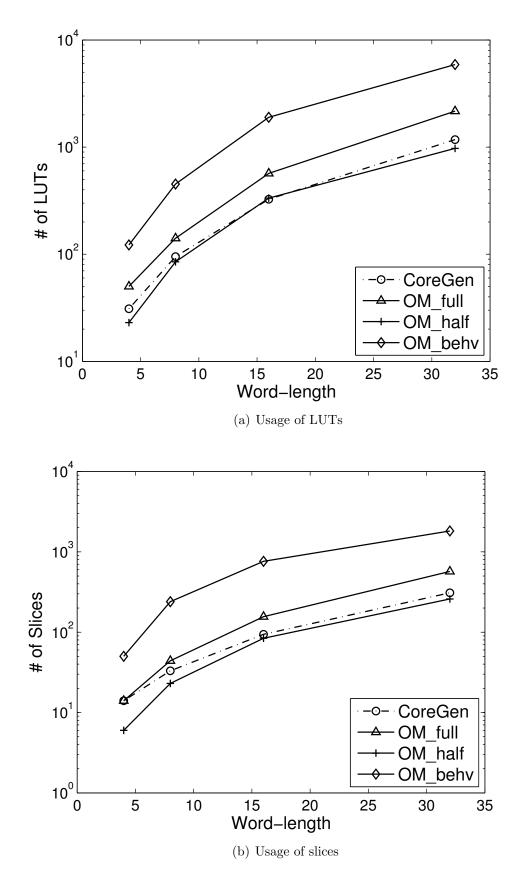

| 5.15 | Area comparisons of different types of binary multipliers                      | 128 |

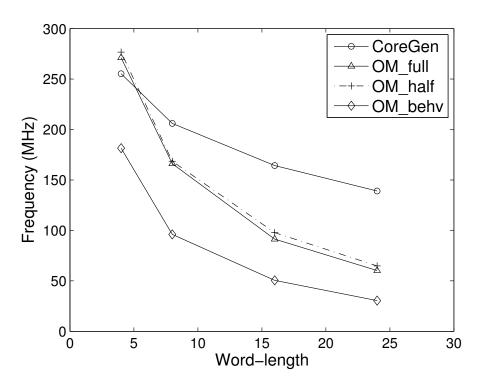

| 5.16 | Rated frequencies of different types of binary multipliers for a variety       |     |

|      | of operand word-lengths                                                        | 129 |

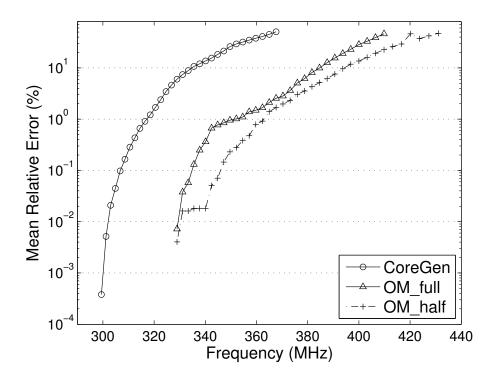

| 5.17 | Mean   | relative  | errors  | s seen | at   | the   | outputs   | of   | different | types   | of | bin | ary |     |

|------|--------|-----------|---------|--------|------|-------|-----------|------|-----------|---------|----|-----|-----|-----|

|      | multip | pliers, w | hen clo | ocked  | witł | n fas | ster-than | -rat | ed freque | encies. |    |     |     | 130 |

| 5.18 | Mean relative errors of Taylor expansion of $log(x)$ implemented with  |     |

|------|------------------------------------------------------------------------|-----|

|      | conventional arithmetic and online arithmetic with full precision out- |     |

|      | puts under overclocking.                                               | 138 |

5.19 Mean relative errors of design implemented with conventional arithmetic and online arithmetic with half precision outputs under overclocking. . 140

# Chapter 1

# Introduction

Circuit performance has increased tremendously over the past decades with the continuous scaling of Complementary Metal-Oxide-Semiconductor (CMOS) technology, such that circuits can occupy less silicon area and operate faster. However, the drastic variations introduced by higher integration densities are anticipated to be the major obstacle when designing reliable, high performance circuits. Typically hardware designers tend to employ conservative safety margins for timing closure and to ensure a uniform functionality of the design across various possible working environments. Nevertheless, continuing with this approach could become very costly in the short term future. As circuit dimensions scale down, it is increasingly difficult to maintain low relative manufacturing variation, meaning that we can no longer expect a uniform circuit performance. Because timing margins in static timing analysis tools increase with process variability, designing for worst-case delay in circuits will become increasingly difficult, expensive, and will result in large yield loss as relative process variation rises.

Hardware accelerator based on Field-Programmable Gate Arrays (FPGAs) serves as an ideal candidate to sustain performance scaling [123]. A large volume of current

studies has demonstrated that significant performance gains can be achieved by using FPGAs over software designs across a wide range of applications [39, 121, 126]. However, one of the major factors that limits the performance of these accelerators is that they typically run at much lower clock frequencies than their counterparts such as General Purpose Processors (GPPs) or Graphics Processing Units (GPUs).

In order to boost the operating frequency of a datapath in an FPGA, the standard approaches are either to heavily pipeline the design or reduce the precision throughout the datapath. For the former method, it should be noted that pipelining will not tend to reduce the circuit latency. Actually the latency in terms of clock cycles will increase. As a result, this method will not be applicable to many embedded applications, which typically have strict latency requirements, or in any datapath containing feedback where C-slow retiming [131] is inappropriate. For the second approach, although at the cost of introducing quantisation errors, tuning the precision of datapath to meet desired accuracy criteria can help to meet the performance demands. Due to the freedom of FPGAs to employ customised variable representations, study into exploiting the potential benefits of using the minimum precision necessary to satisfy a design specification, such as the maximum tolerable error, has been an extensive research topic within the FPGA community [25, 75].

Unfortunately, neither of these conventional approaches tends to remove the conservative timing margin. Over the past few years we have seen a growth of research in the field of "approximate computing". In contrast to the conventional design approach that ensures deterministic circuit performance, approximate computing explores the potential power or performance benefits that can be obtained when designing and/or operating circuits beyond the deterministic region. This topic is expected to be of growing importance in the short term future due to various reasons such as the increasingly stringent timing and power requirements, design complexity and the environmental and process variations, which are all accompanied by the continuous scaling of process technologies [23]. As pointed out by the International Technology Roadmap for Semiconductors (ITRS07) [107], while future technologies may suffer from much poorer timing performance, extra benefits of manufacturing, test and power consumption can be obtained if the tight requirement of absolute correctness is released for devices and interconnect. Current research in this area has typically focused on relaxing the design constraints and the safety margins that are conventionally used.

In this thesis, we demonstrate an alternative approximate computing methodology when considering trade-offs among multiple design specifications, such as accuracy, performance, area and different types of computer arithmetic. Since it is unlikely to create a completely error-free design as any fixed or floating point representations would introduce quantisation errors, we take a radical shift by suggesting that for certain applications it is beneficial to move away from the traditional model of creating a conservative design that is guaranteed to avoid timing violations. Instead, it may be preferable to create a design in which timing violations may only occur rarely. In order to back up this hypothesis, the answers of three main research questions have to be addressed:

- 1. How can we quantify the occurrence and impact of timing errors on a datapath?

- 2. Is it possible to minimise the impact of timing errors by carefully selecting the appropriate computer arithmetic and data representations?

- 3. How can we efficiently implement the selected "overclocking friendly" computer arithmetic on existing hardware platforms such as modern FPGAs?

In this thesis, we attempt to provide answers to all of these questions.

### 1.1 Thesis Organization

Chapter 2 highlights the theoretical background and reviews the relevant work to this thesis. It initially provides the background of existing techniques for numerical precision optimisation within hardware. It then introduces the reader to the subject of approximate computing. The state-of-the-art approaches and techniques are reviewed in-depth, together with their limitations in comparison to our proposed approach. Finally we discuss the background of an alternative form of computer arithmetic known as "online arithmetic", which potentially embodies the overclocking friendly feature.

In Chapter 3, we introduce our proposed overclocking approach for approximate datapath design. We evaluate the probabilistic behaviour of basic arithmetic primitives with different datapath precisions, when operating beyond the deterministic clocking region. We demonstrate that for certain applications it is beneficial to move away from the conservative design approach of ensuring timing closure. Alternatively, it may be preferable to allow timing violations to happen, under the knowledge that they are unlikely to occur frequently, because specific input patterns are required to generate errors. We have created probabilistic models for both design scenarios and we show that not only does the overclocking approach allow us to reduce the need for the conservative timing margin, more importantly, our models and experimental results demonstrate that performance benefits can be achieved in comparison to the traditional situation where target latency is limited by choice of precision.

The limitations of the work in Chapter 3 are addressed in Chapter 4. In standard arithmetic operators such as ripple-carry adders, the most significant digit (MSD) is updated last due to carry propagation, therefore if timing violation happens, it will initially affect the MSD of the results. This potentially results in timing errors of large magnitude. In order to tackle this problem, for the first time we employ an alternative form of MSD-first arithmetic known as "online arithmetic". Similarly to the previous chapter, we develop probabilistic models for basic arithmetic operators such as general purpose multiplier, which is implemented with online arithmetic, when operating beyond the deterministic clocking region. The model is verified with experimental results from an image processing application. We demonstrate that substantial performance benefits can be achieved when compared to the design method using conventional arithmetic as proposed in Chapter 3.

Chapter 5 tackles the major limitation of utilising online arithmetic operators, which is that they normally require a large area overhead for FPGA implementation. In this chapter, we propose novel approaches to implement the key primitives of online arithmetic: adders and multipliers, efficiently on modern FPGA architectures. The proposed new implementation method makes full use of logic resources within an FPGA, such as its 6-input look-up-tables (LUTs) and dedicated carry resources. We demonstrate experimentally that in comparison to a direct Register-Transfer Level (RTL) synthesis, large area savings can be achieved using the proposed architectures. In addition, because an online multiplier generates the MSD first, we develop a method to create a correctly rounded online multiplier with a reduced precision output that is smaller than a traditional multiplier producing the same results.

In the final chapter, Chapter 6, the thesis is summarised and potential avenues for future research are identified.

### **1.2** Statement of Originality

In this thesis, we make three main original contributions, of which the full discussions and the quantitative descriptions are detailed in the introduction section of their own dedicated chapter. Here we summarise and highlight the key information of the three main contributions as below:

- A novel combination of datapath function with overclocking in a holistic framework to trade off between accuracy, latency and silicon area, together with the detailed modelling methods of probabilistic errors generated in basic arithmetic primitives from two different design scenarios: overclocking the datapath or truncating precisions that used throughout the datapath. (Chapter 3, [110, 109, 112])

- According to our knowledge, the first proposal and evaluation of online arithmetic as an "overclocking friendly" arithmetic, and the modelling methods of overclocking errors for a digit-parallel multiplier with online arithmetic. (Chapter 4, [113])

- Efficient methods to map digit-parallel adders and multipliers with online arithmetic to modern FPGAs, and a novel method to implement correctly rounded online multipliers for a chosen output precision. (Chapter 5, [111, 114])

### **1.3** Publications

The following papers and articles have been written during the course of this thesis:

- Overclocking Datapath for Latency-Error Tradeoff, Kan Shi, David Boland, and George A. Constantinides, in Proc. IEEE International Symposium on Circuits and Systems (ISCAS), 2013, pp. 2537-2540.

- Accuracy-Performance Tradeoffs on an FPGA Through Overclocking, Kan Shi, David Boland, and George A. Constantinides, in Proc. IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2013, pp. 29-36. Winner of a HiPEAC paper award.

- 3. Imprecise Datapath Design: An Overclocking Approach, Kan Shi, David Boland, and George A. Constantinides, ACM Transactions on Reconfigurable Technology

and Systems (TRETS), vol. 8, no. 2, pp. 1-23, 2013. Invited paper.

- Datapath Synthesis for Overclocking: Online Arithmetic for Latency-Accuracy Trade-offs, Kan Shi, David Boland, Ed Stott, Samuel Bayliss and George A. Constantinides, in Proc. ACM/IEEE Design Automation Conference (DAC), 2014, pp. 1-6. Winner of a HiPEAC paper award.

- Efficient FPGA Implementation of Digit Parallel Online Arithmetic Operators, Kan Shi, David Boland and George A. Contantinides, in Proc. International Conference of Field-Programmable Technology (FPT), 2014, pp. 115-122. Best paper nominee.

- Evaluation of Design Trade-offs of Adders in Approximate Datapath, Kan Shi and George A. Constantinides, in HiPEAC Workshop on Approximate Computing (WAPCO), 2015.

## Chapter 2

# Background

### 2.1 Introduction

The main focus of this thesis is exploring the trade-off between accuracy and performance when designing a datapath. In this chapter, we discuss relevant work and background theory to help place our work in context. In general, we restrict our discussions to three main research areas as highlighted below.

We initially discuss the work in the area of word-length optimisation in Section 2.2, because reducing the datapath precision will reduce the circuit latency at the cost of introducing quantisation errors into the design. As FPGAs are capable of employing customised variable representations, there has been extensive research into exploiting the potential benefits of using the minimum precision necessary to satisfy a design specification, such as the maximum tolerable error, within the FPGA community. We will use this methodology as the major comparison to our approach throughout this thesis.

It is worth noting that the choice of precision is not the only source of error when designing a datapath. For the past few years we have seen a growth of parallel streams of research which aim at exploring alternative methods to trade accuracy for design efficiency. This strand of research is known as "approximate computing", and it is motivated by the fact that extra benefits of manufacturing, test, power and timing can be obtained if the tight requirement of absolute correctness is released for devices and interconnects, as indicated by the ITRS in 2007 [107]. This topic is expected to be of growing importance in the future, because we will face new design challenges as the technology scales further. Research in this area will be discussed in Section 2.3.

However, applying approximate computing techniques with conventional computer arithmetic may potentially result in large errors as indicated by previous research [140] and will be highlighted in our study in Chapter 3. This is largely due to carry propagation in conventional arithmetic, in which carry is propagated from the least significant end to the most significant end. In this thesis, we attempt to tackle this issue by using an alternative form of computer arithmetic named "online arithmetic", which performs all types of computations in a most-significant-digit-first manner. In Section 2.4, we provide a broad overview of online arithmetic. This section lays the foundation of our discussions on utilising online arithmetic in approximate computing and implementing online arithmetic efficiently on modern FPGAs in Chapter 4 and Chapter 5 respectively.

### 2.2 Word-Length Optimisation

In comparison to implementations based on general purpose processors, the reconfigurable nature of FPGA enables the employment of customised numerical variable representations. The target of optimising the word-length is to represent variables within a design using minimum precision, while meeting the required accuracy and performance constraints [25]. Normally, a word-length optimisation algorithm is designed to provide the trade-offs between computation accuracy and performance. On one hand, more resources and higher cost of data transfer are required for more accurate implementation of a design. On the other hand, the hardware budget is limited due to the consideration of power and performance.

Existing approaches for word-length optimisation can be classified into two main categories: simulation-based and analytical-based. The former approach decides the optimal word-length by comparing simulation outcomes from both the chosen word-length and a very high precision representation, and thereafter checking whether the comparison result meets the error requirement. This straightforward approach is widely employed in industry, since the whole implementation can be treated as a black box, and a very compact data representation can be obtained. However, the major drawback of this approach is that the quality of output highly depends on the selection of input vectors. For large designs, performing exhaustive simulations is infeasible because of the long simulation time, and therefore corner cases may be missed [75].

As for the analytical-based approach, its basic idea is to model the accuracy of computation results in terms of the chosen word-length. In comparison to its counterpart, the analytical-based approach usually provides more conservative determination of word-length and it is better suited for large designs [22]. Existing work employs multiple kinds of modelling methods, including: interval arithmetic (IA) [2, 86], affine arithmetic (AA) [115] and Satisfiability-Modulo Theory (SMT) [68, 69]. The remaining parts of this section briefly review these three approaches.

In interval arithmetic, each variable is bounded with an interval, and the bounds of final computation results can be determined. This approach is straightforward but may generate an extremely loose bound due to the data-dependency problem [75]. That is, the bound will be significantly overestimated when employing the same variable repeatedly [11].

Affine arithmetic is employed to mitigate the data dependency problem. Instead of

representing variables through intervals, AA uses affine expressions which keep track of the correlations of intervals. AA is often employed in digital signal processing (DSP) area, especially for analysis of linear time-invariant (LTI) systems [25], because AA will generate tight bounds for fully affine operations. However, AA still produces loose bounds when there are non-affine calculations.

In the SMT-based approach [68, 69], initial variable ranges are firstly determined through existing analytical methods, *i.e.* AA. Then the initial results are refined using SMT with additional constraints. More specifically, the range refinement procedure of a single variable works similarly as the binary search method, which starts with the initial constraints and update the bounds according to the satisfiability of constraints. For instance, in order to find the upper bound of variable z within a certain expression z = f(x, y), an initial constraint z > 20 is applied to check whether there is a satisfiable assignment. If not then 20 can be treated as a refined upper bound and 10 can be applied to repeat the process. Otherwise increase 20 to 40 and check the satisfiability again. In comparison to IA or AA, the SMT-based approach will generate more compact bounds while retaining robustness. However the major weakness of this approach is that the growing of instance set can result in very long operating time.

### 2.3 Approximate Computing

With the progressive shrinking of fabrication technology into the nanometre range, new design challenges such as design complexity and device uncertainty have arisen in order to sustain performance scaling.

Design complexity becomes a critical challenge due to rapid technology shrinking. Since the introduction of Moore's Law in 1965, the speed of transistor has scaled by nearly fiver orders of magnitude [92]. Meanwhile, the transistor density keeps doubling and power consumption is about 50% lower in every technology generation. In this context, circuit designers are able to create complex architectures by exploiting the increasing transistor integration. On the other hand, the ever rising design complexity has become the driving force of significant research efforts to sustain performance scaling. For instance, we have seen the employment of different levels of parallelism in microprocessor architectures, as well as the shifting from single-core to multi-core architecture, and the rise of heterogeneous parallelism [54].

However, as predicted by the ITRS, the size of individual transistors is reaching physical limits with the transistor gate length near 10nm [108]. As a consequence, the operating frequency is expected to increase slowly in the near future. Besides, device scaling is also curtailed by practical power limits, which is also known as "dark silicon". It is predicted that at 8nm more than 50% of fixed-size chip must be powered off [36]. Therefore, alternative approaches for circuit design and operating must be investigated to release the burden of design complexity.

Another design challenge is the uncertainty accompanied by technology scaling. For example, in 22nm technology the oxide and gate length are only five and 42 atomic layers thick, respectively [45]. With critical device dimensions scaling to atomic range, manufacturing identical devices and maintaining uniform and non-deterministic circuit behaviour become increasingly difficult and expensive. According to Pelgrom's Law [98], the mismatches between device behaviour are inversely proportional to the transistor size. This means the impact of environmental and process variations on performance and reliability of integrated circuits is greatly amplified by technology shrinking.

While a uniform behaviour should no longer be expected with current devices and chip components, the conventional approaches of designing and operating digital circuits remain unchanged. A typical solution to these design challenges is to introduce guard bands, which are designed for worst cases to ensure a uniform circuit behaviour across various operating environments and process variations. This approach is commonly used throughout all types of engineering. It is clearly conservative, and consequently results in significant overhead of both performance and energy. Continuing with this approach and designing for worst-case delay in circuits become increasingly expensive as relative process variation rises.

For the past few years, a novel design strategy known as "approximate computing" has been proposed to tackle the aforementioned design challenges. Research in this area suggests that relaxing the absolute accuracy requirements can provide the freedom to create circuits with better performance and/or energy efficiency. Specifically in this section we review two main research directions in the field of approximate computing. In Section 2.3.1 we discuss one design paradigm called "Better Than Worst-Case (BTWC) Design" [6, 23]. While a typical BTWC design usually contains a checker circuit to ensure the correctness of outputs, another stream of research focuses on providing "good enough" results without adding correction mechanism. This approach can lead to even better performance benefits, at the cost of accuracy loss. In addition, there is also research investigating the methods to provide "imprecise architectures" by designing simplified circuits for approximate computing. Research progress in this area is reviewed in Section 2.3.2.

#### 2.3.1 Better Than Worst-Case Design

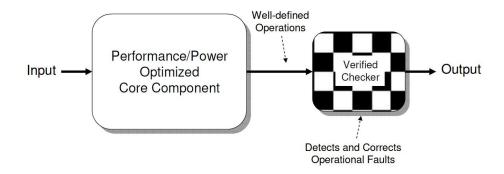

As suggested from the name, the BTWC design allows the circuits to operate beyond the worst cases by either partially or completely removing the conservative guard bands. In this case, either a higher operating frequency can be achieved for better performance, or the supply voltage can be reduced for better power efficiency. A typical BTWC design is composed of cores and checkers, as shown in Figure 2.1 [6].

Figure 2.1: Better Than Worst-Case Design Concept, from [6].

This structure enables the checker to address the design correctness and robustness issues independently, whereas the accuracy requirements of the cores are relaxed such that they can be operated with higher performance. Optionally the system can be recovered at the observation of errors.

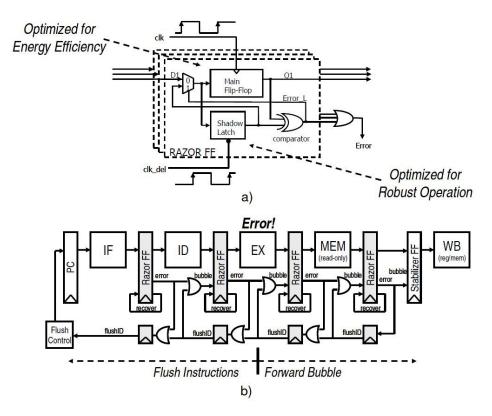

As an exemplary design, the Razor project [7, 35] was proposed to shave the conservative timing margins by dynamically scaling the supply voltage and clock frequency beyond the worst-case levels, while monitoring the output error rates by utilising a self-checking circuit. The Razor flip-flop and the pipeline recovery mechanism are illustrated in Figure 2.2. Each Razor flip-flop contains a shadow latch which is triggered by a delayed clock, and it is constrained such that the shadow latch will always provide reliable results. Once the setup time for the main flip-flop is violated due to excessive voltage or frequency scaling, a different result will be sampled by the main flip-flop in comparison to the shadow latch, and an error signal will be generated from the comparator. Razor utilised a pipeline recovery mechanism, as shown in Figure 2.2b, in order to avoid the timing error from corrupting the register and memory state. On occurrence of timing errors, the recovery mechanism will generate forward a bubble and backward flush signal to recover the pipeline from timing failure. This work demonstrated that the benefits brought by removing the safe margin outweigh the cost of monitoring and recovering from errors. For example, 22%, over 30% and up to 64%

Figure 2.2: Structure of Razor Logic from [7, 35]. (a) the Razor flip-flop. It is utilised to detect timing errors. (b) the pipeline recovery mechanism.

power consumption can be saved with around 0.01%, 1% and 3% error rates at the output, respectively.

Besides the Razor project, related work of BTWC design also includes a similar frequency overscaling technique by operating circuits slightly slower than the critical path delay with dedicated checker circuits to ensure that timing errors will not occur [125] and a processor architecture that decouples the issues of design performance from those of correctness and program verification [5, 16, 130]. In addition, there is work focusing on providing Computer-Aided Design (CAD) solutions, such as synthesis and verification, for BTWC designs. For instance, there is work proposing timing analysis tools that decide the optimum operating frequencies in the non-deterministic region due to process variation [66], and developing synthesis and mapping technologies for BTWC design targeting FPGAs [24, 84].

#### 2.3.2 Unreliable Computing with Unreliable Components

#### Inherent Application Resilience

Although significant performance and power benefits can be achieved from BTWC design, its major problem is the extra cost, such as silicon area, additional clock cycles and power consumption, introduced by implementing the checker circuits for error detection and recovery. Instead, studies have shown that for a large volume of existing and emerging applications, errors can be potentially tolerated [20]. This feature is also referred to as "inherent application resilience". For these applications, acceptable results can still be generated despite the existence of portions of the application that are computed incorrectly or approximately.

In general, inherent application resilience originates from three main sources, as listed below:

- 1. Redundant and noisy input data. Applications processing real-world data are designed to be robust to noise. For instance in medical applications such as electroencephalogram (EEG) and visual evoked potential (VEP) that detect and process biomedical signals, data sampled from sensors are inevitably contaminated by environmental noise, which will in turn become an important factor that determines the quality of successive computations and final results. In order to achieve noise robustness, data redundancy is normally utilised. On the other hand, the redundancy and noise of input data could potentially form resilience to approximations, as it is not necessary to perform fully accurate computations with noisy data in the first place at the cost of expensive computational efforts.

- 2. Algorithmic resilience. Probabilistic algorithms typically take stochastic inputs and generate outputs with non-deterministic behaviour in terms of correctness and time of operation. Normally a range of outputs can be generated but are

treated equally acceptable. This type of algorithm uses randomness to achieve more efficient computations in comparison to their deterministic competitors. For example, several probabilistic algorithms, such as *K*-means clustering, iteratively converge to the final solution by sequentially producing approximate answers. In addition, algorithms such as quicksort and simulated annealing embody randomness within the algorithm. The intrinsic algorithmic resilience can remove the necessity for accurate computation to a large extent.

3. Perceptual resilience. If the end user of an application is human, it may embody inherent application resilience because of the limited sensitivities of human perceptions. In this case, minor fluctuations of outputs can hardly be recognised and/or distinguished by human senses. For example, human hearing can only perceive sounds with frequency range from about 20Hz to 20kHz, and human visual perception systems will unconsciously fill in missing information from images or videos and filter out high frequency patterns. Consequently for applications involving human perception, ensuring 100% computation accuracy can be expensive and unnecessary.

#### **Current Research**

Inspired by the existence of inherent application resilience, a novel design concept "unreliable computing with unreliable components" has been proposed and studied over the past few years [93, 94, 95]. Instead of maintaining absolutely correct and reliable computational results, it is more beneficial in terms of performance and energy to only provide "good enough" results that meet given design specifications. This design strategy is particularly interesting and beneficial to applications with inherent error resilience, such as multimedia [4, 106], digital signal processing (DSP) [77, 1], machine learning [14, 21, 19] and so on. In comparison to BTWC design, another advantage of this design approach is that the checker circuit can be eliminated to reduce extra costs.

Current research in this area mainly focuses on designing probabilistic or imprecise circuits at different levels of the Very-Large-Scale Integration (VLSI) design flow, such as software and algorithm level [60, 78, 100], architecture and circuit level [59] and even transistor level [17, 18, 96]. For instance at the programming language level, a tool was proposed [37, 105] to divide variables and objects in a program into precise parts and approximate parts, which can be mapped to different hardware with different speed-grades, supply voltages, etc., respectively. For instance, approximate data can be processed less reliably, whereas the error sensitive part of the program should be operated with guarantees of correctness. This technique enabled a relatively high service quality, in the meantime energy reduction can be obtained due to approximation. It demonstrated up to 50% of energy saving can be achieved. Another study [139] proposed a design framework that allowed circuit designers to explicitly define the approximate portion of the entire system at Hardware Description Language (HDL) level. The design abstractions were presented as extensions to Verilog HDL through high-level annotations. This framework enabled design and reuse of approximate hardware building blocks.

Similar ideas have also been applied on hardware directly. As an example, a nonuniform voltage scaling technique is proposed for the ripple carry adder [65]. In this study, multiple voltage regions are employed for different bits along a carry chain. That is, higher voltage would be applied for computations generating most significant bits, and vice versa. There is also research developing probabilistic CMOS transistors which modelled the relationship between energy consumption and the probability of correct transistor switching [18].

Another main stream of research focuses on designing approximate logic and impre-

cise arithmetic circuits by mainly simplifying original structure to trade for performance and energy efficiency. For instance, Lu *et al.* proposed a "shrinking" datapath that can be utilised to mimic and speculate the original logic functions [80]. Kulkarni *et al.* described an under-designed  $2 \times 2$  multiplier unit, of which the worst case was replaced by a normal case based on the straightforward Karnaugh-Map analysis [71]. In both cases, reduction of area and power consumption can be achieved with the cost of accuracy.

In addition, a large volume of current work is targeting approximate adder design. For example, Gupta *et al.* developed approximate adders at the transistor level and compared the energy efficiency of their proposed architectures over truncation of input word-length of conventional structures [46]. Based on the observation that the accuracy demands for different applications might vary, Kahng *et al.* proposed an adder architecture which offered the flexibility to trade accuracy for energy benefits by optionally utilising part of the adder or enabling additional circuitry to correct for errors for high accuracy requirements [61]. Ye *et al.* derived the relationship between achievable quality and computational effort for a reconfigurable adder, which can be tuned based on the quality-effort curve to achieve better trade-offs [140].

## 2.3.3 Summary

In this section, we initially discussed the background for the generation of approximate computing. We then reviewed two main research directions in the area of approximate computing: better than worst-case design and unreliable computing with unreliable components. For the BTWC design, we discussed the general architecture that combined cores and checkers, based on an exemplary design: Razor logic. For the second approach of approximate computing, we introduced the inherent application resilience that can be utilised to trade absolute accuracy for performance and power benefits, followed by a review of existing work in this area.

From the current literature, we notice several issues when using the methodology of approximate computing. For example in work conducted by Kedem *et al.* [65] as introduced before, utilising several voltage regions within a ripple carry adder will rarely be practical in real situations. Furthermore, the overhead of applying this technique is not addressed. For research targeting the creation of imprecise architectures, it should be noted that using this type of approach means correct results would never be obtained for certain input patterns. Another limitation is that the link between the probability of output correctness and energy savings or performance improvements for designs beyond operator level are rarely analysed in current research. In addition, these techniques normally target Application-Specific Integrated Circuit (ASIC) implementations and cannot be directly applied onto existing hardware platforms such as FPGAs.

In this thesis, we aim to address these issues by proposing an alternative methodology for designing approximate datapath with the consideration of overclocking into the error regime, as will be discussed in detail in Chapter 3.

## 2.4 Online Arithmetic

A major obstacle of applying approximate computing techniques with conventional computer arithmetic is that it may potentially result in large error magnitudes. This is because in conventional arithmetic, carry propagates from the least significant end to the most significant end, therefore errors generated by the scaling of either voltage or frequency will initially affect the most significant digits. Normally the existing approach of tackling this problem is to either speculate the carry using additional logic [79, 141] or correct the result after computation with actual carry [62, 140]. In comparison to these existing approaches which still employ conventional arithmetic, we attempt to tackle this issue by adopting a different form of computer arithmetic named online arithmetic. In this section, we review and describe basic concepts of online arithmetic, which was introduced by Ercegovac and Trivedi in 1977 [29, 124]. In general, online arithmetic is designed to perform Most Significant Digit First (MSDF) computation. This requires an implementation of redundancy in the number representation system, as will be detailed in Section 2.4.1. Originally online arithmetic was designed for digit serial operations, of which the benefits are highlighted in Section 2.4.2. Finally, we provide an in-depth discussion of online arithmetic together with existing research in this area in Section 2.4.3.

## 2.4.1 Redundant Number System

#### **Fixed Point Number Representation**

For a standard number system with fixed radix r, a number X can be represented by (2.1) where n and m denote the number of integer digits and fractional digits used for representing X, respectively. The selection of  $x_i$  can be either from a canonical system, in which we have  $x_i \in \{0, 1, \dots, r-1\}$ , or from a noncanonical system, *i.e.*  $x_i \in \{-b, \dots, -1, 0, 1, \dots, a\}$  where  $a + b + 1 \ge r$ .

$$X = \sum_{i=-m}^{n-1} x_i r^i \tag{2.1}$$