A SYSTEM FOR THE SIMULATION OF HARDWARE TO SOFTWARE ALLOCATION AND PERFORMANCE EVALUATION

,

JOHN WIELGOSZ

#### ABSTRACT

In this thesis we develope a representation of both hardware and software based on general directed graphs. In a hardware graph arcs represent processors and nodes represent memory stores. In a software graph the arcs are process descriptions and the nodes are groups of data. Program execution is modelled as the binding together of elements of these two graphs, the set of bound elements characterizing the program state at a given time. Binding is regarded as a resource allocation process, and the method of selecting one from the set of binding alternatives as the allocation strategy.

This modelling system was implemented as a program whose input consists of the two graph descriptions in sequential form. The program reconstructs the topology of the graphs within the computer memory using pointers, and proceeds to bind the two graphs until a terminal state is reached. During binding data is gathered using a set of performance measures. On completion statistics are calculated and a summary of the observations is produced. A log of the binding activity is also available.

The latter part of the thesis is concerned with the application of the modelling system to computer networks. The program was validated by modelling a simple store and forward network, and the results proved satisfactory at the ninety-five per cent confidence level. The system was then applied to a proposed linkage between computers in the United Kingdom and the Advanced Research Projects Agency computer network in the United States. The results of this application are described in the penultimate chapter. Finally conclusions drawn from the work are presented and possible extensions discussed.

#### ACKNOWLEDGMENTS

I wish to express my thanks to Professor Peter T. Kirstein for his guidance, patience, and friendship during the course of this research. My gratitude also goes to all the members of staff, both academic and secretarial, at the Institute of Computer Science who have been most generous with their time and help. I have been greatly aided by the service and facilities made available to me at the University of London Computing Centre, and by the cooperation of Control Data Corporation. Finally I would like to thank my wife for her unfailing encouragement and help while this work was carried out.

## CONTENTS

|          |     |                                               | Page |

|----------|-----|-----------------------------------------------|------|

| Figures  |     |                                               | 6    |

| Notation |     | 10                                            |      |

| Chapter  | I   | Introduction                                  |      |

|          | 1.1 | Background                                    | 13   |

|          | 1.2 | Computing power                               | 15   |

|          | 1.3 | Research aims and methods                     | 17   |

|          | 1.4 | Organization of subjects                      | 19   |

|          | 1.5 | Summary of results                            | 20   |

| Chapter  | II  | Review                                        |      |

|          | 2.1 | Graph models                                  | 22   |

|          | 2.2 | Models of resource allocation and utilization |      |

|          |     | in computing systems                          | 29   |

|          | 2.3 | Computer networks                             | 36   |

| Chapter  | III | Theory                                        |      |

|          | 3•1 | Graphical representation of hardware and      |      |

|          |     | software                                      | 49   |

|          | 3•2 | Recursive structure of SIGMA and PIgraphs     | 60   |

|          | 3-3 | Execution of a process by a processor         | 67   |

|          | 3.4 | Allocation of a processor to a process        | 76   |

|          | 3•5 | The hardware allocation problem in team       |      |

|          |     | execution                                     | 85   |

|          | 3.6 | Properties of nodes in SIGMA and PIgraphs     | 96   |

|          | 3-7 | Data dependence and reentrance                | 109  |

| Chapter  | IV  | Implementation                                |      |

|          | 4-1 | General criteria                              | 129  |

|          | 4.2 | Graph input                                   | 134  |

.

|              |                                   | Page        |

|--------------|-----------------------------------|-------------|

| 4.3          | The allocator                     | 151         |

| 4-4          | Ties and IFloops                  | 176         |

| 4.5          | Hardware measurement              | 187         |

| 4.6          | Software measurement              | 201         |

| Chapter V    | Validation                        |             |

| 5-1          | The choice of validation          | 208         |

| 5-2          | Store and forward networks        | 211         |

| 5•3          | The validation model              | 216         |

| 5-4          | The statistical test              | 231         |

| 5.5          | Validation results                | 235         |

| Chapter VI   | Application                       |             |

| 6.1          | A UK link to the ARPA network     | 243         |

| 6.2          | Analysis of the link              | 248         |

| 6.3          | The link model                    | 263         |

| 6.4          | Results                           | 280         |

| Chapter VII  | Conclusion                        |             |

| 7.1          | Summary of research aims achieved | 300         |

| 7-2          | Suggestions for further research  | 304         |

| Appendix I   | Bibliography                      | 307         |

| Appendix II  | SIMULA 67                         | 327         |

| Appendix III | SHAPE limitations                 | 338         |

| Appendix IV  | SHAPE user information            | <b>3</b> 45 |

# FIGURES

|               |                                                   | Page |

|---------------|---------------------------------------------------|------|

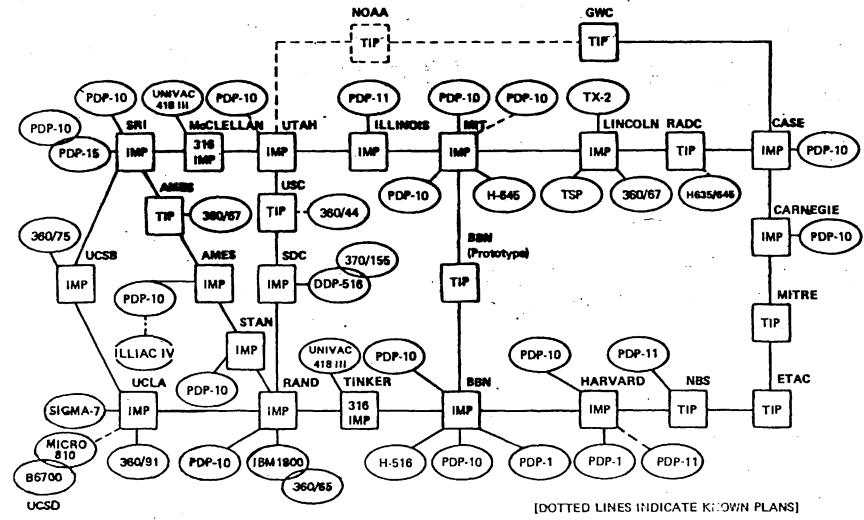

| 2 <b>-</b> 1  | The ARPA computer network as of May, 1972         | 40   |

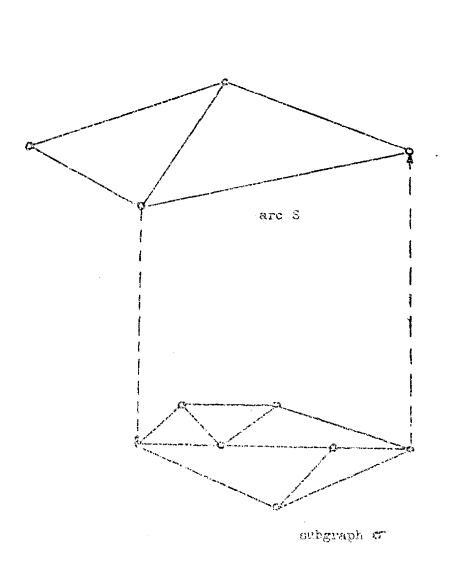

| 3-1           | Relationship of graph and subgraph                | 52   |

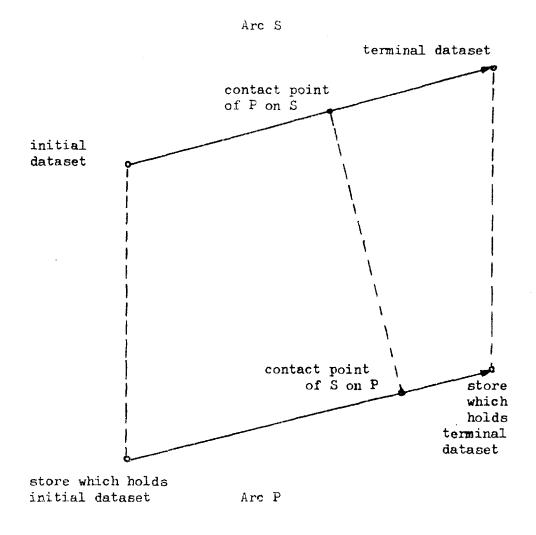

| 3-2           | Contact between arcs s and P                      | 57   |

| 3-3           | Correspondence between software and hardware      |      |

|               | representations                                   | 58   |

| 3-4           | Structure of a graph at more than one level       | 61   |

| 3 <b>-</b> 5  | Planar representation of fine structure           | 62   |

| 3 <b>-</b> 6  | List structure representation showing subgraphs   | 64   |

| 3 <b>-</b> 7  | Recursive call of SIGMA by itself                 | 65   |

| <b>3</b> –8   | Execution of an arc S by Processor $P_O$          | 69   |

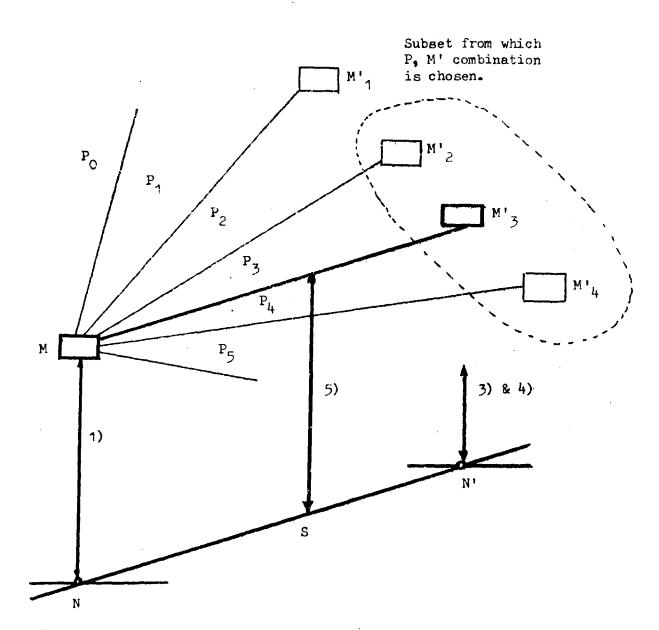

| 3-9           | Range of a processor $P_i$ at s on S              | 72   |

| 3-10          | Division of S when P is allocated                 | 77   |

| 3 <b>-</b> 11 | Microprogramming under program control            | 79   |

| <b>3-</b> 12  | Necessary correspondence between data for P and S | 81   |

| 3-13          | Measures characterizing function execution        | 82   |

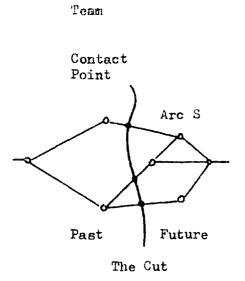

| 3 <b>-</b> 14 | Software graph showing cut zone                   | 86   |

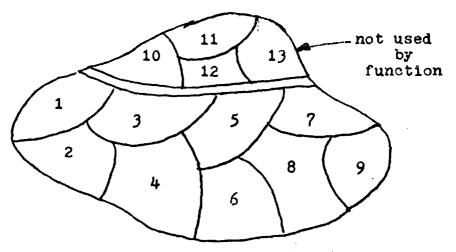

| 3-15          | Memory matrix for a node k                        | 90   |

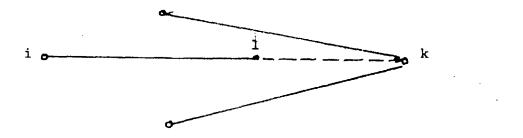

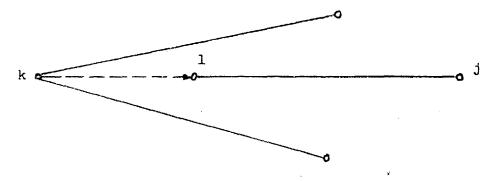

| 3–16          | Use of dummy arcs                                 | 92   |

| 3–17          | Reallocation on more than one level               | 94   |

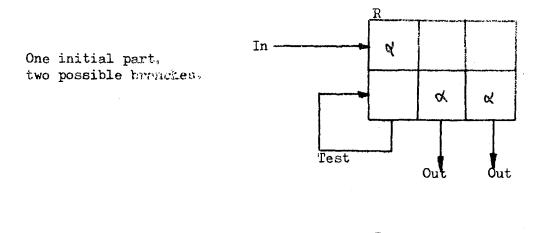

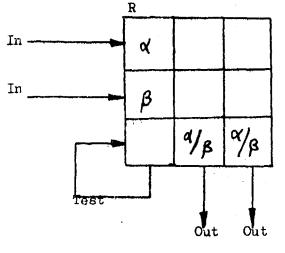

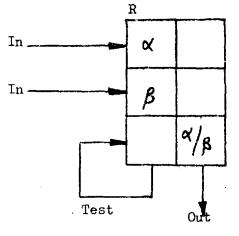

| 3-18          | Repartition Matrix R of a node                    | 98   |

| 3-19          | Binding of an arc S and its terminal node N'      | 100  |

| 3-20          | Branching arcs                                    | 103  |

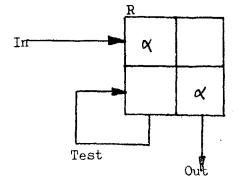

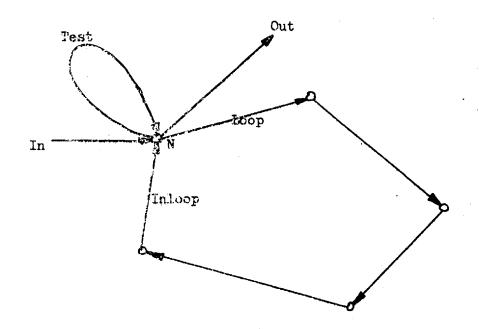

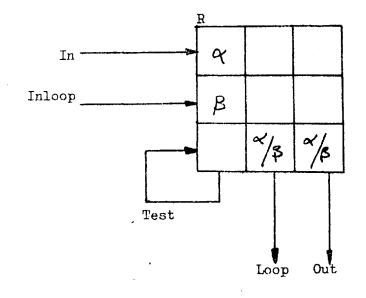

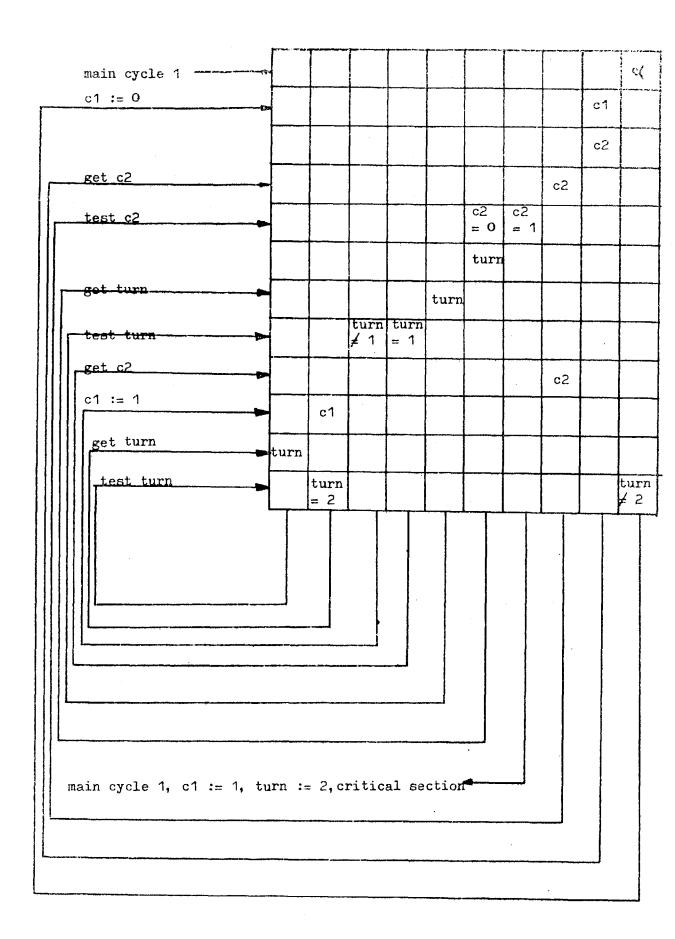

| 3-21          | Loop representation                               | 104  |

| 3-22          | R-matrix for process one of Dijkstra's interlock  |      |

|               | algorithm                                         | 108  |

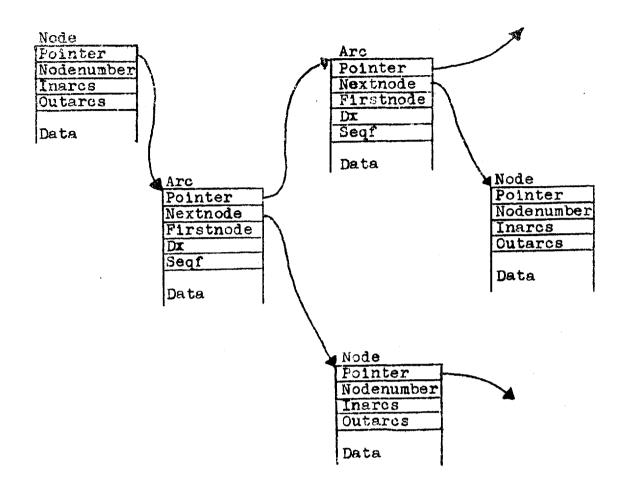

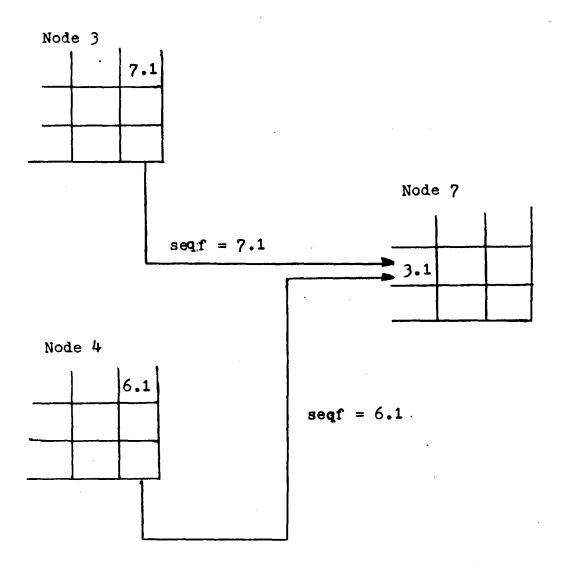

| 4-1           | Node and arc class definition            | <u>Page</u><br>137 |

|---------------|------------------------------------------|--------------------|

| 4-2           | Node and arc linkage                     | 1 <i>3</i> 8       |

| 4-3           | Subgraph linkage                         | 139                |

| 4-4           | Node class definitions                   | 142                |

| 4-5           | Arc class definitions                    | 143                |

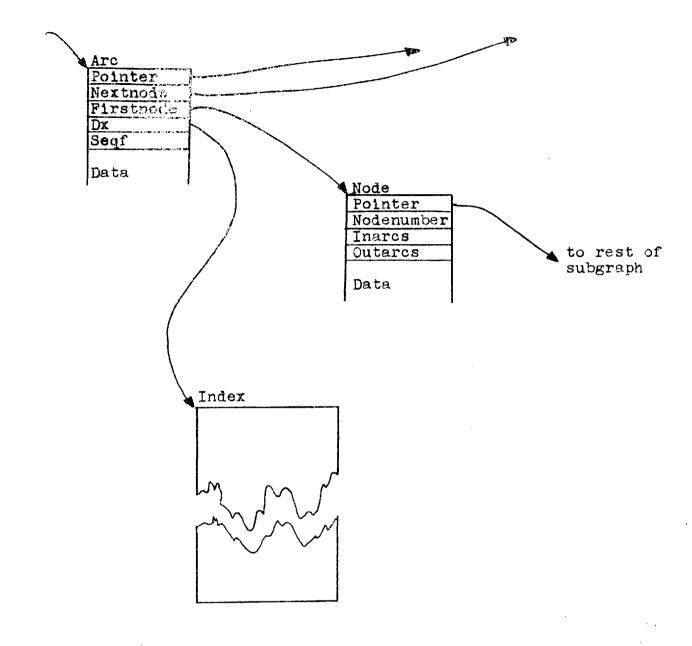

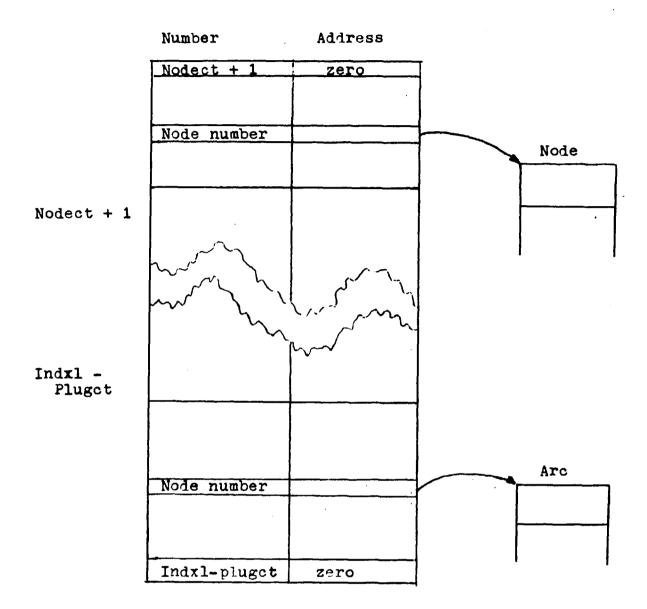

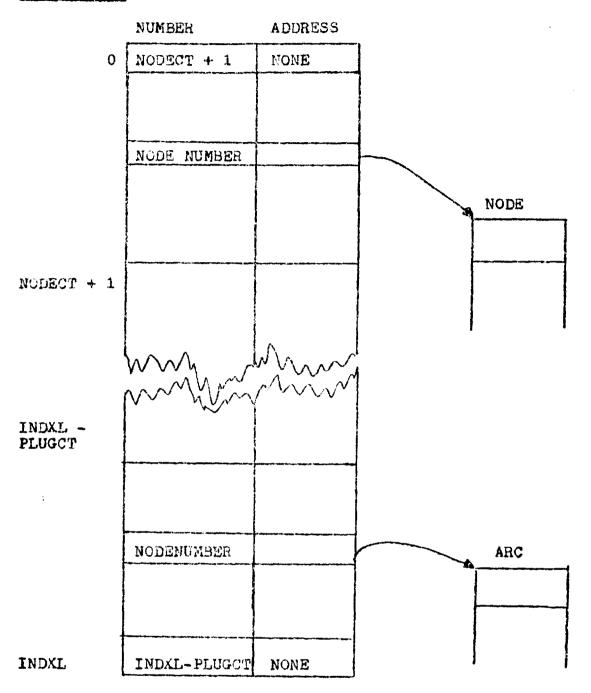

| 4-6           | Index usage for graph input              | 146                |

| 4-7           | Outline of class allocator               | 153                |

| 4_8           | Allocator parameters                     | 156                |

| 4-9           | Multiple INarcs                          | <b>1</b> 61        |

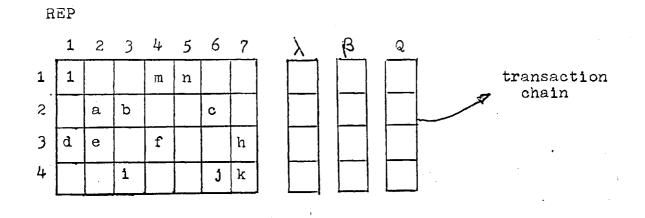

| 4-10          | Transaction entry to REP matrix          | 164                |

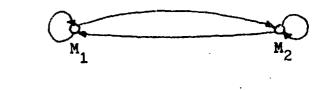

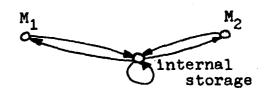

| 4-11          | Four state representation of a processor | 178                |

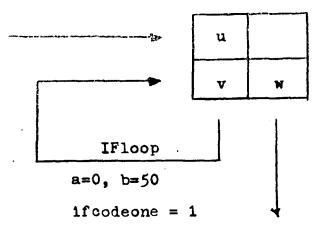

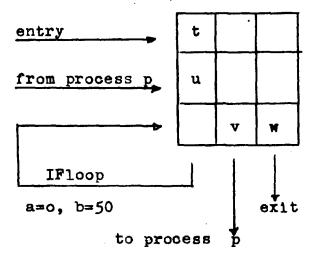

| 4-12          | DOloop examples                          | 182                |

| 4-13          | Summary of IFcode actions                | 186                |

| 4-14          | Processor utilization and efficiency     | 189                |

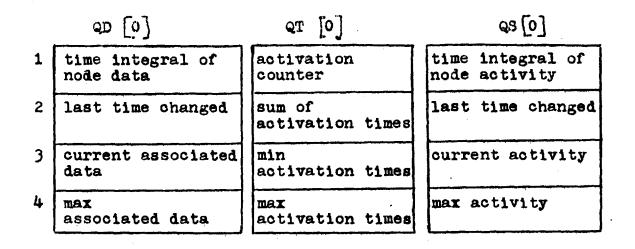

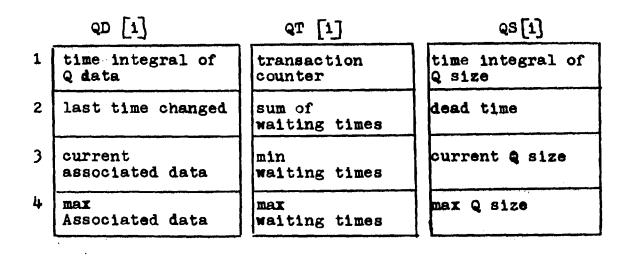

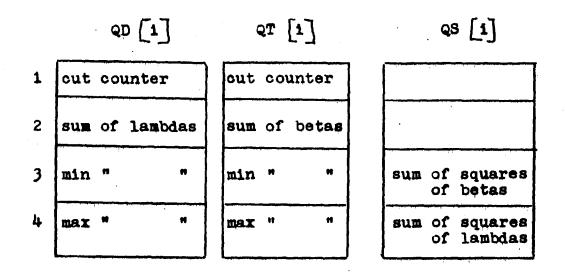

| 4-15          | Node statistics in arrays QD, QT, QS     | 202                |

| 4-16          | Cut statistics                           | 204                |

| 4-17          | Arc statistics in array STARC            | 206                |

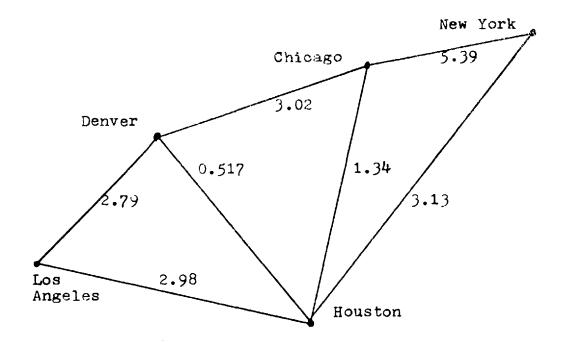

| 5 <b>-</b> 1  | Validation network                       | 217                |

| 5-2           | Proportional traffic matrix              | 218                |

| 5-3           | Message routing                          | 219                |

| 5-4           | Link traffic, delay and capacity         | 220                |

| 5-5           | Message delay matrix Z                   | 221                |

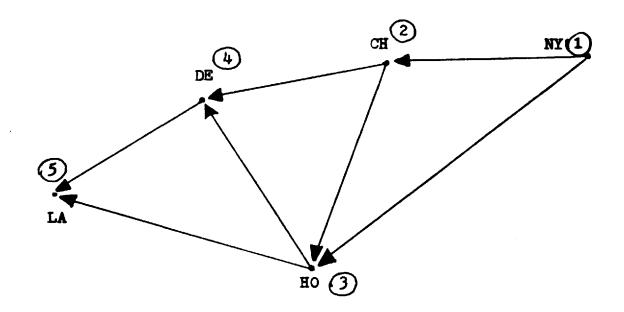

| 5 <b>-</b> 6  | Directed semi-network                    | 223                |

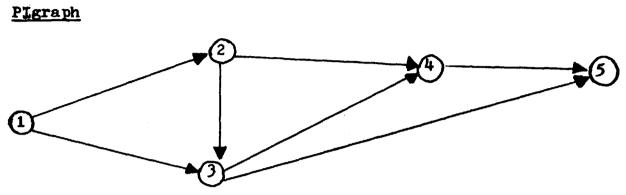

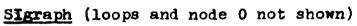

| 5-7           | SIgraph and PIgraph topologies           | 224                |

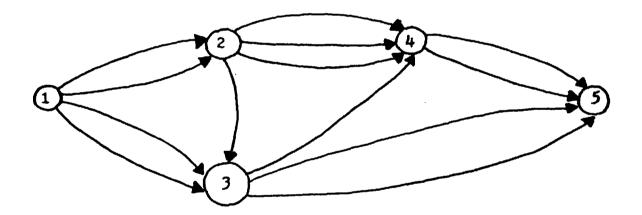

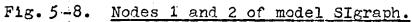

| 5 <b>-</b> 8  | Nodes 1 and 2 of model SIgraph           | 225                |

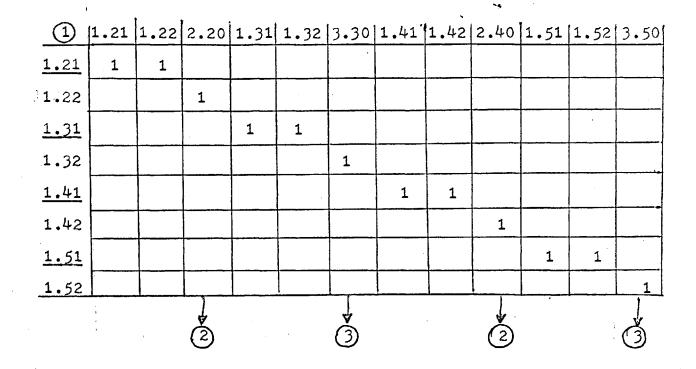

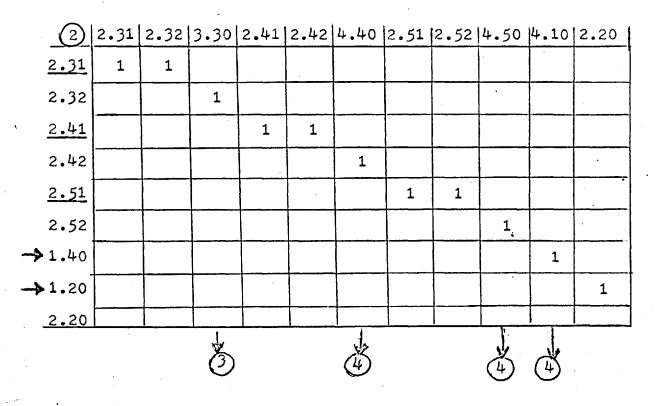

| 5 <b>-</b> 9  | Nodes 3, 4, and 5 of the model SIgraph   | 225                |

| 5 <b>-</b> 10 | Example arc data of the SIgraph          | 227                |

| 5 <b>-</b> 11 | Example node and arc data of the PIgraph | 228                |

|                   |                                                                   | D                  |

|-------------------|-------------------------------------------------------------------|--------------------|

| 5 <b>-</b> 12     | Values of t corresponding to given probabilities                  | <u>Page</u><br>233 |

| 5-13              | Values for t-test and $\overline{x}_k$                            | 236                |

| 5-14              | Mean message delay by message type for eight runs                 | 237                |

| 5 <b>-</b> -15    | Confidence limits for $\bar{x}_k \times 10^{-3}$                  | 238                |

| 5-16              | Mean message delay                                                | 241                |

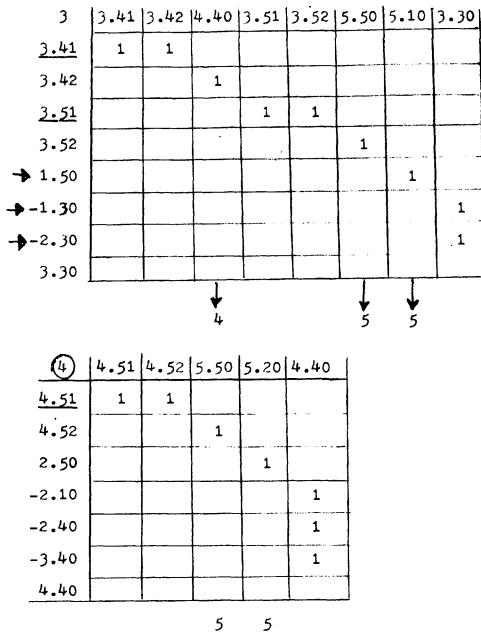

| 6–1               | Tentative ARPA network, logical map, May 1973                     | 244                |

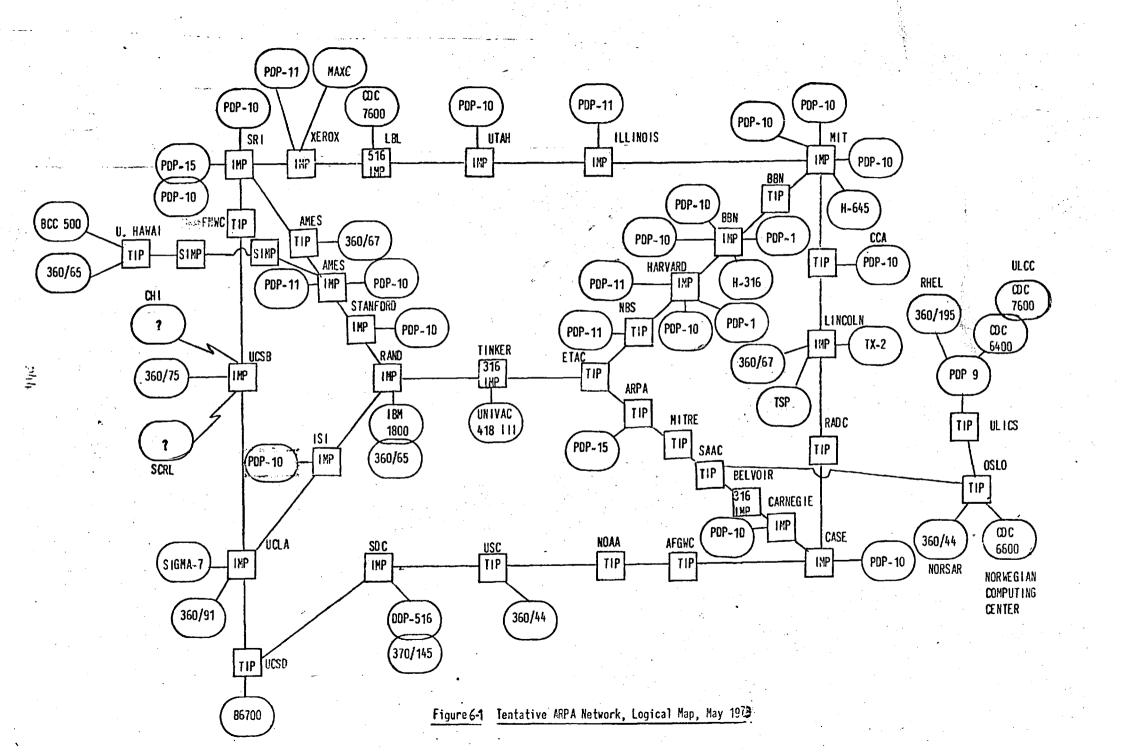

| 6-2               | UK-ARPANET linkage                                                | 249                |

| 6-3               | Traffic on each channel of the subnet                             | 252                |

| 6-4               | Values of $T_i$ and $P_i$ for L = 1/30                            | 254                |

| <b>6-</b> 5       | Values of $T_{600}$ for various combinations of C and C $_3$      | 25 <b>5</b>        |

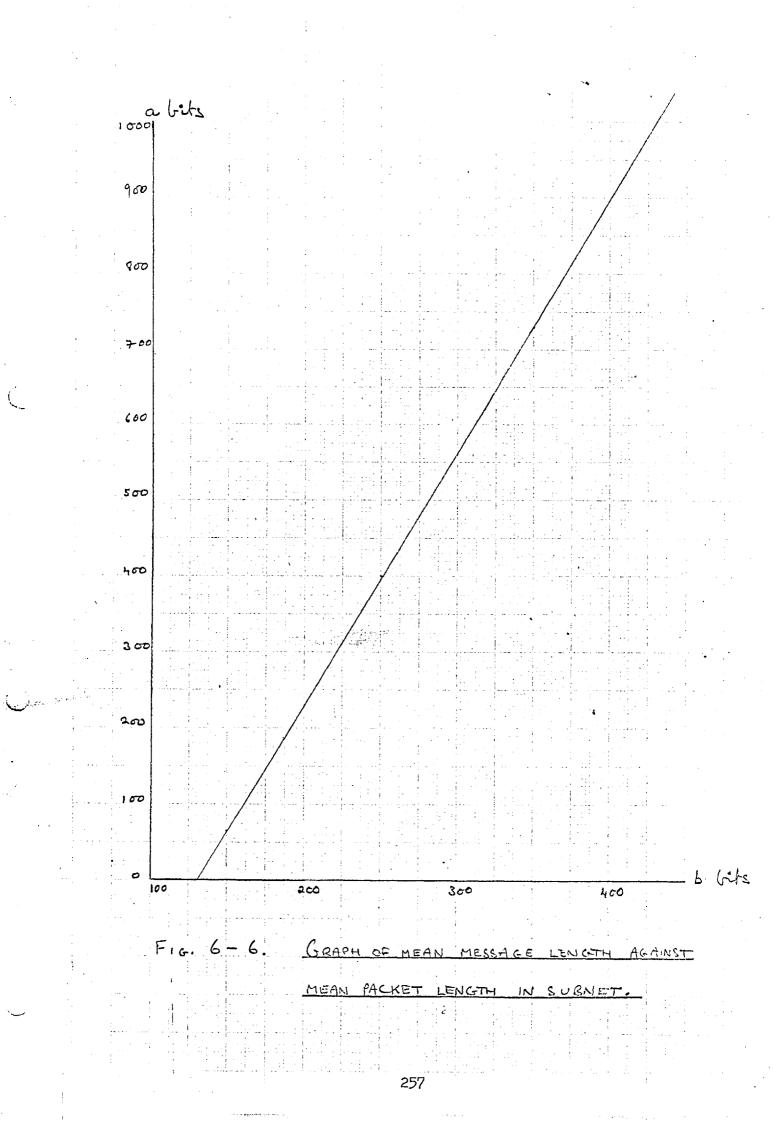

| 6-6               | Graph of mean message length against mean packet                  |                    |

|                   | length in subnet                                                  | 257                |

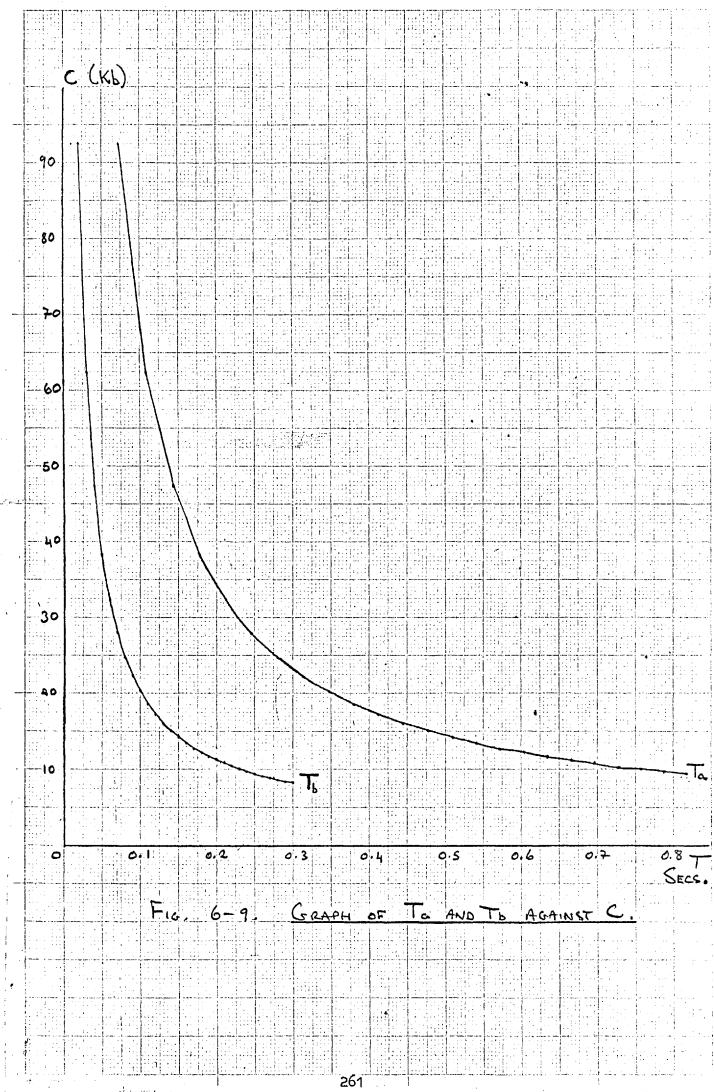

| 6-7               | Values of T and C for various $T_{b}$                             | 259                |

| 6-8               | Values of C <sub>i</sub> corresponding to $T_b$ shown in Fig. 6-7 | 260                |

| 6 <b>-</b> 9      | Graph of T and T against C $b$                                    | 261                |

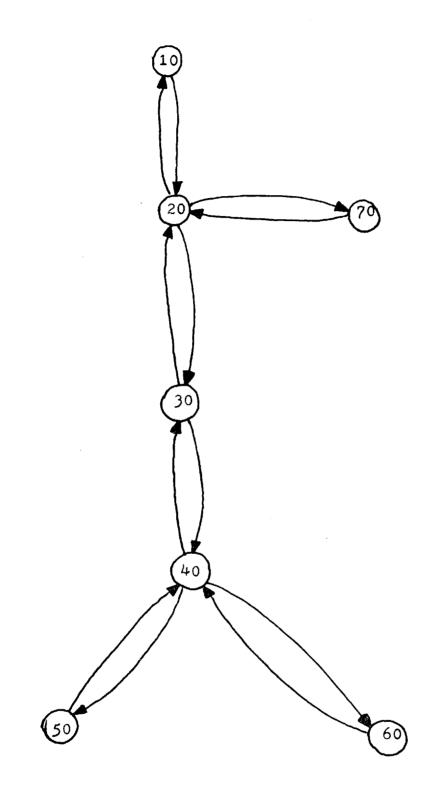

| 6-10              | Hardware graph of subnet                                          | 264                |

| 6 <del>-</del> 11 | Typical data for hardware graph                                   | 265                |

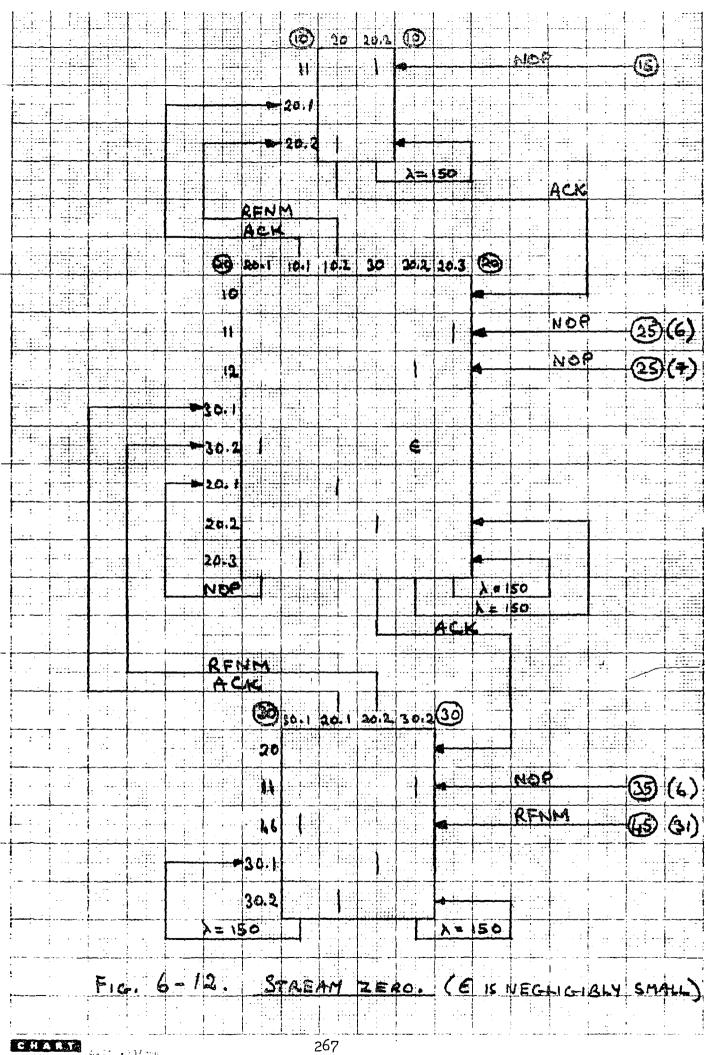

| 6 <b>-</b> 12     | Stream zero                                                       | 267                |

| 6 <b>-</b> 13     | Stream five: nodes 15, 25, 35                                     | 268                |

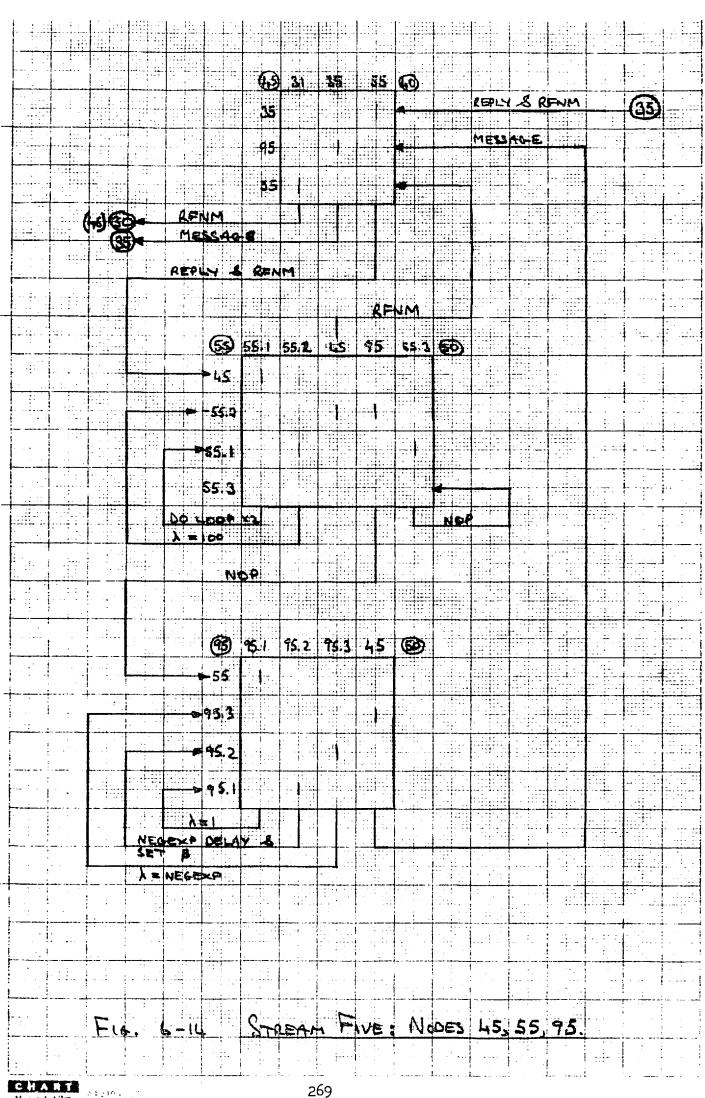

| 6 <del>~</del> 14 | Stream five: nodes 45,55,95                                       | 269                |

| 6 <b>-</b> 15     | Stream three                                                      | 270                |

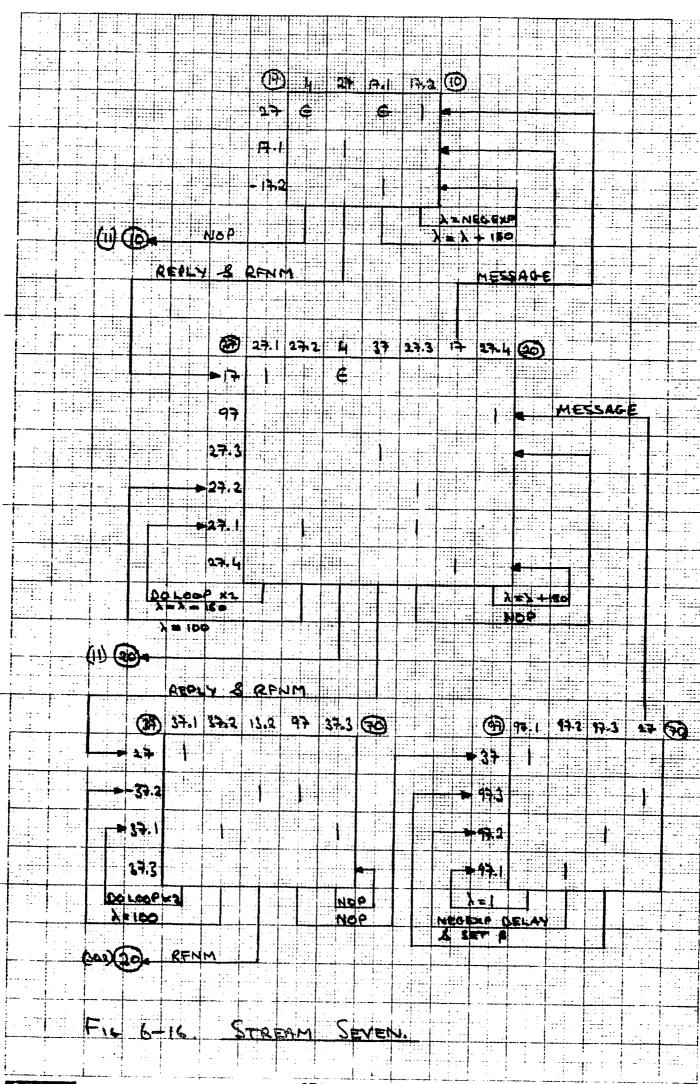

| 6 <b>-</b> 16     | Stream seven                                                      | 271                |

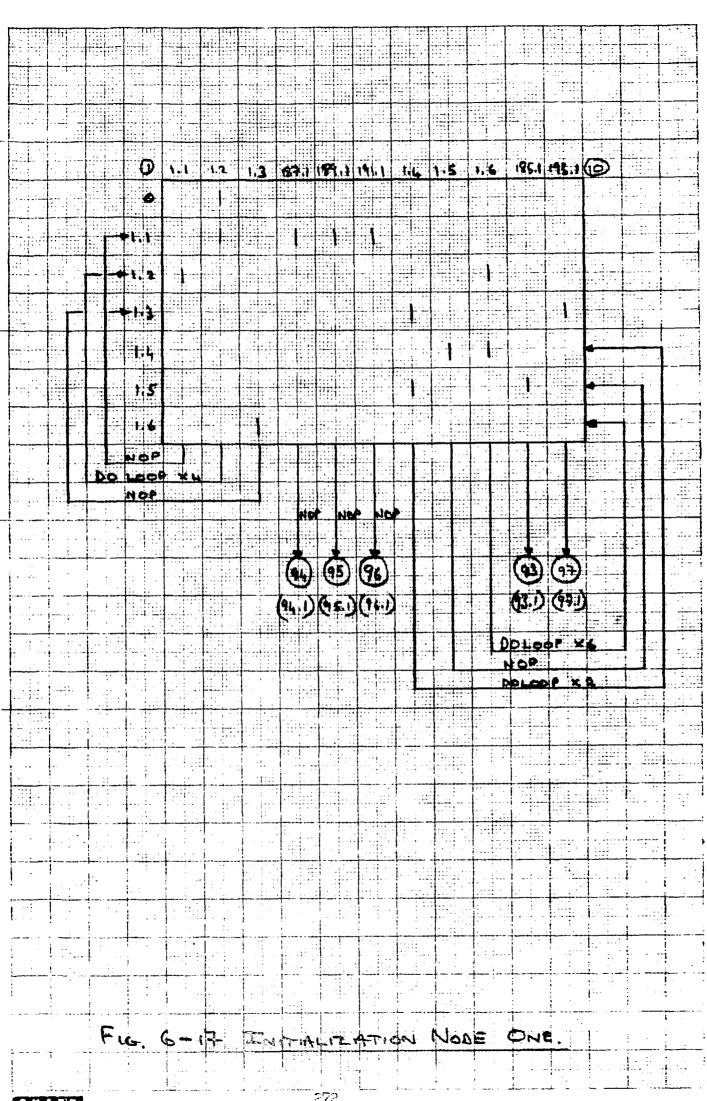

| 6-17              | Initialization node one                                           | 272                |

| 6–18              | Means of truncated negative exponential distributions             | 275                |

| 6–19              | Means of truncated negative exponential distributions             |                    |

|                   | (continued)                                                       | 276                |

| 6-20              | Subnet response when $C = 4.8$                                    | 281                |

| 6 <b>-</b> 21 | Subnet response when $C = 9.6$                                  | 282 |

|---------------|-----------------------------------------------------------------|-----|

| 6 <b>-</b> 22 | Subnet response when $C = 50$                                   | 283 |

| 6-23          | Non-cyclic generation of messages                               | 286 |

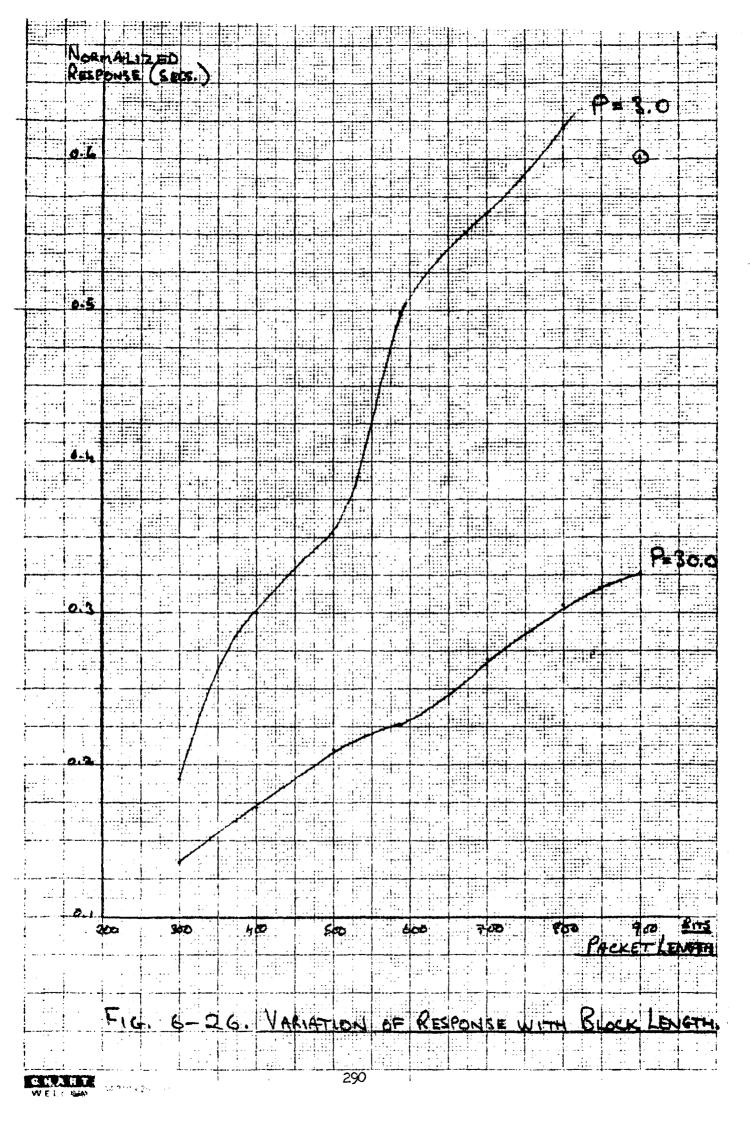

| 6 <b>-</b> 24 | Variation of response with packet length                        | 288 |

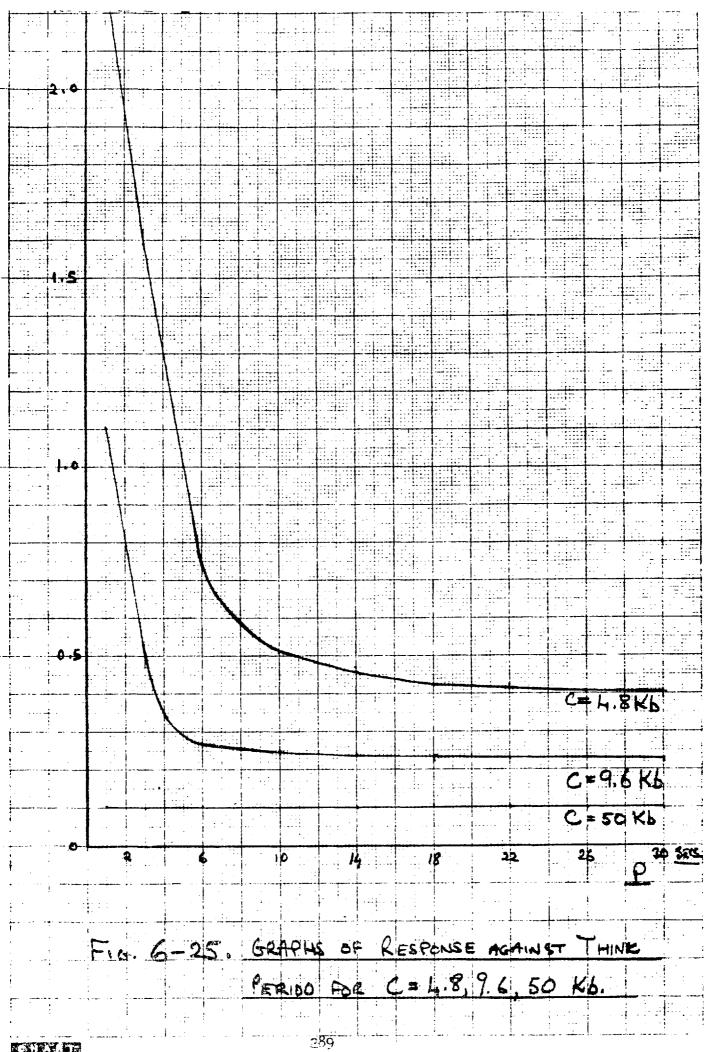

| 6 <b>-</b> 25 | Graphs of response against think period for                     |     |

|               | C = 4.8, 9.6, 50  Kb                                            | 289 |

| 6 <b>-</b> 26 | Variation of response with block length                         | 290 |

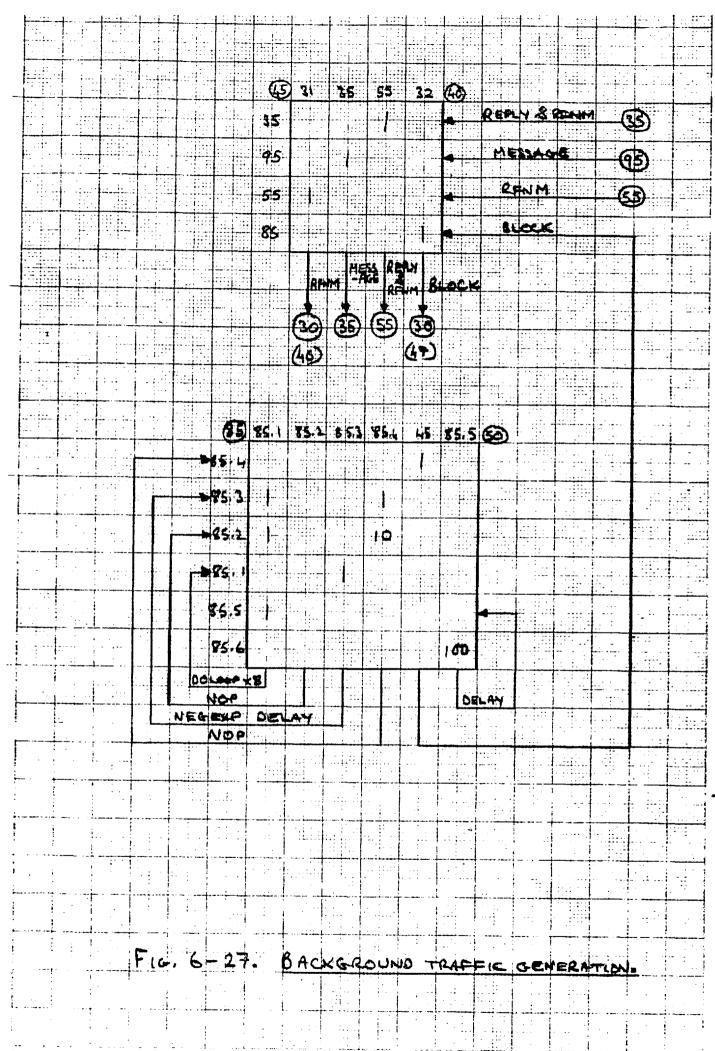

| 6-27          | Background traffic generation                                   | 292 |

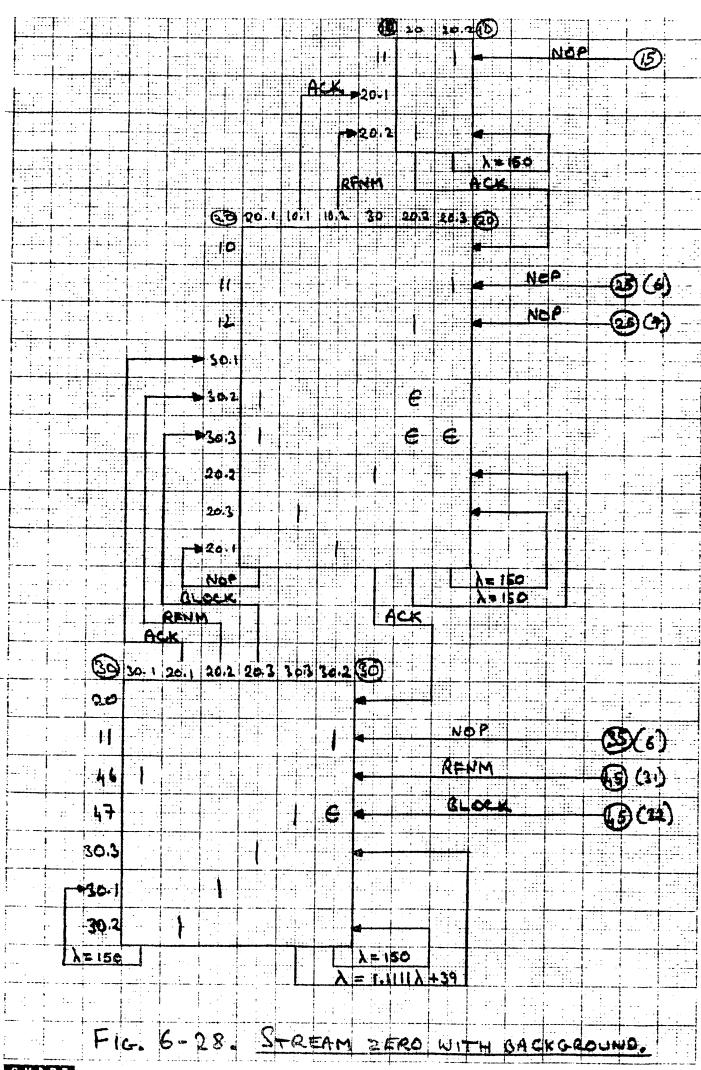

| 6-28          | Stream zero with background                                     | 293 |

| 6-29          | Initialization node one including background                    | 294 |

| 6-30          | Subnet response for various combinations of                     |     |

|               | $C_1$ and $C_3$ when P = 30                                     | 296 |

| 6 <b>-</b> 31 | $T_a$ for various combinations of $C_1$ and $C_3$ when $P = 30$ | 297 |

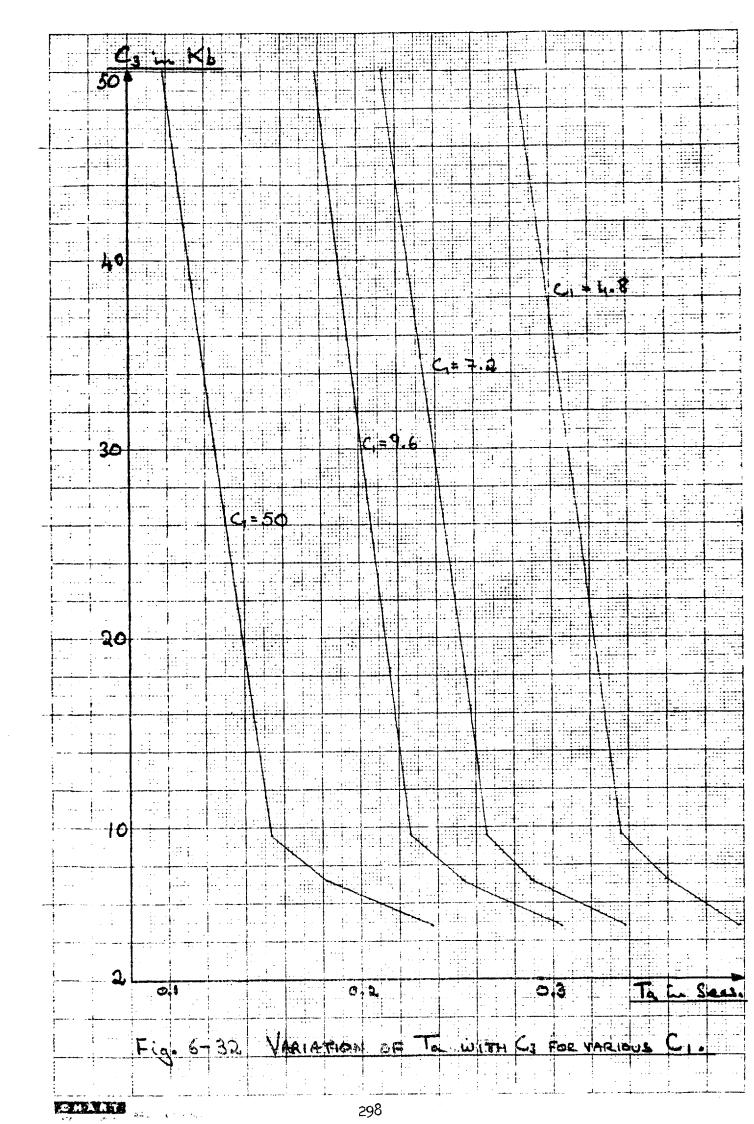

| 6 <b>-</b> 32 | Variation of T with C for various C $\frac{1}{1}$               | 298 |

÷

•

NOTATION

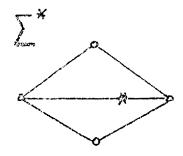

| $\Sigma$ , sigma            | Software graph                            |

|-----------------------------|-------------------------------------------|

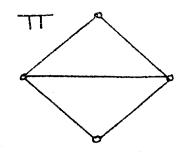

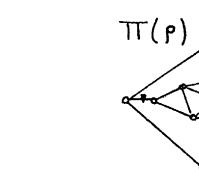

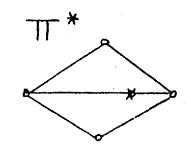

| TT, PI                      | Hardware graph                            |

| $\Phi$                      | Null processor                            |

| 6                           | Software subgraph                         |

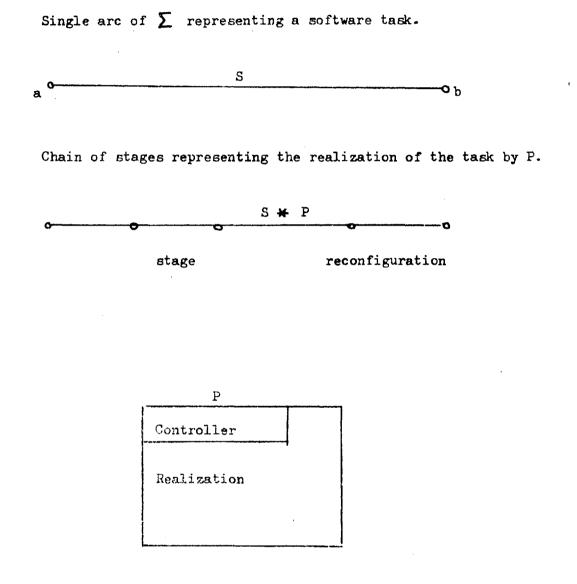

| S                           | Arc of software graph, process            |

| P                           | Arc of hardware graph, processor          |

| PI                          | Identity processor                        |

| PO                          | Ideal processor                           |

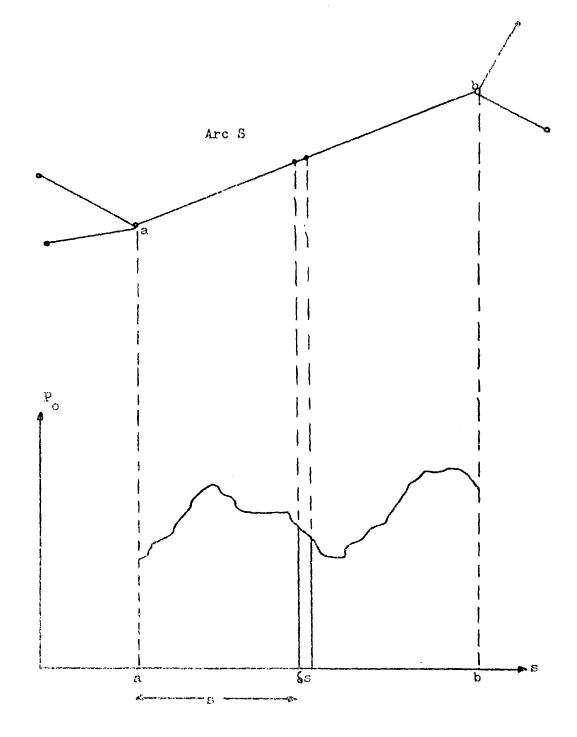

| s                           | Quasi-distance on arc S                   |

| <b>S</b> w                  | Quantity of computation                   |

| j(s)                        | Computation density                       |

| т <sub>о</sub>              | Time for $P_0$ to execute S               |

| W                           | Total computation of S                    |

| u                           | Scaling factor for processor power        |

| Т                           | Time for P to execute S                   |

| r(p,s)                      | Range of P at s on S                      |

| r <sub>0</sub> (s)          | Quantal range at s on S                   |

| $\gamma_{0^{(u)}}$          | Time for $P_0$ to execute $r_0(s)$        |

| L                           | Loss                                      |

| ∝ <sub>i</sub> (s)          | Redundancy of P. at s                     |

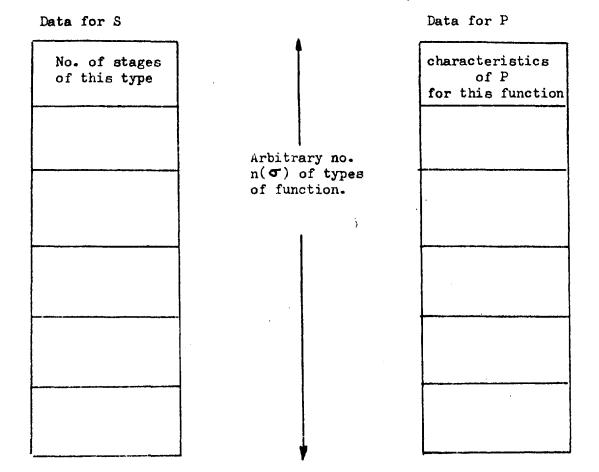

| n( <b>5</b> )               | Number of software functions for subgraph |

| $\emptyset_{i}$             | Number of times i th function is executed |

| К                           | Allocation procedure                      |

| A                           | Graph analysis procédure                  |

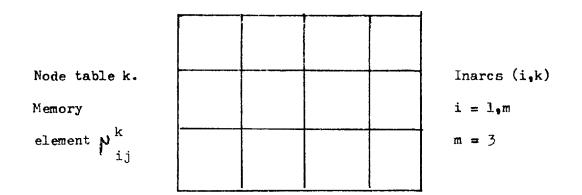

| REP                         | Repartition matrix                        |

| REP[i,j], P <sup>k</sup> ij | Element of repartition matrix of node K   |

| SIgraph                     | Software graph                            |

|                             |                                           |

| SIarc              | Arc of software graph                               |

|--------------------|-----------------------------------------------------|

| SInode             | Node of software graph                              |

| PIgraph            | Hardware graph                                      |

| PIarc              | Arc of hardware graph                               |

| PInode             | Node of hardware graph                              |

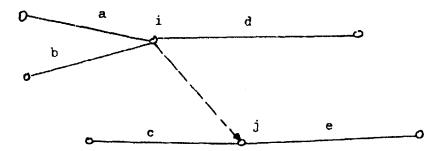

| INarc              | Arc entering a node                                 |

| OUTarc             | Arc leaving a node                                  |

| $\lambda$ , lambda | Size of initial arc data                            |

| Q, BETA            | Cut generation time                                 |

| ACT                | Activity matrix of a node                           |

| V                  | Portion of tie duration due to store characteristic |

| ut                 | Utilization                                         |

| ef                 | Efficiency                                          |

| f                  | Function i of SIarc                                 |

| t <sub>i</sub>     | Time for processor to execute f                     |

| c j                | Cost of processor component j                       |

| t<br>ij            | Time component j in use during j <sub>i</sub>       |

| ut.<br>i           | Utilization of processor during function i          |

| ef.<br>i           | Efficiency of processor during function i           |

The notation above is that used in describing the SHAPE system. We have not included variable names from the SHAPE program, and these are defined when used in Chapter IV. Variables used to describe the systems modelled in validating and applying the SHAPE system only appear, and are defined, in Chapter V and VI respectively.

## CHAPTER I

## INTRODUCTION

•

#### 1.1 Background.

One of the goals of computer designers and users in creating new equipment is increased computing power. Such a goal is not difficult to justify. If achieved it reduces the cost of current computing activity, or allows expansion at a lower price; a previously uneconomic solution to a problem may now seem more attractive; perhaps less frequently, a solution is made feasible on an acceptable time-scale. Intuitively computing power is not a difficult idea to grasp, but interpretations vary and are seldom precise.

Computing power is usually described in relative terms. For example, twice the work done per day implies twice the computing power; alternatively, the same work done in half the time. In practice these need not be the same thing. Such relative comparisons tend to beg the question of what we really mean by computing power or computing work. It is worth emphasizing that computing power (in its normal intuitive sense) is very dependent on the task to be performed. In this sense it is dynamic, and not a function of hardware alone.

Expansion of a computing facility by adding more equipment of the type already in use may be called <u>lateral</u> expansion. Replacement by differently designed, faster, or more appropriate equipment may be termed <u>vertical</u> expansion. It is said, and may generally be the case, that there is more computing power per unit cost in a large system than in a small one. Consequently, simply spending more for a larger system may well do as a first step to increased computing power per unit cost. Having reached some financial limit, a differently designed, or in some sense intrinsically more powerful machine, for the same

1.3

price is needed.

Usually a mixture of these approaches is adopted. Another possibility is to design and build a new machine of the required power, though this is beyond the scope of most users. It is, however, part of a manufacturer's motivation. A counter-productive side-effect in increasingly powerful systems is the difficulty of using that power efficiently. Significant numbers of comparatively trivial tasks underutilize hardware, and difficulty in organizing work flow leads to high system overhead and idle time. At best only partial solutions to these problems have been found.

#### 1.2 Computing power.

Theoretical limits of computing power undoubtedly exist given the current state of physical science. Laws such as the uncertainty principle will limit switching speeds of stores, transmission speed of data, and packing density of information. If we consider the hypothetical situation arising when computer technology reaches these limits, then only one strategy for achieving increased computer power remains. This is the organization of laterally expanding systems to process work in a parallel fashion.

Such an approach makes the implicit assumption that a significant amount of computational work is amenable to parallel processing. Though we are very far from the absolute limits mentioned above, the situation has a practical analog in the problem of a real-time system which is already using the fastest appropriate computer available, and is still unable to meet the completion constraints for some task or set of subtasks. The only way to meet the constraints is to reorganize the task so that it is amenable to parallel processing and then execute it on a laterally expanded system.

A visible trend in recent computer design is <u>functional</u> <u>dispersal</u>. This is based on the view that if too many functions are combined in one module, then much of it is idle, much of the time. Consequently, greater efficiency is obtained by having the functions in separate modules of appropriate cost and computing power. These are used when needed by the task and free for other work the rest of the time. The gain in efficiency presupposes enough different tasks in the system to ensure that individual module utilization is high. Attempts to meet this need have

recently led to pipeline design in some large computers.

Elementary function dispersal is present in computing equipment at the time of writing. Separation and concurrency of computation, I/O, telecommunications control, display regeneration, and so on, is evident in most third generation machines. Such function dispersal places increasing emphasis on the net-like aspects of computer facilities. Net representation of a computing facility can be applied at any level of detail, from computer networks, where the complete computer is the quantal object, to a single processor, where each logic subassembly is considered separately.

Clearly a program organized for parallel processing can take advantage of function dispersal to minimize its total execution time, and to select the functional hardware best suited to its individual processes. This is potentially a means of improving performance over a sequential version of the same task. Indeed, a sequential program may be regarded as one member of the class of parallel programs which achieve the same result.

#### 1.3 Research aims and methods.

We have mentioned above the problems of using powerful computer systems effectively. In this thesis we attempt to provide a framework for the solution of such problems. Some elements common to a wide range of computing processes are isolated and identified. From these a technique for modelling computational activity in complex computer systems is developed. It is hoped that the technique will prove useful both as an aid to problem definition, and as a practical tool in the solution of a problem once it has been defined.

We have tried to introduce measures for aspects of the computational process which will be relevant in most circumstances and useful in evaluating the performance of systems under investigation.

We view computational activity as a hardware to software allocation process. That is to say that a task is realized, or results produced, by the allocation of a task processor to a task description. The basic operation in this process is chosen to be the production of one dataset from another through the action of a processor. A complete task is then regarded as a number of such steps occurring sequentially or in parallel.

The modelling technique uses directed graphs to represent software description and a hardware configuration. Execution of the former by the latter can then be modelled as a dynamic connection, or binding, of the two graphs. The system has been implemented in a high-level language (SIMULA 67) whose syntax provides features which correspond closely to the needs of such a modelling system.

Our goal has been to provide a system which can be used to evaluate and compare various combinations of hardware and software which perform a given task, and so provide a means of optimizing task performance both in existing and proposed computer systems.

## 1.4 Organization of subjects.

The material which follows is organized into six chapters each dealing with one phase of the research that was carried out. In Chapter II there is a brief discussion of related work in the fields of modelling, allocation problems, computing and transmission networks, and performance measurement.

In Chapter III we develope the concepts and theoretical considerations on which the modelling technique is based. We then describe the technique itself and show how it can be applied to computational processes. Chapter IV gives an account of the implementation of the technique on a CDC 6600 computer using the SIMULA 67 programming language.

Chapter V contains the results of a validation of the system, using a small store and forward network as a test situation. In Chapter VI, we apply the system to a proposed network linkage between the U.K. and the ARPA (Advanced Research Projects Agency) computer network in the United States. We describe the way in which the modelling technique was used to investigate the performance of the linkage under various conditions and present the results obtained.

Chapter VII discusses the conclusions which can be drawn from the research undertaken, and makes suggestions for further study. We have added four appendices for reference purposes. These are some remarks on SIMULA 67 and the CDC 6600, information required to use the implementation of the modelling system, a description of the limitations of the implementation and a bibliography.

### 1.5 Summary of results.

We have designed a system, based on graphical representation, which is sufficiently general to model a large class of computational processes. This has required the identification of a set of basic functions which are necessary for such modelling, and a program incorporating them has been written. To create such a system we have had to isolate and define the operation of these functions in some depth, and as a result we believe the modelling system corresponds well with the underlying structure of computational activity.

As necessary adjuncts we have produced computer input procedures which convert a sequential graph description to a topological replica within the computer, as well as a set of performance measures by which different model executions may be compared.

The implementation has been validated using a model of a store and forward network, and the modelling technique was applied to a computer network link between Britain and the U.S. Results predicting the performance of the link under various conditions have been obtained, and hardware parameters for link operation estimated.

CHAPTER II

REVIEW

#### 2.1 Graph models of computation.

In this section we give some of the history and bibliography of models of computational processes which use graph representations. In the following sections we deal with resource allocation in computer systems and the design of computer networks. The references quoted are to be found in Appendix I, which also contains a separate comprehensive bibliography of material related to computer networks.

A number of researchers have produced graph models of computation. The use of graph representations is widespread in the literature of the theory of computation, and has also extended to modelling or describing processes which involve existing hardware or software systems. The utility of such descriptions can be seen, for example, in the short paper by K. A. Bartlett, R. A. Scantlebury and P. T. Wilkinson which gives an algorithm for the detection of errors during data transmission [BART 69]. Here the finite automata state diagram is used in the solution of a highly practical problem in computer communications.

One of the earliest widely quoted models of computational activity is the one put forward by R. M. Karp and R. E. Miller in 1966 [KARP 66]. Their model is called a computation graph. This is a directed graph in which nodes denote operations and arcs denote storage elements where results are placed in firstin-first-out queues. Associated with each arc are four nonnegative integers  $A_p$ ,  $U_p$ ,  $W_p$  and  $T_p$  where  $T_p > W_p$ . For an arc directed from node i to node j these parameters are interpreted as follows:  $A_p$  is the number of data words initially in the queues;  $U_p$  is the number of words added to the queue upon

completion of the operation associated with node k; and  $T_p$  is a threshold giving the minimum queue length of the arc before the operation of node j is initiated. Karp and Miller show that computations represented by these graphs are deterministic. They also give a test to determine whether a computation terminates, and study properties of the data queues associated with the arcs, deriving conditions for the queue lengths to remain bounded.

Another type of model, similar to those above but probably more oriented to hardware representation, is one in which a set of operations are connected to a memory as in Karp and Miller's model but the control is entirely local and is incorporated into the values stored in the memory. Each operation monitors the values in its domain locations and can apply whenever the values belong to a specified set. When an operation applies it replaces the values in its range locations as determined by the current domain values. Models of this type have been investigated by Luconi [LUCO 68] and Petri [PETR 62]. Luconi considers schemata in which only a subset of the memory cells need contain unique sequences of values. Such schemata are called output functional and are realized by allowing more than one determinate computation to nondeterminately "share" operations. Sufficient conditions for a schema to be determinate are given and synthesis procedures for output functional schemata are provided.

E. Van Horn [VANH 66] has proposed an abstract model called machines for coordinated multiprocessing or MCMs. An MCM consists of a set of cells, a count matrix, and a scheduler to control operations. Each cell may behave either as a memory

(value) cell or as a computing (clerk) cell. In the latter case, a table of transactions is associated with the cell where each transaction may read and write cells or modify the count matrix. On the basis of the values in the cells and in the control matrix the scheduler determines which cells are enabled, i.e. can perform one transaction. The scheduler selects a subset of the enabled cells and directs them to perform their transaction. Van Horn has demonstrated that the action of the scheduler insures that the behaviour of any MCM is asynchronously reproducible.

G. Estrin and R. Turn [ESTR 63B] and D. Martin [MART 66] have introduced a directed graph model for computer programs in which the vertices represent computational tasks and the arcs represent data dependency between nodes. In this model, the conditions for the initiation of the computation denoted by a vertex is expressed by writing a boolean expression in terms of boolean variables associated with the arcs incident into the node. A boolean variable associated with an arc is true when the data in that arc becomes available. A computation may be initiated when the boolean expression of the corresponding node, called the vertex input control, is true. There are three types of vertex input control: conjunctive, disjunctive and compound. Vertices with conjunctive input control may be initiated only when all input data are available. Vertices with disjunctive input control may be initiated only when precisely one set of input data (i.e. one arc) becomes available. The compound input control is a combination of the other two. Vertices also have output control which is used to specify the program flow from a

vertex to a subset of its immediate successors. A vertex with conjunctive output control simultaneously makes data available at all of the arcs incident out of the vertex. A vertex with disjunctive output control makes data available at precisely one of its output arcs. Thus vertices with disjunctive output control effectively perform data dependent decisions to control the program flow. The model can properly represent only cycle free graphs. It has been used primarily as a tool for the <u>a priori</u> assignment and sequencing of computation in parallel processor systems. This model, described below, has been developed in a sequence of research reports by Turn, Martin, J. L. Baer, D. P. Bovet, E. C. Russell, S. A. Volansky, and V. G. Cerf, working with Professor G. E. Estrin at the School of Engineering and Applied Science at U.C.L.A.

Cyclic to acyclic graph transformations are the subject of [MART 67B] by Martin and Estrin, and other properties of the model are derived in [ESTR 63A, MART 67A, 67C, 69] by the same authors. Baer [BAER 68] has investigated the assignment of computations to processors by various scheduling techniques. Bovet [BOVE 68, 70A, 70B] has analyzed the model to determine profiles for memory allocation and Russell [RUSS 69] has used the model as a basis for the limited detection of parallelism and developed a system for the automatic generation of graph model descriptions, including attribute sets, from FORTRAN programs. Baer and Bovet have presented a method to test the legality of the initiation/termination conditions described by the graph model [BAER 70].

Volansky [VOLA 70] has further extended use of the model with an investigation of the detection and implementation of

parallelism in a multi-processor environment. Cerf [CERF 72] has considered the flow of program control which can be represented in the model, and determined condition for the proper termination of programs so modelled.

The U.C.L.A. model has been further developed by J. Rodriguez [RODR 69] to study the determinacy of the execution of a program where the parallelism is shown. Further control is introduced on the arcs of the graph. These can be idle, enabled, disabled, and blocked, while nodes are classified by their computational functions (control, data modification, loop junction) and logic (AND, EOR, and OR).

Other work on graph models of computation is that of H. Eisner [EISN 62], in which he has generalized the PERT network technique to take into account alternatives in performing project phases. This was achieved by assigning probabilities to different arcs out of decision nodes.

D. R. Slutz [SLUT 68] has extended the work of Karp and Miller. His models are called Flow Graph Schemata, and contain two structures. The first, called a data flow graph, indicates the paths of data flow and includes both operations to perform data transformations and memory cells to store intermediate results. The second is called a control graph and represents a mechanism to effect sequencing of operation activations. Using these structures Slutz has investigated the problems of determinacy and equivalence.

Three papers of interest in the use of graphs for modelling systems of processes are those of D. L. Parnas [PARN 69A], and of S. Crespi-Reghizzi and R. Morpurgo [CRES 70], and of Pfaltz [PFAL 72].

Parnas deals in some depth with the simulation of simultaneous events and gives an algorithm for the derivation of an efficient sequential process equivalent to a given network of parallel processes, where the network has unconditional rules of immediate dependency, and no delayless loops. Crespi-Reghizzi and Morpurgo present a language for representing graphs. The language uses linked lists to provide facilities such as addition and deletion of nodes and arcs, traversal of graphs, union, intersection, and so on. Pfaltz describes graph structures which allow the introduction of extra subsequences of arcs at nodes and other similar substitutions.

The works referenced above are mostly attempts to model the behaviour of parallel computations. To insure determinate behaviour it is necessary to provide some mechanism that would disallow more than one operation to change the contents of a shared memory cell at one time. Such mechanisms are also present in current proposals for practical parallel and multiprogrammed computer systems.

Dijkstra [DIJK 66] considers a method by which asynchronous sequential processes may communicate 'harmoniously'. The processes are provided access to common integer variables called semaphores. The semaphores can be manipulated by means of two synchronizing primitives, the 'P' and 'V' operations which decrement and increment, respectively, the value of a semaphore by one. The P operation can be executed only when the current value of a semaphore is greater than zero. Thus the facility is available for one process to block another from entering a 'critical section' such as data accessible to

both. A number of interesting examples using semaphores are given. Dijkstra [DIJK 68] has incorporated semaphores into the design of a multiprogramming system and A. Habermann [HABE 69] has provided a theoretical justification of the logical structure. Holt [HOLT 71] has discussed Habermann's work and shown that artificial deadlocks can occur when Habermann's methods are used, and that they do not necessarily eliminate cases of permanent blocking. Holt gives a solution for these situations. Hebalkar [HEBA 71] has extended Habermann's analysis with a graph model of process resource requirements and defined algorithmic tests relevant to resource allocation with the intention of precluding deadlocks.

The interested reader is referred to various other papers on aspects of graph models of computation: [BERN 66, ABLO 68, BRUN 71, CORN 70, IRAN 71, EARN 72, SHOS 69, LOWE 70, GILB 72, TESL 68, CONS 68, COHE 68, GONZ 69, DENN 68, KOTO 68].

#### 2.2 Models of Resource Allocation and Utilization in Computing Systems.

Many of the models mentioned in the previous section have been used to investigate resource allocation strategies. In particular Bovet [BOVE 68] has examined memory allocation profiles using the U.C.L.A. model. P. J. Denning [DENN 68] has also used graph models when investigating multiprocessor assignment.

The literature of resource allocation and utilization in computational systems is extensive. Much of it uses queueing theory to provide mean values for quantities of interest such as service times, waiting times, throughput rates and idle times. However, there is also a wide range of non-stochastic analyses.

One of the earliest papers in this field is that of J. Heller [HELL 61] which deals with the scheduling of the tasks of a computational job among the processing units which can carry them out. Solutions are obtained for completion times of the tasks, and idle times of the processing units, and these are then extended to the concurrent execution of more than one job.

G. K. Manacher [MANA 67] has provided a more extensive treatment of problems similar to that investigated by Heller. In this paper the assignment of tasks to processors is controlled by a task list, which orders all tasks according to servicing priority. A free processor is assigned to the highest priority task available. Two types of constraint are used, starttimes and completion times. Tasks with start-times may not commence before those times, and tasks with completion times must terminate before them. Algorithms are developed to give

schedules which guarantee the execution of tasks within their deadlines, and allow the inclusion of non time-critical tasks in these schedules.

T. C. Hu [HU 61] uses a graphical model to derive an algorithm for the optimum sequencing of the tasks of a job in two cases. The first case is to provide a schedule which satisfies a completion constraint on the whole job with a minimum of processors, and the second is to provide the schedule with the earliest completion time when the number of processors are fixed.

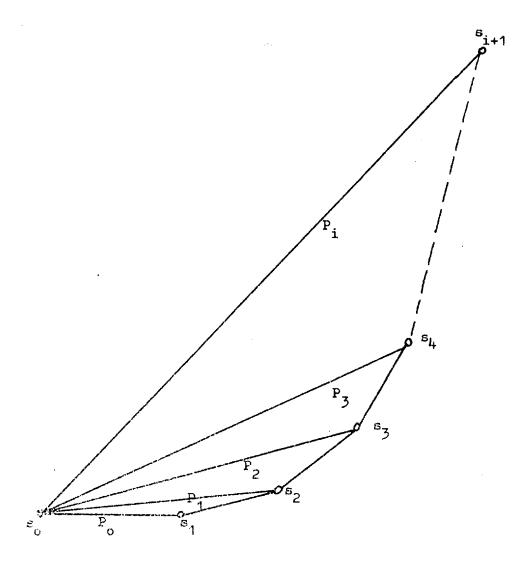

The models described above have been greatly extended by the work of R. R. Muntz and E. G. Coffman [MUNT 69A, 69B, 70]. The authors have used acyclic, directed graphs not unlike the U.C.L.A. description to model computational activity, and have allowed preemption in task scheduling. Two important results are derived in [MUNT 70]. The first is the equivalence of Preemptive Scheduling and General Scheduling. Preemptive Scheduling is a scheduling discipline where a processor, instead of working continuously on a task once assigned to it, can be interrupted and assigned to another task. General Scheduling is a discipline where a fraction of a processor can be assigned to a task, and this fraction varied. The equivalence of these two disciplines is used in the implementation of the modelling system put forward in this thesis.

The second result is the statement and proof of an algorithm for the optimal scheduling of free-structured computations.

Another paper concerned with scheduling in multiprocessor systems is that of J. L. Rosenfeld [ROSE 69]. In this paper, execution of a certain type of program by N identical processors is simulated, and it is shown that with proper programming the solution time approaches 1/N of the single processor solution time.

Further results in this area of research can be found in: [BOWD 69, RAMA 72, SCHW 61, REIT 68, AOKI 63, KATZ 66, GOSD 66, GRAH 66].

The work described above is concerned mostly with scheduling to meet timing constraints. Another body of work deals with scheduling resources in a statistical demand environment, where it is the average behaviour of the system which is of interest. Typically this research has often centred on the response of time-sharing systems, and makes use of queuing theory in many of the results. A well known study of this type, augmented by simulation is that of A. L. Scherr [SCHE 67].

Detailed research has also been undertaken on the behaviour of specific devices. For example, the behaviour of the IEM 2314 disc is the subject of a paper by Abate, Dubner and Weinburg [ABAT 68], and drum scheduling has been investigated by Fuller [FULL 72]. Frank [FRAN 69] has also performed a more general study of disc usage in time sharing systems.

Markovian models have been used to study computational systems and resource usage within them. An example is the paper by J. D. Foley [FOLE 67] on the University of Michigan executive system. The executive is considered to have nine states and transition probabilities between them are provided

from experimental observation of the Michigan system. Results are obtained for the fraction of time spent by the executive in any state, and the effect of changes to the system.

Simulation has been a widely used tool in examining computer behaviour. In particular it is often used to see how well theoretical models predict the behaviour of real systems, and so determine their validity. In most cases the models have been of unique systems, for example [NIEL 66], and consequently the results have not been easily applicable to other situations.

An example which suffers less than most from this disadvantage is B. Randall's paper [RAND 69] on storage fragmentation. Here external fragmentation is defined as the loss in storage utilization caused by the inability to make use of all available storage after it has been fragmented into a large number of separate blocks, and internal fragmentation is the loss of utilization caused by rounding up a request for storage rather than allocating only the exact number of words required. A number of simulation experiments are used to show that rounding up requests for storage, to reduce the number of different sizes of blocks co-existing in the storage, causes more loss of storage by increased internal fragmentation than is saved by decreased external fragmentation. A method of segment allocation and an accompanying technique for segment addressing which take advantage of this result are then derived.

Space does not permit us to list the numerous papers which describe specific simulations, but more general discussions can

be found in: [ZEIG 72, HUTC 65, WEBE 64, NIEL 67, PARN 69B].

Some important results which are applicable to models of computation have been derived by G. F. Newell and W. J. Gordon in the area of queueing theory [NEWE 67A, 67B]. In the first of these papers closed queueing systems are considered. These are characterized by having N customers and M stages each with r, parallel exponential servers of the same mean service rate. Such closed systems are shown to be stochastically equivalent to open systems in which the number of customers cannot exceed N, and equilibrium equations for the joint probability distribution of customers are derived. In the second paper closed cyclic queueing systems with restricted queue lengths are shown to be equivalent to open systems in which the number of customers is a random variable. The differential-difference equations for the time-dependent stochastic structure of the system are derived, and solutions given for a number of special cases.

Queueing theory has been applied to time-sharing systems and related computing situations by L. Kleinrock in a number of papers: [KLEI 66, 67, 68, 70B, 71, 72]. In the first of these papers [KLEI 66] a group of processors is considered to act in sequence on subsets of data belonging to a problem. Such a chain of sequential processing machines (SPM) has been described in [AOKI 63]. Kleinrock shows that the system may be viewed as a cyclic queue, and gives results for the case of two sequential processing stages, where their intermediate buffer is of arbitrary size. Assuming exponentially distributed service times for timeslices of subset processing, the ratio of

expected time to process n subsets by the SPM system and a single processor is derived. An approximation is then derived for an SPM system with 2<sup>p</sup> processors by applying the previous result to pairs of processors, each of which represents a pair of processors, p times.

In [KLEI 67] time-shared computer systems are treated as queueing systems, where the time sharing effect is obtained by giving each request a timeslice Q of processor time and then requeueing it. Results are given for the expected time a request spends in the system by applying queueing theory to the case for which  $Q \longrightarrow 0$ . These are extended to include systems in which requests belong to priority groups which determine the size of their timeslice.

In [KLEI 68] time-shared systems with M consoles are analysed and results given for the behaviour of the normalized average response time. Consoles are again serviced in a timeslicing fashion and after completion of a request, delay for an exponentially distributed think time before requesting service again. A definition of system saturation is given, and the original system is considered as a special case of the class of systems in which the Nth class consists of N processors with capacity 1/N of the original processor and serving M/N consoles each.

Scheduling algorithms for time-shared systems are the subject of [KLEI 70B], and further results for response time are given in [KLEI 71]. In [KLEI 72] the application of queueing theory as  $Q \longrightarrow O$  is again used to provide results for the class of algorithms where the scheduling discipline may change as a function of the accumulated service. In

particular solutions are given for the average response time as a function of the service required by a request.

Further results on aspects of time sharing are given in the following papers: [FIFE 66, LASS 69, LEWI 71, NAKA 71, NIEL 67, RAMA 72, RASC 70, SHEM 67, SMIT 66, STIM 69] which are only a selection of the large body of research in this field.

### 2.3 Computer Networks.

Perhaps the earliest attempt to interconnect a large number of computers was the SAGE (Semi-Automatic Ground Environment) air defence system[EVER 57, MART 69]. This system, developed by the military to collect, analyze and display radar data from sensors scattered over the continent, became operational in 1958 and has subsequently been improved. At about the same time the American Airlines SABRE Reservation System [PLUG 61, EVAN 67] was being developed on a commercial basis. Due to the success of this system, similar systems are now in use by other airlines, hotels, etc. The Ticketron real-time reservation system [DUBN 70] is one such example.

The need by the military for improved data communications led to the development of the AUTODIN (Automatic Digital Network) Communications System in 1963 [HAMS 68, MILL 68]. This system utilized both line switching and message switching facilities and its design was influenced heavily by network survivability and vulnerability considerations. In contrast to military requirements for ultra-reliability, many commercial and experimental networks have relied upon simple interconnections or dial-up telephone lines for communications. Examples of such systems are the Chrysler Message Switching system [ISSA 68], the Rio Grande Railroad Message Switching Transportation System [DAY 68], the Control Data Corporation Cybernet and Kronos Systems [GAIN 71], and the DATRAN (Data Transmission Company) common-carrier network [BINA 71, FISH 71, GAIN 71].

Several networks have been designed using a central store-and-forward message switch which reduces the network cost.

The network topology for this type of design takes the form of the classic Star network. Examples of such networks are the COINS (Community On-Line Intelligence Network System) and the Lawrence Radiation Laboratory OCTOPUS System.

The Lawrence Radiation Laboratory network was called OCTOPUS due to its star-like topology. The central computer is a PDP-6 which serves as a store-and-forward switch between the large processors such as CDC 6600, 7600, and STAR, as well as the IEM Stretch and 360/91 computers. The central switch also provides access to the huge photo-store mass memory by any of the other machines, and allows an evolutionary growth of the multi-computer complex since new computers can be connected to the system resources and can gradually be brought up to operational status.

The third star network is the IEM computer network, NETWORK/440, which has several unusual features [MCKA 71A]. The central node was initially to be a medium size 360/50 computer, but was later changed to be a partition in the large 360/91, which serves not only as a store-and-forward switch, but also as a master operating system. The network consists of several IEM 360 computers and a Control Data 6600 computer, the latter being connected via a small Honeywell DDP-516 preprocessor. The non-IEM machine introduces a degree of generality into the network due to the considerable difference in the CDC and IEM architecture and data structures.

In 1964 the Rand Corporation completed a comprehensive study, "On Distributed Communications" [BARA 64A, BOEH 64, SMIT 64], and a proposal for a distributed store-and-forward

message switched digital network. Although Rand's system was never implemented, their approach has influenced the design philosophy of some military networks and the ARPA Computer Network. During the study, Baran was responsible for the definition of a "packet" and for the "hot potato routing algorithm."

In 1966 Lichtenberger [LICH 66] proposed a network of identical computers; however, this network was only partially implemented. Also in 1966, an experiment was conducted by interconnecting the TX-2 computer at the Lincoln Laboratory and the Q-32 computer at System Development Corporation to test the basic philosophy of a network connection. This experiment showed that resource sharing was possible between two computer systems.

In 1967 the National Physical Laboratory (NPL) in England made a comprehensive proposal [DAVI 67] for a general purpose store-and-forward network. The NPL network was to be a store-and-forward network using interface computers and 1.5 Mb/sec. transmission lines for the message switching net, with an expected network response time (the time from the receipt of a packet to the beginning of the output at the destination) of less than 100msec. Packets were defined as any multiple of 128 bit segments up to a maximum of 1024 bits. Details of the proposed network operation appeared a year later [BART 68, DAVI 68, SCAN 68, WILK 68]. To date, only one node has been implemented and can be described as a multiaccess computer system controlled by a time-sharing computer [BARB 69, SCAN 69, WILK 69]. The authors have so far concentrated on the local rather than trunk level.

A small experimental computer network is being developed at Carnegie Mellon University, consisting of two DEC PDP-10 computers, a pair of PDP-8 minicomputers, and a hybrid computer. All five computers are located together and since the communications costs are insignificant, experiments with completely connected nets as well as with more typical network interconnection topologies have been planned.

In 1968 the Advanced Research Projects Agency released a Request for Quotation to construct a store-and-forward computer The contract was awarded to Bolt, Beranek and Newman, Inc. located in Cambridge, Massachusetts. The basic ARPA Network community consists of about 26 ARPA-sponsored research sites. Some of these sites have areas of specialization such as the graphics work at the University of Utah, picture processing at the University of Southern California, the man-machine interactive work at System Development Corporation, the text editing and information retrieval work at Stanford Research Institute and the network measurement and modelling work at UCLA. Other sites have specialized hardware capability such as the ILLIAC IV computer and the trillion bit laser memory.

Figure 2-1 shows the configuration of the ARPA Computer Network. The various sites (HOSTS) are interconnected via a distributed message switching communication net consisting of IMPs (Interface Message Processors) and dedicated 50 kbit/sec. full duplex communication lines. Each site typically consists of one or more computers, called HOSTs, operating in a timeshared environment, but

Figure 2-1 The ARPA Computer Network as of May 1972.

range in size from a TIP (a terminal IMP) to the ILLIAC IV. Two series of papers presented at Spring Joint Computer Conferences [CARR 70, CROC 72, FRAN 70, FRAN 72, HEAR 70, KLEI 70A, ORNS 72, ROBE 70, ROBE 72, THOM 72] discuss the design, performance and operational aspects of the network.

The problems of message delay, nodal storage requirements and the network routing strategy are some of the more interesting aspects of such a network from a modelling, analysis and operational viewpoint. Once the node locations are given, the network topology is influenced by the required system reliability, by projected user traffic requirements, nodal processing speeds, and total dollar cost allowed for the construction of the network. Then a protocol for passing messages between the nodes must be chosen and the nodal processing programs designed.

Another problem is the specification of an operating system communication protocol which allows for the establishment of a connection between HOST computers [CARR 70]. This task is handled by the NCP (Network Control Process) which is generally a part of a HOST's executive program. Progresses located within a HOST communicate with the network through the NCP.

Finally, a higher level of protocol is needed when a high degree of interaction is required between a user and a particular subsystem in a foreign HOST. This requires the development of interprocess communication techniques; for example, file transfer techniques, communication between dissimilar graphics stations, remote job entry, and interactive terminals.

In the assessment of performance of a general store-andforward computer-communication network, it is necessary to examine the assignment of channel capacities, the effect of queue discipline, choice of the message routing procedures, nodal processing delays, nodal storage requirements, and the design of the network topology. A network performance measure is required to determine how various choices of the above parameters affect performance.

There are basically two classes of performance measures. The first class does not relate in any simple way to individual messages in the network, but rather to the performance of particular components that compose the network. Examples of such performance measures are: average channel utilization, nodal storage utilization, and channel error rates. Many of these performance measures can be computed analytically. The second class of performance measures relates more directly to individual messages. An example of such a performance measure is the average message delay. This provides a measure of system response which may be directly observed and which can be estimated. L. Kleinrock has investigated the minimization of this measure under various constraints in [KLEI 64]. Amongst other results the use of an "independence assumption" was shown to allow analytic solution for the optimal channel capacities in store-andforward communication nets. A further description of this work is given in Chapter V.

One of the problems of current design is the application of general theories to the analysis and design of store-and-forward computer-communication networks.

Four main problems in these networks are construction of models to predict message delay, message routing strategies, channel capacity assignments, and topological design of networks.

All these are dealt with to greater or lesser degree in [KLEI 64]. This work is further developed in [KLEI 69A and 69B] in which exact and approximate analysis, simulation, and measurement are compared to obtain results for networks of the ARPA type. The discussion is carried further in [KLEI 70A] and [FULT 71, 72].

Routing procedures have been investigated from various approaches. Prosser [PROS 62A], Kleinrock [KLEI 64], Shapiro [SHAP 66] and Benes [BENE 66] have examined the effect of random routing procedures on message delay. Their conclusions were that random routing techniques are highly inefficient in terms of message delay, but are relatively unaffected by small perturbations in traffic intensity or network structure. Boehm and Baran [BOEH 64] and Smith [SMIT 64], Boehm and Mobley [BOEH 66], Kahn and Teitelman [TEIT 69] and Kleinrock [KLEI 70A] have examined some stochastic computing techniques. Deterministic routing procedures have been investigated by Prosser [PROS 62B], Boehm and Mobley [BOEH 66], and Kleinrock [KLEI 69A]. Their approaches have been slightly different. Prosser gave an approximate analysis of directory procedures which showed an increase in efficiency and amount of data transfer as compared to random routing, but at the expense of maintaining the directory. Kleinrock has computed average message delay as a function of traffic intensity for a fixed network topology and fixed routing procedures. Boehm and Mobley considered the problem of

computing a fixed routing procedure from estimates of network delay.

The topological design of ARPA-like computer-communication networks has been attacked by the Network Analysis Corporation [FRAN 70, NAC 70A-B, NAC 71A-B]. Their procedure is derived from a natural gas pipeline study [FRAN 69]. In their procedure, both the network topology and channel capacity assignments are varied during the optimization, while the routing procedure is essentially held fixed (it is deterministic for a given network topology). Since this problem defies a precise solution, their results must be viewed as giving good, but not necessarily optimal, network realizations.

Implicit in the optimal design of a network is the network performance function. For most network design problems average message delay has been selected because it is mathematically tractable, because it represents the global performance of such networks, and because it can be measured. Meister, Mueller and Rudin [MEIS 72] considered a slightly different performance measure: a weighted sum of powers of the average message delay in each channel. From this performance measure, they are able to obtain a channel capacity assignment for fixed routing which reduces the variation in delay from channel to channel at the expense of only a moderate increase in average message delay. This technique reduces the delay markedly on lightly utilized channels where, as the authors state, the user would be very much aware of this decrease when using the network.

Measurement of the behaviour of the ARPA network is the subject of [COLE 71]. A measurement collection system is

described and implemented, and data accumulated by observing normal and artificially generated traffic is analysed. J. F. Zeigler [ZEIG 71] has investigated nodal blocking in ARPA-like networks with the aid of a two-state Markov process model. Results for the fraction of blocked nodes in a network are given, and developed for "clumps" of adjacent blocked nodes.

A further effort in computer networks based on the ALOHA system [ABRA 70] is the current examination of satellite communications as a means of extending the ARPA network. Their use, particularly in broadcast mode, is the subject of a series of ARPANET Satellite System Notes. In Note 12 [ASSN 72] L. Kleinrock and S. S. Llam derive expressions for channel efficiency and expected number of retransmissions. In the system analysed simultaneous, or overlapping, broadcasting is regarded as failure of transmission for both messages, which are retransmitted after a stochastic delay.

A study is currently taking place of methods of providing a computer network for a number of Canadian Universities. A first stage in the study is described in [DEME 72A and 72B] by J. DeMercado. These reports deal with the synthesis of minimum cost networks in which either simultaneous or timeshared transmission occurs.

Some interesting papers on computer networks are to be found in the proceedings of the ACM/IEEE Second Symposium on Problems in the Optimization of Data Communication Systems, October, 1971. The ARPA network is the subject of two papers. The first is by G. D. Cole, which is materially similar to [COLE 71], and the second is by R. E. Kahn and W. R. Crowther

on flow control [KAHN 71A]. In this paper the authors describe the various types of storage deadlock which can occur in the ARPA network and present the precautions which were taken against such occurences.

There are also two papers on the NPL network in the proceedings. The first also deals with congestion and proposes an "isorithmic" solution [OAVI 71]. That is to say that there should be a fixed number of packets in the network at all times, whether or not they carry data. The second paper describes various levels of protocols to be used in the NPL network for computer-to-computer communication, [SCAN 71].

A description of Tymshare Inc.'s TYMNET system and its history is given in [BEER 71], while reliability in centralized networks is the subject of [HANS 71]. Two papers in the proceedings deal with distinct loop-type networks. In [HAYE 71] results are given for mean message delay and other characteristics, and confirmed by simulation. In [SPRA 71] loops consisting of a central processor and a number of terminals are analysed and parameters obtained for the variation in terminal message delay with terminal loop position. Error control is the subject of [TRAF 71], which deals with computerto-computer links involving transmission via satellite.

Current developments in the design and operation of computer networks are described in a number of papers presented at the First International Conference on Computer Communications, 1972. In [ANSL 72] methods of data transmission used by the British Overseas Airways Corporation are surveyed, and in [BARB, 72] an outline is given of a project for a European

network initially linking research establishments in France, Italy, Switzerland and the United Kingdom. Methods of operation and maintenance in the ARPA network are the subject of [MCKE 72]. In this paper the detection and diagnosis of network faults by the HOST computer at the Network Control Centre are described. The Centre has the function of receiving IMP situation reports, determining the actual state of the network, and initiating repair activity when appropriate.

In [WHIT 72] V. Kevin Moore Whitney has compared various algorithms which have been used to obtain (heuristically) least cost network topologies. The same networks are submitted for solution by each algorithm and resultant topologies compared. The comparisons are shown to be remarkably consistent, and demonstrate some advantages of the Steepest Ascent Hill Climbing (SAHC) algorithm.

The operation of a network under conditions of saturation is discussed in [DESP 72], and network characteristics for such operations are presented. The performance of satellites for network data transmission is described in [HUST 72] and figures for both performance objectives and measured performance are given. Data management in networks is the subject of [FARB 72 and BOOT 72] in which the problems of safeguarding, accessing and updating dispersed data by equally dispersed users are discussed. Finally a survey of European network development is given in [KIRS 72] which describes current ventures by universities, research establishments, post offices, together with those of some industrial and commercial concerns. In view of the extensive material available, we have added a section on computer network design to the bibliography in Appendix I.

CHAPTER III

THEORY

.

• \*

۰

· 🗸 .

## 3.1 Graphical representation of hardware and software.

For the sake of descriptive convenience in the material below we define the terms <u>team</u> and <u>net</u> as follows: a team is defined as a set of interdependent cooperating programs executing concurrently in real time to perform some welldefined function. A net is any collection of hardware modules, i.e. processors, memories, peripherals, I/O controllers, message switchers, connected by data channels. A net can of course be one computer or many, and generally exhibits the properties of hardware-sharing, function dispersal, and concurrency of operation.

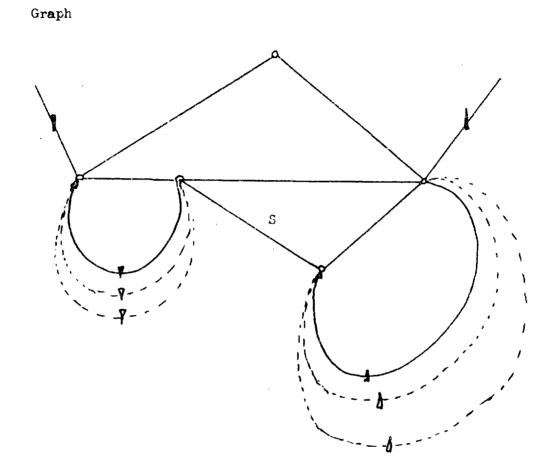

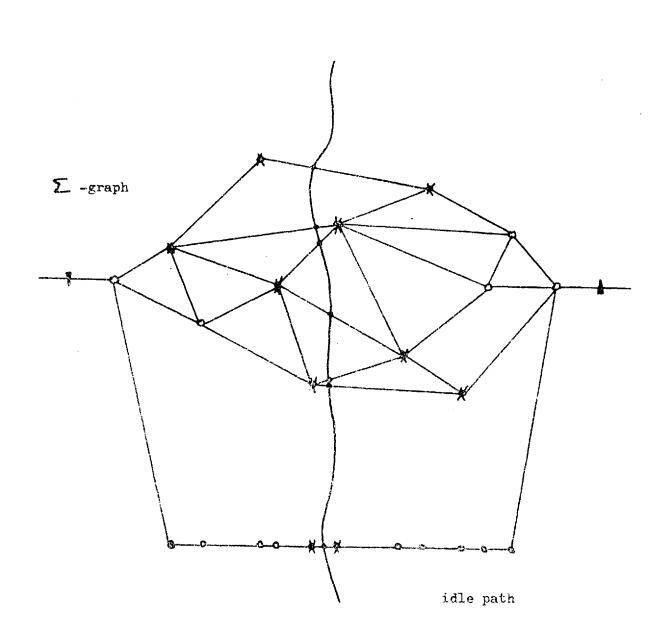

A team can be represented as a directed graph  $\Sigma$ , whose arcs represent the execution of individual sub-programs, and whose nodes represent events where the subprograms interact. Such interaction may be simultaneous completion or initiation of subprograms, or communication of information between two or more subprograms. Processing within an arc is considered logically independent of that within other arcs. That is to say that all interaction between subprograms which is implicit in the intrinsic logic of the overall task occurs only at the nodes. This does not imply that the arcs themselves are purely sequential programs; further, there may be interaction between them because of hardware allocation constraints in the net.

The word <u>processor</u> will be used in the following to denote any hardware module which performs a transformation and/or movement of data. This includes devices such as I/O controllers, multiplexors, regenerators, and so on. In this sense a processor need not possess the full set of functions of a general purpose

computer. Consequently not all processors will be able to execute all programs. A processor P can be regarded as a hardware operator on data. Each arc of a team  $\Sigma$  is a subprogram S executed by some hardware module of the net on which  $\Sigma$ executes. We define <u>regular</u> execution of a team to be execution where hardware allocation only changes at the nodes of  $\Sigma$ . Running programs to completion is regular execution, hardware sharing is not. Transmission of data, without any transformation, may be regarded as processing by an identity processor  $P_{I}$ . Storage of data for a period of time can be regarded as processing by the null processor  $\overline{\Phi}$ .

We now consider an aspect of modelling which might be termed focusing. In constructing any model, a decision must be made as to what level of detail the model will reach. The situation is analogous to choosing the degree of magnification appropriate when using a microscope. Too small a magnification may not show the process of interest, too large a magnification may make it impossible to view the entire process or obscure it with irrelevant detail. For convenience the level of detail a model reaches will be called its depth. When the depth of a model is chosen, this is in effect a decision to treat all objects below that level as black box or quantal ones (if not, then there would be a further level of detail below the chosen depth, which is a contradiction in terms). However this choice is imposed by the model builder; objects at the model depth are of course structured in reality. Consequently the choice of model depth is in effect a decision to ignore (or a cut-off point for) the appropriate fine structure.

In terms of the foregoing, we suggest that graphical representation of a team can be used for modelling computer activity at any depth from the execution of a single machine instruction (which can be regarded as a team of microprograms) to considering entire computers as quantal objects. If we have a graph  $\Sigma$  representing some task performed by a team, we are implicitly deciding to treat the members of the team (arcs of  $\Sigma$ ) as black box processes, since we stipulate that logical interaction between the members occurs only at nodes of  $\Sigma$ . That is to say, we are interested in the change in system state caused by the execution of an arc, but not concerned with the interactions occurring within the execution of an arc.

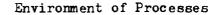

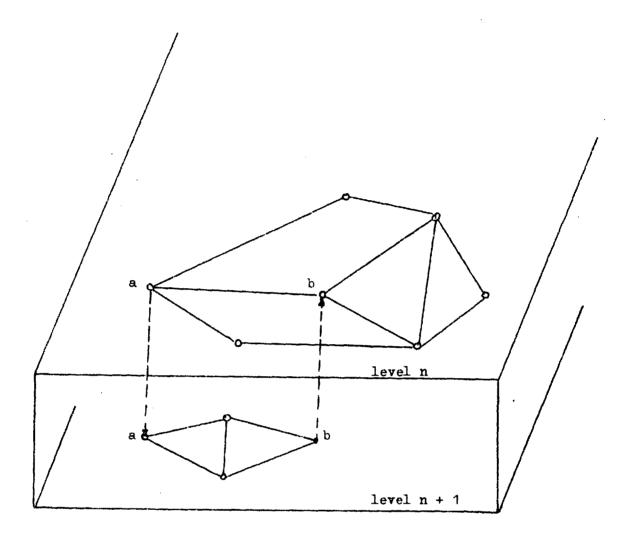

We can of course include this level of interaction if desired, by replacing each arc S of  $\Sigma$  by a <u>subgraph</u>  $\sigma$  of processes, at the next (convenient) level of detail down, which perform the function previously represented by the single arc S. We use the word subgraph here to mean a graph representing the structure of a single arc of another graph (at a higher level) rather than in the normal graph theoretic meaning of a subset of graph elements.

It may be that certain arcs of  $\Sigma$  are of critical interest. In this case a more detailed picture may be obtained by replacing only the arcs concerned by subgraphs, while leaving the rest of  $\Sigma$  as before. Thus the graphical representation is recursive in the sense that any arc may be replaced by a subgraph. If the graph  $\Sigma$  and its attributes are considered as a named data structure, then the name of an arc of  $\Sigma$  may be an element, or the name of a further data structure, i.e. a subgraph. If we envisage a procedure A performing analysis,

Graph  ${\bf Z}$

Fig. 3-1 Relationship of graph and subgraph.

or other processing, of  $\Sigma$ , then an individual arc of  $\Sigma$  may undergo the same analysis by recursive call to A, if the structure of the appropriate subgraph is available.

The progress of a team towards completion can be regarded as the execution of arcs of  $\Sigma$  by processors allotted to them by a control algorithm. The time taken to execute an arc will depend on the computing power of the allotted hardware relative to the subtask represented by the arc, and also on whether the execution is regular. Changing the control algorithm is the equivalent of varying the allocation strategy of the model, but not its structure. Finally, by representation as a team, a control algorithm is itself amenable to the same modelling.

Normal Critical Path concepts apply here, in determining overall execution time for a team, and in detection of a critical path. A cost function can be associated with the net resources, such as processors and memories, allotted to arcs. Slack time represents the time between an arc S completing execution, and the interaction of its results with the rest of the team. This is effectively storage of such results until all arcs which interact with S at its terminal node have completed. Thus slack time has an associated cost for information storage. Overall Completion time for  $\Sigma$  can be decreased by allocation of more powerful processors on critical arcs. This clearly raises the cost unless overhead and idle time created by such action are nonexistent.

We now develope the idea of hardware/software correspondence. This is based on the following premise: any function that can be done by software can also be done by hardware, and vice versa.

We add the proviso that obviously there must always be some quantal level of hardware present, else the function would never be physically executed. This is equivalent to saying that all computing activity is performed by a combination of hardware and software, and that the partition of the task between them is an arbitrary one; further, that this partitioning can be made at any level or part of the function, by building appropriate hardware. An extreme case is the performance of some task entirely by special purpose hardware, which is equivalent to reducing the software èlement to a single instruction. We suggest that the distinction between hardware and software is an artificial and fluid one. Consequently, in developing a model of computing activity we are concerned that it should take into account various possible hardware/ software decompositions of the activity.

We now propose a graphical representation of a net, and consider under what circumstances it may be regarded as the dual of the team representation outlined above. A graph  $\mathbf{T}$ will be considered a model of a net in the following way. Each node of  $\mathbf{T}$  will correspond to a storage element of the net. Each arc will represent a possible data flow through a processor P between such storage elements. We make the remark that a processor P may be able to connect itself across more than one pair of nodes. Thus there will be an arc in  $\mathbf{T}$  for every possible connection that P can make between a pair of memory elements, but at any instant there will be a flow on only one of these arcs. If P is  $P_{I}$ , the identity processor, then no transformation on the data flow will occur.

In the graph  $\mathbf{T}$  traversal of an arc P may be regarded as the execution of some program by the processor P, taking input data and status from the initial node (memory element) and producing output data and status at the terminal node. Regular execution on an arc P of the graph  $\mathbf{T}$  occurs if the program being executed by P remains attached to the arc for the period of time necessary for it to run to completion. For example paging is not regular execution. The previous remarks on model depth and the recursive properties of graphical representation apply equally to the graph  $\mathbf{T}$ , except that in this case a subgraph p represents, not subprograms, but sub-processors; the subgraph p must have the functional capability previously represented by the arc P.