## A DIGITAL SYSTEM DÉSIGN LANGUAGE

This thesis is submitted to the Department of Computing and Control at the Imperial College of Science and Technology, University of London, in fulfillment of the requirements for the degree of Doctor of Philosophy.

B. Shahdad, July 1974

#### ABSTRACT

Digital systems may be viewed at different descriptive levels: at the higher levels the designer is mainly concerned with the behaviour of the system; at the lower levels with the behaviour of its components and the way they are connected, i.e. the system structure.

The design of a system is thought of as involving several steps, each of which is concerned with the transfer of the system description from a particular level to a neighbouring one.

Among the design media being employed are natural languages, block diagrams, logical equations, and combinations of these. This thesis introduces a high level language to serve as a single medium throughout the design process. This approach, as well as providing a formal medium of communication, enables us to develop a processor for the Language which can simulate the behaviour of the system at each design step, before it is implemented in hardware. With regard to this application, the new problems in the implementation of the Language, as compared with conventional programming languages, are also investigated.

#### ACKNOWLEDGEMENTS

The work reported here was carried out under the supervision of Professor D.J. Howarth, to whom I am very grateful for his encouragement throughout the project.

The work was begun at the Institute of Computer Science in February 1972, following the closure of which, in September 1973, it was continued at the Imperial College of Science and Technology. The project was supported by a CENTO scholarship made available to the author through the efficient service of the British Council.

I would like to express my gratitude to Mr. I.H. Gould for constructive suggestions made in many discussions with Professor Howarth and the author. Thanks are also due to Mr. D.R. Brough for his comments on the implementation of the Language, and to Mr. C.T. Burton for his help in editing the manuscript.

The author has been on leave from Arya-Mehr University, Teheran, Iran.

# CONTENTS

|                            | Abstract    |                                        | 2.  |

|----------------------------|-------------|----------------------------------------|-----|

|                            | Acknowledge | ements                                 | 3.  |

|                            | Contents    |                                        | 4.  |

|                            | Chapter I   | Introduction                           | 9.  |

|                            | 1.          | The Digital Description System         |     |

|                            | 2.          | Applications                           |     |

|                            | 3.          | The Process of Design                  |     |

| •                          | 4.          | Levels of Description                  |     |

| •                          | 5.          | The Requirements of the Language       |     |

|                            | 6.          | General Considerations                 |     |

| ¢                          | 7.          | Plan of the Thesis                     |     |

| ي.مر<br>الم ميم .<br>م م . | Chapter II  | The Level of Logic Elements            | 18. |

|                            | 1.          | Introduction                           |     |

|                            | 2.          | Boolean and Integer Constants          |     |

|                            | 3.          | Primitive Elements                     |     |

|                            | 4.          | Graphic Description                    |     |

|                            | 5.          | Symbolic Description                   |     |

|                            | 6.          | same and delay Elements                |     |

|                            | 7.          | Connectivity                           |     |

|                            | 8.          | Networks                               |     |

|                            | 9.          | Symbolic Description of a <u>delay</u> |     |

|                            | 10.         | Sequential and Parallel Operations     |     |

|                            | 11.         | Ordering the Operations                |     |

|                            | 12.         | Terminal Registers                     |     |

|                            |             |                                        |     |

- 1. Introduction

- 2. Representation of Boolean Constants

- 3. The unknown Value

- 4. Arrays

- 5. Constants

- 6. Array Operations

- 7. Expressions

- 8. RT-operations

## Chapter IV The Control Level

- 1. Introduction

- 2. Parallel Networks

3. Sequential Networks

4. Controlled Networks

5. General Networks

6. Systems

7. Implementation of General Networks

· 8. Higher Level Control Structures

9. An Example of Design

Chapter V

#### Miscellaneous Extensions

1. Introduction

2. Logic Elements with Time Delay

3. System-defined Elements

- 4. Element Definition

- 5. Simulation Facilities

6. Input/Output Facilities

7. An Overall View of a Description

44.

64.

- 1. Introduction

- 2. The Choice of the Implementation Language

- 3. Major Strategies

- 4. Linking the Modules

- 5. Declaration of Modules

- 6. Referencing the Modules

- 7. Determination of the Base Address

- 8. The Virtual Stores

- 9. Declarations

- 10. The System Body

- 11. RT-operations

- 12. Considerations Concerning the delay Element

- 13. Delayed Boolean Operators

- 14. Element Designators

- 15. The <u>for</u> Structure

- 16. The Implementation Work

Chapter VII Concluding Remarks

- 1. An Overall View

- 2. Other Design Languages

- 3. Use of Programming Languages

- 4. Formal Description

- 5. Simulation

- 6. Scheduled Event Simulators

- 7. Design Automation

- **1.** Introduction

- 2. General Description

- 3. Effective Address Generation

- 4. Instructions

- 5. The System

- 6. Conclusion

Appendix B The Implementation Language

6

1. Introduction

2. General Description

3. The BCL Sequencing Mechanism

4. Format Handling

5. Repeated Elements

\_\_\_\_ Effectiveness for Semantic Analysis

7. Representation of Data Structures

- 8. The Scope of Variables

- 9. Concluding Remarks

Appendix C Definition of the Syntax

- 1. Constants

- 2. Variables

- 3. Expressions

4. RT-operations

5. Sequential and Parallel Networks

6. The <u>if</u> Structure

7. The for Structure

8. The case Structure

9. Loop Structures

10. Miscellaneous Structures

137.

152.

- 11. Systems

- 12. Declarations

- 13. User-defined Elements

References

#### CHAPTER I

#### Introduction

Digital systems serve for a variety of purposes: the field of computer systems alone gives a great importance to the study of their design.

The designers of digital systems have long been in search of suitable means of presenting the methods and products of their designs. English descriptions, lacking as they do precision, concision, and clarity, were soon replaced by block diagrams, which have the advantage of a certain correspondence to the physical configuration of the system. An alternative language was suggested by the application of Boolean algebra to network-simplification, and logical equations have been used, both alone, and in combination with block diagrams. The relative merits of the two methods have been the subject of several discussions and papers [9,30,46].

The use of flowcharts, which are capable of describing the sequencing and operation of systems, has been suggested and design problems have been presented for which this method is effective [38].

In general, the designer might use a combination of these or other languages in his design: a state diagram might present the initial statement of the problem; the notation of logical equations might serve to observe certain design restrictions and simplify the system; the final solution might be presented in the form of a block diagram.

It is desirable to abstract from these languages the features which are pertinent to the design process, to obtain a single language which could serve as the design medium throughout.

This thesis is concerned with the investigation of the required features of such a language. In recent years several attempts in various directions have been made to evaluate the effectiveness of this approach, e.g. [39,14,5]. Due to their diversity - embracing the fields of digital system design, language design, translator writing, and simulation - and their lack of established terminology, we review them, in our final chapter, in the context of the terminology and conceptual framework of this thesis.

In this chapter we first expand the idea of a high level digital system design language to define what is called the Digital Description System; the purposes for which the Description System could serve are considered, and the requirements of the corresponding Description Language are set out in relation to the multi-level structure of digital systems, and the process of their design; finally we mention characteristics of digital computer systems affecting simulation.

## . The Digital Description System

The Description System is composed of three components: the Description Language, which is the notation in which the user describes his design; a simulator which simulates the behaviour of the system described; and a compiler which can be regarded as an interface between the first two components. The compiler accepts the source description and produces an object description which is acceptable to an object machine. The simulator among other things interprets the object code.

### 2. Applications

The Description System could serve for three kinds of purposes:

a) It could provide a medium of communication in the same way that programming languages have been used to express computational processes. Such a description is formal, concise, precise, and expressive.

- b) The simulator could assist the designer in ensuring the proper working of the system, in investigating its behaviour, and in improving the design before it takes a hardware form. Once the design has been approved, information for assembling the hardware could be derived from the description, with obvious saving in design time and cost. Also effects of mulfunctions in any part of the system could be simulated and investigated.

- c) The Description Language could conceptually help the designer in his creative work by offering facilities which encourage him to take a systematic approach in his design; this is further discussed in ensuing sections.

## 3. The Process of Design

In designing the Language we have had in mind the design process, known as the 'stepwise refinement method', which recently has been considered in the design of programs [58].

According to this process the designer begins with the problem statement, i.e. the specification of the 'component' to be designed. The design task involves several steps. In each step the design of a component is refined, that is, the solution is expressed in terms of the design of sub-components of a lower degree of complexity. This is achieved by decomposing the complex operations into simpler ones, and refining the representation of data into more primitive forms. This process is continued, directing progress toward a level whose 'primitive components', i.e. the components forming the solution, are available to the designer, thus accomplishing the design task. The primitive components of this final level are also referred to as 'primitive elements'. A component designed in this manner might become part of a more complex system.

## 3.1 The Design Tree

As pointed out in [35] one can imagine a design tree whose root,  $P_0$ , represents the initial statement of the problem; the leaves of this tree correspond to possible solutions to the problem; each level of the tree contains all the possible refinements of the previous level.

Po

P1: possible refinements of P0

P<sub>2</sub>: possible refinements of P<sub>1</sub>

possible solutions

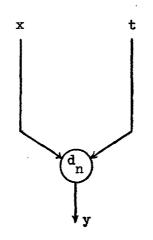

Figure 1. The design tree

In each refinement step the designer, on the basis of certain design criteria, makes design decisions which take him to a node belonging to the next design level.

It may well happen that after reaching a level the designer wishes to reconsider the decisions made at a previous level, and to select an alternative design route. Similarly, the designer might make a choice on the basis of looking ahead one or two levels. An example of trade-offs between various design decisions in the design of a multiplier, leading to several solutions, can be seen in [6].

#### 3.2 Features of this Method of Design

This approach toward design has the following features:

Firstly, the correctness of the design can be ensured at each level so that ideally the final design product is free of logical errors.

Secondly, the design product is accompanied by a design history which shows the decisions made and the reasons for them. While the solution at the final level is suitable for implementation, it obscures the architecture of the design due to too much detail. Intermediate solutions, which are presented at higher levels, aid comprehension of the way the final product has been developed.

Finally, from the documentation viewpoint, if a change is made to the system at a certain level, only the descriptions at lower levels are affected. The nature of the change might be a physical modification or reconsideration of a design decision. Since the design is well documented, modifications and maintenance should prove to be easier.

## 4. Levels of Description

As mentioned earlier a digital system may be described at different levels. At each level the behaviour of the system is defined by the behaviour of its components and the way they are connected, that is the 'system structure'. The lowest level considered here is the one whose primitive components are logic elements, and is therefore referred to as the 'Level of Logic Elements', at which each logic element produces an output signal after performing a certain logical operation on its input signals, possibly (depending on the type of element) with a time delay.

The next higher level is the 'Register Transfer Level', at which a digital system is imagined to be composed of registers connected through blocks of logic elements. Each block performs an operation on the contents of one or more input registers, and places the result in output registers, which may include some of the inputs.

The next higher level is the 'Control Level' where the order in which the operations take place is expressed; an operation may be invoked at a particular step in a sequence of steps, or at a certain time, or in general when certain conditions are satisfied. Such conditions may well be a function of the previous states of the system.

The levels stated above are the important ones. The descriptive levels of digital systems are not rigid or restricted to these; thus it might prove convenient to extract a sub-level from a level, or extend the range of a level. For example, the Control level might be extended to include the instruction level, at which a machine is described in terms of the changes in its states as the result of the execution of each instruction.

At the highest descriptive level a digital system is in general composed of a small number of components, each with a high degree of complexity. As we move downwards, the number of components increases while the degree of complexity of each component decreases. The invariant of this process is the behaviour of the aggregation of the components - i.e. the system.

## 5. The Requirements of the Language

With regard to the purposes for which the Language could serve, the process of design mentioned earlier, and the descriptive levels of digital systems, we state the following requirements for the Description Language.

- a) The same language should be used throughout the design so that the designer need not be obliged to learn several notations (possibly corresponding to different descriptive levels), and so that components of the system described at different levels can interact with each other.

- b) In order for the Language to be used throughout the design, it should have a multi-level structure, and be flexible to the designer's choice of levels.

It should be able to suppress details so that, at a high level, the designer can investigate the overall interaction of a component with the rest of the system, or ignore structural details. Similarly, if a component has already been designed in detail, one should be able to refer to it at a higher level without going into its structural details, and by merely complying with the requirements of the interface.

- c) The concepts on which the Language is based should provide for the description of the complex behaviour of components at a high level, where only a few components are involved, and at the same time for the description of connectivity at a low level where the system is composed of numerous components.

- d) The Language should be equally suitable whether the design approach is top-down, bottom-up, or some combination of the two. From this viewpoint its main concern should be to cater for the design of components in terms of sub-components.

- e) As stated in [57] the required power and flexibility should derive from a unified simplicity rather than the inclusion of integrated

facilities. This should be combined with the Language ability for multi-level description in such a way as to offer the designer a conceptual aid for progressing toward the implementation level, presenting the solution in terms of the pre-defined components which he is likely to have at his disposal.

- f) An ease of expression should be achieved by building into the Description System the abstract behaviour of digital systems. Once the user feels an ease of expression, one of our main objectives, that of creating a medium of communication and a way of documentation, is achieved. For when it is easy to describe, it is easy to read; the description is then self-documented and self-expressive.

- g) One of the important requirements of the Language is to allow the designer to define his own operators and use them in the same manner as the standard operators so that the description is homogeneous. This enables the user to describe his own technology and design his components in terms of this technology.

- h) Finally, the Language should lend itself to implementation so that a simulator can be developed to ensure the proper working of the system at every level, and therefore to raise the designer's degree of confidence in his design.

## 6. General Considerations

The 'model' represented in the computer is in general an approximation to the real digital system. The words, model and system, are used in contrast to each other when one is concerned with those features of the system which are abstracted to obtain the model; otherwise the word, system, refers to both. Using a digital computer for the purpose of simulation implies that the continuous advance of the 'Real Time' in which the digital system runs should be approximated by discrete changes in the variable representing it in the model. This variable is called the 'Simulated Time', or 'time'.

Having only one processor available, the effect of parallelism is created by making available to the receiving component the result of the propagation of parallel signals only after they have all been propagated.

As the simulation process continues the variable know as the 'Computation Time', which corresponds to the computer system used for the purpose of simulation, advances. The following figure shows the correspondence between different systems and Times involved in the process.

| digital system  | <u></u> | Real Time        |

|-----------------|---------|------------------|

| model           | <b></b> | Simulated Time   |

| computer system | <b></b> | Computation Time |

Figure 2. Systems and Times

## 7. <u>Plan of the Thesis</u>

Chapters II, III, and IV of this thesis are concerned, respectively, with the Levels of Logic Elements, Register Transfer, and Control. Chapter V is mainly devoted to the extension of the basic set of operators of the Language, and ways of composition and decomposition of systems in this light. In Chapter VI problems involved in the implementation of the Description System are considered; BCL - the implementation language - is described in Appendix B. Finally, Appendix C gives the syntactic definition of our Language, and Appendix A illustrates its application in presenting a useroriented view of a small computer.

#### CHAPTER II

### The Level of Logic Elements

## 1. Introduction

It is the purpose of this chapter to define the notion of a network, and to study such networks at the Level of Logic Elements. Logic designers often use graphic descriptions to present their design, and we begin by establishing a formal correspondence between this type of description and symbolic notation, since the latter is a more suitable form for computer input, and for representing digital systems at other levels of design.

The notation is then used to introduce and study certain categories of networks, which are regarded here as basic constituent elements of digital systems. Detailed attention is paid to the representation and behaviour of <u>delay</u> elements, from which a suitable notation is developed.

At the same time a theoretical foundation is set up, to form a basis for identifying the requirements of a simulator for the behaviour of digital systems described at this level.

## 2. Boolean and Integer Constants

A Boolean constant is a member of the set

$B = \{ true, false \}$

and an integer constant is a member of the set

$\mathbf{Z} = \{0, -1, 1, -2, 2, \dots\}$

The constant, unknown, is used to indicate an undefined value for a variable.

3. **Primitive Elements**

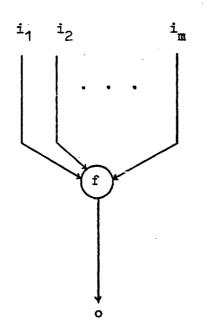

The notion of a 'primitive element' corresponds to a function from the set of its 'input' values into the set of its 'output' values; the element has an arbitrary number of inputs (n), and a single output. The functional form is:

where

$$I: I \to 0$$

$$I = i_1 X i_2 X \dots X i_n, n \ge 1$$

and each  $i_{i}$  is either B or Z; and similarly, O is either B or Z.

'Terminal' is a general word for referring to an input or output. A terminal may take values from an appropriate set of constants. In this respect, we can talk about 'terminal variables'. The value of such a variable is often called a signal; therefore, a signal is either of 'type' Boolean or integer.

#### 3.1 Naming

Terminals may be given names for purpose of reference. Two identical names indicate that their corresponding values are always the same; therefore distinct terminals should be given distinct names.

The whole element may also be given a name, in which case the name is written on the left hand side of its output identifier, separated by a colon (:).

### 4. Graphic Description

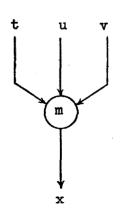

Figure 1 shows graphic description of a primitive element. There are arrows on input and output, pointing towards and out from the centre. If f is a standard function, such as  $\geq$ ,  $\sim$ , +, etc., the corresponding symbol is entered in the circle; otherwise the function name is written. Such a composite function should be described in terms of standard functions.

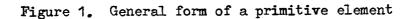

Figure 2. Examples of primitive elements

## 5. Symbolic Description

The symbolic representation of a primitive element is of the form:

$$o = f(i_1, i_2, \dots, i_n);$$

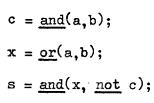

The above form is called a statement. Examples are:

1) w = -v;2) z = +(x,y);3)  $c = \ge (a,b);$

corresponding to the graphic descriptions in Figure 2.

## 6. <u>Same</u> and <u>delay</u> elements

The statement

(1)  $b = \underline{same} a;$

is a symbolic description of the function <u>same</u>, whose output value is always the same as its input value, i.e. it is the identity function. A simpler way to write statement (1) is:

a = b;

The function <u>same</u> may be used to change the name of a signal, in this case from b to a.

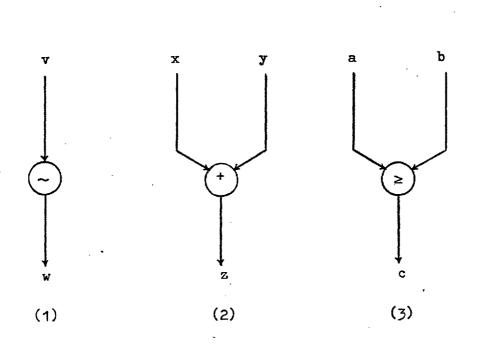

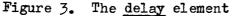

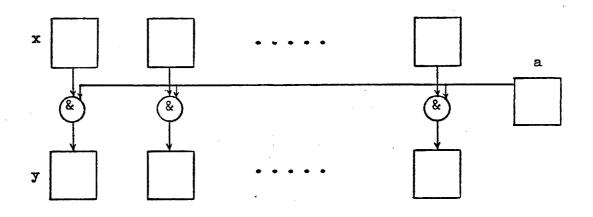

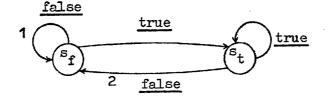

Figure 3 is a description of the <u>delay</u> element. The two input variables are not independent; in fact,

(a) x = f(t)

for the output, we have

(b)

$$y = f(t-n)$$

where  $n \ge 0$  is an integer constant. t is usually referred to as <u>time</u>. Since x = f(t), t need not explicitly be shown.

There are two special cases in which <u>delay</u> behaves like <u>same</u>:

- 1) if n = 0

- 2) if x is a constant. In this case f is a function whose range is a constant, and therefore y = x.

If the function f is not known analytically, the tabulated form is available. Let tabulation points be

(c)

$$t_i = t_{i-1} + 1$$

,  $t_0 = 0$

then

(d)

$$y_{i+n} = f(t_{i+n} - n) = f(t_i) = x_i$$

since according to (d)

$$y_i = x_{i-n}$$

Values enter and leave the buffer on a queue basis, i.e. first in, first out. All  $y_i$ ,  $0 \le i < n$  are <u>unknown</u>. If after  $t = t_i$  no value enters the buffer, those already in will be released at time points

$t_j, i+1 \le j \le i+n$

# 6.1 Functional Form of <u>delay</u>

In order to treat <u>delay</u> elements in the same manner as other primitive elements, a functional form is needed to represent them. The required function is:

$y_i = x_{i-n}$

This function is in a tabulated form. The symbolic representation of <u>delay</u> is discussed in Section 9.

## 6.2 Sub-classes of Primitive Elements

Three sub-classes of primitive elements are introduced here. The members of each sub-class accept a certain type of input signal and produce a certain type of output signal.

a) Boolean elements: and (&), or (v), not (~).

The terminal signals of these elements are of type Boolean.

- b) Relational elements: <u>lt</u> (<), <u>le</u> (≤), <u>eq</u> (=), <u>ne</u> (≠),

<u>ge</u> (≥), <u>gt</u> (>). The input signals are of type integer, and the output signal is of type Boolean.

- c) Arithmetic elements: <u>plus</u> (+), <u>minus</u> (-), <u>mult</u> (\*), <u>div</u> (/). The terminal signals are of type integer.

## 7. <u>Connectivity</u>

## 7.1 Graphic

In graphic description connectivity is indicated by joining lines representing input or output. If two lines are joined, the signals on both lines are the same (in either direction) up to the point where they reach a primitive element. Connection of two outputs as shown in Figure 4 is not 'valid'.

Figure 4. An invalid connection.

The reason such a connection is invalid is that: if c and e are not always the same, we should express what combination of the two exists at d. This is done through replacing the connectivity by a primitive element; otherwise the signal at d is 'ambiguous'. (An ambiguous signal is different from an <u>unknown</u> signal). If c and e are always the same, the network is 'redundant'.

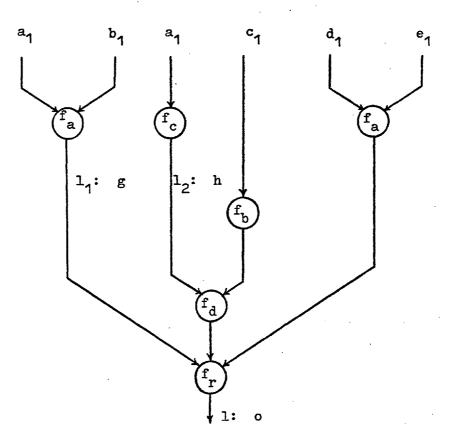

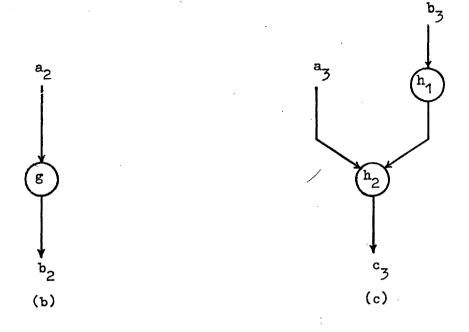

Since distinct identifiers represent distinct signals, similar identifiers may safely be used to indicate connectivity. For example, the following is a symbolic description of Figure 5. Elements 1 and 1 are connected.

$$l_{a}: c = f(a,b);$$

$$l_{b}: d = g(c);$$

$$a \qquad b$$

$$f$$

$$l_{a}: c$$

$$g$$

$$l_{a}: c$$

## Figure 5.

С

Let L and R represent the left and right hand sides of a statement 1. In terms of symbolic description, connectivities due to a set of statements are valid if there are no two statements,  $l_i$  and  $l_j$  (i  $\neq$  j), such that

(a)

$$L_{i} = L_{i}$$

If there exist a pair of statements satisfying (a) and also

(b)

$$R_i = R_i$$

the network is redundant; otherwise, if (a) holds but not (b), an ambiguous signal will be produced.

#### 8. Networks

A 'network' is a set of primitive elements with a set of valid connections over them.

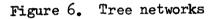

#### 8.1 Tree Networks

We define an input to be 'free' if it is not connected to an output.

Similarly, an output is free if it is not connected to an input. The following is a recursive definition of a 'tree network': a 'tree network' is either

- a) a primitive element, or

- a primitive element with free output provided that either

each of its inputs is free, or the only output connected

to it is the output of a tree network.

The above definition covers both symbolic and graphic descriptions. It excludes all networks containing invalid connections.

'Terminals' of a tree network are those which are free. The element from which the network output emanates is the 'root' of the tree. Since each tree has only one output, its root is unique. A tree is called by the name of its root, therefore it should be made clear which one is meant, when a reference is made.

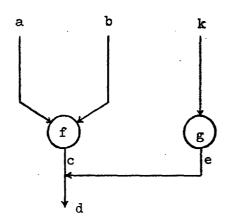

(a)

Figure 6 shows three examples of trees. Inputs of 1 in 6.a are  $a_1, b_1, c_1, d_1, e_1$ , and its output is o. The root of the tree is the element 1 and the function corresponding to the root is  $f_r$ .

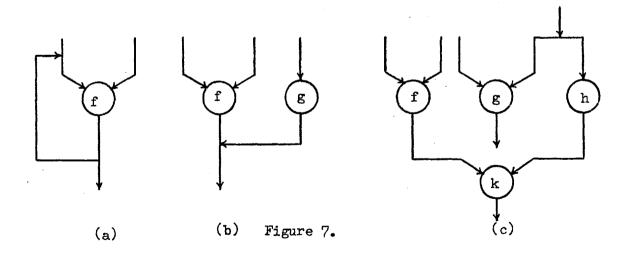

Networks described in Figure 7 are not trees. (a) has no free output, (b) contains an invalid connection, and (c) has an extra element.

## 8.1.1 Behaviour of a Tree Network

The functional property of a tree network is called its behaviour. Let  $i_s$ ,  $1 \le s \le p$  be the inputs of a tree 1. Let o be the output of 1. We are looking for a function f such that:

$$o = f(i_1, i_2, \dots, i_p);$$

Let  $f_r$  be the function corresponding to the element l. Let  $l_i$ ,  $1 \le i \le m$  be the trees connected to l, and  $g_i$ ,  $1 \le i \le m$  be the functions corresponding to these trees. Let  $k_{ij}$ ,  $1 \le j \le n_i$  be the set of inputs to the tree  $l_i$ ; then,

$$o = f_r(i_1, i_2, \ldots, i_p);$$

otherwise,

b)

$$o = f_r(g_1(k_{11}, k_{12}, \dots, k_1^{n_1}), \dots, g_i(k_{i1}, k_{i2}, \dots, k_{ij}, \dots, k_{in_i}), \dots, g_m(k_{m1}, k_{m2}, \dots, k_{mn_m}));$$

Clearly, the functions g<sub>i</sub> are determined in the same manner as f. Note that if an input a is free, it can always be assumed that it is the output of a tree network, say

#### a = same b;

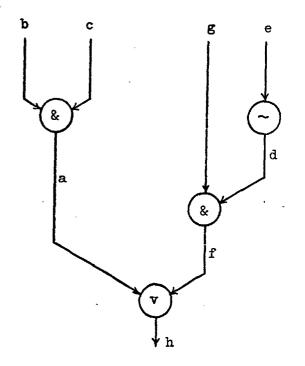

As can be seen from the functional expansion, the behaviour of a tree network depends on the behaviour of its elements and the way they are connected, i.e. the tree 'structure'. Therefore, the behaviour of a tree is independent of the textual position of the statements representing that tree. Similarly, graphic transpositions do not affect the behaviour of a tree provided that the tree structure is retained. Two trees are said to be 'equivalent' if they behave the same way. In the following example, the general functional form derived in this section is employed to determine the function corresponding to the tree

1. From Figure 8 we have,

$m = 2, n_1 = 3, n_2 = 1, p = 4$   $f_r = and, g_1 = or, g_2 = not$  $k_{11} = a, k_{12} = b, k_{13} = c, k_{21} = d$

hence,

$$g = and (or(a,b,c), not d);$$

a:e

# 8.1.2 Sub-trees

'Sub-trees' of a tree 1 are those whose output is connected to an input of the element 1. Each sub-tree has its own terminals; these can be determined by treating it as a tree. In Figure 8,  $1_a$  and  $1_b$ , are sub-trees of 1. The following relation exists between the inputs of a tree and the inputs of its sub-trees:

$$\bigcup {\{k_{ij}\}} = \bigcup {\{i_s\}}$$

$$1 \le i \le m \qquad 1 \le s \le p$$

$$1 \le j \le n_j$$

that is, the set of inputs of sub-trees of a tree, is the same as the set of inputs of the tree itself.

## 8.1.3 Well-formed Trees

Consider the element 1 described as:

1:  $o = f(i_1, i_2, ..., i_n);$

d

f

A set of input signals to this element is identified by the ordered n-tuple

$$S = (s_1, s_2, \ldots, s_n)$$

In order for 1 to be able to operate, types of  $i_j$  and  $s_j$  for all  $1 \le j \le n$  should match; they should be either both integer or both Boolean. The signal is then said to be 'correct'. If the tree structure is such that, given any correct set of input signals, each element of the tree receives correct signals, the tree is 'well-formed'.

# 8.1.4 Linear Description of a Tree

It was mentioned in Section 8.1.1 that the behaviour of a tree is independent of the textual position of statements forming its symbolic description. If the statements are arranged in a sequence such that every input of an element 1 is textually described before the description of 1, the arrangement is said to be 'linear'. Clearly, if an input to an element is also a tree input, it need not be described further.

In general the linear description of a tree is not unique; furthermore each tree has at least one linear description, for if a network cannot be described linearly, there is at least one statement

1:

$$o = f(i_1, i_2, \dots, i_n);$$

with an input  $i_j$  such that  $i_j$  is neither a tree input, nor can be described before 1. This implies that the description of  $i_j$  depends on the description of o, in which case the network does not have the tree property. For example, a linear description of the tree,

$$h = \underline{or}(f,a);$$

$$d = \underline{not} e;$$

$$f = \underline{and}(g,d);$$

$$a = \underline{and}(b,c);$$

is:

$$a = and (b,c);$$

$$d = not e;$$

$$f = and(g,d);$$

$$h = or(f,a);$$

The networks

$$\mathbf{x} = \underline{plus}(1, \mathbf{x});$$

x + +

x

Figure 10.

cannot be described linearly. In the first network, description of x depends on itself, and in the second one, a and c depend on each other.

and

$b = \underline{not} a;$   $c = \underline{not} b;$ a = c;

# 8.2 Composite Trees

A 'composite tree' is either

- a) obtained from a tree by connecting at least one of its inputs to one or more of the elements of another simple tree, or

- b) obtained from a tree by connecting at least one of its inputs to one or more of the elements of a composite tree.

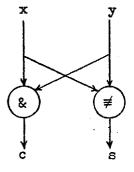

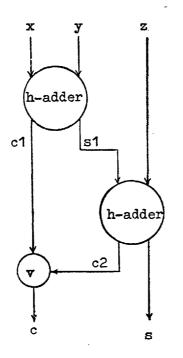

Trees defined in Section 8.1 are referred to as 'simple trees' in contradistinction to composite trees. In general a composite tree has several outputs. The definition of the linear description of a composite tree is the same as that of a simple tree. Following is a graphic and linear description of a half-adder in the form of a composite tree.

Figure 11. A composite tree

Like simple trees, each composite tree has at least one linear description.

## 8.3 Closed Trees

A 'closed tree' is either

- a) obtained from a simple or composite tree by connecting at least one of its outputs to one or more of its inputs, or

- b) obtained by validly connecting a closed tree to a simple, composite, or another closed tree.

The definition of a linear description is relaxed for closed trees, in that the closing terminals need not be described before they are referenced. If a closed tree has a closing terminal t, the symbolic description of that tree will include a network of some form equivalent to:

t = f(..., t, ...)

As this form suggests, the working of the network is 'repetitive', in the sense that the output signals on closing terminals are fed back as input.

Trees defined in Sections 8.1 and 8.2 are referred to as 'open trees' in contradistinction to closed trees.

## 8.4 <u>Networks</u>

We can now give a more precise definition of a network: a network is a set of single/composite/closed trees described together. A linear description of a network is one in which each tree belonging to the network is described linearly. Networks more complex than a certain degree are referred to as 'digital systems'. There is no precise definition for the boundary whereafter a network is, or should be called a digital system.

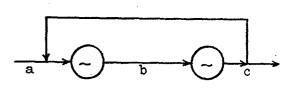

## 9. Symbolic Description of a <u>delay</u>

The discussion of this topic has been deferred up to this point so that examples could be drawn from tree structures for its illustration and

### justification.

The functional form of a delay, i.e.

$$y_i = x_{i-n}$$

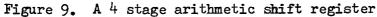

states that the output value of the <u>delay</u> is equal to its input value with a <u>time</u> lag. This suggests calling the terminals of the <u>delay</u> by the same name; in fact one can regard this name as the name of the <u>delay</u> itself. On the basis of this interpretation, we adopt a declarative form for introducing the <u>delay</u> elements in a network; for example,

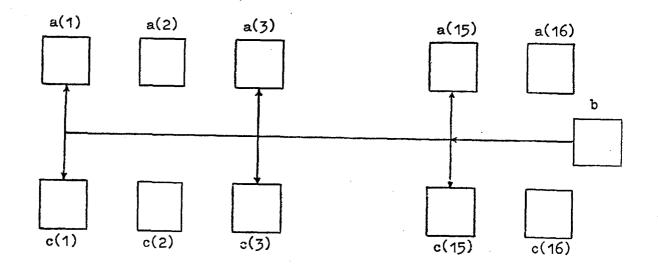

# <u>delay</u> cnt(1:16);

declares that cnt is a 16-bit <u>delay</u> element whose storage locations run from c(1) to c(16), with c(1) being at the front of the queue (the oldest member), and c(16) at the end of the queue (the youngest member).

Distinction between the input and output of a <u>delay</u> is made at the time the connectivity is established. If cnt appears on the left hand side of a statement, then the input of the <u>delay</u> is connected to the output of the right hand side tree; whereas if cnt is referenced in the right hand side, the output of the <u>delay</u> is meant.

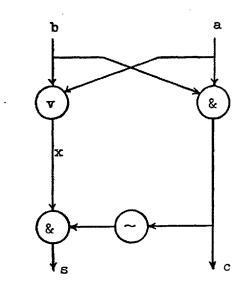

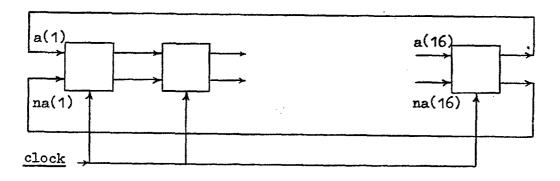

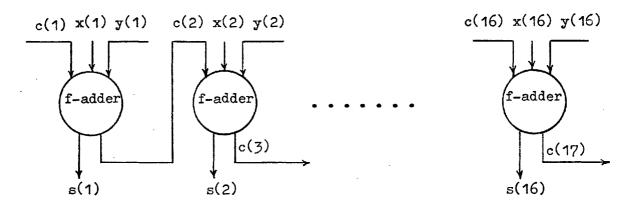

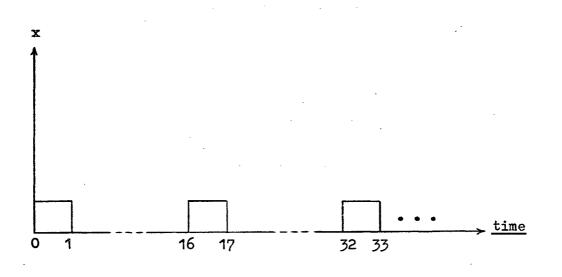

As an example, the half-adder in Figure 11 is turned into a 16-bit serial counter [26]; cnt holds the count, and at every 16-bit time interval a <u>true</u> signal appears at x. Without going into the details of the working of this device, its linear description is given in Figure 12.

- 1- delay cnt(1:16),b; 2- c = or(x,b); 3- d = and(c,cnt); 4- b = d;

- 5-  $\operatorname{cnt} = \operatorname{and}(\operatorname{or}(c,\operatorname{cnt}), \operatorname{not} d);$

x

Figure 12. A serial counter

The above network is a closed tree with two closing terminals, namely cnt and b. Lines 2 to 4 describe the tree located to the right of the dotted line; the rest of the network is described in line 5; note that the name, cnt, at the left hand side of this statement refers to the input of the <u>delay</u>, whereas the same name at the right hand side refers to the output of cnt, with a 16-bit time delay with respect to the input.

The notation introduced here for the symbolic representation of the <u>delay</u> has, apart from a close correspondence to its functional form, three other important advantages discussed in the following sections.

## 9.1 Connection to other Elements

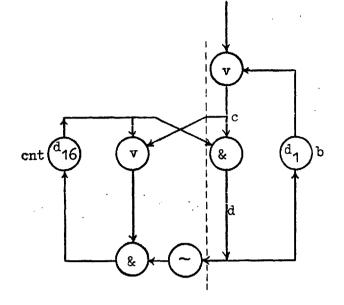

Connecting an element to a <u>delay</u> is quite simple; this is especially useful if one wishes to introduce the inherent delays of logic elements. For instance, an <u>and</u> gate which has a 1-bit propagation delay can be described as:

$\frac{\text{delay } c;}{c = \underline{and}(a,b);}$

Figure 13. An and gate with a propagation delay

If the above tree were part of a network, the name c, which could only be referenced in the right hand side of the statements of the network, would correspond to the output of the <u>delay</u>, and thus the 1-bit propagation delay could easily be introduced. Since a 1-bit propagation delay is quite common, later (Chapter V) we shall see simpler ways of coping with this special case.

Another example of the connection between <u>delay</u> and other elements can be seen in line 5 of the example already given in Figure 12.

## 9.2 Initialization and Store Allocation

The second advantage concerns the fact that one has access to the members of the line (storage buffer associated with the <u>delay</u>). This could be

helpful as it is frequently desired to regard a <u>delay</u> as a storage element during the initialization time. For example, the following segment initializes the first element of cnt to <u>true</u>, and the rest to <u>false</u>.

cnt(1) = true; cnt(2:16) = false;

Finally, with regard to implementation, no matter what notation is adopted, one has to allocate an area of store, of appropriate size, to the delay line. In this respect, the notation given here treats the <u>delay</u> introductions almost in the same manner as declarations, and thus simplifies the implementation task.

# 10. Sequential and Parallel Operations

An output signal is produced as a result of primitive elements operating on their input signals, and thus propagating them. An operation is called by the name of the primitive element it corresponds to. We define the following relations between pairs of operations; by their nature they may also be referred to as meta-operators.

a) x is 'parallel' to y, denoted by x = y

b) x is 'sequential' to y (x after y), denoted by  $x \rightarrow y$

These have the following properties:

| I) | if | х | •> | у | and | у | •> | $\mathbf{z}$ | then | х | •> | $\mathbf{z}$ |

|----|----|---|----|---|-----|---|----|--------------|------|---|----|--------------|

|----|----|---|----|---|-----|---|----|--------------|------|---|----|--------------|

- II) if neither  $x \rightarrow y$  nor  $y \rightarrow x$  then x = y

- III) if  $x \stackrel{\bullet}{=} y$  and  $y \stackrel{\bullet}{=} z$  then  $x \stackrel{\bullet}{=} z$

- IV) if  $x \rightarrow y$  and  $y \doteq z$  then  $x \rightarrow z$

- V) if  $x \rightarrow y$  and  $x \stackrel{\bullet}{=} z$  then  $z \rightarrow y$

VI) if  $x \stackrel{*}{=} y$  then  $y \stackrel{*}{=} x$

VII)  $\dot{\mathbf{x}} \stackrel{*}{=} \mathbf{x}$

Property VI is in fact a consequence of II.

The above axioms represent the nature of parallel and sequential operations, and their inter-relationship. Among these, axiom II has a special importance, for it ensures that one of the two relations, .> or :, holds between any two objects belonging to a set of operations.

From the behaviour of a tree network it is understood that when propagating the signals the operation corresponding to the root of the tree should be carried out after all operations belonging to the sub-trees of that tree have been performed. Therefore, if x is the root of an open tree, and y is a sub-tree of x, we define

(1) x ·> y

As an example, consider the following tree:

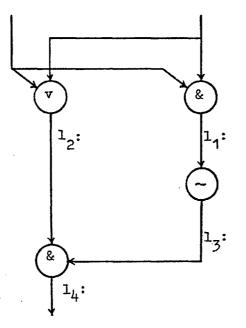

According to the above definition, the following relations hold over the set of operations  $A = \{1_1, 1_2, 1_3, 1_4\}$ :

- a)  $l_4 > l_2$

- b) 1<sub>4</sub> -> 1<sub>3</sub>

- c)  $1_3 \rightarrow 1_1$

According to axiom II, since neither  $l_2 \rightarrow l_3$  nor  $l_3 \rightarrow l_2$ , we have

d)  $1_3 \doteq 1_2$

This means that  $l_3$  and  $l_2$  are parallel. Axiom I and relations (b) and (c) result in

e) 14 -> 11

Axiom V together with relations (c) and (d) results in

f)  $l_2 > l_1$

In this manner we obtained the six relations over the set A; it can be seen which operations are parallel and which are serial to each other. Note that we could have equally said that, since neither  $l_2 \rightarrow l_1$ nor  $l_1 \rightarrow l_2$ , we have

$1_1 = 1_2$

In this case we would have had the following six relations instead:

a')  $l_4 \rightarrow l_2$ b')  $l_4 \rightarrow l_3$

c')  $l_3 > l_1$ d')  $l_1 \doteq l_2$ e')  $l_4 > l_1$ f')  $l_3 > l_2$

The difference is between (d') and (d), and, (f') and (f); the rest are the same. The important thing is that no matter which set of relations we choose, the behaviour of the network is maintained; this is because of the definition (1) which corresponds to the behaviour of trees, and also because the axiomatic properties given at the beginning of this section truly represent parallel and sequential operations and the inter-relation between them.

#### 11. Ordering the Operations

### 11.1 Open Trees

As our natural constraint is that: using a single processor, only one operation can be carried out at a (Computation) time, we should like to arrange the operations in a sequence such that the output signals obtained, as a result of performing them in that order, would correspond to the behaviour of the tree.

An operation x CAN be carried out when all operations  $y \in A$  have been performed,

where  $A = \{y \mid x \rightarrow y\}$

The other constraint is that x SHOULD be carried out before all operations,  $Z \in B$ , have been performed,

where  $B = \{z \mid z \rightarrow x\}$

This suggests a Computation Time interval, understood by z -> u -> y,

where  $u \in C$

and  $C = \{u \mid u \stackrel{*}{=} x\}$

during which x could be performed. We note that all operations  $u \in C$  are parallel to x.

The important result of the above analysis is the following assertion: THE BEHAVIOUR OF AN OPEN TREE CAN BE SIMULATED USING A SINGLE PROCESSOR. This assertion has two cornerstones; the first is axiom II, which as mentioned earlier, establishes one of the two relations,  $\rightarrow$  or  $\doteq$ , between any two operations belonging to a set of operations corresponding to a tree. The second is the fact that, using a single processor, a primitive element can be simulated.

#### 11.2 Closed Trees

As mentioned in Section 7.4, the functional form of a closed tree is repetitive, i.e. once the output signals are obtained, the ones on the closing terminals have to be fed back, and the process repeated. The best possible correspondence between a digital system and its model is obtained if the behaviour of the Simulator is such that the state of the model is re-evaluated at every point in Simulation Time. This repetitive evaluation causes the signals on the closing terminals to be fed back to the network. In this manner the behaviour of a closed tree is simulated using a single processor. Clearly, the Simulation Time is advanced at the end of each cycle.

By now the role of the linear description, in connection with the implementation of the Description System, has become apparent. Since

in a linear description, the root of the tree is described after the sub-trees of that tree are described, the execution of the statements from top to bottom would simulate the behaviour of the open trees; the Simulator repeats its control cycle, and thus the behaviour of the closed trees is simulated.

The user need not necessarily specify his description in a linear form since, using a pre-processor, any symbolic description of a network can be transformed into a linear description.

#### 12. Terminal Registers

The result of an operation may be needed at a later point in Computation Time. If so, we assume that there are imaginary 'terminal registers' connected to the terminals of a primitive element. In this form, c = and (a,b) could be thought of as:

Figure 15. An and gate with its terminal registers

The name of a terminal register is the same as that of the signal it corresponds to. In this respect, one can give another definition for connectivity: two terminals are connected provided they share the same terminal register. The user can give a hint to the Simulator whether the result of an operation is going to be needed later. For example, from

d = and (or (a, b), not c);

it is understood that the intermediate signals, <u>or</u> (a, b) and <u>not</u> c, are not needed later.

In this manner, the operation of a primitive element can be looked at as a transfer of signals from input registers to the output register. This interpretation of the working of primitive elements take us to Chapter III, which discusses the generalised form of register transfer operations.

#### CHAPTER III

#### The Register Transfer Level

#### 1. Introduction

At the Register Transfer Level (RT-Level), a digital system is imagined to be composed of registers connected through blocks of logic elements. Each block performs an operation on the contents of one or more input registers, and places the result in output registers, which may include some of the inputs.

At the end of the previous chapter, we noted that the structure and working of a network, at the Level of Logic Elements, could be described in terms of terminal registers and register transfer operations (RT-operations). In this chapter we generalize such operations to include vectors, as well as scalars. As a result of this generalization, the operators of the Language are defined, which cover the sub-classes of primitive elements mentioned in the previous chapter.

Detailed attention is paid to Language features for describing a digital system at the RT-Level. Some of the topics considered in the previous section, such as types and constants, are reviewed here with more emphasis on linguistic features, and occasionally on implementation requirements.

#### 2. Representation of Boolean Constants

In digital systems information is represented using entities which take one of the two possible states. When concerned with switches and lights, these are called <u>on</u> and <u>off</u>; in connection with logical operations, they are named <u>true</u> and <u>false</u>; when a numerical interpretation is meant, these are referred to as 1 and 0. One or more of these constant sets should be selected in order to assign states to lights, switches, and other binary objects. Whichever is selected, the Description System can choose only one of these representations to output the states of objects, unless the System has already been told about the type of object concerned with the information to be output. This would require introducing declarations such as:

switchs;memorym;registerr;

together with keeping distinct descriptors for each type. The approach might obscure from the user the fact that all objects, s, m, and r are essentially of the same type, namely <u>Boolean</u>.

Another extreme solution would be to allow only one type, for example <u>Boolean</u>, and ask the user to interpret all his binary entities in terms of this type. Besides putting the burden of the interpretation task on the user, we have also decreased the clarity of descriptions. In order to overcome this, the user would be forced to insert comments. For example,

<u>Boolean</u> s; -- s is a switch; <u>Boolean</u> m; -- m is a memory <u>Boolean</u> r; -- r is a register;

A compromise solution, adopted here, is to permit the user to make use of all types (<u>Boolean</u>, <u>switch</u>, <u>memory</u>, etc.) interchangeably. The System will then interpret them all in the same manner. The price paid for this is that the output information would be represented in only one form. Corresponding to this, all sets of binary constants  $\{\underline{on}, \underline{off}\}, \{1, 0\}, \{\underline{true}, \underline{false}\}$

may be used interchangeably. We select the binary constants 1 and 0 for outputting binary information.

### 3. The unknown value

The question is whether to define the logical operators over two-valued or three-valued space. At a low level, a digital system can be thought of as a number of bistables connected through logic elements. When the system is switched on, the bistables take on one of the two possible states at random. Assuming that there are no faulty elements, or disconnections, and that other physical requirements such as the fan-out of the elements are satisfied, the system works on a two-valued space. Thus the only advantage in the inclusion of an unknown value would be the simulation of faults and other undesired effects due to non-initialization of storage elements which should have been initialized. Fault simulation may be done by defining faulty elements, with the aid of the element definition facility. In order to simulate the effect of non-initialization, one may either assume that the output of an element is unknown unless all its inputs are defined, or adopt some other arrangement which propagates the unknown value under certain conditions, so that the user becomes aware of the effects. However, this approach has shortcomings when dealing with networks whose working is independent of the initial values of their storage elements. If all storage elements were initialized to an undefined value by the System, then under this arrangement, the working of the model would not correspond to that of the digital system. Therefore we consider the logic elements to operate on a two-valued space.

#### Arrays

To identify one of many distinct objects, events, or operations, an array of binary entities must be used. In its simplest form, an array is a linear

list, also called a vector. A binary vector may be interpreted numerically, or as a string of bits, an instruction, an address, or otherwise.

Main memories may be regarded as two dimensional arrays, also called matrices. As such, they are identified by the number of words they contain, and the number of bits per word. In the simplest case, the main memory has one address register which holds the address of the word to be written to or read from the memory, and one buffer register which holds the corresponding item of data. The memory read/write time is the same for all words. This type of memory may be declared as a <u>Boolean matrix</u>. More complex and special purpose memories such as stack, associative, multi-access, modular, etc. should be described explicitly.

### 4.1 The Type Integer

Integer entities are at a higher level than the binary ones - an integer can be represented by a binary vector. We therefore introduce the type <u>integer</u> so that arithmetic operations can easily be described at a high level. In input and output, integers are represented in the conventional decimal form. Arrays of integers do not seem to be required and we therefore exclude them.

### 4.2 Array Declaration

Arrays are declared by naming their type, and the lower and upper bounds for each dimension. Arrays and scalars may be declared together, for example

switch console(0:15), start, stop, power;

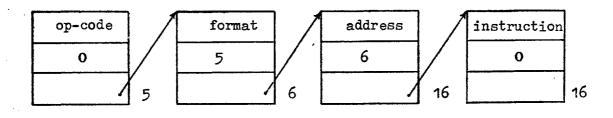

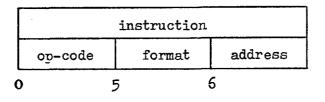

It is often required to refer to a sub-array of an array throughout a description. For example, an instruction in a computer may be composed of the following fields: operation-code, format, and address part, as defined below:

register instruction(op-code(0:4), format, address (0:9));

Some of these fields may in turn contain sub-fields; for example, the address field may be regarded as composed of an indirect addressing flag, an index register indicator, and the static address part.

register instruction(op-code(0:4), format, address(ia,ix(1:2), s-address(1:7)));

Sub-registers, format and ia, are of one bit length only. The above method for declaring arrays is called the nested-top-down method. Sometimes it is convenient to declare sub-arrays by giving the boundary bit positions that they occupy in the array, rather than by declaring the array in terms of its constituent sub-arrays. This is called the simple-top-down method, e.g.

register double-word(0:31);

sub-array word(0:15) = double-word(0:15),

next-word(0:15) = double-word(16:31);

sub-array instruction(0:15) = word(0:15);

Up to now the register, word, has had only one interpretation, i.e. an instruction. One can easily introduce other interpretations, e.g.

sub-array fixed-point(0:15) = word(0:15); sub-array sign = fixed-point(0),

magnitude = fixed-point(1:15);

and similarly for the register double-word:

sub-array floating-point(0:31) = double-word(0:31); sub-array signs = floating-point(0), mantissa(0:23) = floating-point(1:24), exponent(1:7) = floating-point(25:31);

A picture of the structure which has been constructed is given in Figure 1. For clarity the picture is presented in three parts.

| double-word |   |   |     |       |           |  |  |  |

|-------------|---|---|-----|-------|-----------|--|--|--|

| word        |   |   |     |       | next-word |  |  |  |

| instruction |   |   |     |       | · ·       |  |  |  |

| op-code     | f | a | ddr | ess   |           |  |  |  |

| ia ix s-add |   |   |     | s-add | · · ·     |  |  |  |

| word        |           |  |  |  |  |  |

|-------------|-----------|--|--|--|--|--|

| fixed-point |           |  |  |  |  |  |

| <b>S</b> .  | magnitude |  |  |  |  |  |

| double-word |          |                |          |  |  |  |  |

|-------------|----------|----------------|----------|--|--|--|--|

|             |          | floating-point |          |  |  |  |  |

| ຮ           | mantissa |                | exponent |  |  |  |  |

Figure 1. Interpretations of a double-word

Such constructions are ambiguous in the sense that referencing the name of an array, in general, does not convey the full meaning of the contents of that array. For example, word, may have different meanings such as instruction or fixed-point. This ambiguity is due to the very fact that a string of bits in a memory location could be interpreted in different ways: it could be an instruction, a data item, the second word of a double-word instruction, etc. Only the context of reference can clarify the meaning.

# 4.3 Array referencing

# 4.3.1 Referencing Sub-arrays which are Declared

There are two choices:

a) The sub-array might be referenced through the hierarchical

structure it was declared in, e.g.

ix(address(instruction))

b) The sub-array might be called by its name only, e.g.

#### ix

In the first method two sub-arrays not belonging to the same array may have the same name, i.e. a certain name may give different meanings depending on the context, e.g.

> a(c), a(b). (a, b, c are arrays)

This is a useful advantage when one has to declare many names, and wishes to use similar ones. However, as our declarations are not numerous, and because of its simplicity, we adopt the second method.

# 4.3.2 <u>Referencing Sub-arrays which are not Declared</u>

If references to a sub-array do not occur frequently, one may choose not to give it a symbolic name. The same notation used earlier can serve to construct sub-arrays or cascaded arrays, e.g.

instruction(0:4)

instruction(6:15)

op-code:address

word:next-word

In the last two examples, the colon sign serves to concatenate arrays. Dynamic references fall into this category, e.g.

word(n:m)

op-code(i):instruction(j:P):ix

### 4.4 Matrices

A matrix is an ordered list of vectors of the same dimension. In digital systems main memories and groups of registers are examples of matrices. When dealing with a register, one part of it cannot in general play the role of another part, for they usually perform distinct duties. By contrast, in a list of registers forming a matrix, one member may be replaced by another one. The only reason for having several of them instead of one is to increase the speed of the system. Although there is no exception to this general rule in the case of memories, i.e. all memory words perform the same function, there are exceptions with regard to registers. For example, in some computers certain index registers can also be used as accumulators.

Due to this interchangeability of registers and memory words among each other, there is no need to introduce elaborate facilities, as in the case of vectors, for constructing two dimensional structures. The fact is that one member of a list of registers is not going to be interpreted in a different way than another member, except in some special cases.

# 4.4.1 Declaration and Referencing of Matrices

We extend the notation introduced earlier for one-dimensional arrays in order to reference vectors forming a matrix. Also the special cases discussed in the previous section are catered for. Like vectors, matrices are declared by specifying the bounds for each dimension, e.g.

<u>memory matrix M(0:8191, 0:15);</u>

register matrix index-reg(1:3, 0:15);

In order to refer to the kth element of a list of vectors, the integer k is written in place of the first index, and the second index is ommitted, e.g.

> m(i,) ith memory word index-reg(2,) the second index register

Parts of such vectors may also be referenced in the same manner as before, e.g.

index-reg(2,0:4) the first five bits of the second index register.

A vector belonging to a matrix may be given a symbolic name throughout a description, e.g.

sub-array accumulator(0:15) = index-reg(3,);

5. Constants

### 5.1 Declaration

Integer constants may be given symbolic names, e.g.

<u>constant</u> add = 1, sub = 2, mult = 3, div = 4;

#### 5.2 Specification

There are two types of constants, Boolean and integer; the latter is represented in the conventional decimal form. For the sake of simplicity, we allow Boolean constants to be specified in binary, octal, or hexadecimal form, as well as other forms discussed in Section 2, e.g.

| 952                  | a decimal constant     |

|----------------------|------------------------|

| <u>bin</u> (0,0,1)   | a binary constant      |

| <u>oct(7,7,7)</u>    | an octal constant      |

| <u>hexa(f,f,f,f)</u> | a hexadecimal constant |

### 6. <u>Array Operations</u>

As stated earlier in section 4.4, we need only be concerned with operations on one dimensional arrays. The operators and their characteristics are described in Table 1. The type of operand indicated here is that which the operator expects. If the operand is not of the required type it will be transformed according to the following rules: an integer is converted to an unsigned binary number represented by a Boolean vector; conversely, a Boolean vector is treated as an unsigned binary number and transformed into an integer.

If the user wishes to regard the numbers as signed, he may do so by placing a directive at the beginning of description, which indicates whether negative numbers are in two's or one's complement. The operator <u>int</u> in general takes a Boolean vector as its operand and transforms it into a signed integer. Similarly, the operator <u>bln</u> may be employed to convert a signed integer into a Boolean vector.

If the result of a conversion is a Boolean vector, its dimension is determined

in accordance with the context. It should not be overlooked that we permit implicit type conversion at the cost of not forcing the user to distinguish between the state of a register and its interpretation.

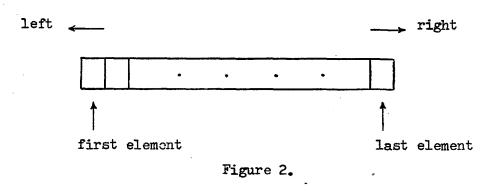

In arrays, the element with the lowest index is called the first element. For positional and directional referencing this element is assumed to be the leftmost one, and in connection with binary numbers it is the most significant digit.

Let  $s_1, s_2, \ldots, s_m, x$  be scalars, and  $v_1, v_2, \ldots, v_m, y$  be vectors of length n, and <u>asop</u> be an associative operator,

and ident (asop) be the identity operand for the operator asop.

Associative operators are allowed to have multiple operands, as shown below for scalars:

$x = \underline{\operatorname{asop}}(s_1, s_2, \dots, s_m) \text{ is the same as}$  $x = \underline{\operatorname{asop}}(s_1, s_2, \dots, \underline{\operatorname{asop}}(s_{m-1}, s_m))$

| operator |         |            |                | num          | ber of ope   | rands        | type of operand<br>and [result] |               | associa-     |

|----------|---------|------------|----------------|--------------|--------------|--------------|---------------------------------|---------------|--------------|

| symbolic | graphic | category   | operation      | monadic      | diadic       | multiple     | Boolean                         | integer       | tive         |

| plus     | +       | arithmetic | addition       | $\checkmark$ | $\checkmark$ | ~            | -                               | √[√]          |              |

| minus    | -       | -          | subtraction    | $\checkmark$ | $\checkmark$ |              |                                 | √ <b>t</b> √J |              |

| mult     | *       | -          | multiplication |              | $\checkmark$ | $\checkmark$ |                                 | √t.√j         | $\checkmark$ |

| div      | 1       | <b>-</b> . | division       |              | $\checkmark$ | · •          |                                 | ~t~j          |              |

| rem      |         |            | remainder      |              | $\sim$       |              |                                 | √ <b>Γ</b> √] |              |

| and      | &       | logical    | and            | $\checkmark$ | $\checkmark$ | $\checkmark$ | _ <b>√</b> τ.∕1                 |               |              |

| or       | v.      | -          | or             | 1            | $\checkmark$ | $\checkmark$ | √t√1                            |               | $\checkmark$ |

| not      | ~       |            | not            | $\checkmark$ |              |              | √ <b>[</b> √]                   |               | ,            |

| nand     |         | ••• ``     | nand           | $\checkmark$ | $\checkmark$ | 1            | <b>√</b> [√]                    |               |              |

| nor      |         | -          | nor            | $\checkmark$ | $\checkmark$ | $\checkmark$ | √t√1                            |               |              |

| eqv      | E       |            | equivalence    |              | ~            | $\checkmark$ | ~ <b>\</b> [\]                  |               | ~~           |

| eor      |         |            | exclusive or   | $\checkmark$ | $\checkmark$ | $\checkmark$ | √t√1                            |               | $\sqrt{2}$   |

|          | ······  |            |                |              |              |              | •                               |               |              |

Table 1.

| operator   |         |            |                          | num          | ber of ope   | erands   | type of<br>and [re | associa-                        |      |

|------------|---------|------------|--------------------------|--------------|--------------|----------|--------------------|---------------------------------|------|

| symbolic   | graphic | category   | operation                | monadic      | diadic       | multiple | Boolean            | integer                         | tive |

| <u>lt</u>  | <       | relational | less than                |              | ~            |          | [י/]               | ~                               | ,    |

| <u>le</u>  | ٤       | · _        | less than or<br>equal to | r            | ~            |          | [ <b>√</b> ]       | $\checkmark$                    |      |

| eq         | =       | -          | equal                    |              | $\checkmark$ |          | <b>Ľ√</b> ]        | $\checkmark$                    |      |

| ne         | ¥       | -          | not equal                |              | $\checkmark$ |          | [√]                | <b>V</b> - 1                    | •    |

| ge         | 2       | -          | greater than<br>equal to | n or         | $\checkmark$ |          | [⁄_]               | $\checkmark$                    |      |

| gt         | >       | -          | greater tha              | n            | $\checkmark$ |          | [√_]               | $\sim$                          |      |

| rshift     |         | shift      | shift right              | $\checkmark$ | $\checkmark$ | •        | for shift          | operaters, t                    | he   |

| lshift     |         | · _        | shift left               | $\checkmark$ | $\checkmark$ |          |                    | erand is Boole                  |      |

| rcirc      |         | -          | circulate<br>right       | ~            | $\checkmark$ |          |                    | second operand<br>t, is integer | • 1  |

| lcirc      |         | . –        | circulate l              | eft 🗸        | 1            |          | Type of r          | esult is Bool                   | ean  |

| <u>bln</u> |         | special    | convert to<br>Boolean    | $\checkmark$ |              |          | [√]                | $\checkmark$                    | · ·  |

| int        |         |            | convert to<br>integer    | $\checkmark$ |              |          | $\checkmark$       | [√]                             |      |

Table 1 - (continued)

:

and for vectors

$$y = \underline{\operatorname{asop}}(v_1, v_2, \dots, v_m) \text{ is the same as}$$

$$\underline{\operatorname{for}} i = 1 \underline{\operatorname{to}} n \underline{\operatorname{do}}$$

$$y(i) = \underline{\operatorname{asop}}(v_1(i), v_2(i), \dots, v_m(i));$$

(see Section IV.8.1 for semantics of <u>for</u> structure.)

If an associative operator is given a vector as its only operand, the operator is distributed through the elements of the vector as shown below:

$x = \underline{asop}(v_1) \text{ is the same as}$  $x = \underline{ident}(asop);$  $\underline{for} \ i = l \ \underline{to} \ n \ \underline{do}$  $x = \underline{asop}(x, \ v_1(i));$

In addition to associative operators, <u>nand</u> and <u>nor</u> are also allowed to have multiple operands; their operation in this role is described below:

nand 1 is the same as not and 1

nor l is the same as <u>not or l</u>

where 1 is a list of operands, possibly only one vector.

The shift operators take a vector as their first operand and an integer as their second operand. The operation is then performed as many times as specified by the second operand. If the operation is to be done only once, the second operand may be omitted. Examples are: <u>rcirc</u>( $v_1$ , 2) circulate  $v_1$  two positions to the right. <u>lshift</u>  $v_1$  shift  $v_1$  one position to the left.

The only case in which the operands of an operator can have different dimensions is when one operand is a scalar. The scalar is then distributed through all elements of the vector as shown below:

$y = op(x, v_1)$  is the same as

$$for i = 1 to n do$$

$$\mathbf{y}(\mathbf{i}) = \underline{op}(\mathbf{x}, \mathbf{v}(\mathbf{i}));$$

where op is an operator.

### 7. Expressions

<expression> ::= <simple expression>|<Boolean expression>|

<integer expression>!<delayed Boolean expression>!

<element designator>

<simple expression> ::= <constant>I<variable>

<Boolean expression> ::= <Boolean operator> <operand list> <operand list> ::= <source vector>!(<source vector>{,<source vector>}\*)

The simplest form of an expression is a constant or variable in which case a connectivity is established, or a reference to the contents of a variable, as defined in Chapter II. For a detailed syntactic definition of variables and constant refer to Appendix C.

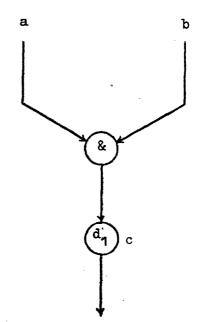

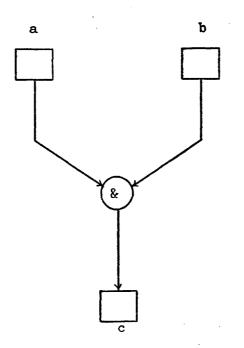

An expression defines the structure and behaviour of a network. Among the structural properties the network inputs are given; the outputs are however not named. This is a feature of expressions which permits the specification of connectivity without naming the signals at the interconnections. An expression, in general, returns a vector as its result, e.g.

- <u>register</u> a,b;

<u>and(a, not b)</u>

- 2) <u>register</u> a(1:16), b(1:16); <u>and(a, not</u> b)

Figure 3. Graphic description In both examples a and b are inputs. The first example returns a vector of length 1 as its result, while the second returns a vector of length 16. The signal in between the two gates is not named.

As was shown earlier in Chapter II, if a good correspondence between graphic and symbolic description of trees is required, it is better to represent the expressions in prefix notation; this also serves for describing elements with multiple inputs, e.g.

nand (a,b,c)

However, the prefix notation is not suitable for simplification, and addressing elements of arrays. The problem could partly be solved by using the prefix notation in general, and employing the infix notation for indexing; however, this would not be a good solution because of the non-uniformity introduced in the structure of expressions.

Boolean, shift, and relational expressions return Boolean results. The first two take Boolean operands, whereas the last one takes integer operands. The results and operands of arithmetic expressions are both integer. Other types of expressions will be discussed in Chapter V.

### 8. <u>RT-operations</u>

<source vector> ::= <exp>{:<exp>}\* <destination vector> ::= <variable>{:variable>}\* <RT-operation> ::= <destination vector> = <source vector> The expressions outputs may be concatenated to form a source vector; Similarly variables may be concatenated to form a destination vector. Neither of these vectors is named. A 'register transfer operation' specifies the outputs of a network. It may also be looked upon as a mapping from a set of input vectors into a set of output vectors whose concatenation is called the destination vector.

Elements concatenated by the colon sign should be of the same type. If the number of elements of the source vector is equal to that of the destination vector, a one-to-one correspondence can easily be established; if the source vector has more elements than the destination vector, the extra elements at the left hand side are ignored; if the source vector has fewer elements, it is expanded to the left by repeating its leftmost element.

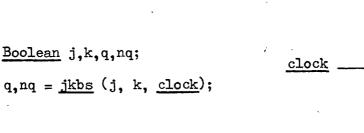

Some examples of RT-operations are given below:

1)

k

nq

i

α

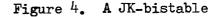

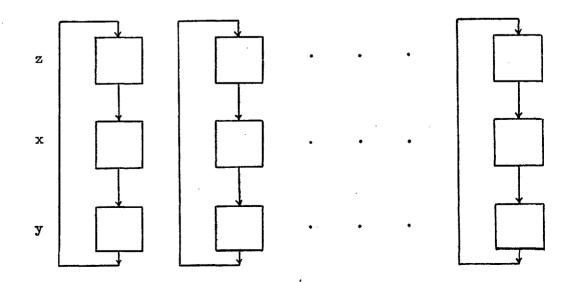

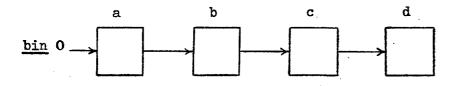

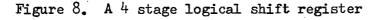

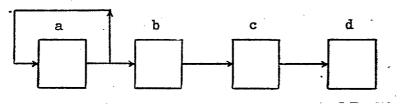

<u>jkbs</u> (JK-bistable) is a System-defined element; its outputs are q and nq (~ q). <u>jkbs</u> returns a vector of length 2; the first element is assigned to q, and the second to nq. When JK-bistables are cascaded (Fig. 8, or Fig. 10), the two inputs are not independent ( $k = \sim j$ ). In this case we use an abbreviated form as shown below:

Figure 5. Graphic description of <u>ajkbs</u>

```

2) register a, b;

```

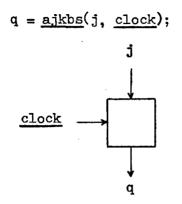

a:b = b:a;

3) register x(1:16), y(1:16), z(1:16);

x:y:z = y:z:x;

Figure 7. Upon activation, the contents of x, y, and z are rotated.

4) <u>register</u> a,b,c,d;

b:c:d:a = a:b:c:<u>bin</u> 0;

5) <u>register</u> a,b,c,d;

b:c:d:a = a:b:c:a;

6) <u>register</u> a(10);

a = <u>rshift</u> a(1:7):~a(8):a(9:10);

Figure 10. All positions of register, a, are shifted one place to the right, with the exception of the 9th position which receives the negation of the 8th position.

7) <u>switch</u> x(1:4);

x = off, off, on, off; switch x is initialised.

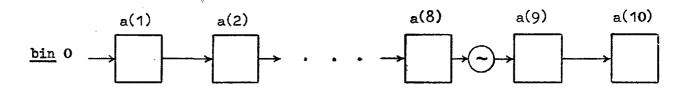

8) register x(1:16), y(1:16),a; y = and(a,x);

#### CHAPTER IV

#### The Control Level

#### 1. Introduction

Up to now we have dealt with the operations without being concerned about when an operation should - or does - take place. At this level, control structures are introduced which can be used to impose an ordering on operations - an operation may be invoked at a particular step in a sequence of steps, or at a certain time, or in general when certain conditions are satisfied. Such conditions may well be a function of the previous state of the system.

The chapter starts with the introduction of the concept of a controlled RT-operation; two basic ways of ordering the operations, namely parallel and sequential are then discussed, and attention is paid to systems expressed in such terms. The latter part of the chapter is concerned with higher level control structures, such as conditionals and loops, which are frequently used for writing procedural algorithms.

Furthermore, the hardware implementation of such structures is discussed in detail; thus once the user has described his ideas in these terms, he has general paths in sight by which to progress toward the implementation level, and features of his design are realized as progress continues. The choice of control structures is important since these are the tools in terms of which the user will tend to think.

At the levels near to the implementation, we are concerned with a subset of RT-operations involving only Boolean variables. In general, a 'controlled RT-operation' is denoted in the following way:

<control condition> -> <RT-operation>

where

<control condition> ::= <Boolean expression>

A controlled operation is said to be 'activated' or 'invoked' when the 'control condition' for that operation becomes <u>true</u>.

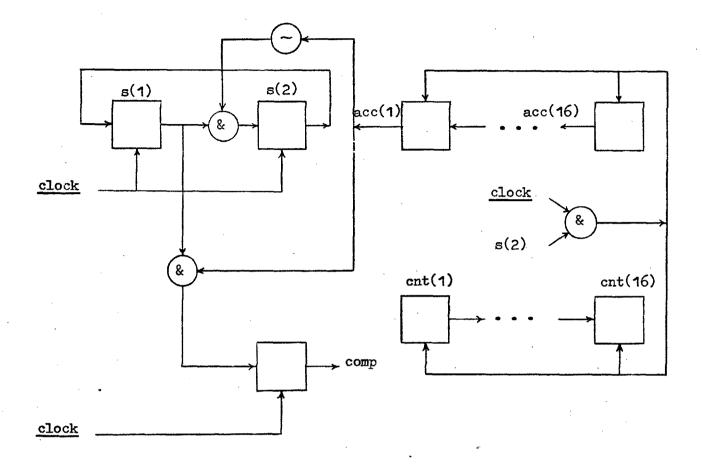

### 2. Parallel Networks

<parallel network> ::= <RT-operation>1[ {<RT-operation>}<sup>+</sup>]

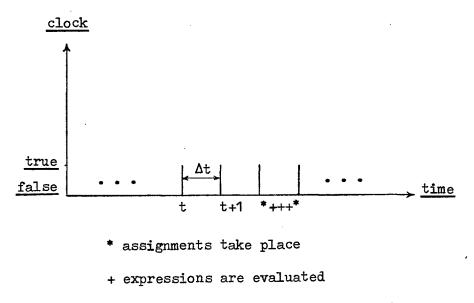

A 'parallel network' is enclosed in square brackets unless it is composed of only one operation. The operations will later be given the same control condition. By parallelism it is meant that the transfers take place in two steps:

- 1) all expressions (source vectors) are evaluated

- 2) destination vectors take on their values simultaneously.

That is, the textual ordering of the RT-operations in a parallel network is immaterial. Examples of parallel networks are given below:

<u>register</u> a(1:4), b(1:4), c(1:4), d;

- 1) a = b;

- 2) [a = b; b = a; d = and c;]

A parallel network is said to be activated when its control condition becomes <u>true</u>, in which case all the RT-operations composing the network are activated. For example, one of the results of activating (2) is that the contents of registers a and b are swapped. 3. Sequential Networks

<sequential network> ::= <parallel network>!({<parallel network>}\*)

A 'sequential network', which is an ordered list of parallel networks, is

enclosed in round brackets unless it is composed of only one parallel network.

Examples are:

<u>register</u> a(1:4), b(1:4), c(1:4), d;

- 1) a = b;

- 2) [a = b; b = a;]

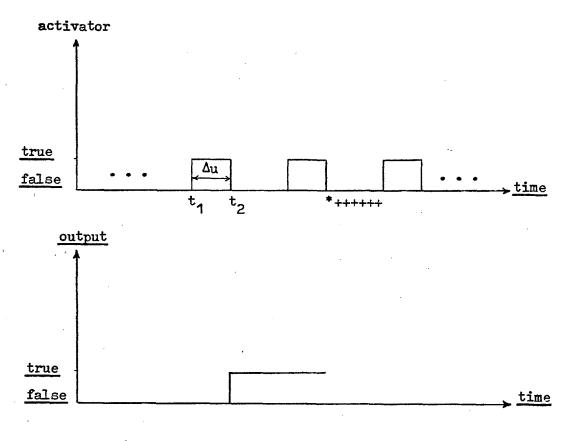

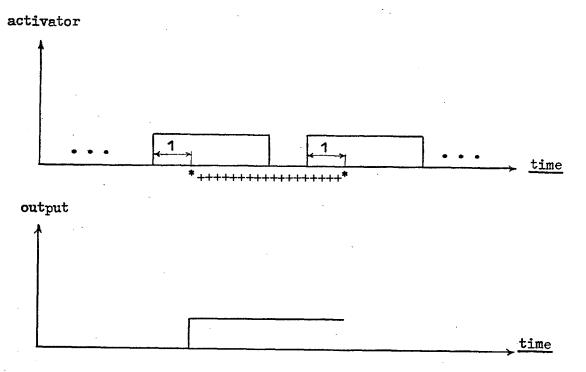

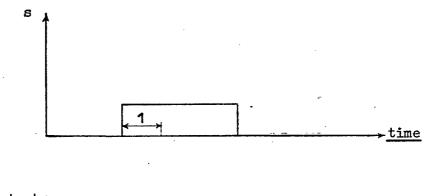

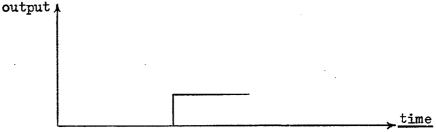

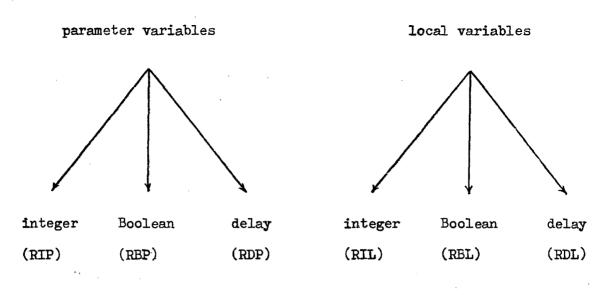

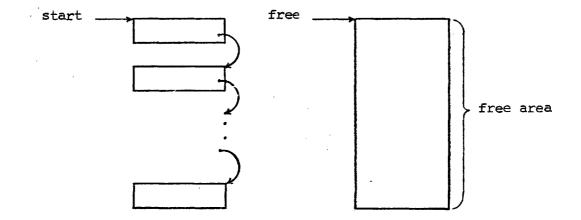

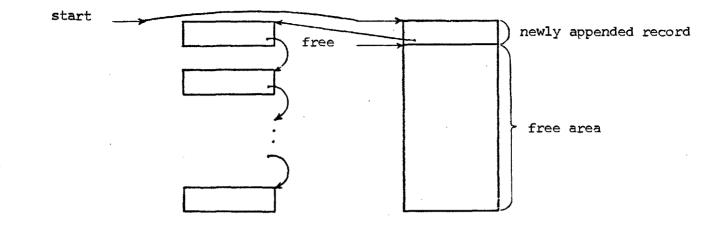

- 3) (d = not b; [c = d; a = b;] d = or a;)