# Imperial College London Department of Electrical and Electronic Engineering

# Online Timing Slack Measurement and its Application in Field-Programmable Gate Arrays

Joshua M. Levine

April 2014

Supervised by Professor Peter Y.K. Cheung

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London and the Diploma of Imperial College London The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

# Abstract

Reliability, power consumption and timing performance are key concerns for today's integrated circuits. Measurement techniques capable of quantifying the timing characteristics of a circuit, while it is operating, facilitate a range of benefits. Delay variation due to environmental and operational conditions, and degradation can be monitored by tracking changes in timing performance. Using the measurements in a closed-loop to control power supply voltage or clock frequency allows for the reduction of timing safety margins, leading to improvements in power consumption or throughput performance through the exploitation of better-than worst-case operation.

This thesis describes a novel online timing slack measurement method which can directly measure the timing performance of a circuit, accurately and with minimal overhead. Enhancements allow for the improvement of absolute accuracy and resolution. A compilation flow is reported that can automatically instrument arbitrary circuits on FPGAs with the measurement circuitry. On its own this measurement method is able to track the "health" of an integrated circuit, from commissioning through its lifetime, warning of impending failure or instigating pre-emptive degradation mitigation techniques.

The use of the measurement method in a closed-loop dynamic voltage and frequency scaling scheme has been demonstrated, achieving significant improvements in power consumption and throughput performance.

# Acknowledgements

I would like to thank my supervisor, Peter Cheung, for taking a chance on me when we first met in 2005, and for providing a research environment with immense intellectual freedom where my creativity could thrive. I am grateful to him and to my second supervisor, George Constantinides, for their insight, guidance and patience. From the inception of this project I have had the privilege of working closely with Ed Stott, my mentor and friend, and I look forward to our continuing collaboration. Thanks also go to the members of the "Reliability Club" and to our research group administrator, Wiesia Hsissen, for bringing order to the chaos.

To my colleagues and friends in the Circuits and Systems Research Group: thanks for the distractions, caffeine breaks, "Thirsty Thursdays" and "Doughts". I'd especially like to thank Adam Powell, Al Smith, David Boland, David Jones, Dom Buchstaller, Eddie Hung, James Davis, James Mardell, Peter Ogden, Rui Duarte, Sam Bayliss, Shane Fleming and Theo Drane; it has been a privilege to work alongside you and I have thoroughly enjoyed the experience. I am also grateful to Chris Chan and Ros Rathouse, for their friendship, advice and support.

Thanks also to my parents, Larry and Tessa, for teaching me the great value of knowledge and always encouraging me in its pursuit, and my brother, Adam, for helping me make this a thesis I am proud of. Special thanks to my girlfriend, Emma Bradley, for getting me through this challenging process, and tolerating me to the end. Final thanks goes to Belka the cat, for keeping me company and monopolising the keyboard!

None of this would have been possible without the funding provided by the EPSRC through grant EP/H013784/1, "Variation-Adaptive Design in FPGAs".

# Contents

| 1        | Intr | roducti | on                                       | 21 |

|----------|------|---------|------------------------------------------|----|

|          | 1.1  | Outlin  | e                                        | 22 |

|          | 1.2  | Publis  | hed Work                                 | 23 |

|          | 1.3  | Staten  | nent of Original Contributions           | 24 |

| <b>2</b> | Bac  | kgrour  | nd                                       | 26 |

|          | 2.1  | Introd  | uction                                   | 26 |

|          | 2.2  | Delay   | Variability and Timing Failure           | 26 |

|          | 2.3  | Source  | es of Variability in Integrated Circuits | 29 |

|          |      | 2.3.1   | Physical Variability                     | 29 |

|          |      | 2.3.2   | Environmental Variability                | 29 |

|          |      | 2.3.3   | Temporal Variability                     | 29 |

|          |      | 2.3.4   | Evaluation of Delay Variability          | 30 |

|          | 2.4  | Digita  | l Delay Measurement                      | 31 |

|          |      | 2.4.1   | Delay Inference                          | 31 |

|          |      | 2.4.2   | Frequency Sweep Based                    | 34 |

|          |      | 2.4.3   | Shadow Registers                         | 36 |

|          |      | 2.4.4   | Evaluation of Measurement Methods        | 40 |

|          | 2.5  | Conclu  | ısion                                    | 43 |

| 3        | Onl  | ine Sla | ack Measurement                          | 44 |

|          | 3.1  | Introd  | uction                                   | 44 |

|          | 3.2  | Princi  | ple of Operation                         | 44 |

|          |      | 3.2.1   | Blind Spot                               | 49 |

|     | 3.2.2  | Discrepancy Storage                   | 50 |

|-----|--------|---------------------------------------|----|

|     | 3.2.3  | Calibration                           | 51 |

|     | 3.2.4  | Measurement Accuracy                  | 54 |

|     | 3.2.5  | Dithering                             | 55 |

|     | 3.2.6  | RUM Selection                         | 58 |

| 3.3 | Measu  | rement Experiment                     | 59 |

|     | 3.3.1  | Temperature Control                   | 60 |

|     | 3.3.2  | Voltage Control and Power Measurement | 62 |

|     | 3.3.3  | Clock Generation                      | 62 |

|     | 3.3.4  | Benchmark Circuits                    | 62 |

|     | 3.3.5  | Benchmark Instrumentation             | 63 |

|     | 3.3.6  | Offline Measurement                   | 65 |

|     | 3.3.7  | Online Slack Measurement              | 66 |

|     | 3.3.8  | Slack Variation                       | 72 |

| 3.4 | Overh  | ead                                   | 75 |

|     | 3.4.1  | "Toronto 20"                          | 75 |

|     | 3.4.2  | "Functional"                          | 77 |

| 3.5 | Other  | Factors for Consideration             | 79 |

|     | 3.5.1  | Performing Measurements               | 79 |

|     | 3.5.2  | Measurement Latency                   | 80 |

|     | 3.5.3  | Path Excitation                       | 80 |

|     | 3.5.4  | Metastability                         | 81 |

| 3.6 | Future | e Work                                | 82 |

|     | 3.6.1  | Path Excitation                       | 82 |

| 3.7 | Concl  | usion                                 | 85 |

| OSI | M Sens | sor Insertion                         | 87 |

| 4.1 | Introd | luction                               | 87 |

| 4.2 | Mapp   | ing of OSM to FPGAs                   | 88 |

|     | 4.2.1  | Clock Generation                      | 88 |

|     | 122    | Shadow Register Manning               | ar |

|   | 4.3 | Online S     | Slack Measurement Insertion Tool           |

|---|-----|--------------|--------------------------------------------|

|   |     | 4.3.1        | RIPPL                                      |

|   |     | 4.3.2        | Tool Flow                                  |

|   |     | 4.3.3        | Flow Details                               |

|   | 4.4 | Results      |                                            |

|   |     | 4.4.1        | Area Overhead                              |

|   |     | 4.4.2        | Timing Overhead                            |

|   | 4.5 | Future '     | Work                                       |

|   |     | 4.5.1        | Mapping to Adaptive Logic Modules          |

|   |     | 4.5.2        | Shadowing Embedded Memory                  |

|   |     | 4.5.3        | Path Excitation                            |

|   |     | 4.5.4        | Razor                                      |

|   | 4.6 | Conclus      | sion                                       |

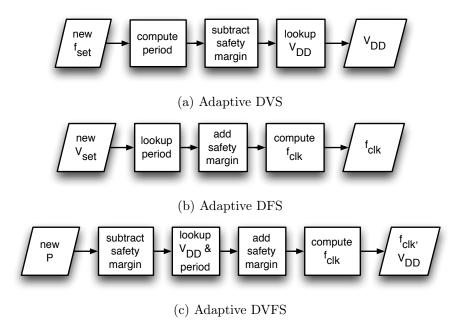

| 5 | Dyr | $\mathbf{v}$ | oltage and Frequency Scaling 115           |

|   | 5.1 | Introdu      | ction                                      |

|   | 5.2 | Backgro      | ound                                       |

|   |     | 5.2.1        | Dynamic Voltage and Frequency Scaling      |

|   |     | 5.2.2        | Summary                                    |

|   |     | 5.2.3        | Life Extension through DVS                 |

|   | 5.3 | Dynami       | ic Voltage and Frequency Scaling using OSM |

|   |     | 5.3.1        | Slack Measurement                          |

|   |     | 5.3.2        | Guardbanding                               |

|   |     | 5.3.3        | Hysteresis                                 |

|   |     | 5.3.4        | Control Algorithm                          |

|   | 5.4 | Experin      | nent                                       |

|   |     | 5.4.1        | Characterisation                           |

|   |     | 5.4.2        | Guardband, Step Size and Hysteresis        |

|   |     | 5.4.3        | Adaptive Scaling Lookup                    |

|   | 5.5 | Results      |                                            |

|   |     | 5.5.1        | Voltage and Frequency Scaling              |

| 6 | Cor | clusio | ns       |          |                       |      |  |      |  |       |       |  |   |  | - | 144 |

|---|-----|--------|----------|----------|-----------------------|------|--|------|--|-------|-------|--|---|--|---|-----|

|   | 5.8 | Conclu | usion    |          |                       | <br> |  | <br> |  |       |       |  | • |  |   | 142 |

|   | 5.7 | Future | e Work   |          |                       | <br> |  | <br> |  |       |       |  |   |  |   | 141 |

|   | 5.6 | Practi | cal Impl | ementat  | ion                   | <br> |  | <br> |  |       |       |  |   |  | • | 140 |

|   |     | 5.5.3  | Guard    | oand Co  | $\operatorname{st}$ . | <br> |  | <br> |  |       |       |  |   |  | • | 139 |

|   |     | 5.5.2  | Adapti   | ve Scali | ng .                  | <br> |  | <br> |  | <br>• | <br>• |  |   |  | • | 137 |

# List of Tables

| 2.1  | A comparison of the ability of the measurement methods to quantify sources      |       |

|------|---------------------------------------------------------------------------------|-------|

|      | of delay variation                                                              | 42    |

| 2.2  | A comparison of the attributes of the measurement methods                       | 42    |

| 3.1  | The blind spot locations for different discrepancy register clocks              | 50    |

| 3.2  | Resolution intervals for slack measurement quantities                           | 55    |

| 3.3  | STA timing report for intadd64, with an $f_{\rm clk}$ specification of 200 MHz. |       |

|      | The right hand side shows the computed effective delay and inclusive CDM,       |       |

|      | the minimum CDM that the sink register will be instrumented                     | 64    |

| 3.4  | STA estimates for the RUMs and shadow registers of intadd64 before and          |       |

|      | after instrumenting.                                                            | 64    |

| 3.5  | STA estimates and offline frequency sweep measurements for RUMs in intadd6      | 4. 66 |

| 3.6  | Online slack and shadow register-supported offline frequency sweep mea-         |       |

|      | surement for intadd64                                                           | 68    |

| 3.7  | Calibrated online slack and shadow register-supported offline frequency sweep   |       |

|      | measurement for intadd64                                                        | 70    |

| 3.8  | Measurements showing calibration offset resolution improvement through          |       |

|      | frequency dithering                                                             | 72    |

| 3.9  | Measurements showing resolution improvement with both calibration offset        |       |

|      | and OSM dithering.                                                              | 73    |

| 3.10 | The number of registers that require instrumenting for various Critical Delay   |       |

|      | Margins in the T20 benchmark set. For the minimum, mean and maximum,            |       |

|      | the percentages (in brackets) are treated independently                         | 78    |

| 3.11 | The number of registers that require instrumenting for various Critical Delay    |

|------|----------------------------------------------------------------------------------|

|      | Margins in the functional benchmark set. For the minimum, mean and               |

|      | maximum, the percentages (in brackets) are treated independently 79              |

| 4.1  | Base resource utilisation for the benchmarks in the functional benchmark set.108 |

| 4.2  | Area overheads for instrumenting the functional benchmarks for OSM with          |

|      | coverages between $5\%$ and $20\%$ CDM                                           |

| 4.3  | Timing overheads for instrumenting the functional benchmarks for OSM             |

|      | with coverages between $5\%$ and $20\%$ CDM                                      |

| 5.1  | A summary of DVFS methods, including OSM, and the operating margins              |

|      | that they can reduce                                                             |

| 5.2  | Resolution intervals for conservative slack measurement                          |

| 5.3  | The system can be controlled in one of three modes, depending on which           |

|      | parameter is constrained                                                         |

| 5.4  | Control variables and responses for power constrained DVFS                       |

| 5.5  | Theoretical and empirically tuned controller parameters                          |

# List of Figures

| 2.1 | CMOS inverter circuit                                                            | 26 |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | Vernier Delay Line from [23]                                                     | 33 |

| 2.3 | Block diagram showing the details of the FRD measurement circuit from [67].      | 35 |

| 2.4 | A circuit diagram illustrating the principle of TP measurement from [69]         | 36 |

| 2.5 | A Failure Prediction sensor from [2]                                             | 37 |

| 2.6 | A pipeline stage augmented with Razor from [25]                                  | 38 |

| 2.7 | The RazorII timing error detecting flip-flop from [18]                           | 39 |

| 3.1 | A typical synchronous circuit consisting of a block of combinatorial logic       |    |

|     | surrounded by registers. Bold lines indicate buses                               | 45 |

| 3.2 | Instrumenting a synchronous circuit with the addition of an OSM sensor. $$ .     | 45 |

| 3.3 | Details of the shadow register and associated circuitry for online timing slack  |    |

|     | measurement. The source register and logic has been removed for clarity          | 46 |

| 3.4 | Timing diagrams where shadow clock lead $(t_{\phi})$ does and does not result in |    |

|     | a discrepancy                                                                    | 47 |

| 3.5 | OSM instrumented buffer chain circuit                                            | 48 |

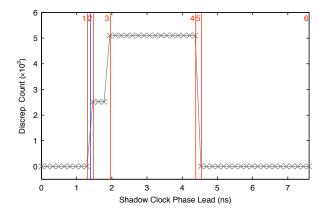

| 3.6 | An example discrepancy profile for buffer running at $f_{\rm sta}$ (128.52 MHz), |    |

|     | with regional annotations. The blue line indicates the measured slack, mid-      |    |

|     | way between the last zero and first non-zero discrepancy count $(d(t_{\phi}))$   | 48 |

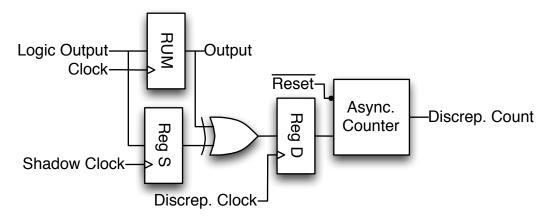

| 3.7 | The discrepancy output can be connected to an asynchronous counter to            |    |

|     | produce an error profile                                                         | 51 |

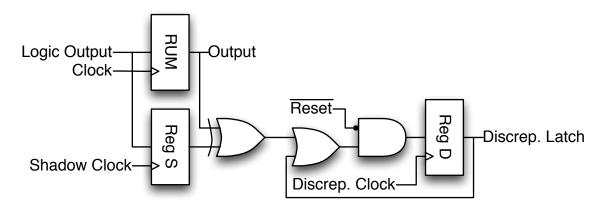

| 3.8 | Using a discrepancy latch rather than counter, which latches when a single       |    |

|     | discrepancy has occurred                                                         | 51 |

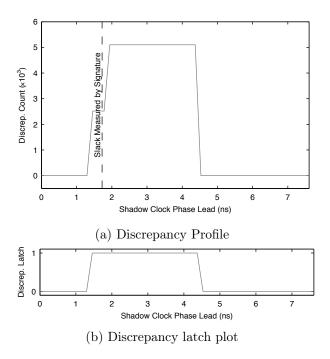

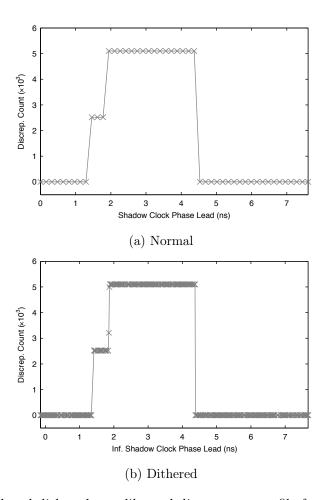

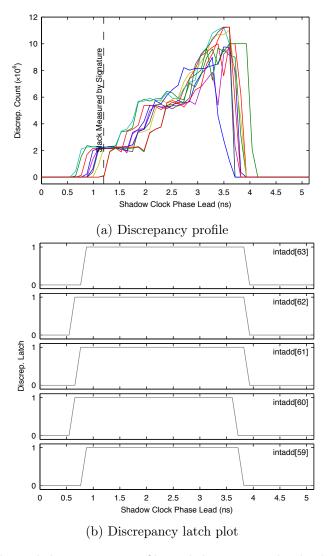

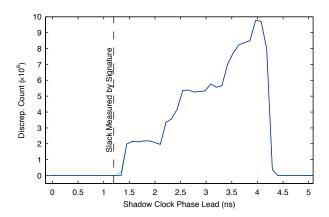

| 3.9  | Discrepancy profile and discrepancy latch plot for buffer operating at $f_{ m sta}$ |       |

|------|-------------------------------------------------------------------------------------|-------|

|      | (128.52 MHz). Also shown is overall circuit slack measured by Signature             |       |

|      | Analysis using an MISR                                                              | 52    |

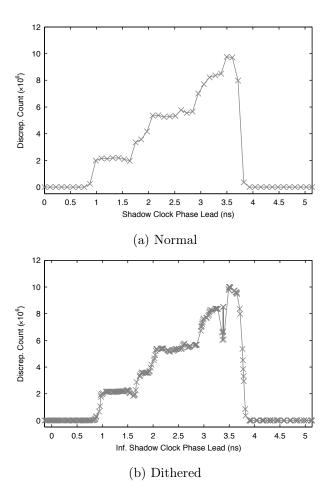

| 3.10 | Normal and dithered uncalibrated discrepancy profile for buffer clocked             |       |

|      | at $f_{\rm sta}$ of 128.52 MHz                                                      | 57    |

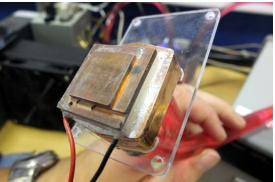

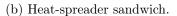

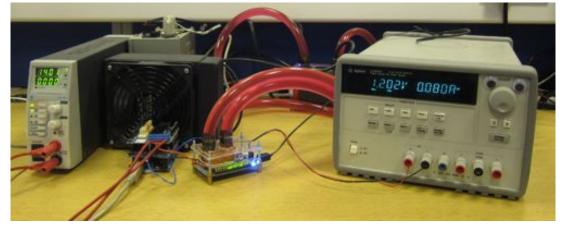

| 3.11 | Temperature and voltage controlled FPGA experimental hardware                       | 61    |

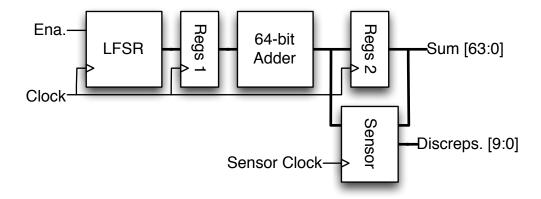

| 3.12 | A 64-bit unsigned adder instrumented with OSM                                       | 65    |

| 3.13 | Uncalibrated discrepancy profile and discrepancy latch plot for the OSM             |       |

|      | instrumented intadd64 circuit running at $f_{\rm sta}$ (190.69 MHz), with slack     |       |

|      | measured by Signature Analysis                                                      | 67    |

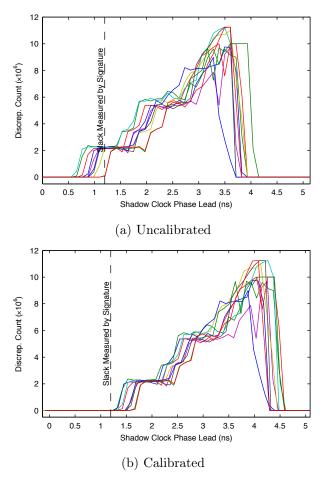

| 3.14 | Uncalibrated and calibrated discrepancy profiles for intadd64 operating             |       |

|      | at $f_{\rm sta}$ (190.69 MHz), with slack measured by Signature Analysis            | 69    |

| 3.15 | Normal and dithered uncalibrated discrepancy profile for the intadd[63]             |       |

|      | RUM in intadd64, clocked at $f_{\rm sta}$ of 190.69 MHz                             | 71    |

| 3.16 | Uncalibrated slack measurement response to clock period variation in intadd6        | 4. 73 |

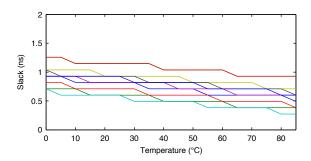

| 3.17 | Uncalibrated slack measurement response to temperature variation in intadd6         | 4. 74 |

| 3.18 | Uncalibrated slack measurement response to voltage variation in intadd64.           | 74    |

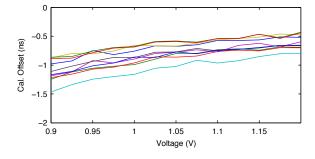

| 3.19 | Calibration offset variation due to voltage in intadd64                             | 74    |

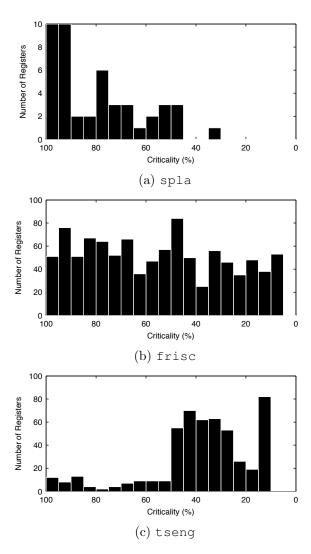

| 3.20 | Register delay distributions (as a percentage of the critical delay) for three      |       |

|      | T20 benchmarks                                                                      | 76    |

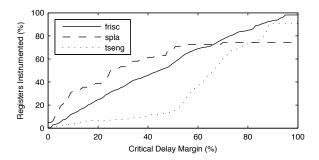

| 3.21 | Cumulative histogram showing the number of registers that need to be mon-           |       |

|      | itored in order to achieve a given CDM, as a percentage of the total number         |       |

|      | of registers in the circuit.                                                        | 77    |

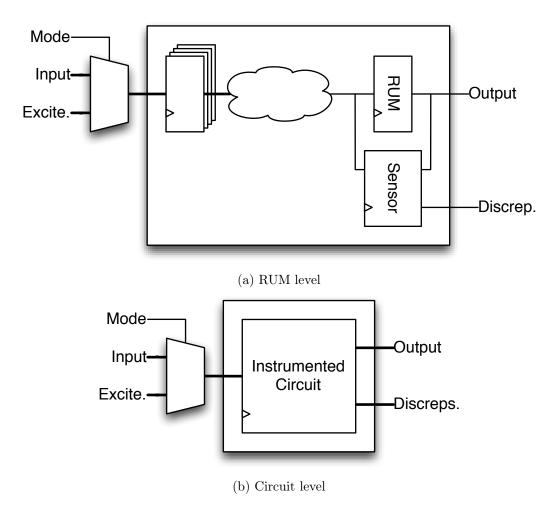

| 3.22 | RUM and circuit level excitation vector injection mechanisms                        | 83    |

| 3.23 | An example discrepancy profile showing slack measurement where critical             |       |

|      | path hasn't been excited in blue, and reconstructed tail in green                   | 85    |

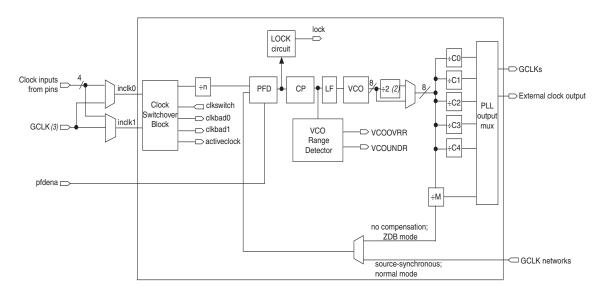

| 4.1  | A block digram of the Cyclone IV PLL from [4]                                       | 89    |

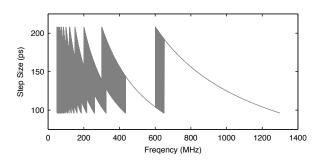

| 4.2  | Plot showing the step sized achieved for output frequencies with OSM opti-          |       |

|      | mised PLL configuration.                                                            | 90    |

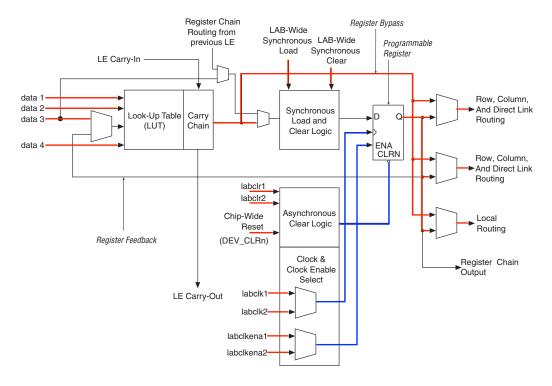

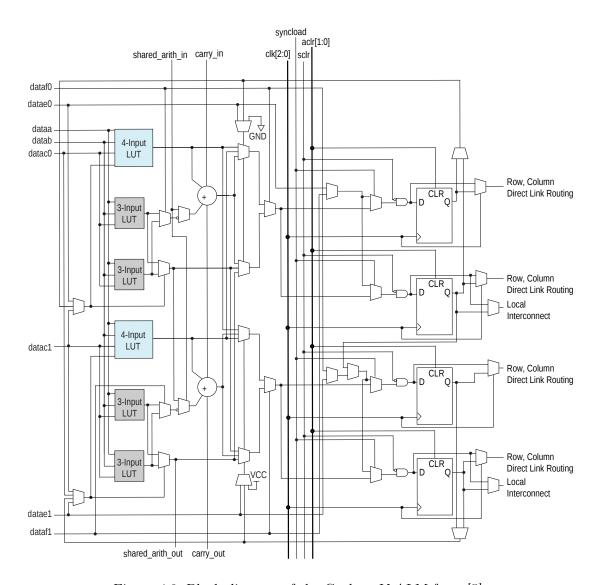

| 4.3  | The Cyclone IV Logic Element, with externally accessible signals in red and                  |    |

|------|----------------------------------------------------------------------------------------------|----|

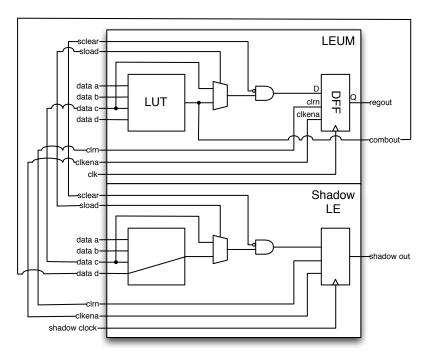

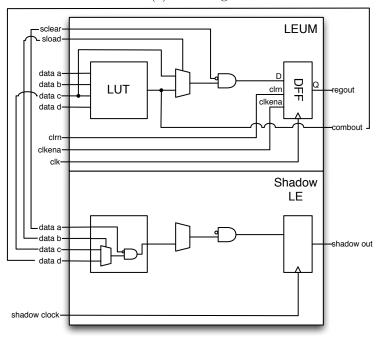

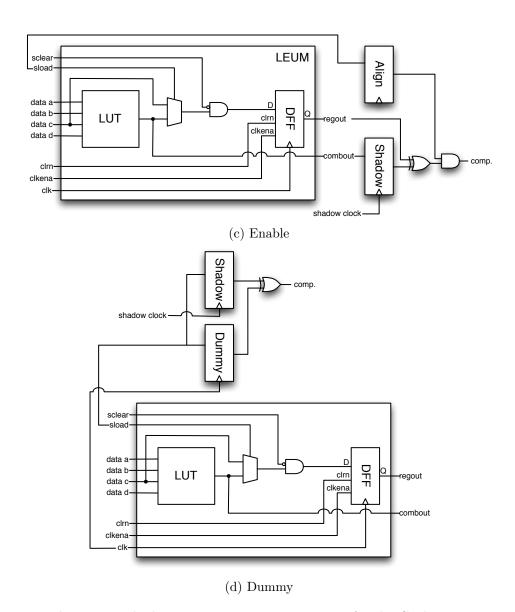

|      | signals accessible from inside the LAB in blue, from [4]                                     | 91 |

| 4.4  | The various shadow register mapping strategies for the Cyclone IV LE.                        |    |

|      | Where appropriate the shadow register has been shown outside of a LE,                        |    |

|      | and comparator and/or discrepancy register negated for the sake of clarity                   | 94 |

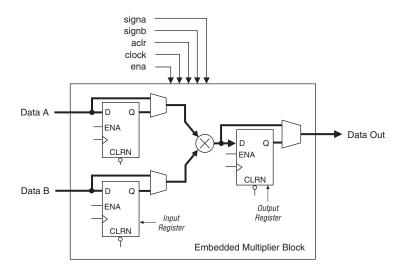

| 4.5  | The Cyclone IV embedded multiplier from [4]                                                  | 96 |

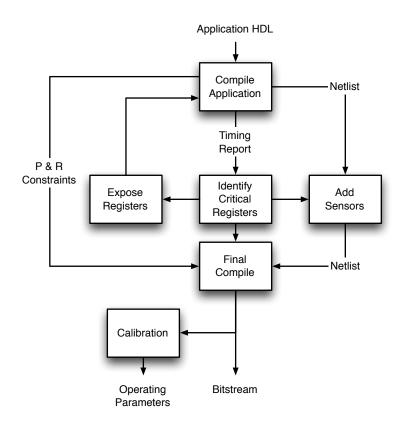

| 4.6  | The SMI compile flow. Details regarding the identification of critical regis-                |    |

|      | ters may be found in Section 3.2.6 and calibration in Section 3.2.3                          | 98 |

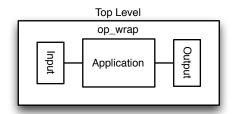

| 4.7  | Application circuit instantiated within wrapper                                              | 99 |

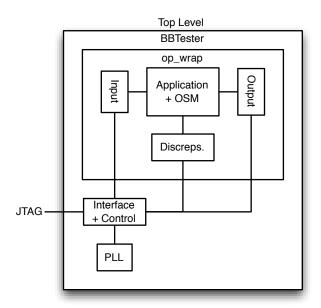

| 4.8  | Structure of the application circuit, within RIPPL after SMI                                 | Э7 |

| 4.9  | Block diagram of the Cyclone V ALM from [5]                                                  | 12 |

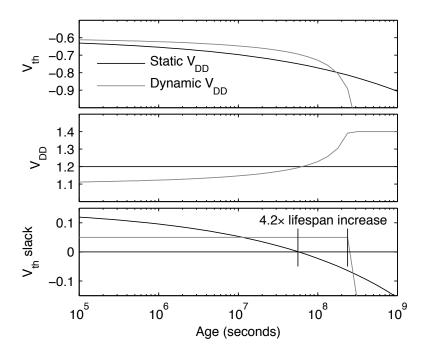

| 5.1  | DVS can be used to extend lifespan by scaling $V_{ m DD}$ to match changes in $V_{ m th}$ 12 | 21 |

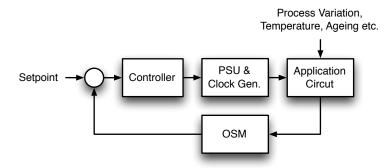

| 5.2  | Block diagram of DVFS controller                                                             | 26 |

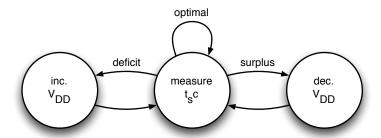

| 5.3  | State diagram for dynamic voltage scaling with static throughput constraint 12               | 27 |

| 5.4  | State diagram for dynamic voltage scaling with dynamic throughput constraint 12              | 28 |

| 5.5  | State diagram for dynamic voltage and frequency scaling with dynamic                         |    |

|      | power constraint                                                                             | 29 |

| 5.6  | The effect of voltage and temperature variation on critical path delay in                    |    |

|      | fpmult3215                                                                                   | 31 |

| 5.7  | The effect of voltage and frequency variation on power consumption in                        |    |

|      | fpmult32                                                                                     | 32 |

| 5.8  | Adaptive lookup for different operating modes                                                | 35 |

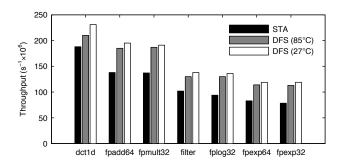

| 5.9  | Throughput comparison between nominal and DFS. Benchmarks achieve a                          |    |

|      | mean improvement of 38.9% at 27 °C and 30.7% at 85 °C                                        | 36 |

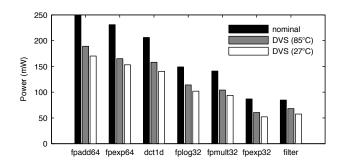

| 5.10 | Operating power comparison between nominal and DVS. Benchmarks achieves                      |    |

|      | a mean improvement of 33.5% at 27 °C and 24.9% at 85 °C $\ \ldots \ \ldots \ 13$             | 37 |

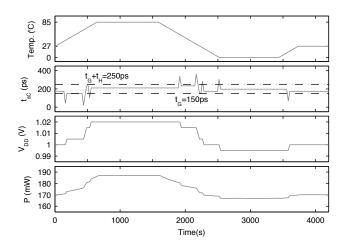

| 5.11 | Transient response to temperature fluctuation in DVS with fpmult32 at                        |    |

|      | 27°C                                                                                         | 38 |

| 5.12 | Transient response to throughput requirements in DVFS with fpmult32                          |    |

|      | at 27°C                                                                                      | 38 |

| 5.13 | Transient response to voltage requirements in DVFS with fpmult32 at $27^{\circ}C138$ |

|------|--------------------------------------------------------------------------------------|

| 5.14 | Transient response to power requirements in DVFS with fpmult32 139                   |

| 5.15 | Power reduction over nominal circuit operation with DVS of fpadd64 for               |

|      | a variety of guardbands at 27 °C                                                     |

| 5.16 | Stand-alone power supply with digital potentiometer allowing FPGA self-              |

|      | control of core voltage                                                              |

# List of Acronyms

ADC Analogue-to-Digital Converter

ALM Adaptive Logic Module

ASIC Application-Specific Integrated Circuit

**BRAM** Block Random-Access Memory

CAD Computer-Aided Design

CDM Critical Delay Margin

CMOS Complementary Metal-Oxide Semiconductor

**CP** Charge Pump

**CPU** Central Processing Unit

CUT Circuit Under Test

**DCT** Discrete Cosine Transform

**DFS** Dynamic Frequency Scaling

**DLL** Delay-Locked Loop

**DSP** Digital Signal Processing

**DVFS** Dynamic Voltage Frequency Scaling

**DVS** Dynamic Voltage Scaling

**EDA** Electronic Design Automation

FF Flip-Flop

FIFO First In, First Out

FP Floating Point

FPGA Field-Programmable Gate Array

FRD Failure Rate Detection

**HCI** Hot Carrier Injection

**HDL** Hardware Description Language

IC Integrated Circuit

IIR Infinite Impulse Response

ITRS International Technology Roadmap for Semiconductors

JTAG Joint Test Action Group

LAB Logic Array Block

LE Logic Element

**LEUM** Logic Element Under Monitoring

**LF** Loop Filter

LFSR Linear Feedback Shift Register

**LUT** Lookup Table

LZA Leading Zero Anticipator

LZC Leading Zero Count

MCNC Microelectronics Center of North Carolina

MISR Multiple-Input Signature Register

MOS Metal-Oxide Semiconductor

MSB Most Significant Bit

**NBTI** Negative-Bias Temperature Instability

nMOS N-Type Metal-Oxide Semiconductor

**OSM** Online Slack Measurement

PBTI Positive-Bias Temperature Instability

PC Personal Computer

**PFD** Phase-Frequency Detector

PID Proportional-Integral-Derivative

PLL Phase-Locked Loop

PMBus Power Management Bus

**pMOS** P-Type Metal-Oxide Semiconductor

PSU Power Supply Unit

PWM Pulse Width Modulation

**QSF** Quartus Settings File

QUIP Quartus University Interface Program

RAM Random-Access Memory

RIPPL Reliability Instrumentation Platform for Programmable Logic

**ROM** Read-Only Memory

**RUM** Register Under Monitoring

SMART Self-Monitoring, Analysis, and Reporting Technology

**SMI** Slack Measurement Insertion

SPI Serial Peripheral Interface

**SRAM** Static Random-Access Memory

SSTA Statistical Static Timing Analysis

**STA** Static Timing Analysis

TCL Tool Command Language

**TDC** Time-to-Digital Converter

TDDB Time Dependent Dielectric Breakdown

**TDL** Tapped Delay Line

**TP** Transition Probability

TRC tunable Replica Circuit

**USB** Universal Serial Bus

VCO Voltage-Controlled Oscillator

VDL Vernier Delay Line

VHDL VHSIC Hardware Description Language

VLSI Very Large-Scale Integration

VQM Verilog Quartus Mapping

# List of Nomenclature

$V_{

m DD}$  Circuit supply voltage

$V_{

m in}$  Circuit input voltage

$V_{

m out}$  Circuit output voltage

$t_{

m pd}$  Propagation delay

$C_{

m L}$  Output capacitance

$\boldsymbol{W}$  Transistor gate width

$\boldsymbol{L}$  Transistor gate length

$\mu$  Charge-carrier effect mobility

$C_{\mathrm{ox}}$  Oxide capacitance per unit area

$V_{

m th}$  Threshold voltage

$T_{

m clk}$  Clock period

$t_{

m cq}$  Flip-flop clock-to-q delay

$t_{

m su}$  Setup time

$t_{

m sk}$  Clock skew

$t_{\rm s}$  Timing (setup) slack

$f_{\rm clk}$  Operating frequency

$f_{

m max}$  Maximum frequency circuit operates correctly under given conditions

$f_{\rm sta}$  Maximum frequency as defined by timing model at  $V_{\rm nom}$

$f_{\rm cal}$  Calibration frequency

$f_{\rm set}$  Requested operating frequency

$t_{\phi}$  Shadow clock phase lead

$\Delta t_{\phi}(f)$  Phase lead step size for frequency f

$d_i(t_\phi)$  Discrepancy count of RUM i at phase lead  $t_\phi$

$t_{\rm sS,i}$  Timing (setup) slack at shadow register i

$t_{\mathrm{sR,i}}$  Timing (setup) slack at RUM i

$t_{dS,i}$  Effective delay at shadow register i

$t_{\mathrm{dR,i}}$  Effective delay at RUM i

$t_{\rm sC}$  Critical timing (setup) slack

$t_{

m dC}$  Critical effective delay

$\Delta t_{\rm cal}$  Clock period step size for calibration sweep

$t_{\rm RS,i}$  Shadow register delay offset for RUM i

$\Delta t_{

m dR,slow/fast}$  Percentage intra-die delay variation at the slow/fast corner

$f_{\rm in}$  PLL input frequency

$f_{\rm ref}$  PLL reference frequency

$f_{\rm vco}$  PLL voltage-controlled oscillator frequency

$f_{\mathrm{out}}$  PLL output frequency

$V_{\mathrm{nom}}$  Nominal operating voltage

$V_{\min}$  Minimum voltage

$I_{leak}$  Leakage current

$\Delta t_{

m clk}$  Clock period step size for frequency scaling

# $\Delta V_{\rm DD}$ Voltage step size for voltage scaling

$t_{\mathbf{G}}$  Timing (setup) slack guardband

$t_{\mathbf{M}}$  OSM latency

$t_{

m L}$  Voltage and frequency control latency

$t_{

m H}$  Timing (setup) slack hysteresis

$\boldsymbol{P}$  Operating power

$P_{

m set}$  Requested operating power

$P_{

m H}$  Power hysteresis

# 1 Introduction

Scaling the process technology used to manufacture integrated circuits ha's historically resulted in improvements in power consumption, switching performance and transistor density, as promised by Dennard [20]. This remains the driving force behind the semiconductor industry today. As these technologies have entered the nanometre scale, devices manufactured using them are increasingly experiencing the effects of delay variability. This variability is affecting the devices, not just at the time of manufacturing or commissioning, but during their lifetime, with an increased susceptibility to the effects of environment, operating conditions and degradation [74]. Newly manufactured devices already experience delay variation of as much as  $\pm 15\%$  [11], which can deteriorate further by an additional 20% during a 10 year operating life [65].

In order for circuits to function reliably, manufacturers must account for the worst-case delay variation using timing margins. As the variability increases, so to do these margins, eroding much of the improvements achieved by process scaling and potentially making it counter-productive. It may no longer be possible for margins alone to protect against this variability, as doing so would jeopardise the circuit's performance to too great an extent. The coupling between variability and reliability is dominating the benefit of scaling [31] and is a chief concern of the International Technology Roadmap for Semiconductors (ITRS), an organisation representing key industrial leaders worldwide.

The use of sensors to monitor how a circuit is being affected by variability offers part of a solution and may make it possible to improve the viability of continued process scaling. Sensors of this type have yet to be fully realised.

Since this variability typically impacts the circuit's delay, measuring this directly would provide the greatest insight. Timing (setup) slack is the difference between the time that data is required, and the time it is provided. A positive timing slack indicates that the circuit is operating safely, with a margin by which the delay can increase before causing failure. Measuring timing slack allows for monitoring of the "health" of a circuit and can provide an early warning of deterioration, trigging pre-emptive actions to avoid failure. These sensors form part of a new paradigm for circuit design know as "resilience", whereby systems are able to cope with stress and catastrophe though self-monitoring and adaptation.

This thesis outlines the Online Slack Measurement method (OSM), a technique which uses circuit level sensors to measure the timing slack at critical nodes in the circuit, thereby directly measuring the effects of delay variability. It can do so accurately and with a low overhead, both in terms of area and performance. A Slack Measurement Insertion (SMI) tool flow is described which allows for the measurement circuitry to be automatically added into arbitrary circuits implemented on Field Programmable Gate Arrays (FPGAs) with little-to-no manual intervention.

Dynamic Voltage and Frequency Scaling (DVFS), is an example of a resilient system, whereby the operating parameters of the circuit are controlled in response to measured changes in performance. This thesis demonstrates DVFS using OSM, which is capable of achieving significant improvements in power efficiency or performance in today's devices through the reduction of timing margins. It also has the potential to increase the lifetime of an integrated circuit through self-adaptation.

## 1.1 Outline

Chapter 2 gives an overview of sources of delay variability and the means by which the effects of this variability can be measured. It points to the need for a method of measuring the timing performance of a circuit directly, while it is operating, in order to establish how it is being affected by variability and from this how "healthy" it is.

Chapter 3 introduces Online Slack Measurement, a technique which is able to directly measure the timing slack in an online circuit, without impacting on its operation. Methods of enhancing this technique to improve accuracy and resolution are described, as is a technique for identifying which parts of the circuit should be instrumented for monitoring.

A variety of circuits are investigated to establish the relationship between delay distribution and amount of the circuit which must be instrumented.

Chapter 4 details how the Online Slack Measurement technique can be mapped to current FPGA architectures, and presents a tool, Slack Measurement Insertion, which can automatically add the measurement circuitry to arbitrary circuits with a minimal overhead, both in terms of the area and timing performance.

Chapter 5 uses Online Slack Measurement in a close loop to quantify the timing performance of the circuit and control its supply voltage and/or clock frequency in order to improve power efficiency, throughput or provide operation beneath a power envelope.

## 1.2 Published Work

The majority of the work presented in this thesis has been published following peer-review.

This section briefly describes the relevant publications.

The principle of Online Slack Measurement was presented at the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays in 2010 [37]. This included calibration and early work on frequency dithering.

In 2012 a paper was published in the IEEE International Symposium on Field-Programmable Custom Computing Machines that described the fully developed Online Slack Measurement technique, calibration, and methodology for the selection of registers for instrumenting [38]. Also included was an analysis of the overheads for monitoring circuits and a provisional study into the use of Online Slack Measurement for Dynamic Voltage and Frequency Scaling.

A paper describing the Slack Measurement Insertion tool flow, and mapping of Online Slack Measurement to the architecture of a current generation FPGA was published at the International Conference on Field Programmable Logic and Applications in 2013 [39].

Also in 2013, Online Timing Slack Measurement formed part of a paper published in the IEEE Design & Test of Computers [56]. This described Online Slack Measurement and its applications in the context of variation and reliability in FPGAs.

Dynamic Voltage Frequency Scaling using Online Slack Measurement automatically added to arbitrary circuits on FPGAs using Slack Measurement Insertion was published at the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays in 2014 [36].

Recently, a paper describing timing error detection using shadow registers in arbitrary circuits, which are instrumented automatically using RIPPL, was presented at the International Conference on Field Programmable Logic and Applications in 2014 [57].

## 1.3 Statement of Original Contributions

As evidenced by the series of associated publications, this thesis describes a number of original contributions. These are the work of the author except where stated otherwise and include:

- A novel method for measuring timing slack in circuits while they are operating and without disrupting this operation.

- The calibration of this measurement method to improve absolute accuracy.

- An analysis of the accuracy of the measurement method.

- A technique for improving the measurement resolution of the online timing slack measurement method.

- A method for the selection of important registers to be monitored by the measurement method.

- Mappings of shadow registers, to be used for the measurement technique or other applications, to a modern FPGA architecture.

- A tool flow for compiling the relevant hardware necessary for the timing measurement method into arbitrary circuits while minimising timing overheads.

- The use of online timing slack measurement for dynamic voltage and frequency scaling.

- A adaptation of the calibration technique to ensure conservative measurement when used for dynamic voltage and frequency scaling.

- Guardbanding techniques to ensure optimised and save circuit functionality under dynamic voltage and frequency scaling.

- Dynamic voltage and frequency scaling controllers for maximising throughput or efficiency, or providing operation under power constraints, either static or dynamic.

# 2 Background

## 2.1 Introduction

Despite manufacturers best efforts, no two integrated circuits are alike. They are affected by delay variation at the time of manufacturing and during the course of their operating life. This chapter reviews the literature relating to the sources of this variation, and methods by which it can be quantified.

# 2.2 Delay Variability and Timing Failure

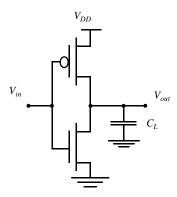

The propagation delay of transistors can be affected by a number of parameters. In synchronous circuits, variation in the propagation delay of the transistors which make up the circuit can result in timing failure, whereby the circuit ceases to function correctly. This delay variability may be investigated by analysing a simple CMOS inverter circuit, as shown in Figure 2.1.

Figure 2.1: CMOS inverter circuit.

This inverter is powered by voltage  $V_{\rm DD}$  with an input signal  $V_{\rm in}$  and output  $V_{\rm out}$  driving output capacitance  $C_{\rm L}$ . The propagation delay  $(t_{\rm pd})$  of this gate defines how quickly it

responds to a change at its input with a change at its output, the delay experienced by a signal when passing through the gate. Since the gate may exhibit a different response to rising or falling transitions these are defined separately as  $t_{\rm pd,LH}$  for low to high (rising) and  $t_{\rm pd,HL}$  for high to low (falling), where  $t_{\rm pd,LH}$  is the time taken for the output to rise from 10% to 90% of  $V_{\rm DD}$  when there is an appropriate change of input, and  $t_{\rm pd,HL}$  the inverse, falling from 90% to 10%. The overall propagation delay is the average of these as in Equation 2.1.

$$t_{\rm pd} = \frac{t_{\rm pd,LH} + t_{\rm pd,HL}}{2} \tag{2.1}$$

When considering delay variability, the relative change in propagation delay from a nominal baseline, due to changes in transistor parameters are of particular interest. It can be shown that the rising propagation delay is approximately equal to to the parameters in Equation 2.2 and falling Equation 2.3 [29], where W is the gate width, L the gate length,  $\mu$  the charge-carrier effective mobility,  $C_{\text{ox}}$  the gate oxide capacitance per unit area and  $V_{\text{th}}$  the threshold voltage.

$$t_{\rm pd,LH} \approx \frac{C_{\rm L}V_{\rm DD}}{\frac{W_{\rm pMOS}}{L_{\rm pMOS}}\mu_{\rm pMOS}C_{\rm ox}(V_{\rm DD} + V_{\rm th,pMOS})^2}$$

(2.2)

$$t_{\rm pd,HL} \approx \frac{C_{\rm L}V_{\rm DD}}{\frac{W_{\rm nMOS}}{L_{\rm LMOS}}\mu_{\rm nMOS}C_{\rm ox}(V_{\rm DD} - V_{\rm th,nMOS})^2}$$

(2.3)

From this he effect of variability on delay can be seen. A increase in L or decrease in W or  $C_{\rm ox}$  results in an increased delay. Increased  $V_{\rm th}$  or  $\mu$  also contributes to increased delay.  $\mu$  typically decreases with increasing temperature (except in cases of temperature-inversion), again resulting in increased delay and decreasing  $V_{\rm DD}$  has the same effect.

In a synchronous system, this increase in delay can result in timing failure. Timing failure occurs when the delayed data does not arrive at the register sufficiently before the clock edge to meet this register's setup requirement (Equation 2.4) where  $T_{\rm clk}$  is the clock period,  $t_{\rm cq}$  the clock-to-Q delay and  $t_{\rm su}$  the register's setup requirement.  $t_{\rm sk}$  is the clock skew, between the source and sink register and has various sources including: systematic (which exists under nominal conditions), random (due to variability in manufacturing

processes), drift (from slow time dependent environmental changes) and jitter (due to high frequency environmental variation).

$$T_{\rm clk} - t_{\rm sk} \ge t_{\rm cq} + t_{\rm pd} + t_{\rm su} \tag{2.4}$$

If data arrival at the flip-flop meets this setup requirement  $(t_{su})$ , the above inequality is satisfied and the circuit never experiences timing failure. The setup requirement is related to the probability of the flip-flop meeting its  $t_{cq}$  specification. If the setup requirement is not met, there is a non-zero probability of timing failure, which increase the more  $t_{su}$  is violated. This may result in the flip-flip latching either a previous or indeterminate value, or becomes metastable, requiring an unpredictable amount of time before settling on an output value. The flip-flip becoming metastable can result in timing failure occurring in subsequent flip-flops, which can also become metastable, resulting in complete failure of the circuit.

The difference between the time that data is required  $(T_{\rm clk} - t_{\rm sk})$  and the time that it is provided  $(t_{\rm cq} + t_{\rm pd} + t_{\rm su})$  is the setup slack, hereon referred to as timing slack  $t_{\rm s}$ . A positive timing slack implies that the combined delay to the register can be increased up to  $t_{\rm s}$  before timing failure occurs. A negative slack implies that the delay is too great for the chosen clock period, and incorrect values are being latched.

Measuring the combined effect delay, setup time and skew  $(t_{cq}+t_{pd}+t_{su}+t_{sk})$ , henceforth referred to as effective delay, or timing slack in a newly manufactured integrated circuit allows us to establish the effect of variability on the timing performance of the circuit. Monitoring this through the life of the device measures the impact of environmental and temporal variability. As the combined delay nears the clock period, or the slack tends towards zero, timing failure becomes imminent. Thus, monitoring of delay or slack in an integrated circuit is an excellent metric for the "health" of this circuit.

Timing margins are additional slack added to ensure that timing failure does not occur despite delay variability. Manufacturers use these timing margins to achieve sufficient parametric yield (the number of circuits that meet their specification). These margins impose worst-case functionality on devices, even in better-than worst-case conditions, resulting in increased power consumption and decreased performance.

# 2.3 Sources of Variability in Integrated Circuits

The behaviour of integrated circuits is primarily affected by three sources of variability: physical, environmental and temporal [74]. The effect of these sources of variation is expected to increase with process scaling [42, 10, 53].

#### 2.3.1 Physical Variability

Process variation is the parametric variation of components in integrated circuits, due to variability in fabrication. It results in variation in parameters including gate oxide thickness, dopant concentration and device geometry and can have an effect on threshold voltage [66]. Process variation can be correlated at the wafer, between dies (inter-die), within a die (intra-die) or uncorrelated (stochastic). In current process technologies, physical variability is responsible for as much as a  $\pm 15\%$  variation in circuit delay at the time of manufacturing [11].

### 2.3.2 Environmental Variability

Environmental variability includes variations in environmental and operational factors, both within and external to the integrated circuit. External factors include fluctuations in supply voltage and package temperature. Internal effects are due to coupling within the circuit and result in delay uncertainty. They are typically high frequency, manifesting as noise, and include: thermal coupling (self-heating [9]), voltage coupling (voltage droop [47]), clock jitter [28] and inductive/capacitive coupling (crosstalk [43]).

## 2.3.3 Temporal Variability

Temporal variability refers to degradation, which can occur gradually over time, or suddenly, resulting in catastrophic failure. It is manifested as a change in circuit parameters or functionality and is due to a number of physical effects [54].

Negative Bias Temperature Instability (NBTI) has been shown to be the dominant effect in current process technologies [51, 14]. It is caused by trapped charges or defects in the interface region, from negative gate-to-source voltages and as such primarily affects pMOS transistors. It results in a gradually increased threshold voltage and reduced channel mobility. Degradation due to NBTI occurs all the time the transistor is turned on, not just during switching. Positive Bias Temperature Instability (PBTI) is the equivalent mechanism in nMOS transistors but currently has negligible effect [35].

Hot Carrier Injection (HCI) is the result of defects being accumulated in the interface between the channel and gate and causes a gradual increase in threshold voltage and reduction in mobility. HCI is dependent on the drain current and predominantly occurs during switching [27].

Time Dependent Dielectric Breakdown (TDDB) results from a breakdown in the gate oxide [72]. In mild cases this can lead to an increase in leakage current, in more sever cases failure in the transistors ability to switch. Like NBTI this is TDDB is driven by gate potential and occurs whenever the transistor is on.

Electromigration is caused by the movement in metal ions in conductors, eventually leading to the creation of open and short circuits as these ions erode or build up [16].

The same degradation mechanisms are not responsible for both gradual deterioration and catastrophic failure. Mechanisms that cause variation in threshold voltage  $(V_{\rm th})$ , such as NBTI, PBTI and HCI, result in a gradual deterioration in switching performance. Catastrophic failure is caused by TDDB and electromigration, although the physical mechanisms by which this occurs differ.

Experimentation has show NBTI to be the primary factor resulting in degradation in current FPGA technologies [59] and that, while degradation is difficult to model, it is repeatable, being highly dependent on data, supply voltage, temperature and circuit structure [58]. NBTI has been shown to cause shifts in threshold voltage ( $V_{\rm th}$ ) of up to 50 mV over an operating lifespan of 10 years in 65 nm technologies. This translates to more than 20% deterioration in circuit operating speed [65].

#### 2.3.4 Evaluation of Delay Variability

Process scaling results in an increase in all sources of delay variability as transistor parameters such as channel length and threshold voltage spread. It is becoming a key factor in the development of mainstream digital circuits. As Dennard's Constant Field Scaling

came to an end with 90nm process technologies, the return to Constant Voltage Scaling has resulted in greater degradation due to increased electric fields. Timing margins must already accommodate delay variations of up to 30% for physical variability and an addition 20% for temporal variability. As the timing margins grow further, the benefits of scaling will no longer be realised; there is thus a requirement for new techniques, from transistor technology upwards. Delay measurement and monitoring is one area in which the development of new methods could prove valuable in addressing this.

# 2.4 Digital Delay Measurement

Measurement of the delay of digital circuits is an active area of research. These measurements are used for a variety of purposes including characterisation of variability and measurement of circuit performance. The primary methods of measuring delay are discussed below.

### 2.4.1 Delay Inference

These dedicated delay measurement circuits are used to characterise an integrated-circuit die. From these measurements the behaviour of an application circuit on the same die can be inferred.

#### Ring Oscillator

The Ring Oscillator remains the industry standard for characterising the effect of intra-die process variation and chipwide temperature and voltage variation in integrated-circuits [52]. The ring oscillator consists of an odd number of inverters, connected into a ring. The output of the last inverter is the inverse of the input, and feeding this back to the first inverter results in the ring oscillating freely at a frequency determined by the delay of the inverter elements.

The frequency can be generalised as in Equation 2.5 where f is the oscillation frequency, n the number of inverters and  $t_{\rm pd}$  the propagation delay of a single inverter. The frequency of the output can be measured using a simple counter. Typically a large number of inverters

are used in order to keep the oscillation frequency well within a measurable range.

$$f = \frac{1}{T} = \frac{1}{n(2t_{\rm pd})} \tag{2.5}$$

Through carefully controlled experiments ring oscillators are capable of independently measuring delay, static and dynamic power and temperature [73]. However, the ring oscillator is not without significant weakness. The free running nature makes it susceptible to self-heating due to dynamic power dissipation and it is not possible to distinguish the difference in propagation delay between rising and falling transitions, only the average, which may be significantly faster than the worst-case delay.

#### Time to Digital Converter

Time to Digital Converters (TDC) provide a method for precisely measuring the delay of the components they are made up from and providing this in a digital representation. They can also be used to measure the propagation delay of a signal through a Circuit Under Test (CUT). They are typically constructed from registers and delay elements (usually buffers) and, like ring oscillators, can be used to measure the effect of intra-die process, temperature and voltage variation, and degradation when measuring a CUT.

Tapped Delay Lines (TDL) [48] consist of a chain of delay elements, with registers D-inputs tapped between them. A measurement is started by pulsing the input to the delay chain high and stopped by pulsing the clock input of the registers high. The stored bit pattern corresponds to the distance that the start pulse has propagated through the delay chain when the measurement is stopped. The delay of the buffer chain can be measured by pulsing the start and stop at a known time interval, and the delay of a CUT by generating a start pulse when the signal enters, and a stop pulse when the signal has propagated through the CUT.

The resolution of the TDL is dependent on the delay of the individual elements and the total delay which can be measured, the delay of the combined chain.

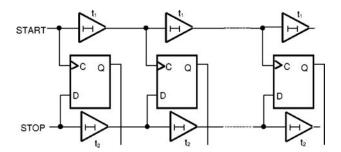

A Vernier Delay Line (VDL)[23], as shown in Figure 2.2, is an enhancement of the TDL which improves measurement resolution. The clock input of the registers taps into an additional chain of delay elements, which have a different delay  $(t_1)$  to those of the

D-inputs  $(t_2)$ . Here, the VDL is started by pulsing the clock input chain and stopped by pulsing the D-input chain. As the start and stop pulses propagate through their respective chains the time difference between the pulses is decreased in each Verner stage. This improves the time resolution to  $t_1 - t_2$  when  $t_1 > t_2$ .

Figure 2.2: Vernier Delay Line from [23].

Where TDC are used to measure a circuit's propagation delay they must be calibrated to remove the effect of variability on the TDC itself. This can be conducted by repeatedly measuring a known time interval. Alternatively, where possible, a Delay Locked Loop (DLL) can be used to bias the delay elements in a closed-loop, actively compensating for any variation in the delay of the TDC itself.

TDC circuits are able to measure their own delay, or the delay of a CUT, accurately and with a high resolution. The primary limitation is difficulty in the generating the of the start and stop signals which must have identical skew so as to cancel out.

## Tunable Replica Circuit

Tunable replica circuits (TRC) allow for degradation in the application to be inferred by exploiting its repeatability. Replica circuits are either designed to be particularly susceptible to the different sources of degradation, or replicate the functionality of critical paths from the application circuit. The replica circuits are excited with either stress data that is worst-case for degradation, or vectors from the application circuit, and their performance monitored with TDC [22] or timing error detection circuits like those described in Section 2.4.3 [61, 60].

The worst-case data for degradation depends on the dominant source of degradation. Currently, this is NBTI, which affects pMOS transistors subjected to negative gate-tosource voltages  $(V_{gs})$ . In the case of a CMOS inverter manufactured in current process technologies, the worst-case data for degradation would be a zero input.

The measurement methods discussed above (i.e. ring oscillators and TDCs) are unable to determine degradation as they do not share the structure of the application circuit, or data driving it. TRCs, combined with a measurement technology, have the capability to infer degradation, in addition to being able to quantify intra-die process variation and chipwide temperature and voltage variation with a reasonable cost. The accurate this degradation inference is uncertain and has not been well explored. Measuring the application circuit directly, using the methods discussed below, overcomes the requirement for this inference.

### 2.4.2 Frequency Sweep Based

These techniques share in common the introduction of timing failure in the circuit to measure delay. As such, they are not suitable for applications where the circuit needs to continue operating correctly while measurement is conducted.

#### Signature Analysis

Timing measurement using signature analysis exploits the fact that a functioning circuit, configured in the same state and receiving the same set of input data, will produce the same output [32]. The output of the CUT is analysed, either by storing the vectors in a memory, or generating a signature. A signature generator such as a Multiple-Input Signature Register [24] can be used, either internal or external to the device. Using a signature generator simplifies comparison and can improve the time it takes to conduct a measurement as the finite memory would have to be copied during measurement and compared for each output value.

The CUT is clocked at a frequency which is known to be safe, and excited with a set of input test vectors, which can be pre-prepared, or generated procedurally at test time. A Linear-Feedback Shift-Register (LFSR) [7] is suitable as it is deterministic and will produce the same input after re-initialising with the same seed. The CUT is run for a fixed number of clocks cycles, and the output recorded. It is reset, and the clock period decreased.

This process is repeated until such a time as the output differs from that of the previous

clock period. Timing failure has occurred and thus the overall delay of the circuit is between the current and previous clock period.

Signature analysis is suitable for measuring the delay of most CUTs. In complex CUTs care must be taking in selecting the input vectors and measurement duration in order to provide an assurance that the critical path of the circuit has been measured.

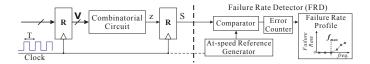

#### Failure Rate Detection

In failure rate detection (FRD) [67], a CUT is sandwiched between two registers which are driven by a variable frequency clock generator as shown in Figure 2.3. An input stimlus generator excites the CUT and the clock frequency is gradually increased, from that at which the circuit is know to work to an upper bound. Timing failure in the CUT is detected by comparing to an at-speed reference generator and the number of errors for each frequency are accumulated by an error counter into an error histogram.

Figure 2.3: Block diagram showing the details of the FRD measurement circuit from [67].

The frequency at which the circuit fails timing, and therefore the delay of the CUT can be found from this histogram. Deriving this from a histogram rather than the point at which the first failure occurs provides greater accuracy and for the measurement and normalisation of clock jitter.

FRD provides a method for measuring real circuits, producing meaningful and realistic characterisation. Unlike Signature Analysis it does not require that the input vectors are identical for each frequency, and the hardware overhead of the reference generator and comparator circuitry is lower than that of an MISR. When used for process characterisation, this allows for more CUTs and associated measurement circuitry to be placed on a single device and finer granularity characterisation to be conducted. However, FRD is limited to testing only one output register at a time and cannot directly support multipath circuits.

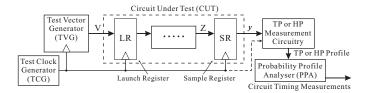

### Transition Probability

Transition probability (TP) [70, 69] is a low overhead means of measuring delay in combinatorial circuits. It is based on the observation that a circuit exercised with vectors of a fixed transition probability will output vectors of a constant transition probability until a timing error occurs, which will result in a change of output transition probability.

Figure 2.4: A circuit diagram illustrating the principle of TP measurement from [69].

A schematic of TP is shown in Figure 2.4. A CUT is connected to a test vector generator and launch register on its input, and a sample register, and measurement circuitry on its output. This measurement circuitry consists primarily of a transition counter and accumulator.

As in the other frequency sweep measurement methods, the circuit is stimulated with input vectors and the clock frequency gradually stepped up. The output transition probability for each frequency is recorded in the accumulator from which the delay of the circuit can be established, which is aided by the presence of clock jitter and an asymmetry between rising and falling delays. Tuning the transition probability of the input vectors improve the accuracy of measurement and can be conducted automatically [68].

Transition probability offers high accuracy characterisation of real circuits, which can be treated as a black-box. It has a lower overhead than the other frequency sweep methods and does not require that the circuit is exercised with a fixed set of input vectors, just that these vectors have the same transition probability.

#### 2.4.3 Shadow Registers

The techniques described in this section use additional registers, which "shadow" chosen registers in the application circuit. These shadow registers share some of their inputs with the main register that they are shadowing and, depending on the relationship of these inputs, can inform of impending timing failure or the occurrence of timing errors. While

not strictly timing measurement, they provide information relating to timing failure of the circuits which they are monitoring.

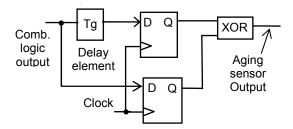

#### Failure Prediction

Failure Prediction [2], provides a warning when a specified guardband has been violated, indicating impending timing failure. Also known as "canary circuits" [34], named after the Miner's Canary which would be taken into a coal mine as an early warning of the presence of toxic gasses, these shadow registers are configured to be more timing critical than the register they shadow, so that timing failure occurs sooner when the circuit's delay increases.

Figure 2.5: A Failure Prediction sensor from [2].

Here, the shadow register shares both the D-input and clock of the main register, but with additional delay inserted into the path of the D-input (see Figure 2.5). This additional delay causes the shadow register to be more timing critical than the main, and fail timing before it.

When there is sufficient slack for both to registers operate correctly, they both latch the same value which is indicated by comparison. When the circuit delay is increased sufficiently, the shadow register will latch the previous value and comparison indicates a guardband violation. The size of the guardband is configured as the amount of delay inserted to the shadow register's D-input.

In some circumstances it is not possible to reliably introduce this additional delay. As an alternative, the clock to the shadow register can be advanced, such that it latches sooner, achieving the same effect [6, 8]. This may be less susceptible to variation, thus achieving more accurate detection. Additional registers can be added with gradually increasing guardbands to provide more timing information [33].

Care must be taken when placing and connecting the shadow registers, so that they are near to the main register, or so that additional path to the shadow register is accounted for.

Failure prediction allows for the monitoring of registers in a circuit at a relatively low cost. It informs when the delay of this circuit exceeds a configured safe value, violating a guardband. It monitors the actual paths of interest, not a different circuit somewhere else on the die, and so can detect directly, guardband violations due to process variation, changes in operating conditions and degradation.

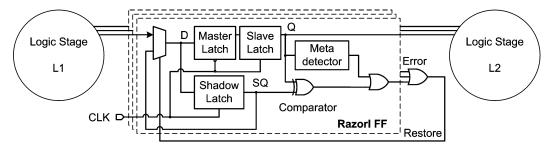

#### Razor

Razor [25] is a flip-flop capable of detecting and responding to the introduction of timing errors. It is intended for use in processors and the accompanying circuitry exploits features commonly available in these.

The Razor flip-flop is shown in Figure 2.6, it consists of a main pipeline register which is rising edge triggered. This register is augmented with a shadow register which samples on the clock's falling edge. This gives the shadow register additional time (corresponding to half the clock period) to capture the correct state of the data. The Razor flip-flop flags an error when the two registers latch different data, implying that a timing violation has occurred in the main register.

Figure 2.6: A pipeline stage augmented with Razor from [25].

The incorrect value in the main register must now be corrected before it propagates to the next pipeline stage. The error signal is ORed with the signals from all other Razor flip-flops and used to stall, or insert a bubble into the pipeline. The correct value must now be reinserted into the main register from the shadow in the same clock cycle. Since timing errors may occur in the main register, there is a possibility of this becoming metastable. This makes it impossible to determine by comparison if the latched value is correct. In an attempt to mitigate this risk, a metastability detector is used in the comparator circuit, detecting and triggering correction.

There is a risk that the shadow register, driven by a delayed clock, may latch a value from a short path of the subsequent clock cycle, which would present as a timing failure in the current clock cycle, resulting in a false-positive measurement. This is overcome by applying minimum path length (hold) constraint to the circuit which results in the introduction of buffers to short paths.

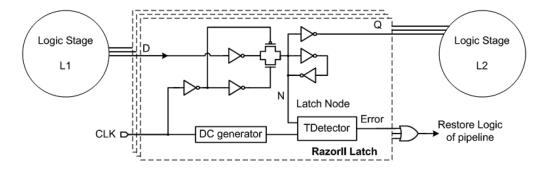

Figure 2.7: The RazorII timing error detecting flip-flop from [18].

Difficulties in the implementation of the metastability detection and restore circuitry (which is liable to becoming timing critical) led to the development of the RazorII flip-flop as shown in Figure 2.7. This performs only error detection, passing responsibility for correction onto the processor architecture. The RazorII flip-flop uses a level sensitive transparent latch instead of main flip-flop. The latch becomes opaque when the clock is low, so never closes when data edges can occur, mitigating the risk of metastability. Timing faults are flagged by a late transition detection triggered by the rising clock edge. The extent of the transition detection window is dictated by the clock duty cycle and hold constraints must still be applied to the circuit in order to avoid false positive error detection due to short paths.

The ability to detect timing failure provided by Razor is the pinnacle of timing measurement technology. Timing faults introduced by all forms of delay variability, including single cycle nose effects can be detected. Combining Razor with closed-loop dynamic voltage and frequency scaling gives almost all of the benefit of asynchronous techniques, without the prohibitive changes in design methodology. It is a highly appealing concept, but does come with some implementation issues related to design requirements and the need to correct timing errors that have been detected:

- The application of hold constraints will increase the area and power consumption of the design.

- Error recovery is either difficult to design or takes many clock cycles.

- Issues with metastability in the main paths of the circuit, or in the case of RazorII, complicated clocking.

- Requires modification to manufacturers highly optimised processor pipeline structures.

Razor has yet to be demonstrated on arbitrary (non-processor) circuits. It is expected that the overhead of implementing timing error recovery in circuits without existing replay/recovery would be prohibitive. The introduction and detection of timing errors makes Razor non-deterministic and unsuitable for tightly coupled systems and those with hard real-time constraints.

### 2.4.4 Evaluation of Measurement Methods

The advantages and disadvantages of the aforementioned measurement methods may be compared in the context of the following applications:

Process Technology Evaluation The evaluation of the delay variability characteristics of new process technologies requires simple circuit which are manufactured on test chips. This is historically the mainstay of ring oscillators but their weaknesses (self-heating and averaged rise/fall time) make TDCs an appealing alternative. While slightly more complex, TDCs such as Tapped Delay Lines used to measure the propagation delay of a reference pulse are not thwarted by these weaknesses.

Circuit Timing Measurement It is often desirable to establish the timing performance of a manufactured circuit under various operating conditions (e.g. in order to measure

timing at the design corners). Doing so requires a non-invasive method, which does not require altering of the circuit and can be used with black-box. Both Signature Analysis and TP can be used although the latter achieves this with a lower overhead and reduced measurement time as the circuit does not need to be exercised with a fixed set of input vectors.

Circuit timing measurement may also be useful in other applications, where it can be used to provide highly accurate calibration measurements. Here all techniques are applicable as smaller elements of a large circuit are being measured, with FRD having the lowest overhead, particularly where the at-speed reference generator circuitry is already implemented.

"Health" Monitoring This is becoming increasingly important as the magnitude of temporal variation increases. It is used to provide an indication of imminent timing failure as setup slack is consumed. In principle, any of the online measurement methods which can establish the effect of degradation can be used, however it is difficult to account for mismatches between the intra-die, temperature and voltage variability and degradation between the TRC and application circuit. As such direct measurement is preferable, leaving failure prediction as the desirable option.

Failure prediction only provides a pass/fail indication of circuit health. A technique that is able to perform similar direct, online measurements, but continuous with high accuracy would be of benefit.

Dynamic Voltage and Frequency Scaling This is an adaptive technique whereby the operating parameters of the circuit and controlled in a closed-loop using circuit performance measurements. Any of the online measurement methods described previously can be used for DVFS, however the more sources of delay variability that can be captured by the measurement, the greater the timing margin that can be recovered.

Razor is at the pinnacle, by detecting timing errors that have occurred it is able to remove all timing margins. The circuit is tuned so that it functions "on the razor's edge", with variations such as noise or excitation of a rarely triggered critical path sufficient to cause a timing error. In some applications (e.g. computer vision) this

error need not be corrected and is simply fed back for control, however, in most cases the application is intolerant to error and it must be corrected. The controller balances overhead of correcting the error to achieve optimum throughput.

The cost of implementing Razor, in terms of area, performance and design effort is substantial, particularly in arbitrary circuits. Taking this into account, similar improvements could be achieved using a direct, online timing measurement method with a lower overhead.

Further discussion of DVFS can be found in Section 5.2.

Table 2.1: A comparison of the ability of the measurement methods to quantify sources of delay variation.

|                      | Intra-Die<br>Variation | Inter-Die<br>Variation | Stochastic<br>Variation | Degradation | Temperature | Voltage | Noise |

|----------------------|------------------------|------------------------|-------------------------|-------------|-------------|---------|-------|

| Ring Oscillator      | ✓                      |                        |                         |             | <b>√</b>    | ✓       |       |

| TDC                  | ✓                      |                        |                         |             | ✓           | ✓       |       |

| $\operatorname{TRC}$ | ✓                      |                        |                         | ✓           | ✓           | ✓       |       |

| Signature Analysis   | ✓                      | ✓                      | ✓                       | ✓           | ✓           | ✓       |       |

| FRD                  | ✓                      | ✓                      | ✓                       | ✓           | ✓           | ✓       |       |

| TP                   | ✓                      | ✓                      | ✓                       | ✓           | ✓           | ✓       |       |

| Failure Prediction   | ✓                      | ✓                      | ✓                       | ✓           | ✓           | ✓       |       |

| Razor                | ✓                      | ✓                      | ✓                       | ✓           | ✓           | ✓       | ✓     |

Table 2.2: A comparison of the attributes of the measurement methods.

|                      | Accuracy     | Resolution                                | Area<br>Overhead | Performance<br>Overhead | Arbitrary<br>Circuits | Direct | Online   |

|----------------------|--------------|-------------------------------------------|------------------|-------------------------|-----------------------|--------|----------|

| Ring Oscillator      | Low          | Medium                                    | Low              | Low                     | -                     | Х      | <b>✓</b> |

| TDC                  | Medium       | Medium                                    | Low              | Low                     | -                     | X      | ✓        |

| $\operatorname{TRC}$ | -            | -                                         | Medium           | Low                     | -                     | X      | ✓        |

| Signature Analysis   | $_{ m High}$ | High                                      | Low              | Low                     | ✓                     | ✓      | X        |

| FRD                  | $_{ m High}$ | High                                      | Medium           | Medium                  | ✓                     | ✓      | X        |

| TP                   | High         | High                                      | Low              | Low                     | ✓                     | ✓      | X        |

| Failure Prediction   | $_{ m High}$ | Pass/Fail                                 | Medium           | Medium                  | ✓                     | ✓      | ✓        |

| Razor                | High         | $\operatorname{Pass}/\operatorname{Fail}$ | High             | High                    | X                     | ✓      | ✓        |

Table 2.1 gives the different sources of delay variability that can be quantified by the various measurement methods discussed. Table 2.2 provides a comparison of the attributes of the measurement methods. For a particular application, the optimum measurement method may be ascertained from these tables, considering the specific requirements.

### 2.5 Conclusion

This chapter has explored the wealth of research relating to variability, its resultant impact on circuit delay, and the means by which this delay can be quantified.

While historically there has been much focus on faults which result in non-functional circuits, in current process technologies concern is directed at variability's impact on timing performance, particularly the deterioration of this during the course of an integrated circuits lifetime due to degradation. This will typically lead to an abrupt catastrophic failure as critical paths in the circuit are no longer able to meet timing. Ongoing measurement of delay or slack, monitoring the "health" of the circuit, can be used to avoid this occurrence, instigating device replacement or degradation mitigation techniques.

This points to a need for a methods which can directly measure the effect of delay variation on an application circuit itself, accounting for the effects of process, environmental and temporal variation, without the need to infer how the behaviour of a circuit somewhere else on the die relates to the application circuit. It must do this without affecting the normal operation of the circuit and be able to track gradual changes in the delay of the circuit, not just provide an indication of timing failure that has occurred, or is impending. It should be general purpose, applicable to arbitrary circuits, not just processors. This can be achieved by combining the strengths of frequency sweep and shadow register based timing measurement to measure the delay of an arbitrary circuit, accurately and with high resolution, while it is operating online.

A technique capable of performing this measurement would be a valuable contribution to research, both as a method in its own right and as a facilitator to other technologies and is the primary objective of this thesis.

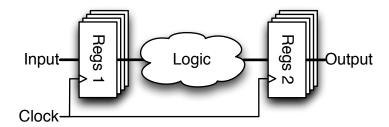

# 3 Online Slack Measurement

### 3.1 Introduction

Timing slack is an excellent measure for the health of a circuit. A large amount of slack indicates that the circuit is "healthy", that it would take a significant deterioration to result in timing errors. A small or negative quantity of slack is a concern, indicating the circuit is close to, or beyond the point of failure. The ability to measure timing slack in a circuit while it is operating opens many possibilities. Potential applications include on-silicon timing debug, timing degradation monitoring and dynamic voltage or frequency scaling.

In this chapter, a new method to precisely measure timing slack at selected registers, while the circuit operates normally, is presented. It allows a circuit to be continually monitored for timing performance variation over time; reductions in the amount of slack indicate that the circuit is degrading and changes due to temperature, voltage and other fluctuations can be tracked. The measurement method is enhanced with: 1) a calibration technique to improve absolute accuracy, 2) a dithering method to increase measurement resolution and, 3) a method of selecting registers from the circuit to monitor. The measurement technique is demonstrated on two simple benchmark circuits under a range of operating conditions.

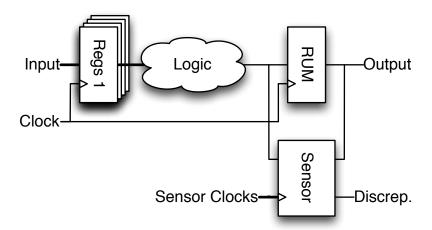

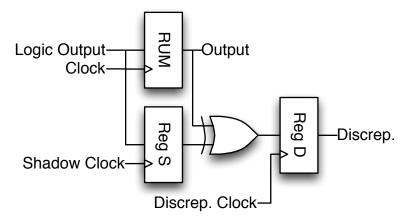

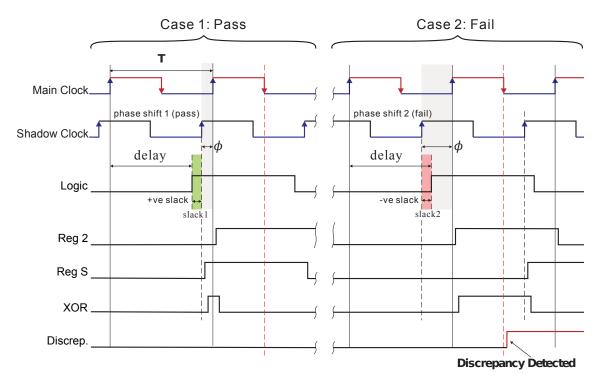

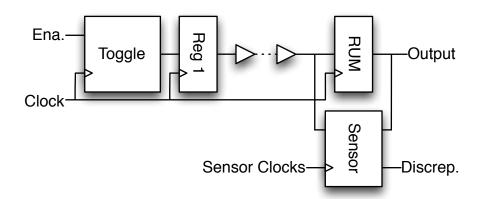

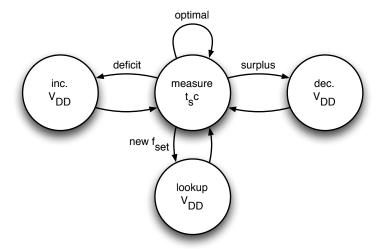

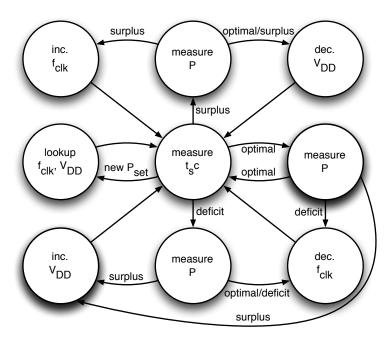

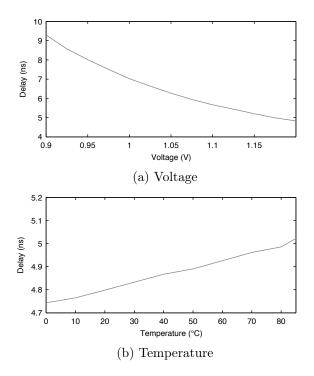

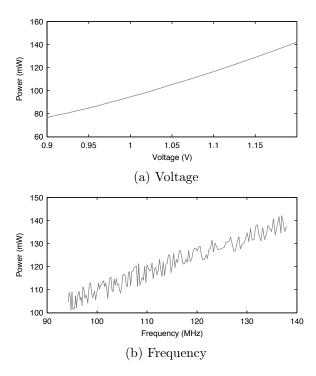

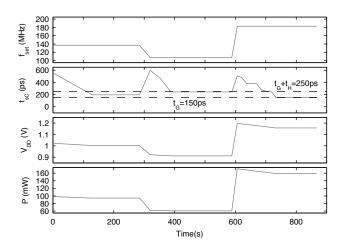

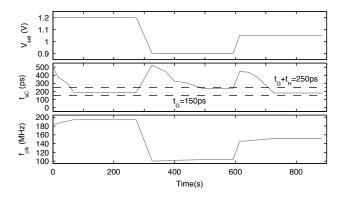

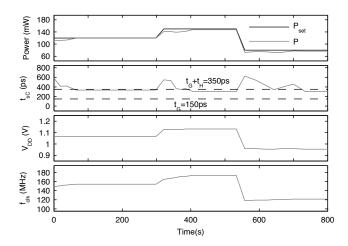

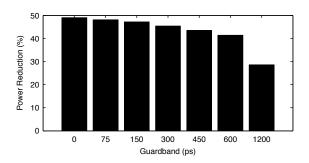

# 3.2 Principle of Operation