#### Imperial College London

Department of Electrical and Electronic Engineering

# DC/DC CONVERTERS FOR HIGH VOLTAGE DIRECT CURRENT TRANSMISSION

by Thomas Lüth

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering of Imperial College London and the Diploma of Imperial College London

December 2014 London United Kingdom

### Abstract

High Voltage Direct Current (HVDC) transmission has to date mostly been used for point-to-point projects, with only a few select projects being designed from the outset to incorporate multiple terminals. Any future HVDC network is therefore likely to evolve out of this pool of HVDC connections. As technology improves, the voltage rating, at the point of commission, of the these connections increases. Interconnection therefore requires the DC equivalent of the transformer, to bridge the voltage levels and create a multi-terminal network.

This thesis investigates new potential DC/DC converter topologies, which may be used for a range of HVDC applications. Simple interconnections of new and legacy HVDC links is unlikely to require a large voltage-step, but will be required to transfer a large amount of power. As the HVDC network develops it may become feasible for wind-farms and load-centres to directly connect to the DC network, rather than requiring new and dedicated links. Such a connection is called an HVDC tap and is typically rated at only a small fraction of the link's peak capacity (around 10%). Such taps would connect a distribution voltage level to the HVDC network. DC/DC converters suitable for large-step ratios (>5:1) may find their application here.

In this work DC/DC converters for both small and large step-ratios are investigated. Two approaches are taken to design such converters: first, an approach utilising existing converter topologies is investigated. As each project comes with a huge price-tag, their reliability is paramount. Naturally, technology that has already proven itself in the field can be modified more readily and quickly for deployment. Using two modular multilevel converters in a front-to-front arrangement has been found to work efficiently for large power transfers and low step-ratios. Such a system can be operated at higher than 50 Hz frequencies to reduce the volume of a number of passive components, making the set-up suitable for compact off-shore applications. This does however incur a significant penalty in losses reducing the overall converter efficiency.

In the second approach DC/DC converter designs are presented, that are more exper-

imental and would require significantly more development work before deployment. Such designs do not look to adapt existing converter topologies but rather are designed from scratch, purely for DC/DC applications. An evolution of the front-to-front arrangement is investigated in further detail. This circuit utilises medium frequency (>50 Hz) square current and voltage waveforms. The DC/DC step-ratio is achieved through a combination of the stacks of cells and a transformer. This split approach allows for high-step ratios to be achieved at similar system efficiencies as for the front-to-front arrangement. The topology has been found to be much more suitable for higher than 50 Hz operation from a losses perspective, allowing for a compact and efficient design.

## Acknowledgements

In my time at Imperial College, so many people have guided and provided me with invaluable advice, that it would be impossible to list them all here. There are, however, some who deserve a special mention. First and foremost I must thank my supervisor Tim Green for his patience through my blunders and the trust that at least some of his advice would eventually stick. He has provided me with fantastic opportunities, for which I am grateful.

From amongst my friends and colleagues at Imperial, special thanks is deserved by Michael Merlin, for he has diligently and repeatedly made time to explain aspects of control and power converters to me. I am also grateful to Adria and Richard for insightful discussions about all things related to transformers.

I also wish to thank the people I met from Alstom Grid for numerous helpful discussions and providing me with an industrial point-of-view on the work.

Finally, a big thank you to my family: my mum and dad have been an immense support through out all my time at Imperial and it simply would not have been possible without them. Last, I want to thank my fiancé Yazhini, who has been a bottomless source of motivation and encouragement, particularly during my writing of this thesis. Without her, it may never have come to an end.

## Contents

| A            | bstra | act     |                                                              | 4         |

|--------------|-------|---------|--------------------------------------------------------------|-----------|

| $\mathbf{A}$ | ckno  | wledge  | ements                                                       | 6         |

| Li           | st of | Figur   | es                                                           | 11        |

| Li           | st of | Table   | ${f s}$                                                      | 20        |

| Sy           | ymbo  | ols     |                                                              | 23        |

| 1            | Intr  | roduct  | ion                                                          | 28        |

|              | 1.1   | Proble  | em Statement and Thesis Outline                              | 29        |

|              | 1.2   | Autho   | or's Publications based on this Work                         | 31        |

| <b>2</b>     | Bac   | kgrou   | nd to HVDC transmission and the role of DC/DC converters     | <b>,</b>  |

|              | wit   | hin it  |                                                              | <b>32</b> |

|              | 2.1   | High '  | Voltage Direct Current Transmission Technology               | 32        |

|              |       | 2.1.1   | Reasons for Using HVDC                                       | 33        |

|              |       | 2.1.2   | HVDC Technology                                              | 35        |

|              | 2.2   | DC/D    | OC Converters for HVDC Networks                              | 40        |

|              |       | 2.2.1   | Switched Mode Power Supplies                                 | 43        |

|              |       | 2.2.2   | Dual Active Bridge Type Converter                            | 45        |

|              |       | 2.2.3   | Switched Capacitor Type Converter                            | 48        |

|              |       | 2.2.4   | Modular Cell Based Converters                                | 49        |

| 3            | Pri   | nciples | and operation of the direct coupled front-to-front converter |           |

|              | arra  | angem   | ent                                                          | <b>51</b> |

|              | 3.1   | Conve   | erters Considered for F2F Topology                           | 52        |

|              |       | 3.1.1   | Modular Multilevel Converter                                 | 53        |

|   |      | 3.1.2 Alternate Arm Converter                                        | 59 |

|---|------|----------------------------------------------------------------------|----|

|   | 3.2  | F2F System Description                                               | 64 |

|   |      | 3.2.1 Coupling Description                                           | 67 |

|   |      | 3.2.2 System Controller                                              | 68 |

|   | 3.3  | Choice of Internal AC Operating Voltage                              | 76 |

|   |      | 3.3.1 Passive Component Sizing                                       | 78 |

|   |      | 3.3.2 System Currents                                                | 90 |

|   |      | 3.3.3 Number of Cells in the stacks                                  | 92 |

|   |      | 3.3.4 Power Losses                                                   | 97 |

|   | 3.4  | Note About DC Fault Propagation Prevention                           | )5 |

|   | 3.5  | Chapter Summary: Direct-coupled F2F system performance               | )8 |

| 4 | Tra  | nsformer-coupled variation of the F2F arrangement 11                 | LO |

|   | 4.1  | Transformer Coupled F2F System Description                           | 11 |

|   |      | 4.1.1 Coupling Description                                           | 11 |

|   |      | 4.1.2 Voltage Drop Across Leakage Inductance                         | 13 |

|   |      | 4.1.3 System Controller                                              | 16 |

|   | 4.2  | System Operation                                                     | 19 |

|   |      | 4.2.1 Converter Specifications                                       | 19 |

|   |      | 4.2.2 Power Losses                                                   | 21 |

|   | 4.3  | Chapter Summary: System performance of F2F topology with galvanic    |    |

|   |      | isolation                                                            | 25 |

| 5 | Hig  | h frequency operation of F2F topologies 12                           |    |

|   | 5.1  | Effect of AC Frequency on Passive Components                         |    |

|   |      | 5.1.1 Arm Inductors                                                  |    |

|   |      | 5.1.2 Cell Capacitors                                                | 30 |

|   |      | 5.1.3 High Frequency Transformer                                     |    |

|   | 5.2  | Converter Losses                                                     |    |

|   | 5.3  | Chapter Summary: Raising the AC frequency in the F2F topologies 13   | 37 |

| 6 | Alte | ernative Waveforms and Converter Formats 13                          | 39 |

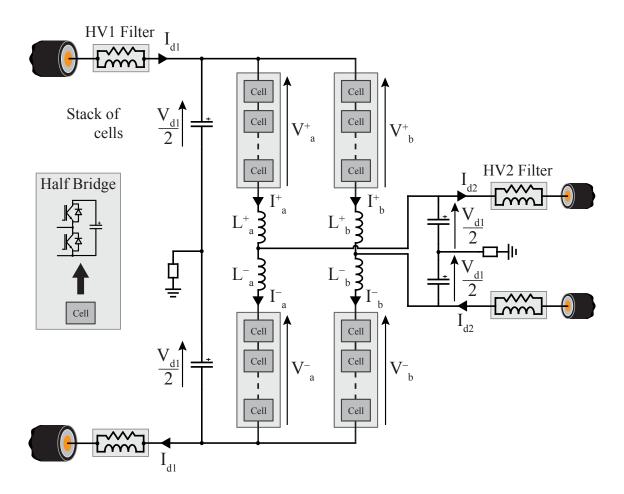

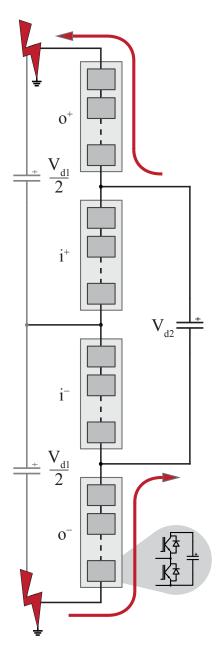

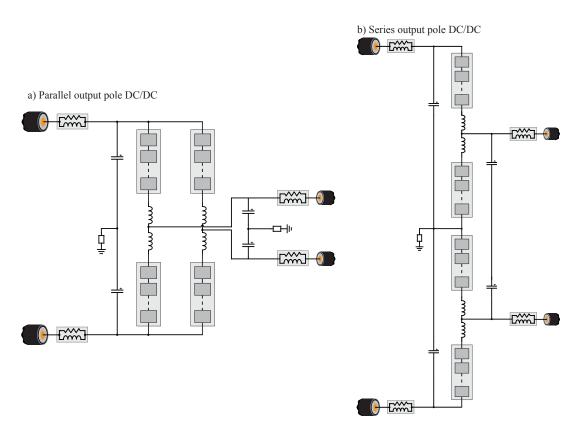

|   | 6.1  | Direct DC/DC Conversion Circuit Topologies                           | 40 |

|   |      | 6.1.1 Parallel Output Pole Topology                                  |    |

|   |      | 6.1.2 Series Output Pole Topology                                    | 54 |

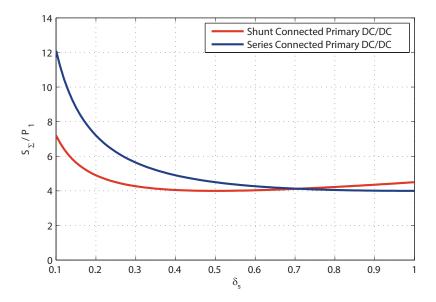

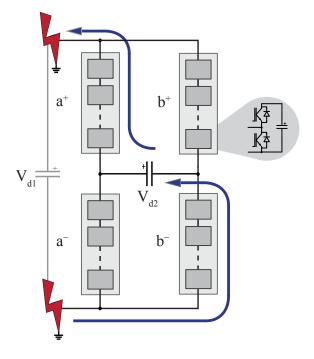

|   | 6.2  | Alternative DC/DC Circuit Topologies With Intermediate AC Step 16 $$ | 33 |

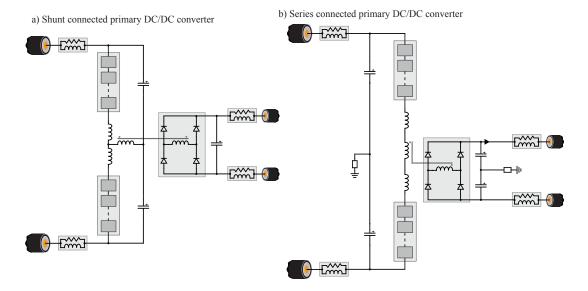

|   |      | 6.2.1 Shunt Connected Primary                                        | 63 |

|   |      | 6.2.2   | Series Connected Primary                                               |

|---|------|---------|------------------------------------------------------------------------|

|   | 6.3  | Discus  | ssion of Alternative DC/DC circuits                                    |

|   |      | 6.3.1   | Total Apparent Power Rating                                            |

|   |      | 6.3.2   | DC Fault Tolerance                                                     |

|   |      | 6.3.3   | Suitable areas of application                                          |

|   | 6.4  | Chapt   | er Summary: New modular DC/DC converter designs                        |

| 7 | Pri  | nciples | of operation of square-wave modular DC/DC converter 190                |

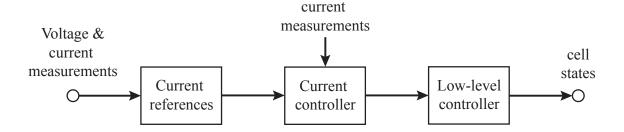

|   | 7.1  | Conve   | rter Controller                                                        |

|   |      | 7.1.1   | Current Controller                                                     |

|   |      | 7.1.2   | Current References                                                     |

|   |      | 7.1.3   | Cell-Level Controller                                                  |

|   |      | 7.1.4   | Enabling bi-directional power transfer                                 |

|   | 7.2  | Basic   | Steady-State Operation                                                 |

|   |      | 7.2.1   | Operation of Stacks of Cells                                           |

|   |      | 7.2.2   | Filter Requirements                                                    |

|   | 7.3  | Chapt   | er Summary: Design considerations for square-wave modular DC/DC $$ 231 |

| 8 | Circ | cuit co | mponent variations in SW-M DC/DC 238                                   |

|   | 8.1  | Passiv  | re Component Sizing                                                    |

|   |      | 8.1.1   | Cell Capacitors                                                        |

|   |      | 8.1.2   | Arm Inductors                                                          |

|   |      | 8.1.3   | DC Filter                                                              |

|   | 8.2  | Transf  | former                                                                 |

|   |      | 8.2.1   | Design Input Parameters                                                |

|   |      | 8.2.2   | Operational Input Parameters                                           |

|   | 8.3  | Cell S  | tacks                                                                  |

|   |      | 8.3.1   | Cell Voltage                                                           |

|   |      | 8.3.2   | Stack Transformation-ratio                                             |

|   |      | 8.3.3   | Voltage Capability of Stacks                                           |

|   |      | 8.3.4   | AC Frequency                                                           |

|   |      | 8.3.5   | Cell Rotation Frequency                                                |

|   | 8.4  | Rectif  | ier                                                                    |

|   |      | 8.4.1   | Active versus Passive Rectifier                                        |

|   | 8.5  | Chapt   | er summary: Performance trade-offs in modular square-wave DC/DC        |

|   |      | conver  | rter                                                                   |

| 9            | Tec   | hnical  | and academic conclusions                                            | 289   |

|--------------|-------|---------|---------------------------------------------------------------------|-------|

|              | 9.1   | Techn   | ical conclusions: modular cell based DC/DC converter topologies for |       |

|              |       | differe | nt step-ratios for HVDC applications                                | . 289 |

|              |       | 9.1.1   | Front-to-front topology                                             | . 290 |

|              |       | 9.1.2   | Alternative DC/DC converter topologies for HVDC applications $$ .   | . 293 |

|              | 9.2   | Acade   | mic contributions by the author                                     | . 297 |

|              | 9.3   | Furthe  | er Work on cell based HVDC DC/DC converters                         | . 298 |

| $\mathbf{A}$ | Tra   | nsform  | ner Modelling                                                       | 299   |

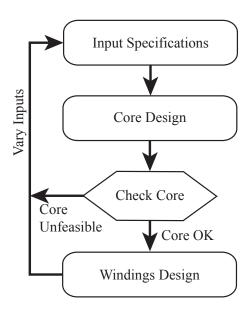

|              | A.1   | Design  | n Procedure                                                         | . 299 |

|              |       | A.1.1   | Input specifications                                                | . 304 |

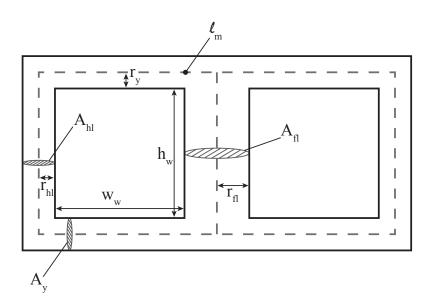

|              |       | A.1.2   | Core Design                                                         | . 304 |

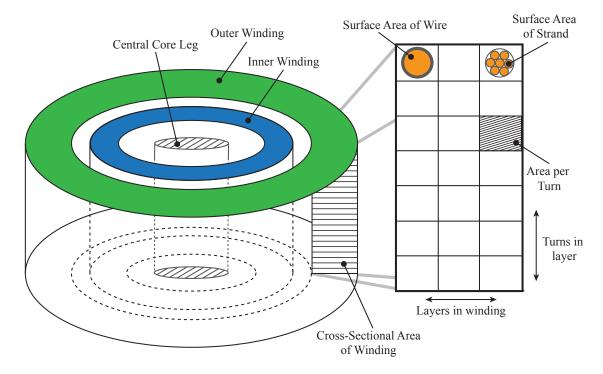

|              |       | A.1.3   | Winding Design                                                      | . 307 |

|              | A.2   | Model   | Limitations                                                         | . 313 |

| В            | Ana   | dytical | lly Estimating Losses in Semiconductors                             | 315   |

|              | B.1   | Analy   | tical Semiconductor Loss Estimation                                 | . 315 |

| $\mathbf{C}$ | Ind   | uctor I | Modelling                                                           | 319   |

|              | C.1   | Brook   | s Coil Inductor Calculations                                        | . 319 |

| D            | Ter   | ms and  | d labels used in this document explained                            | 322   |

| Bi           | bliog | graphy  |                                                                     | 324   |

# List of Figures

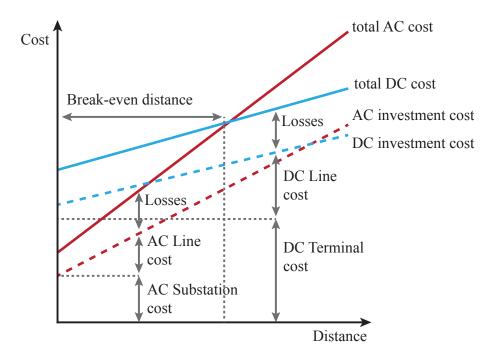

| 2.1  | Relative cost of AC vs. DC transmission against distance                            | 34 |

|------|-------------------------------------------------------------------------------------|----|

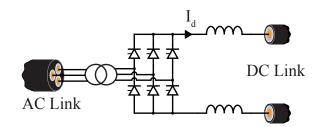

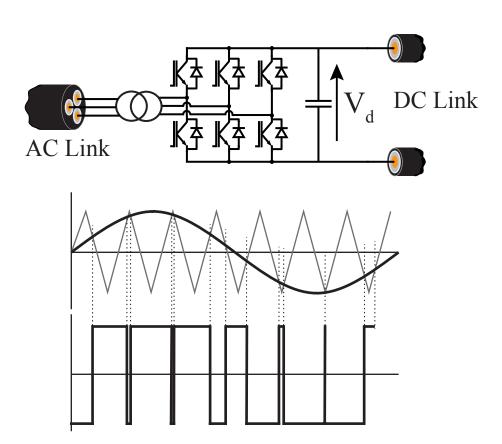

| 2.2  | Six-pulse Current Source Converter                                                  | 36 |

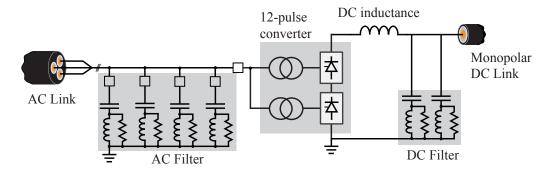

| 2.3  | High level circuit diagram of Current Source Converter and required passive         |    |

|      | components [1]                                                                      | 36 |

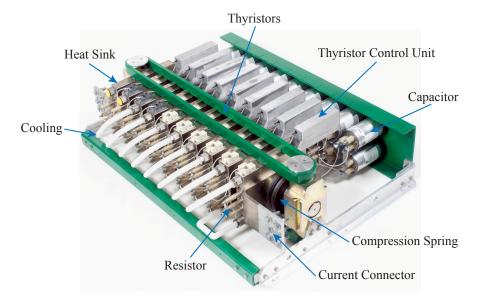

| 2.4  | Thyristor module for HVDC applications built by $ABB^1$                             | 37 |

| 2.5  | Two level voltage source converter                                                  | 38 |

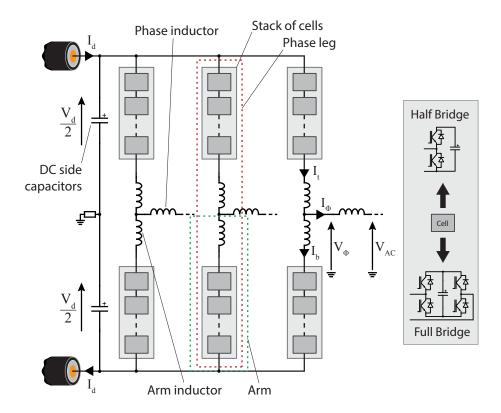

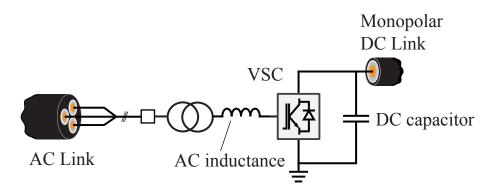

| 2.6  | Three phase VSC modular cell based VSC                                              | 39 |

| 2.7  | High level circuit diagram of Voltage Source Converter and required passive         |    |

|      | components [1]                                                                      | 40 |

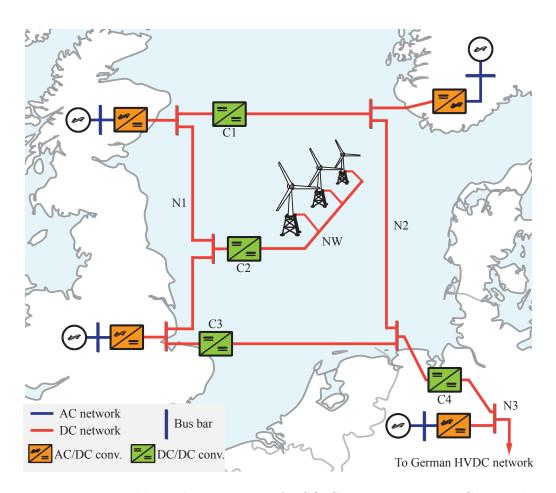

| 2.8  | Possible application areas of DC/DC converters in HVDC network                      | 42 |

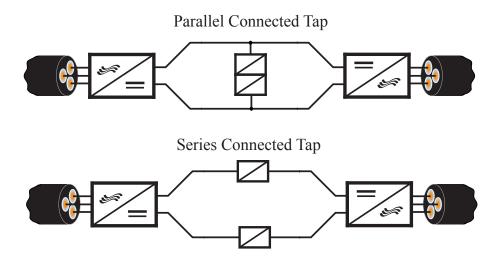

| 2.9  | Series and parallel tap design in a HVDC network                                    | 43 |

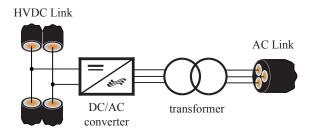

| 2.10 | $\ensuremath{HVDC}$ rap consisting of conventional DC/AC converter and transformer. | 44 |

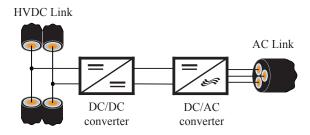

| 2.11 | HVDC tap using a DC/DC and a low voltage DC/AC converter                            | 44 |

| 2.12 | Buck-boost circuit                                                                  | 44 |

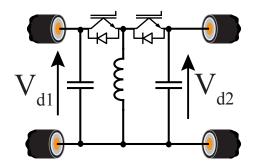

| 2.13 | Circuit of a Dual Active Bridge (DAB) converter                                     | 45 |

| 2.14 | Circuit of a Series Resonant Converter                                              | 46 |

| 2.15 | Illustration of a modular DAB converter                                             | 47 |

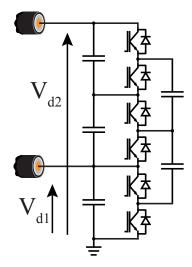

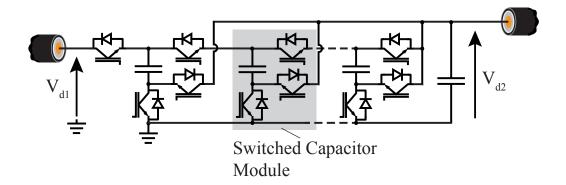

| 2.16 | Circuit diagram of a switched capacitor converter                                   | 48 |

| 2.17 | Illustration of a modular switched capacitor converter                              | 49 |

| 2.18 | Illustration of a front-to-front converter arrangement                              | 50 |

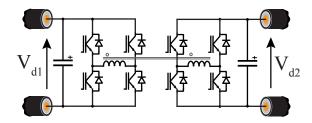

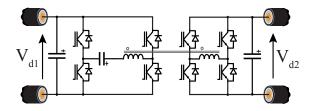

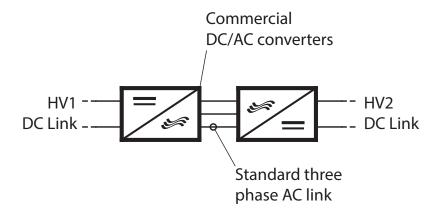

| 3.1  | Front-to-front arrangement utilising DC/AC converters                               | 52 |

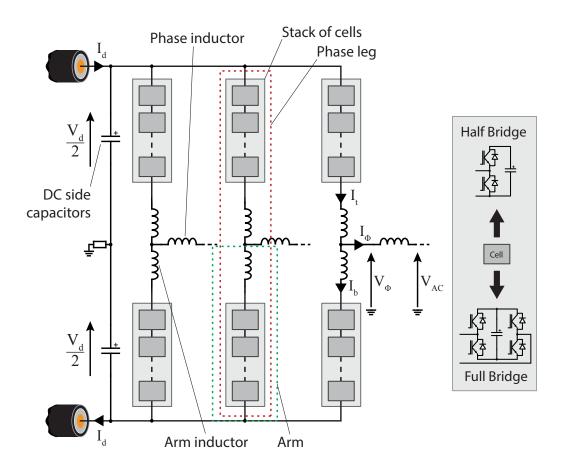

| 3.2  | General modular VSC circuit                                                         | 54 |

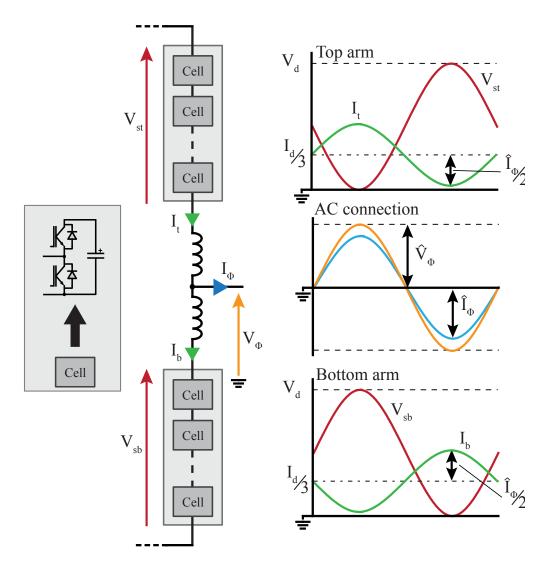

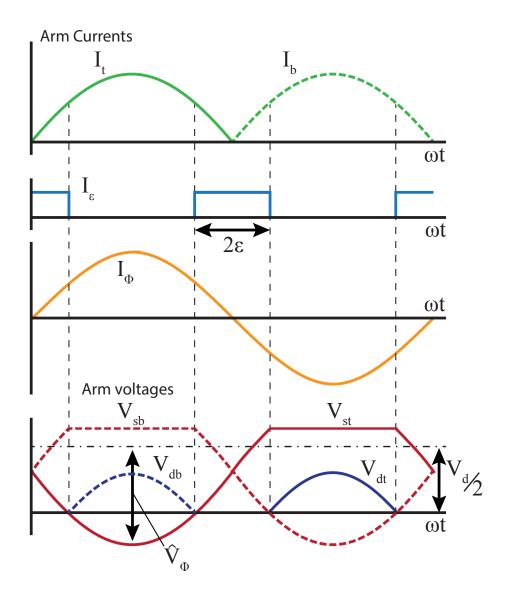

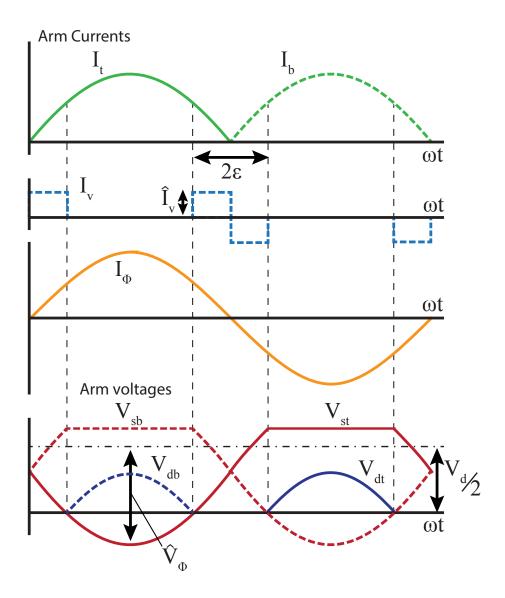

| 3.3  | Currents and voltages during normal operation of the MMC                            | 56 |

| 3.4  | Over- and under-modulation of converter voltage definitions                         | 57 |

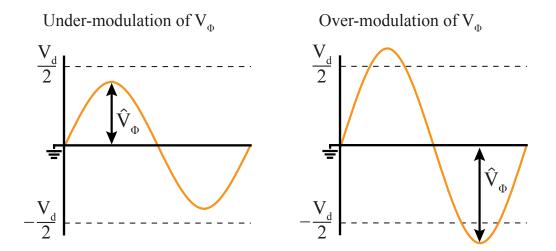

| 3.5  | Currents and voltages during normal operation of the AAC                            | 61 |

| 3.6  | Arm currents and stack voltages with overlap period                                 | 62 |

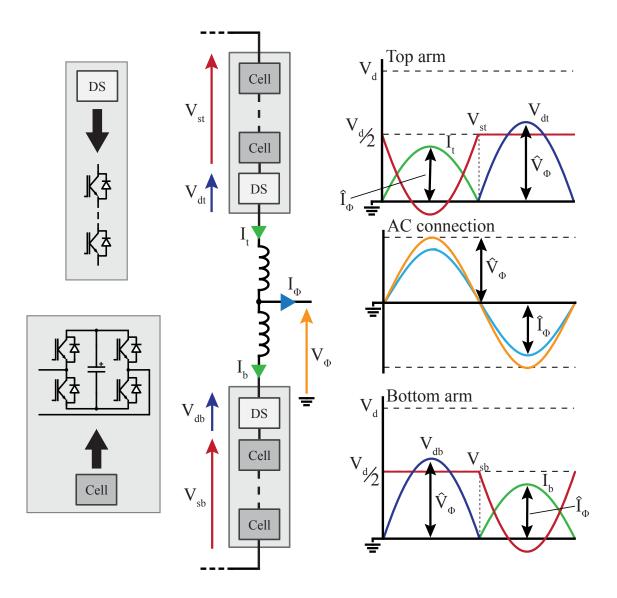

| 3.7  | Arm currents and stack voltages with vertical balancing                            | 65 |

|------|------------------------------------------------------------------------------------|----|

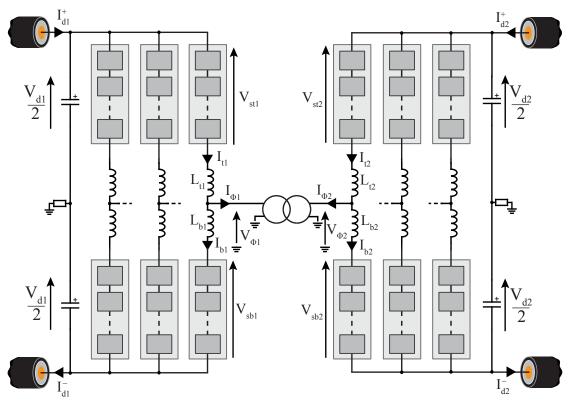

| 3.8  | Front-to-front direct coupled arrangement with two VSCs                            | 66 |

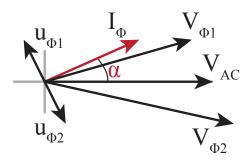

| 3.9  | Phasor diagram of F2F Ac voltages and current                                      | 68 |

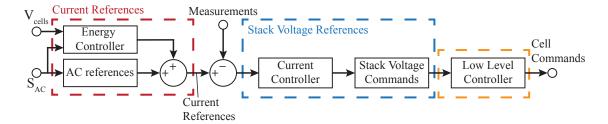

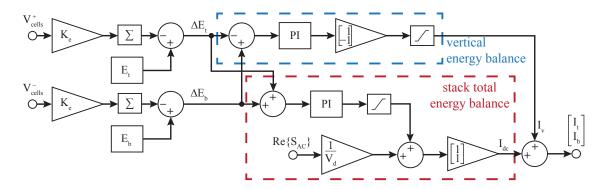

| 3.10 | F2F controller overview                                                            | 69 |

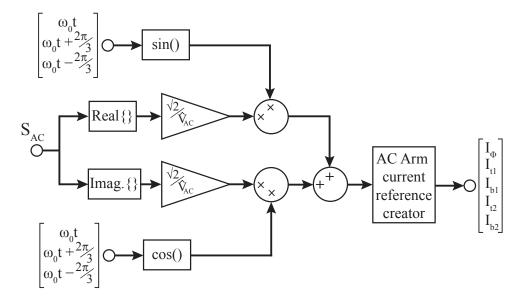

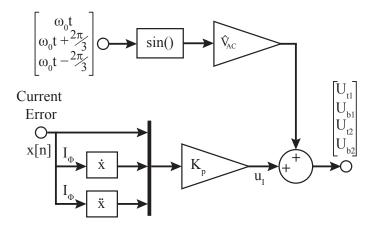

| 3.11 | AC reference current builder for F2F system                                        | 70 |

| 3.12 | F2F Energy controller per converter phase-leg                                      | 70 |

| 3.13 | F2F equivalent inductive network                                                   | 71 |

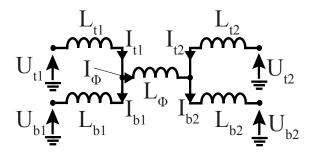

| 3.14 | F2F curret controller                                                              | 73 |

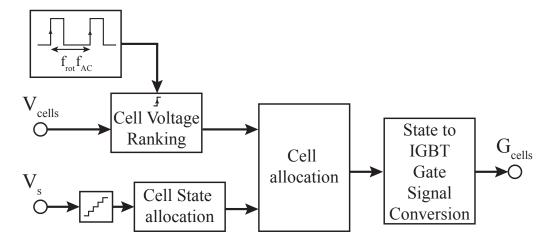

| 3.15 | Low level controller overview                                                      | 76 |

| 3.16 | Full bridge cell manufactured by Alstom <sup>2</sup>                               | 79 |

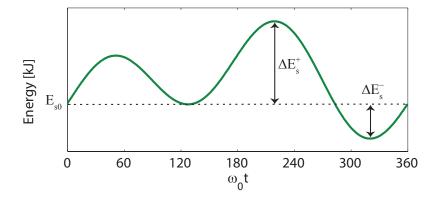

| 3.17 | Definition of absolute energy deviations                                           | 80 |

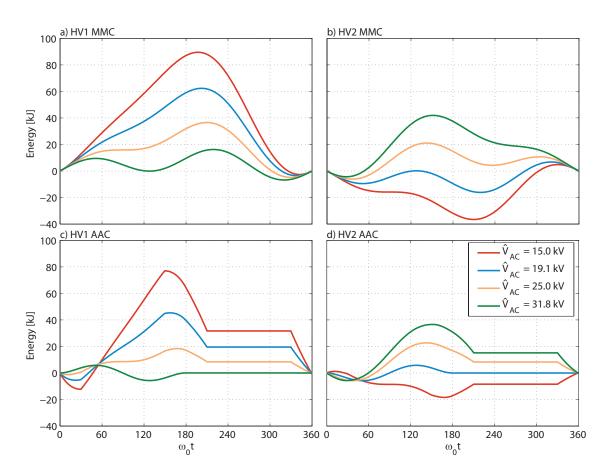

| 3.18 | Normalised intra cycle energy deviation of top cell stack in all converter         |    |

|      | varieties over one AC cycle                                                        | 81 |

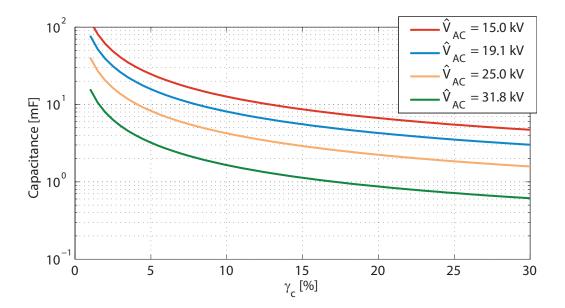

| 3.19 | Cell capacitance with respect to voltage deviation margin $\gamma_c$ for different |    |

|      | AC voltage magnitudes for HV1 MMC                                                  | 83 |

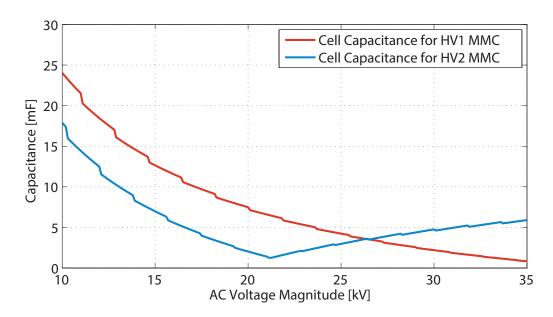

| 3.20 | Cell capacitance with respect to AC voltage magnitudes for both MMCs               |    |

|      | and $\gamma_c = 10\%$                                                              | 84 |

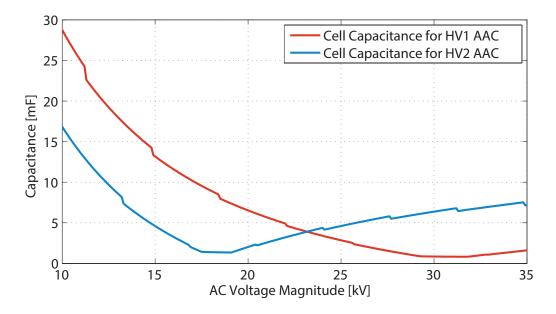

| 3.21 | Cell capacitance with respect to AC voltage magnitudes for both AACs and           |    |

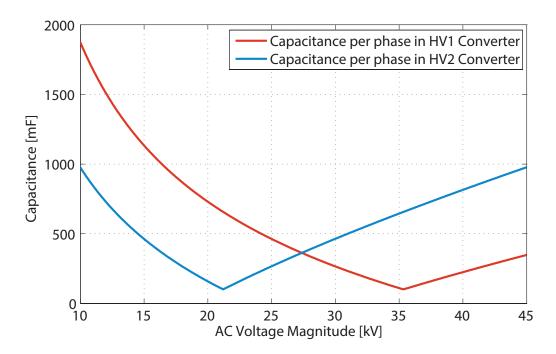

|      | $\gamma_c = 10\%.$                                                                 | 84 |

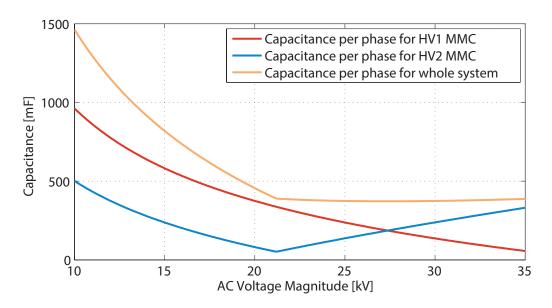

| 3.22 | Capacitance per phase with respect to AC voltage magnitudes for both               |    |

|      | MMCs and system wide, for $\gamma_c = 10\%$                                        | 85 |

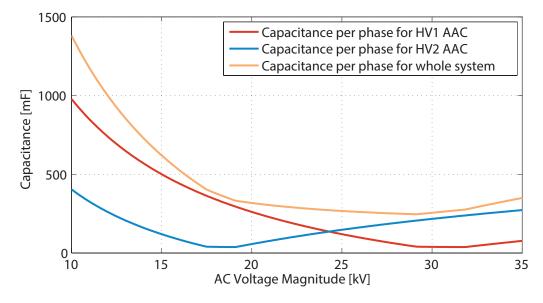

| 3.23 | Capacitance per phase with respect to AC voltage magnitudes for both               |    |

|      | AACs and system wide, for $\gamma_c = 10\%$                                        | 85 |

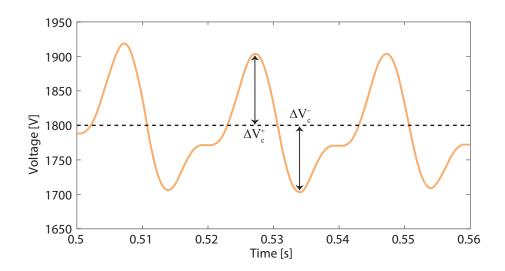

|      | Typical cell voltage deviation from the mean                                       | 87 |

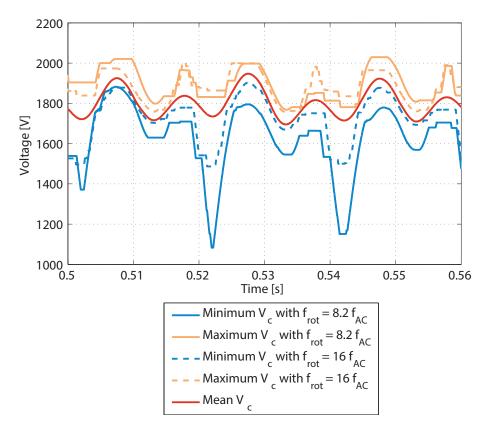

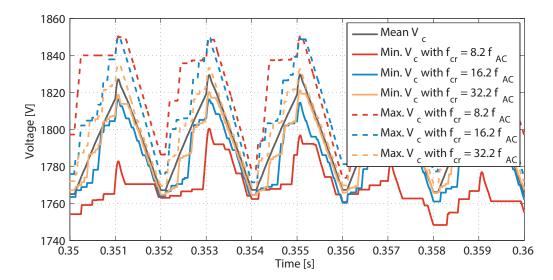

| 3.25 | Cell voltage range for top stack in HV1 side MMC at $\hat{V}_{AC} = 31.8$ kV for   |    |

|      | different cell rotation frequencies                                                | 89 |

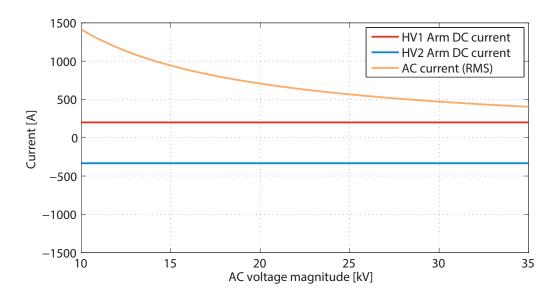

| 3.26 | System currents in F2F system with MMCs at full power rating                       | 91 |

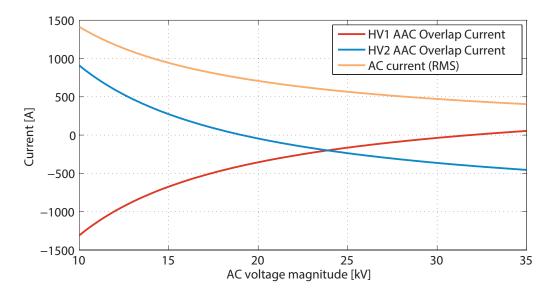

| 3.27 | System currents in F2F system with AACs at full power rating                       | 91 |

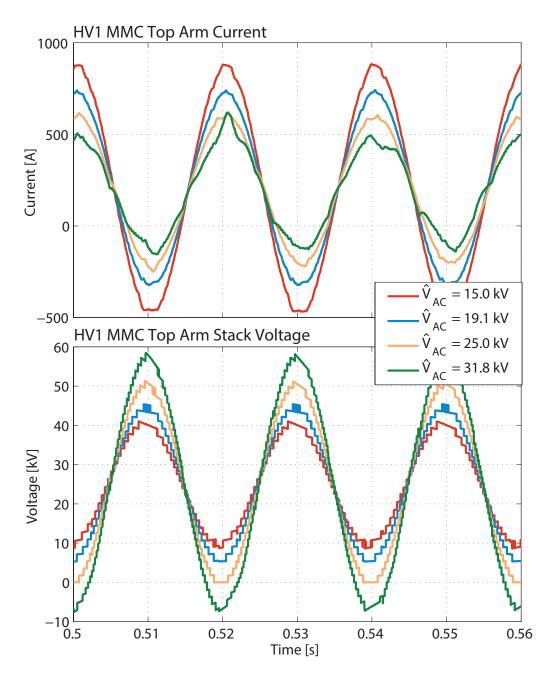

| 3.28 | Top arm current and stack voltages of HV1 MMC for varying AC voltage               |    |

|      | magnitude                                                                          | 93 |

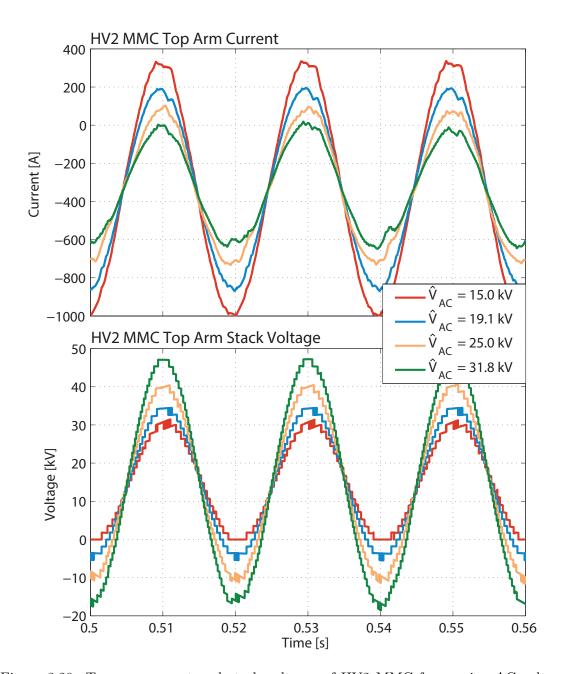

| 3.29 | Top arm current and stack voltages of HV2 MMC for varying AC voltage               |    |

|      | magnitude                                                                          | 94 |

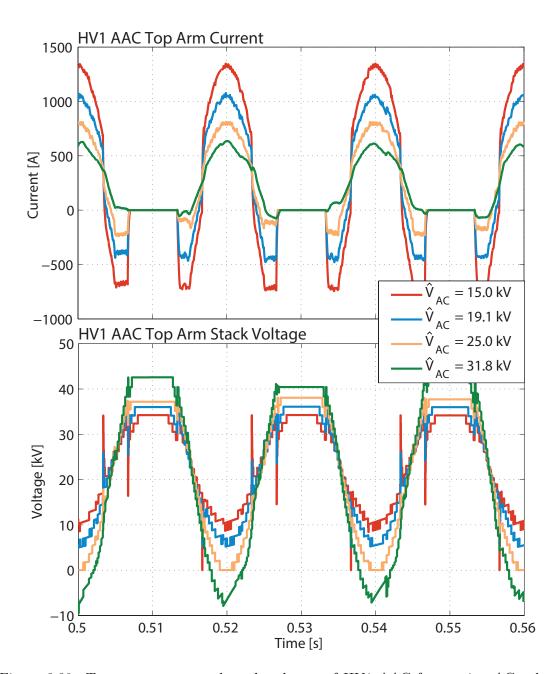

| 3.30 | Top arm current and stack voltages of HV1 AAC for varying AC voltage               |    |

|      | magnitude                                                                          | 95 |

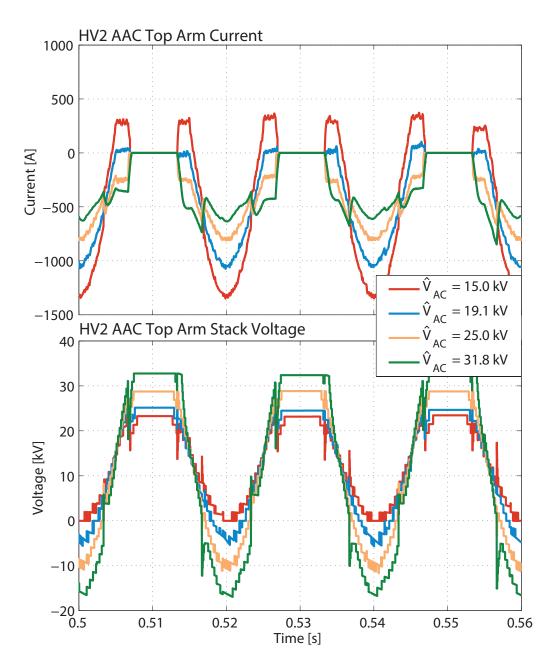

| 3.31 | Top arm current and stack voltages of HV2 AAC for varying AC voltage               |    |

|      | magnitude                                                                          | 96 |

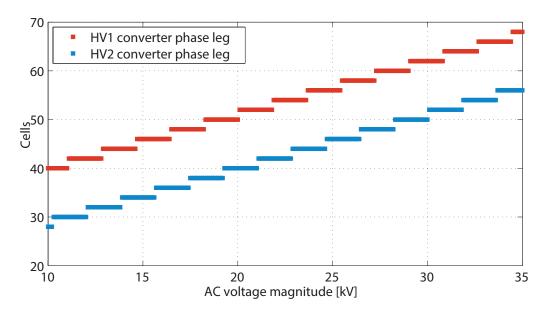

| 3.32 | Number of cells per phase leg in MMC F2F system with respect to AC                                         |

|------|------------------------------------------------------------------------------------------------------------|

|      | voltage magnitude                                                                                          |

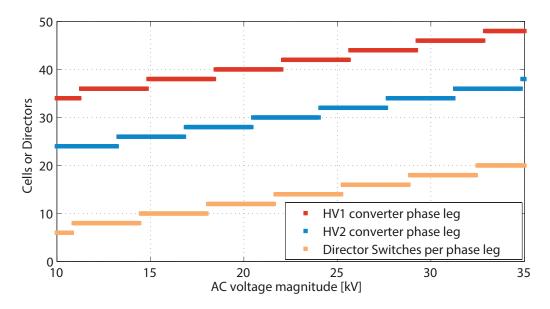

| 3.33 | Number of cells and director switches per phase leg in AAC F2F system with respect to AC voltage magnitude |

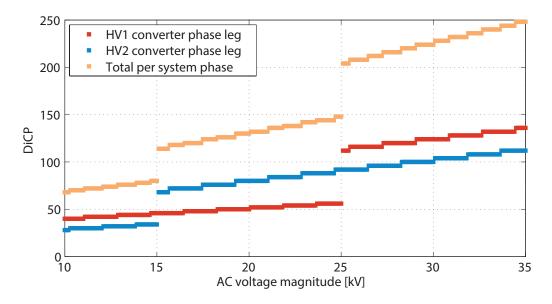

| 3.34 | Number of devices in the conduction path (DiCP) per phase in MMC F2F                                       |

|      | system                                                                                                     |

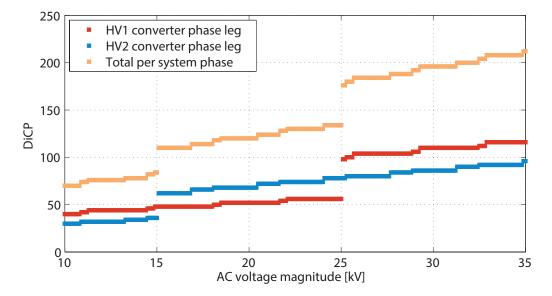

| 3.35 | Number of devices in the conduction path (DiCP) per phase in AAC F2F system                                |

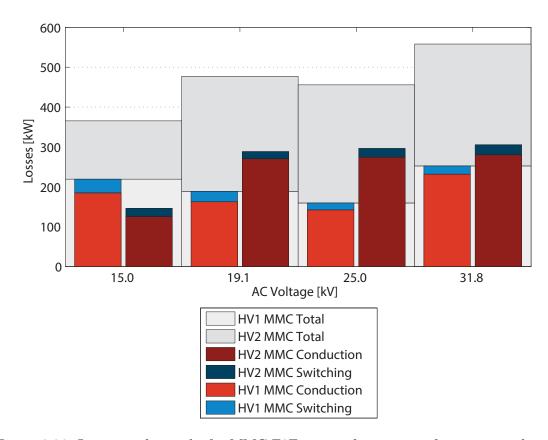

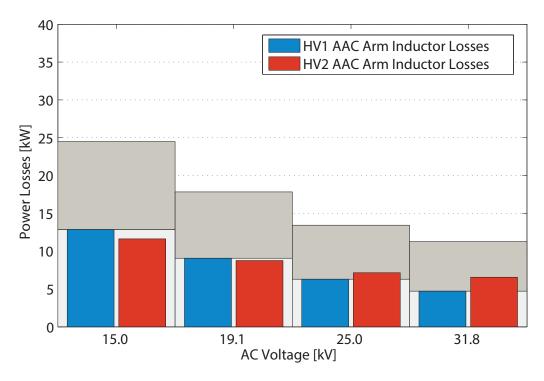

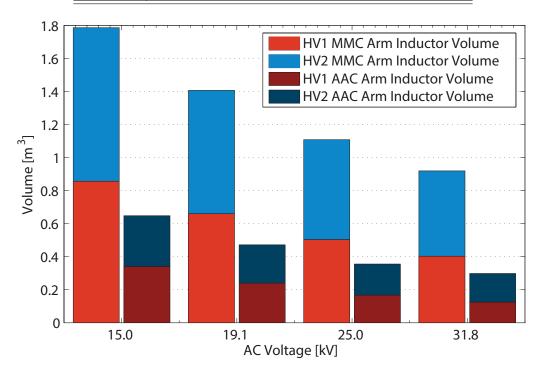

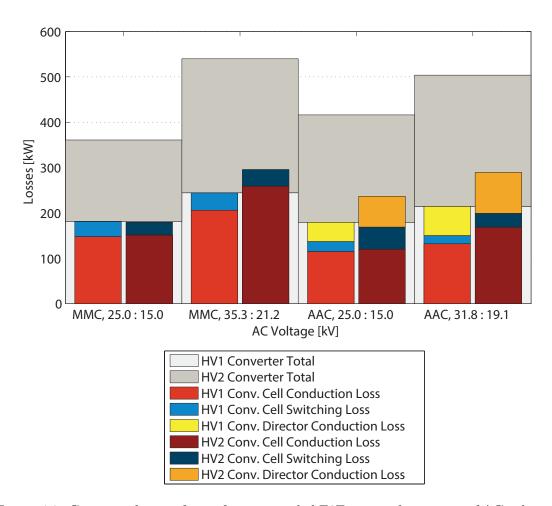

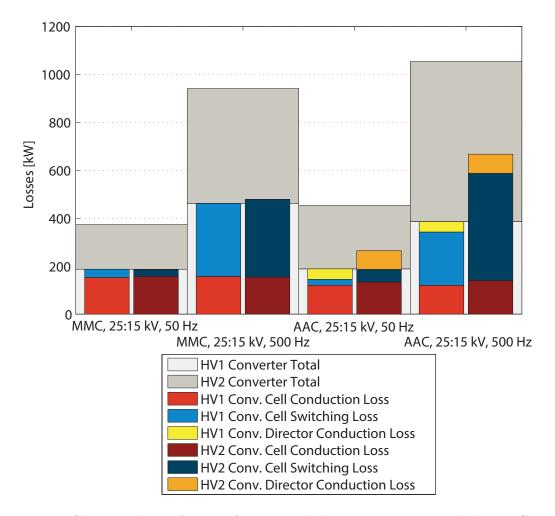

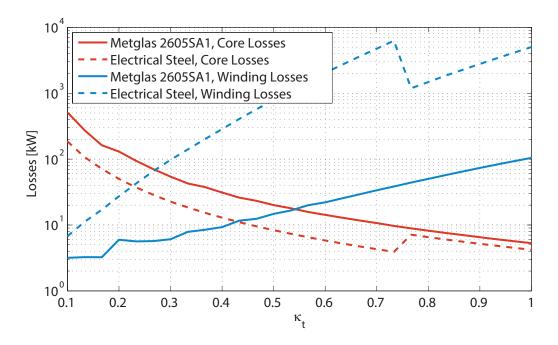

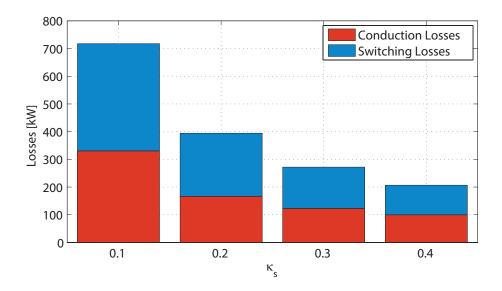

| 3.36 | Losses in the stacks for MMC F2F system for a range of operating voltages. 101                             |

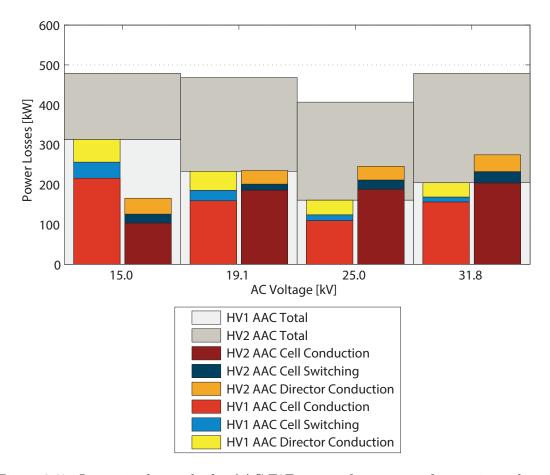

| 3.37 | Losses in the stacks for AAC F2F system for a range of operating voltages. 102                             |

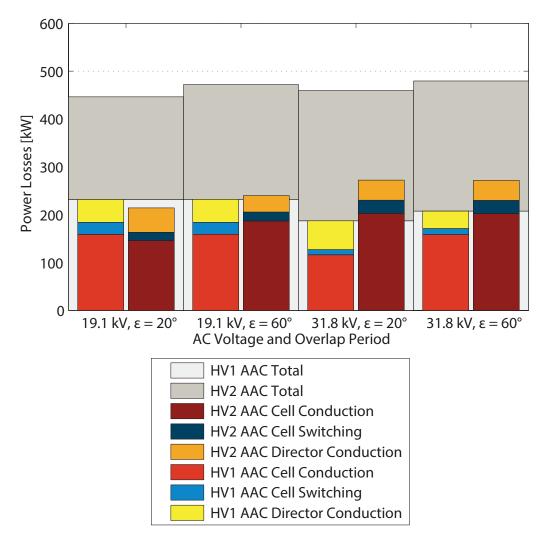

| 3.38 | Losses in the stacks for AAC F2F system for sweet-spot operation with                                      |

|      | reduced overlap period                                                                                     |

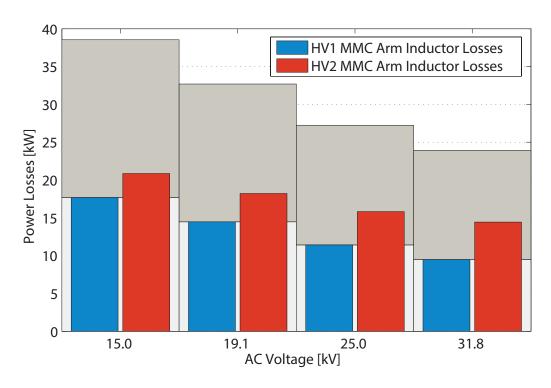

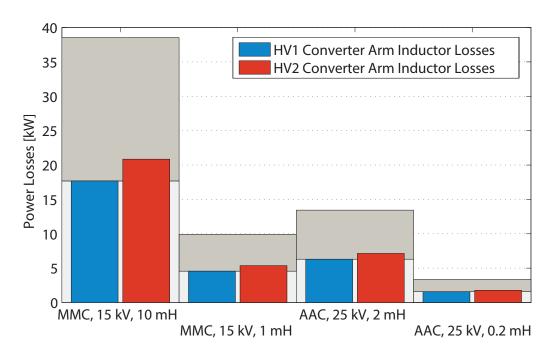

| 3.39 | Losses incurred in the arm inductors of the MMCs for different AC voltage                                  |

|      | magnitudes                                                                                                 |

| 3.40 | Losses incurred in the arm inductors of the AACs for different AC voltage                                  |

|      | magnitudes                                                                                                 |

| 3.41 | Volume of the arm inductors for both MMCs and AACs with varying AC                                         |

|      | voltage                                                                                                    |

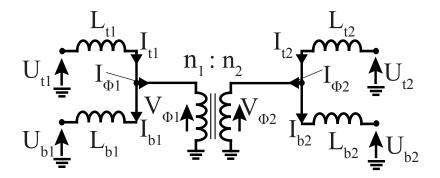

| 4.1  | Circuit diagram of the transformer-coupled F2F topology using two VSCs 111                                 |

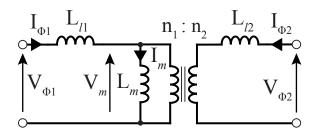

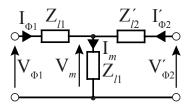

| 4.2  | Equivalent inductance model of single phase transformer                                                    |

| 4.3  | Equivalent transformer circuit with referred secondary                                                     |

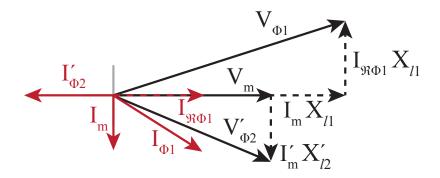

| 4.4  | Phasor diagram illustrating transformer voltages and currents                                              |

| 4.5  | Inductive network per phase of transformer-coupled F2F system $117$                                        |

| 4.6  | Magnetising current magnitude controller used to ensure that the correct                                   |

|      | AC voltages are generated                                                                                  |

| 4.7  | Current controller in transformer-coupled F2F system                                                       |

| 4.8  | Capacitance per phase in F2F MMC system for varying AC voltage 120                                         |

| 4.9  | Converter losses of transformer coupled F2F system for a range of AC voltages.123                          |

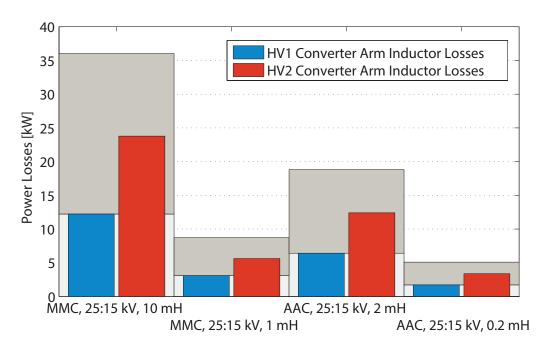

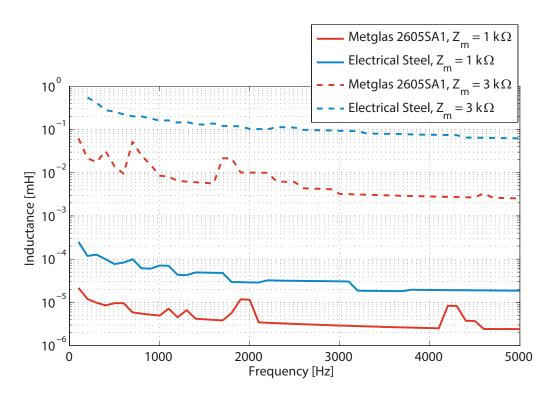

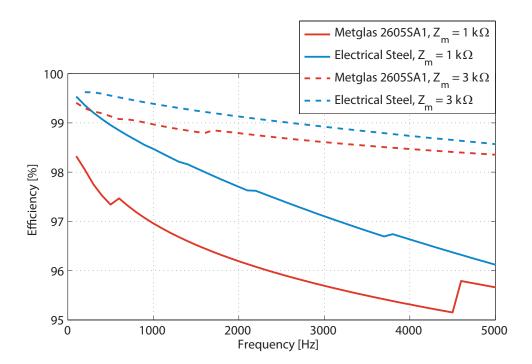

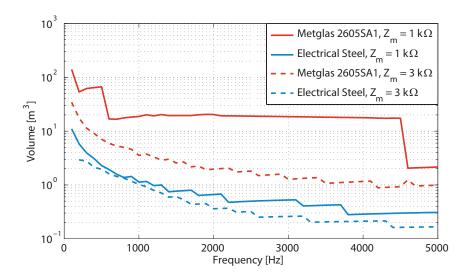

| 5.1  | Arm inductor losses for direct-coupled F2F systems using both MMCs and                                     |

|      | AACs for 50 and 500 Hz                                                                                     |

| 5.2  | Arm inductor losses for transformer-coupled F2F systems using both MMCs $$                                 |

|      | and AACs for 50 and 500 Hz                                                                                 |

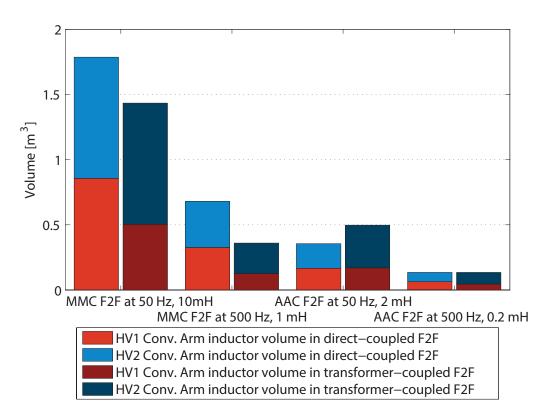

| 5.3  | Volume per arm inductor in direct- and transformer-coupled F2F systems                                     |

|      | for 50 and 500 Hz                                                                                          |

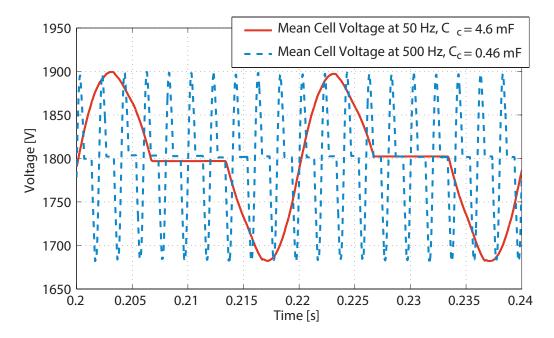

| 5.4  | Mean cell voltage deviation in top stack of HV2 AAC in direct-coupled F2F system at 50 and 500 Hz                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

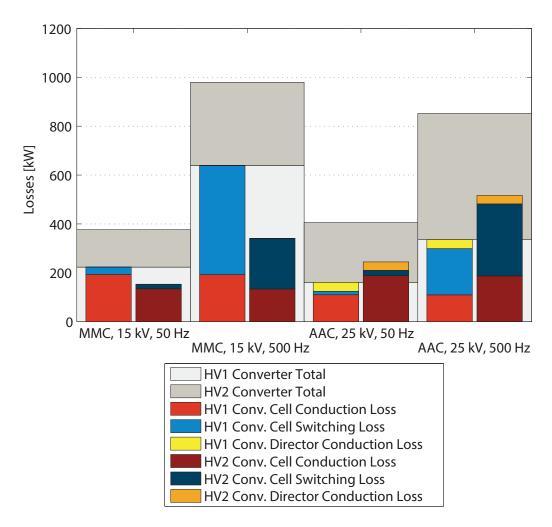

| 5.5  | Converter losses for direct-coupled F2F systems using both MMCs and AACs for 50 and 500 Hz                                                                                       |

| 5.6  | Converter losses for transformer-coupled F2F systems using both MMCs and AACs for 50 and 500 Hz                                                                                  |

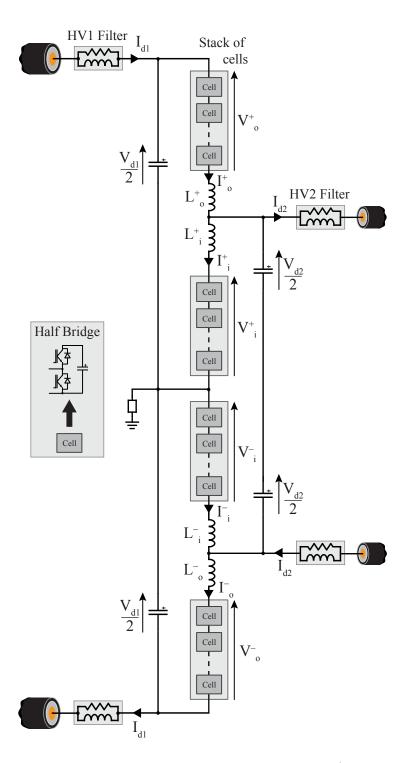

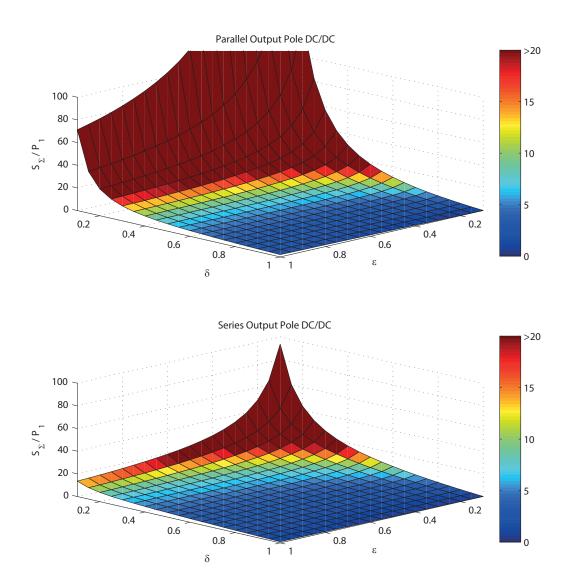

| 6.1  | Parallel output pole, direct conversion DC/DC circuit                                                                                                                            |

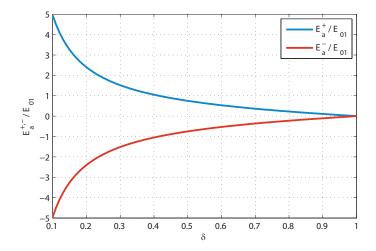

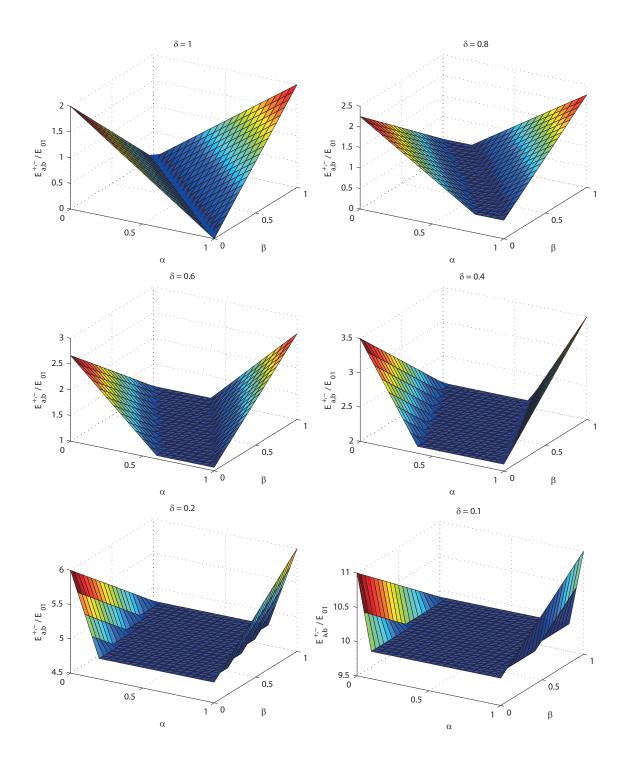

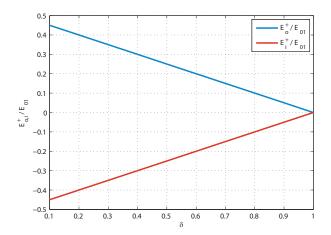

| 6.2  | Energy drift in parallel pole DC/DC converter with respect to step-ratio. $$ . 144                                                                                               |

| 6.3  | Split of DC links currents in parallel output pole DC/DC circuit 145                                                                                                             |

| 6.4  | Scaling of energy drift ratio $(\frac{E_{\Sigma}}{E_{01}})$ for range of step-ratios with respect to                                                                             |

|      | different $I^{+,-}$ and $I_{a,b}$ splits. $\ldots \ldots \ldots$ |

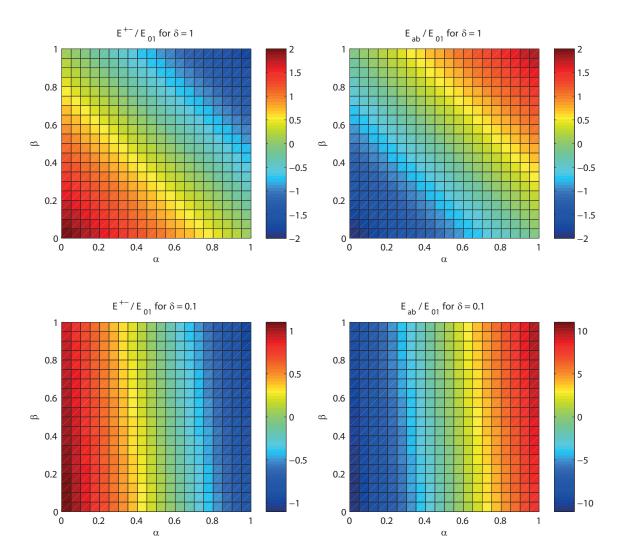

| 6.5  | Vertical $(E^{+-})$ and horizontal $(E_{ab})$ energy drift with respect to $\alpha$ an $\beta$ for                                                                               |

|      | $\kappa = 1$ and $\kappa = 0.1$                                                                                                                                                  |

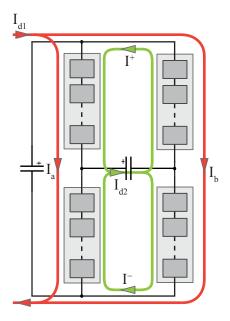

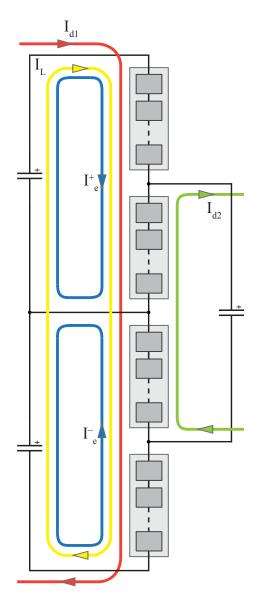

| 6.6  | Circulating AC balancing current overlay on top of DC currents in parallel                                                                                                       |

|      | output pole DC/DC circuit                                                                                                                                                        |

| 6.7  | Illustration of proposed balancing circulating current and AC voltage in                                                                                                         |

|      | parallel output pole DC/DC circuit                                                                                                                                               |

| 6.8  | Series output pole, direct conversion DC/DC circuit                                                                                                                              |

| 6.9  | Energy drift in top inner and outer cell stacks of series output pole DC/DC                                                                                                      |

|      | circuit                                                                                                                                                                          |

| 6.10 | DC and AC balancing current loops in series output pole DC/DC circuit. $\cdot$ 160                                                                                               |

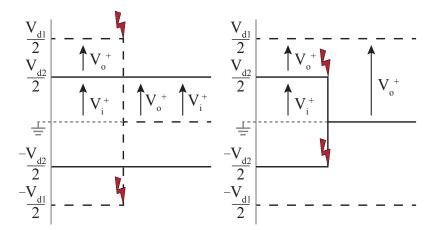

| 6.11 | Stack voltages with AC energy balancing modulation voltage 161                                                                                                                   |

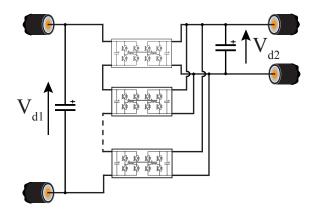

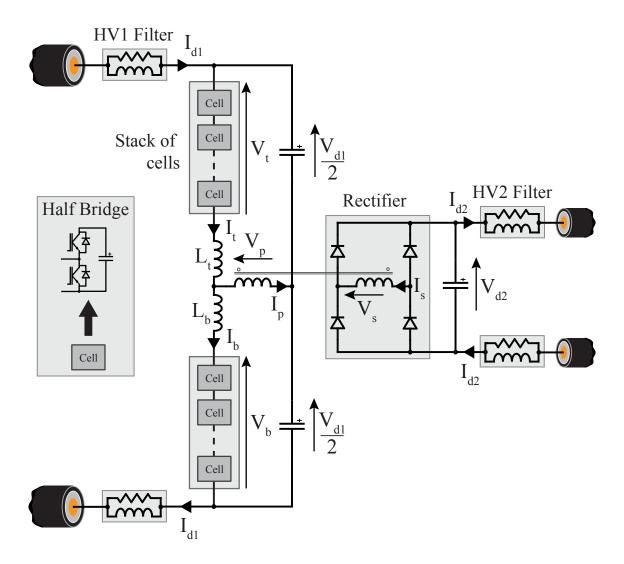

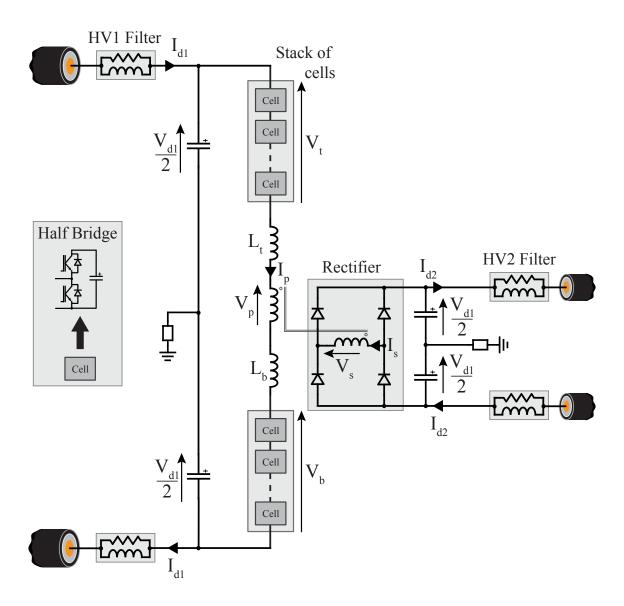

| 6.12 | $\mathrm{DC/AC/DC}$ circuit with galvanic isolation and a shunt connected primary . 164                                                                                          |

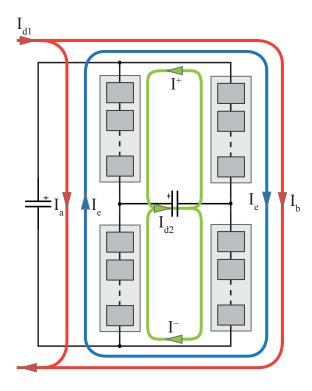

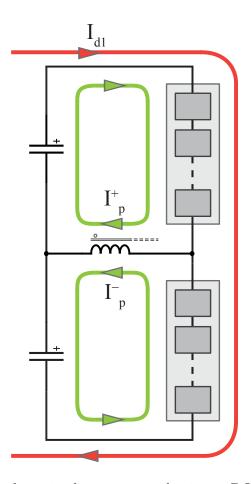

| 6.13 | Current loops in shunt connected primary DC/AC/DC converter 169                                                                                                                  |

| 6.14 | DC/AC/DC circuit with galvanic isolation and a series connected primary. 171                                                                                                     |

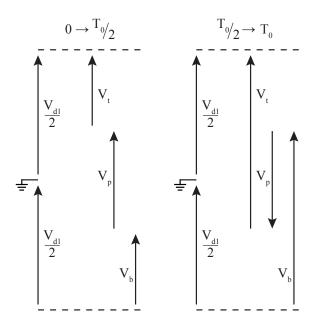

| 6.15 | Diagram illustrating how the primary voltage is generated by the cell stacks                                                                                                     |

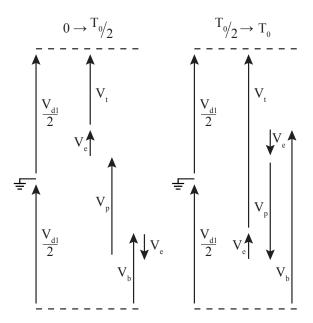

|      | in the series connected primary DC/AC/DC converter                                                                                                                               |

| 6.16 | Diagram illustrating how the balancing voltage is used in the series connec-                                                                                                     |

|      | ted primary DC/AC/DC converter                                                                                                                                                   |

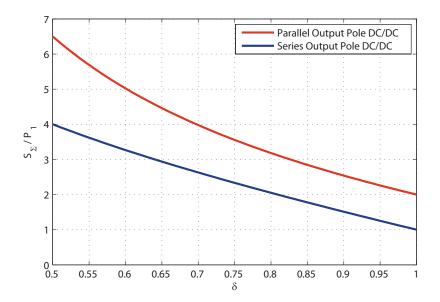

| 6.17 | Capacity ratio of direct conversion DC/DC converters                                                                                                                             |

| 6.18 | Capacity ratio of direct conversion DC/DC converters with $\epsilon = 1$ , focused                                                                                               |

|      | around low step-ratios                                                                                                                                                           |

|      | Capacity ratio of DC/DC converters with intermediate AC step 182                                                                                                                 |

| 6.20 | Possible fault current paths in parallel output pole DC/DC circuit in case                                                                                                       |

|      | of line-to-ground faults on HV1 side                                                                                                                                             |

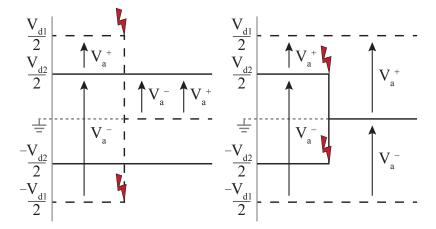

| 6.21 | Stack voltage requirements for phase leg of parallel pole DC/DC circuit in case of faults line-to-ground faults in HV1 (left-hand side diagram) and HV2 side (right-hand side diagram) |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.22 | Stack voltage requirements for phase leg of series pole DC/DC circuit in case of faults line-to-ground faults in HV1 (left-hand side diagram) and                                      |

| 6.23 | HV2 side (right-hand side diagram)                                                                                                                                                     |

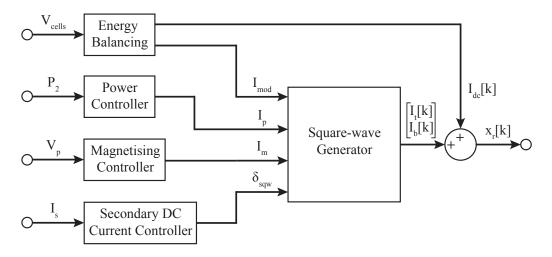

| 7.1  | General overview of controller for square-wave modular DC/DC converter $191$                                                                                                           |

| 7.2  | Equivalent inductive network view of square-wave modular DC/DC with                                                                                                                    |

|      | shunt connected primary                                                                                                                                                                |

| 7.3  | Equivalent inductive circuit for a single phase transformer                                                                                                                            |

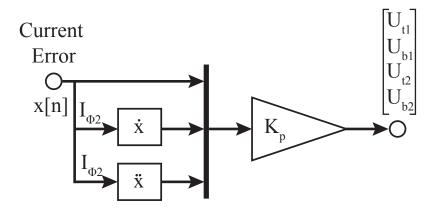

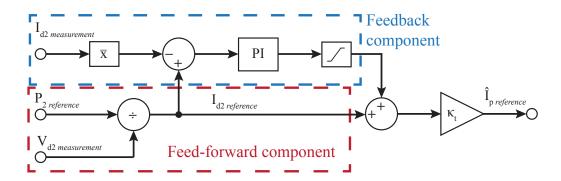

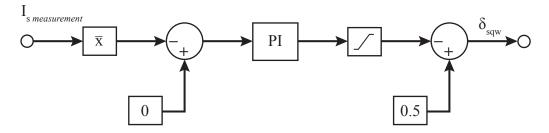

| 7.4  | Current controller for square-wave modular DC/DC converter 193                                                                                                                         |

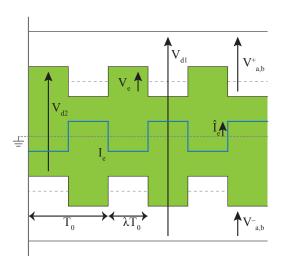

| 7.5  | Voltages on HV1 side of square-wave DC/DC converter with shunt connected primary                                                                                                       |

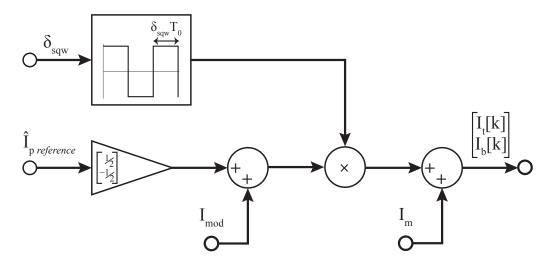

| 7.6  | Layout of the current reference building block of the control system for the square-wave modular DC/DC converter                                                                       |

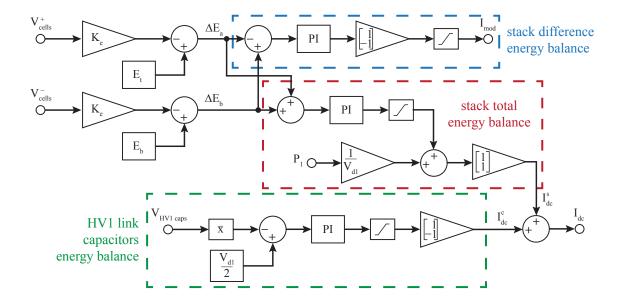

| 7.7  | Energy balance controller for square-wave modular DC/DC converter 197                                                                                                                  |

| 7.8  | Power controller for square-wave DC/DC                                                                                                                                                 |

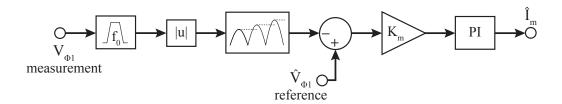

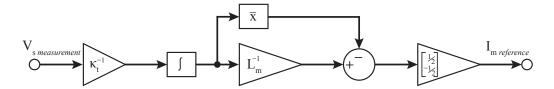

| 7.9  | Magnetising controller for square-wave DC/DC                                                                                                                                           |

| 7.10 | Secondary DC current controller                                                                                                                                                        |

| 7.11 | Square-wave generation block in square-wave DC/DC converter 199                                                                                                                        |

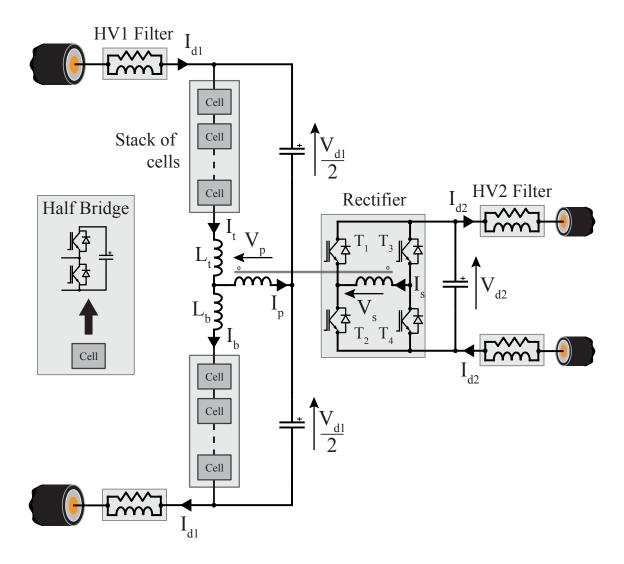

| 7.12 | Circuit diagram for shunt connected primary DC/AC/DC converter with                                                                                                                    |

|      | active rectification                                                                                                                                                                   |

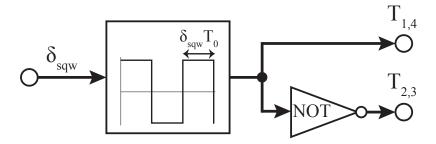

| 7.13 | Switching signal generator for rectifier switches                                                                                                                                      |

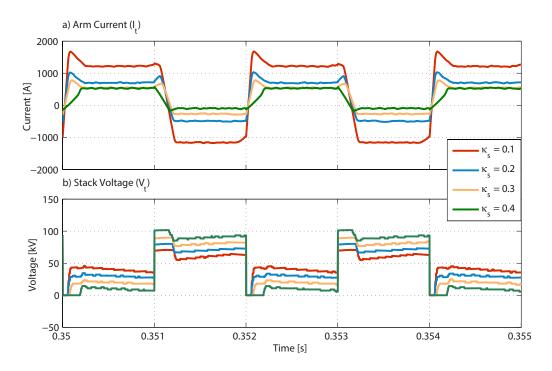

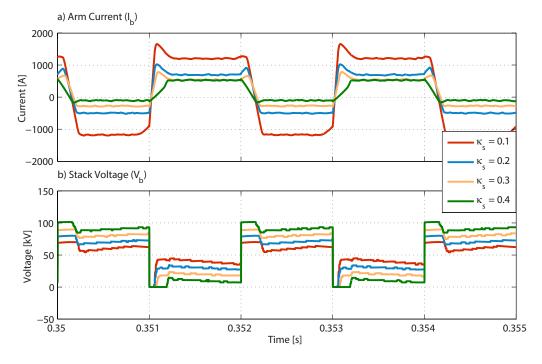

| 7.14 | Arm currents and corresponding stack voltages for top arm for a range of                                                                                                               |

|      | stack transformation-ratios                                                                                                                                                            |

| 7.15 | Arm currents and corresponding stack voltages for bottom arm for a range                                                                                                               |

|      | of stack transformation-ratios                                                                                                                                                         |

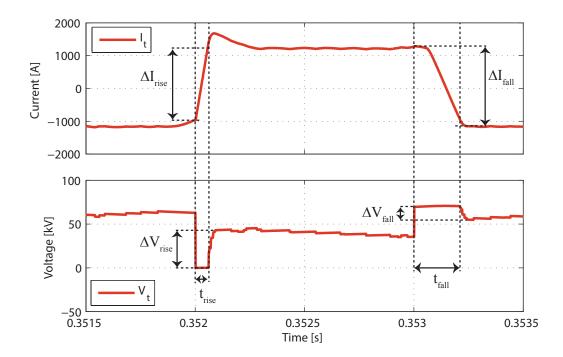

|      | Stack current and voltage illustrating transition times for $\kappa_s = 0.1.$ 205                                                                                                      |

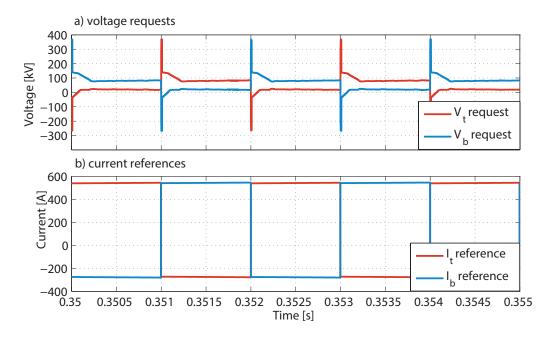

| 7.17 | Requests for stack voltages from the current controller (top) and current references to be tracked (bottom)                                                                            |

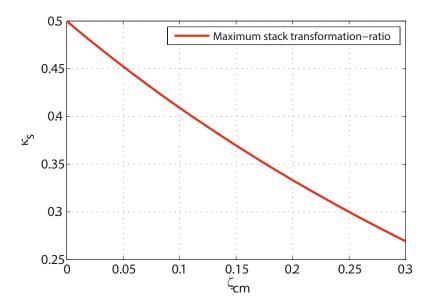

| 7.18 | Maximum stack transformation-ratio possible for varying control voltage margin $(\zeta_{cm})$ , utilising half-bridge cells only                                                       |

|      |                                                                                                                                                                                        |

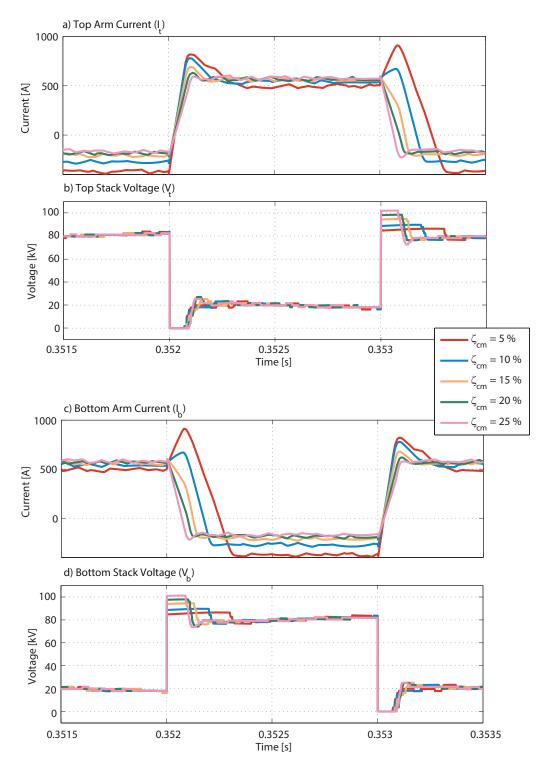

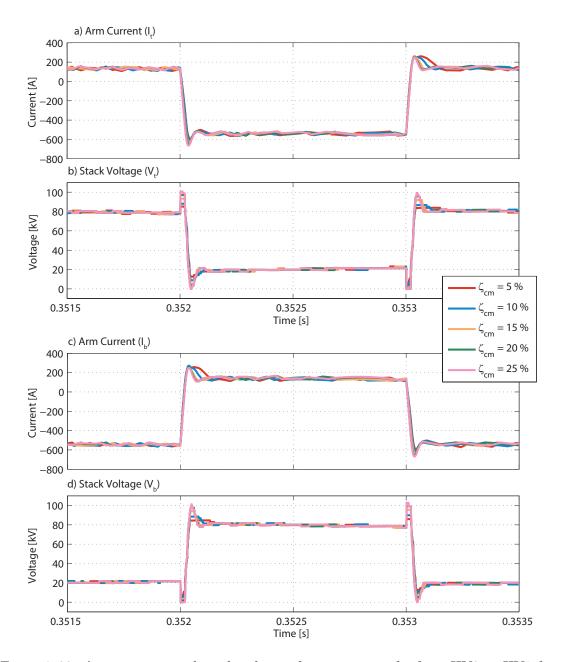

| 7.19 | Arm currents and stack voltages for top and bottom arm with varying $\zeta_{cm}$                                         |

|------|--------------------------------------------------------------------------------------------------------------------------|

|      | for $\kappa_s = 0.3.$                                                                                                    |

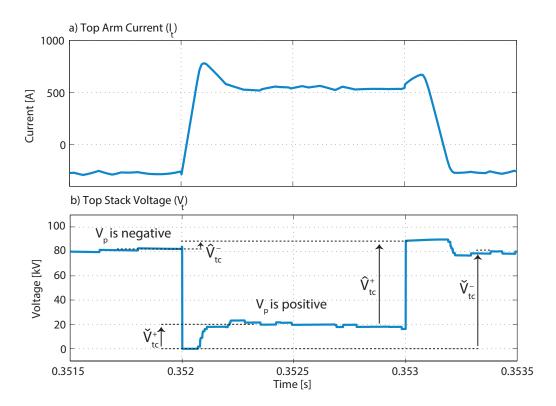

| 7.20 | Arm current and stack voltage to illustrate $\check{V}_{tc}$ and $\hat{V}_{tc}$ , for $\kappa_s = 0.3$ and               |

| 7 91 | $\zeta_{cm} = 0.1.$                                                                                                      |

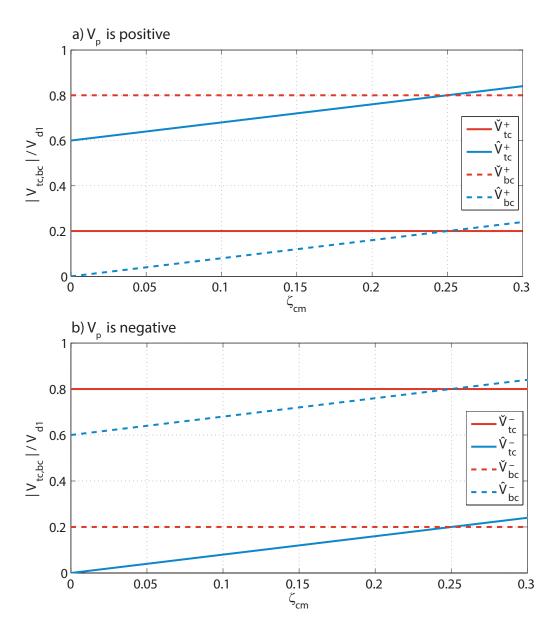

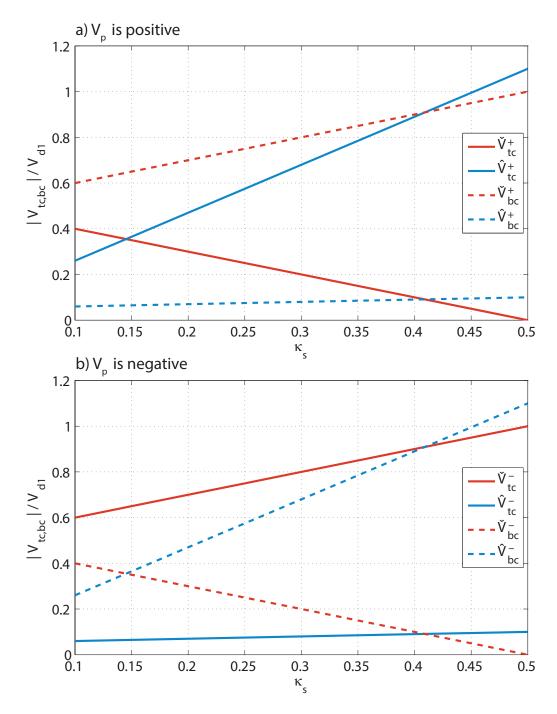

| 1.21 | Normalised maximum and minimum voltage component available in stacks                                                     |

| 7 99 | of cells to control currents, for $\kappa_s = 0.3.$                                                                      |

| 1.22 | Arm currents and stack voltages for power transfer from HV2 to HV1 for a range of control margins, for $\kappa_s = 0.3.$ |

| 7 99 |                                                                                                                          |

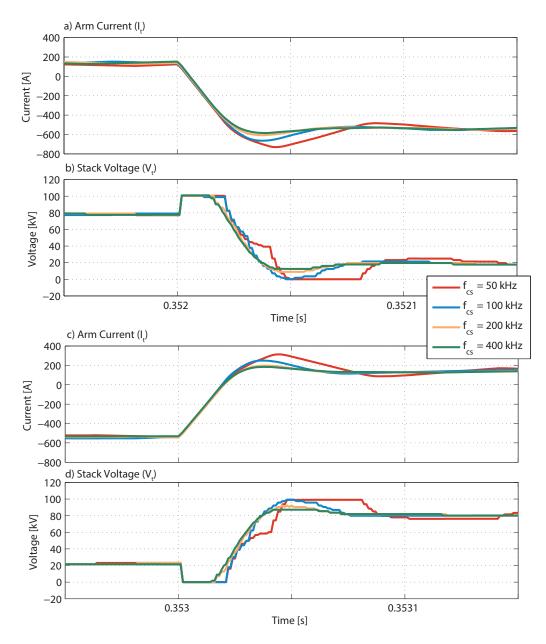

| 1.23 | Current transitions in top arm along with stack voltages for range of con-                                               |

|      | troller sampling frequencies, for a power transfer from HV2 to HV1 and also $\kappa_s = 0.3$ and $\zeta_{cm} = 0.25$     |

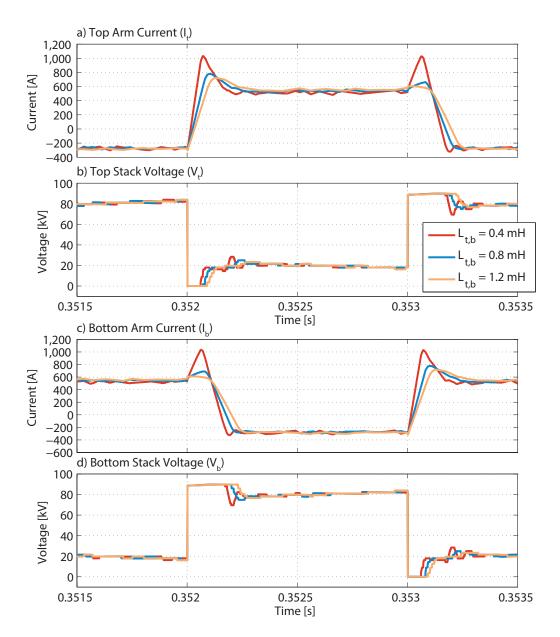

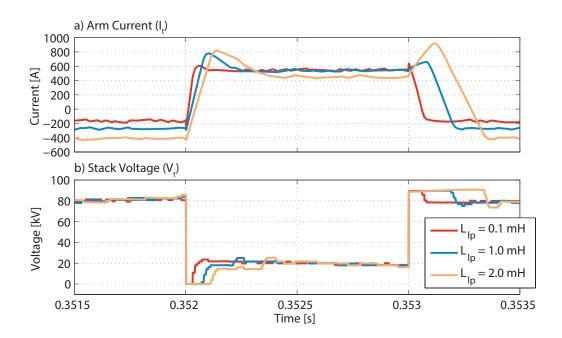

| 7 24 | Arm currents and stack voltages for range of arm inductances, for $\kappa_s = 0.3$ ,                                     |

| 1.27 | $\zeta_{cm}=0.1$ and $L_{lp}=1mH.$                                                                                       |

| 7 25 | Top arm current and stack voltage for range of transformer leakage induct-                                               |

| 1.20 | ances, for $\kappa_s = 0.3$ , $L_{t,b} = 0.8mH$ and $\zeta_{cm} = 0.1$                                                   |

| 7.26 | Voltage limits relevant for current transitions with respect to transformation-                                          |

| 1.20 | ratio $(\kappa_s)$ , for $\zeta_{cm} = 0.1.$                                                                             |

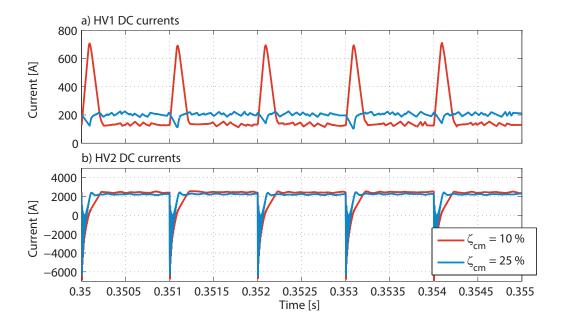

| 7.27 | DC currents for HV1 and HV2 for two control-margins at a transformation-                                                 |

|      | ratio of 0.3, for a power transfer from HV1 to HV2                                                                       |

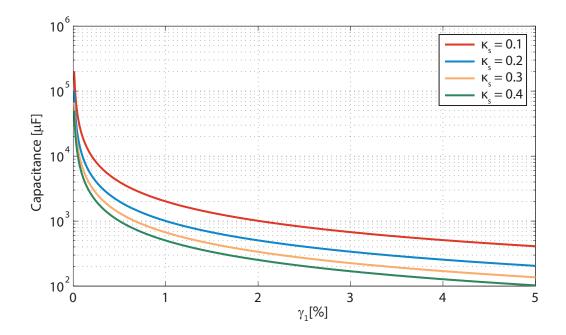

| 7.28 | HV1 DC capacitance as a function of tolerable voltage deviation $(\gamma_1)$ 22-                                         |

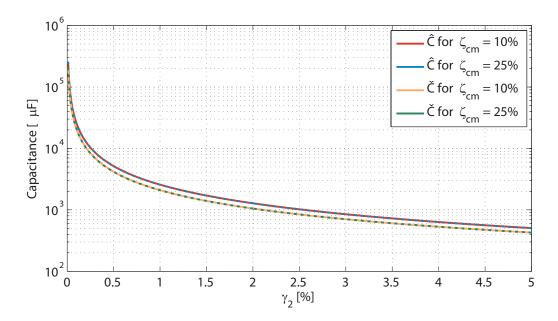

|      | HV2 DC capacitor size for varying ripple margins ( $\gamma_2$ ), for system operating                                    |

|      | with $\zeta_{cm}$ of 10 and 25%                                                                                          |

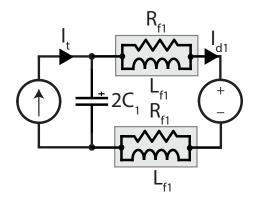

| 7.30 | Low pass filter used on HV1 DC side                                                                                      |

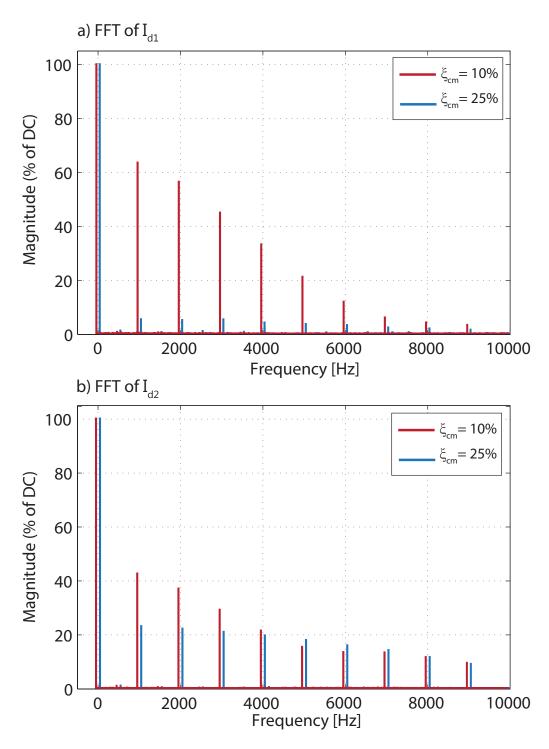

|      | Magnitude of harmonics in unfiltered DC side currents for operation with                                                 |

|      | different control-margins                                                                                                |

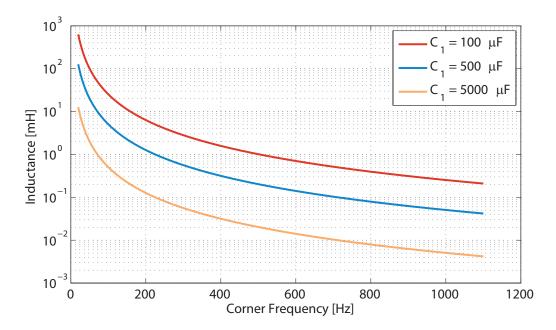

| 7.32 | Required HV1 DC filter inductor size with respect to filter's corner fre-                                                |

|      | quency, for different DC capacitor sizes                                                                                 |

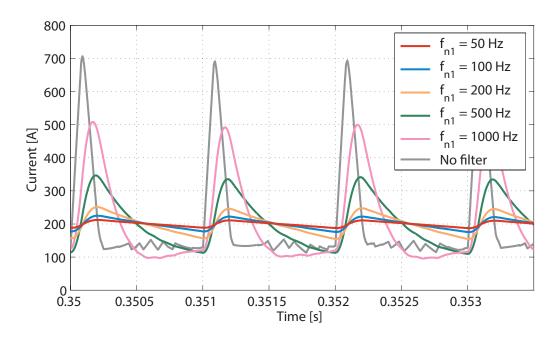

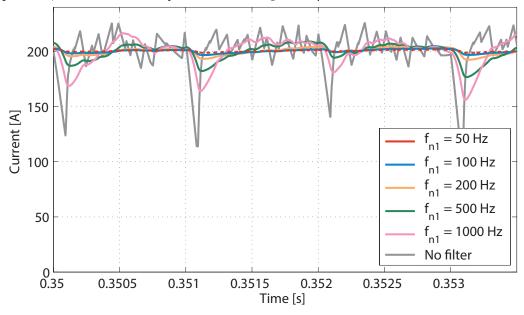

| 7.33 | Effect of filter on HV1 DC current, where $\zeta_{cm}=0.1$ , for varying corner-                                         |

|      | frequencies, for a filter with $Q=0.707$ and $C_1=100\mu F$                                                              |

| 7.34 | Effect of filter on HV1 DC current, where $\zeta_{cm}=0.25$ , for varying corner-                                        |

|      | frequencies, for a filter with $Q=0.707$ and $C_1=100\mu F$                                                              |

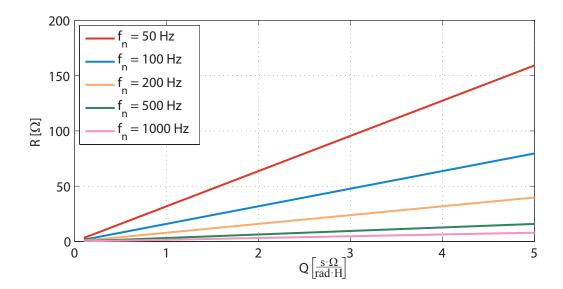

| 7.35 | Filter resistor size for different corner-frequencies with respect to the quality-                                       |

|      | factor (Q), for $C_1 = 100 \mu F$                                                                                        |

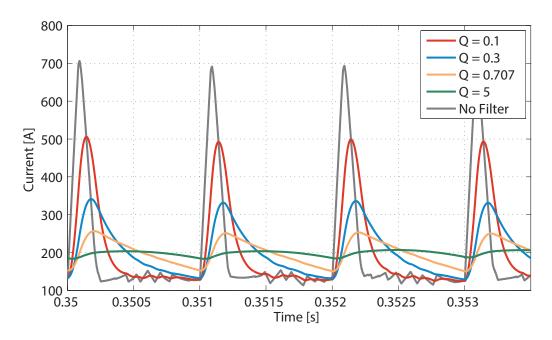

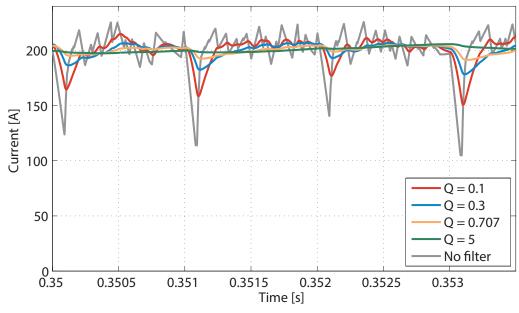

| 7.36 | Effect of filter on HV1 DC current, where $\zeta_{cm}=0.1$ , for different quality-                                      |

|      | factors (Q) with a constant corner-frequency of 220 Hz                                                                   |

| 7.37 | Effect of filter on HV1 DC current, where $\zeta_{cm} = 0.25$ , for different quality-                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------|

|      | factors (Q) with a constant corner-frequency of 220 Hz                                                                                |

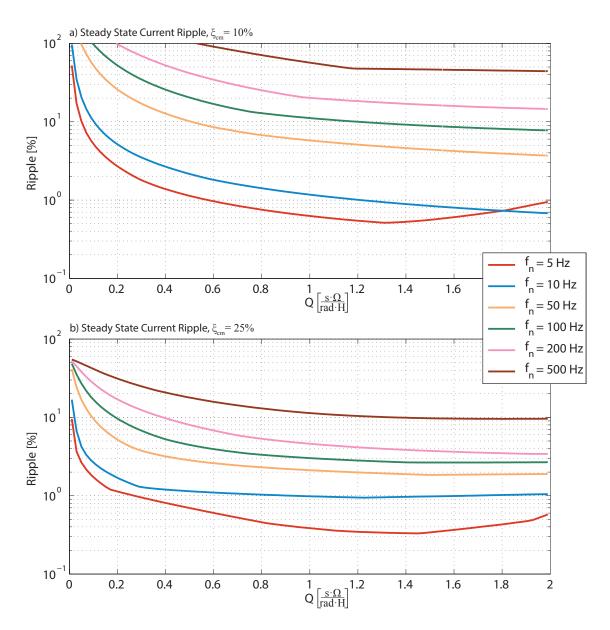

| 7.38 | Graphs showing the steady state ripple of the filtered HV1 DC current for                                                             |

|      | $\zeta_{cm} = 10\%$ , graph a), and 25%, graph b) $(C_1 = 500 \mu F)$                                                                 |

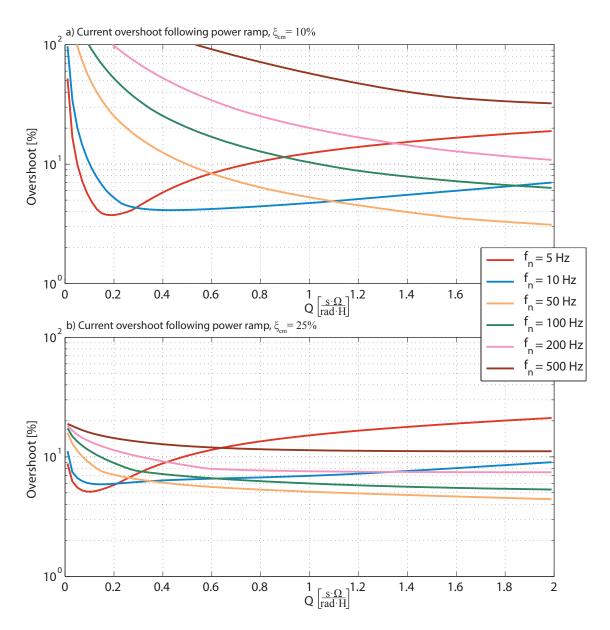

| 7.39 | Graphs showing the overshoot following a power ramp of the filtered HV1                                                               |

|      | DC current for $\zeta_{cm}=10\%$ , graph a), and 25%, graph b) $(C_1=500\mu F)$ 234                                                   |

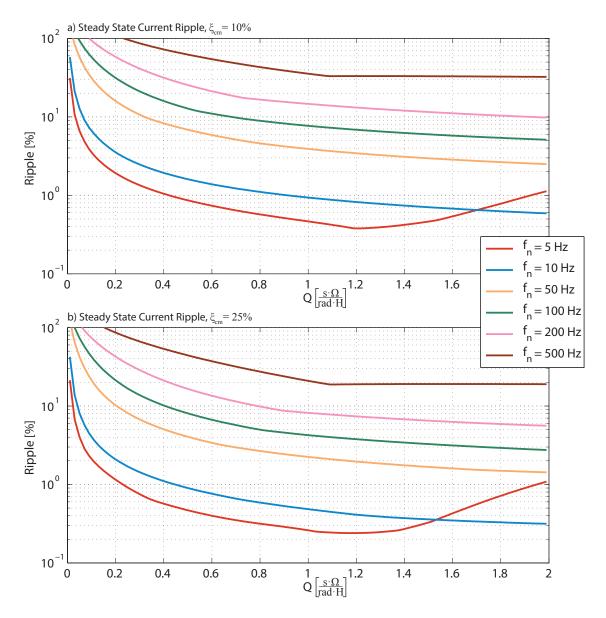

| 7.40 | Graphs showing the steady state ripple of the filtered HV2 DC current for                                                             |

|      | $\zeta_{cm} = 10\%$ , graph a), and 25%, graph b) $(C_2 = 500 \mu F)$                                                                 |

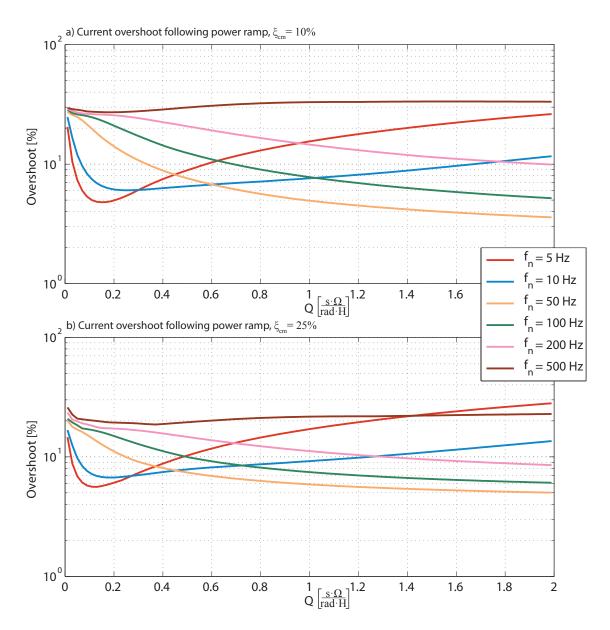

| 7.41 | Graphs showing the overshoot following a power ramp of the filtered HV2                                                               |

|      | DC current for $\zeta_{cm}=10\%$ , graph a), and 25%, graph b) $(C_2=500\mu F)$ 236                                                   |

| 8.1  | Illustration of typical energy deviation in the cell stacks                                                                           |

| 8.2  | Minimum cell capacitance required with varying voltage deviation margin                                                               |

|      | for test system                                                                                                                       |

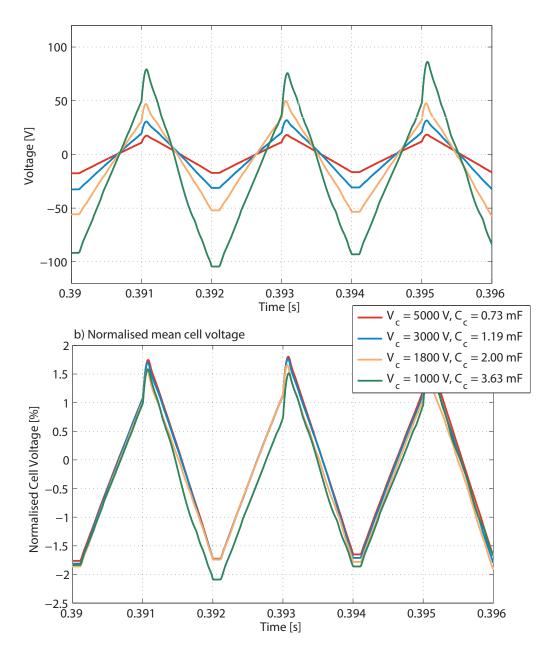

| 8.3  | Mean cell voltages across all cells in the top stack for different cell capacit-                                                      |

|      | ances (system's $\zeta_{cm} = 25\%$ )                                                                                                 |

| 8.4  | Minimum possible stack capacitance for varying transformation-ratio ( $\gamma_c =$                                                    |

|      | 5%)                                                                                                                                   |

| 8.5  | Minimum possible cell capacitance for varying square-wave frequency ( $\gamma_c$ =                                                    |

|      | 5%)                                                                                                                                   |

| 8.6  | Minimum possible cell capacitance for varying nominal cell voltage ( $\gamma_c = 5\%$ ).246                                           |

| 8.7  | Minimum possible total stack capacitance for varying nominal cell voltage                                                             |

|      | $(\gamma_c = 5\%). \dots \dots$ |

| 8.8  | Maximum and minimum voltage of any one cell within top stack for different                                                            |

|      | cell rotation frequencies                                                                                                             |

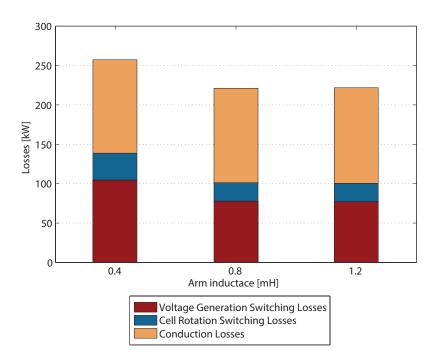

| 8.9  | Losses incurred in cell stacks with varying arm inductance and control mar-                                                           |

|      | gin $(\kappa_s = 0.3 \text{ and } \zeta_{cm} = 25\%)$                                                                                 |

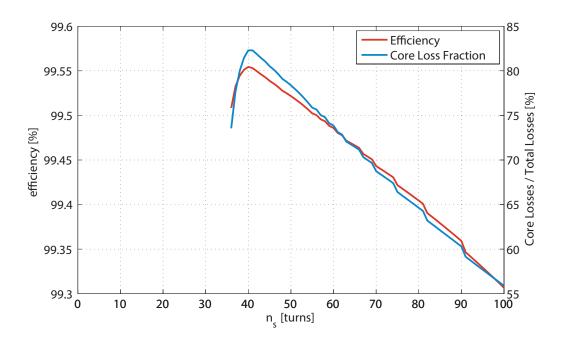

| 8.10 | Transformer efficiency and percentage core losses of total losses with respect                                                        |

|      | to $n_s$ for $w_h = 1m$ and $L_m = 0.95$ H                                                                                            |

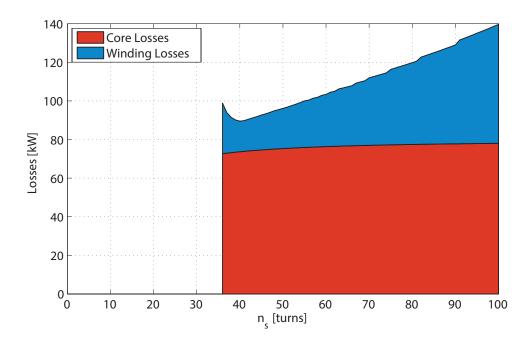

| 8.11 | Core and winding losses with respect to $n_s$ for $w_h=1m$ and $L_m=0.95~\mathrm{H.}$ . 254                                           |

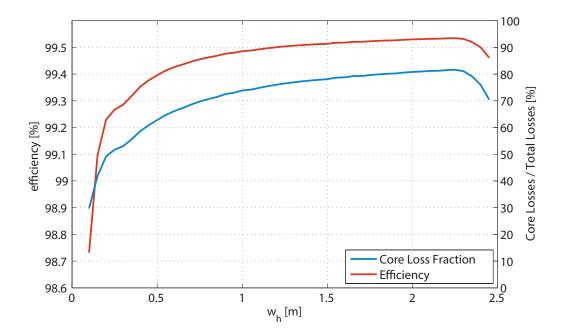

| 8.12 | Transformer efficiency and percentage core losses of total losses with respect                                                        |

|      | to $w_h$ for $n_s = 60$ and $L_m = 0.95H$                                                                                             |

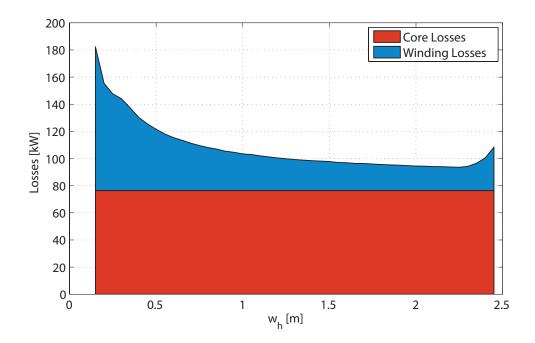

| 8.13 | Core and winding losses with respect to $w_h$ for $n_s=60$ and $L_m=0.95$ H 256                                                       |

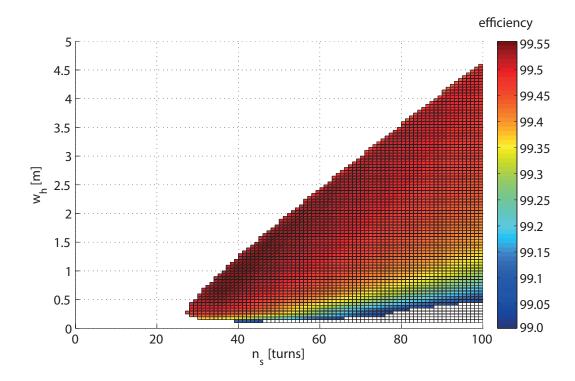

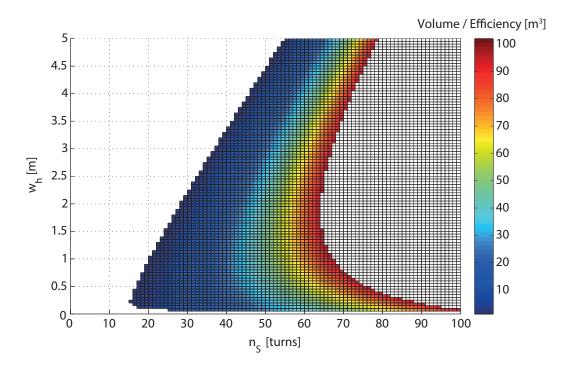

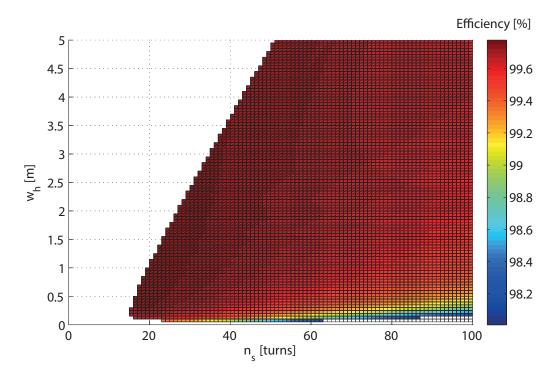

| 8.14 | Transformer efficiency with respect to $w_h$ and $n_s$ for $L_m=0.95$ H 257                                                           |

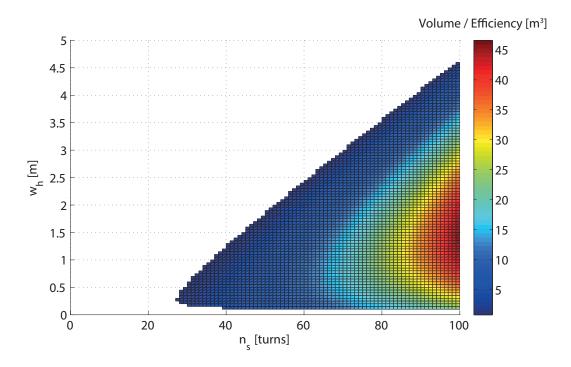

| 8.15 | Normalised transformer volume with respect to $w_h$ and $n_s$ for $L_m=0.95$ H. 258                                                   |

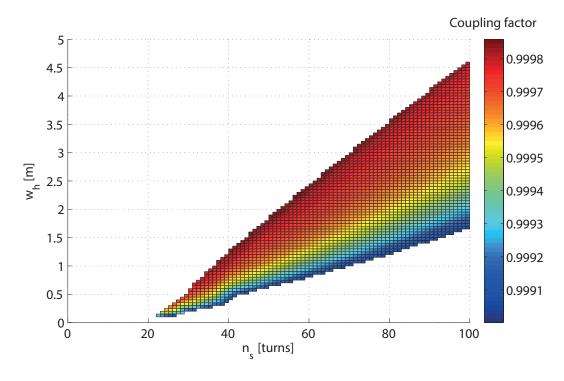

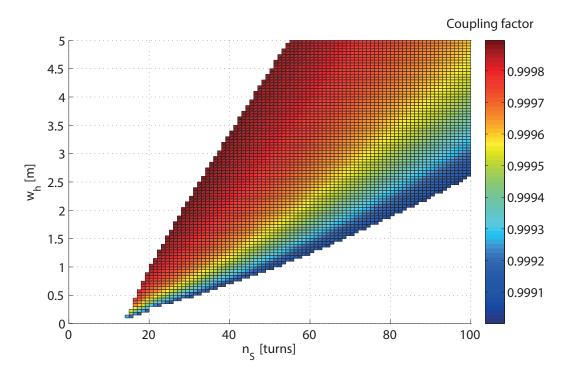

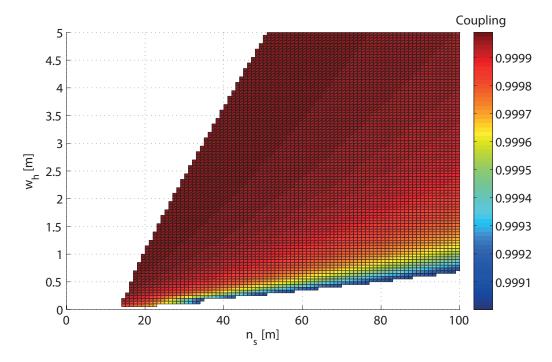

| 8.16 | Coupling factor with respect to $w_h$ and $n_s$ for $L_m = 0.95$ H                                                                    |

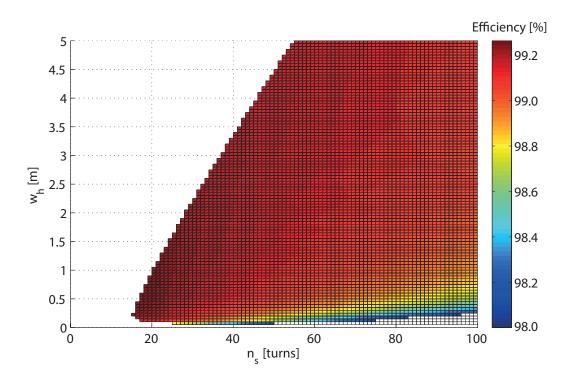

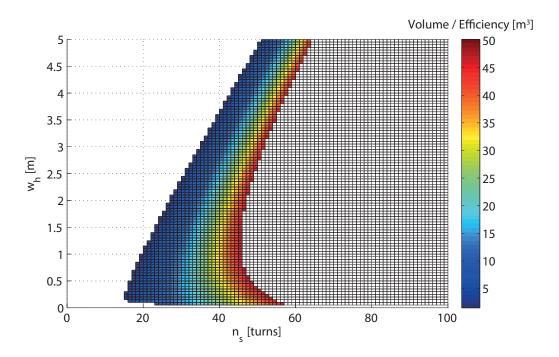

| 8.17 | Transformer efficiency with respect to $w_h$ and $n_s$ for $L_m = 0.48$ H 260                    |

|------|--------------------------------------------------------------------------------------------------|

| 8.18 | Transformer normalised volume with respect to $w_h$ and $n_s$ for $L_m=0.48$ H. 260              |

| 8.19 | Transformer coupling factor with respect to $w_h$ and $n_s$ for $L_m=0.48~\mathrm{H.}$ 261       |

| 8.20 | Transformer efficiency with respect to $w_h$ and $n_s$ for $L_m=4.78~\mathrm{H}$ and core        |

|      | material M.2605SA1                                                                               |

| 8.21 | Transformer normalised volume with respect to $w_h$ and $n_s$ for $L_m = 4.78$                   |

|      | H and core material M.2605SA1                                                                    |

| 8.22 | Transformer coupling factor with respect to $w_h$ and $n_s$ for $L_m = 4.78$ H                   |

|      | and core material M.2605SA1                                                                      |

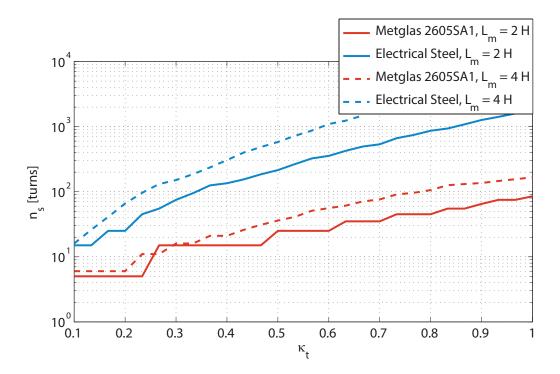

| 8.23 | Number of turns on the secondary for most efficient transformer designs                          |

|      | with varying step-ratio                                                                          |

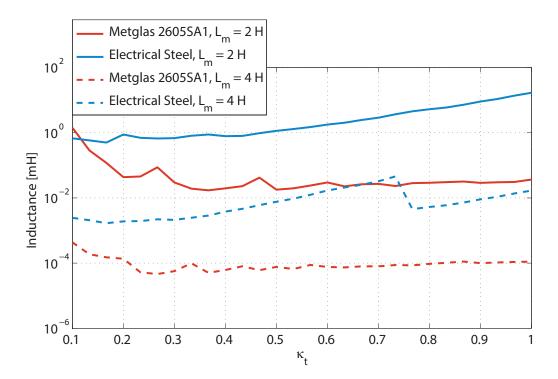

| 8.24 | Leakage inductance referred to primary for most efficient transformer designs                    |

|      | with varying step-ratio                                                                          |

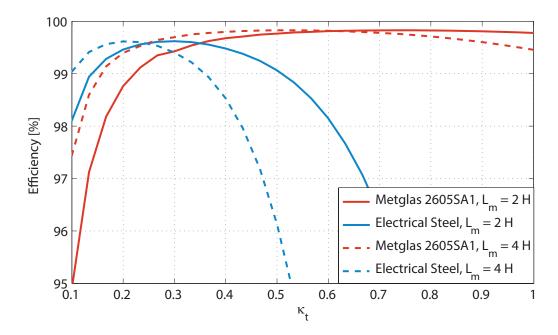

| 8.25 | Efficiencies for transformer designs with varying step-ratio                                     |

| 8.26 | Losses for transformer designs with varying step-ratio for $L_m = 4H$ 267                        |

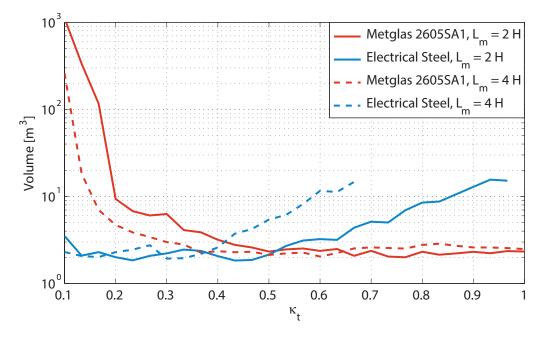

| 8.27 | Transformer volume for most efficient transformer designs with varying                           |

|      | step-ratio                                                                                       |

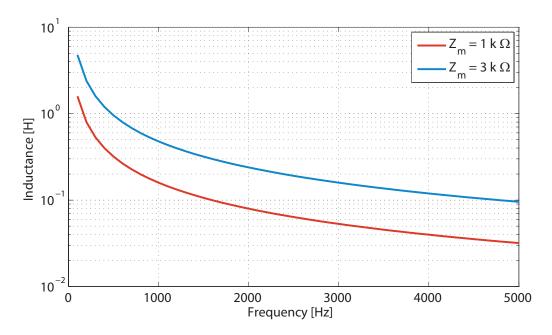

| 8.28 | Magnetising inductance for best efficiency with respect to frequency for                         |

|      | constant magnetising impedance                                                                   |

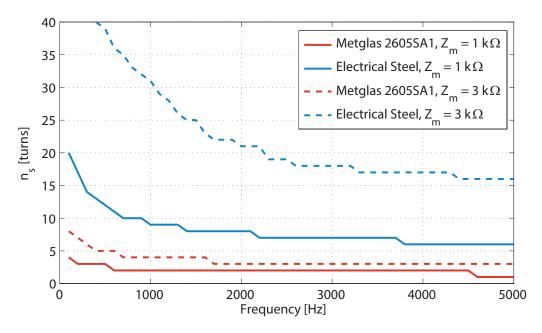

| 8.29 | Number of turns on the secondary for best efficiency with respect to fre-                        |

|      | quency for constant magnetising impedance                                                        |

| 8.30 | Leakage inductance referred to primary for best efficiency with respect to                       |

|      | frequency for constant magnetising impedance                                                     |

| 8.31 | Best transformer efficiency with respect to frequency for constant magnet-                       |

|      | ising impedance                                                                                  |

| 8.32 | Transformer volume for best efficiency with respect to frequency for con-                        |

|      | stant magnetising impedance                                                                      |

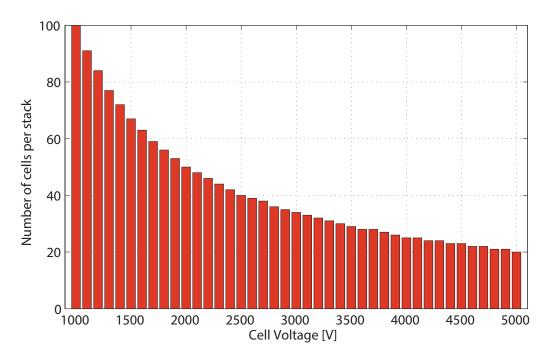

| 8.33 | Number of cells per stack for varying cell voltage, for $\kappa_s=0.3$ and $\zeta_{cm}=25\%.274$ |

| 8.34 | Mean cell voltage across all cells in top stack for different cell voltages, for                 |

|      | $\kappa_s = 0.3$ and $\zeta_{cm} = 25\%$                                                         |

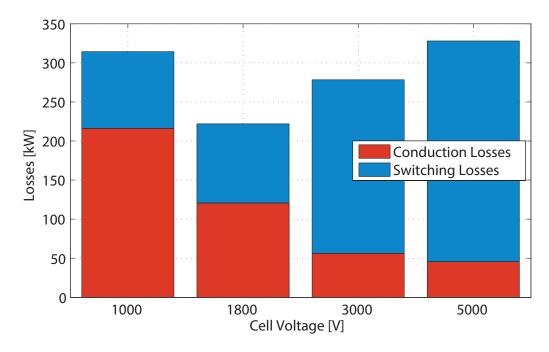

| 8.35 | Stack losses for different cell voltages, for $\kappa_s = 0.3$ and $\zeta_{cm} = 25\%$ 276       |

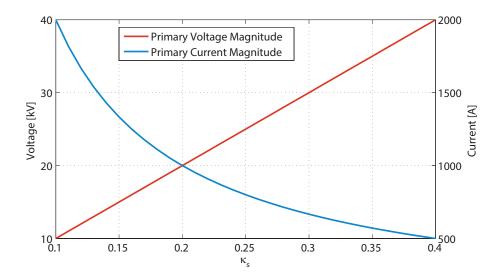

| 8.36 | Primary current and voltages for a range of transformation-ratios $(\kappa_s)$ 277               |

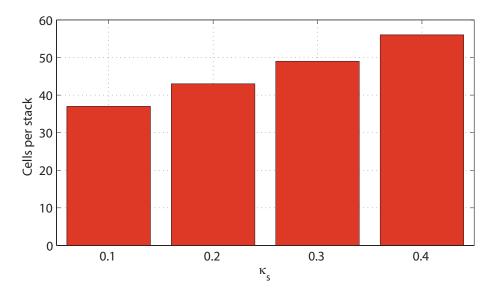

| 8.37 | Number of cells per stack for a cell voltage of 1800 V and $\zeta_{cm}=10\%$ for a               |

|      | range of transformation-ratios $(\kappa_s)$                                                      |

| 8.38 | Losses incurred in the cell stacks for a range of transformation-ratios ( $\kappa_s$ ) 278       |

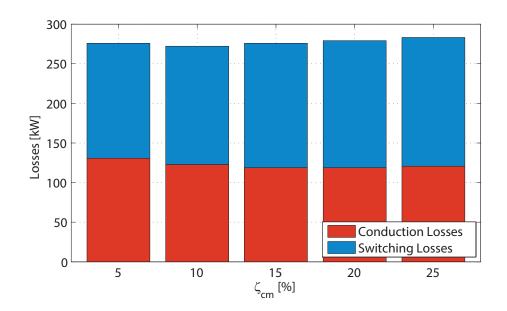

| 8.39 | Losses incurred in cell stacks with varying $\zeta_{cm}$ for $\kappa_s = 0.3.$                   |

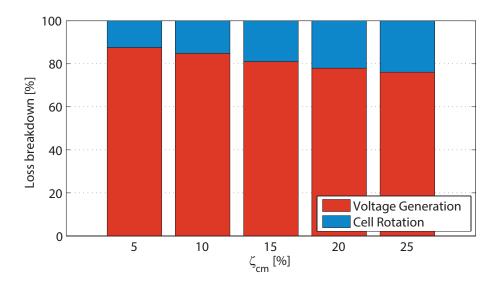

| 8.40 | Switching loss breakdown with varying $\zeta_{cm}$ for $\kappa_s = 0.3.$                                               |

|------|------------------------------------------------------------------------------------------------------------------------|

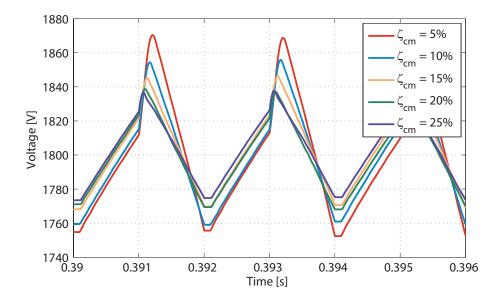

| 8.41 | Mean cell voltage with varying $\zeta_{cm}$ for $\kappa_s = 0.3$                                                       |

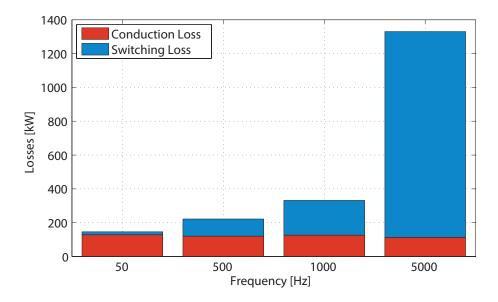

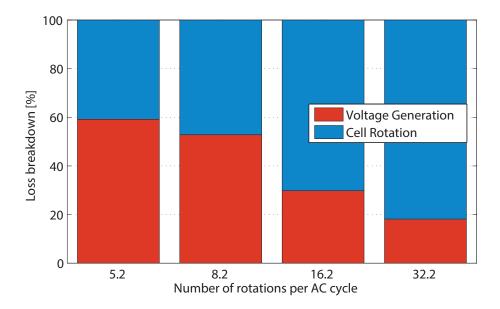

| 8.42 | Losses incurred in the cell stacks for a range of AC frequencies 281                                                   |

| 8.43 | Split of switching losses in the cell stacks for a range of AC frequencies. $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ |

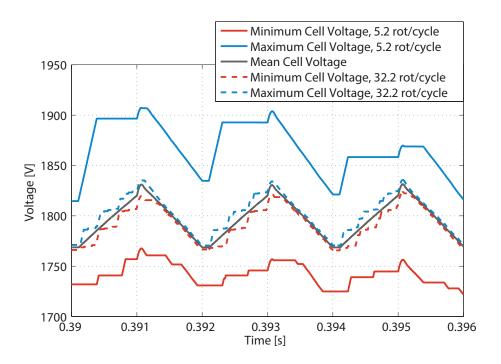

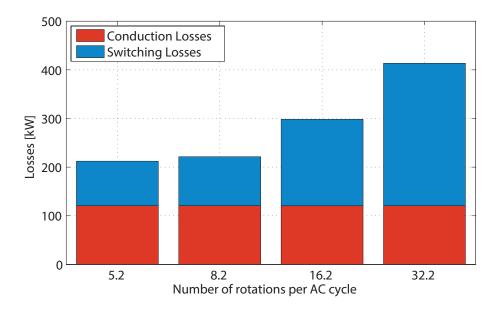

| 8.44 | Cell stack losses for different cell rotation frequencies                                                              |

| 8.45 | Cell stack losses for different cell rotation frequencies                                                              |

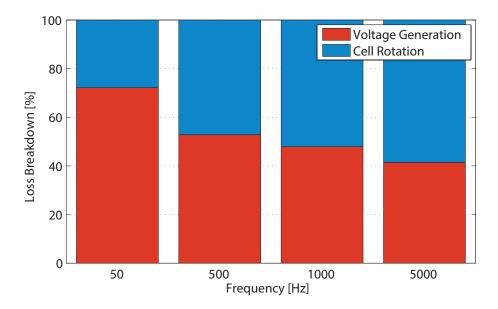

| 8.46 | Loss breakdown for different cell rotation frequencies                                                                 |

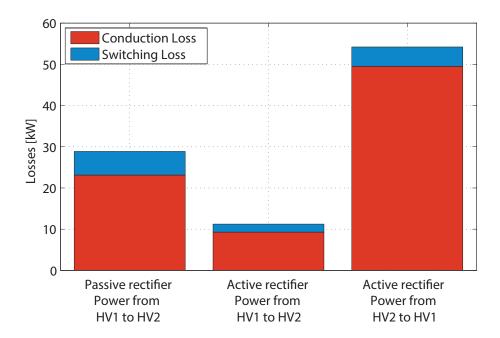

| 8.47 | Rectifier losses for passive and active (for latter in both power flow directions). 285                                |

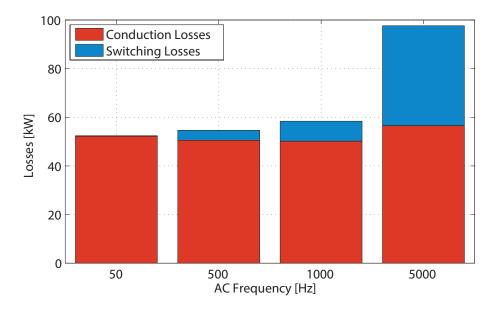

| 8.48 | Rectifier losses with respect to AC frequency                                                                          |

|      |                                                                                                                        |

| 9.1  | Direct-coupled DC/DC converter circuits presented                                                                      |

| 9.2  | Transformer-coupled DC/DC converter circuits presented 295                                                             |

| A.1  | Flowchart illustrating transformer design algorithm                                                                    |

|      |                                                                                                                        |

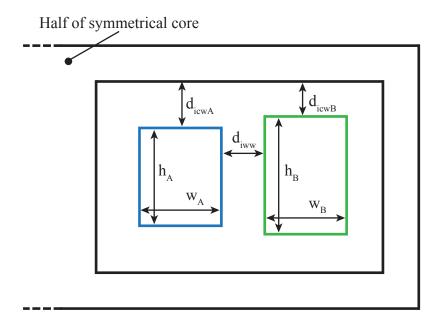

| A.2  | Shell core design and dimension as used in core design algorithm 305                                                   |

| A.3  | Illustration of the winding arrangement                                                                                |

| A.4  | Winding dimensions                                                                                                     |

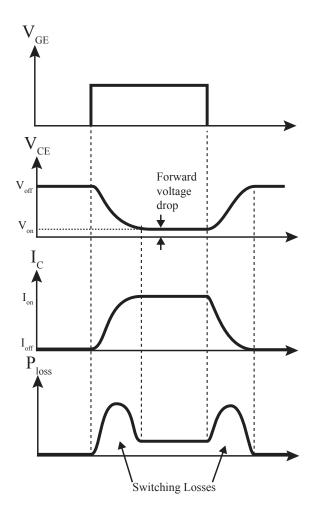

| B.1  | Realistic current and voltage behaviour in a switching device                                                          |

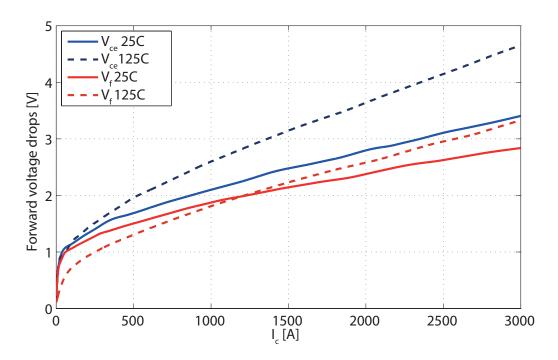

| B.2  | Forward voltage drops of IGBT and anti-parallel diode for Mitsubishi CM1500HG66R                                       |

| D.∠  |                                                                                                                        |

|      | device                                                                                                                 |

|      |                                                                                                                        |

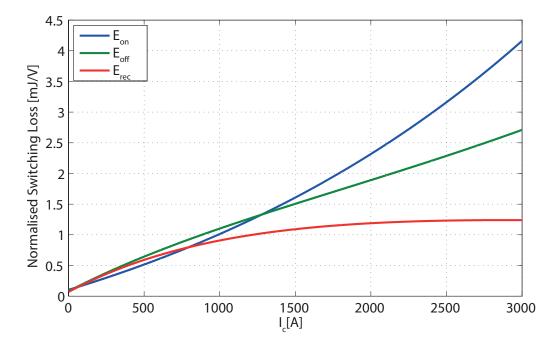

| B.3  | Switching energy loss of IGBT and anti-parallel diode Mitsubishi CM1500HG66R                                           |

| B.3  | Switching energy loss of IGBT and anti-parallel diode Mitsubishi CM1500HG66R device                                    |

|      | -                                                                                                                      |

## List of Tables

| 3.1  | AC voltages of particular interest in test system                                                                                                                                       | 77 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | F2F direct coupled test system parameters                                                                                                                                               | 78 |

| 3.3  | Cell capacitances used in simulations for different AC voltages for $\gamma_c = 10\%$ .                                                                                                 | 86 |

| 3.4  | Voltage deviation of mean cell voltage for F2F using MMCs                                                                                                                               | 87 |

| 3.5  | Voltage deviation of mean cell voltage for F2F using AACs                                                                                                                               | 87 |

| 3.6  | Error between measured and designed for cell voltage deviation in F2F using                                                                                                             |    |

|      | MMCs                                                                                                                                                                                    | 88 |

| 3.7  | Error between measured and designed for cell voltage deviation in F2F using                                                                                                             |    |

|      | AACs                                                                                                                                                                                    | 88 |

| 3.8  | Number of devices in HV2 AAC at an AC voltage of 19.1 kV for different                                                                                                                  |    |

|      | overlap periods                                                                                                                                                                         | 03 |

| 3.9  | Number of devices in HV1 AAC at an AC voltage of $31.8~\mathrm{kV}$ for different                                                                                                       |    |

|      | overlap periods                                                                                                                                                                         | 03 |

| 3.10 | Effective series resistance of arm inductors in MMCs                                                                                                                                    | 07 |

| 3.11 | Effective series resistance of arm inductors in AACs                                                                                                                                    | 07 |

| 3.12 | Summary of the MMC F2F direct-coupled system performance measures. $$ . $1$                                                                                                             | 09 |

| 3.13 | Summary of the AAC F2F direct-coupled system performance measures $1$                                                                                                                   | 09 |

| 4.1  | F2F transformer-coupled system variants to minimise losses or phase capa-                                                                                                               |    |

|      | citance                                                                                                                                                                                 | 21 |

| 4.2  | Transformer losses and dimensions for $\hat{I}_m = 0.01 \hat{I}_{\phi 2}$                                                                                                               | 25 |

| 4.3  | Transformer losses and dimensions for $\hat{I}_m = 0.005 \hat{I}_{\phi 2} \dots $ | 25 |

| 4.4  | Summary of the MMC F2F transformer-coupled system performance meas-                                                                                                                     |    |

|      | ures                                                                                                                                                                                    | 26 |

| 4.5  | Summary of the AAC F2F transformer-coupled system performance measures. $1$                                                                                                             | 26 |

| 5.1  | AC voltages used in F2F system investigated at 500 Hz operation 1                                                                                                                       | 28 |

| 5.2 | Transformer characteristics at 50 and 500 Hz using electrical steel as core                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

|     | material for winding voltages of 25:15 kV                                                                                                         |

| 5.3 | Summary of the MMC F2F direct-coupled system performance measures at                                                                              |

|     | $\hat{V}_{AC} = 15 \text{ kV.} \dots \dots$ |

| 5.4 | Summary of the AAC F2F direct-coupled system performance measures at                                                                              |

|     | $\hat{V}_{AC} = 25 \text{ kV.} \dots \dots$ |

| 5.5 | Summary of the MMC F2F transformer-coupled system performance meas-                                                                               |

|     | ures at winding voltages of 25:15 kV                                                                                                              |

| 5.6 | Summary of the AAC F2F transformer-coupled system performance meas-                                                                               |

|     | ures at winding voltages of 25:15 kV                                                                                                              |

| 7.1 | System parameters used in Simulation of square-wave modular DC/DC test                                                                            |

|     | system                                                                                                                                            |

| 7.2 | Voltage limits relevant for current transitions depending on primary voltage. 211                                                                 |

| 8.1 | Voltage deviations of cells for different cell capacitances                                                                                       |

| 8.2 | Arm inductor sizes and losses                                                                                                                     |

| 8.3 | Filter sizes and losses                                                                                                                           |

| 8.4 | Inductor sizes and losses, current density $(d_{It})$ of 0.5 $MAm^{-2}$                                                                           |

| 8.5 | Test transformer input parameters                                                                                                                 |

| 8.6 | Switching devices used for different cell voltages                                                                                                |

| 8.7 | Cell capacitances and voltages                                                                                                                    |

| 8.8 | Switching losses with respect to frequency                                                                                                        |

| 8.9 | Summary of the losses in the modular square-wave DC/DC operated at $500$                                                                          |

|     | Hz, $\zeta_{cm}=25\%$ and step-ratio of 10:1                                                                                                      |

| A.1 | List of variables for design of transformer                                                                                                       |

| A.1 | List of variables for design of transformer                                                                                                       |

| A.1 | List of variables for design of transformer                                                                                                       |

| A.1 | List of variables for design of transformer                                                                                                       |

| A.2 | List of values used for constants                                                                                                                 |

## **Symbols**

#### Converter quantities for Chapters 3 to 5

$V_{d1,d2}$  DC link voltages

$V_{AC}$  AC voltage

$V_{\phi}$  Converter AC voltage

$V_{st}, V_{sb}$  Voltage across top (t) or bottom (b) stack of cells

$V_{dt}, V_{db}$  Voltage across top (t) or bottom (b) director-switch

$V_c$  Nominal Cell voltage

$\hat{V}_{xx}$  Voltage magnitude

$\Delta V_c^{+,-}$  Voltage deviation above (+) or below (-) nominal cell voltage

$U_t, U_b$  Terminal voltage of inductive network relative to ground

$I_{\phi}$  Converter AC current

$I_{t,b}$  Top (t) or bottom (b) arm current

$I_{d1}, I_{d2}$  DC link current

$I_v$  Vertical energy balancing current

$I_{\Re}$  Real part of complex current I

$I_{\Im}$  Imaginary part of complex current I

$E_{st}, E_{sb}$  Energy drift of top (t) or bottom (b) stack over one cycle

$E_{stx}$  Energy drift in top stack due to current x over one cycle

$E_{cell}$  Energy stored in cell capacitor

$E_{s0}$  Nominal energy stored in stack of cells

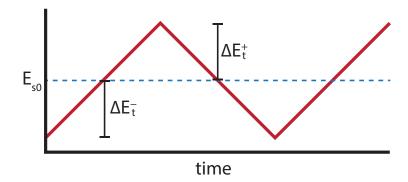

$\Delta E_s^{+,-}$  Energy deviation in stack above (+) or below (-)  $E_{s0}$

$\check{E}_s$  Minimum stored energy in stack

$C_c$  Cell capacitance

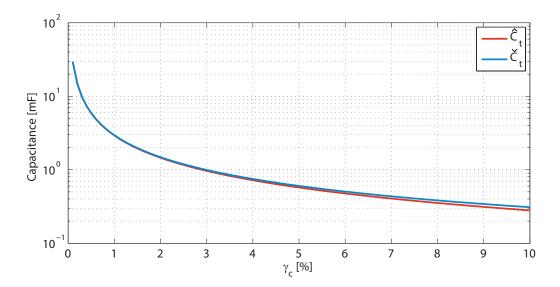

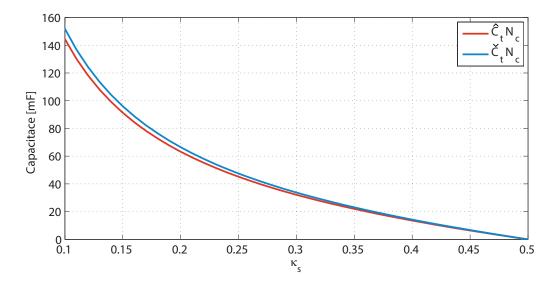

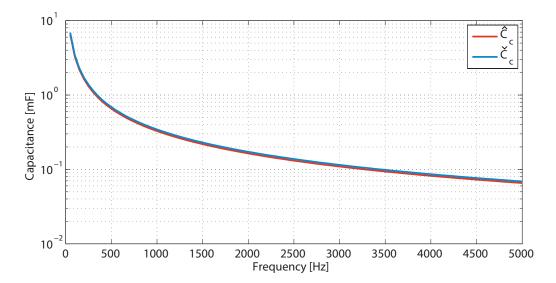

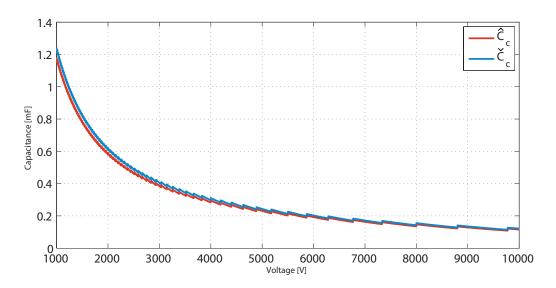

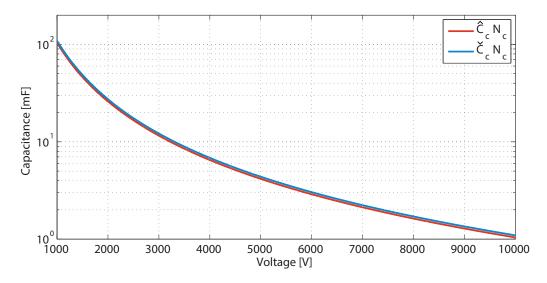

$\hat{C}_c$  Minimum cell capacitance to ensure  $gamma_c$  for  $\hat{E}_s$

$\check{C}_c$  Minimum cell capacitance to ensure  $gamma_c$  for  $\check{E}_s$

$L_{t,b}$  Top (t) or bottom (b) arm inductance

$R_{t,b}$  Effective resistance of arm inductance

$N_c$  Number of cells

$N_d$  Number of director-switches

$P_{AC}$  Active AC power

$Q_{AC}$  Reactive AC power

$S_{\phi}$  Apparent power rating on converter AC side

$f_{AC}$  AC frequency

$\alpha$  Phase angle difference between  $I_{\phi}$  and  $V_{AC}$

$\delta$  Phase angle difference between  $V_{\phi}$  and  $V_{AC}$

$\omega_0$  Natural frequency

$\epsilon$  overlap period

$\gamma_c$  Voltage deviation margin relative to nominal cell voltage

#### Converter quantities for Chapters 6 to 8

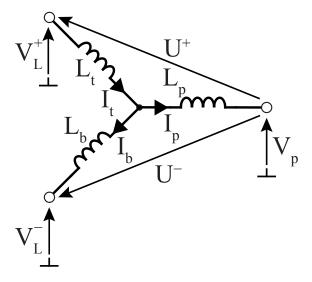

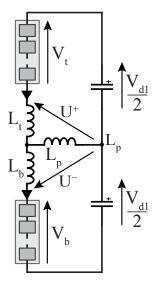

$V_{a,b}^{+,-}, V_{o,i}^{+,-}, V_{t,b}$  Top (+ or t) and bottom (- or b) stack voltages for different stacks

$V_e$  AC balancing voltage

$V_L^{+,-}$  Terminal voltages of inductive network

$V_{tv}, V_{bv}$  Stack voltage required to generate AC voltage

$V_{tc}, V_{bc}$  Stack voltage available to control current

$U^{+,-}$  Voltage between terminals of inductve network

$I_{a,b}^{+,-}, I_{o,i}^{+,-}, I_{t,b}$  Top (+ or t) and bottom (- or b) stack current for different stacks

$I^{+,-}$  Loop currents

$I_e$  Circulating Ac balancing current

$E_{a,b}^{+,-}, E_{c,i}^{+,-}, E_{t,b}$  Top (+ or t) and bottom (- or b) stack energy drifts for different stacks

$E_{\Sigma}$  Sum of absolute stack energy drifts

$E^{+,-}, E_{a,b}$  Energy drift due to loop currents

$E_{01}$  Energy drawn from HV1 link per cycle

$E_{\alpha i}^{+}, E_{\alpha i}^{-}$  Top (+) and bottom (-) stack energy mismatch

$E_c$  Nominal energy in DC link capacitor

$E_{s0}$  Nominal energy stored in stack

$\Delta E_{t,b}^{+,-}$  — Minimum (-) and maximum (+) energy deviation away from  $E_{s0}$

$P_1$  power from HV1 link

$S_{a,b}^{+,-}, S_{o,i}^{+,-}, S_{t,b}$  Apparent power rating of stack

$S_{\Sigma}$  Total apparent power rating of all stacks in converter

$L_{a,b}^{+,-}, L_{o,i}^{+,-}, L_{t,b}$  Arm inductance

$R_f, L_f, C_1$  Passive DC filter components

Q Quality factor of filter

$f_n$  Corner frequency of filter

$f_{AC}$  AC frequency

$\alpha, \beta$  Loop current scalars

$\epsilon$  Energy balancing current scalar

$\lambda$  Duty cycle of  $V_e$

$\kappa$  Converter step-ratio

$\kappa_s$  Transformation-ratio of stacks

$\kappa_t$  Step-ratio of transformer

$\zeta_{cm}$  Voltage control margin

$\gamma_{1,2}$  Voltage rippled of DC side capacitors

$\gamma_c$  Voltage rippled of cell capacitors

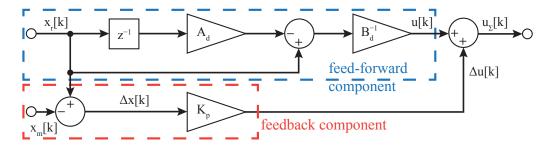

#### Controller quantities

$A, B, M_u, M_L$  State-space matrices

$A_d, B_d$  Discretised state-space matrices

J Cost function of LQR

Q, R Cost matrices of LQR

$Q_{50}, Q_0$  Quality factors of second-order filters

$T_s$  Simulation time-step

$f_{cs}$  Controller sampling frequency

$k_{50}, k_0$  Gains for second-order filters

#### Transformer quantities

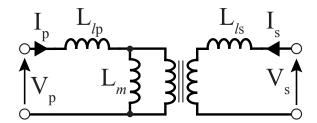

$V_{p,s}$  Primary or secondary voltage

$V_m$  Magnetising voltage

$U_{\ell}$  Voltage across leakage inductance

$I_{p,s}$  Primary or secondary current

$I_m$  Magnetising current

I', V' Referred current or voltage

$L_m$  Magnetising inductance

$L_{1-2,1-2}$  Mutual inductance terms

$L_{\ell}$  Leakage inductance

Z Complex impedance

B Flux density

$\Phi$  Flux

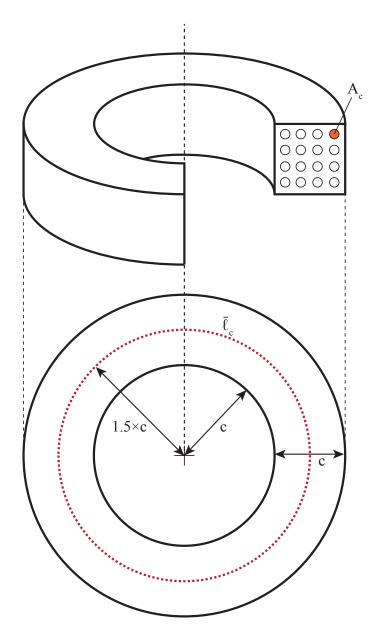

$A_c$  Cross-sectional area of core

$P_t$  Active power rating of transformer

$P_{core,windings}$  Losses in core or windings

$n_{1,2}, n_{p,s}$  Number of turns in (primary or secondary) windings

$n_e$  Ratio of winding turns

$k_t$  Coupling factor

$w_h$  Winding height

$\ell_m$  Mean magnetic path length

$\mu$  Permeability

$\eta_t$  transformer efficiency

$v_t$  Transformer volume

$\tilde{v}_t$  Normalised transformer volume

### Chapter 1

## Introduction

E lectricty is the most refined and valuable form of energy in today's world. To allow widespread access to electricity, a transmission network on an awesome scale has been built over the last century. At the beginning this network was fed by a fleet of mainly coal, later also oil and gas fired generators (referred to as conventional generation). These forms of electricity generation dominate the mix to this day.

In a move to wean ourselves off the raw materials that feed this conventional generation and reduce our carbon dioxide emissions, nuclear and renewable energy sources (RES) have been developed. The potential of some RES has been exploited for a long time, as is the case, for example, with hydro power. Large dam projects, such as the Three Gorges Dam, with a combined generating capacity of 22.4 GW [2], can take phenomenal scales. Some countries, like Norway and Brazil, generate most of their electricity demand using hydro power alone.

This option is, however, not feasible for the majority of countries. Thus alternative RES have been developed, particularly solar and wind. The scale of wind farms in the North Sea has been steadily rising over the last few years, as larger and more numerous turbines are erected further off-shore. The development of off-shore wind generation in the North Sea is estimated to reach 40 GW by 2020 and 150 GW by 2030 [3]. As more windfarms are commissioned, they move ever further away from the shore. Today, projects like BorWin1, are a distance of 125 km away from the shore line [4].

This illustrates the big difference between conventional generation and RES: conventional generators could be placed near the load centres and the fuel be brought to them. This is not the case with RES. They are inherently inflexible and not only require to be built where the resources are, but can also be intermittent in generating.

As the RES content of the European, and indeed world-wide, electricity mix increases,

the transmission system will have to be upgraded as well. Today the network is designed to efficiently transport electricity from the power plants to the load centres. As this has mainly been conventional generation, this tended to be a uni-directional, or trickle-down, system. A more interconnected system, capable of connecting distant RES and allowing more flexible power flows has to be build to accommodate the the new form of generation and ensure supply security.

Regional powers have recognised this and have promoted plans such as the European supergrid [5]. Transmission technology called High Voltage Direct Current (HVDC) transmission, is being advocated to reinforce the existing AC interconnected grid, as well as create new long distance interconnections, such as NorNed, the Norway - Netherlands interconnector [6].

HVDC technology has been around for over 50 years, but its development has recently experienced a surge. New HVDC technologies allow the construction and operation of large multi-terminal DC networks [7]. This does not however mean that all components of a potential future DC network are presently commercially available or even fully developed. One crucial component which, if the development of AC networks is anything to go by, will play an important role, is the DC/DC converter - or the DC equivalent of the transformer.

#### 1.1 Problem Statement and Thesis Outline

This thesis investigates potential DC/DC converters, using the latest HVDC technology, suitable for a range of applications. In particular two approaches to the design of a DC/DC converter are taken: first, an approach which utilises existing and reliable technologies to achieve the required goal. This may be advantageous if a DC/DC converter is to be commissioned in the next ten years, as research and development times have in the past run into several years for similar HVDC DC/AC converters. The second approach takes a longer view: it investigates purpose designed DC/DC circuits, which will take longer to gain viability and commercial acceptance.

The work focuses on better understanding the design parameters of a number of different DC/DC converters. The losses and the converter volume tend to be the most important features of a converter, as they affect the lifetime and initial capital costs. Typically, when designing a converter, internal parameters can be varied to achieve trade-offs to affect the losses or volume.

In particular the chapters of this work cover the following work:

#### Chapter 2

This chapter introduces the basics of HVDC technology. It also provides a review of the existing literature on DC/DC converters and their suitability for HVDC applications.

#### Chapter 3

A front-to-front (F2F) arrangement of two DC/AC converters, connected through a common AC voltage, is presented. Important background information to the method of operation of the two Voltage Source Converters (VSCs) considered for such a circuit topology is provided. A circuit description of, as well as control mechanism for the direct-coupled F2F topology is presented. As both converters share a common AC voltage, but connect to different DC potentials, the choice of AC voltage magnitude has a big impact on the performance of each converter. The effects of this on the overall system efficiency and volume are explored in detail.

#### Chapter 4

The F2F arrangement can be supplemented with galvanic isolation on the internal AC connection. This allows each converter to operate with a different AC voltage, which can potentially improve the system performance. This chapter presents the modified circuit and the relevant changes to the controller of the direct-coupled system. It also investigates how the system performance is affected by the transformer.

#### Chapter 5

Both F2F topologies presented can utilise higher than 50 Hz frequencies in their AC link. The operation and effect on the direct-, as well as the transformer-coupled systems, are investigated at 500 Hz operation.

#### Chapter 6

Two fundamental operating methods for purpose designed cell based DC/DC converters are presented. Two circuits for each method have also been explored in some detail. The power capacity ratio has been used to compare all four converters with each other. This measure indicates the ratio of the installed power rating of the power electronics relative to the transferred power.

#### Chapter 7

One of the four converters presented in chapter six, the shunt connected primary

converter, is analysed in more detail and control mechanisms are presented. Crucial operational design parameters are investigated, such as the number of cells required.

#### Chapter 8

The design trade-offs of the individual components of the shunt connected primary converter are investigated. The focus in this chapter is on the means to optimise the converter for either losses or volume.

#### 1.2 Author's Publications based on this Work

#### Based on Chapter 3

T. Lüth, M. M. C. Merlin, T. C. Green, C. D. Barker, F. Hassan, R. W. Critchley, R. W. Crookes, K. Dyke, "Performance of a DC/AC/DC VSC System to Interconnect HVDC Systems", 10th IET International Conference on AC and DC Power Transmission, pp.1-6, 2012.

#### Based on Chapter 3